(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6624828号

(P6624828)

(45) 発行日 令和1年12月25日(2019.12.25)

(24) 登録日 令和1年12月6日(2019.12.6)

(51) Int.Cl.

F 1

|              |           |      |         |      |

|--------------|-----------|------|---------|------|

| HO3K 17/06   | (2006.01) | HO3K | 17/06   | 063  |

| HO3K 19/0175 | (2006.01) | HO3K | 19/0175 | 220  |

| HO3K 19/096  | (2006.01) | HO3K | 19/096  | 210  |

| HO1L 29/786  | (2006.01) | HO3K | 19/096  | 230  |

| GO9G 3/20    | (2006.01) | HO1L | 29/78   | 618B |

請求項の数 6 (全 51 頁) 最終頁に続く

(21) 出願番号 特願2015-144674 (P2015-144674)

(22) 出願日 平成27年7月22日 (2015.7.22)

(65) 公開番号 特開2016-29797 (P2016-29797A)

(43) 公開日 平成28年3月3日 (2016.3.3)

審査請求日 平成30年7月20日 (2018.7.20)

(31) 優先権主張番号 特願2014-150532 (P2014-150532)

(32) 優先日 平成26年7月24日 (2014.7.24)

(33) 優先権主張国・地域又は機関

日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 梅崎 敦司

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 工藤 一光

最終頁に続く

(54) 【発明の名称】半導体装置、表示モジュール及び電子機器

## (57) 【特許請求の範囲】

## 【請求項 1】

第1乃至第4のトランジスタを有し、

前記第1のトランジスタのソース又はドレインの一方は、第1の配線と電気的に接続され、

前記第1のトランジスタのソース又はドレインの他方は、第2の配線と電気的に接続され、

前記第2のトランジスタのソース又はドレインの一方は、第3の配線と電気的に接続され、

前記第2のトランジスタのソース又はドレインの他方は、前記第1のトランジスタのゲートと電気的に接続され、 10

前記第3のトランジスタのソース又はドレインの一方は、第4の配線と電気的に接続され、

前記第3のトランジスタのソース又はドレインの他方は、前記第2のトランジスタのゲートと電気的に接続され、

前記第4のトランジスタのソース又はドレインの一方は、第5の配線と電気的に接続され、

前記第4のトランジスタのソース又はドレインの他方は、前記第2のトランジスタのゲートと電気的に接続され、

前記第4のトランジスタのゲートは、前記第1の配線と電気的に接続されることを特徴

10

20

とする半導体装置。

【請求項 2】

第 1 乃至第 4 のトランジスタを有し、

前記第 1 のトランジスタのソース又はドレインの一方は、第 1 の配線と電気的に接続され、

前記第 1 のトランジスタのソース又はドレインの他方は、第 2 の配線と電気的に接続され、

前記第 2 のトランジスタのソース又はドレインの一方は、第 3 の配線と電気的に接続され、

前記第 2 のトランジスタのソース又はドレインの他方は、前記第 1 のトランジスタのゲートと電気的に接続され、10

前記第 3 のトランジスタのソース又はドレインの一方は、前記第 3 の配線と電気的に接続され、

前記第 3 のトランジスタのソース又はドレインの他方は、前記第 2 のトランジスタのゲートと電気的に接続され、

前記第 4 のトランジスタのソース又はドレインの一方は、第 4 の配線と電気的に接続され、

前記第 4 のトランジスタのソース又はドレインの他方は、前記第 2 のトランジスタのゲートと電気的に接続され、

前記第 4 のトランジスタのゲートは、前記第 1 の配線と電気的に接続されることを特徴とする半導体装置。20

【請求項 3】

第 1 乃至第 4 のトランジスタを有し、

前記第 1 のトランジスタのソース又はドレインの一方は、第 1 の配線と電気的に接続され、

前記第 1 のトランジスタのソース又はドレインの他方は、第 2 の配線と電気的に接続され、

前記第 2 のトランジスタのソース又はドレインの一方は、第 3 の配線と電気的に接続され、

前記第 2 のトランジスタのソース又はドレインの他方は、前記第 1 のトランジスタのゲートと電気的に接続され、30

前記第 3 のトランジスタのソース又はドレインの一方は、第 4 の配線と電気的に接続され、

前記第 3 のトランジスタのソース又はドレインの他方は、前記第 2 のトランジスタのゲートと電気的に接続され、

前記第 4 のトランジスタのソース又はドレインの一方は、前記第 3 の配線又は前記第 4 の配線と電気的に接続され、

前記第 4 のトランジスタのソース又はドレインの他方は、前記第 2 のトランジスタのゲートと電気的に接続され、

前記第 4 のトランジスタのゲートは、前記第 1 の配線と電気的に接続されることを特徴とする半導体装置。40

【請求項 4】

請求項 1 乃至請求項 3 のいずれか一項において、

前記第 1 乃至第 4 のトランジスタは、チャネル形成領域に酸化物半導体を有することを特徴とする半導体装置。

【請求項 5】

請求項 1 乃至請求項 4 のいずれか一項に記載の半導体装置と、

FPC と、

を有することを特徴とする表示モジュール。

【請求項 6】

請求項5に記載の表示モジュールと、

アンテナ、操作ボタン又はスピーカと、を有する電子機器。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の一態様は、半導体装置、表示モジュール及び電子機器に関する。

【0002】

なお、本発明の一態様は、上記の技術分野に限定されない。本明細書等で開示する発明の一態様の技術分野は、物、方法、または、製造方法に関するものである。または、本発明の一態様は、プロセス、マシン、マニュファクチャ、または、組成物（コンポジション・オブ・マター）に関するものである。または、本発明の一態様は、半導体装置、表示装置、発光装置、蓄電装置、記憶装置、それらの駆動方法、または、それらの製造方法に関する。

【背景技術】

【0003】

記憶装置、イメージセンサ又は表示装置等の駆動回路に適用することが可能な回路の開発が進められている。特に、同じ極性のトランジスタによって構成される回路の開発が活発に進められている。そのような回路に関する技術が特許文献1に開示されている。

【0004】

特許文献1では、トランジスタのゲートとソースとの間の電位差が徐々に小さくなる。そして、トランジスタのゲートとソースとの間の電位差がトランジスタの閾値電圧と等しくなると、トランジスタがオフになり、回路内部のノードが浮遊状態になる。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2005-050502号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

従来の回路では、トランジスタのゲートとソースとの間の電位差が徐々に小さくなるため、トランジスタのドレイン電流も徐々に小さくなる。そのため、回路内部のノードにおける電位の変化に要する時間が長く、高速に動作することが困難である。また、トランジスタのW/Lを大きくする必要があり、レイアウト面積を小さくすることが困難である。また、信号の立ち上がり時間又は立下り時間を短くすることが困難である。

【0007】

本発明の一態様は、新規の半導体装置を提供することを課題の一とする。または、本発明の一態様は、高速に動作すること又はそれを可能にする構成を提供することを課題の一とする。または、本発明の一態様は、レイアウト面積を縮小すること又はそれを可能にする構成を提供することを課題の一とする。または、本発明の一態様は、駆動電圧を小さくすること又はそれを可能にする構成を提供することを課題の一とする。または、本発明の一態様は、信号の立ち上がり時間又は立下り時間を短くすること又はそれを可能にする構成を提供することを課題の一とする。

【0008】

なお、本発明の一態様は、必ずしも上記の課題の全てを解決する必要はなく、少なくとも一の課題を解決できるものであればよい。また、上記の課題の記載は、他の課題の存在を妨げるものではない。これら以外の課題は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の課題を抽出することが可能である。

【課題を解決するための手段】

【0009】

10

20

30

40

50

本発明の一態様は、第1乃至第4のトランジスタを有する半導体装置である。第1のトランジスタのソース又はドレインの一方は、第1の配線と電気的に接続され、第1のトランジスタのソース又はドレインの他方は、第2の配線と電気的に接続され、第2のトランジスタのソース又はドレインの一方は、第3の配線と電気的に接続され、第2のトランジスタのソース又はドレインの他方は、第1のトランジスタのゲートと電気的に接続され、第3のトランジスタのソース又はドレインの一方は、第4の配線と電気的に接続され、第3のトランジスタのソース又はドレインの他方は、第2のトランジスタのゲートと電気的に接続され、第4のトランジスタのソース又はドレインの一方は、第5の配線と電気的に接続され、第4のトランジスタのソース又はドレインの他方は、第2のトランジスタのゲートと電気的に接続される。

10

#### 【0010】

本発明の一態様は、第1乃至第4のトランジスタを有する半導体装置である。第1のトランジスタのソース又はドレインの一方は、第1の配線と電気的に接続され、第1のトランジスタのソース又はドレインの他方は、第2の配線と電気的に接続され、第2のトランジスタのソース又はドレインの一方は、第3の配線と電気的に接続され、第2のトランジスタのソース又はドレインの他方は、第1のトランジスタのゲートと電気的に接続され、第3のトランジスタのソース又はドレインの一方は、第3の配線と電気的に接続され、第3のトランジスタのソース又はドレインの他方は、第2のトランジスタのゲートと電気的に接続され、第4のトランジスタのソース又はドレインの一方は、第4の配線と電気的に接続され、第4のトランジスタのソース又はドレインの他方は、第2のトランジスタのゲートと電気的に接続される。

20

#### 【0011】

本発明の一態様は、第1乃至第4のトランジスタを有する半導体装置である。第1のトランジスタのソース又はドレインの一方は、第1の配線と電気的に接続され、第1のトランジスタのソース又はドレインの他方は、第2の配線と電気的に接続され、第2のトランジスタのソース又はドレインの一方は、第3の配線と電気的に接続され、第2のトランジスタのソース又はドレインの他方は、第1のトランジスタのゲートと電気的に接続され、第3のトランジスタのソース又はドレインの一方は、第4の配線と電気的に接続され、第3のトランジスタのソース又はドレインの他方は、第2のトランジスタのゲートと電気的に接続され、第4のトランジスタのソース又はドレインの一方は、第3の配線又は第4の配線と電気的に接続され、第4のトランジスタのソース又はドレインの他方は、第2のトランジスタのゲートと電気的に接続される。

30

#### 【0012】

なお、上記本発明の一態様において、第4のトランジスタのゲートは、第1の配線又は第2の配線と接続されてもよい。

#### 【0013】

本発明の一態様は、上記半導体装置と、FPCと、を有する表示モジュールである。

#### 【0014】

本発明の一態様は、上記表示モジュールと、アンテナ、操作ボタン又はスピーカと、を有する電子機器である。

40

#### 【発明の効果】

#### 【0015】

本発明の一態様は、新規の半導体装置を提供することができる。または、本発明の一態様は、高速に動作すること又はそれを可能にする構成を提供することができる。または、本発明の一態様は、レイアウト面積を縮小すること又はそれを可能にする構成を提供することができる。または、本発明の一態様は、駆動電圧を小さくすること又はそれを可能にする構成を提供することができる。または、本発明の一態様は、信号の立ち上がり時間又は立下り時間を短くすること又はそれを可能にする構成を提供することができる。

#### 【0016】

なお、これらの効果の記載は、他の効果の存在を妨げるものではない。なお、本発明の一

50

態様は、必ずしも、これらの効果の全てを有する必要はない。なお、これら以外の効果は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の効果を抽出することが可能である。

【図面の簡単な説明】

【0017】

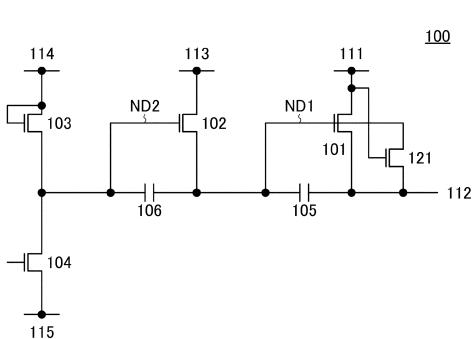

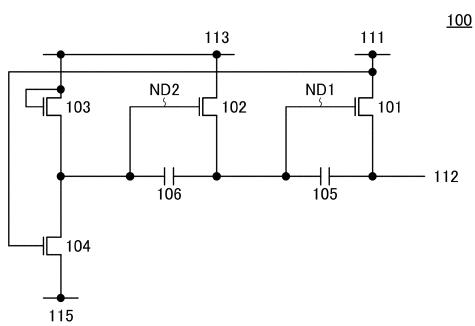

- 【図1】半導体装置の一例を説明する図。

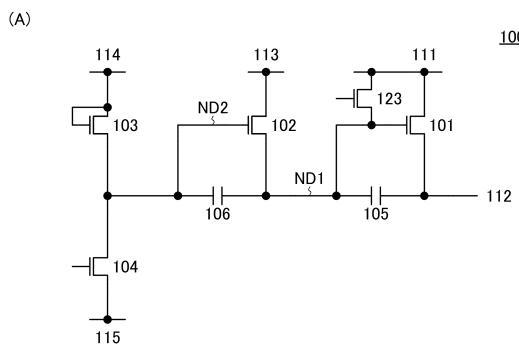

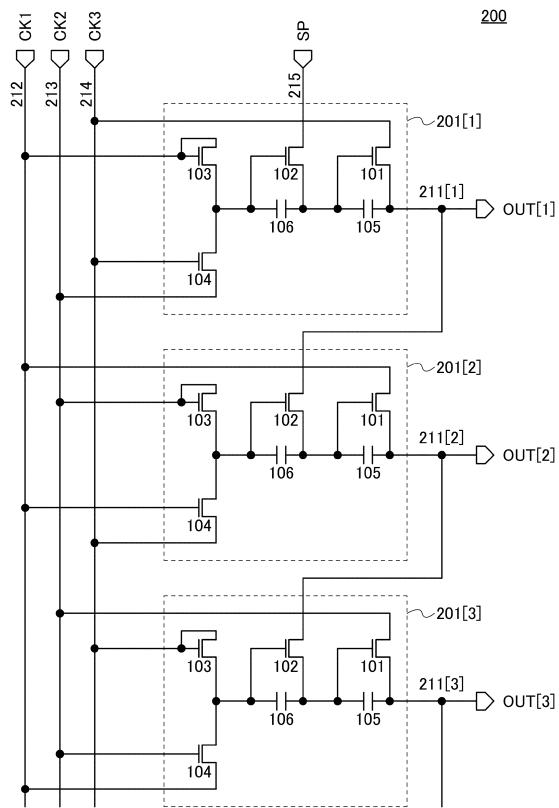

- 【図2】半導体装置の一例を説明する図。

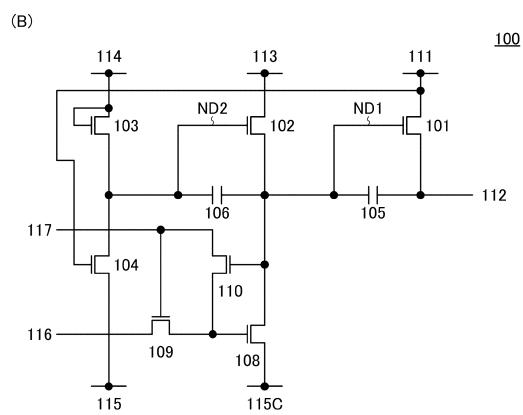

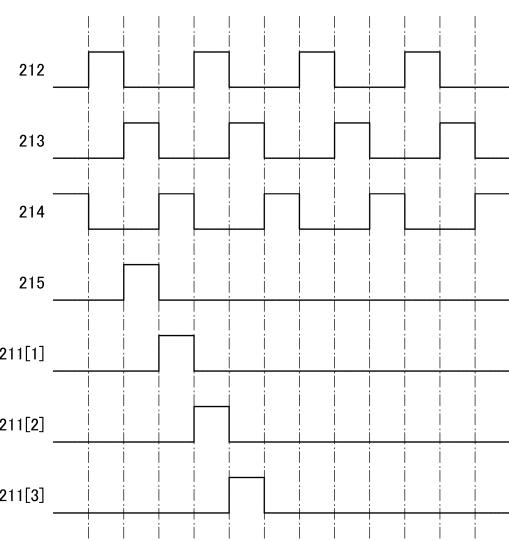

- 【図3】半導体装置の一例を説明する図。

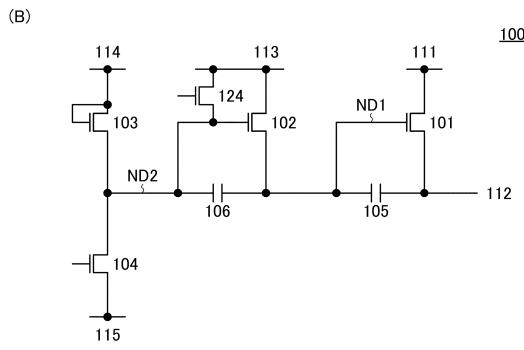

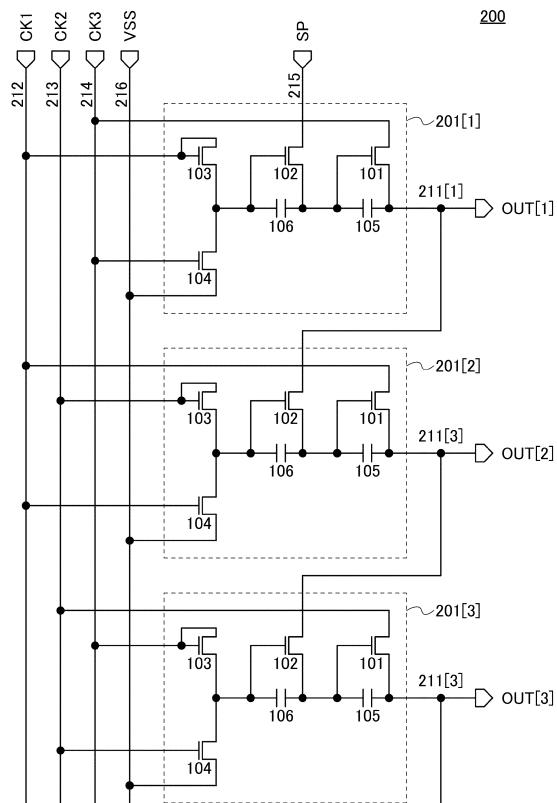

- 【図4】半導体装置の一例を説明する図。

- 【図5】半導体装置の一例を説明する図。

- 【図6】半導体装置の一例を説明する図。

- 【図7】半導体装置の一例を説明する図。

- 【図8】半導体装置の一例を説明する図。

- 【図9】半導体装置の一例を説明する図。

- 【図10】半導体装置の一例を説明する図。

- 【図11】半導体装置の一例を説明する図。

- 【図12】半導体装置の一例を説明する図。

- 【図13】半導体装置の一例を説明する図。

- 【図14】半導体装置の一例を説明する図。

- 【図15】半導体装置の一例を説明する図。

- 【図16】半導体装置の一例を説明する図。

- 【図17】半導体装置の一例を説明する図。

- 【図18】半導体装置の一例を説明する図。

- 【図19】表示装置の一例を説明する図。

- 【図20】半導体装置の一例を説明する図。

- 【図21】半導体装置の一例を説明する図。

- 【図22】半導体装置の一例を説明する図。

- 【図23】半導体装置の一例を説明する図。

- 【図24】表示モジュールの一例を説明する図。

- 【図25】電子機器の一例を説明する図。

- 【図26】半導体装置の一例を説明する図。

10

20

30

【発明を実施するための形態】

【0018】

以下、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の実施の形態における説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは、当業者であれば容易に理解される。したがって、本発明は、以下の実施の形態の記載内容に限定して解釈されるものではない。

【0019】

また、本発明の一態様は、撮像装置の他、RFタグ、表示装置、集積回路を含むあらゆる装置が、その範疇に含まれる。また、表示装置には、液晶表示装置、有機発光素子に代表される発光素子を各画素に備えた発光装置、電子ペーパー、DMD (Digital Micromirror Device)、PDP (Plasma Display Panel)、FED (Field Emission Display) など、集積回路を有する表示装置が、その範疇に含まれる。

40

【0020】

なお、図面を用いて発明の構成を説明するにあたり、同じものを指す符号は異なる図面間でも共通して用いることがある。

【0021】

また、本明細書等においては、ある一つの実施の形態において述べる図または文章において、その一部分を取り出して、発明の一態様を構成することは可能である。したがって、

50

ある部分を述べる図または文章が記載されている場合、その一部分の図または文章を取り出した内容も、発明の一態様として開示されているものであり、発明の一態様を構成することが可能であるものとする。そして、その発明の一態様は明確であると言える。そのため、例えば、能動素子（トランジスタなど）、配線、受動素子（容量素子など）、導電層、絶縁層、半導体層、部品、装置、動作方法、製造方法などが単数もしくは複数記載された図面または文章において、その一部分を取り出して、発明の一態様を構成することが可能であるものとする。例えば、N個（Nは整数）の回路素子（トランジスタ、容量素子等）を有して構成される回路図から、M個（Mは整数で、M < N）の回路素子（トランジスタ、容量素子等）を抜き出して、発明の一態様を構成することは可能である。別の例としては、「Aは、B、C、D、E、または、Fを有する」と記載されている文章から、一部の要素を任意に抜き出して、「Aは、BとEとを有する」、「Aは、EとFとを有する」、「Aは、CとEとFとを有する」、または、「Aは、BとCとDとEとを有する」などの発明の一態様を構成することは可能である。10

#### 【0022】

また、本明細書等においては、ある一つの実施の形態において述べる図または文章において、少なくとも一つの具体例が記載される場合、その具体例の上位概念を導き出すことは、当業者であれば容易に理解される。したがって、ある一つの実施の形態において述べる図または文章において、少なくとも一つの具体例が記載される場合、その具体例の上位概念も、発明の一態様として開示されているものであり、発明の一態様を構成することが可能である。そして、その発明の一態様は、明確であると言える。20

#### 【0023】

また、本明細書等においては、少なくとも図に記載した内容（図の中の一部でもよい）は、発明の一態様として開示されているものであり、発明の一態様を構成することが可能である。したがって、ある内容について、図に記載されていれば、文章を用いて述べていなくても、その内容は、発明の一態様として開示されているものであり、発明の一態様を構成することが可能である。同様に、図の一部を取り出した図についても、発明の一態様として開示されているものであり、発明の一態様を構成することが可能である。そして、その発明の一態様は明確であると言える。

#### 【0024】

また、明細書の中の文章や図面において規定されていない内容について、その内容を除くことを規定した発明の一態様を構成することが出来る。または、ある値について、上限値と下限値などで示される数値範囲が記載されている場合、その範囲を任意に狭めることで、または、その範囲の中の一点を除くことで、その範囲を一部除いた発明の一態様を規定することができる。これらにより、例えば、従来技術が本発明の一態様の技術的範囲内に入らないことを規定することができる。30

#### 【0025】

また、本明細書等においては、能動素子（トランジスタなど）、受動素子（容量素子など）などが有するすべての端子について、その接続先を特定しなくても、当業者であれば、発明の一態様を構成することは可能な場合がある。つまり、接続先を特定しなくても、発明の一態様が明確であると言える。そして、接続先が特定された内容が、本明細書等に記載されている場合、接続先を特定しない発明の一態様が、本明細書等に記載されていると判断することができる場合がある。特に、端子の接続先の候補が複数存在する場合には、その端子の接続先を特定の箇所に限定する必要はない。したがって、能動素子（トランジスタなど）、受動素子（容量素子など）などが有する一部の端子についてのみ、その接続先を特定することによって、発明の一態様を構成することが可能な場合がある。40

#### 【0026】

また、本明細書等においては、ある回路について、少なくとも接続先を特定すれば、当業者であれば、発明を特定することが可能な場合がある。または、ある回路について、少なくとも機能を特定すれば、当業者であれば、発明を特定することが可能な場合がある。つまり、機能を特定すれば、発明の一態様が明確であると言える。そして、機能が特定され50

た発明の一態様が、本明細書等に記載されていると判断することが可能な場合がある。したがって、ある回路について、機能を特定しなくとも、接続先を特定すれば、発明の一態様として開示されているものであり、発明の一態様を構成することが可能である。または、ある回路について、接続先を特定しなくとも、機能を特定すれば、発明の一態様として開示されているものであり、発明の一態様を構成することが可能である。

#### 【0027】

また、本明細書等において、XとYとが接続されている、と明示的に記載されている場合は、XとYとが電気的に接続されている場合と、XとYとが機能的に接続されている場合と、XとYとが直接接続されている場合とが、本明細書等に開示されているものとする。

したがって、所定の接続関係、例えば、図または文章に示された接続関係に限定されず、図または文章に示された接続関係以外のものも、図または文章に記載されているものとする。

10

#### 【0028】

ここで、X、Yは、対象物（例えば、装置、素子、回路、配線、電極、端子、導電膜、層、など）であるとする。

#### 【0029】

XとYとが直接的に接続されている場合の一例としては、XとYとの電気的な接続を可能とする素子（例えば、スイッチ、トランジスタ、容量素子、インダクタ、抵抗素子、ダイオード、表示素子、発光素子、負荷など）が、XとYとの間に接続されていない場合であり、XとYとの電気的な接続を可能とする素子（例えば、スイッチ、トランジスタ、容量素子、インダクタ、抵抗素子、ダイオード、表示素子、発光素子、負荷など）を介さずに、XとYとが、接続されている場合である。

20

#### 【0030】

XとYとが電気的に接続されている場合の一例としては、XとYとの電気的な接続を可能とする素子（例えば、スイッチ、トランジスタ、容量素子、インダクタ、抵抗素子、ダイオード、表示素子、発光素子、負荷など）が、XとYとの間に1個以上接続されることが可能である。なお、スイッチは、オンオフが制御される機能を有している。つまり、スイッチは、導通状態（オン状態）、または、非導通状態（オフ状態）になり、電流を流すか流さないかを制御する機能を有している。または、スイッチは、電流を流す経路を選択して切り替える機能を有している。なお、XとYとが電気的に接続されている場合は、XとYとが直接的に接続されている場合を含むものとする。

30

#### 【0031】

XとYとが機能的に接続されている場合の一例としては、XとYとの機能的な接続を可能とする回路（例えば、論理回路（インバータ、NAND回路、NOR回路など）、信号変換回路（D/A変換回路、A/D変換回路、ガンマ補正回路など）、電位レベル変換回路（電源回路（昇圧回路、降圧回路など）、信号の電位レベルを変えるレベルシフタ回路など）、電圧源、電流源、切り替え回路、增幅回路（信号振幅または電流量などを大きく出来る回路、オペアンプ、差動增幅回路、ソースフォロワ回路、バッファ回路など）、信号生成回路、記憶回路、制御回路など）が、XとYとの間に1個以上接続されることが可能である。なお、一例として、XとYとの間に別の回路を挟んでいても、Xから出力された信号がYへ伝達される場合は、XとYとは機能的に接続されているものとする。なお、XとYとが機能的に接続されている場合は、XとYとが直接的に接続されている場合と、XとYとが電気的に接続されている場合とを含むものとする。

40

#### 【0032】

なお、XとYとが電気的に接続されている、と明示的に記載されている場合は、XとYとが電気的に接続されている場合（つまり、XとYとの間に別の素子又は別の回路を挟んで接続されている場合）と、XとYとが機能的に接続されている場合（つまり、XとYとの間に別の回路を挟んで機能的に接続されている場合）と、XとYとが直接接続されている場合（つまり、XとYとの間に別の素子又は別の回路を挟まずに接続されている場合）とが、本明細書等に開示されているものとする。つまり、電気的に接続されている、と明示

50

的に記載されている場合は、単に、接続されている、とのみ明示的に記載されている場合と同様な内容が、本明細書等に開示されているものとする。

#### 【0033】

なお、例えば、トランジスタのソース（又は第1の端子など）が、Z1を介して（又は介さず）、Xと電気的に接続され、トランジスタのドレイン（又は第2の端子など）が、Z2を介して（又は介さず）、Yと電気的に接続されている場合や、トランジスタのソース（又は第1の端子など）が、Z1の一部と直接的に接続され、Z1の別の一部がXと直接的に接続され、トランジスタのドレイン（又は第2の端子など）が、Z2の一部と直接的に接続され、Z2の別の一部がYと直接的に接続されている場合では、以下のように表現することが出来る。

10

#### 【0034】

例えば、「XとYとトランジスタのソース（又は第1の端子など）とドレイン（又は第2の端子など）とは、互いに電気的に接続されており、X、トランジスタのソース（又は第1の端子など）、トランジスタのドレイン（又は第2の端子など）、Yの順序で電気的に接続されている。」と表現することができる。または、「トランジスタのソース（又は第1の端子など）は、Xと電気的に接続され、トランジスタのドレイン（又は第2の端子など）はYと電気的に接続され、X、トランジスタのソース（又は第1の端子など）、トランジスタのドレイン（又は第2の端子など）、Yは、この順序で電気的に接続されている」と表現することができる。または、「Xは、トランジスタのソース（又は第1の端子など）とドレイン（又は第2の端子など）とを介して、Yと電気的に接続され、X、トランジスタのソース（又は第1の端子など）、トランジスタのドレイン（又は第2の端子など）、Yは、この接続順序で設けられている」と表現することができる。これらの例と同様な表現方法を用いて、回路構成における接続の順序について規定することにより、トランジスタのソース（又は第1の端子など）と、ドレイン（又は第2の端子など）とを、区別して、技術的範囲を決定することができる。

20

#### 【0035】

または、別の表現方法として、例えば、「トランジスタのソース（又は第1の端子など）は、少なくとも第1の接続経路を介して、Xと電気的に接続され、前記第1の接続経路は、第2の接続経路を有しておらず、前記第2の接続経路は、トランジスタを介した、トランジスタのソース（又は第1の端子など）とトランジスタのドレイン（又は第2の端子など）との間の経路であり、前記第1の接続経路は、Z1を介した経路であり、トランジスタのドレイン（又は第2の端子など）は、少なくとも第3の接続経路を介して、Yと電気的に接続され、前記第3の接続経路は、前記第2の接続経路を有しておらず、前記第3の接続経路は、Z2を介した経路である。」と表現することができる。または、「トランジスタのソース（又は第1の端子など）は、少なくとも第1の接続経路によって、Z1を介して、Xと電気的に接続され、前記第1の接続経路は、第2の接続経路を有しておらず、前記第2の接続経路は、トランジスタを介した接続経路を有し、トランジスタのドレイン（又は第2の端子など）は、少なくとも第3の接続経路によって、Z2を介して、Yと電気的に接続され、前記第3の接続経路は、前記第2の接続経路を有していない。」と表現することができる。または、「トランジスタのソース（又は第1の端子など）は、少なくとも第1の電気的バスによって、Z1を介して、Xと電気的に接続され、前記第1の電気的バスは、第2の電気的バスを有しておらず、前記第2の電気的バスは、トランジスタのソース（又は第1の端子など）からトランジスタのドレイン（又は第2の端子など）への電気的バスであり、トランジスタのドレイン（又は第2の端子など）は、少なくとも第3の電気的バスによって、Z2を介して、Yと電気的に接続され、前記第3の電気的バスは、第4の電気的バスを有しておらず、前記第4の電気的バスは、トランジスタのドレイン（又は第2の端子など）からトランジスタのソース（又は第1の端子など）への電気的バスである。」と表現することができる。これらの例と同様な表現方法を用いて、回路構成における接続経路について規定することにより、トランジスタのソース（又は第1の端子など）と、ドレイン（又は第2の端子など）とを、区別して、技術的範囲を決定すること

30

40

50

ができる。

【0036】

なお、これらの表現方法は、一例であり、これらの表現方法に限定されない。ここで、X、Y、Z1、Z2は、対象物（例えば、装置、素子、回路、配線、電極、端子、導電膜、層、など）であるとする。

【0037】

なお、回路図上は独立している構成要素同士が電気的に接続しているように図示されている場合であっても、1つの構成要素が、複数の構成要素の機能を併せ持っている場合もある。例えば配線の一部が電極としても機能する場合は、一の導電膜が、配線の機能、及び電極の機能の両方の構成要素の機能を併せ持っている。したがって、本明細書における電気的に接続とは、このような、一の導電膜が、複数の構成要素の機能を併せ持っている場合も、その範疇に含める。

10

【0038】

（実施の形態1）

本実施の形態では、本発明の一態様に係る半導体装置について説明する。

【0039】

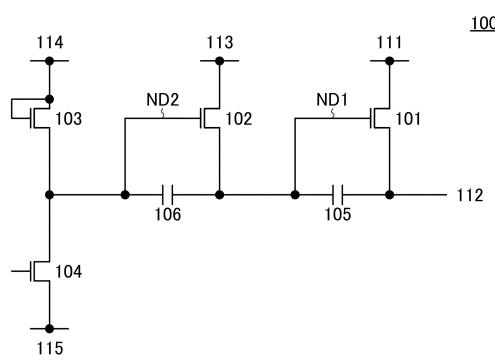

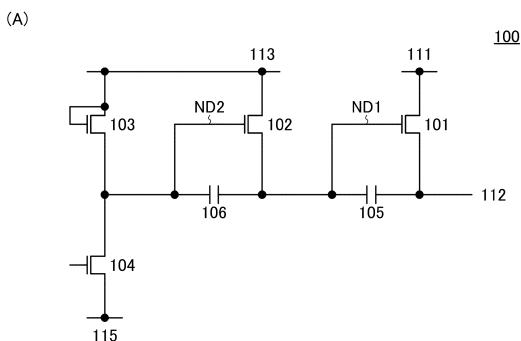

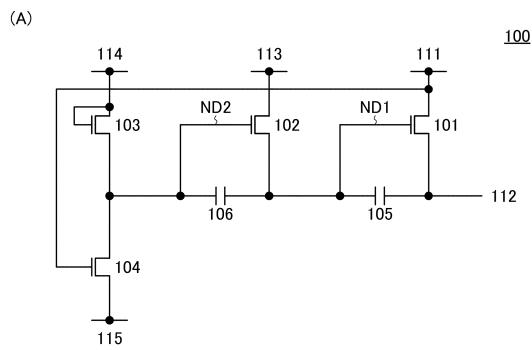

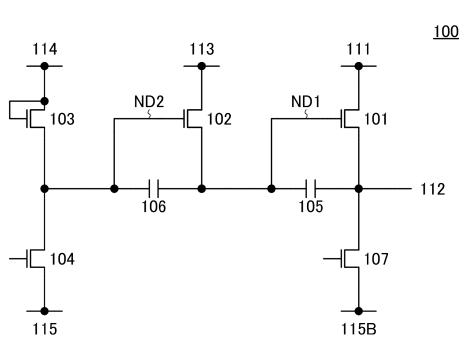

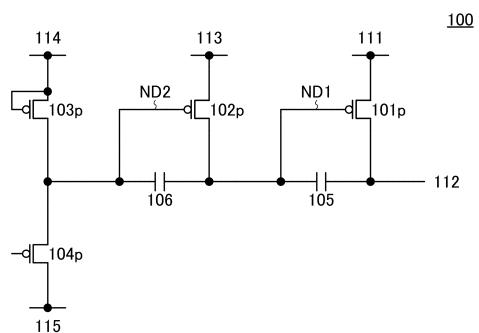

本発明の一態様に係る半導体装置の構成について、図1を参照して説明する。ただし、本発明の一態様は、以下に説明する構成に限定されない。

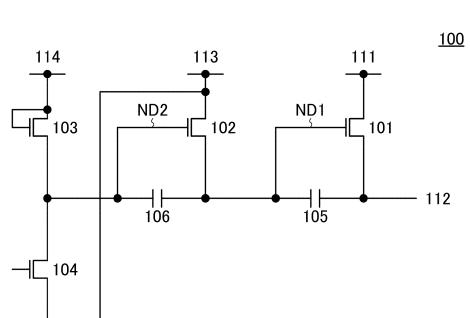

【0040】

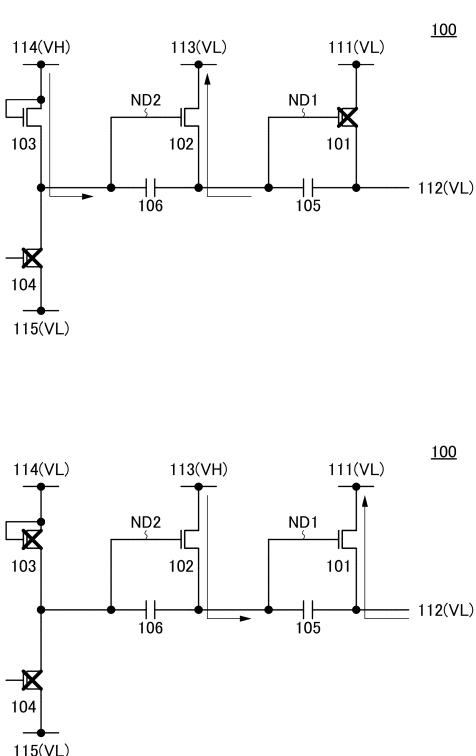

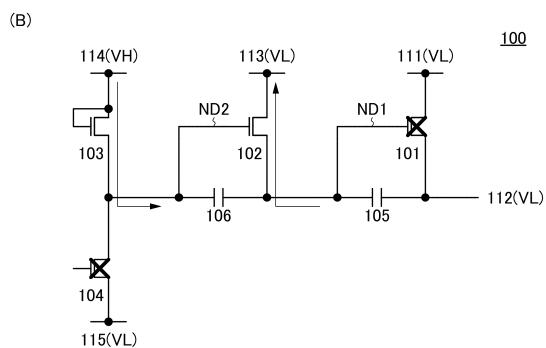

図1に示す半導体装置は、回路100を有する。回路100は、配線111、配線113、配線114及び配線115の電位に基づいて、配線112の電位を制御する機能を有する。回路100は、配線111、配線113、配線114及び配線115の電位に基づいた信号を配線112に出力する。そして、当該信号により、配線112の電位が制御される。このように、回路100は、論理回路又は順序回路としての機能を有する。

20

【0041】

回路100は、トランジスタ101、トランジスタ102、トランジスタ103、トランジスタ104、容量素子105、及び容量素子106を有する。トランジスタ101は、第1の端子（ソース又はドレインの一方ともいう）が配線111と接続され、第2の端子（ソース又はドレインの他方ともいう）が配線112と接続される。トランジスタ102は、第1の端子が配線113と接続され、第2の端子がトランジスタ101のゲートと接続される。トランジスタ103は、第1の端子が配線114と接続され、第2の端子がトランジスタ102のゲートと接続され、ゲートが配線114と接続される。トランジスタ104は、第1の端子が配線115と接続され、第2の端子がトランジスタ102のゲートと接続される。容量素子105は、第1の端子が配線112と接続され、第2の端子がトランジスタ101のゲートと接続される。容量素子106は、第1の端子がトランジスタ101のゲートと接続され、第2の端子がトランジスタ102のゲートと接続される。

30

【0042】

本実施の形態の半導体装置は、上記接続関係を有することにより、新規の構成を提供することができる。

【0043】

なお、トランジスタ101のゲート、トランジスタ102の第2の端子、容量素子105の第2の端子、又は容量素子106の第1の端子をノードND1と示す。また、トランジスタ102のゲート、トランジスタ103の第2の端子、トランジスタ104の第2の端子、又は容量素子106の第2の端子をノードND2と示す。

40

【0044】

なお、配線111、配線113、配線114及び配線115の電位は、各配線に信号又は電圧等が入力されることによって制御される。便宜上、配線111、配線113及び配線114の電位は、ハイレベルとロウレベルとを有するものとする。言い換えると、配線111、配線113及び配線114のそれぞれには、ハイレベルとロウレベルとを有する信号が入力される。そして、ハイレベルの電位をVHとし、ロウレベルの電位をVL（VH

50

> V<sub>L</sub>)とする。また、配線115の電位をV<sub>L</sub>とする。ただし、配線115の電位はハイレベルとロウレベルとを有していてもよい。言い換えると、配線115にはハイレベルとロウレベルとを有する信号を入力してもよい。

#### 【0045】

なお、配線111、配線113及び配線114を入力端子と呼んでもよい。また、配線112を出力端子と呼んでもよい。また、配線111、配線112、配線113、及び配線114を信号線と呼んでもよい。または、配線115を電源線と呼んでもよい。

#### 【0046】

トランジスタ101、トランジスタ102、トランジスタ103及びトランジスタ104に採用することが可能なトランジスタについて説明する。ただし、本発明の一態様は、以下に説明するトランジスタに限定されない。

#### 【0047】

トランジスタ101、トランジスタ102、トランジスタ103及びトランジスタ104としては、チャネル形成領域にアモルファスシリコンを有するトランジスタ、チャネル形成領域に多結晶シリコンを有するトランジスタ、チャネル形成領域に単結晶シリコンを有するトランジスタ、チャネル形成領域に酸化物半導体を有するトランジスタ、チャネル形成領域に化合物半導体を有するトランジスタなどを用いることが可能である。特に、チャネル形成領域に酸化物半導体を有するトランジスタ(0Sトランジスタともいう)は、チャネル形成領域にアモルファスシリコンを有するトランジスタよりも移動度が高く、且つオフ電流が極めて小さいという特徴がある。そのため、トランジスタのチャネル幅を小さくすることができるため、レイアウト面積の縮小を図ることができる。

#### 【0048】

トランジスタ101、トランジスタ102、トランジスタ103及びトランジスタ104の導電型又は極性について説明する。ただし、本発明の一態様は、以下に説明する導電型又は極性に限定されない。

#### 【0049】

トランジスタ101、トランジスタ102、トランジスタ103及びトランジスタ104は、同じ導電型であることが好ましい。或いは、回路100が有するトランジスタの全ては、同じ導電型であることが好ましい。或いは、回路100と同じ基板に設けられるトランジスタは全て同じ導電型であることが好ましい。これにより、製造プロセスの簡略化、歩留まりの向上、製造コストの削減等を図ることができる。

#### 【0050】

特に、トランジスタ101、トランジスタ102、トランジスタ103及びトランジスタ104はNチャネル型であることが好ましい。或いは、回路100が有するトランジスタは全てNチャネル型であることが好ましい。或いは、回路100と同じ基板に設けられるトランジスタは全てNチャネル型であることが好ましい。これにより、チャネル形成領域に酸化物半導体を有するトランジスタ(0Sトランジスタともいう)を採用することができる。図1には、トランジスタ101、トランジスタ102、トランジスタ103及びトランジスタ104がNチャネル型である場合について例示している。ただし、トランジスタ101、トランジスタ102、トランジスタ103及びトランジスタ104はPチャネル型であってもよい。或いは、回路100が有するトランジスタは全てPチャネル型であってもよい。或いは、回路100と同じ基板に設けられるトランジスタは全てPチャネル型であってもよい。図26には、図1のトランジスタ101、トランジスタ102、トランジスタ103及びトランジスタ104を、トランジスタ101p、トランジスタ102p、トランジスタ103p及びトランジスタ104pに置き換えた場合の構成を示す。トランジスタ101p、トランジスタ102p、トランジスタ103p及びトランジスタ104pはPチャネル型である。また、図1以外の構成においても、図26と同様にNチャネル型のトランジスタをPチャネル型のトランジスタに置き換えてよい。

#### 【0051】

なお、便宜上、トランジスタ101、トランジスタ102及びトランジスタ103は、N

10

20

30

40

50

チャネル型であるものとして説明する。

【0052】

トランジスタ101、トランジスタ102、トランジスタ103、トランジスタ104、容量素子105及び容量素子106が有する機能について説明する。ただし、本発明の一態様は、以下に説明する機能に限定されない。

【0053】

トランジスタ101は、配線111と配線112との導通又は非導通を制御する。配線111と配線112とが導通すると、配線111の電位が配線112に供給され、配線112の電位が配線111の電位に基づいて制御される。配線111の電位がハイレベルであれば、配線112の電位が上昇する。特に、ノードND1の電位が配線111のハイレベルの電位とトランジスタ101の閾値電圧との和よりも高い値であれば、配線112の電位がVHまで上昇する。配線111の電位がロウレベルであれば、配線112の電位がVLまで下降する。

【0054】

トランジスタ102は、配線113とノードND1との導通又は非導通を制御する。配線113とノードND1とが導通すると、配線113の電位がノードND1に供給され、ノードND1の電位が配線113の電位に基づいて制御される。配線113の電位がハイレベルであれば、ノードND1の電位が上昇する。特に、ノードND2の電位が配線113のハイレベルの電位とトランジスタ102の閾値電圧との和よりも高い値であれば、ノードND1の電位がVHまで上昇する。こうして、ノードND1の電位が、トランジスタ101がオンになる値に設定される。配線113の電位がロウレベルであれば、ノードND1の電位がVLまで下降する。こうして、ノードND1の電位が、トランジスタ101がオフになる値に設定される。

【0055】

トランジスタ103は、配線114とノードND2との導通又は非導通を制御する。配線114とノードND2とが導通すると、配線114の電位がノードND2に供給され、ノードND2の電位が配線114の電位に基づいて制御される。配線114の電位がハイレベルであれば、ノードND2の電位が上昇する。ただし、トランジスタ103のゲートが配線114と接続されているため、ノードND2の電位が配線114のハイレベルの電位からトランジスタ103の閾値電圧を引いた値まで上昇すると、トランジスタ103がオフになる。そして、ノードND2が浮遊状態になる。こうして、ノードND2の電位が、トランジスタ102がオンになる値に設定されるとともにノードND2が浮遊状態になる。また、配線114の電位がロウレベルであれば、トランジスタ103がオフになるため、配線114とノードND2とは非導通になる。

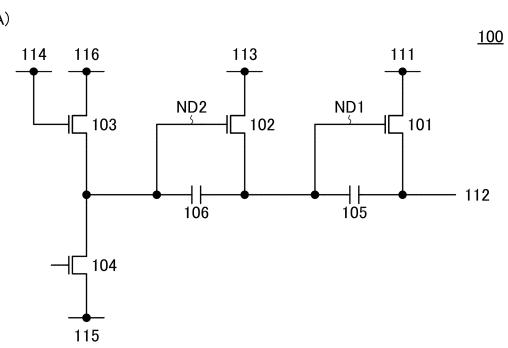

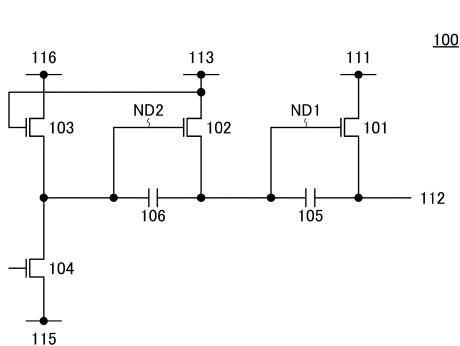

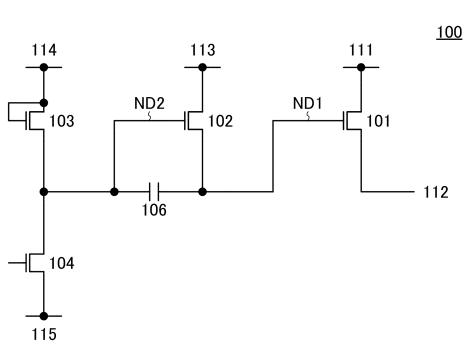

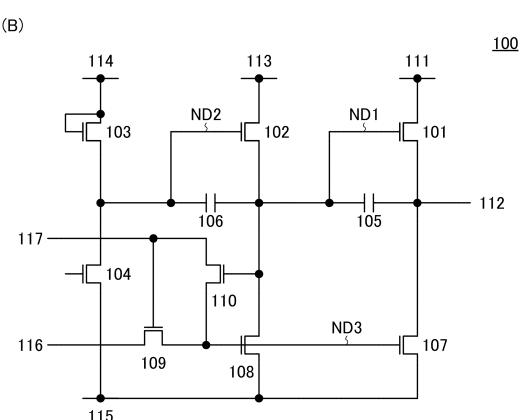

【0056】

なお、図2(A)に示すように、トランジスタ103の第1の端子が配線116と接続され、トランジスタ103のゲートが配線114と接続されてもよい。配線116の電位はVHであることが好ましい。ただし、配線116の電位はハイレベルとロウレベルとを有することも可能である。図2(A)では、トランジスタ103は、配線116とノードND2との導通又は非導通を制御する。配線116とノードND2とが導通すると、配線116の電位がノードND2に供給され、ノードND2の電位が配線116の電位に基づいて制御される。配線116の電位がVH又はハイレベルであれば、ノードND2の電位が上昇する。ただし、トランジスタ103のゲートが配線114と接続されているため、ノードND2の電位が配線114のハイレベルの電位からトランジスタ103の閾値電圧を引いた値まで上昇すると、トランジスタ103がオフになる。そして、ノードND2が浮遊状態になる。こうして、ノードND2の電位が、トランジスタ102がオンになる値に設定されるとともにノードND2が浮遊状態になる。

【0057】

なお、図2(B)に示すように、トランジスタ103の第1の端子が配線114と接続され、トランジスタ103のゲートが配線116と接続されてもよい。図2(B)では、ト

10

20

30

40

50

ランジスタ103は、配線114とノードND2との導通又は非導通を制御する。配線114とノードND2とが導通すると、配線114の電位がノードND2に供給され、ノードND2の電位が配線114の電位に基づいて制御される。配線114の電位がハイレベルであれば、ノードND2の電位が上昇する。ただし、トランジスタ103のゲートが配線116と接続されているため、ノードND2の電位が配線116の電位からトランジスタ103の閾値電圧を引いた値まで上昇すると、トランジスタ103がオフになる。そして、ノードND2が浮遊状態になる。こうして、ノードND2の電位が、トランジスタ102がオンになる値に設定されるとともにノードND2が浮遊状態になる。また、配線114の電位がロウレベルであれば、ノードND2の電位がVLまで下降する。こうして、ノードND2の電位が、トランジスタ102がオフになる値に設定される。

10

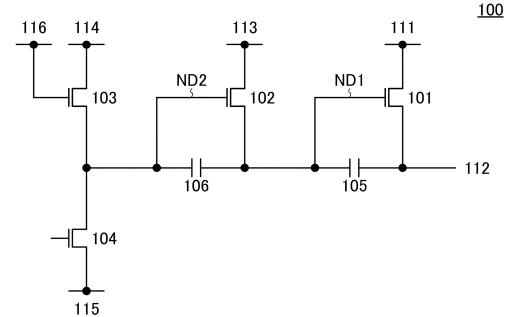

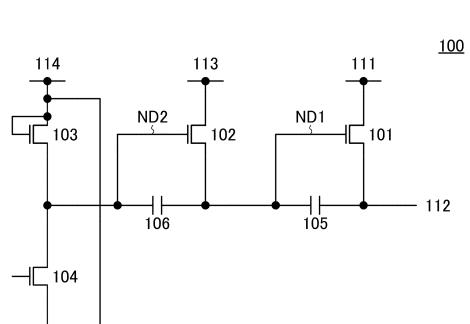

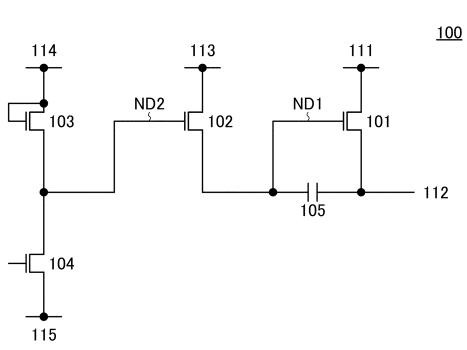

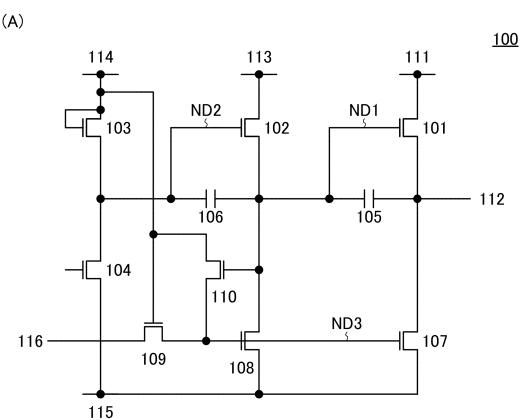

#### 【0058】

なお、図3(A)に示すように、トランジスタ103の第1の端子及びゲートは配線113と接続されてもよい。図3(A)では、トランジスタ103は、配線113とノードND2との導通又は非導通を制御する。配線113とノードND2とが導通すると、配線113の電位がノードND2に供給され、ノードND2の電位が配線113の電位に基づいて制御される。配線113の電位がハイレベルであれば、ノードND2の電位が上昇する。ただし、トランジスタ103のゲートが配線113と接続されているため、ノードND2の電位が配線113のハイレベルの電位からトランジスタ103の閾値電圧を引いた値まで上昇すると、トランジスタ103がオフになる。そして、ノードND2が浮遊状態になる。こうして、ノードND2の電位が、トランジスタ102がオンになる値に設定されるとともにノードND2が浮遊状態になる。また、配線113の電位がロウレベルであれば、トランジスタ104がオフになるため、配線113とノードND2とは非導通になる。

20

#### 【0059】

なお、図3(B)に示すように、トランジスタ103の第1の端子が配線116と接続され、トランジスタ103のゲートが配線113と接続されてもよい。図3(B)では、トランジスタ103は、配線116とノードND2との導通又は非導通を制御する。配線116とノードND2とが導通すると、配線116の電位がノードND2に供給され、ノードND2の電位が配線116の電位に基づいて制御される。配線116の電位がVH又はハイレベルであれば、ノードND2の電位が上昇する。ただし、トランジスタ103のゲートが配線113と接続されているため、ノードND2の電位が配線113のハイレベルの電位からトランジスタ103の閾値電圧を引いた値まで上昇すると、トランジスタ103がオフになる。そして、ノードND2が浮遊状態になる。こうして、ノードND2の電位が、トランジスタ102がオンになる値に設定されるとともにノードND2が浮遊状態になる。

30

#### 【0060】

なお、図示はしないが、トランジスタ103の第1の端子が配線114と接続され、トランジスタ103のゲートが配線113と接続されてもよい。

#### 【0061】

なお、図示はしないが、トランジスタ103の第1の端子が配線113と接続され、トランジスタ103のゲートが配線116と接続されてもよい。

40

#### 【0062】

トランジスタ104は、配線115とノードND2との導通又は非導通を制御する。配線115とノードND2とが導通すると、配線115の電位がノードND2に供給され、ノードND2の電位が配線115の電位に基づいて制御される。配線115の電位がVL又はロウレベルであれば、ノードND2の電位がVLまで下降する。こうして、ノードND2の電位が、トランジスタ102がオフになる値に設定される。

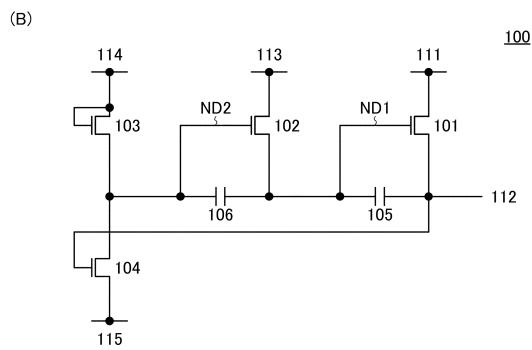

#### 【0063】

なお、図4(A)に示すように、トランジスタ104の第1の端子が配線113と接続されてもよい。図4(A)では、トランジスタ104は、配線113とノードND2との導

50

通又は非導通を制御する。配線 113 とノード ND2 とが導通すると、配線 113 の電位がノード ND2 に供給され、ノード ND2 の電位が配線 113 の電位に基づいて制御される。配線 113 の電位が VL 又はロウレベルであれば、ノード ND2 の電位が VL まで下降する。こうして、ノード ND2 の電位が、トランジスタ 102 がオフになる値に設定される。

【0064】

なお、図 4 (B) に示すように、トランジスタ 104 の第 1 の端子が配線 114 と接続されてもよい。図 4 (B) では、トランジスタ 104 は、配線 114 とノード ND2 との導通又は非導通を制御する。配線 114 とノード ND2 とが導通すると、配線 114 の電位がノード ND2 に供給され、ノード ND2 の電位が配線 114 の電位に基づいて制御される。配線 114 の電位が VL 又はロウレベルであれば、ノード ND2 の電位が VL まで下降する。こうして、ノード ND2 の電位が、トランジスタ 102 がオフになる値に設定される。

10

【0065】

なお、図 5 (A) に示すように、トランジスタ 104 のゲートが配線 111 と接続されてもよい。

【0066】

なお、図 5 (B) に示すように、トランジスタ 104 のゲートが配線 112 と接続されてもよい。

【0067】

20

容量素子 105 は、配線 112 とノード ND1 との電位差を保持する。ノード ND1 が浮遊状態であれば、配線 112 の電位の変化に基づいてノード ND1 の電位が変化する。そのため、配線 112 の電位の上昇に伴ってノード ND1 の電位が上昇すれば、ノード ND1 の電位が配線 111 のハイレベルの電位とトランジスタ 101 の閾値電圧との和よりも高くなる。

【0068】

なお、図 6 (A) に示すように、容量素子 105 を省略してもよい。トランジスタ 101 の第 2 の端子とゲートとの間の寄生容量によって、配線 112 とノード ND1 との間の電位差は保持される。

【0069】

30

容量素子 106 は、ノード ND1 とノード ND2 との電位差を保持する。ノード ND2 が浮遊状態であれば、ノード ND1 の電位の変化に基づいてノード ND2 の電位が変化する。そのため、ノード ND1 の電位の上昇に伴ってノード ND2 の電位が上昇すれば、ノード ND2 の電位が配線 113 のハイレベルの電位とトランジスタ 102 の閾値電圧との和よりも高くなる。

【0070】

なお、図 6 (B) に示すように、容量素子 106 を省略してもよい。トランジスタ 102 の第 2 の端子とゲートとの間の寄生容量によって、ノード ND1 とノード ND2 との間の電位差は保持される。

【0071】

40

なお、トランジスタ 101、トランジスタ 102、トランジスタ 103、トランジスタ 104、容量素子 105 及び容量素子 106 は、上述する機能の全てを有する必要はない。

【0072】

なお、図 1、図 2、図 3、図 4、図 5 及び図 6 等に図示して説明した回路 100、並びに図示せずに説明した回路 100 を適宜組み合わせることが可能である。

【0073】

本実施の形態の半導体装置の動作について、図 1 の構成を例にして説明する。ただし、本発明の一態様は、以下に説明する動作に限定されない。

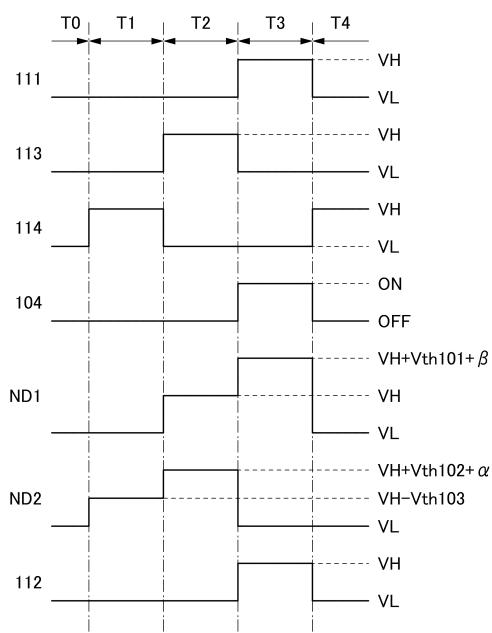

【0074】

図 7 に示すタイミングチャートは、配線 111 の電位、配線 113 の電位、配線 114 の

50

電位、トランジスタ 104 のオン又はオフ、ノード ND1 の電位、ノード ND2 の電位、及び配線 112 の電位の一例を示す。

【0075】

なお、便宜上、期間 T1、期間 T2、期間 T3 及び期間 T4 という 4 つの期間に分けて説明する。例えば、1 フレーム期間が期間 T1 乃至 T4 を有する。

【0076】

なお、便宜上、期間 T1 直前の期間 T0 において、配線 111 の電位がロウレベルであり、配線 113 の電位がロウレベルであり、配線 114 の電位がロウレベルであり、ノード ND1 の電位が VL であり、ノード ND2 の電位が VL であり、配線 112 の電位が VL であるものとする。また、ノード ND1 の電位が VL であるため、トランジスタ 101 はオフである。また、ノード ND2 の電位が VL であるため、トランジスタ 102 はオフである。

10

【0077】

期間 T1 における動作について、図 8 (A) を参照して説明する。配線 111 の電位がロウレベルのままになり、配線 113 の電位がロウレベルのままになり、配線 114 の電位がロウレベルからハイレベルに変化し、トランジスタ 104 がオフのままになる。

【0078】

配線 114 の電位がハイレベルになるため、トランジスタ 103 がオンになる。よって、配線 114 のハイレベルの電位がノード ND2 に供給されるため、ノード ND2 の電位が VL から上昇する。

20

【0079】

その後、ノード ND2 の電位がトランジスタ 102 の第 1 の端子の電位 (VL) とトランジスタ 102 の閾値電圧 (Vth102) との和 (VL + Vth102) よりも高くなると、トランジスタ 102 がオンになる。よって、配線 113 のロウレベルの電位がノード ND1 に供給されるため、ノード ND1 の電位が VL のままになる。また、ノード ND1 の電位が VL のままになるため、トランジスタ 101 がオフのままになる。よって、配線 112 の電位が VL のままになる。

【0080】

その後、ノード ND2 の電位がトランジスタ 103 のゲートの電位 (VH) からトランジスタ 103 の閾値電圧 (Vth103) を引いた値 (VH - Vth103) まで上昇すると、トランジスタ 103 がオフになる。よって、ノード ND2 が浮遊状態になり、ノード ND2 の電位が VH - Vth103 に維持される。

30

【0081】

なお、図 2 (A) では、トランジスタ 103 の第 1 の端子が配線 116 と接続されているため、配線 116 の電位 (例えば VH) がノード ND2 に供給される。

【0082】

期間 T2 における動作について、図 8 (B) を参照して説明する。配線 111 の電位がロウレベルのままになり、配線 113 の電位がロウレベルからハイレベルに変化し、配線 114 の電位がハイレベルからロウレベルに変化し、トランジスタ 104 がオフのままになる。

40

【0083】

配線 114 の電位がロウレベルになるため、トランジスタ 103 がオフのままになる。よって、ノード ND2 が浮遊状態のままになり、ノード ND2 の電位が VH - Vth103 のままになる。また、ノード ND2 の電位が VH - Vth103 のままになるため、トランジスタ 102 がオンのままになる。よって、配線 113 のハイレベルの電位がノード ND1 に供給されるため、ノード ND1 の電位が VL から上昇する。このとき、容量素子 106 はノード ND1 とノード ND2 との電位差を保持しており、且つノード ND2 は浮遊状態である。よって、ノード ND1 の電位の上昇に伴って、ノード ND2 の電位が VH - Vth103 から上昇する。

【0084】

10

20

30

40

50

その後、ノードND1の電位がトランジスタ101の第1の端子の電位(VL)とトランジスタ101の閾値電圧(Vth101)との和(VL + Vth101)よりも高くなると、トランジスタ101がオンになる。よって、配線111のロウレベルの電位が配線112に供給されるため、配線112の電位がVLのままになる。

【0085】

その後、ノードND1の電位の上昇に伴って、ノードND2の電位がトランジスタ102の第1の端子の電位(VH)とトランジスタ102の閾値電圧(Vth102)との和よりも高い値(VH + Vth102 + ( は正の数))まで上昇すると、ノードND1の電位がVHまで上昇する。

【0086】

なお、図2(B)では、トランジスタ103をオフのままにするために、期間T2において配線114の電位はハイレベルのままであることが好ましい。

【0087】

なお、図3(A)及び図3(B)では、期間T2において、トランジスタ103が期間T0後に初めてオンになる。具体的に説明すると、配線113の電位がハイレベルになると、トランジスタ103がオンになる。よって、図3(A)では、配線113のハイレベルの電位がノードND2に供給され、ノードND2の電位がVLから上昇する。一方、図3(B)では、配線116の電位(例えばVH)がノードND2に供給され、ノードND2の電位がVLから上昇する。その後、ノードND2の電位がVL + Vth102よりも高くなると、トランジスタ102がオンになる。よって、配線113のハイレベルの電位がノードND1に供給され、ノードND1の電位がVLから上昇する。その後、ノードND2の電位がVH - Vth103になると、トランジスタ103がオフになり、ノードND2が浮遊状態になる。このとき、ノードND1の電位が上昇している。そして、容量素子106はノードND1とノードND2との電位差を保持している。よって、ノードND1の電位の上昇に伴って、ノードND2の電位がVH - Vth103から上昇する。その後、ノードND1の電位がVL + Vth101よりも高くなると、トランジスタ101がオンになる。よって、配線111のロウレベルの電位が配線112に供給されるため、配線112の電位がVLのままになる。その後、ノードND1の電位の上昇に伴って、ノードND2の電位がVH + Vth102 + ( は正の数)まで上昇すると、ノードND1の電位がVHまで上昇する。このように、図3(A)及び図3(B)では、図1の期間T1及び期間T2における動作を期間T2においてまとめて行うことが可能である。よって、動作速度の向上を図ることができる。

【0088】

期間T3における動作について、図9(A)を参照して説明する。配線111の電位がロウレベルからハイレベルに変化し、配線113の電位がハイレベルからロウレベルに変化し、配線114の電位がロウレベルのままになり、トランジスタ104がオフからオンに変化する。

【0089】

配線114の電位がロウレベルのままになるため、トランジスタ103がオフのままになる。また、トランジスタ104がオンになる。よって、配線115の電位がノードND2に供給されるため、ノードND2の電位がVH + Vth102 + ( は正の数)からVLに下降する。ノードND2の電位がVLになるため、トランジスタ102がオフになる。よって、ノードND1が浮遊状態になり、ノードND1の電位がVHのままになる。ノードND1の電位がVHのままになるため、トランジスタ101がオンのままになる。よって、配線111のハイレベルの電位が配線112に供給されるため、配線112の電位がVLから上昇する。このとき、容量素子105は配線112とノードND1との電位差を保持しており、且つノードND1は浮遊状態である。よって、配線112の電位の上昇に伴って、ノードND1の電位がVHから上昇する。

【0090】

その後、配線112の電位の上昇に伴ってノードND1の電位がトランジスタ101の第

10

20

30

40

50

1の端子 (VH) の電位とトランジスタ101の閾値電圧 (Vth101)との和よりも高い値 (VH + Vth101 + ( は正の数 ))まで上昇すると、配線112の電位が VHまで上昇する。

#### 【0091】

なお、図4(A)では、トランジスタ104の第1の端子が配線113と接続されているため、配線113のロウレベルの電位がノードND2に供給される。また、図4(B)では、トランジスタ104の第1の端子が配線114と接続されているため、配線114のロウレベルの電位がノードND2に供給される。

#### 【0092】

期間T4における動作について、図9(B)を参照して説明する。配線111の電位がハイレベルからロウレベルに変化し、配線113の電位がロウレベルのままになり、配線114の電位がロウレベルからハイレベルに変化し、トランジスタ104がオンからオフに変化する。

#### 【0093】

配線114の電位がハイレベルになるため、トランジスタ103がオンになる。よって、配線114のハイレベルの電位がノードND2に供給され、ノードND2の電位が上昇する。このとき、ノードND1の電位がVH + Vth101 + であるため、トランジスタ101がオンのままである。よって、配線111のロウレベルの電位が配線112に供給されるため、配線112の電位がVHからVLに下降する。

#### 【0094】

その後、ノードND2の電位がトランジスタ102の第1の端子の電位 (VL)とトランジスタ102の閾値電圧 (Vth102)との和よりも高くなると、トランジスタ102がオンになる。よって、配線113のロウレベルの電位がノードND1に供給されるため、ノードND1の電位がVH + Vth101 + からVLに下降する。また、ノードND1の電位がVLになるため、トランジスタ101がオフになる。

#### 【0095】

その後、ノードND2の電位がトランジスタ103のゲートの電位 (VH)からトランジスタ103の閾値電圧 (Vth103)を引いた値まで上昇すると、トランジスタ103がオフになる。よって、ノードND2が浮遊状態になり、ノードND2の電位がVH - Vth103に維持される。

#### 【0096】

なお、図2(A)では、トランジスタ103の第1の端子が配線116と接続されているため、配線116の電位 (例えばVH)がノードND2に供給される。

#### 【0097】

本実施の形態の半導体装置は、上記動作を行うことが可能な接続関係を有することにより、ノードND2の電位をVH + Vth102 + にすることができる。

#### 【0098】

本実施の形態の半導体装置は、ノードND2の電位をVH + Vth102 + にすることにより、トランジスタ102のゲートとソースとの間の電位差をトランジスタ102の閾値電圧よりも大きい値に維持することができる。

#### 【0099】

本実施の形態の半導体装置は、トランジスタ102のゲートとソースとの間の電位差をトランジスタ102の閾値電圧よりも大きい値に維持することにより、ノードND1の電位をVHまで上昇させることができる。

#### 【0100】

本実施の形態の半導体装置は、トランジスタ102のゲートとソースとの間の電位差をトランジスタ102の閾値電圧よりも大きい値に維持することにより、ノードND1における電位の変化に要する時間を短くすることができる。

#### 【0101】

本実施の形態の半導体装置は、ノードND1の電位をVHまで上昇させることにより、ト

10

20

30

40

50

ランジスタ101のゲートとソースとの間の電位差を大きくすることができる。

【0102】

本実施の形態の半導体装置は、トランジスタ101のゲートとソースとの間の電位差を大きくすることにより、配線112における電位の変化に要する時間を短くすることができる。つまり、立ち上がり時間及び立ち下がり時間が短い信号を配線112に出力することができる。

【0103】

本実施の形態の半導体装置は、トランジスタ101及びトランジスタ102のゲートとソースとの間の電位差を大きくすることにより、駆動電圧を小さくすることができる。これにより、消費電力を小さくすることができる。

10

【0104】

本実施の形態の半導体装置は、トランジスタ101及びトランジスタ102のゲートとソースとの間の電位差を大きくすることにより、トランジスタ101及びトランジスタ102のチャネル幅を小さくすることができる。これにより、レイアウト面積を小さくすることができる。

【0105】

本実施の形態の半導体装置は、ノードND1における電位の変化に要する時間、及び配線112における電位の変化に要する時間を短くすることができるため、動作速度の向上を図ることができる。

【0106】

トランジスタ101、トランジスタ102、トランジスタ103及びトランジスタ104のW(Wはチャネル幅) / L(Lはチャネル長)について説明する。ただし、本発明の一態様は、以下に説明するW / Lに限定されない。

20

【0107】

トランジスタ101は配線112を駆動し、トランジスタ102はノードND1を駆動し、トランジスタ103及びトランジスタ104はノードND2を駆動する。そして、配線112の負荷は、ノードND1及びノードND2の負荷よりも大きい場合が多い。よって、トランジスタ101のW / Lは、トランジスタ102、トランジスタ103及びトランジスタ104のW / Lよりも大きいことが好ましい。或いは、回路100が有するトランジスタの中で、トランジスタ101のW / Lが一番大きいことが好ましい。或いは、回路100と同じ基板に設けられるトランジスタの中で、トランジスタ101のW / Lが一番大きいことが好ましい。ただし、トランジスタ101と同じ又は概ね同じW / Lのトランジスタが設けられていてもよい。こうして、トランジスタ101の駆動能力を大きくすることができるため、配線112の負荷を大きくすることができる。さらに、トランジスタ102、トランジスタ103及びトランジスタ104のサイズを小さくするため、レイアウト面積の縮小を図ることができる。

30

【0108】

ノードND1の電位が上昇しても、トランジスタ102のゲートとソースとの間の電位差をトランジスタ102の閾値電圧以上の値に維持することができるため、トランジスタ102のW / Lを小さくすることが可能である。一方、ノードND2の電位が上昇すると、トランジスタ103のゲートとソースとの間の電位差は徐々に小さくなるため、トランジスタ103のW / Lは大きいことが好ましい。よって、トランジスタ103のW / Lは、トランジスタ102のW / Lよりも大きいことが好ましい。こうして、トランジスタ103の駆動能力を大きくすることができるため、ノードND2における電位の変化に要する時間を短くすることができる。さらに、トランジスタ102のサイズを小さくすることができるため、レイアウト面積の縮小を図ることができる。ただし、トランジスタ102のW / Lは、トランジスタ103のW / Lよりも大きくてよい。

40

【0109】

図1、図2、図3、図4、図5及び図6等に図示して説明した回路100、図示せずに説明した回路100、並びにこれらを組み合わせた構成に、追加することが可能なトランジ

50

スタについて説明する。ただし、本発明の一態様は、以下に説明する構成に限定されない。

【0110】

上述する回路100にトランジスタ107を追加してもよい。図10(A)は、図1に示す回路100にトランジスタ107を追加する場合の構成を示す。トランジスタ107は、第1の端子が配線115Bと接続され、第2の端子が配線112と接続される。配線115Bの電位はVLであることが好ましい。ただし、配線115Bの電位はハイレベルとロウレベルとを有していてもよい。トランジスタ107は、配線115Bと配線112との導通又は非導通を制御する。トランジスタ107がオンになると、配線115Bと配線112とが導通し、配線112の電位が配線115Bの電位に基づいて制御される。配線115Bの電位がVL又はロウレベルであれば、配線112の電位はVLになる。また、トランジスタ107は、トランジスタ101乃至104と同じ極性であることが好ましい。

【0111】

期間T1において、トランジスタ107はオンになる。よって、配線115Bの電位が配線112に供給されるため、配線112の電位がVLになる。ただし、期間T1において、トランジスタ107はオフでもよい。

【0112】

期間T2において、トランジスタ107はオンになる。よって、配線115Bの電位が配線112に供給されるため、配線112の電位がVLになる。ただし、期間T2において、トランジスタ107はオフでもよい。

【0113】

期間T3において、トランジスタ107はオフになる。

【0114】

期間T4において、トランジスタ107はオンになる。よって、配線115Bの電位が配線112に供給されるため、配線112の電位がVLになる。ただし、期間T4において、トランジスタ107はオフでもよい。

【0115】

図10(A)は、回路100がトランジスタ107を有することにより、配線112が浮遊状態になることを防止し、配線112の電位を安定させることができる。よって、誤動作の防止を図ることができる。

【0116】

なお、トランジスタ107の第1の端子は、配線111、配線113、配線114又は配線115と接続されてもよい。また、トランジスタ107のゲートは、配線113又は配線114と接続されてもよい。

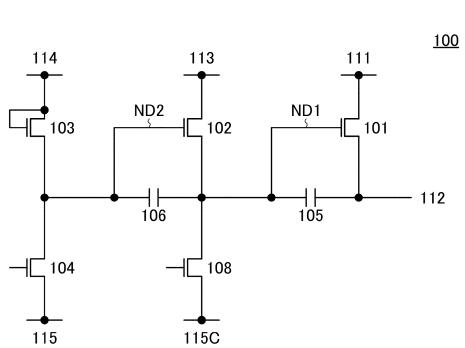

【0117】

上述する回路100にトランジスタ108を追加してもよい。図10(B)は、図1に示す回路100にトランジスタ108を追加する場合の構成を示す。トランジスタ108は、第1の端子が配線115Cと接続され、第2の端子がノードND1と接続される。配線115Cの電位はVLであることが好ましい。ただし、配線115Cの電位はハイレベルとロウレベルとを有していてもよい。トランジスタ108は、配線115CとノードND1との導通又は非導通を制御する。トランジスタ108がオンになると、配線115CとノードND1とが導通し、ノードND1の電位が配線115Cの電位に基づいて制御される。配線115Cの電位がVL又はロウレベルであれば、ノードND1の電位がVLになる。こうして、ノードND1の電位が、トランジスタ101がオフになる値に設定される。また、トランジスタ108は、トランジスタ101乃至104と同じ極性であることが好ましい。

【0118】

期間T1において、トランジスタ108はオンになる。よって、配線115Cの電位がノードND1に供給され、ノードND1の電位がVLになる。ただし、期間T1において、

トランジスタ 108 はオフでもよい。

【0119】

期間 T2 において、トランジスタ 108 はオフになる。

【0120】

期間 T3 において、トランジスタ 108 はオフになる。

【0121】

期間 T4 において、トランジスタ 108 はオンになる。よって、配線 115C の電位がノード ND1 に供給され、ノード ND1 の電位が VL になる。ただし、期間 T4 において、トランジスタ 108 はオフでもよい。

【0122】

図 10 (B) は、回路 100 がトランジスタ 108 を有することにより、ノード ND1 が浮遊状態になることを防止し、ノード ND1 の電位を安定させることができる。よって、誤動作の防止を図ることができる。

10

【0123】

なお、トランジスタ 108 の第 1 の端子は、配線 111、配線 113、配線 114 又は配線 115 と接続されてもよい。また、トランジスタ 108 のゲートは、配線 114 と接続されてもよい。

【0124】

なお、回路 100 にトランジスタ 107 及びトランジスタ 108 の双方が追加される場合、トランジスタ 107 のゲートとトランジスタ 108 のゲートとが接続されてもよい。或いは、トランジスタ 107 の第 1 の端子とトランジスタ 108 の第 1 の端子とが接続されてもよい。

20

【0125】

上述する回路 100 に、トランジスタ 107 又はトランジスタ 108 の一方又は双方を追加するとともに、トランジスタ 109 及びトランジスタ 110 を追加してもよい。図 11 (A) は、図 1 に示す回路 100 に、トランジスタ 107 及びトランジスタ 108 を追加するとともに、トランジスタ 109 及びトランジスタ 110 を追加する場合の構成を示す。トランジスタ 109 は、第 1 の端子が配線 116 と接続され、第 2 の端子がトランジスタ 107 のゲート及びトランジスタ 108 のゲートと接続され、ゲートが配線 114 と接続される。トランジスタ 110 は、第 1 の端子が配線 114 と接続され、第 2 の端子がトランジスタ 107 のゲート及びトランジスタ 108 のゲートと接続され、ゲートがノード ND1 と接続される。トランジスタ 107 のゲート、トランジスタ 108 のゲート、トランジスタ 109 の第 2 の端子又はトランジスタ 110 の第 2 の端子をノード ND3 と示す。トランジスタ 109 は、配線 116 とノード ND3 との導通又は非導通を制御する。トランジスタ 109 がオンになると、配線 116 とノード ND3 とが導通し、ノード ND3 の電位が配線 116 の電位に基づいて制御される。配線 116 の電位が VH 又はハイレベルであれば、ノード ND3 の電位が上昇する。ただし、トランジスタ 109 のゲートが配線 114 と接続されているため、ノード ND3 の電位が配線 114 のハイレベルの電位からトランジスタ 109 の閾値電圧を引いた値まで上昇すると、トランジスタ 109 がオフになる。そして、ノード ND3 が浮遊状態になる。こうして、ノード ND3 の電位が、トランジスタ 107 又はトランジスタ 108 がオンになる値に設定されるとともに、ノード ND3 が浮遊状態になる。また、トランジスタ 110 は配線 114 とノード ND3 との導通又は非導通を制御する。トランジスタ 110 がオンになると、配線 114 とノード ND3 とが導通し、ノード ND3 の電位が配線 114 の電位に基づいて制御される。配線 114 の電位がロウレベルであれば、ノード ND3 の電位が VL まで下降する。こうして、ノード ND3 の電位が、トランジスタ 107 又はトランジスタ 108 がオフになる値に設定される。また、トランジスタ 109 及びトランジスタ 110 は、トランジスタ 101 乃至 104 と同じ極性であることが好ましい。

30

【0126】

期間 T1 において、配線 114 がハイレベルになるため、トランジスタ 109 がオンにな

40

50

る。また、ノードND1の電位がVLになるため、トランジスタ110がオフになる。よって、配線116の電位がノードND3に供給され、ノードND3の電位がVLから上昇する。その後、ノードND3の電位がトランジスタ107の第1の端子の電位(VL)とトランジスタ107の閾値電圧(Vth107)との和よりも高くなると、トランジスタ107がオンになる。また、ノードND3の電位がトランジスタ108の第1の端子の電位(VL)とトランジスタ108の閾値電圧(Vth108)との和よりも高くなると、トランジスタ108がオンになる。その後、ノードND3の電位がトランジスタ109のゲートの電位(VH)からトランジスタ109の閾値電圧(Vth109)を引いた値になると、トランジスタ109がオフになる。よって、ノードND3が浮遊状態になり、ノードND3の電位がVH-Vth109に維持される。

10

#### 【0127】

期間T2において、配線114の電位がロウレベルになるため、トランジスタ109がオフになる。また、ノードND1の電位がトランジスタ110の第1の端子の電位(VL)とトランジスタ110の閾値電圧(Vth110)との和よりも高くなると、トランジスタ110がオンになる。よって、配線114のロウレベルの電位がノードND3に供給され、ノードND3の電位がVH-Vth109からVLに下降する。よって、トランジスタ107及びトランジスタ108はオフになる。

#### 【0128】

期間T3において、配線114の電位がロウレベルのままになるため、トランジスタ109がオフのままになる。また、ノードND1の電位がVH+Vth110+になるため、トランジスタ110がオンのままになる。よって、配線114のロウレベルの電位がノードND3に供給され、ノードND3の電位がVLのままになる。よって、トランジスタ107及びトランジスタ108はオフのままになる。

20

#### 【0129】

期間T4において、配線114の電位がハイレベルになるため、トランジスタ109がオンになる。また、ノードND1の電位がVLになるため、トランジスタ110がオフになる。よって、配線116の電位がノードND3に供給され、ノードND3の電位がVLから上昇する。その後、ノードND3の電位がトランジスタ107の第1の端子の電位(VL)とトランジスタ107の閾値電圧(Vth107)との和よりも高くなると、トランジスタ107がオンになる。また、ノードND3の電位がトランジスタ108の第1の端子の電位(VL)とトランジスタ108の閾値電圧(Vth108)との和よりも高くなると、トランジスタ108がオンになる。

30

#### 【0130】

図11(A)は、回路100がトランジスタ109及びトランジスタ110を有することにより、トランジスタ107又はトランジスタ108を制御する信号を回路100内で生成することができる。よって、信号の数を減らすことができる。

#### 【0131】

なお、図11(B)に示すように、トランジスタ109のゲート及びトランジスタ110の第1の端子は配線117と接続されてもよい。配線117の電位はハイレベル(例えばVH)とロウレベル(例えばVL)と有する。

40

#### 【0132】

なお、トランジスタ109のゲートが配線117と接続され、トランジスタ110の第1の端子が配線114と接続されてもよい。或いは、トランジスタ109のゲートが配線114と接続され、トランジスタ110の第1の端子が配線117と接続されてもよい。

#### 【0133】

なお、トランジスタ109の第2の端子及びトランジスタ110の第2の端子は、トランジスタ107のゲート及びトランジスタ108のゲートのうちトランジスタ107のゲートのみと接続されてもよい。或いは、トランジスタ109の第2の端子及びトランジスタ110の第2の端子は、トランジスタ107のゲート及びトランジスタ108のゲートのうちトランジスタ108のゲートのみと接続されてもよい。

50

## 【0134】

なお、トランジスタ110の第1の端子は配線115、配線115B、配線115C又は配線117と接続されてもよい。

## 【0135】

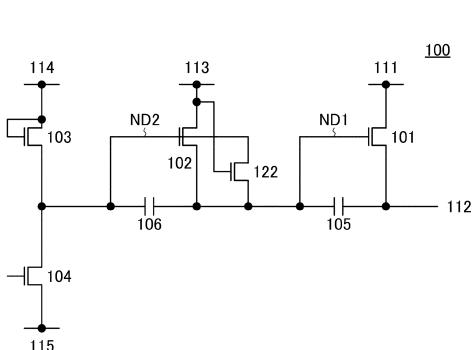

上述する回路100に、トランジスタ121を追加してもよい。図12(A)は、図1に示す回路100に、トランジスタ121を追加する場合の構成を示す。トランジスタ121は、第1の端子が配線112と接続され、第2の端子がノードND1と接続され、ゲートが配線111と接続される。トランジスタ121は、配線112とノードND1との導通又は非導通を制御する。トランジスタ121がオンになると、配線112とノードND1とが導通する。例えば期間T3のように配線112の電位がVLから上昇し、且つノードND1の電位がVHから上昇している場合、ノードND1の電位の上昇が抑制されるとともに、配線112の電位の変化に要する時間が短くなる。ただし、トランジスタ121のゲートが配線111と接続されているため、配線112の電位が配線111のハイレベルの電位からトランジスタ121の閾値電圧を引いた値になると、トランジスタ121がオフになる。また、トランジスタ121は、トランジスタ101乃至104と同じ極性であることが好ましい。

10

## 【0136】

期間T1において、配線111がロウレベルになるため、トランジスタ121がオフになる。

20

## 【0137】

期間T2において、配線111がロウレベルになるため、トランジスタ121がオフになる。

## 【0138】

期間T3において、配線111がハイレベルになるため、トランジスタ121がオンになる。ただし、配線112の電位がトランジスタ121のゲートの電位(VH)からトランジスタ121の閾値電圧(Vth121)を引いた値まで上昇すると、トランジスタ121がオフになる。

## 【0139】

期間T4において、配線111がロウレベルになるため、トランジスタ121がオフになる。

30

## 【0140】

図12(A)は、回路100がトランジスタ121を有することにより、ノードND1の電位が高くなり過ぎることを防止することができる。よって、ノードND1と接続されるトランジスタの劣化の抑制又は破壊の防止等を図ることができる。

## 【0141】

上述する回路100に、トランジスタ122を追加してもよい。図12(B)は、図1に示す回路100に、トランジスタ122を追加する場合の構成を示す。トランジスタ122は、第1の端子がノードND1と接続され、第2の端子がノードND2と接続され、ゲートが配線113と接続される。トランジスタ122は、ノードND1とノードND2との導通又は非導通を制御する。トランジスタ122がオンになると、ノードND1とノードND2とが導通する。例えば、期間T2のようにノードND1の電位がVLから上昇し、且つノードND2の電位がVH - Vth103から上昇している場合、ノードND2の電位の上昇が抑制されるとともに、ノードND1の電位の変化に要する時間が短くなる。ただし、トランジスタ122のゲートが配線113と接続されているため、ノードND1の電位が配線113のハイレベルの電位からトランジスタ122の閾値電圧を引いた値になると、トランジスタ122がオフになる。また、トランジスタ122は、トランジスタ101乃至104と同じ極性であることが好ましい。

40

## 【0142】

期間T1において、配線113がロウレベルになるため、トランジスタ122がオフになる。

50

## 【0143】

期間T2において、配線113がハイレベルになるため、トランジスタ122がオンになる。ただし、ノードND1の電位がトランジスタ122のゲートの電位(VH)からトランジスタ122の閾値電圧(Vth122)を引いた値まで上昇すると、トランジスタ122がオフになる。

## 【0144】

期間T3において、配線113がロウレベルになるため、トランジスタ122がオフになる。

## 【0145】

期間T4において、配線113がロウレベルになるため、トランジスタ122がオフになる。 10

## 【0146】

図12(B)は、回路100がトランジスタ122を有することにより、ノードND2の電位が高くなり過ぎることを防止することができる。よって、ノードND2と接続されるトランジスタの劣化の抑制又は破壊の防止等を図ることができる。

## 【0147】

上述する回路100に、トランジスタ123を追加してもよい。図13(A)は、図1に示す回路100に、トランジスタ123を追加する場合の構成を示す。トランジスタ123は、第1の端子が配線111と接続され、第2の端子がノードND1と接続される。トランジスタ123は、配線111とノードND1との導通又は非導通を制御する。トランジスタ123がオンになると、配線111とノードND1とが導通し、配線111の電位がノードND1に供給される。配線111の電位がロウレベルであれば、ノードND1の電位がVLになる。このように、ノードND1の電位が、トランジスタ101がオフになる値に設定される。また、トランジスタ123は、トランジスタ101乃至104と同じ極性であることが好ましい。

## 【0148】

期間T0において、トランジスタ123がオンになる。よって、配線111のロウレベルの電位がノードND1に供給され、ノードND1の電位がVLになる。

## 【0149】

期間T1、期間T2、期間T3及び期間T4において、トランジスタ123がオフになる。 30

## 【0150】

図13(A)は、回路100がトランジスタ123を有することにより、ノードND1の電位をVLに設定することができる。よって、誤動作の防止を図ることができる。

## 【0151】

上述する回路100に、トランジスタ124を追加してもよい。図13(B)は、図1に示す回路100に、トランジスタ124を追加する場合の構成を示す。トランジスタ124は、第1の端子が配線113と接続され、第2の端子がノードND2と接続される。トランジスタ124は、配線113とノードND2との導通又は非導通を制御する。トランジスタ124がオンになると、配線113とノードND2とが導通し、配線113の電位がノードND2に供給される。配線113の電位がロウレベルであれば、ノードND2の電位がVLになる。このように、ノードND2の電位が、トランジスタ102がオフになる値に設定される。また、トランジスタ124は、トランジスタ101乃至104と同じ極性であることが好ましい。

## 【0152】

期間T0において、トランジスタ124がオンになる。よって、配線113のロウレベルの電位がノードND2に供給され、ノードND2の電位がVLになる。

## 【0153】

期間T1、期間T2、期間T3及び期間T4において、トランジスタ124がオフになる。 50

## 【0154】

図13(B)は、回路100がトランジスタ124を有することにより、ノードND2の電位をVLに設定することができる。よって、誤動作の防止を図ることができる。

## 【0155】

なお、回路100にトランジスタ123及びトランジスタ124の双方が追加される場合、トランジスタ123のゲートとトランジスタ124のゲートとが接続されてもよい。

## 【0156】

図1、図2、図3、図4、図5、図6、図10、図11、図12及び図13等に図示して説明した回路100、並びに図示せずに説明した回路100を自由に組み合わせることが可能である。

10

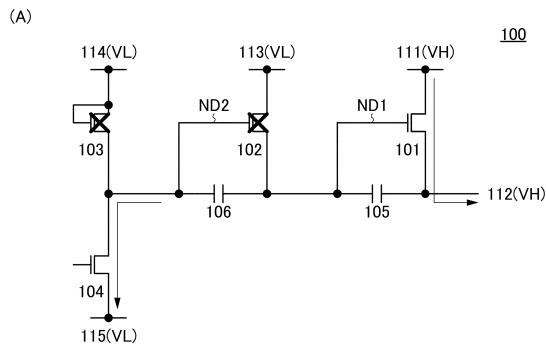

## 【0157】

図14(A)は、トランジスタ103の第1の端子及びゲートが配線113と接続される構成(図3(A)参照)と、トランジスタ104のゲートが配線111と接続される構成(図5(A)参照)と、を組み合わせた場合の構成である。

## 【0158】

図14(B)は、トランジスタ104のゲートが配線111と接続される構成(図5(A)参照)と、トランジスタ108を追加する構成(図10(B)参照)と、トランジスタ109及びトランジスタ110を追加する構成(図11(B)参照)と、を組み合わせた場合の構成である。

20

## 【0159】

なお、本実施の形態は他の実施の形態の記載と適宜組み合わせることができる。よって、本実施の形態の中で述べる内容(一部の内容でもよい)は、その実施の形態で述べる別のある内容(一部の内容でもよい)、及び/又は、一つ若しくは複数の別の実施の形態で述べる内容(一部の内容でもよい)に対して、適用、組み合わせ、又は置き換えなどを行うことができる。なお、実施の形態の中で述べる内容とは、各々の実施の形態において、様々な図を用いて述べる内容、又は明細書に記載される文章を用いて述べる内容のことである。また、ある一つの実施の形態において述べる図(一部でもよい)は、その図の別の部分、その実施の形態において述べる別の図(一部でもよい)、及び/又は、一つ若しくは複数の別の実施の形態において述べる図(一部でもよい)に対して、組み合わせることにより、さらに多くの図を構成させることができる。これは、以下の実施の形態においても同様である。

30

## 【0160】

## (実施の形態2)

本実施の形態では、本発明の一態様に係る半導体装置について説明する。

## 【0161】

本発明の一態様に係る半導体装置の構成について、図15を参照して説明する。ただし、本発明の一態様は、以下に説明する構成に限定されない。

## 【0162】

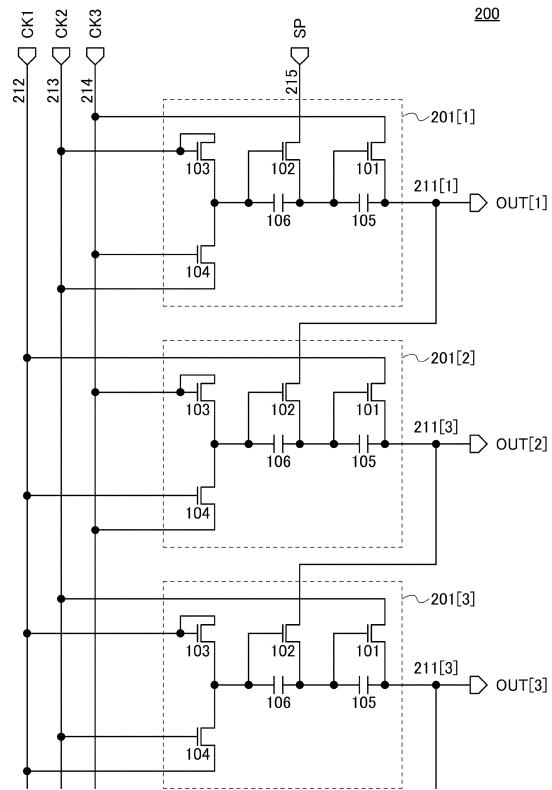

図15に示す半導体装置は、回路200を有する。回路200は、配線212、配線213、配線214及び配線215の電位に基づいて、N(Nは3以上の自然数)本の配線211(配線211[1]乃至[N]とも示す)の電位を制御する機能を有する。回路200は、配線212、配線213、配線214及び配線215の電位に基づいた信号を配線211[1]乃至[N]のそれぞれに出力する。そして、当該信号により、配線211[1]乃至[N]のそれぞれの電位が制御される。

40

## 【0163】

具体的には、回路200は、配線212、配線213、配線214及び配線215の電位に基づいて、配線211[1]乃至[N]の電位を順次アクティブにする機能、即ち配線211[1]乃至[N]の電位を順次ハイレベル又はロウレベルにする機能を有する。図16には、回路200が、配線212、配線213、配線214及び配線215の電位に基づいて、配線211[1]乃至[N]の電位を順次ハイレベルにする場合のタイミング

50

チャートを示す。このように、回路 200 は、シフトレジスタとしての機能を有する。

【0164】

なお、配線 212、配線 213、配線 214 及び配線 215 の電位は、各配線に信号又は電圧等が入力されることによって制御される。例えば、配線 212 には信号 CK1 が入力され、配線 213 には信号 CK2 が入力され、配線 214 には信号 CK3 が入力され、配線 215 には信号 SP が入力され、配線 211 [1] 乃至 [N] のそれぞれには信号 OUT [1] 乃至 [N] が出力される。即ち、信号 OUT [1] 乃至 [N] は、信号 CK1、信号 CK2、信号 CK3 及び信号 SP に基づいた値を有する。信号 CK1、信号 CK2 及び信号 CK3 としては、互いに位相が異なるクロック信号がある。また、信号 SP としては、スタートパルスがある。

10

【0165】

回路 200 は、N 個の回路 201 (回路 201 [1] 乃至 [N] とも示す) を有する。回路 201 [1] 乃至 [N] のそれぞれは、実施の形態 1 において説明する回路 100 に相当する。図 15 では、回路 201 [1] 乃至 [N] のそれぞれに図 5 (A) に示す回路 100 が用いられている。

【0166】

回路 201 [2m + 1] (m は 0 又は正の整数) において、トランジスタ 101 の第 1 の端子及びトランジスタ 104 のゲートは配線 214 と接続される。よって、配線 214 は配線 111 に相当する。また、トランジスタ 101 の第 2 の端子は配線 211 [2m + 1] と接続される。よって、配線 211 [2m + 1] は配線 112 に相当する。また、トランジスタ 102 の第 1 の端子は配線 215 又は配線 211 [2m] と接続される。よって、配線 215 又は配線 211 [2m] は、配線 113 に相当する。また、トランジスタ 103 の第 1 の端子及びゲートは、配線 212 と接続される。よって、配線 212 は、配線 114 に相当する。また、トランジスタ 104 の第 1 の端子は配線 213 と接続される。よって、配線 213 は配線 115 に相当する。

20

【0167】

回路 201 [2m + 2] において、トランジスタ 101 の第 1 の端子及びトランジスタ 104 のゲートは配線 212 と接続される。よって、配線 212 は配線 111 に相当する。また、トランジスタ 101 の第 2 の端子は配線 211 [2m + 2] と接続される。よって、配線 211 [2m + 2] は配線 112 に相当する。また、トランジスタ 102 の第 1 の端子は配線 211 [2m + 1] と接続される。よって、配線 211 [2m + 1] は、配線 113 に相当する。また、トランジスタ 103 の第 1 の端子及びゲートは、配線 213 と接続される。よって、配線 213 は、配線 114 に相当する。また、トランジスタ 104 の第 1 の端子は配線 214 と接続される。よって、配線 214 は配線 115 に相当する。

30

【0168】

回路 201 [2m + 3] において、トランジスタ 101 の第 1 の端子及びトランジスタ 104 のゲートは配線 213 と接続される。よって、配線 213 は配線 111 に相当する。また、トランジスタ 101 の第 2 の端子は配線 211 [2m + 3] と接続される。よって、配線 211 [2m + 3] は配線 112 に相当する。また、トランジスタ 102 の第 1 の端子は配線 211 [2m + 2] と接続される。よって、配線 211 [2m + 2] は、配線 113 に相当する。また、トランジスタ 103 の第 1 の端子及びゲートは、配線 214 と接続される。よって、配線 214 は、配線 114 に相当する。また、トランジスタ 104 の第 1 の端子は配線 212 と接続される。よって、配線 212 は配線 115 に相当する。

40

【0169】

なお、図 17 に示すように、回路 201 [1] 乃至 [N] のそれぞれにおいて、トランジスタ 104 の第 1 の端子は配線 216 と接続されてもよい。配線 216 は配線 115 に相当する。また、配線 216 には、電圧 VSS を供給してもよい。電圧 VSS は、例えば信号 CK1、信号 CK2、信号 CK3 及び信号 SP のロウレベルに対応する値 (等しい又は概ね等しい値) を有する。

【0170】

50

なお、図18に示すように、回路201[2m+1]において、トランジスタ103の第1の端子及びゲートは、配線213と接続されてもよい。また、回路201[2m+2]において、トランジスタ103の第1の端子及びゲートは、配線214と接続されてもよい。また、回路201[2m+3]において、トランジスタ103の第1の端子及びゲートは、配線212と接続されてもよい。即ち、回路201[i](iは2乃至Nのいずれか一)において、トランジスタ103の第1の端子及びゲートは、配線212、配線213及び配線214のうち回路201[i-1]のトランジスタ101の第1の端子が接続される配線と接続されてもよい。

#### 【0171】

なお、回路201[1]乃至[N]のそれぞれにトランジスタ103の第1の端子又はゲートが配線116と接続される回路100(例えば図2(A)、図2(B)、図3(B)参照)を採用する場合、回路201[1]乃至[N]のそれぞれのトランジスタ103の第1の端子又はゲートが接続される新たな配線を設けてもよい。

10

#### 【0172】

なお、本実施の形態は他の実施の形態の記載と適宜組み合わせができる。よって、本実施の形態の中で述べる内容(一部の内容でもよい)は、その実施の形態で述べる別の内容(一部の内容でもよい)、及び/又は、一つ若しくは複数の別の実施の形態で述べる内容(一部の内容でもよい)に対して、適用、組み合わせ、又は置き換えなどを行うことができる。なお、実施の形態の中で述べる内容とは、各々の実施の形態において、様々な図を用いて述べる内容、又は明細書に記載される文章を用いて述べる内容のことである。また、ある一つの実施の形態において述べる図(一部でもよい)は、その図の別の部分、その実施の形態において述べる別の図(一部でもよい)、及び/又は、一つ若しくは複数の別の実施の形態において述べる図(一部でもよい)に対して、組み合わせることにより、さらに多くの図を構成させることができる。これは、以下の実施の形態においても同様である。

20

#### 【0173】

##### (実施の形態3)

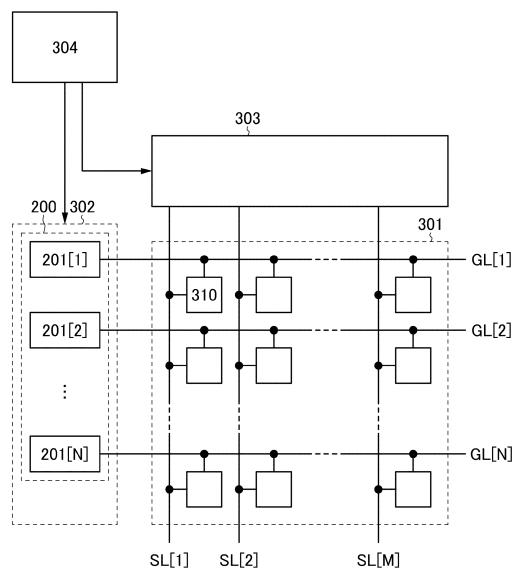

本実施の形態では、本発明の一態様に係る表示装置について説明する。

#### 【0174】

本発明の一態様に係る表示装置の構成について、図19を参照して説明する。ただし、本発明の一態様は、以下に説明する構成に限定されない。

30

#### 【0175】

図19に示す表示装置は、画素部301、走査線駆動回路302及び信号線駆動回路303を有する。

#### 【0176】

画素部301では、N本の走査線GL(走査線GL[1]乃至[N]とも示す)と、M(Mは2以上の自然数)本の信号線SL(信号線SL[1]乃至[M]とも示す)とが交差するように配置されている。また、各交差部には、画素310が配置されている。

#### 【0177】

画素310は、表示素子及びトランジスタを少なくとも有する。表示素子としては、発光素子、液晶素子がある。発光素子としては、EL素子がある。

40

#### 【0178】

例えば、本明細書等において、表示素子、表示素子を有する装置である表示装置、発光素子、及び発光素子を有する装置である発光装置は、様々な形態を用いること、又は様々な素子を有することが出来る。表示素子、表示装置、発光素子又は発光装置は、例えば、EL(エレクトロルミネッセンス)素子(有機物及び無機物を含むEL素子、有機EL素子、無機EL素子)、LED(白色LED、赤色LED、緑色LED、青色LEDなど)、トランジスタ(電流に応じて発光するトランジスタ)、電子放出素子、液晶素子、電子インク、電気泳動素子、グレーティングライトバルブ(GLV)、プラズマディスプレイ(PDP)、MEMS(マイクロ・エレクトロ・メカニカル・システム)を用いた表示素

50

子、デジタルマイクロミラーデバイス（DMD）、DMS（デジタル・マイクロ・シャッター）、IMOD（インターフェアレンス・モジュレーション）素子、シャッター方式のMEMS表示素子、光干渉方式のMEMS表示素子、エレクトロウェッティング素子、圧電セラミックディスプレイ、カーボンナノチューブを用いた表示素子、などの少なくとも一つを有している。これらの他にも、電気的または磁気的作用により、コントラスト、輝度、反射率、透過率などが変化する表示媒体を有していても良い。EL素子を用いた表示装置の一例としては、ELディスプレイなどがある。電子放出素子を用いた表示装置の一例としては、フィールドエミッショニスプレイ（FED）又はSED方式平面型ディスプレイ（SED：Surface-conduction Electron-emitter Display）などがある。液晶素子を用いた表示装置の一例としては、液晶ディスプレイ（透過型液晶ディスプレイ、半透過型液晶ディスプレイ、反射型液晶ディスプレイ、直視型液晶ディスプレイ、投射型液晶ディスプレイ）などがある。電子インク、又は電気泳動素子を用いた表示装置の一例としては、電子ペーパーなどがある。なお、半透過型液晶ディスプレイや反射型液晶ディスプレイを実現する場合には、画素電極の一部、または、全部が、反射電極としての機能を有するようにすればよい。例えば、画素電極の一部、または、全部が、アルミニウム、銀、などを有するようにすればよい。さらに、その場合、反射電極の下に、SRAMなどの記憶回路を設けることも可能である。これにより、さらに、消費電力を低減することができる。なお、LEDを用いる場合、LEDの電極や窒化物半導体の下に、グラフェンやグラファイトを配置してもよい。グラフェンやグラファイトは、複数の層を重ねて、多層膜としてもよい。このように、グラフェンやグラファイトを設けることにより、その上に、窒化物半導体、例えば、結晶を有するn型GaN半導体層などを容易に成膜することができる。さらに、その上に、結晶を有するp型GaN半導体層などを設けて、LEDを構成することができる。なお、グラフェンやグラファイトと、結晶を有するn型GaN半導体層との間に、AlN層を設けてもよい。なお、LEDが有するGaN半導体層は、MOCVDで成膜してもよい。ただし、グラフェンを設けることにより、LEDが有するGaN半導体層は、スパッタ法で成膜することも可能である。

#### 【0179】

走査線駆動回路302は、走査線GL[1]乃至[N]の電位を制御する機能を有する。走査線駆動回路302は、走査線GL[1]乃至[N]のそれぞれに走査信号を出力する。そして、走査信号により、走査線GL[1]乃至[N]のそれぞれの電位が制御される。また、走査線駆動回路302は、実施の形態1において説明する回路100又は実施の形態2において説明する回路200を有することが可能である。そのような場合、例えば走査線GL[1]乃至[N]のそれぞれは配線112に対応する。或いは、走査線GL[1]乃至[N]は配線211[1]乃至[N]にそれぞれ対応する。また、走査線駆動回路302を制御するための信号（クロック信号及びスタートパルス等、又は信号CK1、信号CK2、信号CK3及び信号SP等）は、回路304から供給される。

#### 【0180】

信号線駆動回路303は、信号線SL[1]乃至[M]の電位又は電流を制御する機能を有する。信号線駆動回路303は、信号線SL[1]乃至[M]のそれぞれにビデオ信号を出力する。そして、ビデオ信号により、信号線SL[1]乃至[M]のそれぞれの電位が制御される。また、信号線駆動回路303は、実施の形態1において説明する回路100又は実施の形態2において説明する回路200を有することが可能である。また、信号線駆動回路303を制御するための信号（例えばクロック信号、スタートパルス、ビデオ信号等）は、回路304から供給される。

#### 【0181】

なお、回路304は、走査線駆動回路302及び信号線駆動回路303に信号を供給するため、タイミングコントローラとしての機能を有する。また、回路304は、走査線駆動回路302及び信号線駆動回路303に電圧を供給してもよい。そのような場合、回路304は、電源回路としての機能を有する。

## 【0182】

なお、走査線駆動回路302は、信号線駆動回路303よりも動作速度が遅い。そのため、走査線駆動回路302が有するトランジスタは、酸化物半導体、多結晶シリコン又は非晶質シリコンをチャネル形成領域に有することが好ましい。一方で、信号線駆動回路303が有するトランジスタは、単結晶シリコンをチャネル形成領域に有することが好ましい。よって、画素部301及び走査線駆動回路302を同じ基板に設け、信号線駆動回路303は別の基板に設けることが好ましい。ただし、画素部301、走査線駆動回路302及び信号線駆動回路303を同じ基板に設けてもよい。

## 【0183】

なお、走査線駆動回路302に実施の形態1において説明する回路100又は実施の形態2において説明する回路200を採用することにより、走査線駆動回路302が有するトランジスタを全て同じ極性にすることができる。よって、画素部301及び走査線駆動回路302が同じ基板に設けられる場合、当該基板に設けられるトランジスタの全ては同じ極性であることが好ましい。

10

## 【0184】

なお、走査線駆動回路302に実施の形態1において説明する回路100又は実施の形態2において説明する回路200を採用することにより、走査線駆動回路302のレイアウト面積を小さくすることができる。よって、画素310の解像度を高くすることができる。また、額縁を小さくすることができる。

## 【0185】

20

なお、本実施の形態は他の実施の形態の記載と適宜組み合わせることができる。よって、本実施の形態の中で述べる内容（一部の内容でもよい）は、その実施の形態で述べる別のある内容（一部の内容でもよい）、及び／又は、一つ若しくは複数の別の実施の形態で述べる内容（一部の内容でもよい）に対して、適用、組み合わせ、又は置き換えなどを行うことができる。なお、実施の形態の中で述べる内容とは、各々の実施の形態において、様々な図を用いて述べる内容、又は明細書に記載される文章を用いて述べる内容のことである。また、ある一つの実施の形態において述べる図（一部でもよい）は、その図の別の部分、その実施の形態において述べる別の図（一部でもよい）、及び／又は、一つ若しくは複数の別の実施の形態において述べる図（一部でもよい）に対して、組み合わせることにより、さらに多くの図を構成させることができる。これは、以下の実施の形態においても同様である。

30

## 【0186】

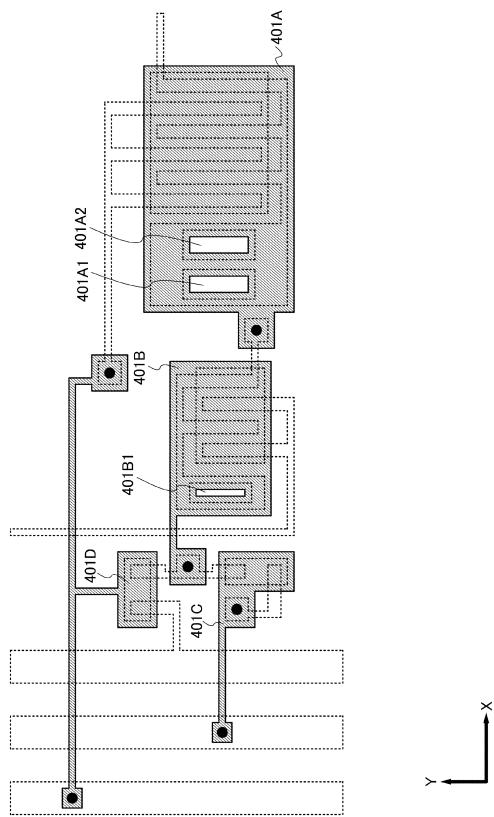

## (実施の形態4)

本実施の形態では、実施の形態1において説明する半導体装置の構造について説明する。

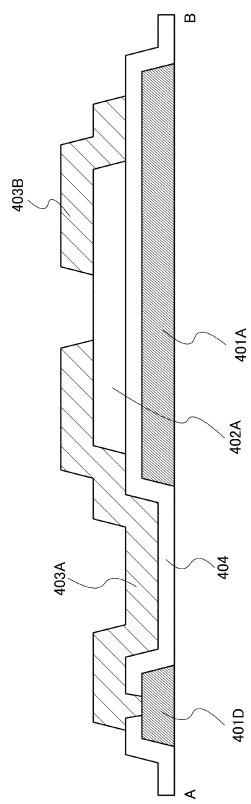

## 【0187】

図20は、図5（A）に示す半導体装置の上面図である。また、図23は、図20に示す上面図のA-B断面である。ただし、本発明の一態様は、以下に説明する構成に限定されない。

## 【0188】

40

図20に示す半導体装置は、導電層401A乃至401D、半導体層402A乃至402D、導電層403A乃至403I、及び絶縁層404を有する。図21には、導電層401A乃至401Dのみを示す。図22には、導電層403A乃至403Iのみを示す。なお、X方向は、Y方向と略垂直な方向である。或いは、X方向は、Y方向と交差する方向である。

## 【0189】

絶縁層404は、トランジスタ101のゲート絶縁層となる領域と、トランジスタ102のゲート絶縁層となる領域と、トランジスタ103のゲート絶縁層となる領域と、トランジスタ104のゲート絶縁層となる領域と、を有する。また、絶縁層404は、導電層401Aと半導体層402Aとに挟まれている領域と、導電層401Bと半導体層402Bとに挟まれている領域と、導電層401Cと半導体層402Cとに挟まれている領域と、

50

導電層 401D と半導体層 402D とに挟まれている領域と、を有する。なお、図中の黒い丸は、絶縁層 404 が有するコンタクトホールを示す。

【0190】

絶縁層 404 としては、プラズマ化学気相堆積 (PECVD: (Plasma Enhanced Chemical Vapor Deposition)) 法、スパッタリング法等により、酸化シリコン膜、酸化窒化シリコン膜、窒化酸化シリコン膜、窒化シリコン膜、酸化アルミニウム膜、酸化ハフニウム膜、酸化イットリウム膜、酸化ジルコニウム膜、酸化ガリウム膜、酸化タンタル膜、酸化マグネシウム膜、酸化ランタン膜、酸化セリウム膜および酸化ネオジム膜を一種以上含む絶縁層を、それぞれ用いることができる。

【0191】

導電層 401A 乃至 401D は同層である。或いは、導電層 401A 乃至 401D は同じ材料を有する。或いは、導電層 401A 乃至 401D は同一の導電膜を加工する工程を経て形成されたものである。

【0192】

導電層 401A 乃至 401D としては、クロム (Cr)、銅 (Cu)、アルミニウム (Al)、金 (Au)、銀 (Ag)、亜鉛 (Zn)、モリブデン (Mo)、タンタル (Ta)、チタン (Ti)、タンゲステン (W)、マンガン (Mn)、ニッケル (Ni)、鉄 (Fe)、コバルト (Co) から選ばれた金属元素、または上述した金属元素を成分とする合金か、上述した金属元素を組み合わせた合金等を用いてそれぞれ形成することができる。

【0193】

また、導電層 401A 乃至 401D は、単層構造でも、二層以上の積層構造としてもよい。例えば、シリコンを含むアルミニウム膜の単層構造、アルミニウム膜上にチタン膜を積層する二層構造、窒化チタン膜上にチタン膜を積層する二層構造、窒化チタン膜上にタンゲステン膜を積層する二層構造、窒化タンタル膜または窒化タンゲステン膜上にタンゲステン膜を積層する二層構造、チタン膜と、そのチタン膜上にアルミニウム膜を積層し、さらにその上にチタン膜を形成する三層構造等がある。また、アルミニウムに、チタン、タンタル、タンゲステン、モリブデン、クロム、ネオジム、スカンジウムから選ばれた一または複数を組み合わせた合金膜、もしくは窒化膜を用いてもよい。

【0194】

また、導電層 401A 乃至 401D としては、インジウム錫酸化物、酸化タンゲステンを含むインジウム酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム亜鉛酸化物、酸化シリコンを添加したインジウム錫酸化物等の透光性を有する導電性材料を適用することもできる。

【0195】

また、導電層 401A 乃至 401D には、Cu-X 合金膜 (X は、Mn、Ni、Cr、Fe、Co、Mo、Ta、または Ti) を適用してもよい。Cu-X 合金膜を用いることでのウエットエッティングプロセスで加工できるため、製造コストを抑制することが可能となる。

【0196】

導電層 401A は、トランジスタ 101 のゲート電極となる領域と、容量素子 105 の第 2 の電極となる領域と、を有する。また、導電層 401A は、開口部 401A1 と、開口部 401A2 と、を有する。開口部 401A1 及び開口部 401A2 は、略 Y 方向に沿う長尺を有する。

【0197】

導電層 401B は、トランジスタ 102 のゲート電極となる領域と、容量素子 106 の第 2 の電極となる領域と、を有する。また、導電層 401B は、開口部 401B1 を有する。開口部 401B1 は、略 Y 方向に沿う長尺を有する。

【0198】

導電層 401C は、トランジスタ 103 のゲート電極となる領域を有する。

10

20

30

40

50

## 【0199】

導電層401Dは、トランジスタ104のゲート電極となる領域を有する。

## 【0200】

なお、導電層401Aの面積は、導電層401B、導電層401C及び導電層401Dの面積よりも大きい。また、導電層401Bの面積は、導電層401C及び導電層401Dの面積よりも大きい。

## 【0201】

なお、開口部401A1及び開口部401A2の面積は、開口部401B1の面積よりも大きい。また、開口部401A1及び開口部401A2の幅は、開口部401B1の幅よりも大きい。また、開口部401A1及び開口部401A2の長尺方向の長さは、開口部401B1の長尺方向の長さよりも長い。

10

## 【0202】

なお、導電層401Aには3つ以上の開口部を設けてもよく、導電層401Bには2つ以上の開口部を設けてもよい。ただし、導電層401Aが有する開口部の数は、導電層401Bが有する開口部の数よりも多いことが好ましい。

## 【0203】

半導体層402A乃至402Dは同層である。或いは、半導体層402A乃至402Dは同じ材料を有する。或いは、半導体層402A乃至402Dは同一の半導体膜を加工する工程を経て形成されたものである。

20

## 【0204】

半導体層402A乃至402Dとしては、単結晶半導体又は非単結晶半導体がある。非単結晶半導体としては、非単結晶シリコン又は非単結晶ゲルマニウムがある。非単結晶シリコンとしては、非晶質シリコン、微結晶シリコン又は多結晶シリコンがあり、非単結晶ゲルマニウムとしては、非晶質ゲルマニウム、微結晶ゲルマニウム又は多結晶ゲルマニウムなどがある。

## 【0205】

特に、半導体層402A乃至402Dとしては、酸化物半導体膜を用いることが好ましい。酸化物半導体膜としては、In-M (Mは、Ti、Ga、Sn、Y、Zr、La、Ce、Nd、またはHfを表す)酸化物、In-M-Zn酸化物を用いることができる。とくに、酸化物半導体膜としては、In-M-Zn酸化物を用いると好ましい。酸化物半導体膜がIn-M-Zn酸化物の場合、In-M-Zn酸化物を成膜するために用いるスパッタリングターゲットの金属元素の原子数比は、In-M-Znを満たすことが好ましい。このようなスパッタリングターゲットの金属元素の原子数比として、In:M:Zn = 1:1:1、In:M:Zn = 1:1:1.2、In:M:Zn = 2:1:3、In:M:Zn = 3:1:2、In:M:Zn = 4:2:4.1が好ましい。また、酸化物半導体膜がIn-M-Zn酸化物の場合、スパッタリングターゲットとしては、多結晶のIn-M-Zn酸化物を含むターゲットを用いると好ましい。多結晶のIn-M-Zn酸化物を含むターゲットを用いることで、結晶性を有する酸化物半導体膜を形成しやすくなる。なお、成膜される酸化物半導体膜の原子数比はそれぞれ、誤差として上記のスパッタリングターゲットに含まれる金属元素の原子数比のプラスマイナス40%の変動を含む。例えば、スパッタリングターゲットとして、原子数比がIn:Ga:Zn = 4:2:4.1を用いる場合、成膜される酸化物半導体膜の原子数比は、In:Ga:Zn = 4:2:3近傍となる場合がある。

30

## 【0206】

酸化物半導体膜は、エネルギーギャップが2eV以上、好ましくは2.5eV以上、より好ましくは3eV以上である。このように、エネルギーギャップの広い酸化物半導体を用いることで、トランジスタのオフ電流を低減することができる。

40

## 【0207】

酸化物半導体膜の厚さは、それぞれ3nm以上200nm以下、好ましくは3nm以上100nm以下、さらに好ましくは3nm以上50nm以下とする。

50

## 【0208】

酸化物半導体膜としては、キャリア密度の低い酸化物半導体膜を用いる。例えば、酸化物半導体膜は、キャリア密度が $1 \times 10^{17}$ 個/ $\text{cm}^3$ 以下、好ましくは $1 \times 10^{15}$ 個/ $\text{cm}^3$ 以下、さらに好ましくは $1 \times 10^{13}$ 個/ $\text{cm}^3$ 以下、より好ましくは $1 \times 10^{11}$ 個/ $\text{cm}^3$ 以下とする。また、酸化物半導体膜は、キャリア密度が $1 \times 10^5$ 個/ $\text{cm}^3$ 以上、より好ましくは $1 \times 10^7$ 個/ $\text{cm}^3$ 以上であってもよい。

## 【0209】

なお、これらに限らず、必要とするトランジスタの半導体特性及び電気特性（電界効果移動度、しきい値電圧等）に応じて適切な組成のものを用いればよい。また、必要とするトランジスタの半導体特性を得るために、酸化物半導体膜のキャリア密度や不純物濃度、欠陥密度、金属元素と酸素の原子数比、原子間距離、密度等を適切なものとすることが好ましい。

10

## 【0210】

なお、酸化物半導体膜としては、それぞれ不純物濃度が低く、欠陥準位密度の低い酸化物半導体膜を用いることで、さらに優れた電気特性を有するトランジスタを作製することができ好ましい。ここでは、不純物濃度が低く、欠陥準位密度の低い（酸素欠損の少ない）ことを高純度真性または実質的に高純度真性とよぶ。高純度真性または実質的に高純度真性である酸化物半導体膜は、キャリア発生源が少ないため、キャリア密度を低くすることができます。従って、該酸化物半導体膜にチャネル領域が形成されるトランジスタは、しきい値電圧がマイナスとなる電気特性（ノーマリーオンともいう。）になることが少ない。また、高純度真性または実質的に高純度真性である酸化物半導体膜は、欠陥準位密度が低いため、トラップ準位密度も低くなる場合がある。また、高純度真性または実質的に高純度真性である酸化物半導体膜は、オフ電流が著しく小さく、チャネル幅が $1 \times 10^6 \mu\text{m}$ でチャネル長 $L$ が $10 \mu\text{m}$ の素子であっても、ソース電極とドレイン電極間の電圧（ドレイン電圧）が $1\text{V}$ から $10\text{V}$ の範囲において、オフ電流が、半導体パラメータアナライザの測定限界以下、すなわち $1 \times 10^{-13}\text{A}$ 以下という特性を得ることができる。

20

## 【0211】

したがって、上記高純度真性、または実質的に高純度真性の酸化物半導体膜にチャネル領域が形成されるトランジスタは、電気特性の変動が小さく、信頼性の高いトランジスタとすることができます。なお、酸化物半導体膜のトラップ準位に捕獲された電荷は、消失するまでに要する時間が長く、あたかも固定電荷のように振る舞うことがある。そのため、トラップ準位密度の高い酸化物半導体膜にチャネル領域が形成されるトランジスタは、電気特性が不安定となる場合がある。不純物としては、水素、窒素、アルカリ金属、またはアルカリ土類金属等がある。

30

## 【0212】

酸化物半導体膜に含まれる水素は、金属原子と結合する酸素と反応して水になると共に、酸素が脱離した格子（または酸素が脱離した部分）に酸素欠損を形成する。該酸素欠損に水素が入ることで、キャリアである電子が生成される場合がある。また、水素の一部が金属原子と結合する酸素と結合して、キャリアである電子を生成することができる。従って、水素が含まれている酸化物半導体膜を用いたトランジスタはノーマリーオン特性となりやすい。このため、酸化物半導体膜は水素ができる限り低減されていることが好ましい。具体的には、酸化物半導体膜において、S I M S 分析により得られる水素濃度を、 $2 \times 10^{20}\text{atoms}/\text{cm}^3$ 以下、好ましくは $5 \times 10^{19}\text{atoms}/\text{cm}^3$ 以下、より好ましくは $1 \times 10^{19}\text{atoms}/\text{cm}^3$ 以下、 $5 \times 10^{18}\text{atoms}/\text{cm}^3$ 以下、好ましくは $1 \times 10^{18}\text{atoms}/\text{cm}^3$ 以下、より好ましくは $5 \times 10^{17}\text{atoms}/\text{cm}^3$ 以下としてもよい。また、酸化物半導体膜において、S I M S 分析により得られる水素濃度を、 $1 \times 10^{16}\text{atoms}/\text{cm}^3$ 以上、より好ましくは $1 \times 10^{17}\text{atoms}/\text{cm}^3$ 以上としてもよい。

40

## 【0213】

酸化物半導体膜において、第14族元素の一つであるシリコンや炭素が含まれると、酸化

50

物半導体膜において酸素欠損が増加し、n型化してしまう。このため、酸化物半導体膜におけるシリコンや炭素の濃度と、酸化物半導体膜との界面近傍のシリコンや炭素の濃度(SIMS分析により得られる濃度)を、 $2 \times 10^{18}$  atoms/cm<sup>3</sup>以下とする。また、酸化物半導体膜におけるシリコンや炭素の濃度と、酸化物半導体膜との界面近傍のシリコンや炭素の濃度(SIMS分析により得られる濃度)を、 $1 \times 10^{17}$  atoms/cm<sup>3</sup>以上、より好ましくは $3 \times 10^{17}$  atoms/cm<sup>3</sup>以上、より好ましくは $1 \times 10^{18}$  atoms/cm<sup>3</sup>以上としてもよい。

#### 【0214】

酸化物半導体膜において、SIMS分析により得られるアルカリ金属またはアルカリ土類金属の濃度を、 $1 \times 10^{18}$  atoms/cm<sup>3</sup>以下、好ましくは $2 \times 10^{16}$  atoms/cm<sup>3</sup>以下にする。アルカリ金属及びアルカリ土類金属は、酸化物半導体と結合するとキャリアを生成する場合があり、トランジスタのオフ電流が増大してしまうことがある。このため、酸化物半導体膜のアルカリ金属またはアルカリ土類金属の濃度を低減することが好ましい。また、酸化物半導体膜において、SIMS分析により得られるアルカリ金属またはアルカリ土類金属の濃度を、 $5 \times 10^{15}$  atoms/cm<sup>3</sup>以上、好ましくは $1 \times 10^{16}$  atoms/cm<sup>3</sup>以上としてもよい。

10

#### 【0215】

酸化物半導体膜に窒素が含まれていると、キャリアである電子が生じ、キャリア密度が増加し、n型化しやすい。この結果、窒素が含まれている酸化物半導体膜を用いたトランジスタはノーマリーオン特性となりやすい。従って、酸化物半導体膜において、窒素はできる限り低減されていることが好ましい、例えば、SIMS分析により得られる窒素濃度は、 $5 \times 10^{18}$  atoms/cm<sup>3</sup>以下にすることが好ましい。また、SIMS分析により得られる窒素濃度は、 $1 \times 10^{16}$  atoms/cm<sup>3</sup>以上、より好ましくは $5 \times 10^{16}$  atoms/cm<sup>3</sup>以上、より好ましくは $1 \times 10^{17}$  atoms/cm<sup>3</sup>以上、より好ましくは $5 \times 10^{17}$  atoms/cm<sup>3</sup>以上としてもよい。

20

#### 【0216】

酸化物半導体膜は、それぞれ非単結晶構造でもよい。非単結晶構造は、例えば、後述するCAAC-OS(C Axis Aligned Crystalline Oxide Semiconductor)、多結晶構造、微結晶構造、または非晶質構造を含む。非単結晶構造において、非晶質構造は最も欠陥準位密度が高く、CAAC-OSは最も欠陥準位密度が低い。

30

#### 【0217】

以下では、酸化物半導体膜の構造について説明する。

#### 【0218】

酸化物半導体膜は、非単結晶酸化物半導体膜と単結晶酸化物半導体膜とに分けられる。または、酸化物半導体は、例えば、結晶性酸化物半導体と非晶質酸化物半導体とに分けられる。

#### 【0219】

なお、非単結晶酸化物半導体としては、CAAC-OS(C Axis Aligned Crystalline Oxide Semiconductor)、多結晶酸化物半導体、微結晶酸化物半導体、非晶質酸化物半導体などがある。また、結晶性酸化物半導体としては、単結晶酸化物半導体、CAAC-OS、多結晶酸化物半導体、微結晶酸化物半導体などがある。

40

#### 【0220】

まずは、CAAC-OS膜について説明する。

#### 【0221】

CAAC-OS膜は、c軸配向した複数の結晶部を有する酸化物半導体膜の一つである。

#### 【0222】

透過型電子顕微鏡(TEM: Transmission Electron Microscope)によって、CAAC-OS膜の明視野像および回折パターンの複合解析像(

50

高分解能TEM像ともいう。)を観察することで複数の結晶部を確認することができる。一方、高分解能TEM像によっても明確な結晶部同士の境界、即ち結晶粒界(グレインバウンダリーともいう。)を確認することができない。そのため、CAC-OS膜は、結晶粒界に起因する電子移動度の低下が起こりにくいといえる。

#### 【0223】

試料面と略平行な方向から、CAC-OS膜の断面の高分解能TEM像を観察すると、結晶部において、金属原子が層状に配列していることを確認できる。金属原子の各層は、CAC-OS膜の膜を形成する面(被形成面ともいう。)または上面の凹凸を反映した形状であり、CAC-OS膜の被形成面または上面と平行に配列する。

#### 【0224】

一方、試料面と略垂直な方向から、CAC-OS膜の平面の高分解能TEM像を観察すると、結晶部において、金属原子が三角形状または六角形状に配列していることを確認できる。しかしながら、異なる結晶部間で、金属原子の配列に規則性は見られない。

#### 【0225】

CAC-OS膜に対し、X線回折(XRD:X-Ray Diffraction)装置を用いて構造解析を行うと、例えば $InGaZnO_4$ の結晶を有するCAC-OS膜のout-of-plane法による解析では、回折角( $2\theta$ )が $31^\circ$ 近傍にピークが現れる場合がある。このピークは、 $InGaZnO_4$ の結晶の(009)面に帰属されることから、CAC-OS膜の結晶がc軸配向性を有し、c軸が被形成面または上面に略垂直な方向を向いていることが確認できる。

10

20

#### 【0226】

なお、 $InGaZnO_4$ の結晶を有するCAC-OS膜のout-of-plane法による解析では、 $2\theta$ が $31^\circ$ 近傍のピークの他に、 $2\theta$ が $36^\circ$ 近傍にもピークが現れる場合がある。 $2\theta$ が $36^\circ$ 近傍のピークは、CAC-OS膜中の一部に、c軸配向性を有さない結晶が含まれることを示している。CAC-OS膜は、 $2\theta$ が $31^\circ$ 近傍にピークを示し、 $2\theta$ が $36^\circ$ 近傍にピークを示さないことが好ましい。

#### 【0227】

CAC-OS膜は、不純物濃度の低い酸化物半導体膜である。不純物は、水素、炭素、シリコン、遷移金属元素などの酸化物半導体膜の主成分以外の元素である。特に、シリコンなどの、酸化物半導体膜を構成する金属元素よりも酸素との結合力の強い元素は、酸化物半導体膜から酸素を奪うことで酸化物半導体膜の原子配列を乱し、結晶性を低下させる要因となる。また、鉄やニッケルなどの重金属、アルゴン、二酸化炭素などは、原子半径(または分子半径)が大きいため、酸化物半導体膜内部に含まれると、酸化物半導体膜の原子配列を乱し、結晶性を低下させる要因となる。なお、酸化物半導体膜に含まれる不純物は、キャリアトラップやキャリア発生源となる場合がある。

30

#### 【0228】

また、CAC-OS膜は、欠陥準位密度の低い酸化物半導体膜である。例えば、酸化物半導体膜中の酸素欠損は、キャリアトラップとなることや、水素を捕獲することによってキャリア発生源となることがある。

#### 【0229】

不純物濃度が低く、欠陥準位密度が低い(酸素欠損の少ない)ことを、高純度真性または実質的に高純度真性と呼ぶ。高純度真性または実質的に高純度真性である酸化物半導体膜は、キャリア発生源が少ないため、キャリア密度を低くすることができる。したがって、当該酸化物半導体膜を用いたトランジスタは、しきい値電圧がマイナスとなる電気特性(ノーマリーオンともいう。)になることが少ない。また、高純度真性または実質的に高純度真性である酸化物半導体膜は、キャリアトラップが少ない。そのため、当該酸化物半導体膜を用いたトランジスタは、電気特性の変動が小さく、信頼性の高いトランジスタとなる。なお、酸化物半導体膜のキャリアトラップに捕獲された電荷は、放出するまでに要する時間が長く、あたかも固定電荷のように振る舞うことがある。そのため、不純物濃度が高く、欠陥準位密度が高い酸化物半導体膜を用いたトランジスタは、電気特性が不安定と

40

50

なる場合がある。

【0230】

また、C A A C - O S 膜を用いたトランジスタは、可視光や紫外光の照射による電気特性の変動が小さい。

【0231】

次に、微結晶酸化物半導体膜について説明する。

【0232】

微結晶酸化物半導体膜は、高分解能TEM像において、結晶部を確認することのできる領域と、明確な結晶部を確認することのできない領域と、を有する。微結晶酸化物半導体膜に含まれる結晶部は、1 nm以上100 nm以下、または1 nm以上10 nm以下の大きさであることが多い。特に、1 nm以上10 nm以下、または1 nm以上3 nm以下の微結晶であるナノ結晶(n c : n a n o c r y s t a l )を有する酸化物半導体膜を、n c - O S (n a n o c r y s t a l l i n e O x i d e S e m i c o n d u c t o r )膜と呼ぶ。また、n c - O S 膜は、例えば、高分解能TEM像では、結晶粒界を明確に確認できない場合がある。

【0233】

n c - O S 膜は、微小な領域(例えば、1 nm以上10 nm以下の領域、特に1 nm以上3 nm以下の領域)において原子配列に周期性を有する。また、n c - O S 膜は、異なる結晶部間で結晶方位に規則性が見られない。そのため、膜全体で配向性が見られない。したがって、n c - O S 膜は、分析方法によっては、非晶質酸化物半導体膜と区別が付かない場合がある。例えば、n c - O S 膜に対し、結晶部よりも大きい径のX線を用いるXRD装置を用いて構造解析を行うと、o u t - o f - p l a n e 法による解析では、結晶面を示すピークが検出されない。また、n c - O S 膜に対し、結晶部よりも大きいプローブ径(例えば50 nm以上)の電子線を用いる電子回折(制限視野電子回折ともいう。)を行うと、ハローパターンのような回折パターンが観測される。一方、n c - O S 膜に対し、結晶部の大きさと近いか結晶部より小さいプローブ径の電子線を用いるナノビーム電子回折を行うと、スポットが観測される。また、n c - O S 膜に対しナノビーム電子回折を行うと、円を描くように(リング状に)輝度の高い領域が観測される場合がある。また、n c - O S 膜に対しナノビーム電子回折を行うと、リング状の領域内に複数のスポットが観測される場合がある。

【0234】

n c - O S 膜は、非晶質酸化物半導体膜よりも規則性の高い酸化物半導体膜である。そのため、n c - O S 膜は、非晶質酸化物半導体膜よりも欠陥準位密度が低くなる。ただし、n c - O S 膜は、異なる結晶部間で結晶方位に規則性が見られない。そのため、n c - O S 膜は、C A A C - O S 膜と比べて欠陥準位密度が高くなる。

【0235】

次に、非晶質酸化物半導体膜について説明する。

【0236】

非晶質酸化物半導体膜は、膜中における原子配列が不規則であり、結晶部を有さない酸化物半導体膜である。石英のような無定形状態を有する酸化物半導体膜が一例である。

【0237】

非晶質酸化物半導体膜は、高分解能TEM像において結晶部を確認することができない。

【0238】

非晶質酸化物半導体膜に対し、XRD装置を用いた構造解析を行うと、o u t - o f - p l a n e 法による解析では、結晶面を示すピークが検出されない。また、非晶質酸化物半導体膜に対し、電子回折を行うと、ハローパターンが観測される。また、非晶質酸化物半導体膜に対し、ナノビーム電子回折を行うと、スポットが観測されず、ハローパターンが観測される。

【0239】

なお、酸化物半導体膜は、n c - O S 膜と非晶質酸化物半導体膜との間の物性を示す構造

10

20

30

40

50

を有する場合がある。そのような構造を有する酸化物半導体膜を、特に非晶質ライク酸化物半導体 (a - like OS : amorphous-like Oxide Semiconductor) 膜と呼ぶ。

【0240】

a - like OS 膜は、高分解能 TEM 像において鬆 (ボイドともいう。) が観察される場合がある。また、高分解能 TEM 像において、明確に結晶部を確認することのできる領域と、結晶部を確認することのできない領域と、を有する。a - like OS 膜は、TEM による観察程度の微量な電子照射によって、結晶化が起こり、結晶部の成長が見られる場合がある。一方、良質な nc - OS 膜であれば、TEM による観察程度の微量な電子照射による結晶化はほとんど見られない。

10

【0241】

なお、a - like OS 膜および nc - OS 膜の結晶部の大きさの計測は、高分解能 TEM 像を用いて行うことができる。例えば、 $InGaZnO_4$  の結晶は層状構造を有し、In - O 層の間に、Ga - Zn - O 層を 2 層有する。 $InGaZnO_4$  の結晶の単位格子は、In - O 層を 3 層有し、また Ga - Zn - O 層を 6 層有する、計 9 層が c 軸方向に層状に重なった構造を有する。よって、これらの近接する層同士の間隔は、(009) 面の格子面間隔 (d 値ともいう。) と同程度であり、結晶構造解析からその値は 0.29 nm と求められている。そのため、高分解能 TEM 像における格子縞に着目し、格子縞の間隔が 0.28 nm 以上 0.30 nm 以下である箇所においては、それぞれの格子縞が  $InGaZnO_4$  の結晶の a - b 面に対応する。

20

【0242】

また、酸化物半導体膜は、構造ごとに密度が異なる場合がある。例えば、ある酸化物半導体膜の組成がわかれば、該組成と同じ組成における単結晶の密度と比較することにより、その酸化物半導体膜の構造を推定することができる。例えば、単結晶の密度に対し、a - like OS 膜の密度は 78.6% 以上 92.3% 未満となる。また、例えば、単結晶の密度に対し、nc - OS 膜の密度および CAAC - OS 膜の密度は 92.3% 以上 100% 未満となる。なお、単結晶の密度に対し密度が 78% 未満となる酸化物半導体膜は、成膜すること自体が困難である。

【0243】

上記について、具体例を用いて説明する。例えば、 $In : Ga : Zn = 1 : 1 : 1$  [原子数比] を満たす酸化物半導体膜において、菱面体晶構造を有する単結晶  $InGaZnO_4$  の密度は 6.357 g / cm<sup>3</sup> となる。よって、例えば、 $In : Ga : Zn = 1 : 1 : 1$  [原子数比] を満たす酸化物半導体膜において、a - like OS 膜の密度は 5.0 g / cm<sup>3</sup> 以上 5.9 g / cm<sup>3</sup> 未満となる。また、例えば、 $In : Ga : Zn = 1 : 1 : 1$  [原子数比] を満たす酸化物半導体膜において、nc - OS 膜の密度および CAAC - OS 膜の密度は 5.9 g / cm<sup>3</sup> 以上 6.3 g / cm<sup>3</sup> 未満となる。

30

【0244】

なお、同じ組成の単結晶が存在しない場合がある。その場合、任意の割合で組成の異なる単結晶を組み合わせることにより、所望の組成の単結晶に相当する密度を算出することができる。所望の組成の単結晶の密度は、組成の異なる単結晶を組み合わせる割合に対して、加重平均を用いて算出すればよい。ただし、密度は、可能な限り少ない種類の単結晶を組み合わせて算出することが好ましい。

40

【0245】

なお、酸化物半導体膜は、例えば、非晶質酸化物半導体膜、a - like OS 膜、微結晶酸化物半導体膜、CAAC - OS 膜のうち、二種以上を有する積層膜であってもよい。

【0246】

本明細書において、「平行」とは、二つの直線が -10° 以上 10° 以下の角度で配置されている状態をいう。したがって、-5° 以上 5° 以下の場合も含まれる。また、「略平行」とは、二つの直線が -30° 以上 30° 以下の角度で配置されている状態をいう。また、「垂直」とは、二つの直線が 80° 以上 100° 以下の角度で配置されている状態を

50

いう。したがって、85°以上95°以下の場合も含まれる。また、「略垂直」とは、二つの直線が60°以上120°以下の角度で配置されている状態をいう。

【0247】

また、本明細書において、結晶が三方晶または菱面体晶である場合、六方晶系として表す。

【0248】

半導体層402Aは、トランジスタ101のチャネル形成領域を有する。

【0249】

半導体層402Bは、トランジスタ102のチャネル形成領域を有する。

【0250】

半導体層402Cは、トランジスタ103のチャネル形成領域を有する。

10

【0251】

半導体層402Dは、トランジスタ104のチャネル形成領域を有する。

【0252】

なお、半導体層402Aの面積は、半導体層402B、半導体層402C及び半導体層402Dの面積よりも大きい。また、半導体層402Bの面積は、半導体層402C及び半導体層402Dの面積よりも大きい。

【0253】

なお、半導体層402Aは、導電層401Aの端部の内側に設けられる。半導体層402Bは、導電層401Bの端部の内側に設けられる。半導体層402Cは、導電層401Cの端部の内側に設けられる。半導体層402Dは、導電層401Dの端部の内側に設けられる。これにより、半導体層402A乃至402Dの段差を無くし、不良の発生を抑制することができる。

20

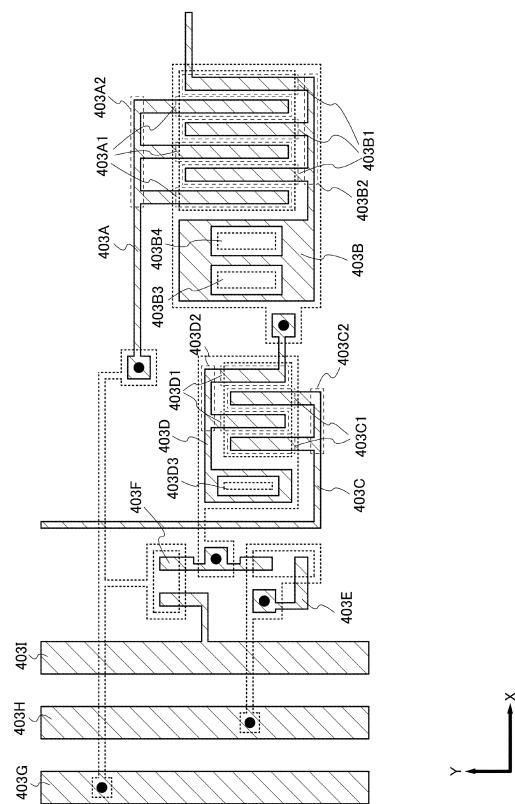

【0254】

導電層403A乃至403Iは同層である。或いは、導電層403A乃至403Iは同じ材料を有する。或いは、導電層403A乃至403Iは同一の導電膜を加工する工程を経て形成されたものである。

【0255】

導電層403A乃至403Iとしては、導電層401A乃至401Dに適用可能な材料又は構造の中から適宜選択することができる。

30

【0256】

導電層403Aは、トランジスタ101のソース電極又はドレイン電極の一方となる領域を有する。また、導電層403Aは、半導体層402Aと接続されている。或いは、導電層403Aは、半導体層402Aと接する領域を有する。また、導電層403Aは、絶縁層404のコンタクトホールを介して導電層401Dと接続される。或いは、導電層403Aは、導電層401Dと接する領域を有する。また、導電層403Aは、複数の領域403A1を有する。複数の領域403A1のそれぞれは、略Y方向に沿う長尺を有し、半導体層402Aを介して導電層401Aと重なる。また、導電層403Aは、領域403A2を有する。領域403A2は、略X方向に沿う長尺を有し、半導体層402A及び導電層401Aと重ならない。

40

【0257】

導電層403Bは、トランジスタ101のソース電極又はドレイン電極の他方となる領域と、容量素子105の第1の電極となる領域と、配線113となる領域と、を有する。また、導電層403Bは、半導体層402Aと接続されている。或いは、導電層403Bは、半導体層402Aと接する領域を有する。また、導電層403Bは、複数の領域403B1を有する。複数の領域403B1は、略Y方向に沿う長尺を有し、半導体層402Aを介して導電層401Aと重なる。また、導電層403Bは、領域403B2を有する。領域403B2は、略X方向に沿う長尺を有し、半導体層402Aを介さずに導電層401Aと重なる。また、導電層403Bは、開口部403B3及び開口部403B4を有する。開口部403B3及び開口部403B4は、略Y方向に沿う長尺を有する。

50

## 【0258】

導電層403Cは、トランジスタ102のソース電極又はドレイン電極の一方となる領域と、配線113となる領域と、を有する。また、導電層403Cは、半導体層402Bと接続されている。或いは、導電層403Cは、半導体層402Bと接する領域を有する。また、導電層403Cは、複数の領域403C1を有する。複数の領域403C1は、略Y方向に沿う長尺を有し、半導体層402Bを介して導電層401Bと重なる。また、導電層403Cは、領域403C2を有する。領域403C2は、略X方向に沿う長尺を有し、半導体層402B及び導電層401Bと重ならない。

## 【0259】

導電層403Dは、トランジスタ102のソース電極又はドレイン電極の他方となる領域と、容量素子106の第1の電極となる領域と、を有する。また、導電層403Dは、半導体層402Bと接続されている。或いは、導電層403Dは、半導体層402Bと接する領域を有する。また、導電層403Dは、絶縁層404のコンタクトホールを介して導電層401Aと接続される。或いは、導電層403Dは、導電層401Aと接する領域を有する。また、導電層403Dは、複数の領域403D1を有する。複数の領域403D1は、略Y方向に沿う長尺を有し、半導体層402Bを介して導電層401Bと重なる。また、導電層403Dは、領域403D2を有する。領域403D2は、略X方向に沿う長尺を有し、半導体層402Bを介さずに導電層401Bと重なる。また、導電層403Dは、開口部403D3を有する。開口部403D3は、略Y方向に沿う長尺を有する。

## 【0260】

導電層403Eは、トランジスタ103のソース電極又はドレイン電極の一方となる領域を有する。また、導電層403Eは、半導体層402Cと接続される。或いは、導電層403Eは、半導体層402Cと接する領域を有する。また、導電層403Eは、導電層401Cと絶縁層404のコンタクトホールを介して接続される。或いは、導電層403Eは、導電層401Cと接する領域を有する。

## 【0261】

導電層403Fは、トランジスタ103のソース電極又はドレイン電極の他方となる領域と、トランジスタ104のソース電極又はドレイン電極の他方となる領域と、を有する。また、導電層403Fは、半導体層402Cと接続され、半導体層402Dと接続される。或いは、導電層403Fは、半導体層402Cと接する領域と、半導体層402Dと接する領域と、を有する。また、導電層403Fは、絶縁層404のコンタクトホールを介して導電層401Bと接続される。或いは、導電層403Fは、導電層401Bと接する領域を有する。

## 【0262】

導電層403Gは、配線111となる領域を有する。また、導電層403Gは、絶縁層404のコンタクトホールを介して導電層401Dと接続される。或いは、導電層403Gは、導電層401Dと接する領域を有する。

## 【0263】

導電層403Hは、配線114となる領域を有する。また、導電層403Hは、絶縁層404のコンタクトホールを介して導電層401Cと接続される。或いは、導電層403Hは、導電層401Cと接する領域を有する。

## 【0264】

導電層403Iは、配線115となる領域と、トランジスタ104のソース電極又はドレイン電極の一方となる領域を有する。また、導電層403Iは、半導体層402Dと接続される。或いは、導電層403Iは、半導体層402Dと接する領域を有する。

## 【0265】

なお、開口部403B3の面積は開口部401A1の面積よりも大きく、開口部403B4の面積は開口部401A2の面積よりも大きい。また、開口部401A1は開口部403B3の内側に設けられ、開口部401A2は開口部403B4の内側に設けられている。これにより、導電層401Aに起因する導電層403Bの段差を無くし、不良の発生を

10

20

30

40

50

抑制することができる。

#### 【0266】

なお、開口部 403D3 の面積は、開口部 401B1 の面積よりも大きい。また、開口部 404A1 は、開口部 403D3 の内側に設けられている。これにより、導電層 401B に起因する導電層 403D の段差を無くし、不良の発生を抑制することができる。

#### 【0267】

なお、導電層 403A の領域 403A2 は導電層 401A 及び半導体層 402A と重ならないのに対し、導電層 403B の領域 403B2 は半導体層 402A を介さずに導電層 401A と重なる。ただし、導電層 403B の領域 403B2 は半導体層 402A を介して導電層 401A と重なってもよい。また、導電層 403A と導電層 401A とが重なる面積は、導電層 403B と導電層 401A とが重なる面積よりも小さい。これにより、導電層 403A と導電層 401A との寄生容量を小さくするとともに、導電層 403B と導電層 401A との寄生容量を大きくすることができる。よって、配線 111 の電位のトランジスタ 101 のゲートへの影響を小さくするとともに、容量素子 105 の容量値を小さくすることが可能になることによるレイアウト面積の縮小を図ることができる。10

#### 【0268】

なお、導電層 403C の領域 403C2 は導電層 401B 及び半導体層 402B と重ならないのに対し、導電層 403D の領域 403D2 は半導体層 402B を介さずに導電層 401B と重なる。ただし、導電層 403D の領域 403D2 は半導体層 402B を介して導電層 401B と重なってもよい。また、導電層 403C と導電層 401B とが重なる面積は、導電層 403D と導電層 401B とが重なる面積よりも小さい。これにより、導電層 403C と導電層 401B との寄生容量を小さくするとともに、導電層 403D と導電層 401B との寄生容量を大きくすることができる。よって、配線 113 の電位のトランジスタ 102 のゲートへの影響を小さくするとともに、容量素子 106 の容量値を小さくすることが可能になることによるレイアウト面積の縮小を図ることができる。20

#### 【0269】

なお、導電層 401A 乃至 401D、半導体層 402A 乃至 402D、導電層 403A 乃至 403I、及び絶縁層 404 が形成される基板の材質などに大きな制限はないが、少なくとも、後の熱処理に耐えうる程度の耐熱性を有している必要がある。例えば、ガラス基板、セラミック基板、石英基板、サファイア基板等を、基板として用いてもよい。また、シリコンや炭化シリコンなどを材料とした単結晶半導体基板、多結晶半導体基板、シリコンゲルマニウム等の化合物半導体基板、SOI 基板等を適用することも可能であり、これらの基板上に半導体素子が設けられたものを、基板として用いてもよい。なお、基板として、ガラス基板を用いる場合、第 6 世代 (1500 mm × 1850 mm)、第 7 世代 (1870 mm × 2200 mm)、第 8 世代 (2200 mm × 2400 mm)、第 9 世代 (2400 mm × 2800 mm)、第 10 世代 (2950 mm × 3400 mm) 等の大面積基板を用いることで、大型の表示装置を作製することができる。30

#### 【0270】

また、基板として、可撓性基板を用い、可撓性基板上に直接、トランジスタを形成してもよい。または、基板とトランジスタの間に剥離層を設けてもよい。剥離層は、その上に半導体装置を一部あるいは全部完成させた後、基板より分離し、他の基板に転載するのに用いることができる。その際、トランジスタは耐熱性の劣る基板や可撓性の基板にも転載できる。

#### 【0271】

例えば、本明細書等において、様々な基板を用いて、トランジスタを形成することができる。基板の種類は、特定のものに限定されることはない。その基板の一例としては、半導体基板（例えば単結晶基板又はシリコン基板）、SOI 基板、ガラス基板、石英基板、プラスチック基板、金属基板、ステンレス・スチール基板、ステンレス・スチール・ホイルを有する基板、タンクステン基板、タンクステン・ホイルを有する基板、可撓性基板、貼り合わせフィルム、繊維状の材料を含む紙、又は基材フィルムなどがある。ガラス基板の一4050

例としては、バリウムホウケイ酸ガラス、アルミニノホウケイ酸ガラス、又はソーダライムガラスなどがある。可撓性基板、貼り合わせフィルム、基材フィルムなどの一例としては、以下のものがあげられる。例えば、ポリエチレンテレフタレート(PET)、ポリエチレンナフタレート(PEN)、ポリエーテルサルフォン(PES)、ポリテトラフルオロエチレン(PTFE)に代表されるプラスチックがある。または、一例としては、アクリル等の合成樹脂などがある。または、一例としては、ポリプロピレン、ポリエステル、ポリフッ化ビニル、又はポリ塩化ビニルなどがある。または、一例としては、ポリエステル、ポリアミド、ポリイミド、アラミド、エポキシ、無機蒸着フィルム、又は紙類などがある。特に、半導体基板、単結晶基板、又はSOI基板などを用いてトランジスタを製造することによって、特性、サイズ、又は形状などのばらつきが少なく、電流能力が高く、サイズの小さいトランジスタを製造することができる。このようなトランジスタによって回路を構成すると、回路の低消費電力化、又は回路の高集積化を図ることができる。

#### 【0272】

また、基板として、可撓性基板を用い、可撓性基板上に直接、トランジスタを形成してもよい。または、基板とトランジスタの間に剥離層を設けてもよい。剥離層は、その上に半導体装置を一部あるいは全部完成させた後、基板より分離し、他の基板に転載するため用いることができる。その際、トランジスタは耐熱性の劣る基板や可撓性の基板にも転載できる。なお、上述の剥離層には、例えば、タンゲステン膜と酸化シリコン膜との無機膜の積層構造の構成や、基板上にポリイミド等の有機樹脂膜が形成された構成等を用いることができる。

#### 【0273】

つまり、ある基板を用いてトランジスタを形成し、その後、別の基板にトランジスタを転置し、別の基板上にトランジスタを配置してもよい。トランジスタが転置される基板の一例としては、上述したトランジスタを形成することが可能な基板に加え、紙基板、セロファン基板、アラミドフィルム基板、ポリイミドフィルム基板、石材基板、木材基板、布基板(天然纖維(絹、綿、麻)、合成纖維(ナイロン、ポリウレタン、ポリエステル)若しくは再生纖維(アセテート、キュプラ、レーヨン、再生ポリエステル)などを含む)、皮革基板、又はゴム基板などがある。これらの基板を用いることにより、特性のよいトランジスタの形成、消費電力の小さいトランジスタの形成、壊れにくい装置の製造、耐熱性の付与、軽量化、又は薄型化を図ることができる。

#### 【0274】

なお、本実施の形態は他の実施の形態の記載と適宜組み合わせることができる。よって、本実施の形態の中で述べる内容(一部の内容でもよい)は、その実施の形態で述べる別の内容(一部の内容でもよい)、及び/又は、一つ若しくは複数の別の実施の形態で述べる内容(一部の内容でもよい)に対して、適用、組み合わせ、又は置き換えなどを行うことができる。なお、実施の形態の中で述べる内容とは、各々の実施の形態において、様々な図を用いて述べる内容、又は明細書に記載される文章を用いて述べる内容のことである。また、ある一つの実施の形態において述べる図(一部でもよい)は、その図の別の部分、その実施の形態において述べる別の図(一部でもよい)、及び/又は、一つ若しくは複数の別の実施の形態において述べる図(一部でもよい)に対して、組み合わせることにより、さらに多くの図を構成させることができる。これは、以下の実施の形態においても同様である。

#### 【0275】

##### (実施の形態5)

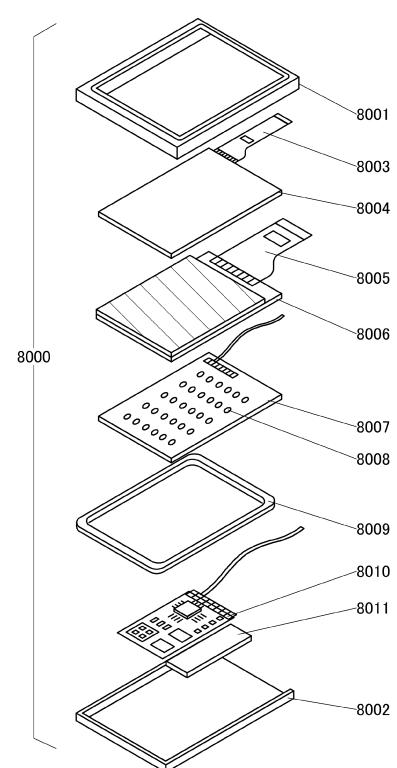

本実施の形態では、本発明の一態様の半導体装置を有する表示モジュール及び電子機器について、図24及び図25を用いて説明を行う。

#### 【0276】

図24に示す表示モジュール8000は、上部カバー8001と下部カバー8002との間に、FPC8003に接続されたタッチパネル8004、FPC8005に接続された表示パネル8006、バックライト8007、フレーム8009、プリント基板8010

10

20

30

40

50

、バッテリ 8011 を有する。

#### 【0277】

本発明の一態様の半導体装置又は表示装置は、例えば、表示パネル 8006 に用いることができる。

#### 【0278】

上部カバー 8001 及び下部カバー 8002 は、タッチパネル 8004 及び表示パネル 8006 のサイズに合わせて、形状や寸法を適宜変更することができる。

#### 【0279】

タッチパネル 8004 は、抵抗膜方式または静電容量方式のタッチパネルを表示パネル 8006 に重畠して用いることができる。また、表示パネル 8006 の対向基板（封止基板）に、タッチパネル機能を持たせるようにすることも可能である。また、表示パネル 8006 の各画素内に光センサを設け、光学式のタッチパネルとすることも可能である。10

#### 【0280】

バックライト 8007 は、光源 8008 を有する。なお、図 24 において、バックライト 8007 上に光源 8008 を配置する構成について例示したが、これに限定さない。例えば、バックライト 8007 の端部に光源 8008 を配置し、さらに光拡散板を用いる構成としてもよい。なお、有機 EL 素子等の自発光型の発光素子を用いる場合、または反射型パネル等の場合においては、バックライト 8007 を設けない構成としてもよい。

#### 【0281】

フレーム 8009 は、表示パネル 8006 の保護機能の他、プリント基板 8010 の動作により発生する電磁波を遮断するための電磁シールドとしての機能を有する。またフレーム 8009 は、放熱板としての機能を有していてもよい。20

#### 【0282】

プリント基板 8010 は、電源回路、ビデオ信号及びクロック信号を出力するための信号処理回路を有する。電源回路に電力を供給する電源としては、外部の商用電源であっても良いし、別途設けたバッテリ 8011 による電源であってもよい。バッテリ 8011 は、商用電源を用いる場合には、省略可能である。

#### 【0283】

また、表示モジュール 8000 は、偏光板、位相差板、プリズムシートなどの部材を追加して設けてもよい。30

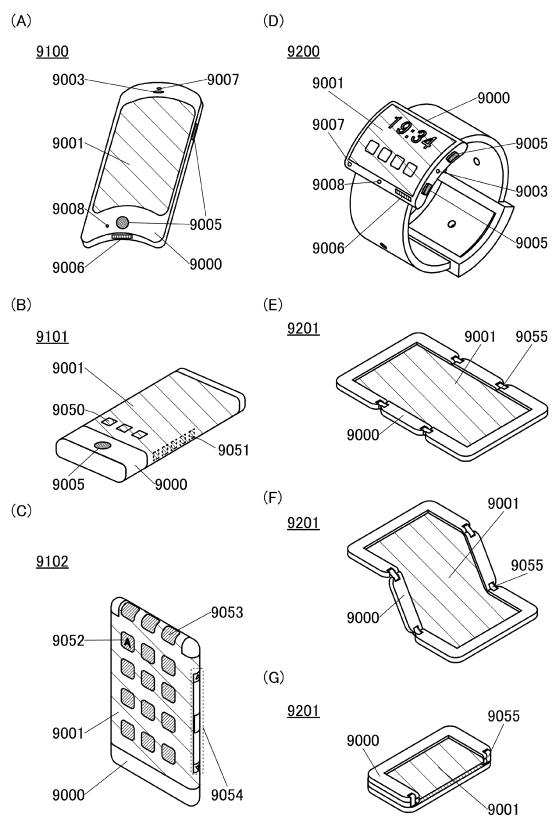

#### 【0284】

図 25 (A) 乃至図 25 (G) は、電子機器を示す図である。これらの電子機器は、筐体 9000、表示部 9001、スピーカ 9003、操作キー 9005（電源スイッチ、又は操作スイッチを含む）、接続端子 9006、センサ 9007（力、変位、位置、速度、加速度、角速度、回転数、距離、光、液、磁気、温度、化学物質、音声、時間、硬度、電場、電流、電圧、電力、放射線、流量、湿度、傾度、振動、におい又は赤外線を測定する機能を含むもの）、マイクロフォン 9008、等を有することができる。

#### 【0285】

図 25 (A) 乃至図 25 (G) に示す電子機器は、様々な機能を有することができる。例えば、様々な情報（静止画、動画、テキスト画像など）を表示部に表示する機能、タッチパネル機能、カレンダー、日付または時刻などを表示する機能、様々なソフトウェア（プログラム）によって処理を制御する機能、無線通信機能、無線通信機能を用いて様々なコンピュータネットワークに接続する機能、無線通信機能を用いて様々なデータの送信または受信を行う機能、記録媒体に記録されているプログラムまたはデータを読み出して表示部に表示する機能、等を有することができる。なお、図 25 (A) 乃至図 25 (G) に示す電子機器が有することのできる機能はこれらに限定されず、様々な機能を有することができる。また、図 25 (A) 乃至図 25 (G) には図示していないが、電子機器には、複数の表示部を有する構成としてもよい。また、該電子機器にカメラ等を設け、静止画を撮影する機能、動画を撮影する機能、撮影した画像を記録媒体（外部またはカメラに内蔵）に保存する機能、撮影した画像を表示部に表示する機能、等を有していてもよい。4050

## 【0286】

図25(A)乃至図25(G)に示す電子機器の詳細について、以下説明を行う。

## 【0287】

図25(A)は、携帯情報端末9100を示す斜視図である。携帯情報端末9100が有する表示部9001は、可撓性を有する。そのため、湾曲した筐体9000の湾曲面に沿って表示部9001を組み込むことが可能である。また、表示部9001はタッチセンサを備え、指やスタイラスなどで画面に触れることで操作することができる。例えば、表示部9001に表示されたアイコンに触れることで、アプリケーションを起動することができる。

## 【0288】

図25(B)は、携帯情報端末9101を示す斜視図である。携帯情報端末9101は、例えば電話機、手帳又は情報閲覧装置等から選ばれた一つ又は複数の機能を有する。具体的には、スマートフォンとして用いることができる。なお、携帯情報端末9101は、スピーカ9003、接続端子9006、センサ9007等を省略して図示しているが、図25(A)に示す携帯情報端末9100と同様の位置に設けることができる。また、携帯情報端末9101は、文字や画像情報をその複数の面に表示することができる。例えば、3つの操作ボタン9050(操作アイコンまたは単にアイコンともいう)を表示部9001の一の面に表示することができる。また、破線の矩形で示す情報9051を表示部9001の他の面に表示することができる。なお、情報9051の一例としては、電子メールやSNS(ソーシャル・ネットワーキング・サービス)や電話などの着信を知らせる表示、電子メールやSNSなどの題名、電子メールやSNSなどの送信者名、日時、時刻、バッテリの残量、アンテナ受信の強度などがある。または、情報9051が表示されている位置に、情報9051の代わりに、操作ボタン9050などを表示してもよい。

10

## 【0289】

図25(C)は、携帯情報端末9102を示す斜視図である。携帯情報端末9102は、表示部9001の3面以上に情報を表示する機能を有する。ここでは、情報9052、情報9053、情報9054がそれぞれ異なる面に表示されている例を示す。例えば、携帯情報端末9102の使用者は、洋服の胸ポケットに携帯情報端末9102を収納した状態で、その表示(ここでは情報9053)を確認することができる。具体的には、着信した電話の発信者の電話番号又は氏名等を、携帯情報端末9102の上方から観察できる位置に表示する。使用者は、携帯情報端末9102をポケットから取り出すことなく、表示を確認し、電話を受けるか否かを判断できる。

20

## 【0290】

図25(D)は、腕時計型の携帯情報端末9200を示す斜視図である。携帯情報端末9200は、移動電話、電子メール、文章閲覧及び作成、音楽再生、インターネット通信、コンピュータゲームなどの種々のアプリケーションを実行することができる。また、表示部9001はその表示面が湾曲して設けられ、湾曲した表示面に沿って表示を行うことができる。また、携帯情報端末9200は、通信規格された近距離無線通信を実行することができる。例えば無線通信可能なヘッドセットと相互通信することによって、ハンズフリーで通話することもできる。また、携帯情報端末9200は、接続端子9006を有し、他の情報端末とコネクターを介して直接データのやりとりを行うことができる。また接続端子9006を介して充電を行うこともできる。なお、充電動作は接続端子9006を介さずに無線給電により行ってもよい。

30

## 【0291】

図25(E)(F)(G)は、折り畳み可能な携帯情報端末9201を示す斜視図である。また、図25(E)が携帯情報端末9201を展開した状態の斜視図であり、図25(F)が携帯情報端末9201を展開した状態または折り畳んだ状態の一方から他方に変化する途中の状態の斜視図であり、図25(G)が携帯情報端末9201を折り畳んだ状態の斜視図である。携帯情報端末9201は、折り畳んだ状態では可搬性に優れ、展開した状態では、継ぎ目のない広い表示領域により表示の一覧性に優れる。携帯情報端末920

40

50

1が有する表示部9001は、ヒンジ9055によって連結された3つの筐体9000に支持されている。ヒンジ9055を介して2つの筐体9000間を屈曲させることにより、携帯情報端末9201を展開した状態から折りたたんだ状態に可逆的に変形させることができる。例えば、携帯情報端末9201は、曲率半径1mm以上150mm以下で曲げることができる。

【0292】

本実施の形態において述べた電子機器は、何らかの情報を表示するための表示部を有することを特徴とする。ただし、本発明の一態様の半導体装置は、表示部を有さない電子機器にも適用することができる。また、本実施の形態において述べた電子機器の表示部においては、可撓性を有し、湾曲した表示面に沿って表示を行うことができる構成、または折り畳み可能な表示部の構成について例示したが、これに限定されず、可撓性を有さず、平面部に表示を行う構成としてもよい。

10

【0293】

本実施の形態に示す構成は、他の実施の形態に示す構成と適宜組み合わせて用いることができる。

【符号の説明】

【0294】

|         |        |    |

|---------|--------|----|

| C K 1   | 信号     | 20 |

| C K 2   | 信号     |    |

| C K 3   | 信号     |    |

| N D 1   | ノード    |    |

| N D 2   | ノード    |    |

| N D 3   | ノード    |    |

| O U T   | 信号     |    |

| S P     | 信号     |    |

| T 0     | 期間     |    |

| T 1     | 期間     |    |

| T 2     | 期間     |    |

| T 3     | 期間     |    |

| T 4     | 期間     | 30 |

| 1 0 0   | 回路     |    |

| 1 0 1   | トランジスタ |    |

| 1 0 2   | トランジスタ |    |

| 1 0 3   | トランジスタ |    |

| 1 0 4   | トランジスタ |    |

| 1 0 5   | 容量素子   |    |

| 1 0 6   | 容量素子   |    |

| 1 0 7   | トランジスタ |    |

| 1 0 8   | トランジスタ |    |

| 1 0 9   | トランジスタ | 40 |

| 1 1 0   | トランジスタ |    |

| 1 0 1 p | トランジスタ |    |

| 1 0 2 p | トランジスタ |    |

| 1 0 3 p | トランジスタ |    |

| 1 0 4 p | トランジスタ |    |

| 1 1 1   | 配線     |    |

| 1 1 2   | 配線     |    |

| 1 1 3   | 配線     |    |

| 1 1 4   | 配線     |    |

| 1 1 5   | 配線     | 50 |

|           |         |    |

|-----------|---------|----|

| 1 1 5 B   | 配線      |    |

| 1 1 5 C   | 配線      |    |

| 1 1 6     | 配線      |    |

| 1 1 7     | 配線      |    |

| 1 2 1     | トランジスタ  |    |

| 1 2 2     | トランジスタ  |    |

| 1 2 3     | トランジスタ  |    |

| 1 2 4     | トランジスタ  |    |

| 2 0 0     | 回路      |    |

| 2 0 1     | 回路      | 10 |

| 2 1 1     | 配線      |    |

| 2 1 2     | 配線      |    |

| 2 1 3     | 配線      |    |

| 2 1 4     | 配線      |    |

| 2 1 5     | 配線      |    |

| 2 1 6     | 配線      |    |

| 3 0 1     | 画素部     |    |

| 3 0 2     | 走査線駆動回路 |    |

| 3 0 3     | 信号線駆動回路 |    |

| 3 0 4     | 回路      | 20 |

| 3 1 0     | 画素      |    |

| 4 0 1 A   | 導電層     |    |

| 4 0 1 A 1 | 開口部     |    |

| 4 0 1 A 2 | 開口部     |    |

| 4 0 1 B   | 導電層     |    |

| 4 0 1 B 1 | 開口部     |    |

| 4 0 1 C   | 導電層     |    |

| 4 0 1 D   | 導電層     |    |

| 4 0 2 A   | 半導体層    |    |

| 4 0 2 B   | 半導体層    | 30 |

| 4 0 2 C   | 半導体層    |    |

| 4 0 2 D   | 半導体層    |    |

| 4 0 3 A   | 導電層     |    |

| 4 0 3 A 1 | 領域      |    |

| 4 0 3 A 2 | 領域      |    |

| 4 0 3 B   | 導電層     |    |

| 4 0 3 B 1 | 領域      |    |

| 4 0 3 B 2 | 領域      |    |

| 4 0 3 B 3 | 開口部     |    |

| 4 0 3 B 4 | 開口部     | 40 |

| 4 0 3 C   | 導電層     |    |

| 4 0 3 C 1 | 領域      |    |

| 4 0 3 C 2 | 領域      |    |

| 4 0 3 D   | 導電層     |    |

| 4 0 3 D 1 | 領域      |    |

| 4 0 3 D 2 | 領域      |    |

| 4 0 3 D 3 | 開口部     |    |

| 4 0 3 E   | 導電層     |    |

| 4 0 3 F   | 導電層     |    |

| 4 0 3 G   | 導電層     | 50 |

|           |         |    |

|-----------|---------|----|

| 4 0 3 H   | 導電層     |    |

| 4 0 3 I   | 導電層     |    |

| 4 0 4     | 絶縁層     |    |

| 4 0 4 A 1 | 開口部     |    |

| 8 0 0 0   | 表示モジュール |    |

| 8 0 0 1   | 上部カバー   |    |

| 8 0 0 2   | 下部カバー   |    |

| 8 0 0 3   | FPC     | 10 |

| 8 0 0 4   | タッチパネル  |    |

| 8 0 0 5   | FPC     |    |

| 8 0 0 6   | 表示パネル   |    |

| 8 0 0 7   | バックライト  |    |

| 8 0 0 8   | 光源      |    |

| 8 0 0 9   | フレーム    |    |

| 8 0 1 0   | プリント基板  |    |

| 8 0 1 1   | バッテリ    |    |

| 9 0 0 0   | 筐体      |    |

| 9 0 0 1   | 表示部     |    |

| 9 0 0 3   | スピーカ    |    |

| 9 0 0 5   | 操作キー    | 20 |

| 9 0 0 6   | 接続端子    |    |

| 9 0 0 7   | センサ     |    |

| 9 0 0 8   | マイクロフォン |    |

| 9 0 5 0   | 操作ボタン   |    |

| 9 0 5 1   | 情報      |    |

| 9 0 5 2   | 情報      |    |

| 9 0 5 3   | 情報      |    |

| 9 0 5 4   | 情報      |    |

| 9 0 5 5   | ヒンジ     |    |

| 9 1 0 0   | 携帯情報端末  | 30 |

| 9 1 0 1   | 携帯情報端末  |    |

| 9 1 0 2   | 携帯情報端末  |    |

| 9 2 0 0   | 携帯情報端末  |    |

| 9 2 0 1   | 携帯情報端末  |    |

【図1】

【図2】

(A)

【図3】

【図4】

(B)

(B)

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

## フロントページの続き

| (51)Int.CI.    |       | F I       |                |       |         |

|----------------|-------|-----------|----------------|-------|---------|

| <i>G 0 9 G</i> | 3/30  | (2006.01) | <i>G 0 9 G</i> | 3/20  | 6 1 1 J |

| <i>G 0 9 G</i> | 3/36  | (2006.01) | <i>G 0 9 G</i> | 3/20  | 6 2 1 F |

| <i>G 1 1 C</i> | 19/28 | (2006.01) | <i>G 0 9 G</i> | 3/20  | 6 2 2 E |

|                |       |           | <i>G 0 9 G</i> | 3/20  | 6 7 0 E |

|                |       |           | <i>G 0 9 G</i> | 3/30  | H       |

|                |       |           | <i>G 0 9 G</i> | 3/36  |         |

|                |       |           | <i>G 1 1 C</i> | 19/28 | 2 3 0   |

(56)参考文献 特開2008-89874 (JP, A)

特開2010-108567 (JP, A)

国際公開第2014/208123 (WO, A1)

特開2005-50502 (JP, A)

特表2008-537275 (JP, A)

## (58)調査した分野(Int.CI., DB名)

H 0 3 K 1 7 / 0 6

H 0 3 K 1 9 / 0 1 7 5

H 0 3 K 1 9 / 0 9 6

H 0 1 L 2 9 / 7 8 6

G 0 9 G 3 / 2 0

G 0 9 G 3 / 3 6

G 1 1 C 1 9 / 2 8