(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2014-0064854

(43) 공개일자 2014년05월28일

- (51) 국제특허분류(Int. Cl.)

*H01L 31/042* (2014.01) *H01L 31/18* (2006.01)

(21) 출원번호 10-2014-7006376

(22) 출원일자(국제) 2012년08월09일

심사청구일자 없음

(85) 번역문제출일자 2014년03월10일

(86) 국제출원번호 PCT/US2012/000348

(87) 국제공개번호 WO 2013/022479

국제공개일자 2013년02월14일

(30) 우선권주장

61/521,743 2011년08월09일 미국(US)

61/521,754 2011년08월09일 미국(US)

(71) 출원인

**솔렉셀, 인크.**

미국 95035-7405 캘리포니아 밀피타스 1530 엠씨

카르시 비엘브이디

(72) 발명자

**모슬레히, 메흐르더드, 엠.**

미국 캘리포니아 94024 로스앨터스 스텐리 애비뉴

956

**카푸르, 파완**

미국 캘리포니아 94306 팔로 알토 마타데로 애비

뉴 565

(뒷면에 계속)

(74) 대리인

**특허법이무한**

전체 청구항 수 : 총 41 항

(54) 발명의 명칭 고효율 태양 광기전 전지 및 박형 결정 반도체 흡수체를 이용한 모듈

(57) 요약

태양 전지 기판 보강재 및 전기 상호접촉을 제공하는 후면 접촉 태양 전지의 백플레이너와 관련된 구조체 및 제조 방법 및 박막 후면 접촉 태양 전지를 형성하기 위한 구조체 및 제조 방법이 개시된다.

## 대 표 도

(72) 발명자

크래머, 케이.-조셉

미국 캘리포니아 95125 산 호세 리버사이드 드라이

브 824

라나, 비렌드라, 브이.

미국 캘리포니아 95032 로스가토스 안드레 코트

101

슈터, 션

미국 캘리포니아 95133 산 호세 해리스버그 플레이

스 629

데쉬펜드, 아난드

미국 캘리포니아 95129 산 호세 유닛 127 알바니

서클 4691

캘카테라, 안토니

미국 캘리포니아 95035 밀피타스 모몽 드라이브

알108 1775

올슨, 게리

미국 캘리포니아 95128 산 호세 와바시 애비뉴 263

멘테기, 캄란

미국 캘리포니아 95111 산 호세 베라노 코트 508

스탈컵, 톰

미국 캘리포니아 95035 밀피타스 매카시 벨딩 1530

카미안, 조지, 디.

미국 캘리포니아 95066 스코츠 뱬리 실버우드 드라

이브 425

왕, 데이비드, 쉬엔-퀴

미국 캘리포니아 94539 프리몬트 비아 산미구엘

91831

수, 엔-셍

미국 캘리포니아 95035 밀피타스 매카시 벨딩 1530

원거트, 미셸

미국 캘리포니아 95030 로스가토스 와일더 애비뉴

140

## 특허청구의 범위

### 청구항 1

패시베이션층을 갖는 광 포획 전측면, 도핑된 베이스 영역, 및 상기 도핑된 베이스 영역과 반대의 극성을 갖는 도핑된 후측 에미터 영역을 포함하는 증착된 반도체층;

상기 후측 에미터 영역 상의 후측 패시베이션 유전체층 및 패터닝된 반사층;

후면 접촉 후면 접합 박형 태양 전지의 후측 상에 제1레벨의 맞물려진(interdigitated) 금속화 패턴을 형성하는 금속 상호 접속에 연결된 후측 에미터 접촉 및 후측 베이스 접촉; 및

상기 후면 접촉 후면 접합 박형 태양 전지의 후측 상에 위치된 적어도 하나의 영구적 지지 보강재(permanent support reinforcement); 및

상기 영구 후측 지지 보강재 구조체에 의해 제1층으로부터 분리되는 제2금속층으로서, 상기 제2층은 상기 영구 후측 지지 보강재 구조체 내 홀의 맞물려진 패턴을 통해 국부적으로 상기 제1레벨 금속화 패턴과 접촉하는, 제2 금속층;

을 포함하는 후면 접촉 후면 접합 박형 태양 전지.

### 청구항 2

제1항에 있어서,

상기 제2금속층은 상기 제1레벨의 맞물려진 금속화 패턴에 직각으로 얼라인되는(aligned) 것인, 후면 접촉 후면 접합 박형 태양 전지.

### 청구항 3

제1항에 있어서,

상기 영구적 보강재 구조체는 프리프레그(prepreg) 물질을 함유하는 것인, 구조체.

### 청구항 4

제1항에 있어서,

상기 후측 패시베이션층은 보로실리케이트 유리와 같은 유리로 이루어지는 것인, 구조체.

### 청구항 5

제1항에 있어서,

상기 후측 패시베이션층은 적어도 알루미늄 산화물의 박층을 함유하는 것인, 구조체.

### 청구항 6

제1항에 있어서,

상기 제2금속층은 극성 당 적어도 하나의 부스바(one bus bar per polarity)를 포함하는 것인, 구조체.

**청구항 7**

제6항에 있어서,

상기 제1레벨의 맞물려진 금속화 패턴은 상기 부스바 아래에 위치하여 전기적 셰이딩을 감소시키는 것인, 구조체.

**청구항 8**

제1항에 있어서,

상기 제1레벨의 금속화 패턴은 프린팅을 이용하여 증착되는 것인, 구조체.

**청구항 9**

제1항에 있어서,

상기 제1레벨의 금속화 패턴은 알루미늄 페이스트 또는 실리콘 물질을 갖는 알루미늄 페이스트를 포함하는 것인, 구조체.

**청구항 10**

제1항에 있어서,

상기 제1레벨의 금속화 패턴은 하나 이상의 알루미늄 페이스트를 포함하는 것인, 구조체.

**청구항 11**

제1항에 있어서,

상기 에미터 영역은 다양한 도편트 농도의 적어도 두개의 영역으로 이루어지고, 상기 에미터 접촉 부근의 영역은 상기 에미터 접촉 영역으로부터 떨어진 영역보다 더 높은 도편트 농도를 갖는 것인, 구조체.

**청구항 12**

제1항에 있어서,

상기 에미터 영역은 고유한 비정질 실리콘의 상부 상에 p+ 도핑된 비정질 실리콘의 초박층으로 이루어지고, 상기 에미터 영역은 다결정 실리콘 게르마늄 합금 또는 전도성 산화물에 의해 지지되는(backed by) 것인, 구조체.

**청구항 13**

다양한 도편트 농도로 도편트 전구체를 증착하는 단계;

더 높은 도편트 전구체 농도를 갖는 영역과 더 낮은 도편트 전구체를 갖는 영역을 레이저 제거에 의해 형성하도록, 영역을 구조화하는 단계;

열적 어닐링 단계를 이용하여 미리 증착된 도편트원으로부터 도편트를 드라이빙하는(driving in said dopant from the predeposited dopant sources) 단계;

를 포함하고, 선택적 에미터 영역이 형성되는, 반도체 태양 전지의 제조방법.

**청구항 14**

제13항에 있어서,

상기 도편트 전구체원(dopant precursor source)은, 도핑된 유리의 화학 증기 증착을 이용하여 증착된 도편트층으로 이루어지는 것인, 방법.

**청구항 15**

제14항에 있어서,

상기 태양 전지는 n형 베이스를 가지고, 상기 도핑된 유리는 보로실리케이트 유리를 포함하는 것인, 방법.

**청구항 16**

n형 도핑된 실리콘 베이스 및 박형 a-Si 함유 에미터 영역을 갖는 실리콘 기판 상에 헤테로 접합 에미터 영역을 형성하는 단계로서, 상기 a-Si 영역 부분은 고유하고, 근접 부분은 p형 도핑되는, 단계;

상기 비정질 실리콘 영역의 결정화를 방지하는 온도에서, 더 높은 전도성의 p+ 도핑된 폴리-실리콘 게르마늄층을 증착하는 단계로서, 상기 더 높은 전도성의 p+ 도핑된 폴리-실리콘 게르마늄층은 상기 비정질 실리콘 영역을 지지하는(backing), 단계;

를 포함하는 반도체 태양 전지의 제조방법.

**청구항 17**

제16항에 있어서,

상기 폴리 실리콘 게르마늄의 증착 온도는 450 deg C 이하인 것인, 방법.

**청구항 18**

에미터 및 베이스 접촉을 형성하기 위한 광 포획 전측면 및 후측면을 포함하는, 결정 반도체 기판;

약 40 미크론 미만의 두께를 갖고, 상기 결정 기판의 후측면 상에 에미터 전극 및 베이스 전극의 맞물려진 패턴을 갖는 제1전기 전도성 금속화층;

상기 결정 기판의 상기 후측면에 라미네이팅되고, 프리프레그층을 포함하고, 상기 결정 기판의 후측면에 부착되는 백플레이인; 및

상기 백플레이인의 홀을 통해 상기 제1전기 전도성 상호접속층과 연결되는 고전도성 전지 상호접속을 제공하는 제2전기 전도성 금속화층으로, 상기 제2전기 전도성 상호접속층은 에미터 전극 및 베이스 전극의 맞물려진 패턴을 가지는, 제2전기 전도성 금속화층;

을 포함하는 후면 접촉 결정 반도체 태양 전지.

**청구항 19**

제18항에 있어서,

상기 프리프레그는 프리프레그로부터 리플로우된 수지를 이용하여 상기 결정 기판에 부착되는 것인, 후면 접촉 결정 반도체 태양 전지.

### 청구항 20

제18항에 있어서,

상기 프리프레그는 상기 결정 기판과 상기 백플레이너 사이에 적어도 일부의 부착 영역에 추가적인 수지를 이용하여 상기 결정 기판에 부착되는 것인, 후면 접촉 결정 반도체 태양 전지.

### 청구항 21

제20항에 있어서,

상기 추가적인 수지는 에미터 전극 및 베이스 전극의 상기 맞물려진 패턴에 적어도 부분적으로 평탄화된 것인, 후면 접촉 결정 반도체 태양 전지.

### 청구항 22

제18항에 있어서,

상기 제2전기 전도성 금속화층은 프린팅, 스프레이 또는 빌트-업(built-up)된 층으로 이루어지는 것인, 후면 접촉 결정 반도체 태양 전지.

### 청구항 23

제18항에 있어서,

상기 제2전기 전도성 금속화층은 솔더 또는 전도성 에폭시와 같은 접촉 금속에 따라 상기 제1전기 전도성 금속화층과 접촉하는 것인, 후면 접촉 결정 반도체 태양 전지.

### 청구항 24

제18항에 있어서,

상기 제2전기 전도성 금속화층은 솔더링 가능한 알루미늄과 같은 정형 금속으로 이루어지는 것인, 후면 접촉 결정 반도체 태양 전지.

### 청구항 25

제18항에 있어서,

상기 제2전기 전도성 금속화층은 상기 제1전기 전도성 금속화층에 필수적으로 직각으로 배열되는 것인, 후면 접촉 결정 반도체 태양 전지.

### 청구항 26

제18항에 있어서,

상기 제2전기 전도성 금속화층은 극성 당 적어도 하나의 부스바를 함유하는 것인, 후면 접촉 결정 반도체 태양 전지.

### 청구항 27

제26항에 있어서,

상기 제1전기 전도성 금속화층의 에미터 전극 및 베이스 전극의 맞물려진 패턴은 상기 제2전기 전도성 금속화층의 상기 부스바 아래 영역에 위치되어, 전기적 셰이딩을 감소시키는 것인, 후면 접촉 결정 반도체 태양 전지.

### 청구항 28

제18항에 있어서,

상기 제2전기 전도성 금속화층은 상기 결정 반도체 기판의 주요 결정 축을 통해 열라인되지 않은 인터락 구조체 (interlocked structures)를 포함하는 것인, 후면 접촉 결정 반도체 태양 전지.

### 청구항 29

제18항에 있어서,

상기 결정 반도체 기판은 에피택셜 실리콘 기판인 것인, 태양 전지.

### 청구항 30

제18항에 있어서,

상기 결정 반도체 기판은 얇아지거나 얇아지지 않은 CZ 실리콘 웨이퍼인 것인, 태양 전지.

### 청구항 31

제18항에 있어서,

상기 결정 반도체 기판은 갈륨 비소를 함유하는 물질인 것인, 태양 전지.

### 청구항 32

결정 실리콘 템플레이트의 표면 상에 적어도 두개의 다른 공극률을 갖는 다공성 실리콘 시드 및 분리층을 형성하는 단계;

상기 다공성 실리콘 시드 및 분리층 상에 에피택셜 반도체층을 증착하는 단계로서, 상기 에피택셜 실리콘층은 100 미크론 미만의 두께 및 인시투 도핑된 베이스 영역을 가지고, 상기 에피택셜 실리콘층은 상기 인시투 도핑된 베이스 영역 및 상기 도핑된 에미터 영역을 갖는 에미터 및 베이스 접촉을 형성하기 위한 후측면 및 도핑된 에미터 영역을 포함하는, 단계;

상기 에피택셜 실리콘층의 후측면 상에 베이스 전극 및 에미터 전극의 맞물려진 패턴을 갖는 전기 전도성 금속의 제1층을 증착하는 단계로서, 상기 전기 전도성 금속의 제1층은 2 미크론 미만의 두께를 갖는, 단계;

상기 반도체 기판의 후측면 상에 베이스 전극 및 에미터 전극의 맞물려진 패턴을 갖는 전기 전도성 금속의 제1층을 증착하는 단계로서, 상기 전기 전도성 금속의 제1층은 약 40 미크론 미만의 두께를 갖는, 단계;

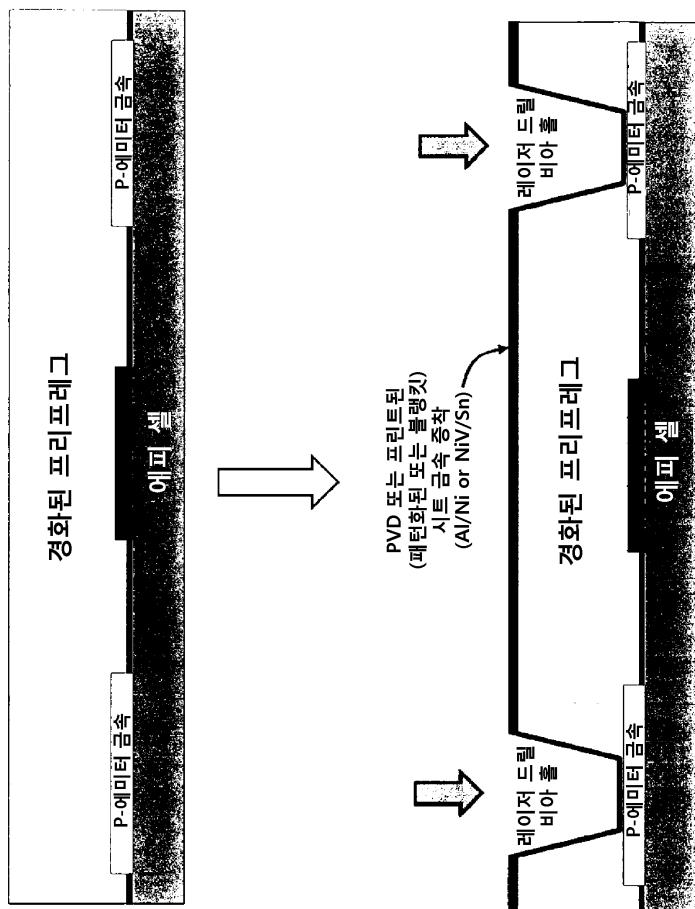

상기 전기 전도성 금속의 제1층에 프리프레그 백플레이인을 라미네이팅하는 단계로서, 상기 프리프레그 백플레이인은 상기 전기 전도성 금속의 제1층과 전기 전도성 금속의 제2층 사이에 전기적 분리를 제공하는, 단계;

레이저 공정에 따라 상기 프리프레그 백플레이인에 홀을 형성하는 단계로서, 상기 홀은 상기 전기 전도성 금속의 제1층에 접근을 제공하는, 단계;

이 구조체의 상부 상에 제2전기 전도성 금속화층을 적용하는 단계로서, 상기 제2전기 전도성 금속화층은 상기 홀을 통해 상기 전기 전도성 금속의 제1층과 접촉하는, 단계;

를 포함하는, 후면 접촉 태양 전지의 제조방법.

### 청구항 33

제32항에 있어서,

상기 백플레이인 보강된 에피택셜 실리콘층은 상기 비아홀을 형성하기 전에 상기 템플레이트로부터 분리되는 것인, 방법.

### 청구항 34

제32항에 있어서,

상기 템플레이트로부터 상기 에피택셜 실리콘층이 분리된 후, 열적 어닐링에 따라 비정질 실리콘 및 실리콘 나이트라이드를 이용하여 상기 전극을 텍스처링 및 패시베이팅하는 단계를 더 포함하는, 방법.

### 청구항 35

제33항에 있어서,

상기 프리프레그 백플레이인의 후측면 상에 상기 제2금속화층의 증착은, 상기 프리프레그 백플레이인의 상기 홀을 통해 전기 전도성 금속의 제1층과 전기적 상호 접속을 형성하는 세미-에디티브 공정에 따라 일어나는 것인, 방법.

### 청구항 36

제33항에 있어서,

상기 제2금속화층은, 블랭킷 시드층의 증착 후, 상기 시드층의 패터닝 마스킹 후, 마스킹되지 않은 영역의 전기 도금 후, 상기 마스킹의 제거 및 상기 마스킹된 영역 아래에 상기 시드층의 제거의 순으로, 전기 도금으로 적용되는 것인, 방법.

### 청구항 37

제33항에 있어서,

상기 제2금속화층은, 우선 패터닝된 시드층의 적용 및 상기 시드층 상에 직접적으로 전기 도금함으로써 적용되는 것인, 방법.

### 청구항 38

제33항에 있어서,

상기 비아홀은 CO<sub>2</sub> 레이저를 이용하여 드릴링되는 것인, 방법.

### 청구항 39

제33항에 있어서,

레이저 드릴링에 의해 상기 비아홀을 개방한 후 및 상기 제2층의 시드의 적용 전, 상기 비아홀은 웨트 화학 에

칭을 이용하여 세정되는 것인, 방법.

## 청구항 40

제33항에 있어서,

레이저 드릴링에 의해 상기 비아홀을 개방한 후 및 상기 제2층의 시드의 적용 전, 상기 비아홀은 대기 또는 감압 플라즈마 에칭을 이용하여 세정되는 것인, 방법.

## 청구항 41

제33항에 있어서,

상기 비아홀은 상기 제1전기 전도성 금속층 내에 상기 비아홀을 중단하는(stopping) 레이저를 이용하여 드릴링 되는 것인, 방법.

## 명세서

### 기술 분야

[0001]

관련 출원의 상호 참조

[0002]

본 출원은 2011년 8월 9일에 출원된 미국 가출원 61/521,754 및 61/521,743의 이익을 주장하는 것이며, 이 내용은 전체가 여기에 참조로 인용된다.

[0003]

본 발명은 일반적으로 광기전 및 반도체 초소형 전자 공학의 분야에 관한 것이다. 더욱 구체적으로, 본 발명은 고효율 후면 접촉 결정 실리콘 광기전 태양 전지에 관련된 방법, 구조체 및 장치에 관한 것이다.

## 배경 기술

[0004]

최근, 결정 실리콘(다결정 및 단결정 실리콘)은 광기전 (PV) 산업에서 가장 큰 마켓 쉐어를 가지고, 최근에는 전체 글로벌 PV 마켓 쉐어의 약 85%를 차지한다. 더 얇은 결정 실리콘 태양 전지로의 이행은 PV 비용 감소를 위해 가장 강력하고 효율적인 방법 중 하나로 오랫동안 이해되고 있지만(총 PV 모듈 비용의 비율로서 태양 전지에 사용되는 결정 실리콘 웨이퍼의 상대적으로 높은 물질의 비용 때문에), 더 얇은 결정 웨이퍼를 이용하는 것은, 박형 웨이퍼가 웨이퍼 처리 및 전지 가공 동안 매우 약해지고, 기계적으로 파손되고, 박형 및 약한 실리콘 웨이퍼에 의해 야기되는 수득하는 제품 수율의 손실의 문제에 의해 방해된다. 실리콘은 간접적 밴드갭 반도체 물질이고, 더 긴 파장 적색 및 적외 광자 (특히 약 900 nm 내지 1150 nm의 파장 범위의 것들)의 흡수가 상대적으로 긴 광학 경로 길이-종종 웨이퍼 두께보다 훨씬 큰 길이-를 요구하기 때문에, 박형 전지 구조체에서 부적절한 광 포획과 같은 다른 문제들을 포함한다. 또한, 공지의 디자인 및 제조 기술을 이용하여, 비용 효율적인 방법으로 PV 공장에서 높은 제조 수율을 가지면서 감소된 웨이퍼 파손율 및 높은 기계적 수율의 요건의 균형을 맞추는 것은 종종 용이하지 않다.

[0005]

현재의 결정 실리콘 웨이퍼 태양 전지의 기판 (반도체 흡수체) 두께와 관련하여, 현재 두께 범위 140  $\mu\text{m}$  to 200  $\mu\text{m}$ 보다 훨씬 더 얇아지도록 하는 움직임은 전지 및 모듈 제조 동안 기계적 수율과 염격하게 충돌하기 위해서 시작되었다. 이는 특히 156 mm x 156 mm 및 210 mm x 210 mm 전지 (더 작은 125 mm x 125 mm 전지와 비교해서)와 같은 더 큰 사이즈의 전지에 있어서는 큰 도전이다. 따라서, 약 100  $\mu\text{m}$ 에서 미크론 사이즈 스케일까지 및 서브미크론 두께보다 더 얇은 전지 반도체 흡수체와 같은 초박형 태양 전지 구조체를 제조하려는 제조 가능한 해결 방법으로는, 공정 흐름에서 일시적 및/또는 영구적 호스트 캐리어에 의해 전지가 완전히 지지되는 동안의 전지 공정, 또는 구조적 혁신을 수반하는 새로운 자가 지지(self-supporting), 독립형(stand-alone) 기판을 이

용하는 전지 공정을 이용해야 한다. 이러한 구조적 혁신으로는 전지 기판이 고출력 태양 전지 및 모듈 공장에서의 과순에 대해서 매우 강해지도록 해야 한다. 후자의 예는 결정 실리콘 박막으로 형성된 3차원 별집 및 피라미드 구조체이다.

[0006] 전지 구조체 측에 대해서, 후면 접합/후면 접촉 단결정 반도체(예컨대 단결정 실리콘) 태양 전지는 초고효율에 도움이 된다. 이는, 주로 블루 리스핀스(blue response)를 높이는데 도움을 주는, 전측 상에 에미터가 없고 전측 상에 손실과 관련된 금속 셰이딩이 없기 때문이다. 또한, n형 베이스의 사용은, p형 베이스와 비교하여 소수 캐리어가 훨씬 길어지도록 할 뿐만 아니라, 광 유도 분해 (Light-Induced Degradation, LID)가 없도록 해준다. 게다가, n형 베이스를 갖는 후면 접촉/후면 접합 전지는 장-보조 패시베이션(field-assisted passivation)에 의해 가능해진 전측면 재조합 속도(Frontside Surface Recombination Velocity, FSRV)를 갖는 개선된 전측면 패시베이션을 제공하는 실리콘 나이트라이드를 포함하는 패시베이션층 (또는 층 스택)에 포지티브 고정된 전하를 갖는 반사 방지 코팅층 및 잘-확립된(well-established) 실리콘 나이트라이드 전측 패시베이션을 사용할 수 있다. 또한, 후측 금속은, 전면 접촉 전지에서 종종 고려되는 셰이딩을 갖도록 트레이드 오프되는 것에 대한 걱정 없이 매우 낮은 직렬 저항(또는 매우 높은 금속 상호 접속 전기 전도성)을 보증하기 위해 더 높은 면적 범위(예컨대 90% 초과)를 가지고, 더 두껍게 제조될 수 있다. 후면 접촉/후면 접합 전지는 특히 초박형(예컨대 적어도 2가지 뚜렷한 이유를 위한 태양 전지 기판)으로 조합되도록 하는 것에 매우 도움이 된다. 첫째, 고효율 후면 접촉/후면 접합 전지는 적어도  $5 \times$  (적어도 약 5의 인자) 기판의 두께(또는 활성 결정 반도체 흡수체)의 소수 캐리어 디퓨전 길이 ( $L_{eff}$ 로 알려진)를 갖는 것에 대한 엄격한 요건을 갖는다. 초박형(예컨대 약 80 미크론 미만, 더욱 바람직하게는 약 50 미크론 미만의 결정 반도체층 두께를 갖는) 태양 전지 기판은 매우 긴 별크 기판 수명 또는 매우 높은 품질의 물질의 손상 없이 이러한 요건을 가능하게 하여, 실제는 가장 엄격한 기판 품질의 요건이 제거된 더 저렴한 출발 물질에서 행해질 수 있다. 이는 다른 비용적 이점을 간접적으로 제공한다: 상기 물질의 품질은 안정화될 수 있고, 더 얇아진다. 두번째 이유는 후면 접촉 전지 구조체 및 관련된 공정 흐름은 전지의 일 측 상에 고온 공정 단계(즉, 약 400 °C 내지 ~1150 °C 범위의 공정 온도를 갖는 임의의 전지 공정 단계)를 가지도록 영향되기 때문에, 다른 측 상에 공정을 겪게되는 경우에, 박형 기판의 캐리어에 대한 요건은 상당히 용이해진다. 따라서, 후면 접촉/후면 접합 구조체와 함께 초박형 기판(예컨대 약 80 미크론 미만, 더욱 바람직하게는 약 50 미크론 미만의 결정 반도체층 두께를 갖는)을 이용하는 것은, 이상적인 태양 전지 조합을 나타낼 수 있다.

[0007] 과거에, 박형 기판으로 유리와 같은 캐리어를 이용하기 위한 태양 PV R&D에서의 시도가 있어왔다; 그러나, 이러한 캐리어는, 소다 라임 유리(또는 대부분의 다른 비실리콘 이물질(non-silicon foreign material))의 경우에, 가공 온도가 약 400 °C 미만-태양 전지 효율과 잠재적으로 절충될 수 있는-이 되도록 제한된다는, 상대적으로 낮은 최대 가공 온도를 포함하는 심각한 제한으로부터 곤란을 겪었다. 또한, 심각한 과순 문제를 갖지 않는 작은 면적(예컨대  $10 \text{ cm}^2$  미만의 전지 면적)의 박형 전지를 제조하려는 시도가 있었다(이들은 약 400 °C 미만의 공정 온도의 제한을 포함하는 고온 가공 제한으로부터 곤란을 겪었기 때문에); 그러나, 큰 전지 면적( $100 \text{ cm}^2$  초과 면적)은 종종 비용 효율적인 제조를 통한 상업적 실행 가능성의 요구되었다.

## 발명의 내용

### 과제의 해결 수단

[0008] 따라서, 후면 접촉 태양 전지와 관련된 디자인 및 제조 방법에 대한 필요가 증가하고 있다. 개시된 주제에 따라, 후면 접촉 태양 전지를 제조하기 위한 방법, 구조체 및 장치가 여기에 개시된다. 이러한 혁신은 이전에 개발된 후면 접촉 태양 전지와 관련된 단점 및 문제를 실질적으로 감소하거나 제거한다.

[0009] 상기 개시된 주제의 일 측면에 따라, 태양 전지 기판 보강재 및 전기 상호접속을 제공하는 후면 접촉 태양 전지의 백플레이에 관련된 구조체 및 제조 방법이 개시된다. 일 실시예에서, 후면 접촉 후면 접합 태양 전지는 광

포획 전측면을 갖는 기판, 도핑된 베이스 영역, 및 상기 도핑된 베이스 영역과 반대의 극성을 갖는 도핑된 후측 에미터 영역을 포함한다. 금속화 패턴은 태양 전지의 후측 상에 위치되고, 영구적 보강재는 전지에 지지를 제공한다.

[0010] 추가적인 새로운 특징들뿐만 아니라 개시된 주제의 이러한 및 다른 이점은 여기에 제공되는 설명으로부터 명백해질 것이다. 이 요약의 목적은, 주제의 포괄적인 설명을 하려는 것이 아니라, 주제의 기능의 일부의 간략한 오버뷰를 제공하기 위한 것이다. 여기에 제공되는 다른 시스템, 방법, 특징 및 이점은 이하 도면들 및 상세한 설명을 검토하면서 당업자에게 명백해질 것이다. 이 설명 내에 포함되는 추가적인 시스템, 방법, 특징 및 이점 모두는 청구항의 범위 내가 되도록 하였다.

### 도면의 간단한 설명

[0011] 개시되는 주제의 특징, 특성 및 이점은, 유사한 참조 번호는 유사한 특징을 나타내는 도면과 함께 취해지는 경우에 이하에 설명되는 상세한 설명으로부터 더욱 명백해질 것이다:

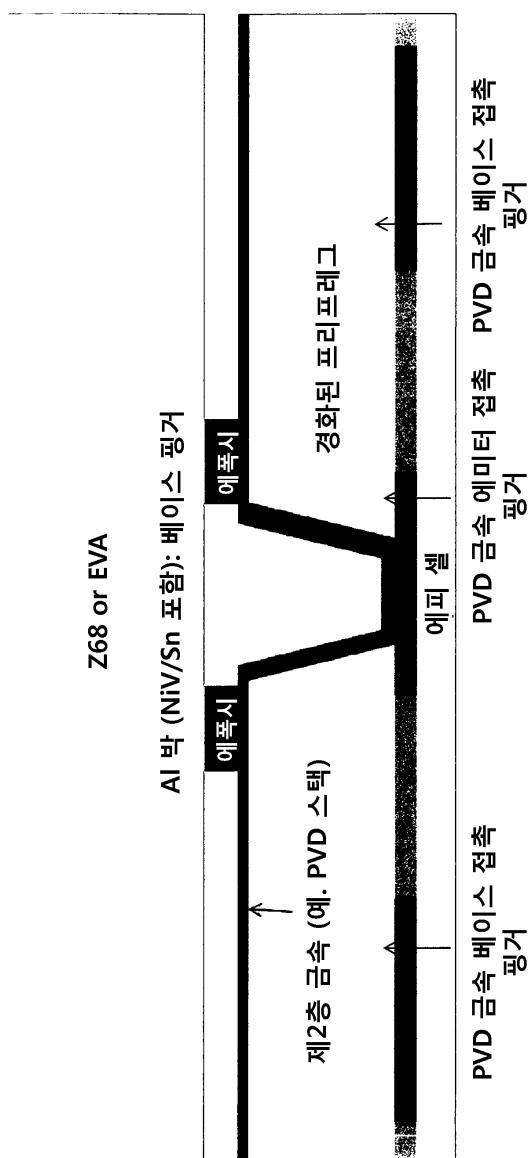

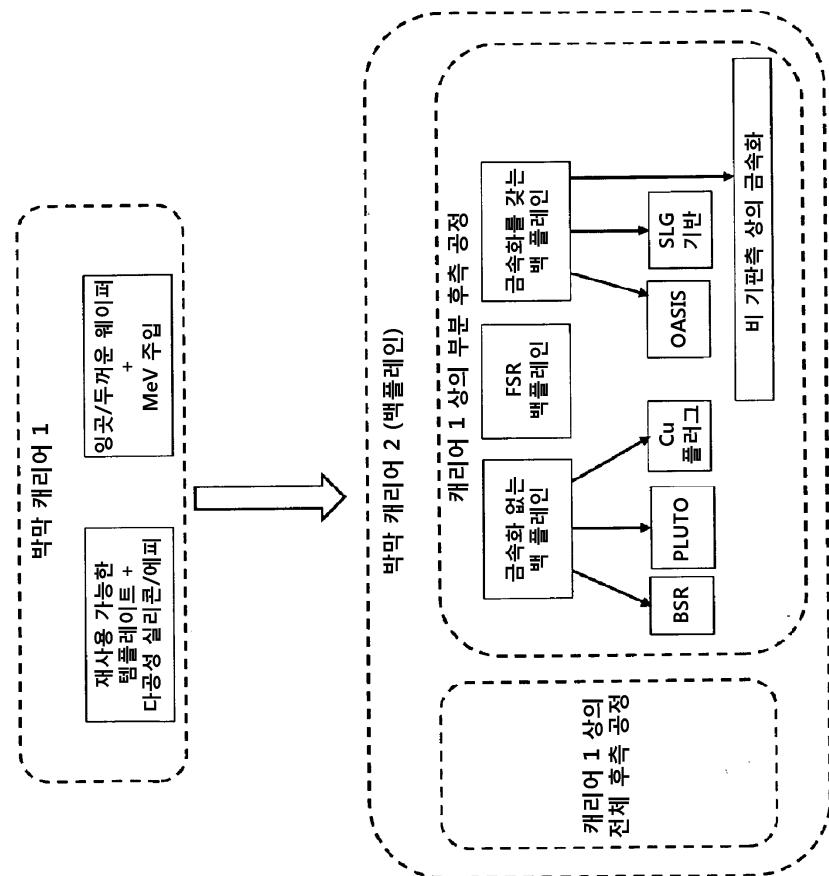

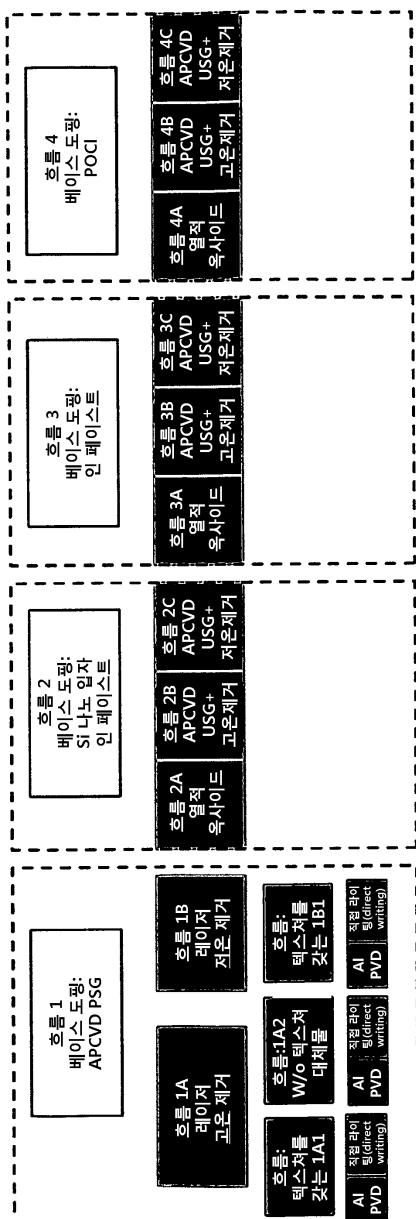

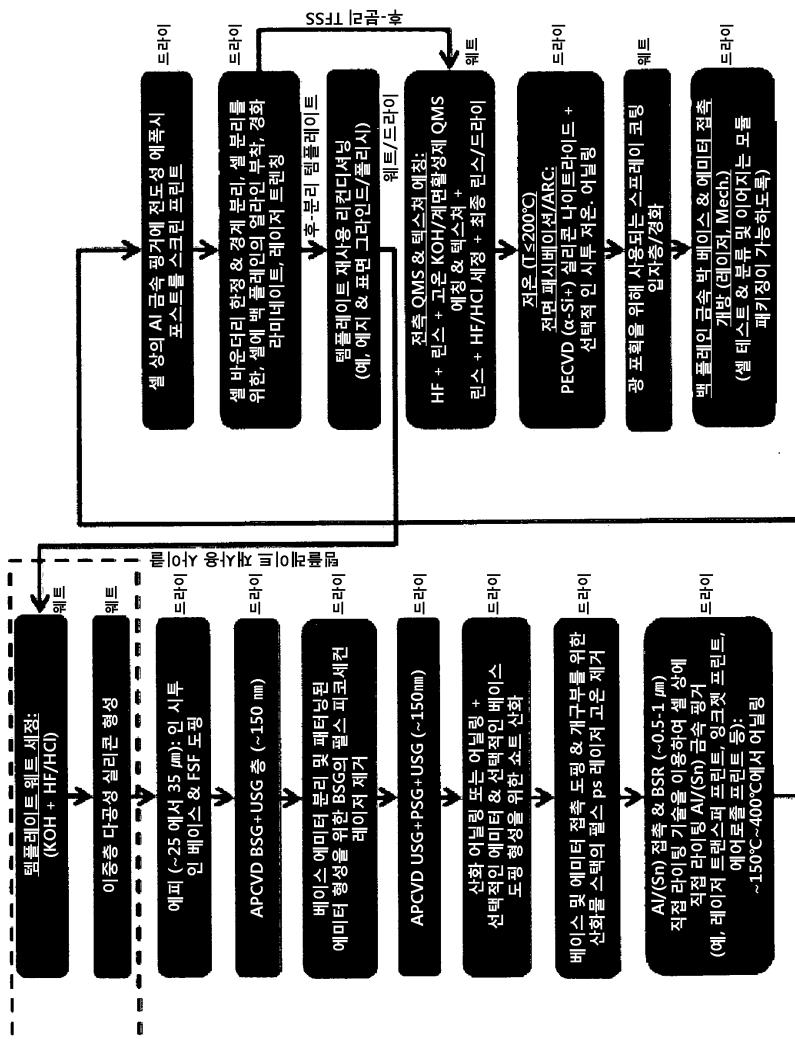

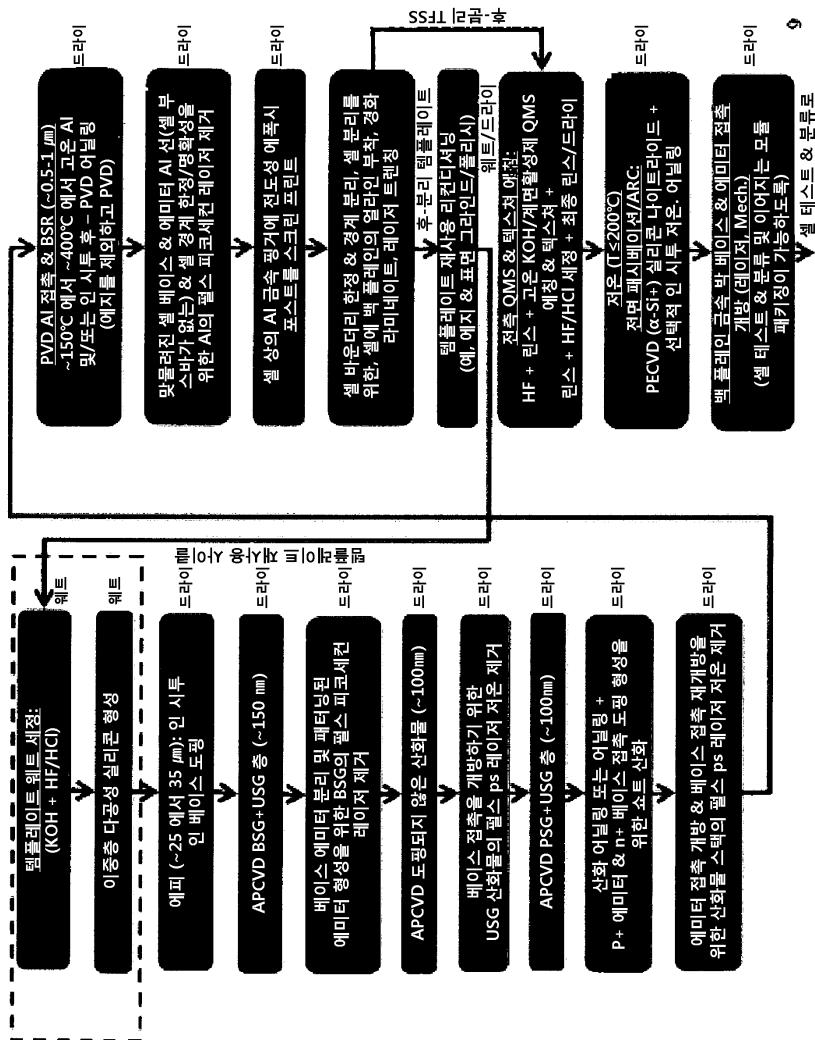

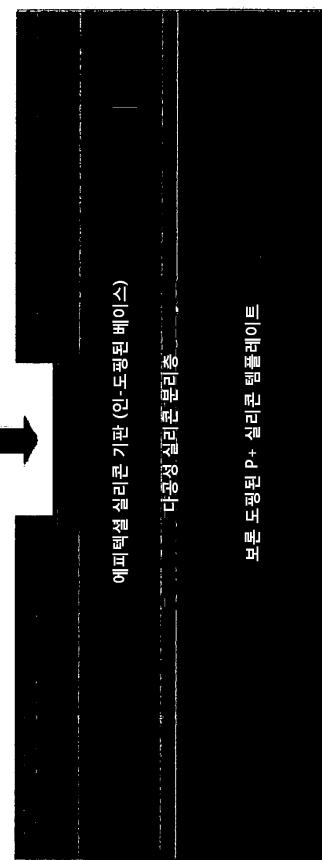

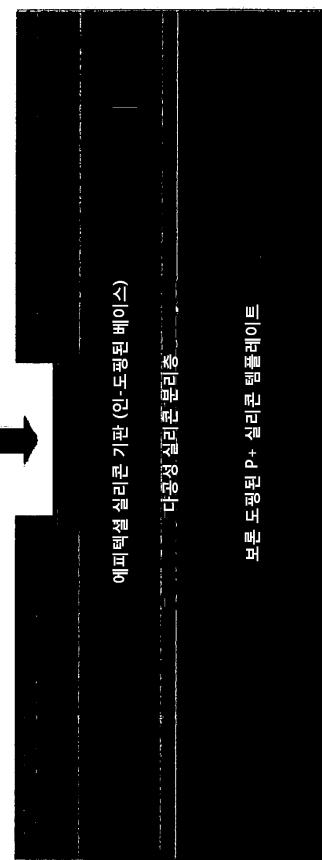

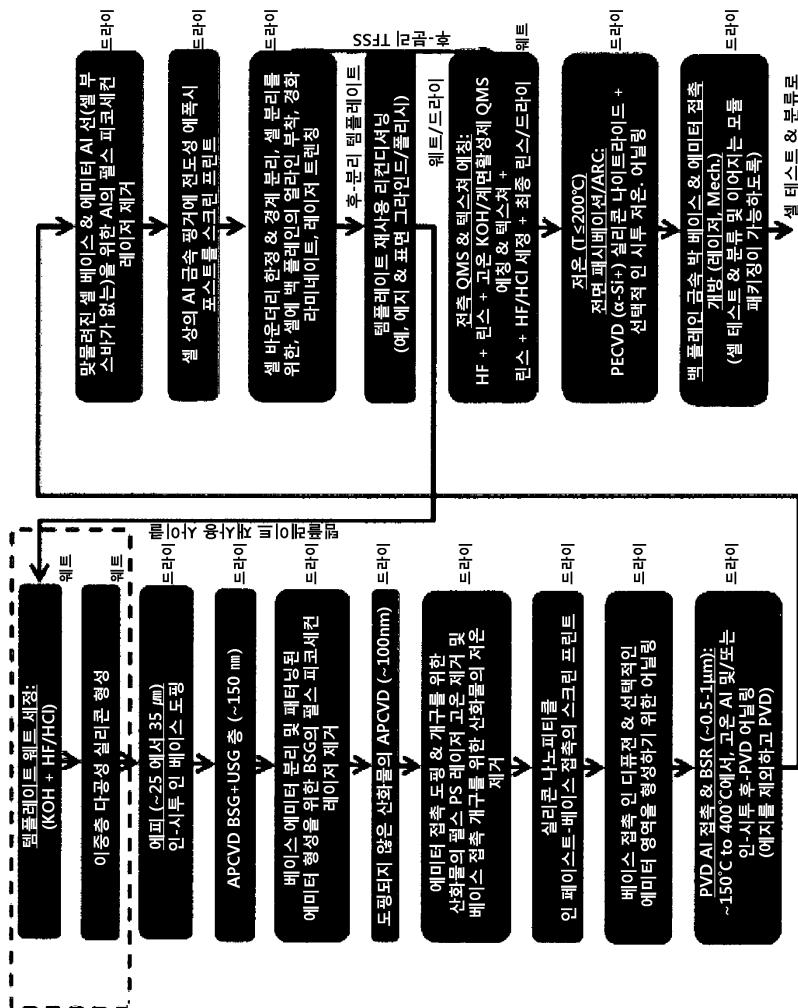

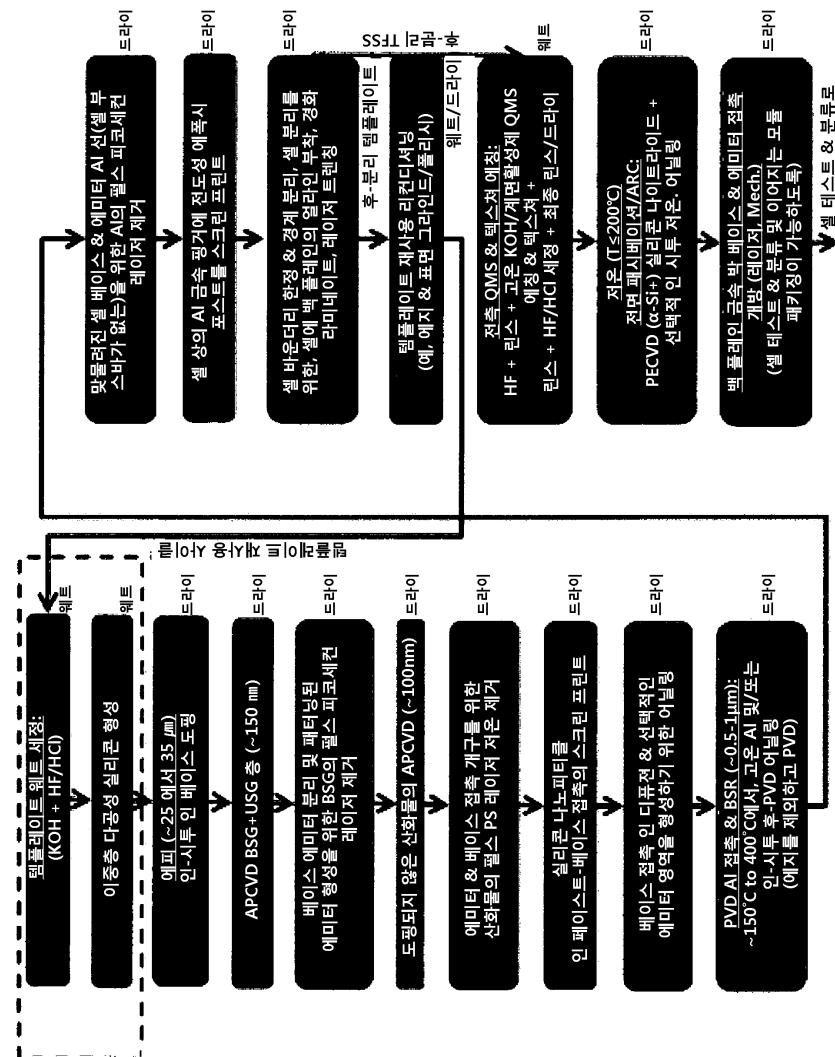

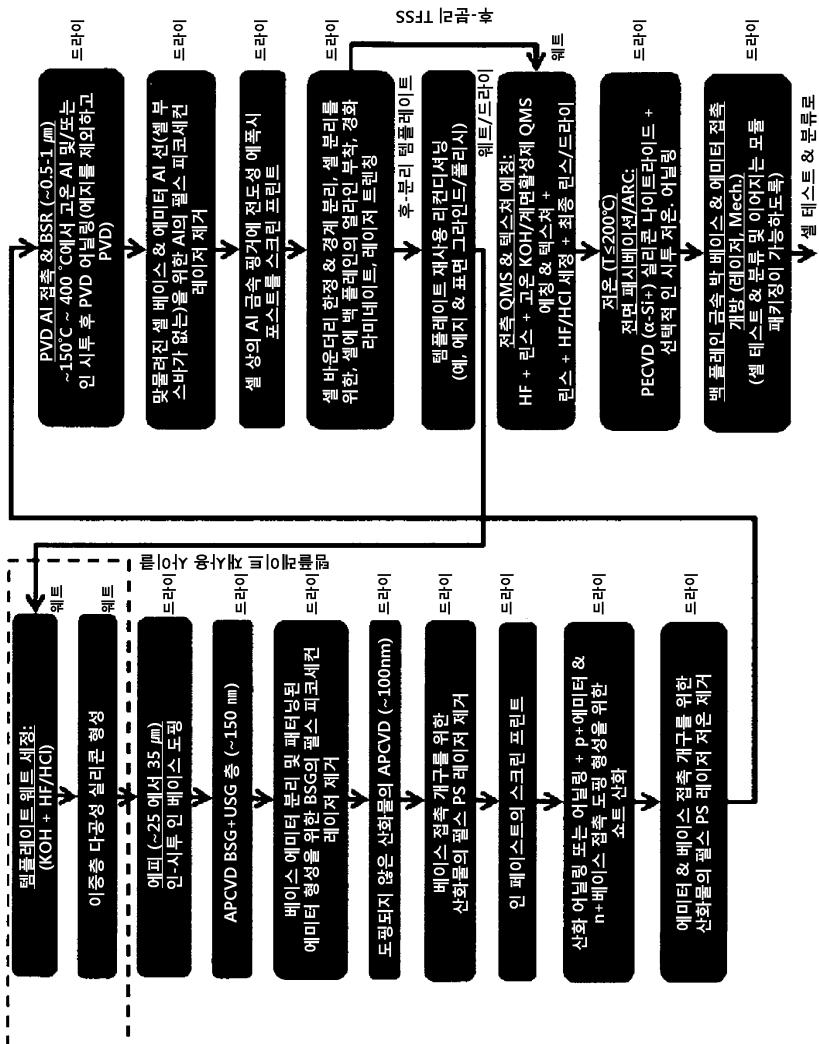

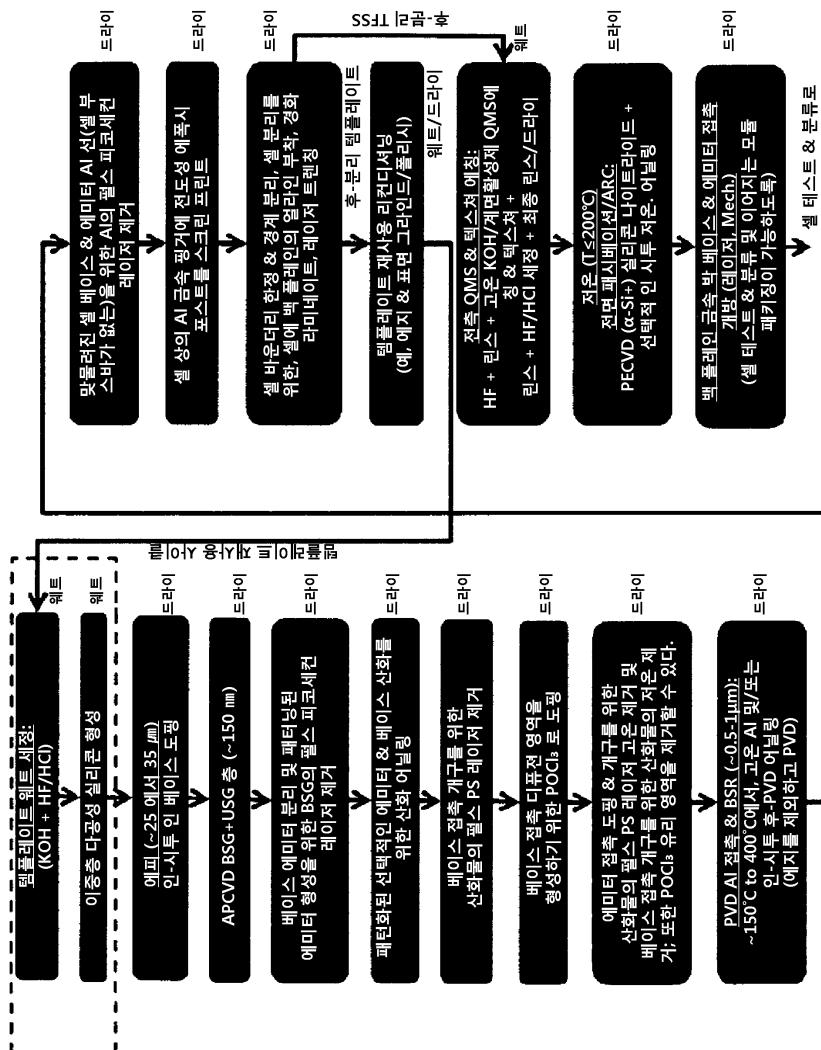

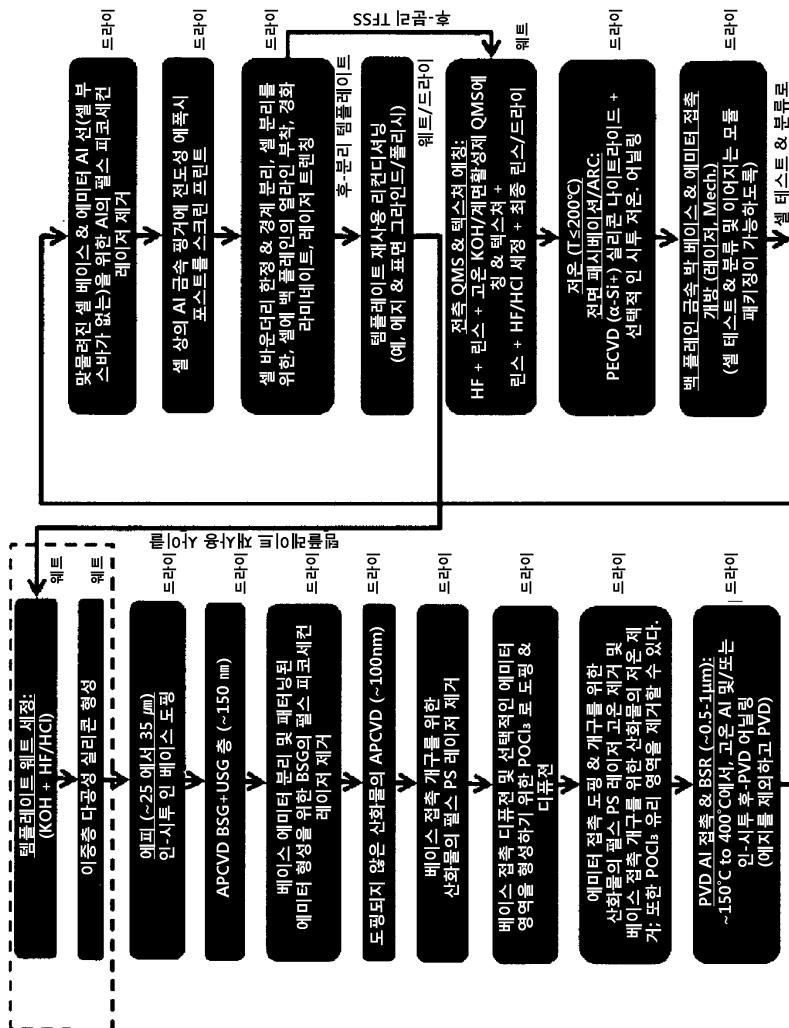

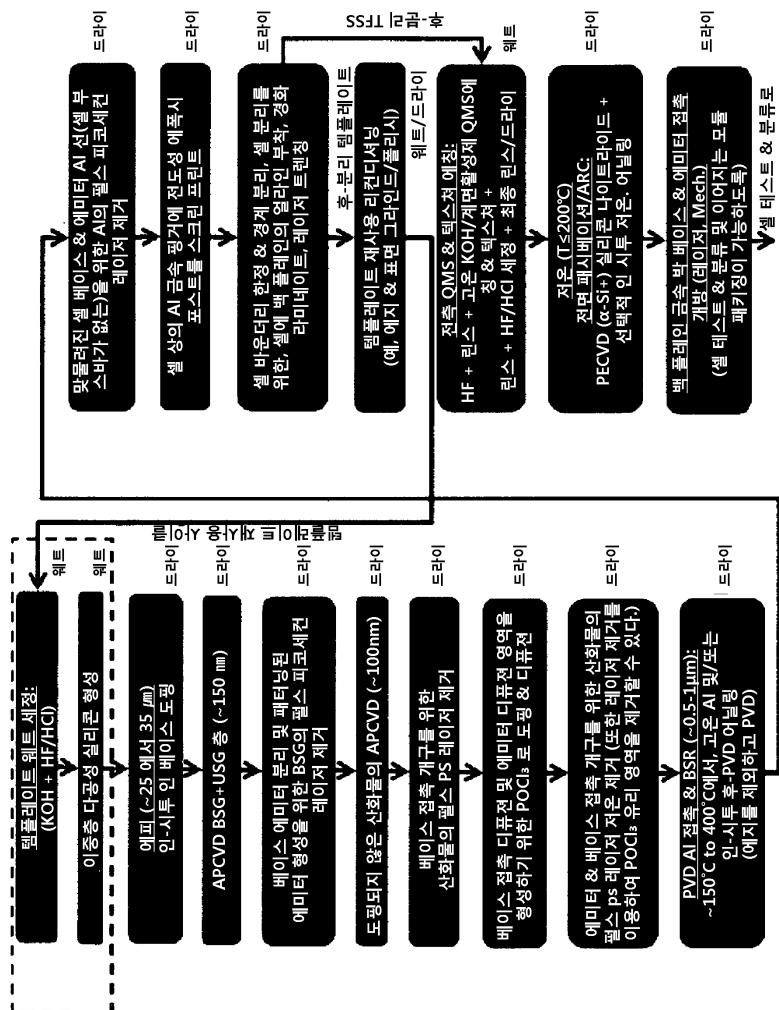

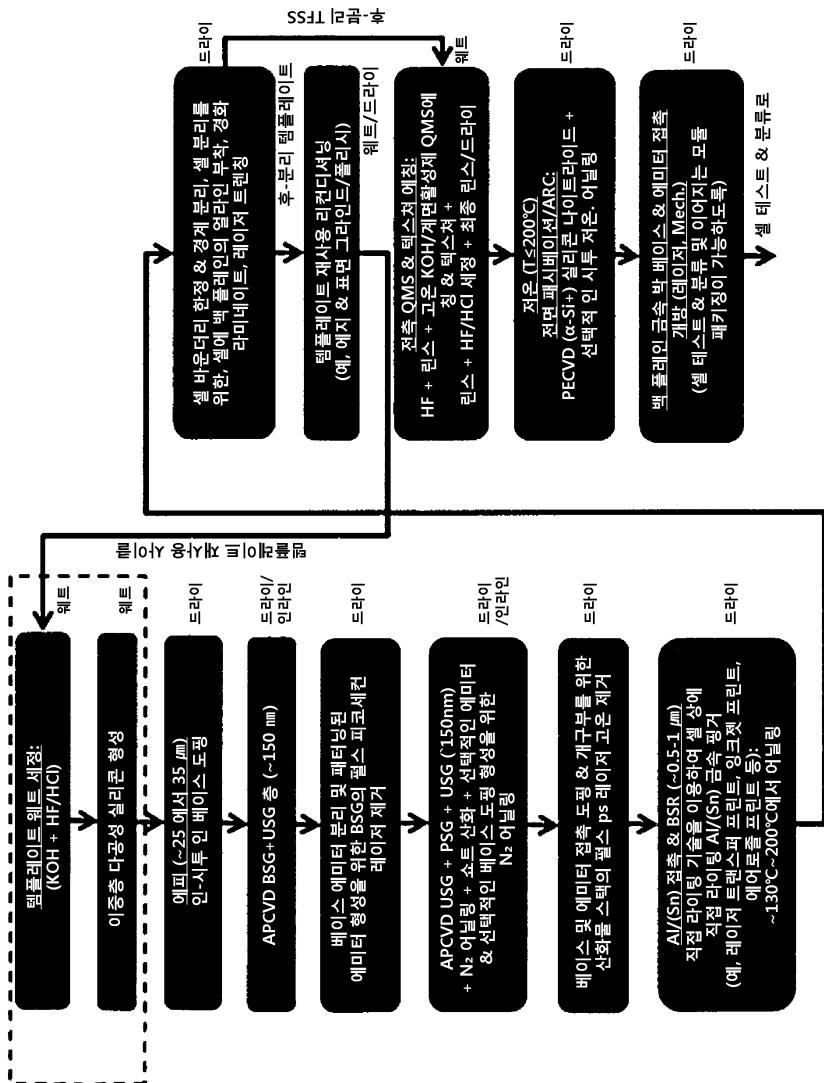

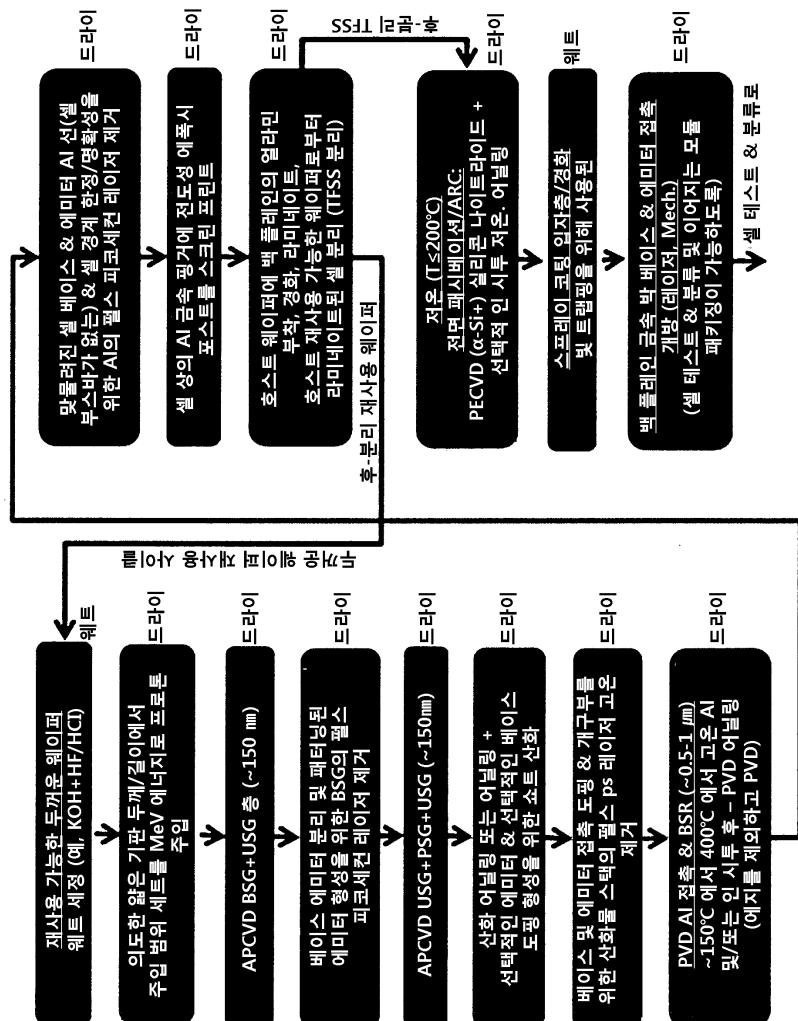

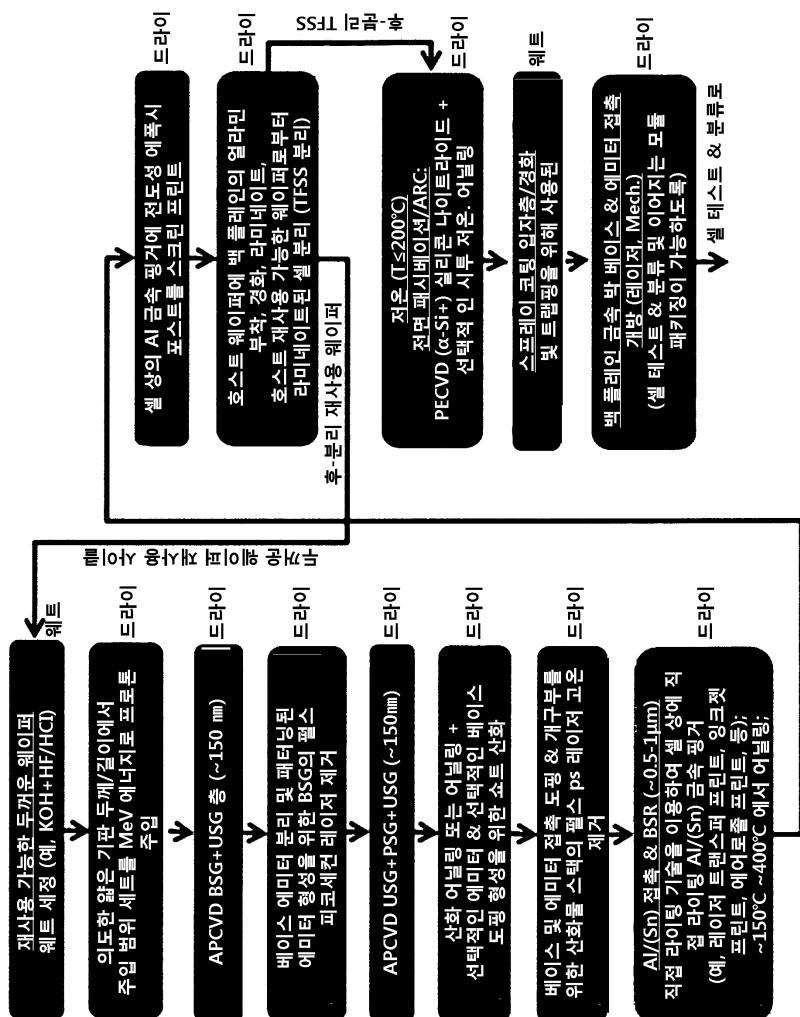

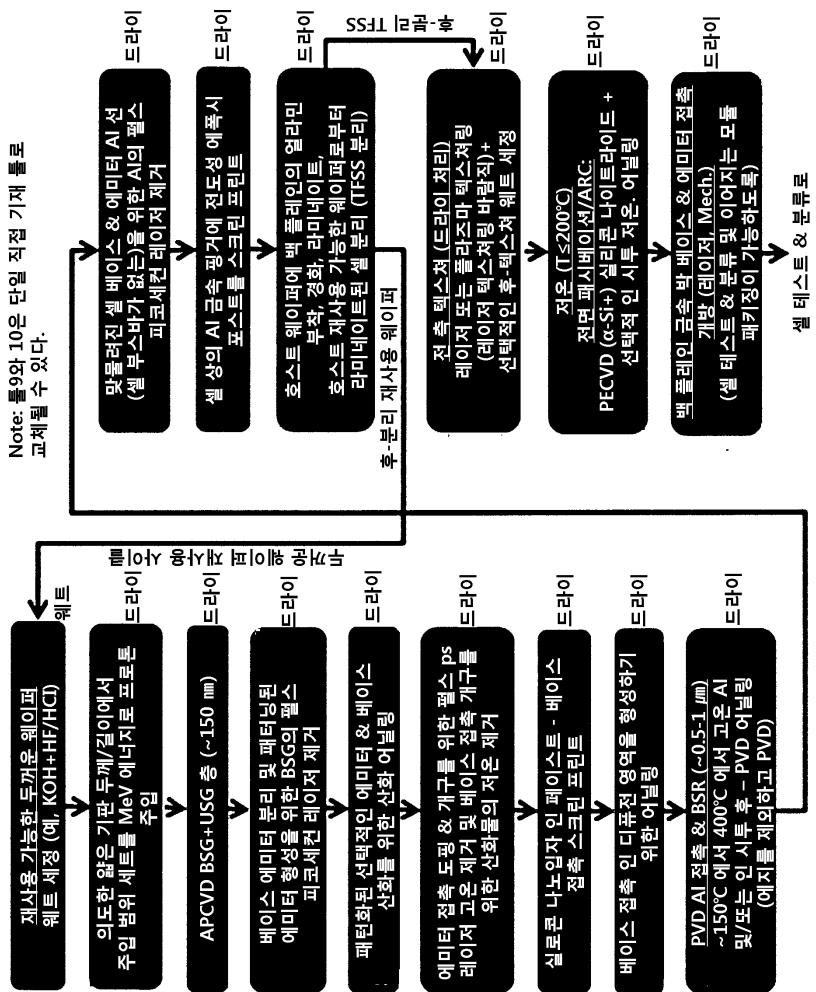

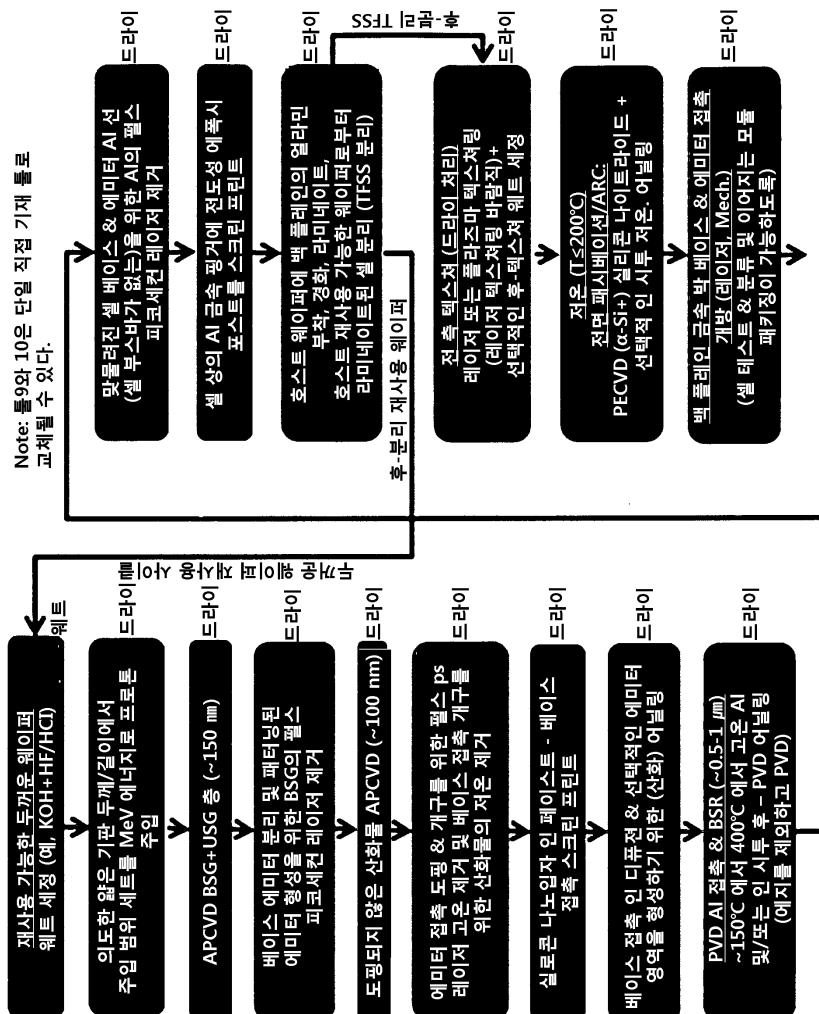

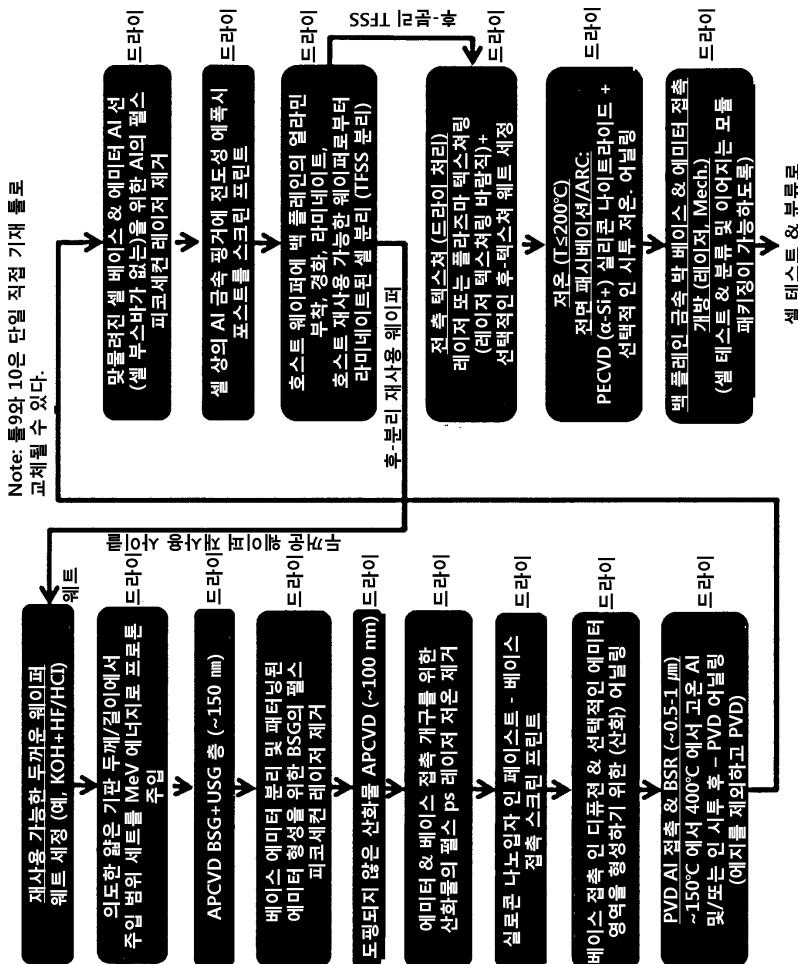

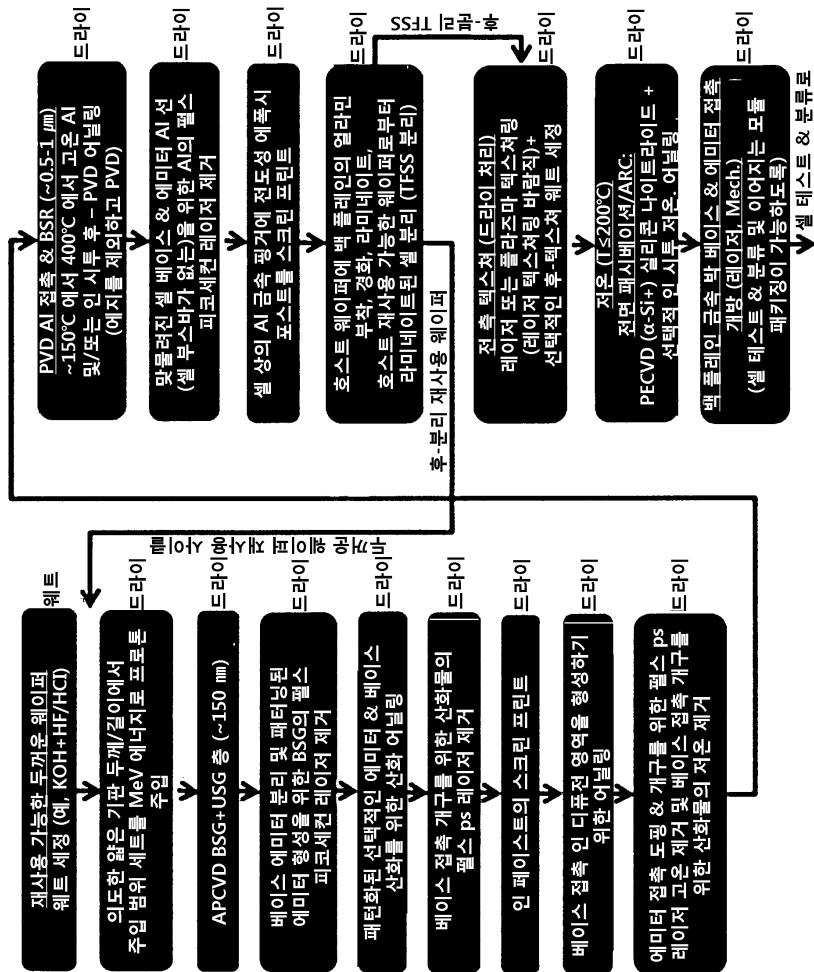

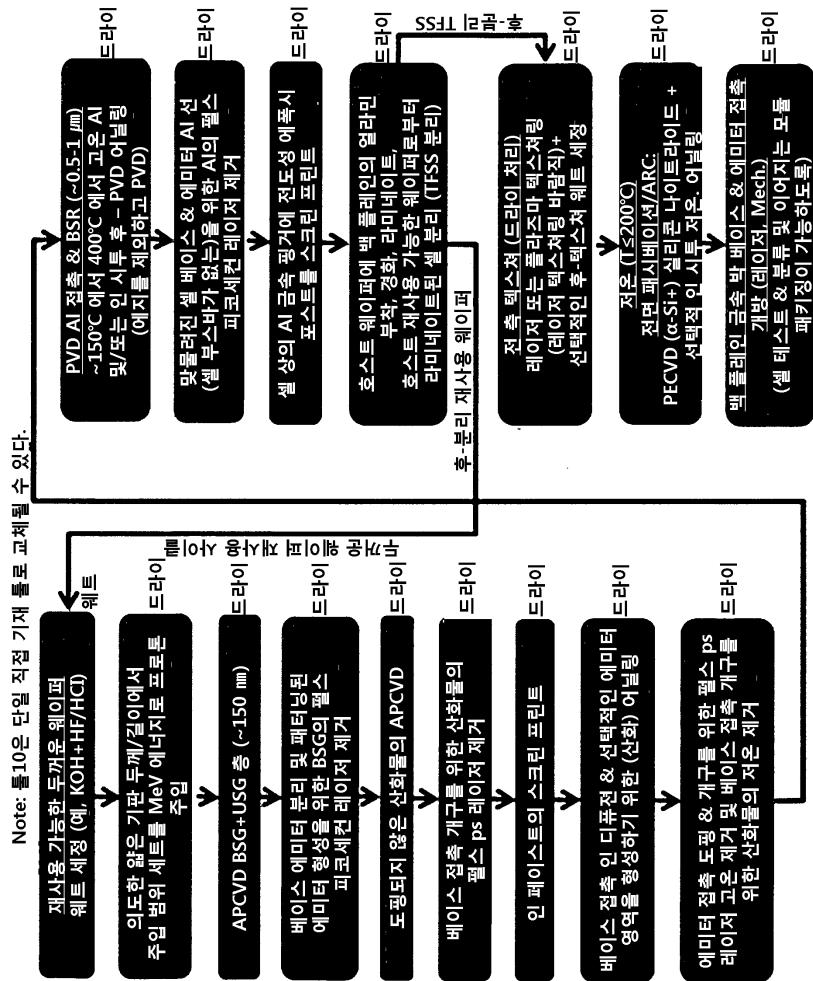

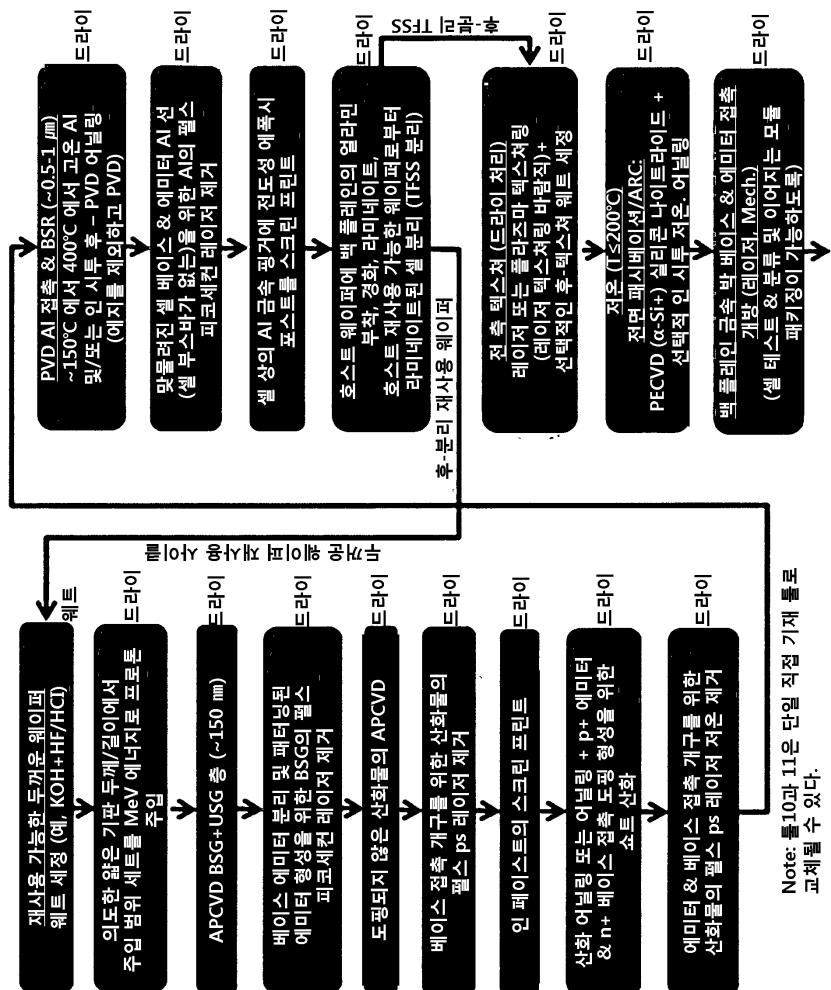

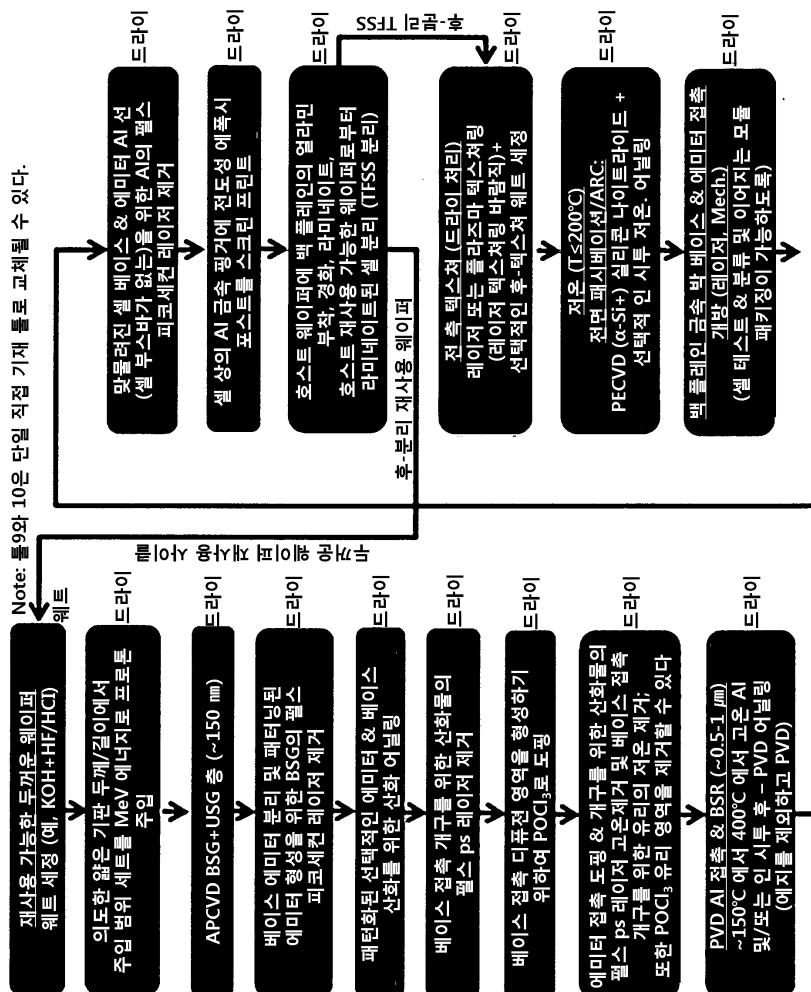

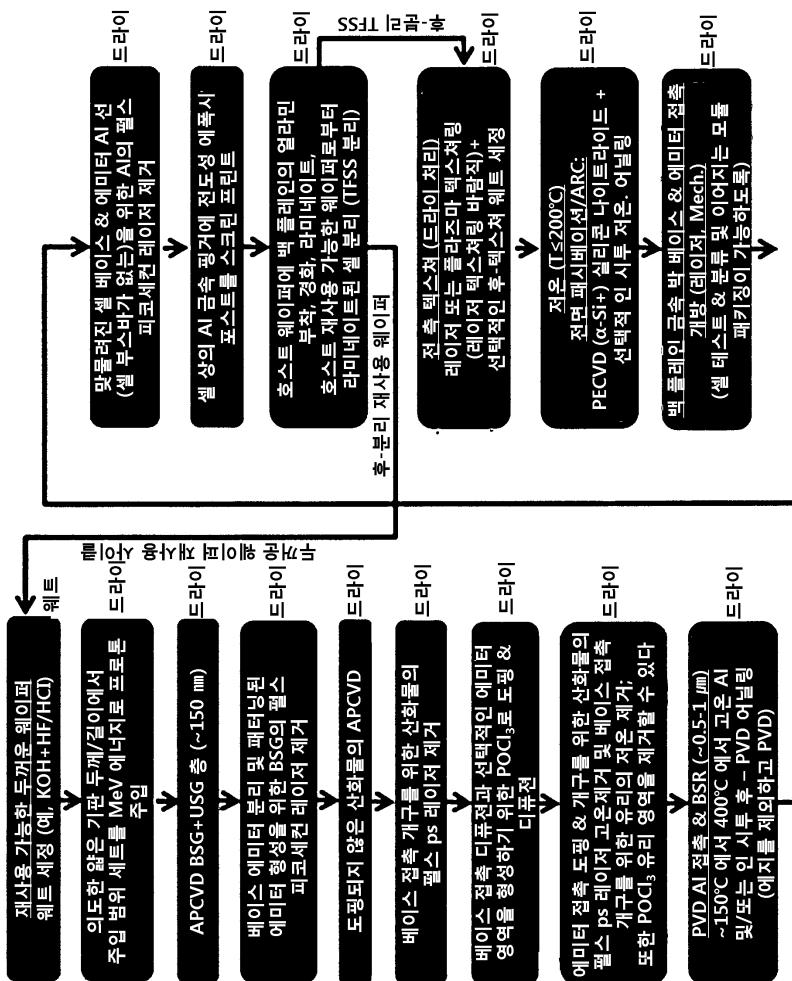

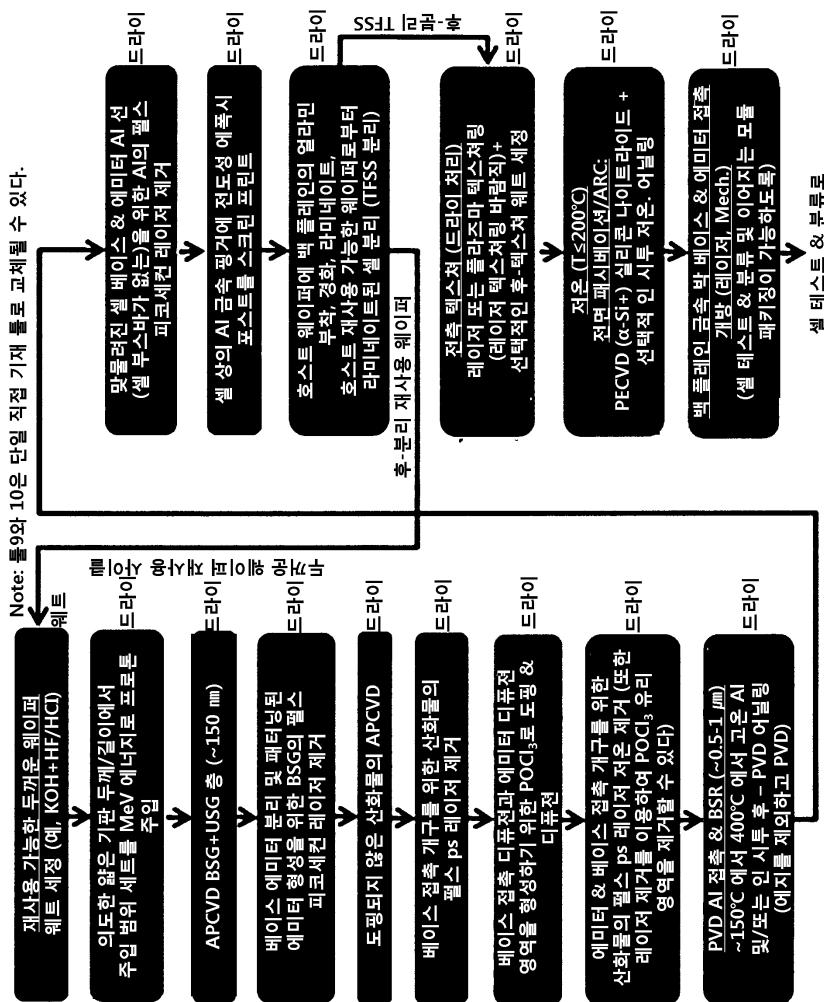

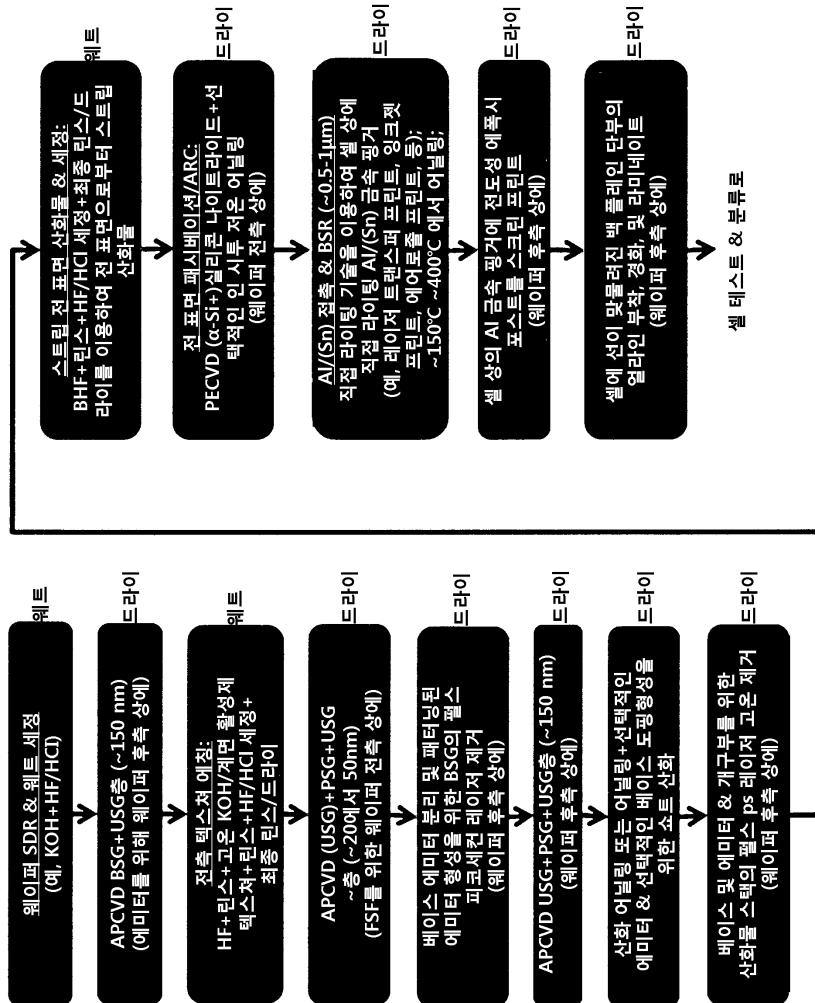

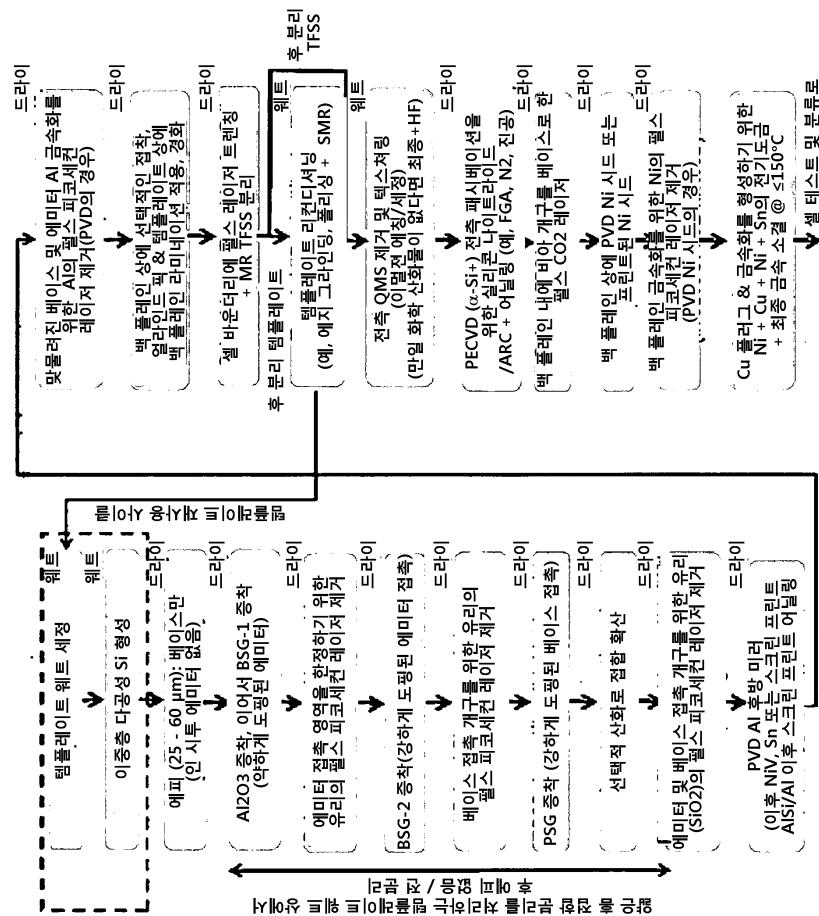

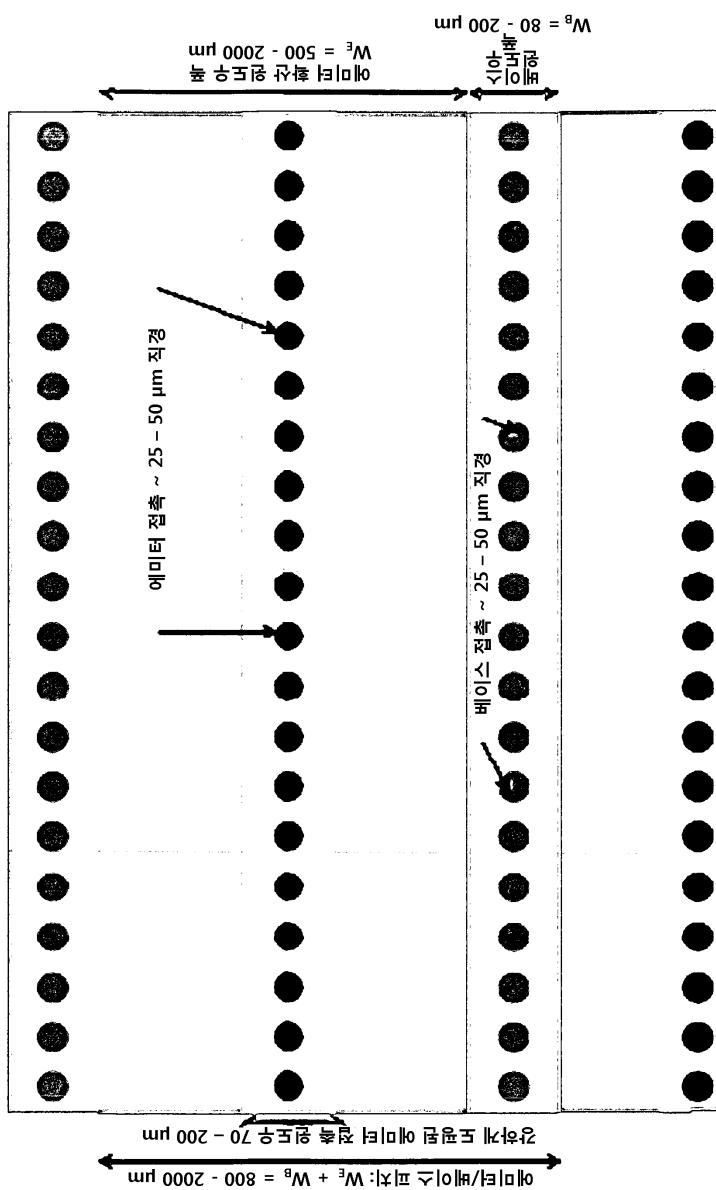

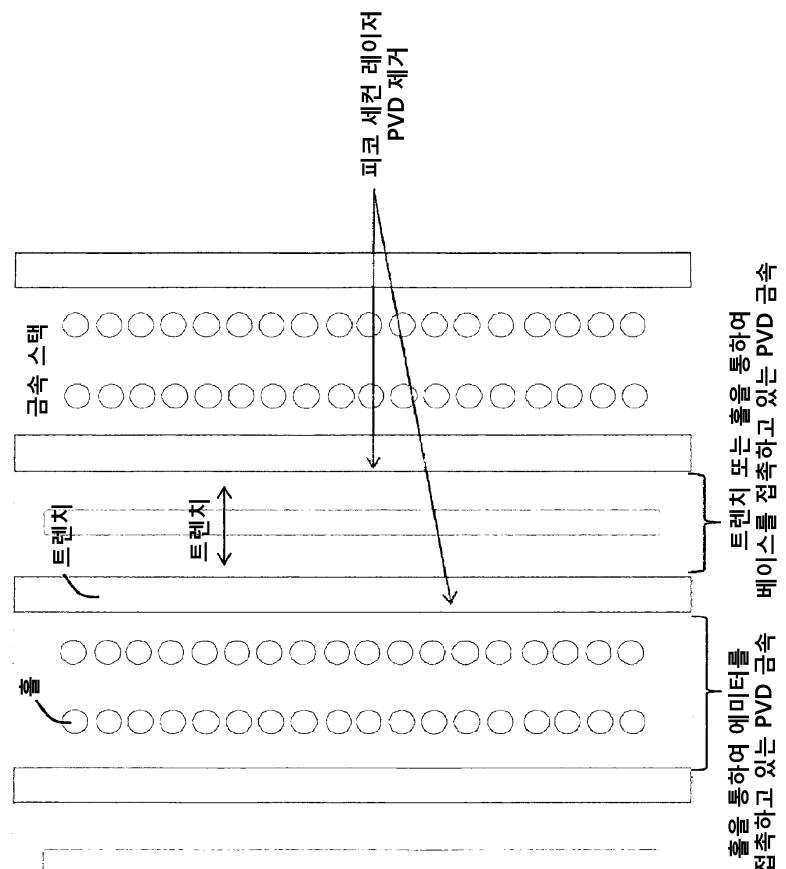

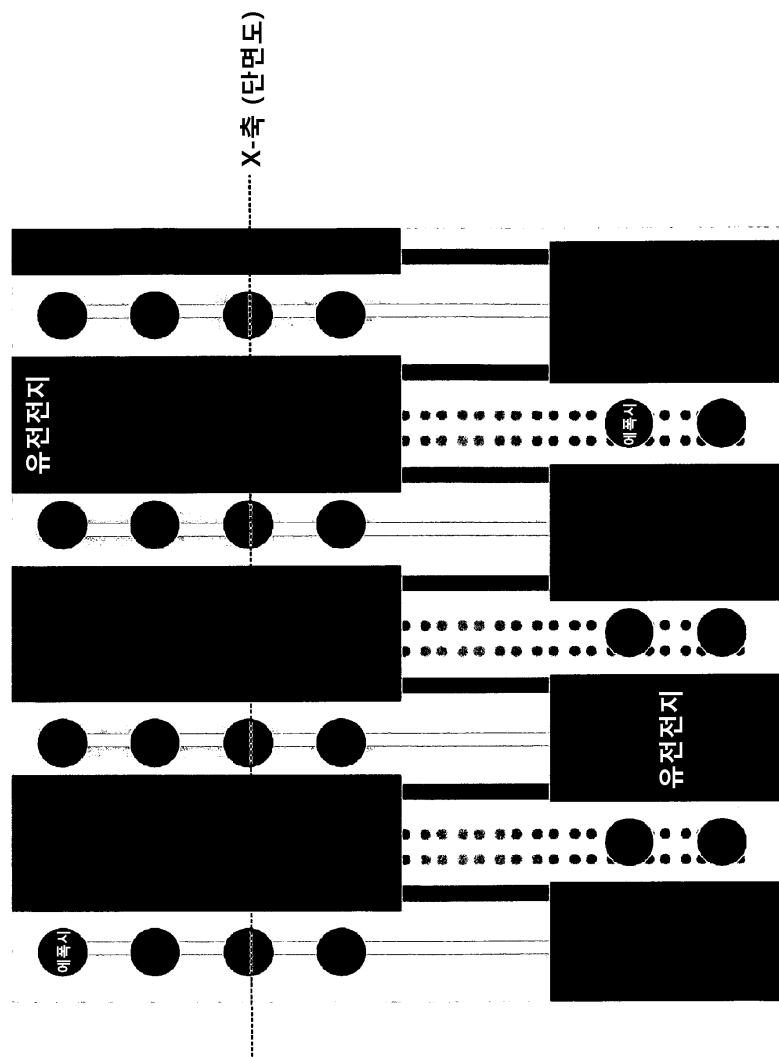

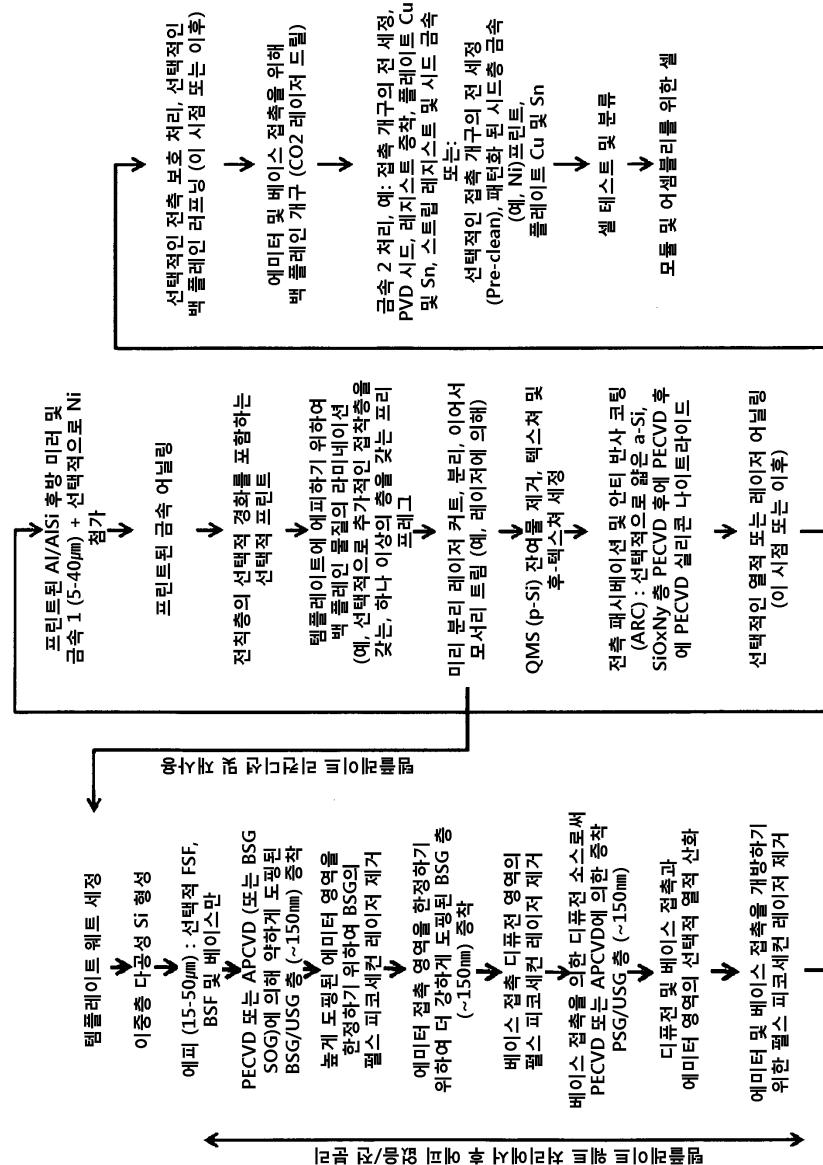

도 1은 태양 전지 가공 캐리어 조합을 설명하는 다이어그램이다;

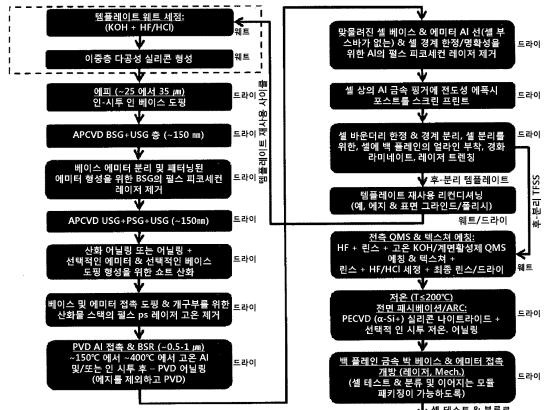

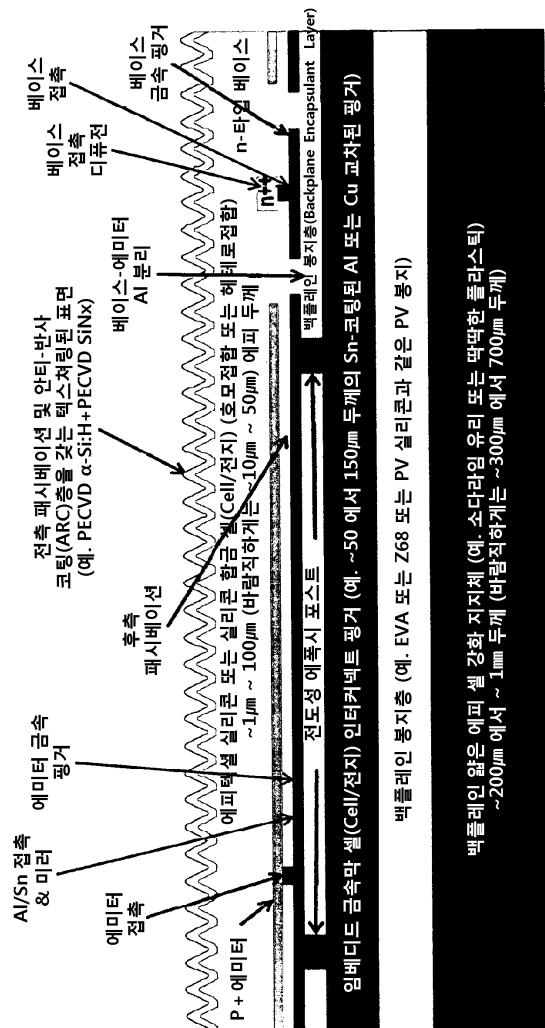

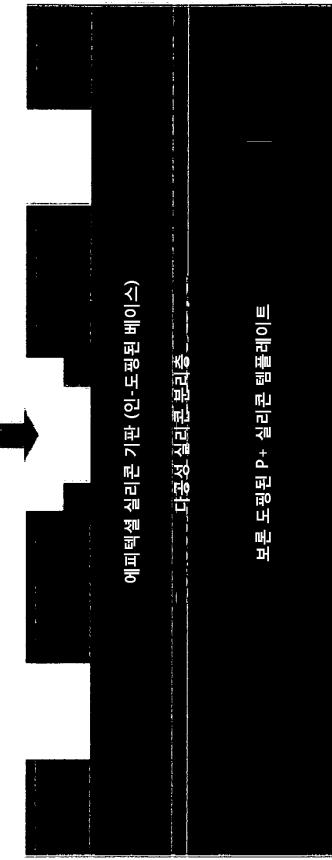

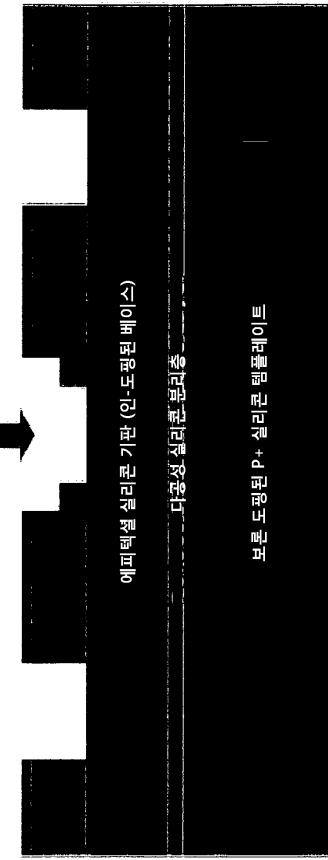

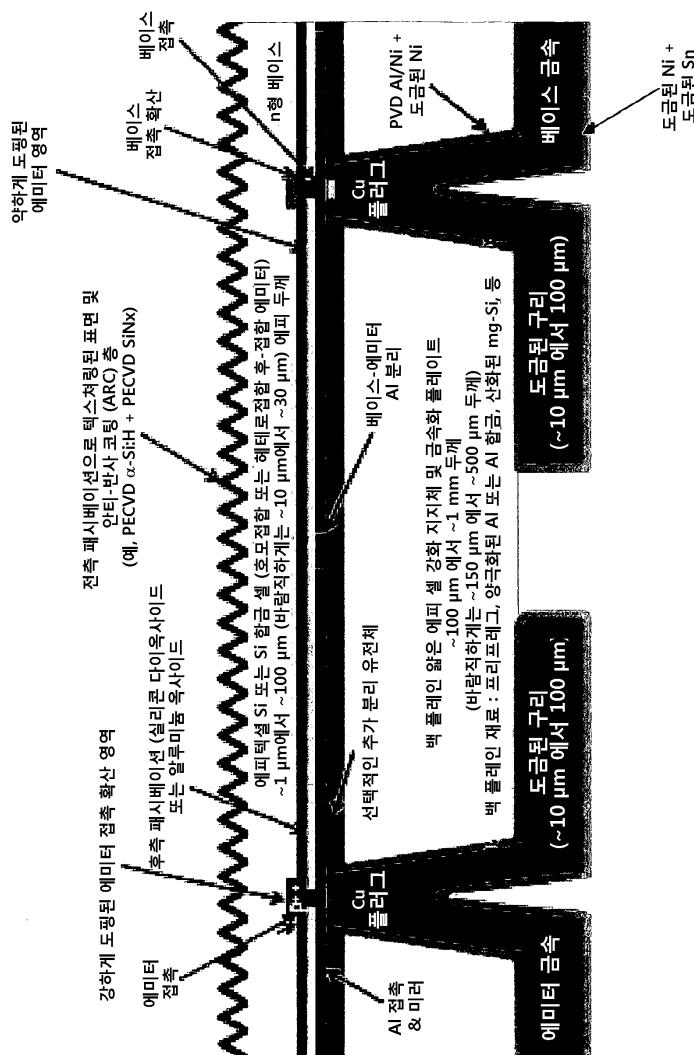

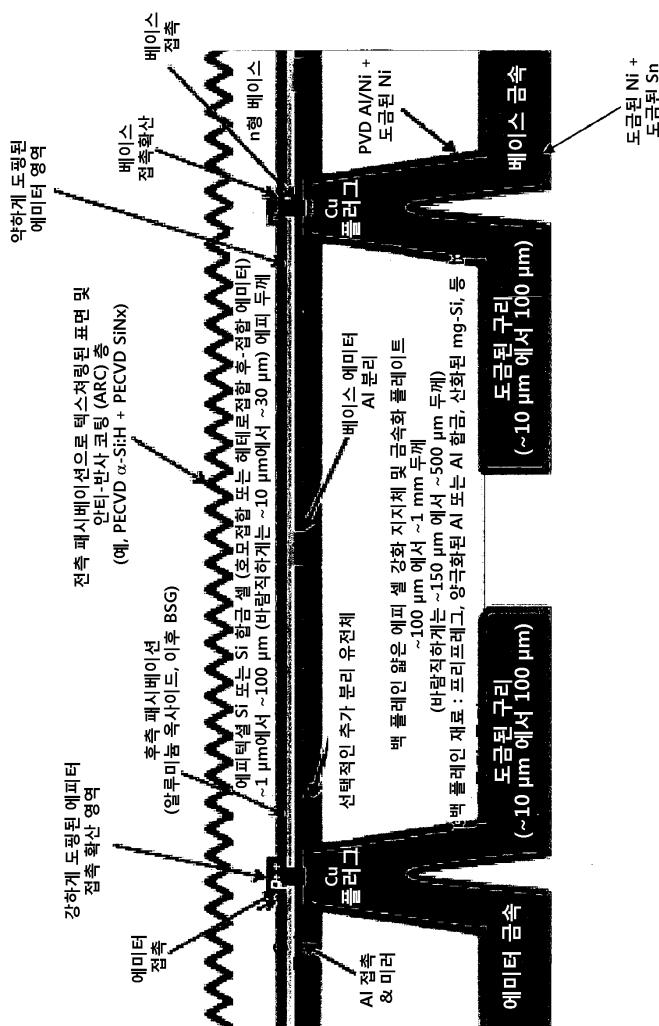

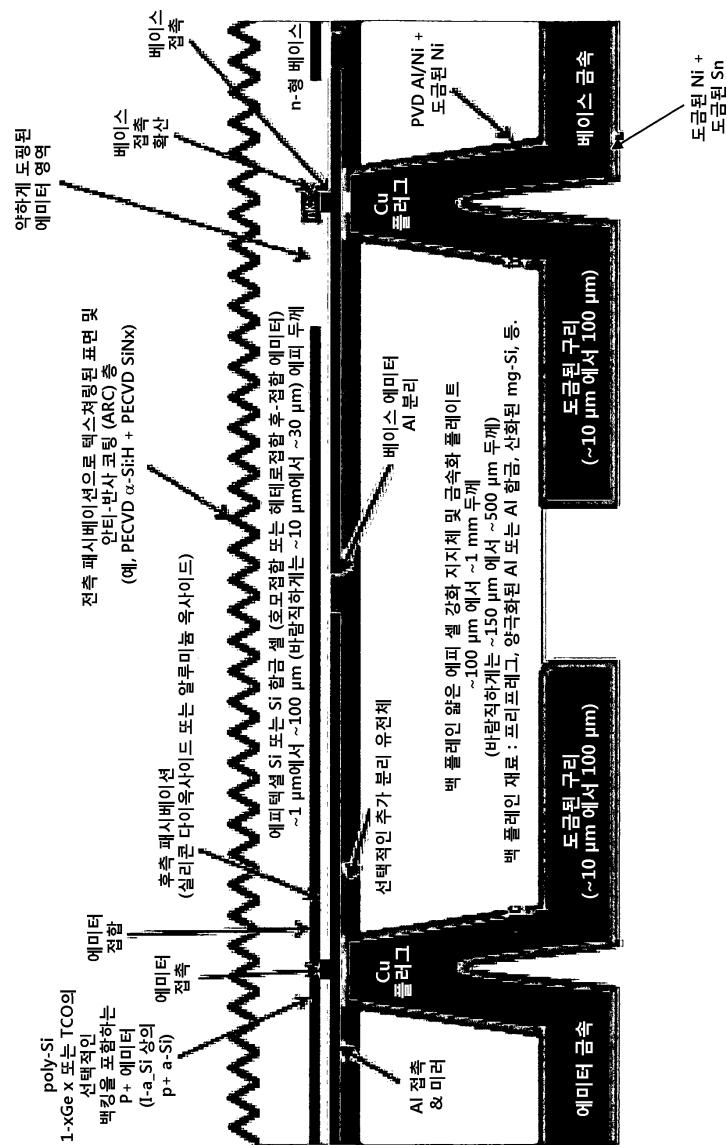

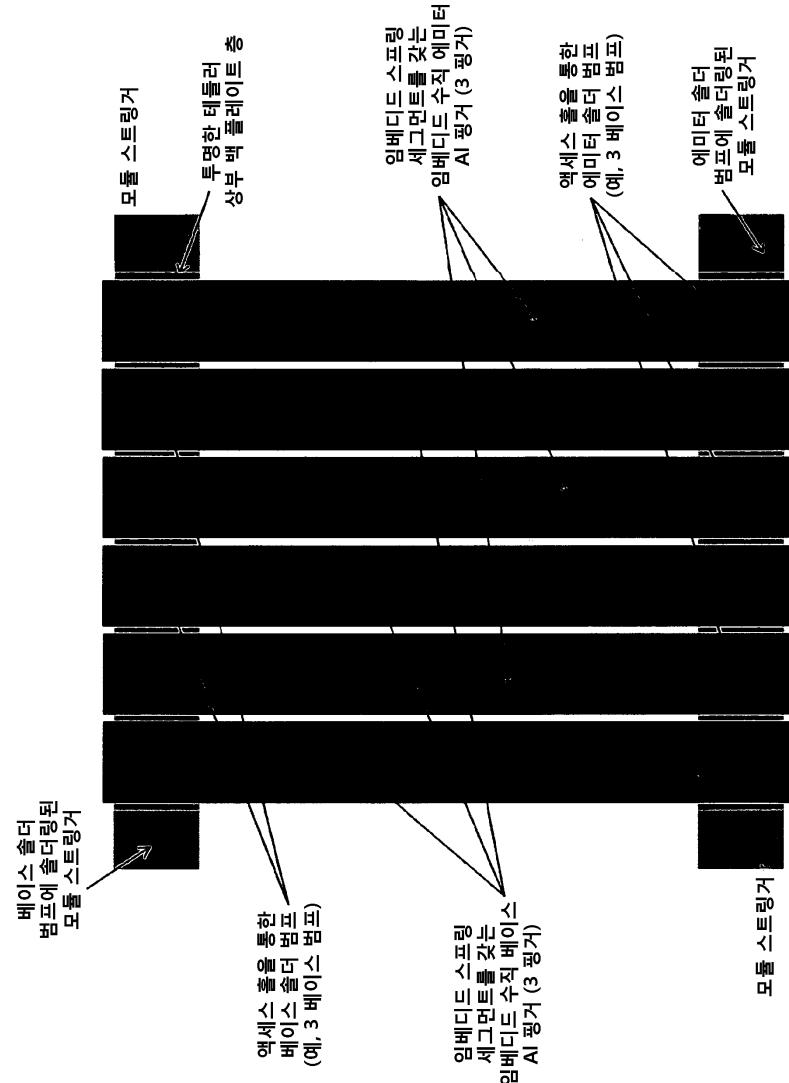

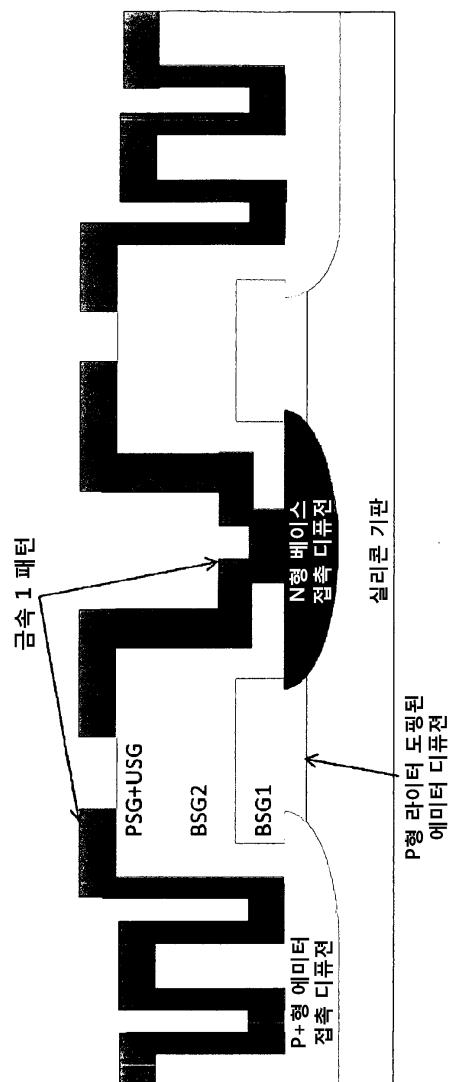

도 2는 후면 접촉 태양 전지의 실시예의 단면도이다;

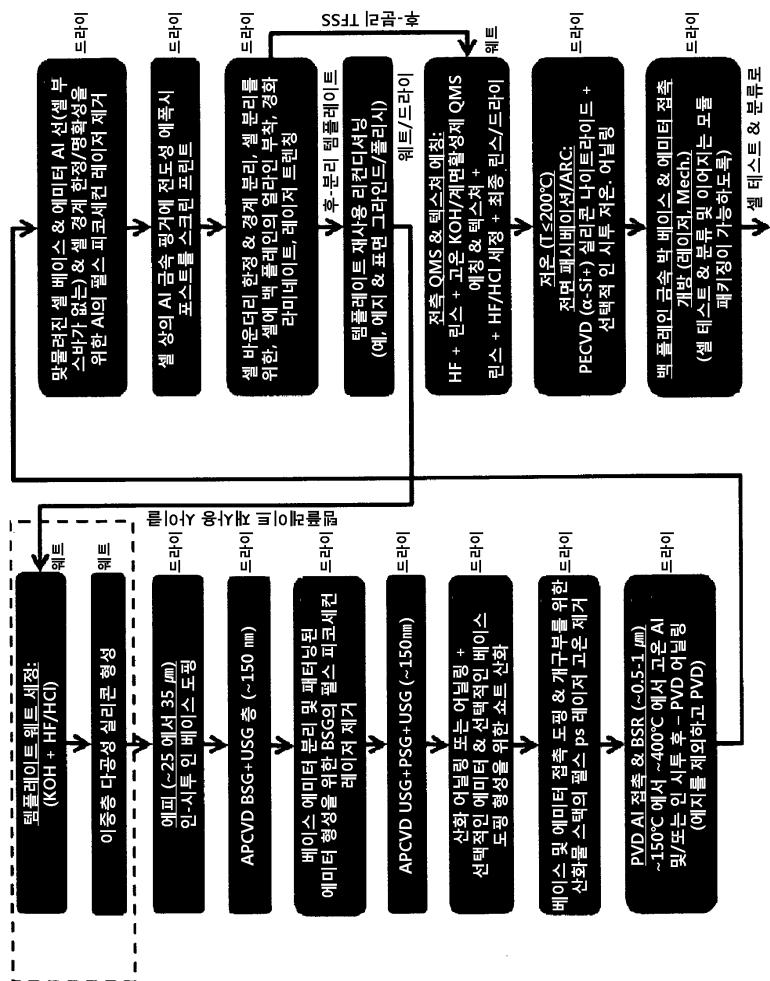

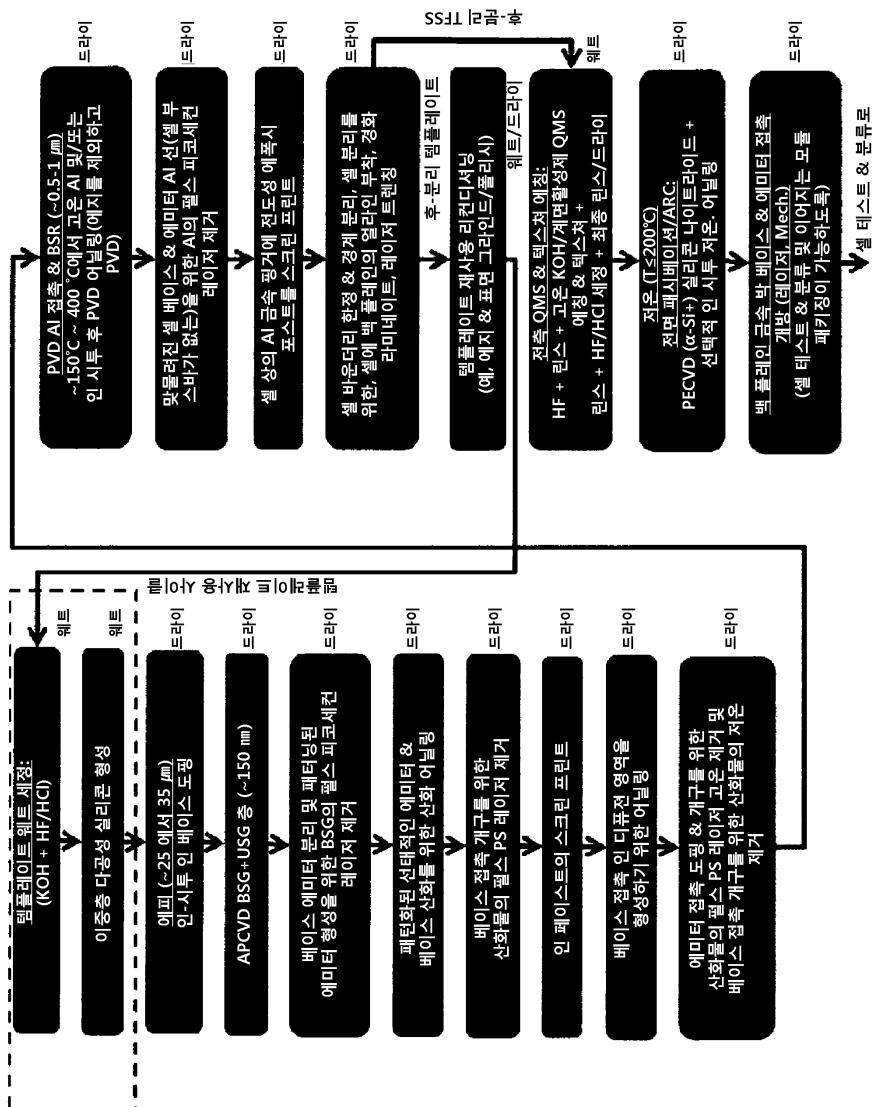

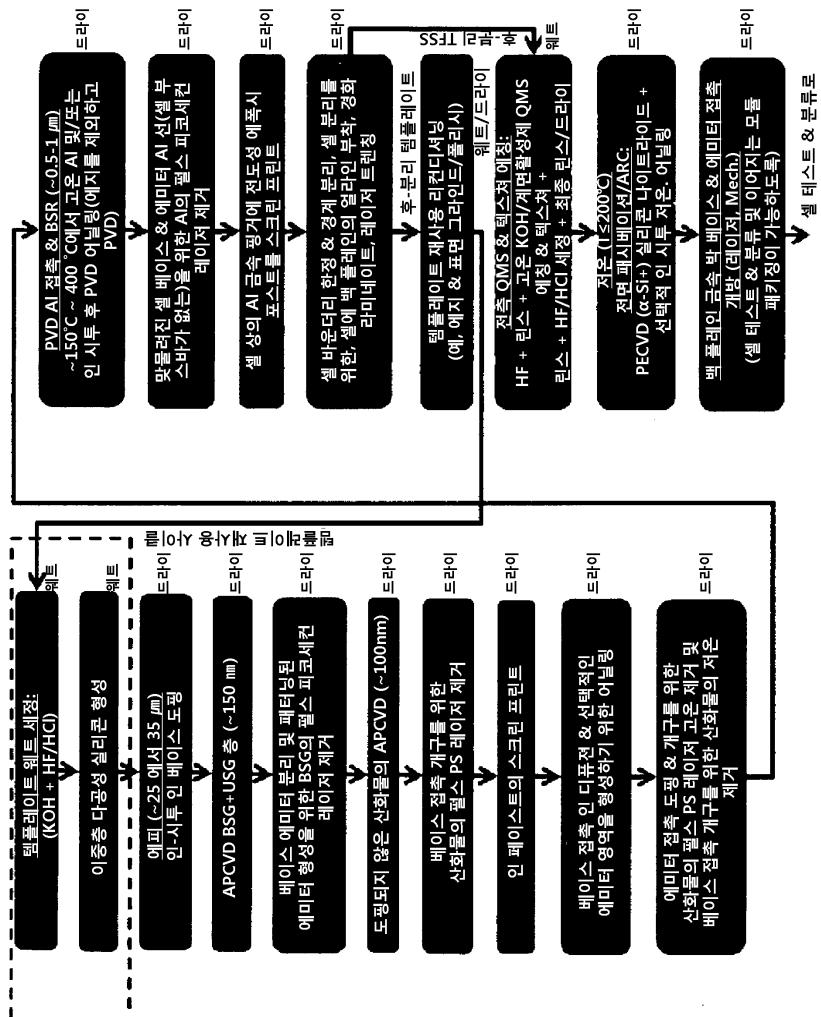

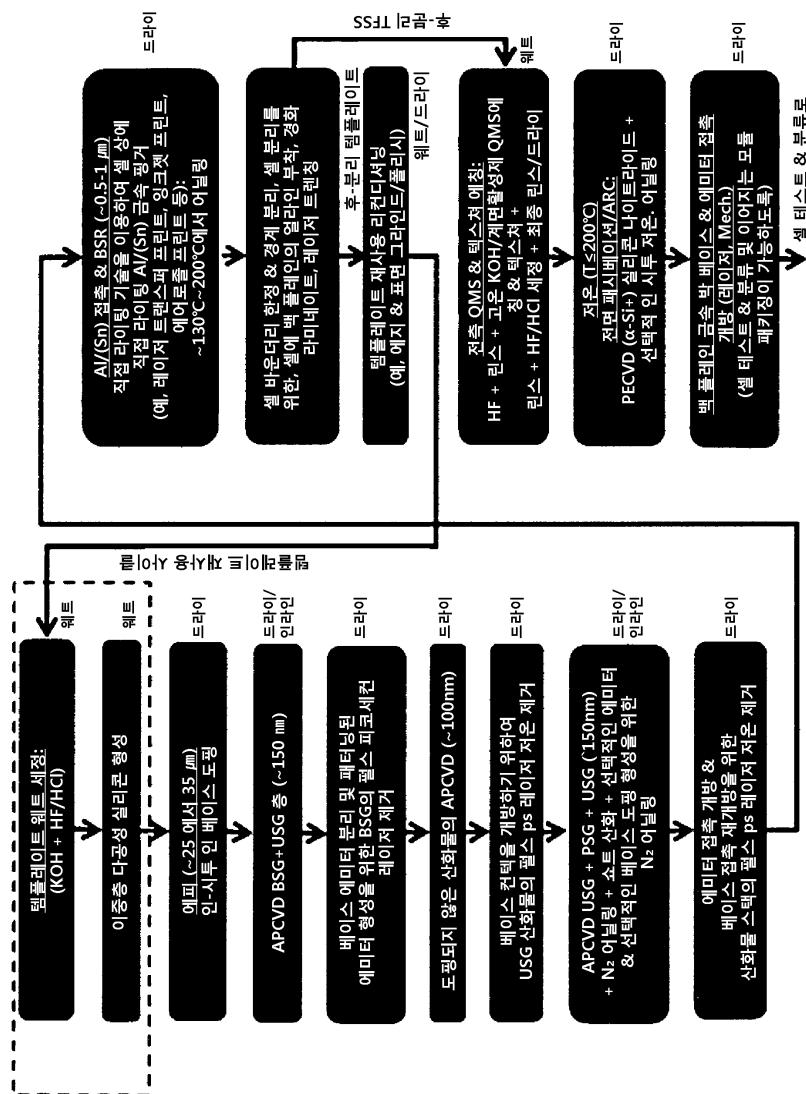

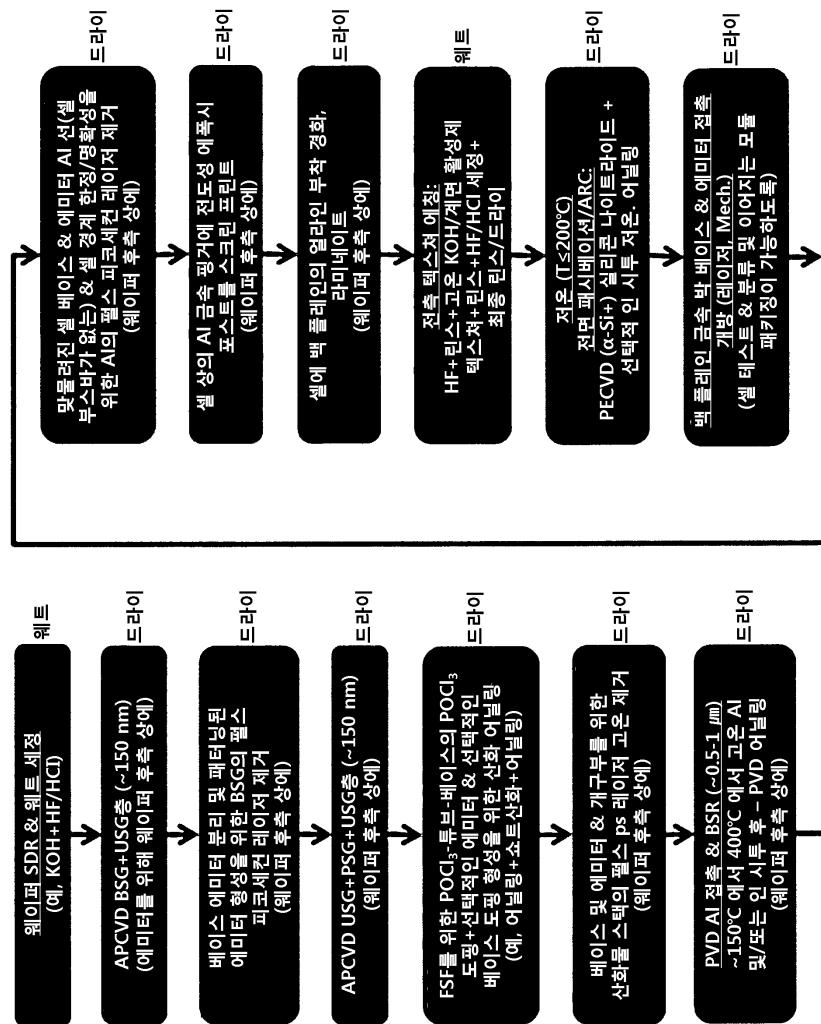

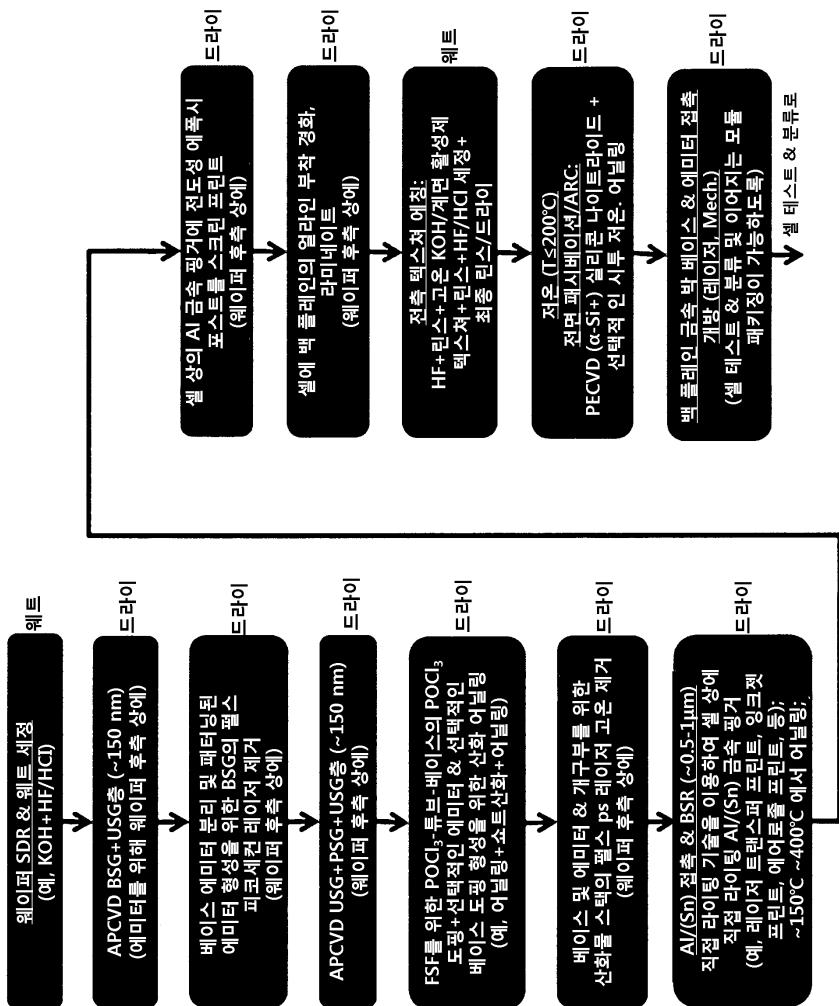

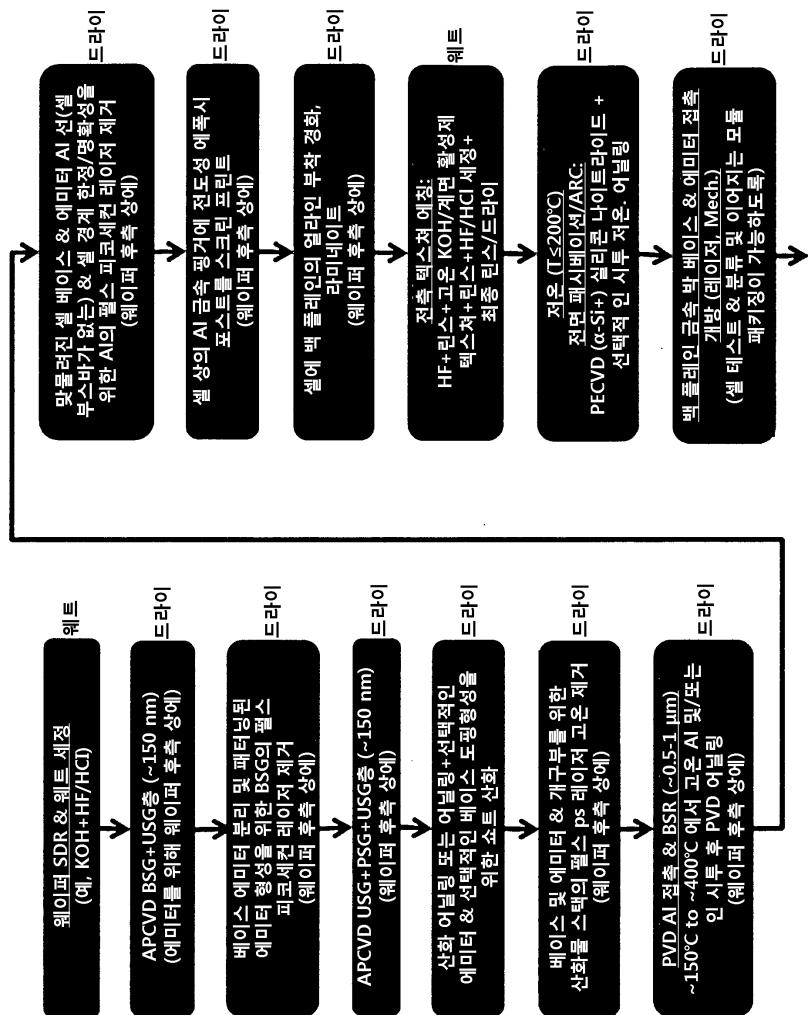

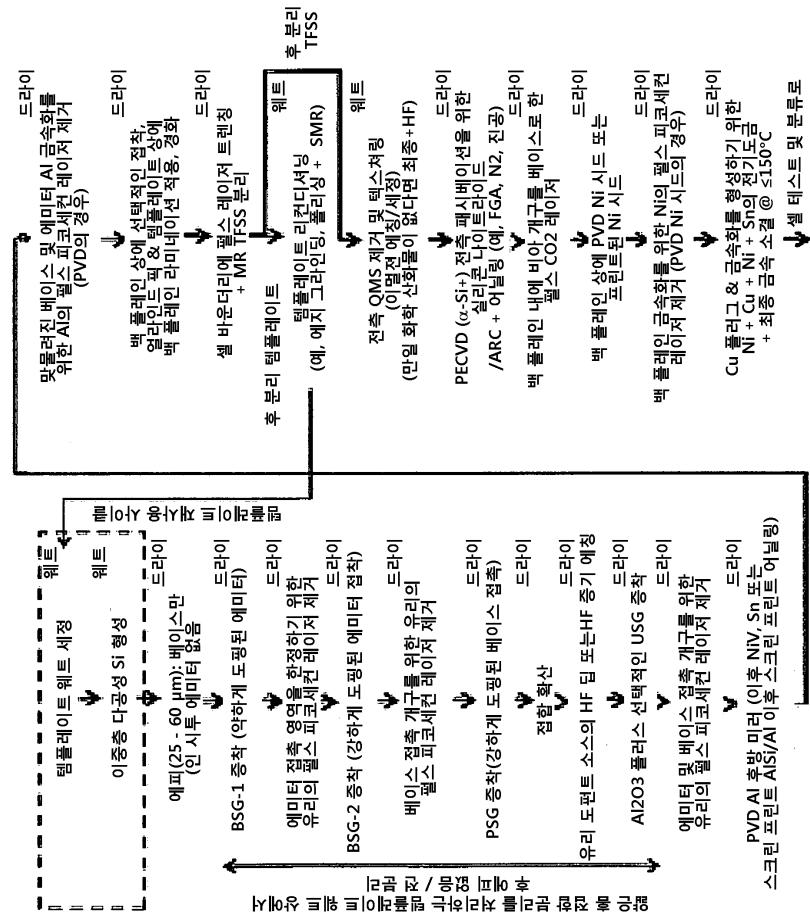

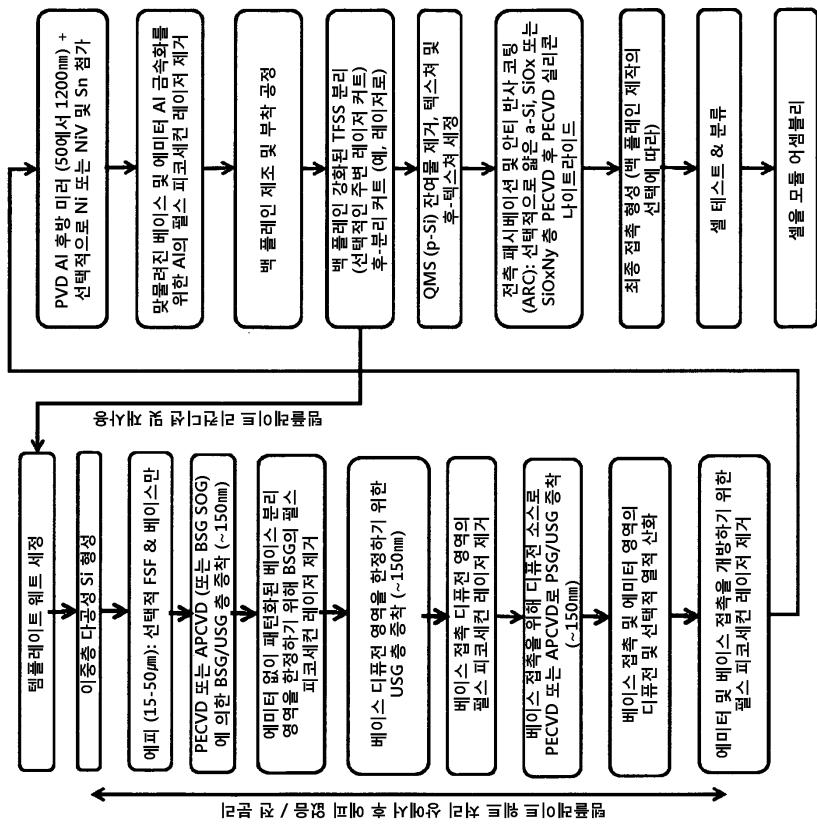

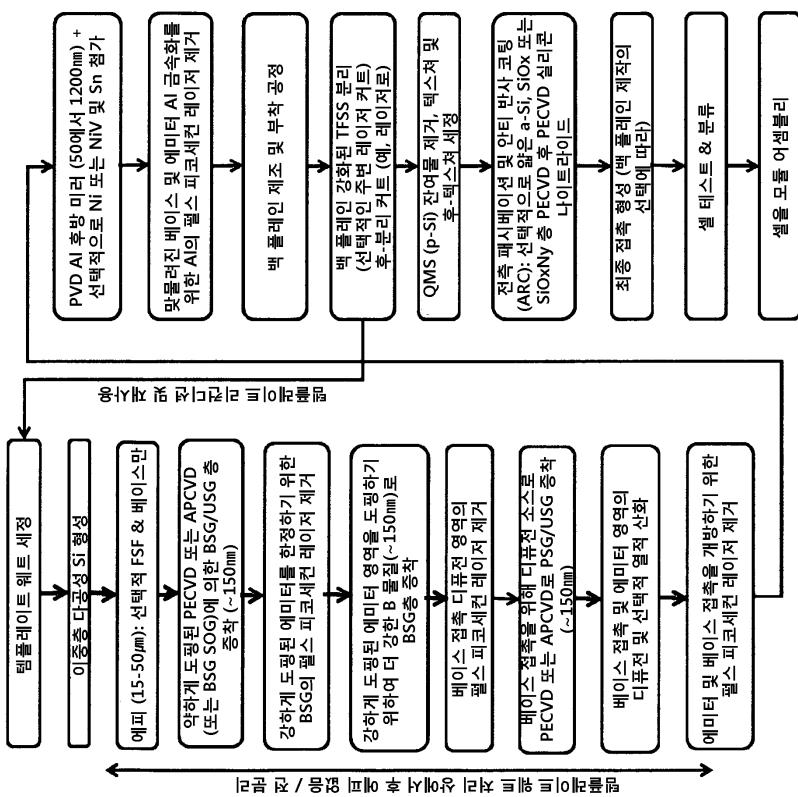

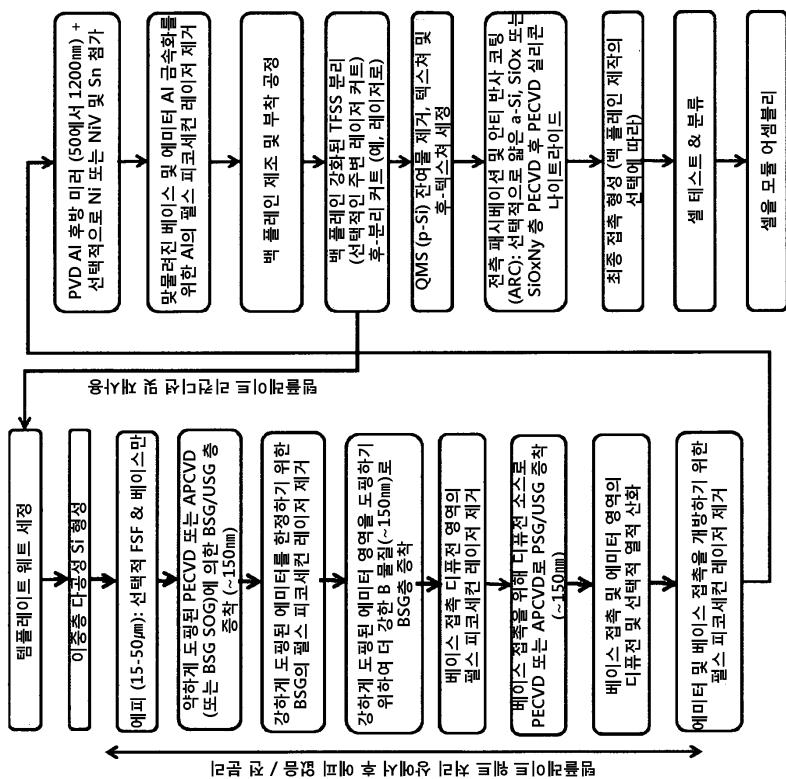

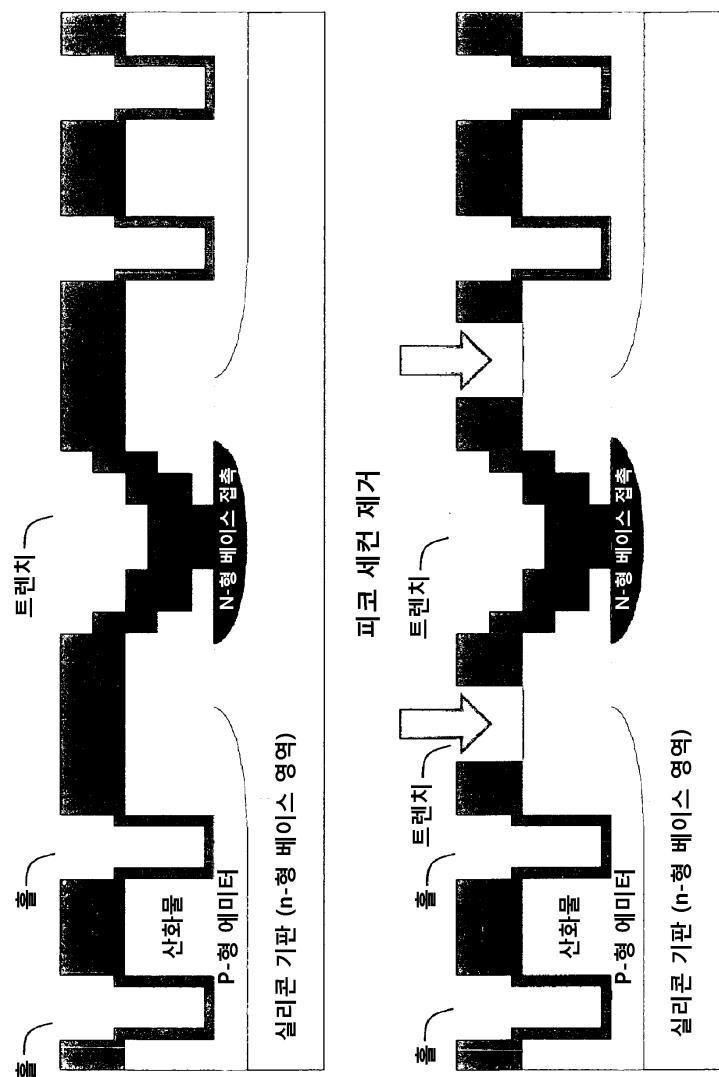

도 3은 엑스시투(ex-situ) 에미터 공정 흐름의 실시예를 설명하는 도이다;

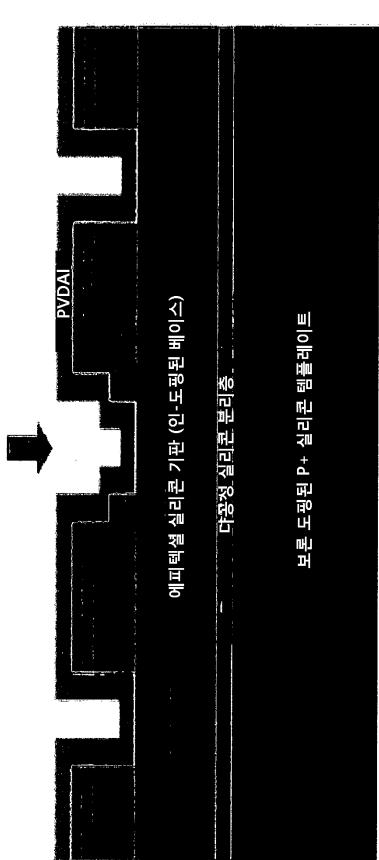

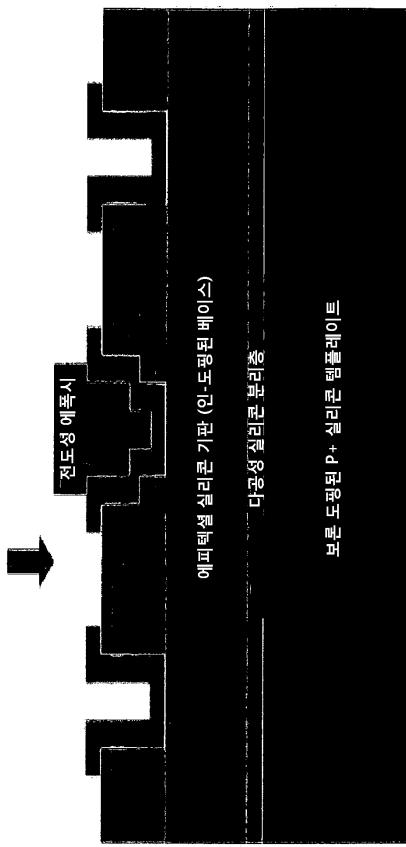

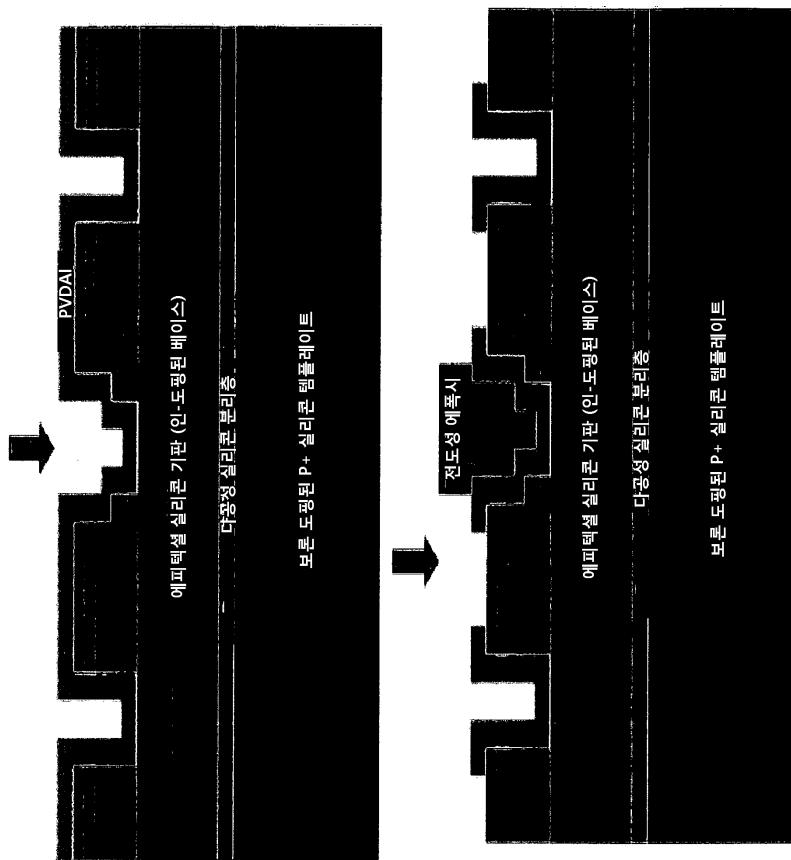

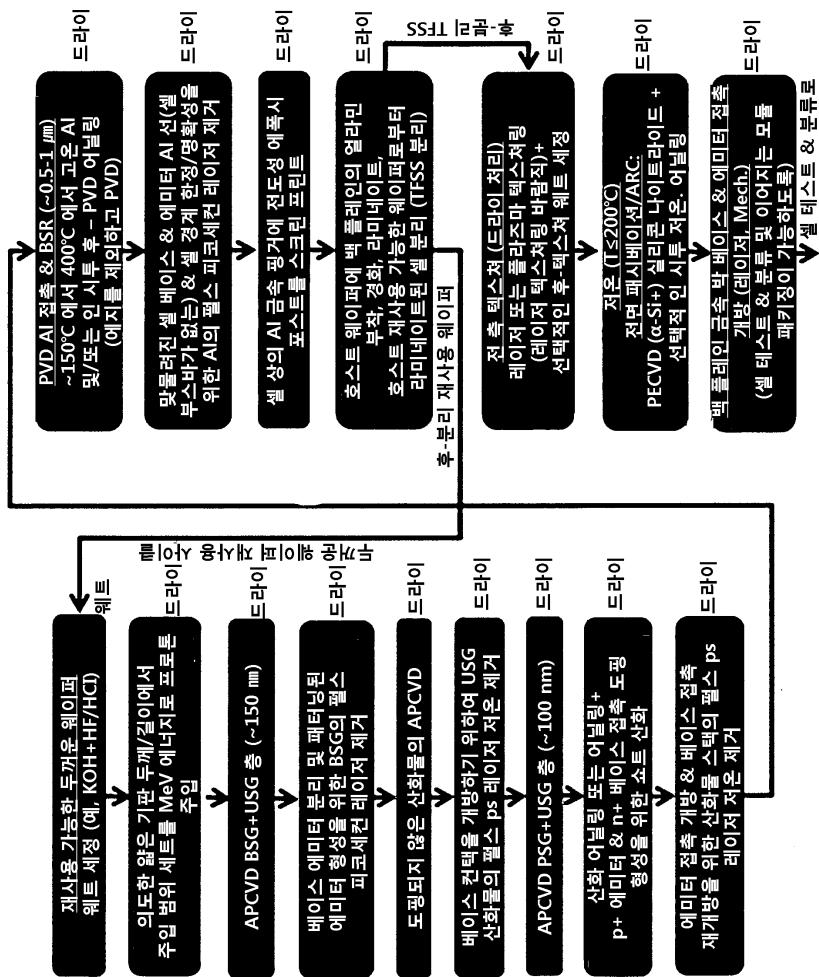

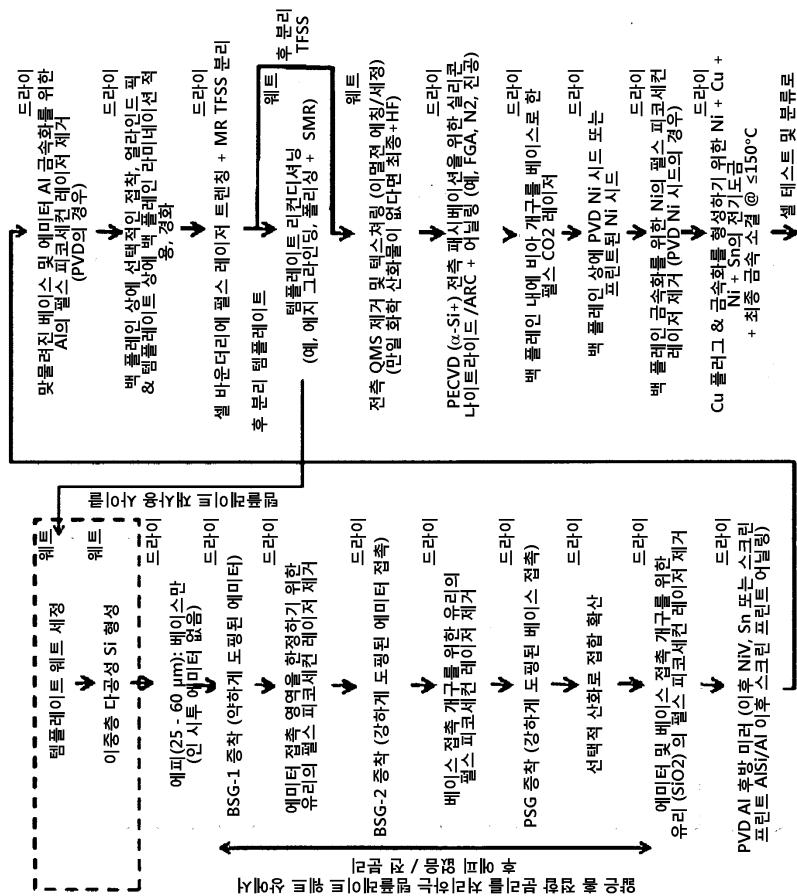

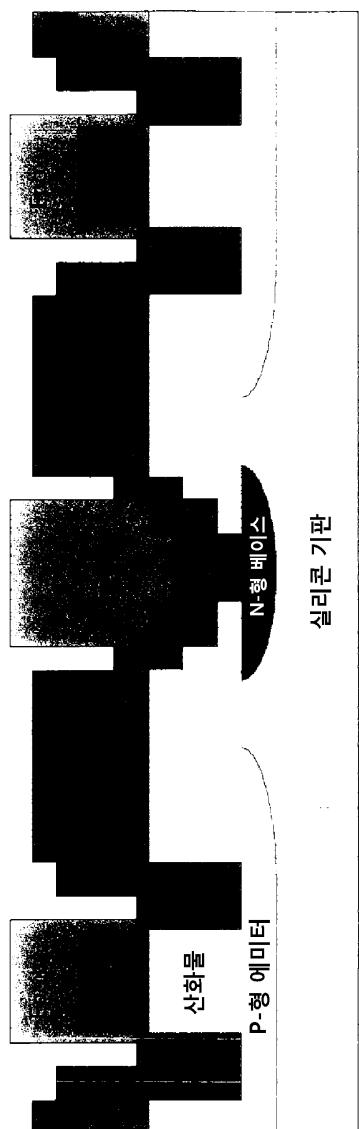

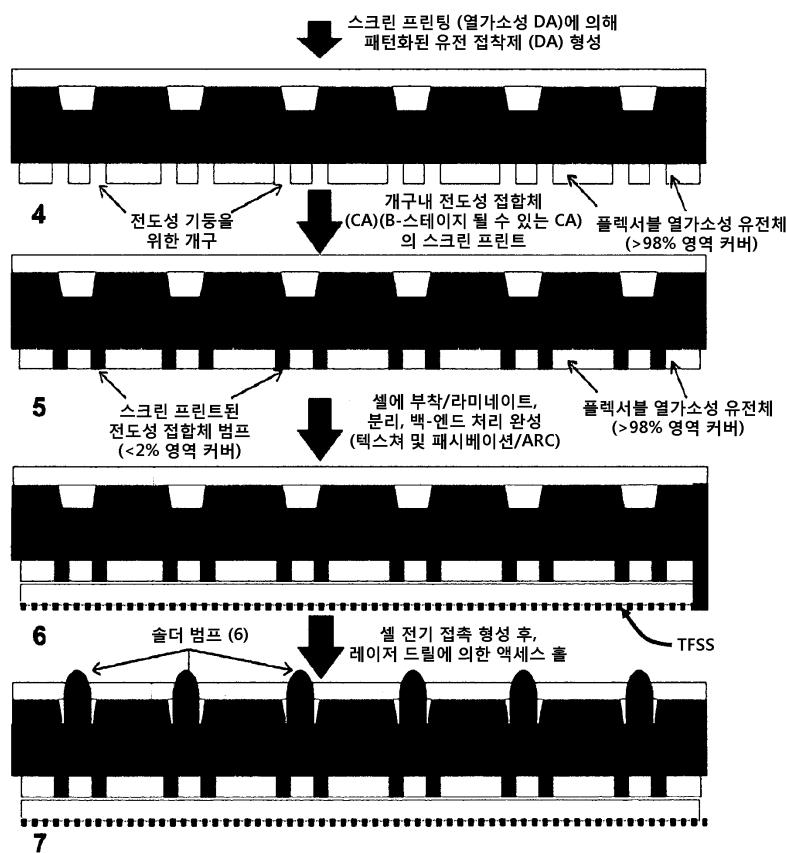

도 4 내지 8은 에피택셜 기판을 이용하는 후면 접촉 태양 전지의 제조 공정 흐름이다;

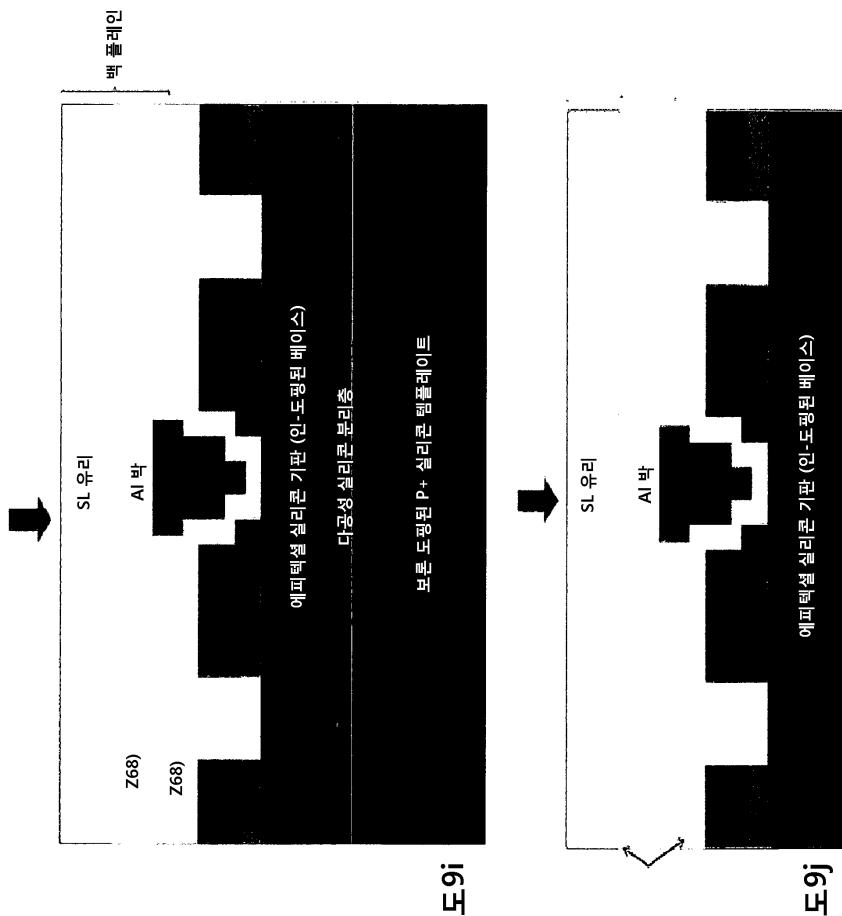

도 9A 내지 L은 후면 접촉 태양 전지의 가공 단계 후 단면도이다;

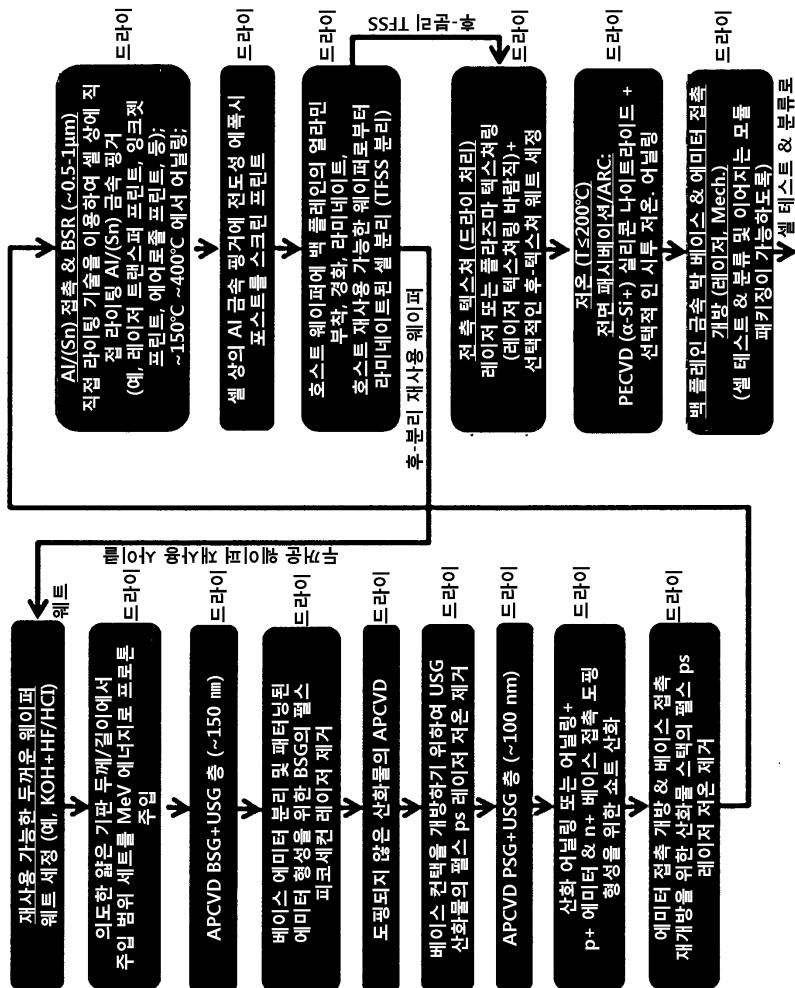

도 10 내지 21은 에피택셜 기판을 이용하는 후면 접촉 태양 전지의 제조 공정 흐름이다;

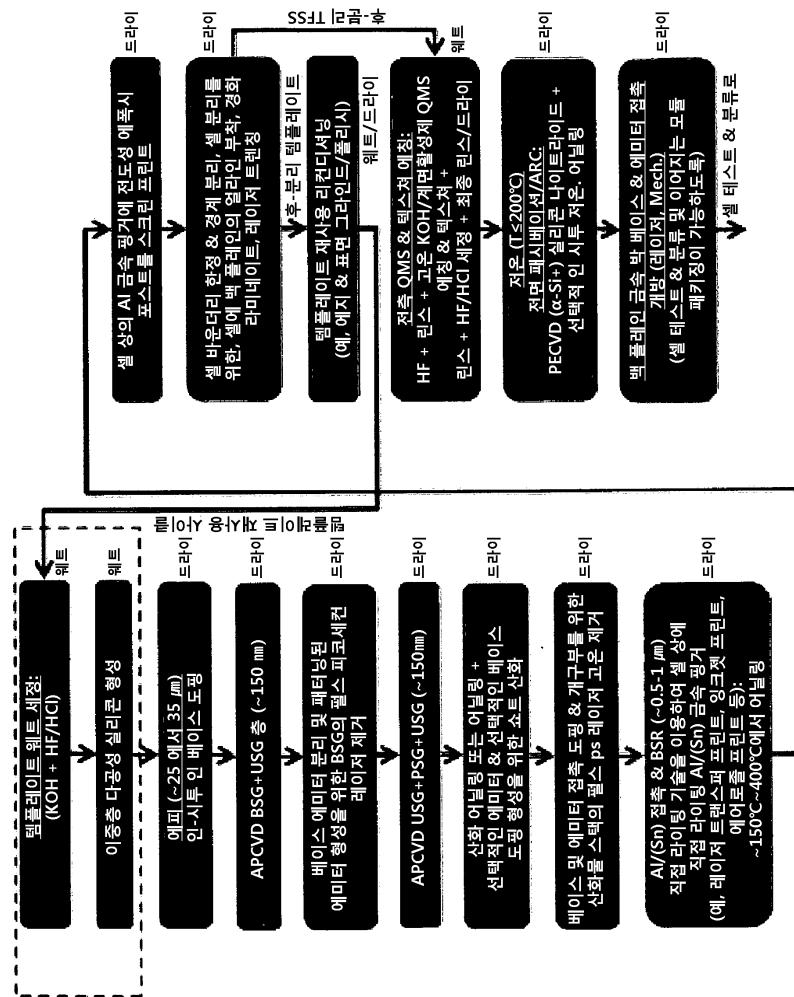

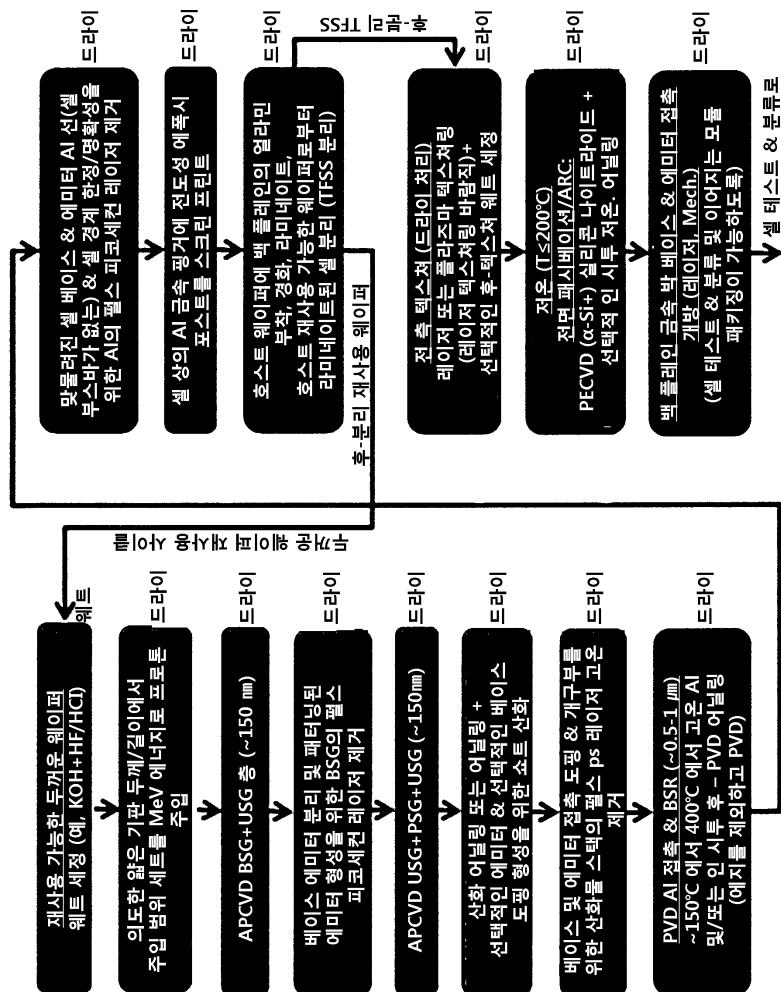

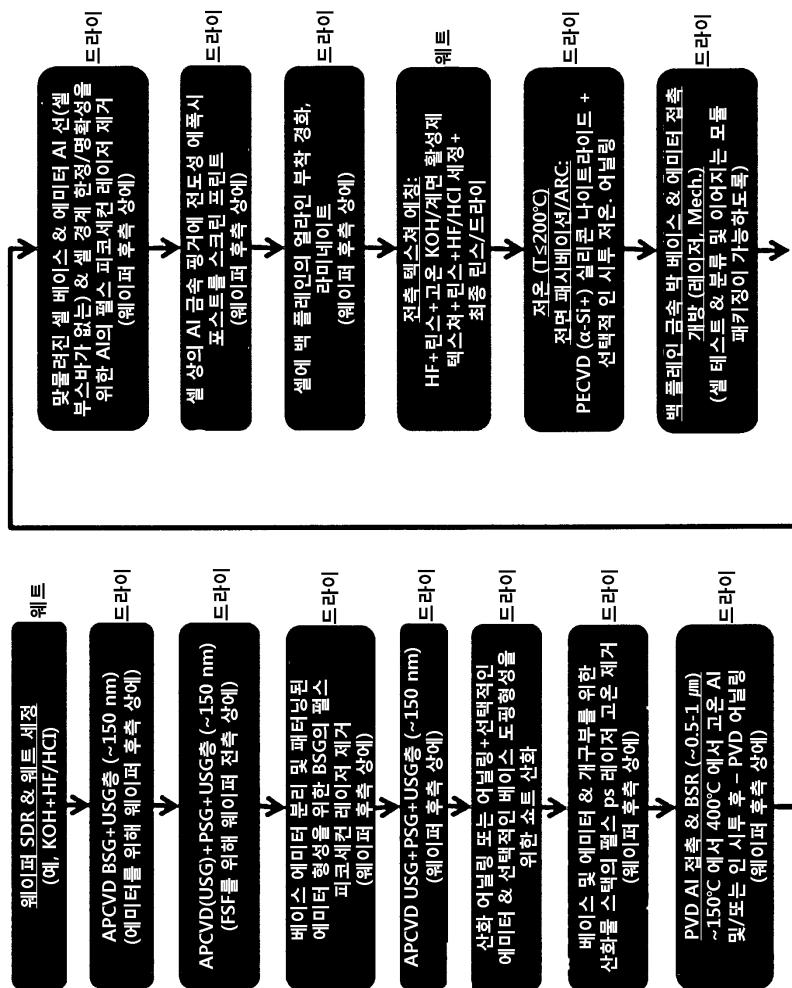

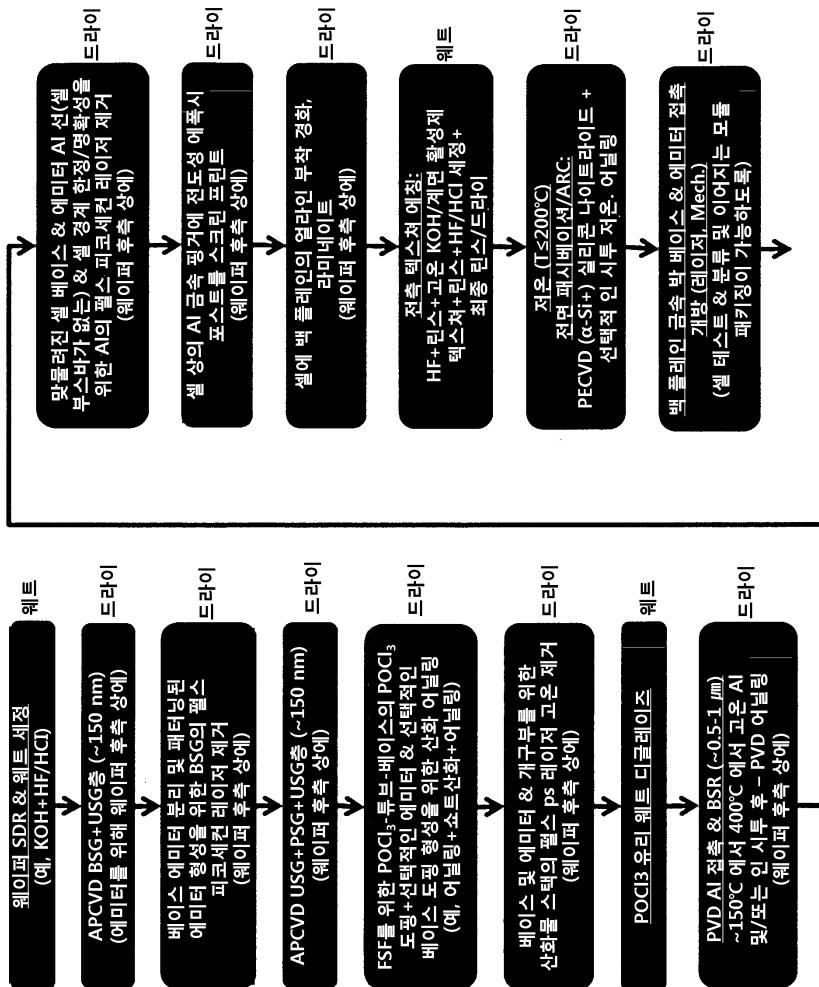

도 22 내지 35는 분열된 기판을 이용하는 후면 접촉 태양 전지의 제조 공정 흐름이다;

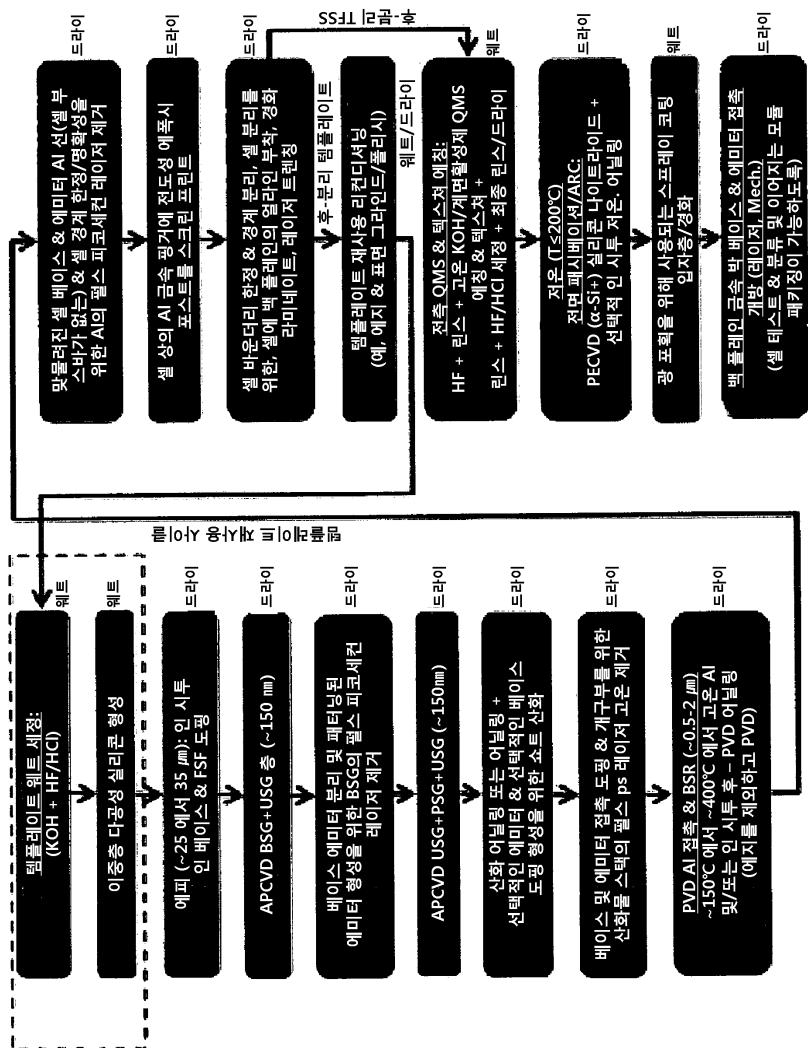

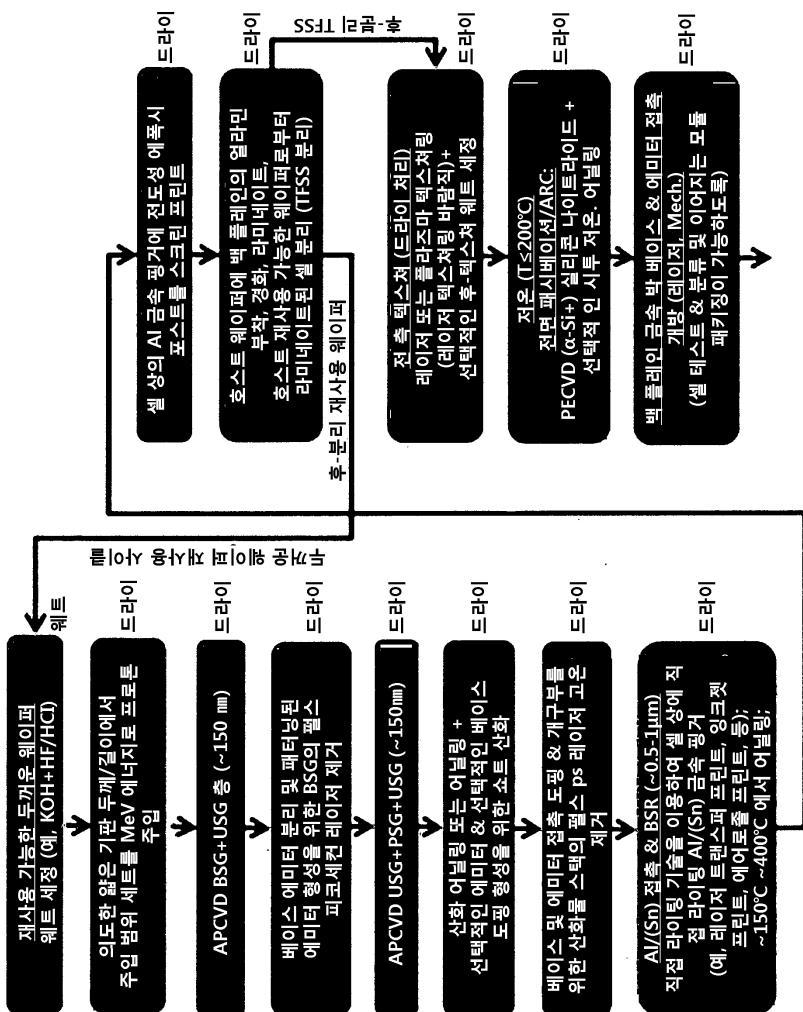

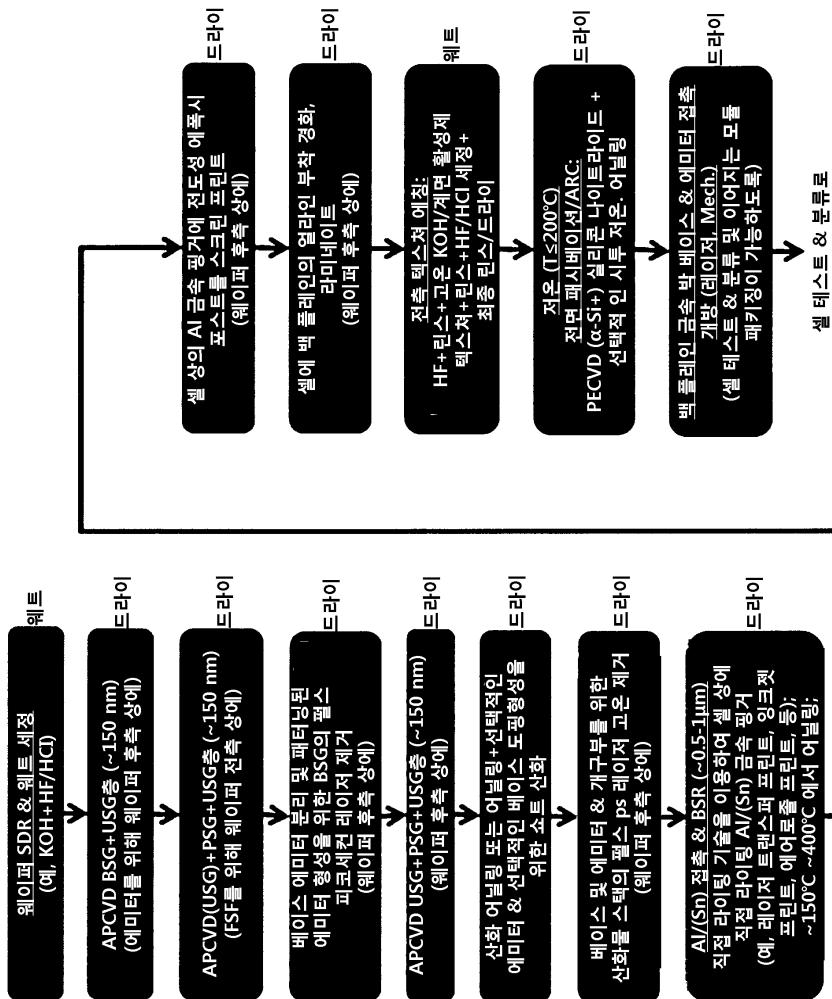

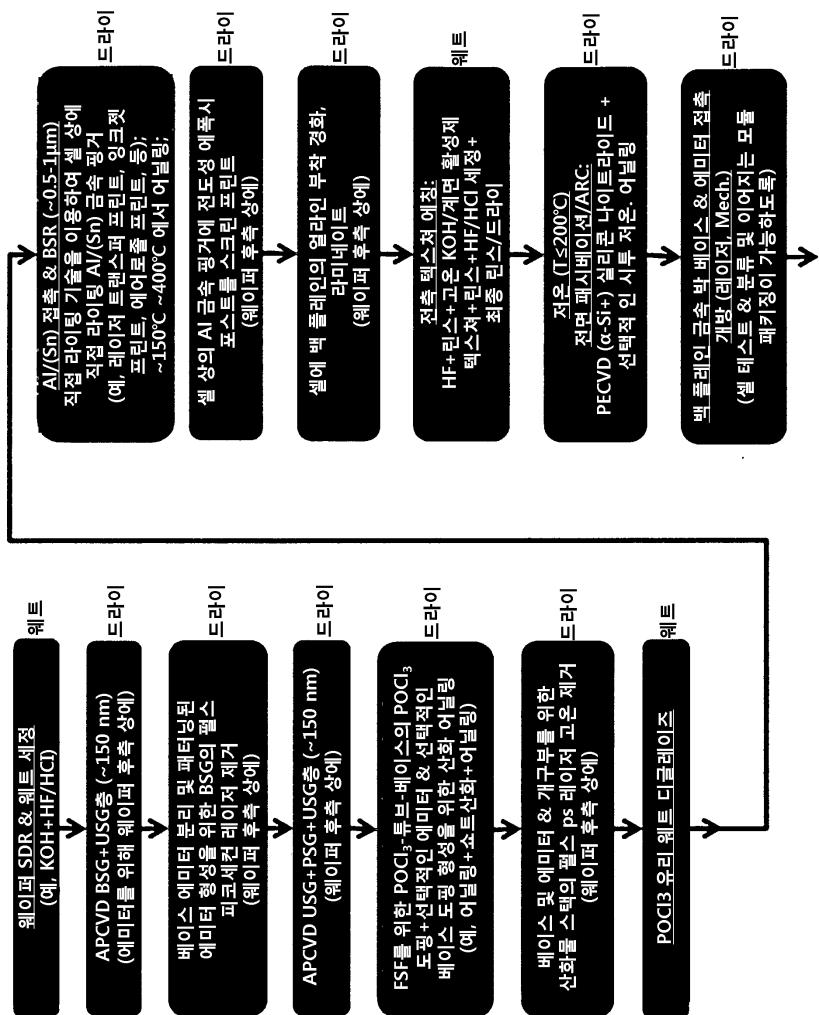

도 36 내지 45는 벌크 웨이퍼를 이용하는 후면 접촉 태양 전지의 제조 공정 흐름이다;

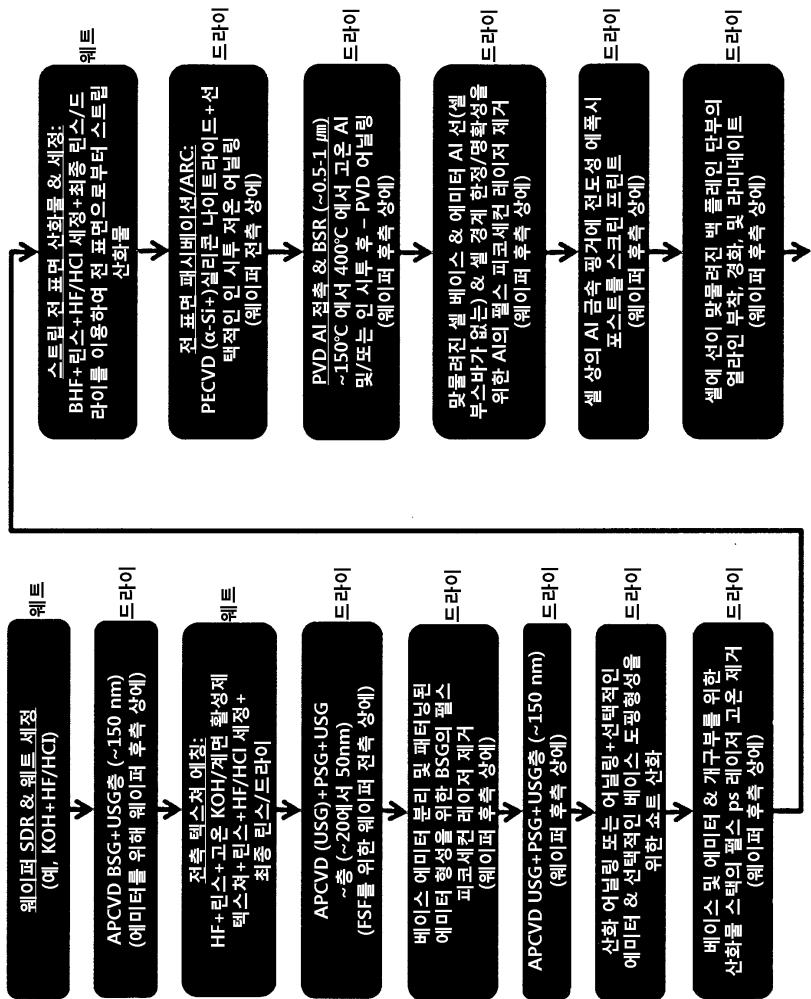

도 46은 선택적 에미터에 대한 후면 접촉 태양 전지의 제조 공정 흐름이다;

도 47은 도 46의 흐름으로부터 얻어지는 전지의 단면도이다;

도 48은 후면 접촉 태양 전지의 제조 공정 흐름이다;

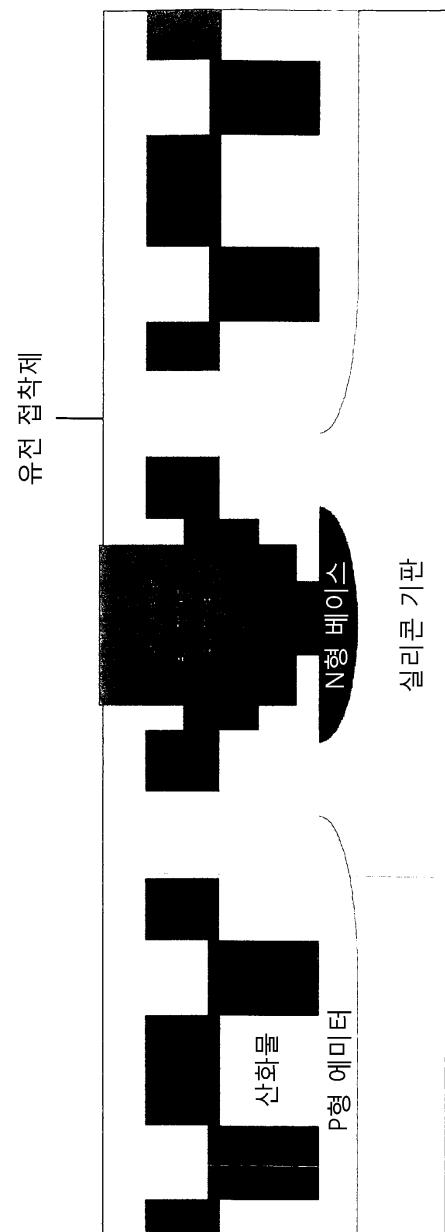

도 49는 도 48의 흐름으로부터 얻어지는 전지의 단면도이다;

도 50은 후면 접촉 태양 전지의 제조 공정 흐름이다;

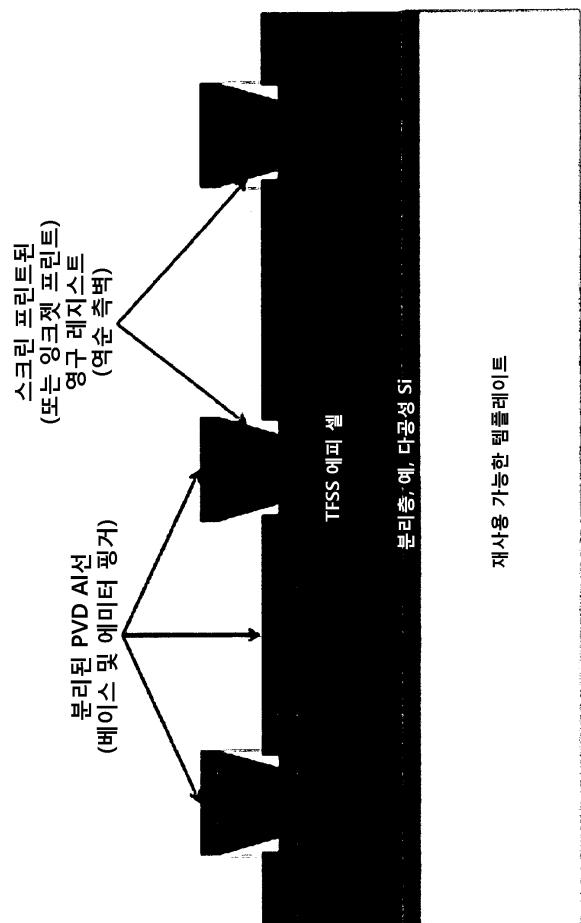

도 51은 역행하는 레지스트 층벽을 갖는 구조체의 단면도이다;

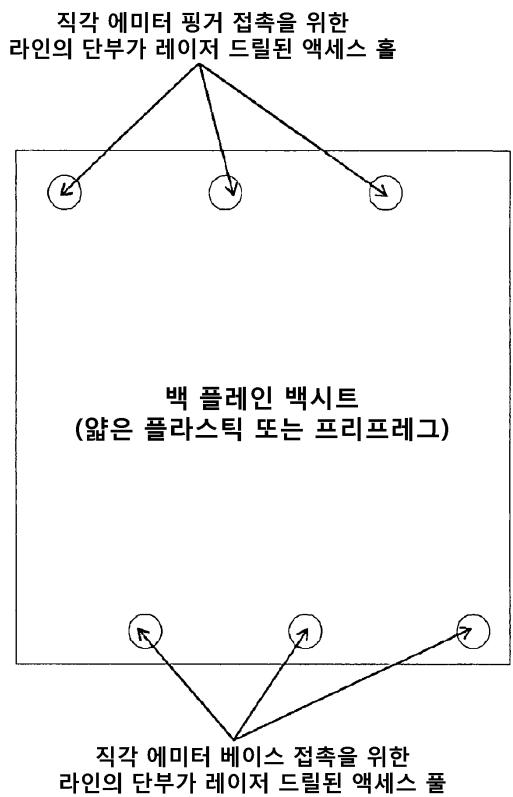

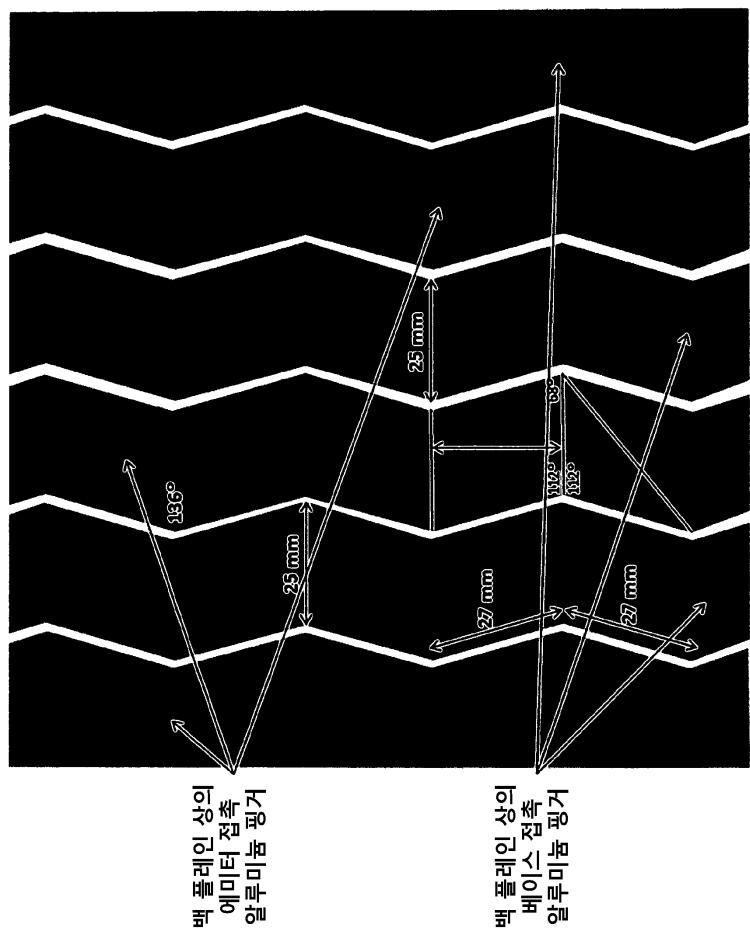

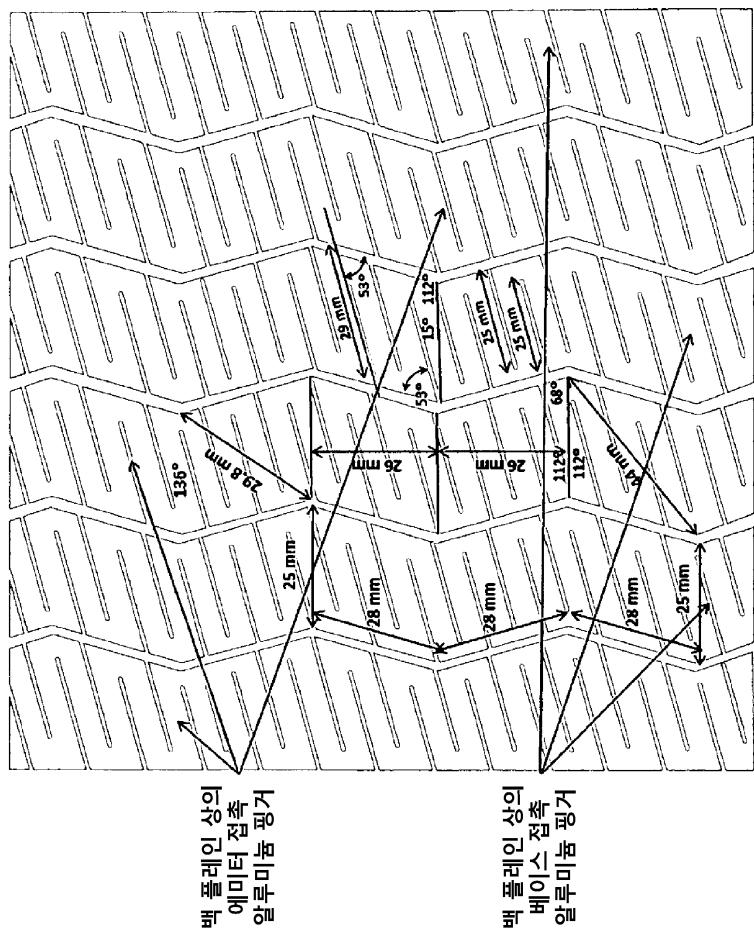

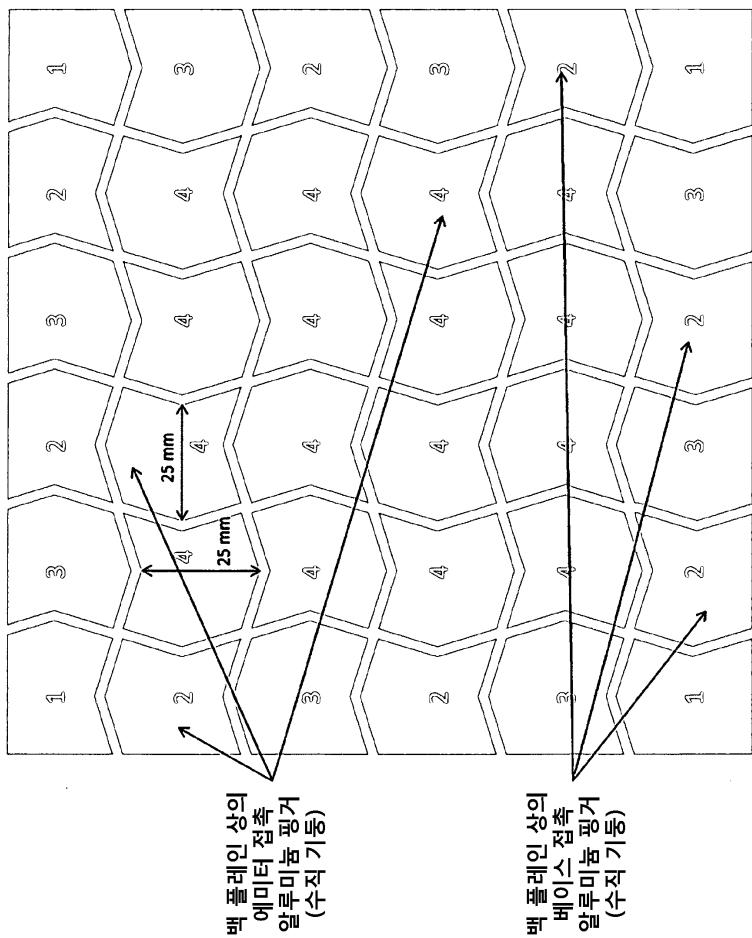

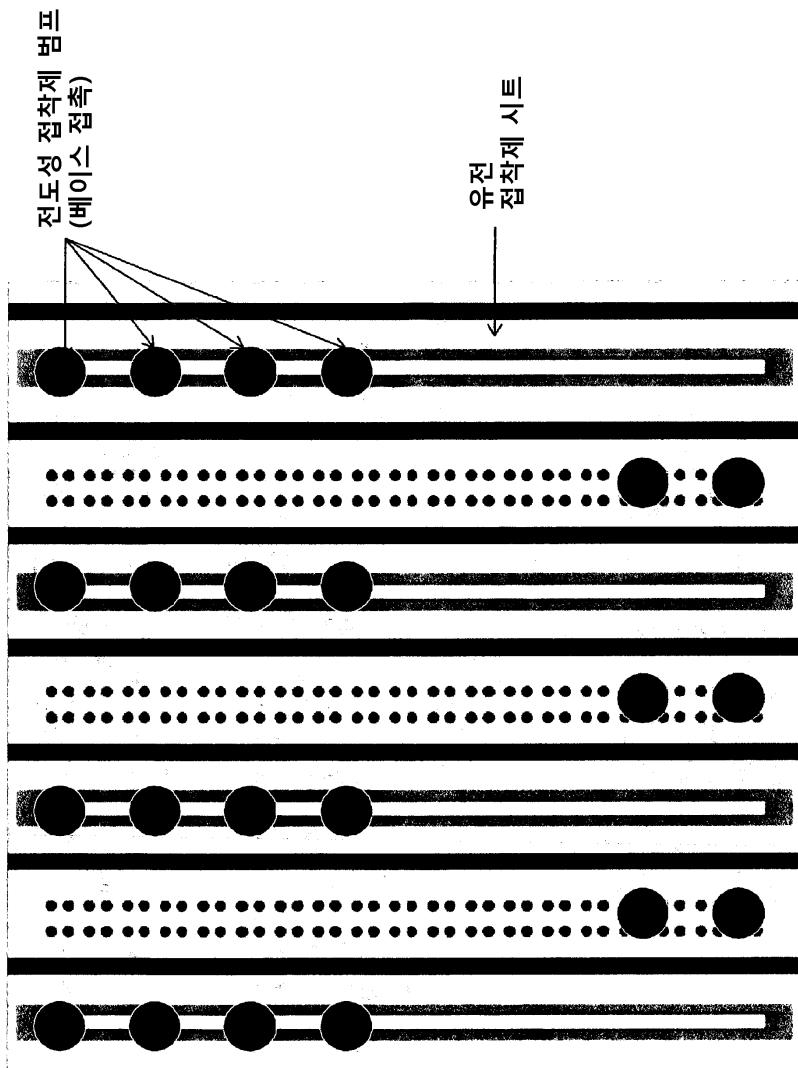

도 52 내지 57은 각종 가공 단계 후, 태양 전지 백플레이인 실시예의 상면도이다;

도 58 및 59는 혼테로 접합 전지에 대한 후면 접촉 태양 전지의 제조 공정 흐름이다;

도 60은 혼테로 접합 구조체를 갖는 태양 전지의 단면도이다;

도 61A 내지 C는 에피택셜 기판을 이용하는 후면 접촉 태양 전지의 제조 공정 흐름이다;

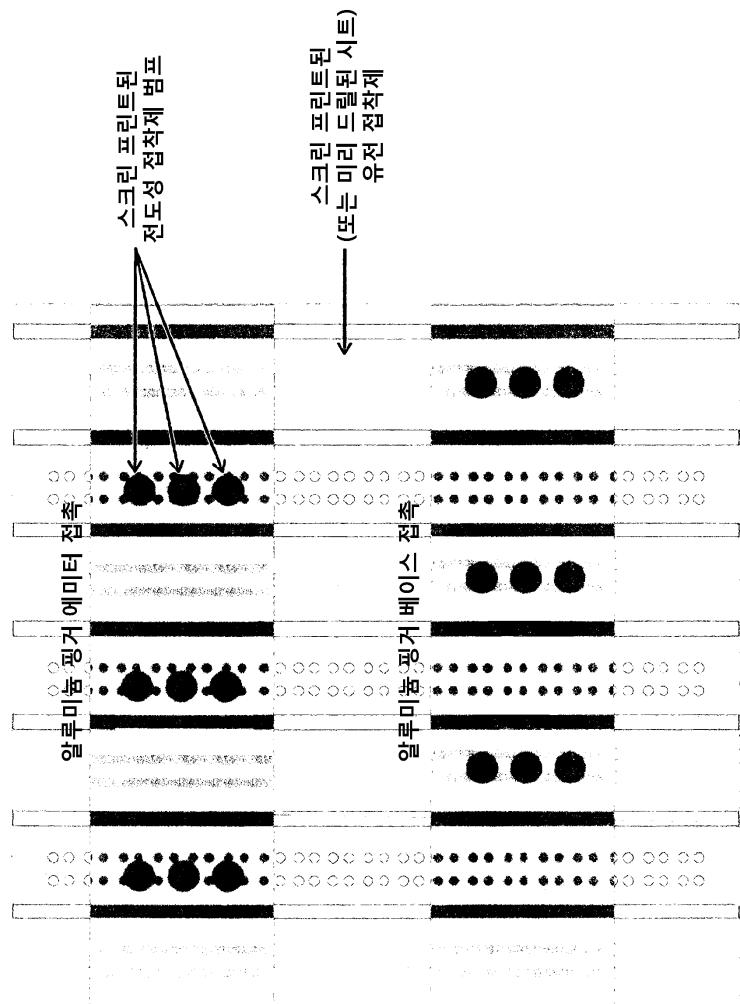

도 62A 내지 G는 백플레이인 가공 단계 후 후면 접촉 태양 전지의 상면도 및 단면도이다;

도 63A 내지 D는 소정의 가공 단계 후 플루토(pluto) 구조체의 단면도이다;

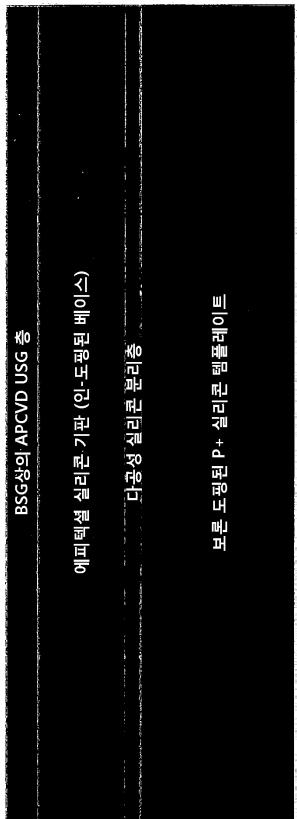

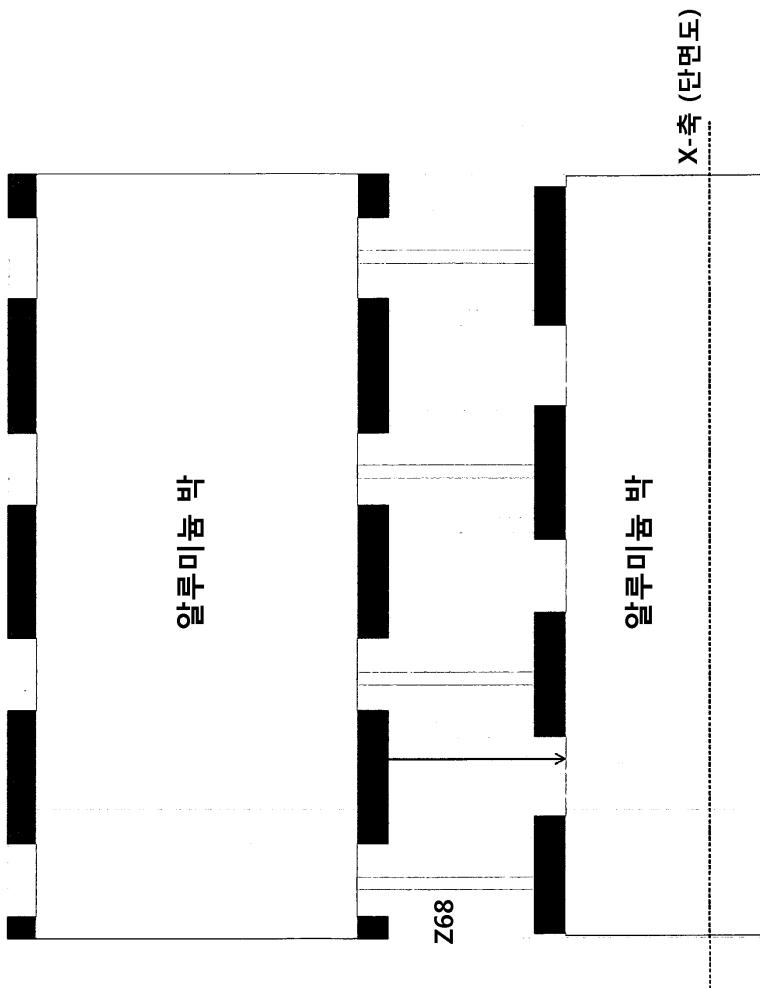

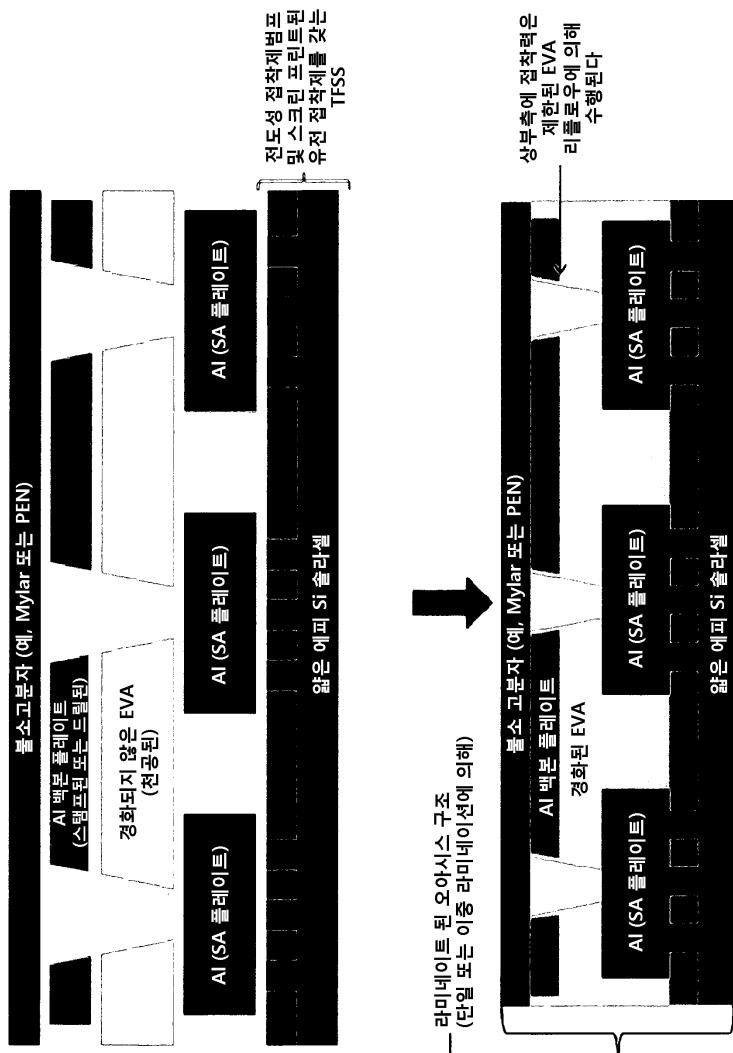

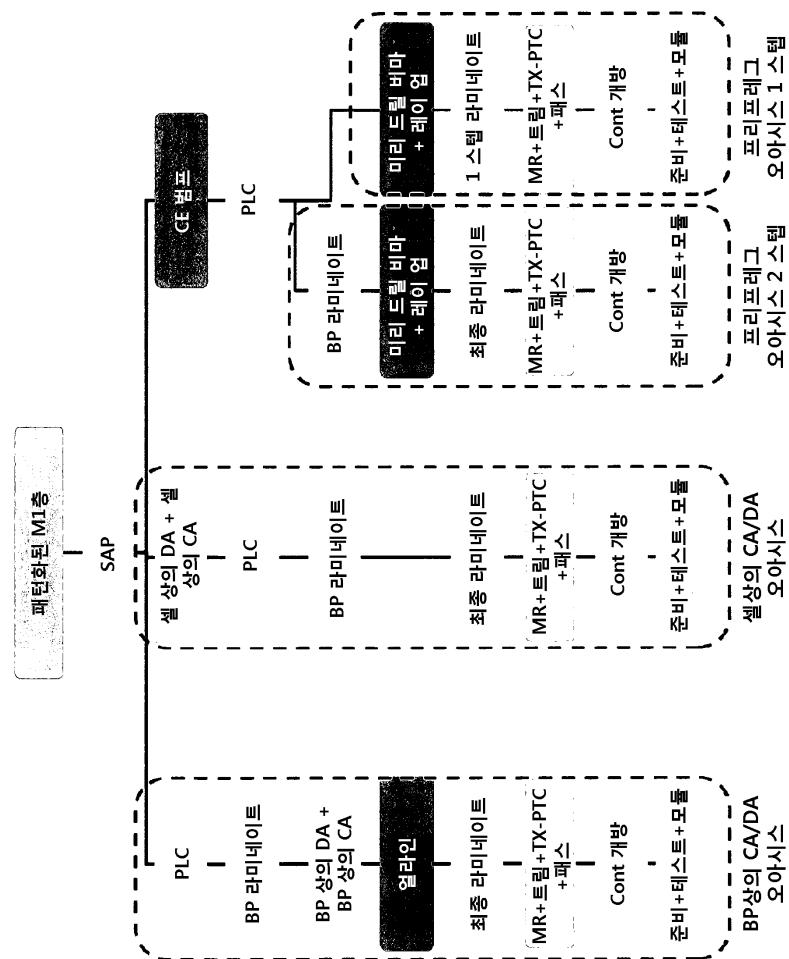

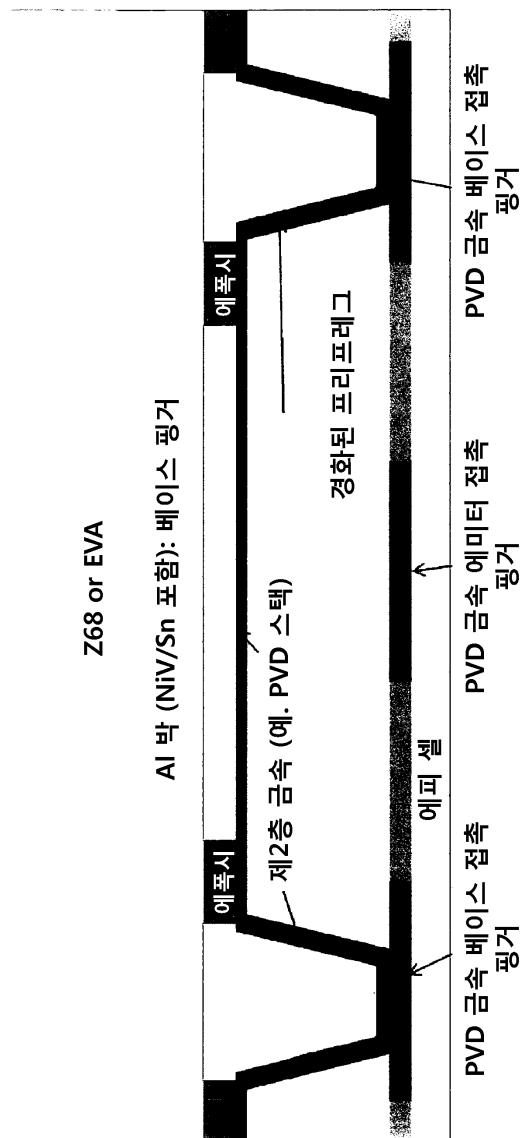

도 64A 내지 F는 4층 백플레이인 오아시스(oasis) 구조체의 각종 실시예, 단면도 및 상면도 및 공정 흐름을 나타낸다;

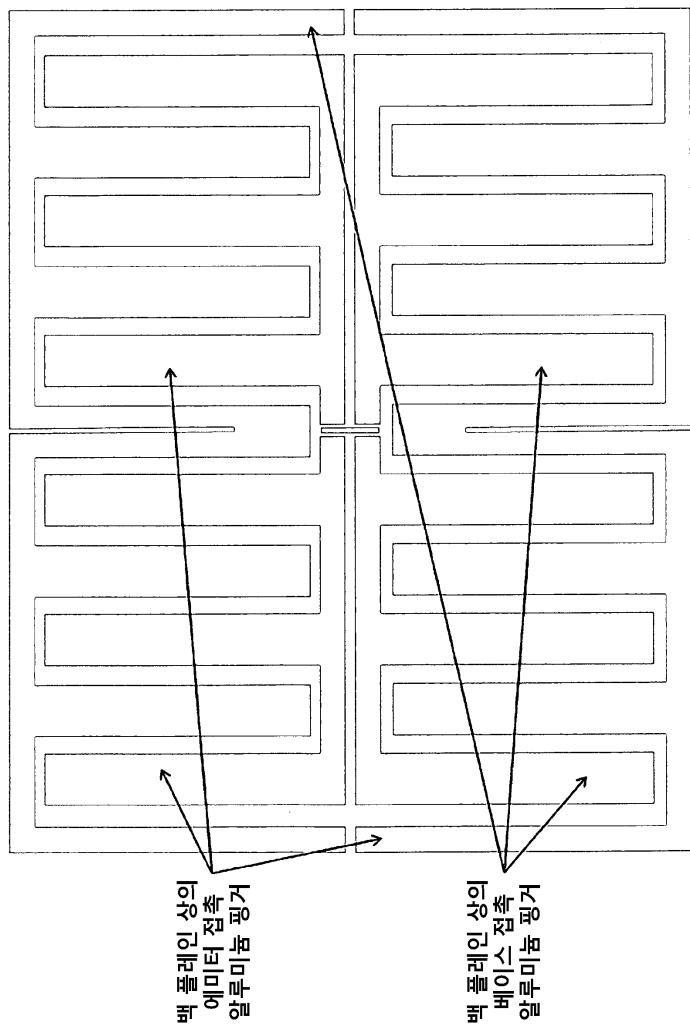

도 65A 내지 D는 각종 전지 백플레이인 금속 평거 디자인의 상면도이다;

도 66은 백플레이인 실시예의 상면도이다;

도 67은 오아시스 구조체의 단면도를 나타낸다;

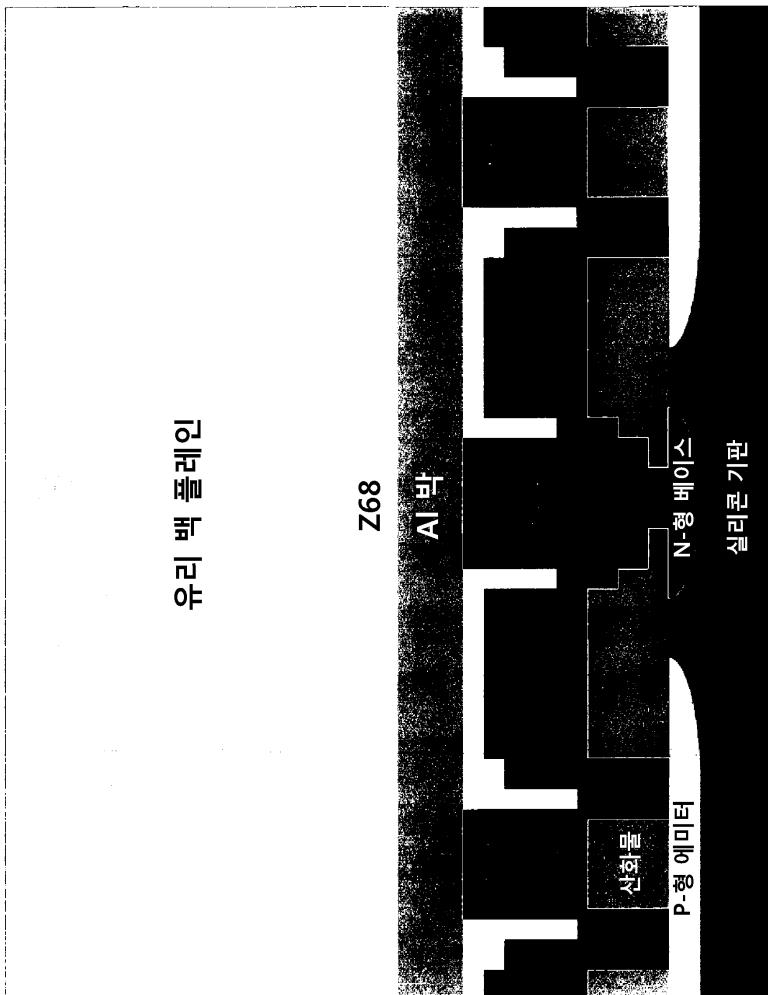

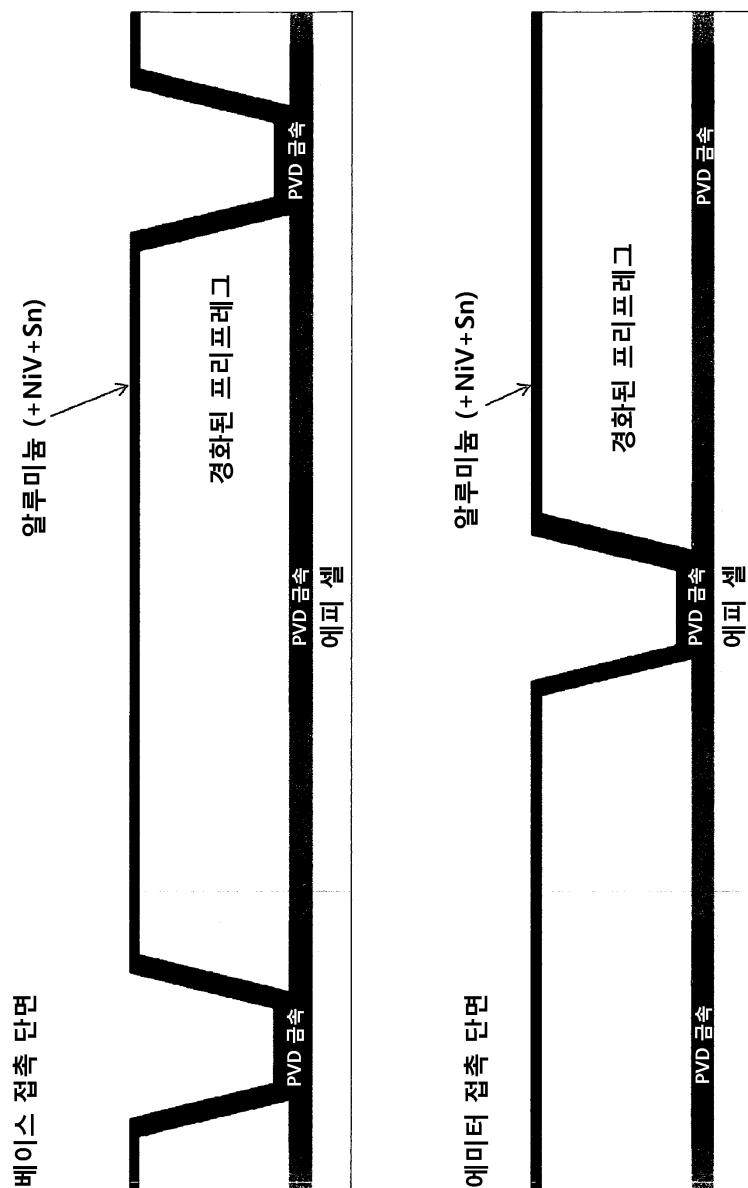

도 68A 내지 C는 하이브리드 구조체의 단면도이다;

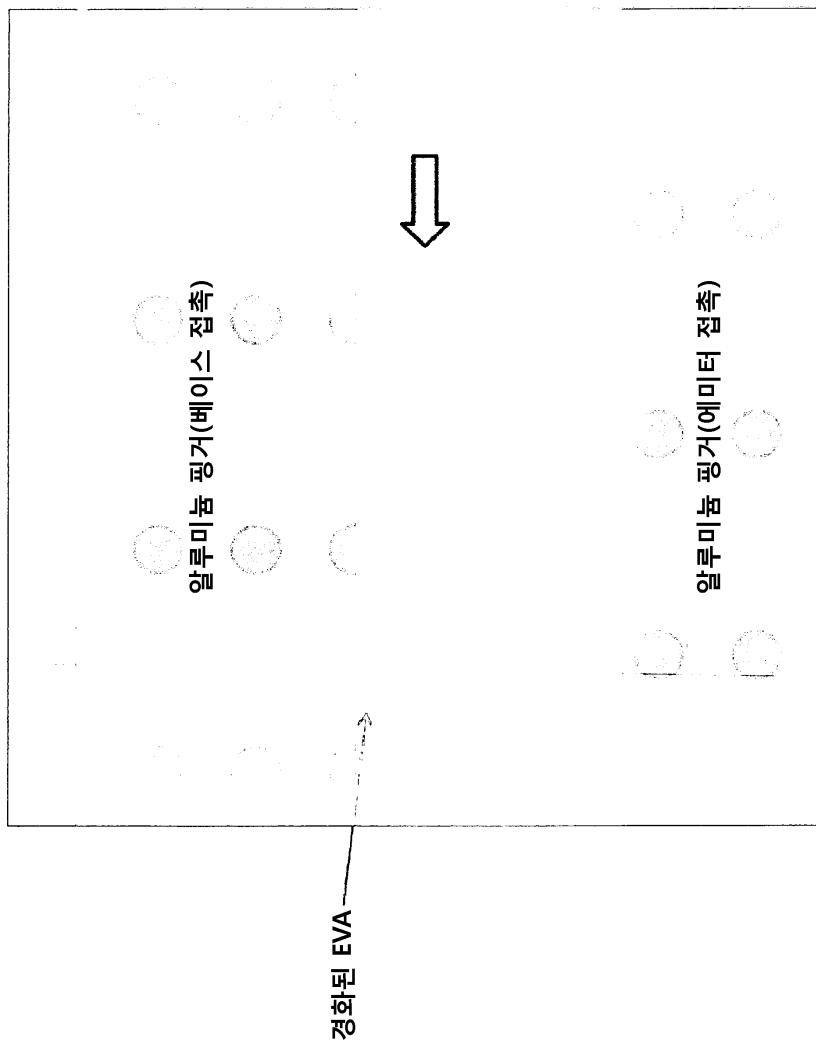

도 69 및 70은 침지 접촉 결합 구조체(immersion contact bonding structure) 실시예의 단면도를 나타낸다;

도 71은 후면 접촉 태양 전지의 제조 공정 흐름이다;

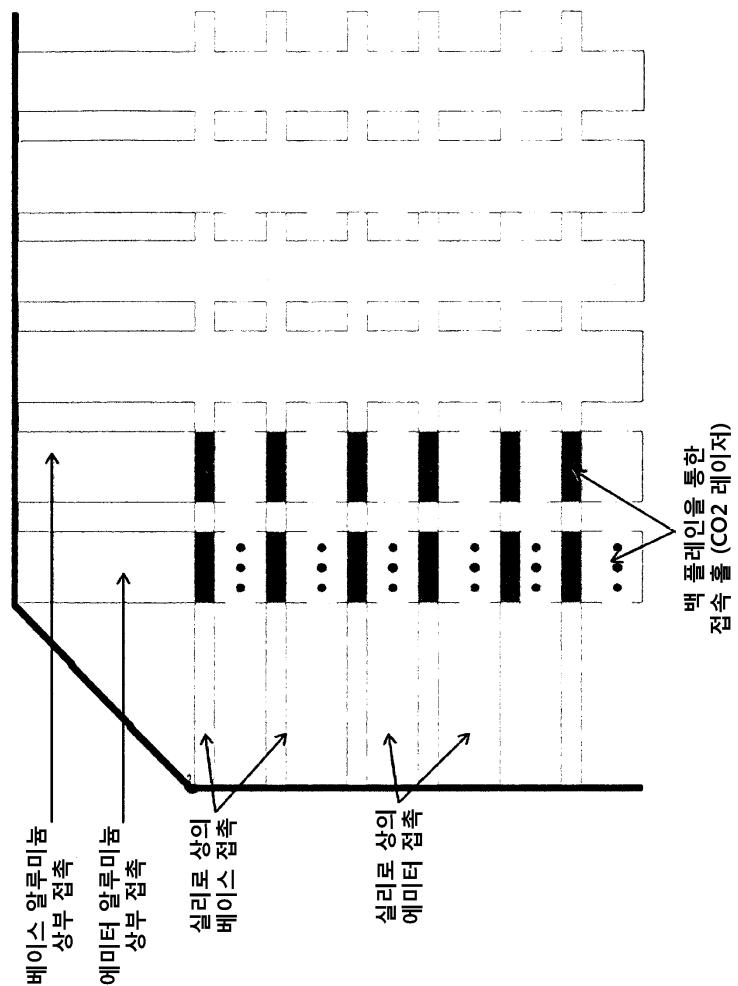

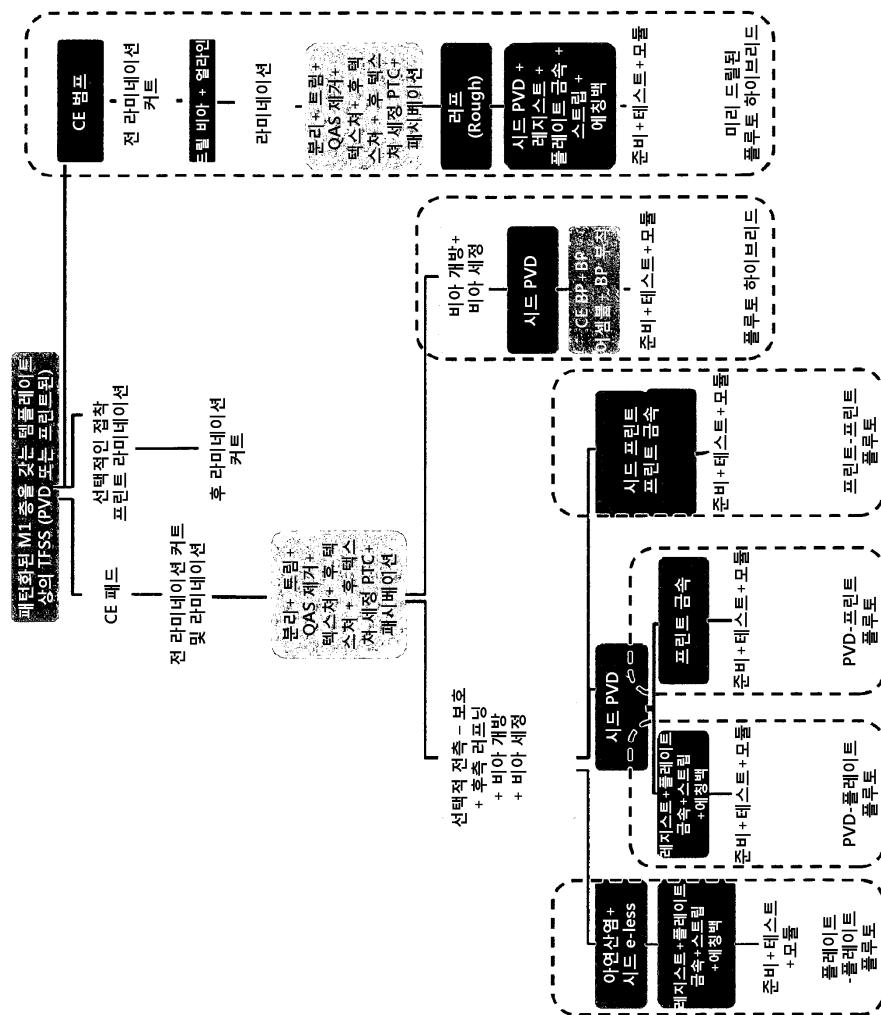

도 72A는 플루토 백플레인 구조체를 제조하기 위한 공정 흐름을 나타낸다;

도 72B는 오아시스 백플레인 구조체를 제조하기 위한 공정 흐름을 나타낸다;

도 73A 내지 J는 후면 접촉 태양 전지 공정 흐름의 플루토 실시예의 제조 단계 동안 전지의 단면도를 나타낸다;

도 74A 내지 D는 후면 접촉 태양 전지 공정 흐름의 오아시스 실시예의 제조 단계 동안 전지의 상면도(도 74A) 및 단면도를 나타낸다;

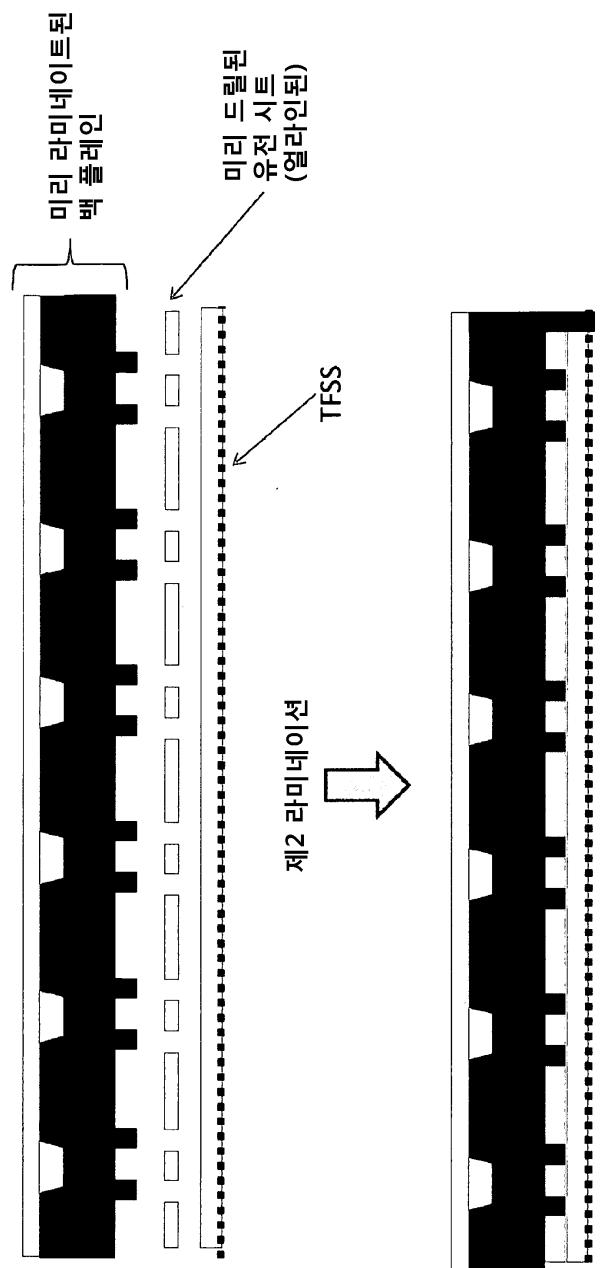

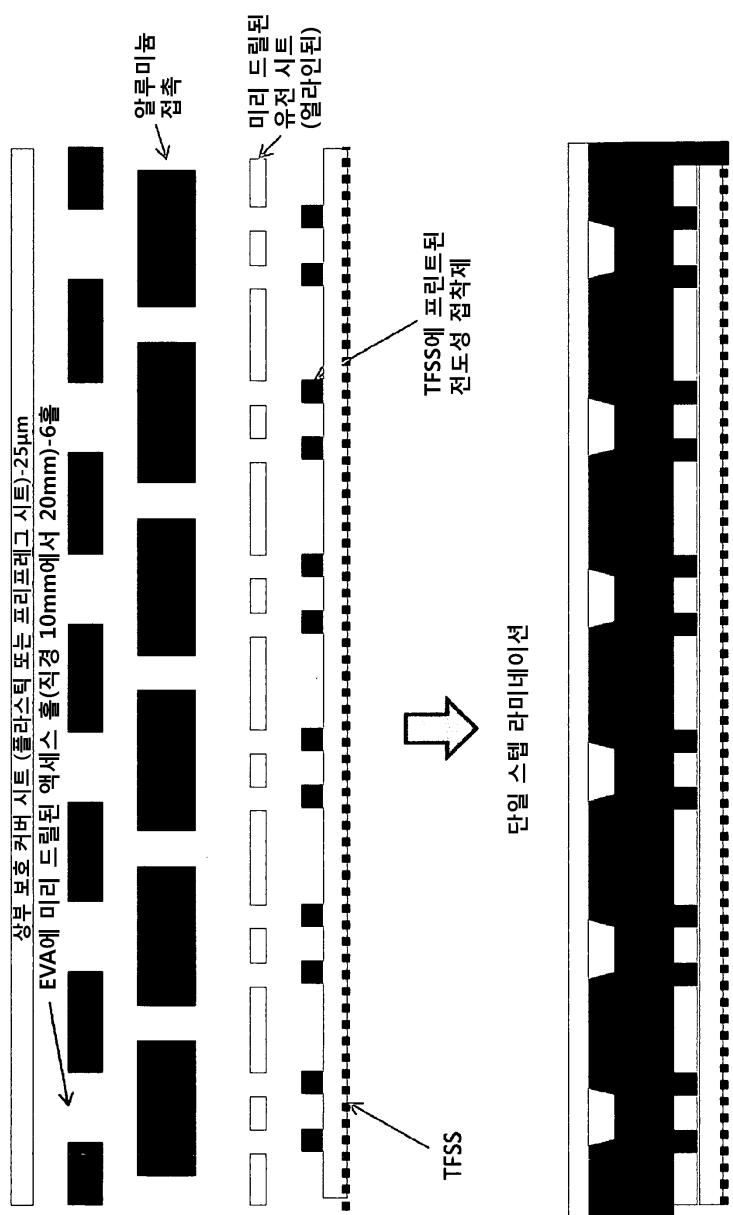

도 75는 미리 드릴링된(predrilled) 유전체 시트를 이용하는 오아시스 구조체 2단계 라미네이션의 단면도를 나타낸다;

도 76은 미리 드릴링된 유전체 시트를 이용하는 오아시스 구조체 단일 단계 라미네이션의 단면도를 나타낸다; 및

도 77A 내지 D는 후면 접촉 태양 전지 형성 동안 플루토-하이브리드(pluto-hybrid) 구조체의 단면도이다.

### 발명을 실시하기 위한 구체적인 내용

[0012]

이하 설명은 제한의 의미로 받아들여지는 것이 아니라, 본 발명의 일반적인 원리를 설명하기 위해 만들어진 것이다. 본 발명의 범위는 청구항을 참조하여 결정되어야 한다. 본 발명의 실시예는, 유사한 숫자는 유사한 것 및 각종 도면의 대응 부위를 참조하도록 사용되는 도면에 설명된다.

[0013]

또한, 본 발명은 결정 실리콘 및 다른 제조 물질과 같은 특정 실시예와 관련하여 기재되지만, 당업자라면 과도한 실험 없이도 다른 물질, 기술 영역, 및/또는 실시예에 개시되는 원리를 적용할 수 있을 것이다.

[0014]

개시되는 주제는, 구체적으로는 바람직하게는 약 1 미크론 ( $1 \mu\text{m}$ ) 미만 내지 약 100 미크론 ( $100 \mu\text{m}$ )의 두께 범위, 더욱 바람직하게는 약 1 미크론 ( $1 \mu\text{m}$ ) 내지 약 50 미크론 ( $50 \mu\text{m}$ ) 두께 범위의 전지 흡수체층(또는 기판)을 갖는 단결정 실리콘과 같은 박형 결정 반도체 흡수체를 이용하는 고효율 후면 접합/후면 접촉 태양 전지의 각종 구조체 및 제조 방법을 제공한다. 또한, 제공되는 전지 구조체 및 제조 방법은, 약  $100 \mu\text{m}$  내지 약  $200 \mu\text{m}$ 의 두께 범위(더욱 종래의 CZ 또는 FZ 웨이퍼 두께의 두께 범위를 포함함)의 흡수체 또는 더 두꺼운 결정 반도체 기판에 적용한다. 결정 태양 전지 기판은 에피택셜 성장을 포함하는 화학-증기-증착 (CVD)법 (예컨대 대기압 에피택시) 또는 다른 결정 실리콘 물질 형성 기술(그것에 제한되지 않지만 소위 커플레스 슬라이싱 (kerfless slicing) 또는 박리(exfoliation)법 이용 프로토 주입을 포함함)을 이용하여 형성될 수 있다. 초박형 결정 반도체 태양 전지 기판을 가공하는 모든 실시예에 관련된 제조방법의 각종 실시예는 다른 형태의 물질 및 주입-보조 웨이퍼 분열법(implantation-assisted wafer cleavage method)과 같은 커플레스 분열 방법(kerfless cleavage method)을 포함하는 웨이퍼 기반의 접근으로 확대될 수 있다. 제공되는 각종 전지 실시예의 주요 속성으로는 실질적으로 감소된 반도체(예컨대 실리콘) 물질 소비, 매우 낮은 제조 비용, 높은 전지 효율, 및 상대적으로 높은 에너지 수율, 따라서 개선된 태양 광기전 모듈 성능을 포함한다. 구체적으로, 이는 본 발명의 특이한 전지 디자인 구조체 및 제조 방법의 조합으로부터 기인하여, 박형 결정 반도체 기판에 매우 높은 전환 효율을 산출하고, 매우 낮은 비용을 산출한다. 다양한 개시된 실시예는 각종 결정 반도체 물질(예컨대 실리콘, 갈륨 비소, 게르마늄 등)에 적용될 수 있지만, 단결정 실리콘의 바람직한 실시예가 제공된다(갈륨 비소, 게르마늄, 갈륨 나이트라이드 등을 포함하는 다른 단결정 반도체에도 적용함).

[0015]

개시되는 주제는 특히 후면 접합/후면 접촉 구조체를 갖는 초박형 결정 태양 전지(약 1 미크론에서 150 미크론 까지, 더욱 바람직하게는 약 1 미크론 내지 약 50 미크론 범위 두께의 전지 흡수체)에 관한 혁신을 제공한다. 첫째, 새로운 초박형(1 미크론 내지 150 미크론 두께 범위) 후면 접촉/후면 접합 결정 실리콘 전지 구조체가 제공된다. 둘째, 후면 접촉/후면 접합 결정 실리콘 전지 구조체를 제조하는 방법이 제공된다. 셋째, 라인을 통

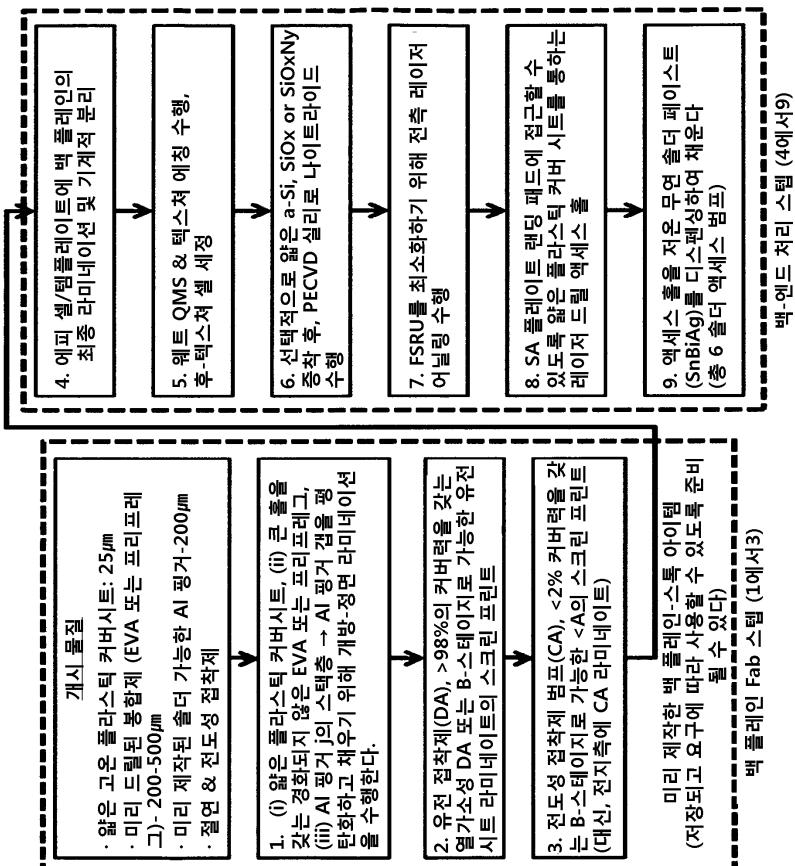

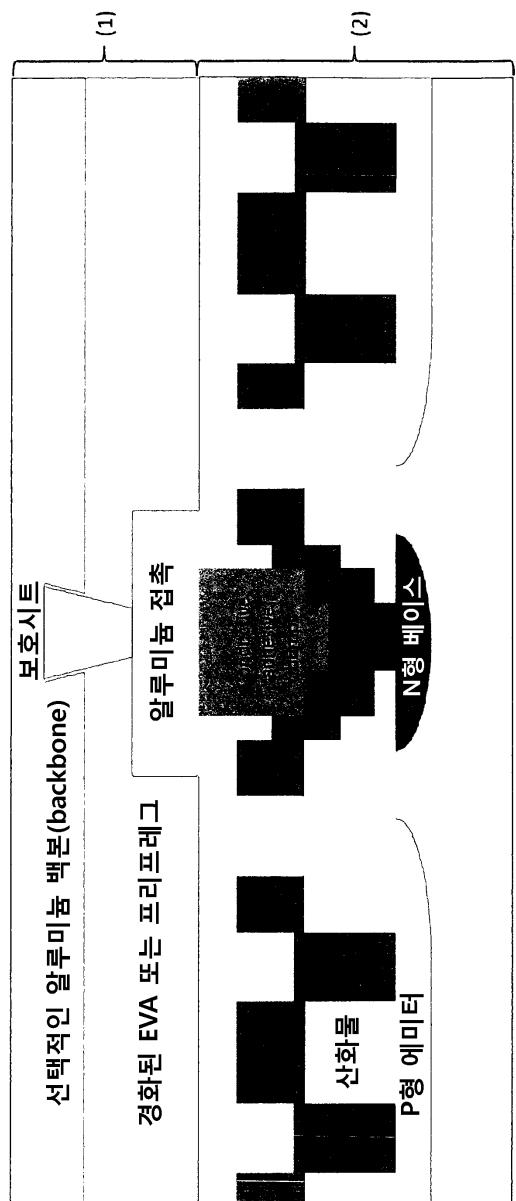

해 가공되고, 장에서 사용되지만, 박형 기판(캐리어를 사용하는)을 지지하는 방법이 제공된다(methods for supporting thin substrates using Carriers) while they have being processed through the line and while they are deployed in the field are provided). 이러한 3가지 카테고리의 각종 조합은 구조체, 공정 흐름 및 박형 전지 지지체 캐리어의 무수히 많은 세트를 생성한다. 도 1은 여기에 개시되는 임시적 박막 캐리어 1 및 영구적 박막 캐리어 2를 포함하는 각종 박막 캐리어 조합을 나타내는 그레픽 플로우 차트이다. 도 1은 캐리어의 다양한 조합의 두 가지 클래스가, 여기에 개시되는 특정 실시예 및 초박형 후면 접촉/후면 접합 결정 반도체 태양 전지를 제조하기 위한 방법 및 새로운 구조체를 구성하는 것을 보여준다. 캐리어의 두 가지 클래스는 제1 캐리어 및 제2캐리어를 포함한다. 또한, 캐리어 1 및 2가 한번 완성되면 다양한 전지 제조 공정 흐름의 옵션이 도 3을 포함하여 여기에 제공된다. 대부분의 캐리어 1 및 캐리어 2 조합으로 짹지어진 임의의 공정 흐름을 갖는 것이 가능하다는 것을 주목한다.

[0016] 이러한 특이한 조합을 이용하여 얻어진 최종 구조체가 후면 접촉 태양 전지이다. 중요하게, 본 명세서에서는 구조체 세트, 공정 흐름, 및 박형 전지 지지체 캐리어의 많은 특이한 세트를 제공하지만, 기반된 가능한 공정 흐름의 모든 세트가 본 명세서에 의해 명쾌하게 커버되는 것은 아니고, 커버되지 않은 건들은 여기에 개시된 전지 디자인 및 공정 흐름 구조체에 기반되는 것으로 암시된다고 여겨진다. 몇몇 공정 흐름 및 다른 실시예는 설명과 함께 여기에 제공되어, 당업자가 각종 개시된 실시예를 조합시킬 수 있다.

[0017] 본 발명은 박형 반도체(예컨대 박형 단결정 실리콘) 전지를 지지하기 위해 사용되는 각종 호스트 캐리어 방법 및 구조체가 제공된다. 우리는 우선, 그 제조 및 영구한 보강을 통해 박막 실리콘 기판(이후, TFSS)을 지지 및 처리하는 것에 관한 카테고리를 강조함으로써 시작한다-이는 도 1의 박형 캐리어 1 및 박막 캐리어 2와 같이 나타낸다.

[0018] 높은 제조 수율은 상업적으로 실행 가능한 박형 실리콘 태양 기술의 전제 조건이다. 본 명세서에서 논의되는 초박형 태양 전지(약 1 미크론에서 150 미크론까지, 더욱 바람직하게는 약 5 미크론 내지 약 60 미크론의 두께 범위의 전지 흡수체)는 상업적 실행가능성 및 높은 제조 수율을 유지하기 위해 전지 처리 및 가공 동안에 완전히 그리고 계속적으로 지지된다. 이는, 박형 전지는 임시 또는 영구적 지지체 부착(기판 캐리어라고도 함) 없이 처리되거나 가공되지 않는다는 것을 의미한다. 또한, 이러한 박형 반도체 전지는, 기계적 탄성, 신뢰성 및 모듈 라미네이션/패키징 동안 높은 수율, 장 설치(field installation), 및 장 동작(field operation)을 유지하기 위해 장에서 설치 및 작동을 위한 광기전 모듈에 한번 어셈블리되면 영구히 지지된다. 태양 전지의 양측은 접근(accessed) 및 가공(processed)될 필요가 있기 때문에(전지의 후측 및 태양이 비치는 측을 완전하게 만들기 위해), 일반적으로 TFSS에 두개의 캐리어가 요구된다(처리, 가공, 및 최후 모듈 패키징에서 박형 반도체 기판을 항상 지지하기 위해서): 태양 전지의 각각의 면을 가공하기 위한 것. 캐리어는 몇몇의 중요한 기준을 만족시켜야 한다: 첫째, 이들은 비용 효율적이어야 한다(즉, 전지 당 낮은 비용 또는 퍼크 와트 당 매우 낮은 비용). 이들의 조합된 분할 상환된 비용은 이들이 절약하는(종래의 와이퍼 기반의 태양 전지와 비교하여) 박형 전지의 실리콘의 비용 미만이 되어야 한다. 둘째, 캐리어의 적어도 하나는, 열팽창계수 (CTE)의 불일치 및/또는 전지에 도입되는 바람직하지 않은 불순물에 기인하는 문제 없이 고효율 태양 전지를 제조하는데 요구되는 상대적으로 고온의 가공(특히 약 300 °C 내지 1150 °C 범위의 온도에서)에 견딜 수 있어야 한다. 또한, 만약 캐리어 중 하나가 고온 전지 가공(즉 필요에 따라 전지 후측 장치 구조체를 완성하기 위한 또한 CVD 에피택시를 이용하여 전지 기판을 형성하기 위한 고온 가공)을 지지할 수 있는 경우, 공정 흐름은, 모든 필요한 고온 가공 단계가 이러한 고온-가능한(hight-temperature-capable) 캐리어(일시적으로 재사용 가능한 캐리어로 작용할 수 있는) 상에 있도록 해야한다. 상기 논의된 바와 같이, 이러한 특정 기준들은 후면 접촉/후면 접합 전지에 매우 유용하여, 고효율 후면 접촉, 후면 접합 박형 전지를 가능하게 한다. 셋째, 캐리어 중 적어도 하나는 바람직하게는 태양 전지를 제조하는데 요구되는 최종 전지 금속화 및 웨트 가공을 견딜 수 있어야 한다. 주요 웨트 가공 단계의 예로는, 희석 및 가열된 알칼리성(KOH 및/또는 NaOH 및/또는 TMAH을 포함하는) 용액으로 실리콘 전면 임의의 피라미드 텍스처링 에칭을 포함한다. 넷째, 제1측(바람직하게는 후면 접촉/후면 접합 전지 가공을 위한 전지 후측)이 부분적으로 또는 완전히 가공되면, 캐리어(일시적으로 재사용 가능한 캐리어로서 작용하는)는, 박형 전지(박막 반도체 기판: TFSS)는 제2측 가공을 위해 리프트 오프 분리 공정(우선 바람직하게는 후면 접촉 전지의 전지 후측이 가공되는)과 함께 다른 캐리어로 전달되는 TFSS 층을 가지고, 높은 수율을 갖는 언제든지 캐

리어로부터 쉽게 분리 또는 리프트 오프될 수 있어야 한다. 그 후, 제1측(바람직하게는 전지 후측)이 부분적으로 가공되는 경우에, 남아 있는 공정 단계(예컨대, 최종 전지 금속화의 완성과 같은)는, 예컨대 이하에 설명되는 각종 실시예를 이용하여 완성될 수 있다. 바람직하게는, 본 발명의 실시예 내에서, 고온-가능한 일시적 캐리어 및 고온 가공 단계는, 영구적 캐리어 및 웨트 가공 및 최종 전지 금속화 단계에 앞선다. 또한, TFSS 충에 영구적 캐리어의 전-리프트 오프(pre-lift-off) 부착까지(till) CVD 에피택시를 이용하여 박형 실리콘 기판의 형성으로 시작하는, 가공 단계 모두는 TFSS 상에서 수행되지만, 일시적 캐리어 상에서 바람직하게는 드라이 가공 단계이다(CVD 에피택시에 의한 TFSS의 형성 전에 웨트 다공성 실리콘 가공 단계를 제외하고 일시적 캐리어 상에서 웨트 가공이 없음). 또한, 전지 접촉 금속화는 바람직하게는 전지 접촉 형성 전에, 영구적 캐리어의 부착 전에, 일시적 재사용 가능한 캐리어 또는 템플레이트로부터 TFSS의 리프트 오프 분리 전에 수행된다.

[0019] **TFSS용 지지 캐리어 # 1 (즉, 재사용가능한 템플레이트).** 후면 접촉/후면 접합 구조체를 갖는 TFSS의 조합에 대해서, 제1캐리어의 두 가지 선택은 이후 캐리어 1로 개시된다. 이러한 옵션은 도 1의 아래 캐리어 1로 나타낸다. 이하 명세서에서, 후면 접촉/후면 접합 전지의 태양이 비치는 측은 전지 "전측(frontside)"으로 상호 교환하여 사용될 수 있고, 태양이 비치지 않는 측은 "후측(backside)"으로 상호 교환하여 사용될 수 있다.

[0020] 1. 캐리어 1의 첫째로 개시된 옵션은, 재사용 가능한 템플레이트로 작용할 수 있는(그 결과 많은 템플레이트 재사용 사이클에 드는 비용을 분할 상환하는) 상대적으로 두꺼운(바람직하게는 약 0.2 mm 내지 2 mm 범위의 두께) 반도체(예컨대, 바람직하게는 고효율 단결정 실리콘 태양 전지용 단결정 실리콘) 웨이퍼( $150 \text{ cm}^2$  내지  $2,000 \text{ cm}^2$  이상 범위의 웨이퍼 면적)이다. 바람직한 전지 면적, 예컨대 스퀘어형 전지 치수 156 mm x 156 mm (이 사이즈는 적어도 210 mm x 210 mm까지 또는 300 mm x 300 mm 및 450 mm x 450 mm보다 큰 사이즈로 크기 변경될 수 있음)을 갖는 대면적 박형 태양 전지 기판은, 우선 재사용 가능한 결정 반도체 템플레이트의 상부에 성장되는 에피택셜 반도체(에피택셜 실리콘)을 이용하여 제조되고, 이어서 제거된다. 재사용 가능한 템플레이트는 실질적으로 평면일 수 있거나, 다른 실시예에서 미리-구조화된(pre-structured) 3차원 프리 패턴(pre-pattern)을 갖는다. 각종 실시예가 임의의 구조체 또는 패터닝된 규칙적인 구조체 3D 특징을 갖는 미리 구조화된 템플레이트에 적용될 수 있지만, 본 발명은 실질적으로 평면인 템플레이트에 초점을 맞춘다. 재사용 사이클에 걸쳐서 그 비용을 분할 상환하는, 에피(에피택셜 실리콘) 성장에 몇 번(바람직하게는 적어도 수십 번) 재사용될 수 있다. 그 재사용 수명 후, 재사용 가능한 템플레이트는 CZ 결정 성장 및 웨이퍼 슬라이싱을 통해 새로운 템플레이트를 제조하기 위해 궁극적으로 리사이클링될 수 있다. TFSS는, 일 실시예에서 다공성 실리콘층, 바람직하게는 적어도 2개의 다른 공극률(더 높은 공극률 매립된 분리층 및 더 낮은 공극률 시드층) 또는 그레이드된 공극률을 갖는 것 일 수 있는 회생 분리층을 이용하여 재사용 가능한 템플레이트로부터 분리된다. 바람직하게는 상대적으로 두꺼운(바람직하게는 약 0.2 mm 내지 2 mm 범위)이기 때문에, 재사용 가능한 템플레이트는, 이하 TFSS와 관련된 CTE 불일치 문제없이, 임의의 오염 문제 없이 상대적으로 높은 가공 온도(예컨대, 약 1150 °C 이상)를 견딜 수 있고, 상기 설명된 캐리어 1의 주요 기준 중 하나를 만족한다. 템플레이트는 156 mm, 165 mm, 200mm, 300mm 또는 450 mm(또는 약 100 mm 내지 몇 백 mm 범위, 적어도 450 mm까지의 임의의 직경 또는 측면 치수)과 같은 다양한 사이즈, 둥글거나 사각하거나 또는 다각형인 형태, 균열 또는 파손 없이 전체 또는 부분 태양 전지 공정을 견딜 수 있는 두께, 약 적어도 200  $\mu\text{m}$  (약 2 mm 이상 두꺼운)의 템플레이트 두께일 수 있다. 비용 효율성과 관련된 캐리어 1에 대한 두번째 기준은, 복수의 TFSS 제조 사이클에 걸쳐 템플레이트 비용을 재사용 및 분할 상환함으로써(또한 필요 또는 소망에 따라 연마되지 않은 템플레이트를 사용함으로써) 완성될 수 있다. 또한, 마지막으로, 이러한 캐리어는 높은 반복성 및 일관성을 갖는 TFSS의 고수율 분리에 도움이 되는 상기 캐리어 기준을 만족한다. 이것은, 바람직하게는 HF 및 IPA (또는 HF 및 아세트산 또는 다른 적당한 물질과 혼합된 HF)를 포함하는 액체로 웨트 전기화학 에칭 공정을 이용하여, 템플레이트와 TFSS의 사이에서 다공성 실리콘층(에피택셜 시드층 및 이후 분리층으로 작용하는)의 형성과 TFSS의 에피택셜 성장을 앞섭으로써 수행된다. 다공성 실리콘층의 공극률은, i) 에피택셜 공정 동안 높은 정확도를 갖는 템플레이트의 결정화도를 전환하고, ii) 템플레이트로부터 필요에 따라 초고수율 분리를 제공할 수 있는 두 가지 목적을 수행하기 위해 공급되고, 공간적으로 깊이에 조절된다(더 낮은 공극률의 상부층 및 더 높은 공극률의 매립된 하부층을 이용함으로써). 전지 분리는, 기계적 분리 (MR) 또는 액체에서 소니케이트되는(sonicated) 기계적 분리 (SMR)와 같은 공정 또는 다른 적당한 방법을 이용하여 수행될 수 있고, 영구적 캐리어 2에 부착 또는 라미네이션 후 TFSS 충의 리프트 오프 분리를 야기한다.

[0021] 2. 캐리어 1의 두번째로 개시된 옵션은, 재사용 가능한 두꺼운 웨이퍼 또는 잉곳일 수 있다. TFSS의 분리는 MeV (메가-전자 전압, mega-electron volt) 프로톤 (수소 이온) 주입과 같은 높은 주입-에너지를 이용하고, 호스트 웨이퍼 또는 잉곳으로부터 박형 슬라이스를 분리하여 수행될 수 있다.

[0022] 호스트 캐리어 상의 다공성 실리콘/에피(epi) 기술이 두꺼운 웨이퍼/잉곳 및 주입 유도 분리 기술과 비교되는 경우에, 몇 가지 트레이드 오프(trade-offs)가 확인될 수 있다. 주입을 이용하는 웨이퍼/잉곳은 다공성 실리콘 및 에피택셜 성장 및 동반되는 인자들을 필요로 하지 않는 이점이 있다(그러나, 폴리실리콘 공급 원료 및 잉곳 성장에 의존성이 있다). 반면에, 약간 비싼 MeV 프로톤 주입 자본 설비(proton implantation capital equipment) 및 주입기를 작동하기 위한 고에너지 소비를 필요로 한다. 실리콘의 품질은 잉곳의 비용에 따라 높아질 수 있고, 잠재적으로 웨트 가공을 하도록 할 수 있다. 아래쪽(downside)은, 과도하게 높은 프로톤 주입량의 필요를 없애기 위해 잉곳이 <111> 배향을 가질 수 있기 때문에, 웨이퍼가 표준 웨트 텍스처링과 반대로 더욱 비싸고 손상이 생기는 드라이 텍스처링에 의존할 수 있는 것이다. 다공성 실리콘/에피(epi) 조합은, 표준 알칼리성 웨트 텍스처링과 양립 가능하고, 기판 도핑은 고효율 요건에 좋은 무엇에도 모듈레이팅/그레이딩될 수 있다는 장점이 있다. 또한, 초박형 실리콘 전지 기판(약 1 미크론 미만)은 다공성 실리콘/에피 제조법을 이용하는 것이 가능하고, 도핑 프로파일은 에피택셜 성장(프로톤 주입에 의해 제조되는 박형 실리콘층에 가능하지 않은) 동안 엔지니어링 및 조절될 수 있다.

[0023] TFSS용 지지 캐리어 # 2: 백플레인. 후면 접촉/후면 접합 전지의 특정 맥락에서, 제2 캐리어는 바람직하게 몇 가지 기준을 만족해야 한다. 둘째, 부착되는(특정 구조체의 후측) 측의 전 가공을 보호해야 하지만, 다른 측(전측)은 가공된다. 제2 캐리어는 바람직하게는, 전측의 가공 동안 사용되는 웨트 화학물질(바람직하게 및 주로 TFSS 태양이 비치는 측을 세정 및 텍스처링하는데 사용되는 웨트 화학물질에 상대적으로 영향을 받지 않거나 내성이 있는 것이 필요하다.셋째, 그 완전한 부분으로서 고전도성 금속화층(바람직하게는 알루미늄 및/또는 구리를 포함하는)을 갖거나 갖지 않을 수 있다. 금속화를 갖고, 캐리어(바람직하게는 매우 낮은 비용의 영구적으로 부착되는 캐리어)가 되는 경우에 대해서, 낮은 저항을 갖는 전지 상의 금속에 이음매 없이 부착하는 금속화를 제공한다. 마지막으로, 공극률이 높지 않지만, 실리콘과의 임의의 CTE 불일치에 기인한 TFSS의 크랙을 생성하지 않고, 캐리어 물질의 열화 없이, 우수한 전측 패시베이션(따라서, 바람직하게는 적어도 약 180 °C의 온도까지, 더욱 바람직하게는 적어도 약 250 °C 또는 300 °C 초과의 온도)을 수행하기 위해 충분한 열 가공 능력을 가져야 한다. 이후 태양 전지 후측에 부착된 제2 캐리어를 태양 전지 "백플레인(backplane)"으로 할 것이다.

[0024] 몇몇 백플레인 실시예는 박막 캐리어 2 제목 하에 도 1에 설명되고 여기에 개시된다. 도 1에 캐리어 2에 대해 설명된 임의의 몇몇의 옵션이, 상기에 논의되는 2가지 캐리어 1 옵션, 즉 재사용 가능한 템플레이트/에피/다공성 실리콘 옵션 또는 잉곳 (또는 두꺼운 웨이퍼)/임플란트의 옵션이 사용되는 임의의 캐리어 2 실시예와 함께 사용될 수 있다는 것을 인지하는 것은 중요하다.

[0025] 캐리어 2(백플레인)는 두 가지 넓은 클래스로 나뉠 수 있다(도 1): 첫번째 카테고리, "캐리어 1 상의 전체 후측 공정(full Backside Process on Carrier 1)"은, 캐리어 2는, 그것이 부착되는 측 (후측) 상에 요구되는 모든 가공이 캐리어 1 상에서 완료된 후에만 부착되는 것이다. 후면 접촉/후면 접합 전지에서, 이것은 패터닝된 도편트 디퓨전, 개방부 접촉, 및 전체 후면 접촉 금속화를 포함하는 태양이 비치지 않는 측 (후측) 가공 단계 모두를 피니싱하는 것을 수반할 수 있다. 최종 전지 금속화에 전기적 접근이 요구되는 일부 경우를 제외하고, 이 측 상에 다른 가공이 요구되지 않는다. 두번째 카테고리, "캐리어 2 상의 부분 후측 공정(partial Backside Process on Carrier 2)"은, 후측 상의 단지 부분 가공이 완료된 후 부착되는 것이다. 본 발명은 부분 가공을 이용하는 후자의 카테고리에 초점을 맞추고, 이 패러다임 내에서 가능한 몇몇의 서브 그룹을 논의하지만, 첫번째 카테고리 당 전체 가공을 수반하는 변경은 내포되고, 본 발명의 범위 내인 것으로 이해한다.

- [0026] 태양이 비치지 않는 측(즉, 전지 후측) 상에 부분 가공 패러다임을 지지하는 구동력 중 하나는(One of the driving forces behind the partial processing paradigm on the non-sunny side), 구리와 같은 잠재적으로 해로운 물질(수명 감소 물질(lifetime degrading materials)이 후측 가공의 일부인 경우, 다른 TFSS를 캐링하기 위해 재사용될 수 있는 캐리어 1을 오염시키지 않는다는 것을 보증하는 것이다(그 결과, 제조 라인에서 금속 상호 오염의 위험을 방지함). 이는 제조 라인에서 상호 오염 및 그로 인한 효율 저하를 방지한다(그 결과 전지에 상호 오염의 위험 없이 고수율 템플레이트 재사용을 가능하게 함). 따라서, 태양이 비치지 않는 측 상의 부분 가공을 지지하는 아이디어는, TFSS가 캐리어 1로부터 분리된(detached and released) 후, 잠재적으로 수명-감소 물질 및 가공(예컨대 고효율 구리 도금 금속화)으로 도입한 결과, 상호 오염의 위험을 제거하는 것이다.

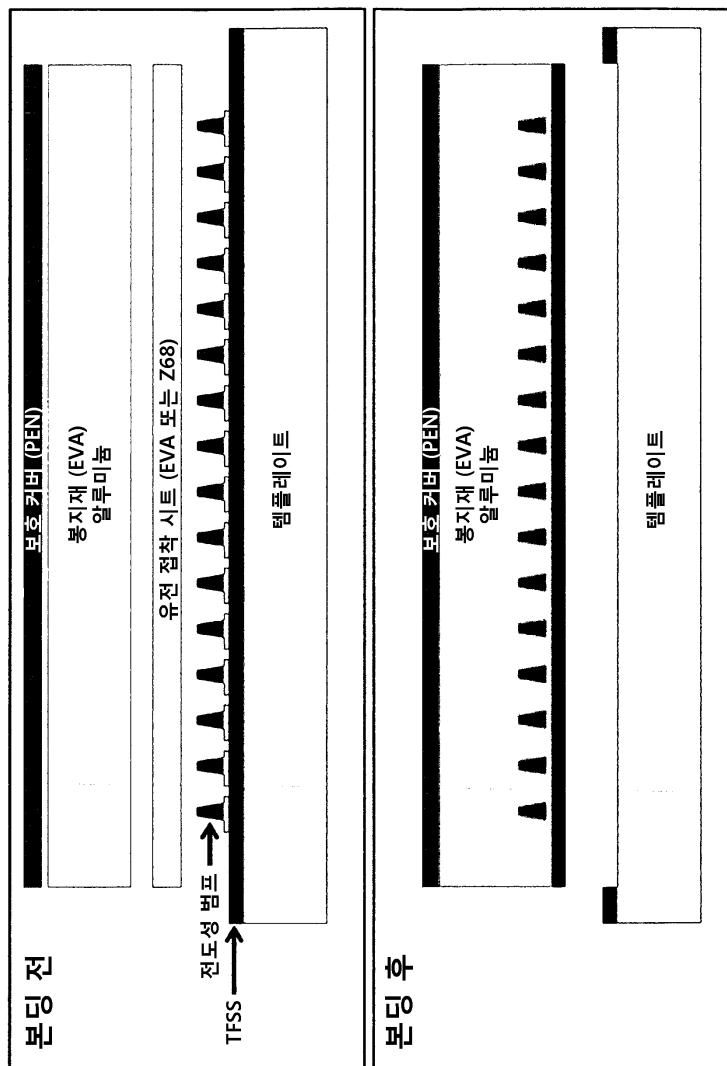

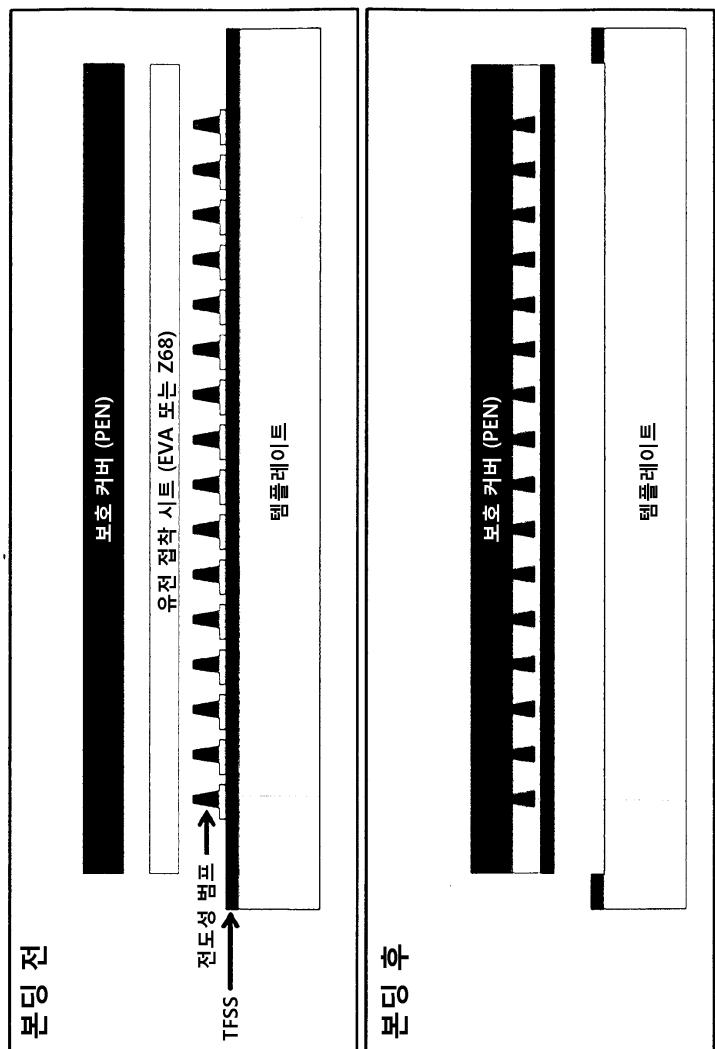

- [0027] 부분 가공 패러다임 내에 백플레인의 3가지 서브 카테고리는 도 1에 나타낸다. 전면 강화, "fSR"라고도 하는 첫번째 케이스에서, TFSS는 부분적으로 가공되는 후측 상에 부착되는 임시적 캐리어를 이용하여 템플레이트로부터 분리된다. 이후, 텍스처링 및 패시베이션과 같은 전측 전지 가공은 TFSS를 지지하는 일시적 후측 캐리어로 수행된다. 일시적 캐리어는 TFSS의 분리의 용이함에 의해 선택되고, 전기(예컨대 모바일 정전 척, MESC), 모바일 진공 척, MOVAC, 또는 가열 시 또는 UV 노출 시 분리되는 일시적 접착과 같은 공지의 방법을 이용할 수 있다. 남아 있는 후측 단계(예컨대, 구리 금속화)는, 일시적 후측 지지체로부터 TFSS를 광학적으로 투명한 영구적 전측 보강재(예컨대 저비용 EVA 봉합재(encapsulant)/유리 조합)로 트랜스퍼함으로써 수행되고, 따라서 남아 있는 공정(예컨대 남아 있는 금속화 단계)을 위해 후측을 없앤다. 전측 보강재의 특정 요건은, 이는 모듈 레벨 패키징에 기인해 일반적으로 발생되는 열화 이상으로 광 투과 및 커플링을 저하시키지 않는 것이다. 따라서, 다른 물질 세트도 가능하지만, EVA/유리 기반 보강재 등이 바람직하다(예컨대 ETFE로 이루어진 깨끗한 전면 플루오로폴리머 시트를 갖는 EVA).

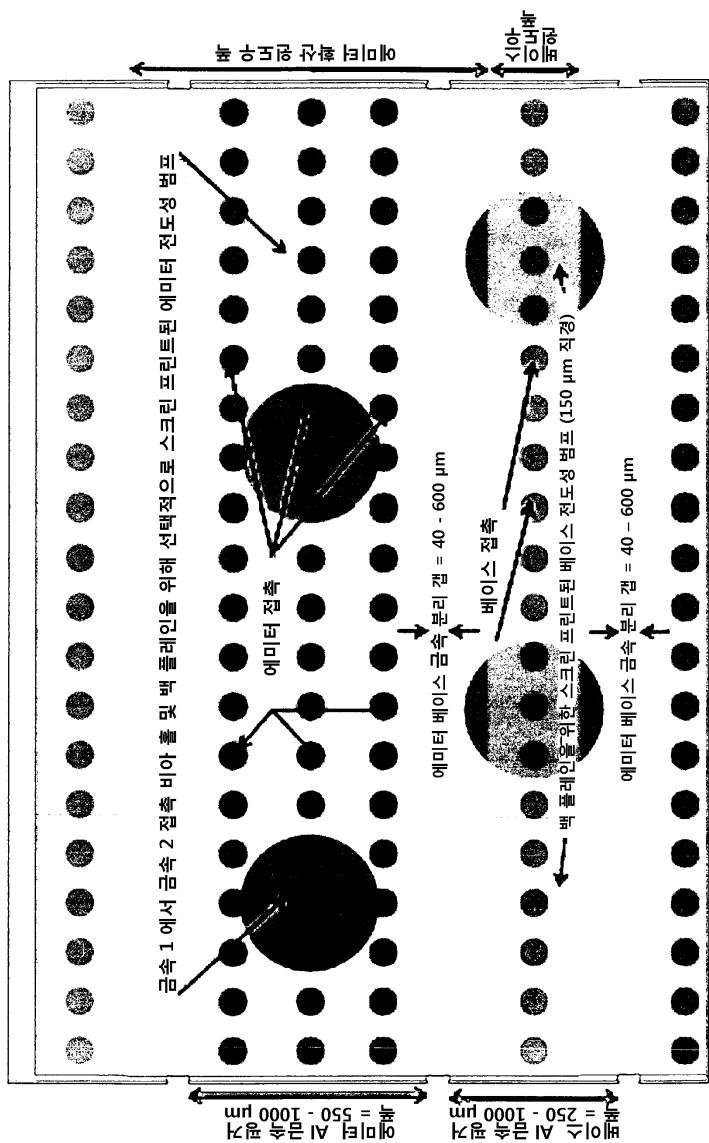

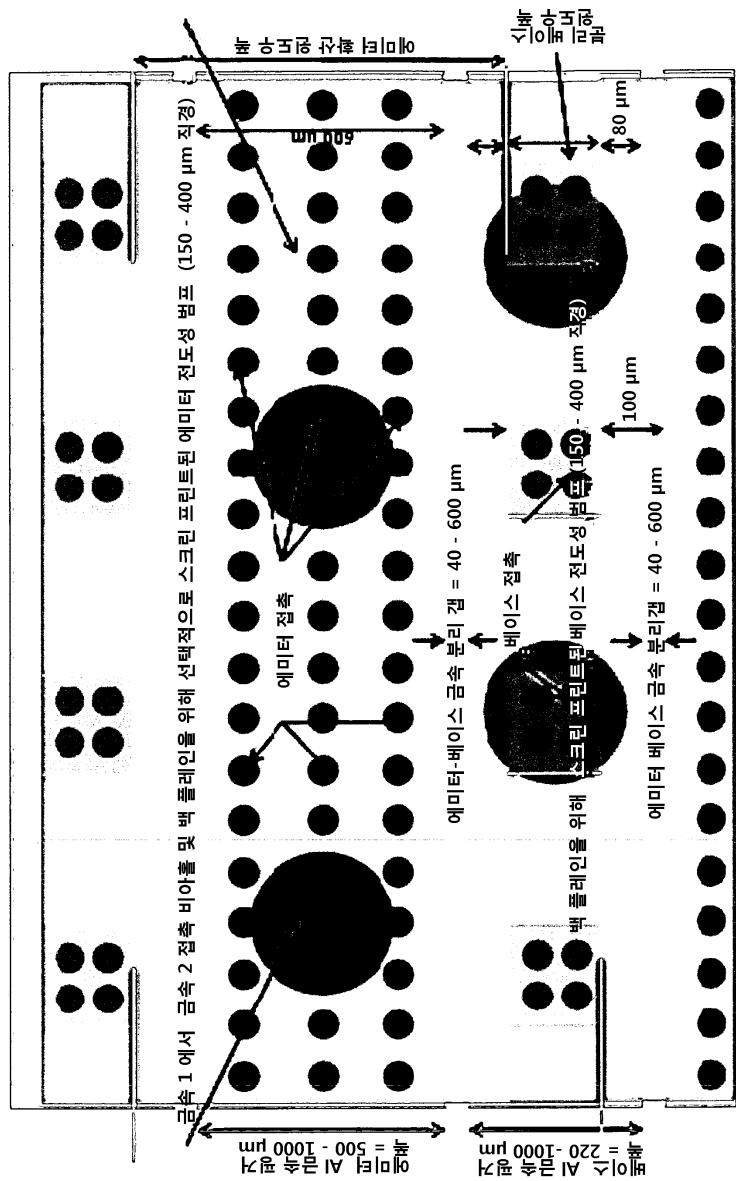

- [0028] 두번째 및 세번째 서브 카테고리, 부분적 후측 가공을 이용하는 백플레인의 "금속화 없는 백플레인" 및 "금속화를 갖는 백플레인"은 영구적인 백플레인에 의해 특징지어진다(상기 FSR과는 대조적으로). 이러한 두개의 카테고리 사이의 차이점은, "금속화 없는 백플레인"은 그 구조체에 통합 또는 임베딩되는 두꺼운 금속화를 갖지 않는다는 점이다; 대신 이러한 금속화는 전측(태양이 비치는 측)이 가공된 후에 백-엔드(back-end) 쪽을 향해 놓인다. 반면에, "금속화를 갖는 백플레인"은 백플레인으로 통합되는 두꺼운 제2 레벨의 금속화(예컨대 패터닝된 금속박)를 갖는다. 백플레인 상의 두꺼운 금속화층은, 상호 접속의 제2층을 형성하는 TFSS 상의 박형 금속화층에 연결되고, 또한 부스바를 함유할 수 있다. 이러한 두꺼운 높은 전기 전도성 금속화층(바람직하게는 알루미늄 및/또는 구리)은 후면 접촉 전지의 저항을 감소시킨다.

- [0029] 본 발명은 백플레인의 "금속화 없는 백플레인" 서브 카테고리 내에서 3가지 특정 실시예를 설명한다. 중요하게, 이는 이러한 3가지 실시예로 이 패러다임을 제한하는 것으로 이해해서는 안된다. 첫번째 케이스는 후면 보강재 또는 "bSR"이라 한다. 이 공정 흐름에서, TFSS는 영구적 후측 보강재를 이용하여 템플레이트(제1 캐리어)로부터 분리된다. 영구적 후측 보강재는 후측을 부분적으로만 커버하여, 전측 가공이 BSR 지지체를 이용하여 완료된 후, 개방 영역을 통해 후측 상에 가공시킨다. 이것의 구조적 예로는, 태양이 비치지 않는 후측 상에 마지막 몇몇 가공을 위해 후측에 접근을 제공하는 그리드들 사이에 실질적으로 넓은 개방 영역을 갖는 그리드 패턴으로 제조된 백플레인이다.

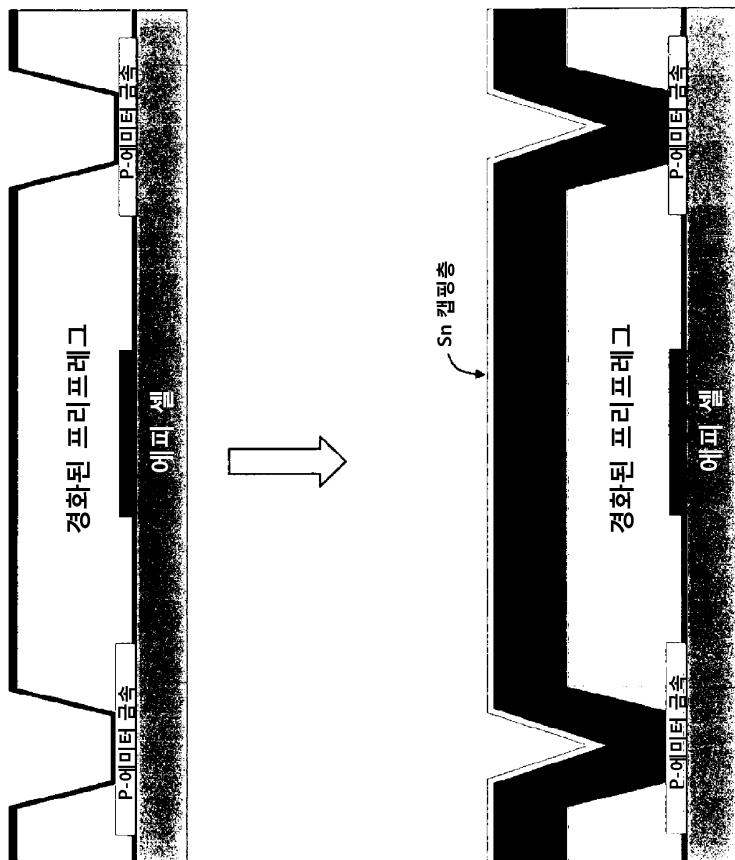

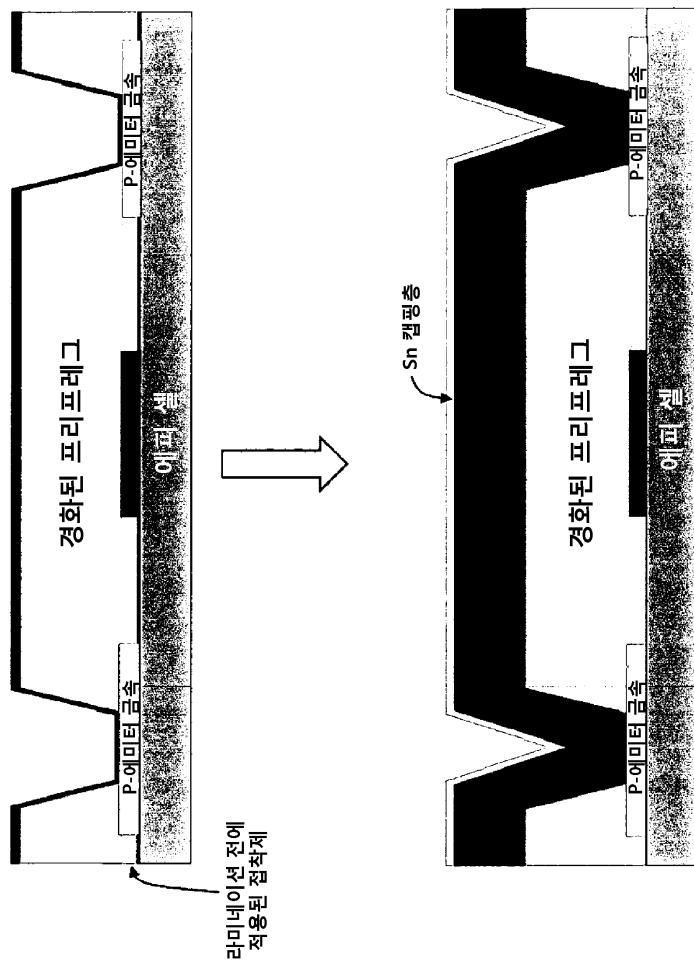

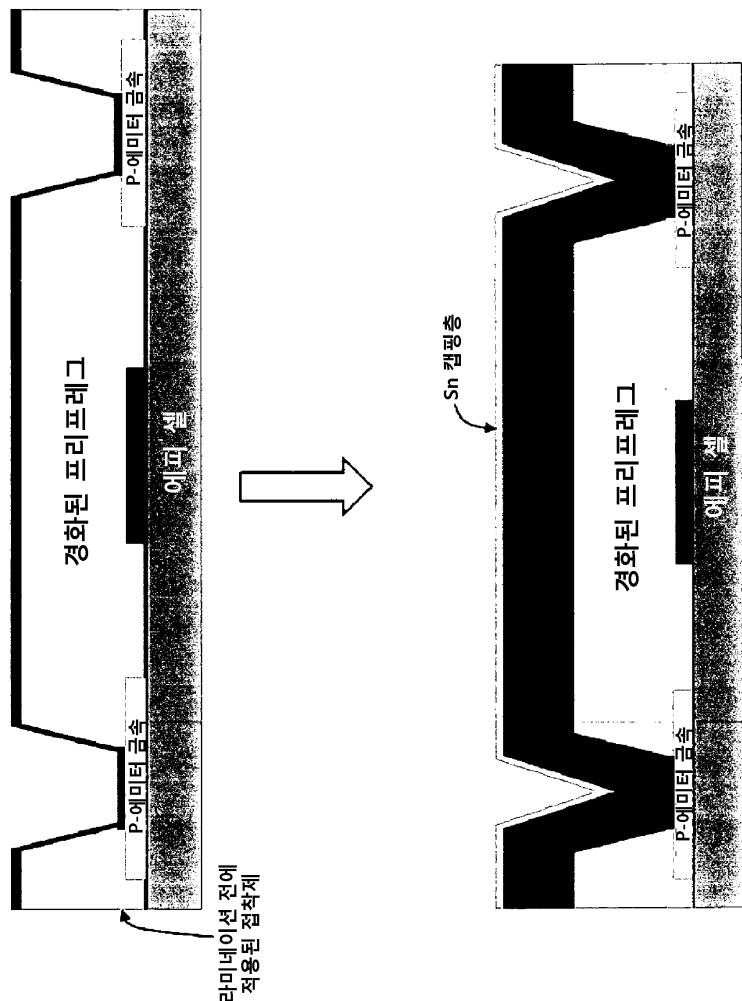

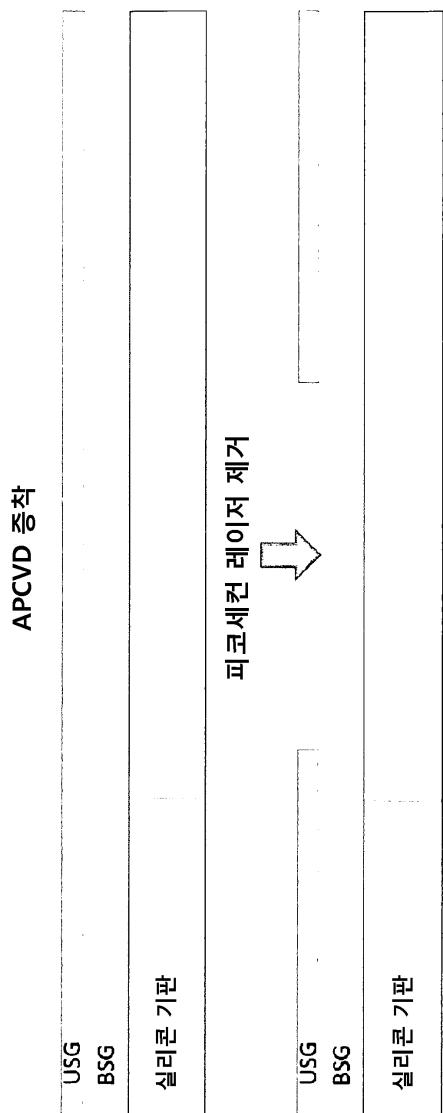

- [0030] 영구적 "금속화 없는 백플레인"의 제2 실시예는 두문자어 "PLUTO"라 알려진 디자인이다. 이 공정 흐름에서, 단순하고 저렴한 백플레인 물질(예컨대, 수지 및 섬유의 혼합물을 포함하는 상대적으로 낮은 CTE 프리프레그 물질)은 TFSS에 부착되지만, 이는 첫번째 캐리어에 부착된다. 백플레인 부착은 직접적 결합/라미네이션(물질이 그 안에 접착성을 가진 경우에)일 수 있고, 또는 스크린 프린팅과 같은 수단을 이용하여 프린팅될 수 있는 (또는 스프레이 코터 또는 롤러 코터를 이용하여 적용되는) 유전체 접착층(DA)과 같은 중간 접착층을 사용한다. 프리프레그 어셈블리/물질 선택은, 이들이 이하 조건을 만족하도록 해야한다:

- a. 분리된 TFSS/프리프레그 어셈블리는 매우 작은 이불(bow)을 가지고 상대적으로 스트레스 및 크랙이 없어야 한다.

- [0032] b. 백플레인은 크랙이 없는 특성을 유지해야 하고, TFSS에 스트레스 크랙을 유도하지 않아야 하지만, 전측 텍스처링(예컨대 고온 KOH를 이용하여) 및 PECVD 패시베이션 공정과 같은 후속 가공 단계를 겪는다.

- [0033] C. 백플레인은 텍스처링 및 후 텍스처링 표면 세정 (및 임의의 가능한 미리 텍스처링 실리콘 에칭)과 같은 전측 가공 동안 사용되는 화학물질에 상대적으로 잘 견뎌야 한다.

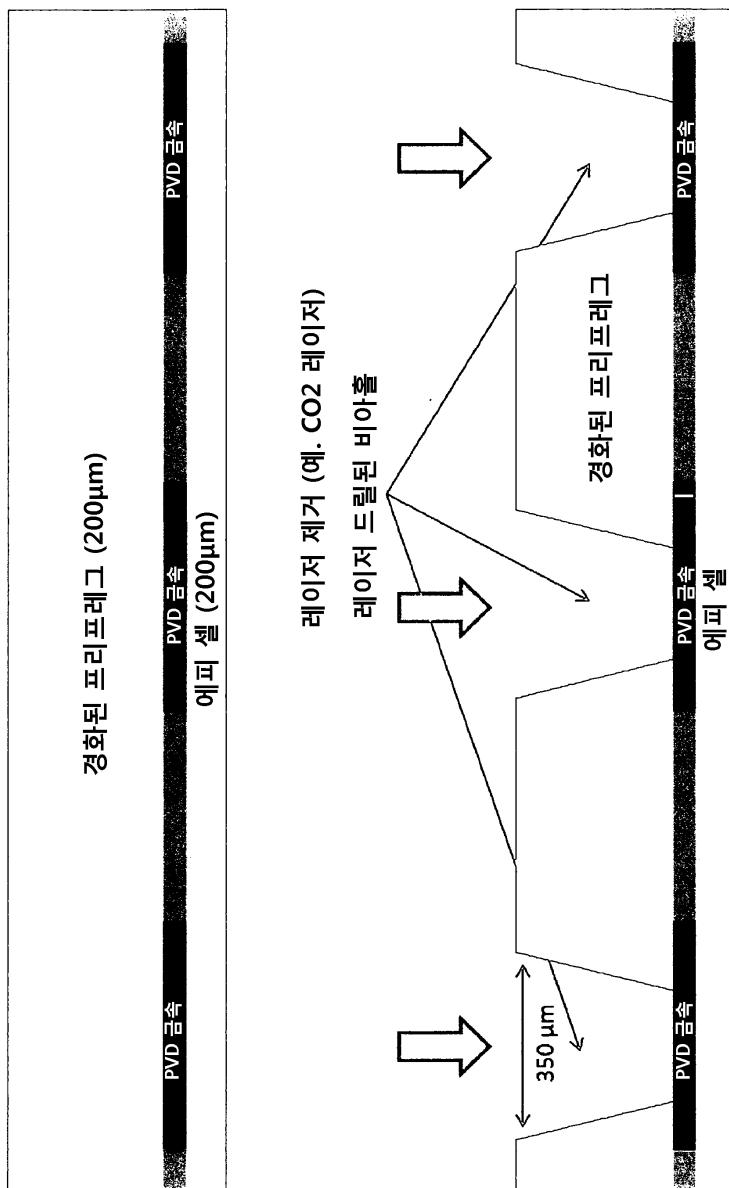

- [0034] 결국, 전측 가공이 PLUTO 백플레인을 이용하여 완료되고, 접근 홀(access holes) (수 100 내지 수 1000개의 홀)은 백플레인 (예컨대 프리프레그 물질)을 통해 바람직하게는 고생산성 레이저 드릴링 수단을 이용하여 드릴링하고, 남아 있는 전지 금속화는, 바람직하게는 패터닝된 전기 전도성 시드 페이스트의 스크린 프린팅 및 프리 패터닝된 금속박층(알루미늄 및/또는 구리를 포함함)의 부착의 조합을 이용하거나 또는 도금함으로써 피니싱된다. 이 홀은, TFSS가 템플레이트 상에 있는 동안 형성되는 언더라잉 온-셀 패터닝된 금속(underlying on-cell patterned metal)에 접근을 제공한다(특정 실시예는 공정 흐름에 대한 이하 논의 동안 설명될 것이다). 홀의 드릴링은 무수히 많은 레이저 및 기계적 방법을 이용하여 수행될 수 있고, 특정 실시예에서 이는 고속의 스루풋 CO2 레이저를 이용하여 수행될 수 있다. 드릴링 기술에 대한 요건은 고속의 스루풋, TFSS 상의 언더라잉 금속 또는 TFSS에 대한 미손상, TFSS 상의 언더라잉 금속에 낮은 저항의 전기적 접근을 갖기 위한 레이저 개방된 접촉(필요에 따라)를 세정하는 믿을 만한 방법, 및 언더라잉 금속에 홀의 적당한 얼라인먼트를 포함한다. 레이저 드릴링 이후에, 금속화의 나머지(제2 레벨의 금속을 포함함)는, 도금(비전해 및/또는 전기 도금), 프레임 스프레이와 같은 직접적인 두꺼운 금속 라이팅 기술, 백플레인에 금속화로 빵판(bread-board)을 부착, 패터닝된 도전성 시드 페이스트의 스크린 프린팅 후 금속박 펑거 부착, 또는 MMA(monolithic module assembly)와 같은 접근으로 모듈 어셈블리의 일부로서 금속화를 갖는 것을 포함하는 몇몇의 방법을 이용하여 피니싱될 수 있다. 약간의 변형 공정은, 프리프레그가 TFSS에 부착/라미네이션 전에 미리 드릴링된 홀을 가지고(TFSS에 레이저 드릴링 유도된 손상 위험을 제거하기 위해서), 다른 쉽게 제거 가능한 저렴한 박형 물질층 또는 시트(예컨대 박형 마일러 시트 또는 다른 적당한 물질)에 의해 보호되는 것을 포함한다. 이 실시예에서, 제거 가능한 보호 시트는 바람직하게, 태양이 비치는 측의 전지 가공(웨트 텍스처 및 PECVD 패시베이션 공정을 포함함)의 완료 전, 최종 전지 금속화의 완료 전(또는 MMA의 경우에 모듈 어셈블리 전) 제거될 것이다.

- [0035] 세번째 실시예, 도 1의 영구적 "금속화 없는 백플레인"의 "Cu 플러그"는 상기 소위 PLUTO 실시예의 약간의 변형된 디자인이다. 또한, 명명 규칙으로 금속을 이용하여 구체적으로 확인되지만, 이러한 접근은 전기적으로 도전성인 물질로서 구리에 제한하는 것으로 이해해서는 안된다. 이 경우에, 백플레인은 PLUTO와 비교하여 백킹하는 추가적인 층을 갖는다. 예컨대, 백플레인은 Z68라고도 하는, 얇게 에틸렌 비닐 아세테이트 (EVA)인 봉합재 PV-FS Z68 (DNP Solar 제품)과 같은 잘 휘어지는 부착 물질을 갖는 유리 또는 다른 두꺼운 고체 백시트 물질(예컨대 양극산화된 Al)로 이루어질 수 있다. 백시트는 미리 드릴링된 홀을 가질 수 있지만, 언더라잉 부착 물질은 전측 공정 동안(예컨대 전측 웨트 알칼리성 텍스처링 동안) 화학적으로 공격되는 것으로부터 TFSS 금속을 보호하기 위해 실란트로 작용한다. 텍스처링 및 패시베이션 공정 후, 실란트 물질은 백시트(예컨대 소다 라임 유리, SLG)의 미리 드릴링된 홀을 통해 개방된다. 이는 레이저 드릴링 또는 기계적 편침과 같은 무수히 많은 방법을 이용하여 수행될 수 있다. 이러한 홀이 한번 개방되면, 연속적 시드 금속층은 직접 라이팅 스팸, 예컨대 금속 잉크/페이스트 프린팅(스텐실 프린터, 스크린 프린터, 잉크젯 프린터 또는 에어로졸 제트 프린터를 이용하여), 또는 PVD (예컨대 플라즈마 스퍼터링), 또는 비전해 도금을 이용하여 증착된다. 그 후, 금속은 백시트의 상부 상에 p 및 n형 디퓨전 접촉 금속 사이에 분리 및 도금함으로써 두꺼워진다. 각종 공지의 도금 및 분리 공정은, 예컨대 스크린 프린트 레지스트, 그 후 금속의 블랭킷 도금, 그 후 레지스트를 에치백 및 언더라잉 박형 시드 금속층을 에칭하기 위해 마스크로서 도금된 금속을 사용하는 것을 포함하여 사용될 수 있다(may be used including, for example a screen print resist, then blanket plating of metal, then etch back the resist and use the plated metal as the mask to etch the underlying thin seed metal layer). 또는 및 바람직하게, 본 실시예에서, 패터닝된 전기적으로 도전성이 페이스트는, 적당한 페이스트(예컨대 구리 또는 니켈 또는 다른 적당한 컨덕터를 함유하는 페이스트)의 스크린 프린팅과 같이 백플레인 상의 직접 라이팅에 의해 형성된다. 그 후, 최종 금속화는 패터닝된 도금 시드 상에 직접 도금(예컨대 구리 도금)을 이용하여 완료된다(그 결과 희생 레지스트 및 레지스트 스트립 및 시드 에치백 공정의 필요를 제거함).

- [0036] 다른 실시예는 단일측 또는 드라이 전측 텍스처링 공정을 사용하여, 부분적으로 가공된 후측을 보고할 필요가

제거되고, 모든 접촉점은 백플레인의 부착 전 또는 전측의 가공 전에 미리 개방될 수 있다(레이저 드릴링 또는 기계적 드릴링 또는 편침을 이용하여).

[0037] 부분 후측 가공을 구비하는 도 1에 나타낸 바와 같이 백플레인의 "금속화를 갖는 백플레인" 서브 카테고리는, 영구적이고 통합된 금속화를 갖는 백플레인으로 특징화된다. "금속화를 갖는 백플레인"의 3가지 실시예는 도 1의 상세한 설명에 개시된다: 두문자어 OASIS, SLG-기반 (소다 라임 유리), 및 "비기판 측 상의 금속화"로 나타낸다. OASIS 및 SLG-기반의 두 가지 실시예에서, 백플레인-통합된 금속은 TFSS에 라미네이션/결합 동안 TFSS와 마주하지만, "비기판 측 상의 금속화"의 제3 실시예에서, 백플레인은 TFSS로부터 빗나간다.

[0038] OASIS 백플레인 실시예는 몇몇의 구성을 갖는다. 첫째, 이는 금속화층으로 작용하거나 하지 않을 수 있는 금속성 백플레이트로 이루어진다. 특정 실시예에서 부스바를 갖는 맞물려진 평거로 패터닝된 이러한 금속화층은, 예컨대 알루미늄박 또는 솔더링 가능한 알루미늄박으로 제조될 수 있다. 알루미늄박은, TFSS 상의 상호 접속의 제1 레벨에 상호 접속의 제2 레벨에 연결하는 도전적 바이어스의 더 나은 접착을 제공하기 위해 니켈 및 Sn(또는 Sn 솔더 합금)으로 미리 코팅 또는 미리 도금될 수 있다. 백플레이트는 Z68, EVA 또는 프리프레그 또는 다른 적당한 폴리머/플라스틱 커버 시트와 같은 적당한 보호층에 의해 상부 상에 화학적 공격으로부터 보호될 수 있다. 이러한 층은 상부로부터 모듈 연결 및 시험을 위한 접근을 제공하기 위해 개방된다. EVA 또는 Z68 같은 물질에 패터닝된 금속의 라미네이션 동안, 실질적인 평면도는 부착 물질의 흐름을 활용함으로써 완성되어야 하고, 최종 어셈블리는 상부 및 하부로부터 실질적으로 평면이어야 한다. 이 어셈블리의 평면 하부에서, 언더라잉 TFSS 금속에 AI박 금속의 연결은 전기적으로 도전성이 있는 바이어스를 제공하기 위해 캡을 갖는 유전체층에 선택적인 도전성 포스트 또는 바이어스(selective conductive posts or vias)를 이용하여 제조된다. 바람직한 실시예에서 도전성 바이어스(이하 도전성 에폭시 또는 CE) 및 유전체 물질(이하 유전체 에폭시 또는 DE)은 TFSS 또는 백플레인 상에 스크린 프린팅된다. CE 물질의 요건은 비용 효율성, 높은 도전성, 바람직한 실시예에서 스크린 프린팅이 가능할 수 있고, 오버라잉 백플레인 금속 및 언더라잉 TFSS 금속에 낮은 접촉 저항으로 부착되는 것을 포함한다. DE 물질 요건은 비용 효율성, 비전기 전도성 유전체이고, 바람직한 실시예에서 스크린 인쇄 가능할 수 있고, 오버라잉 백플레인 물질(금속 및 EVA 또는 Z68 유전체 봉합재)과 TFSS 금속 및 유전체로 이루어진 언더라잉 TFSS 물질에 잘 부착되는 것을 포함한다. 예컨대, OASIS 백플레인은 이하 카테고리의 선택에 근거한 무수히 많은 변형을 가질 수 있다:

[0039] a. 백플레인의 백플레이트 물질: 실시예는 알루미늄박, Sn으로 코팅된 알루미늄박, 또는 유리(소다 라임 유리를 포함하는 다양한 종류의 유리), 또는 다른 폴리머 물질을 포함한다. 필요 조건은 백플레이트 물질이 TFSS를 캐링하기 위해 백플레인에 강도 및 단단함을 제공해야 하는 것이다. 또한, 이후 열 공정 동안, 열팽창계수 불일치 때문에 TFSS에 크랙을 유도하지 않아야 한다.

[0040] b. 패터닝된 금속화 물질: 실시예는, 전기적으로 도전성인 바이어스에 낮은 접촉 저항 부착에 좋도록 만들기 위해 다른 금속과 코팅될 수 있는 알루미늄박을 포함한다. 다른 실시예에서, 이들은 미리 코팅된 알루미늄박일 수 있다. 일 실시예에서, 금속화 물질은 백플레이트 물질과 같을 수 있고, 또는 접착제를 이용하여 백플레이트 물질에 부착될 수 있다. 금속화의 두께는, 백플레이트 및 저항 요건과 동일한 경우에 강도에 의해 좌우된다.

[0041] c. 금속화의 패터닝 디자인: 옵션은 주로 숫자 및 사용되는 맞물려진 평거의 폭으로 이루어진다. 가장 넓은 폭 및 사용되는 최소 평거의 수는, 도전성 비아 포스트들 사이에(between conductive via posts) TFSS 금속선 상의 가장 큰 견딜 만한 저항(충전율(Fill Factor)의 감소 없이)에 의해 측정될 수 있다. 패턴 디자인의 영향을 받는 두번째 고려 사항은 금속박이 추가적인 기능을 갖는가이다. 예컨대, 이들은 예컨대 각각의 평거 내에 물리적으로 분리된 이들을 가짐으로써 또는 뱀과 같은 패턴으로 이들을 부분적으로 커팅함으로써 완성될 수 있는 부분적 스프링 같은 동작을 제공하도록 디자인될 수 있다: 그러나, 다양한 디자인이 가능하다. 스프링 같은 기능은 자유로이 팽창 및 수축하기 위해 금속박을 제공하는 쪽으로 설계되어, 이들은 열팽창계수의 불일치에 기인하여 CE 또는 TFSS를 파열시키지 않는다.

[0042] d. 유전체 및 도전성 연결 물질의 선택: 이러한 물질의 선택 기준은 이미 앞에서 논의되었다.

[0043] e. CE 및 DE 물질을 증착하는 방법: 바람직한 실시예에서 이들은 스크린 프린팅된다. 이러한 프린트는 TFSS 상에서 또는 백플레인 상에서일 수 있다.

[0044] f. 각각 대 평행 디자인: 백플레인 금속화(제2 레벨 금속 또는 M2)가 온-셀 TFSS 금속화(제1 레벨 금속 또는

M1)에 평행한지 또는 직각인지는 몇 가지 고려 사항에 의해 영향을 받는다. 직각 백플레인(M1에 직각 또는 크로스컷 또는 수직인 M2 평거)은, 백플레인 상의 선폭(또는 M2 평거의 폭)이 독립적일 수 있고, 일반적으로 구체적으로는 M1 평거보다 더 넓을 수 있다는 이점이 있다. 이는 이러한 금속화를 더 거칠고 M1보다 덜 염증한 얼라인먼트 요건을 가지고도록 도와준다. 그러나, 직각선이 짧지 않도록 하는 주의가 필요하다. 따라서, 유전체 물질은 우수한 적용 범위를 갖는다. 평행 디자인은 온-셀 TFSS 금속(M1) 디자인과 같도록 백플레인 금속(M2)의 퍼치 및 치수를 제한한다. 전지 상의 이러한 디자인은 일반적으로 상당히 타이트하고, 결국 감소된 베이스 저항, 감소된 전기적 세이딩 등을 포함하는 몇몇의 장치 고려 사항에 의해 영향을 받는다.

[0045] g. 모듈 연결을 위한 박 부스바의 접근 스팸(Access scheme of the foil busbars for the module connections): 예컨대 이는 보호층을 통해 스루홀을 통할 수 있거나(may be through through-holes through the protective layer), 알루미늄박이 백플레인의 상부를 둘러싸고, 예컨대 전측이 가공 동안 라미네이팅된 폴리머에 의해 보호되도록 둘러싸질 수 있고, 박으로의 접촉 접근이 공정의 마지막에 가능해진다.

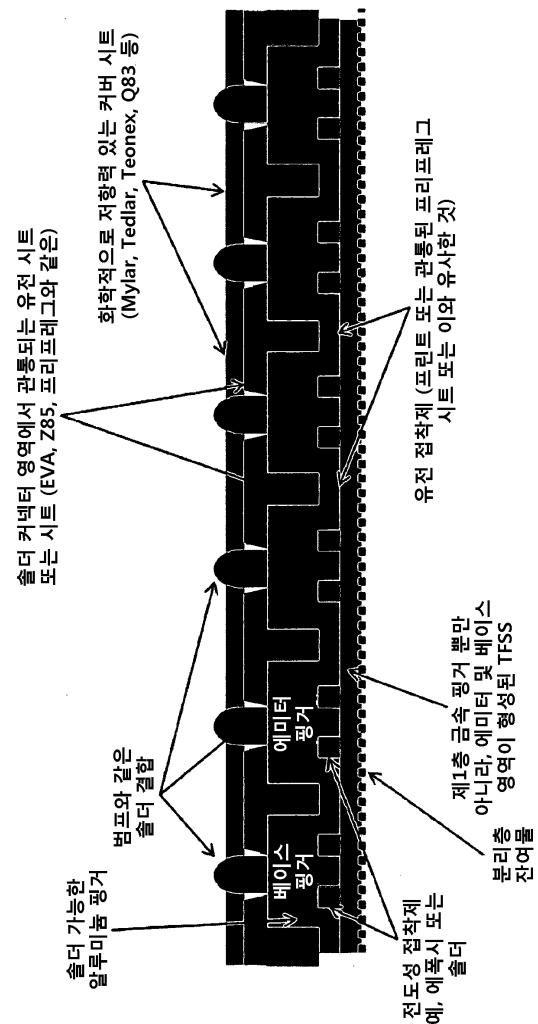

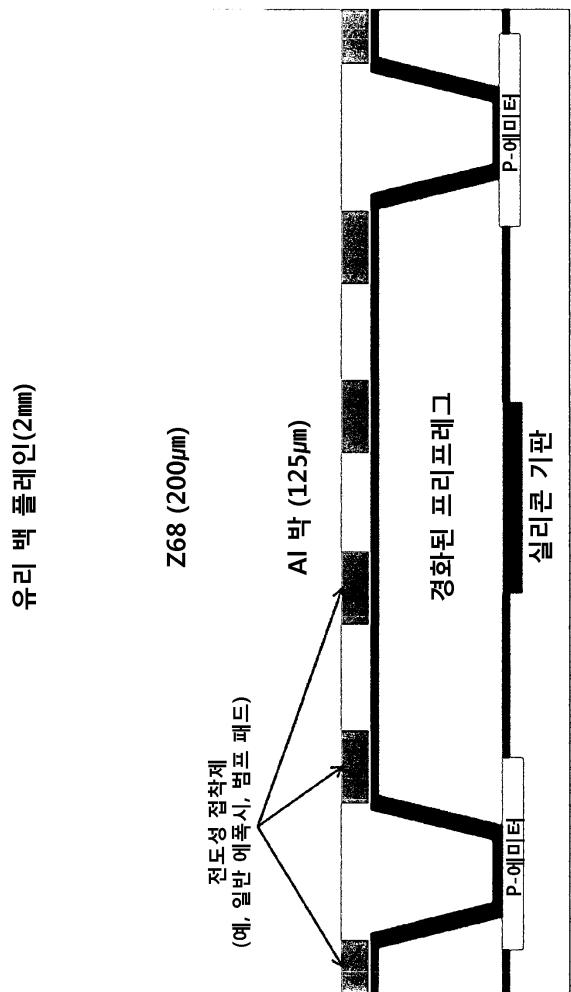

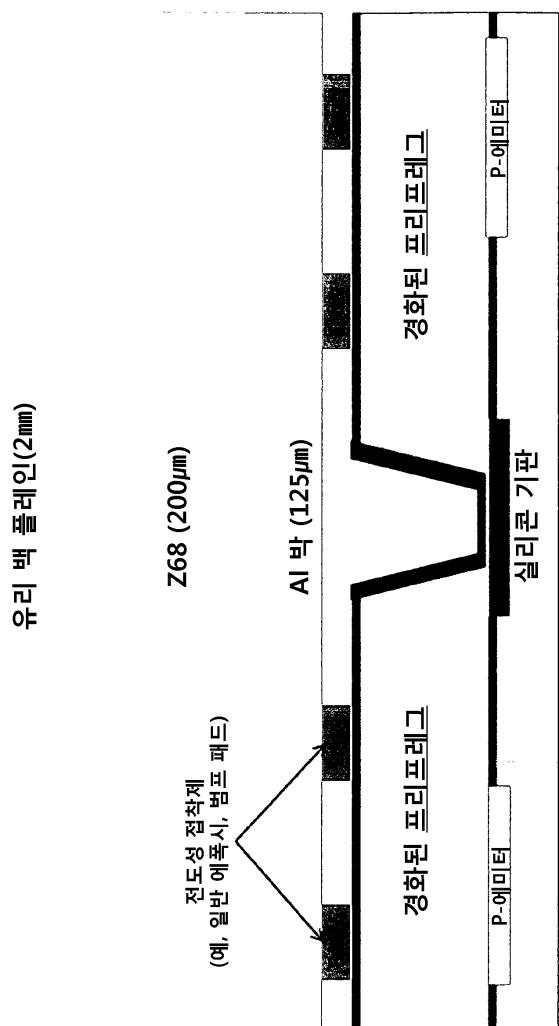

[0046] 도 2는 SLG-기반 후면 접촉 태양 전지 실시예의 단면도이다. 여기에 개시된 소다 라임 유리 또는 SLG 기반 실시예는 소위 OASIS 백플레인의 서브 카테고리이고, 여기서 백플레이트 물질은 도 2에 도시된 바와 같은 소다 라임 유리 시트이다. 이는 Z68 (또는 다른 적당한 봉합재) 물질을 이용하여 Sn-코팅된(또는 코팅된 솔더 합금) 알루미늄박 금속화에 부착된다. 알루미늄박은 유리 백플레인의 상부 상에 부스바를 갖도록 유리를 둘러싸고, 따라서 또한 측부 상에 보호적 z68로 밀봉된다. "비기판측 상의 금속화" 후면 접촉 태양 전지 실시예는 TFSS로부터 빗겨가는 측 상의 백플레인의 통합된 금속화를 갖는다.

[0047] 이러한 백플레인이 후면 접촉 태양 전지를 형성하기 위한 공정 흐름으로 맞춰질 수 있는 특정 실시예는 이하 제조 방법으로 설명된다.

#### TFSS 기반의 후면 접합/후면 접촉 태양 전지의 일반적인 구조체 및 방법

[0049] 상기 논의는, TFSS 후면 접합/후면 접촉 태양 전지에 높은 가공/제조 가능한 수율을 보증하기 위해 제1 및 제2 (백플레인) 캐리어와 관련되는 선택 및 조합과 관련된다. 이하 부분은 이러한 캐리어를 갖는 전체 TFSS 기반의 태양 전지에 대한 제조 방법 및 공정 흐름을 다룬다. 공정 흐름을 묘사하지만, 일부 경우에, 백플레인은 요약된다(abstracted). 이 요약은 상기 부분에 논의된 임의의 몇몇의 백플레인 옵션에 의해 대체될 수 있다. 또한, 특정 흐름을 갖는 백플레인의 조합은 템플레이트/다공성 실리콘(PS) 기반의 캐리어 1 또는 잉곳(또는 두꺼운 웨이퍼)/임플란트 기반의 캐리어 1가 사용될 수 있다. 이러한 두 가지 케이스에 관한 특정 흐름은 도시될 것이다. 도 1은 캐리어 1 및 캐리어 2의 관계 및 공정 흐름 옵션을 도시한다; 그러나, 도 1의 공정 흐름 또는 이하 공정 흐름은 예를 서술하는 것이고, 제한된 의미로 사용되어서는 안된다는 것에 주의해야 한다. 또한, 이러한 예시적 공정 흐름의 실시예는 임의의 두 개의 캐리어 1 옵션 및 무수히 많은 백플레인 옵션으로 사용될 수 있다고 이해되어야 한다. 이것에 공지된 예외는, 인시투 에미터 기반의 공정 흐름은 잉곳(또는 두꺼운 웨이퍼)/임플란트 캐리어 1 옵션이 사용될 수 없다는 것이다.

[0050] 엑스시투 대 인시투 에미터. 도 1에 도시된 공정 흐름은 공정 흐름의 두 가지 큰 카테고리로 더 분류될 수 있다: 에미터는 에피택셜 성장 공정의 통합부로서 형성되고, 대기압 화학 증기 증착(APCVD) 에피택셜 성장과 같은 기술을 이용하여 TFSS가 제조된 후 제조되는, 엑스시투 에미터. 또한, 캐리어 1 템플레이트/다공성 실리콘 옵션에 적당하고, TFSS의 실리콘 에피택셜 성장의 일부로 성장되는(그 결과에미터의 이후 형성의 필요성을 제거하는), 인시투 에미터. 본 발명은 엑스시투 에미터 형성을 이용하는 실시예에 초점을 맞춘다; 그러나, 인시투 에미터 기반의 흐름도 당업자에 의해 일부 예에 적용될 수 있다. 엑스시투 및 인시투 에미터의 상기 옵션에 관해서, 이하 고려 사항을 주의해야 한다.

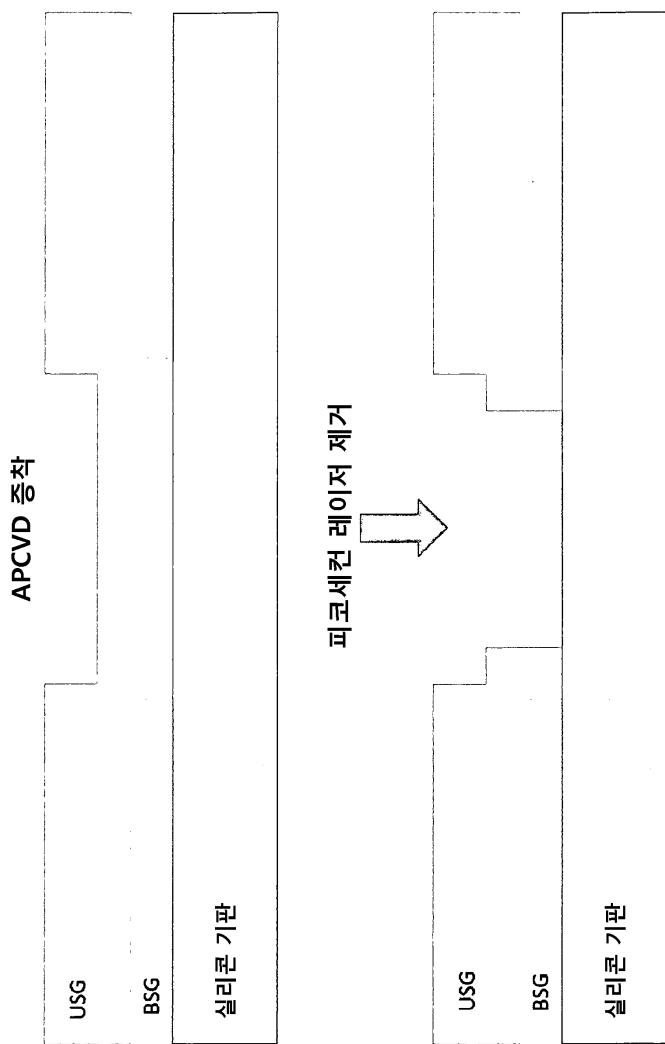

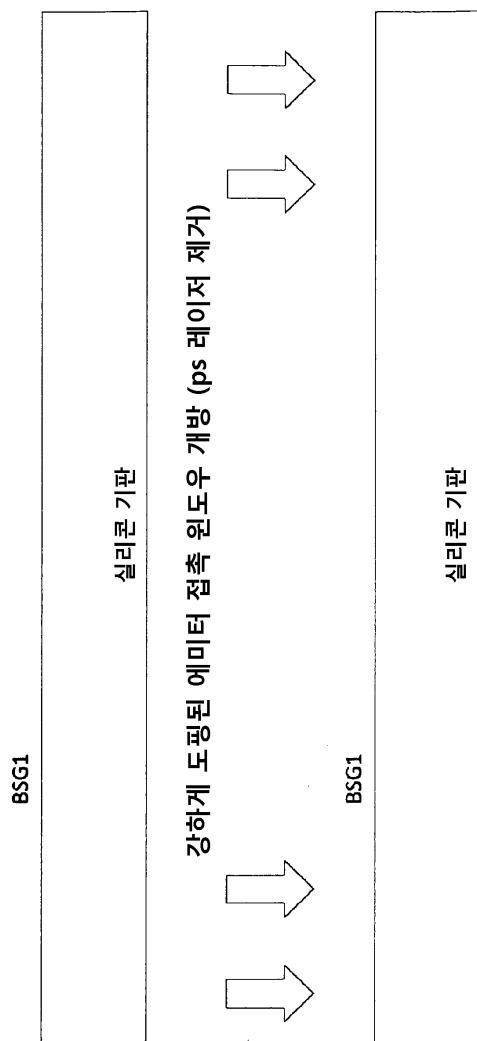

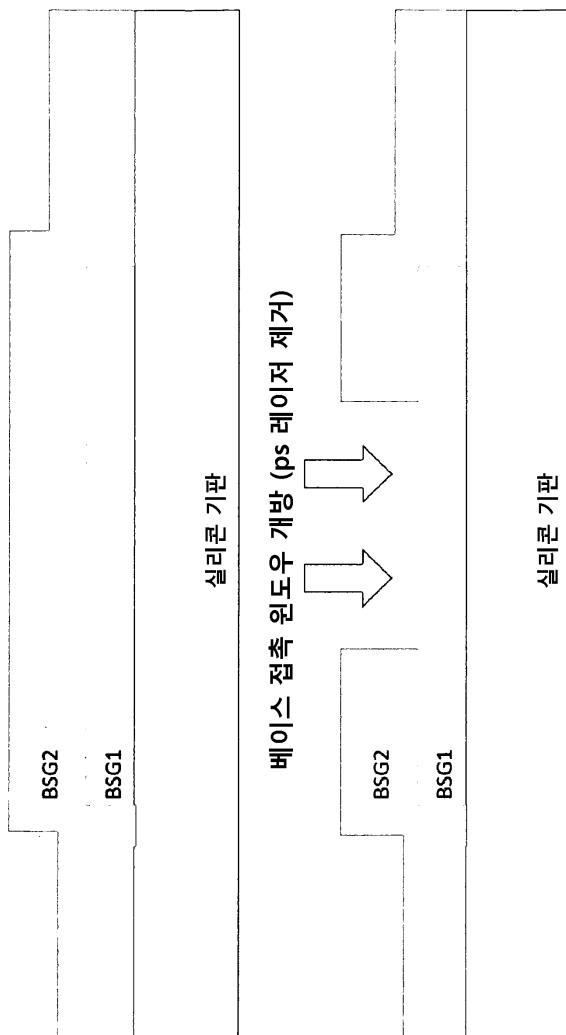

[0051] 1. 엑스시투 보론 도핑된 p+ 에미터는, 인시투 인 기반의 n형 에피택셜 기판이 에피택시를 이용하여 성장된 후에 형성된다. 패터닝된 엑스시투 에미터는 바람직하게는 APCVD BSG (보론과 함께 많이 도핑된 유리), BSG의 레이저 제거 후 에미터의 주입(drive-in)의 조합을 이용하여 형성된다.

[0052] 2. 엑스시투 에미터는, 인시투 에미터의 경우에 존재하는 태양 전지의 고체적 제조 동안 에피택셜 자동-도핑의

위험을 제거한다.

[0053] 3. 엑스시투 에미터는 에미터를 갖는 베이스를 제거하기 위해(또는 패터닝된 에미터 및 베이스 영역을 형성하기 위해서) 실리콘의 펄스 피코세컨 레이저 제거의 필요성을 제거한다.

[0054] 공정 흐름에 의해 공유된 일반적인 구조체 및 제조 방법의 성질. 최종 후면 접합/후면 접촉 태양 전지 구조체 및 제조 방법의 클래스의 특정 실시예는 이하에 설명된다. 구조체 및 방법은 이러한 특정 실시예에 제한되지 않는 것을 주의한다. 실시예의 더 넓은 범위는 당업자에 의해 상기 일반적인 캐리어 방법을 이용하여 유도될 것이다. 여기에 설명되는 특정 구조체 및 방법에 있어서, 확인된 공통된 성질은 이하를 포함한다:

[0055] 1. 개시되는 공정의 실시예에서의 공통된 구조적 성질:

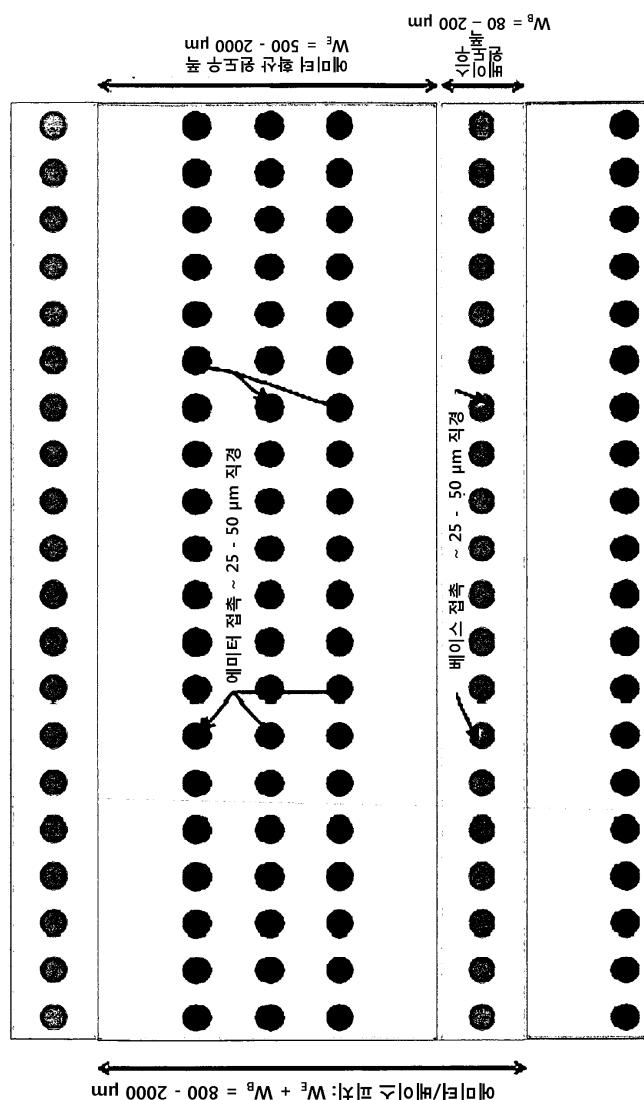

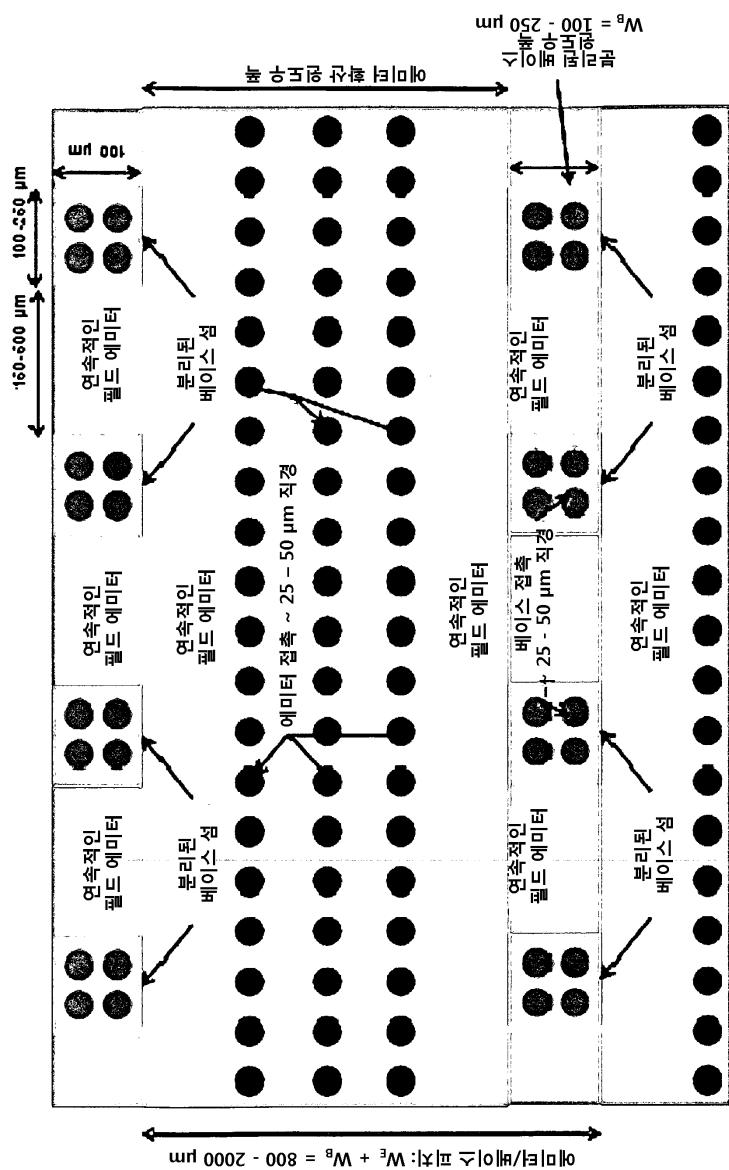

[0056] a. 약  $25\mu\text{m}$  (미크론) 내지  $50\mu\text{m}$  에피 두께. 더욱 일반적으로, 이 범위는  $5\mu\text{m}$  내지 약  $200\mu\text{m}$ 의 종래 두께까지일 수 있다.

[0057] b. 인 기반의 n형 베이스 도핑. 일반적으로, 이는 그것에 제한되지 않지만 보론 또는 갈륨 도핑에 의해 형성되는 p형 베이스 및 다른 n형 도펀트 물질(예컨대 비소 또는 안티몬 또는 인듐)일 수 있다.

[0058] 2. 개시되는 공정의 실시예에서의 공통적인 제조 방법적 성질:

[0059] a. 캐리어 1의 공정(두꺼운 웨이퍼/잉곳의 템플레이트)는 이하를 포함한다:

[0060] i. APCVD-기반의 공정은 바람직하게는 엑스시투 에미터를 형성하기 위해 로 어닐링과 함께 사용된다. 일반적으로 APCVD는 보론 실리케이트 유리(BSG) 및 인 실리케이트 유리 PSG(예컨대 비소 또는 안티몬 또는 인듐)를 갖는다. 그러나, APCVD PSG의 다른 치환체도 가능하고 논의된다.

[0061] ii. 상기 논의된 바와 같이, 템플레이트/다공성 실리콘(PS) 제 캐리어에 관련된 다른 실시예에서, 엑스시투 APCVD 에미터는 에피택셜 기반의 인시투 에미터에 의해 대체된 후 에미터 영역으로부터 베이스를 분리하기 위해 레이저 베이스 실리콘 제거될 수 있다.

[0062] iii. 에미터-베이스 분리, 에미터 및 베이스 접촉, 및 전지 상의 부스바 없는 AI 핑거를 위한 펄스 피코세컨 기반의 레이저 제거 패턴. 일반적인 경우, 패턴은 나노세컨(ns) 레이저와 같은 다른 레이저에 의해 정의될 수 있다. 또한, 전지 상의 AI(또는 Al-Si과 같은 알루미늄 합금) 핑거는 더 우수한 전지 성능에 도움이 되는 비트레이(arbitrary) 디자인일 수 있다. 이는 그것에 제한되지 않지만, 백플레인에서와 같은 온 셀 금속화 레벨 이상의 레벨에서 연결된 부스바를 갖는 미니셀(단일 기판 상에)을 포함한다.

[0063] iv. BSG 도펀트(및 존재한다면 PSG)의 드라이빙(driving) 및 활동 및 열 산화물 기반의 후면 패시베이션을 형성하는 것에 주의를 기울이는 선택적 산화를 이용하는 어닐링 단계. 바람직한 실시예에서, 이는 동일한 단계에서 수행되지만, 필요에 따라, 일반적으로 분리된 단계로 분리될 수 있다. 또한, 이는 튜브 기반 또는 인라인 열 가공(tube based or an in-line thermal processing furnace)에서 수행될 수 있다.

[0064] v. 플라즈마 스퍼터링 또는 증착(evaporation)과 같은 물리적 증기 증착(PVD)과 같은 진공 기반의 증착일 수 있는 금속 1 증착 단계, 그 후 상기 금속 1 층을 패터닝하기 위한 펄스 피코세컨 레이저 제거 단계와 같은 레이저 제거. 또는, 금속 1(M1) 증착 단계는 패터닝된 금속 잉크를 직접 증착 또는 가공된 TFSS 후측에 부착하기 위해 예컨대 잉크젯, 스크린 프린팅, 스텐실 프린팅 또는 에어로졸 제트 프린팅을 이용하여 직접 라이팅 프린팅을 수반한다.

[0065] vi. 캐리어 1이 템플레이트/다공성 실리콘(PS)인 경우에, 바람직한 가공 방법의 실시예는 이르게 TFSS 리프팅 또는 버블링의 위험 때문에 그 후(에피택셜 성장에서 캐리어 2에 부착된 TFSS의 리프트 오프 분리의 완료까지)에 그 위에 웨트 가공을 이용하지 않는 것이다. 그러나, 이는 제한된 의미로 해석되어서는 안된다. 개시된 주제는 실리케이트 유리와 같은 유전체 막을 제거하기 위해서 예컨대 HF 증기와 같은 증기를 에칭을 이용함으로써 웨트 가공 또는 세미 웨트 가공을 하는 것이 가능한 일반적인 경우를 포함한다.

[0066] vii. 캐리어 2에 부착된 때 캐리어 1로부터 TFSS의 분리 및 백플레인의 캐리어 1 상의 라미네이션.

[0067]

b. 캐리어 2 상의 가공 (백플레인)

[0068]

i. 가공된 다공성 실리콘층으로부터 발생하는 쿼시 단결정 실리콘 (QMS) 층을 제거하기 위한 후 분리 웨트 에칭 (Post-release wet etch). 또한 이는 전면을 텍스처링하기 위해 웨트 가공을 이용하는 것을 포함한다. 바람직한 실시예에서, 웨트 단계는 KOH 기반 (또는 NAOH 기반) 에칭 화학물질을 이용하는 단일 단계에서 수행된다. 그러나, 필요에 따라, 일반적으로 이들은 KOH 기반을 이용하는 둘다의 단계 또는 TMAH 기반 또는 분리된 KOH 기반 (또는 NAOH 기반) 화학물질을 이용하여 QMS 제거 단계를 이용하는 두개의 분리된 단계로 분리될 수 있다. 또한, KOH 또는 TMAH를 이용하는 텍스처링 없이 QMS 제거가 행해지는 가능성이 있다(KOH는 더 낮은 비용 이유로 유용할 수 있다). 또한, 웨트 텍스처링 대신에, 레이저 또는 플라즈마 가공에 기반된 드라이 텍스처링을 이용하거나, 또는 텍스처링을 하지 않고, 브로드 밴드 태양광에 효율적으로 커플링하기 위해 다른 방법을 이용한다- 이러한 "다른"의 의미는 유전체 입자 또는 은 또는 금 입자와 같은 분산된 나노 입자에 의존한다.

[0069]

ii. 텍스처링이 관련되는 경우에, 후 텍스처링된 표면 세정 공정은 후면 접합/후면 접촉 전지에 중요한 단계이다. 이러한 세정 단계는 세정 공정 후 고품질의 전면 패시베이션층의 형성을 가능하게 한다. 소위 RCA 세정과 같은 더욱 비싼 대안들이 사용될 수도 있지만, 이러한 목적을 위한 특정 세정 화학물질은 HF/HCl 화학물질 및/ 또는 오존처리된(ozonated) HF 화학물질에 기반될 수 있다. 또한, 희석된 HF 딥 후 텍스처링 세정 및 전 패시베이션을 수행하는 것은 전면 재조합 속도를 더 낮추는데 중요하다(Performing a diluted HF dip post texture clean and just before passivation is also critical to get lower front surface recombination velocities)(그 결과 더 고품질의 패시베이션). 텍스처링 및 후 텍스처링 세정 공정 동안 백플레인의 미미한 통합을 갖고, 언더라잉 추가적인 접착층을 갖는 프리프레그 또는 프리프레그와 같은 유기 백플레인 물질(organic backplane material)의 경우에, a-Si 또는 a-SiO<sub>x</sub> (비정질 실리콘 산화물) 플러스 실리콘 나이트라이드와 같은 층 또는 패시베이션층의 중착 전에 추가적인 공정 단계는, 본래의 산화물 및 백플레인 물질로부터 재중착되는 유기 잔여물을 제거하기 위해 라디칼(예컨대 수소 라디칼 및/또는 이온)의 스트림 또는 감압 또는 대기압 플라즈마를 이용하는 것이 개시된다. 이러한 공정은 바람직하게는 패시베이션 툴 (예컨대 PECVD 패시베이션)의 최초 단계에서 통합될 수 있거나 또는 그 대신에 오프라인에서 수행될 수 있다.

[0070]

c. 요구되는 디바이스 사양을 충족하는 저온 전면 패시베이션 및 ARC층. 일반적으로 이는 선택된 백플레인이 적합하면서, 가공에 적용할 수 있는 온도에서 증착되는 패시베이션층을 포함한다(this includes a passivation layer which is deposited at a temperature which can accommodate processing with the chosen backplane is adequate). 패시베이션의 허용 가능한 최대 온도는, TFSS의 크래킹 없이, 백플레인 물질의 열화 없이 이를 견디는 백플레인의 능력 및/또는 태양 전지 충전을 및 다른 신뢰성 관련 파라미터를 절충한 것에 따라 달라진다. 우수한 패시베이션은 PECVD SiN에 대해 약 150 °C 이상의 범위 온도에서 예측된다. 일 실시예는, 박형 비정질 실리콘의 PECVD (약 150 °C 내지 200 °C 범위의 기판 온도에서 PECVD를 이용하여 증착된) 후 저온 SiN 중착 (바람직하게는 비정질 실리콘 또는 비정질 실리콘 산화물로 동일한 온도에서)을 이용하는 것이다. 더욱 일반적으로, 우수한 패시베이션은, 전면으로부터 빗겨가는 소수 캐리어를 격퇴하는 전하의 극성 및 실리콘을 이용하여 매우 낮은 계면 전하포획 밀도를 가져야 한다. n형 물질에 있어서, 이런 임베딩된 전하는 안정한 포지티브 전하가 될 필요가 있다. 포밍 가스(forming gas), 중성, 또는 진공 또는 패시베이션 후 적당한 시점에서 다른 적당한 주변(ambient)에서 이후의 열적 어닐링은 패시베이션 품질을 개선하기 위해 유익할 수 있다. 이러한 열적 어닐링은 PECVD 패시베이션 온도 이상에서 수행될 수 있다(열 안정성 및 백플레인 물질의 CTE-매치에 따라 약 300 °C 까지).

[0071]

d. 백플레인 금속 및 이의 부스바에 접근. 이의 세부사항은 백플레인의 형태에 따라 달라진다. 백플레인이 통합된 또는 임베딩된 금속박 금속화를 갖는 경우(상기 논의된)에는, 선택은 미리 제조된 스루홀(a pre-made through hole)(웨트 가공 동안 커버될) 또는 랩 어라운드 부스바 개방부(a wrap around bus bar opening)(웨트 가공 동안 커버될)이다. 백플레인 금속화가 최종 가공 단계인 백플레인에 있어서는, 접근이 징점이 아니다.

[0072]

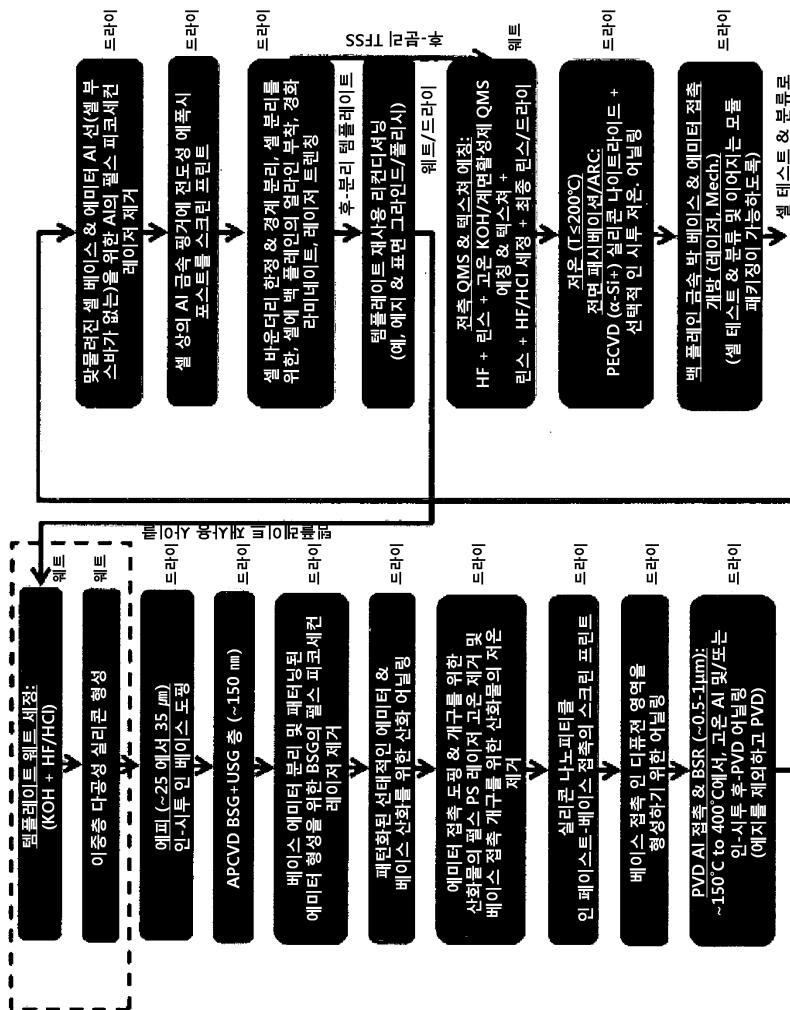

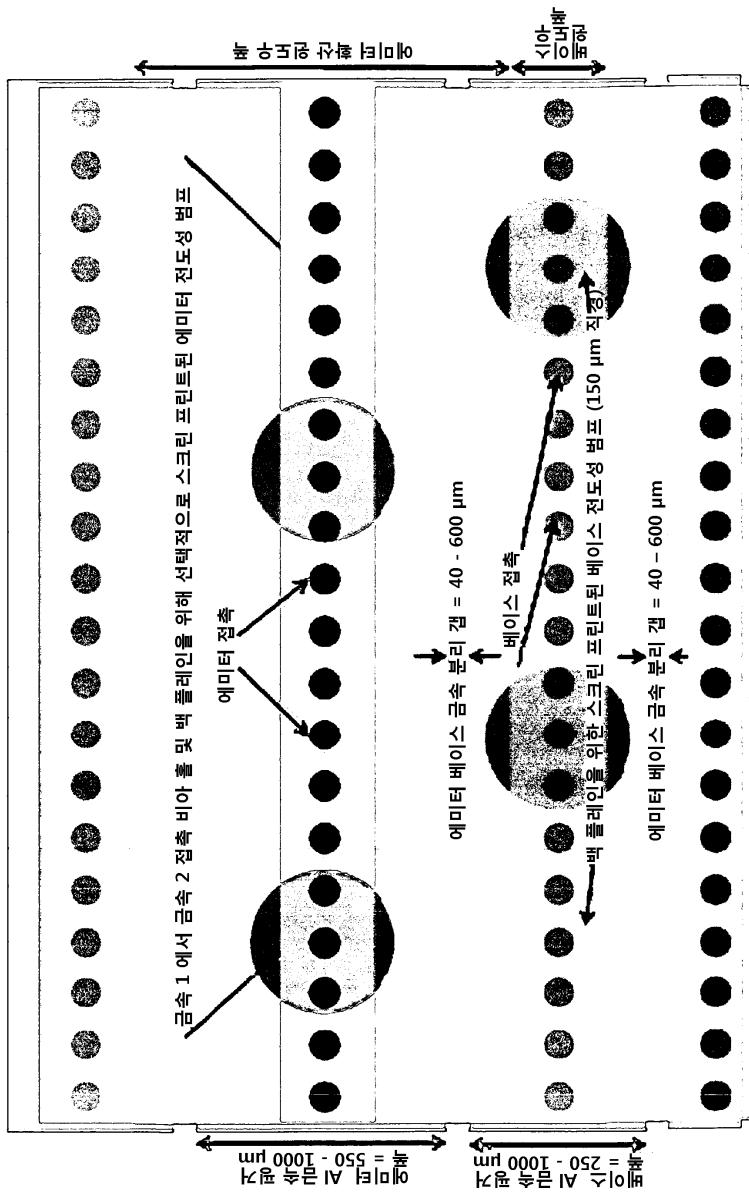

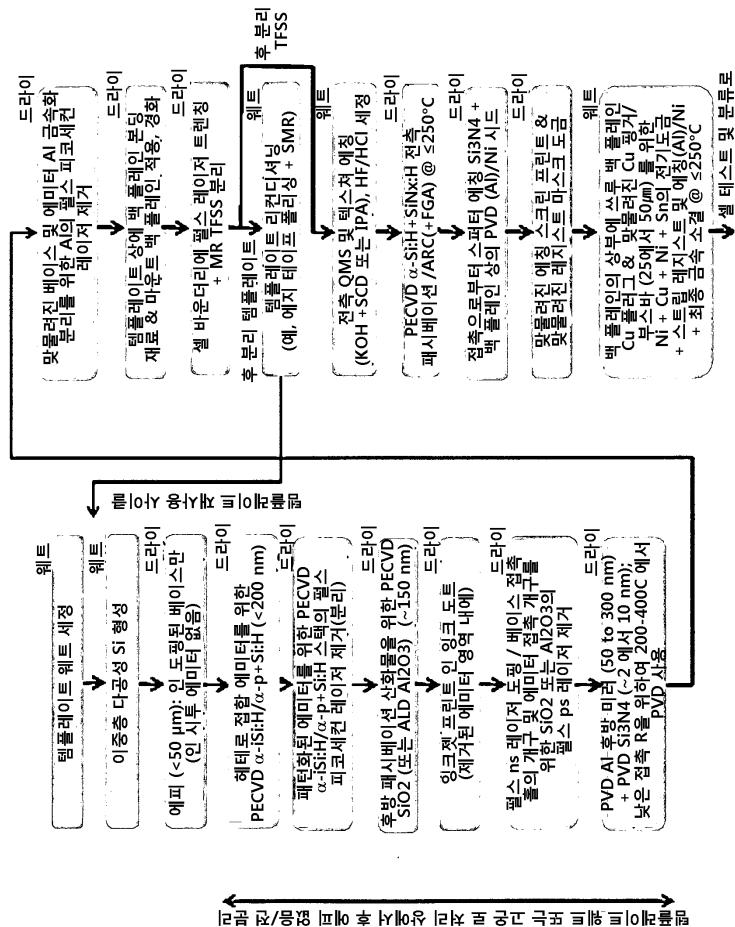

도 3은 개시된 주제에 따른 엑스시투 에미터 공정 흐름의 실시예를 도시한 도면이다. 이 공정 흐름은 베이스 접촉이 제조되는 방법에서 차이점에 의해 구별되는 4가지 카테고리 흐름 1 내지 4로 나뉜다. 도 3에 도시되는 흐름 전체는 본 발명에 설명되는 임의의 백플레인 옵션 및 벌크 웨이퍼 잉곳/임플란트 캐리어 1 또는 템플레이트/다공성 실리콘 캐리어 1이 사용될 수 있다.

- [0073] 흐름 옵션 1: 이 공정 흐름은 베이스 도핑을 제조하기 위해 APCVD PSG를 이용한다. PSG 층은 증착되고, 인은 배치로 어닐링 (batch furnace anneal)을 이용하여 또는 PSG 층의 펄스 나노세컨 레이저 고온 제거를 이용하여 드라이빙된다(driven in)(후자의 경우, 언더라잉 TFSS를 도핑하기 위해 그리고 베이스 접촉 개방부의 PSG 층을 제거하기 위해).

- [0074] 흐름 옵션 2: 이 공정 흐름은 스크린 프린팅된(또는 스텐실 프린팅된) 실리콘 나노입자 인 또는 잉크젯(또는 에어로졸 제트) 프린팅에 의해 적용되는 실리콘 나노입자 인 잉크를 이용한다.

- [0075] 흐름 옵션 3: 이 옵션은 잉크젯 프린팅에 의해 적용되는 인 잉크 또는 인 페이스트의 스크린 프린팅을 사용한다. 이는 그 후 도편트에 드라이빙하기 위해(to drive in) 배치로 장치에 열적 어닐링된다.

- [0076] 흐름 옵션 4: 이 공정은 개시 인 도편트 물질로서 인 옥시클로라이드 POC13을 이용한다(공정은 바람직하게는 POC13 튜브로에서 수행된다). 후 디퓨전 인 유리 웨트 에칭 또는 HF 증기 에칭을 필요로 한다.

- [0077] 도 3의 4가지 공정 흐름 옵션 카테고리의 서브카테고리가 이하에 설명된다.

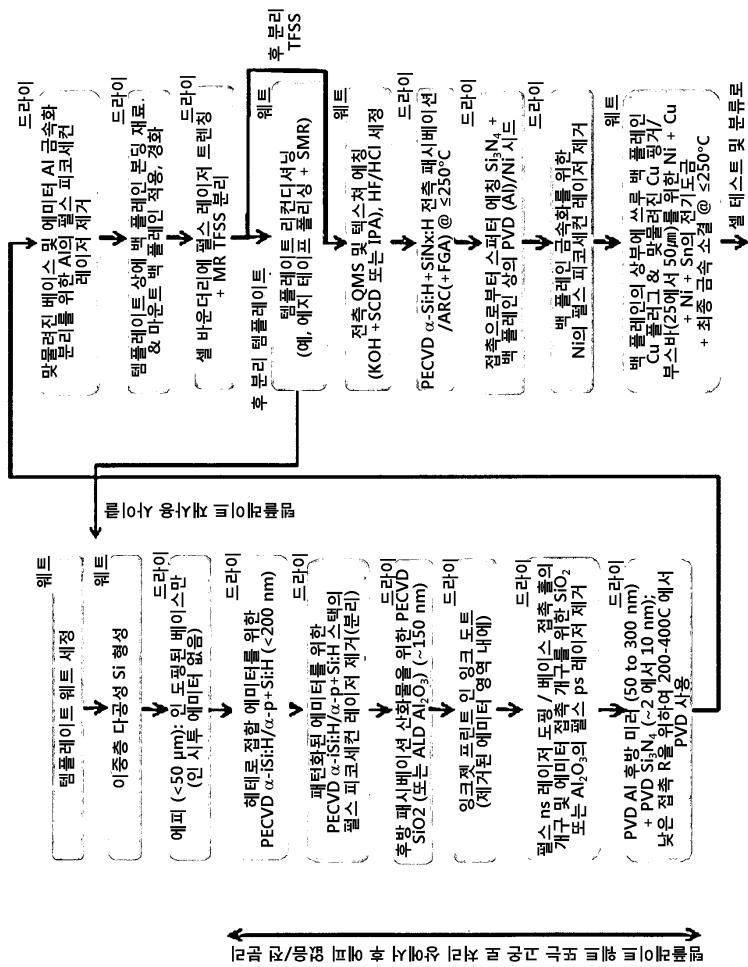

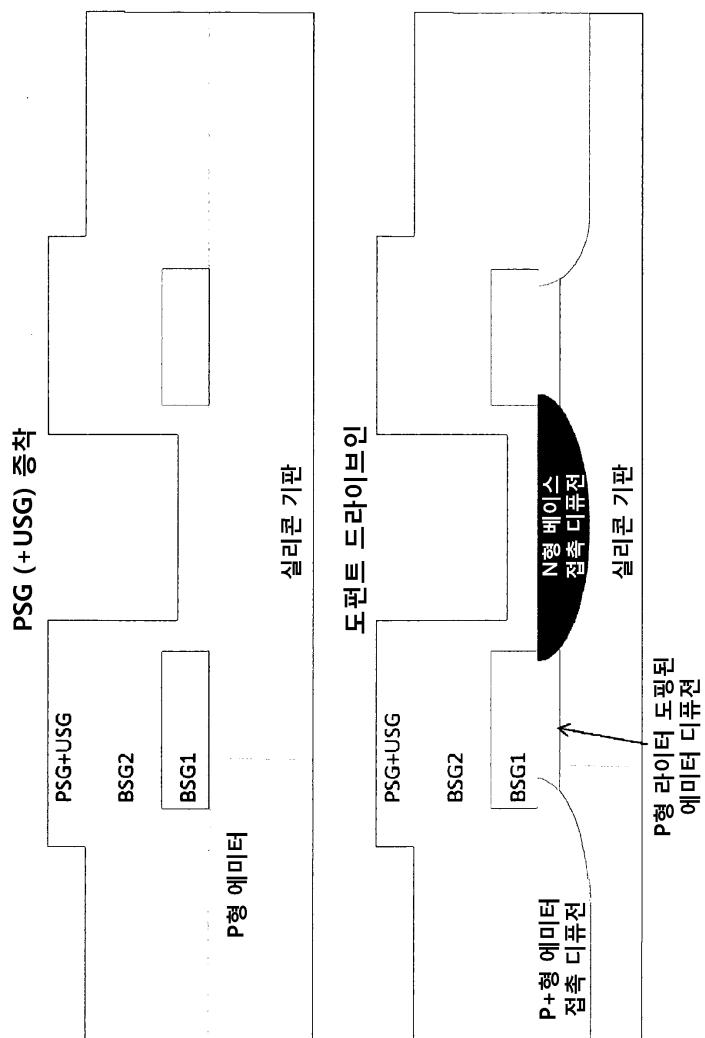

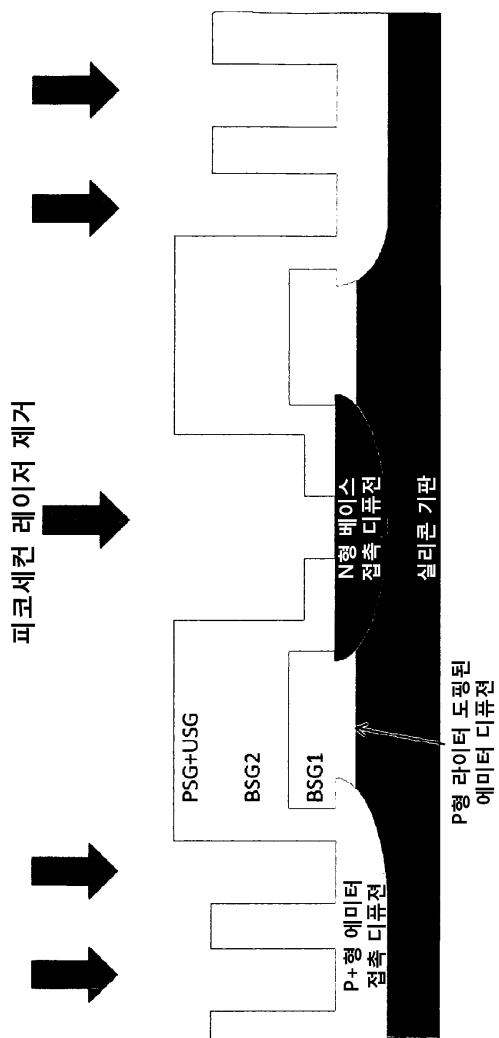

- [0078] **흐름 옵션 1: APCVD PSG 기반의 베이스 도핑.** 이러한 클래스에 두개의 서브 카테고리가 있다: a) 레이저를 이용하여 베이스 및 에미터 접촉을 드라이빙하기 위해(to drive)(또한 베이스 및 에미터 접촉 홀을 동시에 개방하기 위해) 펄스 ns 레이저 가공을 이용한 고온 제거(Hot ablation), b) 열적 어닐링이 베이스 접촉 디퓨전 영역을 제조하는(바람직하게는 펄스 ps 레이저 가공을 이용하는) 저온 제거(Cold ablation). 도 4는 2개의 캐리어를 갖는 박형 후면 접합/후면 접촉 태양 전지를 제조하기 위한 선택적 에미터를 이용하는(바람직하게는 펄스 ns 레이저 가공을 이용하는) 고온 레이저 제거를 이용하는 공정 흐름이다(도 3의 흐름 옵션 1A1에 대응함). 공정은 모 템플레이트 결정 실리콘 웨이퍼(mother template crystalline silicon wafer)의 세정을 시작한다. 일 실시예에서, 이는 200mm 직경, 200  $\mu\text{m}$  내지 1.2 mm 두께의 반도체 표준 웨이퍼일 수 있다. 다른 실시예에서, 이는 165mm 측 풀 스퀘어(side full square), 200  $\mu\text{m}$  내지 1.2 mm 두께의 결정 실리콘 웨이퍼일 수 있다. 템플레이트는, 예컨대 KOH, 및 HF, HCl 또는 이들의 조합 (HF/HCl)과 같은 산과 같은 화학물질, 및/또는 오존처리된 HF를 포함하는 화학물질을 이용하여 세정된다. 또한, 세정은 금속 및 유기 불순물의 세정에 알려진 다른 화학 세정을 이용하여 수행될 수 있다. 다른 예는 RCA 세정이다; 그러나, RCA 세정은 태양 전지 제조의 목적을 위해서는 더욱 비싸다. 세정 후 전기화학 에칭(바람직하게는 HF/IPA에서)을 이용하여 이중층 또는 다층 (적어도 2개의 다른 공극률) 다공성 실리콘의 형성이 이어진다. 형성된 제1층(또는 상부층)은 낮은 공극률의 층이다(예컨대 이는 그것에 제한되지 않지만 15-40% 범위의 공극률을 갖는 층일 수 있다). 이후 아래에 형성되어 템플레이트에 가까워지고 템플레이트로부터 더 낮은 공극률의 층을 분리하는, 더 높은 공극률을 갖는 제2층(매립 층)(예컨대 이는 그것에 제한되지 않지만 45-70% 범위의 공극률을 갖는 층일 수 있다)이다. 일반적으로 층이 이하를 포함하는 몇몇의 주요 요건을 가능하게 하는 한, 단층 또는 3층 또는 그레이드된 공극률의 다공성 실리콘과 같은 다른 배열 형태도 가능하다: 낮은 공극률 다공성 실리콘층의 상부 상에 우수한 품질의 에피택셜 실리콘층의 형성을 가능하게 하기 위한 우수한 상부 에피택셜 시드층, 템플레이트로부터 TFSS 리프트오프 분리를 위한 높은 공극률층의 온-디멘드(on-demand) 파괴에 기인한 믿을 만하고 높은 분리 수율, 온-템플레이트 가공 단계(on-template processing step)(바람직하게는 그것에 제한되지 않지만, TFSS 형성 후 리프트 오프 분리까지 전체-드라이 온-템플레이트(all-dry on-template) 가공 단계) 동안 템플레이트 캐리어로부터 TFSS의 너무 이른 분리 또는 베블링 없음. 다공성 실리콘 형성 공정 후 건조 단계, 그 후 수소 프리베이크 및 바람직하게는 약 5  $\mu\text{m}$  내지 약 50  $\mu\text{m}$ 의 두께 범위로 에피택셜 성장이 이어진다. 수소 프리베이크 및 에피택셜 성장 공정 둘다에는 바람직하게는, 프리베이크 조건의 선택인 성장 공장의 동일한 통합 부분에서 수행된다(are preferably performed in the same An integral part of the growth process is the selection of the pre-bake condition). 수소 프리베이크 공정 단계(바람직하게는 에피택셜 성장 리액터에서 인시투 프리베이크) 동안, 프리베이크는 본래의 산화물 및 다른 잠재적 표면 오염물질을 제거할뿐만 아니라, 실리콘의 고형상 디퓨전 및 리플로우를 야기하여 다공성 실리콘의 표면 기공은 낮은 공극률의 층의 표면에서 밀봉하고(낮은 공극률의 다공성

실리콘의 표면 에너지를 감소시킴으로써 야기되는 구동력에 기인한), 그 결과 고품질의 TFSS 층의 이후 에피택셜 성장을 위해 우수한 에피택셜 시드층을 제조한다. 이는, 결국 높은 소수 캐리어 수명을 갖는 고품질 인시투 도핑된 TFSS 층의 형성 및 더 우수한 에피택셜 성장을 가능하게 한다. 에피택셜 성장 공정은 그 후, 바람직하게는 인라인 대기압 CVD (APCVD) 리액터를 이용하여 BSG 증착이 이어진다. BSG 층은 결국 고온 언닐링을 이용하여 BSG로부터 언더라잉 TFSS로 붕소의 고온 디퓨전에 의해 에미터 영역을 형성하기 위해 보론 원(boron source)으로 작용한다. 150nm 두께가 도 4에 도시되지만, 이는 백 미터 및 에미터 도핑의 요건에 따라 조절될 수 있다. 실제는, BSG 두께는 약 50 nm 내지 250 nm의 범위일 수 있고, BSG 층은 산화물이 언도핑된 층(약 10 nm 내지 100 nm 범위의 언도핑된 유리 두께를 갖는)으로 캡핑될 수 있다. BSG 층 증착 후 BSG 층의 피코세컨(ps) 펄스 레이저 제거가 이어지고, 이러한 레이저 제거는 실리콘에서 정지되어 언더라잉 실리콘을 손상시키지 않는다(펄스 ns 레이저 제거와 비교하여 미미한 열-영향을 받은 영역). 제거된 영역은 결국 디바이스의 베이스 부분이 된다-에미터는 디퓨전되지 않을 것이고, 도핑된 베이스 접촉 영역은 노출될 것이다. 디바이스 디자인에 따라, 이러한 영역의 분율(베이스 개방부의 분획)은 약 3% 내지 약 20% 범위일 수 있다(대략 80% 내지 97% 범위의 에미터 영역 분율에 대응하는). 더 큰 에미터 영역의 분율은 더 높은 전지 효율에 바람직하고, 이는 펄스 ps 레이저 가공을 이용하는 것을 통해 가능하다. 매우 큰 개방부, 따라서 큰 분율의 베이스는 에미터를 얻기 위해 더 큰 거리를 이동해야 하는 소수 캐리어를 야기한다. 이는 전지 전환 효율을 떨어뜨리는 더 많은 재조합을 야기한다(전기적 세이딩으로도 알려져 있음). 개방부의 더 좁은 사이즈의 폭은, 이 영역 내에 베이스 디퓨전 및 접촉 영역을 얼라인 및 놓도록 함으로써(by being able to align and put) 제한된다. BSG의 레이저 제거는 그 후 선택적으로 언도핑된 실리케이트 유리 (USG)의 APCVD, 그 후 PSG/USG, 따라서 3층의 형성이 이어진다. 그 두께에 따라 달라지는 언더라잉 USG 층은 어닐링 동안 인 디퓨전의 범위를 통제한다. 더 두꺼운 USG 층은 인 디퓨전을 방지할 것이고, 후면 전계(이후, BSF) 없이 진정한 분리된 접합을 야기할 것이다(에미터 및 베이스 디퓨전 영역은 접촉하지 않음). BSF 층은 디바이스의 개방 서킷 전압(Voc)의 증가를 도울 수 있다. 언더라잉 USG 층이 얇은(또는 전혀 증착되지 않은) 경우, 일부 인은 열적 어닐링 단계 동안 TFSS 표면 영역에 디퓨전된다. 이는, 결국 소위 인접한(abutted) 접합 전지 구조체 뿐만 아니라 BSF 형성을 야기한다. PSG 및 BSG 층에서 각각의 인 및 보론의 농도는, 에미터 및 베이스 영역에서 적당한 도핑 농도를 얻기 위해 제어된다. 전지 디자인 요건에 따라, BSG 및 PSG 층에서 이러한 도편트 농도는 약 2% 내지 7% 범위일 수 있다. USG/PSG/USG 가 증착된 후(펄스 ps 레이저 제거 직후 페터닝 공정 후), 디바이스는, 질소(또는 불활성 가스) 주변에서 불활성 어닐링 및 선택적 산화 어닐링, 그 후 선택적으로 저온 인시투 게더링 어닐링(바람직하게는 철과 같은 금속 성 오염물질을 모으기 위해 약 550 °C 내지 650 °C의 온도 범위에서 수행됨), 선택적으로 저온 인시투 포밍 가스 어닐링(약 400 °C 내지 500 °C의 온도 범위에서)일 수 있는 다기능으로 어닐링 단계를 통해 가공된다. 동일한 다기능로 어닐링 공정 레시피에서 이러한 인시투 어닐링 단계의 조건을 최적화하여, 우수한 품질의 후면 산화물 패시베이션, 바람직한 인 및 보론 도편트 드라이브인(drive-ins) 및 도편트 활성, 금속 불순물의 게더링 및 후측 패시베이션 특성의 개선을 단일 툴로 완성시키는 것이 목표이다. 또한, 결국 그 표면으로부터 에미터 소수 캐리어, 전자를 격퇴하는 네거티브 전하의 도입을 가능하게 하고, 그 이유로 매우 우수한 표면 패시베이션을 제공할 수 있는 경향이 있기 때문에, 인접한 후면에 알루미늄 산화물 Al203의 박층을 갖는 것은 유용할 수 있다. 이러한 Al203 층은 BSG 층의 증착에 사용되는 동일한 APCVD 툴의 제1단계로서 및 인시투로 증착될 수 있다. Al203을 도입하는 흐름은 본 명세서의 이하에 개시된다.

[0079] 도 4에 도시된 바와 같이, 어닐링 단계 후 개방 접촉에 피코세컨 펄스 레이저 제거가 이어진다(펄스 ns 레이저와 같은 다른 형태의 레이저도 사용될 수 있다). 그러나, 고온 레이저 제거라 불리는 특별한 레이저 제거 공정은, 에미터 및 베이스의 접촉을 개방할 뿐만 아니라 동시에 접촉 개방 영역에 TFSS 실리콘 표면으로 각각의 도편트를 빠르게 드라이빙하는(driving in) 이중의 역할을 수행하는데 사용될 수 있다. 따라서, 베이스 접촉은 실리콘으로 PSG에서 드라이빙되는(driven from) 인을 갖는 USG/PSG 층을 통해 형성되지만, 에미터 접촉은 USG/PSG/USG/BSG 스택을 통해 형성되고, 보론이 드라이빙된다(is driven in)(Al203 초박층만을 갖는 실리콘으로부터 분리되거나 실리콘과 접촉되는 BSG 층으로부터). 고온 제거 가공은, 금속이 결국 실리콘과 접촉하는 곳 아래의 높게 도핑된 n+ 및 p+ 접촉 영역을 형성할 수 있다(베이스 및 에미터 접촉 금속화를 위해). 이는 접촉 저항을 감소시키고, 금속 접촉에서 재조합 속도를 감소시키는데 바람직하다. 따라서, 접촉 영역으로부터 멀리, 패시베이션 하에 더욱 가볍게 도핑된 에미터 영역(더 높은 전지 효율에 바람직한)과 같은 가볍게 도핑된 영역(어닐링에 의해 영향을 받은)을 유지하면서, 국부적으로 높은 도편트 영역이 생성될 수 있다. 이는 접촉으로부터 떨어진 접촉에 가까운 영역에서 도핑 농도의 독립된 최적화를 보증하고, 결국 더 높은 Voc, 우수한 적의 양자 효율 및 더 높은 전체 전지 효율에 유용한 선택적인 에미터 및 베이스의 효율적인 형성을 가능하게 한다.

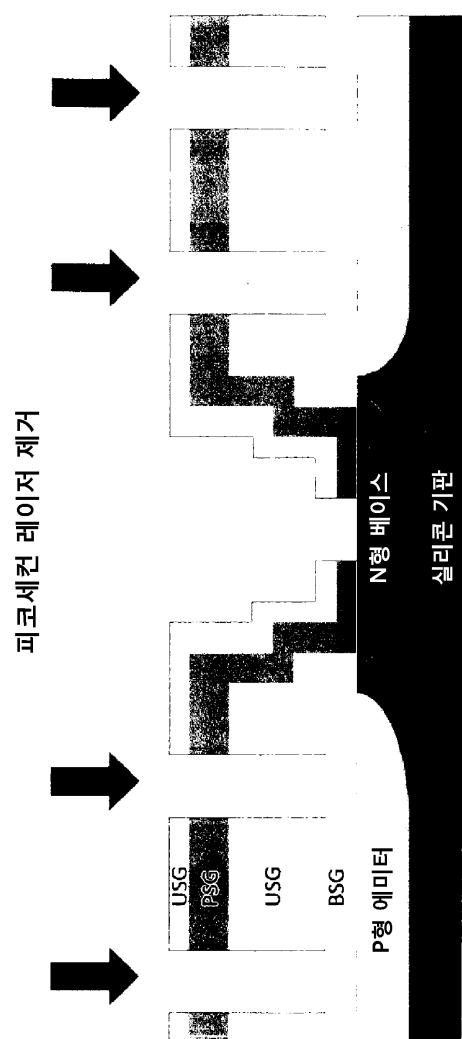

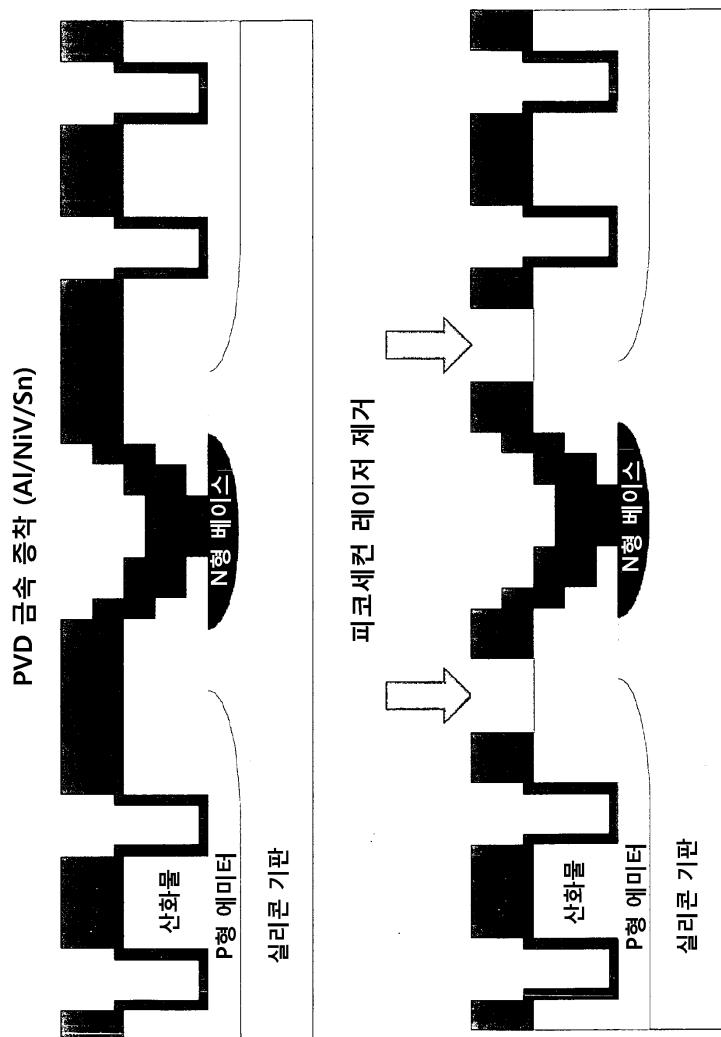

[0080]

레이저 고온 제거 후 박형 알루미늄 또는 Al-Si 층의 물리적 증기 증착(PVD) 기반 증착(예컨대 플라즈마 스퍼터링 또는 증착(evaporation)을 이용하여)에 의한 금속 1에 대한 일 실시예가 이어진다. 이러한 알루미늄(Al) 층은 후측 패시베이션 유전체 스택과 함께 후면 리플렉터 (BSR)의 기능으로 작용할 뿐만 아니라, 디바이스 베이스 및 에미터 영역과 우수한 전기적 접촉을 제공하는데 중요하다. 도핑된 에미터 및 베이스 접촉 영역 둘다에 대한 Al (또는 Si로 도핑된 AI) PVD의 접촉 저항은 중요하다. 또한, PVD 공정은 고온 PVD (전지 기판이 약 150 °C 내지 450 °C 범위의 온도까지 가열되면서 AI 층을 증착)로 수행될 수 있고, 또는 필요에 따라 150 °C 내지 450 °C에서 후 PVD 어닐링이 수행될 수 있다. 이는, 우수한 접촉 저항(그 결과, 더 높은 충전율)을 보증하고, 게다가 APCVD 층으로부터 알루미늄(Al 어닐링) 및 H<sub>2</sub>의 존재 하에 우수한 패시베이션을 이용하는 것이다(후측 패시베이션을 개선하고 전지 Voc를 개선하도록 포밍 가스 어닐링을 효율적으로 수행함). 이어서, 다른 PVD 금속층은 접착성, 반사성 요건 및 레이저 금속 분리 요건의 필요에 따라 증착될 수 있다. 일 해석에 있어서, NiV (또는 Ni) 및 Sn의 조합 역시 AI의 스퍼터 증착 후 PVD 및 인시튜를 이용하여 AI의 상부 상에 제2 및 제3층으로 스퍼터링될 수 있다. Sn의 상부층을 갖는 이 금속 스택의 기능은, 백플레인 금속 또는 M2의 접착이 절충되지 않는 것을 보증할 것이다(그 결과, 전지 충전율 및 장기간 신뢰성을 개선한다). 이 스택의 변경에 있어서, Al/NiV/Sn 스택은 Sn과 NiV 사이에 어닐링과 같은 솔더를 제공하기 위해 Sn의 용융점 이하에서 어닐링될 수 있다. 이어서, 펄스 피코세컨 레이저가 베이스 및 에미터 금속 영역을 분리 및 패터닝하기 위해 사용된다. 일반적인 디자인은 맞물려진 평거 디자인이다. 바람직한 실시예에서, 부스바 없이 맞물려진 평거만이 M1의 전지에 정의되었다(defined). 이는 부스바 하에 전기적 세이딩을 최소화하고, 전지 효능을 증가시킨다. 그러나, 부스바를 갖는 다른 실시예 및 미니-전지와 같은 다른 디자인은, 금속 레이저 공정으로 정의될 수 있다. 일반적으로, 에미터/베이스 선의 피치를 포함하는 특정 치수는, 그것에 제한되지 않지만 베이스 및 에미터 디퓨전 저항을 포함하는 몇몇의 디바이스 디자인 고려 사항에 의해 영향을 받는다. PVD는 진공 스퍼터링, 진공 증착, 이온 범 증착(IBD), 대기 아크 스프레이 및 다른 열적 물리 증기 코팅법을 수반할 수 있다. 다른 그리고 덜 바람직한 실시예에서, 레지스트의 스크린 프린팅 후 에칭도 베이스 및 에미터 패턴을 분리하기 위해 사용될 수 있다. 그러나, 템플레이트 상에 웨트 가공의 수행에 기인한 이러한 접근(금속 에칭 및 레지스트 스트리핑 웨트 단계를 위한)에 위험이 있다.

[0081]

금속화 공정의 다른 변경에 있어서, PVD 금속을 이용하는 것(스퍼터링, 증착 등과 같은 진공 기술을 포함하는) 대신에, 일반적인 금속 스크린 프린팅 접근법이 사용될 수 있다. 이러한 접근법은, 전지가 진공일 때 다공성 실리콘으로부터 박리 압력에 기인하여 모 템플레이트로부터 이르게 예피 기판을 제거하는 위험이 존재하고, 비싼 경향이 있는 진공 공정을 이용하지 않는 이점이 있다. 금속 스크린 인쇄의 실시예에서, 일반적으로 베이스 및 에미터 금속은 스크린 프린팅되고(이는 단일 알루미늄 페이스트 물질을 이용하는 단일 스크린 프린트 공정일 수 있다), 에미터 및 베이스 디퓨전 영역에 금속화 접촉을 제조하기 위해 발화되고(fired), 여기서 베이스 및 에미터 디퓨전이 몇몇의 가능한 기술을 이용하여 생성되고, 이들 중 하나는 상기 기재된 것이고, 몇몇의 다른 것들은 이후에 설명될 것이다. 공정 흐름의 나머지는 유사하다. 스크린 프린팅된 금속 또는 금속들은 함께 발화되거나(co-fired) 순차적으로 발화될 수 있고, 베이스 및 에미터에 동일하거나 다를 수 있다. 또한, 스크린 프린팅된 금속은 융해(fritted), 약하게 융해, 또는 융해되지 않을 수 있다(frit-less)(예컨대 적합한 융해되지 않은 알루미늄 페이스트). 이 공정의 특정 실시예는 동일한 공정 단계를 이용하여 함께 발화 및 에미터 및 베이스 상에 융해되지 않은 AI 금속 페이스트를 스크린 프린팅하는 것을 수반할 수 있다. M1 금속 패턴은 언더레이징 전지 디자인에 따라 달라진다; 그러나 일반적으로 TFSS의 마이크로크랙 형성의 위험을 감소시키고, 웨이퍼 레벨 스트레스를 감소시키기 위해 세그먼트화된 금속선을 포함할 수 있다. 이 공정의 다른 실시예는, 베이스 접촉에 AI을 스크린 프린팅 및 발화하면서, 인 접촉에 Ag를 스크린 프린팅 및 발화하는 것을 수반할 수 있다. 이러한 스크린 인쇄된 선 또는 평거는 계속적이거나 세그먼트화될 수 있다. 이 해석에 있어서, 베이스 상에 세그먼트화되어 있으면, PSG는 베이스 영역에 선택적으로 증착되어, 따라서 베이스 접촉 도핑의 포켓을 형성할 수 있다. 이어서, Ag 금속은, 베이스 포켓 내에 접촉을 생성하기 위해 도핑 원(doping sources) (본 경우에 PSG)을 통해 발화될 수 있다. 이러한 접근법은 매우 더 작은 베이스 접촉 소수 캐리어 재조합을 보증하여, 태양 전지의 Voc 및 Jsc을 개선함으로써 효율 이점을 가질 수 있다. 또한, 레이저 공정을 이용하여 베이스 접촉을 개방할 필요를 제거한다. 이러한 세그먼트화된 금속 디자인은, 백플레인의 융통성 있음 때문에 가능하다. 백플레인은 백플레인 층에 이를 합치면서 전류의 수직 끌어당김을 가능하게 한다(allows a vertical draw of current). Ag 금속 분할된 부분(다른 디바이스의 제한에 영향을 줄 수 있는)과 동일한 타이트 피치에서 백플

레인 레벨 연결을 제공하는 것에 어려움이 있는 경우, 연속 금속(continuous metal)은 에미터 금속이 프린팅되는 동시에 Ag 세그먼트의 상부에 스크린 프린팅(예컨대 Al) 될 수 있다. 이러한 금속(Al)이 금속 페이스트의 옳은 선택을 이용하여 방지될 수 있는 PSG 산화물을 통과시키지 않는다는 것을 보증하기 위해 주의를 기울여야 한다.

[0082] 공정 흐름의 다른 변형을 다루고 있는 이하 부분에 분명하게 논의되지 않지만, 직접 라이팅 금속 스크린 프린팅된 옵션은 이후 논의되는 공정 흐름의 PVD 금속 옵션 대신에 사용될 수 있는 것으로 이해된다.

[0083] 도 4에 도시되는 특정 실시예에서, 다음 단계는 전지 상의 패터닝된 금속 선에 도전성 물질(예컨대 에폭시 물질)을 스크린 프린트하는 것이다. 필요에 따라, 유전체 접착층은 단락(shunting)으로부터 전지를 보호하기 위해 프린팅될 수도 있다. 이는 필요에 따라, 도전성 접착제와 관련되는 이어서 논의되는 공정 흐름 전체에 대한 옵션이 되는 것으로 이해된다(공정 흐름 도에 명확히 도시하지 않지만). 이후 금속선에 백플레이인의 얼라인 먼트, 부착 및 라미네이션이 이어진다. 분리된 실시예에서, 도전성 및/또는 유전체 물질의 스크린 프린트는 백플레이인 금속 상에서 수행될 수 있다. 이어서, 도전성 물질을 갖는 백플레이인 어셈블리는 템플레이트 상의 금속 선에 얼라인 및 부착될 수 있다. 백플레이인 상에 도전성 에폭시를 프린팅하는 이점은, 템플레이트 상에 완전한 접촉 프리 가공(complete contact free processing)을 보증하고, 기계적 수율을 증가시키는, 템플레이트 상의 스크린 프린트 단계가 없다는 것이다. 얼라인먼트가 더욱 염중해지는 시도이다.

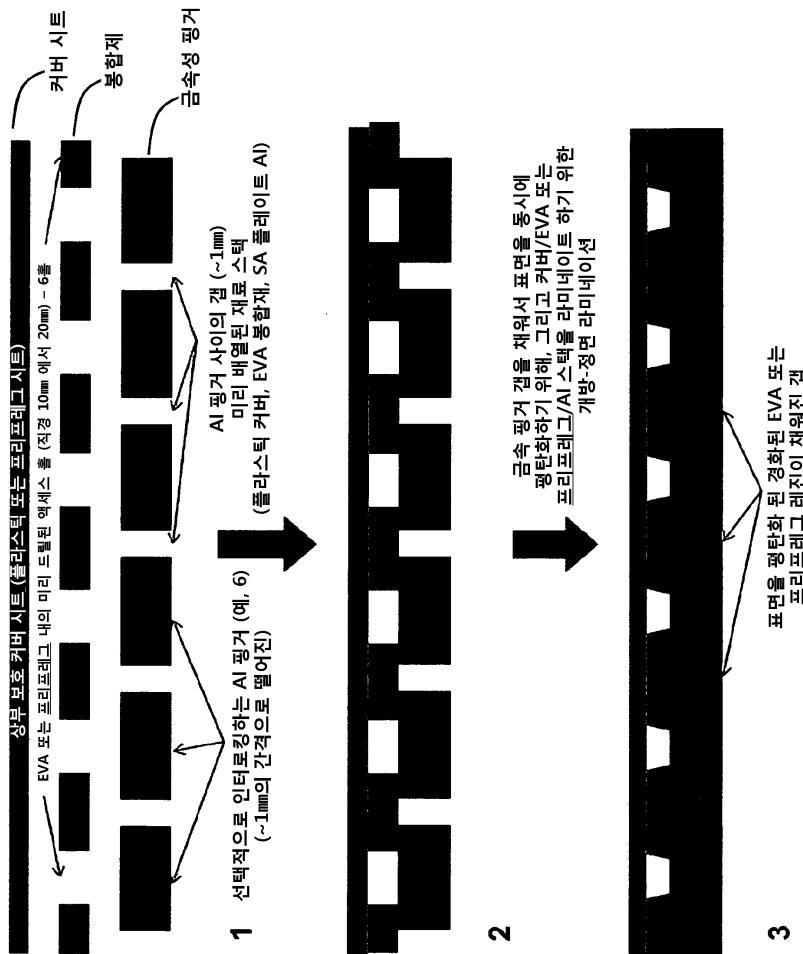

[0084] 또한, 백플레이인의 몇몇의 형태가 앞선 부분에 논의되었지만, 2가지 실시예가 다음과 같이 설명된다:

a. 페이스 투 페이스 결합(Face to Face Bond): 바람직하게는 50  $\mu\text{m}$  내지 300  $\mu\text{m}$  두께의 패터닝된 Al 박으로 제조되는 두꺼운 상호 접속 스택은, 저항 손실 없이 비스듬히 전기 전류를 전도하는 것을 돋는다. 도전성 박은, 예컨대 Z68에 제한되지 않지만 PV 자격을 갖춘, 준수한 봉합재 물질을 이용하는 유리 또는 플라스틱일 수 있는 백플레이인에 부착된다. Al 박, Z68, 및 백플레이인 물질(예컨대 유리 또는 플라스틱)은 백플레이인 어셈블리라 한다. 어셈블리는 상기 도전성 에폭시를 이용하여 템플레이트에 부착되어, 맞물려진 미리 패터닝(pre-patterned) 박 패턴은 템플레이트 상에 거꾸로 부착한다. 이하 두개의 배열 형태에서, Al 박 패턴의 치수는 다를 수 있다. 첫번째 배열 형태에서, Al 박의 선은 템플레이트 상의 패터닝된 선에 평행이다. 두번째 배열 형태에서, 백플레이인 Al 선은 템플레이트 상의 금속선에 수직이다. 수직의 경우에, 에미터 및 베이스 선의 단락을 방지하기 위해서, 다른 템플레이트 금속선은 장기판 교차점 패턴으로 백플레이인 박의 선을 오버러닝하도록 접촉을 만든다. 수직의 배열 형태는, 백플레이인 선 또는 평거(M2 평거)를 더 넓게 숫자가 적게 하여, 그 제조를 조절가능하게 하고, 그 비용을 감소시킬 수 있어 유용할 수 있다. 평행선은 결국 디바이스 디자인에 의해 제한되는 온-템플레이트 금속선의 피치/치수에 따라야 한다. 박형 전지 케이스에서, 이러한 피치는 박형 전지용 베이스의 높은 시트 저항 때문에 더 제한된다. 몇몇의 주의 사항은, 교차 접합에서 수직선들 사이의 단락이 없고, M1에 접촉이 없는 것이 바람직한 것을 보증하도록 제안된다. 이는 라미네이션 동안 Al 박 아래에 Z68 또는 다른 적합한 유전체 봉합재 물질을 흐르게 함으로써 보증될 수 있다. 흐름은 Al 박이 천공되어 있는 경우에 강화될 수 있다. 각각 배열 형태를 이용하여 단락의 위험을 방지하기 위한 다른 방법은 네거티브 장기판 패턴으로 유전체(비도전성) 포스트(post)를 더미 프린팅(dummy print)하는 것이다. 이는 접촉이 바람직하지 않은 교차점에서, Al 박을 오버러닝하는 것이 비전도성 포스트(non-conductive posts)에 의해 지지되고, 결과적으로 온-템플레이트 금속선을 터치하기 위해 치지지 않는(does not sag)다는 것을 보증한다. 전류는 여전히 거꾸로된 측으로부터 백플레이인의 상부까지 끌어질 필요가 있다. 이하는 이의 두 가지 일반적인 도식이다: 첫번째, 다른 측(이후, 랩 어라운드 부스바) 상에 백플레이인의 에지 주변에 Al 박을 둘러싸는 것. 이러한 도식을 이용한 위험은, 이후 단계의 일부 동안 랩핑된 박을 보호하는 것의 어려움을 포함한다. 두번째 도식에서, 조금의 스루홀은 드릴링되고, 전류는 언더라잉 박으로부터 이 위치에 접근된다. 이러한 홀을 생성하기 위한 몇 가지 방법이 여기에 개시된다.

b. 백플레이인의 두번째 배열 형태는 임의의 Al 박을 가지지 않는다. 백플레이인 어셈블리는 백플레이인 물질(거의 폴리머 또는 플라스틱 물질, 또는 가능하게는 유리) 및 Z68 등 물질만으로 이루어진다. 폴리머 또는 플라스틱 물질 시트는, 그것을 통과하는 더욱 많은 홀을 드릴링하기 쉽고/싸고, 얻어지는 태양 전지를 플렉서블하거나 반플렉서블(semi-flexible)하도록 해주기 때문에(그 결과 더 낮은 비용의 전지의 플렉서블한 모듈 패키징을 가능

하게 할 수 있음) 단단한 유리보다 유용할 수 있다. 폴리머 또는 플라스틱 백플레이인을 이용하는 시도는, 유리와 비교하여 실리콘과의 CTE 불일치가 더 높기 때문에(임베딩된 낮은 CTE 섬유 또는 입자로 제조되지 않는다면), 플라스틱을 이용하는 이후 단계가 더 낮은 값으로(예컨대 고작 ~ 150 °C 내지 300 °C) 온도를 캡핑(capping)하는 것을 요구할 수 있는 것이다. 홀은 Z68을 통과하지 않고, 백플레이인만을 통과하여 드릴링된다. 이후 웨트 및 드라이 가공 동안, Z68은 커버는 언더라잉 디바이스를 보호한다. 마지막으로, Z68은 개방되고, 모듈 어셈블리는 언더라잉 전지로부터 전류를 직접 끌어오도록 사용된다. 이는, 모듈에 다소 더욱 복잡한 어셈블리 공정을 요구하지만, 전지 비용을 극적으로 싸게 해준다.

[0087] 공정 흐름은 상기 논의된 백플레이인 실시예와 유사하지만, Al 박 배열 형태는 남아 있는 공정 흐름에서 설명된다. 백플레이인 어셈블리는 셀/템플레이트에 부착되고(도 4), 라미네이팅되고 경화된다. 이후 전지 바운더리 및 분리 바운더리를 정의하기 위해 레이저 트렌칭된다. 이어서, 기계적 분리가 기계적 분리(MR) 또는 소니케이트 기계적 분리(sonicated mechanical release, SMR)와 같은 이용 가능한 기술을 이용하여 수행된다.

[0088] 분리 후, 템플레이트는 세정되고, 다음 재사용을 위한 에피 및 다공성 실리콘의 재사용을 위해 되돌려진다. 백플레이인 어셈블리에 부착되는 TFSS(제2 영구적 캐리어인)는 QMS(또는 다공성 실리콘) 측 상에 세정되고, 텍스처링된다. 일 특정 실시예에서, 이는 KOH/SCD 또는 KOH/IPA 조합과 같은 고온의 KOH 기반의 화학물질을 이용하여 한번에 수행될 수 있다(KOH는 NaOH로 대체될 수 있다). 이후 하나의 경우에 HF/HCl 조합을 이용하여 행해질 수 있는 후 텍스처링 세정이 이어진다. 이어서, TFSS는 (수소화된) SiNx ARC 및 패시베이션층의 증착인 태양이 비치는 측 상의 최종 가공 단계가 취해진다(is taken for its final process step). 백플레이인 어셈블리의 존재 때문에, 이 공정의 최대 온도는, 백플레이인 물질의 선택에 따라 150 °C 내지 300 °C 범위일 수 있는 낮은 값으로 제한된다. 만족스러운 패시베이션이 후면 접촉 전지에 대해서 저온에서 수행될 수 있는 방법은 앞선 패시베이션에서 논의되었다. 이는, SiN 전에 박형(예컨대 3 nm 내지 10 nm) 비정질 실리콘(a-Si) 또는 비정질 실리콘 산화물층의 우수한 세정 후 텍스처링 및 증착을 포함할 것이라고만 해도 충분할 것이다. SiN은 바람직하게는, 표면 재조합을 감소시키고 표면으로부터 떨어진 포지티브하게 하전된 소수 캐리어 홀을 격퇴하기 위해 포지티브 전하에 풍부해야 한다.

[0089] 도 4의 공정 흐름의 최종 단계는 백플레이인의 이미 존재하는 홀을 통하여 Z68 물질의 접근 홀(access hole)을 개방하는 것이다. 이는 Al 박으로부터 에미터 및 베이스 전류를 (또는 에미터 및 베이스 전류에) 수직적으로 끌기 위한 것이다. 일 특정 실시예에 있어서, Z68의 스루-접근 홀은 Z68 물질을 통해 연소하는 고온의 솔더 물질을 이용하여 생성하고, 언더라잉 Al 박과 접촉을 만든다. 이어서, 솔더는 모듈 어셈블리에 사용될 수 있다. 다른 실시예에 있어서, Z68 (또는 다른 적합한 봉합재) 물질은, 그것을 끌어올리고 Sn 또는 솔더 합금에 접근점을 개방하는(which pulls it back and opens the access point to Sn or solder alloy) 빠른 방사선(잠재적으로는 IR)에 노출될 수 있다. 또 다른 배열 형태에 있어서, 홀은 Z68에만 또는 유리 및 Z68 둘다에 결국에 레이저를 이용하여 드릴링된다. 또 다른 배열 구조에 있어서, 홀은 백플레이인 어셈블리 시에 Z68 및 유리 둘다를 통하여 드릴링되지만, 언더라잉 디바이스는, 홀의 상부 상의 Z68을 일시적으로 태깅함으로써 또는 단일 측 텍스처링을 이용하여 텍스처 배스로부터 보호된다(is now protected through from the texture bath).

[0090] 도 5는 직접 금속 라이팅 기술(direct metal write techniques)을 이용하는 것을 제외하고 도 4에 묘사되는 것과 동일한 본 발명의 대표적인 선택적 에미터 및 고온 제거 공정 흐름이다(도 3의 공정 옵션 1A1에 대응함). 직접 라이팅 기술은 PVD 금속 증착 및 이후 레이저 금속 분리 단계의 필요성을 제거할 수 있다. 도 4에 도시된 공정 흐름의 변경으로서, PVD 금속 증착 후 레이저 금속 분리는 임의의 수많은 직접 금속 라이팅 기술로 대체될 수 있다. 이들은, 그것에 한정되지 않지만, 하나 이상의 금속 페이스트의 스크린 프린팅, 하나 이상의 금속 기반의 잉크의 잉크젯/에어로졸 프린팅 및 레이저 트랜스퍼 프린팅을 포함할 수 있다. 이러한 직접 금속 라이팅 기술은 이어서 더 높은 온도 어닐링이 이어질 수 있다.

[0091] 도 6 및 도 7은, 각각 도 6 및 7에 설명된 흐름이 전측의 텍스처를 제거함으로써 에피택셜 실리콘 성장 동안 인시투 전면 전계(FSF)를 형성시키는 차이점을 가지는, 도 4 및 도 5에 병행하는 2개의 선택적 에미터 및 고온 제

거 공정 흐름이다. 따라서, 도 6 및 7은 도 3의 흐름 옵션 1A2에 대응한다. FSF의 이점은, 베이스 저항을 감소시키고, 전면 재조합 속도를 감소시킴으로써(감소된 FSRV) Voc를 증가시키는 것을 돋는 것이다. 이를 지지하는 발상은 어떠한 텍스처 흐름도 인시투 도핑된 전면 전계를 보호할 수 없다는 것이다. QMS 제거를 행한 후(전면으로부터 소량의 실리콘 제거), 흐름은 텍스처링을 수행하지 않고 패시베이션으로 직접 이동한다. 텍스처링 또는 광 포획의 기능은 전면 패시베이션 후 추가적 이후 단계에 의해 수행된다. 이러한 단계는 적합한 유전체 또는 금속 입자층을 증착, 일 예로 스프레이 코팅 및 경화를 수반한다.

[0092] 도 6은 PVD 금속 스택 증착을 도시하고, 도 7은 직접 라이팅 금속 기술을 도시한다. 도 6은 텍스처링 없는 공정을 이용하여 수행되는 인시투 전면 전계를 갖는 PVD 금속 증착을 이용하는 공정 흐름을 묘사한다. 광 포획은 전지의 전측 상에 입자성 층을 이용하여 수행된다. 도 7은 도 6에 도시되는 PVD 금속 및 레이저 분리 방법 대신에 직접 금속 라이팅을 묘사한다.

[0093] 도 8은 도 3의 흐름 옵션 1B에 대응하는 공정 흐름의 실시예이다. 이 흐름은, 하나의 차이점, 즉 도 8의 흐름은 고온 제거 대신에 저온 제거(바람직하게는 펄스 ps 레이저를 이용하여)를 사용한다는 것을 제외하고 상기 논의된 변경을 가진 도 1에 설명된 흐름과 유사하다. 후 단계는 최초 온-템플레이트 단계의 약간의 변경이 있는 도 4의 흐름 옵션 1A와 유사하다. 저온 제거의 공정은 템플레이트 상에 몇 가지 단계를 변경할 수 있다. 도시된 바와 같이, 흐름은 에미터 및 베이스 디퓨전 영역을 분리하기 위해 BSG 층의 레이저 제거까지 동일하다. 이 레이저 단계 후 USG/PSG/(USG) 스택(고온 제거 공정의 경우에 사용될 수 있는) 대신에 APCVD USG 층만의 증착이 이어진다. 이어서, USG 층은 인 도핑 개방부를 생성하기 위해서 레이저 제거를 이용하여 제거된다. 이후 PSG/USG (PSG 상부에 USG 캡) 스택 증착이 이어진다. 이제 열적 산화 어닐링 및 드라이브(drive)가 행해진다. 이는, 에미터 접합의 형성, 실리콘에 베이스 도핑의 형성, 열적 산화물로 후면 패시베이션을 보증한다. 다음 단계는 저온 펄스 ps 레이저 제거를 이용하여 에미터 및 베이스 접촉을 개방하는 것이다. 고온 제거와의 차이점은, 저온 펄스 ps 레이저 제거의 경우에, 레이저가 도펀트를 드라이빙 할 동시적 부담(concurrent burden of driving the dopant in)을 가지지 않는다는 것이다(이는 고온 어닐링을 이용하여 베이스 및 에미터에 이미 행해졌다). 레이저는 접촉만을 개방하고, 실리콘을 거의 손상시키지 않고 실리콘에서 중단된다. 저온 레이저 제거가 더욱 용이한 제조 공정으로 여겨질 수 있지만, 고온 제거는 적어도 2가지의 이점을 유지한다. 첫째, 단계의 수를 둘로 감소시켜 비용 절감을 제공할 수 있다. 둘째, 에미터/베이스 분리에 베이스 접촉을 열라인하는 것만이 요구되지만, 저온 제거는 에미터/베이스 분리 영역에 USG 개방 영역을 우선 열라인한 후 USG 개방 영역에 베이스 접촉을 열라인하는 것이 요구된다. 제공되는 열라인먼트 능력 및 접촉 사이즈에 있어서, 저온 제거는 더 넓은 에미터/베이스 분리 영역으로 개시하는 것이 요구될 것이다. 도 8에 도시된 이후 공정 단계는 이전에 묘사된 흐름과 유사하다.

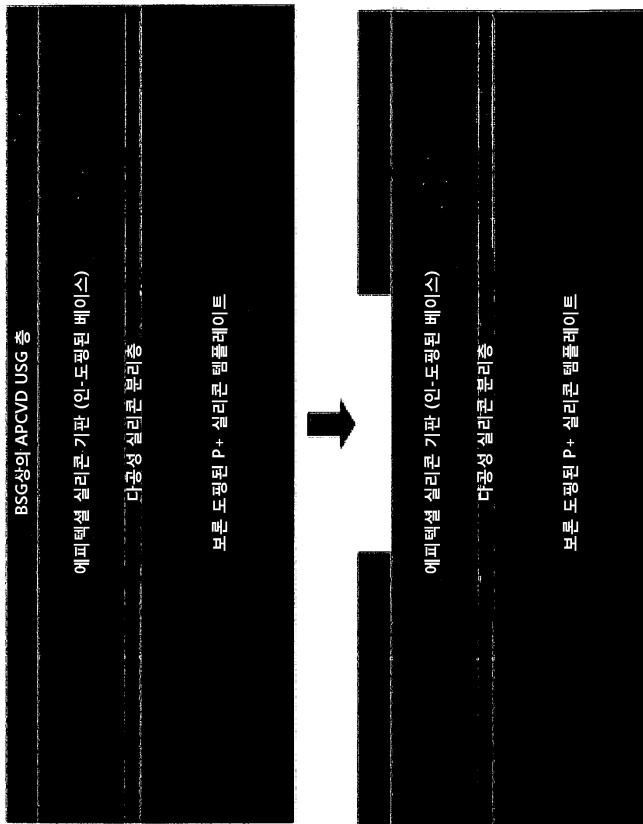

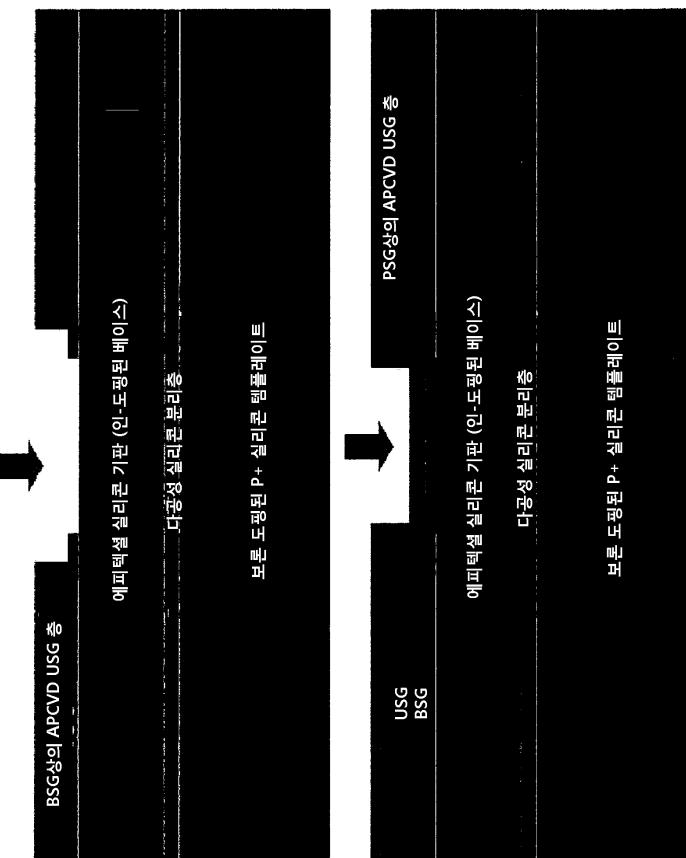

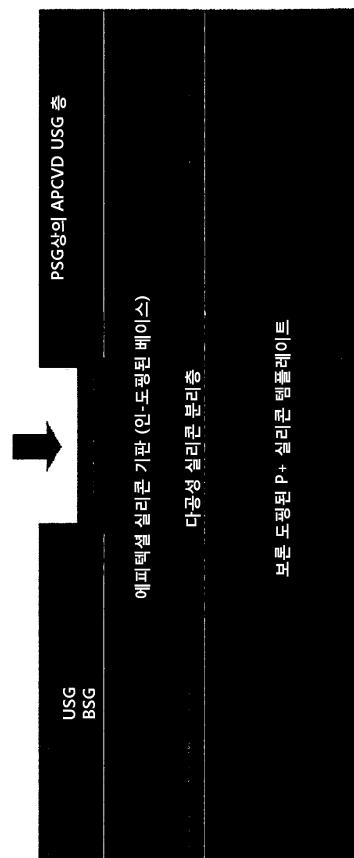

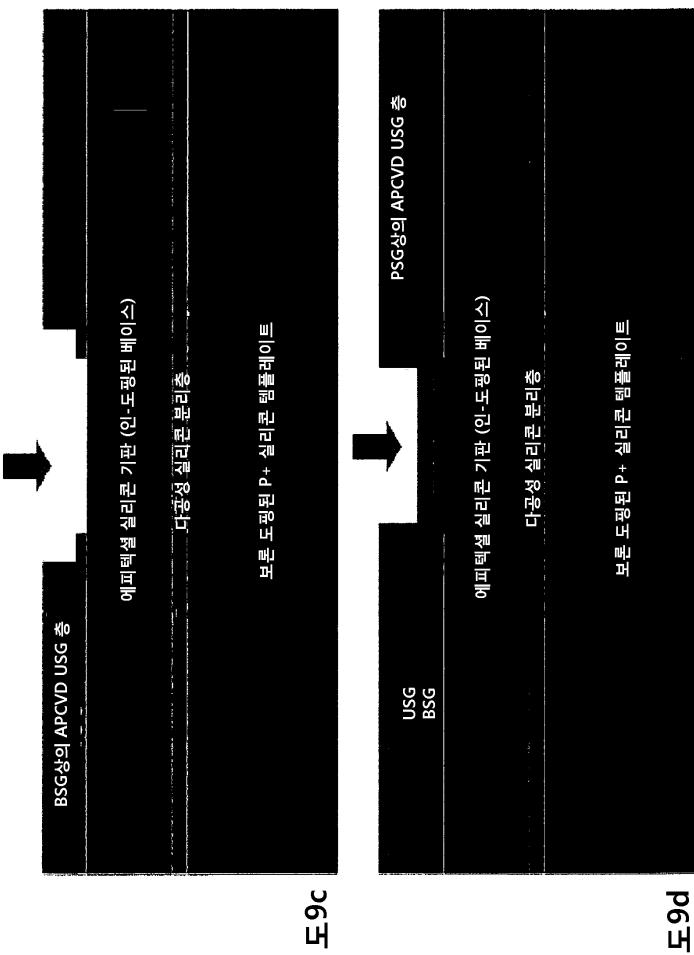

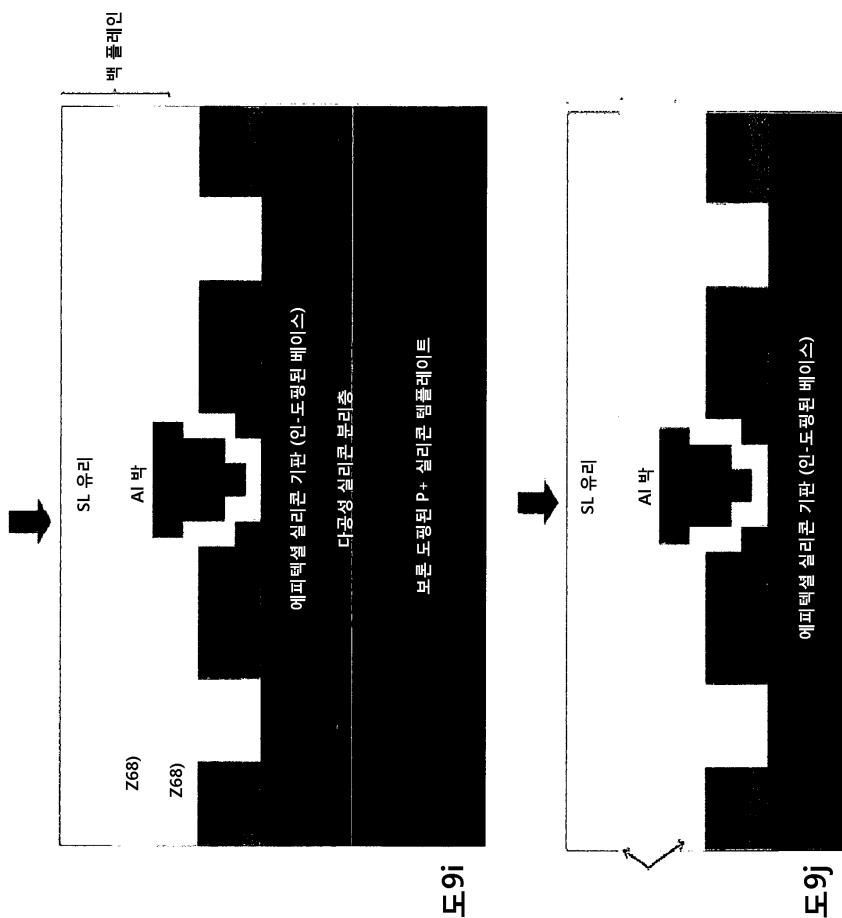

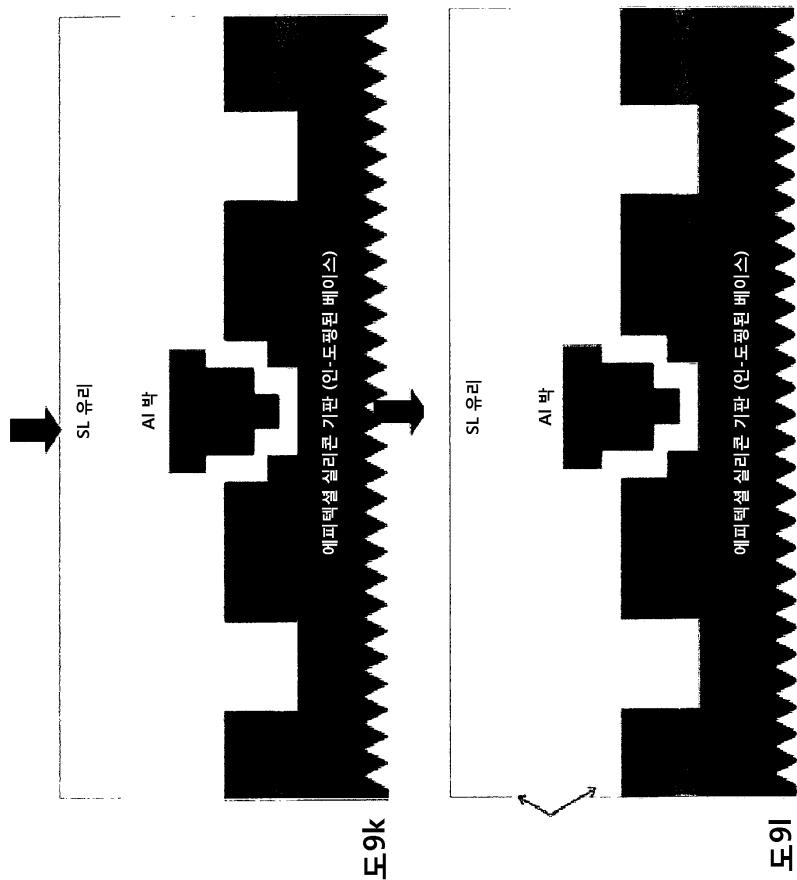

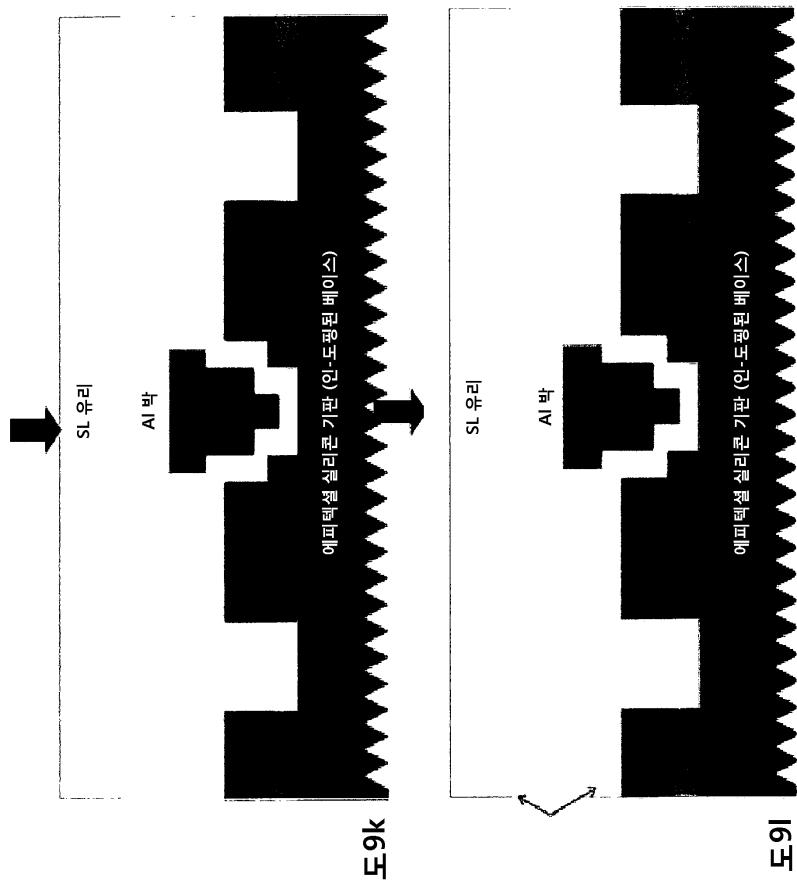

[0094] 도 9A-L은 도 8의 저온 제거의 주요 제조 단계를 묘사하는 단면도이다(도 3의 흐름 옵션 1B에 대응함). 도 9A는 USG/BSG (BSG 상부에 USG 캡) 증착 단계를 도시하고, 도 9B는 USG/BSG 레이저 제거 단계를 도시하고, 도 9C는 USG 증착 단계를 도시하고, 도 9D는 USG/PSG/(USG) 증착 단계를 도시하고, 도 9E는 산화 어닐링/도펀트 드라이브 증착 단계(oxidizing anneal/dopant drive-in deposition step)를 도시하고, 도 9F는 레이저 저온 제거 및 접촉 개방 단계를 도시하고, 도 9G는 PVD Al (또는 Al/NiV/Sn 또는 Al의 아래층 및 적합한 솔더 합금의 윗층을 포함하는 다른 적합한 스택) 증착 단계를 도시하고, 도 9H는 레이저 금속 제거 및 에폭시 프린트 단계를 도시하고, 도 9I는 백플레이인 부착 단계를 도시하고, 도 9J는 전지/템플레이트 분리 단계를 나타내고, 도 9K는 QMS (TFSS 상의 다공성 실리콘 잔여물의 나머지) 제거 및 텍스처링 단계를 도시하고, 도 9L은 저온 전면 패시베이션 단계를 도시한다.

[0095] 도 3 공정 흐름 옵션 2: 실리콘 나노 입자 인 기반의 베이스 도핑. 도 10은 실리콘 나노 입자 인 기반의 베이스 도핑 (페이스트 또는 잉크)의 공정 흐름을 설명한다. Al PVD로 개시하는 공정 흐름의 말미 및 템플레이트 세정/다공성 실리콘/에피/APCVD BSG/USG 증착 및 BSG 스택의 레이저 제거로 이루어진 흐름의 전단은 이미 개시되었고, 도 4 및 도 8을 참조한다. 흐름 옵션 2(옵션 2A, 2B 및 2C)의 3가지 기재된 서브 변형 중, 옵션 2A 및 2B는 고온 제거를 이용하고 옵션 2C는 저온 제거를 이용한다. 도 10, 11 및 12는 각각 도 2의 옵션 2A, 2B 및

2C에 대한 공정 흐름을 묘사한다.

[0096] 옵션 2A를 나타내는 도 10은 후 BSG 레이저 제거, 산화 어닐링은 열적로 어닐링 툴에서 행해지는 것을 도시한다. 이는 다기능적 공정이고, 실리콘으로 BSG에서 보론을 드라이빙함으로써 에미터를 형성하고, 결국 베이스 영역이 되는 패시베이션으로 작용하는, BSG가 제거되는 영역에서 열적 산화층을 형성하는 적어도 이중의 목적을 갖는다. 이후 흐름 옵션 1A에 설명되는 공정과 유사한 선택적 에미터를 형성하기 위해 에미터 영역의 고온 레이저 제거가 이어진다. 동시에 베이스 도핑 접촉의 산화물을 개방하기 위해 베이스 영역에 저온 제거가 사용된다. 이어서, 실리콘 나노 입자 기반의 인 페이스트는 스크린 프린팅되거나, 베이스 개방 영역에 인젝션과 같은 다른 방법을 이용하여 디스펜싱된다. 이어서, 페이스트는 베이스 도핑을 드라이브하도록 어닐링된다. 이후 PVD A1에서 개시되는 옵션 1(그 변형을 모두 함께)과 동일한 공정 흐름이 이어진다.

[0097] 도 11은 2개의 APCVD 툴을 이용하여 고온 제거 및 실리콘 나노 입자 인 페이스트 또는 잉크로 흐름 옵션 2B를 도시한다. 옵션 2B(도 11), 후 BSG 레이저 제거에 있어서, APCVD는 USG를 증착하기 위해 사용되었다(옵션 2A의 열적 산화물 대신에). 이후 에미터의 고온 제거 및 베이스 접촉 개방부의 USG의 저온 제거가 이어진다. 이어서, 스크린 프린팅 또는 인 기반의 실리콘 나노 입자(페이스트 또는 잉크)의 잉크젯이 수행된다. 이후 베이스 접촉 및 선택적 에미터를 형성하기 위해 열적 어닐링이 이어진다. 이후 가공은 흐름 옵션 1에 변형을 가지며 동일할 수 있다.

[0098] 옵션 2C(도 12)는 저온 제거 흐름이다. 도 12는 인 도핑을 위한 실리콘 나노 입자 인 페이스트로 저온 제거를 이용하는 흐름 옵션 2C를 도시한다. 여기서, 후 BSG 레이저 제거, APCVD는 옵션 2B에서와 같이 USG를 증착하기 위해 사용된다. 그러나, 이후 저온 제거를 이용하여 베이스 및 에미터 접촉 개방이 이어진다. 이어서, 나노 입자 인 페이스트는 베이스 영역에 적용되고(페이스트의 스크린 프린팅 또는 잉크의 잉크젯 프린팅에 의해), 어닐링된다. 어닐링 동작은 에미터를 드라이브하고(drive), 베이스 도핑 영역을 형성한다. 이후 가공은 이전에 개시된 것과 유사할 수 있다.

[0099] 실리콘 나노 입자를 이용하는 모든 옵션에서(도 3에서 흐름 옵션 2), 페이스트는 실리콘 나노 입자 기반이기 때문에, 페이스트가 적용된 후 다시 베이스 접촉을 개방할 필요가 없다는 것을 주의한다. 그 결과, 금속은 경화된 페이스트 상에 직접 놓아질 수 있다(may be put down). 또한, 필요에 따라, 흐름은 PVD A1을 놓기 전에 영역의 개방을 적용하기 위해 변형될 수 있다.

[0100] 도 3의 흐름 옵션 2: 인 페이스트 기반의 베이스 도핑. 여기서 이전 흐름과 비교된 차이점은, 베이스 접촉은 상업적으로 이용 가능한 인 페이스트를 이용하여 형성된다는 점이다. AI PVD를 포함하고 후 및 BSG 스택의 레이저 제거 전까지 모든 공정 단계는 옵션 1과 동일하게 유지될 수 있다. 각각 도 3의 흐름 옵션 3A, 3B 및 3C에 대응하는 도 13, 14 및 15에 도시되는 3가지 인 페이스트 기반의 베이스 도핑 변형이 있다. 많은 방법에서, 이러한 3가지 서브 옵션은 소수의 차이점을 가지고 이전에 논의된 나노 입자 페이스트에 대해 3가지 서브 옵션을 반영한다. 도 13(흐름 옵션 3A) 및 도 14(흐름 옵션 3B)는 고온 제거를 이용하지만, 도 15(옵션 3C)는 저온 제거 공정을 이용한다. 추가적으로 도 13(흐름 옵션 3A)은 하나의 APCVD를 이용하지만, 도 14(흐름 옵션 3B) 및 도 15(옵션 3C)는 2개의 APCVD 툴을 이용한다.

[0101] 옵션 3A(도 13) 후(post) BSG 제거에 있어서, 흐름 옵션 2A와 유사한 열적 산화물을 이용하여 베이스 영역 패시베이션 및 에미터 형성을 위해 산화 어닐링이 있다. 이어서, 레이저 제거는 흐름 옵션 2A와 다른 저온 제거로 베이스 접촉만을 개방하기 위해 사용된다. 이 단계 후 스크린 프린팅(또는 잉크젯 프린팅과 같은 직접 라이팅을 위한 인 페이스트의 디스펜싱의 임의의 다른 방법) 후, 베이스 접촉 인 디퓨전 영역을 드라이브(drive)하기 위한 어닐링이 이어진다. 이어서, 에미터의 고온 제거 및 베이스 영역의 저온 제거는 선택적 에미터 및 베이스 접촉을 제조하기 위해 수행된다. PVD A1로부터 개시되는 것을 따르는 모든 단계는 이전에 개시되었다.

- [0102] 옵션 3B(도 14)는 제거 후 APCVD USG 증착, 이후 베이스 접촉을 개방하기 위해 USG의 펄스 ps 레이저 (또는 저온 제거가 본 발명의 임의의 공정 흐름에 요구되는 경우에 펄스 ps 레이저 대신에 사용될 수 있는 펄스 fs 레이저) 저온 레이저 제거가 이어진다. 옵션 3A에서와 같이, 이후 인 페이스트의 스크린 인쇄 및 에미터 영역 및 인 베이스 접촉의 드라이브 및 어닐링이 이어진다. 이후 인 페이스트를 통해 베이스의 접촉을 재개방하기 위해 베이스의 저온 제거 및 에미터의 고온 제거가 이어진다. 이를 따르는 PVD A1로부터 개시되는 모든 단계는 이전에 개시되었다.

- [0103] 옵션 3C(도 15)는, BSG 제거 후 APCVD USG를 사용한다. 이후 베이스 개방부에서 USG의 제거, 이후 인 페이스트의 스크린 프린팅, 이후 에미터, 베이스 도핑 및 패시베이션을 형성하기 위해 산화 어닐링 및/또는 어닐링이 이어진다. 이어서, A1 PVD를 개시하는 모든 단계는 이전에 개시되었다.

- [0104] 흐름 옵션 4: POC13 기반의 베이스 도핑. 도 16, 17 및 18은 베이스 도핑에 POC13 (인 옥시클로라이드) 도핑을 이용하여 흐름의 세트이다. 도시된 바와 같이, BSG 레이저 제거를 포함하는 것까지의 모든 단계 및 A1 PVD를 포함하고 후의 모든 단계는 이전에 개시된 바와 같을 수 있다. 각각 도 3의 흐름 옵션 4A, 4B 및 4C에 대응하는 도 16, 17 및 18에 도시되는 3가지 POC13 기반의 베이스 도핑 변형이 있다. 도 16(흐름 옵션 4A) 및 도 17(흐름 옵션 4B)은 고온 제거를 이용하지만, 도 18(옵션 4C)은 저온 제거 공정이다. 추가적으로, 도 16(흐름 옵션 3A)은 하나의 APCVD를 이용하지만, 도 17(흐름 옵션 3B) 및 도 18(옵션 3C)은 두개의 APCVD 툴을 이용한다.

- [0105] 옵션 4A(도 16)에서, BSG 스택의 레이저 제거 후 동시에 에미터를 드라이브하고, 베이스 영역에 패시베이팅 열적 산화물을 형성하는 배치로에서 산화 어닐링이 이어진다. 이후 베이스 접촉 디퓨전 영역을 형성하기 위해 POC13로 도핑되는 베이스 접촉에 열적 산화물의 저온 제거가 이어진다. 이어서, 고온 제거가 에미터 접촉 개방부에 사용되고, 저온 제거가 베이스 영역의 POC13-형성된 유리를 통한다(hot ablation is used for emitter contact open, and cold ablation to go through the POC13-formed glass in the base area). 또한, 백 미러 시각으로부터 바람직할 수 있는 POC13-형성된 유리 전체를 제거하기 위해 레이저가 사용된다는 것이 가능하다. 이후 이전에 개시된 바와 같이 A1 PVD가 이어진다.

- [0106] 옵션 4B(도 17)에서, APCVD 산화물은 열적 산화물 어닐링 대신에 증착된다. 이후 베이스 접촉을 형성하기 위해 USG 물질의 저온 레이저 제거가 이어진다. 이후, 베이스 디퓨전의 형성 및 실리콘으로 에미터 영역을 드라이빙에 주의를 기울이는 POC13 도핑이 이어진다. 이어서, 고온 제거가 에미터 접촉 개방부에 사용되고, POC13 유리 물질을 통과하고 베이스 접촉을 개방하는데 저온 제거가 사용되는 선택적인 에미터를 형성하기 위해 드라이브(drive)한다. 이후 PVD A1에서 시작하는 표준 공정이 이어진다.

- [0107] 옵션 4C(도 18)에서, 열적 산화물 대신에, USG의 APCVD는 POC13의 블로킹을 형성하기 위해 사용되었다. 이후 베이스 접촉 개방부의 USG의 저온 제거 및 POC13 공정이 이어진다. POC13 공정은 베이스 접촉을 형성할 뿐만 아니라 동시에 에미터를 디퓨전한다. 이후 에미터 및 베이스 접촉 개방부의 저온 제거가 이어진다. 남아 있는 공정 흐름은 전과 같이 유지된다.

- [0108] 최소 전지 공정 흐름. 이 부분은 상기 옵션 1과 같이 기재되는 공정 흐름의 변형이 기재된다(베이스 접촉을 제조하기 위해 PSG를 이용하여). 본 변형에서, 몇몇의 단계는 조합되고, CE 프린트 단계는 고효율 후면 접촉 박형 전지를 형성하기 위해 감소된 수의 툴을 이용하기 위해 제거된다. 이러한 최소 단계 흐름의 속성의 정의는, 도전성 애폴시의 스크린 프린팅은 저온 솔더 합금(예컨대 138 °C 솔더 용융점을 갖는 58%Bi-42%Sn 또는 140-145 °C의 용융점을 갖는 Bi-45%Sn-0.33%Ag)을 이용하여 제거되고, 전지 A1 금속/미러의 상부 상에 오버레이어로서 및 금속 평거 상에 미리 형성된 펀 그리드 어레이를 갖는 백플레이인 금속 평거상에 형성되는 것이다(formed both

as an overlayer on top of the cell Al metal/mirror as well as on the backplane metal fingers with a pre-formed pin grid array on the metal fingers). 백플레인이 전지 상에 열라인 및 위치되면, 백플레인 핀 그리드 어레이는, 열적 라미네이션 공정 동안 전지에 솔더 부착된다.

[0109] 도 19, 고온 제거 직접 라이팅 공정은, 이하 공지된 성질을 갖는 최소 단계 공정 흐름의 제1 실시예를 묘사한다: 사용되는 2개의 APCVD 공정 단계는 텍스처링 공정을 가지고, 베이스 디퓨전, 레이저를 이용하여 형성되는 선택적 에미터를 형성하기 위해 PSG 및 고온 제거를 사용하고, 스크린 프린트, 잉크젯, 에어로졸 프린트, 레이저 트랜스퍼 프린트 및 CE 스크린 프린트 없이 직접 솔더 결합과 같은 직접 금속 라이팅 공정을 갖는다.

[0110] 도 20, 저온 제거 직접 라이팅 공정은, 최소 공정 흐름의 제2 실시예를 묘사한다. 몇 개의 공정 단계를 제거하기 위해 직접 금속 라이팅 및 솔더 부착의 도 19의 공통 성질을 유지한다. 그러나, 고온 제거에 의존하지 않고, 3가지 APCVD 단계를 갖는다는 점에서 도 19와 다르다.

[0111] 논 에피 벌크 박형 기판 공정 흐름(Non Epi Bulk thin substrate process flows). 이전에, 캐리어 1 실시예의 2가지 형태가 개시된다. 캐리어 1의 제1 형태는 템플레이트를 이용하고, 캐리어의 제2 형태는 수소 이온 주입을 포함하는 이용 가능한 기술을 이용하여 박형 CZ 또는 FZ 슬라이스가 분열 또는 박리되는 두꺼운 웨이퍼 또는 잉곳이다. 이하 부분은, 백플레인 혁신을 이용하는 전지 레벨 공정 흐름과 함께 박형 실리콘 기판을 얻기 위한 웨이퍼 분열 접근법이 기재된다. 양자 주입 기반의 분열(Proton implant based cleaving)은 바람직하게는 드라이 텍스처링을 요구하는 <111> 텍스처링된 기판을 제조한다. 실시예는 초박형 기판(예컨대 수 mm 또는 수 cm 두께의 웨이퍼 또는 브릭과 같은 훨씬 더 두꺼운 재사용 가능한 웨이퍼로부터 분리된/분열된 약 1  $\mu\text{m}$  내지 80  $\mu\text{m}$  두께의 기판)의 양자 주입 분열/슬라이싱을 보여준다.

[0112] 도 21은 박형 실리콘을 얻기 위해 웨이퍼 분열 접근법을 이용하는 제1 공정 흐름을 도시한다. 공정 흐름은, 기판을 생성하는데 사용되는 최초 단계를 제외하고 도 4(캐리어 1에 재사용 가능한 템플레이트를 사용하는)에 설명된 흐름 1A1에 평행하다. 이러한 흐름의 특정 성질은: 2개의 APCVD 공정(APCVD PSG 및 고온 레이저 제거를 이용하여 형성되는 베이스 접촉 디퓨전), 인시투 전면 전계 (FSF) 인 도핑을 가지거나 또는 가지지 않는 평면 또는 미리 텍스처링된 템플레이트 상에 수행될 수 있는 전지 전면 텍스처링, 진공 스퍼터링, 진공 증착, 대기 아크(arc)/열 스프레이 코팅 등을 이용하여 수행될 수 있는 금속 증착을 이용한다. 제1 단계는 재사용 가능한 두꺼운 웨이퍼로 시작하는 것이다.

[0113] 도 21에서, 우선 기판 두께를 세팅하는 임플란트 에너지를 가지고, 웨이퍼가 MeV 양자 임플란트가 주입된다. 이러한 기판 생성 단계 이후, 도시되는 단계는, 백플레인 부착 단계까지 도 4에 도시된 흐름과 유사하다. 백플레인 부착 후, 웨이퍼는 임플란트에 의해 생성되는 분열로부터 두꺼운 웨이퍼로부터 분리된다. 이후, 이는 <111> 표면이기 때문에, 레이저 또는 드라이 플라즈마 공정을 이용하여 수행될 수 있는 드라이 텍스처링 공정이 이어진다. 선택적 후 텍스쳐 세정(post texture clean)은 그 뒤에 수행될 수 있다-재사용 가능한 템플레이트를 이용하는 이전 실시예는 드라이 텍스쳐 공정을 필수적으로 요구하지 않는다. 도 21에 도시된 바와 같이, 드라이 텍스처링 패시베이션 후 백플레인 접근 단계가 수행된다.

[0114] 도 22 내지 35는 박형 실리콘 전지에 주입 및 분열되는 양자를 이용하여 후면 접촉 박형 결정 태양 전지에 대한 도 21으로 설명되는 공정 흐름의 몇 가지 변형 및 예를 도시한다. 변형들은 템플레이트 공정 흐름 상에 재사용 가능한 PS/에피택셜 TFSS를 이용하여 기재되는 동일한 흐름을 반영한다. 공정 흐름의 4가지 카테고리는 도 3의 흐름 옵션과 유사하다-이러한 4가지 카테고리는 베이스 디퓨전 영역을 생성하기 위해 사용되는 방법의 베이스 상에 서로로부터 구별된다. 도 21의 흐름을 포함하는 첫번째 카테고리는 베이스 디퓨전 영역을 생성하기 위해 PSG 층을 이용한다; 두번째 카테고리는 실리콘 나노 입자를 이용한다; 세번째 카테고리는 인 페이스트를 이용한

다; 네번째 카테고리는 베이스 디퓨전 영역을 생성하기 위해 POC1 공정을 이용한다.

[0115] 도 22 내지 26은 PSG 기반의 도핑 카테고리에 속하는 흐름을 도시한다. 이 공정 흐름의 각각은 이후 직접적으로 리스트되는 하기 성질에 의해 특징화될 수 있다.

[0116] 도 22는 도 3의 흐름 옵션 1A1에 대응하고, 이하 성질에 의해 특징화될 수 있다:

[0117] · 재사용 가능한 두꺼운 웨이퍼 또는 브릭 또는 잉곳 피스로부터 슬라이싱/분열됨으로써 형성되는 박형 기판(예컨대 MeV 양자 임플란트 후); 박형 기판은 일반적으로 드라이 레이저 또는 플라즈마 텍스처링을 필요로 하는 (111) 배향된 기판이다(합리적인 양자 주입량으로 분열을 가능하게 하기 위해).

[0118] · 추가적인 공정 단계 없이 선택적 에미터 포함함(고온 제거 공정을 이용하여)

[0119] · 2개의 APCVD 공정을 사용함

[0120] · APCVD PSG & 고온 레이저 제거를 이용하여 형성된 베이스 접촉 디퓨전

[0121] · 전지 전면 텍스처링을 포함함

[0122] · 인시투 전면 전계 (FSF) 인 도핑을 하거나 하지 않고 평면 또는 미리 텍스처링된 템플레이트 상에 수행될 수 있음

[0123] · 맞물려진 전지 금속(예컨대 Al 또는 Al/Sn 또는 Al/NiV/Sn) 팽거에 직접 라이팅 공정을 이용하지만 흐름 1A1과 동일함

[0124] · 금속 증착은 스크린 프린팅, 레이저 트랜스퍼 프린팅, 잉크젯 프린팅, 에어로졸 프린팅과 같은 직접 라이팅 공정을 이용하여 수행될 수 있다.

[0125] 도 23은 도 3의 흐름 옵션 1A2에 대응하고, 이하 성질에 의해 특징화될 수 있다:

[0126] · 재사용 가능한 두꺼운 웨이퍼 또는 잉곳 피스로부터 슬라이싱/분열됨으로써 형성되는 박형 기판(예컨대 MeV 양자 임플란트 후); 박형 기판은 일반적으로 드라이 레이저 또는 플라즈마 텍스처링을 필요로 하는 (111) 배향된 기판이다.

[0127] · 추가적인 공정 단계 없이 선택적 에미터 포함함(고온 제거 공정을 이용하여)

[0128] · 2개의 APCVD 공정을 사용함

[0129] · APCVD PSG & 고온 레이저 제거를 이용하여 형성된 베이스 접촉 디퓨전

[0130] · 전지 전면 텍스처링 없음(텍스쳐 없는)-대신 입자성 물질의 광 포획 층을 코팅함으로써 광 포획이 도와진다(예컨대 유전체 또는 금속성 입자성 물질)

[0131] · 전면 전계 (FSF) 인 도핑을 포함함

[0132] · 금속 증착은 플라즈마 스퍼터링, 진공 증착, 대기 아크/열적 스프레이 코팅 등을 이용하여 수행될 수 있다.

[0133] 도 24는 도 3의 흐름 옵션 1A2에 대응하고, 이하 성질에 의해 특징화될 수 있다:

[0134] · 재사용 가능한 두꺼운 웨이퍼 또는 잉곳 피스로부터 슬라이싱/분열됨으로써 형성되는 박형 기판(예컨대 MeV 양자 임플란트 후); 박형 기판은 일반적으로 드라이 레이저 또는 플라즈마 텍스처링을 필요로 하는 (111) 배향된 기판이다.

[0135] · 추가적인 공정 단계 없이 선택적 에미터 포함함(고온 제거 공정을 이용하여)

[0136] · 2개의 APCVD 공정을 사용함

[0137] · APCVD PSG 및 고온 레이저 제거를 이용하여 형성된 베이스 접촉 디퓨전

- [0138] · 전지 전면 텍스처링 없음(텍스쳐 없는)-대신 입자성 물질의 광 포획 층을 코팅함으로써 광 포획이 도와진다(예컨대 유전체 또는 금속성 입자성 물질)

- [0139] · 전면 전계 (FSF) 인 도핑을 포함함

- [0140] · 금속 증착은 스크린 프린팅, 레이저 트랜스퍼 프린팅, 잉크젯 프린팅, 에어로졸 프린팅 등과 같은 직접 라이팅 공정을 이용하여 수행될 수 있다.

- [0141] 도 25는 도 3의 흐름 옵션 1B에 대응하고, 이하 성질에 의해 특징화될 수 있다:

- [0142] · 재사용 가능한 두꺼운 웨이퍼 또는 브릭 또는 잉곳 피스로부터 슬라이싱/분열됨으로써 형성되는 박형 기판(예컨대 MeV 양자 임플란트 후); 박형 기판은 일반적으로 드라이 레이저 또는 플라즈마 텍스처링을 필요로 하는 (111) 배향된 기판이다.

- [0143] · 추가적인 공정 단계 없이 선택적 에미터 포함함(고온 제거 공정을 이용하여)

- [0144] · 3개의 APCVD 공정을 사용함

- [0145] · APCVD PSG 및 로 어닐링을 이용하여 형성된 베이스 접촉 디퓨전

- [0146] · 금속 증착은 플라즈마 스퍼터링, 진공 증착, 대기 아크/열적 스프레이 코팅 등을 이용하여 수행될 수 있다.

- [0147] 도 26은 도 3의 흐름 옵션 1B에 대응하고, 이하 성질에 의해 특징화될 수 있다:

- [0148] · 재사용 가능한 두꺼운 웨이퍼 또는 브릭 또는 잉곳 피스로부터 슬라이싱/분열됨으로써 형성되는 박형 기판(예컨대 MeV 양자 임플란트 후); 박형 기판은 일반적으로 드라이 레이저 또는 플라즈마 텍스처링을 필요로 하는 (111) 배향된 기판이다.

- [0149] · 추가적인 공정 단계 없이 선택적 에미터 포함함(고온 제거 공정을 이용하여)

- [0150] · 3개의 APCVD 공정을 사용함

- [0151] · APCVD PSG 및 로 어닐링을 이용하여 형성된 베이스 접촉 디퓨전

- [0152] · 금속 증착은 레이저 트랜스퍼 프린팅, 잉크젯 프린팅, 에어로졸 프린팅 등과 같은 직접 라이팅 공정을 이용하여 수행될 수 있다.

- [0153] 도 27은 도 3의 흐름 옵션 2A에 대응하고, 이하 성질에 의해 특징화될 수 있다:

- [0154] · 재사용 가능한 두꺼운 웨이퍼 또는 잉곳 피스로부터 슬라이싱/분열됨으로써 형성되는 박형 기판(예컨대 MeV 양자 임플란트 후); 박형 기판은 일반적으로 드라이 레이저 또는 플라즈마 텍스처링을 필요로 하는 (111) 배향된 기판이다.

- [0155] · 추가적인 공정 단계 없이 선택적 에미터 포함함(고온 제거 공정을 이용하여)

- [0156] · 하나의 APCVD 공정 단계만을 사용함

- [0157] · 스크린 프린팅 또는 잉크젯 프린팅된 실리콘 나노 입자 인 페이스트를 이용하여 형성된 베이스 접촉 디퓨전

- [0158] 도 28은 도 3의 흐름 옵션 2B에 대응하고, 이하 성질에 의해 특징화될 수 있다:

- [0159] · 재사용 가능한 두꺼운 웨이퍼 또는 브릭 또는 잉곳 피스로부터 슬라이싱/분열됨으로써 형성되는 박형 기판(예컨대 MeV 양자 임플란트 후); 박형 기판은 일반적으로 드라이 레이저 또는 플라즈마 텍스처링을 필요로 하는 (111) 배향된 기판이다.

- [0160] · 추가적인 공정 단계 없이 선택적 에미터 포함함(고온 제거 공정을 이용하여)

- [0161] · 2개의 APCVD 공정 단계를 사용함

- [0162] · 스크린 프린팅 또는 잉크젯 프린팅된 실리콘 나노 입자 인 페이스트를 이용하여 형성된 베이스 접촉 디퓨전

- [0163] 도 29는 도 3의 흐름 옵션 2C에 대응하고, 이하 성질에 의해 특징화될 수 있다:

- [0164] · 재사용 가능한 두꺼운 웨이퍼 또는 브릭 또는 잉곳 피스로부터 슬라이싱/분열됨으로써 형성되는 박형 기판(예 컨대 MeV 양자 임플란트 후); 박형 기판은 일반적으로 드라이 레이저 또는 플라즈마 텍스처링을 필요로 하는 (111) 배향된 기판이다.

- [0165] · 고온 제거 공정이 없고 선택적 에미터가 없음

- [0166] · 2개의 APCVD 공정 단계를 사용함

- [0167] · 스크린 프린팅 또는 잉크젯 프린팅된 실리콘 나노 입자 인 페이스트를 이용하여 형성된 베이스 접촉 디퓨전

- [0168] 도 30은 도 3의 흐름 옵션 3A에 대응하고, 이하 성질에 의해 특징화될 수 있다:

- [0169] · 재사용 가능한 두꺼운 웨이퍼 또는 브릭 또는 잉곳 피스로부터 슬라이싱/분열됨으로써 형성되는 박형 기판(예 컨대 MeV 양자 임플란트 후); 박형 기판은 일반적으로 드라이 레이저 또는 플라즈마 텍스처링을 필요로 하는 (111) 배향된 기판이다.

- [0170] · 추가적인 공정 단계 없이 선택적 에미터 포함함(고온 제거 공정을 이용하여)

- [0171] · 하나의 APCVD 공정 단계만을 사용함

- [0172] · 표준 시판의 인 페이스트를 이용하여 형성된 베이스 접촉 디퓨전(예컨대 스크린 프린팅에 의해 적용된)

- [0173] 도 31은 도 3의 흐름 옵션 3B에 대응하고, 이하 성질에 의해 특징화될 수 있다:

- [0174] · 재사용 가능한 두꺼운 웨이퍼 또는 브릭 또는 잉곳 피스로부터 슬라이싱/분열됨으로써 형성되는 박형 기판(예 컨대 MeV 양자 임플란트 후); 박형 기판은 일반적으로 드라이 레이저 또는 플라즈마 텍스처링을 필요로 하는 (111) 배향된 기판이다.

- [0175] · 추가적인 공정 단계 없이 선택적 에미터 포함함(고온 제거 공정을 이용하여)

- [0176] · 2개의 APCVD 공정 단계를 사용함

- [0177] · 표준 시판의 인 페이스트를 이용하여 형성된 베이스 접촉 디퓨전(예컨대 스크린 프린팅에 의해 적용된)

- [0178] 도 32는 도 3의 흐름 옵션 3C에 대응하고, 이하 성질에 의해 특징화될 수 있다:

- [0179] · 재사용 가능한 두꺼운 웨이퍼 또는 브릭 또는 잉곳 피스로부터 슬라이싱/분열됨으로써 형성되는 박형 기판(예 컨대 MeV 양자 임플란트 후); 박형 기판은 일반적으로 드라이 레이저 또는 플라즈마 텍스처링을 필요로 하는 (111) 배향된 기판이다.

- [0180] · 고온 제거 공정이 없고 선택적 에미터가 없음

- [0181] · 2개의 APCVD 공정 단계를 사용함

- [0182] · 표준 시판의 인 페이스트를 이용하여 형성된 베이스 접촉 디퓨전(예컨대 스크린 프린팅에 의해 적용된)

- [0183] 도 33은 도 3의 흐름 옵션 4A에 대응하고, 이하 성질에 의해 특징화될 수 있다:

- [0184] · 재사용 가능한 두꺼운 웨이퍼 또는 브릭 또는 잉곳 피스로부터 슬라이싱/분열됨으로써 형성되는 박형 기판(예 컨대 MeV 양자 임플란트 후); 박형 기판은 일반적으로 드라이 레이저 또는 플라즈마 텍스처링을 필요로 하는 (111) 배향된 기판이다.

- [0185] · 추가적인 공정 단계 없이 선택적 에미터 포함함(고온 제거 공정을 이용하여)

[0186] · 하나의 APCVD 공정 단계만을 사용함

[0187] ·  $\text{POCl}_3$ 로 도핑을 이용하여 형성된 베이스 접촉 디퓨전

[0188] 도 34는 도 3의 흐름 옵션 4B에 대응하고, 이하 성질에 의해 특징화될 수 있다:

[0189] · 재사용 가능한 두꺼운 웨이퍼 또는 브릭 또는 잉곳 피스로부터 슬라이싱/분열됨으로써 형성되는 박형 기판(예컨대 MeV 양자 임플란트 후); 박형 기판은 일반적으로 드라이 레이저 또는 플라즈마 텍스처링을 필요로 하는 (111) 배향된 기판이다.

[0190] · 추가적인 공정 단계 없이 선택적 에미터 포함함(고온 제거 공정을 이용하여)

[0191] · 2개의 APCVD 공정 단계를 사용함

[0192] ·  $\text{POCl}_3$ 로 도핑을 이용하여 형성된 베이스 접촉 디퓨전

[0193] 도 35는 도 3의 흐름 옵션 4C에 대응하고, 이하 성질에 의해 특징화될 수 있다:

[0194] · 재사용 가능한 두꺼운 웨이퍼 또는 브릭 또는 잉곳 피스로부터 슬라이싱/분열됨으로써 형성되는 박형 기판(예컨대 MeV 양자 임플란트 후); 박형 기판은 일반적으로 드라이 레이저 또는 플라즈마 텍스처링을 필요로 하는 (111) 배향된 기판이다.

[0195] · 고온 제거 공정이 없고 선택적 에미터가 없음

[0196] · 2개의 APCVD 공정 단계를 사용함

[0197] ·  $\text{POCl}_3$ 로 도핑을 이용하여 형성된 베이스 접촉 디퓨전

[0198] 백플레이인 기술을 이용하여 벌크 CZ 및 FZ을 위한 특정 공정 흐름. 흐름의 이 카테고리에서, 백플레이인 기술을 이용하는 벌크 CZ(Czochralski) 및 FZ(Float Zone) 웨이퍼에 대한 대표적인 후면 접촉/후면 접합 공정 흐름이 설명된다. 구별 요소들 중에서 백플레이인의 삽입 및 직접 패턴 정의를 위한 피코세컨 레이저 공정의 광범위한 사용도 포함한다. 명확히 언급하지 않지만, 바람직하다면, 백플레이인 기술은, 매우 높은 수명을 주지 않을 수 있는 저렴한 벌크 웨이퍼가 소망되는 경우에 유용할 수 있는 더 얇은 전지 흡수체를 형성하기 위해 예전에 의해 이들을 박육화 하기 위한 벌크 FZ 및 CZ 웨이퍼 상에 사용될 수 있다. 또한, 더 저렴하고, 상대적으로 더 낮은 수명 웨이퍼는 p형 벌크 도핑일 수 있다. 묘사되는 공정 흐름 전체는 n형 베이스(벌크) 도핑인 바람직한 도핑을 이용하는 웨이퍼의 예이다.

[0199] 흐름의 5가지 카테고리가 이하에 설명된다-각각의 카테고리는 2개의 서브 카테고리를 갖는다. 서브카테고리는 전지 상에 금속을 증착 및 패터닝하기 위해 사용되는 방법으로 구별된다. 본 명세서에서 이전에 기재된 흐름과 동일한 첫번째 서브-카테고리에 있어서, 레이저 기반 분리 공정과 함께 PVD가 패터닝된 베이스 및 에미터 금속을 얻기 위해 사용되었다. 두번째 서브-카테고리에 있어서, 직접 패터닝된 금속 라이팅 기술은 PVD/레이저 분리 단계 대신에 사용된다. 5개의 주요 카테고리의 전체 공정 흐름은 도면 및 상세한 설명에 설명된다; 그러나, 카테고리가 이하 특성에 따라 정의될 수 있다:

[0200] CZ/FZ 옵션 I: 텍스처링 전에 형성되는 PSG 기반의 전면 전계 (FSF).

[0201] CZ/FZ 옵션 II: 텍스처링 전에 형성되는  $\text{POCl}_3$  기반의 FSF. 이 공정은  $\text{POCl}_3$  유리 디글레이즈(deglaze) 단계가 없다.

[0202] CZ/FZ 옵션 III:  $\text{POCl}_3$  유리 디글레이즈를 갖는  $\text{POCl}_3$  기반의 FSF.

[0203] CZ/FZ 옵션 IV: 텍스처링 후 형성된 PSG 기반의 FSF.

[0204] CZ/FZ 옵션 V: FSF가 없음.

도 36은 CZ/FZ 옵션 I에 대응하고, 이하 성질에 의해 특징화될 수 있다:

- 추가적인 공정 단계 없이 선택적 에미터 포함함(고온 제거 공정을 이용하여)

- 분리된 베이스-에미터 접합

- 2개의 APCVD 공정 단계를 사용함

- APCVD PSG & 고온 레이저 제거를 이용하여 형성된 베이스 접촉 디퓨전

- 전측 FSF에 사용되는 APCVD PSG 및 후측 베이스 접촉 디퓨전

- 미리 텍스처 FSF 형성

- 인라인 백플레이인 부착

- 금속 증착은 플라즈마 스퍼터링, 진공 증착, 대기 아크/열적 스프레이 코팅 등을 이용하여 수행될 수 있다.

도 37은 CZ/FZ 옵션 I에 대응하고, 이하 성질에 의해 특징화될 수 있다:

- 추가적인 공정 단계 없이 선택적 에미터 포함함(고온 제거 공정을 이용하여)

- 분리된 베이스-에미터 접합

- 2개의 APCVD 공정 단계를 사용함

- APCVD PSG & 고온 레이저 제거를 이용하여 형성된 베이스 접촉 디퓨전

- 전측 FSF에 사용되는 APCVD PSG 및 후측 베이스 접촉 디퓨전

- 미리 텍스처 FSF 형성

- 인라인 백플레이인 부착

- 금속 증착은 레이저 트랜스퍼 프린팅, 잉크젯 프린팅, 에어로졸 프린팅 등과 같은 직접 라이팅 공정을 이용하여 수행될 수 있다.

도 38은 CZ/FZ 옵션 II에 대응하고, 이하 성질에 의해 특징화될 수 있다:

- 추가적인 공정 단계 없이 선택적 에미터 포함함(고온 제거 공정을 이용하여)

- 분리된 베이스-에미터 접합

- 2개의 APCVD 공정을 사용함

- APCVD PSG & 고온 레이저 제거를 이용하여 형성된 베이스 접촉 디퓨전

- 후측 베이스 접촉 디퓨전만을 위해 사용되는 APCVD PSG

- 동시 또는 순차적으로 어닐링 및 산화하기 위해 사용되는 POC13-튜브-기반의 어닐링

- POC13 유리 디글레이즈 없음

- 미리 텍스처 FSF 형성

- 금속 증착은 진공 스퍼터링, 진공 증착, 대기 아크/열적 스프레이 코팅 등을 이용하여 수행될 수 있다.

도 39는 금속에 대해 직접 라이팅하는 것을 제외하고는 도 38과 주요 성질이 유사한 CZ/FZ 옵션 II에 대응하고, 이하 성질에 의해 특징화될 수 있다:

- [0234] · 추가적인 공정 단계 없이 선택적 에미터 포함함(고온 제거 공정을 이용하여)

- [0235] · 분리된 베이스-에미터 접합

- [0236] · 2개의 APCVD 공정을 사용함

- [0237] · APCVD PSG 및 고온 레이저 제거를 이용하여 형성된 베이스 접촉 디퓨전

- [0238] · 후측 베이스 접촉 디퓨전만을 위해 사용되는 APCVD PSG

- [0239] · 동시 또는 순차적으로 어닐링 및 산화하기 위해 사용되는 POC13-기반의로 어닐링

- [0240] · POC13 유리 디글레이즈 없음

- [0241] · 미리 텍스처 FSF 형성

- [0242] · 금속 증착은 스크린 프린팅, 레이저 트랜스퍼 프린팅, 잉크젯 프린팅, 에어로졸 프린팅 등과 같은 직접 라이팅 공정을 이용하여 수행될 수 있다.

- [0243] 도 40은 CZ/FZ 옵션 III에 대응하고, 이하 성질에 의해 특징화될 수 있다:

- [0244] · 추가적인 공정 단계 없이 선택적 에미터 포함함(고온 제거 공정을 이용하여)

- [0245] · 분리된 베이스-에미터 접합

- [0246] · 2개의 APCVD 공정을 사용함

- [0247] · APCVD PSG 및 고온 레이저 제거를 이용하여 형성된 베이스 접촉 디퓨전

- [0248] · 후측 베이스 접촉 디퓨전만을 위해 사용되는 APCVD PSG

- [0249] · 동시 또는 순차적으로 어닐링 및 산화하기 위해 사용되는 POC13-기반의로 어닐링

- [0250] · POC13 유리 디글레이즈 있음

- [0251] · 미리 텍스처 FSF 형성

- [0252] · 금속 증착은 플라즈마 스퍼터링, 진공 증착, 대기 아크/열적 스프레이 코팅 등을 이용하여 수행될 수 있다.

- [0253] 도 41은 CZ/FZ 옵션 III에 대응하고, 이하 성질에 의해 특징화될 수 있다:

- [0254] · 추가적인 공정 단계 없이 선택적 에미터 포함함(고온 제거 공정을 이용하여)

- [0255] · 분리된 베이스-에미터 접합

- [0256] · 2개의 APCVD 공정을 사용함

- [0257] · APCVD PSG 및 고온 레이저 제거를 이용하여 형성된 베이스 접촉 디퓨전

- [0258] · 후측 베이스 접촉 디퓨전만을 위해 사용되는 APCVD PSG

- [0259] · 동시 또는 순차적으로 어닐링 및 산화하기 위해 사용되는 POC13-기반의로 어닐링

- [0260] · POC13 유리 디글레이즈 있음

- [0261] · 미리 텍스처 FSF 형성

- [0262] · 금속 증착은 스크린 프린팅, 레이저 트랜스퍼 프린팅, 잉크젯 프린팅, 에어로졸 프린팅 등과 같은 직접 라이팅 공정을 이용하여 수행될 수 있다.

- [0263] 도 42는 CZ/FZ 옵션 IV에 대응하고, 이하 성질에 의해 특징화될 수 있다:

- [0264] · 추가적인 공정 단계 없이 선택적 에미터 포함함(고온 제거 공정을 이용하여)

- [0265] · 분리된 베이스-에미터 접합

- [0266] · 2개의 APCVD 공정을 사용함

- [0267] · APCVD PSG 및 고온 레이저 제거를 이용하여 형성된 베이스 접촉 디퓨전

- [0268] · 전측 FSF에 사용되는 APCVD PSG 및 후측 베이스 접촉 디퓨전

- [0269] · 포스트-텍스처(Post-texture) FSF 형성

- [0270] · 금속 증착은 플라즈마 스퍼터링, 진공 증착, 대기 아크/열적 스프레이 코팅 등을 이용하여 수행될 수 있다.

- [0271] 도 43은 CZ/FZ 옵션 IV에 대응하고, 이하 성질에 의해 특징화될 수 있다:

- [0272] · 추가적인 공정 단계 없이 선택적 에미터 포함함(고온 제거 공정을 이용하여)

- [0273] · 분리된 베이스-에미터 접합

- [0274] · 2개의 APCVD 공정을 사용함

- [0275] · APCVD PSG 및 고온 레이저 제거를 이용하여 형성된 베이스 접촉 디퓨전

- [0276] · 전측 FSF에 사용되는 APCVD PSG 및 후측 베이스 접촉 디퓨전

- [0277] · 포스트-텍스처 FSF 형성

- [0278] · 금속 증착은 스크린 프린팅, 레이저 트랜스퍼 프린팅, 잉크젯 프린팅, 에어로졸 프린팅 등과 같은 직접 라이팅 공정을 이용하여 수행될 수 있다.

- [0279] 도 44는 CZ/FZ 옵션 V에 대응하고, 이하 성질에 의해 특징화될 수 있다:

- [0280] · 추가적인 공정 단계 없이 선택적 에미터 포함함(고온 제거 공정을 이용하여)

- [0281] · 분리된 베이스-에미터 접합

- [0282] · 2개의 APCVD 공정을 사용함

- [0283] · APCVD PSG 및 고온 레이저 제거를 이용하여 형성된 베이스 접촉 디퓨전

- [0284] · 후측 베이스 접촉 디퓨전을 위해 사용되는 APCVD PSG

- [0285] · FSF 없음

- [0286] · 금속 증착은 플라즈마 스퍼터링, 진공 증착, 대기 아크/열적 스프레이 코팅 등을 이용하여 수행될 수 있다.

- [0287] 도 45는 CZ/FZ 옵션 V에 대응하고, 이하 성질에 의해 특징화될 수 있다:

- [0288] · 추가적인 공정 단계 없이 선택적 에미터 포함함(고온 제거 공정을 이용하여)

- [0289] · 분리된 베이스-에미터 접합

- [0290] · 2개의 APCVD 공정을 사용함

- [0291] · APCVD PSG 및 고온 레이저 제거를 이용하여 형성된 베이스 접촉 디퓨전

- [0292] · 후측 베이스 접촉 디퓨전을 위해 사용되는 APCVD PSG

- [0293] · FSF 없음

- [0294] · 금속 증착은 스크린 프린팅, 레이저 트랜스퍼 프린팅, 잉크젯 프린팅, 에어로졸 프린팅 등과 같은 직접 라이팅 공정을 이용하여 수행될 수 있다.

[0295]

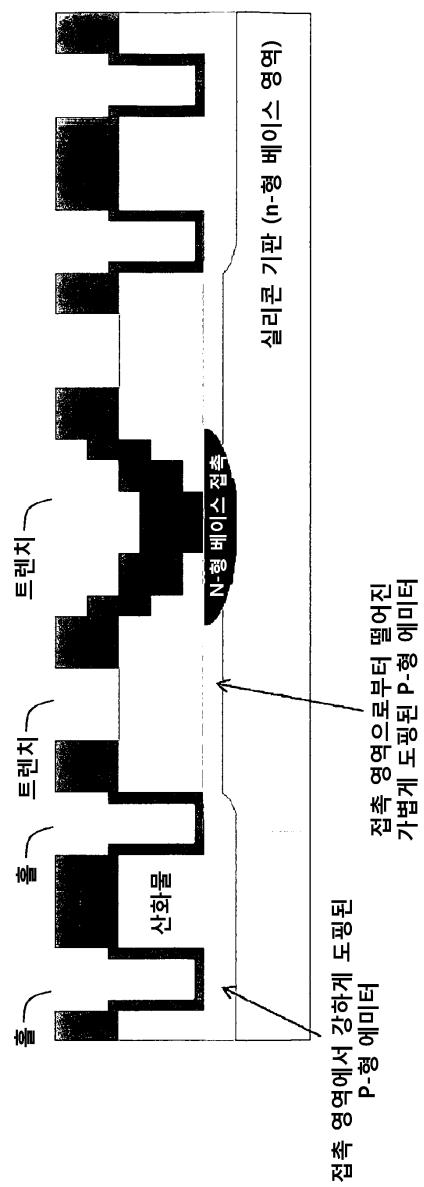

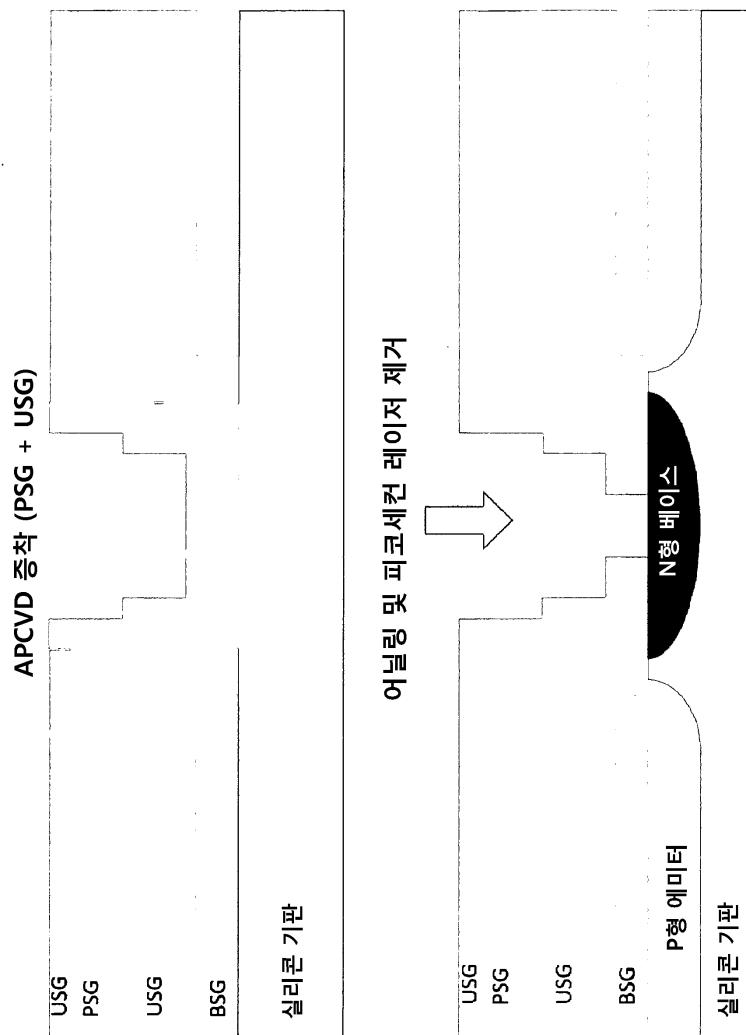

도 3에 설명되는 흐름 패밀리 1B 이외에, 추가적인 저온 필스 ps (또는 fs) 레이저 제거 단계와 함께, 2개의 분리 BSG 층 중착의 이용에 의해 후측 상에 선택적 에미터 구조체를 생성하는 것도 가능하고 바람직하다. APCVD 층 및 레이저 제거를 이용하는 이러한 선택적 에미터 구조체는, 에피택셜 중착된 막으로부터, CZ 웨이퍼로부터, MeV 주입 및 스플릿팅과 같은 고에너지를 이용하여 분열되는 것과 같은 달리 가공되는 흡수층으로부터 생성된 흡수층 상에 있게 되는(be they on absorber layers generated from epitaxially deposited films, from CZ wafer or from otherwise processed absorber layers such as those cleaved using high energy such as MeV implantation and splitting), 이전에 기재된 구조체 및 흐름 전체의 변형으로서 적용 가능하다. 도 46은 추가적인 BSG 층 및 피코세컨 레이저 제거 패터닝을 이용하여 선택적 에미터 구조체(더 가벼운 에미터 접합 도핑 및 더 무거운 에미터 접촉 도핑 농도를 가진)를 생성하기 위해 전지 공정 흐름을 도시한다. 도 47은 도 46의 흐름으로부터 얻어지는 전지 구조체의 단면도를 나타내는 도식이고, 상기 전지는 다양한 디퓨전 시트 저항을 갖는 2개의 BSG 중착에 의해 형성되는 선택적 에미터를 함유한다.

[0296]

도 46에 도시된 바와 같이, 세정된 템플레이트로 개시되는 다공성 실리콘 이중층 또는 층 구조가 형성된다. 가볍게 n형 도핑된 에피택셜막(일반적으로 약  $5 \times 10^{14} \text{ cm}^{-3}$  내지  $1 \times 10^{18} \text{ cm}^{-3}$ 의 범위의 인시투 베이스 도핑, 약  $5 \mu\text{m}$  내지  $100 \mu\text{m}$ 의 두께)이 중착된다. 베이스 인 도핑 농도는 에피택셜 성장 공정 동안 미리 구체화된 프로파일에 기반하여 변경될 수 있다(바람직하게는 약  $5 \times 10^{14} \text{ cm}^{-3}$  내지  $1 \times 10^{18} \text{ cm}^{-3}$ 의 범위). 이전에 설명한 바와 같이, 도핑은 예컨대 높은 Voc(높은 소수 캐리어 수명) 및 높은 충전율(감소된 기생 베이스 저항(parasitic base resistance))을 달성하기 위해 최적화된 도핑을 시행하도록 하나 이상의 도핑 레벨을 이용하여 선택적으로 수행된다. 이러한 최적화된 도핑은 장치의 태양이 비치는 측에 근접하여 더 높은 도핑이 시행되는 전면 전계로 이루어질 수 있다. 그러나, 다른 효과로부터지만, 결국 우수한 전면 재조합 속도를 야기할 수 있는 체제로 더 낮은 도핑을 갖는 것이 유리할 수도 있다(it may also be advantageous to have a lower doping in that regime, which in turn can also lead to a better front surface recombination velocity but from a different effect). 이 효과는 계면 상태의 밴드 위치에 대하여 표면에서의 밴드 라인업(band lineup)에 기인한 것으로 알려져 있고, 이러한 계면 상태가 덜 심하게 해준다.

[0297]

에피택셜 실리콘층 중착 후, 제1 BSG 층은, 후면 영역의 벌크에 가볍게 도핑된 에미터를 이후에 제공하기 위해 약간 낮은 농도의 보론으로 중착된다. 이 공정 후, 에미터 접촉이 형성될 영역의 레이저 제거(바람직하게는 피코세컨 레이저)가 이어진다. 이러한 그리고 이후의 구조화 공정은 구조 전체에 걸쳐 평행선을 유리하게 함유할 수 있다. 에미터 접촉 및 베이스 접촉 영역은 다른 맞물려진 패턴으로 열라인된다. 소정의 영역에서, 즉 이후의 공정에서 부스바가 금속 2 층 상에 위치되는(제2 금속 중착) 영역에서, 선형, 평행한, 맞물려진 베이스 및 에미터 접촉 패턴으로부터 빗나가는 것이 유리할 수 있다. 이러한 빗나감(deviation)은 각각의 부스바 하에서 경험되는 것과는 다른 전기적 셰이딩을 과감하게 저감하기 위해 적용된다. 이어서, 제2 BSG 층은 높게 도핑된 에미터 접촉 영역(예컨대 p++ 도핑을 갖는)을 제공하는 것과 같은 상대적으로 높은 농도의 보론으로 중착된다. 이어서, 베이스 접촉의 영역은 바람직하게는 피코세컨 레이저를 이용하여 레이저 제거된다. 이어서, PSG 층은 인 도핑된 베이스 접촉에 전구체로서 작용하기 위해 중착된다. 이어서, 도편트는, 선택적으로 질소와 같은 중성 주변(neutral ambient), 선택적으로 그 후에 산소 또는 증기와 같은 산화 주변(oxidizing ambient)을 함유할 수 있는(또한, 선택적으로 이후 더 낮은 온도의 게더링 및 최종 포밍 가스의 어닐링을 포함하는) 다기능 고온 공정 단계 동안 드라이빙된다. 접합은 이제 드라이빙된다. 이어서 바람직하게는 피코세컨 레이저를 이용하여 접촉 영역에 레이저 제거에 의해 접촉이 제조될 수 있다. 이어서, 금속 1(전지 가장 가까이에 위치된 금속 및 중착된 제1 금속)은 예컨대 Al, Ni 또는 NiV 및 Sn의 스택의 PVD를 이용, 이후 예컨대 피코세컨 레이저 제거를 이용하여 패터닝하거나, 또는 알루미늄 함유 페이스의 하나 이상의 층을 스크린 프린팅, 에어로졸 프린팅, 잉크젯 또는 다른 프린팅함으로써 중착 및 구조화된다. 알루미늄 페이스트는, 이후 어닐링 동안 접합으로 스파이킹을 줄이기 위한 제1층 일부 실리콘 또는 다른 스파이크 저감제를 함유하도록 선택될 수 있다. 금속 1의 구조체의 결과이기도한(also attributed to the structure of metal 1) 제2층에서, 페이스트 또는 잉크는, 금속 1과 금속 2 사이에 접촉을 만들기 위해 적용되는 이후 비아 접근 홀 드릴링(the later via access hole drilling)과 잘 조화를 이루도록 적합한 그레인(grain) 구조를 함유하기 위해 선택될 수 있다. 다른 선택 조건은 금속 1 (M1) 내에 낮은 선 저항을 갖기 위한 최적화된 도전성이다. 특히 더 낮은 잉크 또는 페이스트(lower ink or paste)에 있어서, 베이스 및 에미터에 낮은 접촉 저항을 위해 옳은 페이스트를 선택하는 것은 중요하다.