(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4940101号

(P4940101)

(45) 発行日 平成24年5月30日(2012.5.30)

(24) 登録日 平成24年3月2日(2012.3.2)

(51) Int.Cl.

H03M 3/02 (2006.01)

F 1

H03M 3/02

請求項の数 19 (全 12 頁)

(21) 出願番号 特願2007-277385 (P2007-277385)

(22) 出願日 平成19年10月25日 (2007.10.25)

(65) 公開番号 特開2008-109671 (P2008-109671A)

(43) 公開日 平成20年5月8日 (2008.5.8)

審査請求日 平成22年10月25日 (2010.10.25)

(31) 優先権主張番号 102006050175.6

(32) 優先日 平成18年10月25日 (2006.10.25)

(33) 優先権主張国 ドイツ(DE)

(73) 特許権者 390023711

ローベルト ポツシュ ゲゼルシヤフト

ミット ペシユレンクテル ハフツング

ROBERT BOSCH GMBH

ドイツ連邦共和国 シュツットガルト (番地なし)

Stuttgart, Germany

(74) 代理人 100061815

弁理士 矢野 敏雄

(74) 代理人 100135633

弁理士 二宮 浩康

(74) 代理人 100114890

弁理士 アインゼル・フェリックス=ライ

ンハルト

最終頁に続く

(54) 【発明の名称】 ΔΣデータ変換装置およびΔΣデータ変換装置の検査方法

## (57) 【特許請求の範囲】

## 【請求項 1】

データ変換装置において、少なくとも、

アナログ入力信号(S1)を受け取って、デジタルデータストリーム信号(S2)を出力するアナログ変調器(3)と、

少なくとも前記デジタルデータストリーム信号(S2)を受け取って、デジタル出力信号(S4)を出力するデジタルフィルタ装置(6, 7)と、

前記デジタルデータストリーム信号(S2)から導出された信号(S4)に応じてテスト信号(S5, S6)を生成するテスト信号発生器(9, 11, 12, 14)と、

前記テスト信号(S5)を受け取って、デジタル基準データストリーム信号(S8)を出力するデジタル基準装置(8)と、 10

前記デジタルデータストリーム信号(S2)と前記デジタル基準データストリーム信号(S8)を受け取って、少なくとも前記デジタルデータストリーム信号(S2)と前記デジタル基準データストリーム信号(S8)を前記デジタルフィルタ装置(6, 7)に出力する信号受け取り装置(13, 5)を有していることを特徴とする、データ変換装置。

## 【請求項 2】

信号受け取り装置(13, 5)は制御信号(S7)に応じて前記デジタルデータストリーム信号(S2)または前記デジタル基準データストリーム信号(S8)またはこれら両方の信号(S2, S8)から求められた信号(S10)を前記デジタルフィルタ装置(6

10

20

, 7 ) に出力する、請求項 1 記載の データ変換装置。

**【請求項 3】**

信号受け取り装置 ( 13 , 5 ) はデジタル加算器 ( 13 ) とスイッチ装置 ( 5 ) とを有しており、デジタル加算器 ( 13 ) は前記デジタルデータストリーム信号 ( S2 ) と基準データストリーム信号 ( S8 ) の差信号 ( S10 ) を形成し、スイッチ装置 ( 5 ) は制御信号 ( S7 ) に応じて前記差信号 ( S10 ) を出力するか、または前記デジタルデータストリーム信号 ( S2 ) と前記デジタル基準データストリーム信号 ( S8 ) とを出力する、請求項 2 記載の データ変換装置。

**【請求項 4】**

テスト信号発生器 ( 9 ) はデジタルフィルタ装置 ( 6 , 7 ) のデジタル出力信号 ( S4 ) を受け取り、該デジタル出力信号 ( S4 ) に応じてデジタルテスト信号 ( S5 ) を出力する、請求項 1 から 3 のいずれか 1 項記載の データ変換装置。 10

**【請求項 5】**

テスト信号発生器 ( 9 ) は、デジタル基準装置 ( 8 ) にはデジタルテスト信号 ( S5 ) を出力し、アナログ 変調器 ( 3 ) にはデジタルテスト信号 ( S5 ) に相応するアナログテスト信号 ( S6 ) を出力する、請求項 1 から 4 のいずれか 1 項記載の データ変換装置。

**【請求項 6】**

テスト信号発生器 ( 9 ) はデジタルテスト信号 ( S5 ) を相応するアナログテスト信号 ( S6 ) に変換するデジタルアナログ変換器 ( 12 ) を有しており、該デジタルアナログ変換器 ( 12 ) の基準電圧はアナログ 変調器 ( 3 ) の基準電圧に相当する、請求項 5 記載の データ変換装置。 20

**【請求項 7】**

デジタル基準装置 ( 8 ) はデジタル 基準変調器 ( 8 ) を有しており、該デジタル 基準変調器 ( 8 ) は、アナログ 変調器 ( 3 ) の伝達関数をデジタル計算アルゴリズムとしてモデル化し、デジタルデータストリーム信号 ( S2 ) と同じワード幅および帯域幅のパルス密度変調されたデジタル基準データストリーム信号 ( S8 ) を出力する、請求項 1 から 6 のいずれか 1 項記載の データ変換装置。

**【請求項 8】**

テスト信号発生器 ( 9 ) は、パルス密度変調されたデータストリームとしてデジタルテスト信号 ( S5 ) を生成するデジタル 変調器 ( 11 ) を有している、請求項 1 から 7 のいずれか 1 項記載の データ変換装置。 30

**【請求項 9】**

デジタルフィルタ装置 ( 6 , 7 ) はフィルタリングおよびダウンサンプリングのためのデシメーションフィルタ ( 6 ) と、雑音成分の抑制および有効帯域における伝達特性の補償のためのデジタルローパスフィルタ ( 7 ) を有している、請求項 1 から 8 のいずれか 1 項記載の データ変換装置。

**【請求項 10】**

完結した集積回路として形成された、請求項 1 から 9 のいずれか 1 項記載の データ変換装置。 40

**【請求項 11】**

アナログ入力信号 ( S1 ) を受け取って、デジタルデータストリーム信号 ( S2 ) を出力するアナログ 変調器 ( 3 ) と、デジタルデータストリーム信号 ( S2 ) を受け取って、デジタル出力信号 ( S4 ) を出力するデジタルフィルタ装置 ( 6 , 7 ) とを具えた

データ変換装置 ( 2 ) を検査する方法において、アナログ 変調器 ( 3 ) とデジタル基準装置 ( 8 ) にテスト信号 ( S5 , S6 ) を供給し、アナログ 変調器 ( 3 ) により出力されたデジタルデータストリーム信号 ( S2 ) とデジタル基準装置 ( 8 ) により出力されたデジタル基準データストリーム信号 ( S8 ) をデジタルフィルタ装置 ( 6 , 7 ) に出力し、デジタルフィルタ装置 ( 6 , 7 ) により出力されたデジタル出力信号 ( S4 ) を評価することを特徴とする、 データ変換装置 ( 2 ) を検査する方法。 50

**【請求項 1 2】**

アナログ 変調器(3)の前記デジタルデータストリーム信号(S2)またはデジタル基準装置(8)の前記デジタル基準データストリーム信号(S8)またはこれらの信号(S2, S8)から形成された差信号(S10)を選択的にデジタルフィルタリングし、評価する、請求項11記載の方法。

**【請求項 1 3】**

第1のテストモード(BIST1)において、テスト信号発生器(9)にテストデータ入力信号(S9)を供給し、続いてデジタル出力信号(S4)をテストデータ入力信号(S9)と比較する、ただし、前記テスト信号発生器(9)はデジタルテスト信号(S5)を生成してデジタル基準装置(8)に出力するものである、請求項11または12記載の方法。10

**【請求項 1 4】**

第2のテストモード(BIST2)において、デジタルフィルタ装置(6, 7)により出力されたデジタル出力信号(S4)をテスト信号発生器(9)にフィードバックさせる、請求項11または13記載の方法。

**【請求項 1 5】**

フィードバックにより同期したデジタルネットワークを構築し、テストパターンを繰り返し形成して評価する、請求項14記載の方法。

**【請求項 1 6】**

第3のテストモードにおいて、デジタル基準装置(8)にはデジタルテスト信号(S5)を供給し、アナログ 変調器(3)にはデジタルテスト信号(S5)に相応するアナログテスト信号(S6)を供給し、アナログ 変調器(3)により出力されたデジタルデータストリーム信号(S2)とデジタル基準装置(8)により出力されたデジタル基準データストリーム信号(S8)を相互に比較する、請求項11から15のいずれか1項記載の方法20

**【請求項 1 7】**

デジタルデータストリーム信号(S2)とデジタル基準データストリーム信号(S8)とから差信号(10)を形成し、選択的にデジタルデータストリーム信号(S2)またはデジタル基準データストリーム信号(S8)または差信号(10)をデジタルフィルタ装置(6, 7)を介してデジタル出力信号(S4)として出力し、評価する、請求項16記載の方法。30

**【請求項 1 8】**

デジタルカウンタを用いてテストデータ入力信号(S9)の値域を重複無くカウントし、差信号(S10)をアナログ 変調器(3)の誤差曲線として評価する、その際、テストデータ入力信号(S9)のワード幅( $n_{in}$ )が誤差曲線の $2^{**} n_{in}$ 個のデータ点を決定する、請求項17記載の方法。

**【請求項 1 9】**

データ変換装置(2)のオフセット、勾配、および非線形誤差を求め、少なくとも部分的に補償する、請求項11から18のいずれか1項記載の方法。

**【発明の詳細な説明】**

40

**【技術分野】**

**【0001】**

本発明は データ変換装置および データ変換装置の検査方法に関する。

**【背景技術】**

**【0002】**

変調の原理に従ったデータ変換器は様々な用途に用いられている。これらのデータ変換器は有利な線形特性を有しており、とりわけ、限られた帯域幅で高い分解能が必要とされるアプリケーションにおいて使用される。有利な使用分野は例えばセンサ信号の評価などの信号処理における アナログデジタル変換器(ADC)である。

**【0003】**

50

変調器の場合、変換すべき信号は、ワード幅がたいてい1ビットと小さくかつ帯域幅の広い、パルス幅変調された信号列の形で表される。この場合、変調器の出力信号はこの変調器の内部でデジタルアナログ変換器を経た後に入力側にフィードバックされる。ワード幅が小さいので、必要な構造が、とりわけD/A変換器が簡単に表現され、高い線形性が得られる。

#### 【0004】

原則的にオーバーサンプリング(つまり、サンプリングレートによって決まる帯域幅が有効信号幅に比べて非常に大きい場合)と入力信号の高い分解能が必要とされるため、検査装置には高い要求が課される。特に大量生産の場合には、検査装置の精度に対する要求のゆえに、解決手段が過度に高コストかつコスト集約的になってしまふ。高分解能は上に述べたオーバーサンプリングと相俟って長いテスト時間とそれに相応して高い単価の原因となる。10

#### 【0005】

テスト時間を最小化し、必要となるテスト信号を内部的に生成するためには、外部検査装置に加えて、部分的に内部検査装置も設けられる。変換器の特性決定とテストのために、すでに様々な自己テストの方法、とりわけBIST(組込自己テスト)とその実装とが公開されている。

#### 【0006】

非特許文献1では、2次変調器に基づいたBISTアーキテクチャが提案されている。そこでは、デジタルテスト信号を用いた変調器のテストないし特性決定に適したDesign-For-Testability(DfT)回路が提供されている。しかしながら、この場合、BIST法の評価は実質的にソフトウェアで行われる。20

#### 【0007】

非特許文献2には、A/D変換器の4つのキーパラメータ、すなわち、オフセット誤差、増幅誤差、積分非線形性、および微分非線形性を測定するためのBIST法が記載されている。そこでは、アナログ正弦波テスト信号とデジタル正弦波基準信号をチップ上で(on Chip)生成する変調器が説明されている。この場合、アナログデジタル変換器の出力信号は生成されたデジタル基準信号の出力信号と比較される。その際、パラメータはこのために求められた方程式に基づいて決定される。しかしながら、このような方法およびこのようなテスト回路では、ICにかかる所要ハードウェアコストが高い。30

【非特許文献1】Chee-Kian Ong, Kwang-Ting (Tim) Cheng and Li-C. Wang "Delta-sigma Modulator Based Mixed-signal BIST Architecture for SoC" Design Automation Conference, 2003, Proceedings of the ASP-DAC 2003, Asia and South Pacific 21-24 Jan., 2003 Page(s): 669 - 674

【非特許文献2】Kuen-Jong Lee; Soon-Jyh Chang; Ruei-Shiuan Tzeng, "A Delta-Sigma modulation based BIST scheme for A/D Converters"; Test Symposium, 2003, ATS 2003, 12111 Asian 16-19 Nov. 2003 Pages 124-127

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0008】

本発明の課題は従来のデータ変換装置に比べて回路コストの低いデータ変換装置とその検査方法を提供することである。

#### 【課題を解決するための手段】

#### 【0009】

本発明の課題は、少なくとも、

アナログ入力信号を受け取って、デジタルデータストリーム信号を出力するアナログ変調器と、

少なくとも前記デジタルデータストリーム信号を受け取って、デジタル出力信号を出力するデジタルフィルタ装置と、

前記デジタルデータストリーム信号から導出された信号に応じてテスト信号を生成する4050

テスト信号発生器と、

前記テスト信号を受け取って、デジタル基準データストリーム信号を出力するデジタル基準装置と、

前記デジタルデータストリーム信号と前記デジタル基準データストリーム信号を受け取って、少なくとも前記デジタルデータストリーム信号と前記デジタル基準データストリーム信号を前記デジタルフィルタ装置に出力する信号受け取り装置を有していることを特徴とする データ変換装置により解決される。

#### 【0010】

同様に、本発明の課題は、アナログ入力信号を受け取って、デジタルデータストリーム信号を出力するアナログ 变調器と、デジタルデータストリーム信号を受け取って、デジタル出力信号を出力するデジタルフィルタ装置とを具えた データ変換装置を検査する方法において、アナログ 变調器とデジタル基準装置にテスト信号を供給し、アナログ 变調器により出力されたデータストリーム信号とデジタル基準装置により出力された基準データストリーム信号をデジタルフィルタ装置に出力し、デジタルフィルタ装置により出力されたデジタル出力信号を評価することにより解決される。

#### 【発明を実施するための最良の形態】

#### 【0011】

本発明によれば、ハードウェアベースで、とりわけオンチップで、 データ変換器の自己テストが可能となる。本発明では、有利には、 データ変換器のアナログモジュールもデジタルモジュールもテストすることができる。

#### 【0012】

本発明によれば、 A D C とそれを検査する検査装置が提供される。ここで、 A D C は - 周知のように - アナログ入力信号の受け取りとデジタルデータストリームの出力をを行う 变調器と、このデータストリームを受け取るデジタルフィルタ装置とを有している。

#### 【0013】

本発明の基本思想は、検査装置において内部的にテスト信号を、有利には最小ワード幅のテスト信号を生成し、それをデジタル式の基準装置へ入力することにある。なお、この基準装置とは、検査すべきアナログ 变調器の理想的な特性を有し、基準信号をデジタルフィルタ装置に出力するものである。その際、個々のコンポーネントの検査を可能にする種々のテストモードを順次実行してよい。

#### 【0014】

本発明によれば、パルス密度変調された信号列を表す自らの出力信号を自らの入力側に内部的にフィードバックさせる 变調器の特別な特性が利用される。本発明によれば、この状況は次のようにして利用される。すなわち、デジタルテスト信号を検査装置で内部的に生成する際に、デジタルテスト信号が有利には小さなワード幅または最小のワード幅を有し、かつ、その帯域幅が有利には検査すべき 变調器の変調された出力信号の帯域幅と実質的に同じであるようにすることで、上記状況は利用される。

#### 【0015】

したがって、このテスト信号を検査装置によってアナログ信号路に入力結合するにあたって、 变調器内で出力信号のフィードバックまたはアナログ入力信号のサンプリングに使用されるのと同じ装置を使用することができる。

#### 【0016】

ここで、デジタル基準装置はとりわけアナログ 变調器をデジタル計算モデルとしてモデル化したデジタル 变調器、すなわち、特にアナログ 变調器の伝達関数ないし z 変換をモデル化したデジタル 基準変調器とすることができる。テスト信号発生器がデジタル基準装置にはデジタルで、検査すべき 变调器にはアナログでテスト信号を送るようにすることで、入力信号が基本的に同一ないし一致するならば、両方の変調器の出力を適切な切り換えによって相互に比較することができ、出力値の偏差は直接、誤差ないし不正確として認識される。

10

20

30

40

50

## 【0017】

テスト信号発生器としては、再びデジタル変調器を用いることができる。デジタル変調器はテスト信号としてデータストリームを、ここでは特に1ビットのワード幅のデータストリームを出力することができる。テスト信号発生器には、一方では、例えば所定の値を走る所定のテストデータが例えば外部制御装置から供給され、他方では、デジタル出力信号がフィードバックされる。

## 【0018】

1ビットのワード幅が例えば値域 (+1, -1) におけるものであれば、テスト信号の D / A 変換は基準電圧のサンプリングによって行うことができる。この D / A 変換の基準電圧が A D C の基準電圧と同一であり、かつ A D C の入力構造がサンプリングに利用されるならば、アナログ信号路へのデジタルテスト信号の最適な入力結合が可能である。

10

## 【0019】

本発明によれば、1つにはその構造のおかげで、テスト信号の入力結合の際に、少なくとも検査すべき変調器の精度に相当する精度を得ることができる。さらに、帯域幅の大きなテスト信号を供給することもできる。このため、全値域にわたる完全検査のテスト時間の最適化が可能になる。

## 【0020】

本発明によれば、様々なテスト方式が可能である。第1のテストモードは基本的な機能検査に使用することができる。テスト信号発生器に直接入力されたテストデータは、後でアナログ変調器のより正確な検査が行われるように、まず、デジタル基準変調器を介して、テスト信号発生器と基準変調器とデジタルフィルタの性能ないし機能の検査に使用することができる。

20

## 【0021】

第2のテストモードでは、第1のテスト方式を変形して、テスト信号発生器の入力側にデジタル出力信号が印加される。それにより、信号路全体が同期したデジタルネットワークとして動作するので、テストは出力データが相応するシミュレーション結果と同一であるかを「テストパターン」に基づいて繰り返し検査することにより行うことができる。

## 【0022】

第3のテストモードでは、変調器にはアナログでテスト信号を供給し、基準変調器にはデジタルで供給することにより、検査すべきアナログ変調器がデジタル基準変調器と比較される。その際、基準モデルの入力値域を極端に制限することによって、例えば (+1, -1) に制限することによって、内部的なワード幅は比較的小さくなり、ひいては面積最適化された実装に通じる。

30

## 【0023】

計算された差は有効信号と両方の変調器のそれぞれの量子化雑音とを重ね合わせたものである。有効信号（理想的に一致した場合）の差として値「0」が得られるのに対して、雑音は無相関に重なり合う。したがって、変調器の場合と同様に、有効帯域外の雑音成分は相応のフィルタリングによって除去しなければならない。

## 【0024】

40

このフィルタリングは通常動作時と同じくテスト動作時にも「デシメーションフィルタ」とそれに後置された「ローパスフィルタ」によって行うことができる。これらのデジタルフィルタ段はワード幅を広げると同時に信号帯域幅を狭くするように作用する。 A D C のこれらフィルタ段は、テスト動作時には、検査すべき変調器と基準モデルの雑音成分を除去するために使用される。

## 【0025】

それゆえ、種々のテスト動作様式を切り換えることにより、装置全体の間断のない機能的なテストが連続して行われる。フィルタリングされた出力値はデジタル形式であるので、そのままデータ変換器の各動作点における理想的な伝達特性からの偏差の尺度として、すなわち、誤差曲線として考慮しうる。この結果から、可能な誤差項、特にオフセッ

50

ト、勾配、および非線形誤差が周知の数学的方法によって導かれ、場合によっては、相応の補正計算により補償される。

#### 【0026】

本発明によれば、必要とされる回路技術上の追加コストをほぼ完全にデジタルで表すことができる。これにより、テスト回路への制御不能なパラメトリックな影響を任意の高い精度で除去することができる。さらに、シリコン面の形態で費用面でのコストを低く保つことができる。これは 変換器の製造に従来使用されてきた半導体プロセスにおいても既に実行可能である。

#### 【実施例】

##### 【0027】

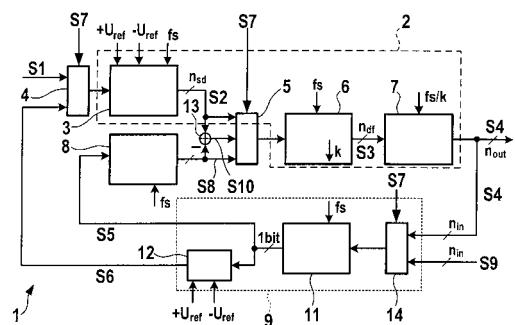

データ変換装置 1 は、図 1 によれば、破線で区画された アナログデジタル変換器 (ADC) 2 を有している。 アナログデジタル変換器 2 は、例えばセンサの測定信号などのアナログ入力信号 S1 を受け取り、それ自体公知の仕方でデジタル出力信号 S4 を出力する。このデジタル出力信号 S4 は例えば下位の制御装置または評価装置によって受け取られる。このために、 ADC 2 は、通常動作には関係のない、スイッチとして機能する入力マルチプレクサ 4 を介してアナログ入力信号 S1 を受け取るアナログデルタシグマ変調器 ( 变調器 ) 3 を有している。

##### 【0028】

アナログ 变调器 3 はその入力段において、それ自体公知の仕方で、高サンプリング周波数 f\_s でのサンプリングによりアナログ入力信号 S1 の時間離散化を行う。その際、

变调器 3 は基準電圧 + U\_ref および - U\_ref に接続されており、それゆえアナログ電圧信号 S1 は、U\_ref によって定まる電圧領域内で、狭いワード幅 n\_sd と帯域幅 f\_s / 2 をもったパルス密度変調されたデジタルデータストリーム信号 S2 を出力する。アナログ

变调器 3 は、例えば、アナログ電圧値を積分ないし積算するための積分器と、例えばコンパレータによって形成される量子化器と、場合によっては、印加されるクロック信号 f\_s に応じてデータストリーム信号 S2 を出力する出力メモリとを具えた従来の構造を有しており、この構造において、デジタルアナログ変換器を介してアナログ加算器へ出力信号ないしデジタルデータストリーム信号 S2 の負のフィードバックが行われる、または、検出すべきアナログ入力信号 S1 とこのアナログフィードバック信号との差が求められる。したがって、データストリーム S2 は、アナログ入力信号 S1 に応じて、パルス密度変調された信号として形成される。アナログ 变调器 3 は有利にはワード幅 n\_sd = 1 ピットで構成しうる。そのため、信号 S2 はパルス密度変調されたビットストリームを形成することとなり、これにより高い線形性がもたらされる。クロック信号 f\_s は例えば 2 ~ 3 MHz の範囲とすることでき、後に outputされるデジタル出力信号 S4 に比べて、1 に対して例えば 1000 という範囲の、非常に高い明らかなオーバーサンプリングを提供する。

##### 【0029】

デジタルデータストリーム S2 はスイッチとして機能するマルチプレクサ 5 を介してデジタルデシメーションフィルタ 6 に供給される。デジタルデシメーションフィルタ 6 はフィルタリングと間引き率 k でのダウンサンプリングとを行い、n\_df >> n\_sd のワード幅 n\_df と帯域幅 f\_s / 2 k をもつ出力信号 S3 を供給する。信号路上で後置されたデジタルローパスフィルタ 7 はこの信号 S3 を受け取り、それに含まれている雑音成分の抑制と有効帯域における伝達特性の補償とに使用される。デジタルローパスフィルタ 7 はワード幅 n\_out のデジタル出力信号 S4 を出力する。

##### 【0030】

本発明によれば、ADC 2 を検査する検査装置がさらに設けられており、この検査装置はデジタル基準装置として機能するデジタル 基準変調器 8 とテスト信号発生器 9 を有している。ここで、既に述べたマルチプレクサ 4 および 5 とテスト信号発生器 9 内に設けられたマルチプレクサ 10 はスイッチとして機能する。

##### 【0031】

テスト信号発生器 9 は有利には低次の、例えば 1 次の、デジタル 变调器 11 を有し

10

20

30

40

50

ており、デジタル 変調器 1 1 はその入力信号から 1 ビットのワード幅と  $f_s / 2$  の帯域幅をもつデジタルテスト信号 S 5 を生成する。デジタルテスト信号 S 5 はデジタル基準変調器 8 に直接入力され、さらに 1 ビット D / A 変換器 1 2 を介してアナログテスト信号 S 6 に変換される。その際、例えばデジタル値域 (+ 1, - 1) は相応するアナログ値域 ( $+ U_{ref}$ ,  $- U_{ref}$ ) に写像される。ここで、 $U_{ref}$  は有利にはアナログ 変調器 3 の基準電圧に相当する。アナログテスト信号 S 6 はマルチプレクサ 4 に出力される。マルチプレクサ 4 は制御信号 S 7 によって駆動され、制御信号 S 7 に応じて選択的にアナログ入力信号 S 1 またはアナログテスト信号 S 6 をアナログ 変調器 3 に出力する。

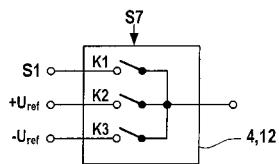

#### 【 0 0 3 2 】

図 3 には、アナログ入力信号 S 1 とアナログ値で記述される基準電圧  $+ U_{ref}$  および  $- U_{ref}$  のための 3 つの入力側を有する共通のスイッチによって DAC 1 2 と入力マルチプレクサ 4 を組み合わせた回路技術的に単純な構造が示されている。ここで、2 進値 [ 0, 1 ] を  $[ - U_{ref}, + U_{ref} ]$  に写像するため、 $S_7 = , , 0$  のときにはスイッチ K 2, K 3 が開き、スイッチ K 1 は閉じ、 $S_7 = , , 1$  のときにはスイッチ K 1 が開き、K 2 または K 3 は S 5 に応じて交互に閉じる。したがって、K 2 のスイッチ位置は S 5 により制御され、相応して K 3 のスイッチ位置は反転値 NOT ( S 5 ) により制御される。これに相応して、アナログ信号 S 6 は  $+ U_{ref}$  または  $- U_{ref}$  の接続によって直接形成される。

#### 【 0 0 3 3 】

デジタル基準変調器 8 はアナログ 変調器 3 の伝達関数 ( Z 変換 ) を正確なデジタル計算アルゴリズムの形で理想的にモデル化する。デジタル基準変調器 8 はデジタル入力信号 S 5 からワード幅  $n_{sd}$  と帯域幅  $f_s / 2$  とをもつパルス密度変調されたデジタル基準データストリーム信号 S 8 を形成する。ここで、デジタル 基準変調器 8 は有利にはハードウェア的に形成されているが、デジタル計算アルゴリズムは原則的に例えばソフトウェア的にも実行することができる。

#### 【 0 0 3 4 】

デジタル加算器 1 3 はアナログ 変調器 3 とデジタル基準変調器 8 の出力信号の差信号  $S_{10} = S_2 - S_8$  を形成する。この信号のワード幅  $n_{sd}$  は有利には 1 ビットと小さいので、これに相応してデジタル加算器 1 3 のための回路技術上のコストも同様に低い。

#### 【 0 0 3 5 】

テスト信号発生器 9 のデジタル 変調器 1 1 にはまた別のマルチプレクサ 1 4 が前置接続されており、このマルチプレクサ 1 4 はデジタル出力信号 S 4 とさらにテストデータ入力信号 S 9 を受け取り、制御信号 S 7 に応じてこれらの信号 S 4, S 9 のうちの一方を通す。ここで、テストデータ入力信号 S 9 はデジタル出力信号 S 4 のワード幅に相当するワード幅  $n_{in}$  を有している。

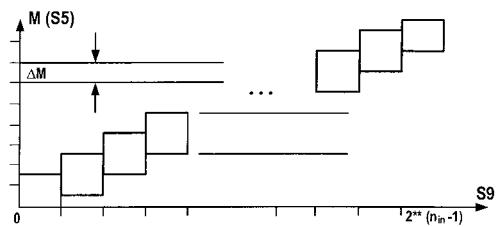

#### 【 0 0 3 6 】

テスト信号 S 5 は変調されたテストデータ信号 S 9 またはフィードバックされた出力信号 S 4 と 変調器 1 1 の量子化雑音の成分とから構成されている。テストデータ入力信号 S 9 のワード幅は、図 2 に従って、全入力範囲にわたる量子化雑音のレベルがテストデータ入力信号 S 9 の LSB ( 最下位ビット ) に関してステップ幅 M よりも大きくなるように選ばれる。このようにしてテスト信号 S 5 は生成される。テスト信号 S 5 は、一方では、図 2 の横軸に示された少数の、有利には  $2 \times p ( n_{in} - 1 )$  の、データ点を有する特性曲線全体をカバーする本来の有効帯域におけるワード幅が小さいという理由から、他方では、同様にテスト信号 S 5 の構成成分として有効な広帯域雑音が重畠されているという理由から、検査すべき ADC 2 の全値域を刺激する。

#### 【 0 0 3 7 】

制御信号 S 7 を用いれば、アナログ入力信号 S 1 を受け取ってデジタル出力信号 S 4 を出力する通常動作モードの他に、それぞれ BIST ( 組込自己テスト ) テストモードを表す少なくとも 3 つのテストモードを選択することができる。

#### 【 0 0 3 8 】

第 1 および第 2 のテストモードでは、装置のデジタルコンポーネントがテストされる。

10

20

30

40

50

アナログ　　変調器 3 の出力側はこの動作モードでは使用されない。

【 0 0 3 9 】

第 1 のテストモードは基本的な機能検査に使用される。マルチプレクサ 1 4 を介してデジタルテストデータ信号 S 9 はテスト信号発生器 9 の入力側に印加される。テスト信号発生器 9 はこのデジタルテストデータ信号 S 9 からデジタルテスト信号 S 5 を形成し、基準変調器 8 に出力する。基準変調器 8 によって出力された基準データストリーム信号 S 8 はマルチプレクサ 5 を経てデシメーションフィルタ 6 の入力側に達し、そこからローパスフィルタ 7 を経て出力信号 S 4 として出力される。それゆえ、この動作モードにおいては出力信号 S 4 が入力データの像であり、直接比較によって機能的に検査される。

【 0 0 4 0 】

第 2 のテストモードは、第 1 のテストモードの変形として、テスト信号発生器 9 のテストデータ入力側への出力信号 S 4 のフィードバックにより行われる。S 4 の有利には下位  $n_{in}$  ビットの負のフィードバックにより、上で述べた信号路全体を短期間のあいだ全値域にわたって刺激する広帯域の疑似ランダムテスト信号 S 5 が生じる。

【 0 0 4 1 】

この動作モードにおいて全信号路は同期したデジタルネットワークとして機能するので、本来のテストは、出力データ S 4 が相応するシミュレーション結果と同一であるかを「テストパターン」に基づいて繰り返し検査することにより行うことができる。「テストパターン」の誤差シミュレーションにより、所定のテストマスクに達するのに最適な検査持続時間が定められる。このようにして、スキャンパスを用いた構造的テストに代わって、デジタル装置の意図された機能を自動的に生成される刺激によって固定マスクを監視することで検査することができる。

【 0 0 4 2 】

第 3 のテストモードでは、同じ刺激の下でアナログ　　変調器 3 の出力データストリームをデジタル基準変調器 8 の出力データストリームと比較することにより、アナログ変調器 3 が検証される。

【 0 0 4 3 】

テストデータ入力信号 S 9 はマルチプレクサ 4 を経てデジタル　　変調器 1 1 に達し、デジタル　　変調器 1 1 の出力側にワード幅 1 ビット、帯域幅  $f_s / 2$  のパルス密度変調されたテスト信号 S 5 として現れる。値域 (+ 1, - 1) のデジタルテスト信号 S 5 はふたたび基準変調器 8 に入力されるのと同時に、相応する値域 (+  $U_{ref}$ , -  $U_{ref}$ ) のアナログ形式 S 6 で、検査すべきアナログ　　変調器 3 の入力信号として使用される。デジタル加算器 1 3 は差信号  $S_{10} = S_2 - S_8$  を形成し、差信号 S 10 はマルチプレクサ 1 3 を介して後続のフィルタ段 6 および 7 に転送される。変調器 3 および 8 の量子化雑音の高周波雑音成分はフィルタ段で除去され、信号帯域幅は  $f_s / 2 k$  に低減される。それゆえ、残余信号 S 4 は S 10 の有効信号帯域の差を表す。両方の変調器が同じ入力信号で刺激されるので、S 4 における結果は　　変調器 3 の理想的な基準モデル 8 からの偏差であり、S 9 によって決まる動作点においてのそのつどの誤差を表す。S 9 の値域を例えばデジタルカウンタが直線的に走破することにより、出力側 S 4 では  $2^{n_{in}}$  個のデータ点をもつ　　A D C の誤差曲線が得られる。

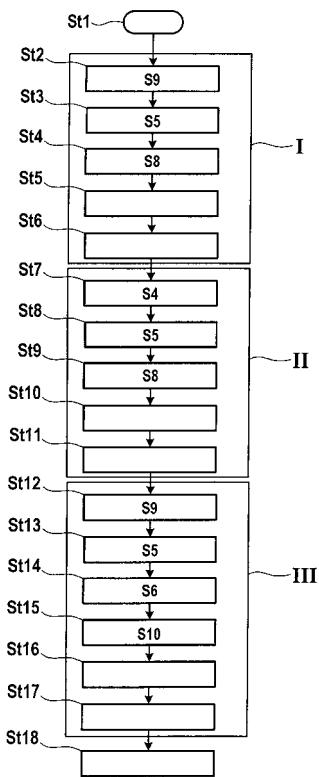

【 0 0 4 4 】

図 4 には、フローチャートの一例が示されている。このフローチャートにおいて、テストモード B I S T 1 , 2 , 3 は I , I I , I I I で表されており、連続して実行される。このために、制御装置を介して外部から制御信号 S 7 がマルチプレクサ 4 , 5 , 1 4 に入力され、テストデータ入力信号 S 9 がマルチプレクサ 1 4 に入力される。

【 0 0 4 5 】

ステップ S t 1 におけるスタートの後、まずステップ S t 2 に従ってテストモード B I S T 1 においてテストデータ入力信号 S 9 がテスト信号発生器 9 に入力され、ステップ S t 3 においてテスト信号発生器 9 によりデジタルテスト信号 S 5 が生成および出力され、その後、ステップ S t 4 において、デジタル　　基準変調器 8 によりデジタルテスト信号

10

20

30

40

50

S 5 からデジタル基準データストリーム信号 S 8 が生成される。デジタル基準データストリーム信号 S 8 はステップ S t 5 においてデジタルフィルタ装置 6 , 7 によりフィルタリングされ、その後、ステップ S t 6 において評価される。

**【 0 0 4 6 】**

テストモード B I S T 2 では、ステップ S t 7 においてデジタル出力信号 S 4 がテスト信号発生器 9 に供給され、ステップ S t 8 においてテスト信号発生器 9 によりデジタルテスト信号 S 5 が出力され、デジタル 基準変調器 8 に供給され、ステップ S t 9 においてデジタル 基準変調器 8 により基準データストリーム信号 S 8 が形成される。この基準データストリーム信号 S 8 はその後ステップ S t 10 においてフィルタリングされ、ステップ S t 11 において評価される。

10

**【 0 0 4 7 】**

続いて、テストモード B I S T 3 が実行される。テストモード B I S T 3 によれば、ステップ S t 12 において信号 S 9 が入力され、ステップ S t 13 においてまず再度デジタルテスト信号 S 5 が形成され、続いてステップ S t 14 においてデジタルアナログ変換器 12 によりこのデジタルテスト信号 S 5 からアナログテスト信号 S 6 が形成され、マルチブレクサ 4 を介してアナログ 变調器 3 に供給される。続いて、ステップ S t 15 において差信号 S 10 が形成され、ステップ S t 16 におけるフィルタリングの後、ステップ S t 17 において評価される。その際、B I S T 3 では補足的に信号 S 2 および S 8 も個々にフィルタリングし、評価してよい。

**【 0 0 4 8 】**

20

このように、自己テストプロセスないし検査プロセスはステップ S t 17 で終了するので、続くステップ S t 18 においてアナログ入力信号 S 1 の受信および評価によって測定を開始することができる。

**【図面の簡単な説明】**

**【 0 0 4 9 】**

**【図 1】**本発明の 1 つの実施形態による データ変換器の回路図を信号ないしデータの推移とともに示す。

**【図 2】**テストデータ入力信号に依存するデジタルテスト信号の強度グラフを示す。

**【図 3】**図 1 のテスト信号発生器のアナログ入力マルチブレクサと D / A 変換器の組合せ実施形態を示す。

30

**【図 4】**本発明によるテスト方法のフローチャートを示す。

**【 符号の説明】**

**【 0 0 5 0 】**

- 1 データ変換装置

- 2 アナログデジタル変換器

- 3 アナログ 变调器

- 4 マルチブレクサ

- 5 マルチブレクサ

- 6 デジタルデシメーションフィルタ

- 7 デジタルローパスフィルタ

- 8 基準変調器

- 9 テスト信号発生器

- 10 マルチブレクサ

- 11 デジタル 变调器

- 12 デジタルアナログ変換器

- 13 デジタル加算器

- 14 マルチブレク

40

【図1】

【図4】

【図2】

【図3】

---

フロントページの続き

(72)発明者 マティアス ベッカート

ドイツ連邦共和国 ロイトリンゲン ケーテ - コルヴィッツ - シュトラーセ 9

(72)発明者 トーマス ヴィーヤ

ドイツ連邦共和国 ゴーマリンゲン マーダッハシュトラーセ 12

(72)発明者 マルコ ノイシェーラー

ドイツ連邦共和国 ロイトリンゲン ホーエンシュタウフェンシュトラーセ 32

(72)発明者 マルクス ブロックマン

ドイツ連邦共和国 テュービンゲン シェーフシュトラーセ 33

(72)発明者 クリストフィアーネ ヘニング

ドイツ連邦共和国 テュービンゲン オットー - エアベ - ヴェーク 76

審査官 北村 智彦

(56)参考文献 特開平06-224772(JP,A)

特開平04-231883(JP,A)

Kuen-Jong Lee, Soon-Jyh Chang, Ruei-Shiuan Tzeng, A Sigma-Delta Modulation Based BIST Scheme for A/D Converters, Proceedings of the 12th Asian Test Symposium(ATS'03), 2003年11月, pp.124-127

Jiun-Lang Huang, Chee-Kian Ong, Kwang-Ting Cheng, A BIST Scheme for On-Chip ADC and DAC Testing, Design, Automation and Test in Europe Conference and Exhibition 2000. Proceedings, 2000年3月, pp.216-220

(58)調査した分野(Int.Cl., DB名)

H03M 3/00 - 11/00