(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5899748号

(P5899748)

(45) 発行日 平成28年4月6日(2016.4.6)

(24) 登録日 平成28年3月18日(2016.3.18)

(51) Int.Cl.

G06F 1/32 (2006.01)

B41J 29/38 (2006.01)

F 1

G06F 1/32

G06F 1/32

B41J 29/38

B41J 29/38Z

B

D

Z

請求項の数 6 (全 18 頁)

|           |                              |

|-----------|------------------------------|

| (21) 出願番号 | 特願2011-210480 (P2011-210480) |

| (22) 出願日  | 平成23年9月27日 (2011.9.27)       |

| (65) 公開番号 | 特開2013-73318 (P2013-73318A)  |

| (43) 公開日  | 平成25年4月22日 (2013.4.22)       |

| 審査請求日     | 平成26年8月12日 (2014.8.12)       |

|           |                                              |

|-----------|----------------------------------------------|

| (73) 特許権者 | 000002369<br>セイコーエプソン株式会社<br>東京都新宿区新宿四丁目1番6号 |

| (74) 代理人  | 110001081<br>特許業務法人クシブチ国際特許事務所               |

| (72) 発明者  | 小山 久和<br>長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内       |

審査官 白石 圭吾

最終頁に続く

(54) 【発明の名称】 媒体処理装置、及び、媒体処理装置の制御方法

## (57) 【特許請求の範囲】

## 【請求項 1】

電源を供給する電源部と、

前記電源部から電源が供給される処理部と、

電源投入時にコンフィギュレーションを行うプログラマブルデバイスと、

所定の条件に基づいて電源供給制御を実行するCPUと、を備え、

前記CPUは、第1の条件が成立した後に前記処理部への通電を停止し前記CPUをスリープ状態に移行させる第1段階と、第2の条件が成立した後に前記処理部及び前記プログラマブルデバイスへの通電を停止し、スリープ状態に移行させる第2段階と、を含む前記電源供給制御を実行し、

前記第1の条件が成立した後前記第1段階に移行させるまでの移行時間、及び、前記第2の条件が成立した後前記第2段階に移行させるまでの移行時間を変更可能であり、

前記CPUのスリープ状態は、前記CPUへの間欠的な通電もしくは前記CPUの一部のモジュールに対する通電を行う状態であることを特徴とする媒体処理装置。

## 【請求項 2】

前記第2段階から通常動作状態への復帰にかかる時間は、前記第1段階から通常動作状態への復帰にかかる時間より長い、請求項1記載の媒体処理装置。

## 【請求項 3】

外部の装置に接続可能なインターフェース部を備え、

前記CPUは、前記所定の条件が成立した後前記スリープ状態に移行させるまでの移行

時間を、前記インターフェース部から受信したコマンドに従って変更する請求項1または2に記載の媒体処理装置。

【請求項4】

前記CPUは、前記第1の条件が成立した後に、前記処理部への通電を停止する段階を実行し、その後所定時間が経過した後に、前記CPUをスリープ状態に移行させる請求項1から3のいずれか1項に記載の媒体処理装置。

【請求項5】

前記処理部は、前記プログラマブルデバイスの制御に従って動作して媒体を処理する処理手段である請求項4に記載の媒体処理装置。

【請求項6】

所定の条件に基づいて、CPUの制御により、コンフィギュレーションを行うプログラマブルデバイスと電源部から電源が供給される処理部とをスリープ状態に移行させる電源供給制御を実行し、

前記電源供給制御において、前記CPUは、第1の条件が成立した後に前記処理部への通電を停止し、前記CPUを前記CPUへの間欠的な通電もしくは前記CPUの一部のモジュールに対する通電を行うスリープ状態に移行させる第1段階と、第2の条件が成立した後に前記処理部及び前記プログラマブルデバイスへの通電を停止し前記CPUをスリープ状態に移行させる第2段階と、を実行し、

前記第1の条件が成立した後前記第1段階に移行させるまでの移行時間、及び、前記第2の条件が成立した後前記第2段階に移行させるまでの移行時間を変更することを特徴とする媒体処理装置の制御方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、媒体処理装置、及び、媒体処理装置の制御方法に関する。

【背景技術】

【0002】

従来、印刷用紙等の処理対象媒体を処理するプリンター等の媒体処理装置において、アイドル時の消費電力を抑制するために、いわゆるスリープモード等、システムコントローラーを含む各部への通電を停止する動作モードに移行するものが知られている（例えば、特許文献1参照）。この種の媒体処理装置は、システムコントローラー等への通電を停止した状態で、外部のホストコンピューターから要求を受け取ると、システムコントローラー等への通電を開始して通常の動作モードに復帰する。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2010-94925号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

ところで、近年、上記の媒体処理装置のような装置のコントローラとして、FPGA(Field-Programmable Gate Array)等のプログラマブルロジックデバイス(PLD:Programmable Logic Device)が採用されることが少なくない。多くのプログラマブルロジックデバイスは、起動時にROMからプログラムやデータをロードして、PLD等の回路データをセットするコンフィギュレーションを行う必要がある。この回路データは揮発的に記憶されているため、PLDへの電源供給を停止した場合には消えてしまい、電源供給復帰後に再度コンフィギュレーションが必要であり、このコンフィギュレーションが完了するまでの待ち時間が発生し、通常の動作モードへの復帰に時間がかかり、利便性を損なう可能性があるという問題があった。

本発明は、上述した事情に鑑みてなされたものであり、PLD等のコンフィギュレシ

10

20

30

40

50

ヨンを要するプログラマブルなデバイス（プログラマブルデバイス）を備えた媒体処理装置において、利便性を損なうことなく、消費電力を抑制できるようにすることを目的とする。

【課題を解決するための手段】

【0005】

上記目的を達成するために、本発明の媒体処理装置は、電源を供給する電源部と、前記電源部から電源が供給される処理部と、電源投入時にコンフィギュレーションを行うプログラマブルデバイスと、所定の条件に基づいて、前記プログラマブルデバイスおよび前記処理部をスリープ状態に移行させる電源供給制御を実行し、前記所定の条件が成立した後前記プログラマブルデバイスをスリープ状態に移行させるまでの移行時間を変更可能にするCPUと、を有することを特徴とする。10

また、本発明は、上記媒体処理装置において、前記CPUは、前記プログラマブルデバイスをスリープ状態とするとき前記プログラマブルデバイスへの電源の供給を停止し、前記処理部を、前記スリープ状態とする。

また、本発明は、上記媒体処理装置において、外部の装置に接続可能なインターフェース部を備え、前記CPUは、前記所定の条件が成立した後前記スリープ状態に移行させるまでの移行時間を、前記インターフェース部から受信したコマンドに従って変更する。

また、本発明は、上記媒体処理装置において、前記CPUは、前記処理部を前記スリープ状態にする第1段階と、前記プログラマブルデバイスを前記スリープ状態にする第2段階とを含む電源供給制御を実行する。20

また、本発明は、上記媒体処理装置において、前記処理部は、前記プログラマブルデバイスの制御に従って動作して媒体を処理する処理手段である。

また、上記目的を達成するために、本発明の媒体処理装置の制御方法は、所定の条件に基づいて、コンフィギュレーションを行うプログラマブルデバイスと電源部から電源が供給される処理部とをスリープ状態に移行させる電源供給制御を実行し、前記所定の条件が成立した後前記プログラマブルデバイスをスリープ状態に移行させるまでの移行時間を変更することを特徴とする。

上記目的を達成するために、本発明は、複数の制御デバイスを備える媒体処理装置であって、少なくとも一つの前記制御デバイスは、CPU (Central Processing Unit) で構成され、少なくとも一つの前記制御デバイスは、少なくとも電源投入時にコンフィギュレーションを要するプログラマブルデバイスで構成され、前記CPUは、所定の条件に基づいて、前記プログラマブルデバイスと、それ以外の前記CPUを含む前記制御デバイスとを段階的にスリープ状態に移行させる電源供給制御を実行し、少なくとも、前記電源供給制御で前記所定の条件が成立した後前記プログラマブルデバイスをスリープ状態に移行させるまでの移行時間に構成されたこと、を特徴とする。30

本発明によれば、外部の装置から所定時間データの受信がない、媒体処理動作が終了してから所定時間経過したなど、所定の条件に基づいて制御デバイスをスリープ状態にすることでアイドル時の消費電力を抑制することができ、また、コンフィギュレーションを要するプログラマブルデバイスと、それ以外の制御デバイスとを段階的にスリープ状態に移行させてるので、例えばプログラマブルデバイスを、それ以外のCPUなどの制御デバイスよりも遅れてスリープ状態に移行させることで、プログラマブルデバイスがスリープ状態に至る前に外部の装置からデータの受信があるようにするなどの事象が発生する確率を上げて、プログラマブルデバイスのスリープ状態への移行頻度を低下させることができる。これにより、プログラマブルデバイスの復帰時のコンフィギュレーションに要する待ち時間の発生を減らし、装置全体としてのスリープ状態からの復帰を高速化することができ、利便性を損なうことなく消費電力を抑制できる。40

【0006】

また、本発明は、前記CPUは、前記電源供給制御において、前記プログラマブルデバイスに対する前記スリープ状態は電源の供給を停止する状態とし、前記プログラマブルデ50

バイス以外の前記 C P U を含む前記制御デバイスを、前記スリープ状態とし、或いは、前記制御デバイスの一部のモジュールにのみ電源を供給する、ことを特徴とする。

本発明によれば、プログラマブルデバイスに対するスリープ状態として電源供給を停止させ、それ以外の C P U を含む制御デバイスには間欠的な電源供給または一部のモジュールに対する電源供給を行うことでスリープ状態とする。C P U などの制御デバイスがスリープ状態から復帰した後、プログラマブルデバイスの復帰を制御することが可能となる。また、段階的に、プログラマブルデバイスに対してはスリープ状態として電源供給を停止するので、消費電力を抑制できる。

#### 【 0 0 0 7 】

また、本発明は、上記媒体処理装置において、外部の装置に接続可能なインターフェース部を備え、前記 C P U は、前記電源供給制御で前記プログラマブルデバイスを前記所定の条件が成立した後前記スリープ状態に移行させるまでの移行時間を、前記インターフェース部から受信したコマンドに従って変更することを特徴とする。10

本発明によれば、外部の装置からのコマンドを受信することによって、プログラマブルデバイスを所定条件が成立した後スリープ状態に移行させるまでの移行時間を設定できるので、スリープ状態に至る頻度、すなわちプログラマブルデバイスのコンフィギュレーションの発生頻度を容易に調整できる。これにより、消費電力の抑制効果とスリープ状態からの復帰に要する時間とのバランスを、媒体処理装置の使用状況に合わせて容易に最適化でき、利便性の向上を図ることができる。

#### 【 0 0 0 8 】

また、本発明は、上記媒体処理装置において、前記 C P U は、前記電源供給制御において、前記プログラマブルデバイス以外の前記 C P U を含む前記制御デバイスを前記スリープ状態にする第 1 段階と、さらに前記プログラマブルデバイスを前記スリープ状態にする第 2 段階とを含む複数の段階に移行させることを特徴とする。20

本発明によれば、プログラマブルデバイスをスリープ状態に移行させる段階が、それ以外の制御デバイスをスリープ状態に移行させる段階と明確に分離されるように制御される。これにより、C P U のスリープ状態への移行条件（移行時間等）と独立して異なる移行条件（移行時間等）を設定でき、コンフィギュレーションの発生頻度を適切に調整できる。。

#### 【 0 0 0 9 】

また、本発明は、上記媒体処理装置において、前記 C P U は、処理対象の媒体を処理する複数の処理手段を備え、少なくともいずれかの前記処理手段は前記プログラマブルデバイスの制御に従って動作するよう構成され、前記電源供給制御において、前記第 1 段階の前に、前記処理手段に対する電源供給を停止する段階に移行し、その後に前記第 1 段階に移行させることを特徴とする。30

本発明によれば、プログラマブルデバイスをスリープ状態に移行させる段階と、それ以外の制御デバイスをスリープ状態に移行させる段階とに加え、媒体に対し、搬送する搬送手段、搬送された媒体に担持された情報を読み取る読み取り手段、搬送された媒体に印刷等の記録をする記録手段等の処理手段への電源供給を停止する段階を設けたことで、処理手段の有するモーターのホールド電流など待機時の消費電流が大きく電源供給停止後の復帰に時間が掛からない処理手段を優先して電源供給を停止することができ、消費電力のより一層の抑制を図ることができ、また、プログラマブルデバイスのコンフィギュレーションの発生頻度を適切に調整できる。40

#### 【 0 0 1 0 】

また、上記目的を達成するために、本発明は、少なくとも電源投入時にコンフィギュレーションを要するプログラマブルデバイスと、それ以外の C P U とを含む複数の制御デバイスを備えた媒体処理装置の制御方法であって、所定の条件に基づいて、前記プログラマブルデバイスと、それ以外の前記 C P U を含む前記制御デバイスとを段階的にスリープ状態に移行させる電源供給制御を実行し、少なくとも、前記電源供給制御で前記所定の条件が成立した後前記プログラマブルデバイスをスリープ状態に移行させるまでの移行時間を50

変更すること、を特徴とする。

本発明によれば、外部の装置から所定時間データの受信がない、媒体処理動作が終了してから所定時間経過したなど、所定の条件に基づいて制御デバイスをスリープ状態にすることでアイドル時の消費電力を抑制することができ、また、コンフィギュレーションを要するプログラマブルデバイスと、それ以外の制御デバイスとを段階的にスリープ状態に移行させてるので、例えばプログラマブルデバイスを、それ以外のCPUなどの制御デバイスよりも遅れてスリープ状態に移行させることで、プログラマブルデバイスがスリープモード状態に至る前に外部の装置からデータの受信があるようにするなどの確率を上げて、プログラマブルデバイスのスリープ状態への移行頻度を低下させることができる。これにより、プログラマブルデバイスの復帰時のコンフィギュレーションを要する待ち時間の発生を減らすことで、装置全体としてのスリープ状態からの復帰を高速化し、利便性を損なうことなく消費電力を抑制できる。10

【発明の効果】

【0011】

本発明によれば、プログラマブルデバイスの復帰時のコンフィギュレーションを要する待ち時間の発生を減らすことで、装置全体としてのスリープ状態からの復帰を高速化し、利便性を損なうことなく消費電力を抑制できる。

【図面の簡単な説明】

【0012】

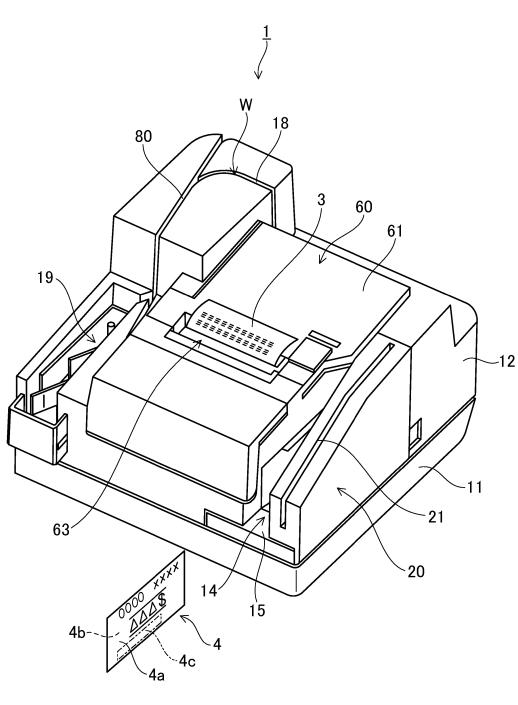

【図1】本発明の実施形態に係る媒体処理装置の斜視図である。20

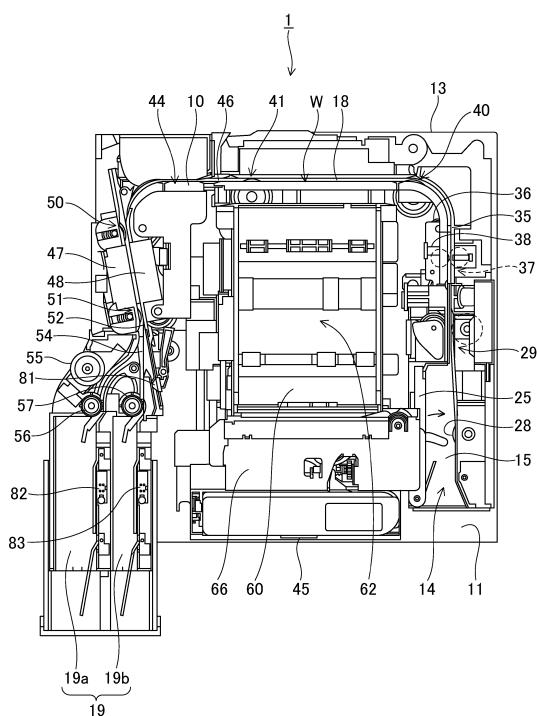

【図2】媒体処理装置の平面図である。

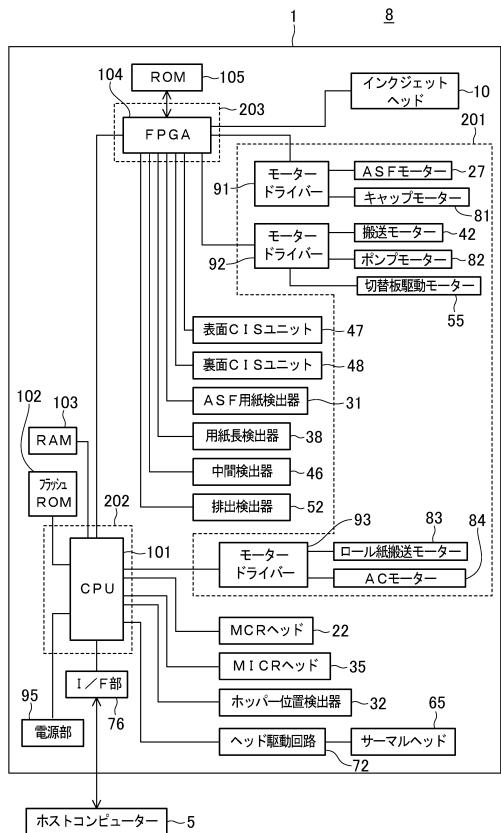

【図3】媒体処理システムの構成図である。

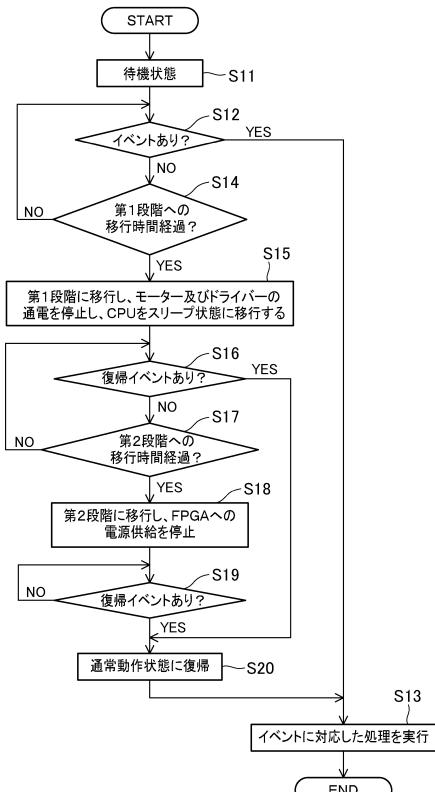

【図4】媒体処理装置の動作を示すフローチャートである。

【図5】媒体処理装置の動作を示すフローチャートである。

【発明を実施するための形態】

【0013】

以下、図面を参照して本発明の実施形態について説明する。

図1は、本実施の形態に係る媒体処理装置1の斜視図である。

図1に示すように、媒体処理装置1は、処理対象媒体であるシート状の小切手や帳票類に対し、この処理対象媒体に記録された磁気インク文字の読み取り、読み取った媒体の両面の光学的読み取り、及び、当該読み取った媒体への文字等の記録を行う装置である。また、媒体処理装置1は、クレジットカード等のカード型の媒体に記録された磁気情報を読み取るリーダーとしての機能、及び、感熱式のロール紙3に画像を記録して切断することにより画像が記録された紙片を発行する機能を備えている。30

【0014】

本実施形態では、処理対象媒体として小切手4(第1の処理対象媒体)及びロール紙3(第2の処理対象媒体)を処理する場合を例に挙げて説明する。

小切手4は、図1に示すように、所定の模様や装飾が施されたシート(用紙)に金額、振出人、通し番号、サインなどが印字または記載された帳票である。これら金額、振出人、通し番号、サインなどは表面4aにあり、裏面4bには裏書き欄が設けられている。この裏書き欄には、後述するインクジェットヘッド10によって、裏書きに係る所定の文字または画像が記録される。また、表面4aには小切手4の長辺方向に延びる磁気インク文字列4cが形成されている。磁気インク文字列4cは、磁気インクで印刷された複数の磁気インク文字(MICR文字)が並んだものであり、磁気的または光学的に読み取ることができる。40

また、ロール紙3は、加熱により発色する感熱紙であり、媒体処理装置1は、サーマルプリンタユニット60によりロール紙3の記録面を加熱することで文字や画像を記録する。

【0015】

媒体処理装置1は、媒体処理装置1の下部を覆う下部ケース11、及び下部ケース11

50

に被せられるカバー12からなる外装を有し、外装の内部に媒体処理装置1の本体が収容されている。媒体処理装置1の前面には、小切手4を挿入する挿入口14が開口しており、挿入口14の奥には複数の小切手4を積層して貯留できるストッカー15が設けられている。このストッカー15は、前面側へ向かって引き出し自在に構成されており、ストッカー15に貯留すべき小切手4のサイズに応じてストッカー15を引き出した上で、このストッカー15に小切手4を貯留させることができる。

また、カバー12には、上面視で略U字形状に、小切手4の搬送路Wとなるスリット18が形成され、スリット18は媒体処理装置1の前面側に設けられたポケット19に達している。ストッカー15に貯留された小切手4は、後述するように1枚ずつ媒体処理装置1の内部に取り込まれ、スリット18を通る間に処理されて、処理後的小切手4はポケット19に排出される。ポケット19には複数の小切手4を溜めることができる。10

図1に示すように、ストッカー15の側方には、磁気カードリーダーユニット20が設けられている。磁気カードリーダーユニット20は、カバー12に形成されたカードスリット21と、このカードスリット21に対応して設けられたMCRヘッド22(図3)とを備え、カードスリット21を通るカード類に磁気的に記録された情報をMCRヘッド22によって読み取る。

#### 【0016】

図2は、媒体処理装置1の外装内部に収容されている本体の構成を示す平面図である。図2に示すように、ストッカー15の一側面にはホッパー25が設けられている。このホッパー25は、図中矢印方向に回動可能に構成されており、ASFモーター27の動力によって移動され、ストッカー15に貯留された小切手4を他方の側面側に付勢する。20

ストッカー15の他方の側面には、後述するASF(Automatically Sheet Feeder)モーター27(図3)により駆動されるピックアップローラー28が配置されており、ホッパー25がピックアップローラー28側に回動すると、この回動に応じてストッカー15内の小切手4のうち1枚がピックアップローラー28に付勢され、当該ローラーに接触して、当該ローラーの回転に応じて搬送路Wに引き込まれる。

ストッカー15の奥には、一対のローラーで構成されるASFローラー29が配置されている。ASFローラー29の2つのローラーは、搬送路Wの両側に配置され、一方は後述するASFモーター27の動力により回転し、他方のローラーは従動ローラーである。ピックアップローラー28に接した小切手4はASFローラー29に挟まれて、スリット18内を下流側へ搬送される。30

#### 【0017】

ストッカー15の所定の位置には、ASF用紙検出器31(図3)が設けられている。ASF用紙検出器31は、例えば透過型光センサーで構成され、ストッカー15における小切手4の有無を検出する。

また、ストッカー15において、ホッパー25の待機位置には、ホッパー位置検出器32(図3)が設けられている。ホッパー位置検出器32は、例えば透過型光センサーで構成され、ホッパー25が待機位置に位置しているか否かを検出する。

ASFローラー29の下流側には、小切手4の表面4aに接して磁気インク文字列4c(図1)を磁気的に読み取るMICR(Magnetic Ink Character Recognition)ヘッド35が配置されている。MICRヘッド35には、MICRローラー36が対向配置される。MICRローラー36はMICRヘッド35側に付勢されており、小切手4をMICRヘッド35に押しつけながら回転して、小切手4を、MICR文字の読み取りに適した定速で搬送する。MICRヘッド35の上流側には、ASFローラー29により繰り出された小切手4をMICRヘッド35に案内する、一対のローラーからなるアシストローラー37が配置されている。40

#### 【0018】

また、搬送路W上においてアシストローラー37とMICRヘッド35との間には、用紙長検出器38が配置されている。用紙長検出器38は、例えば反射型光センサーで構成され、搬送路W上を通る小切手4の検出位置における有無を検出することにより、小切手50

4の先端及び後端を検出する。用紙長検出器38の検出値は後述する制御部70(制御手段)により取得され、この検出値の変化に基づいて小切手4の長さが求められる。

搬送路W上でMICRヘッド35の下流側には、搬送路Wを挟んで対向する一対のローラーを有する第1搬送ローラー40が設けられ、さらに、この第1搬送ローラー40の下流側には第2搬送ローラー41が設けられている。これら第1搬送ローラー40、及び、第2搬送ローラー41は、搬送モーター42(図3)によって回転駆動されるローラーであり、これらローラーによって小切手4はインクジェットプリンターユニット44(印刷手段)へ搬送される。

#### 【0019】

インクジェットプリンターユニット44は、インクジェットヘッド10(インクジェット記録ヘッド)を備えている。インクジェットヘッド10は、媒体処理装置1の前部に収容されているインクカートリッジ45(インク貯留部)からインクの供給を受けて、小切手4にインクを吐出するインクジェット方式の記録ヘッドである。本実施形態においてインクジェットヘッド10は小切手4の裏面4bに、いわゆる裏書きと呼ばれる文字や画像を記録する。

搬送路Wを挟んでインクジェットヘッド10の正面には、キャップ(図示略)が配置されている。このキャップは、キャップモーター81(図3)の動力によりインクジェットヘッド10側に進退可能に構成され、インクの乾燥防止等のため、小切手4を処理していない状態ではインクジェットヘッド10側に進出して、インクジェットヘッド10のノズル面を覆う。このキャップの内部にはインク吸引用の穴が設けられ、この穴は図示しない吸引ポンプに連通している。吸引ポンプは、ポンプモーター82(図3)により駆動され、インクジェットヘッド10のノズルの吐出不良を解消するためのクリーニング動作が実行される際に、キャップを介してインクジェットヘッド10のノズルからインクを吸い出す。吸引ポンプが吸い出したインクは廃液タンク(図示略)に貯留される。

また、インクジェットヘッド10と、第2搬送ローラー41との間には、中間検出器46が設けられている。中間検出器46は、例えば反射型光センサーで構成され、検出位置における小切手4の有無を検出する。

#### 【0020】

インクジェットヘッド10の下流には、小切手4を光学的に読み取るCIS(Contact Image Sensor)ユニットが配置されている。このCISユニットは、小切手4の表面4aを読み取る表面CISユニット47と、裏面4bを読み取る裏面CISユニット48とを有し、小切手4の両面を光学的に読み取り可能である。表面CISユニット47と裏面CISユニット48は搬送路Wを挟んで対向配置されており、これらユニットの上流側には第1CISローラー50が配置され、また、下流側には第2CISローラー51が配置されている。これら第1CISローラー50、及び、第2CISローラー51は、搬送モーター42によって回転駆動されるローラーであり、これらローラーによってCISユニットによって読み取り中の小切手4が安定して搬送される。

第2CISローラー51の下流には、排出検出器52が設けられている。排出検出器52は、例えば反射型光センサーで構成され、検出位置における小切手4の有無を検出する。

#### 【0021】

表面CISユニット47、裏面CISユニット48の下流側には上述したポケット19が設けられている。ポケット19は、メインポケット19aと、サブポケット19bとに区画されており、スリット18が分岐して、それぞれのポケット19に繋がっている。これらメインポケット19a、及び、サブポケット19bには、それぞれ複数の小切手4を収容できる。

そして、スリット18が分岐した位置には、小切手4を排出すべきポケット19を、メインポケット19aとサブポケット19bとのいずれかに切り替える切替板54が配置されている。切替板54は、メインポケット19aに繋がる経路とサブポケット19bに繋がる経路のいずれか一方を塞ぐことで小切手4を他方に案内するガイドであり、切替板驅

10

20

30

40

50

動モーター 5 5 によって駆動される。切替板 5 4 からメインポケット 1 9 a に繋がる経路には排出口ーラー 5 6 が設けられ、また、切替板 5 4 からサブポケット 1 9 b に繋がる経路には排出口ーラー 5 7 が設けられており、小切手 4 は、これらローラーにより切替板 5 4 に案内されたいずれかのポケット 1 9 にスムーズに排出される。

後述するように、媒体処理装置 1 は、MICR ヘッド 3 5 による磁気インク文字列 4 c の読み取り結果に基づいて、小切手 4 が正しくセットされていると判別した場合は、小切手 4 をメインポケット 1 9 a に排出し、一方、小切手 4 が正しくセットされていないと判別した場合は、サブポケット 1 9 b に排出する。

#### 【0022】

また、図 1 及び図 2 に示すように、媒体処理装置 1 の中央部には、サーマルプリンターユニット 6 0 が設けられている。10

図 1 に示すように、サーマルプリンターユニット 6 0 は、媒体処理装置 1 の上部を覆うプリンターカバー 6 1 を備えている。このプリンターカバー 6 1 は、カバー 1 2 に対して開閉自在に取り付けられており、プリンターカバー 6 1 を開くと、ロール紙 3 を収容可能な空間であるロール紙収容部 6 2 が露出し、ロール紙 3 の補充や交換が可能となる。プリンターカバー 6 1 には、排紙口 6 3 が形成されており、ロール紙収容部 6 2 に収容されたロール紙 3 は、排紙口 6 3 を介して、排出される。

#### 【0023】

サーマルプリンターユニット 6 0 は、ロール紙収容部 6 2 に収容したロール紙 3 を繰り出して搬送させるローラー状のプラテン（図示略）と、プラテンに対向配置されたサーマルヘッド 6 5（図 3）と、搬送方向に対し直交する方向にロール紙 3 を切断するカッターユニット 6 6 とを備えている。紙片の発行に際し、サーマルプリンターユニット 6 0 のプラテンは、ロール紙搬送モーター 8 3（図 3）の動力により回転駆動され、ロール紙 3 を搬送方向に搬送する。また、カッターユニット 6 6 は、AC（Auto Cutter）モーター 8 4 の動力で動く可動刃（図示略）と固定刃（図示略）とを備え、ロール紙 3 を挟んで可動刃が固定刃に噛み合うことでロール紙 3 を切断する。サーマルプリンターユニット 6 0 は、プラテンを回転させてロール紙 3 を搬送しながら、サーマルヘッド 6 5 によりロール紙 3 に文字や画像を記録し、カッターユニット 6 6 によって所定の位置でロール紙 3 を切断して、紙片を発行する。この紙片は、例えば、小切手 4 を用いた取引に関する取引記録（レシート）である。20

#### 【0024】

図 3 は、媒体処理装置 1 と、外部の装置としてのホストコンピューター 5 とを接続して構成される媒体処理システム 8 の機能的構成を示すブロック図である。

図 3 に示すように、媒体処理装置 1 は、媒体処理装置 1 全体を制御する制御デバイスとして、CPU 1 0 1 と、FPGA 1 0 4 とを備えている。CPU 1 0 1 は、フラッシュ ROM 1 0 2 に記憶したプログラムを読み出して RAM 1 0 3 に展開して実行することにより、FPGA 1 0 4 を含む媒体処理装置 1 の各部を制御する。FPGA 1 0 4 は、ROM 1 0 5 に格納されたプログラミングファイルにより設定された動作を実行し、後述する各部を制御するプログラマブルデバイスである。30

#### 【0025】

また、媒体処理装置 1 は、外部から供給される電圧の電圧変換等を行い、媒体処理装置 1 の各部に対して電源を供給する電源部 9 5 を備えている。電源部 9 5 は、CPU 1 0 1 の制御に従って、媒体処理装置 1 の各部に対する電源供給の供給状態を切り替える機能を有する。例えば、CPU 1 0 1 は、電源部 9 5 の電源供給容量を超えないように、電源部 9 5 からモータードライバー 9 1、9 2、9 3 への電源供給、ASF モーター 2 7、キャップモーター 8 1、搬送モーター 4 2、ポンプモーター 8 2、切替板駆動モーター 5 5、ロール紙搬送モーター 8 3、AC モーター 8 4 の各モーターへの電源供給を制御する。また、CPU 1 0 1 は、後述する省電力制御（電源供給制御）を実行し、媒体処理装置 1 のアイドル時の消費電力を抑制するため、媒体処理装置 1 の動作状態に基づいて、電源部 9 5 から各部への電源供給のオン／オフを切り替えさせる。40

**【0026】**

CPU101には、CPU101が実行するプログラム、及びこれらのプログラムに係るデータを記憶したフラッシュROM102と、CPU101が実行するプログラムや処理されるデータを一時的に格納するRAM103とが接続されている。

また、FPGA104には、FPGA104のプログラミングファイル（コンフィギュレーションデータ）を記憶したROM105が接続されている。

FPGA104は、電源部95からの電源供給が開始されると、コンフィギュレーションを実行する。

このコンフィギュレーションは、以下の手順を含んでおり、電源部95からFPGA104への電源供給がオフからオンに切り替わる毎に実行される。

- ・電源部95から供給される電源電圧を確認する。

- ・内蔵するメモリーの初期化等の初期化処理を行う。

- ・ROM105に記憶されたプログラミングファイルを検出する。

- ・検出したプログラミングファイルをROM105からロードする。

- ・ロードしたプログラミングファイルに従って回路データを書き込む。

**【0027】**

FPGA104には、インクジェットヘッド10が接続されている。CPU101は、ホストコンピューター5から送信されたコマンドに従って、文字や画像を配置した印刷イメージをRAM103に展開し、この印刷イメージをもとにインクジェットヘッド10の各ノズルからのインク吐出量データを生成して、FPGA104に出力する。FPGA104は、CPU101から入力されるインク吐出量データに基づいてインクジェットヘッド10を動作させ、インクジェットヘッド10から小切手4にインクを吐出させ、印刷させる。

**【0028】**

また、FPGA104には、モータードライバー91、92が接続されており、FPGA104は、CPU101から入力される制御データに基づいてモータードライバー91、92を制御する。モータードライバー91は、ASFモーター27及びキャップモーター81に接続され、FPGA104の制御に従ってASFモーター27及びキャップモーター81の各々に対して駆動電流を供給し、FPGA104が指定した動作方向、動作速度及び動作量に従ってこれら各モーターを回転させる。モータードライバー92は、小切手4を搬送する各ローラーを回転させる搬送モーター42、ポンプモーター82及び切替板駆動モーター55の各々に対して駆動電流を供給し、FPGA104が指定した動作方向、動作速度及び動作量に従ってこれら各モーターを回転させる。

**【0029】**

FPGA104には、表面CISユニット47及び裏面CISユニット48が接続されている。FPGA104は、CPU101から入力される制御データに従って、表面CISユニット47及び裏面CISユニット48に、小切手4の表面4a及び裏面4bの読み取りを実行させる。この際、FPGA104は、表面CISユニット47及び裏面CISユニット48の各々から出力される信号をA/D変換して、変換後のデジタルデータをCPU101に出力する。

また、FPGA104には、ASF用紙検出器31、用紙長検出器38及び中間検出器46の各検出器が接続されている。FPGA104は、これらASF用紙検出器31、用紙長検出器38及び中間検出器46に対して検出パルスを出力し、各検出器の出力値を所定時間周期で取得する。FPGA104は、各検出器から取得した出力値をA/D変換して、変換後のデジタルデータを、検出器毎に定められた所定のしきい値と比較することにより、ストッカー15における小切手4の有無、用紙長検出器38による小切手4の検出の有無、中間検出器46による小切手4の検出の有無を判別し、判別結果を内蔵するレジスター（図示略）に格納する。CPU101は、所定時間周期でFPGA104のレジスターに格納された各検出器の判別結果のデータを取得する。

**【0030】**

10

20

30

40

50

CPU101には、モータードライバー93が接続されている。モータードライバー93は、ロール紙3を搬送するプラテンを駆動するロール紙搬送モーター83と、カッタユニット66が備える可動刃(図示略)を動かすACモーター84に対し、駆動電流を供給して、これら各モーターを、CPU101が指定した動作方向、動作速度及び動作量に従って回転させる。

#### 【0031】

CPU101には、MCRヘッド22及びMICRヘッド35が接続されている。CPU101は、カードスリット21(図1)にカード類が通される際にMCRヘッド22によって磁気情報を読み取らせ、MCRヘッド22が出力する読み取信号を検出する。CPU101は、MICRヘッド35によって小切手4に記録された磁気情報を読み取らせ、MICRヘッド35が出力する読み取信号を検出する。また、CPU101にはホッパー位置検出器32が接続され、CPU101はホッパー位置検出器32に対して検出パルスを出力し、ホッパー位置検出器32の出力値を取得することでホッパー25が待機位置にあるか否かを判別する。

10

さらに、CPU101には、サーマルヘッド65を駆動するヘッド駆動回路72が接続されている。ヘッド駆動回路72は、CPU101の制御に従って、サーマルヘッド65が備える各々の発熱素子への通電を制御し、サーマルヘッド65によってロール紙3に文字や画像を印刷させる。

CPU101には、ホストコンピューター5に対して有線または無線で接続されたインターフェース部76が接続されている。CPU101は、インターフェース部76を制御して、ホストコンピューター5との間で制御データを含む各種データを送受信する。CPU101は、インターフェース部76によって所定時間周期でホストコンピューター5から送信されるコマンドの受信を試行させ、ホストコンピューター5からコマンドが送信された場合に速やかに受信できるようにする。

20

#### 【0032】

CPU101は、ホストコンピューター5から送信される処理指示コマンドを受信して、小切手4に対する処理を実行する。

CPU101、小切手4の処理を指示するコマンドに従って、ASF用紙検出器31の出力値の判別結果に基づいて、ストッカー15における小切手4の有無を判別する。小切手4がセットされていると判別した場合、CPU101は、ホッパー位置検出器32の出力値をもとにホッパー25が待機位置にあることを確認し、FPGA104によりASFモーター27を動作させ、1枚の小切手4をピックアップして搬送路Wに取り込む。次いで、CPU101は、FPGA104を制御して搬送モーター42を動作させ、ASF口-ラ-29、MICR口-ラ-36、アシストローラ-37、第1搬送口-ラ-40、第2搬送口-ラ-41、第1CIS口-ラ-50、第2CIS口-ラ-51、及び、排出口-ラ-56、57を動かして、小切手4を搬送する。さらに、CPU101はFPGA104を制御して切替板駆動モーター55を動作させて、切替板54を動かし、処理が完了した小切手4の排出先をメインポケット19aまたはサブポケット19bのいずれかに設定し、排出口-ラ-56、57により小切手4を排出させる。ここで、CPU101の制御により動作するロール紙搬送モーター83、ACモーター84及びこれらを駆動するモータードライバー93は、搬送手段として機能する。また、FPGA104の制御によって動作するASFモーター27、搬送モーター42、及びこれらを駆動するモータードライバー91、92は、搬送手段(第1搬送手段)に相当する。

30

40

#### 【0033】

CPU101は、小切手4の磁気インク文字列4cの読み取りを指示するコマンドに従って、MCRヘッド22による読み取りを実行させ、MCRヘッド22が読み取った磁気波形を取得し、この磁気波形のデータまたは磁気波形を認識した認識結果をホストコンピューター5に送信する。

また、CPU101、小切手4への印刷を指示するコマンドに従って、このコマンドとともに送信された印刷データに基づいて、文字や画像を配置した印刷イメージを生成及び

50

展開し、FPGA104を制御することにより、印刷イメージに基づく文字や画像をインクジェットヘッド10によって小切手4の表面4aまたは裏面4bに印刷する。

CPU101は、小切手4の光学読取を指示するコマンドに従って、FPGA104を制御し、表面CISユニット47及び裏面CISユニット48によって小切手4の表面4aと裏面4bを読み取らせ、FPGA104から入力される読取画像データをそれぞれホストコンピューター5に送信する。

#### 【0034】

さらに、CPU101は、ホストコンピューター5からロール紙3に対する印刷を指示するコマンドを受信した場合、このコマンドに従って、文字や画像を配置した印刷イメージを生成及び展開する。CPU101は、モータードライバー93を制御してロール紙搬送モーター83を回転させ、プラテンによってロール紙3を搬送させるとともに、ヘッド駆動回路72を制御して印刷イメージに基づく文字や画像をサーマルヘッド65によってロール紙3に印刷する。印刷後、CPU101は、モータードライバー93によりACモーター84を動作させ、ロール紙3をカッターユニット66により切断する。

10

ここで、CPU101の制御によりロール紙3を搬送するロール紙搬送モーター83及びモータードライバー93は、搬送手段（第2搬送手段）として機能する。

#### 【0035】

CPU101は、ホストコンピューター5から受信したコマンドに従って媒体処理装置1がロール紙3を処理する場合と、小切手4を処理する場合とで、電源部95に接続するモータードライバー91、92、93を切り替える制御を行う。電源部95の仕様によつては、例えば、媒体処理装置1が備えるモータードライバー91、92、93に駆動される複数のモーターが同時に動作すると電源部95の定格を超える場合がある。この場合、電源部95が、モータードライバー91、92、93の全てに接続されていると、これらに接続された各モーターが動作可能な状態となってしまい、負荷が定格を超える可能性がある。

20

そこで、CPU101は、電源部95が供給可能な電力に合わせて、電源部95が接続されるモータードライバーを適宜切り替えさせる制御を行う。本実施形態では、CPU101の制御により、モータードライバー91、92と、モータードライバー93とを排他的に電源部95に接続する。すなわち、CPU101は、ホストコンピューター5から受信したコマンドを判別し、ロール紙3を処理する場合は電源部95からモータードライバー93へ通電させ、小切手4を処理する場合は電源部95からモータードライバー91、92に通電させる。

30

#### 【0036】

また、CPU101は、媒体処理装置1の動作状態に基づいて、省電力制御を実行する。この省電力制御は、媒体処理装置1がロール紙3と小切手4のいずれに対する処理も行わず、また、上述したカード型の媒体に記録された磁気情報をMCRヘッド22により読み取るリーダーとしての機能も実行していない状態で、ホストコンピューター5から送信されるコマンドに対する待機状態で実行される。

媒体処理装置1は、待機状態が継続した場合に、媒体処理装置1の各部に対する通電をオフにする省電力状態に移行する。本実施形態で、媒体処理装置1の省電力状態は、第1省電力状態（第1段階）と第2省電力状態（第2段階）との2段階に設定されている。フラッシュROM102には、通常の待機状態から第1省電力状態へ移行する時間の設定値と、第1省電力状態から第2省電力状態に移行する時間の設定値とが、予め記憶されている。CPU101はフラッシュROM102に記憶された設定値に従って、省電力状態への移行を制御する。

40

#### 【0037】

第1省電力状態では、図3に示すモータードライバー91～93及びこれらに接続された各モーターを含む電力制御対象部201と、CPU101で構成される電力制御対象部202が、通電制御の対象となる。第2省電力状態では、電力制御対象部201、202に加え、FPGA104で構成される電力制御対象部203が通電制御の対象となる。な

50

お、図3に示していないモーターを、電力制御対象部201に含めてもよい。モータードライバー91～93は、電源部95から通電されている間は、待機状態においても電力を消費するので、第1、第2省電力状態に移行すれば、この消費電力を節約することができる。ここで、電力制御対象部201、202は本発明の処理手段に相当するが、これらに加えて、インクジェットヘッド10(記録手段)、MICRヘッド35(読み取り手段)、表面CISユニット47(読み取り手段)、裏面CISユニット48(読み取り手段)、サーマルヘッド65(記録手段)を処理手段に含めてもよい。

#### 【0038】

図4は、媒体処理装置1の動作を示すフローチャートであり、CPU101による省電力制御を示す。

10

CPU101は、媒体処理装置1が待機状態になってからの時間を、内蔵するタイマー(図示略)によってカウントし(ステップS11)、イベントの発生を監視する(ステップS12)。ここで、イベントとは、ホストコンピューター5から送信されるコマンドをインターフェース部76が受信した場合、媒体処理装置1が備える操作パネル(図示略)のスイッチが操作された場合、媒体処理装置1のプリンターカバー61やカバー12が開かれたことを、CPU101に接続されたスイッチ式のカバー検出器(図示略)により検出した場合などである。

待機状態においてイベントを検出した場合(ステップS12; Yes)、CPU101は、検出したイベントに対応した処理を実行する(ステップS13)。一方、待機状態においてイベントが検出されない場合(ステップS12; No)、CPU101は、内蔵するタイマーのカウント値が、フラッシュROM102に記憶している第1省電力状態への移行時間の設定値に達したか否かを判別する(ステップS14)。ここで、第1省電力状態への移行時間の設定値に達していなければ(ステップS14; No)、CPU101は、ステップS12に戻ってイベントを検出する。このステップS12～S13の処理は、予め設定された周期で実行される。

20

#### 【0039】

待機状態に移行してからの経過時間が第1省電力状態への移行時間の設定値に達した場合(ステップS14; Yes)、CPU101は、第1省電力状態に移行して、モータードライバー91～93への通電を停止し、CPU101をスリープ状態に移行させる(ステップS15)。ここで、モータードライバー91～93への通電を停止することで、モータードライバー91～93につながる各モーターへの通電も停止される。CPU101のスリープ状態とは、CPU101が次に説明する復帰イベントの検出を所定時間毎に行うため、CPU101に対する電源供給を間欠的に停止する状態である。この場合、CPU101は、第1省電力状態であることをフラッシュROM102に記憶して、電源部95からの通電が再開される毎に復帰イベントの検出を試行する(ステップS16)。具体的には、CPU101につながる各検出器の出力値を取得し、操作パネルの操作を検出し、インターフェース部76によりホストコンピューター5からのコマンドの受信の有無を判別する。なお、復帰イベントとは、第1省電力状態及び後述する第2省電力状態から復帰する条件として設定されたイベントであって、ステップS12で検出するイベントと同じであってもよいし、このイベントのうち一部のイベントのみを復帰イベントとしてもよい。また、第1省電力状態から復帰する場合の復帰イベントと、第2省電力状態から復帰する場合の復帰イベントとして別のイベントが設定されていてもよい。さらに、CPU101に接続されたスイッチ式の検出器が、例えば媒体処理装置1のプリンターカバー61やカバー12が開かれたことを検出した場合に、この検出がCPU101に対する割り込み制御として入力される構成としてもよい。さらにまた、CPU101が、イベントの発生を検出する回路モジュールと、その他の回路モジュールとに対して個別に電源の供給/停止を切り替え可能に構成されていてもよく、この場合、第1省電力状態では、イベントの発生を検出する回路モジュールに対してのみ通電され、その他の回路モジュールに対する通電は停止される。

30

#### 【0040】

40

50

このように、第1省電力状態では、電力制御対象部201への通電が停止されるので、通常動作状態（待機状態を含む）に比べて消費電力を低減できる。さらに、CPU101への通電が間欠的な通電または一部の回路モジュールに対する通電のみとなるため、通常動作状態に比べて、より一層の消費電力の低減を図ることができる。

#### 【0041】

また、CPU101は、ステップS15で第1省電力状態に移行してからの経過時間と、内蔵するタイマーによりカウントする。CPU101は、CPU101への間欠的な通電の周期に基づいてカウントを実行すれば、スリープ状態に移行した後もカウントを行える。

第1省電力状態に移行した後、CPU101は、復帰イベントを検出した場合（ステップS16；Yes）、通常動作状態に復帰する（ステップS20）。このステップS20で、CPU101は、電力制御対象部201、202への通電を通常動作の通電状態に戻し、フラッシュROM102に記憶した第1省電力状態であることを示すデータを消去し、ステップS13に移行してイベントに対応した処理を実行する。10

また、復帰イベントが検出されない場合（ステップS16；No）、CPU101は、内蔵するタイマーのカウント値が、フラッシュROM102に記憶している第2省電力状態への移行時間の設定値に達したか否かを判別する（ステップS17）。ここで、第2省電力状態への移行時間の設定値に達していないければ（ステップS17；No）、CPU101は、ステップS16に戻ってイベントを検出する。このステップS16～S17の処理は、予め設定された周期で実行される。20

#### 【0042】

待機状態に移行してからの経過時間が第2省電力状態への移行時間の設定値に達した場合（ステップS17；Yes）、CPU101は、第2省電力状態に移行して、電力制御対象部202すなわちFPGA104への通電を停止する（ステップS18）。これにより、電力制御対象部201～203の全てに対する通電が抑制される。CPU101は、第2省電力状態に移行してからの経過時間を内蔵するタイマーによりカウントし、第2省電力状態であることをフラッシュROM102に記憶して、電源部95からの通電が再開される毎に復帰イベントの検出を試行する（ステップS19）。CPU101は、復帰イベントを検出した場合（ステップS19；Yes）、ステップS20に移行して、通常動作状態に復帰し、ステップS13に移行してイベントに対応した処理を実行する。30

また、復帰イベントが検出されない場合（ステップS19；No）、CPU101は、ステップS19で復帰イベントの検出を所定時間周期で繰り返し実行する。この間、媒体処理装置1は第2省電力状態を継続し、電力制御対象部201～203の消費電力が抑制された状態を保つ。

#### 【0043】

なお、図4に示した動作例では、ステップS14で第1省電力状態に移行すると、電力制御対象部201、202に対する通電状態が変更されるものとしたが、例えば、電力制御対象部201に対する通電状態が変更される段階と、電力制御対象部202に対する通電状態が変更される段階とを分けてもよい。すなわち、第1省電力状態の前に、電力制御対象部201に対する通電を停止する段階を設け、その後所定時間が経過した後に、電力制御対象部202であるCPU101をスリープ状態に移行させる段階に移行してもよい。この場合、媒体処理装置1における省電力制御をより詳細に切り替えることができ、例えばCPU101が通常動作状態で電力制御対象部201に対する通電を停止する段階では、CPU101の初期化を行わずに極めて短時間で通常動作状態に復帰できる。40

#### 【0044】

また、第2省電力状態に移行した後で、CPU101が復帰イベントを検出すると、電源部95から電力制御対象部201～203への通電が開始される（ステップS20）。ここで、FPGA104に対する通電が開始されると、FPGA104は、上述したコンフィギュレーションを実行する。このため、第2省電力状態から通常動作状態への復帰は、第1省電力状態から通常動作状態への復帰よりも時間がかかり、媒体処理装置1を操作50

するユーザーが待つ待ち時間は長い。その一方で、第2省電力状態は、第1省電力状態よりも深い省電力状態であって、消費電力は大幅に抑制されているので、省電力効果は高い。これに対し、第1省電力状態から通常動作状態への復帰は短時間で済み、復帰に伴うユーザーの待ち時間は短い。

従って、第1省電力状態から第2省電力状態への移行時間の設定値は、媒体処理装置1の使われ方、すなわち広義の使用環境に合わせて最適化されることが好ましい。このため、媒体処理装置1では、第2省電力状態への移行時間の設定値を変更可能となっている。また、媒体処理装置1では、第1省電力状態への移行時間の設定値を変更することも可能である。

#### 【0045】

10

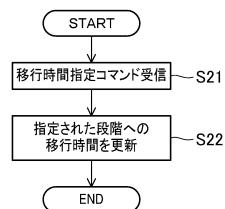

図5は、媒体処理装置1の動作を示すフローチャートであり、第2省電力状態への移行時間の設定値を設定・変更する処理を示す。

CPU101は、ホストコンピューター5からコマンドを受信して、受信したコマンドを解析した結果、受信したコマンドが移行時間設定コマンドであった場合(ステップS21)、受信したコマンドにより指定された段階への移行時間の設定値を、受信したコマンドに付加されたデータに従って更新する(ステップS22)。これにより、フラッシュROM102が記憶している設定値が変更され、第1省電力状態、第2省電力状態への移行時間の設定値を任意に変えることができる。

#### 【0046】

20

以上説明したように、本発明を適用した実施形態に係る媒体処理装置1は、複数の制御デバイスとしてのCPU101、FPGA104を備え、少なくとも一つの制御デバイスはCPU(CPU101)で構成され、少なくとも一つの制御デバイスは、少なくとも電源投入時にコンフィギュレーションを要するプログラマブルデバイス(FPGA104)で構成され、CPU101は、所定の条件に基づいて、FPGA104と、それ以外の制御デバイスであるCPU101とを段階的にスリープ状態に移行させる省電力制御を実行し、少なくとも、省電力制御で上記所定の条件が成立した後FPGA104への電源供給を停止するまでの移行時間を変更可能である。このため、ホストコンピューター5から所定時間データの受信がない、小切手4等の媒体を処理する動作が終了してから所定時間が経過した等、所定の条件に基づいて第1省電力状態、第2省電力状態に移行してCPU101、FPGA104をスリープ状態にすることでアイドル時の消費電力を抑制することができる。また、コンフィギュレーションを要するFPGA104への電源供給の停止と、CPU101のスリープ状態への移行とを段階的に行うので、例えばFPGA104をCPU101よりも遅れてスリープ状態に移行させることで、FPGAがスリープ状態に至る前にホストコンピューター5からのデータの受信等の事象が発生する確率を高め、FPGA104のスリープ状態への移行頻度を低下させることができる。これにより、FPGA104の復帰時のコンフィギュレーションに要する待ち時間の発生を減らし、媒体処理装置1全体としての省電力状態からの復帰を高速化することができ、利便性を損なうことなく消費電力を抑制できる。

30

#### 【0047】

40

また、CPU101は、FPGA104のスリープ状態では電源の供給を停止し、CPU101等のFPGA104以外の制御デバイスに対しては、間欠的に電源が供給され、或いは、CPU101の一部の回路モジュールにのみ電源が供給される状態とする。これにより、省電力制御の対象であるCPU101がスリープ状態から復帰した後、FPGA104の復帰を制御することが可能となる。また、段階的に、FPGA104に対してはスリープ状態として電源供給を停止するので、消費電力を抑制できる。

#### 【0048】

50

また、媒体処理装置1は、ホストコンピューター5に接続可能なインターフェース部76を備え、CPU101は、省電力制御でFPGA104を上記所定の条件が成立した後第2省電力状態に移行させるまでの移行時間の設定値を、ホストコンピューター5から受信したコマンドに従って変更するので、第2省電力状態への移行時間を設定あるいは変更

して、FPGA104がスリープ状態に移行する頻度、すなわちFPGA104のコンフィギュレーションの発生頻度を容易に調整できる。これにより、消費電力の抑制効果と第2省電力状態からの復帰に要する時間とのバランスを、媒体処理装置1の使用状況に合わせて容易に最適化でき、利便性の向上を図ることができる。

#### 【0049】

また、媒体処理装置1において、CPU101は、CPU101をスリープ状態にする第1省電力状態と、さらにFPGA104への電源供給を停止する第2省電力状態とを含む複数の段階に移行させるので、プログラマブルデバイスであるFPGA104への電源供給を停止する段階が、CPU101のスリープ状態への移行と明確に分離されるように制御できる。これにより、CPU101のスリープ状態への移行条件（移行時間など）と独立して、異なる移行条件（移行時間など）を設定でき、コンフィギュレーションの発生頻度を適切に調整できる。10

#### 【0050】

さらに、媒体処理装置1は、媒体としてのロール紙3を搬送する搬送手段と、小切手4を搬送する搬送手段とを備え、一方の搬送手段はFPGA104の制御に従って動作するよう構成され、CPU101は、第1省電力状態でCPU101をスリープ状態に移行させる前に、上記搬送手段を含む電力制御対象部203に対する電源供給を停止させてもよい。この場合、FPGA104への電源供給を停止する段階と、CPU101をスリープ状態に移行させる段階とに加え、ロール紙3を搬送する搬送手段、小切手4を搬送する搬送手段、搬送された小切手4に担持された情報を読み取るMICRヘッド35（読み取り手段）或いは表面CISユニット47（読み取り手段）及び裏面CISユニット48（読み取り手段）、搬送された小切手4に印刷等の記録をするインクジェットヘッド10（記録手段）等の処理手段への電源供給を停止する段階を設けたことで、これら処理手段の有するモーターのホールド電流など待機時の消費電流が大きく電源供給停止後の復帰に時間が掛からない処理手段を優先して電源供給を停止することができ、消費電力のより一層の抑制を図ることができ、また、FPGA104のコンフィギュレーションの発生頻度を適切に調整できる。20

#### 【0051】

なお、上記実施形態は本発明を適用した一例を示すものであり、本発明はこれに限定されるものではない。上記実施形態においては、媒体処理装置1のい制御デバイスとして、CPU101と、コンフィギュレーションを要するプログラマブルデバイスとしてのFPGA104を備えた構成を例に挙げて説明したが、本発明はこれに限定されるものではなく、広義のPLD（プログラマブルロジックデバイス）に含まれるデバイスであれば、例えばCPLD（Complex Programmable Logic Device）を制御デバイスとして備えた構成としてもよい。また、CPU101やプログラマブルデバイスの数について特に制限はなく、より多くのプログラマブルデバイス或いはプログラマブルデバイス以外の制御デバイスを備えた構成としてもよい。また、FPGA104は、ROM105が外部接続された構成に限定されず、内蔵するメモリーからコンフィギュレーションデータをロードするものであってもよい。

また、図3のブロック図に示した各機能部の少なくとも一部は機能的構成を示しており、全ての機能部を独立したハードウェアにより構成する必要はなく、ソフトウェアとハードウェアとの協働により、複数の機能部の機能を1つのハードウェアに集約して実現することも、一つの機能部を複数のハードウェアにより実現することも勿論可能である。また、上述の動作を行うCPU101が実行するプログラムはフラッシュROM102が記憶する構成に限らず、可搬型の記録媒体に記憶されている構成であってもよいし、或いは、通信回線を介して接続された他の装置にダウンロード可能に記憶され、これらの装置から媒体処理装置1が上記プログラムをダウンロードして実行してもよく、その他の構成についても任意に変更可能である。40

#### 【符号の説明】

#### 【0052】

1 … 媒体処理装置、3 … ロール紙（処理対象媒体）、4 … 小切手（処理対象媒体）、5 … ホストコンピューター（外部の装置）、8 … 媒体処理システム、10 … インクジェットヘッド（記録手段）、35 … M I C R ヘッド（読み取り手段）、44 … インクジェットプリンターユニット、47 … 表面C I S ユニット（読み取り手段）、48 … 裏面C I S ユニット（読み取り手段）、60 … サーマルプリンターユニット、65 … サーマルヘッド（記録手段）、91、92、93 … モータードライバー、95 … 電源部、101 … C P U （制御デバイス）、104 … F P G A （制御デバイス、プログラマブルデバイス）、201、202 … 電力制御対象部、203 … 電力制御対象部（処理手段）。

【図1】

【図2】

【図3】

【図4】

【図5】

---

フロントページの続き

(56)参考文献 特開2009-124375(JP,A)

特開2008-203704(JP,A)

特開2011-159047(JP,A)

特開2004-135215(JP,A)

特開平11-259162(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 06 F 1 / 32

B 41 J 29 / 38