# (19)**日本国特許庁(JP)**

# (12)**公表特許公報(A)**

(11)公表番号 **特表2023-528051** (P2023-528051A)

(43)公表日 令和5年7月3日(2023.7.3)

| H 0 1 L 23<br>H 0 1 L 23<br>H 0 1 L 23                                   | 1/822 (2006.01)<br>3/12 (2006.01)<br>1/3205(2006.01)<br>1/8234(2006.01)<br>1/8232(2006.01) | FI<br>H01L<br>H01L<br>H01L<br>H01L<br>H01L<br>mg查請求 有 | 27/04<br>23/12<br>21/88<br>27/04<br>27/06<br>予備審査請习 | A<br>3 0 1 L<br>J<br>E<br>1 0 2 A<br>対 未請求 | 5 F<br>5 F<br>5 F   | コード(参考)<br>033<br>038<br>048<br>102<br>最終頁に続く |  |

|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-------------------------------------------------------|-----------------------------------------------------|--------------------------------------------|---------------------|-----------------------------------------------|--|

| (21)出願番号 特願2022-573672(P2022-573672)<br>(86)(22)出願日 令和3年5月25日(2021.5.25) |                                                                                            |                                                       | (71)出願人                                             | 592054856<br>ウルフスピード インコーポレイテッド            |                     |                                               |  |

| (85)翻訳文提出日 令和5年1月19日(2023.1.19)                                          |                                                                                            |                                                       | WOLFSPEED, INC.                                     |                                            |                     |                                               |  |

| (86)国際出願番号 PCT/US2021/033981                                             |                                                                                            |                                                       | アメリカ合衆国 ノースカロライナ州 2                                 |                                            |                     |                                               |  |

| (87)国際公開番号                                                               | 国際公開番号 WO2021/247276                                                                       |                                                       |                                                     | 7703 ダラム シリコン ドライブ 4                       |                     |                                               |  |

| (87)国際公開日                                                                | 图際公開日 令和3年12月9日(2021.12.9)                                                                 |                                                       |                                                     | 6 0 0                                      |                     |                                               |  |

| (31)優先権主張番号 16/889,432                                                   |                                                                                            | (74)代理人                                               | 110000855                                           |                                            |                     |                                               |  |

| (32)優先日                                                                  | 令和2年6月1日(2020.6.1)                                                                         |                                                       |                                                     | 弁理士法人浅村特許事務所                               |                     |                                               |  |

| (33)優先権主張国・地域又は機関                                                        |                                                                                            |                                                       | (72)発明者                                             | アルコーン、テリー                                  |                     |                                               |  |

|                                                                          | 米国(US)                                                                                     |                                                       |                                                     | アメリカ合                                      | 衆国、ノースカ             | <b>ウロライナ、ケ</b>                                |  |

| (81)指定国・地域                                                               | AP(BW,GH,GM,KE,LR,LS,MW,MZ,NA                                                              |                                                       |                                                     | アリー、ワイベル レイン 107                           |                     |                                               |  |

|                                                                          | ,RW,SD,SL,ST,SZ,TZ,UG,ZM,ZW),EA(                                                           |                                                       | (72)発明者                                             | ナミシア、ダニエル                                  |                     |                                               |  |

|                                                                          | AM,AZ,BY,KG,KZ,RU,TJ,                                                                      | TM),EP(AL,A                                           |                                                     | アメリカ合                                      | アメリカ合衆国、ノースカロライナ、ウ  |                                               |  |

|                                                                          | T,BE,BG,CH,CY,CZ,DE,DI                                                                     | K,EE,ES,FI,FR                                         |                                                     | ェイク フォ                                     | ェイク フォレスト、バークストーン コ |                                               |  |

|                                                                          | ,GB,GR,HR,HU,IE,IS,IT,L <sup>-</sup><br>上                                                  | T,LU,LV,MC,<br>最終頁に続く                                 |                                                     | <b>-</b>                                   | 3                   | 最終頁に続く                                        |  |

(54)【発明の名称】 ダイの前面でのピラー接続及び裏面での受動デバイス集積のための方法

# (57)【要約】

集積回路デバイスは、第1の表面と、第2の表面と、第1の表面と第2の表面との間にあり、第1の表面に隣接する複数のトランジスタ・セルを含む半導体層構造と、トランジスタ・セルに結合された端子と、を有する高周波トランジスタ増幅器ダイを含む。少なくとも1つの受動電子部品が、ダイの第2の表面上に設けられ、例えば、少なくとも1つの導電性ビアによって、端子のうちの少なくとも1つに電気的に接続される。1つ又は複数の導電性ピラー構造がダイの第1の表面から突出して、端子のうちの1つ又は複数への電気的接続を提供することができる。

### 【特許請求の範囲】

### 【請求項1】

第1の表面、第2の表面、前記第1の表面と前記第2の表面との間にあり、前記第1の表面に隣接する複数のトランジスタ・セルを備える半導体層構造、及び前記トランジスタ・セルに結合された端子を備える高周波(「RF」)トランジスタ増幅器ダイと、

前記ダイの前記第2の表面上にあり、前記端子のうちの少なくとも1つに電気的に接続された少なくとも1つの受動電子部品と、

を備える、集積回路デバイス。

### 【請求項2】

前記端子が、前記トランジスタ・セルによって画定されるRFトランジスタ増幅器の入力端子、出力端子、及び/又は接地端子を含む、請求項1に記載の集積回路デバイス。

### 【請求項3】

前記少なくとも1つの受動電子部品が、前記ダイの前記第2の表面上の、前記RFトランジスタ増幅器のための入力インピーダンス整合回路、出力インピーダンス整合回路、及び/又は高調波終端回路の少なくとも一部を画定する、請求項2に記載の集積回路デバイス。

### 【請求項4】

前記少なくとも1つの受動電子部品が、前記ダイの前記第2の表面上のディスクリート・コンデンサ、インダクタ、及び/又は抵抗器を含む少なくとも1つの集積受動デバイス(IPD)である、請求項1から3までのいずれか一項に記載の集積回路デバイス。

### 【請求項5】

前記ダイの前記第2の表面上に延在し、前記少なくとも1つの受動電子部品を前記端子のうちの前記少なくとも1つに電気的に接続する金属層、

をさらに備える、請求項1から3までのいずれか一項に記載の集積回路デバイス。

### 【請求項6】

前記金属層が第1の金属層であり、

前記第2の表面の反対側の前記第1の金属層上に絶縁体層をさらに備え、

前記少なくとも1つの受動電子部品が、前記第1の金属層の反対側の前記絶縁体層上にあり、1つ又は複数のディスクリート・コンデンサ、インダクタ、及び/又は抵抗器を画定する第2の金属層のパターンを含む、

請求項5に記載の集積回路デバイス。

### 【請求項7】

前記ダイの前記第2の表面及び前記半導体層構造内に延在して、前記ダイの前記第2の表面上の前記金属層を前記端子のうちの前記少なくとも1つに電気的に接続する少なくとも1つの導電性ビア、

をさらに備える、請求項5に記載の集積回路デバイス。

### 【請求項8】

前記半導体層構造がIII族窒化物材料を含み、前記ダイが前記III族窒化物材料と前記第2の表面との間に炭化ケイ素基板を含む、請求項1から7までのいずれか一項に記載の集積回路デバイス。

## 【請求項9】

前記ダイの前記第1の表面から突出し、前記端子のうちの1つ若しくは複数に電気的接続を提供する1つ又は複数の導電性ピラー構造、

をさらに備える、請求項1から3までのいずれか一項に記載の集積回路デバイス。

### 【請求項10】

1つ又は複数の導電性接続部を含むパッケージ基板、

### をさらに備え、

前記1つ又は複数の導電性ピラー構造が、前記ダイを前記ダイの前記第1の表面に隣接する前記パッケージ基板に取り付け、前記端子のうちの前記1つ若しくは複数を前記1つ又は複数の導電性接続部に電気的に接続する、

20

10

30

50

請求項9に記載の集積回路デバイス。

### 【請求項11】

第1の表面、第2の表面、前記第1の表面と前記第2の表面との間にあり、前記第1の表面に隣接する複数のトランジスタ・セルを備える半導体層構造、及び前記トランジスタ・セルに結合された端子を備える高周波(「RF」)トランジスタ増幅器ダイと、

前記ダイの前記第1の表面から突出し、前記端子のうちの1つ若しくは複数に電気的に接続された1つ又は複数の導電性ピラー構造と、

前記ダイの前記第2の表面及び前記半導体層構造内に延在し、前記端子のうちの少なくとも1つに電気的である、少なくとも1つの導電性ビアと、

を備える、集積回路デバイス。

# 【請求項12】

前記端子が、前記トランジスタ・セルによって画定されるRFトランジスタ増幅器の入力端子、出力端子、及び/又は接地端子を含む、請求項11に記載の集積回路デバイス。

### 【請求項13】

前記1つ又は複数の導電性ピラー構造が前記入力端子及び/又は前記出力端子への電気的接続を提供し、前記少なくとも1つの導電性ビアが前記接地端子への電気的接続を提供する、請求項12に記載の集積回路デバイス。

### 【請求項14】

前記ダイが前記半導体層構造と前記ダイの前記第2の表面との間に基板を含み、前記少なくとも1つの導電性ビアが前記基板を貫いて延在し、前記半導体層構造が、前記基板上に1つ又は複数のエピタキシャル層を含む、請求項11から13までのいずれか一項に記載の集積回路デバイス。

# 【請求項15】

前記半導体層構造がIII族窒化物材料を含み、前記基板が炭化ケイ素基板を含む、請求項14に記載の集積回路デバイス。

### 【請求項16】

1 つ又は複数の導電性接続部を含むパッケージ基板、

### をさらに備え、

前記1つ又は複数の導電性ピラー構造が、前記ダイを前記ダイの前記第1の表面に隣接する前記パッケージ基板に取り付け、前記端子のうちの前記1つ若しくは複数を前記1つ又は複数の導電性接続部に電気的に接続する、

請 求 項 1 1 か ら 1 3 ま で の い ず れ か 一 項 に 記 載 の 集 積 回 路 デ バ イ ス 。

### 【 請 求 項 1 7 】

少なくとも1つの導電性接続部を含むパッケージ基板をさらに備え、

前記ダイが前記ダイの前記第2の表面に隣接する前記パッケージ基板に取り付けられ、前記少なくとも1つの導電性ビアが前記端子のうちの前記少なくとも1つを前記少なくと も1つの導電性接続部に電気的に接続する、

請求項11から13までのいずれか一項に記載の集積回路デバイス。

# 【請求項18】

前記ダイの前記第2の表面上に少なくとも1つの受動電子部品をさらに備え、前記少なくとも1つの受動電子部品が前記少なくとも1つの導電性ビアによって前記端子のうちの前記少なくとも1つに電気的に接続されている、

請求項11から13までのいずれか一項に記載の集積回路デバイス。

### 【請求項19】

第1の表面、第2の表面、前記第1の表面と前記第2の表面との間にあり、前記第1の表面に隣接する複数のトランジスタ・セルを備える半導体層構造、前記半導体層構造と前記第2の表面との間の基板、及び前記トランジスタ・セルに結合された端子を備える高周波(「RF」)トランジスタ増幅器構造を形成するステップと、

前記第1の表面から突出する1つ又は複数の導電性ピラー構造を形成して、前記端子のうちの1つ又は複数への電気的接続を提供するステップと、

10

20

30

40

前記RFトランジスタ増幅器構造を個片化して、約50~約200ミクロン以上の厚さを有する前記基板の一部を含むRFトランジスタ増幅器ダイを画定するステップと、を含む、集積回路デバイスを製造する方法。

### 【請求項20】

前記第1の表面と前記第2の表面との間に延在する前記ダイの側壁が、前記第2の表面に隣接する第2の部分とは異なる表面特性を有する、前記第1の表面に隣接する第1の部分を含む、請求項19に記載の方法。

### 【請求項21】

前記第1の表面から前記第2の表面に向かって前記半導体層構造を貫いて前記基板内に延在するトレンチを前記半導体層構造内に形成して、前記ダイの前記側壁の前記第1の部分を画定するステップ、

をさらに含む、請求項20に記載の方法。

### 【請求項22】

前記トレンチを形成するステップが前記1つ又は複数の導電性ピラー構造を形成する前に行われる、請求項21に記載の方法。

### 【 請 求 項 2 3 】

個片化するステップが、前記基板の前記トレンチの底部をダイシング又はソーイングして、前記ダイの前記側壁の前記第2の部分を画定するステップを含む、請求項21又は2 2に記載の方法。

# 【請求項24】

前記半導体層構造がIII族窒化物材料を含み、前記基板が炭化ケイ素を含む、請求項19から23までのいずれか一項に記載の方法。

### 【請求項25】

第1の表面、第2の表面、前記第1の表面と前記第2の表面との間にあり、前記第1の表面に隣接する複数のトランジスタ・セルを備える半導体層構造、及び前記トランジスタ・セルに結合された端子を備える高周波(「RF」)トランジスタ増幅器構造を形成するステップと、

前記第1の表面から突出する1つ又は複数の導電性ピラー構造を形成して、前記端子のうちの1つ又は複数への電気的接続を提供するステップと、

前記第2の表面内に、且つ前記半導体層構造を貫いて延在する少なくとも1つの導電性ビアを形成して、前記端子のうちの少なくとも1つへの電気的接続を提供するステップと

を含む、集積回路デバイスを製造する方法。

# 【請求項26】

前記RFトランジスタ増幅器が前記半導体層構造と前記第2の表面との間に基板をさらに含み、前記少なくとも1つの導電性ビアを形成するステップが

前記第1の表面をウエハ・キャリアに取り付けるステップと、

前記第2の表面に対して薄化操作を行って、前記基板の厚さを低減するステップと、

前記薄化操作に応答して、前記第1の表面が前記ウエハ・キャリアに取り付けられた状態で、前記第2の表面内に延在する前記少なくとも1つの導電性ビアを形成するステップと、

を含む、請求項25に記載の方法。

# 【請求項27】

前記1つ又は複数の導電性ピラー構造を形成するステップが前記第1の表面を前記ウエハ・キャリアに取り付ける前に実行される、請求項26に記載の方法。

# 【請求項28】

前記ウエハ・キャリアが第1のウエハ・キャリアであり、前記1つ又は複数の導電性ピラー構造を形成するステップが、

前記第1の表面を前記第1のウエハ・キャリアから分離するステップと、

前記第2の表面を第2のウエハ・キャリアに取り付けるステップと、

20

10

30

40

前記第2の表面が前記第2のウエハ・キャリアに取り付けられた状態で、前記第1の表面上に前記1つ又は複数の導電性ピラー構造を形成するステップと、

を含む、請求項26に記載の方法。

### 【請求項29】

前記第1の表面が前記ウエハ・キャリアに取り付けられた状態で、前記第2の表面上に少なくとも1つの受動電子部品を形成するステップをさらに含み、

前記少なくとも 1 つの受動電子部品が前記少なくとも 1 つの導電性ビアによって前記端子のうちの前記少なくとも 1 つに電気的に接続される、

請求項26から28までのいずれか一項に記載の方法。

### 【 請 求 項 3 0 】

前記少なくとも1つの受動電子部品を形成するステップが、

前記薄化操作に応答して前記第2の表面上に第1の金属層を形成するステップと、

前記第2の表面の反対側の前記第1の金属層上に絶縁体層を形成するステップと、

前記第1の金属層の反対側の前記絶縁体層上に第2の金属層を形成及びパターニングするステップであって、前記少なくとも1つの受動電子部品が、1つ又は複数のディスクリート・コンデンサ、インダクタ、及び/又は抵抗器を画定する前記第2の金属層のパターンを含む、ステップと、

を含む、請求項29に記載の方法。

【発明の詳細な説明】

# 【技術分野】

[0001]

# 優先権主張

本出願は、2020年6月1日に米国特許商標庁に出願された米国特許出願第16/889,432号の優先権を主張するものであり、その開示は参照により本明細書に組み込まれる。

# [0002]

本開示は、集積回路デバイスに関し、より詳細には、電力増幅器デバイス、デバイス・ パッケージング、及び関連する製造方法に関する。

# 【背景技術】

## [0003]

Rバンド(0.5~1GHz)、Sバンド(3GHz)、及びXバンド(10GHz)などの高周波で動作しながら高い電力処理能力を必要とする電気回路が、近年、ますます普及してきている。特に、無線通信システムの基地局などの様々な用途において、高周波(マイクロ波を含む)で高周波(「RF」)信号を増幅するために使用されるRF電力増幅器に対する高い需要が現在ある。RF電力増幅器によって増幅された信号は、多くの場合、メガヘルツ(MHz)~ギガヘルツ(GHz)の範囲の周波数を有する変調搬送波を有する信号を含む。これらのRF電力増幅器は、高い信頼性、良好な線形性を示し、且つ高い出力電力レベルを処理する必要がある場合がある。

# [0004]

多くのRF電力増幅器設計は、増幅デバイスとして半導体スイッチング・デバイスを利用する。これらのスイッチング・デバイスの例には、金属酸化膜半導体電界効果トランジスタ(MOSFET:metal-oxide semiconductor field-effect transistor)、二重拡散金属酸化膜半導体(DMOS:double-diffused metal-oxide semiconductor)トランジスタ、高電子移動度トランジスタ(HEMT:high electron mobility transistor)、金属半導体電界効果トランジスタ(MESFET:metal-semiconductor field-effect transistor)、横方向拡散金属酸化膜半導体(LDMOS:laterally-diffused metal-oxide semiconductor)トランジスタなどを含む電界効果トランジスタ(FET)などのパワー・トランジスタ・デバイスが挙

10

20

30

40

げられる。

# [0005]

RF増幅器は、典型的には、半導体集積回路チップとして形成される。ほとんどのRF増幅器は、シリコンで、又は炭化ケイ素(「SiC」)及びIII族窒化物材料などのワイド・バンドギャップ半導体材料(すなわち、1.40eVよりも大きいバンドギャップを有する)を使用して実装されている。本明細書で使用される場合、「III族窒化物」という用語は、窒素と周期表のIII族の元素、通常は、アルミニウム(A1)、ガリウム(Ga)、及び/又はインジウム(In)との間で形成される半導体化合物を指す。この用語は、A1GaN及びA1InGaNなどの三元化合物及び四元化合物も指す。これらの化合物は、1モルの窒素が合計1モルのIII族元素と結合した実験式を有する。

[0006]

RFトランジスタ増幅器は、各段が、典型的には、トランジスタ増幅器として実装されている1つ又は複数の増幅段を含むことができる。出力電力及び電流処理能力を増加させるために、RFトランジスタ増幅器は、典型的には、多数の個々の「単位セル」トランジスタ構造が電気的に並列に配置された「単位セル」構成で実装される。RFトランジスタ増幅器は、単一の集積回路チップ若しくは「ダイ」として実装されてもよく、又は複数のダイを含んでもよい。ダイ又はチップとは、電子回路素子が製造される半導体材料又は他の基板の小さなブロックを指すことがある。複数のRFトランジスタ増幅器ダイが使用される場合、それらは、直列及び/又は並列に接続されることがある。

### [0007]

シリコン・ベースのRF増幅器は、典型的には、横方向拡散金属酸化膜半導体(LDMOS)トランジスタを使用して実装され、比較的安価な製造で高レベルの線形性を示すことができる。III族窒化物ベースのRF増幅器は、主に、横方向拡散金属酸化膜半導体(LDMOS)トランジスタ増幅器が固有の性能限界を有することがある高電力及び/又は高周波動作を必要とする用途において、典型的には高電子移動度トランジスタ(HEMT)を使用して実装される。

## [00008]

高電子移動度トランジスタ(HEMT)デバイスの動作では、二次元電子ガス(2DEG:two・dimensional electron gas)が、バンドギャップ・エネルギーが異なる2つの半導体材料のヘテロ接合において形成され、バンドギャップが小さい方の材料がより高い電子親和力を有する。二次元電子ガス(2DEG)は、ペンドギャップが小さい方の材料における蓄積層であり、非常に高いシート電子濃度を含むべた不純物散乱が減少しているため高い電子移動度を可能にする二次元電子ガス(2DEG)層に移動する。この高キャリア濃度と高キャリア移動度との組合せは、高電子方の優に移動する。この高キャリア濃度と高キャリア移動度との組合せは、高電子移動度トランジスタ(HEMT)に非常に大きな相互コンダクタンスを与えることができる。度トランジスタ(MOSFET)に勝る強力な特別の優位性をもたらすことがある。III族窒化物ベースの材料系で製造された高電子移動度トランジスタは、前述の高い破壊電界、広いバンドギャップ、大きな伝導帯オフセット、及び/又は高い飽和電子ドリフト速度を含む材料特性の組合せのために、大量の高周波(RF)電力を生成する可能性も有する。

### [0009]

RF増幅器は、多くの場合、基本動作周波数におけるRF信号のために能動トランジスタ・ダイ(例えば、MOSFET、高電子移動度トランジスタ(HEMT)、横方向拡散金属酸化膜半導体(LDMOS)などを含む)とそれに接続された伝送線路との間のインピーダンス整合を改善するように設計されたインピーダンス整合回路などの整合回路と、2次及び3次高調波成分などのデバイス動作中に生成され得る高調波成分を少なくとも部分的に終端するように設計された高調波終端回路と、を含む。高調波成分の終端は、相互変調歪み成分の生成にも影響を与える。

# [0010]

10

20

30

RFトランジスタ増幅器ダイ、並びにインピーダンス整合回路及び高調波終端回路は、デバイス・パッケージ内に封入されることがある。集積回路のパッケージングとは、ダイを物理的損傷及び/又は腐食から保護し、外部回路への接続のための電気的コンタクトを支持する支持ケース又はパッケージ内に1つ若しくは複数のダイを封入することを指してもよい。RF増幅器を入出力RF伝送線路及びバイアス電圧源などの外部システム並びに/又は回路素子に電気的に接続するために、電気リードがパッケージから延在することがある。

### [0011]

集積回路デバイス・パッケージの入力及び出力整合回路は、典型的には、能動トランジスタ・ダイのインピーダンスを固定値に整合させるように構成されたインピーダンス整合回路の少なくとも一部を提供するLCネットワークを含む。典型的には、入力及び出力RF整合回路は、パッケージ・フットプリントを増加させる可能性があるオフダイの構成要素及び実施態様を採用する。また、ダイとオフダイの構成要素との間など、パッケージ内の接続は、ワイヤ・ボンドに依存することがある。このような従来の接続の幾何学的形状は、制御することが困難である場合があり、及び/又はより複雑なRF IC設計では精度に限界がある場合がある。

【先行技術文献】

# 【特許文献】

### [0012]

【特許文献 1 】米国特許第Re.34,861号

【特許文献2】米国特許第4,946,547号

【特許文献3】米国特許第5,200,022号

【特許文献4】米国特許第6,218,680号

【特許文献 5 】米国特許第 5 , 2 1 0 , 0 5 1 号

【特許文献 6 】米国特許第 5 , 3 9 3 , 9 9 3 号

【特許文献7】米国特許第5,523,589号

【特許文献8】米国特許第7,030,428号

【特許文献9】米国特許第8,563,372号

【特許文献10】米国特許第9,214,352号

【特許文献11】米国特許第5,192,987号

【特許文献12】米国特許第5,296,395号

【特許文献13】米国特許第6,316,793号

【特許文献14】米国特許第6,548,333号

【特許文献15】米国特許第7,544,963号

【特許文献16】米国特許第7,548,112号

【特許文献17】米国特許第7,592,211号

【特許文献18】米国特許第7,615,774号

【特許文献19】米国特許第7,709,269号

【特許文献20】米国特許第8,049,252号

【特許文献 2 1 】米国特許第7 , 0 4 5 , 4 0 4 号

【 特 許 文 献 2 2 】 米 国 特 許 第 8 , 1 2 0 , 0 6 4 号

【特許文献23】米国特許第7,291,529号

【特許文献24】米国特許第7,932,111号

【 特 許 文 献 2 5 】 米 国 特 許 第 7 , 2 5 9 , 4 0 2 号 【 特 許 文 献 2 6 】 米 国 特 許 第 8 , 5 1 3 , 6 8 6 号

【特許文献27】米国仮特許出願第63/004,760号

【発明の概要】

【課題を解決するための手段】

### [0013]

一部の実施例によると、集積回路デバイスは、第1の表面と、第2の表面と、第1の表

20

10

30

40

面と第2の表面との間にあり、第1の表面に隣接する複数のトランジスタ・セルを含む半 導体層構造と、トランジスタ・セルに結合された端子と、を有する高周波(「RF」)ト ランジスタ増幅器ダイを含む。少なくとも1つの受動電子部品が、ダイの第2の表面上に あり、端子のうちの少なくとも1つに電気的に接続されている。

### [0014]

一部の実施例において、端子には、トランジスタ・セルによって画定される R F トランジスタ増幅器の入力端子、出力端子、及び / 又は接地端子が含まれてもよい。

### [0015]

一部の実施例では、少なくとも1つの受動電子部品は、ダイの第2の表面上の、RFトランジスタ増幅器のための入力インピーダンス整合回路、出力インピーダンス整合回路、及び/又は高調波終端回路の少なくとも一部を画定することができる。

[0016]

一部の実施例では、少なくとも1つの受動電子部品は、ダイの第2の表面上のディスクリート・コンデンサ、インダクタ、及び/又は抵抗器を含む少なくとも1つの集積受動デバイス(IPD:integrated passive device)であってもよく、又はそれを含んでもよい。

### [0017]

一部の実施例では、金属層が、ダイの第2の表面上に延在し、少なくとも1つの受動電子部品を端子のうちの少なくとも1つに電気的に接続することができる。

### [0018]

一部の実施例では、金属層は、第1の金属層であってもよく、絶縁体層が、第2の表面の反対側の第1の金属層上に設けられてもよい。少なくとも1つの受動電子部品は、第1の金属層の反対側の絶縁体層上にあてもよく、1つ又は複数のディスクリート・コンデンサ、インダクタ、及び/又は抵抗器を画定する第2の金属層のパターンを含むことができる。

# [0019]

一部の実施例では、少なくとも1つの導電性ビアが、ダイの第2の表面及び半導体層構造内に延在して、ダイの第2の表面上の金属層を端子のうちの少なくとも1つに電気的に接続することができる。

# [ 0 0 2 0 ]

一部の実施例では、半導体層構造は、III族窒化物材料を含んでもよく、ダイは、III族窒化物材料と第2の表面との間の炭化ケイ素基板であってもよい。

### [0021]

ー部の実施例では、1つ又は複数の導電性ピラー構造が、ダイの第1の表面から突出し 、端子のうちの1つ又は複数への電気的接続を提供することができる。

# [0022]

一部の実施例では、1つ又は複数の導電性接続部を含むパッケージ基板が提供されてもよい。1つ又は複数の導電性ピラー構造は、ダイをダイの第1の表面に隣接するパッケージ基板に取り付けることができ、1つ又は複数の端子を1つ又は複数の導電性接続部に電気的に接続することができる。

[ 0 0 2 3 ]

一部の実施例によると、集積回路デバイスは、第1の表面と、第2の表面と、第1の表面と第2の表面との間にあり、第1の表面に隣接する複数のトランジスタ・セルを含む半導体層構造と、トランジスタ・セルに結合された端子を有する高周波(「RF」)トランジスタ増幅器ダイと、を含む。1つ又は複数の導電性ピラー構造が、ダイの第1の表面から突出し、端子のうちの1つ又は複数に電気的に接続される。少なくとも1つの導電性ビアが、ダイの第2の表面及び半導体層構造内に延在し、端子のうちの少なくとも1つに電気的である。

### [0024]

一部の実施例では、端子には、トランジスタ・セルによって画定されるRFトランジス

10

20

30

40

夕増幅器の入力端子、出力端子、及び/又は接地端子が含まれてもよい。

### [0025]

一 部 の 実 施 例 で は 、 1 つ 又 は 複 数 の 導 電 性 ピ ラ ー 構 造 は 、 入 力 端 子 及 び / 又 は 出 力 端 子 への電気的接続を提供することができ、少なくとも1つの導電性ビアは、接地端子への電 気的接続を提供することができる。

# [0026]

一部の実施例では、ダイは、半導体層構造とダイの第2の表面との間に基板を含んでも よく、少なくとも1つの導電性ビアは、基板を貫いて延在してもよく、半導体層構造は、 基板上に1つ又は複数のエピタキシャル層を含んでもよい。

### [0027]

一部の実施例では、半導体層構造は、III族窒化物材料を含んでもよく、基板は、炭 化ケイ素基板であってもよい。

### [0028]

一 部 の 実 施 例 で は 、 1 つ 又 は 複 数 の 導 電 性 接 続 部 を 含 む パ ッ ケ ー ジ 基 板 が 提 供 さ れ て も よ い 。 1 つ 又 は 複 数 の 導 電 性 ピラ - 構 造 は 、 ダ イ を ダ イ の 第 1 の 表 面 に 隣 接 す る パ ッ ケ -ジ 基 板 に 取 り 付 け る こ と が で き 、 1 つ 又 は 複 数 の 端 子 を 1 つ 又 は 複 数 の 導 電 性 接 続 部 に 電 気的に接続することができる。

### [0029]

一 部 の 実 施 例 で は 、 少 な く と も 1 つ の 導 電 性 接 続 部 を 含 む パ ッ ケ ー ジ 基 板 が 提 供 さ れ て もよく、ダイは、ダイの第2の表面に隣接するパッケージ基板に取り付けられてもよい。 少 な く と も 1 つ の 導 電 性 ビ ア が 端 子 の 少 な く と も 1 つ を 少 な く と も 1 つ の 導 電 性 接 続 部 に 電気的に接続することができる。

### [0030]

一部の実施例では、少なくとも1つの受動電子部品が、ダイの第2の表面上に設けられ てもよい。少なくとも1つの受動電子部品は、少なくとも1つの導電性ビアによって端子 のうちの少なくとも1つに電気的に接続されてもよい。

# [0031]

一部の実施例によると、集積回路デバイスを製造する方法は、第1の表面、第2の表面 、 第 1 の 表 面 と 第 2 の 表 面 と の 間 に あ り 、 第 1 の 表 面 に 隣 接 す る 複 数 の ト ラ ン ジ ス タ ・ セ ルを含む半導体層構造、半導体層構造と第2の表面との間の基板、及びトランジスタ・セ ルに結合された端子を有する高周波(「RF」)トランジスタ増幅器構造を形成するステ ップと、 第 1 の表面から突出する 1 つ又は複数の導電性ピラー構造を形成して、端子うち の 1 つ 又 は 複 数 へ の 電 気 的 接 続 を 提 供 す る ス テ ッ プ と 、 R F ト ラ ン ジ ス タ 増 幅 器 構 造 を 個 片化して、RFトランジスタ増幅器ダイを画定するステップと、を含む。RFトランジス 夕 増 幅 器 ダ イ は 、 約 5 0 ~ 約 2 0 0 ミ ク ロ ン 以 上 、 例 え ば 、 約 7 5 ~ 約 1 7 5 ミ ク ロ ン 、 約 1 0 0 ~ 約 1 5 0 ミクロン、約 2 0 0 ミクロン ~ 約 5 0 0 ミクロン、又は約 5 0 0 ~ 約 800ミクロンの厚さを有する基板の一部を含む。

## [0032]

一 部 の 実 施 例 で は 、 第 1 の 表 面 と 第 2 の 表 面 と の 間 に 延 在 す る ダ イ の 側 壁 は 、 第 2 の 表 面に隣接する第2の部分とは異なる表面特性を有する、第1の表面に隣接する第1の部分 を含むことができる。

# [ 0 0 3 3 ]

一部の実施例では、方法は、第1の表面から第2の表面に向かって半導体層構造を貫い て 基 板 内 に 延 在 す る ト レ ン チ を 半 導 体 層 構 造 内 に 形 成 し て 、 ダ イ の 側 壁 の 第 1 の 部 分 を 画 定するステップを含んでもよい。

# [0034]

一 部 の 実 施 例 で は 、 ト レ ン チ を 形 成 す る ス テ ッ プ は 、 1 つ 又 は 複 数 の 導 電 性 ピ ラ ー 構 造 を形成する前に行われてもよい。

### [0035]

一部の実施例では、個片化するステップは、基板のトレンチの底部をダイシング又はソ

10

20

30

ーイングして、ダイの側壁の第2の部分を画定するステップを含むことができる。

### [0036]

一部の実施例では、半導体層構造は、III族窒化物材料を含むことができ、基板は、 炭化ケイ素を含むことができる。

### [0037]

一部の実施例によると、集積回路デバイスを製造する方法は、第1の表面、第2の表面、第1の表面と第2の表面との間にあり、第1の表面に隣接する複数のトランジスタ・セルを含む半導体層構造、及びトランジスタ・セルに結合された端子を備える高周波(「RF」)トランジスタ増幅器構造を形成するステップと、第1の表面から突出する1つ又は複数の導電性ピラー構造を形成して、端子のうちの1つ又は複数への電気的接続を提供するステップと、第2の表面内に、且つ半導体層構造を貫いて延在する少なくとも1つの導電性ビアを形成して、端子のうちの少なくとも1つへの電気的接続を提供するステップと、を含む。

### [0038]

一部の実施例では、RFトランジスタ増幅器は、半導体層構造と第2の表面との間に基板を含むことができる。少なくとも1つの導電性ビアを形成するステップは、第1の表面をウエハ・キャリアに取り付けるステップと、第2の表面に対して薄化操作を行って基板の厚さを低減するステップと、薄化操作に応答して、第1の表面がウエハ・キャリアに取り付けられた状態で、第2の表面内に延在する少なくとも1つの導電性ビアを形成するステップと、を含むことができる。

### [0039]

一部の実施例では、1つ又は複数の導電性ピラー構造を形成するステップは、第1の表面をウエハ・キャリアに取り付ける前に実行されてもよい。

### [0040]

一部の実施例では、ウエハ・キャリアは、第1のウエハ・キャリアであってもよい。1つ又は複数の導電性ピラー構造を形成するステップは、第1のウエハ・キャリアから第1の表面を分離するステップと、第2のウエハ・キャリアに第2の表面を取り付けるステップと、第2の表面が第2のウエハ・キャリアに取り付けられた状態で第1の表面上に1つ又は複数の導電性ピラー構造を形成するステップと、を含むことができる。

# [0041]

一部の実施例では、方法は、第1の表面がウエハ・キャリアに取り付けられた状態で、第2の表面上に少なくとも1つの受動電子部品を形成するステップをさらに含むことができる。少なくとも1つの受動電子部品は、少なくとも1つの導電性ビアによって端子のうちの少なくとも1つに電気的に接続されてもよい。

# [ 0 0 4 2 ]

一部の実施例では、少なくとも1つの受動電子部品を形成するステップは、薄化操作に応答して、第2の表面上に第1の金属層を形成するステップと、第2の表面の反対側の第1の金属層上に絶縁体層を形成するステップと、第1の金属層の反対側の絶縁体層上に第2の金属層を形成及びパターニングするステップと、を含むことができる。少なくとも1つの受動電子部品は、1つ又は複数のディスクリート・コンデンサ、インダクタ、及び/又は抵抗器を画定する第2の金属層のパターンを含むことができる。

### [0043]

一部の実施例による他のデバイス、装置、及び/又は方法は、以下の図面及び詳細な説明を検討すると当業者には明らかになるであろう。上記の実施例のいずれか及びすべての組合せに加えて、すべてのそのような追加の実施例は、本明細書内に含まれ、本発明の範囲内にあり、添付の特許請求の範囲によって保護されることが意図されている。

### 【図面の簡単な説明】

# [0044]

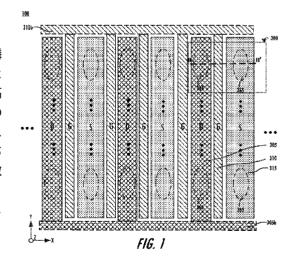

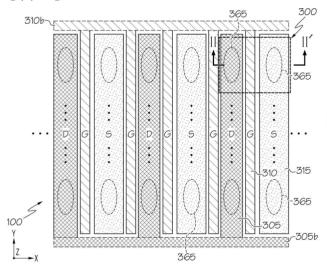

【図1】本開示の一部の実施例によるRFトランジスタ増幅器ダイ又はデバイスの概略平面図である。

20

10

30

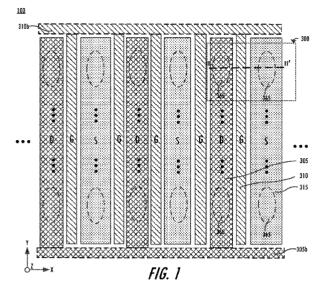

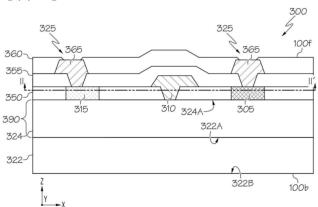

【図2】図1の線II-II′に沿って取られた高周波トランジスタ増幅器ダイのトランジスタ構造の概略断面図である。

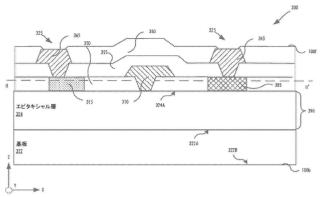

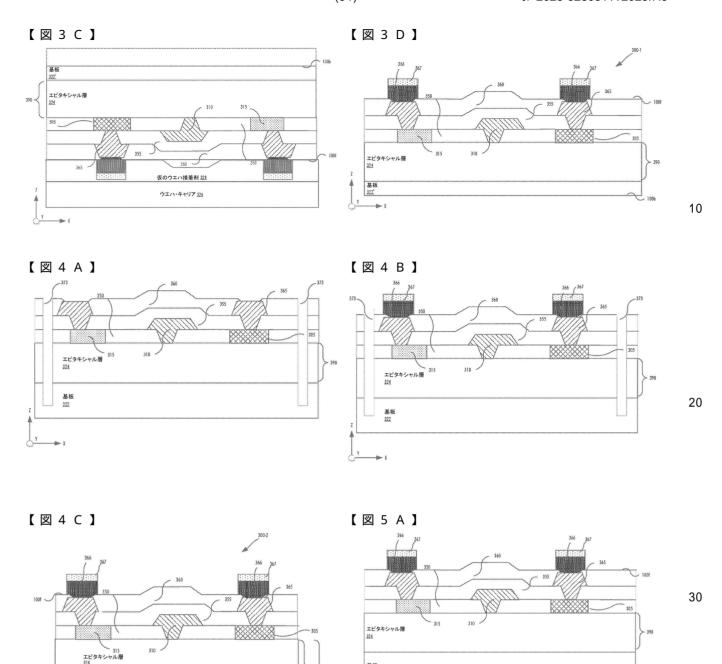

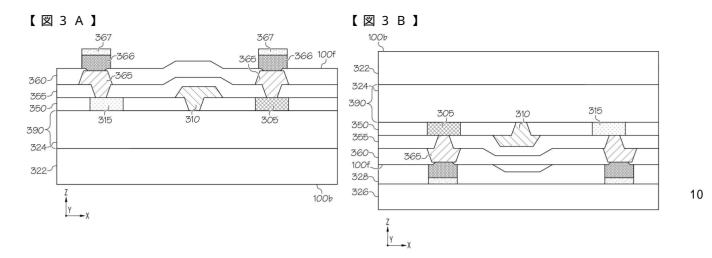

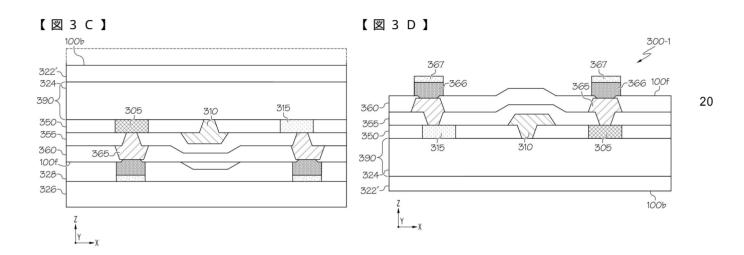

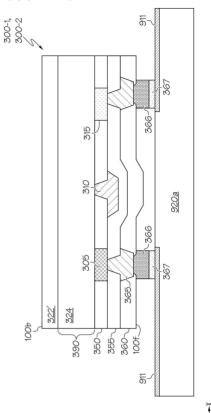

【図3A】本開示の一部の実施例による前面ピラー構造を含むトランジスタ構造を製造する方法を示す断面図である。

【図3B】本開示の一部の実施例による前面ピラー構造を含むトランジスタ構造を製造する方法を示す断面図である。

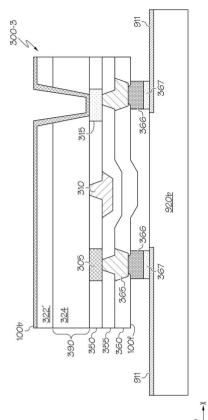

【図3C】本開示の一部の実施例による前面ピラー構造を含むトランジスタ構造を製造する方法を示す断面図である。

【図3D】本開示の一部の実施例による前面ピラー構造を含むトランジスタ構造を製造する方法を示す断面図である。

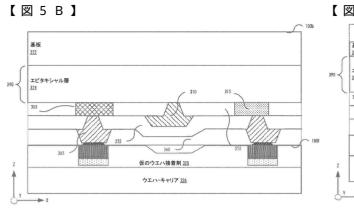

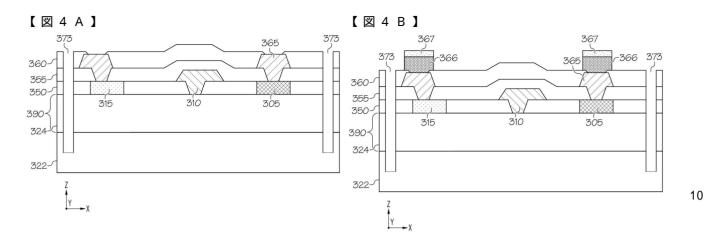

【図4A】本開示の一部の実施例による、ダイ個片化のための前面ピラー構造及びトレンチを含むトランジスタ構造を製造する方法を示す断面図である。

【図4B】本開示の一部の実施例による、ダイ個片化のための前面ピラー構造及びトレンチを含むトランジスタ構造を製造する方法を示す断面図である。

【図4C】本開示の一部の実施例による、ダイ個片化のための前面ピラー構造及びトレンチを含むトランジスタ構造を製造する方法を示す断面図である。

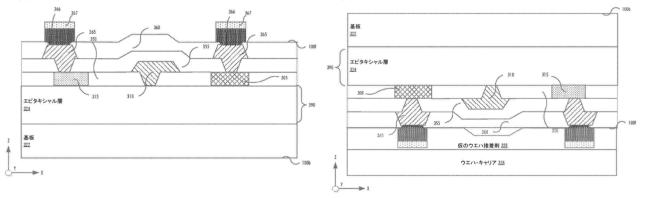

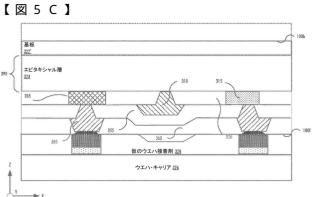

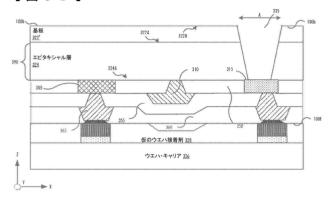

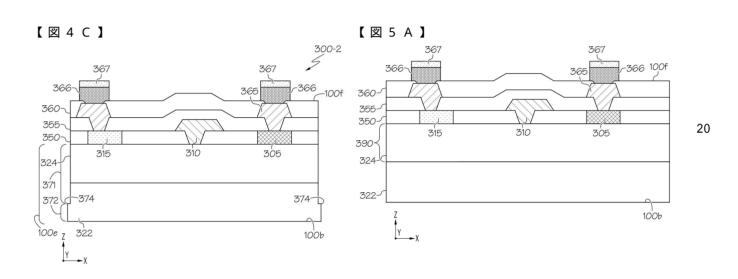

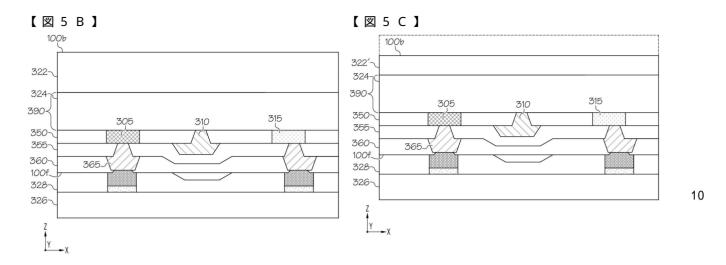

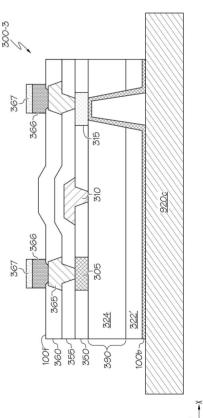

【図 5 A】本開示の一部の実施例による、ウエハ・キャリア・ボンディングを用いて、前面ピラー構造及び導電性ビアを含むトランジスタ構造を製造する方法を示す断面図である

【図 5 B】本開示の一部の実施例による、ウエハ・キャリア・ボンディングを用いて、前面ピラー構造及び導電性ビアを含むトランジスタ構造を製造する方法を示す断面図である

【図 5 C】本開示の一部の実施例による、ウエハ・キャリア・ボンディングを用いて、前面ピラー構造及び導電性ビアを含むトランジスタ構造を製造する方法を示す断面図である

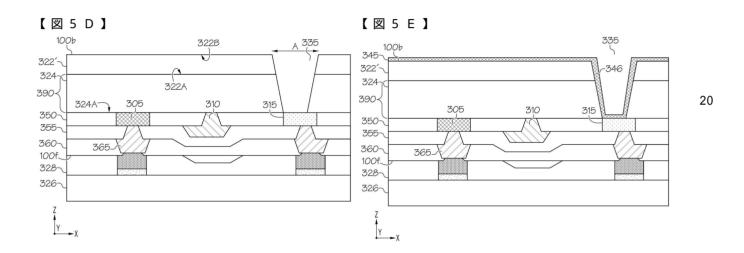

【図5D】本開示の一部の実施例による、ウエハ・キャリア・ボンディングを用いて、前面ピラー構造及び導電性ビアを含むトランジスタ構造を製造する方法を示す断面図である

【図5E】本開示の一部の実施例による、ウエハ・キャリア・ボンディングを用いて、前面ピラー構造及び導電性ビアを含むトランジスタ構造を製造する方法を示す断面図である

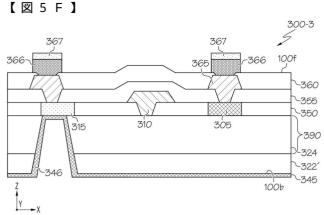

【図 5 F 】本開示の一部の実施例による、ウエハ・キャリア・ボンディングを用いて、前面ピラー構造及び導電性ビアを含むトランジスタ構造を製造する方法を示す断面図である

【図6A】本開示の一部の実施例による、前面ピラー構造及びダイの裏面上の受動デバイスを含むトランジスタ構造を製造する方法を示す断面図である。

【図6B】本開示の一部の実施例による、前面ピラー構造及びダイの裏面上の受動デバイスを含むトランジスタ構造を製造する方法を示す断面図である。

【図7A】本開示の一部の実施例による、複数のウエハ・キャリア・ボンディングを用いて、前面ピラー構造及び導電性ビアを含むトランジスタ構造を製造する方法を示す断面図である。

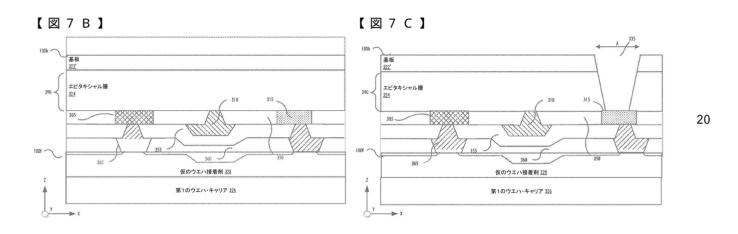

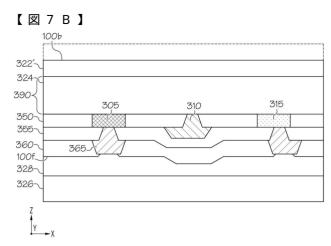

【図7B】本開示の一部の実施例による、複数のウエハ・キャリア・ボンディングを用いて、前面ピラー構造及び導電性ビアを含むトランジスタ構造を製造する方法を示す断面図である。

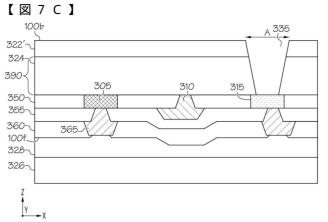

【図7C】本開示の一部の実施例による、複数のウエハ・キャリア・ボンディングを用いて、前面ピラー構造及び導電性ビアを含むトランジスタ構造を製造する方法を示す断面図である。

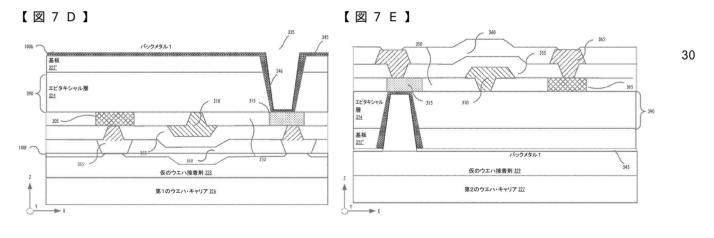

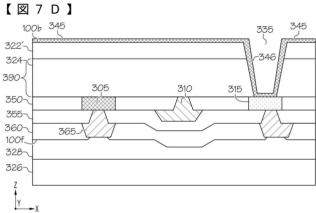

【図7D】本開示の一部の実施例による、複数のウエハ・キャリア・ボンディングを用いて、前面ピラー構造及び導電性ビアを含むトランジスタ構造を製造する方法を示す断面図である。

10

20

30

40

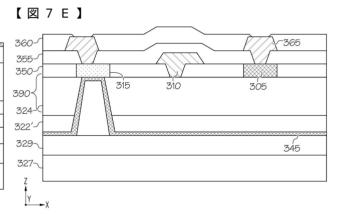

【図7E】本開示の一部の実施例による、複数のウエハ・キャリア・ボンディングを用いて、前面ピラー構造及び導電性ビアを含むトランジスタ構造を製造する方法を示す断面図である。

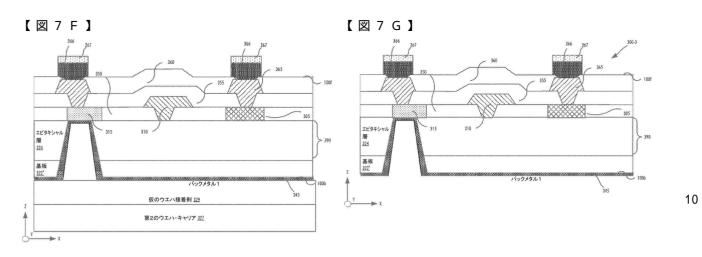

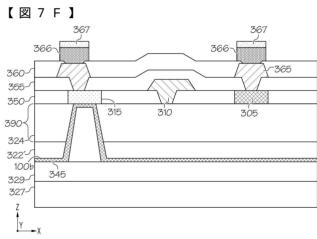

【図7F】本開示の一部の実施例による、複数のウエハ・キャリア・ボンディングを用いて、前面ピラー構造及び導電性ビアを含むトランジスタ構造を製造する方法を示す断面図である。

【図7G】本開示の一部の実施例による、複数のウエハ・キャリア・ボンディングを用いて、前面ピラー構造及び導電性ビアを含むトランジスタ構造を製造する方法を示す断面図である。

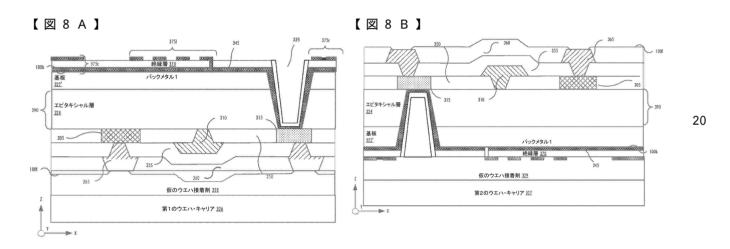

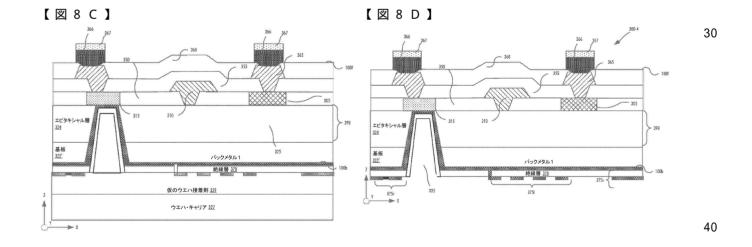

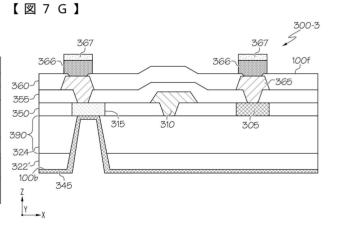

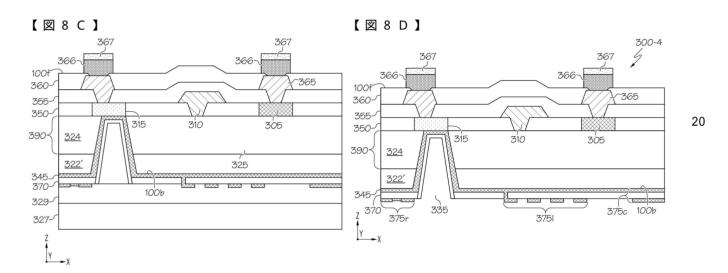

【図8A】本開示の一部の実施例による、複数のウエハ・キャリア・ボンディングを用いて、前面ピラー構造及びダイの裏面上の受動デバイスを含むトランジスタ構造を製造する方法を示す断面図である。

【図8B】本開示の一部の実施例による、複数のウエハ・キャリア・ボンディングを用いて、前面ピラー構造及びダイの裏面上の受動デバイスを含むトランジスタ構造を製造する方法を示す断面図である。

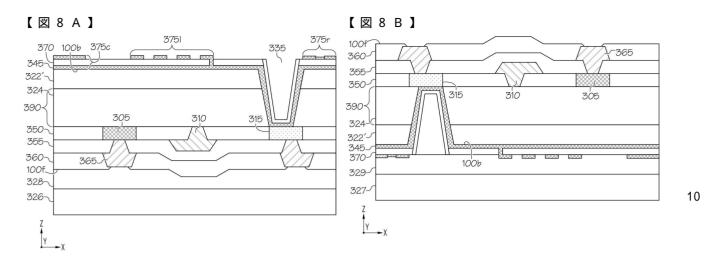

【図8C】本開示の一部の実施例による、複数のウエハ・キャリア・ボンディングを用いて、前面ピラー構造及びダイの裏面上の受動デバイスを含むトランジスタ構造を製造する方法を示す断面図である。

【図8D】本開示の一部の実施例による、複数のウエハ・キャリア・ボンディングを用いて、前面ピラー構造及びダイの裏面上の受動デバイスを含むトランジスタ構造を製造する方法を示す断面図である。

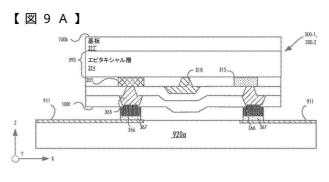

【図9A】本開示の一部の実施例による、前面ピラー構造を有するトランジスタ構造を含むRFトランジスタ増幅器ダイの基板取り付けの例を示す断面図である。

【図9B】本開示の一部の実施例による、前面ピラー構造を有するトランジスタ構造を含むRFトランジスタ増幅器ダイの基板取り付けの例を示す断面図である。

【図9C】本開示の一部の実施例による、前面ピラー構造を有するトランジスタ構造を含むRFトランジスタ増幅器ダイの基板取り付けの例を示す断面図である。

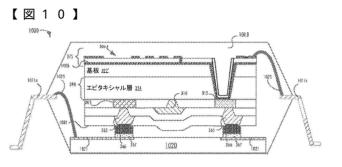

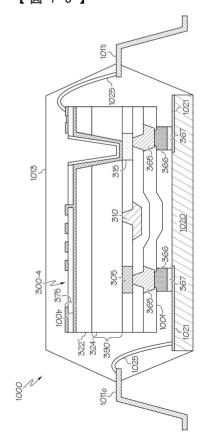

【図 1 0 】本開示の一部の実施例による、トランジスタ構造を含む R F トランジスタ増幅器ダイ又はデバイスを含むデバイス・パッケージの例を示す断面図である。

【図11】本開示の一部の実施例による、トランジスタ構造を含むRFトランジスタ増幅器ダイ又はデバイスを含むデバイス・パッケージの例を示す断面図である。

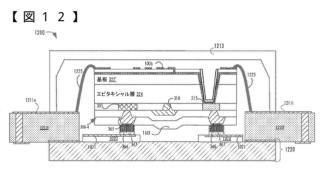

【図 1 2 】本開示の一部の実施例による、トランジスタ構造を含む R F トランジスタ増幅器ダイ又はデバイスを含むデバイス・パッケージの例を示す断面図である。

【発明を実施するための形態】

[0045]

本開示の実施例は、集積回路デバイス・パッケージのワイヤ・ボンドを低減又は排除することができるデバイス及び製造方法を対象とする。パッケージのサイズ及び組立てに制限を課すだけでなく、ワイヤ・ボンドは、特に、より高周波のRF用途において、整合回路(入力/出力インピーダンス整合及び/又は高調波終端回路を含む)の有効性を低減又は無効にする可能性がある望ましくない直列インダクタンスを導入することがある。

[ 0 0 4 6 ]

そのため、本開示の一部の実施例は、RFトランジスタ増幅器ダイ又はデバイスの前面若しくは表面の導電性ピラー(本明細書では前面ピラー構造又は前面ピラーとも呼ばれる)などの電気的接続構造を使用する集積デバイス及び製造方法を提供する。本明細書で使用される場合、ダイ又はデバイスの「前面」若しくは「表面」は、デバイスの半導体層構造内の能動トランジスタ・セルに隣接していてもよく、一方、ダイ又はデバイスの「裏面」若しくは「背面」は、前面の反対側であってもよい(一部の実施例では、半導体層構造が形成されるか、又は他の方法で提供される基板を含んでもよい)。前面ピラーは、ウエハ上に集積することができる導電性構造(金属めっきされた構造又は他の金属構造を含む)であってもよく、前面ピラーのそれぞれの位置又は配置に関する設計の柔軟性で幾何学

10

20

30

的形状に対する制御を改善することができる。前面ピラーは、外部接続(例えば、「オフチップ」接続とも呼ばれる、入力接続、出力接続、及び/又は接地接続)用の、デバイスの1つ又は複数の端子(例えば、トランジスタ・ダイのソース端子、ドレイン端子、及び/又はゲート端子)をプリント回路板(PCB:printed circuit board)、再配線層(RDL:redistribution layer)構造、及び/又は熱強化パッケージ(例えば、TEPAC又はT3PACパッケージ)を含む他のパッケージ基板に接続し、ワイヤ・ボンドを低減又は排除することができる。

### [0047]

本開示のさらなる実施例は、ダイの裏面を用いて、受動電子部品又はデバイス(例えば、ディスクリート・コンデンサ、インダクタ、及び抵抗器)を集積し、例えば、整合回路への(例えば、ワイヤ・ボンドを使用する)オフチップ接続に関連付けられた複雑さを低減又は排除する集積デバイス及び製造方法を提供する。ダイの裏面にパターニングされた金属層及び絶縁体を追加することで、より高い集積レベルが可能になり、多種多様な受動部品を設計するのに必要な構成要素を提供することができる。一部の実施例では、ダイの裏面に必要な構成要素を提供することができる。一部の実施例では、受動デバイスは、ダイの前面のパイスに接続することができる。一部の実施例では、受動デバイスは、ダイの前面とプイスに接続することができる。したがって、本明細書に記載される実施例は、回路精度を改善し、パッケージ・サイズを低減することができる。

### [0048]

添付の図面を参照して以下に詳細に説明される本開示の実施例によるデバイス及び製造方法において前面ピラーを集積する際に、いくつかの設計上のトレードオフが考慮された。例えば、3つのFET端子(例えば、ソース / 接地、ゲート、及びドレイン)はすべて、一部の実施例では、ダイの同じ側(例えば、前面)に配線されることがあるが、そのような配置は、一部の実施例では、最適ではない場合がある。裏面接地面を必要とすることがあるRF IC設計では、(例えば、FETソース端子への接続のために)導電性基板貫通ビアが使用されてもよい。一部の実施例では、前面ピラー接続は、裏面ビア接続の必要性を排除することができる。一部の実施例では、裏面ビア接続は、必要とされない場合があるが、個片化プロセスは、基板の厚さに制限を課すことがある。

### [0049]

図1は、本開示の実施例による半導体ダイ100の一部の概略平面図である。ダイ100は、パワー・トランジスタ・デバイス、例えば、RF電力増幅器のトランジスタ・セルを含むことができる。図2は、図1の線II-II'に沿って取られたデバイス又はダイ100の単位セル・トランジスタ構造(本明細書ではトランジスタ構造又はトランジスタ・セルとも呼ばれる)300の概略断面図である。

# [0050]

図1及び図2に示すように、III族窒化物半導体の高電子移動度トランジスタ(HEMT)又はMOSFET用の半導体構造などの半導体層構造390が炭化ケイ素基板又はサファイア基板などの基板322上に形成されてもよい。基板322は、例えば、4Hポリタイプの炭化ケイ素であってもよい半絶縁性炭化ケイ素基板であってもよい。他の炭化ケイ素候補のポリタイプとしては、3C、6H、及び15Rポリタイプが挙げられる。基板322は、Cree社から入手可能な高純度半絶縁性(HPSI:High Purity Semi-Insulating)基板であってもよい。「半絶縁性」という用語は、絶対的な意味ではなく、本明細書では記述的に使用される。

# [0051]

本明細書で使用される場合、「III族窒化物」という用語は、窒素と周期表のIII族の元素、通常はアルミニウム(Al)、ガリウム(Ga)、及び/又はインジウム(In)との間で形成される半導体化合物を指す。この用語は、例えば、AlGaN及びAlInGaNなどの三元及び四元(又はより高次の)化合物も指す。当業者によってよく理解されているように、III族元素は、窒素と結合して、二元(例えば、GaN)、三元

10

20

30

40

20

30

40

50

(例えば、AlgaN、AlInN)、及び四元(例えば、AlInGaN)化合物を形成することができる。これらの化合物は、1モルの窒素が合計1モルのIII族元素と結合した実験式を有する。

### [0052]

本開示の一部の実施例では、基板322の炭化ケイ素バルク結晶は、室温で約1×10 ・ c m以上の抵抗率を有することができる。本開示の一部の実施例において使用されることがあるSiC基板の例は、例えば、本開示の譲受人であるDurham,N.C.のCree社によって製造されており、このような基板を製造するための方法は、例えば、米国特許第Re.34,861号、米国特許第4,946,547号、米国特許第5,200,022号、及び米国特許第6,218,680号に記載されており、これらの開示は、その全体が参照により本明細書に組み込まれる。基板322として炭化ケイ素が採用されてもよいが、本開示の実施例は、サファイア(A1203)、窒化アルミニウム(A1N)、窒化アルミニウム・ガリウム(A1GaN)、窒化ガリウム(GaN)、シリコン(Si)、GaAs、LGO、酸化亜鉛(ZnO)、LAO、リン化インジウム(InP)などの、任意の適切な基板を基板322に利用することができることを理解されたい。

# [ 0 0 5 3 ]

基板 3 2 2 は、炭化ケイ素ウエハであってもよく、デバイス 1 0 0 は、少なくとも部分的に、ウエハ・レベル処理を介して形成されてもよく、次いで、ウエハは、複数の個々の又は単位セル・トランジスタ(それぞれ、 3 0 0 又は 3 0 0 - n として本明細書において指定され、n は整数である)を含むデバイス 1 0 0 を提供するようにダイシングされてもよい。一部の実施例では、基板 3 2 2 の厚さ(例えば、図 2 の垂直 2 方向の)は、 1 0 0 μ m 超、 2 0 0 μ m 超、 又は 4 0 0 μ m 超であってもよい。

### [0054]

一部の実施例では、例えば、図 3 A ~ 図 3 D、図 5 A ~ 図 5 F、及び図 7 A ~ 図 7 G を 参照して以下で説明するように、トランジスタ構造 3 0 0 は、薄化された基板 3 2 2 'を含むことができる。一部の実施例では、基板 3 2 2 'の厚さ(例えば、図 2 の垂直 Z 方向の)は、1 0 0  $\mu$  m以下であってもよい。一部の実施例では、基板 3 2 2 'の厚さは、 7 5  $\mu$  m以下であってもよい。一部の実施例では、基板 3 2 2 'の厚さは、 5 0  $\mu$  m以下であってもよい。

# [0055]

半導体層構造390は、基板322の表面上(又は本明細書でさらに説明される任意選択の層上)に形成される。図示する例では、半導体層構造390は、エピタキシャル成長によって形成され、したがって、1つ又は複数のエピタキシャル層324を含む。III 族窒化物のエピタキシャル成長のための技術は、例えば、米国特許第5,210,051 号、米国特許第5,393,993号、及び米国特許第5,523,589号に記載されており、これらの開示も、その全体が参照により本明細書に組み込まれる。

## [0056]

炭化ケイ素は、III族窒化物デバイス用の一般的な基板材料である場合があるサファイア(Al2〇3)よりも、(半導体層構造390に採用することができる)III族窒化物にはるかに近い結晶格子整合を有する。格子整合が近いことで、サファイア上で一般的に入手可能なものよりも高品質のIII族窒化物膜を得ることができる。炭化ケイ素は、熱伝導率も比較的高く、したがって、炭化ケイ素上に形成されたIII族窒化物デバイスの総出力電力は、サファイア及び/又はシリコン上に形成された同様のデバイスほど、基板の熱放散によって制限されない可能性がある。また、半絶縁性炭化ケイ素基板は、デバイスの絶縁及び寄生容量の低減を実現することができる。

### [0057]

半導体層構造390は、例示の目的で1つ又は複数のエピタキシャル層324を参照して示されているが、半導体層構造390は、基板322上の、或いは基板322と1つ若しくは複数のエピタキシャル層324との間のバッファ層及び/又は核形成層、並びに/

20

30

40

50

或いはエピタキシャル層324の上面324A上のキャップ層などの、追加の層/構造/要素を含むことができる。例えば、A1Nバッファ層を基板322の上面322Aに形成して、炭化ケイ素基板322とトランジスタ構造300の残りの層との間に適切な結晶構造遷移を設けることができる。さらに、歪み平衡遷移層もまた、及び/又は代替として、例えば、同一出願人による米国特許第7,030,428号に記載されるように設けられてもよく、その開示は、本明細書に完全に記載されているかのように、参照により本明細書に組み込まれる。任意選択のバッファ層/核形成層/遷移層は、有機金属化学気相成長(MOCVD:metal.organic.chemical.vapor.deposition.)、分子線エピタキシ(MBE:molecular.beam.epitaxy)、及び/又はハイライド気相エピタキシ(HVPE:hydride.vapor phase.epitaxy)によって堆積させることができる。

[0058]

依然として図1及び図2を参照すると、ダイ100の前面100fにおいて、ソース・コンタクト315及びドレイン・コンタクト305がエピタキシャル層324の表面324Aに形成されてもよく、互いに横方向に離間されてもよい。単位セル・トランジスタ300のソース領域は、ソース・コンタクト315の直下にある半導体層構造390の部分であり、単位セル・トランジスタ300のドレイン領域は、ドレイン・コンタクト305の直下にある半導体層構造390の部分である。ゲート・コンタクト310は、ソース・コンタクト315とドレイン・コンタクト305との間のエピタキシャル層324上に形成されてもよい。ゲート・コンタクト310の材料は、エピタキシャル層324の組成に基づいて選択されてもよく、一部の実施例では、ショットキー・コンタクトであってもよい。III族室化物ベースの半導体材料にショットキー・コンタクトを行うことができるいくつかの材料、例えば、ニッケル(Ni)、白金(Pt)、ニッケル・シリサイド(NiSix)、銅(Cu)、パラジウム(Pd)、クロム(Cr)、タングステン(W)及び/又は窒化タングステン・シリコン(WSiN)などが使用されてもよい。

[0059]

ソース・コンタクト315及び/又はドレイン・コンタクト305は、III族窒化物ベースの半導体材料に対してオーミック・コンタクトを形成することができる金属を含むことができる。適切な金属としては、Ti、W、チタン・タングステン(TiWN)、ケイ化タングステン(WSi)、レニウム(Re)、ニオブ(Nb)、Ni、金(Au)、アルミニウム(A1)、タル(TiN)、モリブデン(Mo)、NiSi、ケイ化チタン(TiSi)、窒化チタン(TiN)、OSiN、Ptなどの高融点金属を挙げることができる。したがャセース・コンタクト315及び/又はドレイン・コンタクト305は、エピタキシェル層324(例えば、高電子移動度トランジスタ(HEMT)デバイスのバリア層)と直接接するオーミック・コンタクト305は、例えば、同一出願人によるにより下第8,563,372号及び米国特許第9,214,352号に記載されるよく、その開示は、その全体が参照により本明細書に組み込まれる。

[0060]

一部の実施例では、トランジスタ・セル300は、高電子移動度トランジスタ(HEMT)構造であってもよく、エピタキシャル層構造324は、基板322の表面322Aに形成されたチャネル層と、チャネル層の表面に形成されたバリア層とを含んでもよい。チャネル層は、バリア層のバンドギャップよりも小さいバンドギャップを有することができ、チャネル層は、バリア層よりも大きい電子親和力を有することもできる。チャネル層及びバリア層は、III族窒化物ベースの材料を含むことができる。従来の高電子移動度トランジスタ(HEMT)デバイスに関して上述したように、二次元電子ガス(2DEG)層は、チャネル層とバリア層との接合部においてチャネル層内に誘起される。二次元電子ガス(2DEG)層は、ソース・コンタクト315及びドレイン・コンタクト305の下

20

40

50

にそれぞれあるデバイスのソース領域とドレイン領域との間の導通を可能にする高導電性層として機能する。基板、チャネル層、バリア層、及び他の層を含む高電子移動度トランジスタ(HEMT)構造は、一例として、米国特許第5,192,987号、米国特許第5,296,395号、米国特許第6,316,793号、米国特許第6,548,333号、米国特許第7,544,963号、米国特許第7,548,112号、米国特許第7,592,211号、米国特許第7,615,774号、米国特許第7,548,112号、及び米国特許第7,709,269号に記載されており、これらの開示は、その全体が参照により本明細書に組み込まれる。

### [0061]

当業者によって理解されるように、トランジスタ・セル300(例えば、高電子移動度トランジスタ(HEMT)、MOSFET、横方向拡散金属酸化膜半導体(LDMOS)など)は、ゲート・コンタクト310の制御下でソース・コンタクト315とドレイン・コンタクト315、ドレイン・コンタクト315、ドレイン・コンタクト315、ドレイン・コンタクト315、ドレイン・コンタクト315、ドレイン・コンタクト315、ドレイン・コンタクト315、ドレイン・コンタクト315、ドレイン・コンタクト315、ドレイン・コンタクト315、ボート・コンタクト310が、隣接するドレイン・コンタクト305とソース・コンタクト315を共有する。図1に示すように、デバイス100は、ソース・コンタクト315を共有する院にするために、ソース・コンタクト315、ドレイン・コンタクト315を共有するに、ソース・コンタクト315、ドレイン・コンタクト315を共有するに、ソース・コンタクト315、デバイス100は、図示されていない追加のソース・コンタクト315、ドレイン・コンタクト310を含む追加の構造を有してもよいことが理解されるであろう。

### [0062]

典型的には、数百、又はより一般的には数千の単位セル300などの単位セルを半導体 基 板 上 に 形 成 し 、 電 気 的 に 並 列 に 接 続 し て 、 R F ト ラ ン ジ ス タ 増 幅 器 ダ イ 又 は デ バ イ ス 1 00を提供することができる。一部の実施例では、ダイ100は、デバイス端子又は電極 (例えば、入力端子、出力端子、及び接地端子)に並列に接続されてもよい複数のトラン ジスタ・セル300を含むことができる。例えば、ゲート・コンタクト310、ドレイン ・コンタクト 3 0 5 、及びソース・コンタクト 3 1 5 のそれぞれは、第 1 の方向(例えば Y方向)に延在してゲート「フィンガ」、ドレイン「フィンガ」、及び/又はソース「 フィンガ」を画定することができ、これらのフィンガは、半導体層構造390の上面32 4A上の1つ又は複数のそれぞれのバスによって(例えば、図1ではファントムで示すゲ - ト・バス310b及びドレイン・バス305bによって)接続されてもよい。ゲート・ フィンガ310、ドレイン・フィンガ305、及びソース・フィンガ315(及び接続バ ス)は、頂部側又は前面メタライゼーション構造によって画定されるように、デバイス1 0 0 のゲート接続電極、ドレイン接続電極、及びソース接続電極の一部をそれぞれ画定す ることができる。前面メタライゼーション構造の様々な導電性要素を互いに絶縁する誘電 体層は、図面を簡略化するために図1には示されていない。ゲート・フィンガ310は共 通のゲート・バス310bに電気的に接続され、ドレイン・フィンガ305は共通のドレ イン・バス305bに電気的に接続され、ソース・フィンガ315は(例えば、本明細書 に記載されるそれぞれのビア開口部335及び裏面金属層345を介して)互いに電気的 に接続されているため、単位セル・トランジスタ300はすべて互いに並列に電気的に接 続されていることが分かる。

### [0063]

RFトランジスタ増幅器ダイ又はデバイス100の端子のうちの1つ(例えば、ソース・コンタクト315に接続されたソース端子)は、例えば電気的接地などの基準信号に結合されるように構成されてもよい。一部の実施例では、導電性基板貫通ビア接続又は構造(例えば、本明細書に記載されるような基板貫通ビア開口部335に形成された裏面ビア

20

30

40

50

3 4 6 ) は、基板 3 2 2 又は 3 2 2 ′ 及びエピタキシャル層 3 2 4 を貫いて延在して、ソース・コンタクト 3 1 5 を接地に結合することができる。他の実施例では、RFトランジスタ増幅器ダイ又はデバイス 1 0 0 の端子のうちの 1 つ ( 例えば、ソース端子 ) への接地接続は、活性領域の外側に、例えば、ダイ 1 0 0 の周辺領域に設けられてもよい。一部の実施例では、ダイ 1 0 0 の裏面 1 0 0 b のバックメタル層 3 4 5 は、例えば、接地に近接していることが望まれることがある用途において、裏面接地面を提供することができる。

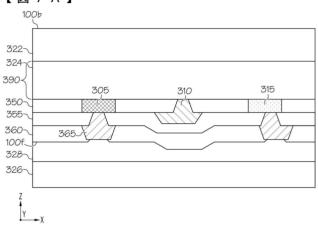

図 2 に示すように、トランジスタ構造 3 0 0 は、前面 1 0 0 f に隣接する、 3 5 0 、 3 5 5 、 及 び 3 6 0 と し て 示 す 1 つ 又 は 複 数 の 誘 電 体 層 又 は 絶 縁 層 を さ ら に 含 む こ と が で き る。 第 1 の 絶 縁 層 3 5 0 は、 半 導 体 層 構 造 3 9 0 の 上 面 ( 例 え ば 、 エ ピ タ キ シ ャ ル 層 3 2 4 の上面 3 2 4 A ) に直接接触してもよい。第 1 の絶縁層 3 5 0 上には第 2 の絶縁層 3 5 5 が形成されてもよく、 第 2 の 絶 縁 層 3 5 5 上には 第 3 絶 縁 層 3 6 0 が形成されてもよい 。一部の実施例では、3つよりも少ない又は多い絶縁層が含まれてもよいことも理解され る で あ ろ う 。 絶 縁 層 3 5 0 、 3 5 5 、 及 び / 又 は 3 6 0 の う ち の 1 つ 又 は 複 数 は 、 ト ラ ン ジスタ構造300のためのパッシベーション層として機能することができる。絶縁層35 0、355、360は、窒化ケイ素(Si<sub>x</sub>N<sub>y</sub>)、窒化アルミニウム(A1N)、二酸 化ケイ素 ( S i O 2 ) 、酸窒化ケイ素、並びに / 或いは他の適切な保護材料、例えば、酸 化マグネシウム、酸化スカンジウム、酸化アルミニウム及び / 又は酸窒化アルミニウムな どの誘電体材料であってもよい。より一般的には、絶縁層350、355、360は、単 一の層であってもよく、又は均一及び/若しくは不均一な組成の複数の層を含んでもよく 、並びに/又は(例えば、ソース・コンタクト315及び/若しくはドレイン・コンタク ト305を提供する)オーミック・コンタクトのその後のアニール中に下にあるエピタキ シャル層324を保護するように十分に厚くてもよい。

[0065]

[0064]

ソース・コンタクト315、ドレイン・コンタクト305、及びゲート・コンタクト310は、ダイ100の前面100 f に隣接する第1の絶縁層350内に形成されてもよい。一部の実施例では、ゲート・コンタクト310の少なくとも一部は、第1の絶縁層350の表面上にあってもよい。一部の実施例では、ゲート・コンタクト310は、T字形ゲート及び/又はガンマ・ゲートとして形成されてもよく、その形成については、米国特許第8,049,252号、米国特許第7,045,404号、及び米国特許第8,120,064号に一例として論じられており、これらの開示は、その全体が参照により本明細書に組み込まれる。第2の絶縁層355は、第1の絶縁層350上と、ドレイン・コンタクト305、ゲート・コンタクト310、及びソース・コンタクト315の部分上と、に形成されてもよい。

[0066]

コンタクト3 0 5 、 3 1 0 、 3 1 5 のうちの1 つ又は複数、例えば、ソース・コンタクト3 1 5 及びドレイン・コンタクト3 0 5 に接触するように、それぞれの金属コンタクト3 6 5 が第 2 の絶縁層 3 5 5 の開口部を通って延在して形成されてもよい。例えば、第 2 の絶縁層 3 5 5 は、金属コンタクト 3 6 5 を配置するために、ソース・コンタクト 3 1 5 及び / 又はドレイン・コンタクト 3 0 5 を露出させる窓を形成するようにパターニングされてもよい。窓は、ソース・コンタクト 3 1 5 及び / 又はドレイン・コンタクト 3 0 5 に対して、パターニングされたマスクと低損傷のエッチングを利用してエッチングされてもよい。ソース・コンタクト 3 1 5 及び / 又はドレイン・コンタクト 3 0 5 の露出部分に導電性金属を形成して、金属コンタクト 3 6 5 を形成することができる。

[0067]

金属コンタクト365は、ダイ100の前面100fにおいてトランジスタ・セル300のコンタクト305、310、315のそれぞれと直接接触してもよい。図1及び図2の例では、金属コンタクト365は、ドレイン・コンタクト305及びソース・コンタクト315上に設けられている。しかしながら、他の実施例では、金属コンタクト365は、ダイ100の前面100fの3つのFET端子(ソース、ゲート、及びドレイン)上す

20

30

40

50

べてに設けられてもよい。また、金属コンタクト365は、例えば、外部入力/出力接続を提供するために(例えば、ゲート310に入力信号を提供し、ドレイン305から出力信号を提供するために)、ゲート・バス310b及びドレイン・バス305bへの接続を提供することができる。特に、一部の実施例では、金属コンタクト365は、ゲート・バス310b及びドレイン・バス305bと、入力/出力接続を提供するそれぞれのワイヤ・ボンド用のそれぞれのランディング/コンタクト・パッドとの間の接続を提供することができる。

# [0068]

金属コンタクト365は、例えば、銅、コバルト、金、及び/又は複合金属を含む、金属若しくは他の高導電性材料を含んでもよい。説明を容易にするために、図1では、第2の絶縁層355、第3の絶縁層360、及び金属コンタクト365は示されていない。(絶縁層350及び/又は355と同様の又は異なる組成の)第3の絶縁層360は、最終パッシベーション層として金属コンタクト365上に形成されてもよく、この最終パッシベーション層は、電気的接続のために、例えば、1つ又は複数の外部デバイスへの「オフチップ」入力及び/又は出力接続のために、並びに/或いは接地接続のために金属コンタクト365を露出させる開口部325を画定するようにパターニングされてもよい。金属コンタクト365は、したがって、入力(例えば、ゲート)、出力(例えば、ドレインタクト365は、したがって、入力(例えば、ゲート)、出力(例えば、ドレインができ、これらは、ダイ100の1つ又は複数のトランジスタ構造300の対応する端子(例えば、高電子移動度トランジスタ(HEMT)又は横方向拡散金属酸化膜半導体(LDMOS)トランジスタなどのFETのゲート端子310、ドレイン端子305、及びソース端子315)に直接又は間接的に接続されてもよい。

## [0069]

本開示の実施例による前面ピラー、裏面ビア、及び/又は裏面受動デバイスを製造するためのさらなる操作が、図2のトランジスタ構造300を参照して本明細書で説明される

## [0070]

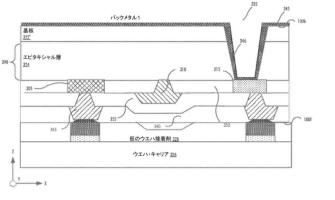

図3 A ~ 図3 D は、本開示の一部の実施例による前面ピラー構造を含むトランジスタ構造を製造する方法を示す断面図である。特に、図3 A ~ 図3 D の操作は、デバイスの裏面への導電性基板貫通ビア接続のないトランジスタ・セル3 0 0 を含むデバイス1 0 0 を形成するためのプロセス・シーケンスを示し、ダイ個片化のためにバルク裏面研削プロセスを使用して基板322の厚さを低減している。

### [0071]

ここで図3Aを参照すると、図2のオフチップ接続用の金属コンタクト365を露出さ せた後、ダイ 1 0 0 の前面 1 0 0 f の金属コンタクト 3 6 5 上にそれぞれの導電性接続部 3 6 6 ( 本明細書では前面接続部又は前面ピラーと呼ばれる)が形成される。前面ピラー 366は、平面図において(例えば、金属コンタクト365を露出させる開口部325と 同様の又はそれに対応する)楕円形又は円形の形状を有してもよい。前面ピラー366は 、一部の実施例では、比較的厚い導電性めっき構造であってもよい。例えば、前面ピラー 3 6 6 は、 C u めっき 構造又は他の金属めっき構造であってもよい。 したがって、前面ピ ラー 3 6 6 は、デバイス 1 0 0 の 1 つ又は複数の端子 ( 例えば、入力、出力、接地 ) と 1 つ 又 は 複 数 の 外 部 デ バ イ ス と の 間 の 電 気 的 接 続 を 、 例 え ば 「 フ リ ッ プ チ ッ プ 」 ( デ バ イ ス 1 0 0 が、デバイス 1 0 0 の前面 1 0 0 f に隣接するピラー 3 6 6 によって基板又は基板 上のデバイスに取り付けられ、電気的に接続される)として、及び/又は積層マルチチッ プ・パッケージにおいて提供することができる。図3Aに示すように、電気的接続及び/ 又は取り付けのために、はんだ層367が前面ピラー366上に設けられてもよい。加え て、パッケージの集積度に応じて、前面ピラー366は、チップ間又はチップと基板間の なんらかの分離を提供し、デバイス100の前面100fからの熱放散を増加させ、機械 的強度を増加させ、及び/又は(特に「フリップチップ」パッケージにおいて)ダイ10 0のエッジ若しくは周辺部から離れた接続パッド若しくはピラーの配置を可能にすること

20

30

40

50

によって設計の柔軟性を向上させることができる。

### [0072]

図3 Bに示すように、前面100fから突出する前面ピラー366を含むデバイス100の前面100fが「裏返されて」、例えば、仮のウエハ接着剤328によって、ウエハ・キャリア326に(前面を下にして)取り付けられる。ウエハ・キャリア326は、剛性を高め、したがって、後続の製造プロセス中に前面ピラー366を支持及び保護するように構成された任意の基板又は構造であってもよい。

### [0073]

特に、デバイス又はダイ100は、共通のウエハ上に形成された複数のダイのうちの1つであってもよく、したがって、デバイス100の製造は、例えば、ダイシング又はソーイング・プロセスによる、ウエハ上の他のダイからの個片化を含むことができる。基板322の材料に応じて、基板322の厚さを低減することによって個片化を容易にすることができる。例えば、一部の実施例では、基板322は、厚さが増加するにつれて個片化をより困難にし得る硬度を有する材料(炭化ケイ素など)である場合がある。

### [0074]

したがって、図3Cに示すように、基板322の厚さは、個片化のために低減される。一部の実施例では、基板322の厚さは、インフィード又はクリープ・フィード・グラインダなどのグラインダを使用して低減されてもよい。他の実施例では、基板322の厚さは、研削の有無にかかわらず、ラッピング、化学的若しくは反応性イオン・エッチング、又はこれらの手法の組合せを用いて低減されてもよい。さらに他の実施例では、エッチングを使用して基板322の裏面を処理し、薄化操作から生じる可能性がある基板322への損傷を低減することができる。ウエハを薄くする方法は、例えば、本発明の譲受人に譲渡された米国特許第7,291,529号、米国特許第7,932,111号、米国特許第7,259,402号、及び米国特許第8,513,686号に記載されており、これらの開示は、その全体が参照により本明細書に組み込まれる。一部の実施例では、基板322は、約40μm~約100μmの厚さに薄くされてもよい。他の実施例では、基板322は、約50μm~約75μmの厚さに薄くされる。

# [ 0 0 7 5 ]

ウエハ・キャリア326及び/又は仮接着剤328によるウエハ・キャリアへの取り付けは、デバイス100の前面ピラー366を支持し、基板322の薄化によって引き起こされる応力から保護する。それによって、基板322′は、裏面研削又は他の薄化プロセスにより、低減されるが、実質的に均一な厚さを有する。図3Dに示すように、基板322′の薄化後、トランジスタ構造300・1を含むデバイス100は、ウエハ・キャリア326から取り外されるか、又は他の方法で分離され、後続のプロセスにおける個片化及び(例えば、図10・12に示すようなパッケージへの)取り付けの準備が整う。

# [0076]

図4A~図4Cは、本開示の一部の実施例による、ダイ個片化のための前面ピラー構造及びトレンチを含むトランジスタ構造の製造方法を示す断面図である。特に、図4A~図4Cの操作は、デバイスの裏面への導電性基板貫通ビア接続のないトランジスタ・セル30を含むデバイス100を形成するためのプロセス・シーケンスを示し、ダイ個片化のために前面パターニングを使用して、特定の領域において基板322の厚さを選択的に低減している。

# [0077]

ここで図4Aを参照すると、図2のオフチップ接続用の金属コンタクト365を露出させた後、デバイス100の前面100fの領域に前面トレンチ(又は「ストリート」)373が選択的に形成されている。トレンチ373は、エピタキシャル層324を貫いて基板322内に部分的に延在し、その結果、トレンチ373を含む基板322の部分は、(トレンチ373の底面又は「フロア」と基板322の裏面との間に画定される)厚さが低減されている。基板322の低減された厚さは、ピラー形成中の安定性を提供すると同時に、その後の個片化を可能にするのに十分であってもよい。例えば、基板322は、約5

20

30

40

50

$00\mu m \sim 1000\mu m$  の厚さを有することができるが、トレンチ 373 は、基板 322 内に延在して、トレンチ 373 のフロアにおいて、約 $40\mu m \sim 200\mu m$  の残りの厚さ、例えば、約 $60\mu m \sim 150\mu m$  の厚さを提供することができる。トレンチ 373 は、選択的パターニング・プロセスによって、例えば、デバイス 100 の前面 100 f の露出した金属コンタクト 365 上に 10 又は複数のマスク・パターンを形成し、10 又は複数の選択的エッチング・プロセスを行って、マスク・パターンによって露出したエピタキシャル層 324 の部分(及び下にある基板 322 の対応する部分)を除去することによって形成されてもよい。マスク・パターンは、その後除去されてもよい。

### [0078]

図4Bに示すように、デバイス100の前面100fにトレンチ373を形成した後、図3Aを参照して上述したものと同様又は同一のやり方で、それぞれの導電性前面ピラー366及びはんだ層367を前面100fの金属コンタクト365上に形成する。トレンチ373の形成後に前面ピラー366を形成することによって、トレンチ形成及び/又はマスク除去操作中の前面ピラー366への損傷を回避することができる。

# [0079]

図4Cに示すように、ダイ100は、トレンチ373によって画定された低減された厚 さを有する基板322の部分において、複数のダイを含むウエハから個片化される。例え ば、トレンチ373のフロアと基板322の裏面との間の基板322の厚さが低減されて いるために、基板322を薄くするための裏面研削プロセスを行うことなく、ダイシング 又はソーイング・プロセスを利用して、ダイ100をウエハから分離することができる。 個片化後、ダイ100の側壁又はエッジ100eは、裏面100bに隣接する第2の部分 3 7 2 ( 例 えば、 ダ イ シン グ 、 ソ ー イ ン グ 、 又 は 他 の 個 片 化 プ ロ セ ス を 受 け た 基 板 3 2 2 の部分)とは異なる表面特性(例えば、傾斜角及び/又は表面粗さ)を有する、前面10 0 f に 隣接する 第 1 の 部 分 3 7 1 ( 例 え ば 、 トレンチ 3 7 3 の 側 壁 を 画 定 した 基 板 3 2 2 の部分)を含むことができる。例えば、選択的エッチング・プロセスによって形成された 側 壁 又 は エ ッ ジ 1 0 0 e の 第 1 の 部 分 3 7 1 は 、 ダ イ シ ン グ 又 は ソ ー イ ン グ ・ プ ロ セ ス に よって形成された第2の部分372とは異なる傾斜及び/又は異なる表面粗さを有するこ とができる。ダイシング・ソーの幅は、トレンチ373の幅よりも狭くてもよく、それに よって、 基板 3 2 2 のエッジ 1 0 0 e において第 1 の部分 3 7 1 と第 2 の部分 3 7 2 との 間に突出したリップ374を画定する。したがって、高硬度を有する材料(SiCなど) を含むウエハ又は基板322上に形成された場合であっても、基板薄化操作を行うことな く、デバイス100を個片化することができる。それによって、結果として得られるトラ ンジスタ構造300-2は、(トランジスタ構造300-1の基板322'に対して)厚 さを増加させた基板322を含み、これは、例えば、その後の処理において、堅牢性を向 上させることができる。一部の実施例では、個片化されたダイ100は、約50~約20 0 μ m 、 例えば、 約 7 5 ~ 約 1 7 5 μ m 、 又は約 1 0 0 ~ 約 1 5 0 μ m の厚さを有する基 板322を含むことができる。一部の実施例では、個片化されたダイ100は、約200 μmよりも大きい、例えば、約200~500μm、又は約500~約800μmの厚さ を有する基板322を含むことができる。

# [0080]

図3 A ~ 図3 D及び図4 A ~ 図4 Cの実施例では、トランジスタ構造3 0 0 - 1 及び3 0 0 - 2 は、ゲート・コンタクト3 1 0、ソース・コンタクト3 1 5、又はドレイン・コンタクト3 0 5 への導電性基板貫通ビア接続がない。むしろ、図9 A に示すように、導電性接続部 / 前面ピラー3 6 6 は、前面ピラー3 6 6 が、電気信号配線のために、例えば、はんだ層3 6 7 によって、対応する導電性トレース9 1 1 に物理的に取り付けられ、且つ電気的に接続されるように、例えば、ダイ1 0 0 を基板9 2 0 a (例えば、プリント回路板(PCB)又は再配線層(RDL))上に「裏返す」ことによってオフチップ電気的接続を提供するために使用されてもよい。再配線層(RDL)構造とは、導電層パターン及び/又は導電ビア構造を有する基板又は積層板を指す。再配線層(RDL)構造は、半導体処理技術を使用して、例えば、ベース材料上に導電層及び絶縁層並びに/又はパターン

20

30

40

50

を堆積させ、再配線層(RDL)構造を通して信号を伝送するためのビア及び銅配線パターンを構造内に形成することによって製造されてもよい。それによって、一部の実施例では、(特により高周波のRF用途において、インピーダンス整合ネットワーク及び/又は高調波終端回路の有効性を低減又は無効にする可能性がある直列インダクタンスを導入することがある)ワイヤ・ボンドの必要性及び/又は使用を低減若しくは排除することができる。

### [0081]

本明細書に記載されるさらなる実施例は、ゲート・コンタクト310、ソース・コンタクト315、及び/又はドレイン・コンタクト305への導電性基板貫通ビア接続(又は「導電性ビア」)を提供するデバイス及び製造方法を対象とする。例えば、一部の実施例は、ソース・コンタクト315を電気的接地に接続するように構成された裏面ビアを含むことができ、裏面接地面を提供するためのバックメタル層をさらに含むことができる。製造可能性は、裏面薄化後のウエハ処理量によって、及び/又は前面ピラー構造の幾何学的形状によって制限されることがあるが、本明細書に記載されるさらなる実施例は、これら及び/又は他の制限に対処することができる。

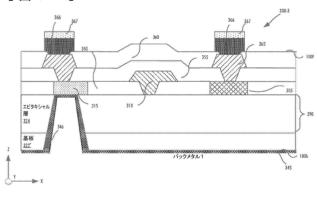

### [0082]

図 5 A ~ 図 5 F は、本開示の一部の実施例による、前面ピラー構造と、デバイスの裏面への導電性基板貫通ビア接続とを含むトランジスタ構造を製造する方法を示す断面図である。特に、ウエハ接合操作が前面ピラーの幾何学的形状によって制限されることがあるため、図 5 A ~ 図 5 F の操作は、わずか 1 つのウエハ・キャリア・ボンディング・ステップ又はプロセスを使用してトランジスタ・セル 3 0 0 を含むデバイス 1 0 0 を形成するためのプロセス・シーケンスを示す。

## [0083]

ここで図 5 A を参照すると、図 2 のオフチップ接続用の金属コンタクト 3 6 5 を露出させた後、図 3 A を参照して上述したものと同様又は同一のやり方で、ダイ 1 0 0 の前面 1 0 0 f の金属コンタクト 3 6 5 上に、それぞれの導電性前面ピラー 3 6 6 及びはんだ層 3 6 7 が形成される。図 5 B に示すように、デバイス 1 0 0 から突出する前面ピラー 3 6 6 を含むデバイス 1 0 0 の前面 1 0 0 f が、「裏返されて」、図 3 B を参照して上述したものと同様又は同一のやり方で、例えば、仮のウエハ接着剤 3 2 8 によってウエハ・キャリア 3 2 6 に(前面を下にして)取り付けられる。図 5 C において、基板 3 2 2 の厚すとは同的で(例えば、均一な裏面研削プロセスによって)低減される。ウエハ・キャリア 3 2 6 (及び/又は仮接着剤 3 2 8 によるウエハ・キャリアへの取り付け)は、デバイス 1 0 の前面ピラー 3 6 6 を支持し、基板 3 2 2 の薄化によって引き起こされる応力から保護する。それによって、基板 3 2 2 が、裏面研削又は他の薄化プロセスにより、低減されるが、実質的に均一な厚さを有する。

### [0084]

図5 Dに示すように、基板3 2 2 ′ 及びエピタキシャル層3 2 4 を貫いてビア開口部3 3 5 が形成され、コンタクト3 0 5、3 1 0、3 1 5 のうちの1 つ(ソース・コンタクト3 1 5 を参照して示されている)の一部を露出させる。特に、ビア開口部3 3 5 は、(基板3 2 2 ′ の裏面3 2 2 Bによって画定される)ダイ1 0 0 の裏面1 0 0 b から、基板3 2 2 ′ 及びエピタキシャル層3 2 4 を貫いてエピタキシャル層3 2 4 の表面3 2 4 A まで延在し、ソース・コンタクト3 1 5 の下側又は下面がビア開口部3 3 5 によって露出されるようにする。ビア開口部3 3 5 は、平面図で楕円形又は多角形の形状を有してもよい。一部の実施例では、ビア開口部3 3 5 の側壁は、基板3 2 2 ′ の裏面3 2 2 B に対して傾斜して及び / 又は傾いていてもよい。例えば、ビア開口部3 3 5 の寸法(例えば、直径又は面積)「A」は、基板3 2 2 ′ の裏面3 2 2 B の開口部では、ソース・コンタクト3 1 5 に隣接する部分よりも大きくてもよい。

### [0085]

ビア開口部335は、当業者によって理解されるように、マスキング及びエッチング技

20

30

40

50

術によって形成されてもよい。例えば、ビア開口部335は、湿式又は乾式エッチングに よって形成されてもよい。一部の実施例では、ソース・コンタクト315は、ビア開口部 335の形成中にエッチ・ストップ材料として機能することができる。一部の実施例では 、ビア開口部335は、ビア開口部335の側壁が基板322′の裏面322Bに対して 傾斜し、及び/又は傾くようにエッチングされてもよい。一部の実施例では、エッチング ・プロセスは、ビア開口部335の側壁が傾斜した又は斜めの形状を有するようにエッチ ン グ 化 学 物 質 及 び / 又 は 他 の プ ロ セ ス ・ パ ラ メ - タ が 調 整 さ れ た 異 方 性 エ ッ チ ン グ ・ プ ラ ットフォーム或いは処理条件に基づいてもよい。すなわち、ビア開口部335を画定する ために使用されるエッチング・プロセスは、トレンチ又は開口部335の側壁に十分な金 属被覆を可能にする所望の側壁傾斜を達成するために、異方性と等方性のエッチング態様 の組合せを含むことができる。エッチングにより、ビア開口部335の最大寸法Aは、基 板 3 2 2 'の裏面 3 2 2 B に隣接することができる。ビア開口部 3 3 5 の寸法 A はまた、 より厚い基板322のエッチングが結果としてより広いビア開口部335をもたらすため 、基板322~の厚さに関連することがある。したがって、基板322~の厚さを低減する ことにより、より小さい寸法Aを有するビア開口部335を形成することができ、これに より、デバイス100の全体的なサイズを低減し、インダクタンスを低減することができ る。すなわち、基板322′を薄くするための操作は、ビア形成に関して追加の利点を提 供することができる。

### [0086]

図5 Eに示すように、基板 3 2 2 7 の裏面 3 2 2 B上に、またビア開口部 3 3 5 の側壁及び底面上にも、金属層 3 4 5 を堆積させ又は他の方法で形成して、導電性基板貫通ビア接続又は裏面ビア 3 4 6 を画定する。バックメタル層 3 4 5 及び裏面ビア 3 4 6 は、ソース・コンタクト 3 1 5 に接触して電気信号を結合する導電層を含むことができる。例えば、バックメタル層 3 4 5 は、チタン、白金、及び / 又は金などの導電性金属を含むことができる。図 5 A ~ 図 5 F の例では、バックメタル層 3 4 5 は、ソース・コンタクト 3 1 5 を電気的接地に結合するように構成されてもよい。より一般的には、バックメタル層 3 4 5 、及びこれに結合された基準信号は、ビア開口部 3 3 5 を通って延在する導電性ビア 3 4 6 によって、デバイス・コンタクト 3 0 5 、 3 1 0 、 3 1 5 のうちの 1 つに電気的に接続されてもよい。

### [0087]

図5Fに示すように、バックメタル層345の形成後、トランジスタ構造300-3を含むデバイス100は、ウエハ・キャリア326から取り外されるか、又は他の方法で分離され、後続のプロセスにおける個片化及び(例えば、図10-12に示すようなパッケージへの)取り付けの準備が整う。そのため、前面ピラー366は、デバイス100の前面100fの1つ又は複数の端子(例えば、入力、出力、接地)への接続を提供することができ、バックメタル層345/裏面ビア346は、デバイス100の裏面100bの端子(例えば、入力、出力、接地)のうちの別の端子への接続を提供することができる。

一部の実施例では、図9Bに示すように、図5Fのトランジスタ構造300-3を含むダイ100は、前面ピラー366が、基板920bによって提供される、基板を通る電気信号配線用の対応する導電性トレース911に物理的に取り付けられ、且つ電気的に接続されるように、パッケージ基板920b(例えば、プリント回路板(PCB)又は再配線層(RDL)構造)上に裏返されてもよい。他の実施例では、図9Cに示すように、トランジスタ構造300-3を含むダイ100は、バックメタル層345が、基板を通る電によいで提供される熱伝導性ヒートシンクに物理的に取り付けられ、且つ電気的に接続されるように、パッケージ基板920c(例えば、熱強化パッケージの導電性フランジ)に取り付けられてもよい。例えば、SiC基板322,は良好な熱伝導体である可能性があるため、ダイ100は、裏面を下にして、ヒートシンク(図示するような導電性フランジ920cとして、又はヒートシンクを含むプリント回路板(PCB)若しくは再配線層(RD

20

30

40

50

L)構造として実装されてもよい)に取り付けられてもよい。図9Cに示す向きで、1つ又は複数の追加のダイ又は受動部品(集積受動デバイス(IPD)など)が、例えば、積層構成で、基板920cと反対側のピラー366に電気的に接続されてもよい。一部の実施例では、ダイ及び/又は受動部品は、例えば、2020年4月3日に出願された共同所有の米国仮特許出願第63/004,760号に記載されるように、ピラー366のうちの1つ又は複数(例えば、ドレイン接続ピラー366)をパッケージ・リードに電気的に接続するために使用されてもよく、その開示は、参照により本明細書に組み込まれる。

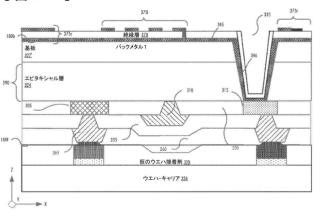

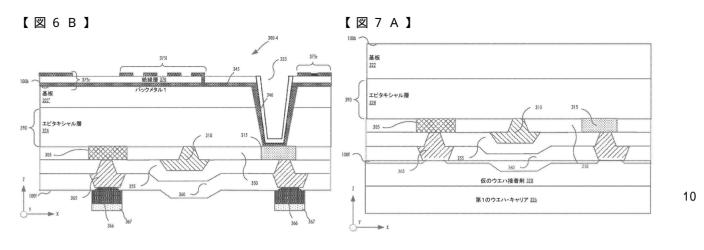

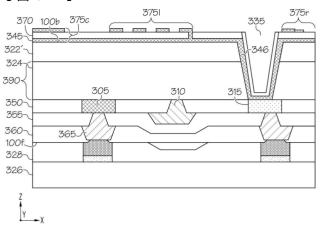

[0089]

図6A及び図6Bは、本開示の一部の実施例による、前面ピラー構造及びダイ100の 裏面上の受動デバイスを含むトランジスタ構造を製造する方法を示す断面図である。特に 、 バックメタル層 3 4 5 の形成は、デバイス 1 0 0 の裏面 1 0 0 b のバックメタル層 3 4 5 上に受動デバイス 3 7 5 ( すなわち、抵抗器 3 7 5 r などの抵抗部品並びに / 又はコン デンサ375c及び/若しくはインダクタ3751などのリアクタンス部品)を設けるこ とによってデバイス集積度を向上させるために使用されてもよい。受動デバイス375は 、 イン ピ ー ダン ス 整 合 回 路 、 高 調 波 フ ィ ル タ 、 カ プ ラ 、 バ ラ ン 、 及 び 電 力 合 成 器 / 分 配 器 などの1つ又は複数の機能ブロックをデバイス100の裏面100b上に実装するために 使用されるディスクリート部品であってもよい。例えば、ディスクリート部品375は、 R F 電力増幅器のための入力若しくは出力のインピーダンス整合回路及び / 又は高調波終 端回路の少なくとも一部を画定することができる。一部の実施例では、デバイス100の 裏面100b上にインピーダンス整合回路及び/又は高調波終端回路を実装することで、 そのような整合回路への(例えば、ワイヤ・ボンドを使用する)オフチップ接続に関連付 けられた複雑さを低減又は排除することができる。受動回路375は、一部の実施例では 、 裏 面 ビ ア 3 4 6 に よ っ て デ バ イ ス 1 0 0 の 前 面 1 0 0 f に 隣 接 す る 能 動 ト ラ ン ジ ス タ ・ セル300に接続されてもよい。しかしながら、一部の実施例では、裏面ビア346及び / 又は前面ピラー366が存在しなくてもよいことが理解されるであろう。

[0090]

一部の実施例では、受動デバイス375は、集積受動デバイス(IPD)を含んでもよい。集積受動デバイス(IPD)は、受動電気部品を含み、薄膜及び/又はフォトリソグラフィ処理などの標準的な半導体処理技術を使用して製造することができる。集積受動デバイス(IPD)は、フリップチップ実装可能又はワイヤ・ボンディング可能な構成要素とすることができ、シリコン、アルミナ、又はガラスなどの薄膜基板を含むことがある。 【0091】

ここで図 6 A を参照すると、図 5 E で第 1 のバックメタル層 3 4 5 を形成した後、デバ イス 1 0 0 の 裏 面 1 0 0 b の 第 1 の バック メタル 層 3 4 5 上 、 及 び ビ ア 開 口 部 3 3 5 の 裏 面ビア346上に、絶縁体層370が形成される。絶縁体層370は、窒化ケイ素(Si x N v ) 、 窒化アルミニウム ( A 1 N ) 、二酸化ケイ素 ( S i O 2 ) などの 1 つ又は複数 の誘電体材料を含むことができる。受動デバイス375は、例えば、第2のバックメタル 層を形成及びパターニングして、1つ又は複数のディスクリート・コンデンサ375c( 例えば、第2のバックメタル層、第1のバックメタル層345、及びそれらの間の絶縁体 層370の部分のパターニングされた部分によって画定される)、1つ又は複数のディス クリート・インダクタ3751(例えば、導電性トレース/コイルを画定するようにパタ ーニングされた第2のバックメタル層の部分によって画定される)、及び/又は1つ又は 複数のディスクリート抵抗器375r(例えば、抵抗セグメントを画定するようにパター ニングされた第2のバックメタル層の部分によって画定される)を画定することによって - 絶縁体層370上に形成される。絶縁体層370及び受動デバイス375は、デバイス 1 0 0 の前面 1 0 0 f の導電性ピラー 3 6 6 を応力から保護するように、基板 3 2 2 '及 びエピタキシャル層324が(例えば、仮接着剤328によって)ウエハ・キャリア32 6に取り付けられている間に形成される。

[0092]

図6Bに示すように、受動デバイス375の形成後、トランジスタ構造300-4を含

20

30

40

50

むデバイス100は、ウエハ・キャリア326から取り外されるか、又は他の方法で分離され、後続のプロセスにおける個片化及び(例えば、図10~図12に示されるようなパッケージへの)取り付けの準備が整う。したがって、前面ピラー366は、デバイス100の前面100 f の1つ又は複数の端子(例えば、入力、出力、接地)への接続を提供することができ、バックメタル層345上の受動回路は、デバイス100の端子のうちの1つ若しくは複数と外部デバイス又は接地接続との間の整合回路(例えば、入力/出力インピーダンス整合回路又は高調波終端回路)をデバイス100の裏面100b上に実装することができる。

### [0093]

一部の実施例では、図6Bのトランジスタ構造300-4を含むデバイス100は、図9Bを参照して説明されるものと同様又は同一のやり方で、前面ピラー366によって基板(例えば、プリント回路板(PCB)又は再分配層(RDL)構造)に接続されてもよい。すなわち、ダイ100は、前面ピラー366が、基板によって提供される、基板を通る電気信号配線用の対応する導電性トレースに物理的に取り付けられ、且つ電気的に接続されるように、パッケージ基板上に裏返されてもよい。他の実施例では、トランジスタ構造300-4を含むデバイス100は、図9Cを参照して説明されるものと同様の同一のやり方で、裏面を下にして基板に接続することができ、受動デバイス375を保護及び絶縁するために、裏面100bと基板との間に1つ若しくは複数の追加の金属層及び/又は保護誘電体層が設けられる。

### [0094]

図7A~図7Gは、本開示の一部の実施例による、複数のウエハ・キャリア・ボンディングを用いて、導電性貫通ビア構造を有する前面ピラー構造を含むトランジスタ構造を製造する方法を示す断面図である。特に、図7A~図7Gの操作は、前面ピラーが存在する間のウエハ・キャリアの取り付けを回避するために、複数のウエハ・キャリア・ボンディング・ステップ又はプロセスを使用してトランジスタ・セル300を含むデバイス100を形成するプロセス・シーケンスを示し、これにより、一部の単一のウエハ・キャリア・ボンディング実施態様と比較してよりアグレッシブな、例えば、前面ピラーのアスペクト比(高さ対幅)が2~5倍増加した幾何学的形状を有するより多くの前面ピラーが可能になる場合がある。

### [0095]

ここで図7Aを参照すると、図2のオフチップ接続用の金属コンタクト365を露出させた後、デバイス100は、「裏返され」、例えば、仮ウエハ接着剤328によって、第1のウエハ・キャリア326に(前面を下にして)取り付けられる。図7Bにおいて、基板322の厚さは、図3Cを参照して上述したものと同様又は同一のやり方で、個片化及びビア形成の両方の目的で(例えば、均一な裏面研削プロセスによって)低減される。それによって、基板322′は、裏面研削又は他の薄化プロセスにより、低減されるが、実質的に均一な厚さを有する。

# [0096]

図7Cに示すように、デバイス100が依然として第1のウエハ・キャリア326に取り付けられた状態で、ビア開口部335が、図5Dを参照して上述したものと同様又は同一のやり方で、基板322<sup>7</sup>及びエピタキシャル層324を貫いて形成され、コンタクト305、310、315のうちの1つ(ソース・コンタクト315を参照して示されている)の一部を露出させる。図7Dでは、図5Eを参照して上述したものと同様又は同一のやり方で、バックメタル層345を、基板322の裏面322B上に、またビア開口部335の側壁及び底面上にも堆積させるか、又は他の方法で形成して、裏面ビア346を画定する。

### [0097]

図 7 E に示すように、バックメタル層 3 4 5 を形成した後、デバイス 1 0 0 は、再び「裏返され」、例えば、仮のウエハ接着剤 3 2 9 によって、第 2 のウエハ・キャリア 3 2 7 に(裏面を下にして)取り付けられる。デバイス 1 0 0 はまた、ウエハ・キャリア 3 2 6

20

30

40

50

から取り外されるか、又は他の方法で分離される。図7Fでは、それぞれの導電性前面ピラー366及びはんだ層367が、図3Aを参照して上述したものと同様又は同一のやり方で、前面100fの金属コンタクト365上に形成される。図7Gに示すように、導電性前面ピラー366の形成後、トランジスタ構造300・3を含むデバイス100は、図5Fを参照して上述したものと同様又は同一のやり方で、第2のウエハ・キャリア327から取り外されるか、又は他の方法で分離され、後続のプロセスにおける個片化及び(例えば、図10~図12に示すようなパッケージへの)取り付けの準備が整う。

[0098]

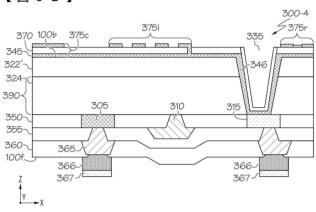

図8A~図8Dは、本開示の一部の実施例による、複数ウエハ・キャリア・ボンディングを用いて、前面ピラー構造及びダイの裏面上の受動デバイスを含むトランジスタ構造を製造する方法を示す断面図である。

[0099]

ここで図8Aを参照すると、図7Dにおいてバックメタル層345を形成した後、デバイス100の裏面100bのバックメタル層345上、及びビア開口部335の裏面ビア346上に絶縁体層370が形成され、(1つ若しくは複数のコンデンサ375c、1つ若しくは複数のインダクタ3751、及び/又は1つ若しくは複数の抵抗器375rを含む)受動デバイス375が、例えば図6Aを参照して上述したものと同様又は同一のやり方で、絶縁体層370上に形成される。絶縁体層370及び受動デバイス375は、基板322′及びエピタキシャル層324が第1のウエハ・キャリア326に(例えば、仮接着剤328によって)取り付けられている間に形成される。

[0100]

図8Bに示すように、受動デバイス375を形成した後、デバイス100は、図7Eを参照して上述されたものと同様又は同一のやり方で、再び「裏返され」、(例えば、仮のウエハ接着剤329によって)第2のウエハ・キャリア327に(裏面を下にして)取り付けられ、デバイス100は、第1のウエハ・キャリア326から取り外されるか、又は他の方法で分離される。図8Cでは、それぞれの導電性前面ピラー366及びはんだ層367が、図7Fを参照して上述したものと同様又は同一のやり方で、前面100fの金属コンタクト365上に形成される。図8Dに示すように、導電性前面ピラー366の形成後、デバイス100は、図7Gを参照して上述したものと同様又は同一のやり方で、第2のウエハ・キャリア327から取り外されるか、又は他の方法で分離される。トランジスタ構造300・4を含むデバイス100は、図6Bを参照して上述したものと同様又は同一のやり方で、後続のプロセスにおける個片化及び(例えば、図10~図12に示すようなパッケージへの)取り付けの準備が整う。

[0101]

[0102]

図10は、本開示の一部の実施例による、RFトランジスタ増幅器ダイ100を含むオ

20

30

40

50

ーバ・モールド型集積回路デバイス・パッケージの一例を示す断面図である。図10に示すように、パッケージ1000は、本明細書に記載される実施例のいずれかと同様の構の関素及び接続部を有するデバイス100(トランジスタ構造300-4を参照して例えば、で示される)を含み、これらは、前面ピラー366及びダイ・アタッチ材料層(例えば、はんだ層367)によって、プリント回路板(PCB)又は再配線層(RDL)構造な図10の例では、オーバ・モールド型パッケージング材料1013は、デバイス100をバイスに接続するためのワイヤ・ボンド接続1025を介して、パッケージ・リード(例えば、ゲート・リード及びドレイン・リード)1011i、10110(まとめて1011)へのアクセスを提供する。オーバ・モールド1013は、プラスチック又はプラスチックスにが、ゲート・リード及びドレイン・リード)1011 は、プラスチック又はプラスチックスがリマー化合物で形成されてもよく、それによって外部環境からの保護を提供する。オーバ・モールド1013は、パッケージ1000の会にでいるででいるででででいる。オーバ・モールド型パッケージング材料1013の一部の利点は、パッケージ1000の音にのででででは厚さの低減、並びにリード1011の配置及び/又はそれらの間の間隔の設計上の柔軟性を含む。

[0103]

特に、図10の例では、入力リード1011iは、ワイヤ・ボンド1025、ダイ100の裏面100 b 上の入力インピーダンス整合ネットワークを画定する受動デバイス375のうちの1つ又は複数、及びゲート310への基板貫通ビア(図示する断面の外側にある)によってゲート310に結合され、出力リード10110は、ワイヤ・ボンド1025、導電性トレース1021、及び対応する前面ピラー366によってドレイン305に結合され、ソース315は、対応する前面ピラー366を介して接地されている。図10は、入力インピーダンス整合のみのための裏面受動デバイス375の使用を示しているが、裏面受動デバイス375のうちの1つ又は複数の受動デバイス375に接続するワイヤ・ボンド1025とのリカインピーダンス整合のために、又は図11及び図12の例に示すように入力インピーダンス整合のために、又は図11及び図12の例に示すように入力インピーダンス整合の両方のために同様に使用されてもよいことが理解といて、変合と出力インピーダンス整合の両方のために同様に使用されてもよいことが理解といて、前面ピラー366を介してソース315への接地接続は、ピア346を用いてまたったれているが、他の実施例では、ソース315への接地接続は、ピア346を用いて実装されてもよく、一部の実施例では、受動デバイス375のうちの1つ又は複数が裏面100 b 上に高調波終端回路を画定する。

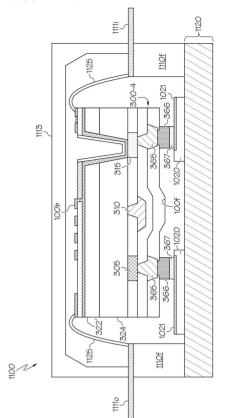

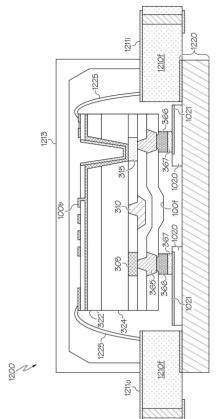

[0104]

図11及び図12は、本開示の一部の実施例による、RFトランジスタ増幅器ダイ100を含む熱強化集積回路デバイス・パッケージの例を示す断面図である。図11及び図12に示すように、オープンキャビティ・パッケージ1100、1200は、(トランンスタ構造300・4を参照して例として示す)本明細書に記載される実施例のいずれかと同様の構成要素及び接続部を有するが、導電性ベース又はフランジ1120、1220上に取り付けられ、熱強化パッケージの蓋部材1113、1213によって保護されたでバス100を含む。特に、図11は、本開示の実施例による熱強化パッケージの第1の所による熱強化パッケージの第1のの実施機(T3PACパッケージ1200と呼ばれる)を示す。一部の実施例では、フランジ1120、1220は、ダイ100(及び/又に構成要素によって生成された熱を示す。一部の実施例では、フランジ1120、1220は、ダイ100、1200の外部に放散又は他の方法で伝達するための熱伝導性(外ッケージ1100、1200の外部に放散又は他の方法で伝達するための熱伝導性(例えば、ヒートシンク)の両方を提供することができる。フランジ1120、1220は、プランジ1120、1220は、電気的な接地接続を提供するように構成されてもよい。

[ 0 1 0 5 ]

図 1 1 の T E P A C パッケージ 1 1 0 0 は、蓋部材 1 1 1 3 及び(断面では側壁 1 1 1 0 f として示される)フレーム部材によって画定される上部ハウジングを含むセラミック

20

30

40

50

ベースのパッケージであってもよい。蓋部材1113及び/又は側壁1110 f は、セラミック材料(例えば、アルミナ)を含むことができ、導電性ベース又はフランジ1120上のダイ100を取り囲む開放キャビティを画定することができる。蓋部材1113は、エポキシ接着剤を用いて側壁1110 f に接着されてもよい。側壁1110 f は、ろう付けを介してベース1120に取り付けられてもよい。

# [0106]

図 1 2 の T 3 P A C パッケージ 1 2 0 0 も、ベース 1 2 2 0 と、蓋部材 1 2 1 3 及び (断面では側壁 1 2 1 0 f として示される)フレーム部材を有する上部ハウジングとを含むセラミックベースのパッケージであってもよい。蓋部材 1 2 1 3 及び側壁 1 2 1 0 f は、導電性ベース又はフランジ 1 2 2 0 上のダイ 1 0 0 を取り囲む開放キャビティを同様に画定する。パッケージ 1 2 0 0 において、蓋部材 1 2 1 3 は、セラミック材料(例えば、アルミナ)であってもよく、側壁 1 2 1 0 f は、プリント回路板(P C B )であってもよい

# [0107]

図 1 1 及び図 1 2 において、フランジ 1 1 2 0 、 1 2 2 0 は、導電性材料、例えば、銅層 / 積層体、又はその合金若しくは金属マトリックス複合体であってもよい。一部の実施例では、フランジ 1 1 2 0 は、銅・モリブデン(CuMo)層、CPC(Cu/MoCu/Cu)、若しくは銅・タングステンCuWなどの他の銅合金、及び/又は他の積層/多層構造を含むことができる。図 1 1 の例では、フランジ 1 1 2 0 は、側壁 1 1 1 0 f 及び/又は蓋部材 1 1 1 3 が取り付けられるCPCベースの構造であってもよい。図 1 2 の例では、フランジ 1 2 2 0 は、側壁 1 2 1 0 f 及び/又は蓋部材 1 2 1 3 が例えば導電性接着剤によって取り付けられる銅・モリブデン(RCM60)ベースの構造であってもよい

### [0108]

図 1 1 及び図 1 2 において、ダイ 1 0 0 の端子のうちの 1 つ ( 例えば、ソース・コンタクト 3 1 5 ) は、フランジ 1 1 2 0 、 1 2 2 0 に取り付けられてもよく、したがって、フランジ 1 1 2 0 、 1 2 2 0 は、パッケージ 1 1 0 0 、 1 2 0 0 のためのソース・リードを提供することができる。導電性リード 1 1 1 1 、 1 2 1 1 は、パッケージ 1 1 0 0 のゲート・リード及びドレイン・リードを提供することができ、フランジ 1 1 2 0 、 1 2 2 0 に取り付けられ、それぞれの側壁 1 1 1 0 f 、 1 2 1 0 f によって支持されている。図 1 1 及び図 1 2 の 例では、したがって、パッケージ 1 1 0 0 、 1 2 0 0 の外部にある回路又はデバイスに接続するためのパッケージ・リード 1 1 1 1 、 1 2 1 1 をダイ 1 0 0 に接続するために、それぞれのワイヤ・ボンド 1 1 2 5 、 1 2 2 5 が使用されている。

# [0109]

特に、図11及び図12の例では、入力リード11111、1211iは、ワイヤ・ボ ン ド 1 1 2 5 、 1 2 2 5 、 ダ イ 1 0 0 の 裏 面 1 0 0 b 上 の 入 カ イ ン ピ ー ダ ン ス 整 合 ネ ッ ト ワークを画定する受動デバイス375のうちの1つ又は複数、及びゲート310への基板 貫通ビア(図示する断面の外側にある)によってゲート310に結合され、出力リード1 1 1 1 0 、 1 2 1 1 0 は、ワイヤ・ボンド 1 1 2 5 、 1 2 2 5 、ダイ 1 0 0 の裏面 1 0 0 b 上の出力インピーダンス整合ネットワークを画定する受動デバイス 3 7 5 のうちの 1 つ 又 は 複 数 、 及 び ド レ イ ン 3 0 5 へ の 基 板 貫 通 ビ ア ( 図 示 す る 断 面 の 外 側 に あ る ) に よ っ て ドレイン305に結合され、ソース315は、対応する前面ピラー366を介して接地さ れている。しかしながら、裏面受動デバイス375は、入力インピーダンス整合のために のみ、又は出力インピーダンス整合のためにのみ使用されてもよいことが理解されよう。 同様に、一部の実施例では、裏面受動デバイス375は、高調波終端を実装するために使 用されてもよい。また、ワイヤ・ボンド1125、1225は、他の実施例では省略され てもよく、異なる電気的接続が使用されてもよい。より一般的には、本明細書に記載され るパッケージ 1 0 0 0 、 1 1 0 0 、 1 2 0 0 は、裏面受動デバイス 3 7 5 の使用の有無に かかわらず、端子310、305、315をパッケージの入力、出力、及び/又は接地リ ードに電気的に接続するために、導電性ビア、ワイヤ・ボンド、及び/又は導電性ピラー

の任意の組合せを含むことができる。

### [0110]

図では、導電性ピラー366は、他の非導電性材料によって封入されることなく、自立しているものとして示されている。このような自立したピラー366は、例えば、ピラー間、チップとチップ / 基板間、及び / 又はピラーとチップ / 基板間のRF寄生結合の低減を含むが、これらに限定されない利点を提供することができる。しかしながら、本明細書に記載されるような導電性ピラー366を有する実施例のうちのいずれも、ピラー366のためのさらなる保護(機械的、湿気など)及び / 又は支持を提供するように、絶縁層350、355、360と取り付け基板との間のピラー366上に又はこれを覆う、オーバ・モールドなどの封止材料をさらに含んでもよいことを理解されたい。一部の実施例では、ピラー366が自立しているか、又は封止材料によって支持されているかは、設計要素(例えば、電力、周波数、整合回路、パッケージングなど)に基づいて変化することがある

# [0111]

本開示の実施例は、基板又は積層体(例えば、再配線層(RDL)積層体)上に組み立てることができ、最新の高度化されたウエハ・レベル・パッケージング技術を使用してバッチで組み立てることができる。受動デバイス375をダイ100の裏面に直接設けることによって、ワイヤボンディング・プロセスを低減又は排除することができ、それによって、製造時間、コスト、及びパッケージ寸法を低減することができる。ダイ100は、例えば、RF電力増幅器を画定するパワー・トランジスタ・デバイスのトランジスタ・セルを含むことができる。一部の実施例では、ダイ100は、ディスクリート・マルチステージ、モノリシック・マイクロ波集積回路(MMIC)、及び/又はマルチパス(例えば、ドハティ)トランジスタ・デバイスを含むことができる。

### [0112]

本開示の実施例は、様々なセルラ・インフラストラクチャ(CIFR:cellularinfrastructure)RF電力製品(5W、10W、20W、40W、60W、80W及び異なる周波数帯を含むが、これらに限定されない)、例えば、5G及び基地局用途に使用することができる。本開示の実施例は、レーダ及びMMICタイプの用途に適用することもできる。より一般的には、本開示の実施例は、GaN高電子移動度トランジスタ(HEMT)ディスクリート及びRF IC技術、並びにパワーMOSFET、ショットキー、或いは外部接続のためにワイヤ・ボンドを使用する可能性があり、及び/又は受動デバイス要素の集積から恩恵を受ける可能性がある任意のデバイスにおいて適用されてもよい。

# [0113]

本明細書では、例示的な実施例が示される添付の図面を参照して様々な実施例を説明してきた。しかしながら、これらの実施例は、異なる形態で具現化されてもよく、本明細書に記載される実施例に限定されるものとして解釈されるべきではない。むしろ、これらの実施例は、本開示が完璧且つ完全であり、当業者に発明概念を十分に伝えるように提供されている。本明細書に記載される例示的な実施例並びに包括的な原理及び特徴に対する様々な修正は、容易に明らかになるであろう。図面において、層並びに領域のサイズ及び相対的なサイズは、縮尺通りに示されておらず、場合によっては、明確にするために誇張されていることがある。

# [0114]

「第1」、「第2」などの用語は、本明細書では様々な要素を説明するために使用されることがあるが、これらの要素は、これらの用語によって限定されるべきではない。これらの用語は、ある要素を別の要素と区別するためにのみ使用される。例えば、本開示の範囲から逸脱することなく、第1の要素を第2の要素と呼ぶことができ、同様に、第2の要素を第1の要素と呼ぶことができる。本明細書で使用される場合、「及び/又は」という用語は、関連付けられた列挙された項目の1つ又は複数の任意の及びすべての組合せを含む。

10

20

30

40

20

30

40

50

### [0115]

本明細書で使用される術語は、特定の実施例のみを説明するためのものであり、本発明を限定することは意図されていない。本明細書で使用される場合、単数形「1つの(a)」、「1つの(an)」、及び「その(the)」は、文脈がそうでないと明白に示さない限り、複数形を同様に含むことが意図されている。用語「備える(comprises)」、「備えている(comprising)」、「含む(includes)」及び/又は「含んでいる(including)」は、本明細書で使用される場合、述べられた特徴、整数、ステップ、動作、要素、及び/又は構成要素の存在を指定するが、1つ又は複数の他の特徴、整数、ステップ、動作、要素、構成要素、及び/又はそれらのグループの存在若しくは追加を排除しないことがさらに理解されるであろう。

[0116]

その他の方法で定義されない限り、本明細書で使用されるすべての用語(技術用語及び科学用語を含む)は、本発明が属する技術分野の当業者によって一般に理解されるものと同じ意味を有する。本明細書で使用される用語は、本明細書及び関連技術の文脈におけるそれらの意味と一致する意味を有すると解釈されるべきであり、本明細書で明示的に定義されない限り、理想化された又は過度に形式的な意味で解釈されないことがさらに理解されるであろう。

[0117]

層、領域、又は基板などの要素が別の要素の「上に」ある、別の要素に「取り付けられている」、又は別の要素の「上に」延在していると言及される場合、それは他の要素の直接上にあってもよく、又は介在する要素が存在してもよいことが理解されよう。対照的に、要素が別の要素の「直接上に」ある、又は「直接取り付けられている」、又は「直接上に」延在していると言及される場合、介在要素は存在しない。ある要素が別の要素に「接続されている」又は「結合されている」と言及される場合、それは他の要素に直接接続若しくは結合されていてもよく、又は介在する要素が存在してもよいことも理解されるであるう。対照的に、要素が別の要素に「直接接続されている」又は「直接結合されている」と言及される場合、介在する要素は存在しない。

[0118]

「下(below)」、「上(above)」、「上部(upper)」、「下部(lower)」、「水平(horizontal)」、「横方向(lateral)」、「垂直(vertical)」などの相対語は、本明細書では、1つの要素、層又は領域と別の要素、層又は領域との関係を図に示すように記述するために使用されることがある。これらの用語は、図に示されている向きに加えて、デバイスの異なる向きを包含することが意図されていることが理解されるであろう。

[0119]

本発明の実施例は、本発明の理想化された実施例(及び中間構造)の概略図である断面図を参照して本明細書で説明されている。図面における層及び領域の厚さは、明確にするために誇張されていることがある。さらに、例えば、製造技術及び / 又は公差の結果として、図の形状とは異なることが予想される。したがって、本発明の実施例は、本明細書に示される領域の特定の形状に限定されると解釈されるべきではなく、例えば、製造に起因する形状の逸脱を含むべきである。点線で示された要素は、図示された実施例では任意選択である場合がある。

[ 0 1 2 0 ]

同様の番号は、全体を通して同様の要素を指す。したがって、同一又は類似の番号は、対応する図面で言及又は説明されていない場合であっても、他の図面を参照して説明することができる。また、参照番号で示されていない要素については、他の図面を参照して説明することができる。

[0121]

図面及び明細書では、本発明の典型的な実施例が開示されており、特定の用語が用いられているが、それらは、限定を目的としたものではなく、一般的且つ説明的な意味でのみ

使用されており、本発明の範囲は以下の特許請求の範囲に記載されている。

# 【図面】

# 【図1】

【図2】

20

10

# 【図3A】

【図3B】

30

【図5D】

【図5F】

【図6A】

40

10

20

# 【図9B】 | 100b | 接板 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 | 300-3 |

【図9C】

366 367

300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 300-3

1000 3

40

10

20

### 【手続補正書】

【提出日】令和5年1月19日(2023.1.19)

【手続補正1】

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

【補正の内容】

【特許請求の範囲】

【 請 求 項 1 】

第1の表面、第2の表面、前記第1の表面と前記第2の表面との間にあり、前記第1の表面に隣接する複数のトランジスタ・セルを備える半導体層構造、及び前記トランジスタ・セルに結合された端子を備える高周波(「RF」)トランジスタ増幅器ダイと、

前記ダイの前記第2の表面上にあり、前記端子のうちの少なくとも1つに電気的に接続された少なくとも1つの受動電子部品と、

を備える、集積回路デバイス。

### 【請求項2】

前記端子が、前記トランジスタ・セルによって画定されるRFトランジスタ増幅器の入力端子、出力端子、及び/又は接地端子を含む、請求項1に記載の集積回路デバイス。

### 【請求項3】

前記少なくとも1つの受動電子部品が、前記ダイの前記第2の表面上の、前記RFトランジスタ増幅器のための入力インピーダンス整合回路、出力インピーダンス整合回路、及び/又は高調波終端回路の少なくとも一部を画定する、請求項2に記載の集積回路デバイス。

### 【請求項4】

前記少なくとも1つの受動電子部品が、前記ダイの前記第2の表面上のディスクリート・コンデンサ、インダクタ、及び/又は抵抗器を含む少なくとも1つの集積受動デバイス(IPD)である、請求項1から3までのいずれか一項に記載の集積回路デバイス。

### 【請求項5】

前記ダイの前記第2の表面上に延在し、前記少なくとも1つの受動電子部品を前記端子のうちの前記少なくとも1つに電気的に接続する金属層、

をさらに備える、請求項1から3までのいずれか一項に記載の集積回路デバイス。

# 【請求項6】

前記金属層が第1の金属層であり、

前記第2の表面の反対側の前記第1の金属層上に絶縁体層をさらに備え、

前記少なくとも1つの受動電子部品が、前記第1の金属層の反対側の前記絶縁体層上にあり、1つ又は複数のディスクリート・コンデンサ、インダクタ、及び/又は抵抗器を画定する第2の金属層のパターンを含む、

請求項5に記載の集積回路デバイス。

# 【請求項7】

前記ダイの前記第2の表面及び前記半導体層構造内に延在して、前記ダイの前記第2の表面上の前記金属層を前記端子のうちの前記少なくとも1つに電気的に接続する少なくとも1つの導電性ビア、

をさらに備える、請求項5に記載の集積回路デバイス。

### 【請求頂8】

前記半導体層構造がIII族窒化物材料を含み、前記ダイが前記III族窒化物材料と前記第2の表面との間に炭化ケイ素基板を含む、請求項1から7までのいずれか一項に記載の集積回路デバイス。

# 【請求項9】

前記ダイの前記第1の表面から突出し、前記端子のうちの1つ若しくは複数に電気的接続を提供する1つ又は複数の導電性ピラー構造、

10

20

30

40

をさらに備える、請求項1から3までのいずれか一項に記載の集積回路デバイス。

### 【請求項10】

1 つ又は複数の導電性接続部を含むパッケージ基板、

#### をさらに備え、

前記1つ又は複数の導電性ピラー構造が、前記ダイを前記ダイの前記第1の表面に隣接する前記パッケージ基板に取り付け、前記端子のうちの前記1つ若しくは複数を前記1つ 又は複数の導電性接続部に電気的に接続する、

請求項9に記載の集積回路デバイス。

### 【請求項11】

第1の表面、第2の表面、前記第1の表面と前記第2の表面との間にあり、前記第1の表面に隣接する複数のトランジスタ・セルを備える半導体層構造、及び前記トランジスタ・セルに結合された端子を備える高周波(「RF」)トランジスタ増幅器ダイと、

前記ダイの前記第1の表面から突出し、前記端子のうちの1つ若しくは複数に電気的に接続された1つ又は複数の導電性ピラー構造と、

前記ダイの前記第2の表面及び前記半導体層構造内に延在し、前記端子のうちの少なくとも1つに電気的である、少なくとも1つの導電性ビアと、

を備える、集積回路デバイス。

### 【請求項12】

前記端子が、前記トランジスタ・セルによって画定されるRFトランジスタ増幅器の入力端子、出力端子、及び/又は接地端子を含む、請求項11に記載の集積回路デバイス。

### 【請求項13】

前記1つ又は複数の導電性ピラー構造が前記入力端子及び/又は前記出力端子への電気的接続を提供し、前記少なくとも1つの導電性ビアが前記接地端子への電気的接続を提供する、請求項12に記載の集積回路デバイス。

#### 【請求項14】

前記ダイが前記半導体層構造と前記ダイの前記第2の表面との間に基板を含み、前記少なくとも1つの導電性ビアが前記基板を貫いて延在し、前記半導体層構造が、前記基板上に1つ又は複数のエピタキシャル層を含む、請求項11から13までのいずれか一項に記載の集積回路デバイス。

## 【請求項15】

前記半導体層構造がIII族窒化物材料を含み、前記基板が炭化ケイ素基板を含む、請求項14に記載の集積回路デバイス。

### 【請求項16】

1つ又は複数の導電性接続部を含むパッケージ基板、

## をさらに備え、

前記1つ又は複数の導電性ピラー構造が、前記ダイを前記ダイの前記第1の表面に隣接する前記パッケージ基板に取り付け、前記端子のうちの前記1つ若しくは複数を前記1つ又は複数の導電性接続部に電気的に接続する、

請 求 項 1 1 か ら 1 3 ま で の い ず れ か 一 項 に 記 載 の 集 積 回 路 デ バ イ ス 。

### 【請求項17】

少なくとも1つの導電性接続部を含むパッケージ基板をさらに備え、

前記ダイが前記ダイの前記第2の表面に隣接する前記パッケージ基板に取り付けられ、前記少なくとも1つの導電性ビアが前記端子のうちの前記少なくとも1つを前記少なくと も1つの導電性接続部に電気的に接続する、

請求項11から13までのいずれか一項に記載の集積回路デバイス。

### 【請求項18】

前記ダイの前記第2の表面上に少なくとも1つの受動電子部品をさらに備え、前記少なくとも1つの受動電子部品が前記少なくとも1つの導電性ビアによって前記端子のうちの前記少なくとも1つに電気的に接続されている、

請 求 項 1 1 か ら 1 3 ま で の い ず れ か 一 項 に 記 載 の 集 積 回 路 デ バ イ ス 。

10

20

30

### 【請求項19】

第1の表面、第2の表面、前記第1の表面と前記第2の表面との間にあり、前記第1の表面に隣接する複数のトランジスタ・セルを備える半導体層構造、前記半導体層構造と前記第2の表面との間の基板、及び前記トランジスタ・セルに結合された端子を備える高周波(「RF」)トランジスタ増幅器構造を形成するステップと、

前記第1の表面から突出する1つ又は複数の導電性ピラー構造を形成して、前記端子のうちの1つ又は複数への電気的接続を提供するステップと、

前記RFトランジスタ増幅器構造を個片化して、約50~約200ミクロン以上の厚さを有する前記基板の一部を含むRFトランジスタ増幅器ダイを画定するステップと、を含む、集積回路デバイスを製造する方法。

### 【請求項20】

第1の表面、第2の表面、前記第1の表面と前記第2の表面との間にあり、前記第1の表面に隣接する複数のトランジスタ・セルを備える半導体層構造、及び前記トランジスタ・セルに結合された端子を備える高周波(「RF」)トランジスタ増幅器構造を形成するステップと、

前記第1の表面から突出する1つ又は複数の導電性ピラー構造を形成して、前記端子のうちの1つ又は複数への電気的接続を提供するステップと、

前記第2の表面内に、且つ前記半導体層構造を貫いて延在する少なくとも1つの導電性ビアを形成して、前記端子のうちの少なくとも1つへの電気的接続を提供するステップと

を含む、集積回路デバイスを製造する方法。

【手続補正2】

【補正対象書類名】図面

【補正対象項目名】全図

【補正方法】変更

【補正の内容】

【図面】

【図1】

【図2】

40

10

20

30

## 【図6A】

10

## 【図 6 B】

【図7A】

20

30

# 【図9A】

## 【図9B】

10

20

# 【図9C】

# 【図10】

30

# 【図11】

【図12】

10

20

30

20

30

40

## 【国際調査報告】

### INTERNATIONAL SEARCH REPORT International application No PCT/US2021/033981 A. CLASSIFICATION OF SUBJECT MATTER H03F3/195 H01L23/66 H01L25/16 H01L29/66 H01L21/70 INV. H01L23/495 ADD. According to International Patent Classification (IPC) or to both national classification and IPC B. FIELDS SEARCHED Minimum documentation searched (classification system followed by classification symbols) HO3F HO1T. Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched Electronic data base consulted during the international search (name of data base and, where practicable, search terms used) EPO-Internal, WPI Data C. DOCUMENTS CONSIDERED TO BE RELEVANT Category\* Citation of document, with indication, where appropriate, of the relevant passages Relevant to claim No. X US 2012/140432 A1 (ANDREI CRISTIAN [FR]) 1-4 7 June 2012 (2012-06-07) Y paragraphs [0031] - [0033], [0041] -R [0045]; figures 2,3 WO 2019/066878 A1 (INTEL CORP [US]; THEN 8,15,24, Y HAN WUI [US] ET AL.) 4 April 2019 (2019-04-04) page 1, lines 9-21 page 6, lines 28-31 WO 2019/170045 A1 (WAYTHON INTELLIGENT х 9,10 TECH SUZHOU CO LTD [CN]) 12 September 2019 (2019-09-12) pages 3-5; figures 2,3 11-30 Y -/--Further documents are listed in the continuation of Box C. See patent family annex. Special categories of cited documents : "T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention "A" document defining the general state of the art which is not considered to be of particular relevance "E" earlier application or patent but published on or after the international filing date "X" document of particular relevance;; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone "L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified) document of particular relevance;; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art "O" document referring to an oral disclosure, use, exhibition or other "P" document published prior to the international filing date but later than the priority date claimed "&" document member of the same patent family Date of the actual completion of the international search Date of mailing of the international search report 7 December 2021 21/12/2021 Name and mailing address of the ISA/ Authorized officer European Patent Office, P.B. 5818 Patentlaan 2 NL - 2280 HV Rijswijk Tel. (+31-70) 340-2040 Cortes Rosa, João Fax: (+31-70) 340-3016

Form PCT/ISA/210 (second sheet) (April 2005)

page 1 of 2

## INTERNATIONAL SEARCH REPORT

International application No. PCT/US2021/033981

| Box No. II Observations where certain claims were found unsearchable (Continuation of item 2 of first sheet)                                                                                                                                                                                                                                                                            |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| This international search report has not been established in respect of certain claims under Article 17(2)(a) for the following reasons:                                                                                                                                                                                                                                                | 10 |

| Claims Nos.:     because they relate to subject matter not required to be searched by this Authority, namely:                                                                                                                                                                                                                                                                           | 10 |

| Claims Nos.:  because they relate to parts of the international application that do not comply with the prescribed requirements to such an extent that no meaningful international search can be carried out, specifically:                                                                                                                                                             |    |

| Claims Nos.:  because they are dependent claims and are not drafted in accordance with the second and third sentences of Rule 6.4(a).                                                                                                                                                                                                                                                   | 20 |

| Box No. III Observations where unity of invention is lacking (Continuation of Item 3 of first sheet)                                                                                                                                                                                                                                                                                    |    |

| This International Searching Authority found multiple inventions in this international application, as follows:                                                                                                                                                                                                                                                                         |    |

| see additional sheet                                                                                                                                                                                                                                                                                                                                                                    |    |

| As all required additional search fees were timely paid by the applicant, this international search report covers all searchable daims.                                                                                                                                                                                                                                                 | 30 |

| 2. As all searchable claims could be searched without effort justifying an additional fees, this Authority did not invite payment of additional fees.                                                                                                                                                                                                                                   |    |

| 3.  As only some of the required additional search fees were timely paid by the applicant, this international search report covers only those claims for which fees were paid, specifically claims Nos.:  1-4, 8-30                                                                                                                                                                     |    |

| 4. No required additional search fees were timely paid by the applicant. Consequently, this international search report is restricted to the invention first mentioned in the claims;; it is covered by claims Nos.:                                                                                                                                                                    | 40 |

| Remark on Protest  The additional search fees were accompanied by the applicant's protest and, where applicable, the payment of a protest fee.  The additional search fees were accompanied by the applicant's protest but the applicable protest fee was not paid within the time limit specified in the invitation.  X  No protest accompanied the payment of additional search fees. |    |

|                                                                                                                                                                                                                                                                                                                                                                                         |    |

Form PCT/ISA/210 (continuation of first sheet (2)) (April 2005)

## International Application No. PCT/US2021 /033981

### FURTHER INFORMATION CONTINUED FROM PCT/ISA/ 210

This International Searching Authority found multiple (groups of) inventions in this international application, as follows:

### 1. claims: 1-4, 8

IC device comprising RF transistor amplifier die with transistor cells and terminals coupled thereto. General passive component on a surface of the die.

#### 1.1. claim: 4

IC device comprising RF transistor amplifier die with transistor cells and terminals coupled thereto.

Passive component on a surface of the die is integrated passive device comprising discrete capacitor, inductor and/or resistor.

#### 1.2. claim: 8

IC device comprising RF transistor amplifier die with transistor cells and terminals coupled thereto. Semiconductor layer structures comprise group-III nitrides; substrate comprises silicon carbide.

## 2. claims: 5-7

IC device comprising RF transistor amplifier die with transistor cells and terminals coupled thereto. Metal layer connects general passive component on a surface of the die to the terminals.

### 3. claims: 9-30

IC device and manufacturing method for IC device comprising RF transistor amplifier die with transistor cells and terminals coupled thereto (and a general passive component on a surface of the die in claims 9, 10, 18, 29 and 30). Conductive pillars connected to terminals protrude from a surface of the die.

10

20

30

20

30

40

## INTERNATIONAL SEARCH REPORT

international application No

PCT/US2021/033981

| CíContinu | ation). DOCUMENTS CONSIDERED TO BE RELEVANT                                                                                                                                             | <u> </u>              |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| ategory*  | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                      | Relevant to claim No. |

| ,         | US 8 138 087 B2 (MOREL STEPHANE [FR]; DEN DEKKER ARNOLDUS [NL] ET AL.) 20 March 2012 (2012-03-20) column 2, line 50 - column 3, line 23; figure 1 column 6, line 54 - column 7, line 49 | 11-30                 |

|           | EP 1 670 055 A1 (IMEC INTER UNI MICRO<br>ELECTR [BE]) 14 June 2006 (2006-06-14)<br>paragraph [0010]                                                                                     | 21-23                 |