US 20090107545A1

## (19) United States(12) Patent Application Publication

### Moslehi

### (10) Pub. No.: US 2009/0107545 A1 (43) Pub. Date: Apr. 30, 2009

### (54) TEMPLATE FOR PYRAMIDAL THREE-DIMENSIONAL THIN-FILM SOLAR CELL MANUFACTURING AND METHODS OF USE

(75) Inventor: Mehrdad Moslehi, Los Altos, CA (US)

> Correspondence Address: HULSEY IP INTELLECTUAL PROPERTY LAWYERS, P.C. 919 Congress Avenue, Suite 919 AUSTIN, TX 78701 (US)

- (73) Assignee: Soltaix, Inc.

- (21) Appl. No.: 11/868,492

- (22) Filed: Oct. 6, 2007

### **Related U.S. Application Data**

(60) Provisional application No. 60/828,678, filed on Oct. 9, 2006, provisional application No. 60/886,303, filed on Jan. 24, 2007.

### **Publication Classification**

- (51) Int. Cl. *H01L 31/00* (2006.01) *H01L 21/02* (2006.01)

- (52) U.S. Cl. ..... 136/256; 438/57; 257/E21.002

### (57) ABSTRACT

A template **120** for pyramidal three-dimensional thin-film solar cell substrate formation for use in pyramidal three-dimensional thin-film solar cells. The template **120** comprises a substrate which comprises a plurality of pyramid trenches **122** between a plurality of posts **123**. The template **120** forms an environment for pyramidal three-dimensional thin-film solar cell substrate formation.

(PRIOR ART)

# Competitive Advantages of

## <u>Current Invention</u>

- 1. < 1 gram of silicon per watt

- 2. Decoupled from silicon supply chain

- 3. No polysilicon feedstock cost

- 4. No crystal growth cost

- 5. No wire saw cost

- 6. No wafer saw damage removal cost

- 7. No texturing cost

- 8. No lithography cost for cell processing

- 9. Fewer process steps self aligned flow

- 10.Reduced PV fab capital cost

- 11.>60% reduction in module mfg. cost/Wp 12.Ultra-high-efficiency cells & modules

216

216

216

216

280

×

≻

N

FIG. 29

FIG. 30

FIG. 31

FIG. 34

FIG. 35

**Patent Application Publication**

US 2009/0107545 A1

FIG. 64

0.00 1.00 2.00 3.00 4.00 5.00 6.00 H/d (ratic of hexagonal pyramid height to base diagonal dimension)

## TEMPLATE FOR PYRAMIDAL THREE-DIMENSIONAL THIN-FILM SOLAR CELL MANUFACTURING AND METHODS OF USE

**[0001]** This application claims the benefit of provisional patent applications 60/828,678 filed on Oct. 9, 2006 and 60/886,303 filed on Jan. 24, 2007, which are hereby incorporated by reference.

### FIELD

**[0002]** This disclosure relates in general to the field of photovoltaics and solar cells, and more particularly to threedimensional (3-D) Thin-Film Solar Cells (TFSCs) and methods for manufacturing same. Even more particularly, the presently disclosed subject matter relates to a template for pyramidal 3-D TFSC substrate manufacturing and methods for making and using the template.

### DESCRIPTION OF THE RELATED ART

[0003] Renewable, high-efficiency, and cost-effective sources of energy are becoming a growing need on a global scale. Increasingly expensive, unreliable, and environmentally-risky fossil fuels and a rising global demand for energy, including electricity, have created the need for alternate, secure, clean, widely available, cost-effective, environmentally-friendly, and renewable forms of energy. Solar photovoltaic (PV) electricity generation using solar cells is uniquely suited to meet the needs of residential, commercial, industrial, and centralized utility applications. Key attributes that make solar energy attractive are the abundant, worldwide, point-of-use supply of sunlight, environmental friendliness, scalability (from milliwatts to megawatts), secure point-of-use generation of solar electricity, and excellent distributed energy economics. The sun provides more energy to the earth in one hour than the annual energy consumption of the entire world. Much of the earth's surface receives a significant amount of annual sun-hours which may be effectively harnessed for clean and secure electricity generation. A key driver for this market pull is a rising public awareness of environmentally-benign technologies. However, due to relatively low solar cell efficiencies (e.g., less than 12% for most thin-film technologies and roughly 12% to 18% for most crystalline silicon solar cell technologies), high costs of raw materials (e.g., silicon for crystalline silicon wafer solar cells) and manufacturing processes, limitations on cost-effective and efficient electrical storage, and a general lack of infrastructure to support solar cell proliferation, to date there has been limited use of this energy solution (currently, electricity generation by solar photovoltaics accounts for less than 0.1% of total worldwide electricity generation).

**[0004]** For commercial applications, cost of energy to the end-user (e.g., in cents/kWh for electricity) should be sufficiently low and comparable to or even better than that from utility grids using conventional electricity generation, sources. The solar photovoltaic electricity generation, which currently accounts for less than 0.1% of the global electricity generation, may be substantially expanded if it achieves cost parity with conventional grid electricity. As the costs of solar cells and modules (typically expressed as  $\$/W_p$ ) are reduced, grid-tied solar photovoltaic applications are gaining acception.

tance at an accelerated pace, making them an attractive option for significant proliferation in electricity generation.

[0005] In the price-sensitive solar cell market, two principal technology options exist. On the one hand, crystalline silicon (c-Si) wafers may serve as the basis for solar cell formation (currently accounting for more than 90% of the solar PV market). On the other hand, thin-film (amorphous and polycrystalline) technologies using silicon and other semiconductor absorber materials (such as amorphous silicon, CdTe, or CIGS) may offer significant cost advantages compared to crystalline silicon wafer-based solar cells. These different approaches are at opposite ends of the price-performance scale. Crystalline silicon wafers offer higher performance, but at higher costs (due to the relatively high cost of starting monocrystalline and multicrystalline silicon wafers). Thin-film technologies may offer lower manufacturing costs, but typically at lower performance levels (i.e., lower efficiencies). For both approaches, the price-per-watt typically increases as cell efficiencies rise (due to higher material and/ or manufacturing costs).

**[0006]** Due to a rapid annual growth rate of more than 40% during the past ten years and the concurrent demands for silicon material by both semiconductor microelectronics and solar PV industries, the solar PV industry has been experiencing a shortage of polysilicon feedstock supply. The polysilicon feedstock shortage has significantly constrained the solar PV industry growth, particularly during the past several years. In fact, the solar cell industry currently consumes over half of the worldwide production of high-purity polysilicon feedstock. Within the last few years, the contract price of polysilicon has increased from roughly \$30/kg to roughly \$85/kg, with spot prices exceeding \$250/kg. This has led to large increases in the price of monocrystalline and multicrystalline silicon wafers, which now account for roughly half of the total solar module manufacturing cost.

[0007] The trend in the mainstream crystalline silicon (c-Si) wafer solar cell industry has been to scale down wafer thicknesses to below 200 microns (in order to reduce the amount of silicon material in grams used per watt of solar cell rated peak power). For example, monocrystalline silicon wafer solar cells are projected to scale down to a thickness of roughly 120 microns by 2012, from a current wafer thickness of roughly 200 microns. Multicrystalline silicon wafer solar cells are projected to scale down to a thickness of roughly 180 microns by 2012, from a current average wafer thickness of roughly 260 microns. This wafer thickness reduction, however, presents additional challenges related to mechanical rigidity, manufacturing yield, and solar cell efficiency. Despite its high cost, crystalline silicon (c-Si) technology still dominates the solar cell market, mainly due to higher efficiencies and synergies with the established microelectronics industry and supply chain. Currently, c-Si accounts for slightly over 90% of the solar cell market (95% when ribbon silicon is included).

**[0008]** Historically, crystalline silicon solar cells have achieved a 20% cost reduction for each doubling of cumulative global cell production (measured in megawatts or  $MW_p$  and gigawatts or  $GW_p$ ). It is projected that through innovative cost reduction and efficiency enhancement methods, the cost of electricity derived from grid-connected rooftop solar photovoltaic modules may become comparable to the cost of electricity purchased from the utility grid in five to ten years. A 2005 survey of the commercially available monocrystalline silicon and multicrystalline silicon solar modules reports the

solar module efficiencies then in the range of 9.1% to 16.1%, with a median efficiency value of about 12.5%. Commercial crystalline silicon modules usually show a rapid initial efficiency degradation of 1% to 3% (relative) due to various effects, including photodegradation effects in wafered solar cells (e.g., wafer minority carrier lifetime degradation). Monocrystalline silicon wafer solar cell efficiencies are projected to increase to roughly 20.5% by 2012, from a current efficiencies are currently about 21.5% and 18%, respectively). Multicrystalline silicon wafer solar cell efficiencies are projected to increase to roughly 18% by 2012, from a current efficiencies are currently about 21.5%.

[0009] State-of-the-art crystalline silicon solar cell manufacturing currently uses about 10 grams of high-purity polysilicon feedstock per peak watt ( $g/W_p$ ), resulting in a polysilicon feedstock material cost of about  $0.85/W_p$  (assuming a polysilicon price of \$85/kg). Over the next five years, the projected trends of solar cell wafer thickness reduction (e.g., to less than 200 micron wafers) and a long-term assumed price of about \$20/kg for solar-grade polysilicon may reduce the polysilicon feedstock cost (in  $g/W_p$ ) by about a factor of four to eight to about  $0.10/W_p$  to  $0.20/W_p$ . Thus, any competing solar cell technologies should benchmark their manufacturing cost goals against this reduced raw material cost number. For a given cell efficiency, silicon wafer thickness reduction presents a prime opportunity for solar cell cost reduction by reducing the amount of polysilicon feedstock consumed per watt of peak solar power.

[0010] The cost associated with wire saws, amounting to about \$0.25/W<sub>p</sub> for current silicon solar cells provides another wafer-related cost component for silicon wafer solar cells. Innovative and cost-effective technologies that eliminate the kerf losses associated with sawing and slicing should further facilitate silicon solar cell cost reductions. It is projected that the wafer-based crystalline silicon solar module manufacturing cost (which is currently on the order of \$2.10 per watt to more than \$2.70 per watt) may be reduced to the range of roughly  $1.50/W_p$  to  $1.80/W_p$  by the year 2012, in part due to wafer sawing kerf loss reduction to roughly 130 microns by 2012 from the current value of roughly 200 microns. The overall cost reductions for wafer-based crystalline silicon solar cells may come from various sources including: lower cost polysilicon feedstock, thinner wafers, higher cell-level efficiencies, reduced wafer sawing kerf losses, and increased economy of scale or manufacturing volume.

[0011] State-of-the-art silicon wafer solar cell fabrication facilities ("solar fabs") typically produce 125 mm×125 mm up to 156 mm×156 mm solar cells today. The trend in crystalline silicon wafer solar cells is toward thinner and larger wafers. The monocrystalline and cast (as well as ribbon) multicrystalline silicon solar cell wafer thicknesses in leading-edge solar cells used for power generation modules are projected to be reduced to around 150 and 200 microns, respectively, by around 2009-2010. Any cost-effective, highefficiency, innovative silicon solar cell technology which enables a substantial reduction of the silicon material consumption (e.g., wafer or film thickness) per  $W_p$  of cell power compared to the above-mentioned current and projected 2009-2010 numbers may offer significant promise as a viable commercial solar cell technology for solar photovoltaic applications (e.g., residential, commercial, and industrial rooftop as well as large-scale centralized utilities electrical power generation applications).

[0012] Higher solar cell efficiencies have favorable effects on the entire solar cell value chain and levelized cost of energy (LCOE in \$/kWh) due to reduced material consumption and cost as well as reduced balance-of-system (BOS) costs (e.g., area-related solar module installation and inverter costs). The current mainstream commercial crystalline solar cells provide efficiencies on the order of 14% to 17%. It is expected that the projected crystalline silicon solar cell efficiencies in commercial solar cells may approach around 19% and 17% for monocrystalline and multicrystalline silicon solar cells, respectively, by the year 2009. A key area for new solar cell business opportunities is development of innovative cell structures and simplified process flows which may drive efficiencies up while lowering overall solar cell and module manufacturing costs. For alternative (e.g., thin-film PV) approaches to succeed over the mainstream wafer-based crystalline silicon solar cell technologies, they should provide higher efficiencies at even lower manufacturing costs compared to the projected efficiency and cost numbers for the mainstream wafer-based crystalline silicon solar cells when the new technology is fully commercialized.

[0013] Economy-of-scale fab cost reduction associated with high-volume solar fab capacities is a key factor impacting LCOE. The state-of-the-art high-volume solar photovoltaic fabs have annual production capacities on the order of or in excess of 50 MW<sub>p</sub> to 100 MW<sub>p</sub> (MW<sub>p</sub>=1 million W<sub>p</sub>). High-volume solar photovoltaic fab capacities are expected to increase substantially to annual production rates of several hundred  $MW_p$  or even approaching 1  $GW_p$  ( $GW_p=1$  billion  $W_p$ ) in the coming decade. While very-high-volume solar fabs in the range of 100 MW<sub>n</sub> to 1 GW<sub>n</sub> should facilitate longer term cost reductions (including LCOE) through highvolume manufacturing economies of scale, the relatively high initial fab investment costs, which may easily exceed \$100M, may impose certain limits on solar photovoltaic fab construction options. Ideally, the preference may be to develop innovative crystalline silicon solar cell designs and simplified manufacturing processes which facilitate substantial manufacturing cost reductions in solar cells and modules even in smaller-scale (and less capital intensive) fabs with modest production volumes (e.g., annual production volumes in the range of 5 MW<sub>p</sub> to 50 MW<sub>p</sub>). This type of technology would allow for modest-volume solar photovoltaic fabs with modest fab setup and operation costs. Reduced fab setup and operation costs would further facilitate global proliferation of costeffective solar modules, enabling construction of a multitude of very affordable modest-volume fabs (in contrast to having to set up very expensive high-volume fabs in order to achieve sufficient economy of scale for manufacturing cost reduction). Of course, an innovative solar cell technology that meets the above-mentioned criteria for cost-effective, modest-volume fabs (i.e., meeting the LCOE roadmap requirements even at modest production volumes in low-cost fabs set up for simplified solar cell processing), may also be applicable to very-high-volume (e.g., greater than 100 MW<sub>p</sub>) solar fabs. Such solar photovoltaic fabs can take further advantage of the economies of scale associated with increased volume. [0014] Thin-film solar cell (TFSC) technologies (e.g., amorphous silicon, CdTe, and CIGS) require little absorber material (usually much less than 10 microns in thickness) to absorb typical standard "Air Mass 1.5" (AM-1.5) solar illumination due to absorption bands that are well matched to the

solar spectrum. The TFSC absorber material may be deposited on inexpensive substrates such as glass or flexible metallic or non-metallic substrates. TFSCs typically offer low cost, reduced module weight, reduced materials consumption, and a capability for using flexible substrates, but are usually much lower in efficiency (e.g., usually 5% to 12%). In the case of prior art thin crystalline silicon films, there are a number of major problems and challenges with the use of flat silicon films (such as epitaxially growth silicon films with thicknesses below 50 microns) for low-cost, high-performance solar cells. These include: relatively low solar module efficiencies (typically 7% to 12%), field degradation of module efficiencies, scarce and expensive absorber materials (e.g., In and Se for CIGS and Te for CdTe), limited validation of system field reliability, and adverse environmental impact of non-silicon technologies such as CIS/CIGS and CdTe.

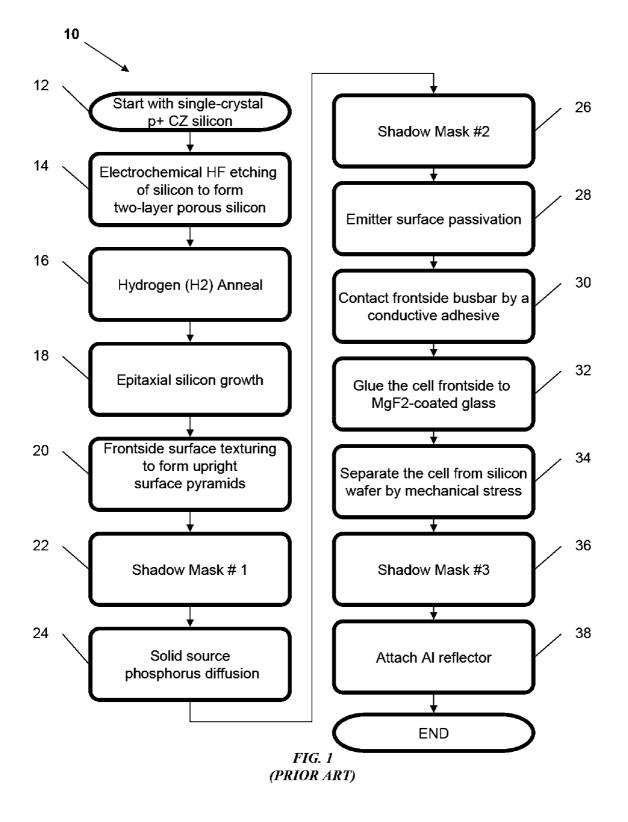

[0015] Prior art FIG. 1 shows process flow 10 for fabricating c-Si TFSCs using planar silicon thin-film absorber layers produced by epitaxial silicon. This prior art TFSC fabrication process flow uses several shadow mask process steps to form the cell structure. The cell absorber is simply a thin planar film of c-Si formed by silicon epitaxial growth processing. The cell uses frontside silicon texturing to improve light trapping and a detached rear aluminum mirror to improve the cell efficiency. Step 12 starts with single-crystal p<sup>+</sup> CZ silicon. Step 14 involves electrochemical HF etching of silicon to form 2-layer porous silicon comprising a 1 micron top layer with 20% porosity and a 200 nanometer rear layer with greater than 50% porosity. Step 16 involves a hydrogen (H<sub>2</sub>) anneal at 1100° C. for 30 minutes. Step 18 involves epitaxial silicon growth at 1100° C. using trichlorosilane or SiHCl<sub>3</sub> (deposition rate of 1 micron per minute), forming 2 microns of p<sup>+-</sup>Si and 30 microns of p-Si. Step 20 involves frontside surface texturing by wet KOH etching to form upright surface pyramids. Step 22 involves the first shadow mask process, with LPCVD silicon nitride  $(SiN_x)$  deposition through a shadow mask to define emitter diffusion windows. Step 24 involves solid source phosphorus diffusion at 830° C. (to achieve 80  $\Omega$ /square for the n<sup>+</sup> doped junction). Step 26 involves the second shadow mask process, with frontside metallization (titanium/Pd/silver grid) by evaporation through shadow mask. Step 28 involves emitter surface passivation by hydrogenated PVD or PECVD SiN, Step 30 involves contact frontside busbar by a conductive adhesive. Step 32 involves gluing the cell frontside to MgF<sub>2</sub>-coated glass using clear glue. Step 34 involves separating the cell from silicon wafer by mechanical stress. Step 36 involves the third shadow mask process, with backside aluminum metallization using evaporation through shadow mask. Finally, step 38 involves attaching an aluminum reflector at 200 micron spacing from the cell backside.

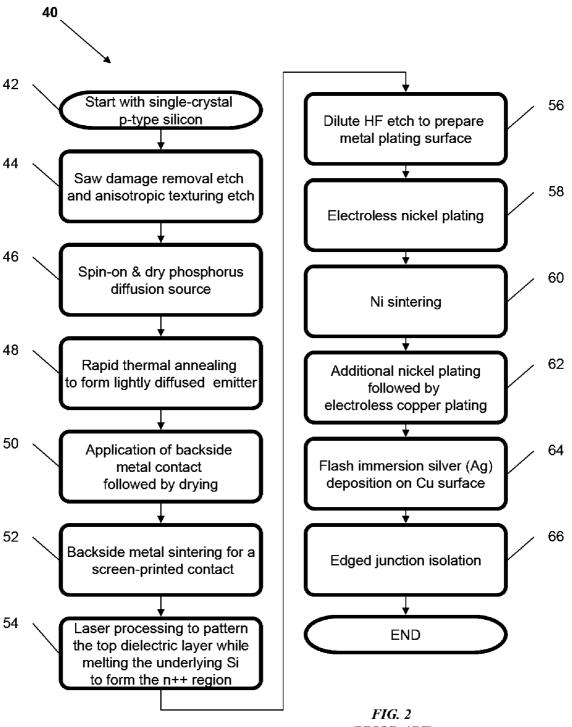

**[0016]** Prior art FIG. **2** shows another process flow method **40** for fabrication of solar cells on silicon wafers with selfaligned selective emitter and metallization. This prior art process uses laser processing to pattern the top cell dielectric layer while melting the underlying silicon to form the heavily-doped n<sup>++</sup> emitter contact diffusion regions (after formation of the lightly diffused selective emitter regions by rapid thermal annealing). Step **42** starts with single-crystal p-type silicon. Step **44** involves saw damage removal etch and anisotropic texturing etch in dilute NaOH at 90° C. Step **46** involves spin-on application and drying of phosphorus diffusion source. Step **48** involves rapid thermal annealing to form lightly diffused emitter (80 to 200  $\Omega$ /square). Step **50** involves application of backside metal contact by vacuum evaporation or screen printing of aluminum or silver/aluminum alloy, followed by drying. Step 52 involves backside metal sintering/firing (e.g., at 820° C. in oxygen/nitrogen) for a screenprinted contact (fires the metal paste while oxidizing the dielectric to raise its resistance to the metal plating solution). Step 54 involves laser processing to pattern the top dielectric layer while melting the underlying silicon to form the n<sup>++</sup> contact diffusion region. Step 56 involves dilute HF etch to prepare metal plating surface. Step 58 involves electroless nickel plating at 90° C. for five minutes. Step 60 involves nickel sintering at 350° C. to 450° C. (in nitrogen, argon, or forming gas). Step 62 involves an additional 2 minutes of nickel plating followed by long electroless copper plating to form thick high-conductivity copper film. Step 64 involves flash immersion silver (silver) deposition on copper surface. Finally, step 66 involves edged junction isolation (e.g., using laser grooving, edge cleavage, or plasma etching).

[0017] With regard to the prior art crystalline silicon (c-Si) thin-film solar cell (TFSC) technology, there are difficulties associated with sufficient surface texturing of the thin silicon film to reduce surface reflectance losses, while reducing the crystalline silicon film thickness. This places a limit on the minimum flat (co-planar) monocrystalline silicon thickness due to production yield and cell performance (efficiency) considerations. In the case of a flat or co-planar film, it is essential to use surface texturing since the reflectance of an untextured crystalline silicon film is quite excessive (can be greater than 30%) and results in substantial optical reflection losses and degradation of the external quantum efficiency. Thus, reduction of reflectance-induced photon losses in coplanar epitaxial silicon films requires effective surface texturing which itself places a limit on the minimum epitaxial silicon layer thickness. Depending on the film surface texturing requirements and processes, the minimum crystalline silicon layer thickness may be on the order of at least 10 microns (so that the texturing process does not break through any portions of the crystalline silicon layer).

[0018] In addition, substantially reduced mean optical path lengths in thin planar crystalline silicon films result in reduced photon absorption, particularly for photons with energies near the infrared bandgap of silicon (800 to 1100 nanometers), resulting in reduced solar cell quantum efficiency (reduced short-circuit current or  $J_{sc}$ ). This results in serious degradation of the solar cell efficiency due to reduced cell quantum efficiency and reduced J<sub>sc</sub>. For instance, in a co-planar (flat) crystalline silicon absorber layer with thickness of 20 microns, a solar light beam impacting the cell at a near-normal angle would have an effective path length equal to the film thickness, far too short for the solar radiation photons with energies near the infrared bandgap of silicon (i.e., with wavelengths of roughly 800 to 1100 nanometers) to be absorbed effectively in the silicon thin film. In fact, a reduction of the active cell silicon thickness to below roughly 50 microns results in appreciable reduction of  $J_{sc}$  and the resulting solar cell efficiency, with this degradation effect rapidly accelerating when the silicon film thickness is reduced below roughly 20 microns. Thus, a co-planar thin crystalline silicon film may also require effective light trapping using both top surface texturing and rear surface back reflection of the light exiting the back surface of the crystalline silicon film in order to create effective optical path lengths equal to a large multiple of the crystalline silicon film thickness.

**[0019]** The prior art technologies using this approach mostly use either back reflection through internal reflection of the light at the crystalline silicon film/silicon substrate, or reflection from a blanket backside contact (such as a back surface field aluminum contact/mirror). The back reflectance provided by these techniques may not be great (e.g., roughly 70% effective near-IR rear reflectance), constraining the performance gain that would have otherwise been achieved by an optimal back reflector. The problem with this approach is that the primary incident beam always passes the crystalline silicon film only once. Any subsequent second passes of the primary incident beam photons are dependent on the back surface reflection.

[0020] There is also the problem of lack of rigidity and mechanical support of the thin film during cell and module processing steps. This problem relates to the mechanical strength of a large-area (e.g., 200 mm×200 mm) thin silicon film. It is well known that reducing the large-area crystalline silicon wafer thickness to below 100 microns results in a substantial loss of cell substrate mechanical strength/rigidity, and such thin wafers tend to be flexible and very difficult to handle without breakage during cell fabrication process flow. [0021] Large-area, co-planar (flat) crystalline silicon films thinner than, for instance, 50 microns must be properly mounted and supported on a cost-effective support or handle substrate in order to achieve acceptable yield for solar cell and module manufacturing. One approach is to grow and retain the thin epitaxial film on a relatively low-cost (e.g., metallurgical-grade) silicon substrate (over which the epitaxial layer is grown); however, this approach suffers from some inherent problems constraining the ultimate solar cell efficiency. Another approach is to release or lift off the epitaxial silicon film from its (reusable) parent silicon substrate and subsequently place it on a cheaper non-silicon support or handle substrate to provide mechanical strength through the solar cell process flow. This approach may suffer from any thermal coefficient of expansion (TCE) mismatch between the support/handle substrate and silicon film during any high-temperature oxidation and anneal processes, as well as potential contamination of the thin epitaxial silicon film from the nonsilicon support substrate (both creating possible manufacturing yield and performance/efficiency degradation problems).

[0022] The cost of the monocrystalline silicon film growth process using silicon epitaxy, particularly for thicker epitaxial films with thicknesses in excess of 30 microns is an additional issue which should be addressed. Using a relatively small epitaxial film thickness (in one embodiment, much below 30 microns) may lower the cost of epitaxy to an attractive range. However, this would present various challenges for fabrication of planar silicon thin-film solar cells. As stated, thinner co-planar (flat) epitaxial films (e.g., in the range of much less than 30 microns) produce a number of problems and challenges, including a lack of film mechanical strength, constraints limiting effective surface texturing of thin silicon films for low surface reflectance and reduced optical reflectance losses, relatively short optical path lengths, and reduced cell quantum efficiencies. Effective light trapping is essential for enhanced thin-film c-Si solar cell efficiencies. The requirement for effective light trapping is based on a combination of front surface texturing and back surface mirror, while achieving sufficiently low surface recombination velocities (for high cell efficiencies). This is very difficult to achieve in the co-planar (flat) c-Si thin film solar cells.

**[0023]** High-performance c-Si thin-film solar cells require some patterning steps or patterned processing steps (e.g., for formation of selective emitter, frontside emitter or backside emitter wrap-through metallization contacts, backside base metallization contacts, etc.). These patterning steps are usually achieved using photolithography, screen printing, and/or shadow-mask deposition (e.g., shadow-mask sputtering or evaporation) processes. The use of photolithography and/or screen printing and/or shadow-mask deposition patterning steps usually increases the manufacturing process flow complexity and cost, and may also detrimentally impact the fabrication yield as well as the ultimate achievable solar cell efficiency.

**[0024]** Therefore a need has arisen for a thin-film solar cell (TFSC) which corrects the problems identified above.

**[0025]** Yet a further need exists to address shortcomings of existing mainstream c-Si solar cell technology. This includes reducing the amount of polysilicon feedstock consumed per peak watt of solar power, and eliminating the kerf losses associated with sawing and slicing; thus, substantially reducing the overall solar cell manufacturing cost.

**[0026]** A further need exists for innovative solar cell structures and simplified process flows, increasing cell and module efficiencies while significantly lowering the overall solar cell and module manufacturing costs. A still further need exists for innovative c-Si solar cell designs and simplified self-aligned manufacturing processes which facilitate substantial solar cell and module cost reduction even in fabs with modest production volumes, enabling low to mid-volume solar cell fabs with modest fab setup and operation costs (thus, achieving economies of scale for manufacturing cost reduction at substantially lower fab volumes than the prior art fabs).

[0027] A still further need exists to address shortcomings of existing TFSC technology. This includes addressing difficulties associated with sufficient surface texturing of the thin planar silicon films to reduce surface reflectance losses, which currently places a limit on the minimum flat (co-planar) crystalline silicon thickness due to production yield and cell performance considerations. A still further need exists for effective light trapping based on a combination of front surface texturing and back surface mirror, while achieving low surface recombination velocities (for high cell efficiencies). [0028] A still further need exists to address additional shortcomings of existing TFSC technologies. This includes the problem of lack of rigidity and mechanical support of the thin film substrate during cell and module processing steps, thus, necessitating the use of support or handle substrates (made of silicon or another material) for the TFSC substrates. This further includes the cost of the epitaxial silicon film growth process, particularly for thicker epitaxial films required for planar crystalline silicon TFSCs. This further includes the requirement of multiple photolithography and/or screen printing and/or shadow-mask processing/patterning steps which usually increase the manufacturing process flow complexity and cost, and may also detrimentally impact the fabrication yield as well as the ultimate achievable solar cell efficiency.

### SUMMARY

**[0029]** In accordance with the present disclosure, a template is provided which may be used to form a pyramidal three-dimensional thin-film solar cell substrate (3-D TFSC substrate). The 3-D TFSC substrates may be used to form pyramidal three-dimensional thin-film solar cells (3-D

5

TFSCs) and modules, substantially eliminating or reducing disadvantages and problems associated with previously developed semiconductor wafer-based solar cells as well as TFSCs, both in terms of conversion efficiency as well as cell and module manufacturing costs.

**[0030]** According to one aspect of the disclosed subject matter, there is a provided a template for pyramidal 3-D TFSC substrate formation. The template comprises a template substrate; the template substrate comprises a plurality of posts and a plurality of pyramid trenches between said plurality of posts. The template forms an environment for pyramidal 3-D TFSC substrate formation.

**[0031]** The template is preferably reused to fabricate a plurality of 3-D TFSC substrates without a need for substantial reconditioning of the template.

**[0032]** According to another aspect of the disclosed subject matter, there is a provided a method for fabrication of a template for pyramidal 3-D TFSC substrate formation. The method comprises removing semiconductor material from select regions of a semiconductor substrate to form a plurality of posts and a plurality of trenches.

**[0033]** More specifically, the disclosed subject matter includes removing semiconductor material from select regions of a semiconductor substrate by the steps of lithography patterning to produce a design on the semiconductor substrate and transferring the design onto the semiconductor substrate using an etching process.

**[0034]** More specifically, the disclosed subject matter includes removing semiconductor material from select regions of a semiconductor substrate by laser micromachining to produce a design on said semiconductor substrate.

**[0035]** These and other advantages of the disclosed subject matter, as well as additional novel features, will be apparent from the description provided herein. The intent of this summary is not to be a comprehensive description of the claimed subject matter, but rather to provide a short overview of some of the subject matter's functionality. Other systems, methods, features and advantages here provided will become apparent to one with skill in the art upon examination of the following FIGURES and detailed description. It is intended that all such additional systems, methods, features and advantages be included within this description, be within the scope of the accompanying claims.

#### BRIEF DESCRIPTIONS OF THE DRAWINGS

**[0036]** The features, nature, and advantages of the disclosed subject matter may become more apparent from the detailed description set forth below when taken in conjunction with the drawings in which like reference characters identify correspondingly throughout and wherein:

**[0037]** FIG. **1** (PRIOR ART) shows a prior art process flow for fabricating crystalline silicon (c-Si) thin-film solar cells (TFSCs) using planar silicon thin-film absorber layers produced by silicon epitaxy;

**[0038]** FIG. **2** (PRIOR ART) shows a prior art process flow for fabrication of solar cells on silicon wafers including selfaligned selective emitter and metallization;

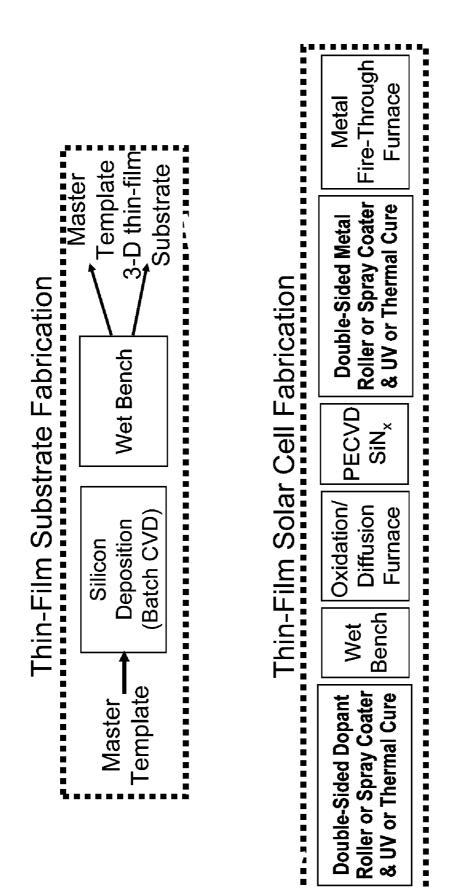

**[0039]** FIG. **3** provides an overview of the 3-D TFSC substrate and solar cell fabrication process flow;

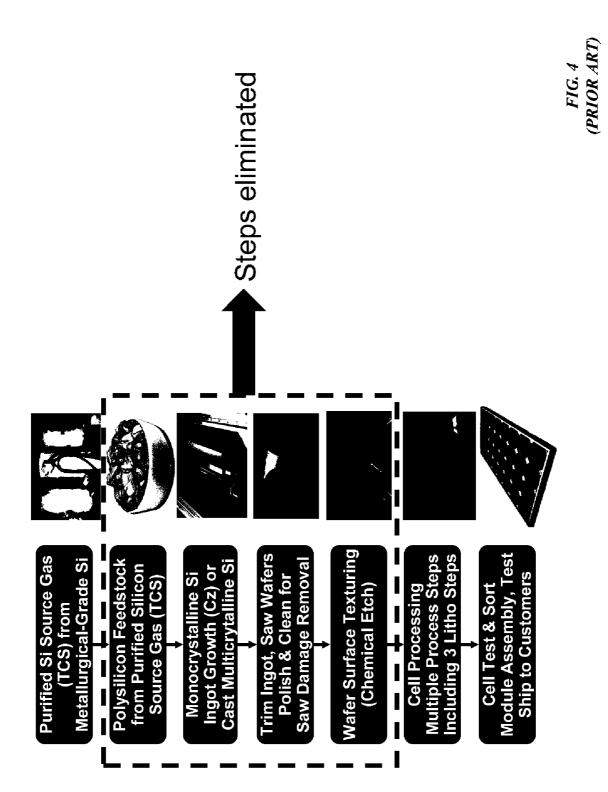

**[0040]** FIG. **4** (PRIOR ART) summarizes the key process steps eliminated by the current disclosure, compared to the prior art;

**[0041]** FIG. **5** summarizes the high-level process flow and the competitive advantages of the current disclosure, compared to the prior art;

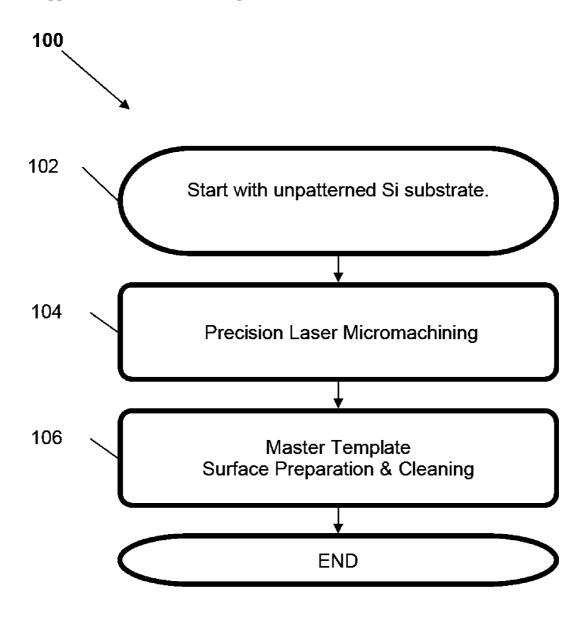

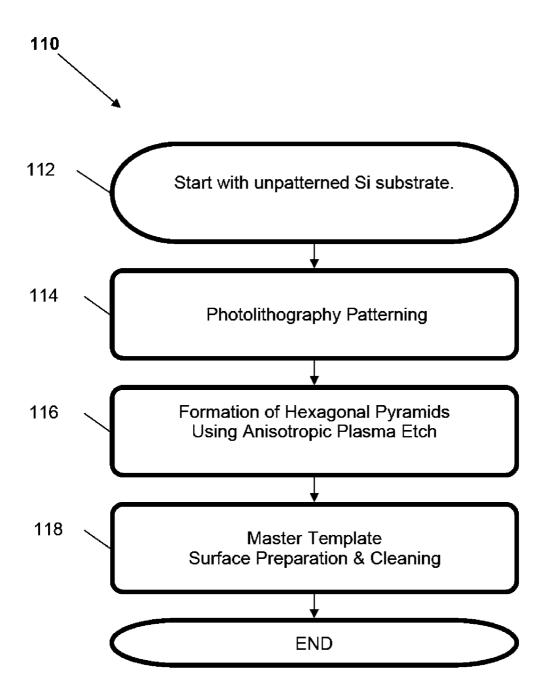

**[0042]** FIGS. **6** and **7** outline embodiments of process flows for fabrication of a template using either direct laser micromachining or photolithography patterning;

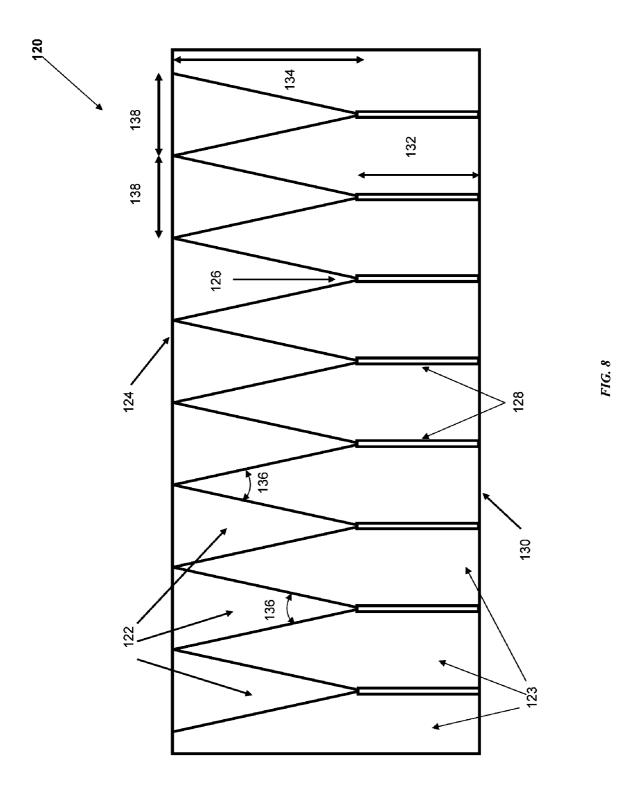

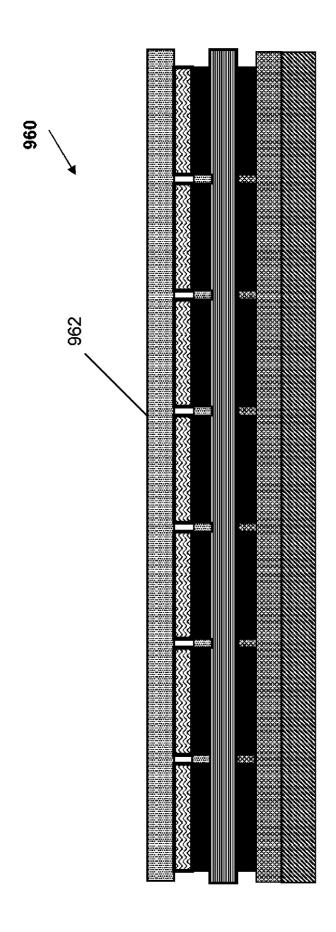

**[0043]** FIG. **8** shows a Y-Y cross-sectional view of an embodiment of a template;

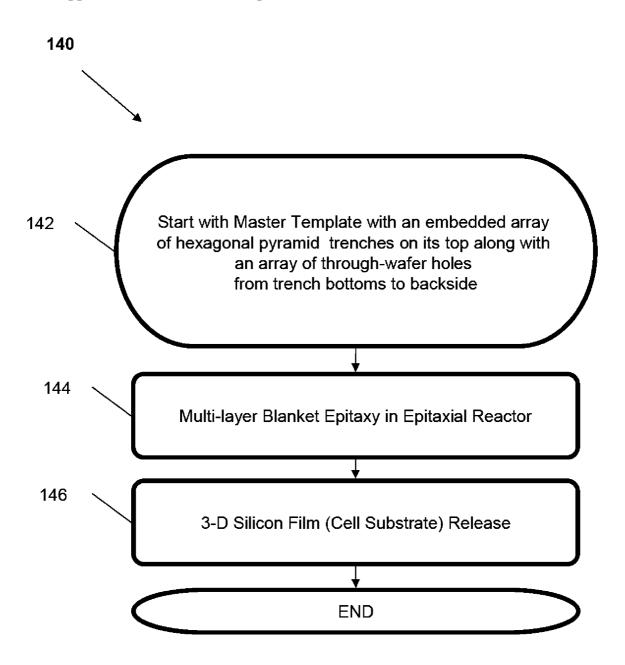

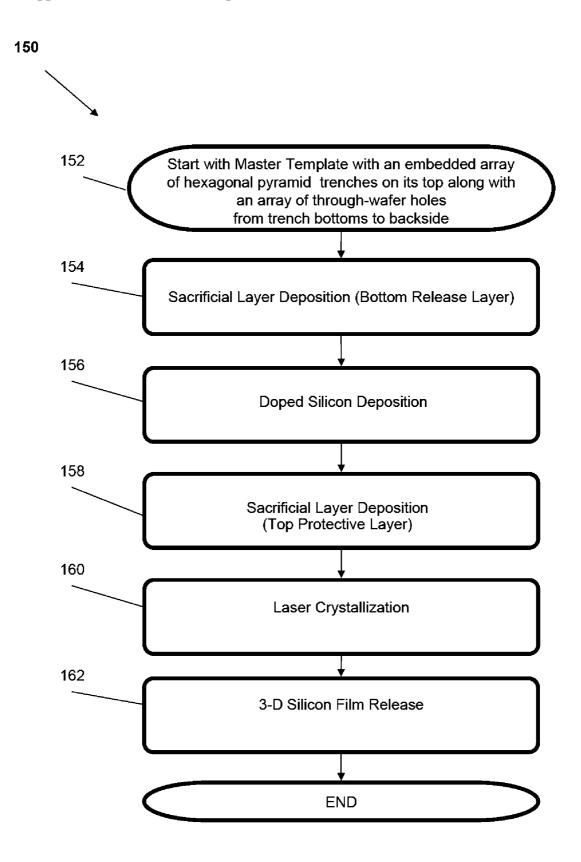

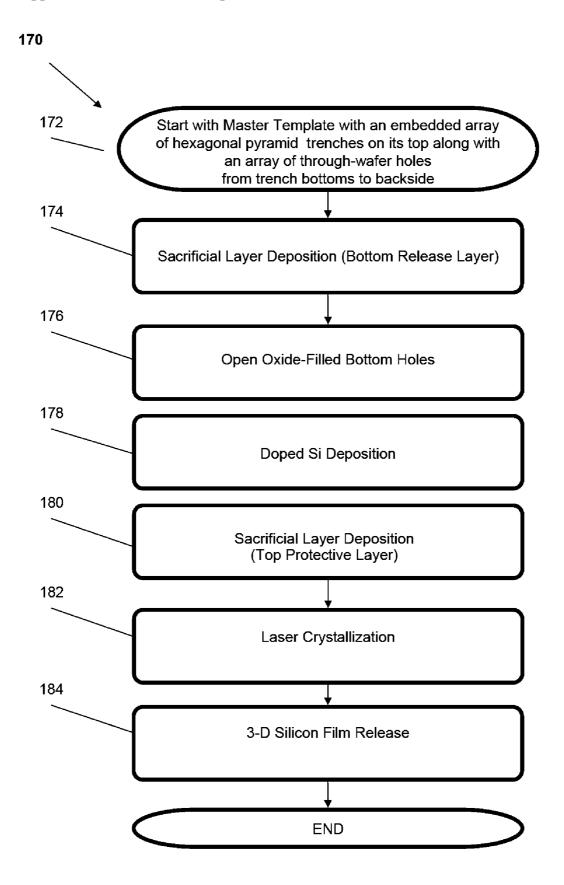

**[0044]** FIGS. **9** through **12** show embodiments of process flows for fabrication of pyramidal 3-D TFSC substrates;

**[0045]** FIGS. **13** and **14** show the Y-Y and Z-Z cross-sectional axes on an embodiment of a hexagonal-pyramidal (honeycomb) 3-D TFSC substrate;

**[0046]** FIG. **15** shows a 3-D view of a single unit cell in a hexagonal-pyramidal 3-D TFSC substrate;

**[0047]** FIG. **16** shows a schematic ZZ cross-sectional-view of an embodiment of a 3-D hexagonal-pyramid TFSC substrate;

**[0048]** FIG. **17** shows a schematic YY cross-sectional-view of an embodiment of a 3-D hexagonal-pyramid TFSC substrate;

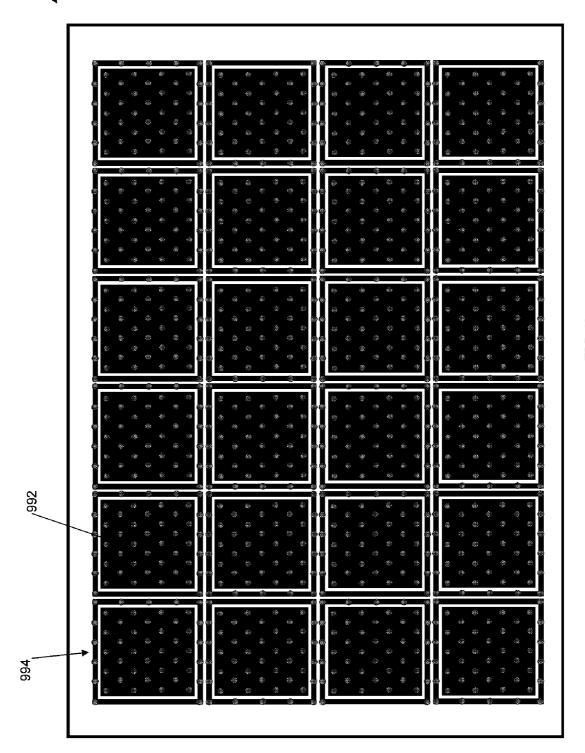

**[0049]** FIG. **18** shows a top view of a honeycomb hexagonal-pyramid array design TFSC substrate, with a peripheral planar silicon frame;

**[0050]** FIG. **19** shows a YY cross-sectional view of an embodiment of a 3-D self-supporting hexagonal-pyramid TFSC substrate with thin square-shaped silicon frame;

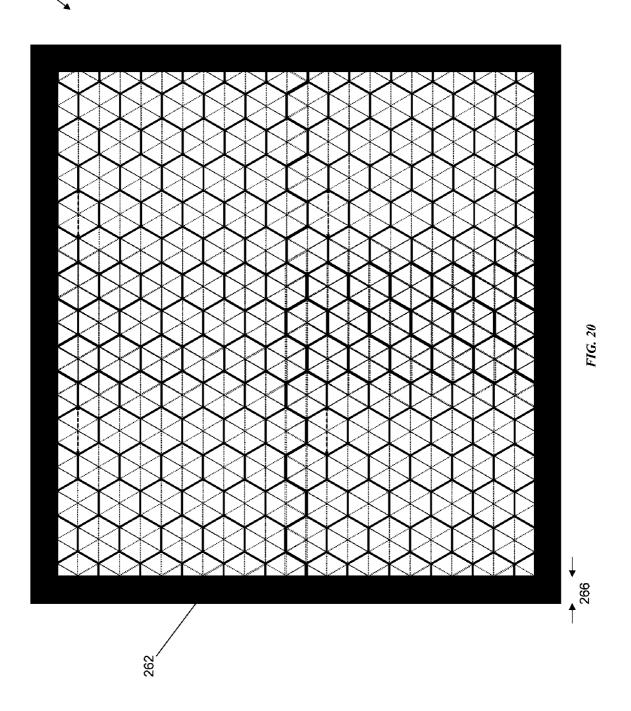

**[0051]** FIG. **20** shows a top view of an alternative honeycomb hexagonal-pyramid array design TFSC substrate, with a larger thickness peripheral planar frame;

**[0052]** FIG. **21** shows a YY cross-sectional view of an embodiment of a 3-D self-supporting hexagonal-pyramid TFSC substrate with thick square-shaped silicon frame;

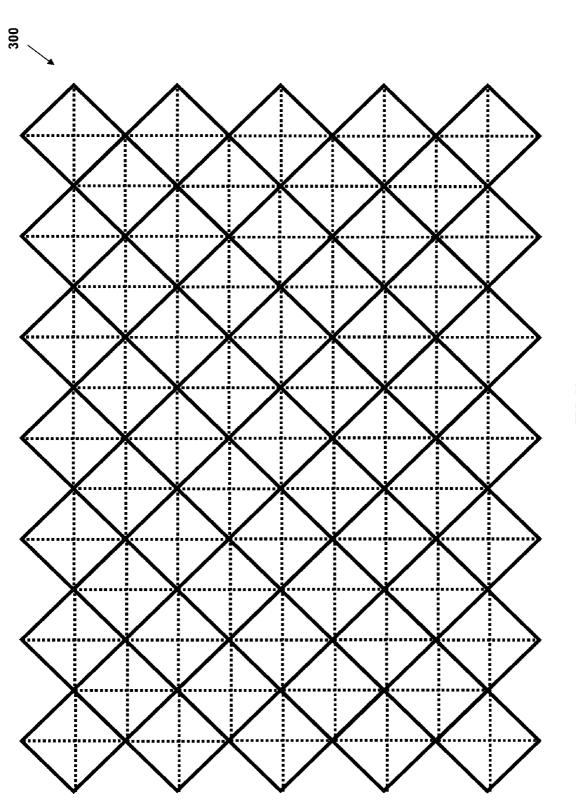

**[0053]** FIG. **22** shows a top view of a 3-D TFSC substrate with a square-pyramid unit cell structure;

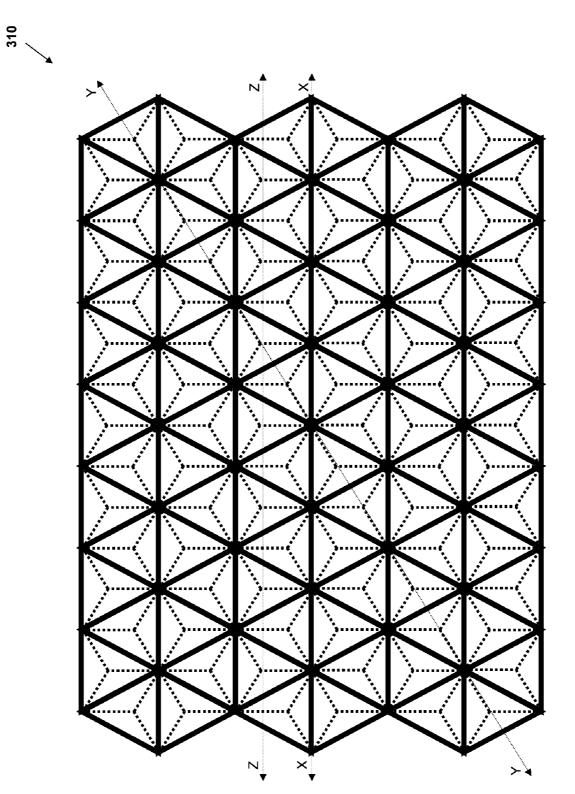

**[0054]** FIG. **23** shows a top view of a 3-D TFSC substrate with a triangular-pyramid unit cell structure;

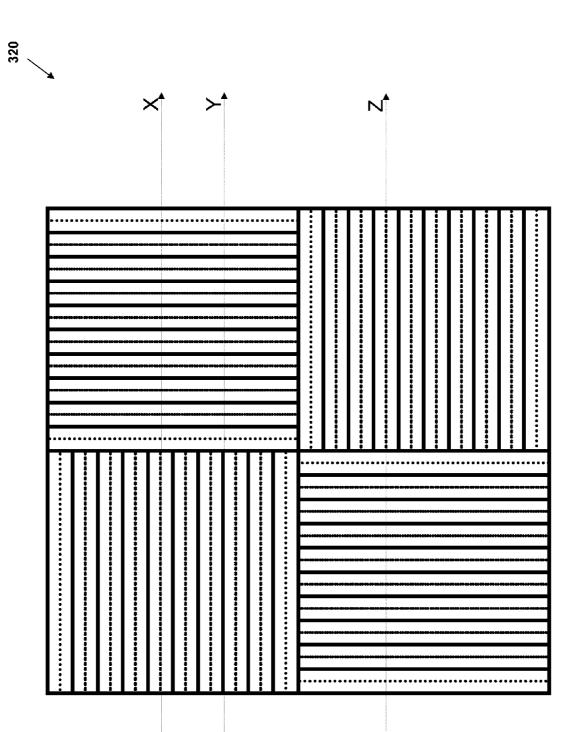

**[0055]** FIG. **24** shows a top view of a 3-D TFSC substrate with an orthogonal V-groove unit cell structure;

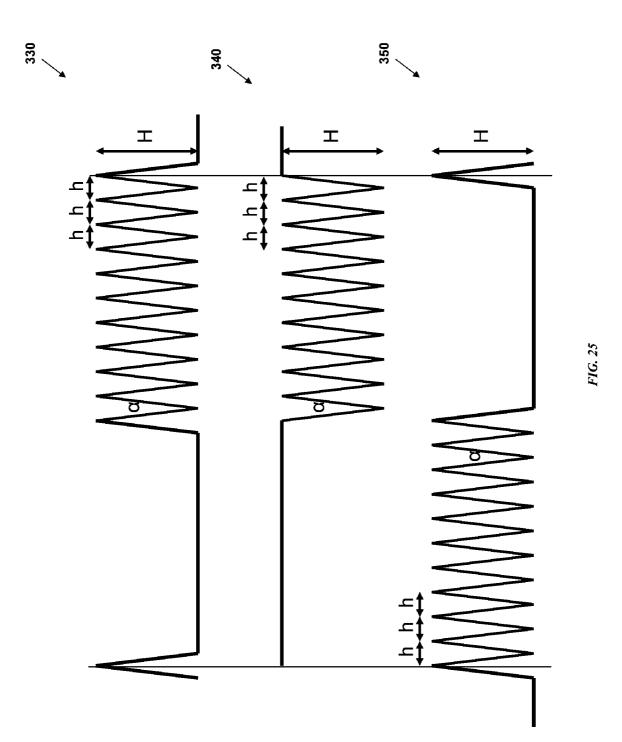

**[0056]** FIG. **25** shows alternative cross sectional views of the 3-D TFSC substrate with an orthogonal V-groove unit cell structure, shown in FIG. **24**;

**[0057]** FIG. **26** shows a top view of a 3-D TFSC substrate with an alternative orthogonal diagonal V-groove unit cell structure;

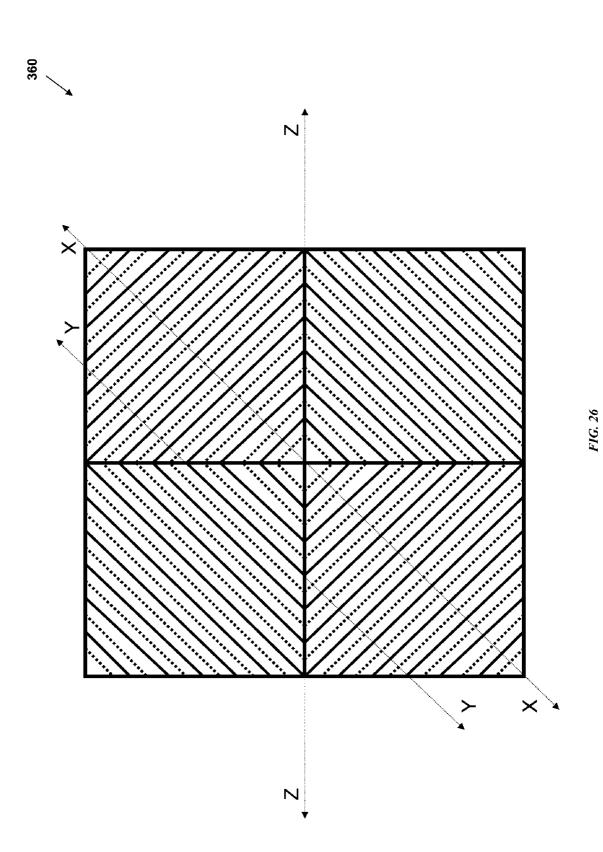

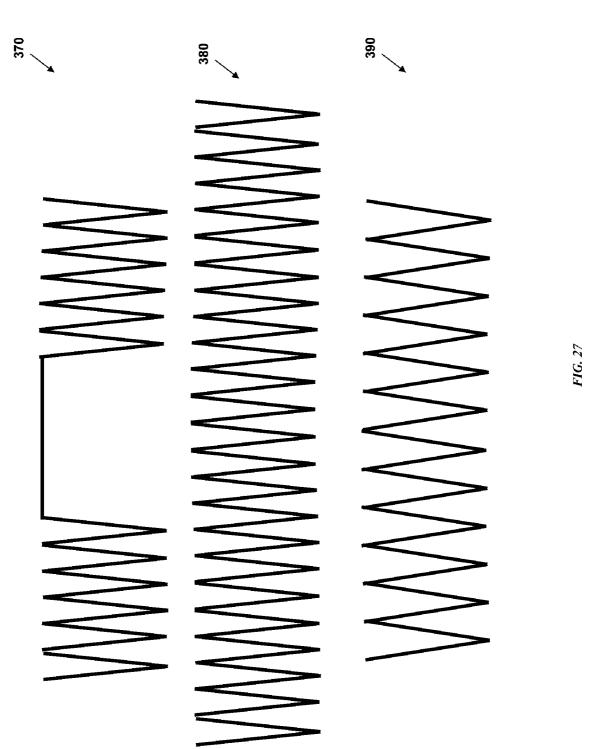

**[0058]** FIG. **27** shows alternative cross sectional views of the 3-D TFSC substrate with an orthogonal diagonal V-groove unit cell structure, shown in FIG. **26**;

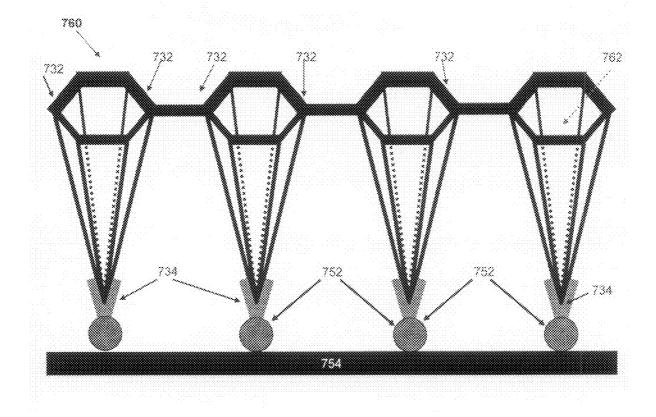

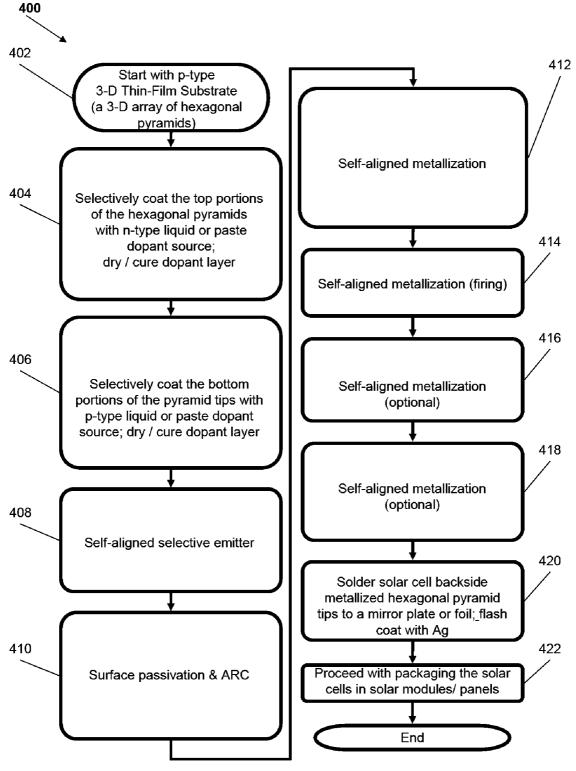

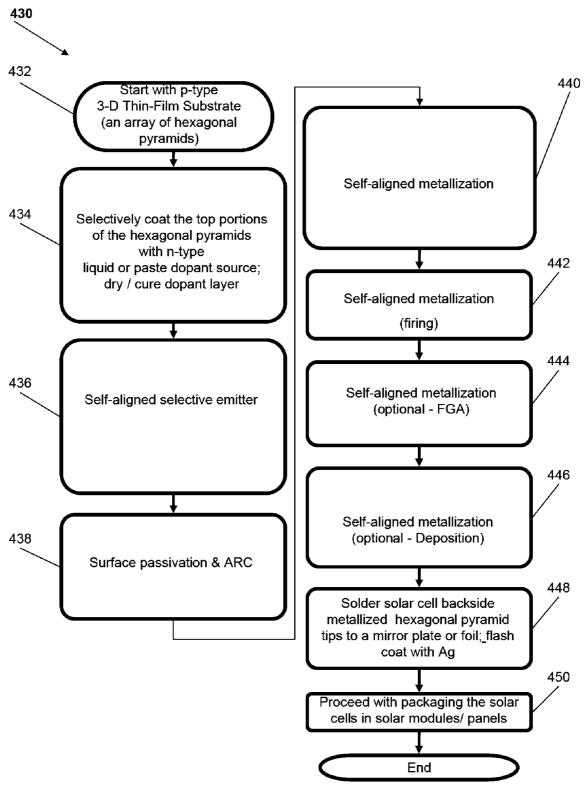

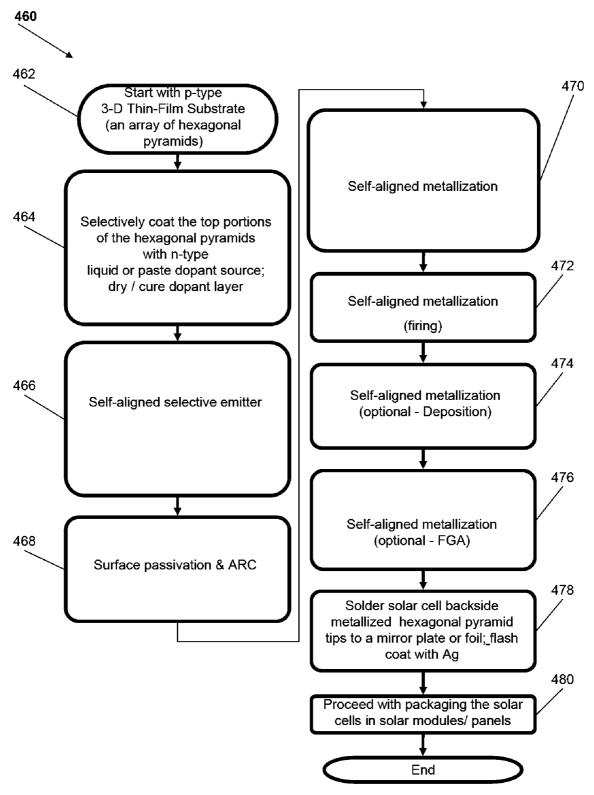

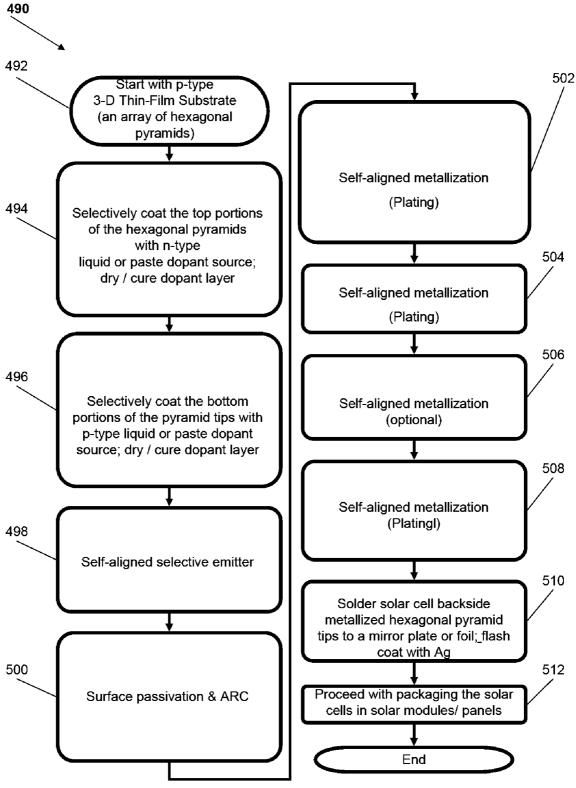

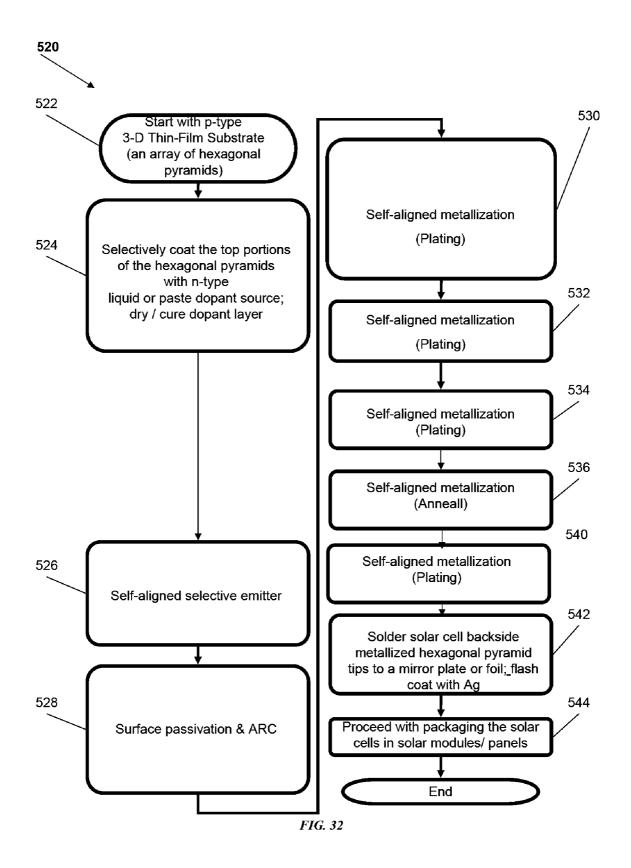

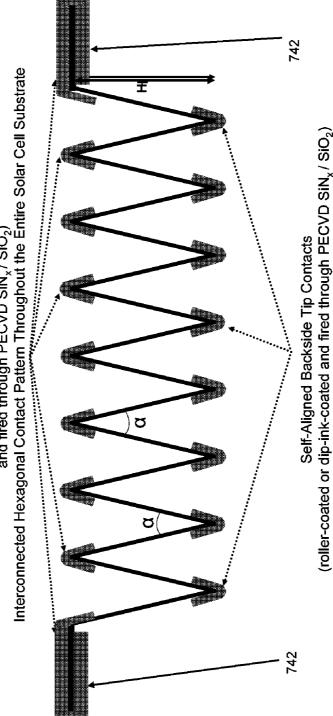

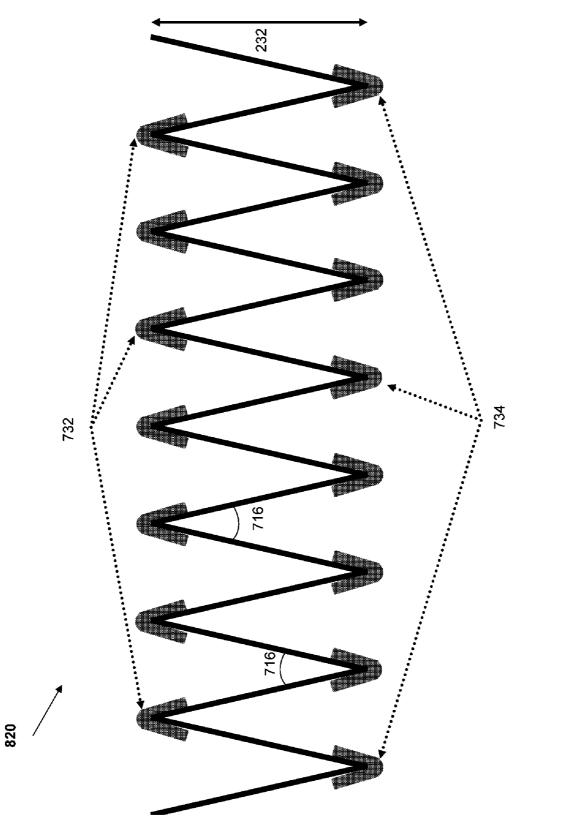

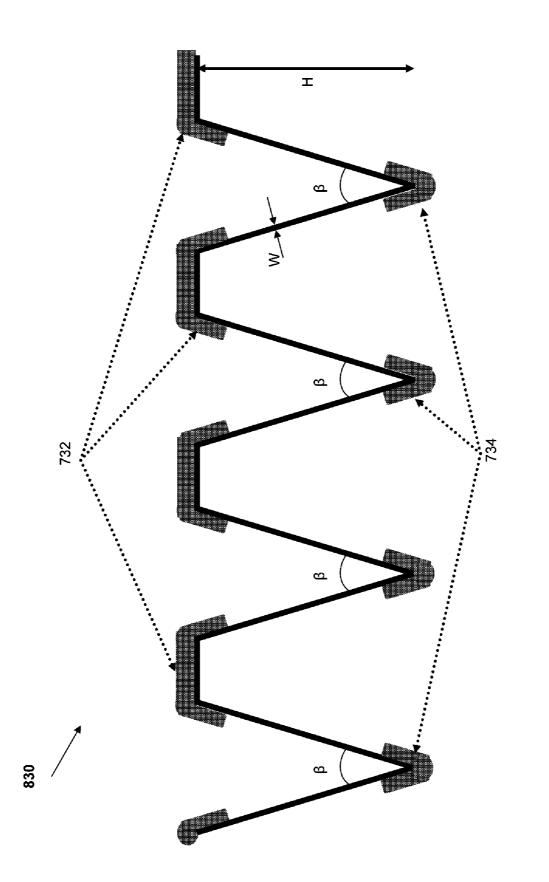

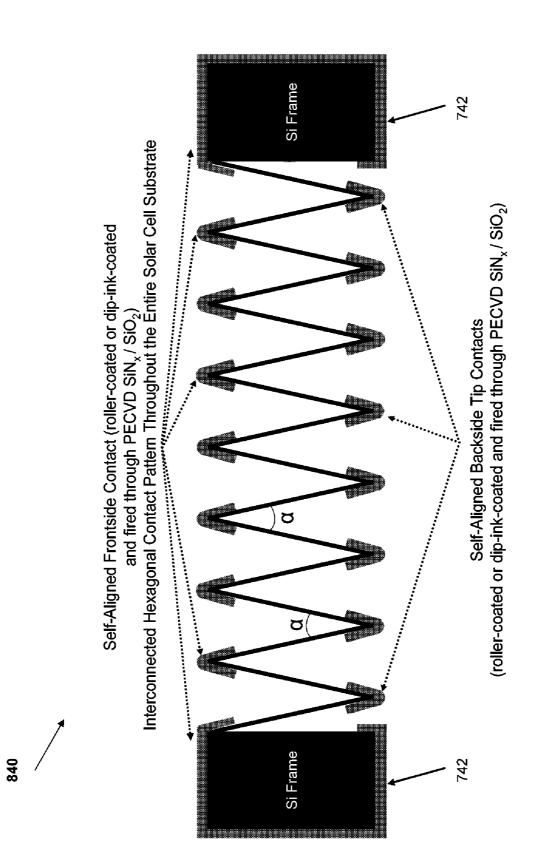

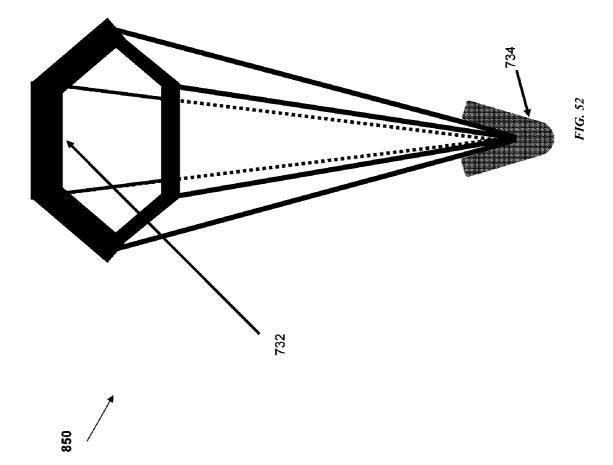

**[0059]** FIGS. **28** through **30** describe process flows for fabrication of a 3-D TFSC using fire-through metallization;

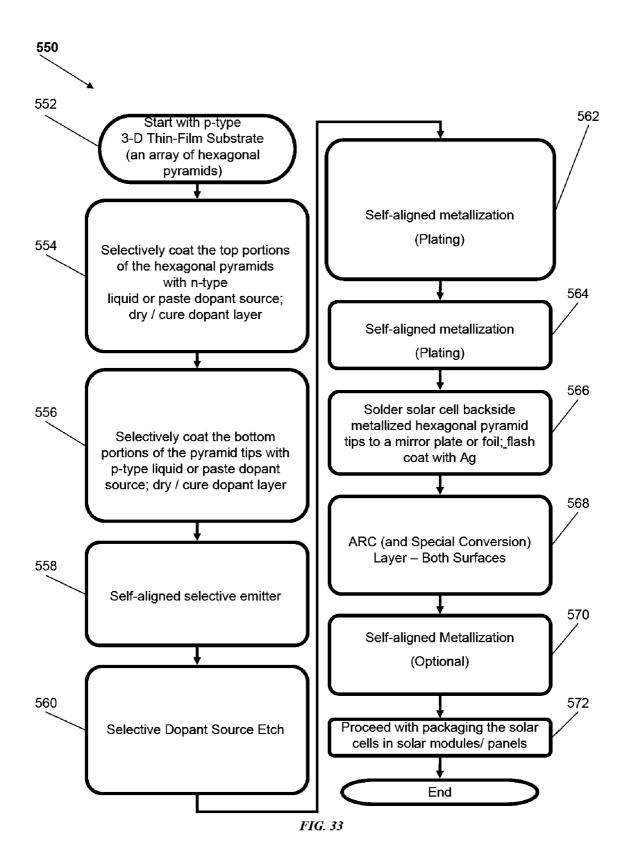

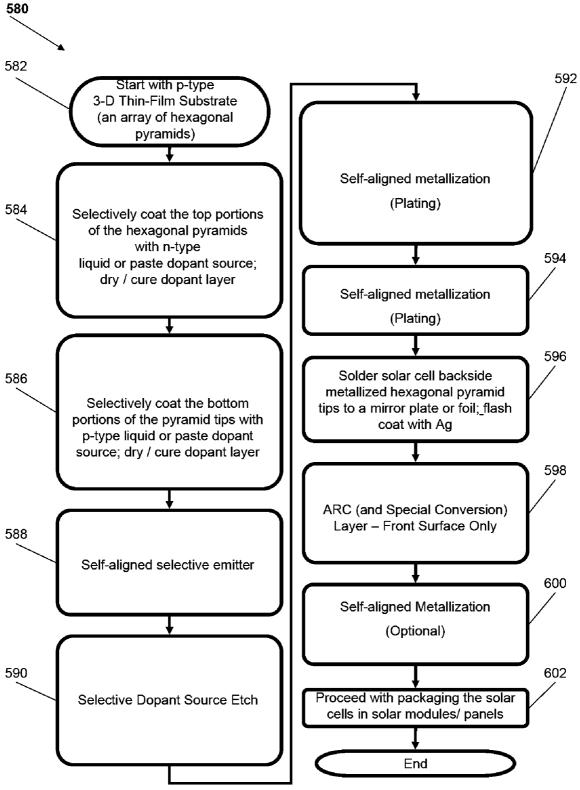

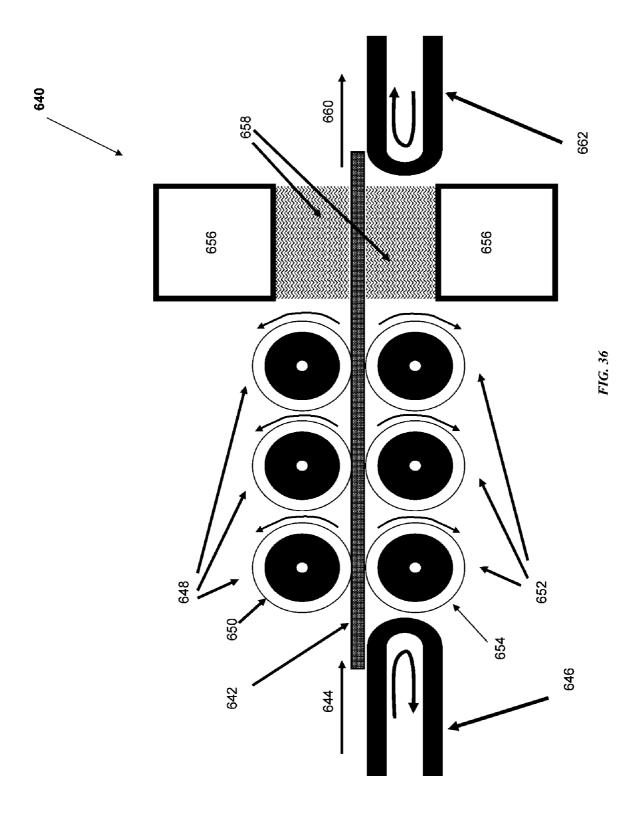

**[0060]** FIGS. **31** through **35** describe process flows for fabrication of a 3-D TFSC using selective plating metallization;

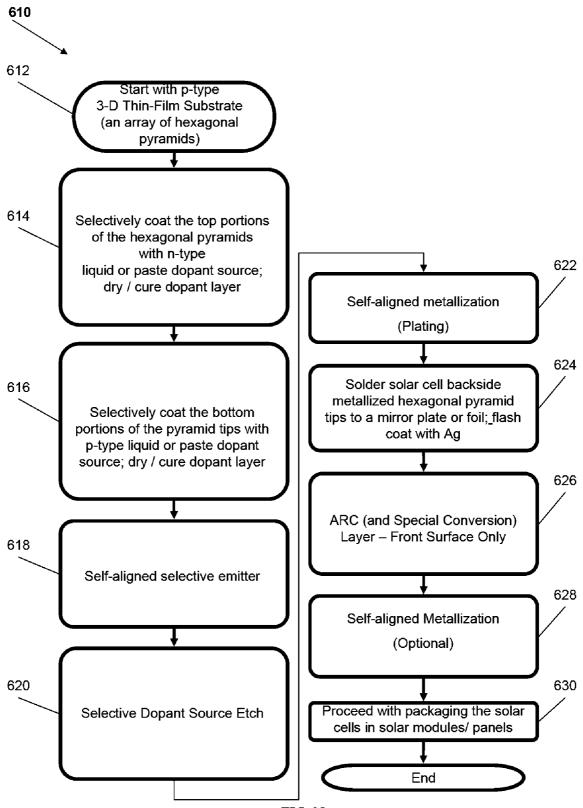

**[0061]** FIG. **36** shows a schematic view of a double-sided coater setup for self-aligned application (coating) of dopant liquid or paste layers on 3-D TFSC substrate top ridges and rear surface or ridges by roller coating and in-line curing of the applied liquid/paste layers (shown in conjunction with an integrated belt-driven process equipment);

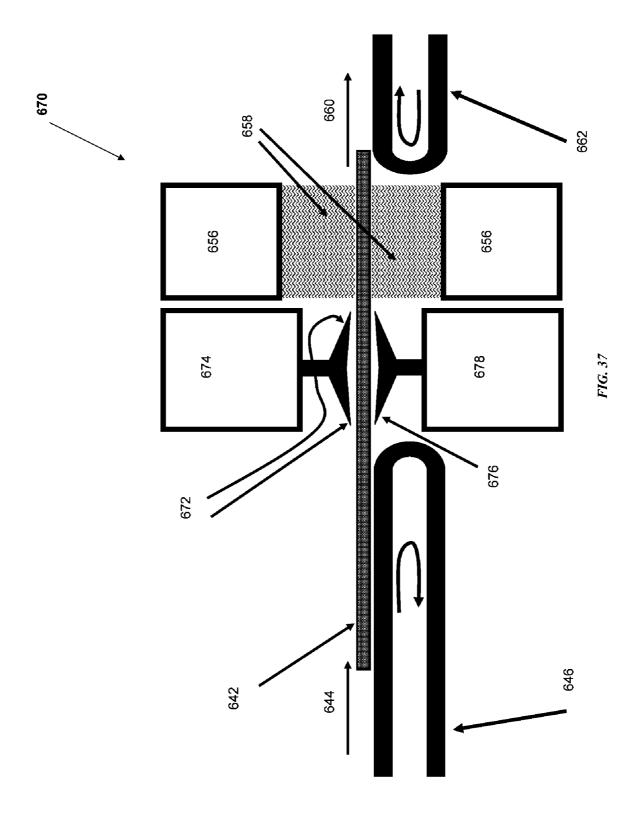

[0062] FIG. 37 shows a view of an alternative spray coater and curing setup to perform the same processes as the roller coater and curing setup of FIG. 36;

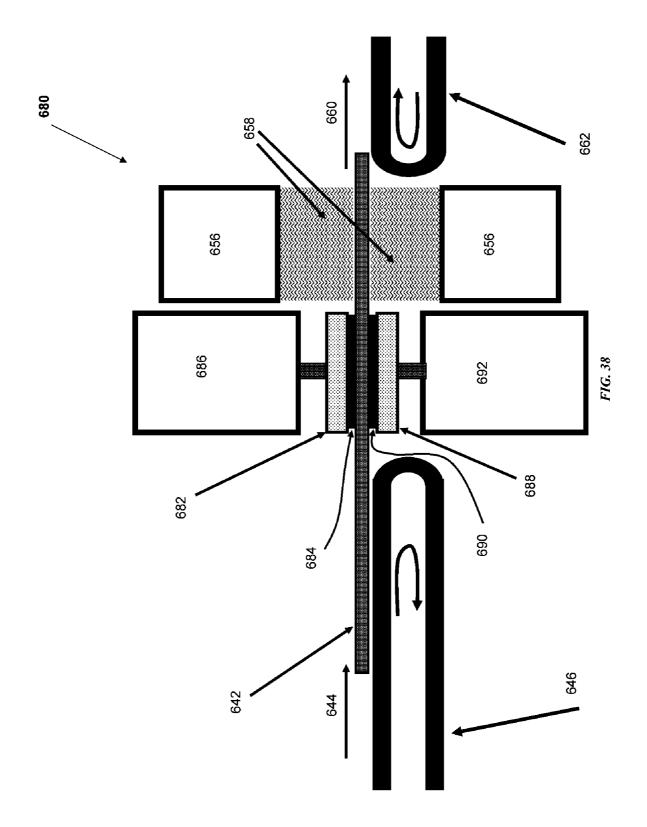

**[0063]** FIG. **38** shows a view of another alternative setup design using liquid-dip coating or liquid-transfer coating to

perform the same processes as the roller coater and curing setup of FIG. **36** and the spray coater and curing setup of FIG. **37**;

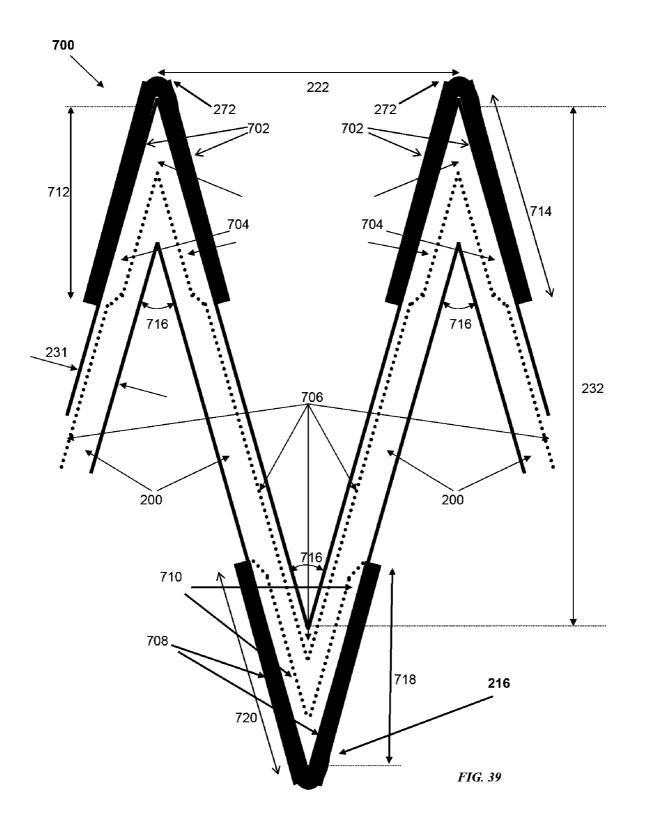

**[0064]** FIG. **39** shows a cross-sectional view of a 3-D substrate (showing one of the hexagonal-pyramid cells) after the above-mentioned doping process step;

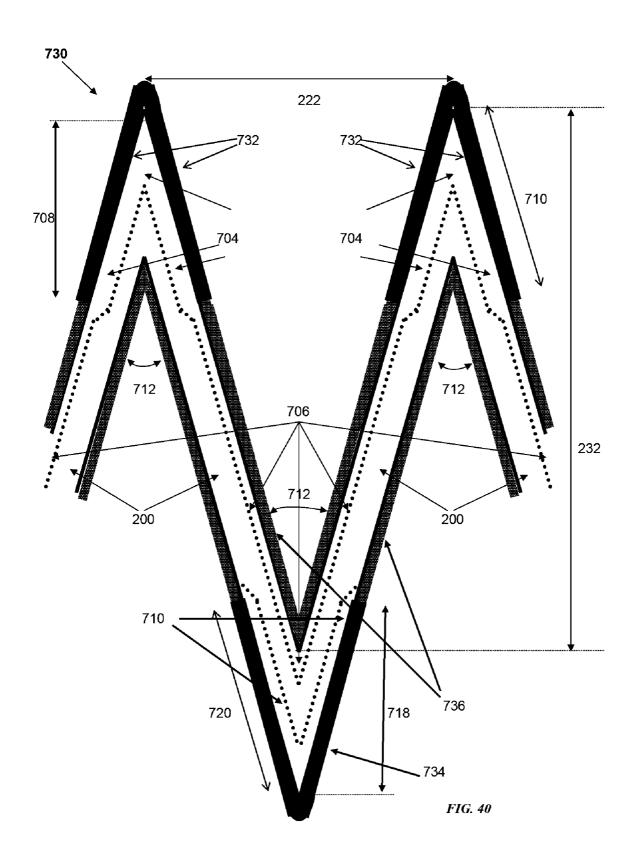

**[0065]** FIGS. **40** and **41** show YY cross-sectional views after self-aligned formation of the emitter and base contacts and solar cell interconnects;

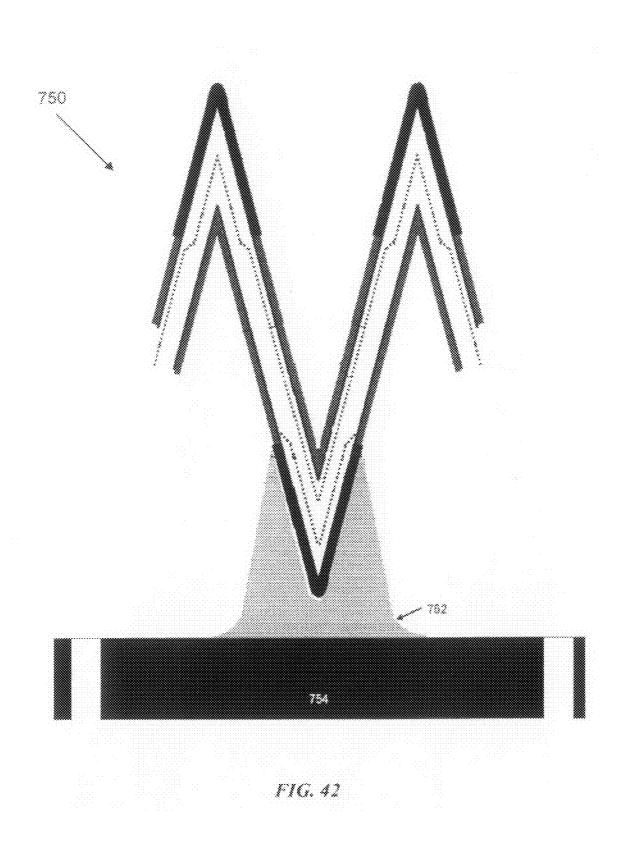

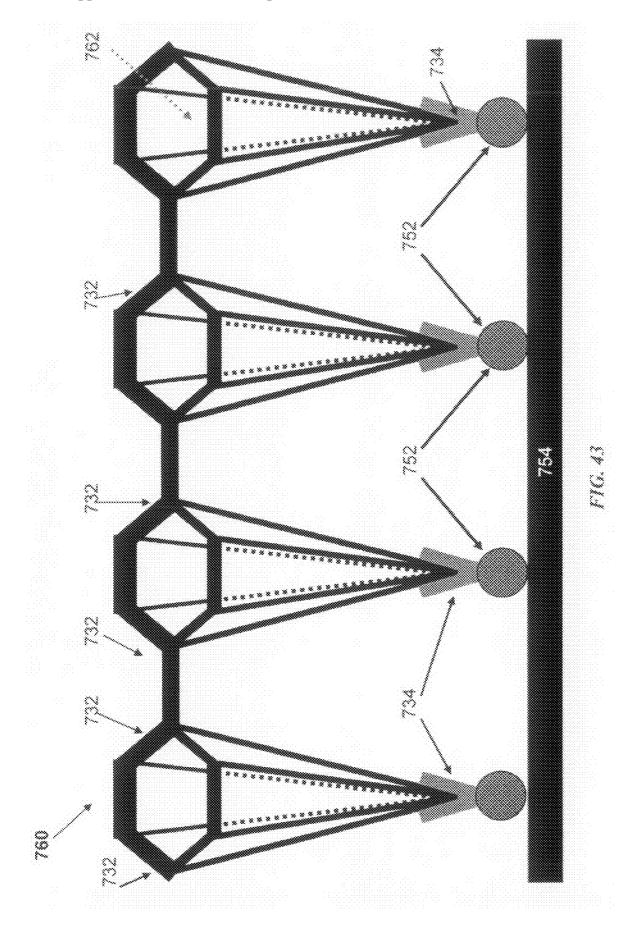

**[0066]** FIGS. **42** and **43** show YY cross-sectional views of the 3-D hexagonal-pyramid solar cells (showing a single hexagonal-pyramid unit cell and several adjacent unit cells, respectively) after completion of the solar cell fabrication process and after soldering the rear base contacts to the rear cell mirror (and base interconnect) plate;

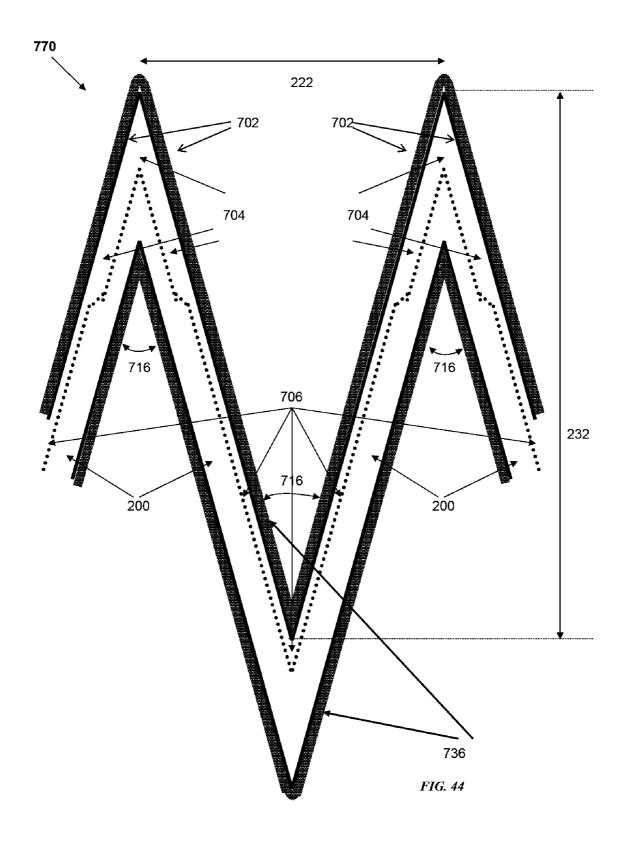

**[0067]** FIG. **44** shows a YY cross-sectional view of the 3-D hexagonal-pyramid TFSC substrate (showing one pyramid unit cell) after self-aligned roller coating of n-type dopant paste on the frontside honeycomb ridges, and after curing and furnace annealing to form the selective emitter regions and heavily-doped emitter contact regions;

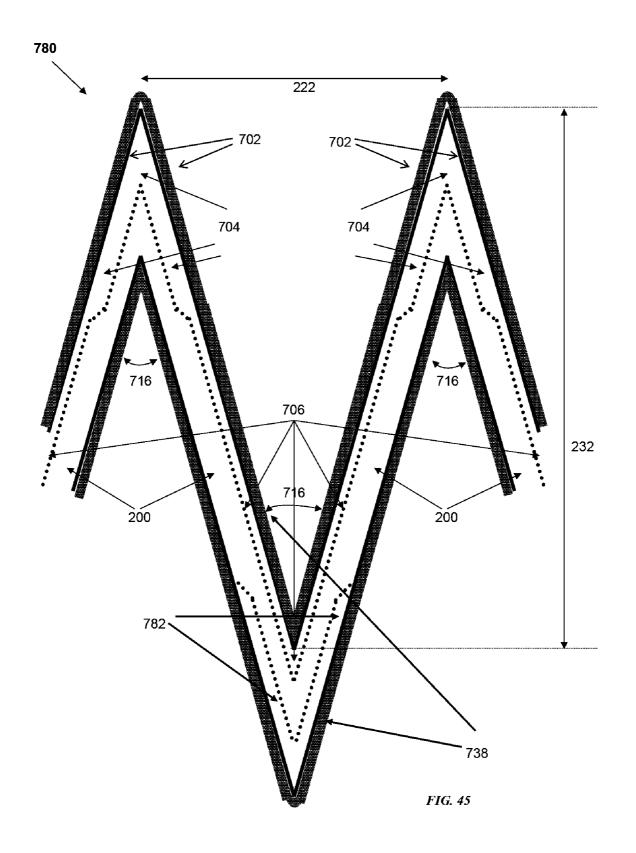

**[0068]** FIG. **45** is similar to FIG. **44**, except FIG. **45** roller coating of a p-type dopant layer and subsequent curing and anneal;

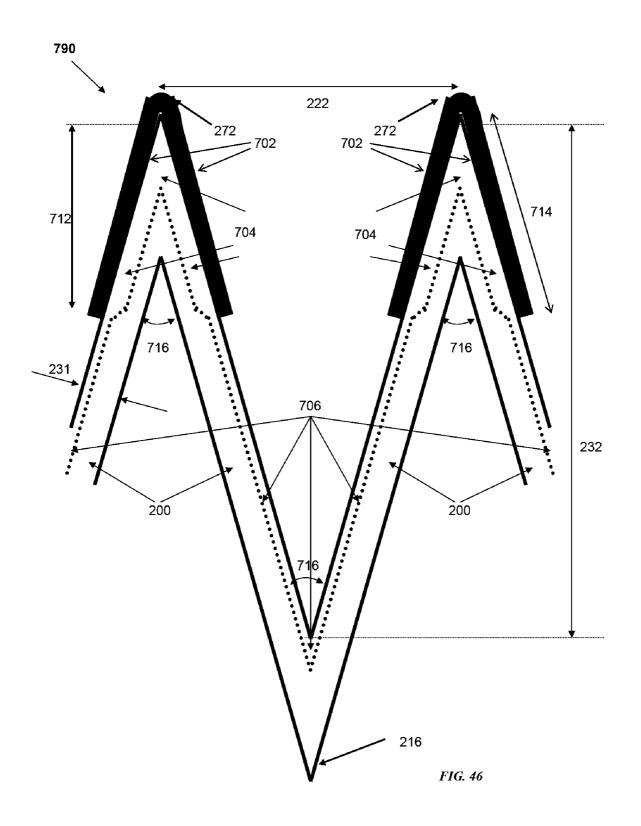

**[0069]** FIG. **46** shows a cross-sectional view similar to the view shown in FIG. **39**. However, in the embodiment shown in FIG. **46** there is only coating of n-type dopant paste on the frontside honeycomb ridges;

**[0070]** FIG. **47** shows a YY cross-sectional view of a 3-D hexagonal-pyramid substrate after self-aligned formation of the frontside solid dopant source layer and selective emitter, while FIG. **48** shows a ZZ cross-sectional view;

**[0071]** FIG. **49** shows a YY cross-sectional view of a 3-D hexagonal-pyramid substrate after self-aligned formation of the frontside solid dopant source layer, selective emitter, as well as the self-aligned frontside emitter and rear base contacts, while FIG. **50** shows a ZZ cross-sectional view;

**[0072]** FIG. **51** shows a view of a 3-D self-supporting hexagonal-pyramid TFSC substrate with thick silicon frame, compared to the thin frame shown in FIG. **41**;

**[0073]** FIG. **52** shows a schematic quasi-3-D view of a hexagonal-pyramid unit cell after formation of the self-aligned frontside emitter contact and the rear base contact;

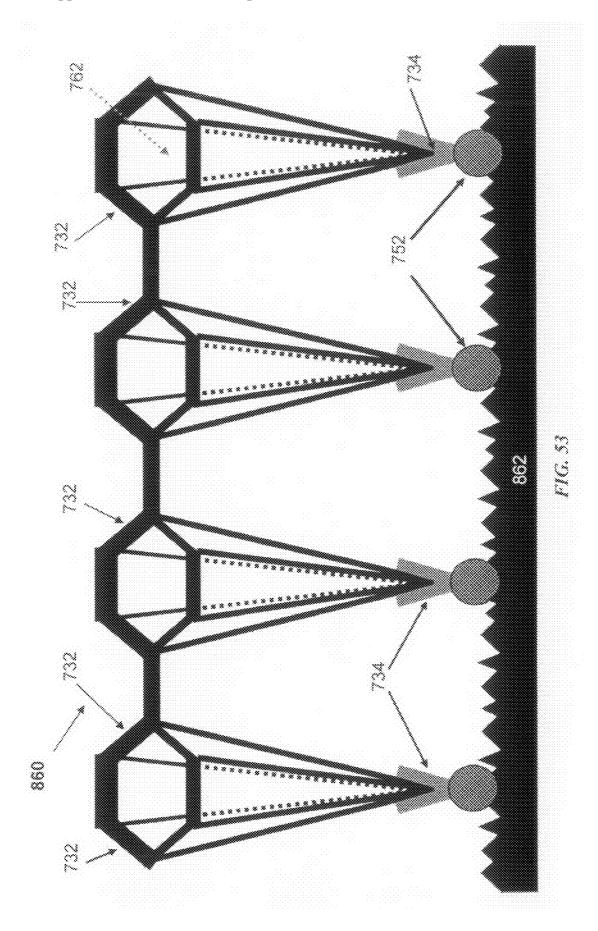

**[0074]** FIG. **53** shows a view of an alternative embodiment of solar cell assembly on the rear mirror and base interconnect (the first embodiment shown in FIG. **43**);

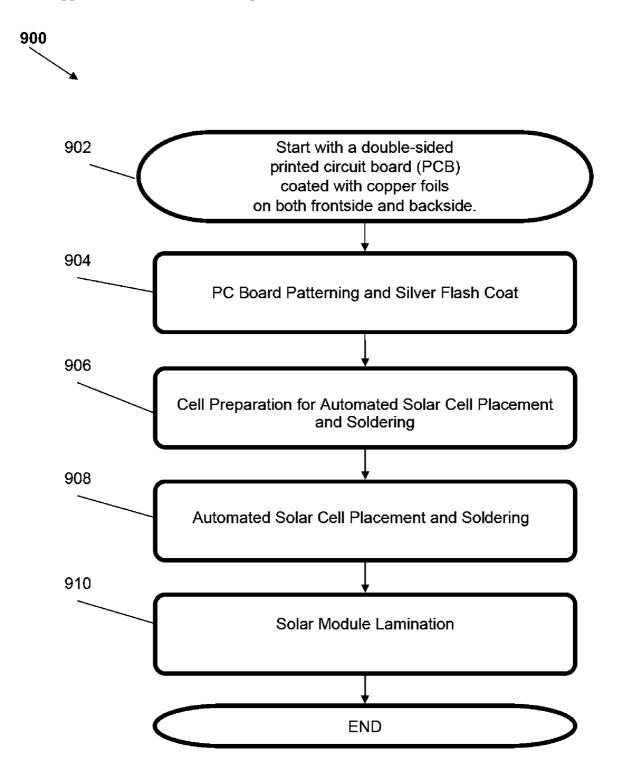

**[0075]** FIG. **54** illustrates a first embodiment of a process flow for fabrication of solar modules with top protective glass plates and embedded PCBs of this disclosure (corresponding to the solar module structure of FIG. **55** with a PCB and a TFSC mounted on the PCB);

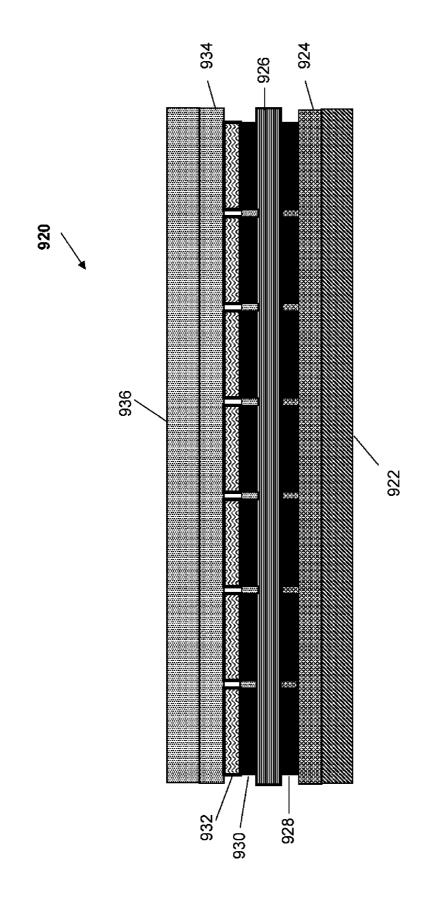

**[0076]** FIG. **55** shows a cross-sectional view of a solar module (solar panel) structure (resulting from the process flow described in FIG. **54**);

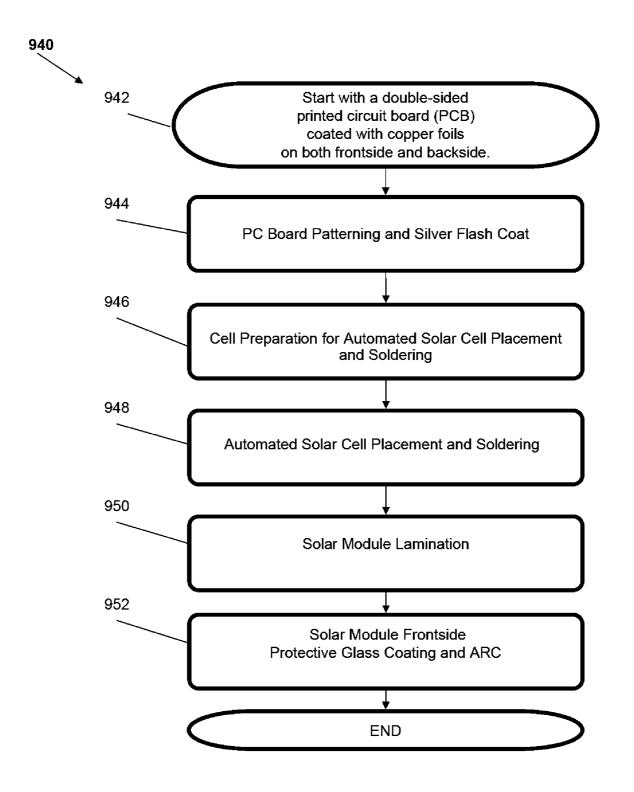

**[0077]** FIG. **56** outlines an alternative embodiment of an assembly process flow for fabrication of solar modules (corresponding to the solar module structure of FIG. **57**);

**[0078]** FIG. **57** shows a cross-sectional view of another embodiment of a solar module structure (resulting from the process flow described in FIG. **56**);

**[0079]** FIG. **58** shows a view of a solar cell integrated or assembled in building windows;

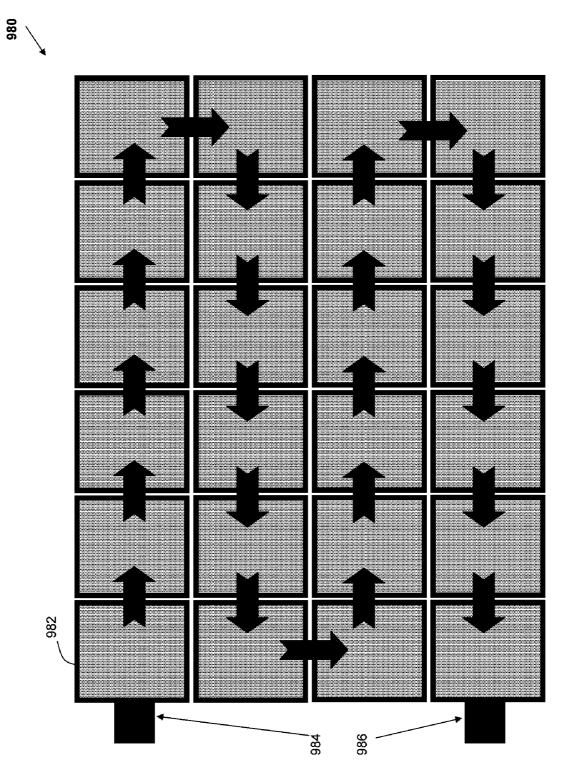

**[0080]** FIG. **59** shows a view of a representative example of series connections of TFSCs of this disclosure in a solar module assembly;

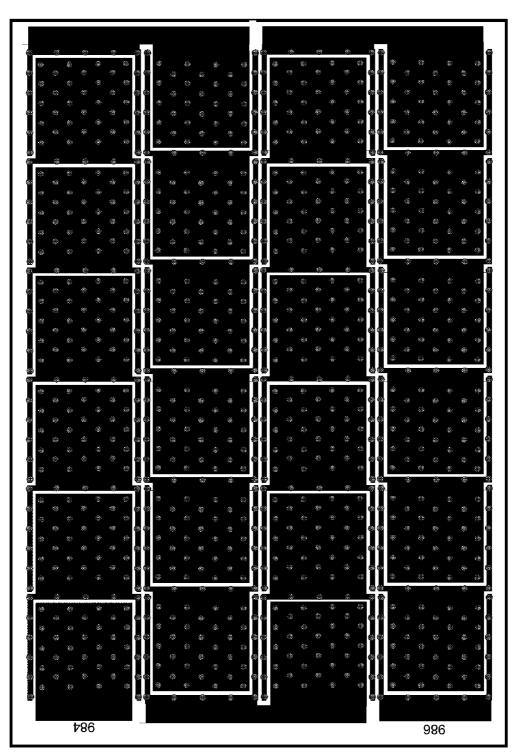

[0081] FIG. 60 shows a view of the frontside layout of the printed-circuit board (PCB) used for solar module assembly; [0082] FIG. 61 shows a top view of the backside layout of the printed-circuit board (PCB) used for solar module assembly, showing the series connection of the TFSCs;

**[0083]** FIG. **62** shows a backside view of the copper pattern on the PCB and is essentially similar to FIG. **61**;

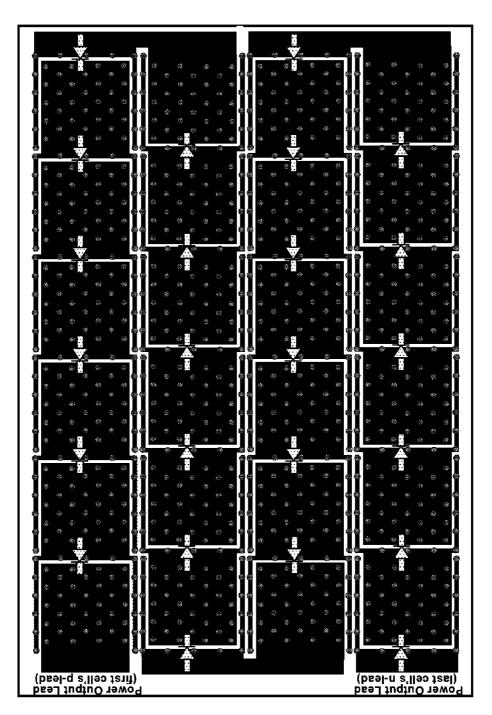

**[0084]** FIG. **63**A shows an enlarged top view of the pattern on the frontside of the solar module printed-circuit board (PCB);

**[0085]** FIG. **63**B shows an enlarged top view of the interconnect pattern on the backside of the solar module printedcircuit board (PCB);

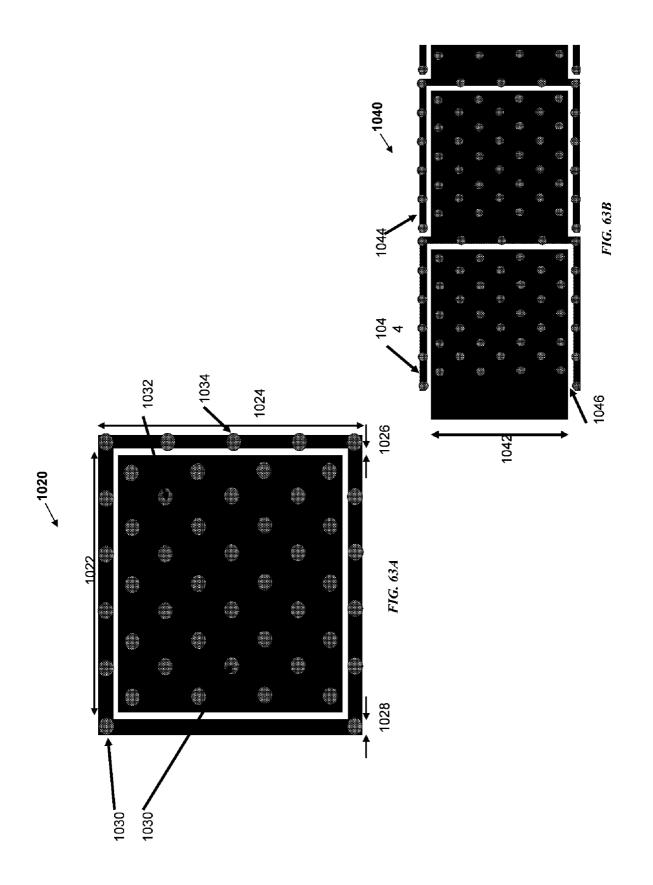

**[0086]** FIG. **64** shows various schematic views of a thick silicon frame, silicon frame slivers, and a representative method to produce (e.g., cut) silicon slivers;

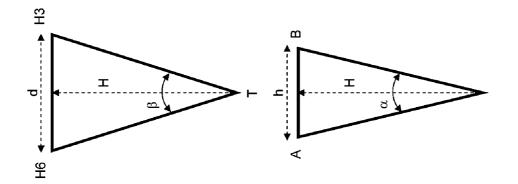

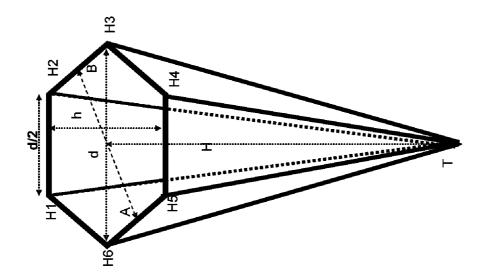

**[0087]** FIG. **65** (similar to FIG. **15**) is provided for reference for calculations;

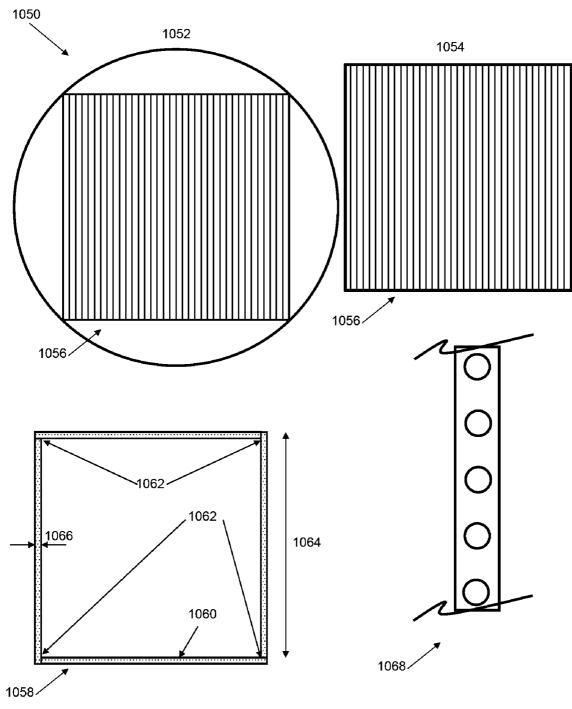

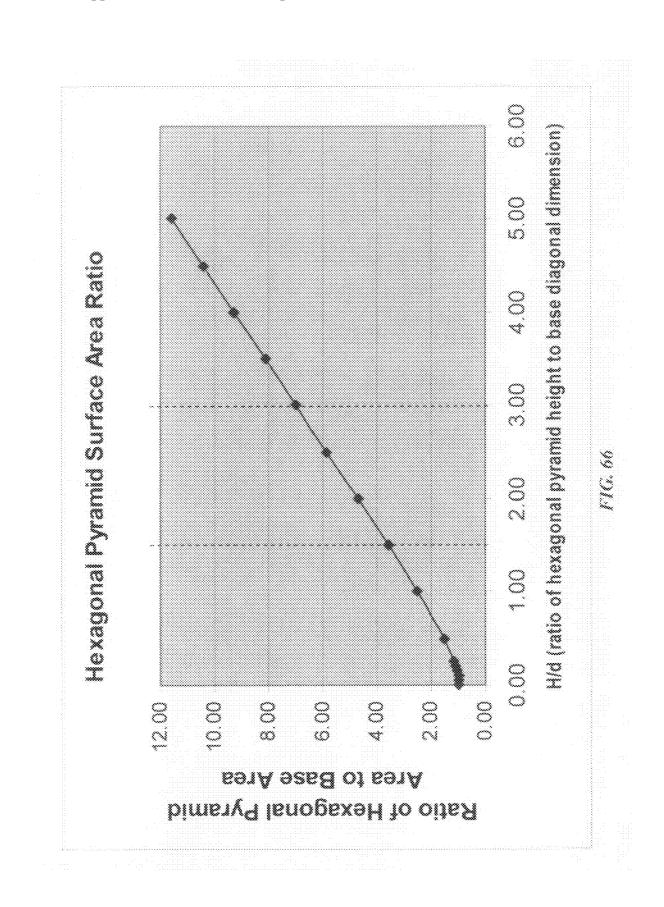

**[0088]** FIG. **66** shows the ratio of the hexagonal-pyramid sidewall area to the planar hexagonal base area  $(S_{hp}/S_{hb})$  versus the height-to-base diagonal diameter ratio (H/d) of the hexagonal-pyramid unit cell;

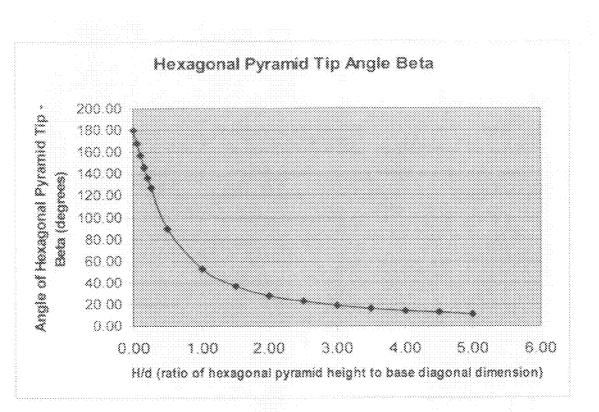

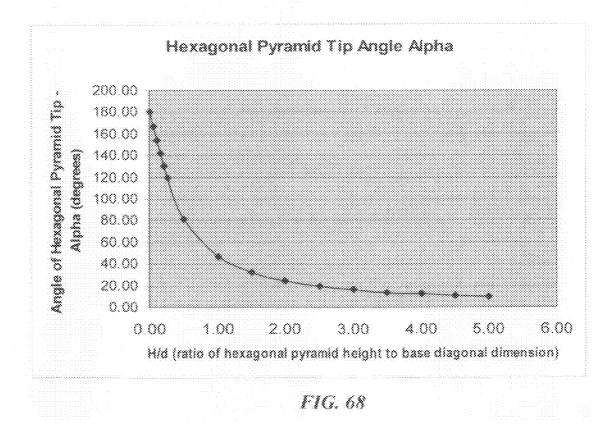

**[0089]** FIGS. **67** and **68** shows calculated frontside aperture angles of the solar cell hexagonal-pyramid unit cell versus the height-to-base diagonal diameter ratio (H/d) of the hexagonal-pyramid unit cell;

[0090] FIG. 69 is provided for reference for calculations;

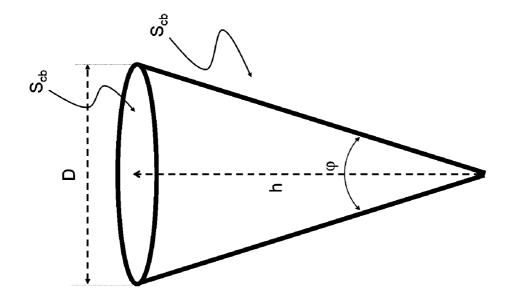

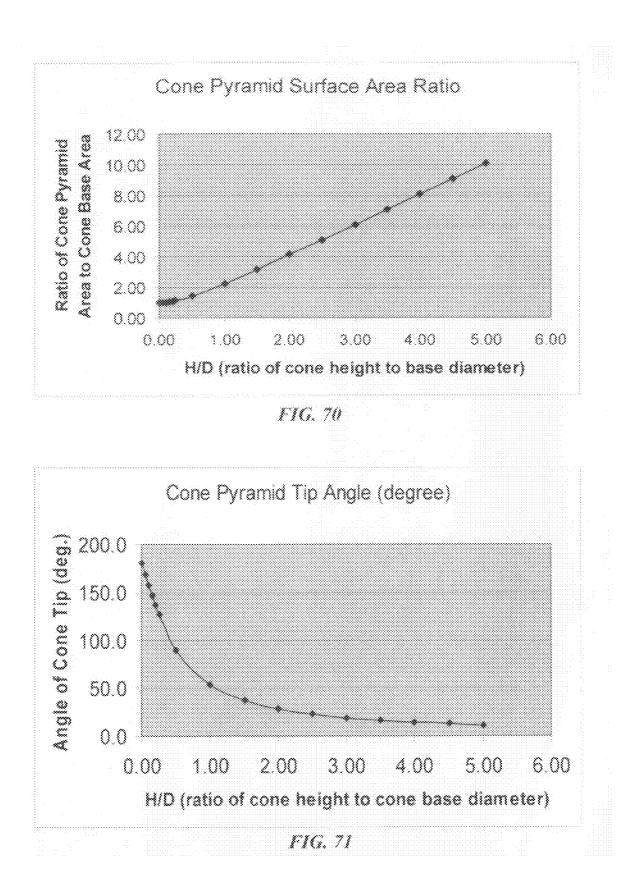

[0091] FIGS. 70 and 71 show the ratio of the cone-shaped unit cell sidewall area to the planar circular base area ( $S_{cp}/S_{cb}$ ) versus the height-to-base diameter ratio (H/D) of the coneshaped unit cell and calculated frontside aperture angle of the solar cell cone-shaped unit cell (approximation for hexagonal-pyramid units cells) versus the height-to-base diameter ratio (H/D) of the cone-shaped unit cell;

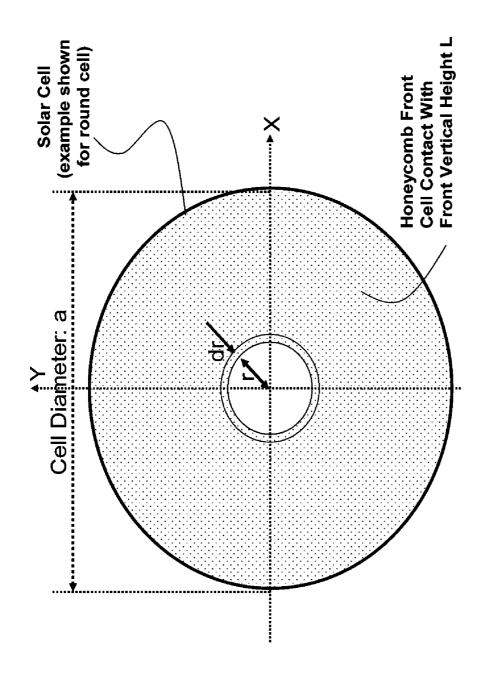

**[0092]** FIG. **72** may be used for reference with an approximate analytical calculation of the TFSC interconnect ohmic losses, assuming a circular substrate with hexagonal-pyramid array of unit cells:

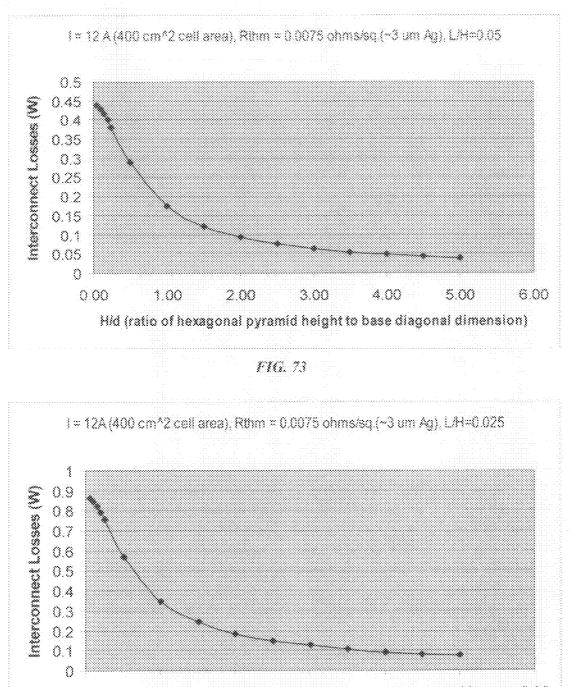

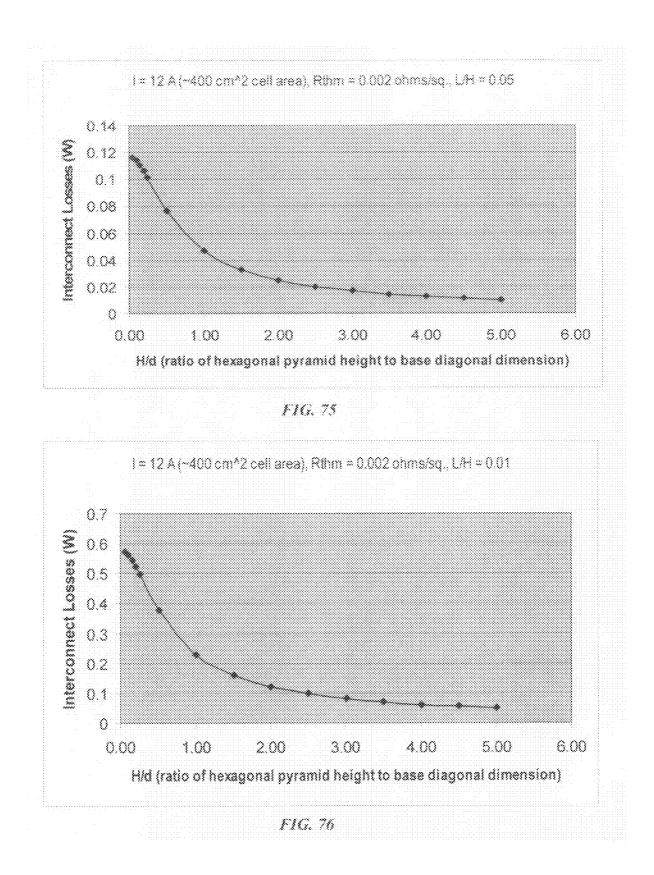

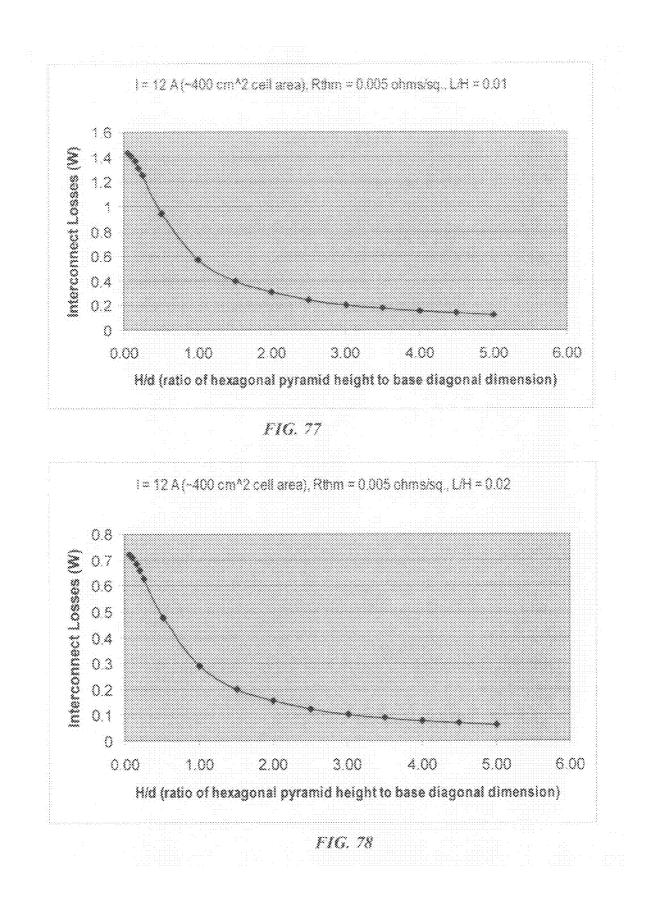

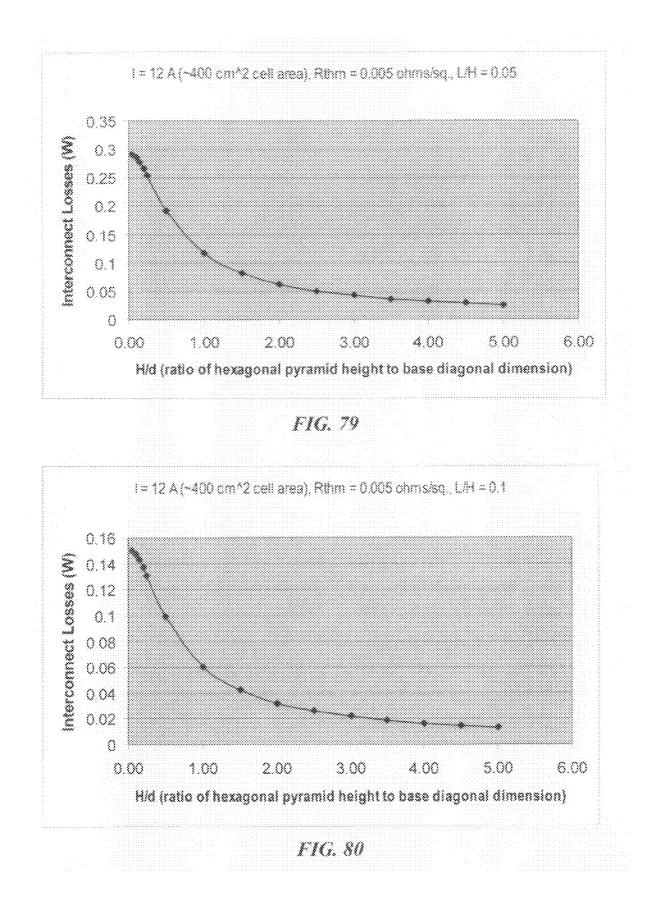

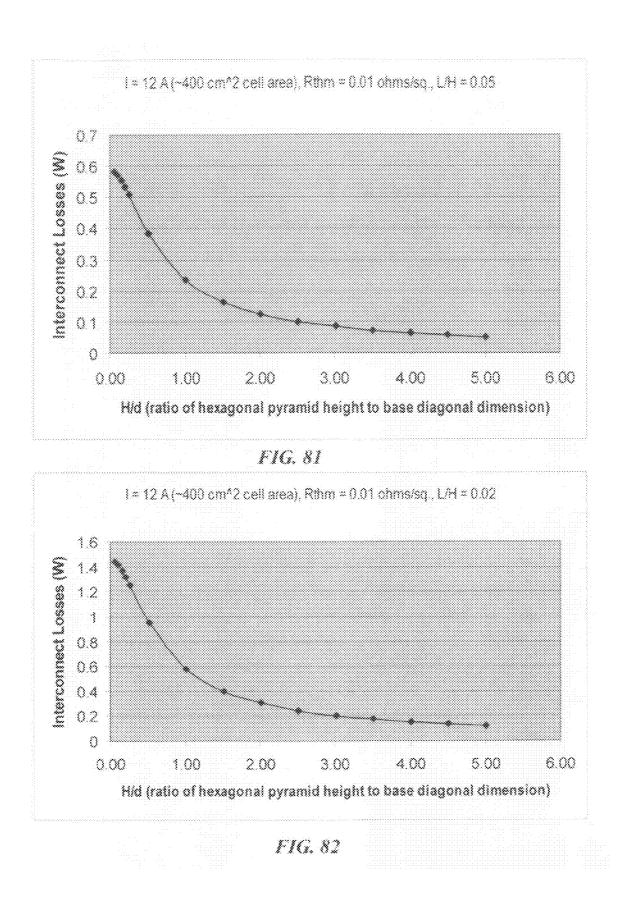

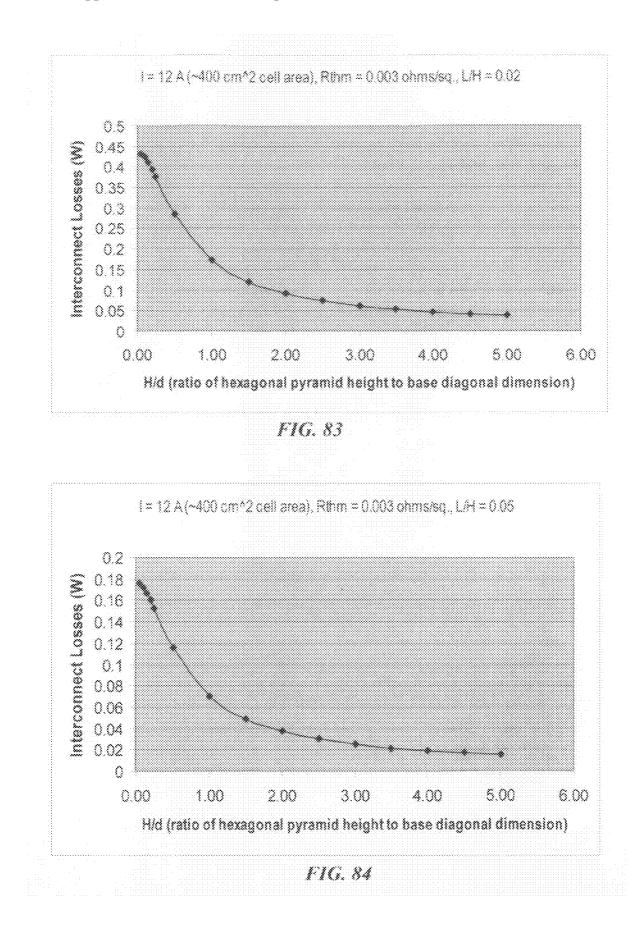

[0093] FIGS. 73 and 74 plot the projected (calculated) interconnect-related solar cell power losses as a function of the ratio of the hexagonal-pyramid height to diagonal base dimension (H/d) for two different emitter interconnect area coverage ratios on the top of the 3-D solar cell substrate; while FIGS. 73 through 84 show plots for various values of  $R_{thm}$  and L/H.

# DETAILED DESCRIPTION OF THE SPECIFIC EMBODIMENTS

**[0094]** Preferred embodiments of the present disclosure are illustrated in the drawings, like numbers being used to refer to like and corresponding parts of the various drawings. The innovative solar cell designs and technologies of the current disclosure are based on the use of a three-dimensional (3-D), self-supporting, doped (in one embodiment, in-situ-doped) semiconductor thin film, deposited on and released from a reusable crystalline (embodiments include monocrystalline or multicrystalline silicon) semiconductor template.

**[0095]** A preferred semiconductor material for the 3-D TFSC substrate is crystalline silicon (c-Si), although other semiconductor materials may also be used. One embodiment uses monocrystalline silicon as the thin film semiconductor

material. Other embodiments use multicrystalline silicon, polycrystalline silicon, microcrystalline silicon, amorphous silicon, porous silicon, and/or a combination thereof. The designs here are also applicable to other semiconductor materials such as germanium, silicon germanium, silicon carbide, a crystalline compound semiconductor, or a combination thereof. Additional applications include copper indium gallium selenide (CIGS) and cadmium telluride semiconductor thin films.

**[0096]** The 3-D TFSC designs and production technologies as well as associated module structures and assembly approaches of this disclosure effectively overcome the abovementioned problems and challenges and enable cost-reduced fabrication of very-high-efficiency solar cells and modules using self-aligned cell process flows without the use of any photolithography patterning or screen printing or shadowmask deposition process steps during cell fabrication (i.e., during 3-D TFSC substrate and cell fabrication after fabrication of the reusable 3-D template). The 3-D TFSC technologies of this disclosure are based on the formation of a 3-D pyramid-array TFSC substrate structure on a low-cost reusable template and its subsequent release and lift-off from the template to form a free-standing, self-supporting 3-D thinfilm semiconductor substrate structure.

**[0097]** The current disclosure combines the benefits of TFSC fabrication on a proven high-efficiency crystalline silicon (c-Si) platform. The 3-D c-Si TFSC designs and technologies of this disclosure enable significant advancements in the areas of c-Si solar cell and module efficiency enhancement as well as manufacturing cost reduction. Based on innovative thin-film process steps, dependence on an expensive and constrained silicon wafer supply-chain is eliminated. Some of the unique advantages of the cells designs and technologies of this disclosure which enable achieving ultra-high-efficiency at reduced manufacturing cost are substantial decoupling from the traditional solar PV silicon supply chain, performance enhancement, cost reduction, and reliability improvement.

[0098] The disclosed subject matter improves solar cell efficiency by using a 3-D c-Si film as an absorber layer in conjunction with highly efficient light trapping. Use of the crystalline silicon absorber layer leverages known solar cell manufacturing techniques and supply chain, while reducing absorber layer thickness (e.g., reduced by a factor of ten or more compared to silicon wafers used for wafer-based solar cells). The disclosed method and system eliminates or substantially reduces photo-degradation and enhances open-circuit voltage  $(V_{ac})$  of cells. In addition, the disclosed method and system provides efficient frontside and rear side lighttrapping in conjunction with a highly reflective rear mirror for maximum absorption of incident solar flux. Also, the disclosed method and system provides a selective emitter to enhance blue response and external quantum efficiency, with minimal shadowing of the cell and reduced ohmic losses due to a unique folded emitter metallization contact design and improved module assembly.

[0099] Manufacturing cost is reduced by decreasing silicon usage (by a significant factor, e.g.,  $3 \times$  to over  $10 \times$ ), with thinner deposited c-Si films also reducing the finished solar module energy payback time to less than 1 to 2 years. Manufacturing cost is further reduced by eliminating wire sawing and related kerf losses associated with mainstream solar cell wafer manufacturing technology. Manufacturing cost is still further reduced by using self-aligned processing without any

lithography or patterning steps used during the substrate and cell fabrication process flow, and a reduced number of fabrication process steps, with improved yield and cycle time. Production cost is still further reduced by using a simplified interconnection and cell-module assembly process and lightweight monolithic modules.

**[0100]** Operational reliability is improved by using thinner silicon films, eliminating photo-degradation and reducing temperature coefficients. Operational reliability is further improved by using a simple distributed high-conductance electrical interconnection, minimizing field failures. Operational reliability is still further improved by eliminating module glass cover (for glassless module assembly), thus reducing cost and facilitating field installation and operation. Operational reliability is still further improved by reducing the number of manufacturing process steps and process variations using in-line manufacturing process control.

[0101] The current disclosure reduces the solar module cost per watt for the user (by at least 30% to 50%) and cuts balance-of-system (BOS) and installation costs for the integrators and installers. This may offer major benefits to the global grid-tied end-users and solar system installers and integrators. The current disclosure reduces the module integration and installation cost and installed solar cell system  $\cot per W_p$  for the user, thereby lowering finished system  $\cot t$ per  $W_p$ . The current disclosure increases module efficiency, with higher module efficiency resulting in lower BOS cost. The lower installed solar cell system cost results in reduction of the economic break-even time to a lower fraction of the system lifetime, from roughly 1/2 to 1/3 for current best-ofbreed c-Si solar cell systems to less than 1/4 to 1/8 for the embodiments of this disclosure. The current disclosure reduces energy pay-back time (EPBT) from 3 to 7 years for best-of-breed c-Si solar cell systems to less than 1 to 2 years for the embodiments of this disclosure. Reduced EPBT substantially increases the net lifetime energy output (in kWh) for field-installed modules. The cell designs and module assemblies of this disclosure also provide stable degradationfree field operation over an extended time (e.g., 30 to 40 year life of the module), further increasing the net lifetime electrical energy output. Module manufacturing costs are expected to be 30% to 65% lower than that of the leading high-performance c-Si solar cells/modules at the time of market entry. This may shorten the ROI break-even time for the users compared to the current industry roadmap and projections. Further benefits include increased field performance stability and reliability and reduced environmental impact (non-toxic materials and shortened EPBT). Further, the cell and module designs of this disclosure are ideal for grid-tied applications where it is advantageous to maximize electricity generation from a limited building rooftop or façade area.

**[0102]** The absorber silicon film thickness of the current disclosure may be a value in the range of roughly 1 to 30-microns, where a thinner silicon layer is preferred for less material consumption (in one embodiment, in the range of 1 to 10 microns). Even after taking into account the effective surface area increase due to the 3-D geometric structure of the 3-D TFSC substrates, the 3-D TFSC substrates of this disclosure consume substantially less silicon material than the state-of-the-art wafer-based c-Si solar cells. Moreover, there are no sawing or kerf losses. Similarly, there is no requirement for saw damage removal since the 3-D crystalline silicon film is process-ready upon release from the reusable template. This substantially reduces the solar cell cost associated with sili-

con consumption. The self-supporting 3-D epitaxial silicon thin film is deposited on and released from a low-cost reusable crystalline (monocrystalline or multicrystalline) silicon substrate (template). The template may be reused numerous times before being reconditioned or recycled. The template may even be chosen from the much lower cost metallurgicalgrade c-Si since any metallic impurities are prevented from contaminating the 3-D crystalline silicon film.

[0103] FIG. 3 provides an overview of the 3-D TFSC substrate and cell fabrication process flow. Focusing on the top of FIG. 3 illustrating the 3-D TFSC substrate fabrication, note that the first step in this process flow uses a pre-fabricated template. The template with a pre-fabricated 3-D trench or groove pattern may be used for formation of 3-D TFSC substrates, which are then used in the formation of 3-D TFSCs, substantially eliminating or reducing disadvantages and problems associated with previously developed TFSCs and the wafer-based crystalline silicon cell technologies. The template is capable of being used numerous times (e.g., tens to hundreds of times) to fabricate numerous 3-D TFSC substrates before being reconditioned or recycled. In one embodiment, the template may be used hundreds of times to fabricate 3-D TFSC substrates before being recycled. The template may be reused for as long as it remains relatively free of dislocations and/or for as long as it maintains an acceptable trench or groove pattern with widths and surface conditions within acceptable control limits (e.g., as gauged by in-line metrology).

**[0104]** FIG. **4** summarizes the overall crystalline solar cell fabrication process flow of prior art techniques and highlights the specific steps eliminated by the current disclosure, compared to the prior art. FIG. **5** summarizes the overall cell and module fabrication process flow and the competitive advantages of the current disclosure, compared to the prior art. As highlighted here, the current disclosure enables fabrication of 3-D TFSC substrates and 3-D TFSCs, thus, substantially reducing consumption of semiconductor absorber material (e.g., silicon) and the cell and module manufacturing costs.

**[0105]** In the following section, alternative embodiments of process flows for fabricating templates using either lithography and etch techniques or laser micromachining (or laser drilling) are described. The templates are then used and reused numerous times to fabricate the 3-D TFSC substrates for 3-D TFSC fabrication.

**[0106]** Templates may be fabricated using electronic-grade silicon wafers, solar-grade silicon wafers, or lower-cost metallurgical-grade silicon wafers. Moreover, templates made of silicon can be fabricated either using monocrystalline or multicrystalline silicon wafers. The starting template wafer may either be a standard polished wafer (after saw damage removal) or even a lower grade wafer immediately after wire sawing (without saw damage removal). The latter may further reduce the cost of the templates. The relatively low cost of each template is spread over numerous 3-D TFSC substrates, resulting in much lower TFSC substrate and finished module costs compared to the standard state-of-the-art (e.g., 200 microns thick) solar-grade monocrystalline and multicrystalline silicon wafers and associated modules.

**[0107]** For further explaining how a template is fabricated, FIG. **6** shows an embodiment of a process flow **100**. The process begins with step **102**, where an unpatterned monocrystalline silicon or multicrystalline silicon, either squareshaped or round substrate (e.g., 200 mm×200 mm square or 200-mm round) is provided. The starting template wafer may be a wafer prepared by wire saw either with or without saw damage removal (the latter may further reduce the cost of template). The starting template wafer may also be made of a lower purity (and lower cost) metallurgical-grade silicon. In one embodiment, the substrate is roughly 200 to 800 microns thick. Optionally, step 102 includes performing gettering on a low-cost metallurgical-grade silicon and/or performing a surface texturing etch (e.g., using isotropic acid texturing by a mixture of nitric acid and hydrofluoric acid, or using alkaline texturing in KOH/IPA) to create an optional textured template surface. Step 104 involves the use of programmable precision laser micromachining to form the desired periodic array of deep trenches. This process may be performed in a controlled atmospheric ambient based on either physical ablation or a combination of physical ablation and laser-assisted chemical etching. Step 106 involves template surface preparation and cleaning. This process includes stripping the patterned photoresist layer from the substrate. The template substrate is then cleaned in a wet bench prior to subsequent thermal deposition processing to form the TFSC substrates. Such cleaning may involve DRIE-induced polymer removal (using a suitable wet etchant such as a mixture of sulfuric acid and hydrogen peroxide) followed by an isotropic silicon wet etch (such as in a mixture of nitric acid and hydrofluoric acid) in order to isotropically remove a thin layer (e.g., on the order of 10 to 500 nanometers) of silicon from the trench sidewalls and bottoms. This may remove any surface and buried contaminants, such as any surface and embedded metallic and/or polymeric/organic contaminants introduced by the deep RIE (DRIE) process, from the sidewalls and bottoms of the DRIEproduced template trenches. Template processing may complete after a deionized (DI) water rinse and drying. Optionally and if desired, the template wafer may also go through a standard pre-diffusion (or pre-thermal processing) wafer cleaning process such as a so-called RCA wet clean prior to the above-mentioned DI water rinsing and drying. Another optional surface preparation step (either performed instead of or after the wet isotropic silicon etch process) includes performing a short thermal oxidation (e.g., to grow 5 to 100 nanometers of sacrificial silicon dioxide), followed by wet hydrofluoric acid (HF) oxide strip (to remove any residual contaminants from the patterned template). If no optional oxide growth/HF strip is used, an optional dilute HF etch may performed to remove the native oxide layer and to passivate the surface with hydrogen (forming Si-H bonds) in preparation for subsequent 3-D TFSC substrate fabrication. After the completion of step 106, the resulting template may then be used and reused multiple times to fabricate 3-D (e.g. hexagonal-pyramid) TFSC substrates.

**[0108]** An alternative embodiment of a process flow **110** for patterning of a template is outlined in FIG. **7**, which uses photolithography and etch instead of direct laser micromachining. Step **112** (providing an unpatterned substrate) corresponds to step **102** of FIG. **6**. Step **114** uses photolithography patterning (in one embodiment, using a relatively lowcost contact or proximity aligner/patterning) to produce a mask pattern such as hexagonal-pyramid pattern in photoresist (i.e., interconnected hexagonal openings in the photoresist layer). The process sequence includes the formation of an oxide and/or nitride (optional) layer, photoresist coating (e.g., spin-on or spray coating) and pre-bake, photolithography exposure through a hexagonal-array mask, and photoresist development and post-bake. One embodiment includes an optional hard mask layer (SiO<sub>2</sub> and/or SiN<sub>x</sub>; for example, a

thin thermally grown oxide layer can be used as an optional hard mask) below the photoresist (although the process may be performed without the use of any hard mask layer by placing the photoresist coating directly on silicon). When using a hard mask layer, the exposed portions of the hard mask layer are etched after photoresist patterning (thus, forming hexagonal openings). Such etching of the exposed hard mask layer may be simply performed using a wet etchant such as hydrofluoric acid for oxide hard mask or using plasma etching. Step 116 involves formation of hexagonal-pyramids using anisotropic plasma etch; where a high-rate deep reactive ion etch (DRIE) process forms a closely-packed array of deep (e.g., 100 to 400 microns) hexagonal-pyramid shaped trenches (i.e., pyramidal trenches with sloped sidewalls) in silicon. The photoresist and/or oxide and/or nitride hard mask layer(s) are used for pattern transfer from the patterned photoresist layer to silicon substrate. In one embodiment, the deep RIE (DRIE) process parameters are set to produce a controlled-angle hexagonal-pyramid sidewall slope. The RIE is allowed to produce small-diameter (e.g., less than 5 microns) holes at the bottom of pyramids by punching through the substrate backside. Alternatively, separate smalldiameter backside holes may be formed which connect to the bottom tips of the pyramidal trenches. Step 118 (surface preparation and cleaning) corresponds to step 106 of FIG. 6. After the completion of step 118, the resulting template may then be used and reused multiple times to fabricate 3-D (e.g. hexagonal-pyramid) TFSC substrates.

[0109] FIG. 8 shows a Y-Y cross-sectional view of a template 120 showing hexagonal-pyramid trenches 122 between posts 123, formed in the substrate fronstide 124 using the process flows described above. The bottom 126 of the trenches 122 connects to through-wafer backside, preferably small-diameter, holes 128 which connect to the template backside 130. In one embodiment, the holes 128 are 1 to 10 microns in diameter. The holes 128 are used for subsequent wet etching of the sacrificial layer and 3-D silicon film release and lift-off. The template 120 has dimensions of L 132 (in one embodiment, 0 to 25 microns although it may also be much larger up to several hundred microns), 3-D unit cell height H 134, pyramidal angle  $\alpha$  136, and unit cell aperture diameter h 138.

[0110] The templates described above may be used to fabricate 3-D TFSC substrates for use in 3-D TFSCs. All of the embodiments shown in FIGS. 9 through 12 use sacrificial layer formation (e.g., porous silicon sacrificial layer) and trench-fill deposition processes (e.g., epitaxial silicon deposition) which may be highly conformal, for conformal formation of the sacrificial (porous silicon) layer and subsequent seamless void-free filling of the trenches with a semiconductor absorber layer such as in-situ-doped (e.g., in-situ boron doped) monocrystalline or multicrystalline silicon layer. One embodiment uses a patterned single-crystal (monocrystalline) silicon or multicrystalline silicon (mc-Si) square-shaped (or round) template, with dimensions of approximately 150 mm×150 mm to over 200 mm×200 mm. Alternative embodiments may use much lower cost metallurgical-grade or solargrade silicon.

**[0111]** FIG. **9** shows an embodiment of a process flow for fabrication of self-supporting, free-standing 3-D hexagonalpyramid TFSC substrates. The process uses a lift-off 3-D thin-film release process based on a highly selective etch process to remove an interfacial sacrificial layer (of  $Ge_{1-x}Si_x$ ) without any appreciable etching of silicon. The  $Ge_{1-x}Si_x$  layer may be a single layer with a constant Ge fraction or a multilayer (e.g., 2 to 3 layers) structure with varying Ge fractions. In step 142, a patterned square-shaped template is provided. This template has already been processed to form an array of hexagonal-pyramid trenches on its frontside 124 along with an array of through-wafer holes 128 from trench bottoms 126 to backside 130. Step 144 involves a multi-layer blanket epi in an epitaxial reactor. Step 144 first involves an  $H_2$  or  $GeH_4/H_2$ in-situ cleaning, which is performed after a standard pre-epi wet clean. Next, a thin sacrificial epi layer is deposited on the frontside only. In one embodiment,  $Ge_xSi_{1-x}$  is used for the sacrificial epi layer and is between 10 and 200 nanometers. Next, a doped silicon epi layer is deposited on the frontside only. In one embodiment, the layer is p-type, boron-doped and has a thickness between 2 and 20 microns. Step 146 involves 3-D TFSC substrate release. A highly selective isotropic wet or dry etch of Ge<sub>x</sub>Si<sub>1-x</sub> is performed, with very high selectivity with respect to silicon. In one embodiment, a mixture of hydrofluoric acid, nitric acid and acetic acid (HNA) is used to etch the  $Ge_xSi_{1-x}$  layer. Alternatively, a mixture of ammonia, peroxide, and water (NH<sub>4</sub>OH+H<sub>2</sub>O<sub>2</sub>+H<sub>2</sub>O) may be used. This process releases the silicon epi layer as a hexagonal-pyramid 3-D TFSC substrate, which may then be used for subsequent 3-D TFSC fabrication.

**[0112]** Depending on the emitter doping type (n-type or p-type), the in-situ base doping type is chosen to be p-type (e.g., boron) or n-type (e.g., phosphorus). The embodiments shown provide examples of boron-doped hexagonal-pyramid 3-D TFSC substrates which may be used to fabricate TFSCs with n-type, phosphorus-doped selective emitters. In an alternative embodiment, all the doping polarities may be inverted, resulting in phosphorus-doped hexagonal-pyramid 3-D TFSC substrates which may be used for fabricating cells with boron-doped selective emitters.

[0113] FIG. 10 shows an alternative embodiment of a process flow 150 for fabrication of self-supporting, free-standing 3-D hexagonal-pyramid TFSC substrates. The same process flow may be used for fabrication of 3-D TFSC substrates with other unit cell structures (square pyramid, triangular pyramid, orthogonal V-grooves, orthogonal diagonal V-grooves, etc.). This process uses a suitable sacrificial material layer (e.g., silicon dioxide) to facilitate the 3-D TFSC substrate release and lift-off (or removal from the template). Laser crystallization may be used to crystallize the amorphous silicon or polysilicon layer. Step 152 (providing a template) corresponds to step 142 above. Step 154 involves sacrificial layer deposition, where a thin sacrificial layer (e.g., SiO<sub>2</sub>) is deposited preferably by APCVD (alternatively, use LPCVD or PECVD or even thermal oxidation). In one embodiment, this layer is between 20 nm and 200 nm of SiO<sub>2</sub>. In step 156, doped (e.g., p-type) silicon layer (preferably doped amorphous silicon or polysilicon) is deposited on oxide-coated substrate (top only) by a CVD process such as PECVD (e.g., 2 to 20 microns thick; boron-doped). Step 158 involves depositing a thin sacrificial layer (e.g., SiO<sub>2</sub>) as a top protective layer, preferably by chemical-vapor deposition process such as APCVD (alternatively, use LPCVD or PECVD or even thermal oxidation). In one embodiment, this layer may be 5 nm to 50 nm of SiO<sub>2</sub>. In step 160, laser crystallization (preferably starting from a silicon frame at substrate edge) of doped silicon layer is performed, using a preferably squareshaped single-crystal silicon frame as laser crystallization seed (edge-to-center crystallization). Step 162 involves releasing the 3-D TFSC substrate, by performing a highly selective isotropic HF wet etching of the sacrificial  $SiO_2$  layer (with high selectivity with respect to silicon) to etch off the oxide release layer between the p-type 3-D silicon film and the template (this process lifts the 3-D hexagonal-pyramid silicon film). For all embodiments, releasing the 3-D film may be aided by applying a small mechanical stress (e.g., wafer warpage) or applying ultrasonic or megasonic agitation during the release etch.

[0114] FIG. 11 shows an alternative embodiment of a process flow 170 for fabrication of self-supporting, free-standing 3-D hexagonal-pyramid TFSC substrates. The same process flow may be used for fabrication of 3-D TFSC substrates with other unit cell structures (square pyramid, triangular pyramid, orthogonal V-grooves, orthogonal diagonal V-grooves, other types of pyramids, etc.). This process uses a sacrificial or disposable material layer (e.g., silicon dioxide) to facilitate the 3-D TFSC substrate release and. Laser crystallization may be used to crystallize the amorphous silicon or polysilicon layer. Step 172 (providing a template) corresponds to step 142 above. Step 174 (sacrificial layer deposition) corresponds to step 154 above. Step 176 involves performing a backside wet etching of SiO<sub>2</sub> to re-open the oxide-filled substrate bottom holes. Step 178 (doped silicon deposition) corresponds to step 156 above; and step 180 (sacrificial layer deposition) corresponds to step 158. In step 182, laser crystallization of the doped silicon layer is performed, using the single-crystal islands at the bottom holes of hexagonal-pyramids as laser crystallization seeds. Step 184 (3-D TFSC substrate release) corresponds to step 162 above.

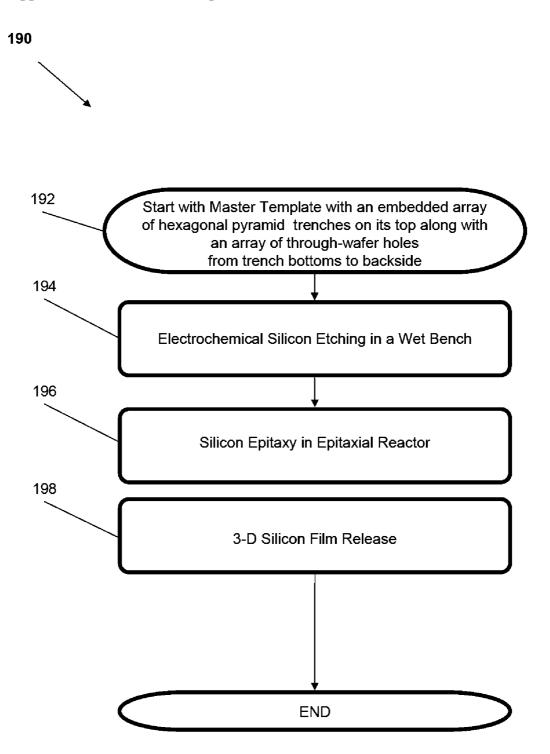

[0115] FIG. 12 shows an alternative embodiment of a process flow 190 for fabrication of self-supporting, free-standing 3-D hexagonal-pyramid TFSC substrates. The same process flow may be used for fabrication of 3-D TFSC substrates with other unit cell structures (square pyramid, triangular pyramid, orthogonal V-grooves, orthogonal diagonal V-grooves, other pyramidal unit cell structures, etc.). This process uses electrochemical silicon etching to form low and/or high porosity porous silicon layer(s) prior to semiconductor (e.g., silicon) epitaxy. Step 192 (providing a template) corresponds to step 142 above. Step 194 involves Electrochemical Silicon Etching in a Wet Bench to produce a single-layer porous silicon or a bilayer stack of a top layer of low-porosity porous silicon on a layer of high-porosity porous silicon, using electrochemical HF etching (also known as electrochemical anodization of silicon to form porous silicon). The porous silicon layer or layer stack may be formed either by direct electrochemical etching of the template substrate or by first depositing a thin layer of epitaxial silicon and then converting the thin silicon epi layer to sacrificial porous silicon using electrochemical etching. In step 196, silicon epitaxy is performed in an epitaxial reactor to form preferably monocrystalline silicon on top of the porous silicon sacrificial layer or layer stack, with the following in-situ process steps performed: H<sub>2</sub> in-situ clean; deposition of doped (e.g., p-type) silicon epi (top only) (e.g., 2 to 20 microns thick; boron-doped). Finally, in step 198, the 3-D TFSC substrate is released by either applying a mechanical stress to the substrate (e.g., by applying a slight warpage to the substrate), or simply by selective wet etching of the sacrificial porous silicon layer (or layer stack) using a suitable etchant (such as HF+H2O2 or TMAH or another suitable selective porous silicon etchant).

**[0116]** The following FIGURES show embodiments of 3-D TFSC substrate structures. The crystalline silicon film thickness is in the range of 2 to 30 microns, and preferably in

the lower-end range of 2 to 10 microns. This is substantially less (by a factor of roughly  $20 \times$  to  $100 \times$ ) than the state-of-the-art silicon solar cell wafer thickness (roughly 200 microns).

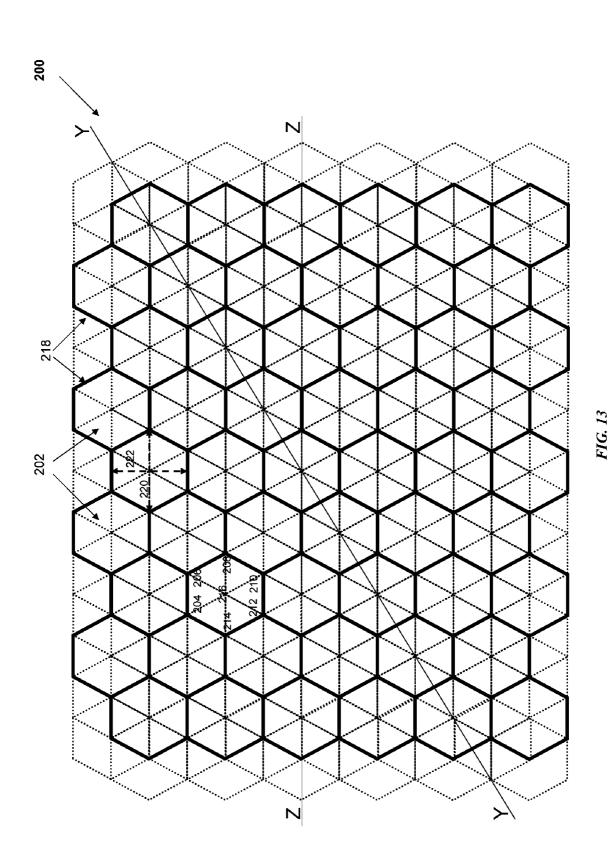

**[0117]** FIG. **13** shows a top view of a regular (equilateral) hexagonal-pyramid 3-D TFSC substrate **200**, formed using the process steps outlined above. Each hexagonal unit cell **202** contains hexagonal unit cell points ( $H_1$ ,  $H_2$ ,  $H_3$ ,  $H_4$ ,  $H_5$ , and  $H_6$ ) **204**, **206**, **208**, **210**, **212**, and **214**, with the bottom tip (which will form the back contact) of the hexagonal-pyramid shown as point **216**. FIG. **13** further shows the hexagonal dimension of the unit cell hexagon (d) **220**; and hexagonal unit cell horizontal distance (h) **222**. In one embodiment, the hexagonal-pyramid 3-D TFSC substrate sidewalls **218** are between 2 and 30 microns thick.

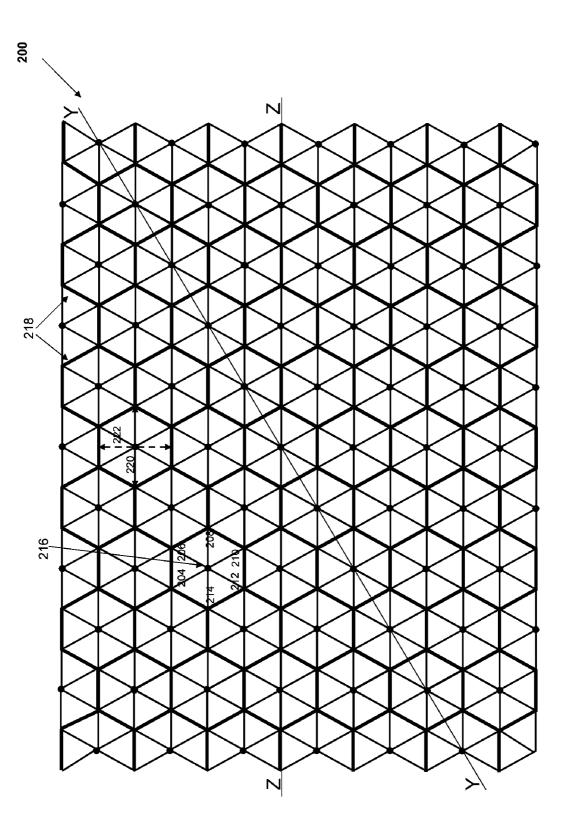

**[0118]** FIG. **14** shows a bottom view of the TFSC substrate **200** shown in FIG. **13**. In this view, the hexagonal-pyramid rear (bottom) tips **216** are shown at the centers of the hexagons. The honeycomb hexagons are the bottom views of the top honeycomb ridges of the 3-D TFSC substrate.

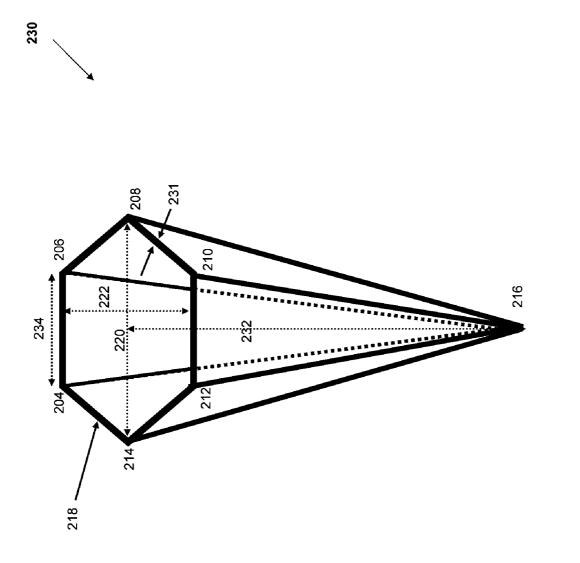

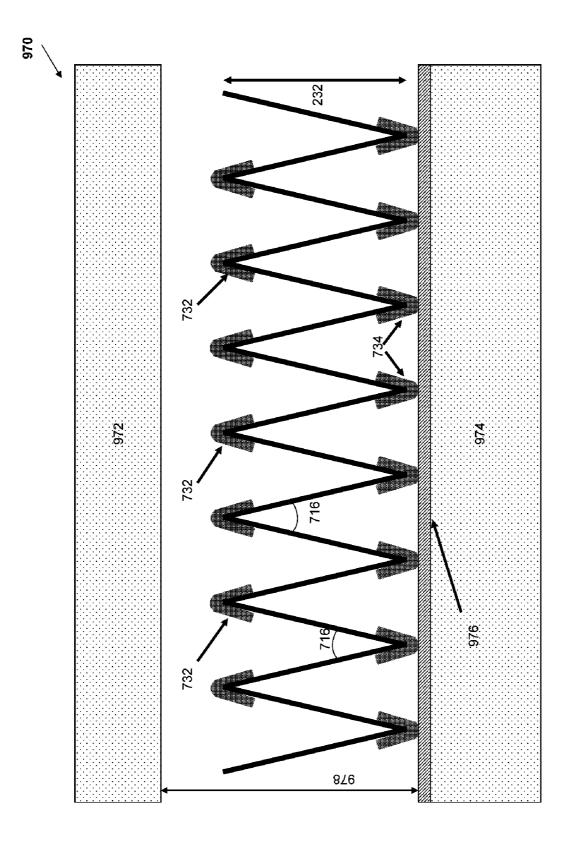

[0119] FIG. 15 shows a quasi 3-D view 230 of an individual hexagonal-pyramid unit cell 202 of the TFSC substrate 200 shown above. The top hexagonal opening of the unit cell 202 forms the frontside self-aligned interconnected contacts of the thin-film solar cell (TFSC). Also shown in this view is the width (W) 231 of the semiconductor film forming the side-walls of the hexagonal-pyramid cell 202 and the height (H) 232 of the cell 202, and d/2 234.

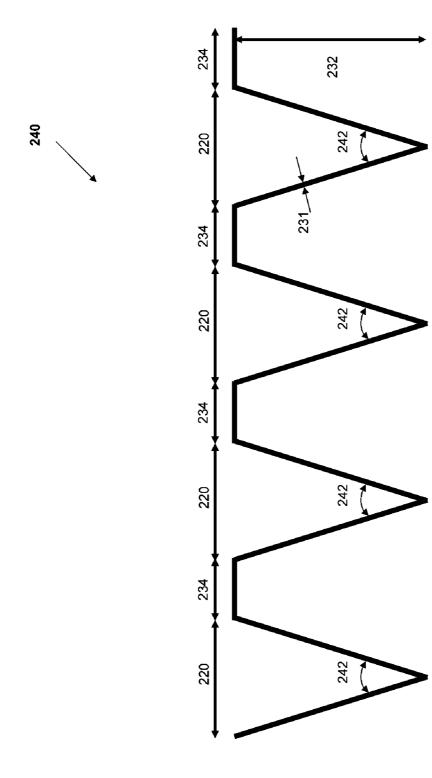

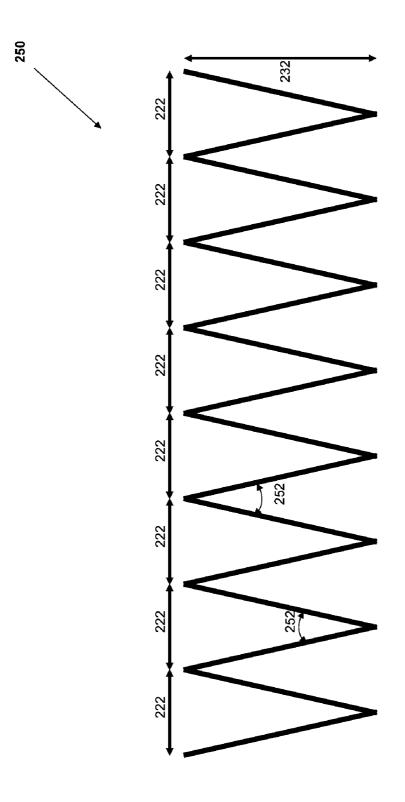

**[0120]** When referring to the following FIGURES, the YY and ZZ axes are shown in FIGS. **13** and **14**. FIG. **16** shows a ZZ cross-sectional-view **240** of the 3-D hexagonal-pyramid TFSC substrate **200**, showing the hexagonal-pyramid top aperture angles  $\beta$  **242**. The bottom tips **216** of the triangles are the rear tips of the hexagonal-pyramids (where the base contacts will be placed). The solid line shows the 3-D TFSC substrate thin-film silicon layer, with thickness **231** (in one embodiment, roughly 1 to 25 microns thick). FIG. **17** shows a YY cross-sectional-view **250** of the hexagonal-pyramid top aperture angles  $\alpha$  **252**.

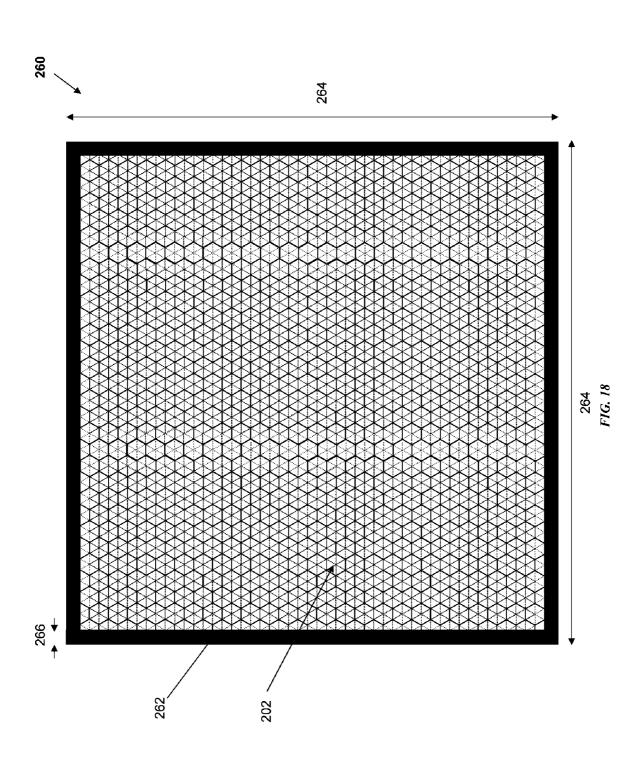

[0121] FIG. 18 shows a top view 260 of a honeycomb hexagonal-pyramid array design TFSC substrate 200, with a peripheral planar silicon frame 262. The design includes a periodic array of high-aspect-ratio (or low-aperture-angle) hexagonal-pyramid unit cells 202. In one embodiment, frame length (S) 264 is 125 mm to over 200 mm. Silicon Frame 262 may have the same thickness as the TFSC substrate 200 or may be much thicker (e.g., silicon frame thickness=5 to 500 microns). The top surface of the frame is also preferably used as the top solar cell interconnect (it is metallized along with the top honeycomb contacts, and is electrically connected to the honeycomb contacts). In one embodiment, the width 266 of the frame 262 is roughly 125 microns to 1 mm. The film thickness 231 of the TFSC substrate is roughly 2 to 30 microns, preferably 2 to 10 microns. Typically, there are millions (or as few as thousands) of these hexagonal-pyramid unit cells 202 form a large-area (e.g., 200 mm×200 mm) TFSC substrate 200.

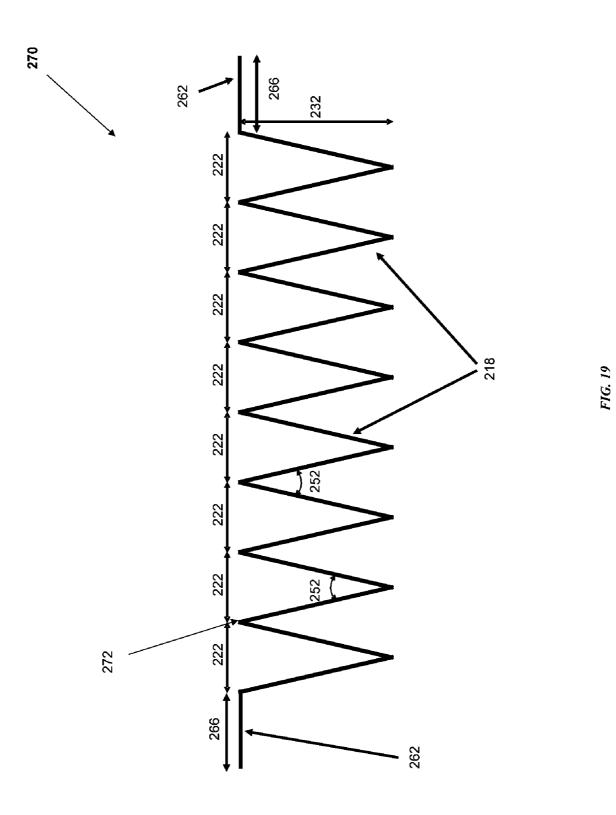

**[0122]** FIG. **19** shows a YY cross-sectional view **270** (not to scale) of an embodiment of a 3-D self-supporting hexagonalpyramid TFSC substrate **200** with thin square-shaped silicon frame **262** (like the frame **262** shown in FIG. **18**), with thickness the same as the film thickness **231**. The silicon frame width (W) **266** is between 50 and 250 microns. Note that the width of the top hexagonal honeycomb silicon ridges **272** is preferably much smaller than h **222** and H **232**. In one embodiment, the width of the top honeycomb ridges **272** is roughly 0.5 microns to less than 5 microns.

**[0123]** FIG. **20** shows a top view **280** of an alternative honeycomb hexagonal-pyramid array design TFSC substrate **200**, with a larger thickness **266** peripheral planar silicon frame **262**.

[0124] FIG. 21 shows a YY cross-sectional view 290 (not to scale) of an embodiment of a 3-D self-supporting hexagonalpyramid TFSC substrate 200 with thicker square-shaped silicon frame 262 (like the frame 262 shown in FIG. 20). Note that the thickness of the frame is not the same as the film thickness 231. Instead, the thick silicon frame may be roughly 100 to 500 microns thick. The silicon frame width (W) 266 is between 50 and 250 microns. The thick peripheral silicon frame may be preferably made of low-cost metallurgicalgrade silicon and may be attached to the 3-D TFSC substrate using one of the following methods: (i) thick silicon frame placed on the reusable silicon template and fused to the 3-D thin-film silicon film during the epitaxial silicon growth process; (ii) e-beam welding of the 3-D TFSC substrate to the thick silicon frame (after lift-off/release of the 3-D TFSC substrate from the reusable silicon template); or (iii) thermal bonding (under clamping pressure) of the thick silicon frame to the 3-D TFSC substrate. The thick silicon frame maybe used for enhanced mechanical support and rigidity of the 3-D TFSC substrate.

[0125] The previous section illustrated a preferred embodiment of a hexagonal-pyramid TFSC substrate. Alternative embodiments may use alternative designs for the unit cells such as inverted pyramid unit cells with polygon bases, including square pyramid, triangular pyramid, etc.; other embodiments may include 3-D TFSC substrates with V-groove or orthogonal V-groove patterns, etc. For example, FIG. 22 shows a top view 300 of a 3-D TFSC substrate with a square-pyramid unit cell structure. The primary difference between this pattern and the preferred embodiment hexagonal-pyramid unit cell pattern is the top base (or pyramid aperture) geometry (square base versus hexagonal base for the inverted pyramid unit cells). The vertical height and base area values of the square pyramid unit cells are comparable to those of the hexagonal-pyramid unit cells (similar considerations apply). Another example is shown in FIG. 23, which shows a top view 310 of a 3-D TFSC substrate with a triangular-pyramid unit cell structure. The primary difference between this pattern and the preferred embodiment hexagonal-pyramid unit cell pattern is the top base or pyramid aperture geometry (triangular base versus hexagonal base for the inverted pyramid unit cells). The vertical height and base area values of the triangular pyramid unit cells are comparable to those of the hexagonal-pyramid unit cells (similar considerations apply).