(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5925507号

(P5925507)

(45) 発行日 平成28年5月25日(2016.5.25)

(24) 登録日 平成28年4月28日(2016.4.28)

(51) Int.Cl.

G06F 11/18 (2006.01)

F 1

G06F 11/18 310C

請求項の数 12 (全 11 頁)

(21) 出願番号 特願2012-24235 (P2012-24235)

(22) 出願日 平成24年2月7日 (2012.2.7)

(65) 公開番号 特開2013-161354 (P2013-161354A)

(43) 公開日 平成25年8月19日 (2013.8.19)

審査請求日 平成26年8月6日 (2014.8.6)

前置審査

(73) 特許権者 000005108

株式会社日立製作所

東京都千代田区丸の内一丁目6番6号

(74) 代理人 110000062

特許業務法人第一国際特許事務所

(72) 発明者 勝田 敬一

茨城県日立市大みか町七丁目1番1号 株式会社 日立製作所 日立研究所内

(72) 発明者 前川 景示

茨城県日立市大みか町七丁目1番1号 株式会社 日立製作所 日立研究所内

(72) 発明者 柴田 直樹

茨城県日立市大みか町七丁目1番1号 株式会社 日立製作所 日立研究所内

最終頁に続く

(54) 【発明の名称】データ照合装置、照合方法及びそれを用いた安全保安システム

## (57) 【特許請求の範囲】

## 【請求項 1】

複数のデータ元から送出されるデータに基づいて同期信号を生成する同期信号生成回路と、前記同期信号に基づいて同期調整信号を生成する同期ずれ検知回路と、前記同期調整信号に基づいて照合タイミングを調整して前記データを照合する同期調整照合回路とを有し、

前記同期ずれ検知回路は、前記同期信号生成回路から入力される前記同期信号を格納する前記複数のデータ元に対応する複数の同期信号用シフトレジスタと、格納された前記同期信号を該同期信号に固有の性質に基づいて比較することで同期ずれを検知し前記同期調整信号を生成する同期ずれ検知部とを有し、

前記同期信号用シフトレジスタは、複数段で構成され、

前記同期ずれ検知部は、複数段の前記同期信号用シフトレジスタに格納された複数ビットの同期信号を比較することで同期ずれを検知し、

前記同期調整照合回路は、前記複数のデータ元から送出される複数の前記データを格納する各データ元に対応した複数の照合用シフトレジスタと、前記同期ずれ検知回路から入力される前記同期調整信号に基づいて出力するデータを選択するマルチブレクサと、前記データを照合する排他的論理回路と、を有し、

前記複数のデータ元から送出される同期の取れていない可能性のあるデータを照合することを特徴とするデータ照合装置。

## 【請求項 2】

10

20

請求項 1 に記載のデータ照合装置において、前記同期信号生成回路は、前記複数のデータ元からある特定のビット列が入力されたことを検知する前記複数のデータ元に対応する複数の同期トリガー検出部と、前記特定のビット列を検知したことをトリガーとして前記同期信号を生成する前記複数のデータ元に対応する複数の同期信号生成部とを有することを特徴とするデータ照合装置。

【請求項 3】

請求項 1 または請求項 2 に記載のデータ照合装置において、前記同期調整照合回路は、前記複数のデータ元に対応する複数の直交波形生成回路と複数の排他的論理回路とを有し、前記複数のデータ元から送出される前記データが一致している場合には、信号のレベルが一定間隔で変化する固有の信号を出力することを特徴とするデータ照合装置。 10

【請求項 4】

複数の C P U とデータ照合装置とからなり、前記複数の C P U では同じデータ処理を実行し、前記データ照合装置には前記複数の C P U から送出されるデータに基づいて同期信号を生成する同期信号生成回路と、前記同期信号に基づいて同期調整信号を生成する同期ずれ検知回路と、前記同期調整信号に基づいて照合タイミングを調整して前記データを照合する同期調整照合回路とを実装し、

前記同期ずれ検知回路は、前記同期信号生成回路から入力される前記同期信号を格納する前記複数の C P U に対応する複数の同期信号用シフトレジスタと、格納された前記同期信号を該同期信号に固有の性質に基づいて比較することで同期ずれを検知し前記同期調整信号を生成する同期ずれ検知部とを有し、 20

前記同期信号用シフトレジスタは、複数段で構成され、

前記同期ずれ検知部は、複数段の前記同期信号用シフトレジスタに格納された複数ビットの同期信号を比較することで同期ずれを検知し、

前記同期調整照合回路は、前記 C P U から送出される前記データを格納する前記複数の C P U に対応する複数の照合用シフトレジスタと、前記同期ずれ検知回路から入力される前記同期調整信号に基づいて出力するデータを選択する前記複数の C P U に対応する複数のマルチプレクサと、前記データを照合する排他的論理回路とを有し、

前記複数の C P U から送出される同期の取れていない可能性のあるデータを照合することを特徴とする安全保安システム。 30

【請求項 5】

請求項 4 に記載の安全保安システムにおいて、前記複数の C P U を異なるクロックで動作させ、前記複数の C P U から送出される前記データを前記データ照合装置に実装された同期調整照合回路で照合することによって、前記クロックのいずれかに障害が発生した場合に該障害を検出できることを特徴とする安全保安システム。

【請求項 6】

請求項 4 または請求項 5 に記載の安全保安システムにおいて、前記複数の C P U は 2 つの異型の C P U であり、前記 2 つの C P U から送出される前記データを前記データ照合装置に実装された同期調整照合回路で照合することによって、どちらか一方の C P U に障害が内在している場合にも該障害を検出できることを特徴とする安全保安システム。 40

【請求項 7】

請求項 4 乃至請求項 6 のいずれか 1 項に記載の安全保安システムにおいて、前記同期信号生成回路は、前記複数の C P U からある特定のビット列が入力されたことを検知する前記複数の C P U に対応する複数の同期トリガー検出部と、前記特定のビット列を検知したことをトリガーとして前記同期信号を生成する前記複数の C P U に対応する複数の同期信号生成部とを有することを特徴とする安全保安システム。

【請求項 8】

請求項 4 乃至請求項 7 のいずれか 1 項に記載の安全保安システムにおいて、前記同期調整照合回路は、前記複数の C P U に対応する複数の直交波形生成回路と複数の排他的論理回路とを有し、前記複数の C P U から送出される前記データが一致している場合には、信号のレベルが一定間隔で変化する固有の信号を出力することを特徴とする安全保安シス 50

テム。

【請求項 9】

請求項4乃至請求項8のいずれか1項に記載の安全保安システムにおいて、前記データ照合装置はFPGAに実装されることを特徴とする安全保安システム。

【請求項 10】

複数のデータ元から送出されるデータに基づいて同期信号を生成し、

前記同期信号に基づいて同期調整信号を生成し、

前記同期調整信号に基づいて照合タイミングを調整して前記データを照合し、

前記複数のデータ元から送出される同期の取れていない可能性のあるデータを照合する

データ照合方法であって、

前記同期信号を前記複数のデータ元に対応する同期信号用シフトレジスタに格納し、

複数段の前記同期信号用シフトレジスタに格納された前記同期信号を該同期信号の固有の性質に基づいて比較することで同期ずれを検知し、前記同期調整信号を生成し、

前記データを照合する際に、前記複数のデータ元に対応する複数の照合用シフトレジスタに前記複数のデータ元から送出される前記データを格納し、

前記複数のデータ元に対応する複数のマルチプレクサにより前記同期調整信号に基づいて出力するデータを選択し、

前記データを照合することを特徴とするデータ照合方法。

【請求項 11】

請求項10に記載のデータ照合方法において、

前記データ元からある特定のビット列が入力されたことを検知し、

前記特定のビット列を検知したことをトリガーとして前記同期信号を生成することを特徴とするデータ照合方法。

【請求項 12】

請求項10または請求項11に記載のデータ照合方法において、

前記データ元から送出される前記データが一致している場合には、信号のレベルが一定間隔で変化する固有の信号を出力することを特徴とするデータ照合方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、データ照合装置、照合方法及びそれを用いた安全保安システムに関し、列車制御システム（ATP、ATC）や連動装置システムなどの鉄道信号システムに適用可能なデータ照合装置、照合方法及び安全保安システムに関する。

【背景技術】

【0002】

本技術分野の背景技術として、特開平5-120047（特許文献1）がある。この公報には、「コンピュータを用いた制御システムにおいて、高い信頼性と安全性を確保するための1つの方式として完全クロック同期形2重系システムがある」と記載されている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開平5-120047号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

特許文献1には、高い安全性を要するコンピュータを用いた制御システムにおいて、2個のCPUと、それらから出力されるデータの一致・不一致を照合するフェールセーフな照合回路を用いてCPUのフォルトを検知する仕組みが記載されている。しかし、特許文献1の完全クロック同期形2重系回路は、2個のCPUから送出されるデータの同期がず

10

20

30

40

50

れた場合にはデータを正確に照合することができない。

【0005】

つまり、このような回路では、2個のCPUから出力されるデータの同期が完全には取れない可能性のある場合、例えば、2個のCPUが独立したクロックで動作する場合やそもそも異型のCPUであるような場合、正確にCPUのフォルトを検知することが難しい。

【0006】

そこで、本発明は、少なくとも2つのCPUから送出されるデータの同期ずれを検知し、照合タイミングを調整して前記データを照合することのできるデータ照合装置、照合方法及びそれを用いた安全保安システムを提供することを目的とする。

10

【課題を解決するための手段】

【0007】

上記課題を解決するために、本発明のデータ照合装置は、複数のデータ元から送出されるデータに基づいて同期信号を生成する同期信号生成回路と、前記同期信号に基づいて同期調整信号を生成する同期ずれ検知回路と、前記同期調整信号に基づいて照合タイミングを調整してデータを照合する同期調整照合回路とを有し、前記同期調整照合回路は、前記複数のデータ元から送出される複数の前記データを格納する各データ元に対応した複数の照合用シフトレジスタと、前記同期ずれ検知回路から入力される前記同期調整信号に基づいて出力するデータを選択するマルチプレクサと、前記データを照合する排他的論理和回路と、を有し、前記複数のデータ元から送出される同期の取れない可能性のあるデータを照合することを特徴とする。

20

【0008】

また、本発明の安全保安システムは、複数のCPUとデータ照合装置とからなり、前記複数のCPUでは同じデータ処理を実行し、前記データ照合装置には前記複数のCPUから送出されるデータに基づいて同期信号を生成する同期信号生成回路と、前記同期信号に基づいて同期調整信号を生成する同期ずれ検知回路と、前記同期調整信号に基づいて照合タイミングを調整して前記データを照合する同期調整照合回路とを実装し、前記同期調整照合回路は、前記CPUから送出される前記データを格納する前記複数のCPUに対応する複数の照合用シフトレジスタと、前記同期ずれ検知回路から入力される前記同期調整信号に基づいて出力するデータを選択する前記複数のCPUに対応する複数のマルチプレクサと、前記データを照合する排他的論理和回路とを有し、前記複数のCPUから送出される同期の取れない可能性のあるデータを照合することを特徴とする。

30

また、本発明のデータ照合方法は、複数のデータ元から送出されるデータに基づいて同期信号を生成し、前記同期信号に基づいて同期調整信号を生成し、前記同期調整信号に基づいて照合タイミングを調整して前記データを照合し、前記複数のデータ元から送出される同期の取れない可能性のあるデータを照合するデータ照合方法であって、前記データを照合する際に、前記複数のデータ元に対応する複数の照合用シフトレジスタに前記複数のデータ元から送出される前記データを格納し、前記複数のデータ元に対応する複数のマルチプレクサにより前記同期調整信号に基づいて出力するデータを選択し、前記データを照合することを特徴とする。

40

【発明の効果】

【0009】

本発明によれば、複数のデータ元から出力されるデータの同期ずれを検知し、照合タイミングを調整してデータを照合することのできるデータ照合装置、照合方法及びそれを用いた安全保安システムを提供することができる。上記した以外の課題、構成及び効果は、以下の実施形態の説明により明らかにされる。

【図面の簡単な説明】

【0010】

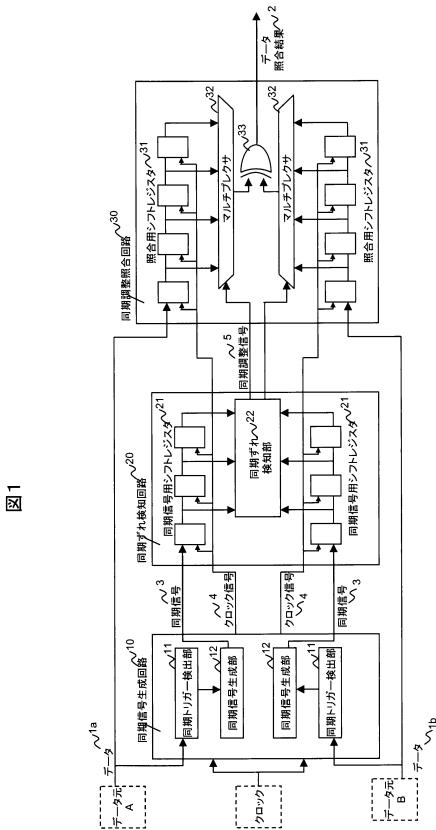

【図1】図1は、本発明の実施例1のデータ照合装置の構成図の例である。

50

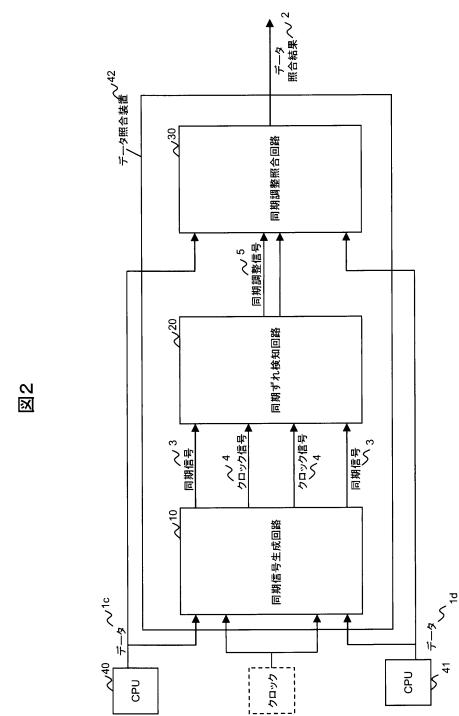

【図2】図2は、本発明の実施例2の安全保安システムの構成図の例である。

【図3】図3は、本発明の実施例3の装置内の故障の潜在化を防ぐことのできる安全保安システムの構成例である。

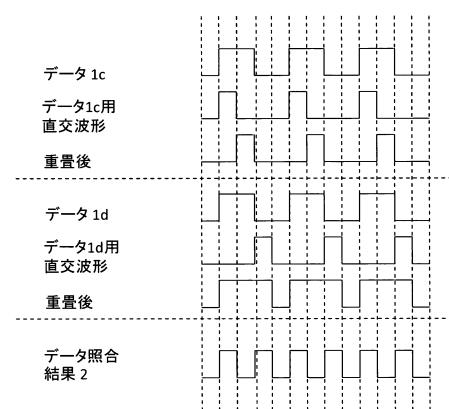

【図4】図4は、本発明の実施例3の装置内の故障の潜在化を防ぐことのできる安全保安システムにおける直交関数と照合結果信号の例を示す図である。

【発明を実施するための形態】

【0011】

以下、本発明の実施の形態について図面を用いて説明する。

【実施例1】

【0012】

10

本実施例では、複数のデータ元から送出されるデータの同期ずれを検知し、照合タイミングを調整してデータを照合することのできるデータ照合装置の例を説明する。

【0013】

図1は、本発明の実施例1のデータ照合装置の構成図の例である。本実施例のデータ照合装置は、同期信号生成回路10、同期ずれ検知回路20、同期調整照合回路30から構成され、2つのデータ元から送出される同期の取れていない可能性のあるデータを照合する場合を想定する。

【0014】

同期信号生成回路10は、データ元ごとに用意される同期トリガー検出部11と同期信号生成部12とから構成される。

20

【0015】

同期トリガー検出部11は、各データ元から入力されるデータ1a、データ1bの中から、ある特定のビット列が入力された場合に、これを検知して同期信号生成部12へデータ元からある特定のビット列が入力されたことを伝達する。

【0016】

特定のビット列は、データ元から送出されるデータの传送プロトコルに適したものであればどのようなものでもよく、例えば、調歩同期方式で使われるスタートビットや、イーサネット(登録商標)で使われるプリアンブルなどが考えられる。なお、トリガーを検出するためには十分周期の短いクロック信号が必要であるが、これについては、外部から入力される構成でもよいし、内部にクロックを持つ構成でもよい。

30

【0017】

同期信号生成部12は、同期トリガー検出部11からデータ元からある特定のビット列が入力されたことを伝達された場合に同期信号3を生成し、この同期信号3を同期ずれ検知回路20へ伝達する。同期信号3は、同期ずれを観測できる信号であればどのようなものでもよく、例えば、M系列信号などが考えられる。

【0018】

さらに、同期信号生成回路10は、同期信号3を比較するためや、照合タイミングを調整するために十分周期の短いクロック信号4を生成し、同期ずれ検知回路20、同期調整照合回路30に提供する。

【0019】

40

同期ずれ検知回路20は、データ元ごとに用意される同期信号用シフトレジスタ21と、それらの同期信号3を比較する同期ずれ検知部22とから構成される。

【0020】

同期信号用シフトレジスタ21は、データ元ごとに同期信号生成回路10から入力される同期信号3を格納する。

【0021】

同期ずれ検知部22は、同期信号用シフトレジスタ21に格納された同期信号3を、その固有の性質に基づいて比較することでそれぞれのデータ元から送出されるデータ1a、データ1bの同期ずれを検知する。例えば、同期信号3が、周期が7である1001110のようなM系列信号の場合、同時に3ビットを比較することで同期ずれを検知すること

50

ができる。一方が 100 の時、他方が 001 の場合は 1 ビット、011 の場合は 2 ビット、111 の場合は 3 ビットだけ同期がずれていると検知できる。

【0022】

なお、周期が 7 である同期信号 3 では、7 ビット以上のずれを検知することができない。従って、同期ずれを検知するデータ 1a、データ 1b の両者間で想定されるビットずれを予め検討し、これに対して十分に長い周期の同期信号 3 を使用することが望ましい。また、同期信号用シフトレジスタ 21 についても、使用する同期信号 3 の性質を踏まえて、ビットずれを検知するのに十分に長い段数を備えることが望ましい。

【0023】

このように検知したビットずれを同期調整信号 5 として同期調整照合回路 30 に伝達する。同期調整信号 5 は、ずれているビット数を識別できる信号であればどのようなものでもよく、例えば、ずれているビット数の分だけずらしたマルチプレクサ 32 の選択制御信号などが考えられる。

【0024】

同期調整照合回路 30 は、データ元ごとに用意される照合用シフトレジスタ 31 とマルチプレクサ 32 と、各データ元からのデータ 1a、データ 1b を照合する排他的論理和回路 33 とから構成される。

【0025】

照合用シフトレジスタ 31 は、データ元から入力されるデータ 1a、データ 1b を格納する。なお、4 段のシフトレジスタでは 4 ビット以上のずれを調整することができない。従って、両者間で想定されるビットずれを予め検討し、これに対して十分に長い段数の照合用シフトレジスタ 31 を備えることが望ましい。

【0026】

マルチプレクサ 32 は、同期ずれ検知回路 20 から入力される同期調整信号 5 に基づいて、照合用シフトレジスタ 31 に格納されているデータを選択して出力し、排他的論理和回路 33 がそれらのデータ 1a、データ 1b を照合してデータ照合結果 2 を出力する。

【0027】

このように、本発明のデータ照合装置によって、複数のデータ元から送出されるデータ 1a、データ 1b が完全には同期していない場合であっても、そのデータ 1a、データ 1b の同期ずれを検知し、照合タイミングを調整してデータ 1a、データ 1b を照合することが可能になる。

【実施例 2】

【0028】

本実施例では、安全保安システムの複数の C P U に同じデータ処理を実行させ、その C P U から送出されるデータの同期ずれをデータ照合装置で検知し、照合タイミングを調整してデータを照合することのできる安全保安システムの例を説明する。

【0029】

図 2 は、安全保安システムの 2 つの C P U とデータ照合装置で構成される本発明の安全保安システムの構成図の例である。本実施例の安全保安システムは、安全保安システムの C P U 40、C P U 41、データ照合装置 42 から構成される。なお、データ照合装置 42 は、実施例 1 で説明したデータ照合装置と同様の構成で、同期信号生成回路 10、同期ずれ検知回路 20、及び同期調整照合回路 30 から構成される。

【0030】

この安全保安システムでは、まず C P U 40 と C P U 41 で、安全保安システムの同じデータ処理を実行させる。その処理結果として出力されるそれぞれのデータ 1c、データ 1d を、データ照合装置 42 の同期信号生成回路 10 と同期調整照合回路 30 に入力する。以後、実施例 1 と同様の動作で、C P U 40 と C P U 41 から出力される同期の取れていない可能性のあるデータ 1c とデータ 1d をデータ照合装置 42 で照合する。

【0031】

この安全保安システムでは、C P U にフォルト（障害、問題）が発生してデータ処理に

10

20

30

40

50

誤りが発生した場合など、データ照合の結果が不一致と判定された場合には、割込み処理によるCPUの停止、電源の切断処理、あるいは、外部インターフェースの遮断処理などを実施することによりシステムの安全性を確保することができる。

#### 【0032】

さらに、本実施例の安全保安システムでは、CPU40とCPU41を異なるクロックで動作させる構成にすることが可能で、その場合、同一クロックで動作させる場合よりも高い安全性が確保できる。

#### 【0033】

具体的には、CPU40とCPU41を同一クロックで動作させた場合、クロックにフォルトが発生し両方のCPUの処理が遅くなっても、出力データの同期が必ずしもずれるわけではないので、データを照合してもそのフォルトを検知できない可能性が残る。

10

#### 【0034】

これに対し、CPU40とCPU41を異なるクロックで動作させる場合、どちらか一方のクロックにフォルトが発生した時には、データ1cとデータ1dが想定の許容範囲以上にずれて、データ照合の結果が不一致と判定されるため、このフォルトを検知することができる。なお、両方のクロックが正常な時には、データ1cとデータ1dのビットずれは想定の許容範囲内に収まり、データ照合の結果は一致と判定される。

#### 【0035】

また、本実施例の安全保安システムは、異型のCPUでCPU40とCPU41を構成にすることが可能で、その場合、同一CPUで構成される場合よりも高い安全性が確保できる。

20

#### 【0036】

具体的には、同一CPUで構成される場合、CPUに系統的なフォルトが内在していた時に、両CPUとも同じように誤った処理を行って誤ったデータを出力するため、データ1cとデータ1dを照合してもそのフォルトを検知できない。これに対し、異型のCPUで構成される場合、両方のCPUに同じように誤った処理を行って誤ったデータを出力するようなフォルトが存在することは考えにくく、その可能性は極めて低い。

#### 【0037】

従って、系統的なフォルトによって一方のCPUが誤ったデータを出力した場合には、その出力データは他方のCPUからの出力データとは極めて高い確率で異なることが期待でき、この時、データ照合の結果は不一致と判定され、このフォルトを検知することができる。

30

#### 【0038】

このように、本発明の安全保安システムによって、複数のCPUに同じデータ処理を実行させ、それらのCPUから出力される同期の取れていない可能性のあるデータを、照合タイミングを調整してデータを照合することが可能になる。

#### 【0039】

さらに、本発明の安全保安システムを構成する2つのCPUを異なるクロックで動作させ、あるいは、異型のCPUで構成する場合には、1つのクロックで2つの同型CPUを動作させる構成の従来の安全保安システムに比べて高い安全性を確保することができる。

40

#### 【実施例3】

#### 【0040】

本実施例では、複数のCPUからの送出されるデータの同期ずれを検知し、照合タイミングを調整してデータを照合するだけでなく、装置内の故障の潜在化を防ぐことのできるデータ照合装置を用いた安全保安システムの例を説明する。

#### 【0041】

本実施例の安全保安システムは、実施例2の安全保安システムの同期調整照合回路30のマルチブレクサ32と排他的論理和回路33との間に、直交波形生成回路34、直交波形生成回路35と排他的論理和回路36、排他的論理和回路37を追加することで、複数のCPUから送出されるデータ1c、データ1dが一致している場合に、信号のレベルが

50

一定間隔で変化する固有の信号を出力することができ、データ照合装置42内の半導体素子の故障や配線の絶縁不良による混触などによってデータ照合結果2が長期にわたって「一致」を意味するように固定されるような故障が潜在化することを防ぐことのできる安全保安システムの例である。

【0042】

図3は、本実施例の安全保安システムの同期調整照合回路30の構成図の例である。なお、前段の同期信号生成回路10、同期ずれ検知回路20の構成や動作は実施例1と同様である。

【0043】

まず、直交波形生成回路34、直交波形生成回路35で、それぞれ相関を持たない直交波形を発生させる。次に、排他的論理和回路36、排他的論理和回路37でマルチプレクサ32が選択して出力した各データに発生させた直交波形を重畠させる。最後に、直交波形が重畠された各データを排他的論理和回路33で照合する。この結果、複数のデータ元から送出されたデータ1c、データ1dが一致している場合には、信号のレベルが一定間隔で変化する固有のデータ照合結果2が出力される。直交波形は、どのようなものでもよく、例えば、直交性質を持つ、三角関数、Walsh-Hadamard関数、M系列、Waveletなどの直交関数から生成することが考えられる。図4に、直交波形とデータ照合結果2の例を示す。

【0044】

このように、本発明の安全保安システムによって、複数のCPUに同じデータ処理を実行させ、それらのCPUから出力される同期の取れていない可能性のあるデータを、照合タイミングを調整してデータを照合するだけでなく、「一致」を意味する状態で固定されるような故障が潜在化することを防ぐことが可能になる。

【実施例4】

【0045】

本実施例では、データ照合装置42の回路論理を、ハードウェア記述言語を用いて記述し、この論理をFPGA(Field Programmable Gate Array)に実装する。

【0046】

半導体分野の技術革新は、鉄道などの分野で使用される安全保安システムの製品寿命に比べて速いため、安全保安システムに使われる電子回路は、電子部品の改廃に対応していかなければならない。もし、回路の中核となる部品が入手できなくなれば、新しい部品を使って再設計しなければならない。さらに、集積度の高い半導体では、完全互換部品が存在しない場合もあり、そのような場合には再設計するために非常に高いコストを要する。

【0047】

これに対し、FPGAは、ハードウェア記述言語を用いて任意の論理回路を実装できる集積回路であり、一度、回路論理をハードウェア記述言語で記述しておけば、同じ回路論理を様々な種類のFPGAに実装することができる。

【0048】

従って、本実施例の安全保安システムは、半導体技術の進化による電子部品の改廃に合わせて再設計する必要はなく、一度ハードウェア記述言語で記述したデータ照合装置42の回路論理を、将来に渡ってその時に入手可能なFPGAに実装することで実現することができ、長期間低コストで製品ラインナップを維持できる。

【0049】

なお、本発明は上記した実施例に限定されるものではなく、様々な変形例が含まれる。上記した実施例は本発明を分かりやすく説明するために詳細に説明したものであり、必ずしも説明した全ての構成を備えるものに限定されるものではない。

【0050】

例えば、データ元やクロックの一部または全部を、本発明のデータ照合装置や安全保安システムに含める構成も可能であるし、本発明の同期信号発生回路、同期ずれ検知回路、

10

20

30

40

50

同期調整照合回路を個別のチップに実装する構成や、上記の構成要素の一部または全部を同一のチップに実装する構成も可能である。

【符号の説明】

【0051】

- |         |              |    |

|---------|--------------|----|

| 1 a     | データ          |    |

| 1 b     | データ          |    |

| 1 c     | データ          |    |

| 1 d     | データ          |    |

| 2       | データ照合結果      |    |

| 3       | 同期信号         | 10 |

| 4       | クロック信号       |    |

| 5       | 同期調整信号       |    |

| 1 0     | 同期信号発生回路     |    |

| 1 1     | 同期トリガー検出部    |    |

| 1 2     | 同期信号生成部      |    |

| 2 0     | 同期ずれ検知回路     |    |

| 2 1     | 同期信号用シフトレジスタ |    |

| 2 2     | 同期ずれ検知部      |    |

| 3 0     | 同期調整照合回路     |    |

| 3 1     | 照合用シフトレジスタ   | 20 |

| 3 2     | マルチプレクサ      |    |

| 3 3     | 排他的論理和回路     |    |

| 3 4、3 5 | 直交波形生成回路     |    |

| 3 6、3 7 | 排他的論理和回路     |    |

| 4 0     | C P U        |    |

| 4 1     | C P U        |    |

| 4 2     | データ照合装置      |    |

| A       | データ元         |    |

| B       | データ元         |    |

【 四 1 】

【 义 3 】

【 四 2 】

【 図 4 】

四

---

フロントページの続き

(72)発明者 今本 健二

茨城県日立市大みか町七丁目1番1号 株式会社 日立製作所 日立研究所内

(72)発明者 金川 信康

茨城県日立市大みか町七丁目1番1号 株式会社 日立製作所 日立研究所内

(72)発明者 渡部 悅

茨城県ひたちなか市市毛1070番地 株式会社 日立製作所 交通システム事業部内

審査官 田中 幸雄

(56)参考文献 特開平08-297588 (JP, A)

特開2006-060507 (JP, A)

特開平09-288150 (JP, A)

特開2002-207607 (JP, A)

特開2009-94891 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 06 F 11 / 18