(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4917012号

(P4917012)

(45) 発行日 平成24年4月18日(2012.4.18)

(24) 登録日 平成24年2月3日(2012.2.3)

|              |           |

|--------------|-----------|

| (51) Int.Cl. | F 1       |

| HO1L 21/8238 | (2006.01) |

| HO1L 27/092  | (2006.01) |

| HO1L 29/423  | (2006.01) |

| HO1L 29/49   | (2006.01) |

| HO1L 21/28   | (2006.01) |

請求項の数 25 (全 22 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2007-500919 (P2007-500919)  |

| (86) (22) 出願日 | 平成17年2月22日 (2005.2.22)        |

| (65) 公表番号     | 特表2007-524252 (P2007-524252A) |

| (43) 公表日      | 平成19年8月23日 (2007.8.23)        |

| (86) 国際出願番号   | PCT/US2005/005565             |

| (87) 国際公開番号   | W02005/083780                 |

| (87) 国際公開日    | 平成17年9月9日 (2005.9.9)          |

| 審査請求日         | 平成20年2月5日 (2008.2.5)          |

| (31) 優先権主張番号  | 10/786,901                    |

| (32) 優先日      | 平成16年2月25日 (2004.2.25)        |

| (33) 優先権主張国   | 米国(US)                        |

|           |                                                                                                                                           |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 390009531<br>インターナショナル・ビジネス・マシーンズ・コーポレーション<br>INTERNATIONAL BUSINESS MACHINES CORPORATION<br>アメリカ合衆国10504 ニューヨーク州<br>アーモンク ニュー オーチャード ロード |

| (74) 代理人  | 100108501<br>弁理士 上野 剛史                                                                                                                    |

| (74) 代理人  | 100112690<br>弁理士 太佐 種一                                                                                                                    |

| (74) 代理人  | 100091568<br>弁理士 市位 嘉宏                                                                                                                    |

最終頁に続く

(54) 【発明の名称】相補型金属酸化物半導体(CMOS)を形成する方法及びその方法に従い製造されたCMOS

## (57) 【特許請求の範囲】

## 【請求項1】

シリサイド接点を有する相補型金属酸化物半導体(CMOS)を形成する方法であって、

半導体基板上に配置される複数のポリSiゲートを備える構造物を準備する工程、前記複数のポリSiゲートおよび前記半導体基板を備える前記構造物上にシリサイド金属を堆積する工程、

前記シリサイド金属の堆積後に、各ポリSiゲートの間に凹形のリフロー材料を形成する工程、

前記リフロー材料の形成後に、エッティングプロセスを用いて前記複数のポリSiゲートのそれぞれの上からシリサイド金属を選択除去して前記複数のポリSiゲートのそれぞれの上部表面を露出させる工程であって、前記エッティングプロセスは前記複数のポリSiゲートをエッティングしない、前記露出させる工程、

前記シリサイド金属の除去後に、前記凹形のリフロー材料を除去する工程、および前記リフロー材料の除去後に、前記構造物をアニールし、これによって、前記複数のポリSiゲートのそれぞれの間にシリサイド接点領域を形成する工程

を含む、前記方法。

## 【請求項2】

シリサイド接点を有する相補型金属酸化物半導体(CMOS)構造物を形成する方法であって、

10

半導体基板上に配置される複数のポリSiゲートを備える構造物を準備する工程、

前記複数のポリSiゲートおよび前記半導体基板を備える前記構造物上に金属層および

キャッピング層を備える二層を形成する工程、

前記二層の形成後に、前記半導体基板上に平坦化材料を形成する工程、

前記平坦化材料の形成後に、各ポリSiゲート上で前記金属層を露出させる工程、

前記金属層の露出後に、エッチングプロセスを用いて前記複数のポリSiゲートのそれ

ぞれの上から前記金属層を選択除去して前記複数のポリSiゲートのそれぞれの上部表面

を露出させる工程であって、前記エッチングプロセスは前記複数のポリSiゲートをエッ

チングしない、前記露出させる工程、

前記複数のポリSiゲートのそれぞれの上部表面の露出後に、前記平坦化材料を除去す

る工程、および 10

前記平坦化材料の除去後に、前記構造物をアニールし、これによって、前記複数のポリ

Siゲートのそれぞれの間にシリサイド接点領域を形成する工程

を含む、前記方法。

【請求項3】

シリサイド接点を有する相補型金属酸化物半導体(CMOS)構造物を形成する方法であ

って、

半導体基板上に配置される複数のポリSiゲートを備える構造物を準備する工程、

前記複数のポリSiゲートおよび前記半導体基板を備える前記構造物上にシリサイド金

属を堆積する工程、 20

前記シリサイド金属の堆積後に、各ポリSiゲートの間に凹形のリフロー材料を形成す

る工程、

前記リフロー材料の形成後に、前記複数のポリSiゲートのそれぞれの上からシリサイ

ド金属を除去する工程、

前記シリサイド金属の除去後に、前記凹形のリフロー材料を除去する工程、および

前記リフロー材料の除去後に、前記構造物をアニールし、これによって、前記複数のポ

リSiゲートのそれぞれの間にシリサイド接点領域を形成する工程

を含む、前記方法。

【請求項4】

シリサイド接点を有する相補型金属酸化物半導体(CMOS)構造物を形成する方法であ

って、 30

半導体基板上に配置される複数のポリSiゲートを備える構造物を準備する工程、

前記複数のポリSiゲートおよび前記半導体基板を備える前記構造物上に金属層および

キャッピング層を備える二層を形成する工程、

前記二層の形成後に、前記半導体基板上に平坦化材料を形成する工程、

前記平坦化材料の形成後に、各ポリSiゲート上で前記金属層を露出させる工程、

前記金属層の露出後に、前記複数のポリSiゲートのそれぞれの上から前記金属層を除

去する工程、および

前記平坦化材料の除去後に、前記構造物をアニールし、これによって、前記複数のポリ

Siゲートのそれぞれの間にシリサイド接点領域を形成する工程 40

を含む、前記方法。

【請求項5】

前記エッチングプロセスによって形成される前記露出されるポリSiゲートは同じ高さ

を有する、請求項3又は4に記載の方法。

【請求項6】

前記凹形のリフロー材料は、反射防止コーティングまたはスピノンオン誘電体を含む、請

求項1又は3に記載の方法。

【請求項7】

前記凹形のリフロー材料を形成する工程は、堆積およびオプションのエッチングを含む

、請求項1、3又は6のいずれか一項に記載の方法。 50

## 【請求項 8】

前記シリサイド金属を除去する工程は、ウェットエッティングプロセスを含む、請求項1～7のいずれか一項に記載の方法。

## 【請求項 9】

前記シリサイド接点領域を形成する工程後に、SiO<sub>2</sub>およびSi<sub>3</sub>N<sub>4</sub>を含むキャッピング二層を堆積し、平坦化させることによって金属シリサイドゲートを形成する工程、オプションのウェットエッティングプロセスを実行して前記SiO<sub>2</sub>を除去する工程、選択RIEプロセスを実行して前記ゲート上の前記Si<sub>3</sub>N<sub>4</sub>を除去する工程、前記除去する工程後に、前記ゲート上にシリサイド金属を形成する工程、および前記シリサイド金属を形成後に、サリサイドプロセスを実行する工程

をさらに含む、請求項1～8のいずれか一項に記載の方法。

## 【請求項 10】

前記シリサイド金属は、Ti、Ta、W、Co、Ni、Pt、Pd、またはそれらの合金を含む、請求項9に記載の方法。

## 【請求項 11】

前記シリサイド金属は、Co、Ni、またはPtである、請求項10に記載の方法。

## 【請求項 12】

前記アニールする工程は、300～600の温度で実行される少なくとも第一のアニールする工程を含む、請求項1～11のいずれか一項に記載の方法。

## 【請求項 13】

600～800の温度で実行されるオプションの第二のアニールする工程をさらに含む、請求項12に記載の方法。

## 【請求項 14】

前記キャッピング層は、TiN、W、またはTiを含む、請求項2又は4に記載の方法

## 【請求項 15】

前記平坦化材料は、フォトレジストまたは低温度酸化物を含む、請求項2又は4に記載の方法。

## 【請求項 16】

前記露出させる工程は、前記平坦化材料の化学機械研磨、および前記キャッピング層のエッティングを含む、請求項2又は4に記載の方法。

## 【請求項 17】

前記各ポリSiゲートの上からの前記金属含有シリサイド金属を除去する工程は、ウェットエッティングプロセスを含む、請求項2又は4に記載の方法。

## 【請求項 18】

前記凹形のリフロー材料は、前記複数のポリSiゲートの高さよりも低い上部表面を有する、請求項1又は3に記載の方法。

## 【請求項 19】

前記凹形のリフロー材料は、前記複数のポリSiゲートの各ポリSiゲートの間にだけ配置される、請求項18に記載の方法。

## 【請求項 20】

前記平坦化材料を形成する工程において、前記平坦化材料は、前記複数のポリSiゲートの高さよりも高くなるような厚さを有する、請求項2又は4に記載の方法。

## 【請求項 21】

前記平坦化材料の形成後であって、前記金属層を露出させる工程の前に、前記平坦化材料が形成されずに露出されている前記キャッピング層を除去する工程をさらに含む、請求項2又は4に記載の方法。

## 【請求項 22】

前記アニール後に、残りの前記キャッピング層を除去する工程をさらに含む、請求項2に記載の方法。

10

20

30

40

50

**【請求項 2 3】**

前記残りのキャッピング層を除去する工程後に、残りの前記金属層を除去する工程をさらに含む、請求項 2 2 に記載の方法。

**【請求項 2 4】**

請求項 1 若しくは 3、又は、請求項 6、7、18 若しくは 19 に記載の方法に従い製造された相補型金属酸化物半導体 (C M O S)。

**【請求項 2 5】**

請求項 2 若しくは 4、又は、請求項 14 ~ 17 若しくは 20 ~ 23 に記載の方法に従い製造された相補型金属酸化物半導体 (C M O S)。

**【発明の詳細な説明】**

10

**【技術分野】****【0 0 0 1】**

本発明は、半導体基板上の回路デバイスの製作に関する。より詳しくは、本発明は、実質的に同じ高さを有するシリサイド金属ゲートを形成するための相補型金属酸化物半導体 (C M O S) トランジスタ製作方法に関する。本発明は、ポリシリコンゲート導体の高さに影響を及ぼすことなく、シリサイド化ソース / ドレイン領域を形成する方法にも関する。

**【背景技術】****【0 0 0 2】**

従来技術全体を通じて、C M O S トランジスタのための通常のプロセスフローでは、金属ゲート集積化を実現することは難しいことが証明された。ほとんどの金属ゲート材料は、ソース / ドレイン (S / D) 接合活性化アニールに必要な高温プロセスの間にゲート誘電体と相互作用する。金属ゲートスタックが高温アニールを受けないようにする必要から、ゲートスタックを最後に作製し、後続のプロセスの間 500 より低温に保つ「ゲート最後」または「置換ゲート」プロセスが開発された。従来技術の置換ゲートプロセスによって、金属ゲート用の材料選択肢の数は増加するが、プロセスの複雑さおよびコストは増加する。

20

**【0 0 0 3】**

2002年11月20日出願の本出願人の米国特許出願第10/300,165号には、通常のC M O S トランジスタプロセスフローで金属ゲートシリサイドを形成するための「置換ゲート」プロセスを用いない手法が記載されている。この代替手法では、余分なプロセス工程の数を最小限にし、それによって複雑さを最小限に抑え、コストを低くしている。

30

**【0 0 0 4】**

「置換ゲート」プロセスを回避すると、非常に有利である。「165号出願に記載される手法の第二の利点は、標準的な物理的気相堆積法によってシリサイド金属を堆積することができる」とある。「165号出願では、ゲート誘電体上に金属を直接堆積しないので、化学的気相堆積 (C V D) 法も原子層堆積 (A L D) 法もまったく必要なく、そのため、プラズマの使用を排除することによって、ゲート誘電体の損傷は最小限になる。別の利点は、シリサイド金属ゲート形成後のゲート誘電体の不動態化が容易なことある。水素はシリサイドを通じて容易に拡散し、通常の炉アニールプロセスでの不動態化を可能にする。

40

**【0 0 0 5】**

通常のC M O S プロセスフローで金属ゲートシリサイドを形成することは、いくつかの工程の追加によって実現することができる。以下は、そのようなプロセスフローの例示である。通常、ソース / ドレイン領域のシリサイド化の間、ゲート多結晶S i (すなわちポリS i) 上には、窒化物または酸化物キャップ層が必要である。酸化物または窒化物キャップは、ソース / ドレインシリサイド化の間、ゲートポリS i領域のシリサイド化を防ぐ。ポリS iキャップを組み込むことを除けば、ソース / ドレイン領域上のシリサイド接点の形成全体を通じて、他のプロセス工程はすべて通常のものである。

50

## 【0006】

シリサイドソース／ドレイン接点形成後、通常、CMOS構造物上に窒化物／酸化物二層を堆積し、平坦化し、これによって、ソース／ドレインシリサイドおよびトレンチ・アイソレーション領域を被覆する。通常、化学機械研磨（CMP）プロセスを利用して、平坦化を実行する。CMPを実行し、これによって、ポリSiゲートスタック上のキャップを除去し、ポリSiを平坦化表面と接触させる。

## 【0007】

この時点では、通常の自己整合シリサイド（すなわちシリサイド）プロセスを用いてシリサイド金属ゲートを形成することができる。この後、通常のCMOS集積化フローに従って複数のバックエンド相互配線層を形成する。

10

## 【0008】

上記で説明したシリサイド金属ゲートプロセスの不利な点は、CMP後、ポリSiゲート高さ（厚さ）がゲートの長さによって変化することである。この変化は、（1）ゲートCMPの間のダイ内、ウエハ内、ウエハ間およびロット間の非一様性、および（2）シャロー・トレンチ・アイソレーション（STI）のCMPおよびその後の清掃の間に発生するSTIとシリコン表面（活性区域）との間に生じるトポグラフィーに起因する。

## 【0009】

STIのCMPは、STIからSiへのステップ高さを最小限にすることによって最適化されているが、そのようなステップ高さは依然存在し、デバイスのパターン密度によって変化する。そのようなステップ高さのあらゆる変化から、後のゲートCMPの間にゲート高さの変化が生じる。種々のパターン密度を有する構成要素に、ゲートCMP自体が、ゲート高さのまた別の非一様性および変化を付け加える。両方の組み合わせによって、所定のウエハ中に最大400 nmのゲート高さの変化が生じることがある。そのような変化があるときにシリサイド金属を堆積すると、異なるゲートではシリサイド形成で消費されるポリSiの量が異なるので、異なる相のシリサイドが形成されることがある。これらの異なる相によって、異なる仕事関数（したがってトランジスタのターンオン電圧）および抵抗（デバイス性能）の変化が生じることがある。

20

## 【0010】

上記で述べた欠点を考慮すると、ゲート寸法に関らず実質的に同じ高さを有するシリサイド金属ゲートのポリSiの領域上で形成を可能にする新しい、改善されたCMOSシリサイド金属ゲート集積化方式を提供することが求められている。

30

## 【発明の開示】

## 【課題を解決するための手段】

## 【0011】

本発明の第一の実施態様では、形成されるシリサイド金属ゲート相の変化を生じさせるポリSiゲートスタック高さの変化という欠点のないCMOSシリサイド金属ゲート集積化手法が提供される。本発明の集積化手法は、プロセスの複雑さ最小限に保ち、それによって、CMOSトランジスタの製造コストを増加させない。

## 【0012】

本発明の第一の実施態様では、ポリSiゲートの上の厚い誘電体キャップ（約20 nm以上、より好ましくは50 nm以上の厚さを有する）を利用することによって、上記の目的を実現する。層間誘電体の堆積および平坦化の後、反応性イオンエッティング（RIE）によって、層間誘電体およびポリSiゲートに対して誘電体キャップを選択的に除去する。ポリSiゲートはエッティングされないので、ゲート寸法（長さ）に関わらずウエハ全体で実質的に同じ厚さ（すなわち、堆積したときの厚さ）を有する。ポリSiを消費して金属ゲートシリサイドを形成した後、本発明の集積化方式によって提供される最初の一様なポリSiに起因して、ウエハ全体のシリサイド高さおよびシリサイド相は実質的に同じになる。断面画像化を用いて本発明の第一の実施態様の集積化方式によって形成される金属ゲートシリサイドの高さを決定することができる。

40

## 【0013】

50

従来技術の集積化方式に対する本発明の集積化方式の一つの大きな利点は、シリサイド形成のための金属ポリSiの反応が起こり、ゲート寸法に関わらず同じ量のポリSiを消費し、非一様なまたは不完全な相形成を防ぐという事実である。一例として、従来技術集積化方式では、寸法によって、あるゲートは他のゲートの二倍のポリSiを有することがあり得る。この場合、多めのポリSiが配置されている厚めのゲート上にCoSi<sub>2</sub>を形成しようとするとCoSi<sub>2</sub>が形成されるが、少なめのポリSiが配置されている薄めのゲート上にはCoSi相が形成されてしまう。CoSi相は、CoSi<sub>2</sub>と比較すると5~6倍高い比抵抗を有する。このため、一様でない性能が生じる。

【0014】

全体として、本発明の第一の実施態様は、以下の工程を含む。

半導体基板の上に配置される複数のポリSiゲートを準備する工程であって、各ポリSiゲートはその上部表面に配置される誘電体キャップを備える工程、

半導体基板中にシリサイド化ソース/ドレイン領域を形成する工程、

半導体基板上に平坦化誘電体 STACK を形成する工程、

エッチングプロセスを実行して各ポリSiゲートの上部表面を露出する工程、および

各ポリSiゲートを金属シリサイドゲートに変換するシリサイドプロセスを実行する工程。この実施態様では、同じポリSiイオン注入条件の場合、各金属シリサイドゲートは、実質的に同じ高さを有し、同じシリサイド相で構成され、実質的に同じ仕事関数を有する。

【0015】

本発明の別の様相は、上記に述べた本発明の集積化方式を用いて製造されるCMOS構造物に関する。全体として、本発明のCMO構造物は、以下を含む。

ゲート誘電体の表面の上に配置される複数のシリサイド化金属ゲートであって、同じポリSiイオン注入条件の場合、シリサイド金属ゲートのそれぞれは、シリサイド金属ゲートの寸法に関らず、同じシリサイド相で構成され、実質的に同じ高さを有し、実質的に同じ仕事関数を有する。

【0016】

本発明の第二の実施態様は、シリサイド化ソース/ドレイン領域(すなわち接点)を有するCMOS構造物を形成し、それによって、ポリシリコンゲートの高さは、半導体構造物の全表面にわたって実質的に同じである方法に関する。本発明の第二の実施態様は、以下の工程を含む。

半導体基板の上に配置される複数のポリSiゲートを備える構造物を準備する工程、

ポリSiゲートおよび半導体基板を備える構造物の上にオプションのキャッピング層とともにシリサイド金属を堆積する工程、

各ポリSiゲートの間でリフローさせることによって、凹形の材料を形成する工程、

ポリSiゲートのそれぞれの上からシリサイド金属およびオプションのキャッピング層を除去する工程、

形成された凹形の材料をリフローによって除去する工程、および

構造物をアニールし、これによって、ポリSiゲートのそれぞれの間にシリサイド接点領域を形成する工程。

【0017】

本発明の第三の実施態様は、シリサイド化ソース/ドレイン領域を有するCMOS構造物を形成し、それによって、半導体構造物の全表面にわたってポリシリコンゲートの高さを実質的に同じにする方法に関する。本発明の第三の実施態様は、以下の工程を含む。

半導体基板の上に配置される複数のポリSiゲートを備える構造物を準備する工程、

ポリSiゲートおよび半導体基板を備える構造物の上に金属含有層およびキャッピング層を含む二層層を形成する工程、

半導体基板上に平坦化誘電体を形成する工程、

各ポリSiゲートの上の金属含有層を露出させる工程、

各ポリSiゲートの上から金属含有層を除去する工程、および

10

20

30

40

50

構造物をアニールし、これによって、ポリSiゲートのそれぞれの間にシリサイド接点領域を形成する工程。

【0018】

上記で説明した第二の実施態様または第三の実施態様のどちらにおいても、同じポリSi予備ドーピング条件の場合、実質的に同じ高さ、相および仕事関数を有する金属シリサイドゲートを形成することができる。

【0019】

本発明の第二の実施態様および第三の実施態様は、以下を含む本発明の代替CMOS構造物を提供する。

【0020】

ゲート誘電体の表面の上に配置される複数のポリSiゲートであって、ポリSiゲートのそれぞれは、ポリシリコンゲートの寸法に関らず実質的に同じ高さを有する複数のポリSiゲート、および各ポリSiゲートの間に配置されるシリサイド化接点。

【0021】

本発明では、シリサイド接点（またはシリサイドソース／ドレイン領域）は、各ポリSiまたはシリサイド金属ゲートの垂直側壁上に配置されるスペーサのエッジに自己整合される。

【発明を実施するための最良の形態】

【0022】

次に、本出願の添付図面を参照して、本発明をより詳細に説明する。本発明は、一つの実施態様では、各ゲート寸法に関わらず、同じシリサイド相で構成され、実質的に同じ仕事関数および高さを有するシリサイド金属ゲートを形成することができるCMOSシリサイド金属ゲート集積化プロセスを提供する。添付図面は、実寸に比例して描かれておらず、同じおよび／または対応する要素は、同じ参照番号で指定される。

【0023】

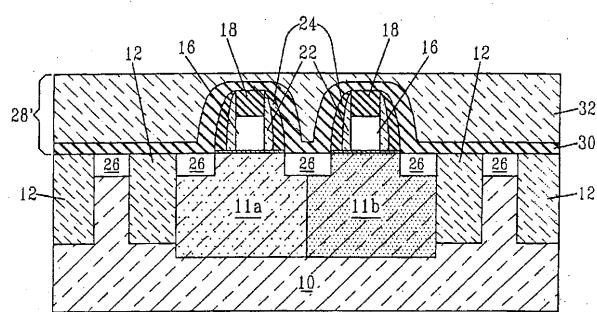

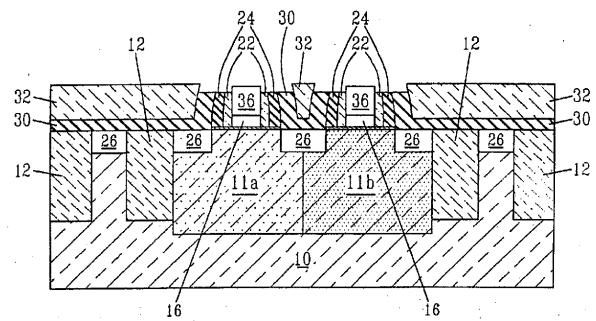

図1～10を参照する。図1～10は、本発明の第一の実施態様のさまざまな段階の間のCMOS構造物の断面図である。図面には二つのポリSiゲート（すなわちpFETおよびnFETトランジスタを有するCMOSトランジスタ構造物）が存在するように示しているが、本発明は、その数のポリSiゲートに限定されない。代わりに、本集積化プロセスは、任意の数のポリSiゲートの場合に機能する。従って、単一の半導体構造物全体にわたって、複数個のポリSiゲートが存在してよい。

【0024】

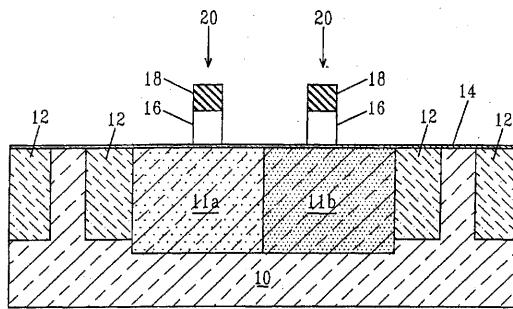

図1は、本発明の第一の実施態様で使用される初期構造物を示す。詳しくは、図1に示した初期構造物は、内部に形成されるアイソレーション領域12を有する半導体基板10を備える。初期構造物は、半導体基板10の上ならびに分離領域12の上に配置されるゲート誘電体14を備える。これは、誘電体が高k材料のように堆積される場合に該当するが、誘電体がSiO<sub>2</sub>またはSiO<sub>x</sub>N<sub>y</sub>で一般的であるように成長させられる場合には該当しない。本発明では、各ポリSiゲート16は誘電体キャップ18を有し、これらの両方はゲート誘電体14の選ばれた部分の上に配置される。本明細書中では、各ポリSiゲート16およびその対応する誘電体キャップ18をゲートスタック20と呼ぶ。

【0025】

図1に示した初期構造物の半導体基板10は、Si、Ge、SiGe、SiC、SiGeC、Ga、GaAs、InAs、InPおよびその他のII族/V族化合物半導体をすべて含むがそれらに限定されない任意の半導体材料を含む。半導体基板10は、Si/SiGe、シリコン・オン・インシュレータ(SOI)またはSiGe・オン・インシュレータ(SGOI)などの層状半導体を含んでよい。本発明のいくつかの実施態様では、半導体基板10は、Si含有半導体材料で構成されることが好ましい。半導体基板10はドーピングされていてもよく、ドーピングされていてもよく、あるいは内部にドーピング領域および非ドーピング領域を含んでもよい。

【0026】

10

20

30

40

50

図1で、参照番号11aは第一のドーピング( n または p )領域を指し、参照番号11bは第二のドーピング( n または p )領域を指す。第一のドーピング領域および第二のドーピング領域は同じであってよく、あるいは異なる導電率を有してもよい。これらのドーピング領域は、「ウェル」として知られる。

#### 【0027】

半導体基板10中にアイソレーション領域12を形成する。アイソレーション領域12は、図に示したようにトレンチ・アイソレーション領域であってもよく、あるいは電界酸化物アイソレーション領域であってもよい。トレンチ・アイソレーション領域は、当業者に公知の通常のトレンチ・アイソレーション・プロセスを利用して形成される。トレンチ・アイソレーション領域を形成する際には、例えば、リソグラフィー、エッチングおよびトレンチ誘電体によるトレンチの充填を用いてよい。オプションとして、トレンチ充填の前にトレンチ内にライナーを形成してよく、トレンチ充填後に高密度化工程を実行してよい。トレンチ充填に続いて平坦化プロセスを行ってよい。電界酸化物領域は、いわゆるシリコンプロセスの局所酸化を利用して形成してよい。

10

#### 【0028】

半導体基板10中にアイソレーション領域12を形成した後、半導体基板10を含む構造物の表面全体の上、およびアイソレーション領域12が堆積された誘電体ならアイソレーション領域12の上に、ゲート誘電体14を形成する。ゲート誘電体14は、例えば、酸化、窒化またはオキシ窒化などの熱成長プロセスによって形成してよい。あるいは、ゲート誘電体14は、例えば、化学的気相堆積(CVD)法、プラズマ支援CVD法、原子層堆積(ALD)法、蒸発法、反応性スパッタリング法、化学的溶液相堆積法およびその他の同様な堆積プロセスなどの堆積プロセスによって形成してよい。ゲート誘電体14は、上記のプロセスの任意の組み合わせを利用して形成してもよい。

20

#### 【0029】

ゲート誘電体14は、酸化物、窒化物、オキシ窒化物またはケイ酸塩あるいはそれらの組み合わせを含むが、それらに限定されない絶縁材料で構成される。一つの実施態様では、ゲート誘電体14は、例えば、 $\text{SiO}_2$ 、 $\text{HfO}_2$ 、 $\text{ZrO}_2$ 、 $\text{Al}_2\text{O}_3$ 、 $\text{TiO}_2$ 、 $\text{La}_2\text{O}_3$ 、 $\text{SrTiO}_3$ 、 $\text{LaAlO}_3$ およびそれらの混合物などの酸化物で構成されることが好ましい。

#### 【0030】

30

ゲート誘電体14の物理的な厚さは変化してよいが、一般的には、ゲート誘電体14は約0.5から約10nmの厚さを有し、約0.5から約3nmの厚さがより一般的である。

#### 【0031】

ゲート誘電体14を形成した後、例えば、物理的気相堆積法、CVD法または蒸発法などの既知の堆積プロセスを利用して、ゲート誘電体14上に多結晶シリコン(すなわちポリSi)のプランケット層を形成する。多結晶シリコンのプランケット層は、ドーピングされていてもよく、あるいはドーピングされていなくてもよい。ドーピングされるなら、多結晶シリコンを形成する際にインサイチュドーピング堆積プロセスを使用してよい。あるいは、ドーピングされたポリSi層は、堆積、イオン注入およびアニーリングによって形成してもよい。ポリSi層のドーピングによって、形成されるシリサイドゲートの仕事関数はシフトする。ドーパントイオンを説明する例は、As、P、B、Sb、Bi、In、Al、Ga、Tlまたはそれらの混合物を含む。本発明のこの時点で堆積される多結晶シリコン層の厚さ(すなわち高さ)は、使用される析出プロセスによって変化してよい。一般的に、多結晶シリコン層は、約20から約180nmの垂直厚さを有し、約40から約150nmの厚さがより一般的である。

40

#### 【0032】

多結晶シリコンのプランケット層の堆積後、例えば、物理的気相堆積法または化学的気相堆積法などの堆積プロセスを利用して、多結晶シリコンのプランケット層の上に誘電体キャップ層を形成する。誘電体キャップ層は、酸化物、窒化物、オキシ窒化物またはそれ

50

らの任意の組み合わせであってよい。一つの実施態様では、例えば  $\text{Si}_3\text{N}_4$  などの窒化物が誘電体キャップ層として使用される。誘電体キャップ層の厚さ、すなわち高さは約 20 から約 180 nm であり、約 30 から約 140 nm の厚さがより一般的である。

【0033】

一つの実施態様では、多結晶シリコンのプランケット層と誘電体キャップ層とは、70 から 180 nm の範囲の全高を有する。さらに別の実施態様では、プランケット多結晶シリコン層と誘電体キャップ層との高さは約 120 nm であり、通常、70 nm ポリ Si と 50 nm 誘電体キャップとである。

【0034】

次に、リソグラフィーおよびエッチングによって、プランケット多結晶シリコン層と誘電キャップ層とをパターン化してパターン化ゲートスタックを提供する。パターン化ゲートスタック 20 は、同じ寸法（すなわち長さ）を有してもよく、あるいはデバイス性能を改善するために寸法を変えてよい。図 1 に示したように、各パターン化ゲートスタック 20 は、ポリ Si ゲート 16 および誘電キャップ 18 を備える。リソグラフィー工程は、誘電体キャップ層の上面部にフォトレジストを塗布すること、フォトレジストを所望のパターンの放射に露光させることおよび露光させたフォトレジストを通常のレジスト現像液を利用して現像することを含む。次に、一回以上のドライエッチング工程を利用して、フォトレジスト中のパターンを誘電キャップ層および多結晶シリコンのプランケット層に転写する。いくつかの実施態様では、パターンを誘電キャップ層中に転写した後、パターン化フォトレジストを除去してよい。その他の実施態様では、エッチングが完了した後、パターン化フォトレジストを除去する。

【0035】

パターン化ゲートスタック 20 を形成する際に本発明で用いることができる適当なドライエッチングプロセスは、反応性イオンエッチング、イオンビームエッチング、プラズマエッチングまたはレーザーアブレーションを含むが、それらに限定されない。通常、使用されるドライエッチングプロセスは、下地ゲート誘電体 14 に対して選択的であり、それによって、通常、このエッチング工程はゲート誘電体を除去しない。しかし、いくつかの実施態様では、このエッチング工程を用いてゲートスタック 20 で保護されていないゲート誘電体 14 の部分を除去してよい。

【0036】

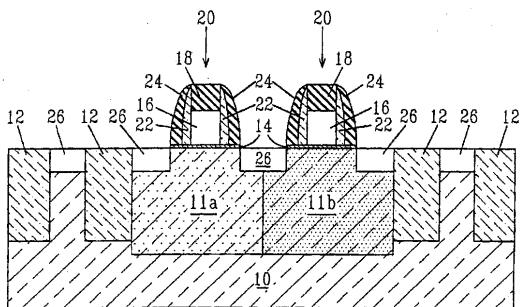

次に、各パターン化ゲートスタック 20 の露出された側壁上に、少なくとも一つのスペーサを形成する。この少なくとも一つのスペーサは、酸化物、窒化物、オキシ窒化物またはそれらの任意の組み合わせ、化合物などの絶縁体で構成される。この少なくとも一つのスペーサは、堆積およびエッチングによって形成される。図 2 は、ゲートスタック 20 の各露出側壁上に二つのスペーサが形成される本発明の実施態様を示す。詳しくは、図 2 は、第一の幅を有する第一のスペーサ 22 と、第二の幅を有する第二のスペーサ 24 とを備え、第一の幅は第二の幅より狭い構造物を示す。別の実施態様では、二層スペーサ方式を一層スペーサに換え、この場合一層スペーサは、図 2 に示した第一の幅と第二の幅との和と実質的に等しい幅を有する広いスペーサである。

【0037】

第一のスペーサと第二のスペーサとを用いるとき、第一のスペーサと第二のスペーサとを異なる絶縁体で構成してよい。例えば、第一のスペーサ 22 を  $\text{SiO}_2$  で構成し、第二のスペーサ 24 を  $\text{Si}_3\text{N}_4$  で構成してよい。

【0038】

スペーサの幅は、ソース / ドレインシリサイド接点（続いて形成される）がゲートスタックのエッジの下に浸入しないように十分に広くなければならない。通常、ソース / ドレインシリサイドは、スペーサが底部で測定して約 20 から約 80 nm の幅を有するとき、ゲートスタックのエッジの下に浸入しない。

【0039】

スペーサ形成後、基板中にソース / ドレイン拡散領域（特に示してはいない）を形成す

10

20

30

40

50

る。イオン注入およびアニーリング工程を利用してソース／ドレイン拡散領域を形成する。アニーリング工程は、前段の注入工程によって注入されたドーパントを活性化するために使用される。イオン注入およびアニーリングの条件は、当業者に公知である。

【0040】

次に、もしそれ以前に除去されていなければ、ゲート誘電体14を選択除去する化学エッチングプロセスを利用してゲート誘電体14の露出部分を除去する。このエッチング工程は、半導体基板10の上部表面ならびにアイソレーション領域12の上部表面で停止する。ゲート誘電体14の露出部分を除去する際には任意の化学エッチング剤を用いてよいが、一つの実施態様では、希薄なフッ化水素酸(DHF)を用いる。

【0041】

次に、サリサイドプロセスを用いて、ソース／ドレインシリサイド接点26を形成する。サリサイドプロセスは、ソース／ドレイン拡散領域を備える基板10の露出表面上に金属を堆積する工程、シリサイドを形成する第一のアニーリング工程、用いられているなら、キャッピング層を含むあらゆる未反応金属の選択エッチング工程、および、必要なら、第二のアニーリング工程を実行することを含む。例えば、図3に、ソース／ドレインシリサイド接点26を備える結果として得られる構造物を示す。

【0042】

半導体基板がシリコンを含まないとき、半導体基板10の露出表面上にシリコンの層(図示していない)を成長させてよく、ソース／ドレインシリサイド接点を形成する際に用いてよい。

【0043】

ソース／ドレインシリサイド接点を形成する際に用いられる金属は、シリコンと反応して金属シリサイドを形成することができる任意の金属を含む。そのような金属の例は、Ti、Ta、W、Co、Ni、Pt、Pdおよびそれらの合金を含むが、それらに限定されない。一つの実施態様では、Coが好ましい金属である。そのような実施態様では、第二のアニーリング工程が必要である。別の実施態様では、NiまたはPtが好ましい。この実施態様では、通常、第二のアニーリング工程を実行しない。

【0044】

例えば、スパッタリング法、化学的気相堆積法、蒸発法、化学的溶液相堆積法、めっき法および類似法を含む任意の通常の析出プロセスを用いて金属を堆積してよい。

【0045】

通常、第一のアニールは第二のアニーリング工程より低い温度で実行される。通常、連続加熱領域またはさまざまな昇温および保温加熱サイクルを用いて、約300から約600の温度で第一のアニーリング工程を実行する。第一のアニーリング工程は、高抵抗シリサイド相材料を形成してもよく、形成しなくてもよい。より好ましくは、約350から約550の温度で第一のアニーリング工程を実行する。連続加熱領域またはさまざまな昇温および保温サイクルを用いて、約600から約800の温度で第二のアニーリング工程を実行する。より好ましくは、約650から約750の温度で第二のアニーリング工程を実行する。通常、第二のアニールによって、高抵抗シリサイドはより低抵抗のシリサイド相に変換される。

【0046】

気体雰囲気、例えばHe、Ar、N<sub>2</sub>またはフォーミング気体中でサリサイドアニールを実行する。ソース／ドレインシリサイド接点アニーリング工程は、異なる雰囲気を用いてよく、あるいは同じ雰囲気中でアニーリング工程を実行してよい。例えば、両方のアニーリング工程でHeを用いてよく、あるいは第一のアニーリング工程でHeを用い、第二のアニーリング工程でフォーミング気体を用いてよい。

【0047】

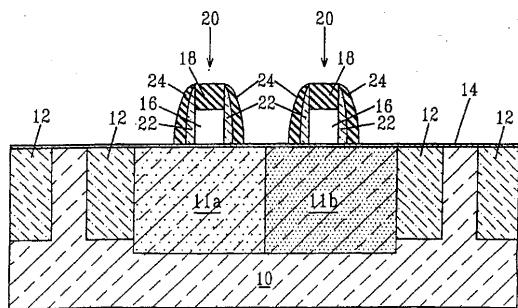

図3に示した構造物を形成した後、第一の誘電体層30および第二の誘電体層32を含む誘電体スタック28を形成し、図4に示す構造物を提供する。第一の誘電体層30はエッチング停止層として使用され、一方、第二の誘電体層32は層間誘電体として使用され

10

20

30

40

50

る。誘電体スタック 28 の第一の誘電体層および第二の誘電体層は、例えば、酸化物、窒化物およびオキシ窒化物を含む異なる絶縁材料で構成される。

【0048】

本発明によれば、第一の誘電体層 30 は、誘電体キャップ 18 の誘電体と同じ誘電体で構成される。本発明の一つの実施態様では、誘電体スタック 28 の第一の誘電体層 30 は  $Si_3N_4$  で構成され、一方、第二の誘電体層は  $SiO_2$  で構成される。図に示したように、誘電体スタック 28 は、アイソレーション領域 12、ゲートスタック 20、ならびにソース／ドレインシリサイド接点 26 を被覆する。

【0049】

第一の誘電体層 30 および第二の誘電体 32 は、同じ堆積プロセスまたは異なる堆積プロセスを利用して形成される。誘電体スタック 28 の層 30 および 32 を形成する際に用いることができる適当な堆積プロセスの例は、化学的気相堆積法、原子層堆積法、物理的気相堆積法、化学的溶液相堆積法、蒸発法およびその他の同様な堆積プロセスを含むが、それらに限定されない。誘電体スタック 28 の厚さは変化してよいが、ゲートスタック 20 の高さより高い厚さがなければならない。

【0050】

誘電体スタック 28 の形成後、第二の誘電体層 32 を平坦化し、平坦化誘電体スタック 28' を備える構造物を提供する。例えば、図 5 にそのような構造物を示す。例えば、化学機械研磨または研削を含む通常の平坦化プロセスによって、平坦化誘電体スタック 28' を形成してよい。

10

20

【0051】

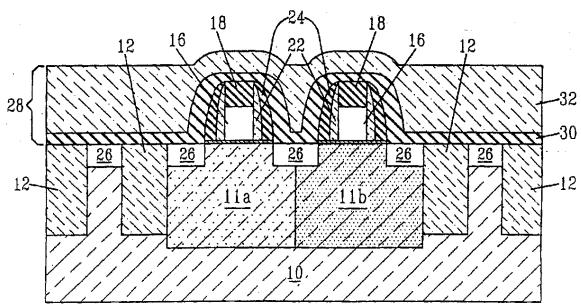

次に、図 6 に示すように、反応性イオンエッチバックプロセスを実行し、これによって、第一の誘電体層 30 および誘電体キャップ 18 を第二の誘電体層 32 に対して選択除去する。例えば、第一の誘電体層および誘電体キャップが  $Si_3N_4$  で構成され、第二の誘電体層が  $SiO_2$  で構成されているとき、酸化物に対して窒化物を選択除去する。この反応性イオンエッチバック工程によって、各ゲートスタック 20 のポリシリコンゲート 16 が露出される。例えば、図 6 に、反応性イオンエッチバック工程を実行した後の構造物を示す。反応性イオンエッチバック工程は、ポリシリコンゲート 16 をエッチングしない点に注意すること。ポリシリコンゲート 16 はエッチングされていないので、厚さ（すなわち高さ）は、寸法（すなわち長さ）に関わりなく実質的に同じである。

30

【0052】

次に、第二のサリサイドプロセスを実行し、ポリシリコンゲート 16 を消費して金属シリサイドゲートを形成する。以下の諸図面は、二段階アニール工程が必要な実施態様の例を示す。いくつかの実施態様では、サリサイドプロセスは、選択エッチング工程後に完了する。従って、そのような実施態様では第一のアニールによって低抵抗相金属シリサイドゲートが形成されるので、第二のアニールは必要ない。

【0053】

第二のサリサイドプロセスの第一の工程は、図 6 に示す構造物の上にブランケットシリサイド金属 34 を堆積することを含む。例えば、図 7 に、得られるブランケットシリサイド金属 34 を含む構造物を示す。ソース／ドレインシリサイド接点形成で用いられる金属を形成する際に上記で言及した堆積プロセスの一つを用いて、シリサイド金属 34 を堆積してよい。

40

【0054】

シリサイド金属 34 は、Ti、Ta、W、Co、Ni、Pt、Pd またはそれらの合金で構成させてよい。一つの実施態様では、シリサイド金属 34 は Co であり、二工程アニーリングプロセスを使用すると  $CoSi_2$  が生成する。本発明の別の実施態様では、シリサイド金属 34 は Ni または Pt であり、一段アニーリング工程を使用すると  $NiSi$  および  $PtSi$  が生成する。シリサイド金属厚さは、特定の CMOS デバイスに適切な仕事関数を有するシリサイド相を形成するように選ばれる。例えば、 $NiSi$  は  $4.65\text{ eV}$  の仕事関数を有し、最初の多結晶シリコン高さが  $50\text{ nm}$  なら、必要な Ni の量は約 27

50

$\text{nm}$ である。 $\text{CoSi}_2$ は $4.45\text{ eV}$ の仕事関数を有し、最初の多結晶シリコン高さが $50\text{ nm}$ なら、必要な $\text{Co}$ の量は約 $14\text{ nm}$ である。所定のシリサイド金属厚さは多結晶シリコンを消費するのにちょうど必要な量であるが、消費が完了することを確実にするためには約 $10\%$ 過剰の厚さが好ましい。

【0055】

いくつかの実施態様(示していない)では、シリサイド金属の上に $\text{TiN}$ または $\text{W}$ などの酸素拡散障壁を形成する。

【0056】

シリサイド金属 $34$ の堆積後、第一のアニールを使用して構造物中に第一のシリサイド相 $36$ を形成する。第一のシリサイド相は、金属シリサイドの最も低い比抵抗相を表してもよく、あるいは表さなくてもよい。図 $8$ を参照すること。ソース/ドレインシリサイド接点 $26$ を形成する際に上記で説明した雰囲気および温度を利用して、第一のアニールを実行する。次に、図 $9$ に示すように、選択ウェットエッティング工程を使用してあらゆる未反応シリサイド金属を構造物から除去する。

10

【0057】

いくつかの金属シリサイドの場合、多結晶シリコンは消費され、第一のシリサイド相 $36$ の比抵抗はこの相の最小値に近いので、シリサイドプロセスをこの時点で止めてよい。これは、 $\text{Ni}$ および $\text{Pt}$ の場合である。この実施態様は、図には示していない。他の場合、例えば、シリサイド金属として $\text{Co}$ または $\text{Ti}$ を用いるとき、残存する多結晶シリコンの消費および第二のシリサイド相材料 $38$ の形成のために第二の高温アニール(上記で説明したように)が必要である。図 $10$ を参照すること。この実施態様では、第一のシリサイド相は高比抵抗相シリサイド材料であり、一方、第二のシリサイド相材料 $38$ は低比抵抗相シリサイド材料である。

20

【0058】

上述の本発明の金属シリサイドゲートプロセスの完了後、トランジスタからトランジスタ、およびトランジスタから外部への接続のための多層相互配線構造物を構築するための通常の手法を使用してよい。

【0059】

上記で述べたように、本発明の第一の実施態様のプロセス工程によって、各金属シリサイドゲートが、その寸法に関わらず、同じ相を有し、実質的に同じ高さである $\text{CMOS}$ 構造物を作製することができる。前述の集積化プロセス方式を用いて形成される $\text{CMOS}$ 構造物の別の特徴は、同じポリ $\text{Si}$ イオン注入条件による各金属シリサイドゲートが実質的に同じ仕事関数を有することである。

30

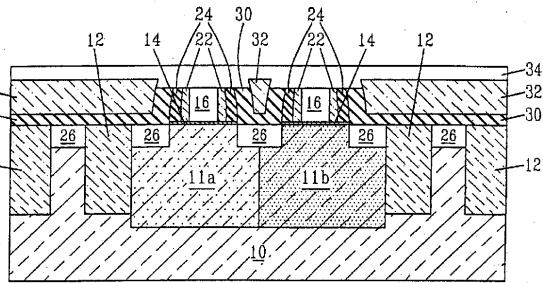

【0060】

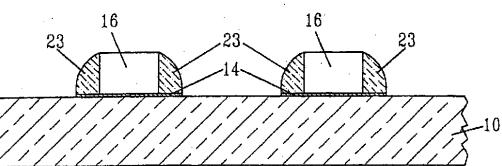

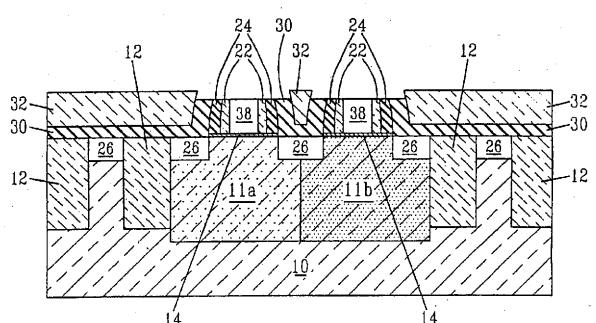

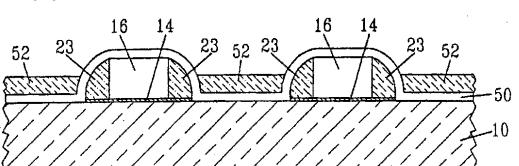

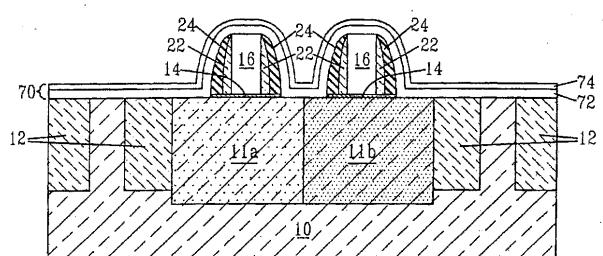

図 $11$ ~ $15$ を参照する。図 $11$ ~ $15$ は、本発明の第二の実施態様のさまざまな段階の間の $\text{CMOS}$ 構造物の断面図である。これらの図面では、二つのポリ $\text{Si}$ ゲート(すなわち $\text{pFET}$ および $\text{nFET}$ トランジスタを有する $\text{CMOS}$ トランジスタ構造物)の存在を示すが、本発明は、その数のポリ $\text{Si}$ ゲートに限定されない。代わりに、本集積化プロセスは、任意の数のポリ $\text{Si}$ ゲートの場合に機能する。従って、単一の半導体構造物全体にわたって、複数個のポリ $\text{Si}$ ゲートが存在してよい。

40

【0061】

図 $11$ は、本発明の第二の実施態様で使用することができる初期構造物を示す。図に示したように、初期構造物は、半導体基板 $10$ 、半導体基板 $10$ の表面上に配置されるパターン化ゲート誘電体 $14$ 、パターン化ゲート誘電体 $14$ の表面部分の上に配置されるパターン化ポリ $\text{Si}$ ゲート $16$ 、および各パターン化ポリ $\text{Si}$ ゲート $16$ の露出垂直側壁上に形成されるスペーサ $23$ を備える。図 $11$ に示した構造物は、第一の実施態様の場合と同じ材料を含み、同構造物を形成するために、図 $2$ に示した構造物を形成する際に用いたものと類似のプロセスフローを用いる。この実施態様では、ドープ化領域およびアイソレーション領域は描かれていない。しかし、半導体基板 $10$ 中に同領域を含んでよい。この実施態様では、パターン化ポリ $\text{Si}$ ゲート $16$ の各露出垂直側壁上に一層スペーサ $23$ が示

50

されている点に注意すること。一層スペーサが示されているが、二層スペーサ22および24(図2に示したように)が使用されるとき、第二の実施態様は機能する。酸化物、窒化物、オキシ窒化物またはそれらの任意の組み合わせで一層スペーサ23を構成してよい。

【0062】

図11に示した初期構造物の形成に続いて、初期構造物のすべての露出表面(垂直および水平)上にシリサイド金属50を形成し、例えば、図12に示す構造物を提供する。本発明の第二の実施態様で使用されるシリサイド金属50は、Ti、Ta、W、Co、Ni、Pt、Pdまたはそれらの合金を含む。例えば物理的気相堆積法(スパッタリング)、化学的気相堆積法、原子層堆積法またはめっき法などの共形堆積プロセスを利用してシリサイド金属50を形成する。シリサイド金属50は、堆積される金属の種類および同金属を形成する際に用いられる技法によって変化する厚さを有してよい。しかし、通常、シリサイド金属50は、堆積後、約0.5から約25nmの厚さを有する。

【0063】

半導体基板10がSi含有材料で構成されていない実施態様では、シリサイド金属50の形成の前に、非Si含有基板の露出表面の上にSi含有材料を形成してよい。

【0064】

次に、通常の堆積技法によって、図12に示した構造物の上にリフローすることができる材料(以下リフロー材料と称する)を形成する。リフロー材料は、反射防止コーティング(ARC)またはスピノン誘電体材料を含む。堆積するリフロー材料の厚さは変化してよいが、通常、堆積するリフロー材料は、ポリSiゲート16の高さより低い厚さを有する。詳しくは、堆積直後のリフロー材料は、約20から約180nmの厚さを有する。

【0065】

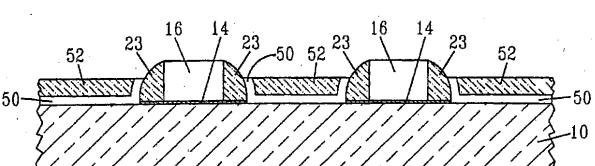

堆積後、リフロー材料は凹形になり、例えば図13に示す構造物を提供する。図13で、参照番号52が凹形のリフロー材料を示す。エッチング工程を用いてリフロー材料をさらに凹ませてよい。図に示したように、凹形のリフロー材料52は、ポリSiゲート16の高さより低い上部表面を有する。その結果、本発明の第二の実施態様のこの時点で、凹形のリフロー材料52は、ポリSiゲート16の間にだけ配置される。

【0066】

凹形のリフロー材料52の形成後、各ポリSiゲート16の上のシリサイド金属50を除去し、それによって、各ポリSiゲート16の上部表面を露出させる。例えば、図14に、ポリSiゲート16の上からシリサイド金属50を除去した後に結果として形成される構造物を示す。誘電体またはポリSiに対して金属を選択的に除去するエッチングプロセスを利用して、ポリSiゲート16上のシリサイド金属50の除去を実行する。詳しくは、本発明のこの工程では、硫酸/過酸化水素溶液を使用するウェットエッチングプロセスを使用してよい。

【0067】

本発明の第二の実施態様のこの時点で、ARCまたはスピノン材料を選択除去するストリッピングプロセスを利用して構造物から凹形のリフロー材料52を除去した後、アニーリングプロセスを実行する。

【0068】

アニーリングプロセスは、第一のアニーリング、およびオプションとして、第二のアニールを含んでよい。第一のアニールの後、または第二のオプションのアニールの後、未反応金属は除去される。通常、第一のアニールは第二のアニーリング工程より低い温度で実行される。通常、連続加熱領域またはさまざまな昇温および保温加熱サイクルを用いて、約300から約600の温度で第一のアニーリング工程を実行する。第一のアニーリング工程は、高抵抗シリサイド相材料を形成してもよく、形成しなくてもよい。より好ましくは、約350から約550の温度で第一のアニーリング工程を実行する。連続加熱領域またはさまざまな昇温および保温加熱サイクルを用いて、約600から約800の温度で第二のアニーリング工程を実行する。より好ましくは、約650から約750

10

20

30

40

50

0 の温度で第二のアニーリング工程を実行する。通常、第二のアニールによって、高抵抗シリサイドはより低抵抗のシリサイド相に変換される。

【0069】

気体雰囲気、例えばHe、Ar、N<sub>2</sub>またはフォーミング気体中でシリサイドアニールを実行する。ソース／ドレインシリサイド接点アニーリング工程は、異なる雰囲気を用いてよく、あるいは同じ雰囲気中でアニーリング工程を実行してよい。例えば、両方のアニーリング工程でHeを用いてよく、あるいは第一のアニーリング工程でHeを用い、第二のアニーリング工程でフォーミング気体を用いてよい。金属を選択除去するエッティングプロセスを利用して、未反応金属を除去する。例は、硫酸／過酸化水素溶液を用いるウェットエッティングを含む。

10

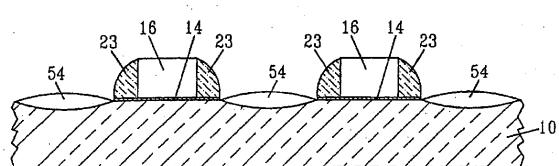

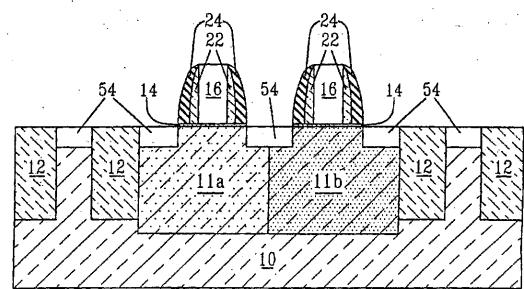

【0070】

図15は、アニーリングおよびシリサイド接触54の形成後、結果として形成される構造物を示す。本発明の方法は、ポリSiゲート16の寸法に関わりなく、各ポリSiゲート16が同じ高さを有する構造物を提供する点に注意すること。

【0071】

本発明の第二の実施態様のこの時点で、ポリSiゲート16を、同じポリSi予備ドーピング条件のとき、実質的に同じ高さ、相および仕事関数を有するシリサイド金属ゲートに変換することができる。本発明の第一の実施態様で言及したシリサイドプロセスを利用して、シリサイド金属ゲートを形成してよい。詳しくは、最初に、ポリSiゲート16および誘電体キャッピング層だけが続いて堆積されるシリサイド金属と接触するように、構造物の上に誘電体キャッピング層（例えばSi<sub>3</sub>N<sub>4</sub>、SiO<sub>2</sub>、Si<sub>3</sub>N<sub>4</sub>上のSiO<sub>2</sub>等）を提供することによって、シリサイド金属ゲートを形成してよい。本発明のこの工程によって、ソース／ドレイン領域を誘電体層でキャップし、これによって、ゲート形成に用いられるシリサイド金属がソース／ドレイン領域と接触しないようにする。キャッピング層のための可能な手法は、プランケットSi<sub>3</sub>N<sub>4</sub>層を堆積した後、続いて高密度プラズマ（HDP）SiO<sub>2</sub>層（ゲート高さより大きな厚さ）を堆積することである。化学機械研磨を用いてHDP SiO<sub>2</sub>停止層をSi<sub>3</sub>N<sub>4</sub>層のレベル、あるいは若干Si<sub>3</sub>N<sub>4</sub>層内まで平坦化してよい。SiO<sub>2</sub>がいくらか残ったら、ウェットエッチプロセスを用いてSiO<sub>2</sub>を除去してよい。選択的RIEプロセスを用いてゲート上のSi<sub>3</sub>N<sub>4</sub>を除去し、次に、シリサイド金属を堆積し、上記で説明したシリサイドプロセスに付す。

20

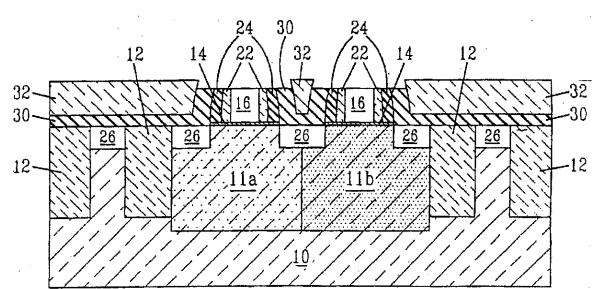

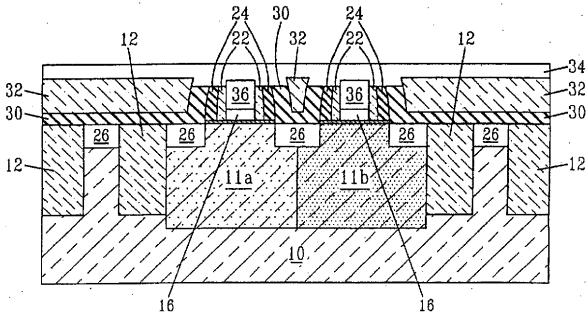

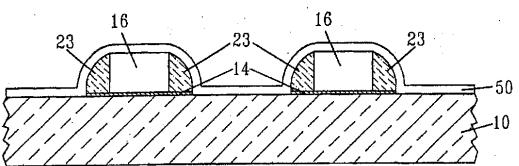

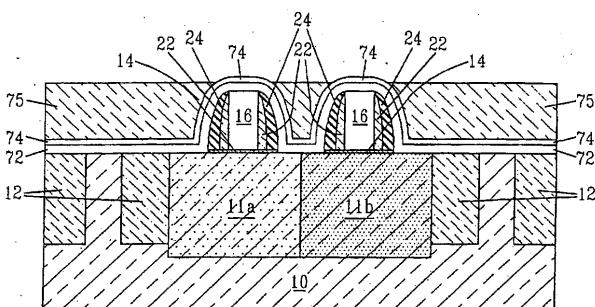

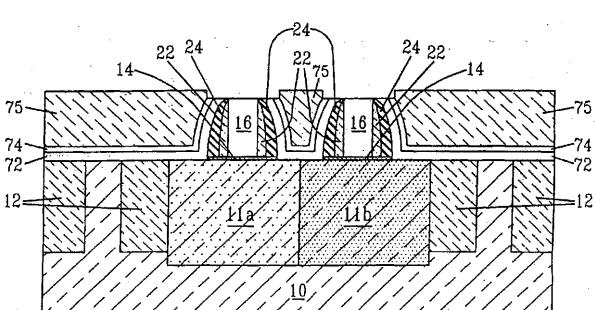

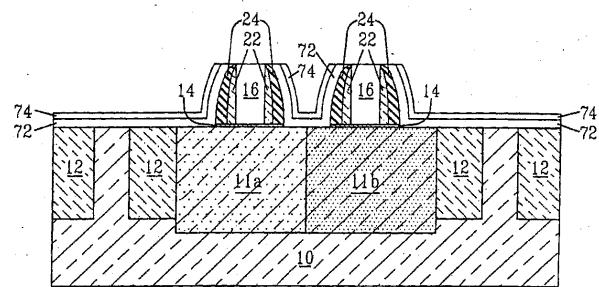

【0072】

図16～21を参照する。図16～21は、本発明の第三の実施態様のさまざまな段階の間のCMOS構造物の断面図である。これらの図面では、二つのポリSiゲート（すなわちpFETおよびnFETトランジスタを有するCMOSトランジスタ構造物）の存在を示すが、本発明は、その数のポリSiゲートに限定されない。代わりに、本集積化プロセスは、任意の数のポリSiゲートの場合に機能する。従って、単一の半導体構造物全体にわたって、複数個のポリSiゲートが存在してよい。

30

【0073】

図16は、本発明の第三の実施態様で使用することができる初期構造物を示す。図に示したように、初期構造物は、内部に形成される第一のドーピング領域11a、第二のドーピング領域11bおよびアイソレーション領域12を有する半導体基板10、半導体基板10の表面上に配置されるパターン化ゲート誘電体14、パターン化ゲート誘電体14の表面部分の上に配置されるパターン化ポリSiゲート16、および各パターン化ポリSiゲート16の露出垂直側壁上に形成されるスペーサ22および24を含む。本発明の第三の実施態様で使用される初期構造物の前述の構成要素は、ポリSiゲート16の上に誘電体キャップ18が存在しない点を除いて、図2に示した構成要素と類似する。

40

【0074】

図16の構造物は、金属含有層72とキャッピング層74とを含む二層スタック70を備える。図に示したように、最初に金属含有層70を形成し、その後、キャッピング層74を形成する。

50

## 【0075】

二層スタック70の金属含有層72は、シリコンと反応して金属シリサイドを生成することができる任意の金属で構成してよい。そのような金属の例は、Ti、Ta、W、Co、Ni、Pt、Pdまたはそれらの合金を含むが、それらに限定されない。これらの金属のスタックを金属含有層70として用いてもよい。これらのさまざまな金属の中で、CoまたはNiが使用されることが好ましい。二層スタック70の金属含有層72は、一般的に、厚さが約0.5から約25nmの層であり、約0.5から約15nmの厚さがより一般的である。

## 【0076】

例えば、物理的気相堆積法（スパッタリング法または蒸発法）、化学的気相堆積法、原子層堆積法、化学的溶液相堆積法、めっき法および類似法を含む任意の通常の堆積プロセスを利用して、二層スタック70の金属含有層72を形成する。

10

## 【0077】

金属含有層72の上に形成される二層スタック70のキャッピング層74は、シリサイドを形成するために用いられる下地金属中の酸素取り込みを妨げることができる任意の材料を含む。そのようなキャッピング層を説明する例は、TiN、WまたはTiを含む。一般的に、キャッピング層72は約5nmから約50nmの厚さを有し、約10から約25nmの厚さがより一般的である。例えば物理的気相堆積法または化学的気相堆積法などの通常の堆積プロセスを利用して、キャッピング層72を形成する。

## 【0078】

20

次に、図16に示した構造物の上に平坦化誘電体75を形成し、図17に示す構造物を提供する。平坦化誘電体75は、平坦化層として機能することができるフォトレジスト、低温酸化物（LTO）またはその他の同様な誘電体を含んでよい。平坦化前の平坦化誘電体75の初期厚さは変化してよいが、ポリSiゲート16の高さより高い厚さがなければならない。

## 【0079】

次に、例えば、化学機械研磨または研削あるいはその両方を含む通常の平坦化プロセスによって平坦化誘電体75を平坦化し、これによって、図18に示す構造物を提供する。平坦化の間、各ポリSiゲート16より高い位置にある平坦化誘電体75を除去し、これによって、下地の二層スタック70のキャッピング層74を露出させる。本発明のこの実施態様では、ポリSiゲート16の上のキャッピング層74は、CMPエッティング停止層として機能する。

30

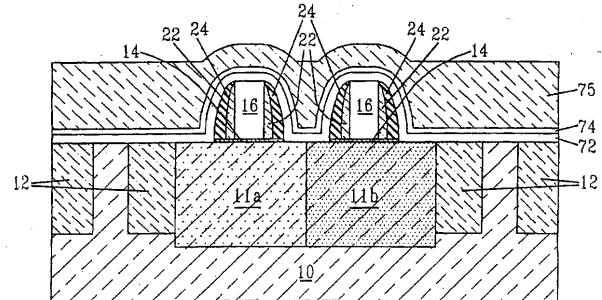

## 【0080】

次に、露出したキャッピング層74を除去して、下地の金属含有層72を露出させる。選択ウェットエッティングプロセスを利用して、露出したキャッピング層74を除去する。

## 【0081】

次に、各ポリSiゲート16の上の露出した金属含有層72を除去し、これによって、ポリSiゲート16の上部表面を露出させる。図19を参照すること。金属を選択除去するエッティングプロセスを利用して、露出した金属含有層72を除去する。例は、硫酸／過酸化水素溶液を用いるウェットエッティングを含む。

40

## 【0082】

露出した金属含有層72を各ポリSiゲート16の上から選択除去した後、フォトレジストまたは低温酸化物を選択除去するエッティングプロセスを利用して、隣接する平坦化材料75を除去する。例えば、図20に、上記のプロセス工程に従って形成された構造物を示す。

## 【0083】

次に、シリサイド接点54を形成するアニーリングプロセスを実行する。図21を参照すること。アニーリングプロセスは、第一のアニーリング、およびオプションとして、第二のアニールを含んでよい。第一のアニールの後、または第二のオプションのアニールの後、未反応金属およびキャッピング層を除去してよい。通常、第一のアニールは第二のア

50

ニーリング工程より低い温度で実行される。通常、連続加熱領域またはさまざまな昇温および保温加熱サイクルを用いて、約300から約600の温度で第一のアニーリング工程を実行する。第一のアニーリング工程は、高抵抗シリサイド相材料を形成してもよく、形成しなくてもよい。より好ましくは、約350から約550の温度で第一のアニーリング工程を実行する。連続加熱領域またはさまざまな昇温および保温加熱サイクルを用いて、約600から約800の温度で第二のアニーリング工程を実行する。より好ましくは、約650から約750の温度で第二のアニーリング工程を実行する。通常、第二のアニールによって、高抵抗シリサイドはより低抵抗のシリサイド相に変換される。

## 【0084】

10

気体雰囲気、例えばHe、Ar、N<sub>2</sub>またはフォーミング気体中でシリサイドアニールを実行する。ソース／ドレインシリサイド接点アニーリング工程は、異なる雰囲気を用いてよく、あるいは同じ雰囲気中でアニーリング工程を実行してよい。例えば、両方のアニーリング工程でHeを用いてよく、あるいは第一のアニーリング工程でHeを用い、第二のアニーリング工程でフォーミング気体を用いてよい。アニーリングの後、該当する材料を選択除去するエッティングプロセスを利用して、誘電体キャップ74および未反応金属（すなわち金属含有層72）を除去する。

## 【0085】

図21は、アニーリングおよびシリサイド接点54の形成後、形成される構造物を示す。本発明の方法は、ポリSiゲート16の寸法に関わりなく、各ポリSiゲート16が同じ高さを有する構造物を提供する点に注意すること。

20

## 【0086】

第三の実施態様では、本発明の第二の実施態様において上記で説明したように、シリサイド金属ゲートを形成してよい。

## 【0087】

上記で言及した本発明のさまざまな実施態様では、シリサイドを形成する際に使用される金属は、金属シリサイドの形成を促進することができる合金添加物を含んでよい。本発明において使用することができる合金添加物の例は、C、Al、Ti、V、Cr、Mn、Fe、Co、Ni、Cu、Ge、Zr、Nb、Mo、Ru、Rh、Pd、Ag、In、Sn、Hf、Ta、W、Re、Ir、Ptまたはそれらの混合物を含む。ただし、合金添加物は、シリサイドを形成する際に用いられる金属と同じでないという条件がある。存在するとき、合金添加物は、約0.1から約50原子パーセントの量で存在する。

30

## 【0088】

本発明の好ましい実施態様について、本発明を詳しく示し説明してきたが、本発明の技術思想および範囲から逸脱することなく、前述およびその他の形式および詳細の変化を施すことができることは、当業者に理解されるものとする。従って、本発明は、記載され例が示された正確な形式および詳細に限定されるものではなく、付属の請求項の範囲に属するものとする。

## 【図面の簡単な説明】

## 【0089】

40

【図1】本発明の第一の実施態様で使用される初期キャップ付きポリSiゲート構造物を示す説明図（断面図による）である。

【図2】図1に例を示したキャップ付きポリSiゲートのそれぞれの側壁上に二重スペーサが形成された後の構造物を示す説明図（断面図による）である。

【図3】図2に例を示した構造物上にソース／ドレインシリサイド化が実行された後の構造物を示す説明図（断面図による）である。

【図4】図3に例を示した構造物上での窒化物／酸化物誘電体スタックの堆積の後の構造物を示す説明図（断面図による）である。

【図5】図4で例を示した構造物を平坦化した後の構造物を示す説明図（断面図による）である。

50

【図6】キャップ材料を含む酸化物および窒化物をバックエッティングし、各ポリSiゲートの上面部を露出させた後の構造物を示す説明図（断面図による）である。

【図7】シリサイド金属堆積後の構造物を示す説明図（断面図による）である。

【図8】第一の自己整合シリサイドアニール後の構造物を示す説明図（断面図による）である。

【図9】シリサイド選択性エッティングを実行した後の構造物を示す説明図（断面図による）である。

【図10】オプションの第二の自己整合シリサイドアニールを実行した後の構造物を示す説明図（断面図による）である。

【図11】本発明の第二の実施態様の基本プロセスフローの例を示す説明図（断面図による）である。 10

【図12】本発明の第二の実施態様の基本プロセスフローの例を示す説明図（断面図による）である。

【図13】本発明の第二の実施態様の基本プロセスフローの例を示す説明図（断面図による）である。

【図14】本発明の第二の実施態様の基本プロセスフローの例を示す説明図（断面図による）である。

【図15】本発明の第二の実施態様の基本プロセスフローの例を示す説明図（断面図による）である。

【図16】本発明の第三の実施態様の基本プロセスフローの例を示す説明図（断面図による）である。 20

【図17】本発明の第三の実施態様の基本プロセスフローの例を示す説明図（断面図による）である。

【図18】本発明の第三の実施態様の基本プロセスフローの例を示す説明図（断面図による）である。

【図19】本発明の第三の実施態様の基本プロセスフローの例を示す説明図（断面図による）である。

【図20】本発明の第三の実施態様の基本プロセスフローの例を示す説明図（断面図による）である。

【図21】本発明の第三の実施態様の基本プロセスフローの例を示す説明図（断面図による）である。 30

【図1】

【図3】

【図2】

【図4】

【図5】

【図7】

【図6】

【図8】

【図9】

【図11】

【図10】

【図12】

【図13】

【図14】

【図15】

【図18】

【図16】

【図19】

【図17】

【図20】

【図21】

## フロントページの続き

(74)代理人 100086243

弁理士 坂口 博

(72)発明者 アモス、リッキー、エス

アメリカ合衆国 12572 ニューヨーク州 レインベック クアリー・ロード 512

(72)発明者 ボイド、ダイアン、シー

アメリカ合衆国 12540 ニューヨーク州 ラグランジュヴィラ マーティン・ロード 16

2

(72)発明者 カプラル、セロ、ジュニア

アメリカ合衆国 10541 ニューヨーク州 マオパク ゴールドフィンチ・レーン 17

(72)発明者 カプラン、リチャード、ディー

アメリカ合衆国 12590 ニューヨーク州 ワピンジャーズ・フォールズ チャニングヴィラ

・ロード 43

(72)発明者 ケンジェルスキ、ジャクブ、ティー

アメリカ合衆国 10566 ニューヨーク州 ピークスキル ベネフィールド・プラヴァード

132

(72)発明者 ケーユー、ヴィクター

アメリカ合衆国 10591 ニューヨーク州 テリータウン ホワイト・プレーンズ・ロード

177 アパートメント ビルディング8 #41B

(72)発明者 リー、ウヒョン

アメリカ合衆国 12570 ニューヨーク州 ブーケアグ ゴールド・ロード 11

(72)発明者 リー、イン

アメリカ合衆国 12603 ニューヨーク州 ポーキプシー ジャックマン・ドライブ 124

B

(72)発明者 モクタ、アンダ、シー

アメリカ合衆国 12540 ニューヨーク州 ラグランジュヴィラ ヘリティジ・レーン 73

(72)発明者 ナラヤナン、ビジェイ

アメリカ合衆国 10069 ニューヨーク ニューヨーク リバーサイド・プラヴァード 1

80 #12C

(72)発明者 ズテーゲン、アン、エル

アメリカ合衆国 06902 コネチカット州 スタンフォード サウスフィールド・アベニュー

150 アパートメント 2438

(72)発明者 スレンドラ、マエスワレン

アメリカ合衆国 10520 ニューヨーク州 クロトン・オン・ハドソン グランド・ストリー

ト 64

審査官 宇多川 勉

(56)参考文献 特開平11-121745 (JP, A)

特開2000-252462 (JP, A)

特開昭62-154784 (JP, A)

特開平05-021458 (JP, A)

特開平08-203845 (JP, A)

特表2003-536259 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/8238

H01L 21/28

H01L 27/092

H01L 29/423

H01L 29/49