#### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

## (19) World Intellectual Property Organization

International Bureau

## (43) International Publication Date 5 August 2010 (05.08.2010)

# (10) International Publication Number WO 2010/086651 A1

(21) International Application Number:

PCT/GB2010/050123

(22) International Filing Date:

27 January 2010 (27.01.2010)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

0901389.7 28 January 2009 (28.01.2009)

GB

- (71) Applicant (for all designated States except US): NANO EPRINT LIMITED [GB/GB]; Core Technology Facility, 46 Grafton Street, Manchester M13 9NT (GB).

- (72) Inventors; and

- (75) Inventors/Applicants (for US only): SONG, Aimin [CN/GB]; 80 Craig Road, Stockport Greater Manchester SK4 2BG (GB). WHITELEGG, Stephen [GB/GB]; 48 Marina Road, Bredbury, Stockport Greater Manchester SK6 2PR (GB). SUN, Yanming [CN/CN]; No 66 Fukang Village, Jingzhi Town, Weifang City, Shandong 262119 (CN). LIN, Shiwei [CN/CN]; College of Materials and Chemical Engineering, Hainan University, Haikou, Hainan 570228 (CN).

- (74) Agent: HARRISON GODDARD FOOTE; 106 Micklegate, York, Yorkshire YO1 6JX (GB).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PE, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### **Declarations under Rule 4.17:**

— of inventorship (Rule 4.17(iv))

#### Published:

- with international search report (Art. 21(3))

- before the expiration of the time limit for amending the claims and to be republished in the event of receipt of amendments (Rule 48.2(h))

(54) Title: ELECTRONIC DEVICES, CIRCUITS AND THEIR MANUFACTURE

(57) Abstract: A method of manufacturing an electronic device, comprising a layer of semiconductive material and at least one insulative feature arranged to interrupt the layer of semiconductive material, comprises: providing a layer of semiconductive material, and a layer of compressible material supporting the layer of semiconductive material; and forming the or each insulative feature by a method comprising displacing a respective selected portion of the layer of semiconductive material towards the compressible material so as to compress compressible material under the or each displaced portion and separate at least partly the or each displaced portion from undisplaced semiconductive material.

1

#### ELECTRONIC DEVICES, CIRCUITS AND THEIR MANUFACTURE

#### Field of the Invention

The present invention relates to electronic devices and electronic circuits and methods of manufacturing such devices and circuits. In particular, although not exclusively, certain embodiments of the invention are concerned with nano electronic devices and circuits and their manufacture, that is devices and circuits having features with dimensions in the range of 10 to 300 nanometres.

#### Background to the Invention

Electronic devices and features comprising a layer of semiconductive material patterned with insulated features are known. Examples of such devices and circuits are disclosed in WO 02/086973 A2, WO 2006/008467 A1, and WO 2006/120414 A2. The contents of each of these documents are incorporated herein by reference. The disclosed devices include devices formed in a single layer of semiconductive material and in which a pattern of insulative features has been formed to interrupt the semiconductive layer and define at least one operational characteristic of the device. These documents also disclose certain methods suitable for forming the insulative features required to define these electronic devices in the layer of semiconductive material. Those techniques include X-ray beam and electron beam lithography. Another suitable technique disclosed is a so-called nano imprint process (from US-A-5,772,905) in which a mould having extremely small projections formed by E-beam lithography is pressed into a plastics polymer layer on a substrate so as to create depressions in the layer corresponding to the mould projections. It is further disclosed that an etching process may then be carried out to expose the substrate (underlying the patterned layer) in the depression areas. In other words, the disclosed technique embosses a pattern of depressions in the upper layer supported by the substrate. The substrate is not deformed by the patterning process. The embossing process forms depressions, but generally speaking do not completely interrupt the upper layer; some of the upper layer material remains at least at the bottom of the depressions, thereby providing a connection between the upper layer material on one side of the depression with that on the other side. In order to convert an embossed depression into a fully insulating feature it is necessary to perform some post-processing, such as etching, to remove or "clean out" upper layer material from the depressions, leaving exposed insulative

2

substrate. Clearly, whilst this imprinting or embossing technique offers some advantages in terms of facilitating the initial patterning of the upper layer, it has disadvantages as a technique for forming insulative features, because additional processing steps are required. Furthermore, this imprinting technique may undesirably distort the upper layer of semiconductive material, at least in the vicinity of each embossed trench. Furthermore, the etching technique required to expose the underlying substrate may result in undesirable removal of semiconductive material from other portions of the semiconductive layer.

It will be appreciated that in the fabrication of electronic devices and circuits, disadvantages associated with additional processing steps include the fact that the total manufacturing time is increased, and so are the complexity and costs of the overall process.

An additional problem with existing techniques for etching features in semiconductive materials is that those techniques may be suitable for use with certain materials but not others. The requirement to choose a technique compatible with the device materials being employed represents a further restriction on the process engineering.

#### Summary of the Invention

It is an aim of certain embodiments of the invention to solve, mitigate or obviate, at least partly, at least one of the problems and/or disadvantages associated with the prior art.

Certain embodiments of the invention aim to provide methods which facilitate the manufacture of electronic devices and/or circuits comprising a plurality of devices. Certain embodiments aim to provide methods of manufacture which are faster than certain prior art techniques. Further embodiments aim to provide methods of manufacture which are compatible with fast, high volume production of electronic devices and/or circuits. Certain embodiments aim to provide methods of manufacturing electronic circuits comprising a plurality of electronic devices formed on a common, flexible substrate. Certain embodiments aim to provide methods of manufacturing electronic devices and/or circuits having a reduced number of steps compared with prior art techniques.

3

According to a first aspect of the present invention there is provided a method of manufacturing an electronic device (or component) comprising a layer of semiconductive material and at least one insulative feature, the or each insulative feature being arranged to interrupt the layer of semiconductive material (e.g. so as to at least inhibit current flow across the feature), the method comprising:

providing a layer of semiconductive material, and a layer of compressible material supporting the layer of semiconductive material; and

forming the or each insulative feature by a method comprising displacing a respective selected portion of the layer of semiconductive material towards the compressible material so as to compress compressible material under the or each displaced portion and separate at least partly the or each displaced portion from undisplaced semiconductive material.

For the purposes of the present specification, the term "insulative" is to be understood as encompassing both completely insulative (i.e. completely electrically isolating) features as well as "relatively insulative", that is having a conductivity less than, or substantially less than, that of the uninterrupted semiconductive material. In other words, each insulative feature provides at least a partial barrier to current flow in the layer of semiconductive material across the feature.

In certain embodiments, the electronic device comprises a plurality of said insulative features.

In certain embodiments, the insulative feature or features define a pattern, and the step of forming the or each insulative feature comprises patterning the layer of semiconductive material with the insulative feature or features.

The term "pattern" in this context should be interpreted as meaning any predetermined arrangement, which could comprise a single element, shape, line or other feature, or may comprise a plurality of elements, which may be separate from one another, connected to one another, or the pattern may comprise a combination of one or more separate elements and one or more connected elements.

According to another aspect of the invention there is provided an electronic device comprising a patterned layer of semiconductive material, the method comprising:

4

providing a layer of semiconductive material, and a layer of compressible material supporting the layer of semiconductive material; and

patterning the layer of semiconductive material by displacing at least one selected portion of the layer of semiconductive material towards the compressible material so as to compress compressible material under the or each displaced portion and separate (divide, sever) at least partly the or each displaced portion from undisplaced semiconductive material (e.g. undisplaced semiconductive material immediately adjacent to the displaced portion) such that the or each displaced portion forms at least part of a respective insulative feature interrupting the layer of undisplaced semiconductive material, whereby the insulative feature or features define a pattern.

In certain embodiments, said displacing comprises separating the or each displaced portion from undisplaced semiconductive material.

In certain embodiments, the or each displaced portion forms a said insulative feature.

In certain embodiments, the pattern defines at least one electrical and/or electronic characteristic of the device.

In certain embodiments, the electronic device is an active device.

In certain embodiments, the pattern defines at least one elongate channel of semiconductive material extending from a first portion (or area) of the layer of semiconductive material to a second portion (or area) of the layer of semiconductive material.

In certain embodiments, the length of this channel may be in the range 60 to 2000nm and the width of the channel may be in the range 20-400nm

In certain embodiments, the pattern defines at least one gate region of the layer of semiconductive material to which a potential may be applied to control a conductivity of the elongate channel.

In certain embodiments, the gate region comprises at least part of one of the first and second regions.

In certain embodiments, the gate region is distinct (separated) from the first and second

5

regions.

For example, this gate region may be separated from the first and second regions by

one or more of the insulative features.

In certain embodiments, the pattern is arranged such that the device is operable as (i.e.

functions as) at least one of: a self-switching device; a diode; a FET; a memory device;

and a logic gate (e.g. an AND gate; a NAND gate; an OR gate; a NOR gate; a NOT

gate).

In certain embodiments, the pattern is arranged to define a plurality of electronic

devices in the layer of semiconductive material.

In certain embodiments, the pattern is further arranged to define at least one

connecting portion of semiconductive material in the layer of semiconductive material,

the or each connecting portion providing an electrical connection between a respective

pair of said plurality of electronic devices.

In certain embodiments, the pattern is arranged to define a plurality of electronic

devices and interconnections in the layer of semiconductive material, the plurality of

electronic devices and interconnections forming at least part of an electronic circuit.

It will be appreciated that these interconnections may include connections between two

or more devices, between a device and a voltage or supply rail or rails, a connection

between a device and a terminal etc.

In certain embodiments, the or each selected portion has a width in the range from 300

nm to 1 mm depending on the need of integration density and easy of manufacture.

In certain embodiments, the layer of semiconductive material has a thickness T and

said displacing comprises displacing the or each selected portion towards the

compressible material by a distance greater than T.

6

said displacing comprises displacing the or each selected portion towards the

In certain embodiments, the layer of semiconductive material has a thickness T and

compressible material by a distance less than or equal to T.

In certain embodiments, the compressible material is at least partially resilient, the method further comprising allowing the or each displaced portion to return at least partially towards the layer of semiconductive material.

In certain embodiments, the said displacing comprises producing an inelastic (i.e. permanent, irreversible, plastic etc) deformation of compressible material under the or each displaced portion, so as to leave the or each displaced portion permanently offset from the layer of semiconductive material.

In other words, the displacing of selected portions and the compression of compressible material may produce deformations of the compressible material having at least an inelastic component, such that when the force or action causing the displacement is removed, the compressible material does not return fully, or in certain cases does not return at all, to its original position, leaving the displaced portion of semiconductive material permanently offset from the semiconductive layer.

In certain embodiments, said inelastic deformation is such that the or each displaced portion is permanently displaced by a distance greater than T.

In certain embodiments, the displacement of the or each selected portion forms a permanent depression or trench in the layer of semiconductive material.

In some embodiments, the displacing operation may be such that substantially no semiconductive material lines the side walls of the depression or trench, such that the displaced portion of semiconductive material is electrically isolated or disconnected from portions of the semiconductive layer on either side of the trench. However, in alternative embodiments there may be some semiconductive material on the side walls of the depressions or trenches, and the method may comprise a step to remove such material in order to more fully electrically isolate the displaced portion from the undisplaced layer.

7

In certain embodiments, the method further comprises removing semiconductive

material from side walls of the or each depression or trench.

In certain embodiments, the method further comprises filling the or each depression or

trench with insulative material.

In certain embodiments, said displacing comprises severing the or each selected

portion of semiconductive material from the layer of semiconductive material.

In certain embodiments, said compressible material is porous and said displacing

comprises compressing the compressible material to reduce a porosity of the

compressible material under the or each displaced portion.

In certain embodiments, said displacing comprises compressing compressible material

from a first density to a second, higher density.

In certain embodiments, said compressible material is an insulative material, for

example an insulative material selected from a list comprising: polymethyl methacrylate,

polybutyl methacrylate, polyethyl methacrylate, polyvinyl acetate, polyvinyl pyrrolidone,

polyvinylphenol, polyvinylchloride, polystyrene, polyethylene, polyvinyl alcohol,

polycarbonate.

In certain embodiments, the method further comprises providing a substrate arranged to

support the compressible layer.

Typically, this substrate will then form an integral part of the manufactured device, the

substrate supporting both the compressible layer and the layer of semiconductive

material patterned with one or more insulative features by the manufacturing method.

In certain embodiments, the substrate is substantially non-compressible.

In certain embodiments the substrate comprises a layer of material selected from a list

comprising: glass (rigid or flexible); polymer (e.g. polyethylene naphthalate or

polyethylene terephthalate); polymeric foil; paper; insulator coated metal (e.g. coated

stainless-steel); cellulose; polymethyl methacrylate; polycarbonate, polyvinylalcohol;

polyvinyl acetate; polyvinyl pyrrolidone; polyvinylphenol; polyvinyl chloride; polystyrene;

polyethylene naphthalate; polyethylene terephthalate; polyamide (e.g. Nylon); poly(hydroxyether); polyurethane; polycarbonate; polysulfone; polyarylate; acrylonitrile butadiene styrene, 1-Methoxy-2-propyl acetate (SU-8), polyhydroxybenzyl silsesquioxane (HSQ), polyimide, Benzocyclobutene (BCB), Al<sub>2</sub>O<sub>3</sub>, SiO<sub>x</sub>N<sub>y</sub>, SiO<sub>2</sub>, Si<sub>3</sub>N<sub>4</sub>.

In certain embodiments, the method further comprises providing a support surface, and supporting the compressible layer with the support surface during said displacing.

In such embodiments, the support surface can then be removed or separated from the compressible layer and semiconductive layer after patterning. In certain embodiments the support surface is flat, but in other embodiments the support surface may have another shape, for example it may be curved. In certain embodiments, the support surface is the cylindrical surface of a support roller.

In certain embodiments, the layer of compressible material is arranged to support the layer of semiconductive material directly.

In certain embodiments, the method further comprises providing at least one intermediate layer of material between the layer of semiconductive material and the layer of compressible material.

In certain embodiments the intermediate layer of material may comprise or consist of material selected from a list comprising: self-assembled monolayer, siloxanes, thin-film inorganic oxide (e.g. alumina, silica, silicon sub-oxide) or nitride (e.g. SiN) or other materials which can selectively promote or discourage adhesion across the whole layer or can be patterned to provide regions of relatively good or poor adhesion as appropriate. The material choice would be determined by matching the hydrophobicity or hydrophilicity of the intermediate layer with that of the semiconductor material. The intermediate layer should be substantially insulating though it may be used to affect and/or control the charge carrier concentration within the semiconductor material.

Suitable self-assembled monolayers could be selected from the following list: Organosilane such as 3-Aminopropyl-triethoxysilane, Trichloro(1H,1H,2H,2H-perfluorooctyl)silane [CF<sub>3</sub>(CF<sub>2</sub>)<sub>5</sub>CH<sub>2</sub>CH<sub>2</sub>SiCl<sub>3</sub>], Trichloro(3,3,3-trifluoropropyl)silane [CF<sub>3</sub>CH<sub>2</sub>CH<sub>2</sub>SiCl<sub>3</sub>],Triethoxy(1H,1H,2H,2H)perfluorodecylsilane [CF<sub>3</sub>)(CF<sub>2</sub>)<sub>7</sub>(CH<sub>2</sub>)<sub>2</sub>Si(OC<sub>2</sub>H<sub>5</sub>)<sub>3</sub>], Octadecyltrichlorosilane [CH<sub>3</sub>(CH<sub>2</sub>)<sub>17</sub>SiCl<sub>3</sub>],

9

Butyltrichlorosilane [CH<sub>3</sub>(CH<sub>2</sub>)<sub>3</sub>SiCl<sub>3</sub>], Trichloro(octyl)silane [CH<sub>3</sub>(CH<sub>2</sub>)<sub>7</sub>SiCl<sub>3</sub>] and Hexamethyldisilazane [CH<sub>3</sub>)<sub>3</sub>SiNHSi(CH<sub>3</sub>)<sub>3</sub>]. Other organosilane materials, which may be used in embodiments of the invention, are contained within the following articles incorporated by reference herein: *Nature Materials* 3, 317 - 322 (2004); PRAMANA-JOURNAL OF PHYSICS, 67(1), pp 17-32, JUL 2006; J. Appl. Phys. **96**, 6431 (2004).; Appl. Phys. Lett. **91**, 192112 (2007).

Alternatively or in addition to the intermediate layer, other processing techniques may be used in embodiments of the invention to modify the surface (e.g. to improve adhesion of the semiconductive material to the compressible material and/or intermediate layer) prior to deposition or introduction of the semiconductive material. These include UV, plasma, ozone, corona discharge, piranha etch, and surface treatment such as described in EP1124791 or US7034129, the contents of which are incorporated by reference herein.

In certain embodiments, said displacing comprises pressing (urging) the or each selected portion towards the compressible layer using an embossing tool (which in certain embodiments may also be described as a stamp or shim).

In general, this embossing tool may take a wide variety of forms, and may be described as some means for positioning with respect to the semiconductive layer and then urging towards the layer of compressible material supporting the semiconductive layer so as to displace a selected portion or portions of the semiconductive material. The embossing tool may be arranged to produce the insulative features only by stamping (i.e. while any embossing surface of the embossing tool is in the process of pressing a portion of semiconductive material towards the compressible layer that surface is confined to moving only in a direction substantially perpendicular to the semiconductive layer; there is substantially no relative movement between the embossing surface and semiconducting layer in any direction along the semiconductive layer). However, in alternative embodiments, the embossing tool may be arranged so as to be moveable, whilst depressing the semiconductive layer (either directly or indirectly), in one or more directions substantially parallel to that layer so as to produce an extended insulative feature. In other words, whereas in certain embodiments the embossing tool may be arranged to produce insulative features by a pressing or stamping process, in alternative embodiments the embossing tool may be moveable so as to "write"

10

insulative features in the substrate. Such written features can include insulative lines, for example.

In certain embodiments, the embossing tool comprises at least one embossing feature raised above a base surface, the method comprising urging the embossing tool towards the compressible layer such that each embossing feature displaces a respective selected portion of the layer of semiconductive material.

In other words, the embossing tool may comprise a plurality of embossing features, each corresponding to a respective insulative feature in the semiconductive layer of the manufactured device.

In certain embodiments, the embossing tool comprises a plurality of said embossing features arranged to define the pattern of insulative features in the semiconductive layer of the device.

In certain embodiments, the method further comprises using the embossing tool to displace a plurality of selected portions of the layer of semiconductive material in parallel.

In certain embodiments, the method comprises using the embossing tool to displace a plurality of portions of semiconductive material in parallel so as to define a plurality of devices (and, optionally, one or more interconnections between the devices) in the layer of semiconductive material in parallel (i.e. at the same time).

In certain embodiments, the method further comprises arranging the embossing tool such that the base surface is substantially planar, arranging the layer of semiconductive material to be substantially planar and parallel to the base surface, and urging the embossing tool towards the layer of semiconductive material such that each embossing feature displaces a respective selected portion of the layer of semiconductive material at the same time.

In certain embodiments, the embossing tool is substantially rigid.

In certain embodiments, the embossing tool is substantially flexible, the method further comprising supporting the embossing tool on a substantially planar (flat) support surface.

In certain embodiments, the method further comprises arranging the embossing tool such that the base surface lies substantially on the surface of a cylinder having a longitudinal axis, and rotating the embossing tool about said axis to pattern the layer of semiconductive material with the or each embossing feature of the tool.

In certain embodiments, the embossing tool is substantially flexible, the method further comprising supporting the embossing tool on a cylindrical surface (e.g. the surface of a support roller).

In certain embodiments, the embossing tool has a three-dimensional pattern or step created with two or more levels (e.g. the embossing tool may comprise a plurality of embossing surfaces arranged at a plurality of different heights with respect to a base surface), such as described in US patent 7202179, for example. In other words, the embossing tool may comprise stepped embossing features, at two or more heights or levels.

In certain embodiments, the layer of semiconductive material and the layer of compressible material are substantially flexible, the method further comprising supporting the layers of semiconductive and compressible material on a cylindrical support surface during said displacing.

In certain embodiments, at least one embossing feature comprises an embossing surface raised a distance d above the base surface.

In certain embodiments, d can be in the range or ranges 10 to 3000nm.

In certain embodiments, the or each embossing surface is substantially flat.

In certain embodiments, the or each embossing feature has a substantially rectangular cross section.

In certain embodiments, the or each embossing surface has a width w.

12

In certain embodiments, w can be in the range or ranges 10 to 3000nm

In certain embodiments, d is substantially equal to w.

In certain embodiments, d is >w.

In certain embodiments, d is  $\geq 2w$ .

In certain embodiments, the aspect ratio of the embossing features can be even higher, for example d may be 3, 4, 5, 6 times greater (or even more), than w.

In certain embodiments, the embossing tool comprises a plurality of embossing features, and wherein the minimum separation between any two of such embossing features is  $\geq w$ .

In certain embodiments, the embossing tool comprises at least one embossing surface, the method comprising using the or each embossing surface to press a respective selected portion of the layer of semiconductive material towards the compressible layer.

In certain embodiments, the method further comprises pressing the or each embossing surface directly against a respective portion of the layer of semiconductive material to displace that portion.

In certain embodiments, the method further comprises coating the or each embossing surface (e.g. with one or more coating materials) before using each coated embossing surface to displace a respective portion of the layer of semiconductive material.

In certain embodiments, the coating material is arranged to reduce adhesion between the embossing surface and the layer of semiconductive material, or an intermediate layer of material between the embossing surface and semiconductive material to improve the definition of the insulative features formed by the embossing technique. The use of a suitable coating material can reduce or even prevent the coating of the side walls of any trenches with semiconductive material, so helping electrically isolate the displaced portions from the undisplaced semiconductive material. The use of a suitable coating material can also reduce or prevent distortion of the nominally

13

undisplaced layer of semiconductive material when the embossing tool is withdrawn (i.e.

separated from the device pre-form).

In certain embodiments, the method further comprises providing at least one separating

layer of material between the embossing tool and the layer of semiconductive material,

and using the embossing tool to press the or each selected portion of semiconductive

material towards the compressible layer through the separated layer or layers.

For example, the at least one separating layer may include a separating layer in the

form of a non-stick or adhesion-reducing film used just in the manufacturing process,

and/or the at least one layer of separating material may include a further device layer

(such as a layer of insulative material) provided over the layer of semiconductive

material. For example, the separating layers may include an upper layer, which

together with the semiconductive layer, compressible layer, and any supporting layer

beneath, form the eventual device or at least part of that device.

In certain embodiments, the method further comprises setting a temperature of the layer

of semiconductive material to a predetermined value t1 before using the embossing tool

to displace the or each selected portion.

It will be appreciated that controlling the temperature in this way can be used to various

effects, such as to render the semiconductive material more flexible, to set the

semiconductive material above or below a glass transition temperature, to embrittle the

semiconductive material, etc.

In certain embodiments, the method further comprises setting a temperature of the

embossing tool to a predetermined value t2 before using the embossing tool to displace

the or each selected portion of semiconductive material.

In certain embodiments, t1 = t2.

In certain embodiments, t1 does not equal t2.

In certain embodiments, t1 > t2.

14

PCT/GB2010/050123

Such a method can be used to selectively cool the portions of semiconductive material to be displaced. In certain embodiments, this selective cooling can be used to selective embrittle the layer of semiconductive material prior to displacement and improve electrical separation from the undisplaced semiconductive material.

In certain embodiments, t1 < t2.

Such methods can be used to selectively heat portions of semiconductive material to be displaced, and in certain embodiments this can achieve selective softening of portions of the layer of semiconductive material.

Thus, in certain embodiments, the method may comprise controlling (e.g. setting) the temperature of one or more of the embossing tool and semiconductive layer before using the embossing tool to displace selected portions of semiconductive material and produce insulative features. In certain embodiments, the methods may further comprise the step of controlling and changing the temperature of at least one of the embossing tool and semiconductive layer whilst the embossing tool is in contact with the semiconductive layer or at least some intermediate layer between the two, and then withdrawing the embossing tool away from the semiconductive layer whilst this different temperature is maintained. This gives the device fabricator another adjustable parameter which can be tailored generally to improve the electrical characteristics of the insulative features produced by the embossing feature and/or reduce (even to zero) the number of post-processing steps required to complete the semiconductive device or circuit.

In certain embodiments, the method further comprises controlling a force applied to pattern the layer of semiconductive material with the embossing tool.

In certain embodiments, the method further comprises modulating said force (e.g. by pulsing the force, or in other words modulating its magnitude).

In certain embodiments, the method further comprises controlling a length of time for which the embossing tool is pressing the or each selected portion.

In other words, in certain embodiments the method further comprises controlling a length of time for which the embossing tool is directly or indirectly in contact with the

15

semiconductive layer before the end of the embossing step (i.e. before the embossing tool is withdrawn). This control may also take the form of controlling the speed of rotation of a roller supporting the embossing tool or layer of semiconductive material.

In certain embodiments, the method comprises pulsed-heating (e.g. by voltage, or other electrical, heating) of the embossing tool and/or pulsed pressure (i.e. modulation of the force applied to the embossing tool). This can improve the fidelity of the embossed features or structures.

For example, in certain embodiments the de-stamping (or withdrawal/separation of the embossing tool from the embossed "target" or object) can be done from a substantially cold material.

In certain embodiments, the method can comprise selectively heating the substrate, tool, or both.

In certain embodiments, the method comprises active cooling of the tool, for example prior to, or during contact with the target /object of the embossing process, such as to cool the tool before withdrawal/separation.

For example, certain embodiments comprise clamping an embossing tool to the target substrate at a desired temperature (e.g. room temperature, RT), then heating the arrangement to a desired higher temperature (e.g. 110 degrees C), then applying a desired force (e.g. 2000N) to exert a desired pressure (e.g. 500N/cm2), holding for a predetermined time (e.g. 30 minutes), then cooling the arrangement down to a desired temperature (e.g. RT), and then separating the tool from the embossed target at this temperature (e.g. RT).

In certain embodiments, the semiconductive material comprises at least one semiconductive material selected from a list comprising: polymer semiconductor, organic semiconductor, printable inorganic semiconductor, crystalline inorganic semiconductor, amorphous inorganic semiconductor.

Examples of polymer semiconductor include polyalkylthiophenes (e.g. P3HT), polyarylamines (e.g. PTAA), copolymers of fluorene and thiophene, polyparaphenylenevinylene (PPV). Other examples of n- or p-type organic

semiconductor materials are described in the following references: Chem. Rev. 2007, 107, 953-1010; Chem. Rev. 2007, 107, 1066-1096 and US 7029945; Angew. Chem. Int. Ed. 2008, 47, 452 – 483 (precursor organic semiconductors); US2004038459A1, Nature Materials VOL 4 Aug 2005 p601, Nature Materials VOL 5 Dec 2006 p950, EP1579518A1 (blends of organic semiconductors with semiconductors).

Examples of organic conductors include polystyrenesulfonate doped poly(3,4-ethyelenedioxythiophene) - (PEDOT/PSS), polyaniline (PANI), polyfuran, polypyrrole or polycarbazole.

Other examples of organic conductors and semiconductors are described in the following articles incorporated by reference herein: Current Applied Physics 3 (2003) 293–305.

Examples of organic insulators include polymethyl methacrylate, polyvinylalcohol, polyvinyl acetate, polyvinyl pyrrolidone, polyvinylphenol, polyvinyl chloride, polystyrene, polyamide (e.g. Nylon), poly(hydroxyether), polyurethane, polycarbonate, polysulfone, polyarylate, acrylonitrile butadiene styrene, 1-Methoxy-2-propyl acetate (SU-8), polyhydroxybenzyl silsesquioxane (HSQ), polyimide, benzocyclobutene (BCB). Other examples are described in the following incorporated by reference herein: Chemistry of Materials (2004), 16(23), 4543-4555; Organic Electronics (2003), 4(1), 27-32; Advanced Functional Materials (2003), 13(3), 199-204.

The active material may optionally be chemically doped with one of the following:

For p-type: 2,3,5,6-tetrafluoro-7,7,8,8-tetracyano-quinodimethane (F4-TCNQ); WO<sub>3</sub>, MoO<sub>3</sub> or V<sub>2</sub>O<sub>5</sub>; Lewis acids such as FeCl<sub>3</sub> or SbCl<sub>5</sub>.; Ruthenium tris-(terpyridine), Tetrakis (1,2,3,3a,4,5,6,6a,7,8-decahydro-1,9,9b-triazaphenalenyl) ditungsten (II));

For n-type: Acridine Orange Base (AOB, C17H19N3); Li; Cs; Rhodamine P

and examples contained within: US 7161292, EP1837926, WO2007DE00587, EP1837927 (A1), WO2007107356, EP1643568 (A1), EP1538684 (A1), EP1860709 (A1), US2007278479, US2007148812, US2007145355

Examples of printable inorganic semiconductors include metal oxides such as indium tin-oxide, zinc oxide, titanium dioxide, indium zinc-oxide, gallium indium zinc oxide or

metal oxides as described in Appl. Phys. Lett. 88, 123509 (2006) or WO2005112045, the contents of which are incorporated herein by reference.; silicon inks

Examples of crystalline inorganic semiconductors include group IV semiconductors such as silicon, germanium or the like; III-V semiconductor such as gallium arsenide, indium phosphide.

Examples of amorphous inorganic semiconductors include amorphous silicon.

Doping or control of carrier concentration can also be achieved using induced dipole effects as described in UK patent application no. GB819684.2, incorporated in its entirety by reference herein.

In certain embodiments, the semiconductive material is a precursor material, the method further comprising processing the patterned layer of semiconductive material to render the semiconductive material semiconducting.

In certain embodiments, the layer of compressible material comprises at least one compressible material selected from a list comprising polymethyl methacrylate, polybutyl methacrylate, polyethyl methacrylate, polyvinyl acetate, polyvinyl pyrrolidone, polyvinylphenol, polyvinylchloride, polystyrene, polyethylene, polyvinyl alcohol, polycarbonate.

According to another aspect of the invention there is provided a method of manufacturing an electronic circuit comprising a plurality of electronic devices and a plurality of interconnections between the electronic devices in a single layer of semiconductive material, the method comprising:

providing a layer of semiconductive material, and a layer of compressible material supporting the layer of semiconductive material; and

patterning the layer of semiconductive material with a plurality of insulative features, each insulative feature being arranged to interrupt the layer of semiconductive material and the pattern of insulative features defining the electronic devices and interconnections.

wherein said patterning comprises:

forming each insulative feature by a method comprising displacing a respective selected portion of the layer of semiconductive material towards the compressible

material so as to compress compressible material under each displaced portion and separate at least partly each displaced portion from undisplaced semiconductive material.

18

It will be appreciated that the electronic circuit manufactured in this way may be described as a substantially planar electronic circuit.

According to another aspect of the invention there is provided an electronic device comprising:

a layer of semiconductive material;

at least one insulative feature arranged to interrupt the layer of semiconductive material (e.g. so as to at least inhibit current flow across the feature); and

a layer of compressible material arranged to support the layer of semiconductive material,

wherein the or each insulative feature comprises a respective selected portion of semiconductive material from the layer of semiconductive material, the respective selected portion being separated at least partly from adjacent semiconductive material of (or in) the layer of semiconductive material.

According to another aspect of the invention there is provided an electronic circuit comprising, in a single layer of semiconductive material, a plurality of electronic devices and a plurality of interconnections between the electronic devices, and a layer of compressible material arranged to support the layer of semiconductive material, wherein the layer of semiconductive material is patterned with a plurality of insulative features, each insulative feature being arranged to interrupt the layer of semiconductive material and the pattern of insulative features defining the electrical devices and interconnections, and wherein each insulative feature comprises a respective selected portion of semiconductive material from the layer of semiconductive material, the respective selected portion being separated at least partly from adjacent semiconductive material of the layer of semiconductive material.

In certain embodiments, the or each respective selected portion is displaced from the layer of semiconductive material in a direction towards the compressible layer such that the compressible layer has a higher density under the or each selected portion than under the undisplaced portions of the layer of semiconductive material.

Another aspect of the invention provides an electronic device or electronic circuit manufactured using a method in accordance with any other aspect of the invention.

19

For example, certain embodiments provide a ZnO planar nano transistor, with an on/off ratio of approximately 300, formed from a substrate structure comprising: ZnO (10nm)/PMMA (1000nm)/SiO<sub>2</sub>/Si.

It will be appreciated that certain embodiments of the present invention relate to methods for forming device templates suitable for post-processing into devices, such as electronic or photonic devices, by forming isolating regions in templates which have an active layer (of semiconductive material) supported on a carrier substrate. In particular, certain embodiments relate to the production of layered device templates with nanometre scale structures.

It is known to produce devices, such as individual electronic components or integrated circuits, from pre-forms which have a thin active layer, such as a semiconductor layer, supported on a carrier substrate. In electronic devices, regions of the active layer are modified into a device template by a variety of treatments in order to make them n-type semiconductor, p-type semiconductor, conductive, insulating, etc. For photonic devices, a nanostructure is typically formed via conventional nanolithography techniques.

For both electronic and for photonic device templates, it may be necessary to form regions which act as isolating areas between regions of active layer. This is also the case with templates for integrated circuit devices. Conventional methods for forming isolating areas involve a complex processing step such as electron beam lithography or ion bean lithography for each individual device template. This is time consuming when many device templates are to be formed to the same design.

As discussed above, US 5,772,905 discloses a lithographic method and apparatus for creating nanometre scale patterns in a thin film coated onto a substrate. Protruding features on the mould create a recess in the thin film. The thin film is then subsequently processed to remove the material in the recesses, exposing the underlying substrate.

Hence there is a need for a method for forming isolating areas on device templates which is less complex and more rapid than prior art methods for mass production of

device templates, and which can produce isolating areas in a device template in a single processing step.

20

According to another aspect of the invention there is provided a method for forming a device template from a pre-form comprising an active layer, of active layer semiconductive material, having an active layer thickness, supported on a carrier substrate wherein one or more isolating areas are provided in the active layer, characterized in that the isolating areas are apertures in the active layer formed by permanently displacing portions of the active layer material into a non-conductive layer between the insulating substrate and the active layer with a stamp having a base area and raised embossing areas having a height above the base area of the stamp which is greater than the active layer thickness whereby the embossing areas of the stamp displace portions of the active layer such that are no longer in contact with undisplaced active layer.

The method has the advantage that the design template for the device need only be etched once, into the stamp, and can subsequently be imprinted onto device templates by the simple and rapid method of repeatedly pressing, either by flat/stamp, step-and-move rotary or continuous roll-to-roll embossing, the embossed face of the stamp into pre-forms. The method also gives the advantage that the use of beams such as ion, electron or light, to perform lithography on each device template, is no longer needed. If, for instance, mechanical engraving is used for the production of the stamp, the minimum size of the features produced by the method of the invention need not be limited by beam resolution, as is the case with direct beam lithography technologies.

Certain methods embodying the invention also provide a device, formed from the device template resulting from the method. By device template is meant a patterned active layer carried on a carrier substrate which is suitable for subsequent further processing in order to form a device. The device template may also be usable at once, for instance if it is in the form of an optical grating produced by the method of the invention.

The device may comprise a plurality of interconnected components on the same carrier substrate. The method may be used to form a plurality of device templates on a single pre-form, such that a plurality of devices may be formed by post-processing the preform and separating it into individual devices.

Another aspect of the invention provides a device comprising an active layer, of semiconductive active layer material, having an active layer thickness, supported on a carrier substrate wherein one or more isolating areas are provided in the active layer, characterized in that the device comprises a non-conductive layer between the active layer and the carrier substrate wherein one or more displaced portions of active layer material are present in the non-conductive layer between the apertures in the active layer and the carrier substrate and that the displaced portions of active layer material are not in conductive contact with the active layer.

Further features of embodiments of the invention, detailed below, apply, where appropriate, to any of the above-mentioned aspects of the invention.

In certain embodiments the pre-form comprises an active layer of semiconductive material supported on a carrier substrate. The pre-form may also comprise other layers between the active layer and carrier substrate, or also on top of the carrier substrate. The active layer may be active at the time of carrying out the method of the invention, or may be a layer formed from a precursor material as the active layer material, which precursor material is subsequently processed to form an electrically semiconductive active layer, or the like. In other words, active layer refers to the ultimate use of the layer in the device to be formed from the device template generated by the method embodying the invention.

Certain embodiments of the invention involve the application of a stamp to the pre-form in order to emboss the pre-form. The stamp (which may also be described as an embossing tool) may have a base area and raised embossing areas having a height above the base area of the stamp which is greater than the active layer thickness such that when the stamp is pressed into the pre-form the embossing areas of the stamp displace portions of the active layer such that are no longer in contact with undisplaced active layer.

The embossing stamp may be in the form of a planar stamp such that the contact surfaces of the raised embossing area, which contact the pre-form in the method of the invention, are arranged in a common plane. The embossing stamp may be in the form of a cylindrical roller, with the contact surfaces of the raised embossing area arranged to be at the surface of a cylinder.

22

Alignment of the stamp with the pre-forms prior to pressing the stamp into the pre-forms may be carried out by conventional methods, such as optical registration. Optical markers, such as diffraction gratings, lines or holograms, can be easily integrated into the stamp during origination, e.g. using beam lithography.

In certain configurations for carrying out methods embodying the invention, the pre-form will be placed on a surface with the carrier substrate downwards and the active layer upwards, and the face of the embossing stamp having the raised embossing areas will be pressed into the pre-form, whilst that face of the embossing stamp is held substantially parallel to upper surface of the pre-form (or if the embossing stamp is in the form of a roller, the axis of the roller will be held substantially parallel to upper surface of the pre-form). The raised embossing areas will be pushed into the upper surface of the pre-form and will form apertures in the active layer by permanently displacing portions of the active layer material into a non-conductive layer between the insulating substrate and the active layer. The distance of penetration of the raised embossing areas into the pre-form will be determined either by a control means (such as a software programme operating on a computer) or may be limited by the base area of the embossing stamp contacting the upper surface of the pre-form. Conventional control methods (e.g. piezoelectric stepper) can be used to prevent the base area of the embossing stamp applying excessive pressure to the pre-form. The method could be carried out with the stamp and the pre-form oriented in other configurations, provided that the stamp contacts the pre-form on the side of the pre-form such that the active layer is between the embossing face of the stamp and the carrier substrate of the preform.

The stamp in certain embodiments is made of a corrosion resistant material such as nickel or a nickel cobalt alloy, titanium, steel, stainless-steel, silicon, brass, plastic (e.g. PDMS, PMMA, PB) and other materials well-known in the fields of nanoimprinting and, more particularly, origination and recombination for optical holographics. The stamp can also be coated with a hydrophobic layer, such as octadecyltrichlorosilane (OTS) or trichloro(1H,1H,2H,2H-perfluorooctyl)silane (FOTS) or a fluoropolymer, to prevent adhesion of one or more materials from the pre-form on removal of the stamp after embossing.

23

For the production of a stamp, a latent image of the desired pattern of raised embossing areas on the stamp may be formed using conventional methods such as electron beam lithography, photolithography, focussed ion beam lithography, anode oxidation, etc. The latent image may then be developed, for instance by chemical etching, with the raised embossing areas corresponding to unetched surfaces, and the base area of the stamp being the bottoms of the etched areas. Another method for stamp production is mechanical engraving, for instance with a diamond-tipped tool. Stamp production can be achieved by origination of micro or nanofeatures, e.g. using e-beam lithography or focussed ion-beam lithography, to produce a master, typically in nickel but could also be silicon wafer. The master is kept securely and used to produce production shims by galvanoplastic replication. Recombination approaches (e.g. step-and-repeat) enable up-scale to larger shims for a range of production sizes to be generated.

The carrier substrate may be any suitable material for carrying layers, and can be rigid or flexible depending on application requirements. It may, for instance, be a layer of semiconductor such as silicon. Suitably, the carrier substrate is an electrically insulating layer, such as a semiconductor material which has been doped to convert it into an electrically insulating form. Another suitable material for the carrier substrate is flexible PET (polyethylene terephthalate). Another suitable material is silica (such as quartz or glass). Another suitable material is flexible metal, such as stainless-steel. Another suitable material is paper.

In certain embodiments there is a yielding layer (which may also be described as a compressible, or buffer layer) between the active layer and the carrier substrate and displacement of the portions of the active layer material is effected by compaction of the yielding layer by the raised embossing areas of the stamp.

For devices according to certain aspects of the invention, this will result in portions of yielding layer between the displaced portions of active layer and the carrier substrate which are in a compacted state whereby the displaced portions of active layer are no longer in conductive contact with the active layer.

By yielding layer is meant a layer which, when subjected to pressure above a certain value (known as the yield stress) deforms permanently, without returning to its original shape after the applied pressure is released.

The yielding layer may be a single layer of material, or may be made up of two or more substantially parallel layers of material. It may be appropriate for a plurality of yielding layers to be present, either in contact with each other, or with other layers sandwiched between them.

24

The yielding or compressible layer may comprise a deformable, or yielding polymer which could include polymethyl methacrylate, polyvinyl acetate, polyvinyl pyrrolidone, polyvinylphenol, and mixtures thereof. Such polymers yield when subjected to sufficient pressure, leading to collapse of the yielding layer, allowing the portions of active layer material to be punched out of the remaining active layer device template by the raised embossing areas of the stamp. The yield stress of the yielding layer (defined as the stress above which the yielding layer is permanently deformed after the stress is released) may be chosen by selection of polymer characteristics such as molecular weight. A suitable yield stress is from 0.01 to 50N/mm² preferably from 0.05 to 10N/mm² more preferably from 0.1 to 0.5 N/mm².

The yielding or compressible layer in certain embodiments is deposited onto the carrier (or backing or support) substrate (or layer) by solution-processing, such as spin-coating or dip-coating, but more preferably knife-coating or any other solution processing method that generate a homogeneous surface. The yielding layer may also be extruded. Substrates with pre-coated yielding layers can also be sourced commercially, such as from Dupont-Teijin Films.

In certain methods embodying the invention, the yielding layer is also the non-conductive layer. In this way, when a portion of active material from the active layer is pushed into the yielding layer by an embossing area of the stamp, it causes the yielding layer to deform below it, and remains positioned in the yielding layer, out of conductive contact with the remaining, undisturbed active layer.

Another configuration according to an embodiment of the invention has a pre-form with a non-conductive layer below the active layer and a yielding layer between the non-conductive layer and the carrier substrate. Other layers may be interposed or sandwiched between the specified layers. For this configuration, pressure from the raised embossing area punches a portion of active layer and a portion of non-conductive layer downwards and away from the remaining active layer. The yielding

layer is compacted to allow for this displacement of the active layer and non-conducting layer. The embossing area penetrates into the pre-form a distance sufficient to displace the portion of active layer into the same level as the undisturbed non-conducting layer, such that it is no longer in conductive contact with the undisturbed active layer.

25

The active layer may be directly in contact with the yielding (compressible) layer or with the non-conductive layer, or there may be other intermediate layers situated between the active layer and the yielding and/or non-conductive layer. For instance, the yielding layer may first have a layer of self-assembling monomer deposited upon it (using silane based materials such octadecyltrichlorosilane (OTS), hexamethyldisilazane (HMDS) or perfluorooctyltrichlorosilane (FOTS) or mixtures of OTS/FOTS, OTS/HMDS, etc.)), for instance as a self-assembled monolayer (SAM), followed by deposition of the active layer. Such a layer is particularly advantageous to improve the mobility of organic semiconductors or, in the case of FOTS, to induce doping of the active layer at the interface between the active layer and SAM. Note that a SAM is not necessary to induce doping of the active layer. These other layers will be punched out of place, along with the regions of active layer that are punched into the non-conductive layer, by a method embodying the invention. It is important that each layer has good adhesion with the layer and/or substrate beneath. For instance, it is known that multiple layers of organic materials must be processed using orthogonal solvents such that each new deposition of a layer does not damage the preceding layer deposited beneath. To address this problem, the yielding layer may be cross-linked prior to deposition of other layers, using for example high-temperature or UV light, to improve adhesion with other layers including the SAM where used. One example of this is to use UV-crosslinkable copolymers, such as PMMA (Optical Materials, 23, (3-4), 583-592), which can be crosslinked prior to deposition of an active layer to minimise damage caused by subsequent solution-based deposition.

The active layer of semiconductive material may be doped or undoped. Organic semiconductor materials, for example, may be doped by the application of a self-assembled monolayer of FOTS below the active layer. Alternatively, organic semiconductor materials may be chemically doped or doped by intentionally introducing an oxygen-rich environment. Inorganic semiconductors may be chemically doped or deposited in conjunction with a suitable dopant, e.g. vapour co-deposition of inorganic semiconductor and dopant material.

A further layer or layers may be in place over the active layer of the template, for instance in order to protect the active layer from direct contact with the raised embossing areas of the stamp, or because it is needed for the final device, e.g. to provide additional isolation from the active layer. Such layers will be punched out of place, along with the regions of active layer that are punched into the non-conductive layer, by the method of the invention. Suitable materials for use in layers positioned over the active layer include insulating polymers such as PMMA and PVA, PVP.

26

It is desirable for the raised embossing area to have a height above the base area of the stamp such that portions of active layer displaced by the stamp are punched into the pre-form such that the upper surface of the displaced active layer is at a distance from the pre-form surface greater than the depth of the lower surface of the active layer (i.e. the surface of the active layer towards the carrying substrate). This ensures that the displaced portions of active layer are no longer in conductive contact with the undisplaced active layer.

The active layer may be any suitable active layer of semiconductive material for forming a device template. The active layer may be a conventional semiconductor such as a group IV semiconductor such as silicon, germanium or the like or it may be a III-V semiconductor such as gallium arsenide, indium phosphide or the like, or it may be an inorganic semiconductor such as zinc oxide or titanium dioxide, or it may be an organic semiconductor. Typically the active layer thickness will be 100nm or less, preferably 50nm or less more preferably 20nm or less.

Characteristics of the active layer may be modified before or after the application of methods embodying the invention to provide isolating areas in the active layer, in order to further modify the device template. Completion of the device from the device template may not be necessary, or may take place after application of a method embodying the invention, and is referred to as post-processing. This may require further modification of the active layer, the application of further layers to the pre-form, the application of conductive contacts to the pre-form. These may all be achieved by methods know in the art. For instance the active layer may be photo-etched, solution patterned or annealed.

Suitable active layers include thin-films of semiconductor material that can suitably have been vacuum or vapour deposited (for instance pentacene) or sputter-coated (e.g.

27

metal oxide layers), thin-films of semiconductor material that have been solution deposited (e.g. polyalkylthiophenes - P3HT, polyarylamine - PTAA, copolymers of fluorene and thiophene, soluble precursors of pentacene, silicon inks). The active layer may be in a form, when it is subjected to the method of the invention, such that if requires further processing before it is useful in a device. For instance, the active layer may be a thin film of precursor material (such as Diels-Alder product of pentacene pentachlorophenyl bridged-pentacene) that can be deposited (for instance by solution processing) and photopatterned or annealed to produce a semiconductor after deposition and an electronic device after processing by the method of the first aspect of the invention. For instance, following the formation of the device template by the method of the invention, a further layer or layers may be deposited onto or over the active layer, for instance a dielectric layer such as PMMA, PVP or high-k dielectrics such as nanocomposites for organic semiconductors or SiO<sub>2</sub> for inorganic and conventional semiconductors. High-k nanocomposite dielectric materials may require post-processing to planarise the pre-form. High-k dielectrics are dielectrics with a higher dielectric constant (k) than silicon dioxide.

In certain embodiments of the invention the semiconductive material (i.e. the active material) has a glass transition temperature. Suitably, the active layer material has a glass transition temperature from 30 to  $200^{\circ}$ C, preferably from 40 to  $150^{\circ}$ C, more preferably from 70 to  $100^{\circ}$ C.

The active layer may for instance be an organic semiconductor having a glass transition temperature, or a precursor for an organic semiconductor, wherein the precursor has a glass transition temperature.

When the active layer is such a material, a method for putting an aspect of the invention into effect may involve the active layer being heated to a temperature in excess of the glass transition temperature prior to forming the apertures (insulative features). This is suitably achieved by heating the pre-form prior to application of the embossing stamp to the pre-form.

It has been found that heating the active layer to a temperature in excess of its glass transition temperature leads to an improvement in the cleanness of the edges of apertures formed in the active layer, minimising any smearing or transfer of material.

Another method for putting an aspect of the invention into effect has the active layer at a temperature less than the glass transition temperature immediately prior to forming the apertures, and the stamp at a temperature greater than the glass transition temperature immediately prior to forming the apertures.

28

This method also leads to an improvement in the cleanness of the aperture edges, minimising any smearing or transfer of material, but without any risk of degradation to the active layer, or to other layers of the pre-form, which may be caused by heating the pre-form. A further advantage of this method is that the heated stamp can convert the displaced active layer into an insulating state, thereby improving the isolation with the undisturbed active layer.

Certain methods embodying the invention are applicable to device templates which are intended for an electronic or photonic device. The apertures formed in the active layer of the device template by the method may typically be small apertures, having dimensions in the range 20 to 1000 nm, or 100 to 300nm. However, methods embodying the invention may also be used to form larger apertures (having dimensions of 10 micrometres or more). This may be particularly advantageous compared to direct beam lithography to form large apertures in devices or device templates, as each part of an isolating area will need to be written by the beam used, leading to long processing times.

Certain methods embodying the invention are particularly suitable when the device template is for a planar nanoelectronic diode, transistor or circuit (a so-called self-gating Device), particularly for devices such as described in WO 2002/086973 and WO 2006/120414. Such devices, as detailed in WO 2002/086973, comprise electronic circuit component comprising a substrate supporting mobile charge carriers, insulative features formed on the substrate surface to define first and second substrate areas on either side of the insulative features, the insulative features including first and second regions which are positioned close to one another but spaced apart so as to provide an elongate channel, which provides a charge carrier flow path in the substrate from the first area to the second area, and wherein said elongate channel is dimensioned and arranged such that the parameters of the charge carrier flow path are dependent on a potential difference between said first and second areas. In WO 2006/120414, electronic devices are described comprising a substrate supporting mobile charge carriers (or in this case the active layer), insulative features formed on the substrate

surface (i.e. embossed within the active layer) to define first and second substrate areas on either side of the insulative features, the first and second substrate areas being connected by an elongate channel defined by the insulative features, the channel providing a charge carrier flow path in the substrate from the first area to the second area, the conductivity between the first and second substrate areas being dependent upon the potential difference between the areas, wherein the mobile charge carriers can be within at least two modes in each of the three dimensions within the substrate.

29

In each case, the insulative features are suitably formed within the active layer, using the method of the invention, creating diodes, diode arrays, transistors, transistor arrays

or circuit elements combining many diodes and/or transistors..

### Brief Description of the Drawings

Embodiments of the invention will now be described with reference to the accompanying drawings, of which:

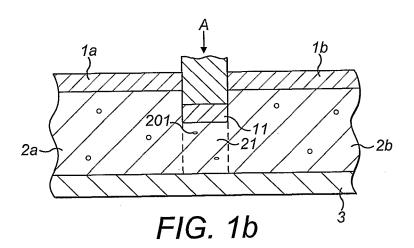

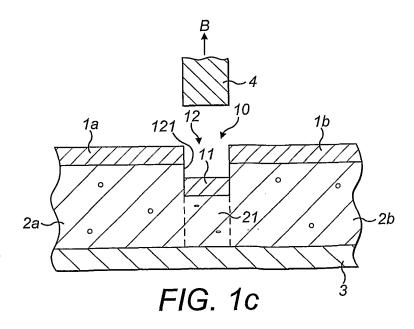

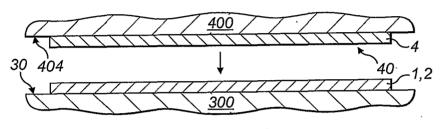

Figs. 1a, 1b and 1c illustrate steps in a method of manufacturing an electronic device in accordance with the present invention;

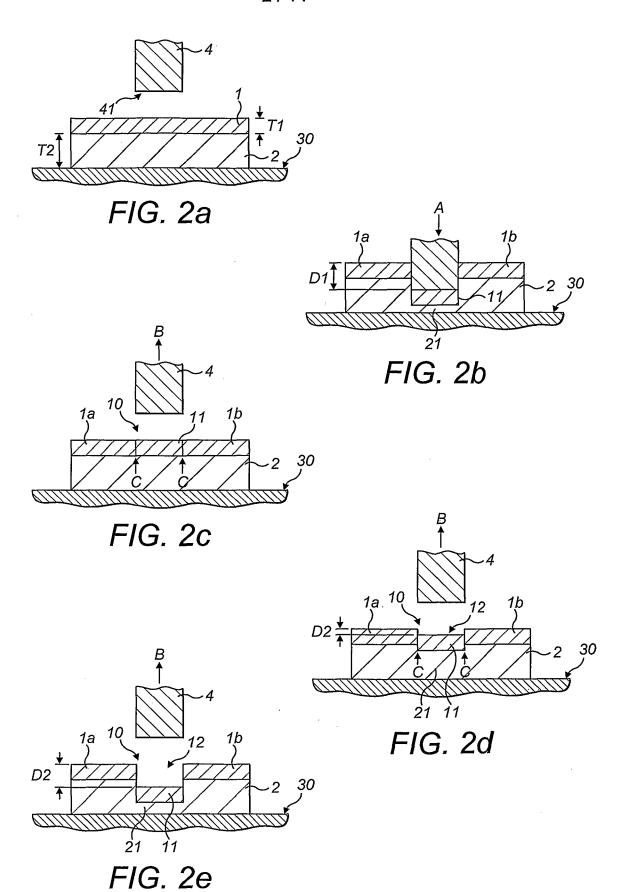

Figs. 2a-2e illustrate the formation of insulative features in another method embodying the invention;

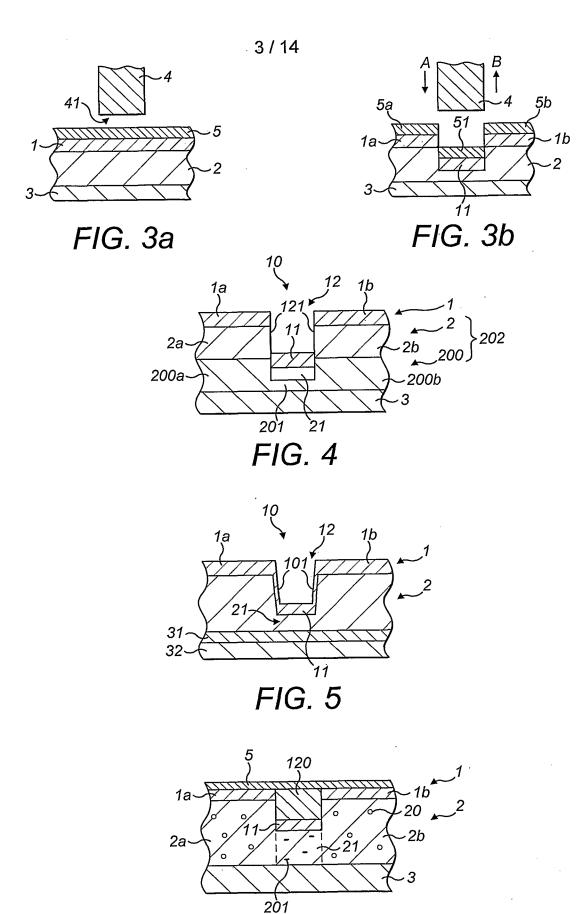

Figs. 3a and 3b illustrate the formation of an insulative feature in another embodiment of the invention;

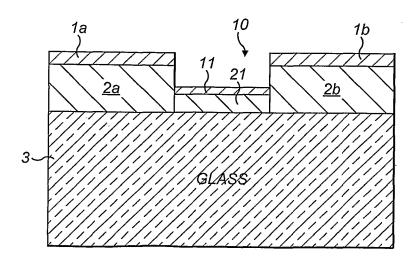

Fig. 4 is a schematic cross section or part of an electronic device embodying the invention;

Fig. 5 is a schematic cross section of part of another electronic device embodying the invention;

Fig. 6 is a schematic cross section of yet another electronic device embodying the invention;

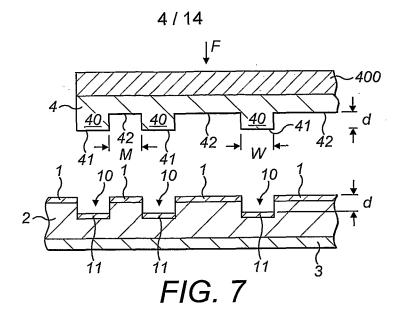

Fig. 7 is a schematic representation of part of an electronic device embodying the invention and embossing apparatus used to pattern the device;

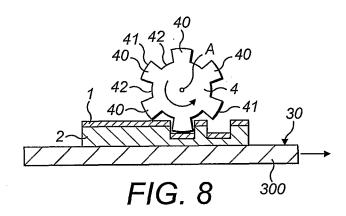

Fig. 8 is a schematic representation of alternative embossing apparatus being used to pattern a layer of semiconductive material in a method embodying the invention;

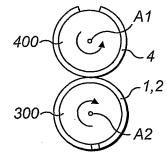

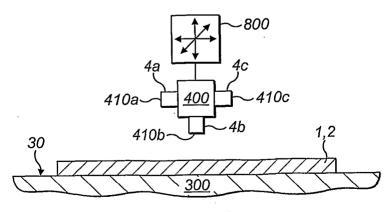

Fig. 9 is a schematic representation of yet further embossing apparatus being used to pattern a layer of semiconductive material in a method embodying the invention;

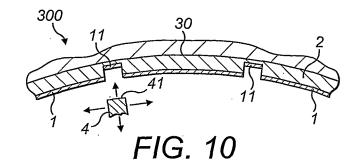

Fig. 10 is a schematic representation of embossing apparatus and a device substrate in another method embodying the invention;

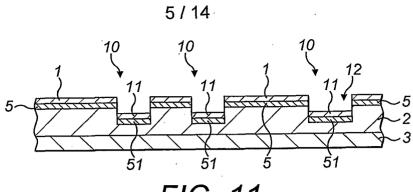

Fig. 11 is a schematic cross section of part of an electronic device embodying the invention;

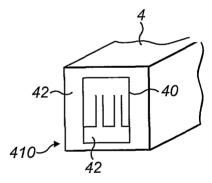

Fig. 12 is a schematic representation of an embossing tool in the form of a stamp or shim, arranged to pattern a layer of semiconductive material in an embodiment of the invention;

Fig. 13 is a schematic representation of part of an embossing tool used in embodiments of the invention, the tool having an embossing surface provided with a raised pattern for producing corresponding insulative features in a semiconductive layer to define a complete electronic device;

Fig. 14 is a schematic representation of embossing apparatus used in another method of manufacturing electronic devices and embodying the invention;

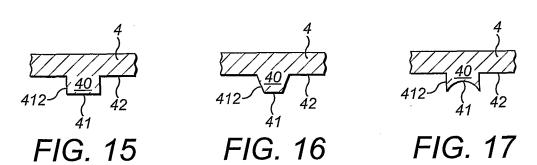

Figs. 15-17 are schematic cross sections of different embossing features of embossing tools used in methods embodying the invention;

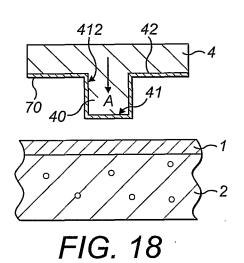

Fig. 18 is a schematic representation of an embossing tool arranged to produce an insulative feature in a device substrate in another method embodying the invention;

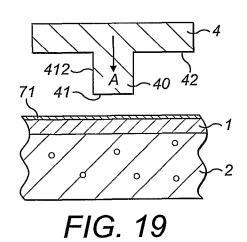

Fig. 19 is a schematic representation of another embossing tool arranged to pattern the semiconductive layer of an electronic device in another method embodying the invention;

WO 2010/086651

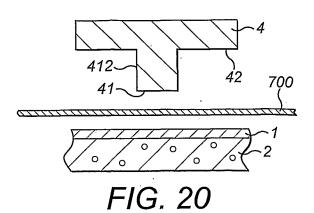

- Fig. 20 is a schematic representation of an embossing tool arranged to emboss a semiconductive layer via an intermediate layer or film in another method embodying the invention;

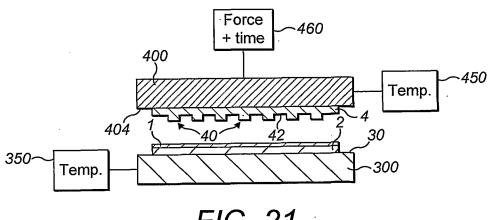

- Fig. 21 is a schematic representation of embossing apparatus and substrate support apparatus used in methods of manufacturing electronic devices and circuits embodying the invention;

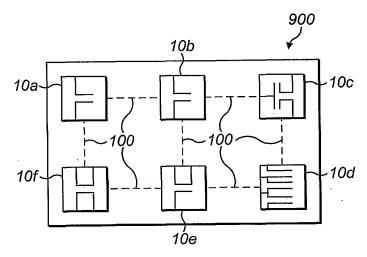

- Fig. 22 is a schematic representation of an electronic circuit embodying the invention;

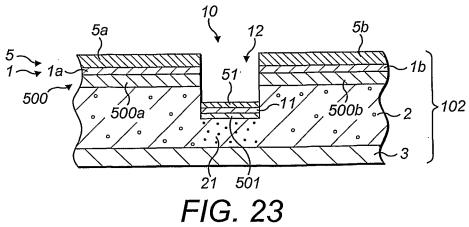

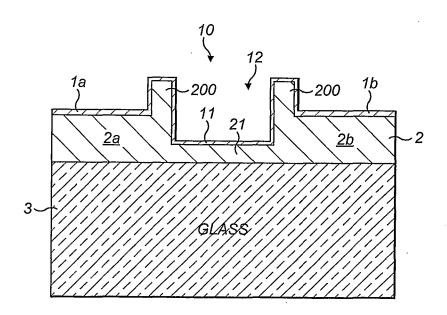

- Fig. 23 is a schematic representation of a cross section of part of an electronic device embodying the invention;

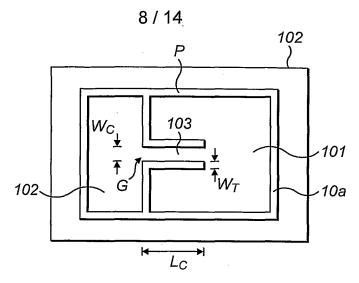

- Fig. 24 is a schematic plan view of an electronic device embodying the invention;

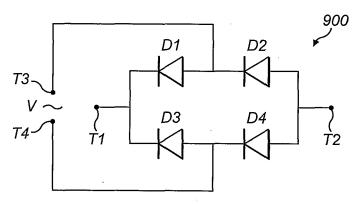

- Fig. 25 is a schematic representation of an electronic circuit which may be manufactured using methods embodying the invention;

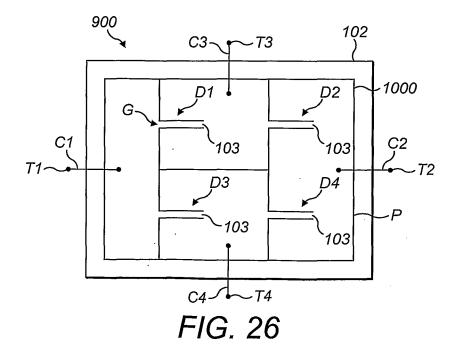

- Fig. 26 is a schematic plan view of the circuit of Fig. 25 implemented in an embodiment of the invention (in other words Fig. 26 illustrates an electronic circuit embodying the invention;

- Fig. 27 is an image of part of an electronic device embodying the invention;

- Fig. 28 is a schematic representation of the cross section of part of an electronic device embodying the invention;

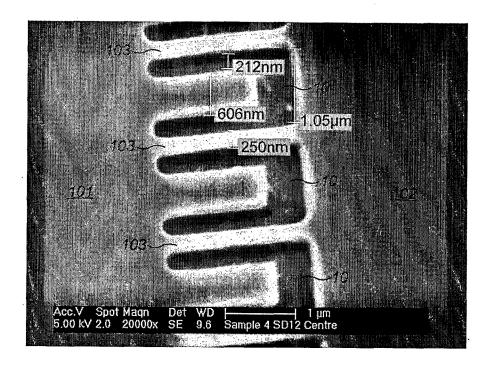

- Fig. 29 is a microscope image of an insulative feature of an embodiment of the invention;

- Fig. 30 is a schematic cross section of part of another electronic device embodying the invention;

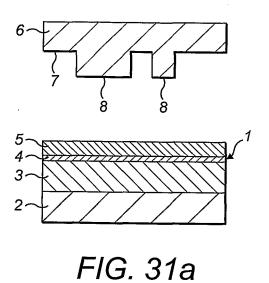

- Figure 31A is a cross section through a stamp and a device pre-form according to an embodiment of the invention,

32

Figure 31B is a cross section through a device template prepared in accordance with the embodiment of the invention of fig. 31A,

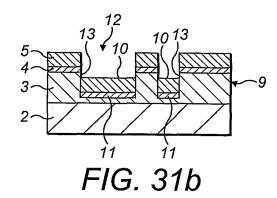

Figure 32A is a cross section through a stamp and a device pre-form according to a another embodiment of the invention,

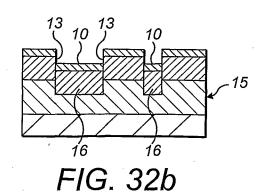

Figure 32B is a cross section through a device template prepared in accordance with an embodiment of the invention.

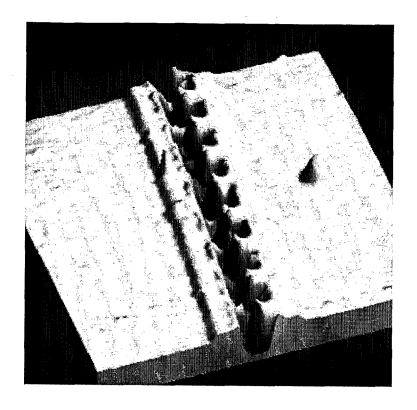

Figure 33 is an image of a stamp suitable for use in a method embodying the invention,

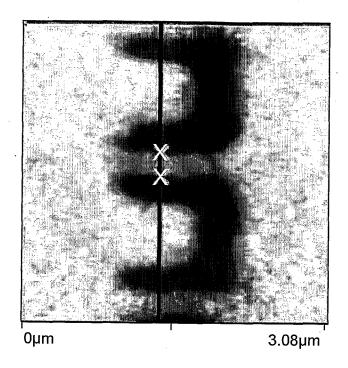

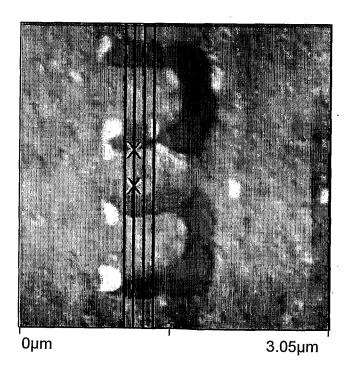

Figure 34 is an image of a device prepared using the stamp of figure 33;

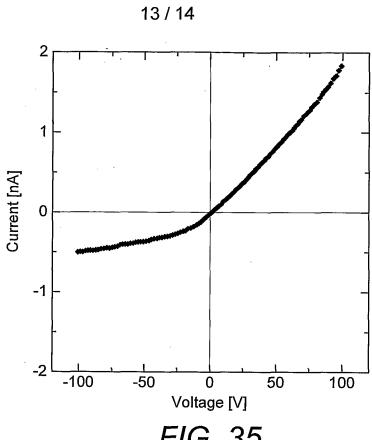

Figure 35 is a current/voltage plot for the device as shown in figure 34;

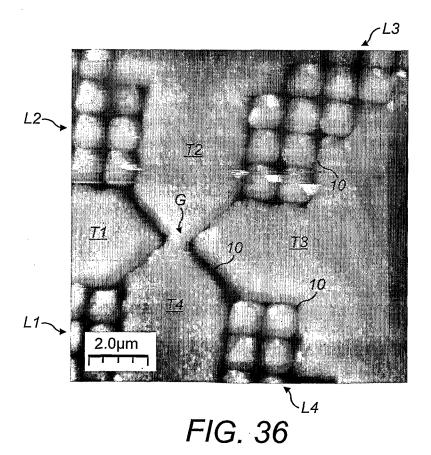

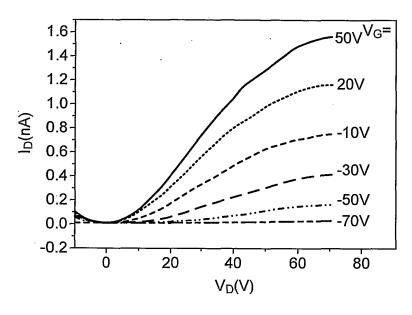

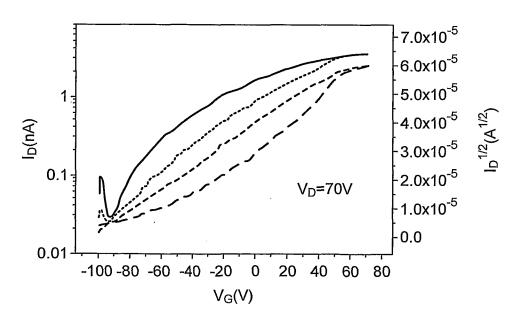

Figure 36 is an image of a nano transistor embodying the invention and manufactured using a method embodying the invention; and

Figures 37 and 38 are output and transfer characteristics, respectively, of the transistor of fig. 36.

#### Detailed Description of Embodiments of the Invention

Referring now to Figs. 1a-1c, in a first method embodying the invention a layer of semiconductive material 1 is provided, supported by a layer 2 of insulative and compressible material.

The insulative layer 2 is itself supported by an underlying substrate layer 3, in this example formed of substantially non-compressible material. The semiconductive layer 1, compressible layer 2, and substrate or backing layer 3 can together be described as forming a multi-layer device substrate. It will be appreciated that a wide variety of techniques known in the art may be used to fabricate such a multi-layer structure, and embodiments of the invention may utilise any suitable such techniques, for example techniques selected to suit the particular material or materials of each layer. In certain embodiments, for example, the semiconductive layer 1 is a layer of organic semiconductive material, which may be formed over the compressible layer by spin-

33

coating. In this first example, the material of the compressible layer 2 is porous, that is comprising a plurality of pores 20, and having an initial porosity. Fig. 1a shows an embossing tool 4 having an embossing surface 41 and arranged over the semiconductive layer 1 to be patterned, ready to form an insulative feature. Fig. 1b illustrates a subsequent step in the manufacturing method, in which the embossing tool 4 has been moved in a direction generally towards the compressible layer 2 (and hence towards the backing layer 3), that direction being generally indicated by arrow A. In making this movement, the embossing surface 41 has engaged a corresponding portion of the upper surface of the semiconductive layer 1, and has driven a selected portion 11 of the layer of semiconductive material 11 downward, out of the plane of the initial layer 1, and compressing a portion 21 of the compressible material beneath it. compression has formed compressed pores 201 in the portion 21, and it will be appreciated that compressed portion 21 has a reduced porosity and increased density compared with uncompressed portions 2a and 2b. In this example, this displacement of the selected portion 11 of semiconductive material has completely separated it from undisplaced portions 1a, 1b of the semiconductive layer 1. Fig. 1c shows another subsequent step in the manufacturing method, in which the embossing tool 4 has been withdrawn, in direction shown by arrow B, leaving the displaced portion 11 of semiconductive material at the bottom of a depression or trench 12 formed in the upper surface of the device substrate. The material of the compressible layer 2 in this example is such that the compression of the portion 21 is substantially irreversible, such that there is substantially no return of the portion 21 to its original dimensions. In other words, the compressible material 2 has been arranged to yield under the force applied via the embossing tool, and remains in its compressed state. In this example, the side walls 121 of the trench 12 comprise exposed portions of the layer of insulative, compressible material 2 such that the insulative feature 10 formed by the embossing tool 4 (and which comprises the trench and displaced portion 11 of semiconductive material) forms a substantially complete electrical block to current flow in the semiconductive layer 1 across the feature 10.

Referring now to Figs. 2a-2e, in another method embodying the invention a device multi-layer substrate comprises a layer of semiconductive material 1 formed on a layer of compressible material 2 without any incompressible backing layer or layers. Instead, during the patterning process to produce insulative features the device substrate is temporarily supported on a support surface 30, which in this example is flat. The semiconductive layer has been formed to have a substantially uniform thickness T1,

34

and the compressible material has been formed so as to have a substantially uniform thickness T2. Again, an embossing tool 4 having an embossing surface 41 is arranged to produce insulative features by a stamping process alone, i.e. by movement solely in a direction substantially perpendicular to the flat support surface 30. Fig. 2a shows the embossing tool 4 positioned ready to emboss the device substrate. Fig. 2b shows a subsequent point in the manufacturing process, at which the embossing tool 4 has been urged towards the support surface 30 in the direction shown by arrow A so as to press and displace the selected portion 11 of semiconductive material from the layer 1 towards the support surface 30, compressing a portion 21 of the compressible material beneath it. In this example, the embossing tool 4 has been used to displace the portion 11 initially by a distance D1, where D1 is greater than T1, and less than T2.