(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5679397号

(P5679397)

(45) 発行日 平成27年3月4日(2015.3.4)

(24) 登録日 平成27年1月16日(2015.1.16)

(51) Int.Cl.

F 1

H01L 21/336 (2006.01)

H01L 29/786 (2006.01)

H01L 29/78 H01L 29/78 H01L 29/78 H01L 29/78

612D 616U 616V 627C

請求項の数 15 (全 16 頁)

(21) 出願番号

特願2007-265748 (P2007-265748)

(22) 出願日

平成19年10月11日(2007.10.11)

(65) 公開番号

特開2008-98642 (P2008-98642A)

(43) 公開日

平成20年4月24日(2008.4.24)

審査請求日

平成22年10月8日(2010.10.8)

審判番号

不服2014-1528 (P2014-1528/J1)

審判請求日

平成26年1月28日(2014.1.28)

(31) 優先権主張番号

10-2006-0099187

(32) 優先日

平成18年10月12日(2006.10.12)

(33) 優先権主張国

韓国(KR)

(73) 特許権者

512187343

三星ディスプレイ株式会社

Samsung Display Co., Ltd.

大韓民国京畿道龍仁市器興区三星二路95

95, Samsung 2 Ro, Gih

eung-Gu, Yongin-City

, Gyeonggi-Do, Korea

(74) 代理人

110000671

八田国際特許業務法人

李德重

大韓民国忠清南道天安市佛堂洞 デンドダ

スップアパート111棟804号

最終頁に続く

(54) 【発明の名称】薄膜トランジスタ基板の製造方法

## (57) 【特許請求の範囲】

## 【請求項1】

ゲートライン及び前記ゲートラインと連結されたゲート電極を含むゲート配線が形成された基板上にゲート絶縁膜及び活性層を順次に形成する段階と、

前記活性層上に第1金属層、第2金属層、及び第3金属層が連続して積層されたデータ用金属膜を形成する段階と、

前記データ用金属膜上にチャンネル形成領域に対応する部分が前記チャンネル形成領域以外に対応する部分に対して相対的に薄い厚みを有する第1フォトレジストパターンを形成する段階と、

前記第1フォトレジストパターンを利用して前記第3金属層をドライエッチングする段階と、

前記第1フォトレジストパターンを利用して前記第2金属層及び前記第1金属層を同時にドライエッチングし、前記活性層が備えるオーミックコンタクト層を露出させ、データラインを形成する段階と、

前記第1フォトレジストパターンを利用して前記活性層をドライエッチングする段階と、

前記第1フォトレジストパターンをエッチングして前記チャンネル形成領域に対応する部分が除去された第2フォトレジストパターンを形成する段階と、

前記第2フォトレジストパターンを利用して前記データ用金属膜の前記チャンネル形成領域をドライエッチングして前記データラインと連結されたソース電極及び前記ソース電

10

20

極と離隔したドレイン電極を形成する段階と、

を含むことを特徴とする薄膜トランジスタ基板の製造方法。

**【請求項 2】**

前記第1金属層はモリブデンを含み、前記第2金属層はアルミニウムを含み、前記第3金属層はモリブデンを含むことを特徴とする請求項1記載の薄膜トランジスタ基板の製造方法。

**【請求項 3】**

前記第1フォトレジストパターンを利用して前記第2金属層及び前記第1金属層を同時にドライエッチングする段階は、三塩化ホウ素(BC13)ガスと塩素(C12)ガスを利用して進行することを特徴とする請求項1または2記載の薄膜トランジスタ基板の製造方法。10

**【請求項 4】**

前記三塩化ホウ素(BC13)ガスと前記塩素(C12)ガスの組成比は1:1~1:5であることを特徴とする請求項3記載の薄膜トランジスタ基板の製造方法。

**【請求項 5】**

前記第2フォトレジストパターンを利用して前記データ用金属膜の前記チャンネル形成領域をドライエッチングする段階は、

前記第2フォトレジストパターンを利用して前記第3金属層をドライエッチングする段階と、

前記第2フォトレジストパターンを利用して前記第2金属層及び前記第1金属層を同時にドライエッチングする段階と、20

を含むことを特徴とする請求項1から4のいずれかに記載の薄膜トランジスタ基板の製造方法。

**【請求項 6】**

前記活性層は、非晶質シリコンからなるチャンネル層及びイオンがドーピングされた非晶質シリコンからなるオームックコンタクト層を含み、

前記ソース電極及びドレイン電極を形成する段階後に、前記第2フォトレジストパターンを利用して前記チャンネル形成領域の前記オームックコンタクト層を除去して薄膜トランジスタを形成する段階を更に含むことを特徴とする請求項1から5のいずれかに記載の薄膜トランジスタ基板の製造方法。30

**【請求項 7】**

前記薄膜トランジスタが形成された基板上に保護膜を形成する段階と、

前記保護膜上に前記ドレイン電極と電気的に連結される画素電極を形成する段階と、

を更に含むことを特徴とする請求項6記載の薄膜トランジスタ基板の製造方法。

**【請求項 8】**

ゲートライン及び前記ゲートラインと連結されたゲート電極を含むゲート配線が形成された基板上にゲート絶縁膜及び活性層を順次に形成する段階と、

前記活性層上に第1金属層、第2金属層、及び第3金属層が連続して積層されたデータ用金属膜を形成する段階と、

前記データ用金属膜上にチャンネル形成領域に対応する部分が前記チャンネル形成領域以外に対応する部分に対して相対的に薄い厚みを有するフォトレジストパターンを形成する段階と、40

前記フォトレジストパターンを利用して前記第3金属層をドライエッチングする段階と、

前記フォトレジストパターンを利用して前記第2金属層をドライエッチングする段階と、

前記フォトレジストパターンを利用して前記第1金属層及び前記活性層を同時にドライエッチングして、前記ゲート絶縁膜を露出させるとともに前記チャンネル形成領域に対応する部分をオープンしてデータラインを形成する段階と、

前記フォトレジストパターンを利用して前記データ用金属膜の前記チャンネル形成領域

50

をドライエッティングして前記データラインと連結されたソース電極及び前記ソース電極と離隔したドレイン電極を形成する段階と、

を含む薄膜トランジスタ基板の製造方法。

**【請求項 9】**

前記第1金属層はモリブデンを含み、前記第2金属層はアルミニウムを含み、前記第3金属層はモリブデンを含むことを特徴とする請求項8記載の薄膜トランジスタ基板の製造方法。

**【請求項 10】**

前記フォトレジストパターンを利用して前記第1金属層及び前記活性層を同時にドライエッティングする段階は、フッ素(F)系列ガスと塩素(C12)ガスを利用して進行することを特徴とする請求項8または9記載の薄膜トランジスタ基板の製造方法。10

**【請求項 11】**

前記フッ素(F)系列ガスは、六フッ化硫黄(SF6)ガスを含むことを特徴とする請求項10記載の薄膜トランジスタ基板の製造方法。

**【請求項 12】**

前記六フッ化硫黄(SF6)ガスと前記塩素(C12)ガスの組成比は、1:5~1:7であることを特徴とする請求項11記載の薄膜トランジスタ基板の製造方法。

**【請求項 13】**

前記フォトレジストパターンを利用して前記第1金属層及び前記活性層を同時にドライエッティングする過程で前記チャンネル形成領域の前記第3金属層が同時にエッティングされることを特徴とする請求項8から12のいずれかに記載の薄膜トランジスタ基板の製造方法。20

**【請求項 14】**

前記活性層は、非晶質シリコンからなるチャンネル層及びイオンがドーピングされた非晶質シリコンからなるオーミックコンタクト層を含み、

前記ソース電極及びドレイン電極を形成する段階後に、前記フォトレジストパターンを利用して前記チャンネル形成領域の前記オーミックコンタクト層を除去して薄膜トランジスタを形成する段階を更に含むことを特徴とする請求項8から13のいずれかに記載の薄膜トランジスタ基板の製造方法。

**【請求項 15】**

前記薄膜トランジスタが形成された基板上に保護膜を形成する段階と、30

前記保護膜上に前記ドレイン電極と電気的に連結される画素電極を形成する段階と、

を更に含むことを特徴とする請求項14記載の薄膜トランジスタ基板の製造方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は薄膜トランジスタ基板の製造方法に関し、より詳細には製造工程を単純化させることができる薄膜トランジスタ基板の製造方法に関する。

**【背景技術】**

**【0002】**

一般に、液晶表示装置は、薄膜トランジスタ及び画素電極が形成された薄膜トランジスタ基板とカラーフィルタ及び共通電極が形成されたカラーフィルタ基板が液晶を挟んで結合された構造を有する。40

**【0003】**

薄膜トランジスタ基板を形成する工程は、マスクを利用したフォトリソグラフィ工程を通じて行われるが、最近では工程単純化のために4枚のマスクのみを使用する4枚マスク工程が開発されたことがある。

**【0004】**

通常、4枚マスク工程ではデータ用金属層をエッティングすることにおいて、データラインを形成するための1次エッティング段階とチャンネル形成領域をエッティングするための250

次エッチング段階を進行することになる。

【0005】

既存の4枚マスク工程では、前記1次エッチング段階及び2次エッチング段階の全てにウェットエッチング工程を適用することにより、チャンネル幅の増加及び工程散布を減少させるために配線幅を広くデザインしなければならないという問題が発生される。

【0006】

最近では、前記1次エッチング段階はウェットエッチング工程を使用し、2次エッチング段階はドライエッチング工程を使用する製造工程が開発されたことがあるが、ウェットエッチング工程とドライエッチング工程を全部使用することにより製造工程が複雑になり、製造時間が増加されるという問題が発生する。

10

【発明の開示】

【発明が解決しようとする課題】

【0007】

従って、本発明はこのような従来の問題点を解決するためのもので、本発明はドライエッチング工程のみを利用して製造工程を単純化させることができる薄膜トランジスタ基板の製造方法を提供する。

【課題を解決するための手段】

【0008】

本発明の一特徴による薄膜トランジスタ基板の製造方法によると、ゲートライン及び前記ゲートラインと連結されたゲート電極を含むゲート配線が形成された基板上にゲート絶縁膜及び活性層を順次に形成する。その後、前記活性層上に第1金属層、第2金属層、及び第3金属層が連続して積層されたデータ用金属膜を形成する。その後、前記データ用金属膜上にチャンネル形成領域に対応する部分が前記チャンネル形成領域以外に対応する部分に対して相対的に薄い厚みを有する第1フォトレジストパターンを形成する。その後、前記第1フォトレジストパターンを利用して前記第3金属層をドライエッチングする。その後、前記第1フォトレジストパターンを利用して前記第2金属層及び前記第1金属層を同時にドライエッチングし、前記活性層が備えるオーミックコンタクト層を露出させ、データラインを形成する。その後、前記第1フォトレジストパターンを利用して前記活性層をドライエッチングする。その後、前記第1フォトレジストパターンをエッチングして前記チャンネル形成領域に対応する部分を除去して第2フォトレジストパターンを形成する。その後、前記第2フォトレジストパターンを利用して前記データ用金属膜の前記チャンネル形成領域をドライエッチングして前記データラインと連結されたソース電極及び前記ソース電極と離隔したドレイン電極を形成する。

20

【0009】

前記第1金属層はモリブデンを含み、前記第2金属層はアルミニウムを含み、前記第3金属層はモリブデンを含む。

【0010】

前記第1フォトレジストパターンを利用して前記第2金属層と前記第1金属層を同時にドライエッチングする工程は、三塩化ホウ素( $BCl_3$ )ガスと塩素( $Cl_2$ )ガスを利用して進行される。この際、前記三塩化ホウ素( $BCl_3$ )ガスと前記塩素( $Cl_2$ )ガスの組成比は約1:1~1:5程度で構成される。

30

【0011】

前記第2フォトレジストパターンを利用して前記データ用金属膜の前記チャンネル形成領域をドライエッチングする工程は、前記第2フォトレジストパターンを利用して前記第3金属層をドライエッチングする工程と、前記第2フォトレジストパターンを利用して前記第2金属層及び前記第1金属層を同時にドライエッチングする工程で進行されることができる。

【0012】

前記ソース電極及びドレイン電極を形成した後に、前記第2フォトレジストパターンを利用して前記チャンネル形成領域のオーミックコンタクト層を除去して薄膜トランジスタ

40

50

を形成する。

**【0013】**

その後、前記薄膜トランジスタが形成された基板上に保護膜を形成し、前記保護膜上に前記ドレイン電極と電気的に連結される画素電極を形成する。

**【0014】**

本発明の他の特徴による薄膜トランジスタ基板の製造方法によると、ゲートライン及び前記ゲートラインと連結されたゲート電極を含むゲート配線が形成された基板上にゲート絶縁膜及び活性層を順次に形成する。その後、前記活性層上に第1金属層、第2金属層、及び第3金属層が連続して積層されたデータ用金属膜を形成する。その後、前記データ用金属膜上にチャンネル形成領域に対応する部分が前記チャンネル形成領域以外に対応する部分に対して相対的に薄い厚みを有するフォトレジストパターンを形成する。10その後、前記フォトレジストパターンを利用して前記第3金属層をドライエッチングする。その後、前記フォトレジストパターンを利用して前記第2金属層をドライエッチングする。その後、前記フォトレジストパターンを利用して前記第1金属層及び前記活性層を同時にドライエッチングして、前記ゲート絶縁膜を露出させるとともに前記チャンネル形成領域に対応する部分をオープンしてデータラインを形成する。その後、前記フォトレジストパターンを利用して前記データ用金属膜の前記チャンネル形成領域をドライエッチングして前記データラインと連結されたソース電極及び前記ソース電極と離隔したドレイン電極を形成する。

**【0015】**

前記第1金属層はモリブデンを含み、前記第2金属層はアルミニウムを含み、前記第3金属層はモリブデンを含む。

**【0016】**

前記フォトレジストパターンを利用して前記第1金属層及び前記活性層を同時にドライエッチングする工程は、六フッ化硫黄( $SF_6$ )ガスと塩素( $Cl_2$ )ガスを利用して進行される。この際、前記六フッ化硫黄( $SF_6$ )ガスと前記塩素( $Cl_2$ )ガスの組成比は、1:5~1:7程度で構成される。

**【発明の効果】**

**【0017】**

このような薄膜トランジスタ基板の製造方法によると、データラインを形成するための1次エッチング工程とチャンネルを形成するための2次エッチング工程を全部ドライエッチング工程で進行することにより、ウェットエッチングによる問題点を解決し、製造工程を単純化させることができる。30

**【発明を実施するための最良の形態】**

**【0018】**

以下、添付図面を参照して、本発明による薄膜トランジスタ基板の製造方法をより詳細に説明する。

**【0019】**

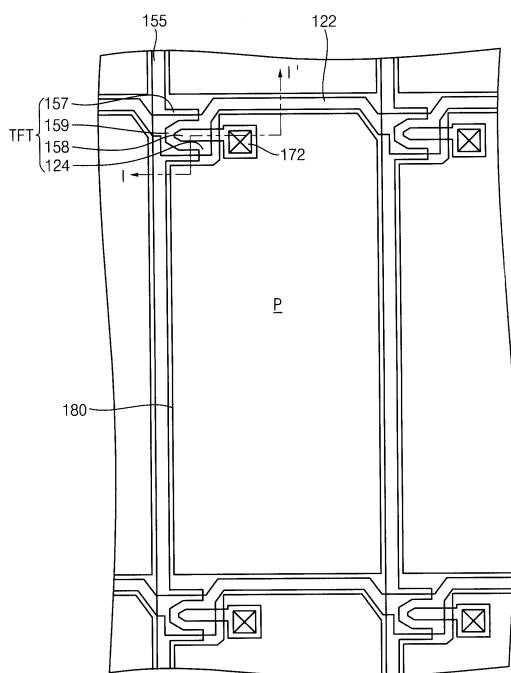

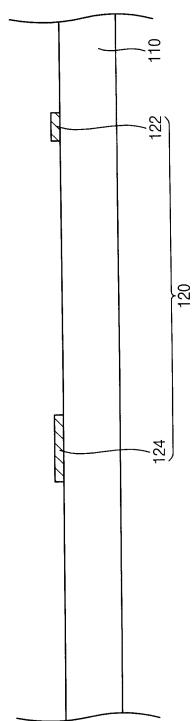

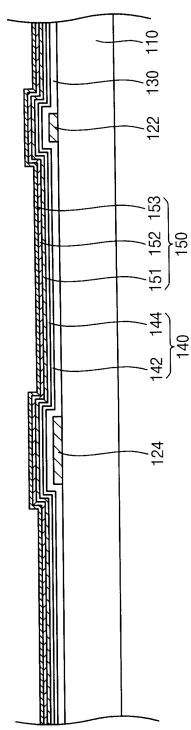

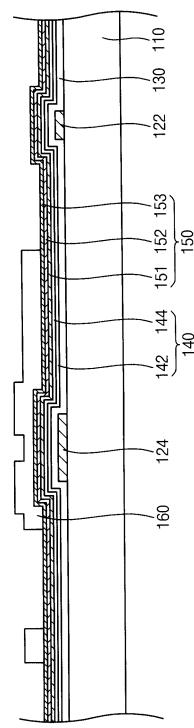

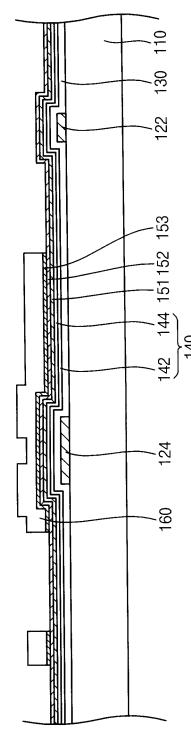

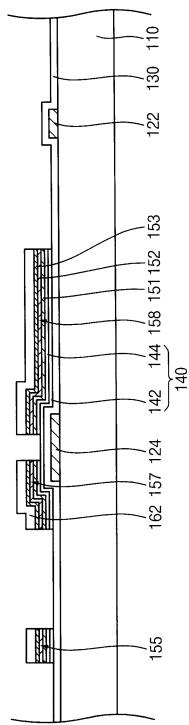

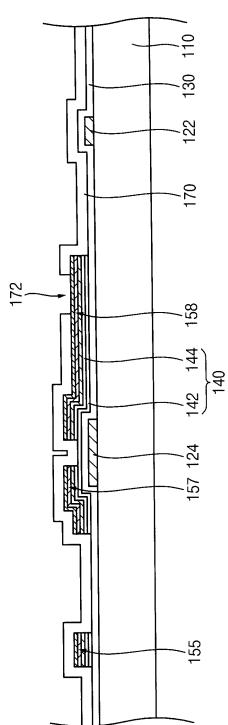

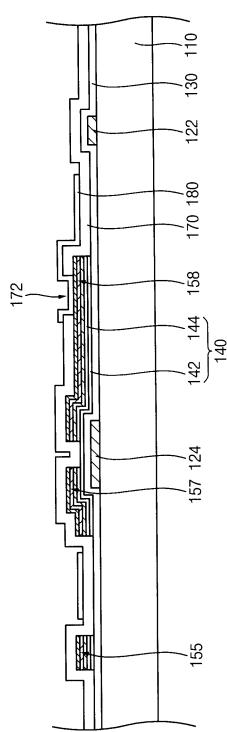

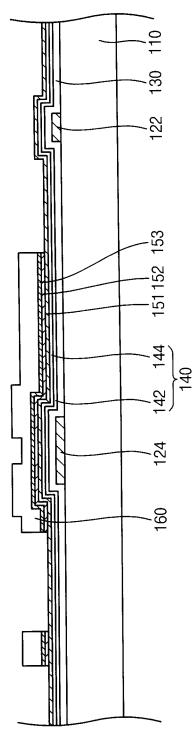

図1は、本発明の実施例によって製造された薄膜トランジスタ基板を示す平面図で、図2乃至図11は、図1に図示された薄膜トランジスタ基板の製造過程を示す工程図である。40ここで、図2乃至図11は、図1のI-I'に沿って切断した場合の断面図である。

**【0020】**

図1及び図2を参照すると、基板110上にゲート用金属膜を形成した後、第1露光マスクを利用したフォトリソグラフィ工程を通じて前記ゲート用金属膜をパターニングしてゲートライン122及びゲートライン122と連結されたゲート電極124を含むゲート配線120を形成する。前記ゲート用金属膜は、例えば、スパッタリング方法を通じて基板110上に形成されることがある。

**【0021】**

基板110は、透明性絶縁基板、例えば、ガラス基板からなる。

**【0022】**

50

20

30

40

50

ゲート配線 120 は、例えば、アルミニウム (A1)、モリブデン (Mo)、クロム (Cr)、タンタル (Ta)、チタニウム (Ti)、タングステン (W)、銅 (Cu)、銀 (Ag) 等の単一金属又はこれらの合金で形成されることができる。又、ゲート配線 120 は、物理的性質の異なる 2 つ以上の金属層で形成されることができる。例えば、ゲート配線 120 は低抵抗配線のために、アルミニウム (A1) とモリブデン (Mo) が積層された A1 / Mo 二層膜構造で形成されることができる。

#### 【0023】

ゲートライン 122 は、例えば、横方向に延長される。ゲート電極 124 はゲートライン 122 と連結され、各画素 (P) に形成されるスイッチング素子である薄膜トランジスタ TFT のゲート端子を構成する。

10

#### 【0024】

図 3 を参照すると、ゲート配線 120 が形成された基板 110 上にゲート絶縁膜 130 及び活性層 140 を順次に形成する。ゲート絶縁膜 130 及び活性層 140 は、例えば、プラズマ化学気相蒸着方法を通じて形成されることがある。

#### 【0025】

ゲート絶縁膜 130 はゲート配線 120 を保護し、ゲート絶縁膜 130 の上部に形成されるデータ用金属膜 150 等と絶縁させるための絶縁膜であって、例えば、窒化シリコン (SiNx) 又は酸化シリコン (SiOx) で形成され、CVD 工程を通じて約 4500 の厚みに形成される。

#### 【0026】

活性層 140 は、チャネル層 142 及びオーミックコンタクト層 144 を含む。例えば、チャネル層 142 は、非晶質シリコン (以下、a-Si) で形成され、オーミックコンタクト層 144 は、n 型不純物が高濃度でドーピングされた非晶質シリコン (以下、n+a-Si) で形成されることがある。

20

#### 【0027】

その後、活性層 140 上に第 1 金属層 151、第 2 金属層 152、及び第 3 金属層 153 を連続して積層してデータ用金属膜 150 を形成する。例えば、第 1 金属層 151 はモリブデン (Mo)、第 2 金属層 152 はアルミニウム (A1)、第 3 金属層 153 はモリブデン (Mo) で形成されることがある。従って、データ用金属膜 150 は、低抵抗配線の形成のために、Mo / A1 / Mo 三層膜構造で形成される。データ用金属膜 150 は、例えば、スパッタリング方法を通じて活性層 140 上に形成されることがある。

30

#### 【0028】

図 4 を参照すると、データ用金属膜 150 上にフォトレジストを形成した後、スリットマスク又はハーフトンマスク等の第 2 露光マスクを利用してフォトリソグラフィ工程を通じて前記フォトレジストをパターニングして第 1 フォトレジストパターン 160 を形成する。前記フォトレジストは、例えば、露光された領域が現像液によって除去されるポジティブ型フォトレジストで形成される。

#### 【0029】

第 1 フォトレジストパターン 160 は、チャネル形成領域に対応する部分が前記チャネル形成領域以外に対応する部分に対して薄い厚みを有するように形成される。例えば、第 1 フォトレジストパターン 160 のチャネル形成領域に対応する部分は、約 500 ~ 8000 の厚みに形成される。

40

#### 【0030】

図 5 を参照すると、第 1 フォトレジストパターン 160 をエッチングマスクとして利用して、データ用金属膜 150 のうち、最も上部に形成された第 3 金属層 153 をドライエッティングする。

#### 【0031】

モリブデン (Mo) で形成された第 3 金属層 153 のドライエッティングのために、エッティングガスとしては六フッ化硫黄 (SF<sub>6</sub>) ガスと塩素 (Cl<sub>2</sub>) ガスが主に使用されることがある。例えば、六フッ化硫黄 (SF<sub>6</sub>) ガスと塩素 (Cl<sub>2</sub>) ガスは約 1 : 0.

50

5～約1：1.5程度の組成比で混合され使用される。

**【0032】**

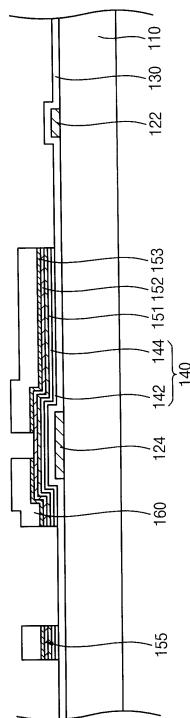

図1及び図6を参照すると、第1フォトレジストパターン160をエッティングマスクとして利用して第2金属層152及び第1金属層151を同時にドライエッティングする。

**【0033】**

アルミニウム(A1)で形成された第2金属層152とモリブデン(Mo)で形成された第1金属層151を同時にドライエッティングするために、エッティングガスとしては三塩化ホウ素(BCl<sub>3</sub>)ガスと塩素(Cl<sub>2</sub>)ガスが主に使用されることができる。例えば、三塩化ホウ素(BCl<sub>3</sub>)ガスと塩素(Cl<sub>2</sub>)ガスは約1：1～約1：5程度の組成比で混合され使用される。アルミニウム(A1)で形成された第2金属層152のみをエッティングする場合に対して三塩化ホウ素(BCl<sub>3</sub>)の組成比率を高めることにより、第2金属層152と第1金属層151を同時にドライエッティングすることが可能になる。10

**【0034】**

一方、第3金属層153、第2金属層152、及び第1金属層151をそれぞれドライエッティングする場合、チャンネル形成領域に位置するフォトレジストの残量不足によってドライエッティング途中に活性層140のチャンネル領域が開く現象が発生する。従って、第2金属層152と第1金属層151を同時にドライエッティングすることにより、工程を単純化させ、工程マージンを増加させてチャンネルが開く現象をある程度除去することができる。20

**【0035】**

第1フォトレジストパターン160を利用したドライエッティング工程を通じて第3金属層153、第2金属層152、及び第1金属層151のエッティングが完了されると、データライン155とソース／ドレイン用金属パターン156のみが残ることになる。データライン155は、例えば、ゲートライン122と交差する縦方向に延長される。20

**【0036】**

図7を参照すると、第1フォトレジストパターン160をエッティングマスクとして利用して活性層140をドライエッティングする。

**【0037】**

このように同じ第1フォトレジストパターン160を利用してデータ用金属膜150及び活性層140をエッティングすることにより、残られる活性層140の外部輪郭は、データライン155及びソース／ドレイン用金属パターン156の外部輪郭と実質的に一致するように形成される。30

**【0038】**

図8を参照すると、酸素プラズマを利用したアッシング工程を通じて第1フォトレジストパターン160を一定厚みだけエッティングしてチャンネル形成領域に対応する部分が除去された第2フォトレジストパターン162を形成する。これによって、チャンネル形成領域に対応されるソース／ドレイン用金属パターン156が外部に露出される。

**【0039】**

図1及び図9を参照すると、第2フォトレジストパターン162をエッティングマスクとして利用してソース／ドレイン用金属パターン156のチャンネル形成領域をドライエッティングする。40

**【0040】**

第2フォトレジストパターン162を利用したドライエッティング工程は、前述した第1フォトレジストパターン160を利用したドライエッティング工程と同様に、第3金属層153を1次にドライエッティングし、第2金属層152及び第1金属層151を同時に2次にドライエッティングする工程に進行されることができる。これと異なり、第2フォトレジストパターン162を利用したドライエッティング工程は、第3金属層153、第2金属層152、及び第1金属層151をそれぞれドライエッティングする工程に進行されることがある。

**【0041】**

50

20

30

40

50

第2フォトレジストパターン162を利用したドライエッチング工程を通じてソース/ドレイン用金属パターン156のチャンネル形成領域のエッチングが完了されると、ソース電極157及びドレイン電極158が形成される。ソース電極157は、データライン155と連結され薄膜トランジスタTFTのソース端子を構成する。ドレイン電極158は、ソース電極157と離隔して薄膜トランジスタTFTのドレイン端子を構成する。

#### 【0042】

その後、第2フォトレジストパターン162をエッチングマスクとして利用してチャンネル形成領域のオーミックコンタクト層144をエッチングする。これによって、ソース電極157とドレイン電極158との間にはチャンネル層142が露出され薄膜トランジスタTFTのチャンネル159が形成される。

10

#### 【0043】

このように、第1、第2、及び第3金属層151、152、153で形成されたデータ用金属膜150の全てのエッチング工程をドライエッチング工程で進行することにより、ウェットエッチングによる配線幅増加等の問題点を改善し、製造工程をより単純化させることができる。

#### 【0044】

その後、データライン155、ソース電極157、及びドレイン電極158上に存在する第2フォトレジストパターン162を除去する。例えば、第2フォトレジストパターン162は、ストリップ溶液を利用したストリップ工程を通じて除去される。これによって、薄膜トランジスタTFTの製造が完了される。

20

#### 【0045】

図1及び図10を参照すると、薄膜トランジスタTFTが形成された基板110上に保護膜170を形成する。保護膜170は、薄膜トランジスタTFT及びデータライン155を保護して絶縁させるための絶縁膜であって、例えば、窒化シリコン(SiNx)又は酸化シリコン(SiOx)で形成され、CVD工程を通じて約500~2000の厚みに形成される。

#### 【0046】

その後、第3露光マスクを利用したフォトリソグラフィ工程を通じて保護膜170をパターニングしてドレイン電極158の一部を露出させるコンタクトホール172を形成する。

30

#### 【0047】

図1及び図11を参照すると、保護膜170上に透明性導電膜を形成した後、第4露光マスクを利用したフォトリソグラフィ工程を通じて前記透明性導電膜をパターニングして各画素(P)内に画素電極180を形成する。

#### 【0048】

画素電極180は、保護膜170に形成されたコンタクトホール172を通じてドレイン電極158と電気的に連結される。画素電極180は、例えば、インジウムジンクオキサイド(IZO)又はインジウムティンオキサイド(ITO)で形成される。

#### 【0049】

一方、図示されていないが、画素電極180を形成する前に保護膜170上に平坦化のための有機絶縁膜を更に形成することができる。

40

#### 【0050】

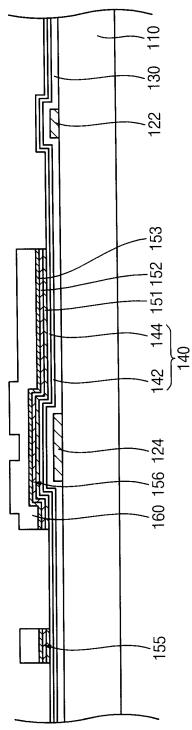

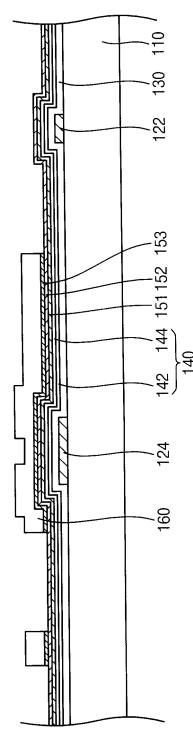

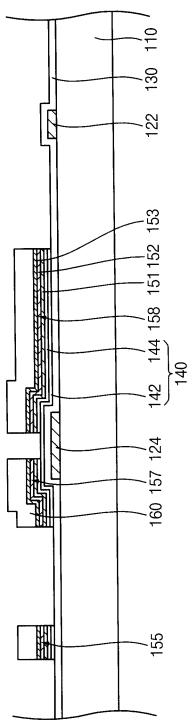

図12乃至図15は、他の実施例によるデータ用金属膜のエッチング過程を示す工程図である。データ用金属膜を形成する過程までは、図2乃至図4に図示された工程図と同じなので、これらの図と関連する詳細な説明は省略する。

#### 【0051】

図12を参照すると、チャンネル形成領域に対応する部分が前記チャンネル形成領域以外に対応する部分に対して相対的に薄い厚みを有するフォトレジストパターン160をエッチングマスクとして利用して第3金属層153をドライエッチングする。

#### 【0052】

50

モリブデン(Mo)で形成された第3金属層153のドライエッチングのために、エッチングガスとしてはフッ素(F)系列のガスと塩素(Cl<sub>2</sub>)ガスが使用される。例えば、フッ素(F)系列のガスとしては、六フッ化硫黄(SF<sub>6</sub>)ガスが使用されることがある。この際、六フッ化硫黄(SF<sub>6</sub>)ガスと塩素(Cl<sub>2</sub>)ガスは約1:0.5~約1:1.5程度の組成比で混合され使用される。

#### 【0053】

図13を参照すると、フォトレジストパターン160をエッチングマスクとして利用して第2金属層152をドライエッチングする。

#### 【0054】

アルミニウム(Al)で形成された第2金属層152のドライエッチングのために、エッチングガスとしては三塩化ホウ素(BCl<sub>3</sub>)ガスと塩素(Cl<sub>2</sub>)ガスが使用される。例えば、三塩化ホウ素(BCl<sub>3</sub>)ガスと塩素(Cl<sub>2</sub>)ガスは、第2金属層152のみをエッチングするために、約1:8~約1:12程度の組成比で混合され使用される。

10

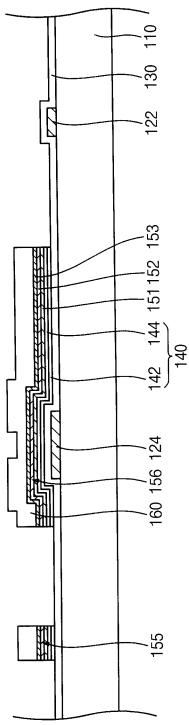

#### 【0055】

図14を参照すると、フォトレジストパターン160をエッチングマスクとして利用して第1金属層151と活性層140を同時にドライエッチングする。

#### 【0056】

モリブデン(Mo)で形成された第1金属層151とa-Si及びn+a-Siで形成された活性層140を同時にドライエッチングするために、エッチングガスとしてはフッ素(F)系列のガスと塩素(Cl<sub>2</sub>)ガスが使用される。例えば、フッ素(F)系列のガスとしては六フッ化硫黄(SF<sub>6</sub>)ガスが使用されることがある。この際、六フッ化硫黄(SF<sub>6</sub>)ガスと塩素(Cl<sub>2</sub>)ガスは、約1:5~約1:7程度の組成比で混合され使用される。このように、モリブデン(Mo)で形成された第1金属層151のみをエッチングする場合に対して塩素(Cl<sub>2</sub>)ガスの組成比率を高めることにより、第1金属層151と活性層140を同時にドライエッチングすることが可能になる。

20

#### 【0057】

このように、第1金属層151と活性層140を同時にドライエッチングすることにより、工程を単純化させ、工程マージンを増加させてチャンネルが開く現象を完全に除去することができる。

#### 【0058】

30

一方、第1金属層151と活性層140を同時にドライエッチングする途中に、フォトレジストパターン160のチャンネル形成領域に対応する部分がオープンされ第3金属層153が同時にエッチングされる。

#### 【0059】

場合によっては、チャンネル形成領域にフォトレジストが残存があるので、チャンネル形成領域に残存するフォトレジストを完全に除去するために、アッシング工程を更に進行することができる。

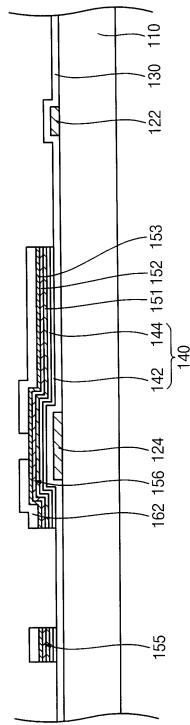

#### 【0060】

図15を参照すると、フォトレジストパターン160をエッチングマスクとして利用してチャンネル形成領域の第2金属層152及び第1金属層151をドライエッチングする。

40

#### 【0061】

チャンネル形成領域の第2金属層152及び第1金属層151をドライエッチングする工程は、図9に説明したように、1回のドライエッチングで第2金属層152及び第1金属層151を同時にドライエッチングするか、第2金属層152及び第1金属層151をそれぞれドライエッチングする工程で進行されることがある。

#### 【0062】

以後、チャンネル形成領域のオーミックコンタクト層144をエッチングすると、ソース電極157とドレイン電極158との間のチャンネル層142が露出され薄膜トランジスタTFTのチャンネルが形成される。

50

**【0063】**

以後の製造工程は、図10及び図11に図示されたものと同じなので、これらの図と関連する詳細な説明は省略する。

**【0064】**

このような薄膜トランジスタ基板の製造方法によると、低抵抗配線のために、Mo/A<sub>1</sub>/Mo三層膜構造で形成されたデータ用金属膜の全てのエッティング工程をドライエッティング工程で進行することにより、ウェットエッティングによって発生した配線幅増加等の問題点を改善し、製造工程を単純化させることができる。

**【0065】**

又、アルミニウムと下部モリブデンを同時にドライエッティングするか、下部モリブデンと活性層を同時にドライエッティングすることにより、製造工程をより単純化させ、工程マージンを増加させてチャンネルが開く現象を防止することができる。 10

**【0066】**

以上、本発明の実施例によって詳細に説明したが、本発明はこれに限定されず、本発明が属する技術分野において通常の知識を有するものであれば本発明の思想と精神を離れることなく、本発明を修正または変更できる。

**【産業上の利用可能性】****【0067】**

本発明は、薄膜トランジスタ基板の製造方法に利用することができる。

**【図面の簡単な説明】****【0068】**

【図1】本発明の実施例によって製造された薄膜トランジスタ基板を示す平面図である。

【図2】図1に図示された薄膜トランジスタ基板の製造過程を示す工程図である。

【図3】図1に図示された薄膜トランジスタ基板の製造過程を示す工程図である。

【図4】図1に図示された薄膜トランジスタ基板の製造過程を示す工程図である。

【図5】図1に図示された薄膜トランジスタ基板の製造過程を示す工程図である。

【図6】図1に図示された薄膜トランジスタ基板の製造過程を示す工程図である。

【図7】図1に図示された薄膜トランジスタ基板の製造過程を示す工程図である。

【図8】図1に図示された薄膜トランジスタ基板の製造過程を示す工程図である。

【図9】図1に図示された薄膜トランジスタ基板の製造過程を示す工程図である。 30

【図10】図1に図示された薄膜トランジスタ基板の製造過程を示す工程図である。

【図11】図1に図示された薄膜トランジスタ基板の製造過程を示す工程図である。

【図12】他の実施例によるデータ用金属膜のエッティング過程を示す工程図である。

【図13】他の実施例によるデータ用金属膜のエッティング過程を示す工程図である。

【図14】他の実施例によるデータ用金属膜のエッティング過程を示す工程図である。

【図15】他の実施例によるデータ用金属膜のエッティング過程を示す工程図である。 30

**【符号の説明】****【0069】**

110 基板、

122 ゲートライン、

124 ゲート電極、

130 ゲート絶縁層、

140 活性層、

142 チャンネル層、

144 オーミックコンタクト層、

150 データ用金属膜、

151 第1金属層、

152 第2金属層、

153 第3金属層、

155 データライン、

40

50

- 1 5 7 ソース電極、

1 5 8 ドレイン電極、

1 6 0 第1フォトレジストパターン、

1 6 2 第2フォトレジストパターン、

1 7 0 保護膜、

1 8 0 画素電極。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

---

フロントページの続き

(72)発明者 宋 大 炳

大韓民国全羅北道完州郡所陽面シンギョ里215

(72)発明者 金 京 燐

大韓民国京畿道水原市勸善区谷伴亭洞 三星アパート102棟703号

(72)発明者 李 庸 豔

大韓民国京畿道城南市盆唐区藪内洞 ヤンジマウルチヨングアパート212棟1203号

合議体

審判長 松本 貢

審判官 鈴木 匠明

審判官 加藤 浩一

(56)参考文献 特開2005-228826(JP,A)

特開2002-341367(JP,A)

特開2002-311445(JP,A)

特開2006-091823(JP,A)

米国特許出願公開第2006/0076562(US,A1)

(58)調査した分野(Int.Cl., DB名)

H01L 21/336

H01L 29/786