(19) 日本国特許庁(JP)

(12) 特 許 公 報(B2)

(11) 特許番号

特許第5235960号

(P5235960)

(45) 発行日 平成25年7月10日(2013.7.10)

(24) 登録日 平成25年4月5日(2013.4.5)

(51) Int.Cl.

F 1

**HO 1 L** 29/78 (2006.01)

**HO 1 L** 21/336 (2006.01)

HO 1 L 29/78 652N

HO 1 L 29/78 652H

HO 1 L 29/78 658A

HO 1 L 29/78 658E

請求項の数 11 (全 18 頁)

|           |                              |

|-----------|------------------------------|

| (21) 出願番号 | 特願2010-203423 (P2010-203423) |

| (22) 出願日  | 平成22年9月10日 (2010. 9. 10)     |

| (65) 公開番号 | 特開2012-60017 (P2012-60017A)  |

| (43) 公開日  | 平成24年3月22日 (2012. 3. 22)     |

| 審査請求日     | 平成24年8月17日 (2012. 8. 17)     |

(73) 特許権者 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(74) 代理人 100108062

弁理士 日向寺 雅彦

(72) 発明者 木村 淑

東京都港区芝浦一丁目1番1号 株式会社

東芝内

(72) 発明者 角 保人

東京都港区芝浦一丁目1番1号 株式会社

東芝内

(72) 発明者 大田 浩史

東京都港区芝浦一丁目1番1号 株式会社

東芝内

最終頁に続く

(54) 【発明の名称】 電力用半導体装置及びその製造方法

## (57) 【特許請求の範囲】

【請求項 1】

対向する第1の電極と第2の電極との間に垂直方向に電流が流れる素子部と、前記垂直方向と直交する水平面内で前記素子部を囲んだ環状構造の終端部と、を有する電力用半導体装置であって、

## 第1導電形の第1の半導体層と、

前記第1の半導体層の上に形成された前記第1の半導体層よりも第1導電形の不純物濃度が低い第1導電形の第1のエピタキシャル層と、前記第1のエピタキシャル層中の前記素子部においてのみ前記水平面に平行な第1の方向に交互に繰り返し配置され前記第1のエピタキシャル層よりも第1導電形の不純物濃度が高い第1の第1導電形ピラー層と第1の第2導電形ピラー層と、を有する、第1のドリフト層と、

前記第1のドリフト層上に形成され、前記第1のエピタキシャル層よりも第1導電形の不純物濃度が高い第1導電形の第2のエピタキシャル層と、前記第2のエピタキシャル層中の前記素子部において前記第1の方向に沿って離間配置され前記第1の第2導電形ピラー層と接続された第2の第2導電形ピラー層と、隣り合う前記第2の第2導電形ピラー層に挟まれた前記第2のエピタキシャル層からなり前記第1の第1導電形ピラー層と接続された第2の第1導電形ピラー層と、前記第2のエピタキシャル層中の前記終端部において前記第1の方向に沿って離間配置され前記第1のエピタキシャル層上に配置された第3の第2導電形ピラー層と、隣り合う前記第3の第2導電形ピラー層に挟まれた前記第2のエピタキシャル層からなり前記第1のエピタキシャル層上に配置された第3の第1導電形ピ

ラー層と、を有する第2のドリフト層と、

前記素子部において、前記第2のドリフト層の表面に選択的に形成され、前記第2の第2導電形ピラー層と電気的に接続された複数の第2導電形ベース層と、

前記第2導電形ベース層の表面に選択的に形成された第1導電形のソース層と、

前記ソース層、前記ベース層、前記第2の第1導電形ピラー層の上に、ゲート絶縁膜を介して形成されたゲート電極と、

を備え、

前記第1の電極は、前記第1の半導体層の前記第1のドリフト層とは反対側の表面に電気的に接続され、

前記第2の電極は、前記ソース層及び前記ベース層と電気的に接続されていることを特徴とする電力用半導体装置。 10

#### 【請求項2】

前記第1のドリフト層中の前記第1の第1導電形ピラー層は、前記垂直方向における前記第1導電形不純物の濃度分布の中心に前記第1導電形不純物濃度の極大値を有する複数の第1の第1導電形層が前記垂直方向に第1の結合部で結合して形成され、前記第1の結合部において前記第1導電形不純物濃度が極小値を有しております、

前記第1のドリフト層中の前記第1の第2導電形ピラー層は、前記垂直方向における前記第2導電形不純物の濃度分布の中心に前記第2導電形不純物濃度の極大値を有する複数の第1の第2導電形層が前記垂直方向に第2の結合部で結合して形成され、前記第2の結合部において前記第2導電形不純物濃度が極小値を有しております、 20

前記第2のドリフト層中の前記第2の第2導電形ピラー層は、前記垂直方向における前記第2導電形不純物の濃度分布に前記第2導電形不純物濃度の極大値を有しない、ことを特徴とする請求項1記載の電力用半導体装置。

#### 【請求項3】

前記複数の第1の第1導電形層と前記複数の第1の第2導電形層とは、それぞれ、中心に不純物濃度の極大値を有する拡散層であり、

前記第2のドリフト層の前記第2の第2導電形ピラー層は、前記第2の第1導電形エピタキシャル層に形成されたトレンチに埋め込まれた埋込層であることを特徴とする請求項2記載の電力用半導体装置。

#### 【請求項4】

前記第2のドリフト層の前記第2の第1導電形ピラー層は、前記第1のドリフト層の前記第1の第1導電形ピラー層よりも第1導電形の不純物濃度が高く、

前記第2のドリフト層の前記第2の第2導電形ピラー層は、前記第1のドリフト層の第1の第2導電形ピラー層よりも第2の導電形の不純物の濃度が高いことを特徴とする請求項1～3のいずれか1つに記載の電力用半導体装置。 30

#### 【請求項5】

前記第1のドリフト層中のダイシングされたチップ端部に隣接した部分において、前記垂直方向における前記第1導電形不純物の濃度分布の中心に前記第1導電形不純物濃度の極大値を有する複数の第2の第1導電形層が前記垂直方向に結合して形成されたピラー層がさらに配置されていることを特徴とする請求項1～4のいずれか1つに記載の電力用半導体装置。 40

#### 【請求項6】

前記第2のドリフト層の前記第2の第2導電形ピラー層は、前記第2の電極側に向かうほど前記第1の方向における幅が広くなることを特徴とする請求項1～5のいずれか1つに記載の電力用半導体装置。

#### 【請求項7】

第2導電形のコレクタ層が前記第1の電極と前記第1の半導体層との間にさらに設けられ、

前記第2導電形のコレクタ層は、前記第1の電極と前記第1の半導体層とにそれぞれ電気的に接続されていることを特徴とする請求項1～6のいずれか1つに記載の電力用半導 50

体装置。

**【請求項 8】**

第1の電極と第2の電極との間に垂直方向に電流が流れる素子部と、前記垂直方向と直交する水平面内で前記素子部を囲んだ環状構造の終端部と、を有する電力用半導体装置を製造する方法であって、

第1導電形の第1の半導体層を形成する工程と、

前記第1の半導体層よりも第1導電形の不純物濃度が低い第1導電形の第1のエピタキシャル層を有する第1のドリフト層を前記第1の半導体層の上に形成する工程と、

前記第1のエピタキシャル層よりも第1導電形の不純物濃度が高い第1導電形の第2エピタキシャル層と、前記第2エピタキシャル層中の前記素子部に設けられた第2の第2導電形ピラー層と、前記第2エピタキシャル層中の前記素子部に設けられ前記第2のエピタキシャル層からなる第2の第1導電形ピラー層と、前記第2エピタキシャル層中の前記終端部に設けられ前記第1のエピタキシャル層上に配置された第3の第2導電形ピラー層と、前記第2エピタキシャル層中の前記終端部に設けられ前記第2のエピタキシャル層からなり前記第1のエピタキシャル層上に配置された第3の第1導電形ピラー層と、を有する第2のドリフト層を前記第1のドリフト層上に形成する工程と、

熱処理の工程と、

素子部において、ゲート絶縁膜を介してゲート電極を形成する工程と、

素子部において、前記第2のドリフト層の表面に選択的に形成され、前記第2の第2導電形ピラー層と電気的に接続された複数の第2導電形ベース層を形成する工程と、

前記第2導電形ベース層の表面に選択的に形成された第1導電形ソース層を形成する工程と、

前記第1の半導体層の前記第1のドリフト層と反対側の表面に電気的に接続されるよう前記第1の電極を形成する工程と、

前記第1導電形ソース層と前記第2導電形ベース層と電気的に接続されるよう前記第2の電極を形成する工程と、

を備え、

前記第1のドリフト層を形成する工程は、

前記第1のエピタキシャル層の第1層を前記第1の半導体層上にエピタキシャル成長する工程と、

前記素子部においてだけ、前記第1のエピタキシャル層の第1層の表面に、第1のマスクを介して、前記水平面に平行な第1の方向に離間して第1導電形不純物を含む第1の第1導電形不純物層を形成する工程と、

前記素子部においてだけ、前記第1のエピタキシャル層の第1層の表面に、第2のマスクを介して、前記第1の方向に所定の間隔で離間しそれぞれの隣り合う前記第1の第1導電形不純物層の間に第2導電形不純物を含む第2導電形不純物層を形成する工程と、

前記第1の第1導電形不純物層及び前記第2導電形不純物層が形成された前記第1のエピタキシャル層の前記第1層上に、前記第1のエピタキシャル層の第2層をエピタキシャル成長する工程と、

を含み、

前記第2のドリフト層を形成する工程は、

前記第2のエピタキシャル層を前記第1のドリフト層上にエピタキシャル成長する工程と、

前記素子部において、前記第1の方向に離間配置され、前記第1の第1導電形不純物層の直上で前記第1のドリフト層に達する第1のトレンチ、及び、前記終端部において、前記第1の方向に離間配置され、前記第1のドリフト層の前記第1のエピタキシャル層に達する第2のトレンチを、それぞれ第3のマスクを介して前記第2のエピタキシャル層に形成することで、隣り合う前記第1のトレンチ間に前記第2の第1導電形ピラー層を、隣り合う前記第2のトレンチ間に前記第3の第1導電形ピラー層をそれぞれ形成する工程と、

10

20

30

40

50

前記第2のエピタキシャル層の前記第1のトレンチ及び前記第2のトレンチ内に、前記第2の第2導電形ピラー層及び前記第3の第2導電形ピラー層を埋込形成する工程と、

、

を含み、

前記熱処理の工程は、前記第1導電形不純物を拡散させることで前記第1の第1導電形不純物層から第1の第1導電形ピラー層を、前記第2の第1導電形ピラー層に電気的に接続されるように前記第1のドリフト層中に形成し、前記第2導電形不純物を拡散させることで前記第2導電形不純物層から第1の第2導電形ピラー層を、前記第2の第2導電形ピラー層に電気的に接続されるように前記第1のドリフト層中に形成する工程を含む、

ことを特徴とする電力用半導体装置の製造方法。

10

#### 【請求項9】

前記第1のドリフト層を形成する工程中の、前記素子部においてだけ前記第1のマスクを介して第1の第1導電形不純物層を形成する工程は、前記第1のマスクを介して、前記終端部のダイシングされてチップ端部となるべき位置に隣接して、前記第1導電形不純物を含む第2の第1導電形不純物層も一体に形成する工程を含むことを特徴とする請求項8記載の電力用半導体装置の製造方法。

#### 【請求項10】

前記第1のトレンチ及び前記第2のトレンチは、前記垂直方向において前記第1のドリフト層から離れるほど、前記第1の方向における幅が広くなることを特徴とする請求項8または9に記載の電力用半導体装置の製造方法。

20

#### 【請求項11】

前記第1の電極と前記第1の半導体層との間に、第2導電形のコレクタ層を形成する工程をさらに含むことを特徴とする請求項8～10のいずれか1つに記載の電力用半導体装置の製造方法。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明の実施形態は、パワーMOSFETなどの大電力用の半導体装置及びその製造方法に関する。

##### 【背景技術】

30

##### 【0002】

パワーMOSFET (Metal Oxide Semiconductor Field Effect Transistor) では、オン抵抗はドリフト層の不純物濃度できる。オン抵抗を下げるために不純物濃度を上げると、ベース層からドリフト層中に空乏層が十分に広がらないために耐圧が低下する。つまり、オン抵抗と耐圧との間には、トレードオフの問題がある。この問題を解決する手段として、nピラー層とpピラー層とを交互に水平方向に繰り返し配置されたスーパージャンクション構造が用いられる。スーパージャンクション構造は、nピラー層中のn形不純物量とpピラー層中のp形不純物量とのバランスをとることで、完全に空乏化しやすく、擬似的にノンドープ層を形成している。このため、各ピラー層の不純物濃度を上げてオン抵抗を低減しても、MOSFETの耐圧の低下を抑制することができる。パワーMOSFETには、電流が流れる素子部と、その素子部を取り囲んでチップの外周部に形成される終端部と、が形成される。アバランシェ耐量が高い素子部で先にアバランシェを発生させることで、パワーMOSFETを破壊から防ぐことができる。スーパージャンクション構造を有するパワーMOSFETにおいても、素子部より終端部での耐圧が高いことが望まれる。

40

#### 【先行技術文献】

##### 【特許文献】

##### 【0003】

#### 【特許文献1】特開2007-36213号公報

#### 【発明の概要】

50

**【発明が解決しようとする課題】****【0004】**

終端部での耐圧が向上して、素子破壊を抑制できる電力用半導体装置を提供する。

**【課題を解決するための手段】****【0005】**

本発明の実施形態にかかる電力用半導体装置は、対向する第1の電極と第2の電極との間に垂直方向に電流が流れる素子部及び垂直方向と直交する水平面内で素子部を囲んだ環状構造の終端部を有し、第1導電形の第1の半導体層と、第1のドリフト層と、第2のドリフト層と、ゲート配線層と、複数の第2導電形ベース層と、第1導電形のソース層と、ゲート電極と、を備える。第1のドリフト層は、第1の半導体層の上に形成され第1の半導体層よりも第1導電形の不純物濃度が低い第1導電形の第1のエピタキシャル層と、第1のエピタキシャル層中の素子部においてのみ水平面に平行な第1の方向に交互に繰り返し配置され第1のエピタキシャル層よりも第1の不純物濃度が高い第1の第1導電形ピラー層と第1の第2導電形ピラー層と、を有する。第2のドリフト層は、第1のドリフト層上に形成され第1のエピタキシャル層よりも第1導電形の不純物濃度が高い第1導電形の第2のエピタキシャル層と、第2の第2導電形ピラー層と、第2の第1導電形ピラー層と、第3の第2導電形ピラー層と、第3の第1導電形ピラー層と、を有する。第2の第2導電形ピラー層は、第2のエピタキシャル層中の素子部において第1の方向に沿って離間配置され第1の第2導電形ピラー層と接続される。第2の第1導電形ピラー層は、隣り合う第2の第2導電形ピラー層に挟まれた第2のエピタキシャル層からなり第1の第1導電形ピラー層と接続される。第3の第2導電形ピラー層は、第2のエピタキシャル層中の終端部において第1の方向に沿って離間配置され第1のエピタキシャル層上に配置される。第3の第1導電形ピラー層は、隣り合う第3の第2導電形ピラー層に挟まれた第2のエピタキシャル層からなり第1のエピタキシャル層上に配置される。ゲート配線層は、素子部と終端部との境界において、絶縁膜を介して第2のドリフト層上に配置される。複数の第2導電形ベース層は、素子部において、第2のドリフト層の表面に選択的に形成され、第2の第2導電形ピラー層と電気的に接続される。第1導電形のソース層は、第2導電形ベース層の表面に選択的に形成される。ゲート電極は、ソース層、ベース層、第2の第1導電形ピラー層の上に、ゲート絶縁膜を介して形成され、ゲート配線層に電気的に接続される。第1の電極は、第1の半導体層の第1のドリフト層とは反対側の表面に電気的に接続されている。第2の電極は、ソース層及びベース層と電気的に接続されている。10

20

30

**【図面の簡単な説明】****【0006】**

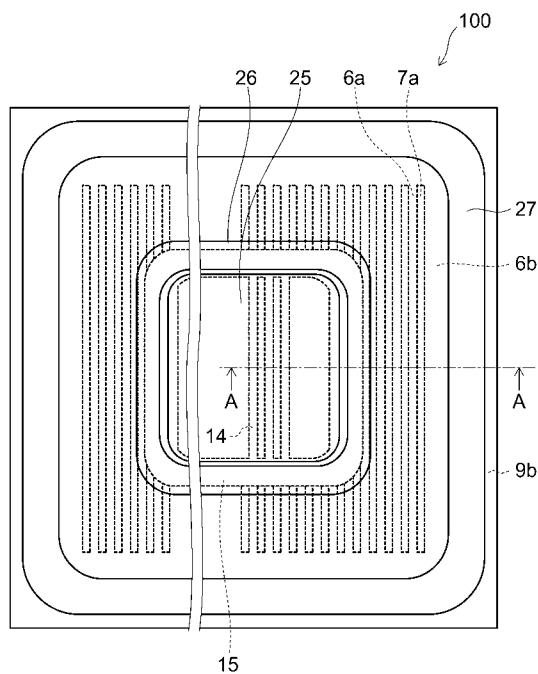

【図1】第1の実施の形態に係る電力用半導体装置のチップ上面図。

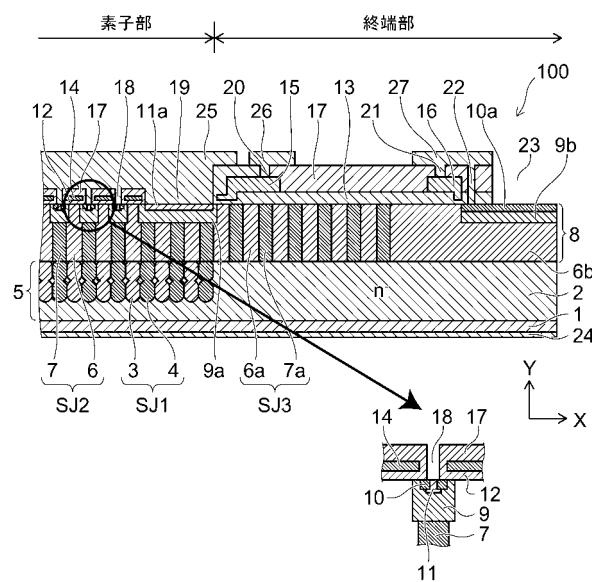

【図2】第1の実施の形態に係る電力用半導体装置の要部断面図。

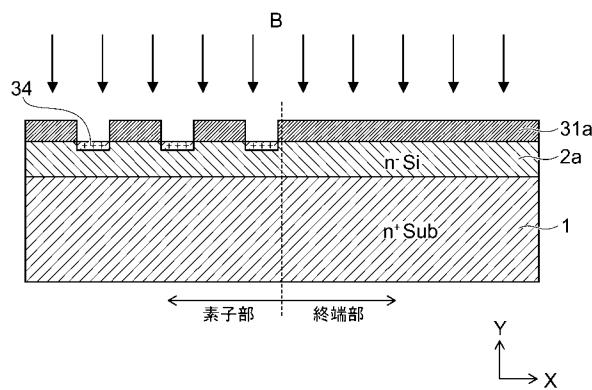

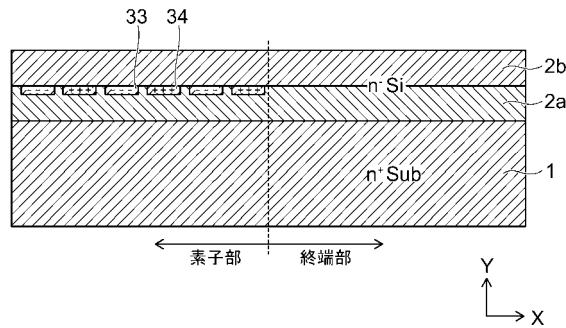

【図3】第1の実施の形態に係る電力用半導体装置の製造工程を示す要部断面図。

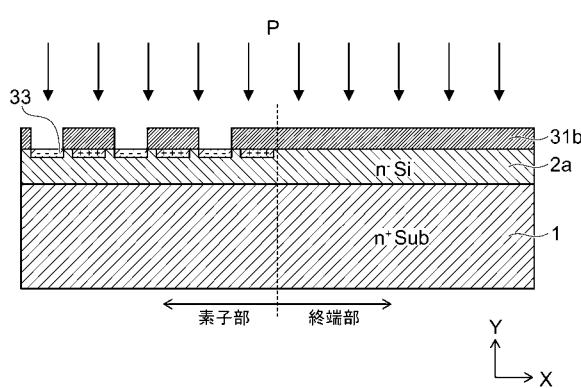

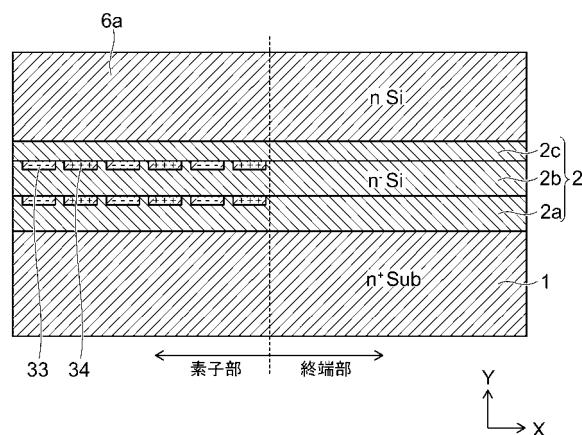

【図4】第1の実施の形態に係る電力用半導体装置の製造工程を示す要部断面図。

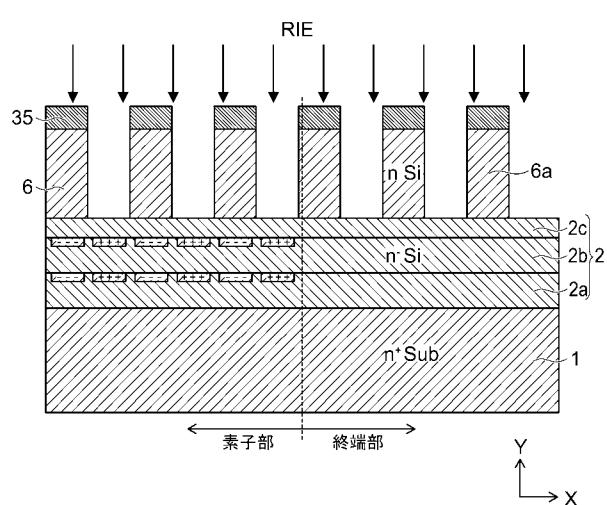

【図5】第1の実施の形態に係る電力用半導体装置の製造工程を示す要部断面図。

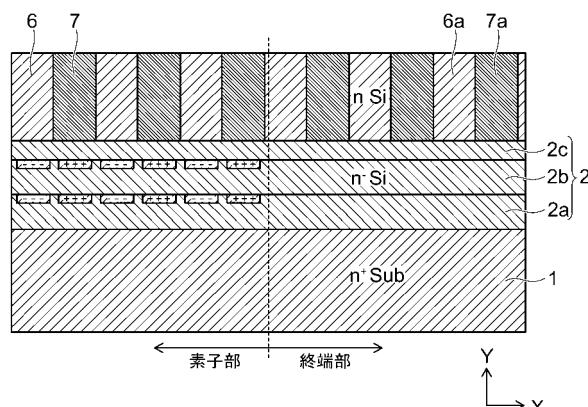

【図6】第1の実施の形態に係る電力用半導体装置の製造工程を示す要部断面図。

【図7】第1の実施の形態に係る電力用半導体装置の製造工程を示す要部断面図。40

【図8】第1の実施の形態に係る電力用半導体装置の製造工程を示す要部断面図。

【図9】第2の実施の形態に係る電力用半導体装置の要部断面図。

**【発明を実施するための形態】****【0007】**

以下、本発明の実施の形態について図を参照しながら説明する。実施の形態中の説明で使用する図は、説明を容易にするための模式的なものであり、図中の各要素の形状、寸法、大小関係などは、実際の実施においては必ずしも図に示されたとおりとは限らず、本発明の効果が得られる範囲内で適宜変更可能である。第1導電形をn形で、第2導電形をp形で説明するが、それぞれこの逆の導電形とすることも可能である。半導体としては、シリコンを一例に説明するが、SiCやGaNなどの化合物半導体にも適用可能である。絶50

縁膜としては、シリコン酸化膜を一例に説明するが、シリコン窒化膜、シリコン酸窒化膜、アルミナなどの他の絶縁体を用いることも可能である。n形の導電形をn<sup>+</sup>、n、n<sup>-</sup>で表記した場合は、この順にn形不純物濃度が低いものとする。p形においても同様に、p<sup>+</sup>、p、p<sup>-</sup>の順にp形不純物濃度が低いものとする。

## 【0008】

## (第1の実施の形態)

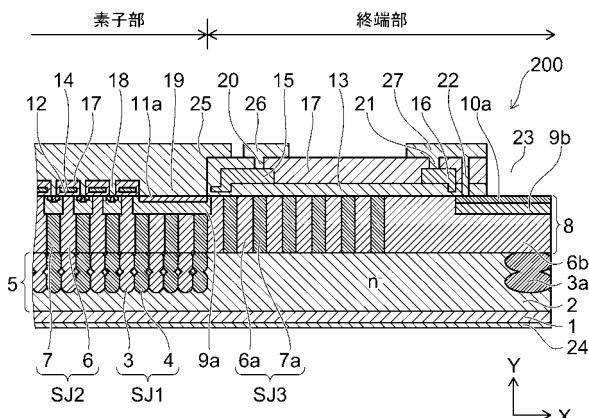

第1の実施の形態について、図1及び図2を用いて説明する。図1は、第1の実施の形態に係る電力用半導体装置のチップを上からみた上面図である。図2は、第1の実施の形態に係る電力用半導体装置の要部断面図であり、図1のA-Aに沿った断面図である。

## 【0009】

第1の実施形態にかかる電力用半導体装置100は、n形チャネルのMOSFET(Metal Oxide Semiconductor Field Effect Transistor)であり、n<sup>+</sup>形(第1導電形)のドレイン層(第1の半導体層)1と、第1のドリフト層5と、第2のドリフト層8と、ゲート電極14と、ドレイン電極(第1の電極)24と、ソース電極(第2の電極)25とを備え、ドレイン電極24からこれに対向するソース電極25に向かって図中Y方向(垂直方向)にゲート電極14により制御された電流が流れる素子部と、水平面内で素子部を囲んだ環状構造の終端部とを有する。すなわち、素子部は、ドレイン電極24からソース電極24へ流れる電流をゲート電極が制御するMOSFETのセル領域を内部に有する。終端部は、そのMOSFETのセル領域を含まず、その外側で素子部を囲んでいる。

## 【0010】

シリコンからなるn<sup>+</sup>形のドレイン層1の上に第1のドリフト層5が形成されている。n<sup>+</sup>形のドレイン層1のn形不純物濃度は、例えば10<sup>19</sup>/cm<sup>3</sup>台であればよい。第1のドリフト層5は、シリコンからなるn<sup>-</sup>形の第1のエピタキシャル層2と、シリコンからなる第1のn形(第1導電形)ピラー層3と、シリコンからなる第1のp形(第2導電形)ピラー層4とを有する。n<sup>-</sup>形の第1のエピタキシャル層2は、第1の半導体層1よりもn形不純物濃度が低い低不純物濃度層であり、そのn形不純物濃度は例えば10<sup>13</sup>~10<sup>14</sup>/cm<sup>3</sup>であり、第1の半導体層1の上に形成される。第1のエピタキシャル層2よりもn形不純物濃度が高い第1のn形ピラー層3と第1のp形ピラー層4とが、第1のエピタキシャル層2中の素子部においてのみ、図中X方向(水平面に平行な第1の方向)に交互に繰り返し配置された第1のスーパージャンクションSJ1が形成されている。第1のn形ピラー層3のn形不純物量と第1のp形ピラー層4の不純物量とが等しくなるように形成される。第1のn形ピラー層3と第1のp形ピラー層4の不純物量が等しくなることで、逆バイアスが印加されたときに、両者が完全に空乏化されやすく、擬似的に低不純物濃度層と同じ働きをする。第1のエピタキシャル層2中の終端部においては、第1のn形ピラー層3及び第1のp形ピラー層4は、形成されていない。第1のエピタキシャル層2の終端部においては、第1のエピタキシャル層が低不純物濃度層としてそのまま配置される。

## 【0011】

第1のn形ピラー層3は、Y方向におけるn形不純物の濃度分布の中心に不純物濃度の極大値を有する複数の第1のn形層(第1導電形層)が、互いに結合して形成されている。その結合部では、n形不純物濃度が極小値を有する。すなわち、第1のn形ピラー層3は、Y方向に沿って不純物濃度の極大値と極小値を繰り返した不純物濃度分布を有する。上記n形層は、その中に不純物濃度の極大値を有する拡散層であり、イオン注入及び熱処理により形成される。本実施の形態では、第1のn形ピラー層3は、2つの第1のn形層から構成される。

## 【0012】

第1のp形ピラー層4は、Y方向におけるp形不純物の濃度分布の中心に不純物濃度の極大値を有する複数のp形層(第2導電形層)が互いに結合して形成されている。その結合部では、p形不純物濃度が極小値を有する。すなわち、p形ピラー層4は、Y方向に沿って不純物濃度の極大値と極小値を繰り返した不純物濃度分布を有する。上記p形層は、

10

20

30

40

50

その中心に不純物濃度の極大値を有する拡散層であり、イオン注入及び熱処理により形成される。本実施の形態では、第1のp形ピラー層4は、2つの第1のp形層から構成される。

#### 【0013】

本実施の形態では、一例として、第1のエピタキシャル層2の厚さは30μmである。第1のn形層の不純物濃度の極大値は、第1のエピタキシャル層2の表面から約5μmと約15μmの深さにあり、2つのn形層が拡散によりY方向に結合して第1のn形ピラー層3を形成している。p形層の不純物濃度の極大値は、第1のn形層同様に、第1のエピタキシャル層2の表面から例えば約5μmと約15μmの深さにあり、2つのp形層が拡散によりY方向に結合して第1のp形ピラー層4を形成している。第1のn形ピラー層3及び第1のp形ピラー層4の底部は、第1のn形層と、p形層の、拡散の程度によりきまり、第1のエピタキシャル層の表面から例えば約20～25μmの深さである。すなわち、第1のn形ピラー層3と第1のp形ピラー層4のY方向の厚さが約20～25μmである。

なお、第1のn形ピラー層3及び第1のp形ピラー層4は、設計に応じてn<sup>+</sup>ドレイン層1に達するように形成されてもよい。

#### 【0014】

第2のドリフト層8が、第1のドリフト層5の上に形成される。第2のドリフト層8は、それぞれシリコンからなる、n形の第2のエピタキシャル層6bと、第2のn形ピラー層6と、第2のp形ピラー層7と、第3のn形ピラー層6aと、第3のp形ピラー層7aと、を有する。n形の第2のエピタキシャル層6bは、第1のドリフト層5上に形成され、第1のエピタキシャル層2よりもn形不純物濃度が高く、例えば、10<sup>15</sup>～10<sup>16</sup>/cm<sup>3</sup>であり、厚さは、例えば20μmである。

#### 【0015】

第2のエピタキシャル層6b中の素子部において、第2のp形ピラー層7は、X方向に沿って第1のp形ピラー層と同じ間隔で離間配置され、第1のp形ピラー層と電気的に接続する。第2のn形ピラー層6は、隣り合う第2の第2導電形ピラー層7に挟まれた第2のエピタキシャル層6bからなり第1のn形ピラー層3と接続する。第2のn形ピラー層6と第2のp形ピラー層7とが素子部に第1の方向に繰り返し配置されることで第2のスーパージャンクションSJ2を形成している。両ピラー層は、第1のn形及びp形ピラー層と同様に、両ピラー層の不純物量が等しくなるように形成される。

#### 【0016】

第2のエピタキシャル層8中の終端部において、第3のp形ピラー層7aは、X方向に沿って離間配置され、第1のエピタキシャル層2上に配置される。第3のn形ピラー層6aは、隣り合う第3のp形ピラー層7aに挟まれた第2のエピタキシャル層6bからなり、第1のエピタキシャル層2上に配置される。第3のn形ピラー層6aと第3のp形ピラー層7aとが終端部に第1の方向に繰り返し配置されることで第3のスーパージャンクションSJ3を形成している。

#### 【0017】

両ピラー層は、第1のn形及びp形ピラー層と同様に、両ピラー層の不純物量が等しくなるように形成される。第2のp形ピラー層7及び第3のp形ピラー層7aは、第1のp形ピラー層4と同様に拡散層で形成することもできるが、本実施の形態では一例として、後述の製造方法の説明のように、それぞれ第2のエピタキシャル層6b中に形成されて第1のドリフト層に達する第1のトレンチと第2のトレンチとに埋め込んで形成された埋込層である。従って、第2のn形ピラー層6、第2のp形ピラー層7、第3のn形ピラー層6a、及び第3のp形ピラー層7aのY方向の厚さは、第2のエピタキシャル層6bと同じ厚さの20μmである。

#### 【0018】

また、本実施の形態では、第2のn形ピラー層6と第3のn形ピラー層6aとは、同じn形ピラー層であり、X方向における幅及び不純物量が同じである。第2のp形ピラー層

10

20

30

40

50

7と第3のp形ピラー層7aに関しても同様で、同じp形ピラー層であり、X方向における幅及び不純物量が同じである。

#### 【0019】

素子部では、p形ベース層9が第2のドリフト層8の表面に形成され、第2のp形ピラー層7に接続されている。素子部と終端部の境界には、p形ベース層9aが、第2のドリフト層8の表面に形成され、第2のp形ピラー層7に接続されていて、素子部のp形ベース層9よりもX方向の幅が広く形成されている。終端部には、p形ベース層9bが、ダイシングによりチップ端部となる部分に隣接して、第2のエピタキシャル層6bの表面に形成されている。p形ベース層9、9a、9bはシリコンからなる。

#### 【0020】

$n^+$ ソース層10が、素子部のp形ベース層9の表面に選択的に形成されている。 $n^+$ ソース層10aが、終端部のチップ端部に隣接してp形ベース層9bの表面に形成されている。 $n^+$ ソース層10、10aはシリコンからなる。ゲート電極14が、 $n^+$ ソース層10、p形ベース層9、及び第2のn形ピラー層6上に、ゲート絶縁膜12を介して形成されている。例えば、ゲート電極は、ポリシリコンで、ゲート絶縁膜は、シリコンの熱酸化膜で形成できる。

#### 【0021】

終端部では、p形ベース層9a、第3のn形ピラー層6a、第3のp形ピラー層7a、第2のエピタキシャル層6b、及びn形ソース層10a上に絶縁膜13が形成されている。絶縁膜13も、シリコンの熱酸化膜で形成可能である。ポリシリコンからなるゲート配線層15が、絶縁膜13上の終端部と素子部の境界部に形成される。ポリシリコンからなるチャネルストッパ層16が、絶縁膜13上の第3のn形ピラー層6a及び第3のp形ピラー層7aよりもチップ端部側に形成される。p<sup>+</sup>形コンタクト層11が、素子部のp形ベース層9上のn<sup>+</sup>形ソース層10間に形成される。p<sup>+</sup>形コンタクト層11aが、素子部と終端部の境界部のp形ベース層9a上に形成される。

#### 【0022】

層間絶縁膜17が、ゲート電極14、ゲート配線層15、及びチャネルストッパ層16上に形成され、ゲート電極14、ゲート配線層15、及びチャネルストッパ層16を外部から絶縁する。第1の開口部18が、隣り合うゲート電極14の間に、層間絶縁膜を貫通し素子部のp形ベース層9及びn<sup>+</sup>形ソース層10に達するように形成される。第2の開口部19が、素子部と終端部の境界部で、層間絶縁膜を貫通しp形ベース層9aに達するように形成される。

#### 【0023】

ソース電極25が層間絶縁膜13上に形成され、第1の開口部18を介してn<sup>+</sup>ソース層10及びp<sup>+</sup>形コンタクト層11と、第2の開口部19を介してp<sup>+</sup>形コンタクト層11aと電気的に接続される。ソース電極は、p<sup>+</sup>形コンタクト層11及びp<sup>+</sup>形コンタクト層11aを介して、p形ベース層9及びp形ベース層9aに電気的に接続される。ドレイン電極24が、n<sup>+</sup>形ドレイン層1の第1のドリフト層5と反対側の表面に形成され、n<sup>+</sup>形ドレイン層1と電気的に接続される。

#### 【0024】

ゲート金属配線層20が、層間絶縁膜13の開口部20を介してゲート配線層15に電気的に接続される。チャネルストッパ電極16が層間絶縁膜13の開口部21を介してチャネルストッパ層16と電気的に接続され、層間絶縁膜13の開口部22を介してn<sup>+</sup>形ソース層10aと電気的に接続される。これにより、チャネルストッパ層16、チャネルストッパ電極27、及びn<sup>+</sup>形ソース層10aは電気的に接続され、導電性の高いチップの端部を介してドレイン電極と同電位に維持される。

#### 【0025】

次に本実施形態にかかるMOSFET100の動作について説明する。ゲート電極14に閾値を超える電圧が印加されてMOSFET100がON状態になると、n<sup>+</sup>形ソース層10と第2のn形ピラー層6との間のp形ベース層9にはチャネル層が形成さる。ドレ

10

20

30

40

50

イン電極 24 にソース電極 25 に対して正電圧を印加すると、チャネル層を介してドレイン電極 24 からソース電極 25 に電流が流れる。

#### 【0026】

ゲート電極 14 に閾値より低い電圧が印加されると MOSFET 100 は OFF 状態となり、チャネル層が消失し電流は流れない。ドレイン・ソース間の電圧が上昇し、第 1 のドリフト層と第 2 のドリフト層は空乏化する。ドレイン・ソース間の電圧が、第 1 及び第 2 のドリフト層の耐圧を超えるとアバランシェ降伏が起こり、これにより生じた電子及び正孔は、それぞれ、ドレイン電極 24 及びソース電極 25 に排出される。素子部により生じた正孔は、第 1 の開口部 18 を介してソース電極 25 に排出され、終端部により生じた正孔は、素子部と終端部の境界にある第 2 の開口部 19 からソース電極 25 に排出される。第 2 の開口部 19 の方が、素子部の全体に形成されている第 1 の開口部 18 より、正孔による電流が流れる断面積が狭い。このため、素子部と終端部で耐圧が同じであると、終端部のアバランシェにより生じた正孔の電流により、素子部と終端部の境界部にある第 2 の開口部 19 で電流集中が発生し破壊しやすい。すなわち、終端部では耐量が低い。10

#### 【0027】

本実施の形態に係る MOSFET 100 は、ドリフト層を第 1 のドリフト層 5 と第 2 のドリフト層 8 の 2 断構造とし、それぞれのドリフト層の水平方向に n 形ピラー層と p 形ピラー層を交互に繰り返し配置したスーパージャンクション構造を備えている。第 2 ドリフト層 8 は、素子部と終端部のどちらにもスーパージャンクション構造を備えている。これに対して、第 1 のドリフト層 5 は、素子部にはスーパージャンクション構造を備えているが、終端部にはスーパージャンクション構造を備えていない。すなわち、第 1 のドリフト層 5 は、終端部には n ピラー層と p ピラー層が繰り返し配置されたスーパージャンクション構造の代わりに、n<sup>-</sup> のエピタキシャル層 2 が配置される。20

#### 【0028】

スーパージャンクション構造は、n 形ピラー層と p 形ピラー層の不純物量が等しくなるように形成し、擬似的に低濃度不純物層としているが、製造バラツキにより不純物量のバランスが崩れやすい。不純物量のバランスが崩れると、スーパージャンクション構造は、擬似的に n 形または p 形の不純物層となり、MOSFET が OFF 状態のときに、完全に空乏化しにくくなり耐圧が低下する。これに対し、n<sup>-</sup> のエピタキシャル層 2 は、MOSFET が OFF 状態のときは、完全に空乏化しやすいうように不純物が低濃度に設定されており、製造バラツキによる n<sup>-</sup> のエピタキシャル層 2 の空乏化への影響が少ない。製造バラツキに対して耐圧が安定している。30

#### 【0029】

ここで、第 1 のドリフト層 5 の素子部と終端部の両者にスーパージャンクションが形成されると、素子部と終端部で耐圧が同じなので、素子部のアバランシェの発生と同時に、終端部でのアバランシェが発生する。この場合、終端部の方がアバランシェの電流に対する耐量が低いので、終端部で MOSFET が破壊されてしまい、MOSFET の耐量は低い。しかし、本実施形態の MOSFET 100 では、第 1 のドリフト層の終端部には、製造バラツキに対して耐圧が安定している n<sup>-</sup> のエピタキシャル層 2 がスーパージャンクションの代わりに配置されているので、耐圧の低い素子部の SJ 1 でアバランシェが発生する。素子部の方がアバランシェに対する耐量が高いので、MOSFET 100 の耐量が向上する。40

#### 【0030】

MOSFET 100 では、第 1 のドリフト層と第 2 のドリフト層の厚さの和が耐圧をきめる。本実施の形態に係る MOSFET 100 は、耐圧が約 600 V を想定し、一例として、第 1 のドリフト層の厚さを 30 μm、第 1 の n 形ピラー層と p 形ピラー層は厚さ約 20 ~ 25 μm で 2 つの n 形層の結合で形成され、第 2 のドリフト層、第 2 の n 形ピラー層及び p 形ピラー層、第 3 の n 形ピラー層及び p 形ピラー層は、厚さ 20 μm で形成されている。しかしながら、これらの設定は耐圧に対する設計事項により変更されるものである。また、第 1 の n 形ピラー層 3 及び第 1 の p 形ピラー層 4 は、それぞれ Y 方向の 2 つの n50

形層と p 形層の結合で形成されているが、これも設計に応じて、3 つ以上の n 形層と p 形層の結合によりそれぞれ形成されていてもよい。

#### 【 0 0 3 1 】

本実施の形態に係る M O S F E T 1 0 0 では、第 1 のドリフト層中の第 1 の n 形ピラー層 3 と第 1 の p 形ピラー層 4 との不純物量とが等しく、第 2 のドリフト層中の第 2 の n 形ピラー層 6 と第 2 の p 形ピラー層 7 との不純物量とが等しく、及び第 2 のドリフト層中の n 形ピラー層 6 a と第 2 の p 形ピラー層 7 a との不純物量が等しく設定されていればよい。第 1 のドリフト層中の不純濃度と第 2 のドリフト層中の不純物濃度との高低関係は任意である。しかし、詳細な実施例による説明は省略するが、本実施形態の変形例に係る M O S F E T 1 0 1 として、第 2 のドリフト層のスーパージャンクション S J 2 、 S J 3 中の n 形及び p 形の不純物濃度が、第 1 のドリフトのスーパージャンクション S J 1 よりも高くすることもできる。例えば、各スーパージャンクション S J 1 、 S J 2 、 S J 3 中の n 形不純物量と p 形不純物量とのバランスがとれた状態 ( n 形と p 形の不純物量が互いに等しい等しい状態 ) で、スーパージャンクション S J 2 、 S J 3 の各 n 形ピラー層及び各 p 形ピラー層の不純物濃度がスーパージャンクション S J 1 の n 形ピラー層及び p 形ピラー層よりも高くして形成されることも可能である。10

#### 【 0 0 3 2 】

M O S F E T 1 0 0 が O F F になると、徐々にドレイン・ソース電圧が上昇していく。ドリフト層にスーパージャンクション構造を用いると、ドレイン・ソース間電圧が低い段階で急激にゲート・ドレイン容量  $C_{G D}$  が減少し、これが原因でゲート電極からノイズが発生する。上記のように第 2 ドリフト層中の n 形ピラー層と p 形ピラー層の不純物濃度を第 1 のドリフト層中よりも高くすることで、ドレイン・ソース間電圧の低い段階での第 2 のドリフト層の空乏化が抑制されるので、急激なゲート・ドレイン容量  $C_{G D}$  の減少が抑制される。この結果、本実施形態の変形例に係る M O S F E T 1 0 1 では、ゲートからのノイズの発生が抑制される。本変形例は、以後の実施形態でも適用可能である。20

#### 【 0 0 3 3 】

本実施の形態の係る M O S F E T 1 0 0 は、ドリフト層を第 1 のドリフト層と第 2 のドリフト層の 2 断構造とし、それぞれのドリフト層の水平方向に n ピラー層と p ピラー層を交互に繰り返し配置したスーパージャンクション構造を備えている。第 2 ドリフト層は、素子部と終端部のどちらにもスーパージャンクション構造を備えている。これに対して、第 1 のドリフト層は、素子部にはスーパージャンクション構造を備えているが、終端部にはスーパージャンクション構造を備えていない。すなわち、第 1 のドリフト層は、終端部において、n ピラー層と p ピラー層が繰り返し配置された構造の代わりに、n<sup>-</sup> のエピタキシャル層 2 が配置される。30

#### 【 0 0 3 4 】

後述の製造方法で説明するように、第 1 のドリフト層の n 形ピラー層 3 と p 形ピラー層 4 は、第 1 のエピタキシャル層 2 のエピタキシャル成長と n 形不純物及び p 形不純物のイオン注入を繰り返すマルチエビの手法により形成され、Y 方向における n 形不純物の濃度分布の中心に不純物濃度の極大値を有する複数の n 形拡散層及び p 形拡散層がそれぞれが互いに結合して形成されている。第 2 のドリフト層の p 形ピラー層 7 、 7 a は、それぞれ第 2 のエピタキシャル層 6 b に形成された第 1 及び第 2 のトレンチに埋込形成され、それに p 形ピラー層 7 、 7 a に挟まれた第 2 のエピタキシャル層 6 b が第 2 のドリフト層の n 形ピラー層 6 、 6 a として形成されている。この第 2 のドリフト層のようにトレンチに埋め込まれた p 形ピラー層で第 1 のドリフト層 5 のスーパージャンクション S J 1 を形成すると、n 形ピラー層は第 1 のエピタキシャル層 2 から形成されるので、第 1 のドリフト層の終端部に低不純物濃度の n<sup>-</sup> 形エピタキシャル層を形成することができない。また、第 1 のドリフト層 5 の n 形ピラー層 3 及び p 形ピラー層 4 をどちらもトレンチに埋め込まれたピラー層で形成すると、製造工程が複雑となり製造が困難である。さらに、第 2 のドリフト層 8 のスーパージャンクションの構造を、第 1 のドリフト層のスーパージャンクションを形成するマルチエビの手法を用いた拡散層で形成すると、製造工程が増大して製4050

造コストが増大してしまう。

#### 【0035】

本実施形態に係るMOSFET100では、第1のドリフト層の第1のスーパージャンクションを、複数のn形拡散層からなるn形ピラー層と複数のp形拡散層からなるp形ピラー層とで形成し、第2のドリフト層の第2及び第3のスーパージャンクションをトレーニに埋め込まれたp形ピラー層とこれに挟まれたn形ピラー層で形成している。このことが、容易な製造工程で、MOSFET100が、素子部に第1のスーパージャンクション構造SJ1を有し、終端部に低不純物濃度のエピタキシャル層2を有した第1のドリフト層5と、素子部と終端部にそれぞれ第2のスーパージャンクションSJ2及び第3のスーパージャンクションSJ3を有した第2のドリフト層8とを、有することを可能にしている。10

#### 【0036】

なお、本実施の形態に係るMOSFET100における、第2のドリフト層8の素子部の第2のn形ピラー層6と第2のp形ピラー層7と、終端部の第3のn形ピラー層6aと第3p形ピラー層7aとは、それぞれn形とp形の不純物量が互いに等しく形成されている。そして、第2のn形ピラー層6と第3のn形ピラー層6aとは、同じn形ピラー層であり、第2のp形ピラー層7と第3のp形ピラー層7aとは、同じp形ピラー層である。しかしながら、設計に応じて、第3のn形ピラー層6a及び第3のp形ピラー層7aは、各ピラー層のX方向の幅などを変えることで、それぞれ、第2のn形ピラー層6及び第2のp形ピラー層7との不純物量と異なって形成されても良い。20

#### 【0037】

次に、本実施の形態に係るMOSFET100の製造方法を、図3～図8を用いて説明する。図3～図8の各図は、本実施の形態に係るMOSFET100の製造工程を示す要部断面図である。各図は、図2の断面図をさらに簡略化し、素子部と終端部のそれぞれの要部を簡単に比較しながら説明する。

#### 【0038】

図3に示すように、n形不純物濃度が $10^{19} / \text{cm}^3$ 台のn<sup>+</sup>形シリコン基板をn<sup>+</sup>形のドレン層1とし、この上に、低不純物濃度( $10^{13} \sim 10^{14} / \text{cm}^3$ )のn<sup>-</sup>形の第1のエピタキシャル層2の一部(第1層)2aが、シリコンのエピタキシャル成長により形成される。n<sup>-</sup>形の第1のエピタキシャル層2の第1層2aの厚さは、15μmである。フォトレジスト31aが、n<sup>-</sup>形の第1のエピタキシャル層2の第1層2aの表面に形成され、素子部においてだけX方向に所定の間隔で離間した開口部を有する。p形不純物のボロン(B)が、イオン注入により、n<sup>-</sup>形の第1のエピタキシャル層2の第1層2aの表面に、上記フォトレジスト31aの開口部を介して注入され、ボロン注入層(第2導電形不純物層)34が形成される。イオン注入の条件は、例えば、ボロンのドーズ量が数 $10^{13} / \text{cm}^2$ 程度で、加速電圧は数100kV程度である。なお、イオン注入以外にも、ボロンの原料ガスを含んだ雰囲気中から気相拡散によりボロンを注入させること、または、ボロンを含んだ固体から固相拡散によりボロンを注入させることも可能である。30

#### 【0039】

次に図4に示すように、フォトレジスト31aを剥離した後に、別のフォトレジスト31bが、n<sup>-</sup>形の第1のエピタキシャル層2の第1層2aの表面に形成される。フォトレジスト31bは、素子部においてだけX方向に所定の間隔で離間し、それぞれの隣り合う上記ボロン注入層34の間に開口部を有する。n形不純物のリン(P)が、イオン注入により、n<sup>-</sup>形の第1のエピタキシャル層2の第1層2aの表面に、上記フォトレジスト31bの開口部を介して注入され、リン注入層(第1導電形不純物層)33が形成される。イオン注入の条件は、例えば、リンのドーズ量が数 $10^{13} / \text{cm}^2$ 程度で、加速電圧は数100kV程度である。なお、イオン注入以外にも、リンの原料ガスを含んだ雰囲気中から気相拡散によりリンを注入させること、または、リンを含んだ固体から固相拡散させることによりリンを注入させることも可能である。4050

## 【0040】

フォトレジスト31bを剥離した後に、図5に示したように、さらに、n<sup>-</sup>形の第1のエピタキシャル層2の第2層2bが、エピタキシャル成長により形成される。n<sup>-</sup>形の第1のエピタキシャル層2の第2層2bの厚さは、例えば10μmである。

## 【0041】

図6に示したように、n<sup>-</sup>形の第1のエピタキシャル層2の第2層2bの表面に、図3に示した上記フォトレジスト31aを介したイオン注入によるボロン注入層34の形成、及び図4に示したフォトレジスト31bを介したイオン中によるリン注入層33の形成が行われる。なお、MOSFETの耐圧を上げる設計に対応して、上記n<sup>-</sup>形の第1のエピタキシャル層2の第2層2bの形成、ボロン注入層34の形成、及びリン注入層33の形成を、単位工程として、この単位工程が複数回さらに繰り返されることも可能である。本実施の形態に係るMOSFET100は、この単位工程が1回行われて、二段構造のボロン注入層34とリン注入層33を有する。さらに、n<sup>-</sup>形の第1のエピタキシャル層2の第3層2cが、エピタキシャル成長により形成される。n<sup>-</sup>形の第1のエピタキシャル層2の第3層2cの厚さは、例えば5μmである。以上により、n<sup>-</sup>形の第1のエピタキシャル層2中に、2段のボロン注入層34とリン注入層33が、X方向に沿って交互に配置されて形成された構造を備えた、第1のドリフト層5が形成される。n<sup>-</sup>形の第1のエピタキシャル層2の厚さは、合計30μm形成され、ボロン注入層34とリン注入層33は、n<sup>-</sup>形の第1のエピタキシャル層2の表面から、深さ5μm及び15μmの位置に形成される。

10

20

## 【0042】

次に、n形の第2のエピタキシャル層6bが、第1のドリフト層5上にシリコンのエピタキシャル成長により形成される。n形の第2のエピタキシャル層6bの厚さは、例えば20μmであり、n形不純物濃度は、例えば、10<sup>15</sup>~10<sup>16</sup>/cm<sup>3</sup>である。図7に示したように、フォトレジスト35が、n形の第2のエピタキシャル層6bの表面上に形成され、素子部と終端部にそれぞれ後述の第2及び第3のp形ピラー層の形成される位置に対応させてX方向に離間配置された開口部を有する。なお、本実施形態にかかるMOSFET100は、第2及び第3のp形ピラー層は同じp形ピラー層を有するので、上記の素子部及び終端部でのX方向の開口幅は同じ幅である。

## 【0043】

30

n形の第2のエピタキシャル層6bが、上記フォトレジスト35の開口部を介して、RIE(Reactive Ion Etching)によりエッティングされる。この結果、n形の第2のエピタキシャル層6bの素子部に第1のトレンチが、終端部に第2のトレンチが、それぞれ、n形の第2のエピタキシャル層6bを貫通し、第1のドリフト層5に達するように形成される。

## 【0044】

フォトレジスト35を剥離した後に、図8に示したように、p形のシリコン層が、n形の第2のエピタキシャル層6bに形成された第1のトレンチと第2のトレンチに、エピタキシャル成長により埋込まれる。この結果、素子部には、第1のトレンチに埋め込まれた第2のp形ピラー層7が形成され、終端部には、第2のトレンチに埋め込まれた第3のp形ピラー層7aが形成される。隣り合う第2のp形ピラー層で挟まれたn形の第2のエピタキシャル層6bは、第2のn形ピラー層6であり、隣り合う第3のp形ピラー層7aで挟まれたn形の第2のエピタキシャル層6bは、第3のn形ピラー層6aである。なお、上記トレンチが埋め込まれるp形シリコンのエピタキシャル成長のp形不純物のドーピング条件は、第2及び第3のp形ピラー層中のp形不純物量が、それぞれ第2及び第3のn形ピラー層のn形不純物量と同じとなるように決められる。以上により、n形の第2のエピタキシャル層6b中に、第2のn形ピラー層6と、第2のp形ピラー層7と、第3のn形ピラー層6aと、第3のp形ピラー層7aを有する、第2のドリフト層8が形成される。

40

## 【0045】

50

続いて図示しない工程において熱処理工程が行われる。この熱処理工程にて、第1のドリフト層中の2段のリン注入層33は、それぞれ、その中のリン原子が拡散して広がりそれがn形拡散層となり、Y方向で互いに結合する。この結果、n形拡散層がY方向に連結した第1のn形ピラー層3が、第1のドリフト層5中に形成される。同様にして、第1のドリフト層中の2段のボロン注入層34は、それぞれ、その中のボロン原子が拡散して広がりそれがp形拡散層となり、Y方向で互いに結合する。この結果、p形拡散層がY方向に連結した第1のp形ピラー層4が、第1のドリフト層5中に形成される。また、第1のn形ピラー層3は、第2のn形ピラー層6とリンの拡散により連結され、第2のp形ピラー層4は、第2のp形ピラー層7とボロンの拡散により連結される。

## 【0046】

10

以上により、第1のスーパージャンクション構造SJ1が、第1のドリフト層中の素子部に形成され、n<sup>+</sup>形の第1のエピタキシャル層2が、終端部に形成される。また、第2のスーパージャンクションSJ2及び第3のスーパージャンクションSJ3が、それぞれ第2のドリフト層8中の素子部及び終端部に形成される。

## 【0047】

以後は、図示による詳細な説明は省略するが、通常のMOSFETの素子部を形成する製造工程が行われる。例えば、絶縁膜13が熱酸化により終端部の第2ドリフト層8上に形成される。素子部の隣り合うp形ベース層9の間で、n<sup>+</sup>形ソース層10、p形ベース層9及び第2のn形ピラー層6上に、ゲート絶縁膜12を介してゲート電極14がポリシリコンで形成される。ゲート電極14と同一工程にて、ゲート配線層15及びチャネルストップ層16がポリシリコンで形成される。ゲート絶縁膜12、ゲート電極14、ゲート配線層15、絶縁膜13、及びチャネルストップ層16上に、シリコン酸化膜の層間絶縁膜17がCVD(Chemical Vapor Deposition)等で形成される。その後、層間絶縁膜17の素子部のゲート電極14間に第1の開口部18が、層間絶縁膜17の素子部と終端部の境界部に第2の開口部19が、p形ベース層9とn<sup>+</sup>形ソース層10に達するようにそれぞれ形成される。また、ゲート配線層15に達する開口部20、チャネルストップ層16に達する開口部21、p形ベース層9bに達する開口部22、及びチップ端部に開口部23が形成される。p形ベース層9が素子部に、p形ベース層9aが素子部と終端部の境界部に、及びp形ベース層9bがチップ端部に、それぞれ同一工程のp形不純物の拡散により形成される。p形不純物のイオン注入のドーズ量は、例えば10<sup>13</sup>/cm<sup>2</sup>台とすることができる。続いて、n<sup>+</sup>形ソース層10が素子部に、n<sup>+</sup>形ソース層10aがチップ端部に、n形不純物の拡散により形成される。n形不純物のイオン注入のドーズ量は、例えば10<sup>15</sup>/cm<sup>2</sup>台とすることができる。

20

## 【0048】

30

ドレン電極24が、n<sup>+</sup>形ドレン層1に電気的に接続するように形成される。ソース電極25が、第1の開口部と第2の開口部を介して、p形ベース層9とn<sup>+</sup>形ソース層10に電気的に接続するように形成される。ゲート金属配線層26が、開口部20を介してゲート配線層に電気的に接続するよう形成される。チャネルストップ電極27が、開口部21及び開口部22を介して、それぞれチャネルストップ層及びn<sup>+</sup>形ソース層10aに電気的に接続されるように形成される。ドレン電極24、ソース電極25、ゲート金属配線層26、及びチャネルストップ電極27は、金属材料であればよく、例えば、アルミニウム、銅、金などを用いることができる。

40

## 【0049】

以上説明した製造方法を用いることで、図1及び図2に記載の本実施の形態に係るMOSFET100を製造することができる。なお、上記製造方法の説明の中で、第2のp形ピラー層7及び第3のp形ピラー層7aが、それぞれ第1及び第2のトレンチに、p形のシリコン層がエピタキシャル成長で埋め込まれて形成される工程を説明した。ここで、第1及び第2のトレンチのアスペクト比が高すぎる場合に、第2のp形ピラー層7及び第3のp形ピラー層7a内にボイドが形成されることがある。この場合は、第1及び第2のトレンチのX方向の幅が、第2の電極側に向かって(第1の電極から離れるほど)広くなる

50

構造としてもよい。こうすることで、p形のシリコン層がエピタキシャル成長によりトレンチ内に良好に埋め込まれるようになるので、第2のp形ピラー層7及び第3のp形ピラー層7a内のボイドの発生を抑制できる。

#### 【0050】

(第2の実施の形態)

第2の実施の形態に係るMOSFET200を、図9を用いて説明する。図9は、第2の実施の形態に係る電力用半導体装置の要部断面図である。なお、第1の実施の形態で説明した構成と同じ構成の部分には同じ参照番号または記号を用いその説明は省略する。第1の実施の形態との相異点について主に説明する。

#### 【0051】

本実施の形態に係る電力用半導体装置は、第1の実施の形態同様のMOSFETであり、そのチップ上面図は、図1に示した第1の実施の形態に係るMOSFET100と同じである。図9は、図1に示したA-Aに沿った断面図である。本実施の形態に係るMOSFET200は、以下の点で第1の実施形態に係るMOSFET100と相異する。MOSFET200は、チップ端部において、n形のピラー層3aが、n<sup>-</sup>形の第1のエピタキシャル層2中にさらに形成されており、Y方向におけるn形不純物の濃度分布の中心に、n形不純物濃度の極大値を有する2つの第2のn形層がY方向に互いに結合して形成されている。その結合部では、n形不純物濃度が極小値を有する。すなわち、ピラー層3aは、Y方向に沿って不純物濃度の極大値と極小値を繰り返した不純物濃度分布を有する。上記第2のn形層は、その中心に不純物濃度の極大値を有する拡散層であり、イオン注入及び熱処理により形成される。このピラー層3aは、第2のドリフト層中の第2のエピタキシャル層6bに接続し、p形ベース層9bの直下に配置される。ピラー層3aの第2のn形層は、第1のn形ピラー層3を構成する第1のn形層と同様に拡散層であり、第1のn形層と一緒に形成されることができる。つまり、第2のn形層は、第1のエピタキシャル層2中に第1のn形層と表面から同じ深さの位置に極大値を有する。これ以外は、第1の実施の形態に係るMOSFET100と同じ構造である。

#### 【0052】

また、製造方法も第1の実施の形態に係るMOSFETと同じ製造方法で製造することができる。図4及び図6に示された製造工程において、MOSFET200の第1のドリフト層の第1のn形ピラー層3を形成する際に、チップ端部に隣接する位置にフォトレジスト31bの開口部をさらに設けることで、第1のn形ピラー層3の第1のn形層と同時に、ピラー層3aの第2のn形層を形成することができる。すなわち、図4及び図6に示された工程において、ピラー層3aの第2のn形層を形成するためのリン注入層(第2のn形不純物層)が、第1のn形ピラー層の第1のn形層を形成するリン注入層33とともに、チップ端部にY方向に二段形成される。この後の熱処理で、リンが拡散して、第2のn形層がY方向に結合したn形ピラー層3aが形成される。

#### 【0053】

本実施形態のMOSFET200においても、ドリフト層を第1のドリフト層と第2のドリフト層の2断構造とし、それぞれのドリフト層の水平方向にnピラー層とpピラー層を交互に繰り返し配置したスーパージャンクション構造を備えている。第2ドリフト層は、素子部と終端部のどちらにもスーパージャンクション構造を備えている。これに対して、第1のドリフト層は、素子部にはスーパージャンクション構造を備えているが、終端部には、nピラー層とpピラー層が繰り返し配置されたスーパージャンクション構造の代わりに、n<sup>-</sup>のエピタキシャル層2が配置される。ドリフト層が上記第1のドリフト層5及び第2のドリフト層8から構成されることで、第1の実施の形態に係るMOSFET100と同様に、本実施形態に係るMOSFET200も、アバランシェに対する耐量が高い素子部でアバランシェを起こさせてるので、MOSFET100の耐量が向上する。

#### 【0054】

さらに、本実施形態に係るMOSFET200においても、上記第1のドリフト層5の第1のスーパージャンクションSJ1を、複数のn形拡散層からなるn形ピラー層3と複

10

20

30

40

50

数の p 形拡散層からなる p 形ピラー層 4 とで形成し、上記第 2 のドリフト層 8 の第 2 及び第 3 のスーパージャンクション SJ2、SJ3 をトレンチに埋め込まれた p 形ピラー層とこれに挟まれた n 形ピラー層とで形成している。これにより、本実施の形態に係る MOSFET200 は、第 1 の実施の形態に係る MOSFET100 と同様に、容易な製造工程で製造されることができる。

#### 【0055】

さらに、本実施の形態に係る MOSFET200 は、第 1 のエピタキシャル層 2 のチップ端部に隣接して、n 形のピラー層 3a が形成されている。MOSFET200 が OFF 状態の時に、ドレイン・ソース電極間の電圧が上昇するとともに、空乏層が素子部からチップ端部に向かって広がっていく。n 形のピラー層 3a は、この空乏層がチップ端部に達することを防ぐことで、チップ端部でのリーク電流を防止する。このため、本実施形態の係る MOSFET200 は、第 1 の実施形態に係る MOSFET100 に比べて、チップ端部での破壊が起こりにくく、信頼性が高い。10

#### 【0056】

以上、本発明の実施の形態を説明したが、各実施形態や変形例で説明した特徴は、それ組み合わせて実施することも可能である。また、大電力用半導体装置として、MOSFET を例にして説明したが、これに限定されることなく、SBD (Schottky Barrier Diode) や IGBT (Insulated Gate Bipolar Transistor) などの他の大電力用半導体装置のドリフト層に対して適用することが可能である。例えば、SBD の場合は、図 2 に示した構造で、素子部にゲート電極とゲート絶縁膜を設げずに、第 2 のドリフト層の表面で、ソース電極が第 2 の n 形ピラー層 6 とショットキー接合するように形成することで SBD が提供される。SBD の場合は、図 2 中のゲート配線層 15 は、フィールドプレート電極として作用することができる。また、IGBT の場合、図 2 の構造の n<sup>+</sup> 形ドレイン層 2 とドレイン電極 24との間に、p<sup>+</sup> 形コレクタ層を設けることで、IGBT が提供される。20

#### 【0057】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。30

#### 【符号の説明】

#### 【0058】

- 1 n<sup>+</sup> 形ドレイン層

- 2、2a、2b、2c n<sup>-</sup> 形エピタキシャル層

- 3 第 1 の n 形ピラー層

- 3a ピラー層

- 4 第 2 の p 形ピラー層

- 5 第 1 のドリフト層

- 6 第 2 の n 形ピラー層

- 6a 第 3 の n 形ピラー層

- 6b n 形エピタキシャル層

- 7 第 2 の p 形ピラー層

- 7a 第 3 の p 形ピラー層

- 8 第 2 のドリフト層

- 9、9a、9b p 形ベース層

- 10、10a n<sup>+</sup> 形ソース層

- 11、11a、11b p<sup>+</sup> コンタクト層

- 12 ゲート絶縁膜

4050

- 1 3 絶縁膜

1 4 ゲート電極

1 5 ゲート配線層

1 6 チャネルストップ層

1 7 チャネルストップ電極

1 8 第1の開口部

1 9 第2の開口部

2 0 ~ 2 3 開口部

2 4 ドレイン電極

2 5 ソース電極

2 6 ゲート金属配線層 10

2 7 フィールドストップ電極

3 1 a、3 1 b、3 5 レジストマスク

3 3 リン注入層

3 4 ボロン注入層

1 0 0、2 0 0 M O S F E T

S J 1 第1のスーパー・ジャンクション

S J 2 第2のスーパー・ジャンクション

S J 3 第3のスーパー・ジャンクション

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

---

フロントページの続き

(72)発明者 入船 裕行

東京都港区芝浦一丁目1番1号 株式会社東芝内

審査官 柴山 将隆

(56)参考文献 特表2001-522145 (JP, A)

特開2007-335844 (JP, A)

特開2007-036213 (JP, A)

特開2007-243092 (JP, A)

特開2007-067447 (JP, A)

特開2007-012858 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 29/78

H01L 21/336