(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

**(19) World Intellectual Property Organization**

International Bureau

A standard linear barcode is located at the bottom of the page, spanning most of the width. It is used for tracking and identification of the document.

**(43) International Publication Date

11 August 2011 (11.08.2011)**

(10) International Publication Number

**WO 2011/096276 A1**

(51) International Patent Classification:

*G02F 1/1368* (2006.01)    *G09F 9/30* (2006.01)

*G02F 1/1333* (2006.01)    *G09F 9/35* (2006.01)

*G02F 1/1343* (2006.01)    *H01L 29/786* (2006.01)

**(21) International Application Number:** PCT/JP2011/050906

**(22) International Filing Date:** 13 January 2011 (13.01.2011)

**(25) Filing Language:** English

**(26) Publication Language:** English

(30) Priority Date: 2010-024643 5 February 2010 (05.02.2010) JP

(71) *Applicant (for all designated States except US): SEMICONDUCTOR ENERGY LABORATORY CO., LTD.*

[JP/JP]; 398, Hase, Atsugi-shi, Kanagawa, 2430036 (JP).

(72) **Inventor; and**

(75) **Inventor/Applicant (for US only): YAMAZAKI, Shun-pei [JP/JP]; c/o SEMICONDUCTOR ENERGY LABORATORY CO., LTD., 398, Hase, Atsugi-shi, Kanagawa, 2430036 (JP).**

(81) **Designated States** (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PE, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(84) **Designated States** (*unless otherwise indicated, for every kind of regional protection available*): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

**Published:**

— with international search report (Art. 21(3))

**(54) Title: LIQUID CRYSTAL DISPLAY DEVICE**

FIG. 1A

**(57) Abstract:** In a reflective liquid crystal display device, a space where a pixel electrode is not provided between adjacent pixels causes a decrease in proportion of a display region in a pixel (i.e., aperture ratio). As a result, the reflective liquid crystal display device has a problem in that contrast and luminance of display images are decreased. An object is to provide a liquid crystal display device which displays an image with high contrast and high luminance. In the liquid crystal display device, an end portion of a pixel electrode is provided to overlap with an end portion of an adjacent pixel electrode with an insulating layer interposed therebetween so that a space between adjacent pixels is narrowed; thus, the proportion of a display region in a pixel is increased.

## DESCRIPTION

**LIQUID CRYSTAL DISPLAY DEVICE**5 **TECHNICAL FIELD**

[0001]

The present invention relates to a reflective display device, particularly relates to a liquid crystal display device provided with a plurality of pixel electrodes that reflect external light.

10

**BACKGROUND ART**

[0002]

With the development of the information society, portable information devices such as phones, computers, and digital cameras have been widely used. There are 15 limitations on weight and volume of a portable information device so that the information device is carried. In particular, the proportion of weight and volume of a battery is high in an information device; thus, the capacity of the battery is limited.

[0003]

In order to provide a portable information device having a battery with limited 20 capacity that can be used for a long time, it is necessary to use components and devices with less power consumption for the portable information devices. As an example of the display device with less power consumption, a reflective liquid crystal display device is given.

[0004]

25 Since in a reflective liquid crystal display device, a backlight is not used and external light is utilized for display, the power consumption of the liquid crystal display device is low. As an example of the reflective liquid crystal display device, a display device in which a reflective electrode is provided with a texture structure formed including a material with a low refractive index and a light-reflecting film formed 30 including a material with a high refractive index is formed thereover has been invented (see Patent Document 1).

[Reference]

[0005]

[Patent Document 1] Japanese Published Patent Application No. 2000-2875

## DISCLOSURE OF INVENTION

5 [0006]

In a reflective liquid crystal display device, images are displayed using external light; thus, a space where a pixel electrode is not provided between adjacent pixels causes a decrease in proportion of a display region in a pixel (i.e., aperture ratio). As a result, the reflective liquid crystal display device has a problem in that contrast and 10 luminance of display images are decreased.

[0007]

The present invention is made in view of the foregoing technical background. Therefore, an object of one embodiment of the present invention is to provide a liquid crystal display device which displays an image with high contrast and high luminance.

15 [0008]

In order to achieve the above object, the following may be performed: in a liquid crystal display device, an end portion of a pixel electrode is provided to overlap with an end portion of an adjacent pixel electrode with an insulating layer interposed therebetween so that a space between adjacent pixels is narrowed; thus, the proportion 20 of a display region in a pixel is increased.

[0009]

That is, one embodiment of the present invention is a liquid crystal display device including an insulating layer; a first pixel electrode and a second pixel electrode each electrically connected to a switching element; a counter electrode facing the first 25 pixel electrode and the second pixel electrode; and a liquid crystal layer between the first and second pixel electrodes and the counter electrode. Further, in the liquid crystal display device, an end portion of the second pixel electrode overlies an end portion of the first pixel electrode with the insulating layer interposed therebetween.

[0010]

30 Another embodiment of the present invention is the above liquid crystal display device in which the insulating layer extends from the end portion of the second pixel electrode, overlies a top surface of the first pixel electrode, and is colored.

## [0011]

Another embodiment of the present invention is the above liquid crystal display device in which the insulating layer covers a side surface of the second pixel electrode overlying the top surface of the first pixel electrode.

## 5 [0012]

Another embodiment of the present invention is the above liquid crystal display device in which a transistor including an oxide semiconductor is used as the switching element.

## [0013]

10 Another embodiment of the present invention is a liquid crystal display device including a first insulating layer; a second insulating layer; a first pixel electrode, a second pixel electrode, and a third pixel electrode each electrically connected to a switching element; a counter electrode facing the first pixel electrode, the second pixel electrode, and the third pixel electrode; and a liquid crystal layer between the first, second, and third pixel electrodes and the counter electrode. Further, in the liquid crystal display device, a transistor including an oxide semiconductor is used as the switching element; the first, second, and third pixel electrodes adjoin one another with the second pixel electrode interposed between the first pixel electrode and the third pixel electrode; one end portion of the second pixel electrode overlies an end portion of 15 the first pixel electrode with the first insulating layer interposed therebetween; and the other end portion of the second pixel electrode underlies an end portion of the third pixel electrode with the second insulating layer interposed therebetween.

20

## [0014]

Another embodiment of the present invention is a liquid crystal display device 25 including a first insulating layer; a second insulating layer; a first pixel electrode, a second pixel electrode, and a third pixel electrode each electrically connected to a switching element; a counter electrode facing the first pixel electrode, the second pixel electrode, and the third pixel electrode; and a liquid crystal layer between the first, second, and third pixel electrodes and the counter electrode. Further, in the liquid 30 crystal display device, a transistor including an oxide semiconductor is used as the switching element; the first, second, and third pixel electrodes adjoin one another with the second pixel electrode interposed between the first pixel electrode and the third

pixel electrode; one end portion of the second pixel electrode overlies an end portion of the first pixel electrode with the first insulating layer interposed therebetween; and the other end portion of the second pixel electrode overlies an end portion of the third pixel electrode with the second insulating layer interposed therebetween.

5 [0015]

Another embodiment of the present invention is a liquid crystal display device including a first insulating layer; a second insulating layer; a first pixel electrode, a second pixel electrode, and a third pixel electrode each electrically connected to a switching element; a counter electrode facing the first pixel electrode, the second pixel 10 electrode, and the third pixel electrode; and a liquid crystal layer between the first, second, and third pixel electrodes and the counter electrode. Further, in the liquid crystal display device, a transistor including an oxide semiconductor is used as the switching element; the first, second, and third pixel electrodes adjoin one another with the second pixel electrode interposed between the first pixel electrode and the third 15 pixel electrode; one end portion of the second pixel electrode underlies an end portion of the first pixel electrode with the first insulating layer interposed therebetween; and the other end portion of the second pixel electrode underlies an end portion of the third pixel electrode with the second insulating layer interposed therebetween.

[0016]

20 Another embodiment of the present invention is the above liquid crystal display device including the pixel electrode and a photo sensor electrically connected to the transistor including an oxide semiconductor over one substrate; and a black matrix between the pixel electrode and the photo sensor.

[0017]

25 Note that in this specification, an off-state current is a current which flows between a source electrode and a drain electrode when a transistor is off. For example, in the case of an n-channel transistor, the off-state current refers to a current which flows between a source electrode and a drain electrode when the gate voltage is lower than the threshold voltage of the transistor.

30 [0018]

According to the present invention, a liquid crystal display device displaying an image with high contrast and high luminance can be provided.

**BRIEF DESCRIPTION OF DRAWINGS****[0019]**

In the accompanying drawings:

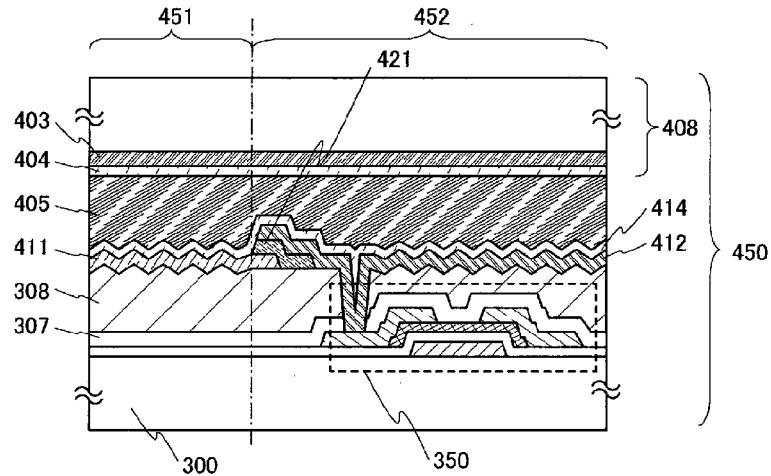

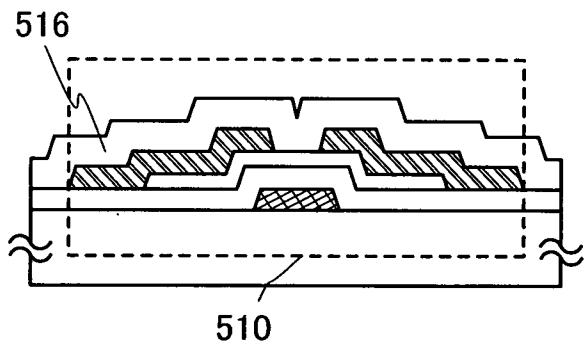

5 FIGS. 1A and 1B are cross-sectional views each illustrating a pixel portion according to an embodiment;

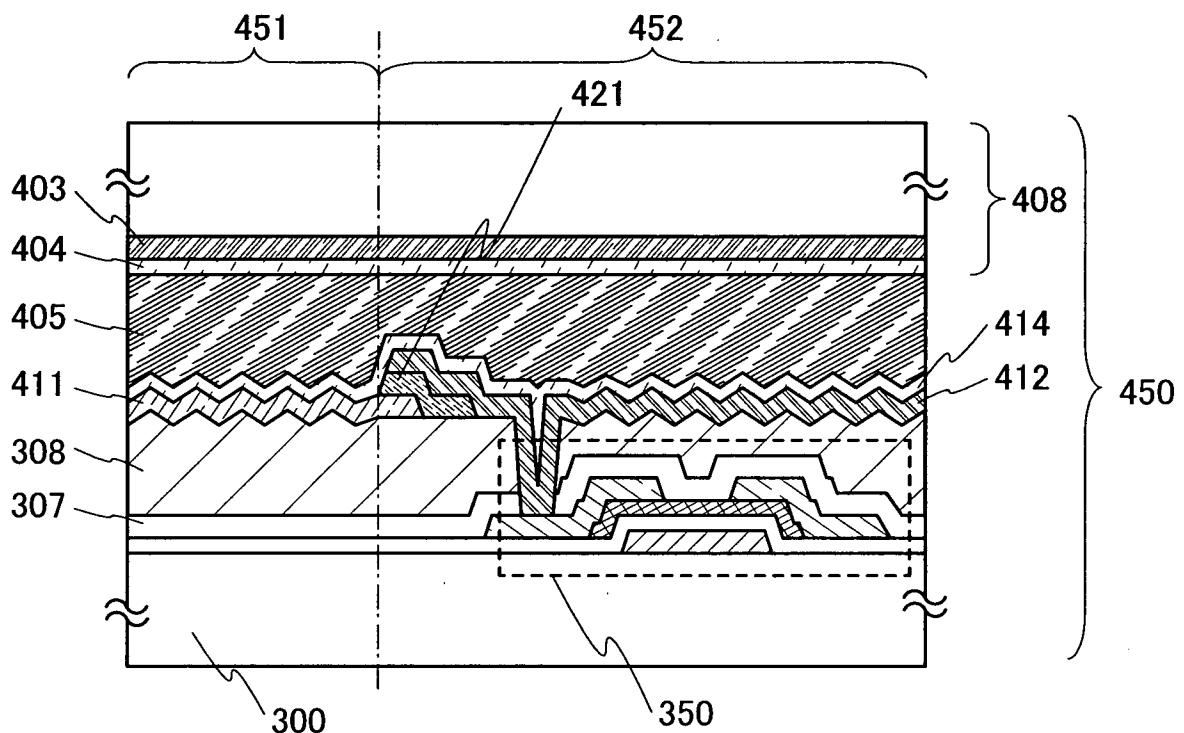

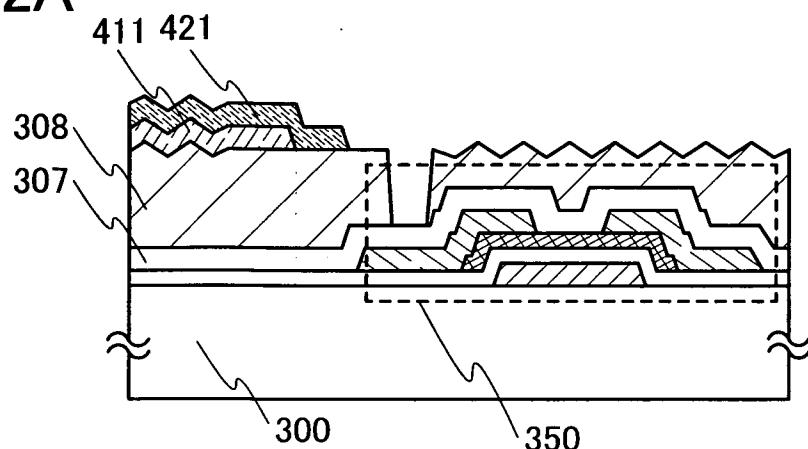

FIGS. 2A to 2C are cross-sectional views illustrating a process for manufacturing a pixel portion according to the embodiment;

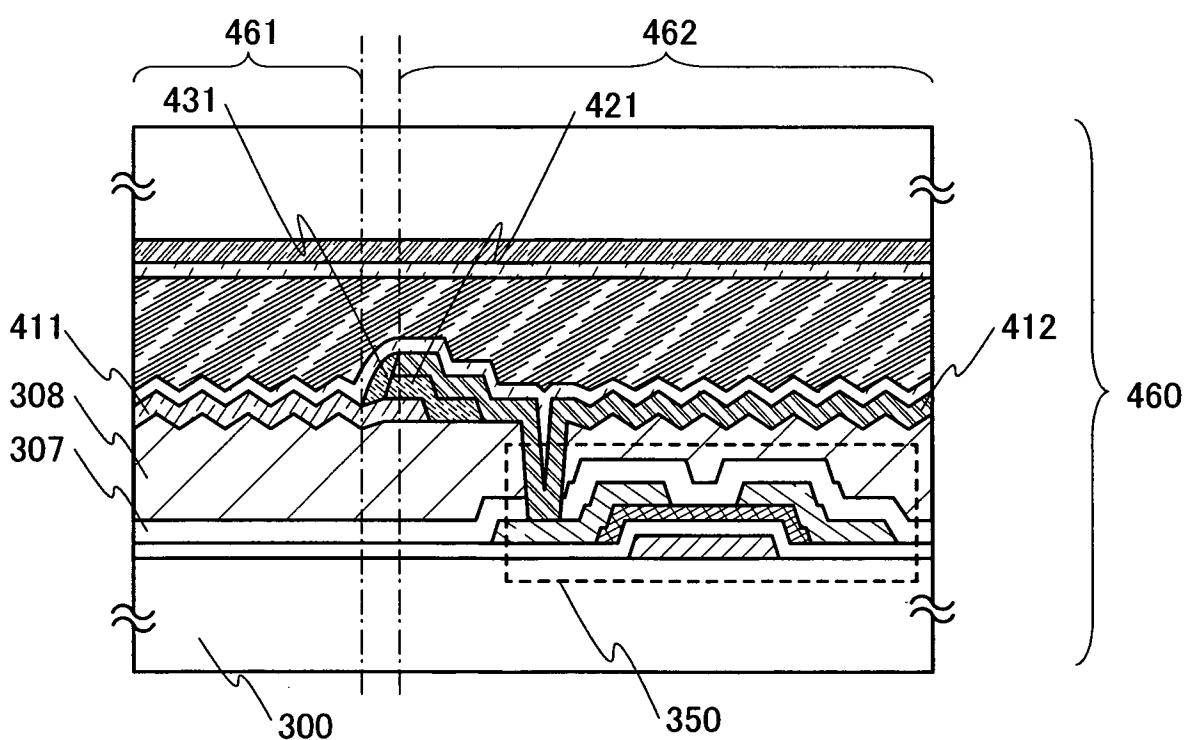

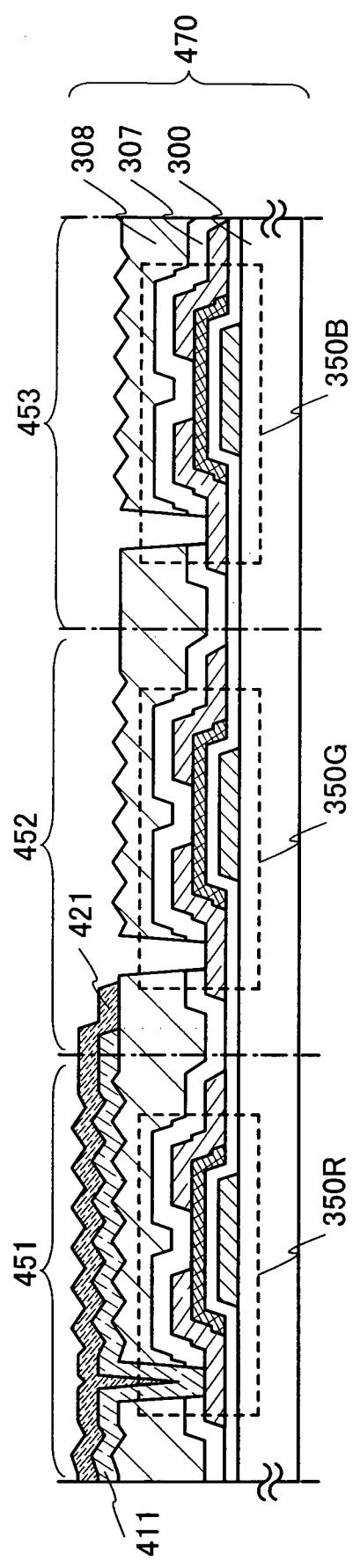

10 FIGS. 3A and 3B are top views each illustrating a pixel portion according to an embodiment;

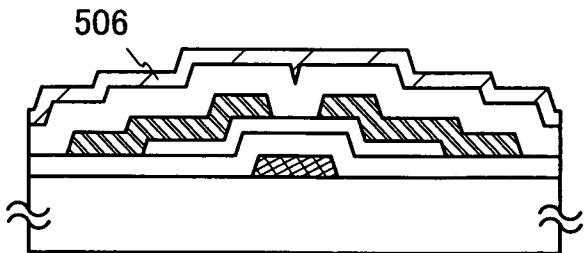

FIG. 4 is a cross-sectional view illustrating a pixel portion according to the embodiment;

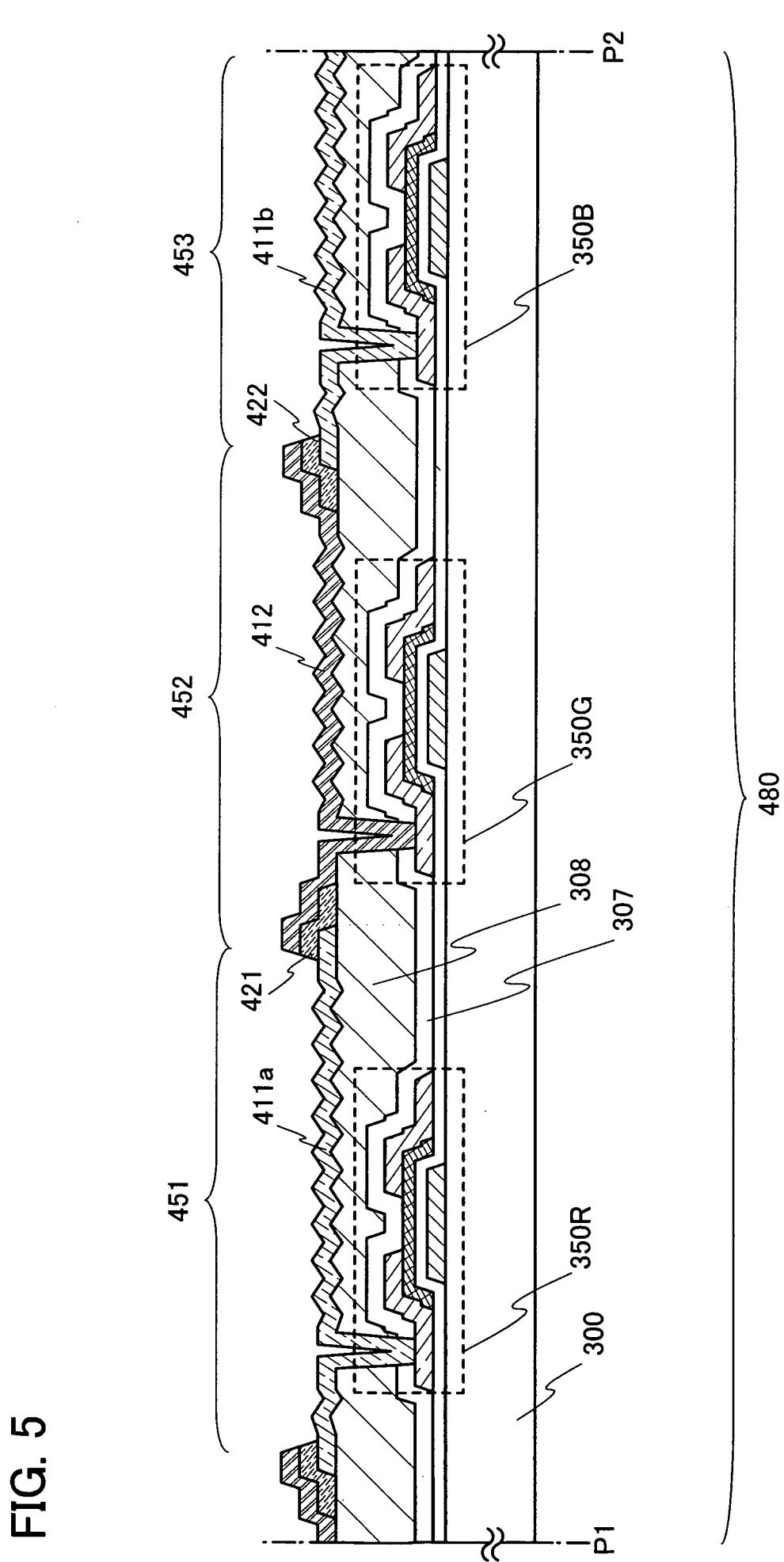

FIG. 5 is a cross-sectional view illustrating a pixel portion according to the embodiment;

15 FIGS. 6A and 6B are cross-sectional views illustrating a process for manufacturing a pixel portion according to the embodiment;

FIGS. 7A and 7B are cross-sectional views illustrating a process for manufacturing a pixel portion according to the embodiment;

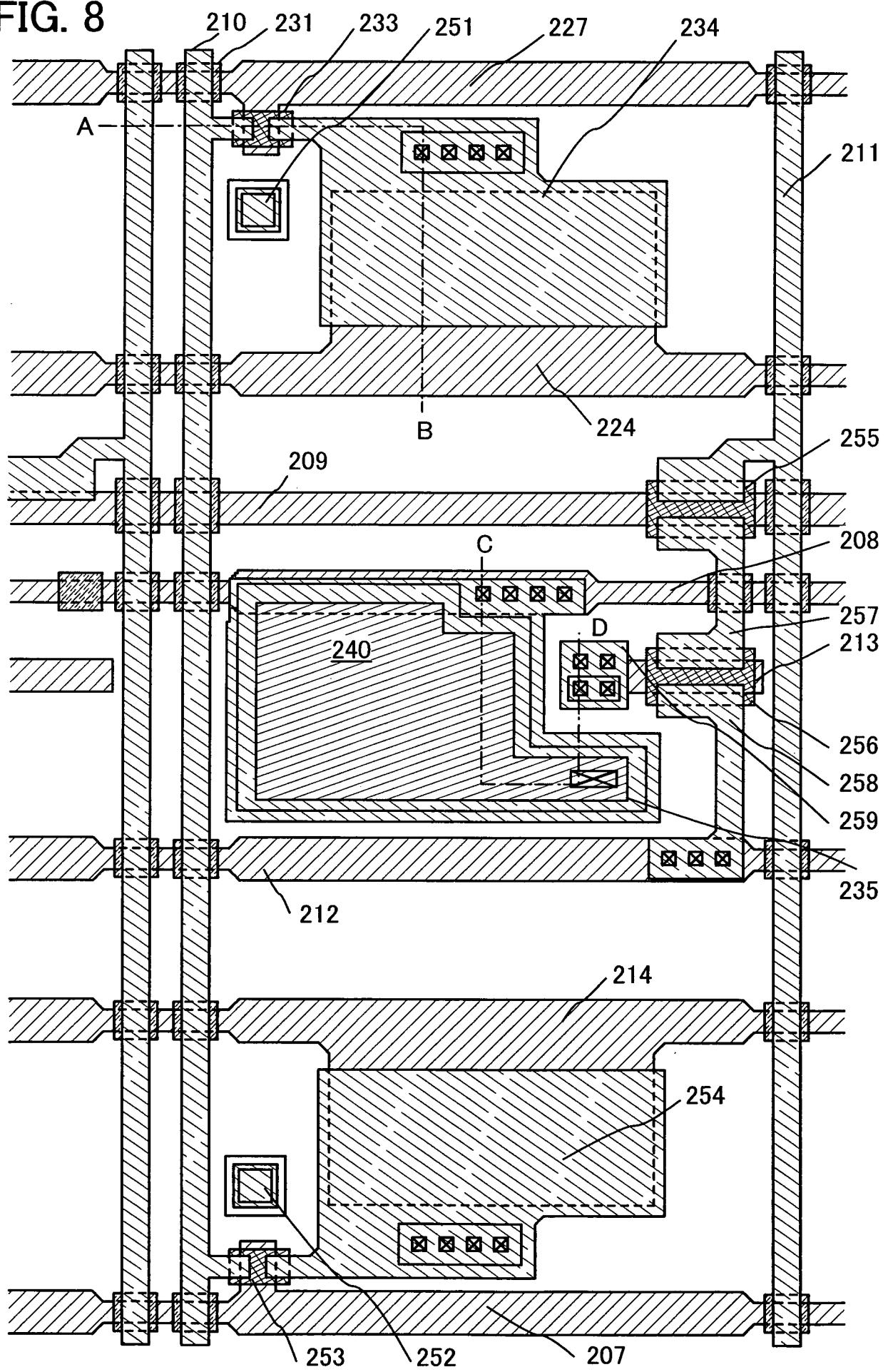

FIG. 8 is a top view illustrating a pixel portion according to an embodiment;

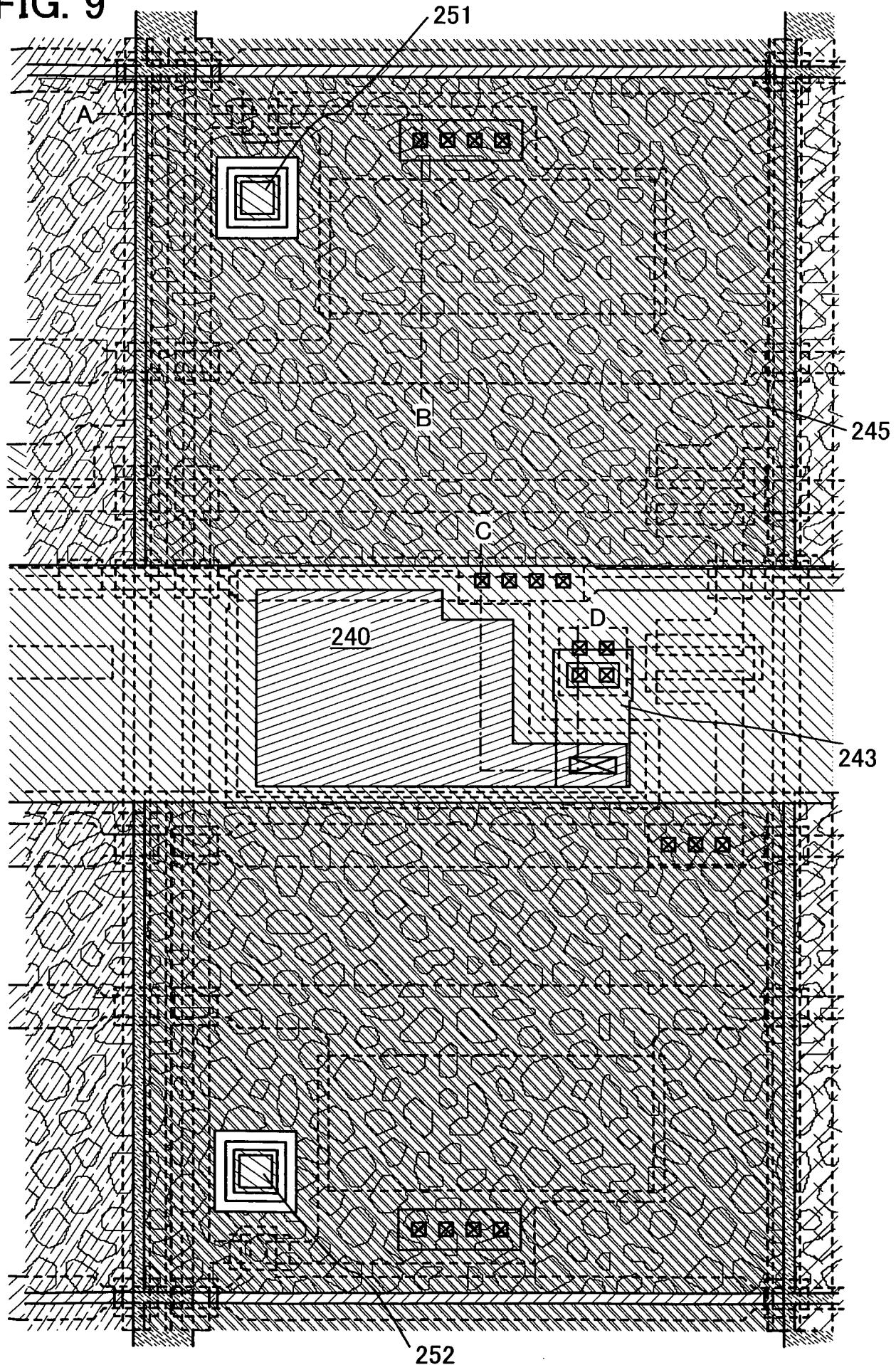

20 FIG. 9 is a top view illustrating a pixel portion according to the embodiment;

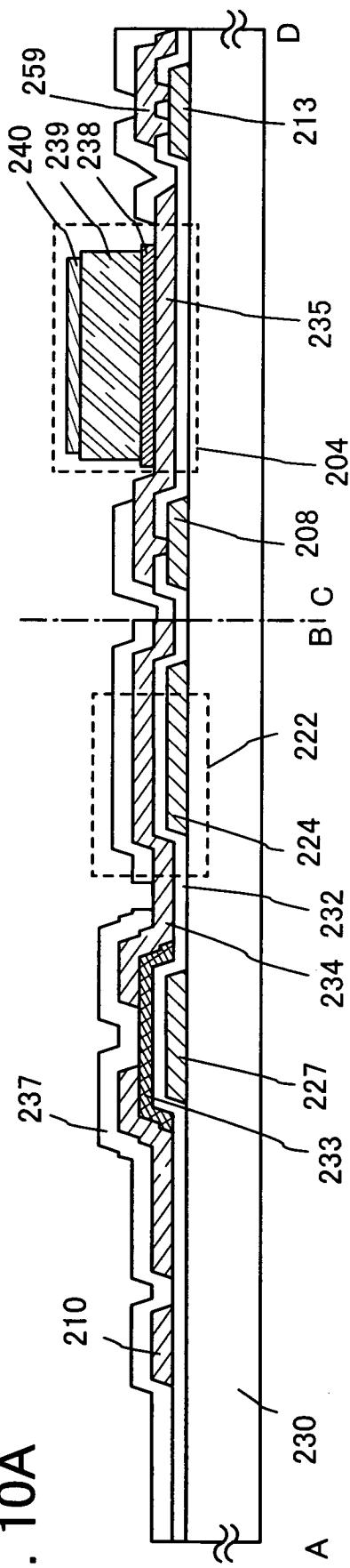

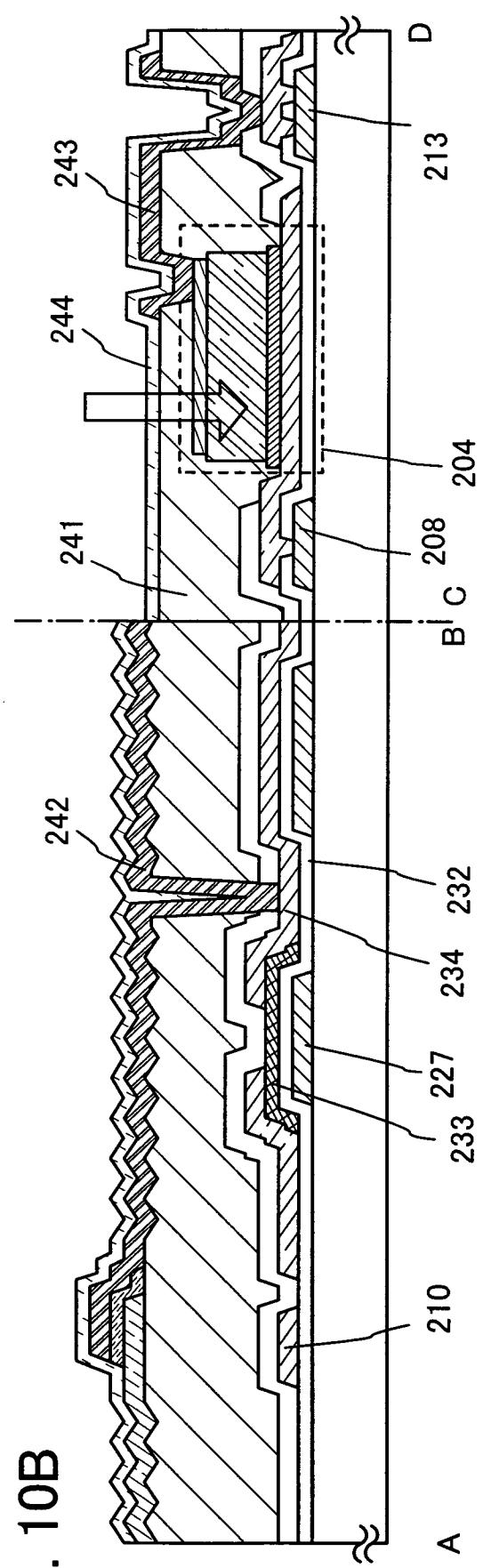

FIGS. 10A and 10B are cross-sectional views illustrating a pixel portion according to the embodiment;

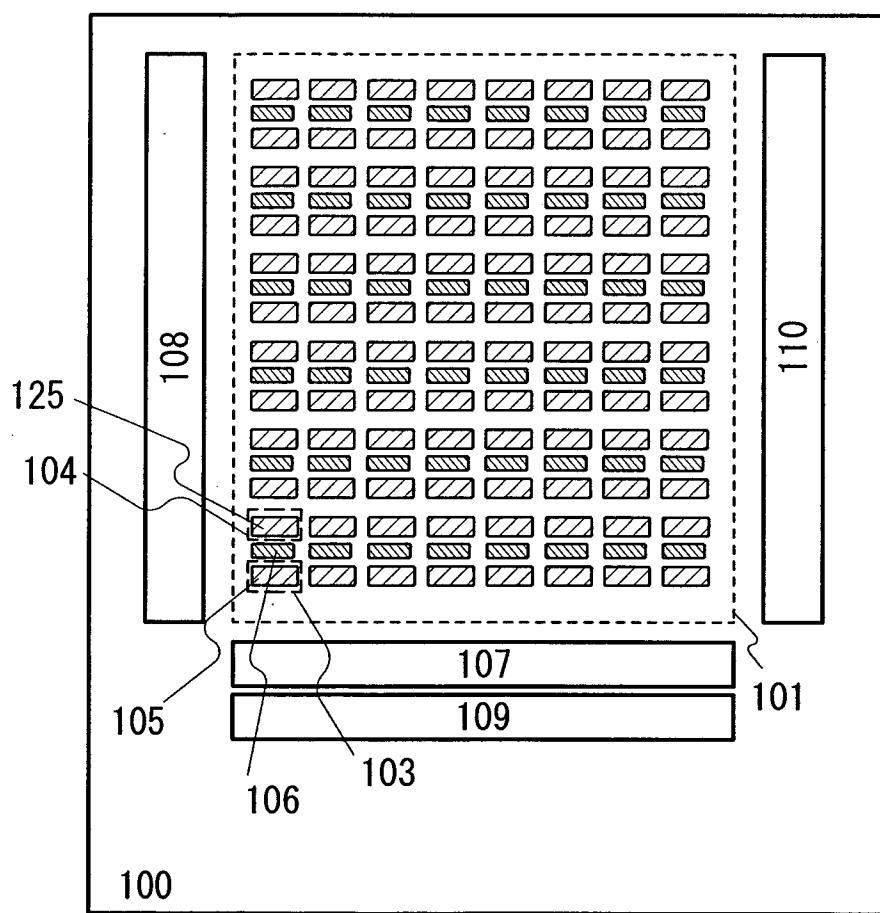

FIG. 11 is a block diagram illustrating a liquid crystal display device according to an embodiment;

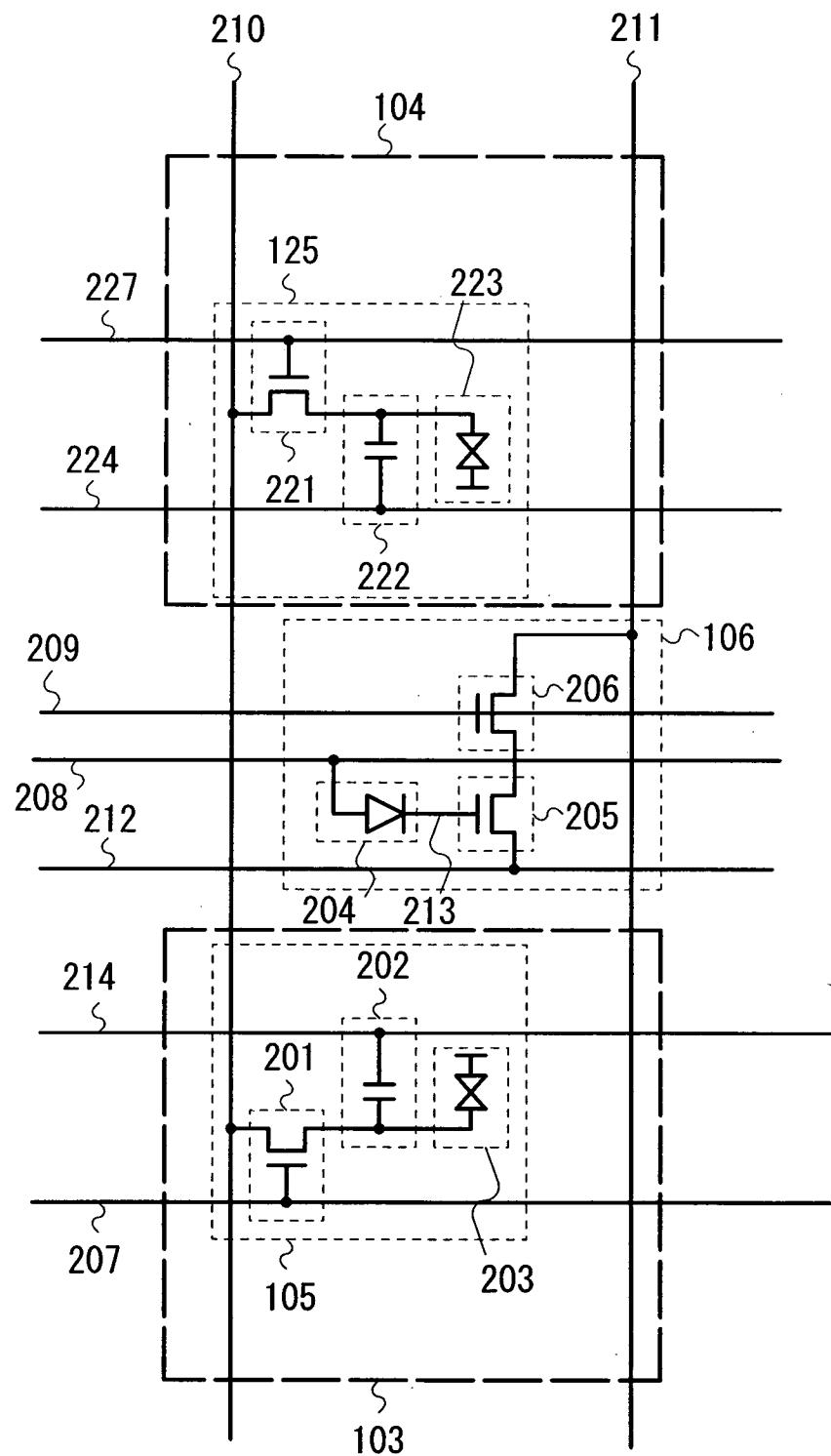

25 FIG. 12 is an equivalent circuit diagram illustrating a liquid crystal display device according to the embodiment;

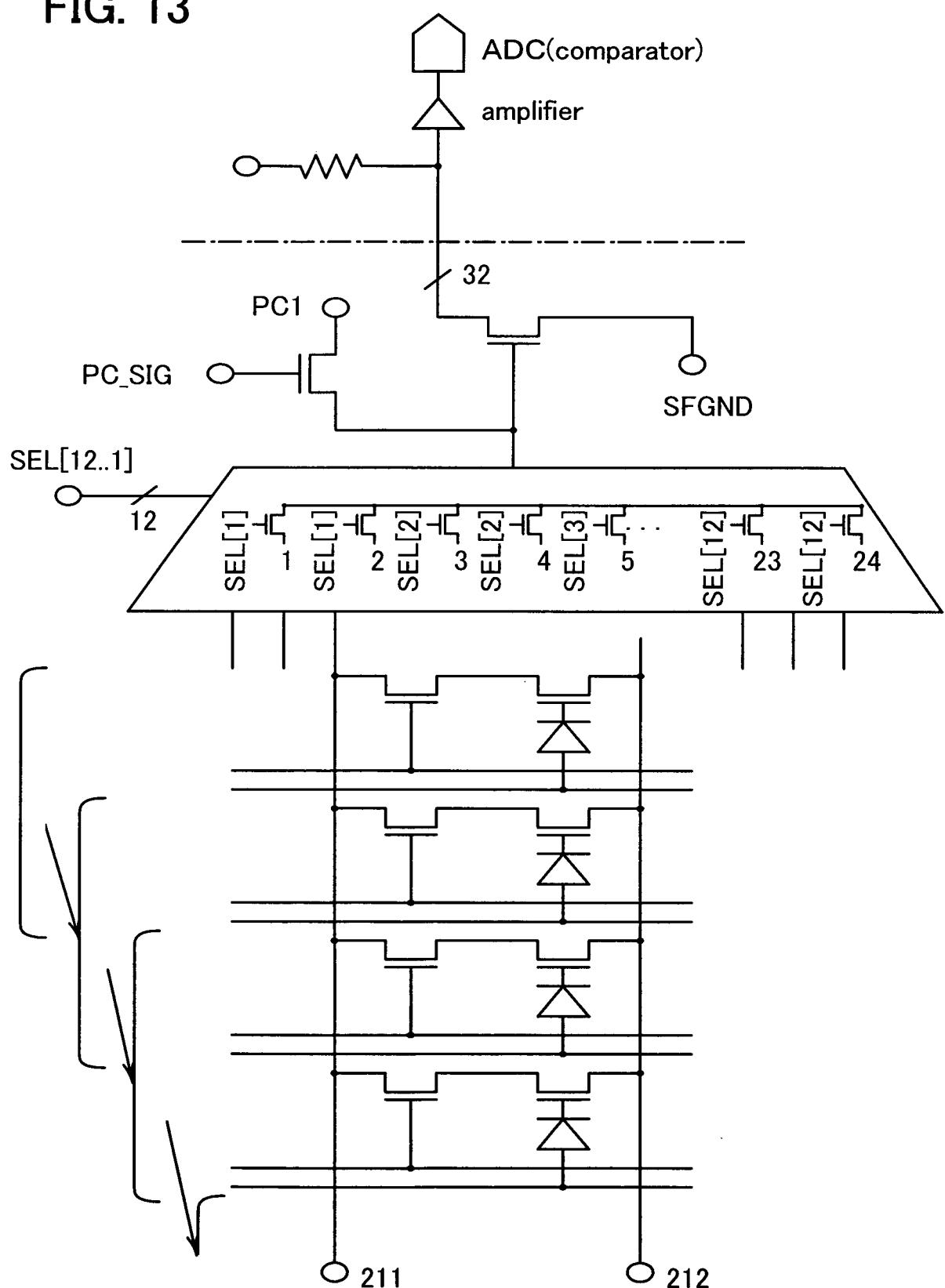

FIG. 13 is a schematic view illustrating a driver circuit of a photo sensor according to the embodiment;

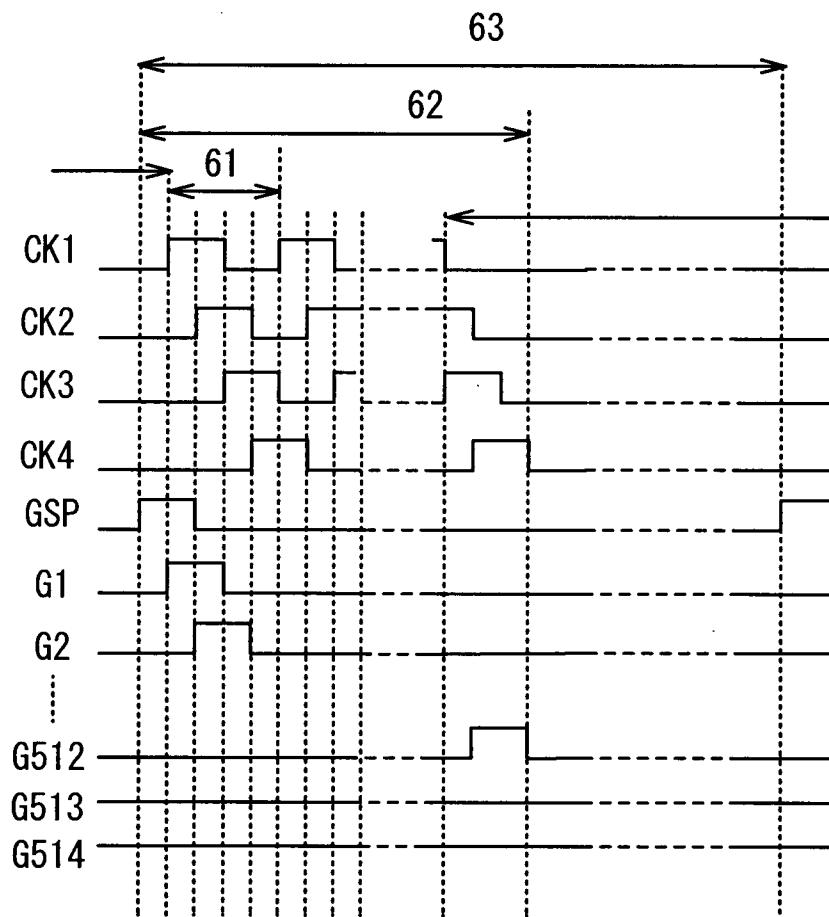

30 FIG. 14 is a timing chart of a liquid crystal display device according to the embodiment;

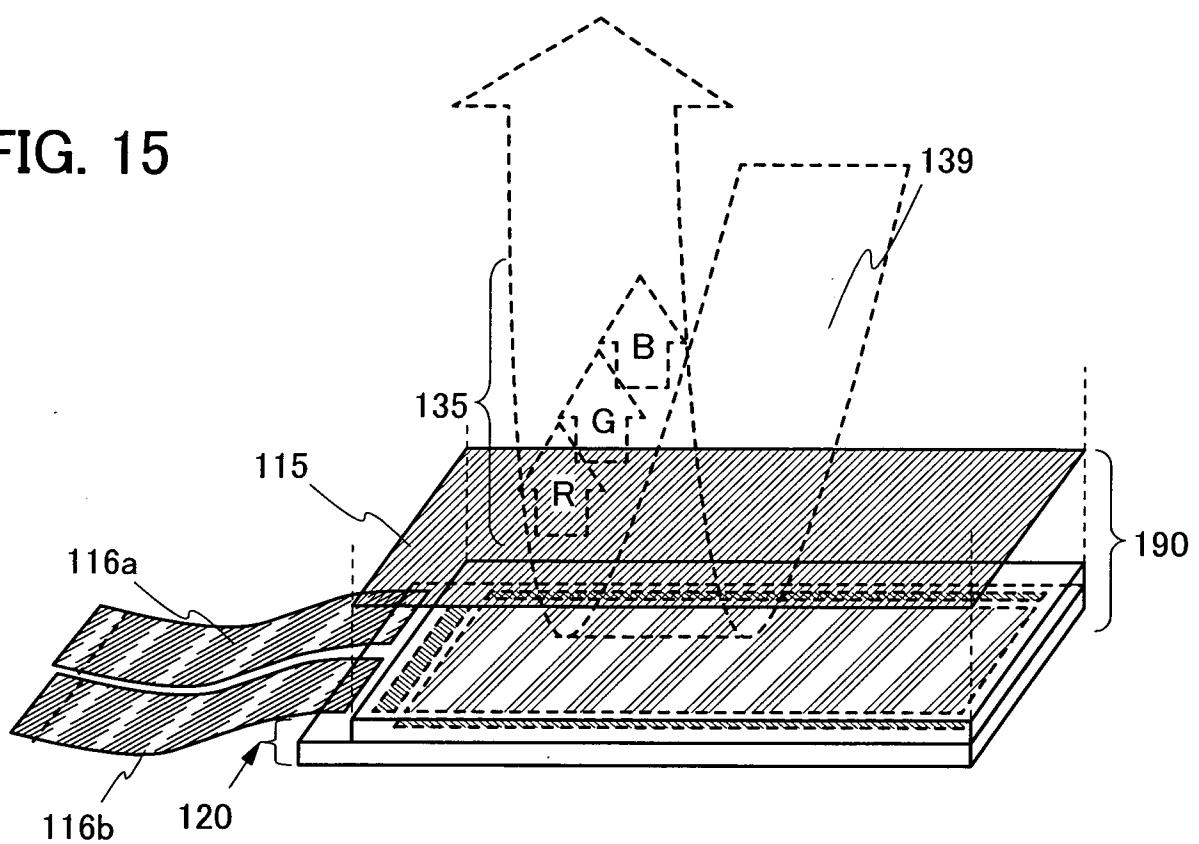

FIG. 15 is a diagram illustrating a liquid crystal display device according to an embodiment;

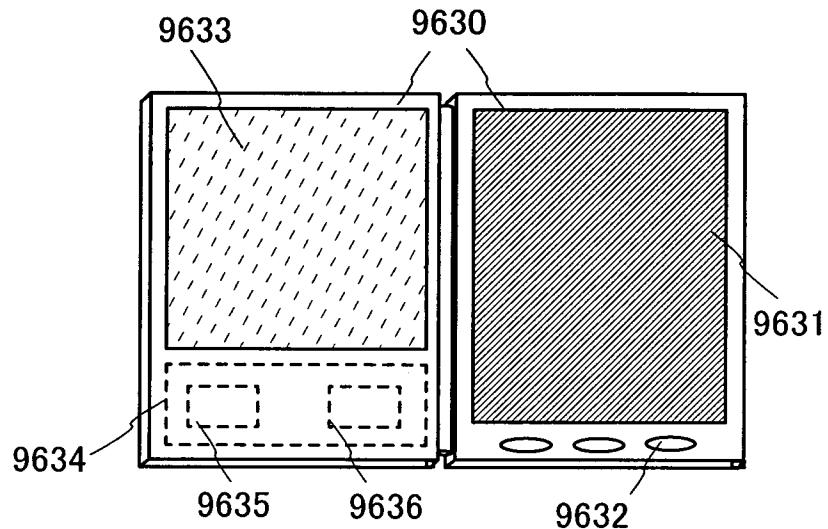

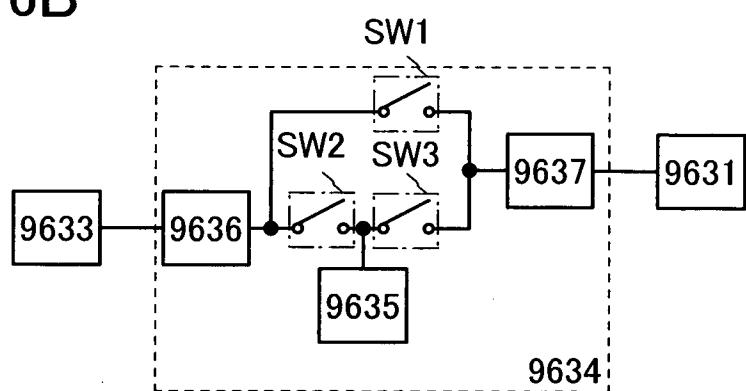

FIGS. 16A and 16B illustrate a liquid crystal display device according to an embodiment;

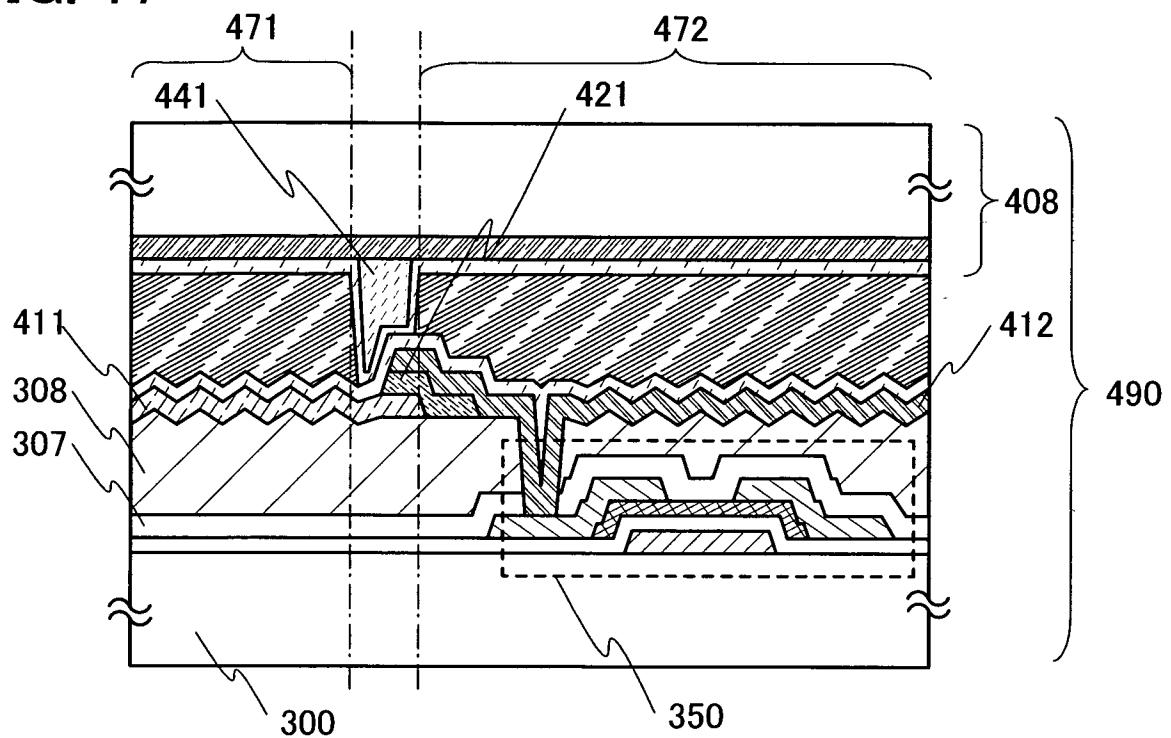

FIG. 17 is a cross-sectional view illustrating a pixel portion according to the embodiment;

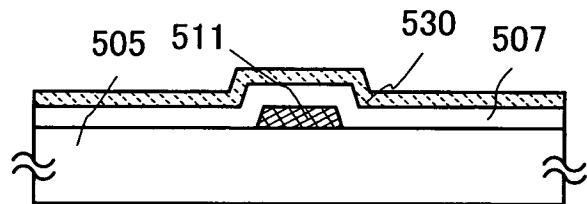

5 FIGS. 18A to 18E are cross-sectional views illustrating an example of a transistor including an oxide semiconductor layer and a manufacturing method thereof;

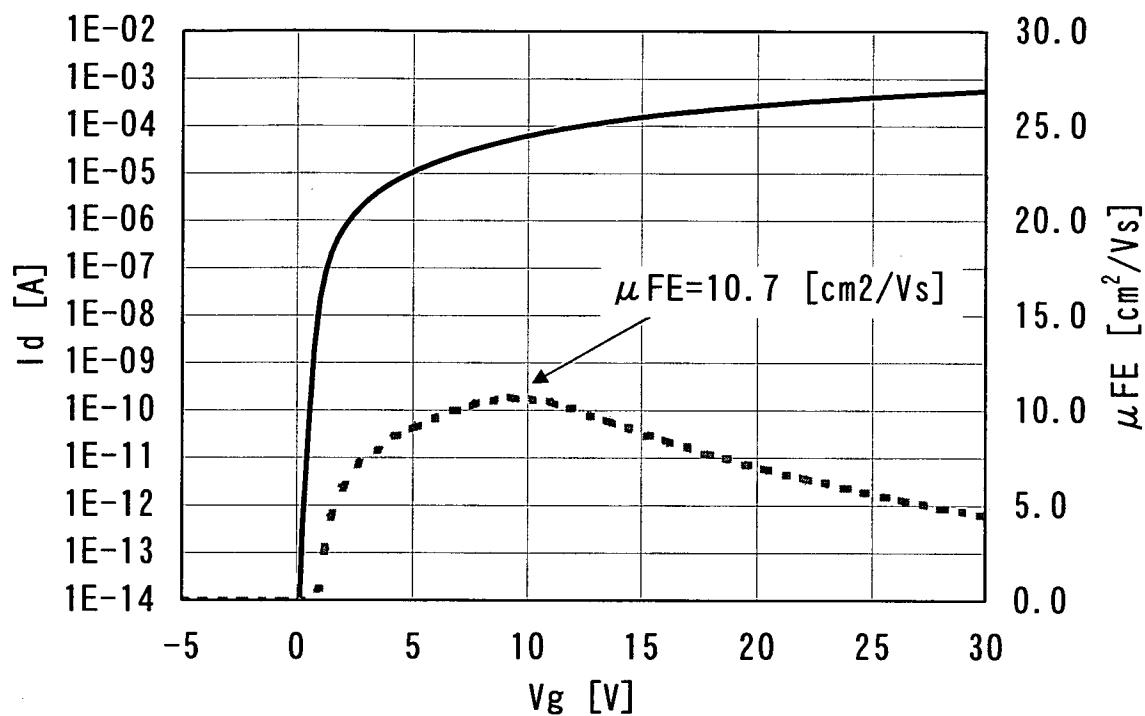

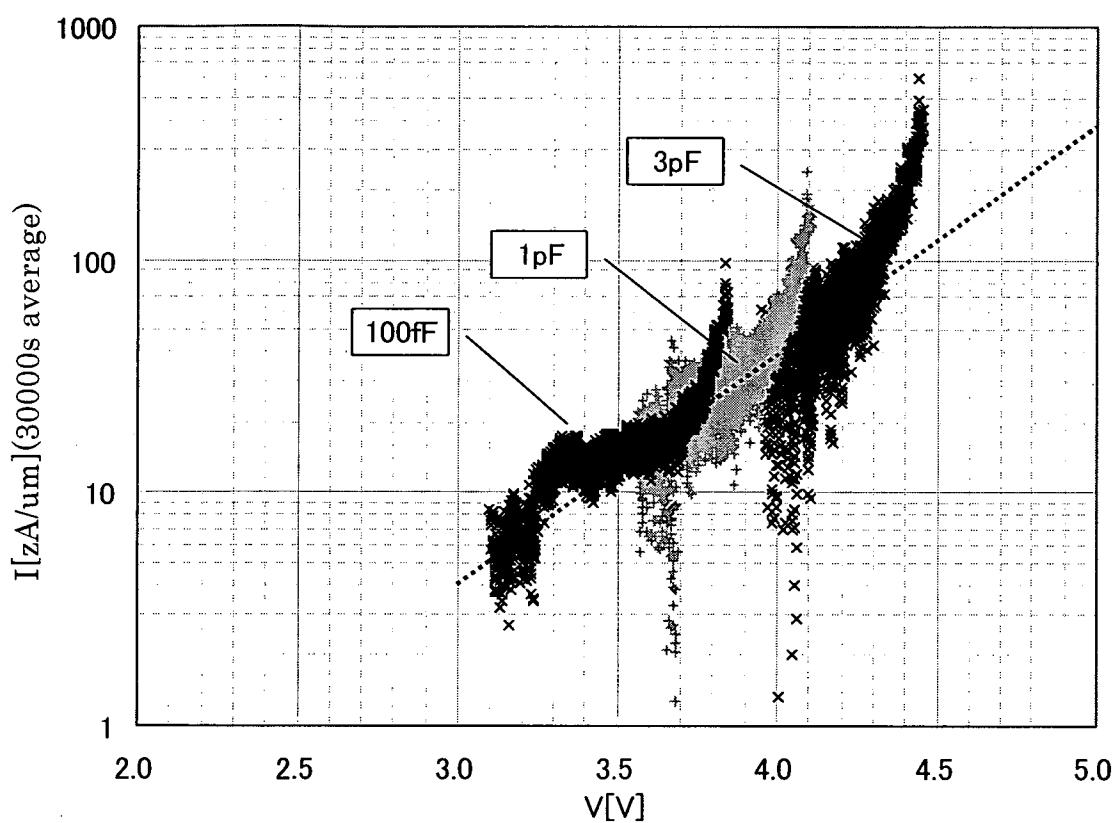

FIG. 19 is a graph showing  $V_g$ - $I_d$  characteristics of a transistor including an oxide semiconductor;

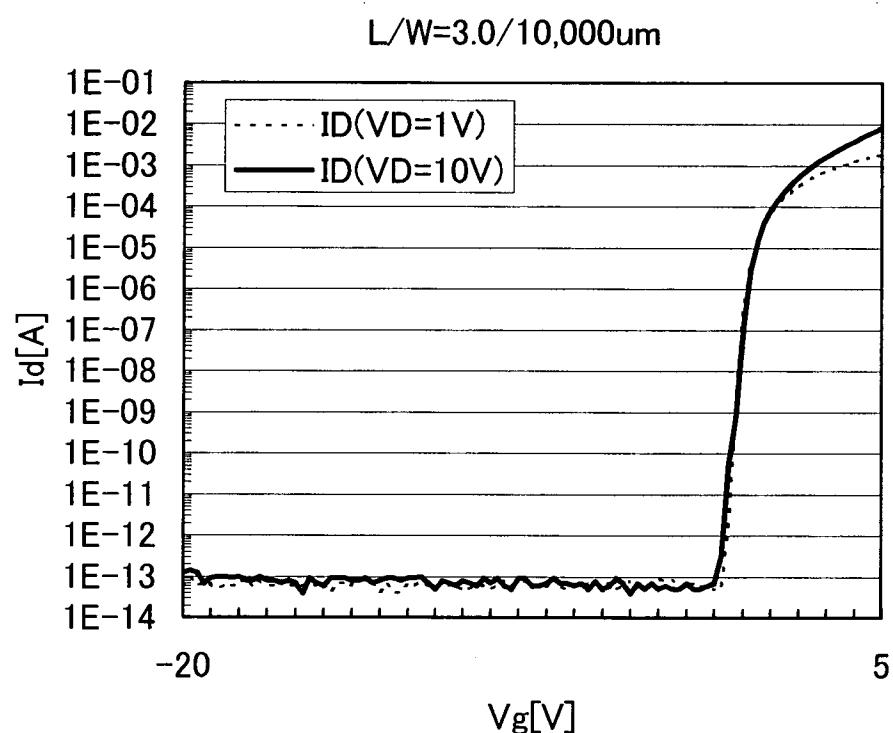

10 FIG. 20 is a graph showing off-state characteristics of  $V_g$ - $I_d$  characteristics of a transistor including an oxide semiconductor; and

FIG. 21 is a graph showing a relationship between a source-drain voltage  $V$  and an off-state current  $I$ .

#### BEST MODE FOR CARRYING OUT THE INVENTION

##### 15 [0020]

Embodiments will be described with reference to the drawings. Note that the present invention is not limited to the following description, and it will be easily understood by those skilled in the art that modes and details thereof can be changed in various ways without departing from the spirit and the scope of the present invention.

20 Therefore, the invention should not be interpreted as being limited to the description in the following embodiments. Note that in the structures of the invention described below, the same portions or portions having similar functions are denoted by the same reference numerals in different drawings, and description of such portions is not repeated.

##### 25 [0021]

###### (Embodiment 1)

In this embodiment, a structure of a liquid crystal display device in which an end portion of a pixel electrode overlaps with an end portion of an adjacent pixel electrode with an insulating layer interposed therebetween will be described with 30 reference to FIGS. 1A and 1B. Further, a manufacturing method thereof will be described with reference to FIGS. 2A to 2C.

##### [0022]

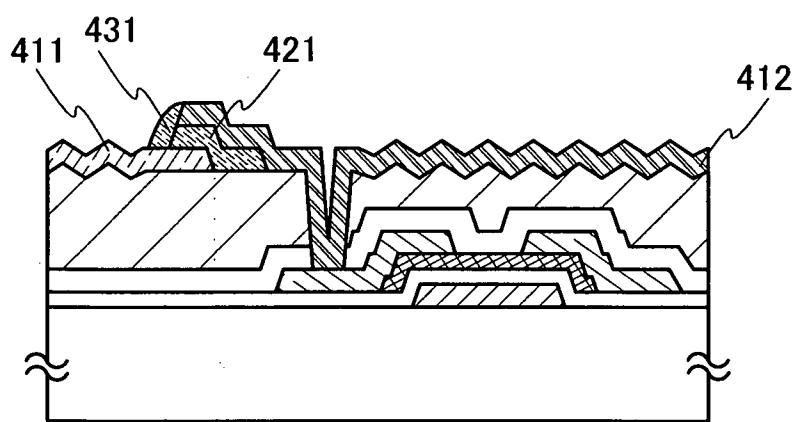

Structures of two adjacent pixel electrodes of a liquid crystal display device described in this embodiment will be described with reference to cross-sectional views. FIG. 1A illustrates a liquid crystal display device 450 where a first pixel 451 and a second pixel 452 adjoin to each other.

5 [0023]

The liquid crystal display device 450 includes a plurality of pixels such as the first pixel 451 and the second pixel 452. The first pixel 451 includes a first pixel electrode 411. The second pixel 452 includes a second pixel electrode 412. Note that the first pixel electrode 411 and the second pixel electrode 412 are formed over an insulating layer 308 provided over a substrate 300. An alignment film 414 is formed over the first pixel electrode 411 and the second pixel electrode 412. A counter electrode 403 is provided on a surface of a counter substrate 408, and an alignment film 404 is provided on the counter electrode 403. A liquid crystal layer 405 is in contact with the alignment films 414 and 404, and interposed between the substrate 300 and the counter substrate 408.

15 [0024]

The irregularities of a surface of the insulating layer 308 in FIG. 1A schematically illustrates an uneven structure in an irregular state called a texture structure. Since the first pixel electrode 411 and the second pixel electrode 412 are formed over the insulating layer 308 having a texture structure, the texture structure appears on surfaces of the first pixel electrode 411 and the second pixel electrode 412. As a result, light incident on the pixel electrodes irregularly reflects, and the first pixel electrode 411 and the second pixel electrode 412 are macroscopically white in general. Note that when alignment of liquid crystal is controlled using a pixel electrode that is seen white, contrast can be increased.

25 [0025]

The first pixel electrode 411 is electrically connected to a source electrode or a drain electrode of a transistor that is not shown. The second pixel electrode 412 is electrically connected to a source electrode or a drain electrode of the transistor 350. Note that the transistor 350 functions as a switching element of the pixel 452. A pixel transistor including the transistor 350 is formed over the substrate 300, and the first pixel electrode 411 and the second pixel electrode 412 are formed over an insulating

layer 307 and the insulating layer 308 which cover the pixel transistor.

[0026]

An end portion of the second pixel electrode 412 is provided to overlap with an end portion of the first pixel electrode 411 with an insulating layer 421 interposed therebetween. The insulating layer 421 prevents electrical connection between the first pixel electrode 411 and the second pixel electrode 412.

[0027]

With a structure in which two adjacent pixel electrodes are provided so as to overlap with each other, a space between the two pixel electrodes is not seen when the display device is viewed from the front. As a result, the ratio of an area of a pixel electrode in each pixel can be increased. A display device including pixel electrodes with such a structure can display an image with high luminance and high contrast.

[0028]

The structure of pixel electrodes of a liquid crystal display device 460, which differs from the structure illustrated in FIG. 1A, will be described. FIG. 1B illustrates a liquid crystal display device 460 where a first pixel 461 and a second pixel 462 adjoin to each other.

[0029]

The first pixel 461 and the second pixel 462 are formed over the substrate 300. The first pixel 461 includes the first pixel electrode 411, and the second pixel 462 includes the second pixel electrode 412. The end portion of the second pixel electrode 412 is provided to overlap with the end portion of the first pixel electrode 411 with an insulating layer 421 interposed therebetween. The insulating layer 421 prevents electrical connection between the first pixel electrode 411 and the second pixel electrode 412.

[0030]

A side surface of the second pixel electrode 412 in the liquid crystal display device 460 is covered with an insulating layer 431 provided over the first pixel electrode 411. Note that as the insulating layer 431, a layer functioning as a black matrix, for example, a coloring layer containing a coloring material, is preferably used. The liquid crystal display device 460 has the same structure as the liquid crystal display device 450 except that the insulating layer 431 is provided.

## [0031]

When a high electric field is generated between the first pixel electrode 411 and the side surface of the second pixel electrode 412, the alignment of liquid crystal located in such a region is disordered in some cases. The insulating layer 431 covering the 5 side surface of the second pixel electrode 412 in the liquid crystal display device 460 reduces the electric field generated between the first pixel electrode 411 and the side surface of the second pixel electrode 412. As a result, the alignment of liquid crystal is hardly disordered, leading to improvement in quality of a display image. Further, a 10 layer functioning as a black matrix is used as the insulating layer 431, the optical density of a dark region (i.e., a shadow portion) in a display image can be increased, so that the gradation of the shadow portion can be displayed more clearly.

## [0032]

The structure of pixel electrodes of a liquid crystal display device 490, which differs from the structures illustrated in FIGS. 1A and 1B, will be described. FIG. 17 15 illustrates a liquid crystal display device 490 where a first pixel 471 and a second pixel 472 adjoin to each other.

## [0033]

The first pixel 471 and the second pixel 472 are formed over the substrate 300. The first pixel 471 includes the first pixel electrode 411, and the second pixel 472 20 includes the second pixel electrode 412. The end portion of the second pixel electrode 412 is provided to overlap with the end portion of the first pixel electrode 411 with an insulating layer 421 interposed therebetween. The insulating layer 421 prevents electrical connection between the first pixel electrode 411 and the second pixel electrode 412.

## 25 [0034]

A spacer 441 is provided in a region where the first pixel electrode 411 and the second pixel electrode 412 in the liquid crystal display device 490 overlap with each other. The spacer 441 is provided between the counter substrate 408 and the substrate 300, using a dielectric material, for example. Specifically, the spacer 441 can be 30 formed on the counter substrate 408, using an organic resin. Alternatively, the spacer 441 can be formed using a layer functioning as a black matrix, for example, a coloring layer containing a coloring material. The liquid crystal display device 490 has the

same structure as the liquid crystal display device 450 except that the spacer 441 is provided.

[0035]

As described above, when a high electric field is generated between the first 5 pixel electrode 411 and the side surface of the second pixel electrode 412, the alignment of liquid crystal located in such a region is disordered in some cases. In the liquid crystal display device 490, the spacer 441 is provided in such a region; thus, the alignment of liquid crystal can be prevented from being disordered.

[0036]

10 Next, a method for manufacturing the pixel electrode of one embodiment of the present invention, which is illustrated in FIG. 1B, over a substrate provided with a switching element will be described with reference to FIGS. 2A to 2C.

[0037]

15 There is no particular limitation on the switching element formed over the substrate 300. As the switching element, a top gate transistor or a bottom gate transistor can be employed, for example. Further, the transistor may have a single gate structure including one channel formation region, a double gate structure including two channel formation regions, or a triple gate structure including three channel formation regions. Alternatively, the transistor may have a dual gate structure including two gate 20 electrode layers positioned over and below a channel region with a gate insulating layer provided therebetween. As an example, FIGS. 2A to 2C illustrate the case where the transistor 350 with a bottom gate structure is employed. Note that a transistor including an oxide semiconductor layer in which off-state current is reduced is especially suitable as the switching element. When the transistor including an oxide 25 semiconductor layer in which off-state current is reduced is used as a pixel transistor, for example, frequency of rewrites of display elements is reduced in a period during which a still image is displayed; thus, a display device with less power consumption can be provided.

[0038]

30 The insulating layer 307 is formed over the transistor 350. As the insulating layer 370, typically, an inorganic insulating film such as a silicon oxide film, a silicon oxynitride film, an aluminum oxide film, and an aluminum oxynitride film can be used.

Alternatively, the insulating layer 307 may be formed by stacking a plurality of insulating films. For example, an inorganic insulating film such as a silicon nitride film, an aluminum nitride film, a silicon nitride oxide film, or an aluminum nitride oxide film can be stacked over the above-mentioned inorganic insulating film. Note 5 that the inorganic insulating film is formed by a sputtering method or the like.

[0039]

The insulating layer 308 is formed over the insulating layer 307. For the insulating layer 308, a photosensitive organic resin can be used, for example. A photosensitive organic resin layer is formed over the insulating layer 307 by a spin 10 coating method or the like, and exposed to light using a photomask in order to form an opening that reaches the source electrode or the drain electrode of the transistor 350. Then, light exposure is performed using another photomask in order to form a texture structure on the surface of the insulating layer 308 and developed, thereby forming the insulating layer 308.

15 [0040]

Next, the first pixel electrode 411 is formed over the insulating layer 308. Any conductive film can be used for the first pixel electrode 411 as long as it reflects visible light. As an example of the conductive film, a film including Al, Ag, an alloy thereof, aluminum containing Nd, or an Ag-Pd-Cu alloy is given. Note that the 20 conductive film can be formed by a sputtering method, a vacuum evaporation method, or the like. Then, an unnecessary portion is removed with use of a resist mask formed using a photomask, thereby forming the first pixel electrode 411.

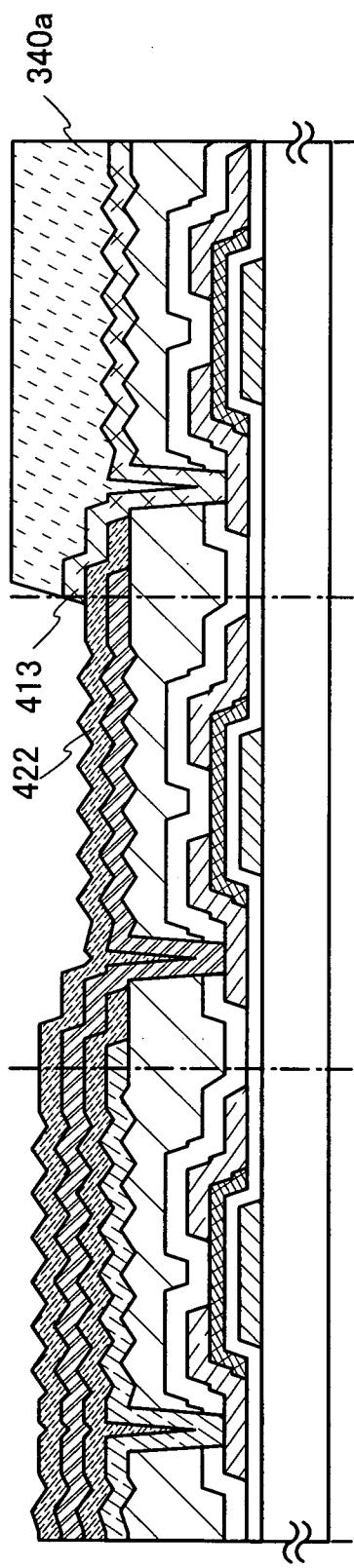

[0041]

Next, an insulating film to be the insulating layer 421 is provided so as to cover 25 the first pixel electrode 411. Any material can be used for the insulating layer 421 as long as it has an insulating property. For example, an inorganic material such as silicon oxide, silicon oxynitride, aluminum oxide, aluminum oxynitride, silicon nitride, aluminum nitride, silicon nitride oxide, or aluminum nitride oxide; or an organic material such as polyimide, acrylic, or benzocyclobutene can be used. Note that an 30 insulating film including the inorganic material can be formed by a sputtering method, a sol-gel method or the like, and an insulating film including the organic material can be formed by a spin coating method, a printing method, or the like. Then, an unnecessary

portion is removed with use of a resist mask, for example, thereby forming the insulating layer 421 covering the first pixel electrode 411. FIG. 2A is a cross-sectional view when up to this step is completed.

[0042]

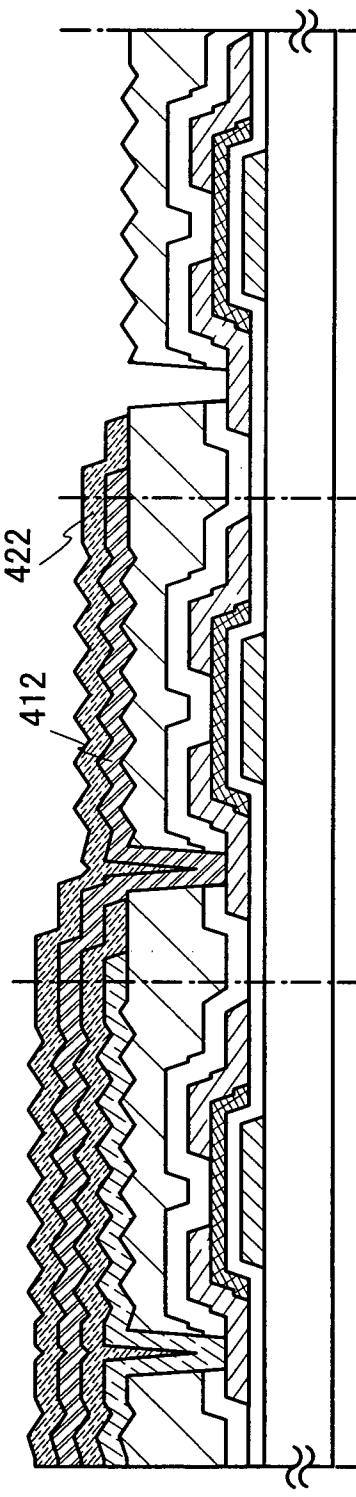

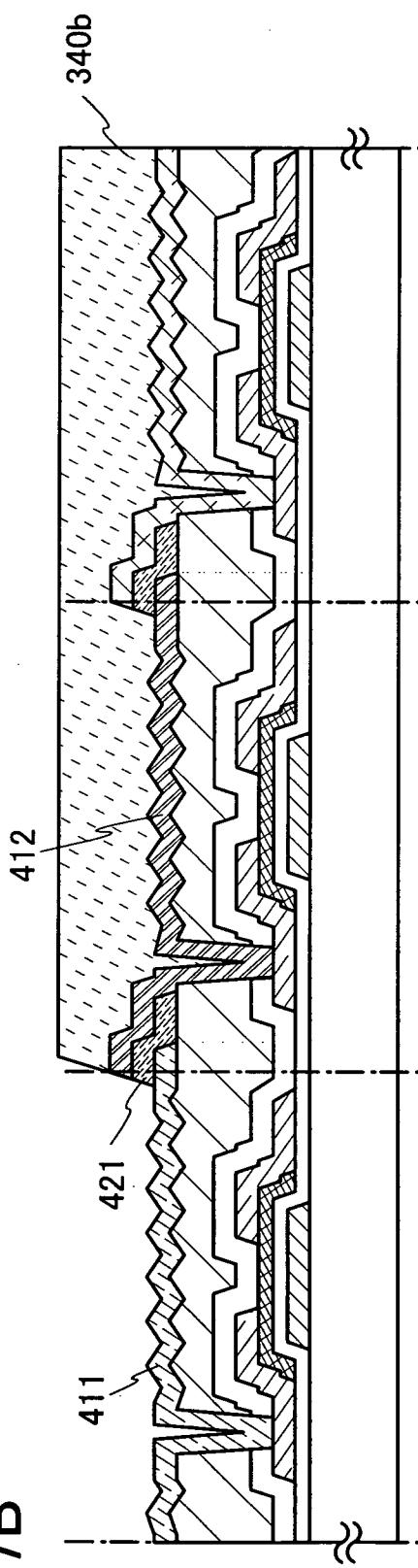

5 Next, the second pixel electrode 412 is formed over the insulating layer 421 and the insulating layer 308. A conductive film to be the second pixel electrode 412 is formed in a manner similar to that of the first pixel electrode 411. Then, an unnecessary portion is removed with use of a resist mask 340 formed using a photomask, thereby forming the second pixel electrode 412. Note that the insulating 10 layer 421 provided over the first pixel electrode 411 functions as an etching stopper and protects the first pixel electrode 411 from etching in this etching step. FIG. 2B is a cross-sectional view when this step is completed.

[0043]

15 An unnecessary portion of the insulating layer 421 is removed with use of the resist mask 340, and then the resist mask 340 is removed, thereby manufacturing the pixel electrode illustrated in FIG. 1A, which is one embodiment of the present invention.

[0044]

20 The insulating layer 431 is formed so as to cover the side surface of the second pixel electrode 412 over the first pixel electrode 411. A material that can be used for the insulating layer 421 is employed for the insulating layer 431. As a method for forming the insulating layer 431, in stead of a method by which an insulating film is formed and etched with use of a resist mask, a method by which the insulating layer 431 is formed using a photoresist may be employed. Alternatively, the insulating layer 431 can be formed by a printing method or an inkjet method. FIG. 2C is a cross-sectional 25 view when this step is completed.

[0045]

30 Through the above steps, the pixel electrode of the liquid crystal display device with a structure in which the second pixel electrode 412 overlaps with the end portion of the adjacent first pixel electrode 411 with the insulating layer 421 interposed therebetween, and the insulating layer 431 covers the side surface of the second pixel electrode 412 over the first pixel electrode 411 can be manufactured.

[0046]

The liquid crystal display devices described in this embodiment each have a structure in which two adjacent pixel electrodes are provided so as to overlap with each other. A space between the two pixel electrodes is not seen when the display device is viewed from the front. As a result, the ratio of an area of a pixel electrode in each 5 pixel can be increased. A display device including pixel electrodes with such a structure can provide a display image with high luminance and excellent contrast.

[0047]

In the liquid crystal display device described in this embodiment, which is provided with an insulating layer covering the side surface of the second pixel electrode 10 overlying the top surface of the first pixel electrode, the alignment of liquid crystal is hardly disordered, so that a high-quality image can be displayed. Further, when a layer functioning as a black matrix is used as the insulating layer covering the side surface of the second pixel electrode, the optical density of a dark region (i.e., a shadow portion) in a display image is increased, so that the gradation of the shadow portion can be 15 displayed more clearly.

[0048]

Note that this embodiment can be combined with any of the other embodiments described in this specification as appropriate.

[0049]

20 (Embodiment 2)

In this embodiment, a structure of a display device including three or more adjacent pixel electrodes in which end portions of the adjacent pixel electrodes overlap with one another with an insulating layer interposed therebetween will be described with reference to FIGS. 3A and 3B and FIGS. 7A and 7B.

25 [0050]

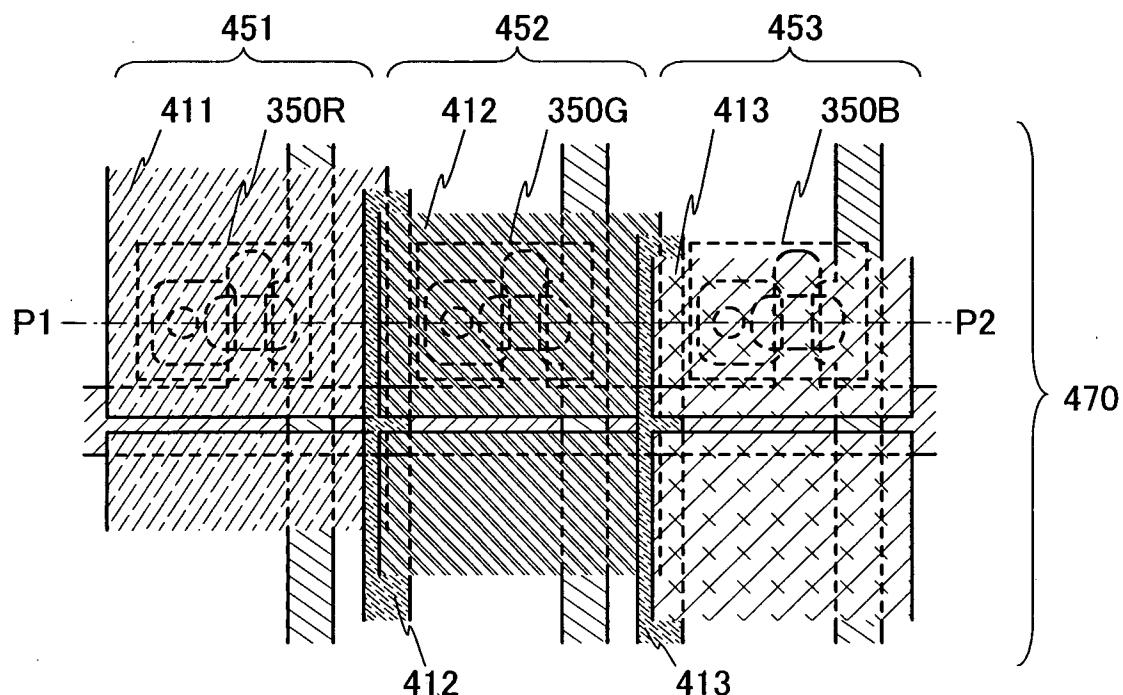

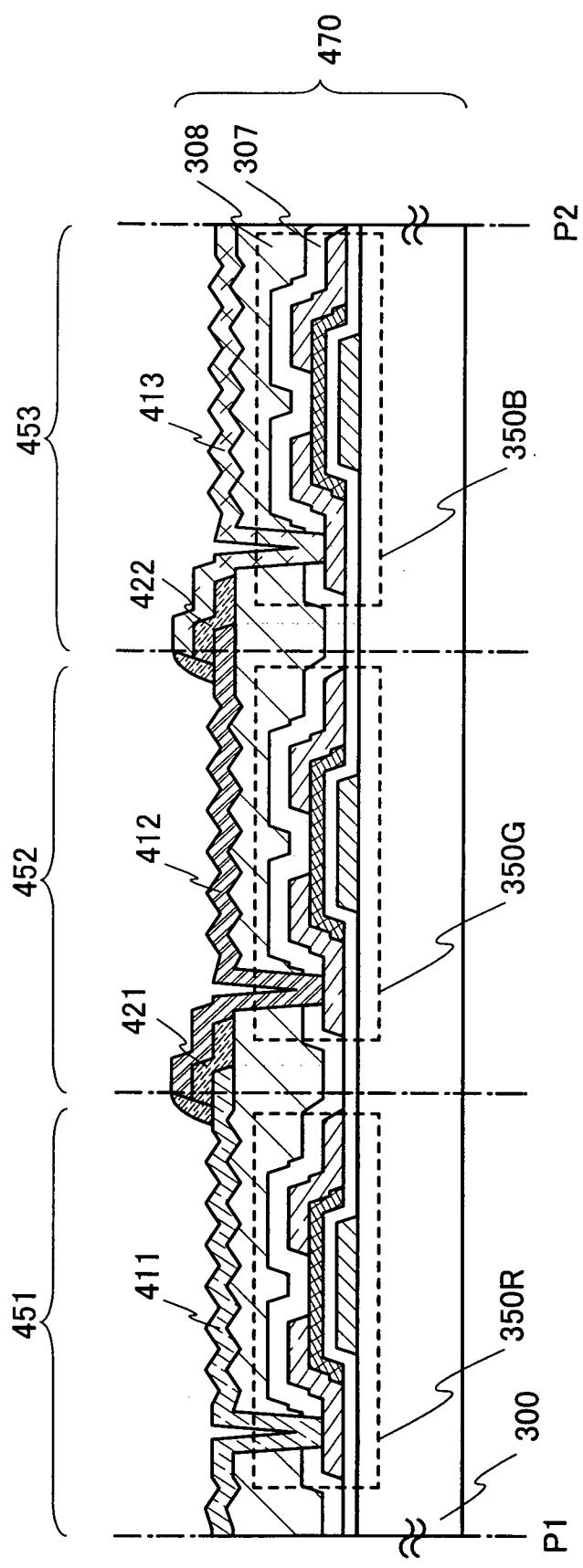

FIG. 3A is a top view of a pixel portion of a liquid crystal display device 470 described in this embodiment. The liquid crystal display device 470 includes a first pixel 451, a second pixel 452, and a third pixel 453. The first pixel 451 includes the first pixel electrode 411 and a first transistor 350R. The second pixel 452 includes the 30 second pixel electrode 412 and a second transistor 350G. The third pixel 453 includes a third pixel electrode 413 and a third transistor 350B.

[0051]

FIG. 4 is a cross-sectional view of the liquid crystal display device 470 taken along line P1-P2 in FIG. 3A. The liquid crystal display device 470 includes the three transistors 350R, 350G, and 350B over the substrate 300, the insulating layer 307 covering the transistors, and the insulating layer 308 covering the insulating layer 307.

5 The first pixel electrode 411, the second pixel electrode 412, and the third pixel electrode 413 are formed over the insulating layer 308.

[0052]

Through openings formed in the insulating layer 307 and the insulating layer 308, the first pixel electrode 411 is electrically connected to a source electrode or a drain electrode of the transistor 350R, the second pixel electrode 412 is electrically connected to a source electrode or a drain electrode of the transistor 350G, and the third pixel electrode 413 is electrically connected to a source electrode or a drain electrode of the transistor 350B.

[0053]

15 One end portion of the second pixel electrode 412 overlies the first pixel electrode 411 with the first insulating layer 421 interposed therebetween, and the other end portion of the second pixel electrode 412 underlies the third pixel electrode 413 with the second insulating layer 422 interposed therebetween.

[0054]

20 One end portion of a pixel electrode provided between two pixel electrodes overlies the adjacent pixel electrode, and the other end portion thereof underlies the other adjacent pixel electrode. This structure is not limited to the case where three pixel electrodes are arranged, and can be applied to the case where four pixel electrodes are arranged in line. Specifically, the following structure may be used: a left end portion of each of four pixel electrodes is overlies a right end portion of the immediate left pixel electrode.

25

[0055]

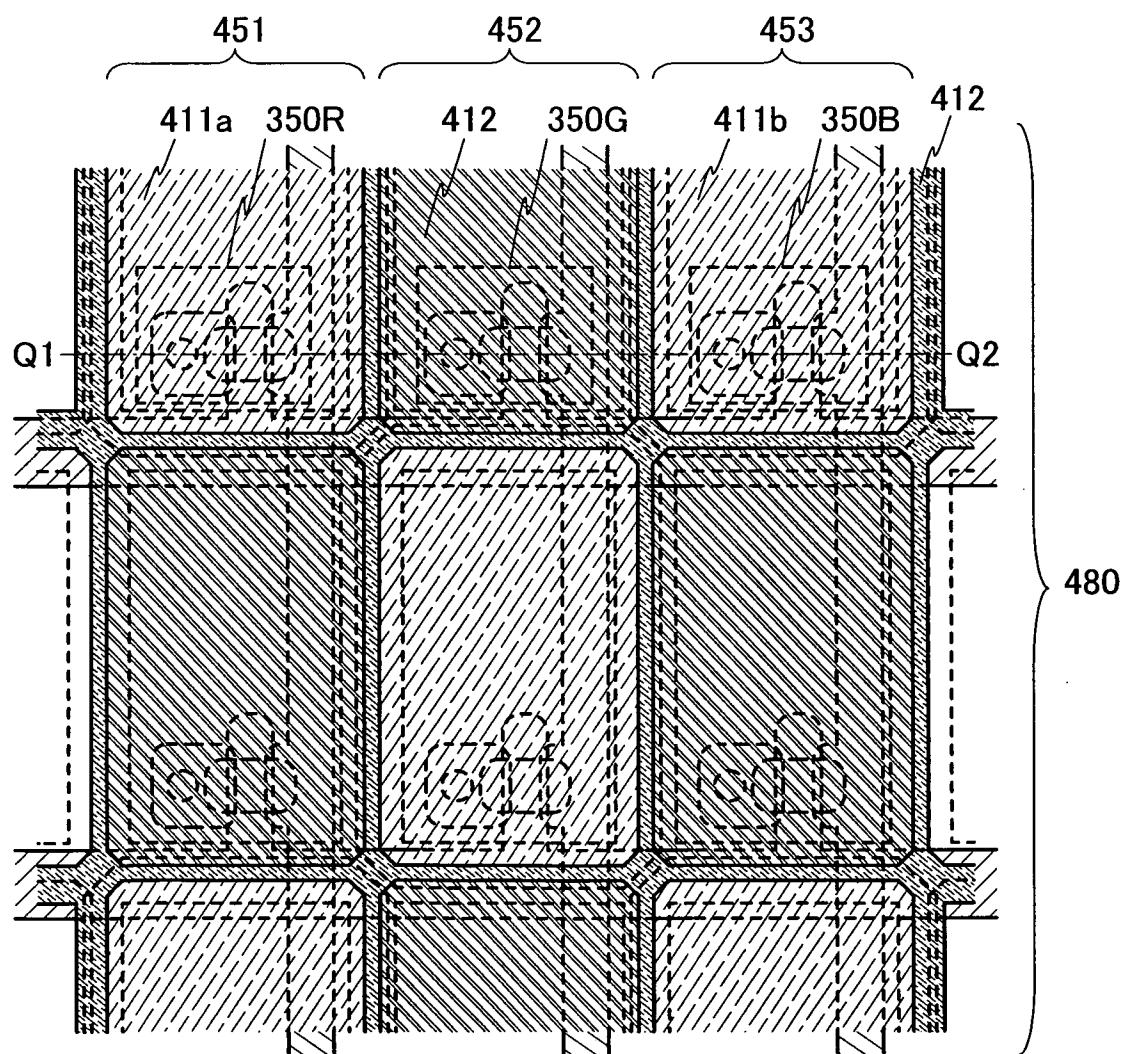

30 Next, a structure of a pixel electrode, which differs from the structure illustrated in FIG. 3A, will be described. FIG. 3B is a top view of a liquid crystal display device 480. The liquid crystal display device 480 includes the first pixel 451, the second pixel 452, and the third pixel 453. The first pixel 451 includes a first pixel electrode 411a and the first transistor 350R. The second pixel 452 includes the second

pixel electrode 412 and the second transistor 350G. The third pixel 453 includes a third pixel electrode 411b and the third transistor 350B.

[0056]

FIG. 5 is a cross-sectional view of the liquid crystal display device 480 taken 5 along line Q1-Q2 in FIG. 3B. The liquid crystal display device 480 includes three transistors 350R, 350G, and 350B over the substrate 300, the insulating layer 307 covering the transistors, and the insulating layer 308 covering the insulating layer 307. The first pixel electrode 411a, the second pixel electrode 412, and the third pixel electrode 411b are formed over the insulating layer 308.

10 [0057]

Through an opening of the insulating layer 307 and the insulating layer 308, the first pixel electrode 411a is electrically connected to a source electrode or a drain electrode of the transistor 350R, the second pixel electrode 412 is electrically connected to one of a source electrode and a drain electrode of the transistor 350G, and the third 15 pixel electrode 411b is electrically connected to one of a source electrode and a drain electrode of the transistor 350B.

[0058]

One end portion of the second pixel electrode 412 overlies the first pixel electrode 411a with the first insulating layer 421 interposed therebetween, and the other 20 end portion of the second pixel electrode 412 overlies the third pixel electrode 411b with the second insulating layer 422 interposed therebetween.

[0059]

The structure in which end portions of a pixel electrode provided between two 25 pixel electrodes overlie end portions of the adjacent pixel electrodes can be applied to the case where three or more pixel electrodes are arranged in line.

[0060]

Alternatively, the structure in which end portions of a pixel electrode provided between two pixel electrodes underlie end portions of the adjacent pixel electrodes. In other words, in the case where four or more pixel electrodes are arranged, the following 30 two structures are provided alternately: a structure in which end portions of a pixel electrode provided between two pixel electrodes overlie end portions of the adjacent pixel electrodes; and a structure in which end portions of a pixel electrode provided

between two pixel electrodes underlie end portions of the adjacent pixel electrodes.

[0061]

An example of a method for manufacturing the pixel portion of the liquid crystal display device 470 will be described with reference to FIGS. 6A and 6B and FIGS. 7A and 7B. The pixel portion of the liquid crystal display device 470 can be manufactured by a method that is substantially the same as that of Embodiment 1.

[0062]

The transistors 350R, 350G, and 350B and the insulating layers 307 and 308 having openings that reach source electrodes or drain electrodes of the transistors are provided over the substrate 300. Then, the first pixel electrode 411 is formed over the insulating layer 308 by the method described in Embodiment 1, and the first insulating layer 421 is formed over the first pixel electrode 411. FIG. 6A is a cross-sectional view when this step is completed.

[0063]

Similarly, the second pixel electrode 412 and the second insulating layer 422 are formed as in FIG. 6B, and a conductive film to be the third pixel electrode 413 is formed in a manner similar to that of other pixel electrodes. Then, a resist mask 340a is formed to remove an unnecessary portion, thereby forming the third pixel electrode 413. FIG. 7A is a cross-sectional view when this step is completed.

[0064]

An unnecessary portion of the second insulating layer 422 is etched away with use of the resist mask 340a. Next, a resist mask 340b is formed over the conductive film to be the second pixel electrode 412, and unnecessary portions of the first pixel electrode 411 and the first insulating layer 421 are removed with use of the resist mask 340b so that the pixel portion of the liquid crystal display device 470 is formed.

[0065]

An example of a method for manufacturing the pixel portion of the liquid crystal display device 480 illustrated in FIG. 3B and FIG. 5 will be described with reference to FIG. 5.

[0066]

The transistors 350R, 350G, and 350B and the insulating layers 307 and 308 having openings that reach a source electrodes or a drain electrode of the transistors are

provided over the substrate 300. Then, a conductive film is formed over the insulating layer 308, and the first pixel electrode 411a and the third pixel electrode 411b are formed with use of a resist mask formed using a photomask.

[0067]

5 Next, an insulating film covering the first pixel electrode 411a and the third pixel electrode 411b is formed, and an unnecessary portion of the insulating film is removed with use of a resist mask. Note that the resist mask used here extends beyond the end portions of the first pixel electrode 411a and the third pixel electrode 411b and covers portions to be the first insulating layer 421 and the second insulating layer 422 so 10 that the resist mask protects these portions from an etchant.

[0068]

15 Thus, portions of the insulating layer which overlaps with the first pixel electrode 411a and the third pixel electrode 411b are not removed, so that the shape of the insulating layer is different from the shapes of the first insulating layer 421 and the second insulating layer 422.

[0069]

20 Next, the resist mask is removed, the conductive film to be the second pixel electrode 412 is formed, and then a resist mask is formed thereover using a photomask. Then, an unnecessary portion is removed with use of the resist mask, thereby forming the second pixel electrode 412.

[0070]

25 With use of the resist mask used for forming the second pixel electrode 412, unnecessary portions of the the insulating layer which overlap with the first pixel electrode 411a and the third pixel electrode 411b are etched away so that the first insulating layer 421 and the second insulating layer 422 are formed.

[0071]

30 The structure illustrated in FIG. 3B and FIG. 5 in which end portions of a pixel electrode provided between two pixel electrodes overlie end portions of the adjacent pixel electrodes can be formed by the formation of pixel electrodes in two separate steps, which is relatively easy. Similarly, it is also relatively easy to form the structure in which end portions of a pixel electrode provided between two pixel electrodes underlie end portions of the adjacent pixel electrodes.

[0072]

With a structure in which three or more adjacent pixel electrodes are provided so that end portions of the adjacent pixel electrodes overlap with one another with an insulating layer interposed therebetween, a space between the two pixel electrodes is not seen when the display device is viewed from the front. As a result, the ratio of an area of a pixel electrode in each pixel can be increased. A display device including pixel electrodes with such a structure can display an image with high luminance and high contrast.

[0073]

10 Note that this embodiment can be combined with any of the other embodiments described in this specification as appropriate.

[0074]

(Embodiment 3)

15 In this embodiment, a liquid crystal display device which includes the pixel electrodes described in Embodiments 1 and 2 and further includes a photodiode as a photo sensor over one substrate will be described with reference to FIG. 8, FIG. 9, and FIGS. 10A and 10B.

[0075]

20 FIG. 8 is an example of a top view of a pixel, which illustrates a state before an electrode of a photodiode is formed. Note that cross-sectional views taken along chain line A-B and chain line C-D in FIG. 8 correspond to FIG. 10A.

[0076]

25 Next, a method for manufacturing the liquid crystal display device described in this embodiment will be described mainly using FIG. 8 together with FIGS. 10A and 10B. First, a conductive film is formed over a substrate 230, and then gate signal lines 207, 213, and 227 including gate electrodes, a capacitor wiring 224, a photodiode reset signal line 208, a reading signal line 209, and a photo sensor reference signal line 212 are formed through a first photolithography process using a first light-exposure mask. Note that in this embodiment, a glass substrate is used as the substrate 230.

30 [0077]

An insulating film serving as a base film may be provided between the substrate 230 and the conductive film (see FIGS. 10A and 10B). The base film has a

function of preventing diffusion of an impurity element from the substrate 230. The base film can be formed with a single-layer structure or a layered structure including one or more of a silicon nitride film, a silicon oxide film, a silicon nitride oxide film, and a silicon oxynitride film.

5 [0078]

The conductive film can be formed with a single-layer structure or a layered structure including a metal material such as molybdenum, titanium, tantalum, tungsten, aluminum, copper, neodymium, or scandium, or an alloy material which contains any of these metal materials as its main component.

10 [0079]

Next, an insulating layer is formed to cover these wirings, and selectively etched through a second photolithography process using a second light-exposure mask so that the insulating layer 231 is formed in only portions where wirings formed later intersect with each other. In this embodiment, a 600-nm-thick silicon oxynitride film 15 is used as the insulating layer 231.

[0080]

Then, a gate insulating layer 232 and an oxide semiconductor film are formed (see FIGS. 10A and 10B), and a first oxide semiconductor layer 233, a second oxide semiconductor layer 253, a third oxide semiconductor layer 255, and a fourth oxide semiconductor layer 256 are formed through a third photolithography process using a third light-exposure mask. The first oxide semiconductor layer 233, the second oxide semiconductor layer 253, the third oxide semiconductor layer 255, and the fourth oxide semiconductor layer 256 overlap with the gate signal lines 207, 213, and 227 and the reading signal line 209, respectively, with the gate insulating layer 232 provided 20 therebetween. In this embodiment, a 100-nm-thick silicon oxynitride film is used as the gate insulating layer 232, and a 25-nm-thick In-Ga-Zn-O film is used as the oxide semiconductor layer.

[0081]

An oxide thin film represented by a chemical formula  $\text{InMO}_3(\text{ZnO})_m$  ( $m > 0$ ) 30 can be used for the first oxide semiconductor layer 233, the second oxide semiconductor layer 253, the third oxide semiconductor layer 255, and the fourth oxide semiconductor layer 256. Here,  $M$  represents one or more metal elements selected from Ga, Al, Mn,

and Co. For example,  $M$  can be Ga, Ga and Al, Ga and Mn, Ga and Co, or the like. Further,  $\text{SiO}_2$  may be contained in the above oxide thin film.

[0082]

As the target for forming the oxide thin film by a sputtering method, for example, an oxide target having a composition ratio of  $\text{In}_2\text{O}_3:\text{Ga}_2\text{O}_3:\text{ZnO} = 1:1:1$  [molar ratio] is used to form an In-Ga-Zn-O film. Without limitation on the material and the component of the target, for example, an oxide target having a composition ratio of  $\text{In}_2\text{O}_3:\text{Ga}_2\text{O}_3:\text{ZnO} = 1:1:2$  [molar ratio] may be used. Note that in this specification, for example, an In-Ga-Zn-O film means an oxide film including indium (In), gallium (Ga), and zinc (Zn), and there is no particular limitation on the stoichiometric proportion.

[0083]

Next, the oxide semiconductor layer is subjected to first heat treatment. The oxide semiconductor layer can be dehydrated or dehydrogenated by the first heat treatment. The temperature of the first heat treatment is higher than or equal to 400 °C and lower than or equal to 750 °C, or higher than or equal to 400 °C and lower than the strain point of the substrate. In this embodiment, heat treatment is performed using a rapid thermal annealing (RTA) apparatus at 650 °C for 6 minutes under a nitrogen atmosphere; the substrate is introduced to an electric furnace that is one of heat treatment apparatuses without exposure to the air; and the oxide semiconductor layer is subjected to heat treatment at 450 °C for one hour under a nitrogen atmosphere; thus, the oxide semiconductor layer can be obtained without entry of water or hydrogen into the oxide semiconductor layer.

[0084]

The gate insulating layer 232 is selectively removed through a fourth photolithography process using a fourth light-exposure mask, thereby forming an opening that reaches the gate signal line 213 and an opening that reaches the photodiode reset signal line 208 (see FIGS. 10A and 10B).

[0085]

Next, a conductive film is formed over the gate insulating layer 232 and the oxide semiconductor layer. As the conductive film, for example, a metal film

containing an element selected from Al, Cr, Cu, Ta, Ti, Mo, and W, an alloy film containing a nitride of any of these elements, an alloy film containing a combination of any of these elements, or the like can be employed. Then, a resist mask is formed over the conductive film through a fifth photolithography process using a fifth light-exposure mask and etching is selectively performed, thereby forming a video data signal line 210, a photo sensor output signal line 211, and electrode layers 234, 235, 254, 257, 258, and 259.

[0086]

Note that a transistor including the first oxide semiconductor layer 233 illustrated in FIG. 8 is a transistor in which the electrode layer 234 serves as a source electrode layer or a drain electrode layer, and functions as a switching element of a pixel. As illustrated in FIGS. 10A and 10B, a storage capacitor 222 is formed by the electrode layer 234 and the capacitor wiring 224, using the gate insulating layer 232 as a dielectric. A transistor including the second oxide semiconductor layer 253 illustrated in FIG. 8 is a transistor in which the electrode layer 254 serves as a source electrode layer or a drain electrode layer, and functions as a switching element of a pixel.

[0087]

A transistor including the third oxide semiconductor layer 255 illustrated in FIG. 8 is a transistor in which the electrode layer 257 serves as a source electrode layer or a drain electrode layer, and is one component of a photo sensor.

[0088]

A transistor including the fourth oxide semiconductor layer 256 illustrated in FIG. 8 is a transistor in which the electrode layer 257 or the electrode layer 258 serves as a source electrode layer or a drain electrode layer. As illustrated in FIG. 10A, the gate signal line 213 of the transistor is electrically connected to the electrode layer 259.

[0089]

Next, second heat treatment is performed under an inert gas atmosphere or oxygen gas atmosphere (preferably at higher than or equal to 200 °C and lower than or equal to 400 °C, for example, higher than or equal to 250 °C and lower than or equal to 350 °C). In this embodiment, the second heat treatment is performed at 300 °C for one hour under a nitrogen atmosphere. Through the second heat treatment, part of the

oxide semiconductor layer (a channel formation region) is heated while being in contact with the insulating layer.

[0090]

Then, an insulating layer 237 to be a protective insulating layer is formed, and 5 an opening that reaches the electrode layer 235, an opening that reaches the electrode layer 234, and an opening that reaches the electrode layer 259 are formed through a sixth photolithography process using a sixth light-exposure mask.

[0091]

Next, a p-layer 238, an i-layer 239, and an n-layer 240 are stacked by a plasma 10 CVD method. In this embodiment, a 45-nm-thick microcrystalline silicon film containing boron as the p-layer 238, a 400-nm-thick amorphous silicon film as the i-layer 239, an 80-nm-thick microcrystalline silicon film containing phosphorus as the n-layer 240 are employed. Through a seventh photolithography process using a seventh light-exposure mask, the p-layer 238, the i-layer 239, and the n-layer 240 are 15 removed except a portion in contact with and overlapping with the electrode layer 235. FIG. 10A is a cross-sectional view when this step is completed and FIG. 8 is a top view thereof.

[0092]

Then, a photosensitive organic resin layer is formed, an eighth 20 photolithography process is performed through which a region to be an opening is exposed to light using an eighth light-exposure mask, a region to be uneven (a region having a texture structure) is exposed to light using a ninth light-exposure mask and developed, thereby forming an insulating layer 241 partly having unevenness.

[0093]

Next, a first pixel electrode, a second pixel electrode, and a third pixel 25 electrode are manufactured. In this embodiment, the method described in Embodiment 2 with reference to FIGS. 3A and 3B, FIG. 4, FIGS. 6A and 6B, and FIGS. 7A and 7B is employed, and description is made without a specific drawing here.

[0094]

Specifically, a conductive film having reflectivity to be the first pixel electrode 30 is formed and a ninth photolithography process using a tenth light-exposure mask is performed. Then, an insulating layer to be a first insulating layer is formed to cover

the conductive film to be the first pixel electrode, and a tenth photolithography process using an eleventh light-exposure mask is performed.

[0095]

Next, a conductive film having reflectivity to be the second pixel electrode is formed and an eleventh photolithography process using a twelfth light-exposure mask is performed. Then, an insulating layer to be a second insulating layer is formed to cover the conductive film to be the second pixel electrode, and a twelfth photolithography process using a thirteenth light-exposure mask is performed.

[0096]

10 Next, a conductive film having reflectivity to be the third pixel electrode is formed, and a thirteenth photolithography process using a fourteenth light-exposure mask is performed, thereby forming the third pixel electrode and a second insulating layer. Then, a fourteenth photolithography process using a fifteenth light-exposure mask is performed so that the second pixel electrode, the first insulating layer, and the 15 first pixel electrode are formed. Further, a connection electrode layer 243 is formed in a manufacturing process of the pixel electrodes (see FIG. 9). The photodiode 204 and the gate signal line 213 are electrically connected to each other through the connection electrode layer 243.

[0097]

20 Note that Al, Ag, or an alloy thereof such as aluminum containing Nd or an Ag-Pd-Cu alloy is used as the conductive film having reflectivity. After the ninth photolithography process, third heat treatment is performed. In this embodiment, the third heat treatment is performed at 250 °C for one hour under a nitrogen atmosphere.

[0098]

25 Through the above steps, as illustrated in FIG. 10B, a reflective electrode layer 242 whose end portion overlaps with an end portion of the adjacent reflective electrode with an insulating layer interposed therebetween, a transistor electrically connected to the reflective electrode layer 242, and the photodiode 204 electrically connected to the gate signal line 213 through the connection electrode layer 243 can be formed over one 30 substrate, by fourteen photolithography processes with use of fifteen light-exposure masks in total.

[0099]

An alignment film 244 is formed to cover the reflective electrode layer 242. FIG. 10B is a cross-sectional view of this step. Thus, an active matrix substrate can be manufactured.

[0100]

5 Then a counter substrate to be bonded to the active matrix substrate is prepared. In the counter substrate, a light-blocking layer (also referred to as a black matrix) and a light-transmitting conductive film are formed to surround a light-receiving portion of a photo sensor, and a columnar spacer including an organic resin is further formed. Then, an alignment film is formed to cover them.

10 [0101]

The counter substrate is bonded to the active matrix substrate with use of a sealing material, and a liquid crystal layer is interposed between the pair of substrates. Note that the light-blocking layer of the counter substrate is formed so that the light-blocking layer surrounds a photodiode and does not overlap with the reflective 15 electrode layer 242 and an exposed region of the photodiode. The columnar spacer provided on the counter substrate is positioned so as to overlap with the electrode layers 251 and 252. Since the columnar spacer overlaps with the electrode layers 251 and 252, the pair of substrates is held at a certain distance. The electrode layers 251 and 20 252 can be formed in the same step as that of the electrode layer 234; thus, it is not necessary to increase the number of masks.

[0102]

FIG. 9 is a top view of a pixel in the pair of substrates which are bonded in such a manner. The reflective electrode layer 242 has a random plane pattern illustrated in FIG. 9 because the reflective electrode layer 242 is provided over the photosensitive 25 organic resin layer having an uneven shape. The surface shape of the photosensitive organic resin layer is reflected on a surface of the reflective electrode layer 242 so that the surface of the reflective electrode layer 242 has an uneven shape; thus, specular reflection is prevented. Note that FIG. 9 also illustrates a depressed portion 245 of the reflective electrode layer 242. The periphery of the depressed portion 245 is located 30 on an inner side than the periphery of the reflective electrode layer 242, and the photosensitive organic resin layer below the depressed portion 245 has a smaller thickness than other regions.

[0103]

If necessary, a surface of the counter substrate where external light enters may be provided with an optical film such as a retardation film for adjusting phase difference, a film having a polarization function, an anti-reflection plate, or a color filter.

5 [0104]

Note that this embodiment can be combined with any of the other embodiments described in this specification as appropriate.

[0105]

(Embodiment 4)

10 In this embodiment, a method for driving a liquid crystal display device in which a pixel electrode and a photo sensor are formed over one substrate and an end portion of the pixel electrode overlaps with an end portion of an adjacent pixel electrode with an insulating layer interposed therebetween will be described.

[0106]

15 An example of a display panel in which the pixel electrode described in Embodiment 3 and a photo sensor are formed over one substrate will be described with reference to FIG. 11. A display panel 100 includes a pixel circuit 101, a display element control circuit, and a photo sensor control circuit. The pixel circuit 101 includes a plurality of pixels 103 and 104 and a plurality of photo sensors 106 which are arranged in a matrix of rows and columns. Each of the pixels 104 and 103 includes 20 one display element. Although in this embodiment, one photo sensor 106 is provided between the pixel 103 and the pixel 104 and the number of the photo sensors is half of the number of the pixels, an embodiment is not limited thereto. One photo sensor may be provided per one pixel so that the number of the photo sensors is the same as the 25 number of the pixels. Alternatively, the number of the photo sensors may be one third of the number of the pixels.

[0107]

30 A display element 105 includes a liquid crystal element including a transistor, a storage capacitor, and a liquid crystal layer, or the like. The transistor has a function of controlling injection or discharge of charge to/from the storage capacitor. The storage capacitor has a function to retain charge which corresponds to voltage applied to the liquid crystal layer. Taking advantage of the change in the direction of a polarization

due to a voltage application to the liquid crystal layer, contrast (gray scale) of light passing through the liquid crystal layer is made, so that image display is realized. External light which enters from a surface side of a liquid crystal display device is used as the light passing through the liquid crystal layer.

5 [0108]

The liquid crystal element in this embodiment has a structure in which an end portion of a pixel electrode overlaps with an end portion of an adjacent pixel electrode with an insulating layer interposed therebetween. Thus, a space between adjacent pixels can be narrowed, so that the area of a pixel that reflects external light can be increased. The structure with which a space between adjacent pixels can be narrowed is suitable particularly in the case where a display element and a photo sensor are formed over one substrate because the area of a pixel electrode of the display element is limited.

[0109]

15 Further, the display element control circuit is a circuit configured to control the display elements 105 and includes a display element driver circuit 107 which inputs a signal to the display elements 105 through signal lines (also referred to as source signal lines) such as video data signal lines, and a display element driver circuit 108 which inputs a signal to the display elements 105 through scan lines (also referred to as gate signal lines).

[0110]

20 For example, the display element driver circuit 108 on the scan line side has a function of selecting the display elements included in the pixels placed in a particular row. The display element driver circuit 107 on the signal line side has a function of applying a predetermined potential to the display elements included in the pixels placed in a selected row. Note that in the display element to which the display element driver circuit 108 on the scan line side applies high potential, the transistor is brought into conduction, so that the display element is supplied with charge from the display element driver circuit 107 on the signal line side.

25 [0111]

30 The photo sensor 106 includes a transistor and a light-receiving element which has a function of generating an electrical signal when receiving light, such as a

photodiode.

[0112]

The photo sensor control circuit is a circuit configured to control the photo sensors 106 and includes a photo sensor reading circuit 109 on the signal line side for a 5 photo sensor output signal line, a photo sensor reference signal line, or the like, and a photo sensor driver circuit 110 on the scan line side. The photo sensor driver circuit 110 on the scan line side has a function of performing reset operation and selecting operation on the photo sensors 106 included in the pixels placed in a particular row, which is described below. Further, the photo sensor reading circuit 109 on the signal 10 line side has a function of taking out an output signal of the photo sensors 106 included in the pixels in the selected row.

[0113]

A circuit diagram of the pixel 103, the photo sensor 106, and the pixel 104 is described in this embodiment with reference to FIG. 12. The pixel 103 includes the 15 display element 105 including a transistor 201, a storage capacitor 202, and a liquid crystal element 203. The photo sensor 106 includes a photodiode 204, a transistor 205, and a transistor 206. The pixel 104 includes a display element 125 including a transistor 221, a storage capacitor 222, and a liquid crystal element 223.

[0114]

20 A gate of the transistor 201 is electrically connected to a gate signal line 207, one of a source and a drain of the transistor 201 is electrically connected to a video data signal line 210, and the other of the source and the drain of the transistor 201 is electrically connected to one electrode of the storage capacitor 202 and one electrode of the liquid crystal element 203. The other electrode of the storage capacitor 202 is 25 electrically connected to a capacitor wiring 214 and held at a fixed potential. The other electrode of the liquid crystal element 203 is held at a fixed potential. The liquid crystal element 203 is an element including a pair of electrodes and a liquid crystal layer provided between the pair of electrodes.

[0115]

30 When a potential "H" is applied to the gate signal line 207, the transistor 201 supplies the potential of the video data signal line 210 to the storage capacitor 202 and the liquid crystal element 203. The storage capacitor 202 retains the applied potential.

The liquid crystal element 203 changes light transmittance in accordance with the applied potential.

[0116]

One electrode of the photodiode 204 is electrically connected to a photodiode 5 reset signal line 208, and the other electrode of the photodiode 204 is electrically connected to a gate of the transistor 205. One of a source and a drain of the transistor 205 is electrically connected to a photo sensor reference signal line 212, and the other of the source and the drain of the transistor 205 is electrically connected to one of a source 10 and a drain of the transistor 206. A gate of the transistor 206 is electrically connected to a reading signal line 209, and the other of the source and the drain of the transistor 206 is electrically connected to a photo sensor output signal line 211.

[0117]

A gate of the transistor 221 is electrically connected to a gate signal line 227, one of a source and a drain of the transistor 221 is electrically connected to the video 15 data signal line 210, and the other of the source and the drain of the transistor 221 is electrically connected to one electrode of the storage capacitor 222 and one electrode of the liquid crystal element 223. The other electrode of the storage capacitor 222 is electrically connected to a capacitor wiring 224 and held at a fixed potential. The other electrode of the liquid crystal element 223 is held at a fixed potential. The liquid 20 crystal element 223 includes a pair of electrodes and a liquid crystal layer provided between the pair of electrodes.

[0118]

Next, an example of a structure of the photo sensor reading circuit 109 is described with reference to FIG. 12 and FIG. 13. For example, the display portion 25 includes pixels provided in 1024 rows and 768 columns. One display element is provided in one pixel in each row and each column and one photo sensor is provided between two pixels in two rows and one column. That is, the display elements are provided in 1024 rows and 768 columns, and the photo sensors are provided in 512 rows and 768 columns. In addition, this embodiment describes an example in which 30 output to the outside of the display device is performed in the case where photo sensor output signal lines in two columns are regarded as one pair. That is, one output is obtained from two photo sensors provided between four pixels in two rows and two

columns.

[0119]

FIG. 12 illustrates a circuit configuration of pixels, in which two pixels and one photo sensor in two rows and one column are illustrated. One display element is provided in one pixel and one photo sensor is provided between two pixels. FIG. 13 illustrates a circuit configuration of the photo sensor reading circuit 109, in which some photo sensors are illustrated for explanation.

[0120]

As illustrated in FIG. 13, an example of a driving method described below is considered: by a scan line driver circuit of photo sensors, two rows of photo sensors which correspond to four rows of pixels are driven concurrently, and selected rows are shifted by one row of photo sensors which corresponds to two rows of pixels. In that case, each row of photo sensors is successively selected twice by the scan line driver circuit. Such a driving method facilitates improving frame frequency at the time of imaging by a photo sensor. In particular, it is advantageous in the case of a large-sized display device. Note that outputs of photo sensors in two rows are superimposed on the photo sensor output signal line 211 at one time. All of the photo sensors can be driven by repeating shift of selected rows 512 times.

[0121]

As illustrated in FIG. 13, in the photo sensor reading circuit 109, one selector is provided per pixels in 24 columns. The selector selects one pair from 12 pairs of photo sensor output signal lines 211 (one pair corresponds to photo sensor output signal lines 211 in two columns) in the display portion and obtains an output. In other words, the photo sensor reading circuit 109 includes 32 selectors in total and obtains 32 outputs at one time. Selection is performed on all of the 12 pairs in each selector, whereby 384 outputs which correspond to one row of photo sensors can be obtained in total. The selector selects one pair from the 12 pairs every time selected rows are shifted by the scan line driver circuit of photo sensors, whereby outputs from all of the photo sensors can be obtained.

[0122]

In this embodiment, as illustrated in FIG. 13, the following structure is considered: the photo sensor reading circuit 109 on the signal line side takes out outputs

of photo sensors, which are analog signals, to the outside of the display device, and the outputs are amplified with use of an amplifier provided outside the display device and converted to digital signals with use of an AD converter. Needless to say, the following structure may be employed: the AD converter is mounted on a substrate over 5 which the display device is provided, and the outputs of photo sensors are converted to digital signals and then the digital signals are taken out to the outside of the display device.

[0123]

10 In addition, operation of individual photo sensors is realized by repeating reset operation, accumulating operation, and selecting operation. The "reset operation" refers to operation in which the potential of the photodiode reset signal line 208 is set to a potential "H". When the reset operation is performed, the photodiode 204 is brought into conduction, and the potential of a gate signal line 213 connected to the gate of the transistor 205 is set to a potential "H".

15 [0124]

The "accumulating operation" refers to operation in which the potential of the photodiode reset signal line 208 is set to a potential "L" after the reset operation. Further, the "selecting operation" refers to operation in which the potential of the reading signal line 209 is set to a potential "H" after the accumulating operation.

20 [0125]

When the accumulating operation is performed, the potential of the gate signal line 213 to which the gate of the transistor 205 is connected is reduced as light with which the photodiode 204 is irradiated is stronger, and a channel resistance of the transistor 205 is increased. Therefore, when the selecting operation is performed, a 25 current which flows to the photo sensor output signal line 211 through the transistor 206 is small. On the other hand, as the light with which the photodiode 204 is irradiated is weaker at the time of the accumulating operation, a current which flows to the photo sensor output signal line 211 through the transistor 206 is increased at the time of the selecting operation.

30 [0126]

In this embodiment, when the reset operation, the accumulating operation, and

the selecting operation are performed on the photo sensors, a partial shadow of external light can be detected. In addition, when image processing or the like is performed on the detected shadow appropriately, a position where a finger, a pen, or the like touches the display device can be recognized. Operation corresponding to the position where the display device is touched, for example, as for input of letters, kinds of letters are regulated in advance, so that desired letters can be input.

5 [0127]

Note that in the display device in this embodiment, the partial shadow of external light is detected by the photo sensors. Therefore, even if a finger, a pen, or the like does not touch the display device physically, when the finger, the pen, or the like gets close to the display device without contact and a shadow is formed, detection of the shadow is possible. Hereinafter, "a finger, a pen, or the like touches the display device" includes the case where the finger, the pen, or the like is close to the display device without contact.

10 15 [0128]

With the above structure, the display portion 1032 can have a touch-input function.

[0129]

In the case where touch input is performed, the display device has a structure in which an image partly including a still image such as a keyboard is displayed and input is performed by touching a position where a keyboard or a desired letter is displayed with a finger or a pen, whereby operability is improved. In the case where such a display device is realized, power consumption in the display device can be considerably reduced in the following manner. That is, in a first screen region where the still image is displayed on the display portion, it is effective that supply of power to display elements in the first screen region is stopped after the still image is displayed and that a state in which the still image can be seen is kept for a long time after the stop of supply. In a second screen region that is the rest of the display portion, a result from the touch input is displayed, for example. The display element control circuit is in a non-operation state in a period other than the time of updating the displayed image in the second screen region, whereby power can be saved. A driving method which

enables the above control is described below.

[0130]

For example, FIG. 14 shows a timing chart of a shift register of the scan line driver circuit in the display device including the display portion in which the display elements are arranged in 1024 rows and 768 columns. A period 61 in FIG. 14 corresponds to one cycle period (64.8  $\mu$ sec) of a clock signal. A period 62 corresponds to a period (8.36 msec) which is needed for finishing writing of the display elements from a 1st to 512th rows corresponding to the second screen region. A period 63 corresponds to one frame period (16.7 msec).

[0131]

Here, the shift register of the scan line driver circuit is a four-phase-clock-type shift register which is operated by a first clock signal CK1 to a fourth clock signal CK4. In addition, the first clock signal CK1 to the fourth clock signal CK4 are sequentially delayed by a quarter of one cycle period. When a start pulse signal GSP is set to a potential "H", a gate signal line G1 in a 1st row to a gate signal line G512 in a 512th row are set to a potential "H" in sequence with a delay of a quarter of one cycle period. In addition, each of the gate signal lines is set at a potential "H" during half of one cycle period, and two gate signal lines in successive rows are set at a potential "H" concurrently during a quarter of one cycle period.

[0132]

Here, the display elements in each row are continuously selected in a period in which the scan line driver circuit shifts selected rows twice. When data of the displayed image are input in the latter half of a period in which the display elements in the row are selected, the displayed image can be updated.

[0133]

Here, in a period other than a period in which the displayed image by the display elements from the 1st row to the 512th row which correspond to the second screen region is updated, the display element control circuit is in a non-operation state. That is, the displayed image by display elements in a 513th row to a 1024th row corresponding to the first screen region is not updated and the display element control circuit is in a non-operation state.

[0134]

The non-operation state of the display element control circuit can be realized by stopping the clock signal (keeping a clock signal at a potential "L") as shown in FIG. 14. It is effective to stop of supply of power supply voltage at the same time as the 5 stop of the clock signal.

[0135]

In addition, supply of a clock signal and a start pulse signal may be stopped also in the driver circuit on the source in a period in which the display elements corresponding to the second screen region are not selected, that is, in a period in which 10 the displayed image is not updated. In such a manner, power can be further saved.

[0136]

Note that this embodiment can be combined with any of the other embodiments described in this specification as appropriate.

[0137]

15 (Embodiment 5)

In this embodiment, an example of a liquid crystal display module capable of full-color display in which a color filter is provided will be described.

[0138]

FIG. 15 illustrates a structure of a liquid crystal display module 190. The 20 liquid crystal display module 190 includes a display panel 120 in which liquid crystal elements are provided in matrix, and a polarizing plate and a color filter 115 which overlap with the display panel 120. In addition, flexible printed circuits (FPCs) 116a and 116b serving as external input terminals are electrically connected to a terminal portion provided in the display panel 120. The display panel 120 has the same 25 structure as the display panel 100 described in Embodiment 1. Note that since full-color display is employed, the display panel 120 uses three display elements of a red display element, a green display element, and a blue display element and has a circuit configuration in which the three display elements are supplied with respective video signals different from each other.

30 [0139]

Further, FIG. 15 schematically illustrates a state in which external light 139 is transmitted through the liquid crystal elements over the display panel 120 and reflected

at the reflective electrode. For example, in a pixel overlapping with a red region of the color filter, the external light 139 is transmitted through the color filter 115 and then through the liquid crystal layer, reflected at the reflective electrode, and transmitted again through the color filter 115 to be extracted as red light. FIG. 15 schematically 5 illustrates light 135 of three colors by arrows R, G, and B. The intensity of the light which is transmitted through the liquid crystal elements is modulated by an image signal. Therefore, a viewer can capture an image by reflection light of the external light 139.

[0140]

In addition, the display panel 120 includes photo sensors and has a touch-input 10 function. When the color filter also overlaps with a light-receiving region of photo sensors, the photo sensors can also function as a visible light sensor. Further, in order to improve the optical sensitivity of the photo sensor, a large amount of incident light is taken in. Therefore, an opening may be provided in the color filter in a region overlapping with the light-receiving region of photo sensors so that the light-receiving 15 region of photo sensors and the color filter do not overlap with each other.

[0141]

Note that this embodiment can be combined with any of the other embodiments described in this specification as appropriate.

[0142]

20 (Embodiment 6)

In this embodiment, an example of a transistor including an oxide semiconductor layer, which is used for the liquid crystal display devices described in Embodiments 1 to 3, and an example of a manufacturing method of the transistor will be described in detail with reference to FIGS. 18A to 18E. The same portion as or a 25 portion having a function similar to that in the above embodiments can be formed in a manner similar to that described in the above embodiments, and also the steps similar to those in the above embodiments can be performed in a manner similar to that described in the above embodiments, and repetitive description is omitted. In addition, detailed description of the same portions is not repeated.

30 [0143]

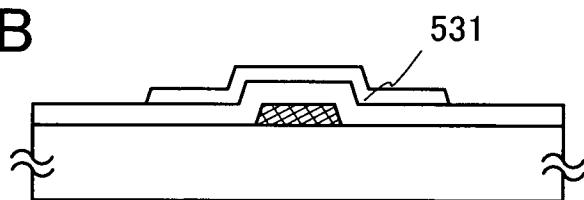

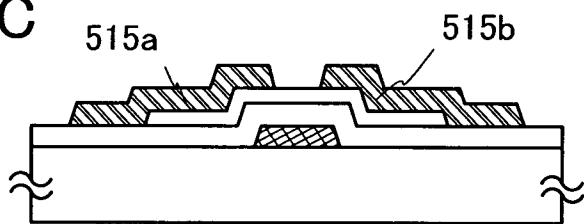

FIGS. 18A to 18E illustrate an example of a cross-sectional structure of a transistor. A transistor 510 illustrated in FIGS. 18A to 18E is an inverted staggered

transistor with a bottom gate structure which is similar to that of the transistor 350 illustrated in FIG. 1A.

[0144]

A process for manufacturing the transistor 510 over a substrate 505 will be 5 described below with reference to FIGS. 18A to 18E.

[0145]

First, a conductive film is formed over the substrate 505 having an insulating surface, and then, a gate electrode layer 511 is formed through a first photolithography process. Note that a resist mask may be formed by an inkjet method. Formation of 10 the resist mask by an inkjet method needs no photomask; thus, manufacturing cost can be reduced.

[0146]

In this embodiment, a glass substrate is used as the substrate 505 having an insulating surface.

15 [0147]

An insulating film serving as a base film may be provided between the substrate 505 and the gate electrode layer 511. The base film has a function of preventing diffusion of an impurity element from the substrate 505. The base film can be formed with a single-layer structure or a layered structure including one or more of a 20 silicon nitride film, a silicon oxide film, a silicon nitride oxide film, and a silicon oxynitride film.

[0148]