(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-279049

(P2006-279049A)

(43) 公開日 平成18年10月12日(2006.10.12)

|                              |             |             |

|------------------------------|-------------|-------------|

| (51) Int.C1.                 | F 1         | テーマコード (参考) |

| <b>HO1L 21/336 (2006.01)</b> | HO1L 29/78  | 612D        |

| <b>HO1L 29/786 (2006.01)</b> | GO2F 1/1368 | 5F11O       |

| <b>GO2F 1/1368 (2006.01)</b> | HO1L 29/78  | 626C        |

審査請求 未請求 請求項の数 9 O L (全 18 頁)

|              |                            |            |                                                                                             |

|--------------|----------------------------|------------|---------------------------------------------------------------------------------------------|

| (21) 出願番号    | 特願2006-86916 (P2006-86916) | (71) 出願人   | 390019839<br>三星電子株式会社<br>Samsung Electronics<br>Co., Ltd.<br>大韓民国443-742京畿道水原市靈通<br>区梅灘洞416 |

| (22) 出願日     | 平成18年3月28日 (2006.3.28)     | (74) 代理人   | 100094145<br>弁理士 小野 由己男                                                                     |

| (31) 優先権主張番号 | 10-2005-0026015            | (74) 代理人   | 100106367<br>弁理士 稲積 朋子                                                                      |

| (32) 優先日     | 平成17年3月29日 (2005.3.29)     | (72) 発明者   | 崔 泰 榮<br>大韓民国ソウル市城北区敦岩1洞ヒョンデ<br>アパート102棟605号                                                |

| (33) 優先権主張国  | 韓国 (KR)                    | F ターム (参考) | 2H092 GA11 GA31 JA24 JA28 JA37<br>JA41 JB57 KB24 NA11 NA27                                  |

|              |                            |            | 最終頁に続く                                                                                      |

(54) 【発明の名称】薄膜トランジスタ表示板の製造方法

## (57) 【要約】

【課題】プラスチック基板の熱膨張による整列誤差を最小化する。

【解決手段】第1間隔Lを有する複数のゲート電極を含むゲート線121を、熱膨張率を有する基板上に形成する段階；ゲート線121上にゲート絶縁膜140及び半導体層150,160を形成する段階；半導体層150,160を第1間隔Lと異なる第2間隔L+αを有する半導体用マスクでパターニングし、複数の半導体部材154,164を形成する段階、半導体部材154,164及びゲート絶縁膜140上にソース電極を含むデータ線171及びソース電極と対向するドレイン電極175を形成する段階；ドレイン電極と接続されている画素電極を形成する段階；を含む。

【選択図】図12C

**【特許請求の範囲】****【請求項 1】**

第1間隔を有する複数のゲート電極を含むゲート線を、熱膨張率を有する基板上に形成する段階と、

前記ゲート線上にゲート絶縁膜及び半導体層を形成する段階と、

前記半導体層を前記第1間隔と異なる第2間隔を有する半導体用マスクでパターニングし、複数の半導体部材を形成する段階と、

前記半導体部材及びゲート絶縁膜上にソース電極を含むデータ線及び前記ソース電極と対向するドレイン電極を形成する段階と、

前記ドレイン電極と接続されている画素電極を形成する段階と、

を含む薄膜トランジスタ表示板の製造方法。

**【請求項 2】**

前記第2間隔は、前記第1間隔と前記基板の熱膨張率によって変化する間隔との和である、請求項1に記載の薄膜トランジスタ表示板の製造方法。

**【請求項 3】**

前記第2間隔は前記第1間隔より100乃至500ppm広い、請求項1または2に記載の薄膜トランジスタ表示板の製造方法。

**【請求項 4】**

前記半導体部材を形成する段階は、前記半導体層をパターニングすることにより、前記半導体部材を島状に形成する、請求項1に記載の薄膜トランジスタ表示板の製造方法。

**【請求項 5】**

前記ゲート線を形成する段階の前に、前記基板の上部及び下部のうちの少なくとも一つに基板保護膜を形成する段階をさらに含む、請求項1に記載の薄膜トランジスタ表示板の製造方法。

**【請求項 6】**

前記画素電極を形成する段階の前に、絶縁物質からなる保護膜を形成する段階をさらに含む、請求項1に記載の薄膜トランジスタ表示板の製造方法。

**【請求項 7】**

前記保護膜を形成する段階は、無機物質からなる第1保護膜を形成する段階及び有機物質からなる第2保護膜を形成する段階を含む、請求項6に記載の薄膜トランジスタ表示板の製造方法。

**【請求項 8】**

前記ゲート絶縁膜及び半導体層を形成する段階の後に、不純物がドーピングされている非晶質ケイ素からなる抵抗性接触層を形成する段階を連続的に遂行する、請求項1に記載の薄膜トランジスタ表示板の製造方法。

**【請求項 9】**

前記画素電極を形成する段階の前に、カラーフィルタを形成する段階をさらに含む、請求項1に記載の薄膜トランジスタ表示板の製造方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は薄膜トランジスタ表示板の製造方法に関し、より詳しくは、プラスチック基板を含む薄膜トランジスタ表示板の製造方法に関する。

**【背景技術】****【0002】**

現在、広く使用されている平板表示装置のうちの代表的なものが液晶表示装置及び有機発光表示素子である。

液晶表示装置は、一般に、電界生成電極と偏光板が具備された一対の表示板の間に位置した液晶層を含む。電界生成電極は、液晶層に電界を生成し、このような電界の強さが変化することによって、液晶分子の配列が変化する。例えば、電界が印加された状態で液晶

10

20

30

40

50

層の液晶分子はその配列を変化させ、液晶層を透過する光を偏光させる。ここに偏光フィルタを適切に配置すれば、偏光フィルタが偏光された光を遮断して暗い領域を形成することによって、所望の映像を表示する。

### 【0003】

有機発光表示装置は、正孔注入電極（アノード）と電子注入電極（カソード）とこれら間に形成されている有機発光層を含み、アノードから注入される正孔とカソードから注入される電子が有機発光層で再結合して消滅しながら発光する自発光型表示装置である。

しかし、このような液晶表示装置または有機発光表示装置は、重くて破損しやすいガラス基板を使用するため、携帯性及び大画面表示に限界がある。

### 【0004】

従って、近来、重量が軽く、衝撃に強いだけでなく、プラスチックなどの可撓性基板を使用する表示装置が開発されている。

### 【発明の開示】

#### 【発明が解決しようとする課題】

### 【0005】

既存のガラス基板の代わりに柔軟性のあるプラスチック基板を利用することによって、携帯性、安全性及び軽量性等で既存のガラス基板に比べて多くの利点を有することができる。また、工程的な側面においても、プラスチック基板は蒸着またはプリントイングによって製作が可能であるので、製造費用を低くすることができ、既存のシート単位の工程とは異なって、ロール・トゥ・ロール工程によって表示装置を製作することができるので、大量生産による低費用の表示装置を製造することができる。

### 【0006】

しかし、プラスチック基板は熱に弱いため、高温段階で容易に膨脹するという問題点がある。従って、プラスチック基板の製造工程では、膨脹に起因したパターン間の整列誤差が発生する。

本発明は上記問題点を解決するためのものであって、本発明の目的は、プラスチック基板の熱膨張による整列誤差を最小化することができる薄膜トランジスタ表示板の製造方法を提供する。

### 【課題を解決するための手段】

### 【0007】

本発明1は、下記の段階を含む薄膜トランジスタ表示板の製造方法を提供する。

- ・第1間隔を有する複数のゲート電極を含むゲート線を、熱膨張率を有する基板上に形成する段階、

- ・前記ゲート線上にゲート絶縁膜及び半導体層を形成する段階、

- ・前記半導体層を前記第1間隔と異なる第2間隔を有する半導体用マスクでパターニングし、複数の半導体部材を形成する段階、

- ・前記半導体部材及びゲート絶縁膜上にソース電極を含むデータ線及び前記ソース電極と対向するドレイン電極を形成する段階、

- ・前記ドレイン電極と接続されている画素電極を形成する段階。

### 【0008】

この発明によれば、基板の熱膨張率を考慮してパターンの間の間隔を調節したマスクを利用してパターニングすることによって、下部パターンと上部パターンの整列誤差を最小化することができる。

本発明2は、発明1において、前記第2間隔が、前記第1間隔と前記基板の熱膨張率によって変化する間隔との和である薄膜トランジスタ表示板の製造方法を提供する。

### 【0009】

本発明3は、前記発明1または2において、前記第2間隔が前記第1間隔より100乃至500 ppm広い薄膜トランジスタ表示板の製造方法を提供する。

本発明4は、前記発明1において、前記半導体部材を形成する段階が、前記半導体層をパターニングすることにより、前記半導体部材を島状に形成する薄膜トランジスタ表示板

10

20

30

40

50

の製造方法を提供する。

#### 【0010】

本発明5は、前記発明1において、前記ゲート線を形成する段階の前に、前記基板の上部及び下部のうちの少なくとも一つに基板保護膜を形成する段階をさらに含む、薄膜トランジスタ表示板の製造方法を提供する。

基板保護膜は、外部からの酸素や水分などの通過を防ぐ役割を果たす。

本発明6は、前記発明1において、前記画素電極を形成する段階の前に、絶縁物質からなる保護膜を形成する段階を含む薄膜トランジスタ表示板の製造方法を提供する。

#### 【0011】

本発明7は、前記発明6において、前記保護膜を形成する段階が、無機物質からなる第1保護膜を形成する段階及び有機物質からなる第2保護膜を形成する段階を含む、薄膜トランジスタ表示板の製造方法を提供する。

本発明8は、前記発明1において、前記ゲート絶縁膜及び半導体層を形成する段階の後に、不純物がドーピングされている非晶質ケイ素からなる抵抗性接触層を形成する段階を連続的に遂行する薄膜トランジスタ表示板の製造方法を提供する。

#### 【0012】

本発明9は、前記発明1において、前記画素電極を形成する段階の前に、カラーフィルタを形成する段階をさらに含む、薄膜トランジスタ表示板の製造方法を提供する。

#### 【発明の効果】

#### 【0013】

本発明を用いれば、プラスチック基板の熱膨張による整列誤差を低減することができる。

#### 【発明を実施するための最良の形態】

#### 【0014】

以下、添付した図面を参照して、本発明の実施形態について本発明の属する技術分野における通常の知識を有する者が容易に実施できるように詳細に説明する。しかし、本発明は多様な相異な形態に実現でき、ここで説明する実施形態に限定されない。

図面において、複数の層及び領域を明確に表現するために厚さを拡大して示した。明細書全体にわたって類似する部分については同一の図面符号を付した。層、膜、領域、板などの部分が他の部分の“上に”あるとする時、これは他の部分の“すぐ上に”ある場合だけでなく、その中間に他の部分がある場合も含む。逆に、ある部分が他の部分の“すぐ上に”あるとする時には、中間に他の部分がないことを意味する。

#### <実施形態1>

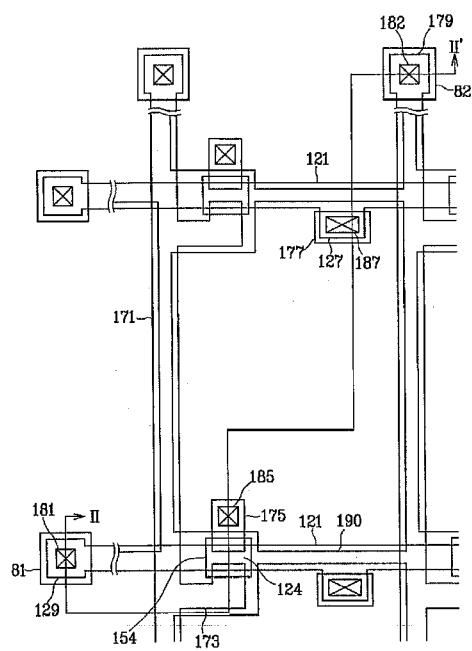

まず、図1及び図2を参照して、本発明の一実施形態による薄膜トランジスタ表示板について詳細に説明する。

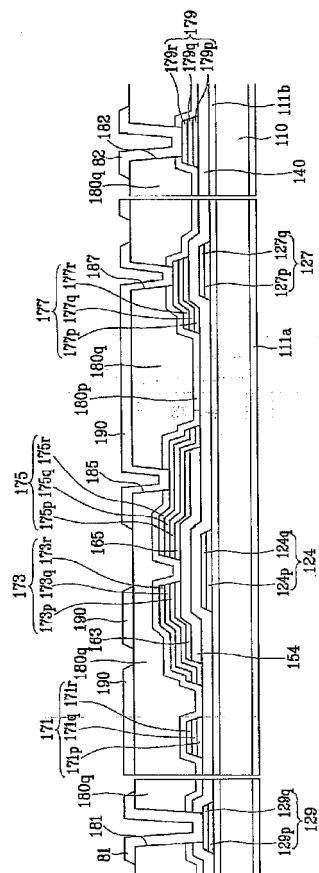

#### 【0015】

本実施形態による薄膜トランジスタ表示板は、基板110の下部及び上部に酸化ケイ素(SiO<sub>2</sub>)または窒化ケイ素(SiN<sub>x</sub>)のような無機物質または有機物質などからなる基板保護膜111a、111bが設けられている。

基板110は、例えば、ポリアクリレート、ポリエチレンエーテルフタレート、ポリエチレンナフタレート、ポリカーボネート、ポリアリレート、ポリエーテルイミド、ポリエーテルスルホンまたはポリイミドなどより選択された1種または2種以上のプラスチック素材からなり、2つ以上の層が重畳することができる。

#### 【0016】

基板保護膜111a、111bは、外部から酸素または水分が流入することを防止する役割を果たし、プラスチック基板110の下部及び上部に全て形成することが好ましいが、下部及び上部のうちのいずれか一つにだけ形成することもでき、場合によって省略することもできる。

基板保護膜111b上にはゲート信号を伝達する複数のゲート線121が形成されている。ゲート線121は横方向に延在しており、各ゲート線121の一部は、複数のゲート

10

20

30

40

50

電極 124、拡張部 127、及び外部回路の接続のために拡張された幅を有するゲート線の端部 129を含む。

【0017】

ゲート線 121は、物理的性質が異なる二つの膜、つまり、下部膜 121pとその上の上部膜 121qを含む。下部膜 121pはゲート信号の遅延や電圧降下を減らすことができるよう 10 に低い比抵抗の金属、例えば、アルミニウム (A1) やアルミニウム合金などアルミニウム系金属からなる。これとは異なって、上部膜 121qは他の物質、特にIZO (indium zinc oxide)との物理的、化学的、電気的接触特性に優れた物質、例えば、モリブデン (Mo)、モリブデン合金 [例:モリブデン-タンゲステン (MoW)合金]、クロム (Cr)などからなる。下部膜 121pと上部膜 121qの組み合 12 10 わせの例としては、アルミニウム (アルミニウム合金) /モリブデン (モリブデン合金)がある。図2において、ゲート電極 124の下部膜と上部膜は各々図面符号 124p、124qに、拡張部 127の下部膜と上部膜は各々図面符号 127p、127qに、ゲート線の端部 129の下部膜と上部膜は 129p、129qで示している。

【0018】

ゲート線 124の側面は傾斜しており、その傾斜角は基板 110の表面に対して約 30 乃至 80°をなす。

ゲート線 121上には、窒化ケイ素 (SiNx)などからなるゲート絶縁膜 140が形成されている。

ゲート絶縁膜 140上部には、水素化非晶質シリコンなどからなる島状半導体部材 15 20 4が形成されている。

【0019】

島状半導体部材 154の上部には、シリサイドまたはn型不純物が高濃度にドーピング 20 5 25 30 されているn+水素化非晶質ケイ素などの物質からなる島状抵抗性接触部材 163、165が形成されている。島状抵抗性接触部材 163、165は対をなして島状半導体部材 154上に設けられている。島状抵抗性接触部材 163、165は、島状半導体部材 154とその上部のソース電極 173及びドレイン電極 175の間に存在し、接触抵抗を低くする役割を果たす。

【0020】

島状半導体部材 154と島状抵抗性接触部材 163、165の側面も傾斜しており、傾 30 斜角は基板 110に対して 30乃至 80°である。

抵抗性接触部材 163、165及びゲート絶縁膜 140上には、各々複数のデータ線 171、複数のドレイン電極 175、及び複数のストレージキャパシタ用導電体 177が形成されている。

【0021】

データ線 171は、縦方向に延在してゲート線 121と交差し、データ電圧を伝達する。各データ線 171は、外部回路の接続のために拡張された幅を有するゲート線の端部 179、及びドレイン電極 175に向かって延在した複数の分岐がソース電極 173を含む。一対のソース電極 173とドレイン電極 175は互いに分離されており、ゲート電極 124に対して互いに反対側に位置している。ゲート電極 124、ソース電極 173及びド 40 レイン電極 175は、島状半導体層 154と共に薄膜トランジスタ (TFT)をなし、薄膜トランジスタのチャンネルは、ソース電極 173とドレイン電極 175の間の島状半導体層 154に形成される。

【0022】

ストレージキャパシタ用導電体 177は、ゲート線 121の拡張部 127と重畠している。

ソース電極 173を含むデータ線 171及びドレイン電極 175は、クロム (Cr)、アルミニウム (A1) またはモリブデン (Mo)などからなる単一層、二重層または三重層に形成できる。このうち、三重層に形成する場合、第1金属層 171p、173p、175p、177pは、下部層との接着性が優れて、半導体層をなすケイ素への拡散を防止 50

する金属にて形成し、第3金属層171r、173r、175r、177rは、ITOまたはIZO接着性に優れた金属にて形成される。好ましくは、モリブデン(Mo)を含む第1金属層171p、173p、175p、177p、アルミニウム(Al)を含む第2金属層171q、173q、175q、177q、及びモリブデン(Mo)を含む第3金属層171r、173r、175r、177rが順次に形成することができる。

#### 【0023】

データ線171、ドレイン電極175及びストレージキャパシタ用導電体177もゲート線121と同様に、その側面が基板110に対して約30乃至80°の角度で各々傾斜している。

島状抵抗性接触部材163、165は、島状半導体層154とその上部のソース電極173及びドレイン電極175の間に存在し、接触抵抗を低くする役割を果たす。 10

#### 【0024】

データ線171、ドレイン電極175及びストレージキャパシタ用導電体177上には、保護膜180p、180qが形成されている。

保護膜180p、180qは、窒化ケイ素(SiNx)などからなる下部保護膜180pと、有機物質からなる上部保護膜180qが形成されている。下部保護膜180pは約500乃至2000の厚さに形成されており、上部保護膜180qは約2乃至3.5μmの厚さに形成されている。有機物質からなる上部保護膜180qは、データ線171、ドレイン電極175及びストレージキャパシタ用導電体177と上部膜との整列誤差を相殺してクロス・トークが発生することを防止する。 20

#### 【0025】

保護膜180p、180qには、ドレイン電極175、ストレージキャパシタ用導電体177、ゲート線の端部129及びデータ線の端部179を各々露出させる複数の接触孔185、187、181、182が形成されている。

保護膜180p、180q上には、ITOまたはIZOからなる複数の画素電極190及び複数の接触補助部材81、82が形成されている。

#### 【0026】

画素電極190は、接触孔185、187を通じてドレイン電極175及びストレージキャパシタ用導電体177と各々物理的・電気的に接続され、ドレイン電極175からデータ電圧の印加を受け、ストレージキャパシタ用導電体177にデータ電圧を伝達する。 30

データ電圧が印加された画素電極190は、共通電圧の印加を受ける他の表示板(図示せず)の共通電極(図示せず)と共に電場を生成することによって、液晶層の液晶分子を再配列させる。

#### 【0027】

接触補助部材81、82は、接触孔181、182を通じてゲート線の端部129とデータ線の端部179に各々接続される。接触補助部材81、82は、ゲート線の端部129またはデータ線の端部179と駆動集積回路のような外部装置との接着性を補完し、これらを保護する。

以下、図3乃至図8Bを参照して、本発明の一実施形態による薄膜トランジスタ表示板の製造方法について説明する。 40

#### 【0028】

プラスチック素材からなる基板110は、ポリアクリレート、ポリエチレンエーテルフタレート、ポリエチレンナフタレート、ポリカーボネート、ポリアリレート、ポリエーテルイミド、ポリエーテルスルホンまたはポリイミド等より選択された1種または2種以上などからなり、2つ以上の層を重畳して形成することもできる。

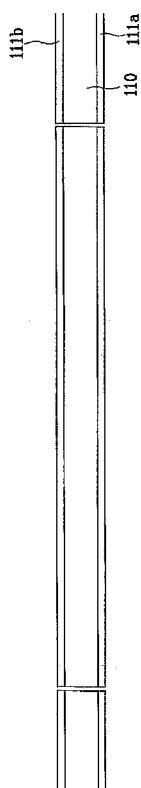

図3に示したように、基板110の下部及び上部に基板保護膜111a、111bを形成する。基板保護膜111a、111bは、例えば酸化ケイ素(SiO<sub>2</sub>)または窒化ケイ素(SiNx)を化学気相蒸着方法によって形成する。基板保護膜111a、111bは、プラスチック基板110の下部及び上部の両方に形成することが好ましいが、下部及び上部のうちのいずれか一つにだけ形成することもでき、場合によっては省略することも 50

できる。基板保護膜 111a、111b は、外部からの酸素または水分等の通過を防ぐ役割を果たす。

【0029】

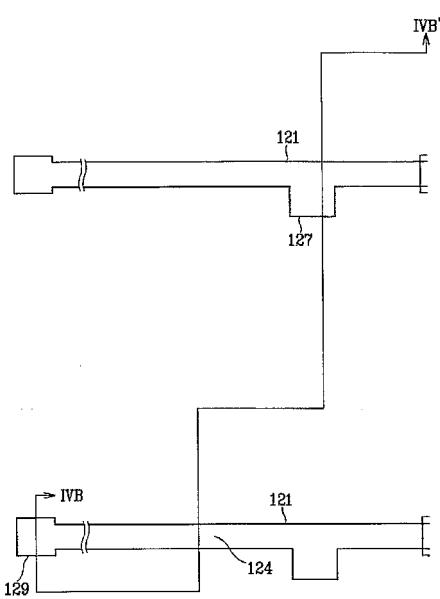

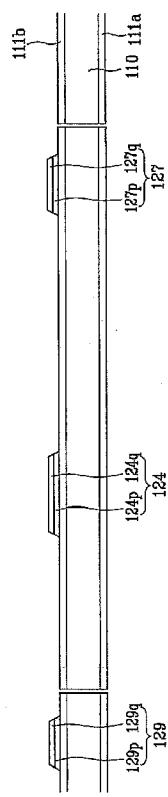

次に、図4A及び図4Bに示したように、基板保護膜111b上にゲート電極124、拡張部127及び外部回路接続部であるゲート線の端部129を含むゲート線121を形成する。

ゲート電極124、複数の拡張部127及びゲート線の端部129を含むゲート線121は、単一層または二重層に形成することができ、本実施形態ではアルミニウム(A1)またはアルミニウムにネオジム(Nd)が所定量添加されたアルミニウム合金(A1-Nd)を含む下部金属層124p、127p、129p、及びモリブデン(Mo)を含む上部金属層124q、127q、129qからなる二重層に形成する。

10

【0030】

下部金属層及び上部金属層は、co-sputtering (Co-sputtering) によって形成する。co-sputteringのターゲットとしては、例えば、アルミニウム(A1)にネオジム(Nd)が所定量添加されたアルミニウム合金(A1-Nd)とモリブデン(Mo)を用いる。

初期にモリブデン合金ターゲットにはパワーを印加せず、アルミニウム合金ターゲットにだけパワーを印加して、基板110上にアルミニウムまたはアルミニウム合金からなる下部金属層を形成する。この場合、約2、500程度の厚さを有することが好ましい。

【0031】

次に、アルミニウム合金ターゲットに印加されるパワーをオフした後、モリブデンに印加されるパワーを印加して上部金属層を形成する。

その後、下部金属層及び上部金属層を一度にエッチングして、複数のゲート電極124、複数の拡張部127及び外部回路接続部であるゲート線の端部129を含むゲート線121を完成する。

20

【0032】

次に、図5に示したように、ゲート電極124、複数の拡張部127及びゲート線の端部129を含むゲート線121の全面を覆うように、窒化ケイ素(SiNx)または酸化ケイ素(SiO<sub>2</sub>)を蒸着してゲート絶縁膜140を形成する。

次いで、ゲート絶縁膜140上に真性非晶質シリコン層(inttrinsic amorphous silicon)150と、不純物がドーピングされた非晶質シリコン層(extrinsic amorphous silicon)160を連続して積層する。

30

【0033】

ゲート絶縁膜140、真性非晶質シリコン層150、不純物がドーピングされた非晶質シリコン層160は約110乃至180、好ましくは、約150の温度で、各々約2、000乃至5,000、1000乃至3500及び200乃至1000の厚さに形成する。

この段階で、プラスチック素材からなる基板110は熱膨張する。プラスチック基板は素材によって多少差はあるが、一般に、約50 ppm/K乃至60 ppm/Kの熱膨張係数(Coefficient of Thermal Expansion, CTE)を有する。従って、基板110は前記ゲート絶縁膜140、真性非晶質シリコン層150、不純物がドーピングされた非晶質シリコン層160の形成段階で膨張する。

40

【0034】

このような基板110の膨張によって、基板110の上部に形成されているゲート電極124、複数の拡張部127及びゲート線の端部129を含むゲート線121も本来の位置からずれるようになる。

そうすると、本来のゲート電極124の位置を基準として真性非晶質シリコン層150、不純物がドーピングされた非晶質シリコン層160をエッチングし、複数の島状半導体部材154及び抵抗性接触部材164を含む半導体パターンを形成すると、ゲート電極1

50

24と島状半導体部材154及び抵抗性接触部材164との整列誤差が大きくなつて、正確な位置に薄膜トランジスタのチャンネルを形成することが難しい。

【0035】

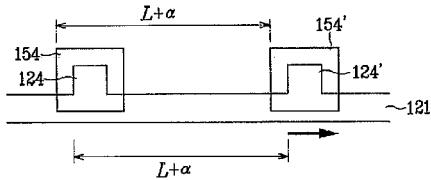

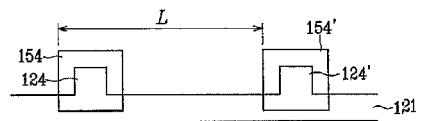

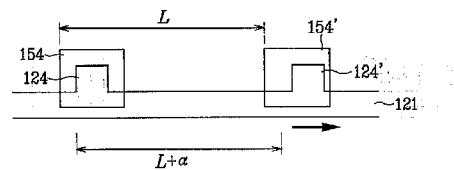

図12は、基板の熱膨張によって、下部のゲート電極124と上部の島状半導体部材154及び抵抗性接触部材164の間に発生する整列誤差を示す模式図である。

図12Aは、熱膨張率が極めてわずかであるガラス基板上に、複数のゲート電極124を含むゲート線121と半導体パターンを順次に形成した場合、隣接するゲート電極124、124'に隣接する島状半導体部材154、154'の間に正確に整列された状態を示す。

【0036】

具体的には、所定間隔Lを有するゲート用マスクを利用してゲート電極124、124'を含むゲート線121を形成した後、前記ゲート電極の中心部の間隔Lと同一の間隔Lを有する半導体用マスクを利用して島状半導体部材154、154'を形成する。この場合、基板の熱膨張によるゲート線121の位置変化がないため、ゲート電極124、124'の中心部と島状半導体部材154、154'の中心部とが一致して正確な整列が行われる。

【0037】

これに対し、図12Bは、約40ppm/K乃至50ppm/Kの熱膨張率を有するプラスチック素材の基板上にゲート線121と半導体パターンを順次に形成した場合、隣接するゲート電極124、124'に隣接する島状半導体部材154、154'との間に整列誤差が発生した状態を示す。

まず、上記と同様に、所定間隔Lを有するゲート用マスクを利用してゲート電極124、124'を含むゲート線121を形成する。次に、約110乃至180でゲート絶縁膜140、真性非晶質シリコン層150及び不純物がドーピングされた非晶質シリコン層160を形成する場合、基板が膨脹しながら前記基板上に形成されているゲート線121の位置も変化して、隣接するゲート電極124、124'の中心部の間隔が、間隔Lから間隔L+に広がる。従って、本来のゲート電極の中心部と同一の間隔Lを有する半導体用マスクを利用して島状半導体部材154、154'を形成する場合、隣接するゲート電極124、124'の中心部の間の間隔L+と、隣接する島状半導体部材154、154'の中心部の間の間隔Lが一致しないため、整列誤差が発生する。

【0038】

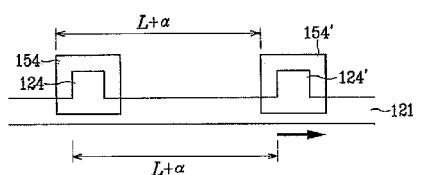

従って、本発明では、前記整列誤差を最小化するために、基板の熱膨張率だけ間隔を広げたマスクパターンを利用して島状半導体部材154、154'を形成する。

図12Cは、本発明によるパターン形成方法を示す。

まず、所定間隔Lを有するゲート用マスクを利用してゲート線121、ゲート電極124、124'を形成する。次に、約110乃至180でゲート絶縁膜140及び真性非晶質シリコン層150を形成する場合、基板が所定比率で膨脹するとき前記基板上に形成されているゲート線121の位置も変化して、隣接するゲート電極124、124'の間の間隔Lが間隔L+に広がる。次いで、前記ゲート電極124、124'の中心部の間隔Lに基板の熱膨張率を考慮した間隔L'を加えた間隔L+のパターンを含んだ半導体用マスクを利用して、各ゲート電極124、124'上に、島状半導体部材154、154'を含む半導体パターンをそれぞれ形成する。この場合、基板の熱膨張によるゲート線121の位置変化を考慮したので、ゲート電極124、124'の中心部と半導体パターン154、154'の中心部とが一致して、正確な整列が行われる。一般に、プラスチック素材からなる基板の熱膨張率を考慮する場合、前記広くなる間隔L'は、約100乃至500ppmである。

【0039】

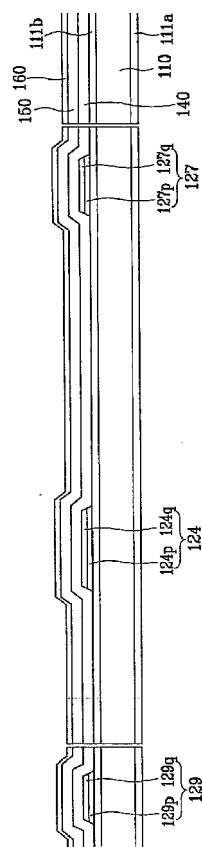

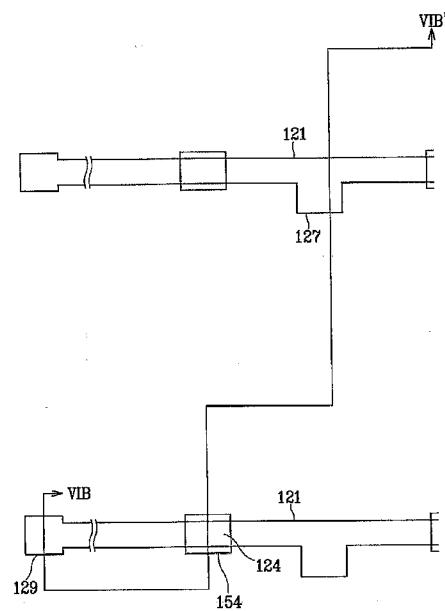

これによって、図6A及び図6Bに示したように、ゲート電極124上に正確に整列された島状半導体部材154及び抵抗性接触部材164が形成される。

次に、図7A及び図7Bに示したように、ゲート絶縁膜140及び抵抗性接触部材164

10

20

30

40

50

上にスパッタリングなどの方法によって金属層を形成する。金属層は単一層、二重層または三重層に形成できるが、本実施形態では、モリブデン(Mo)を含む第1金属層171p、173p、175p、177p、179p、アルミニウム(Al)を含む第2金属層171q、173q、175q、177q、179q、及びモリブデン(Mo)を含む第3金属層171r、173r、175r、177r、179rを順次に形成する。第1金属層171p、173p、175p、177p、179p、第2金属層171q、173q、175q、177q、179q、及び第3金属層171r、173r、175r、177r、179rを全て合せて約3000程度の厚さに形成する。

## 【0040】

次に、前記金属層をエッティング液で一度に写真エッティングして、ソース電極173、ドレイン電極175、ストレージキャパシタ用導電体177及びデータ線の端部179を形成する。 10

次に、ソース電極173及びドレイン電極175の間の抵抗性接触部材164を乾式エッティングして島状抵抗性接触部材163、165として形成する。

## 【0041】

次いで、図8A及び図8Bに示したように、ソース電極173、ドレイン電極175、ストレージキャパシタ用導電体177及びデータ線の端部179を覆う保護膜180p、180qを形成する。

保護膜180p、180qは、窒化ケイ素(SiNx)などからなる下部保護膜180pと、ポリイミド(polyimide)などの有機物質からなる上部保護膜180qを含む二重層に形成する。この場合、下部保護膜180pは約500乃至2000の厚さに形成し、上部保護膜180qは約2乃至3.5μmの厚さに形成する。 20

## 【0042】

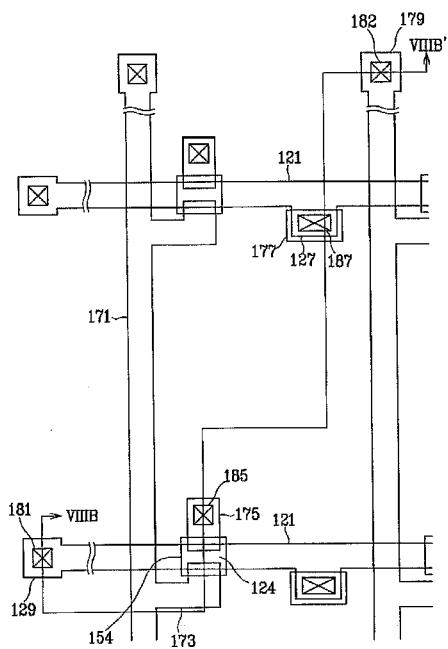

次に、下部保護膜180pと上部保護膜180q内に、マスクを利用した写真エッティング工程によって、ドレイン電極175、ストレージキャパシタ用導電体177、ゲート線の端部129及びデータ線の端部179を各々露出させる接触孔185、187、181、182を形成する。

最後に、図1及び図2に示したように、ドレイン電極175と接触孔185を通じて接続される画素電極190と接触補助部材81、82などを保護膜180上に形成する。

## 【0043】

上述のように、下部保護膜180pと有機物質からなる上部保護膜180qを含む2層の保護膜を形成することによって、ソース電極173、ドレイン電極175、ストレージキャパシタ用導電体177及びデータ線の端部179と、以後に形成されるITOまたはIZOからなる画素電極190及び接触補助部材81、82との整列誤差を相殺して、クロス・トークを防止することができる。 30

## &lt;実施形態2&gt;

まず、図9A及び図9Bを参照して、本発明の一実施形態による薄膜トランジスタ表示板について詳細に説明する。

## 【0044】

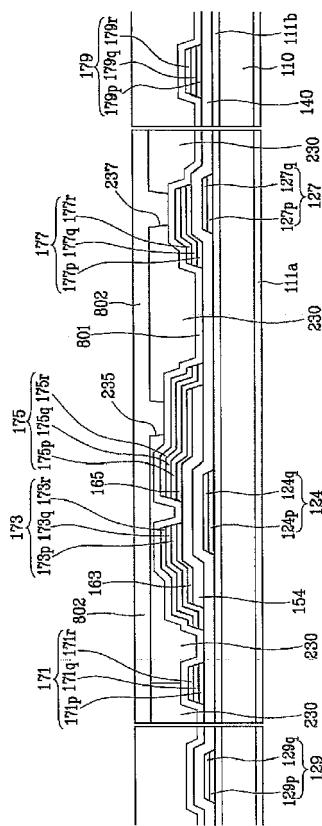

図9A及び9Bに示したように、本実施形態による液晶表示装置用薄膜トランジスタ表示板の層状構造は、ほとんど図1及び図2に示した液晶表示装置用薄膜トランジスタ表示板の層状構造と同一である。 40

つまり、プラスチック基板110上に複数のゲート電極124、複数の突出部127及び複数の端部129を各々含む複数のゲート線121が形成されており、その上にゲート絶縁膜140、複数の島状半導体部材154、複数の島状抵抗性接触部材163、165が順次に形成されている。島状抵抗性接触部材163、165及びゲート絶縁膜140上には、複数のソース電極173を含む複数のデータ線171、複数のドレイン電極175及びストレージキャパシタ用導電体177が形成されており、その上に下部及び上部保護膜180p、180qが形成されている。次いで、下部及び上部保護膜180p、180q及び/またはゲート絶縁膜140には複数の接触孔181、182、185、187が 50

形成されており、上部保護膜 180q 上には複数の画素電極 190 と複数の接触補助部材 81、82 が形成されている。

【0045】

しかし、下部保護膜 180p 上にはカラーフィルタ 230 が形成されている。カラーフィルタ 230 はデータ線 171 によって区画される画素列に沿ってデータ線 171 と並んでいる方向に長く延在している。カラーフィルタ 230 は赤色、緑色及び青色のうちのいずれか一つの色相を表現することができる。下部保護膜 180p はカラーフィルタ 230 の顔料が半導体層 154 に流入することを防止する。

【0046】

ここで、カラーフィルタ 230 は、外部回路と接合されるゲート線の端部 129 及びデータ線の端部 179 には形成しない。そして、これらカラーフィルタ 230 の周縁はデータ線 171 上部で重畠しており、このようにカラーフィルタ 230 の周縁を重畠して形成することによって、画素領域の間で漏洩される光を遮断する機能を有し、データ線 171 上部で互いに隣接するカラーフィルタ 230 を共に重畠して配置することもでき、互いに重畠する周縁部は、液晶分子の配列が歪曲されることを防止するための平坦化のために、データ線 171 の間に位置する中央部より薄い厚さを有することが好ましい。

【0047】

カラーフィルタ 230 上の上部保護膜 180q は、カラーフィルタ 230 の顔料が画素電極 190 に流入することを防止し、省略することができる。

以下、図 3 乃至図 7B 及び図 10A 乃至図 11B を参照して、図 9A 及び図 9B に示した本発明の他の一実施形態による薄膜トランジスタ表示板の製造方法について詳細に説明する。

【0048】

まず、図 3 乃至図 7B に示したように、プラスチック素材からなるプラスチック基板 10 上に、複数のゲート電極 124、複数の突出部 127 及び複数の端部 129 を各々含む複数のゲート線 121 を形成し、その上にゲート絶縁膜 140 を形成する。次に、上述の実施形態と同一に、複数の島状半導体部材 154 及び複数の島状抵抗性接触部材 163、165 を形成し、その上に複数のソース電極 173 を含む複数のデータ線 171、複数のドレイン電極 175 及びストレージキャパシタ用導電体 177 を形成する。

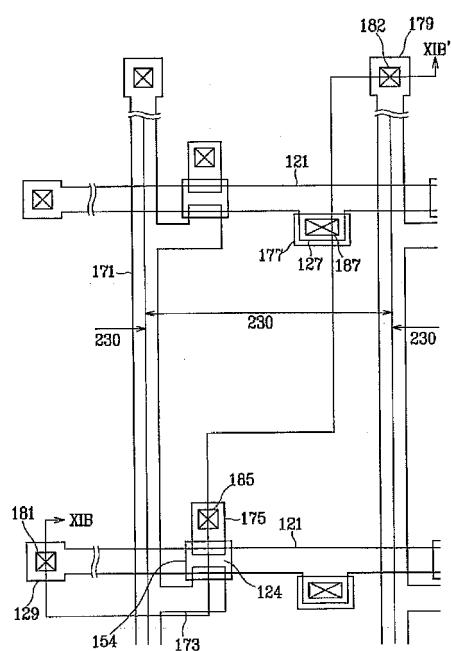

【0049】

次いで、図 10A 及び図 10B に示したように、ソース電極 173、ドレイン電極 175、ストレージキャパシタ用導電体 177、データ線の端部 179 及びゲート絶縁膜 140 を覆う下部保護膜 180p を形成する。

次に、下部保護膜 180p 上に赤色、緑色及び青色顔料を含む感光性有機物質を各々順次に塗布し、それぞれの写真工程によって赤色、緑色及び青色のカラーフィルタ 230 を順次に形成する。

【0050】

カラーフィルタ 230 を形成する時、ドレイン電極 175 及びストレージキャパシタ用導電体 177 と対応する部分に開口部 235、237 を形成する。

カラーフィルタ 230 上にポリイミドなどの有機物質からなる上部保護膜 180q を形成する。

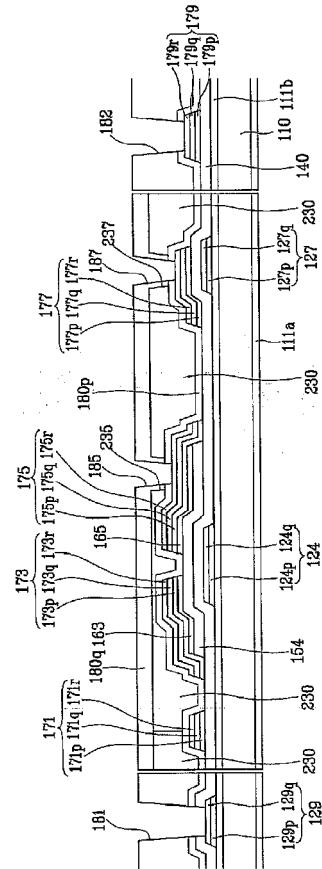

次に、図 11A 及び図 11B に示したように、下部及び上部保護膜 180p、180q を、マスクを利用した写真エッチング工程によってゲート絶縁膜 140 と共にパターニングし、複数の接触孔 181、182、185、187 を形成する。

【0051】

最後に、図 9A 及び図 9B に示したように、上部層間絶縁膜 802 上にドレイン電極 175 と接触孔 185 を通じて接続される画素電極 190 と接触補助部材 81、82 などを形成する。

以上、本発明の好ましい実施形態について詳細に説明したが、本発明の権利範囲はこれに限定されるわけではなく、添付した請求範囲で定義している本発明の基本概念を利用し

10

20

30

40

50

た当業者の種々の変形及び改良形態も本発明の権利範囲に属するものである。

【図面の簡単な説明】

【0052】

【図1】本発明の一実施形態による薄膜トランジスタ表示板の構造を示した配置図である。

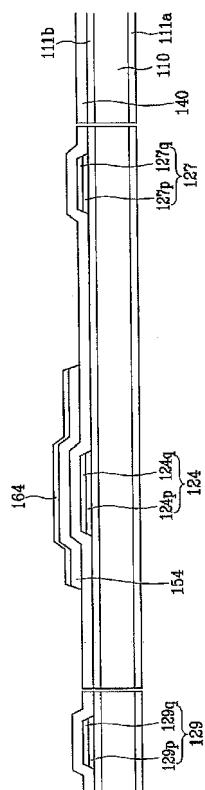

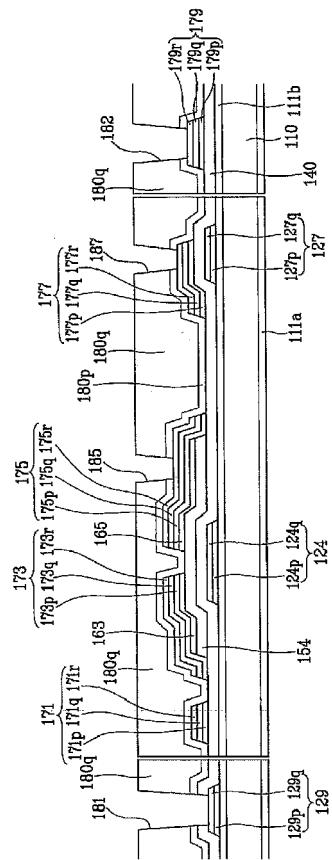

【図2】図1の薄膜トランジスタ表示板をI—I—I'線に沿って切断した断面図である。

【図3】本発明の実施形態による薄膜トランジスタ表示板の製造方法で第1段階を示した断面図である。

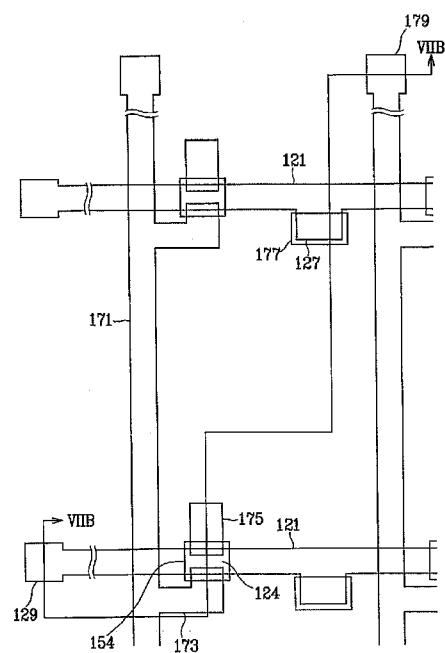

【図4A】図1及び図2に示した薄膜トランジスタ表示板を本発明の一実施形態によって製造する方法を順次に示した薄膜トランジスタ表示板の配置図である(平面図1)。

【図4B】図1及び図2に示した薄膜トランジスタ表示板を本発明の一実施形態によって製造する方法を順次に示した薄膜トランジスタ表示板の断面図である(断面図1)。

【図5】図1及び図2に示した薄膜トランジスタ表示板を本発明の一実施形態によって製造する方法を順次に示した薄膜トランジスタ表示板の断面図である(断面図2)。

【図6A】図1及び図2に示した薄膜トランジスタ表示板を本発明の一実施形態によって製造する方法を順次に示した薄膜トランジスタ表示板の配置図である(平面図2)。

【図6B】図1及び図2に示した薄膜トランジスタ表示板を本発明の一実施形態によって製造する方法を順次に示した薄膜トランジスタ表示板の断面図である(断面図3)。

【図7A】図1及び図2に示した薄膜トランジスタ表示板を本発明の一実施形態によって製造する方法を順次に示した薄膜トランジスタ表示板の配置図である(平面図3)。

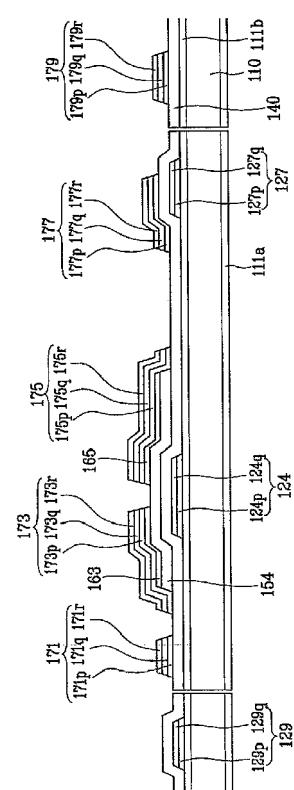

【図7B】図1及び図2に示した薄膜トランジスタ表示板を本発明の一実施形態によって製造する方法を順次に示した薄膜トランジスタ表示板の断面図である(断面図4)。

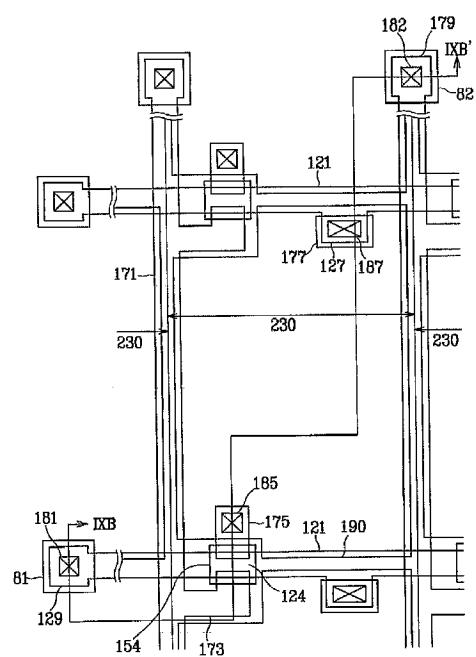

【図8A】図1及び図2に示した薄膜トランジスタ表示板を本発明の一実施形態によって製造する方法を順次に示した薄膜トランジスタ表示板の配置図である(平面図4)。

【図8B】図1及び図2に示した薄膜トランジスタ表示板を本発明の一実施形態によって製造する方法を順次に示した薄膜トランジスタ表示板の断面図である(断面図5)。

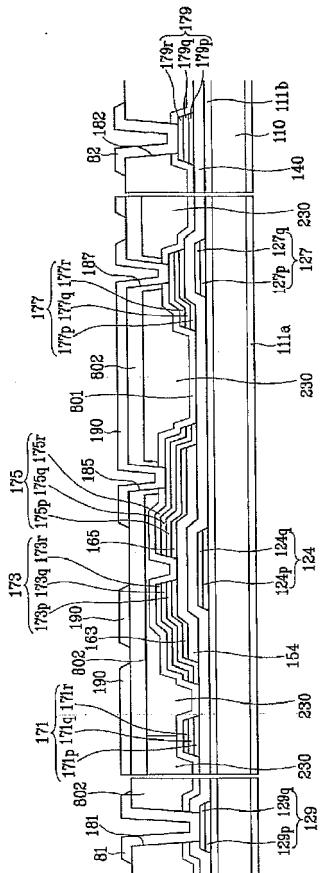

【図9A】本発明の他の一実施形態による薄膜トランジスタ表示板の構造を示した配置図である。

【図9B】図9AのIXb-IXb'線に沿って切断した断面図である。

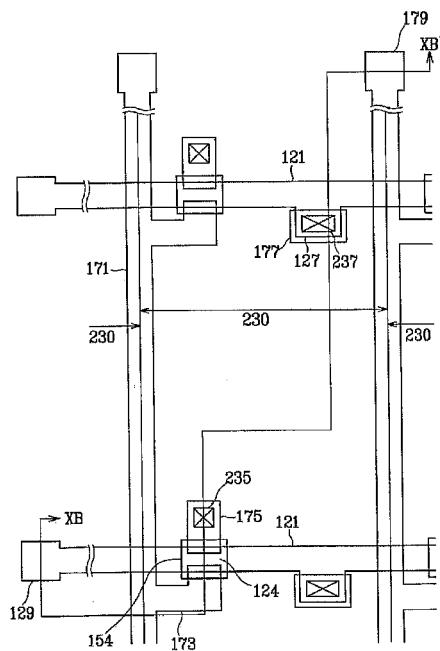

【図10A】本発明の他の一実施形態による薄膜トランジスタ表示板の構造を示した配置図である。

【図10B】図10AのXb-Xb'線に沿って切断した断面図である。

【図11A】本発明の他の一実施形態による薄膜トランジスタ表示板の構造を示した配置図である。

【図11B】図11AのXIb-XIb'線に沿って切断した断面図である。

【図12A】プラスチック基板の熱膨張による上部パターンの整列を示した模式図である(整列している場合)。

【図12B】プラスチック基板の熱膨張による上部パターンの整列を示した模式図である(配列誤差が生じている場合)。

【図12C】プラスチック基板の熱膨張による上部パターンの整列を示した模式図である(本発明の場合)。

【符号の説明】

【0053】

110 基板

111a、111b 基板保護膜

121 ゲート線

124 ゲート電極

127 複数の拡張部

129 ゲート線の端部

10

20

30

40

50

- |             |                |

|-------------|----------------|

| 1 4 0       | ゲート絶縁膜         |

| 1 5 0       | 真性非晶質シリコン層     |

| 1 5 4       | 島状半導体部材        |

| 1 6 0       | 不純物非晶質シリコン層    |

| 1 6 4       | 島状抵抗性接触部材      |

| 1 7 1       | データ線           |

| 1 7 3       | ソース電極          |

| 1 7 5       | ドレイン電極         |

| 1 7 7       | ストレージキャパシタ用導電体 |

| 1 7 9       | データ線の端部        |

| 1 8 0       | 保護膜            |

| 1 8 1、1 8 2 | 接触孔            |

| 1 9 0       | 画素電極           |

| 8 1、8 2     | 接触補助部材         |

10

【図1】

【 図 2 】

【図3】

【図4 A】

【図4 B】

【図5】

【図 6 A】

【図 6 B】

【図 7 A】

【図 7 B】

【 図 8 A 】

【 図 8 B 】

【 図 9 A 】

【 図 9 B 】

【図 10A】

【 図 1 0 B 】

【図11A】

【 図 1 1 B 】

【図 1 2 A】

【図 1 2 B】

【図 1 2 C】

---

フロントページの続き

F ターム(参考) 5F110 AA30 BB01 CC07 DD01 DD13 DD14 EE03 EE04 EE06 EE07

EE23 FF02 FF03 GG02 GG15 GG22 GG24 GG35 HK03 HK04

HK05 HK07 HK09 HK16 HK21 HK33 HM03 NN01 NN03 NN24

NN27 NN72 NN73 QQ01 QQ09