(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4057791号

(P4057791)

(45) 発行日 平成20年3月5日(2008.3.5)

(24) 登録日 平成19年12月21日(2007.12.21)

(51) Int.Cl.

F 1

H03L 7/093 (2006.01)

H03L 7/10 (2006.01)H03L 7/08

H03L 7/10E

D

請求項の数 14 (全 20 頁)

(21) 出願番号 特願2001-83973 (P2001-83973)

(22) 出願日 平成13年3月23日 (2001.3.23)

(65) 公開番号 特開2002-208856 (P2002-208856A)

(43) 公開日 平成14年7月26日 (2002.7.26)

審査請求日 平成16年9月10日 (2004.9.10)

(31) 優先権主張番号 00311746.2

(32) 優先日 平成12年12月28日 (2000.12.28)

(33) 優先権主張国 欧州特許庁 (EP)

前置審査

(73) 特許権者 000005108

株式会社日立製作所

東京都千代田区丸の内一丁目6番6号

(73) 特許権者 500385980

ティーティーピー コム リミテッド

イギリス国、ハートフォードシャー エス

ジー8 6イーイー、ロイストン、メルボ

ルン、ケンブリッジ ロード、メルボルン

サイエンス パーク (番地なし)

(74) 代理人 100080001

弁理士 简井 大和

(72) 発明者 山脇 大造

東京都国分寺市東恋ヶ窪一丁目280番地

株式会社日立製作所 中央研究所内

最終頁に続く

(54) 【発明の名称】 P L L回路および無線通信端末機器

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の周波数変調された入力信号と第2の入力信号の位相差に比例した信号を出力する電流出力型位相比較器と、前記電流出力型位相比較器の出力端に接続された低域通過フィルタと、前記低域通過フィルタの出力端に接続されたVCOと、前記VCOの出力端に接続され前記VCOの出力周波数を周波数変換し前記第2の入力信号を出力するミキサと、前記電流出力型位相比較器の出力端に接続された第1、第2、第3の定電流源と、前記電流出力型位相比較器と基準電位との間に接続されたスイッチとを有し、前記第1、第2、第3の定電流源のオンオフと前記スイッチの短絡、開放の制御手段を有し、

前記基準電位は0Vであり、前記第1と第3の定電流源は前記電流出力型位相比較器の出力端に定電流を出力し、前記第2の定電流源は前記電流出力型位相比較器の出力端から定電流を吸収し、

非動作状態では、前記第1、第2、第3の定電流源がオフで前記スイッチは短絡されており、前記非動作状態から動作状態への移行には第1と第2の手段が存在し、前記PLL回路の収束周波数が、前記スイッチの短絡時の前記VCOの出力周波数と設定周波数との間の周波数であるという条件を満たす場合には前記第1の手段が用いられ、前記条件を満たさない場合には前記第2の手段が用いられるPLL回路であって、前記第1の手段においては、前記スイッチの開放と前記第1の定電流源のオンが行われ、前記第2の手段においては、まず前記スイッチの開放と前記第3の定電流源のオンが行われ、その一定期間の後、前記第3の定電流源のオフと前記第2の定電流源のオンが行われるものであり、該設

10

20

定周波数は前記 V C O の発振周波数範囲の略中間に当たる周波数であり、

前記第 1、第 2 の定電流源の出力電流値は等しく、前記第 3 の定電流源の出力電流値は前記第 1、第 2 の定電流源の出力電流値の少なくとも 2 倍以上であることを特徴とする P L L 回路。

**【請求項 2】**

第 1 の周波数変調された入力信号と第 2 の入力信号の位相差に比例した信号を出力する電流出力型位相比較器と、前記電流出力型位相比較器の出力端に接続された低域通過フィルタと、前記低域通過フィルタの出力端に接続された V C O と、前記 V C O の出力端に接続され前記 V C O の出力周波数を周波数変換し前記第 2 の入力信号を出力するミキサと、前記電流出力型位相比較器の出力端に接続された第 1、第 2、第 3 の定電流源と、前記電流出力型位相比較器と基準電位との間に接続されたスイッチとを有し、前記第 1、第 2、第 3 の定電流源のオンオフと前記スイッチの短絡、開放の制御手段を有し、

前記基準電位は電源電位であり、前記第 1 と第 3 の定電流源は前記電流出力型位相比較器の出力端から定電流を吸収し、前記第 2 の定電流源は前記電流出力型位相比較器の出力端に定電流を出力し、

非動作状態では、前記第 1、第 2、第 3 の定電流源がオフで前記スイッチは短絡されており、前記非動作状態から動作状態への移行には第 1 と第 2 の手段が存在し、前記 P L L 回路の収束周波数が、前記スイッチの短絡時の前記 V C O の出力周波数と設定周波数との間の周波数であるという条件を満たす場合には前記第 1 の手段が用いられ、前記条件を満たさない場合には前記第 2 の手段が用いられる P L L 回路であって、前記第 1 の手段においては、前記スイッチの開放と前記第 1 の定電流源のオンが行われ、前記第 2 の手段においては、まず前記スイッチの開放と前記第 3 の定電流源のオンが行われ、その一定期間の後、前記第 3 の定電流源のオフと前記第 2 の定電流源のオンが行われるものであり、該設定周波数は前記 V C O の発振周波数範囲の略中間に当たる周波数であり、

前記第 1、第 2 の定電流源の出力電流値は等しく、前記第 3 の定電流源の出力電流値は前記第 1、第 2 の定電流源の出力電流値の少なくとも 2 倍以上であることを特徴とする P L L 回路。

**【請求項 3】**

第 1 の周波数変調された入力信号と第 2 の入力信号の位相差に比例した信号を出力する電流出力型位相比較器と、前記電流出力型位相比較器の出力端に接続された低域通過フィルタと、前記低域通過フィルタの出力端に接続された V C O と、前記 V C O の出力端に接続され前記 V C O の出力周波数を周波数変換し前記第 2 の入力信号を出力するミキサと、前記電流出力型位相比較器の出力端に接続された第 1、第 2 の定電流源と、前記電流出力型位相比較器と第 1 の基準電位との間に接続された第 1 のスイッチと、前記電流出力型位相比較器の出力端と第 2 の基準電位との間に接続された第 2 のスイッチとを有し、前記第 1、第 2 の定電流源のオンオフと前記第 1 と第 2 のスイッチの短絡、開放を制御する手段を有し、

前記第 1 の基準電位は 0 V であり、前記第 2 の基準電位は電源電位であり、前記第 1 の定電流源は前記電流出力型位相比較器の出力端に定電流を出力し、前記第 2 の定電流源は前記電流出力型位相比較器の出力端から定電流を吸収し、

非動作状態では、前記第 1、第 2 の定電流源がオフで前記第 1 のスイッチは短絡され、前記第 2 のスイッチは開放されており、前記非動作状態から動作状態への移行には第 1 と第 2 の手段が存在し、前記 P L L 回路の収束周波数が、前記第 1 のスイッチの短絡時の前記 V C O の出力周波数と設定周波数との間の周波数であるという条件を満たす場合には前記第 1 の手段が用いられ、前記条件を満たさない場合には前記第 2 の手段が用いられる P L L 回路であって、前記第 1 の手段においては、前記第 1 のスイッチの開放と前記第 1 の定電流源のオンが行われ、前記第 2 の手段においては、まず前記第 1 のスイッチの開放と前記第 2 のスイッチの短絡が行われ、その一定期間の後、前記第 2 のスイッチの開放と前記第 2 の定電流源のオンが行われるものであり、該設定周波数は前記 V C O の発振周波数範囲の略中間に当たる周波数であり、

10

20

30

40

50

前記第1、第2の定電流源の出力電流値が等しいことを特徴とするPLL回路。

**【請求項4】**

第1の周波数変調された入力信号と第2の入力信号の位相差に比例した信号を出力する電流出力型位相比較器と、前記電流出力型位相比較器の出力端に接続された低域通過フィルタと、前記低域通過フィルタの出力端に接続されたVCOと、前記VCOの出力端に接続され前記VCOの出力周波数を周波数変換し前記第2の入力信号を出力するミキサと、前記電流出力型位相比較器の出力端に接続された第1、第2の定電流源と、前記電流出力型位相比較器と第1の基準電位との間に接続された第1のスイッチと、前記電流出力型位相比較器の出力端と第2の基準電位との間に接続された第2のスイッチとを有し、前記第1、第2の定電流源のオンオフと前記第1と第2のスイッチの短絡、開放を制御する手段を有し。

10

前記第1の基準電位は電源電圧であり、前記第2の基準電位は0Vであり、前記第1の定電流源は前記電流出力型位相比較器の出力端から定電流を吸収し、前記第2の定電流源は前記電流出力型位相比較器の出力端に定電流を出力し、

非動作状態では、前記第1、第2の定電流源がオフで前記第1のスイッチは短絡され、前記第2のスイッチは開放されており、前記非動作状態から動作状態への移行には第1と第2の手段が存在し、前記PLL回路の収束周波数が、前記第1のスイッチの短絡時の前記VCOの出力周波数と設定周波数との間の周波数であるという条件を満たす場合には前記第1の手段が用いられ、前記条件を満たさない場合には前記第2の手段が用いられるPLL回路であって、前記第1の手段においては、前記第1のスイッチの開放と前記第1の定電流源のオンが行われ、前記第2の手段においては、まず前記第1のスイッチの開放と前記第2のスイッチの短絡が行われ、その一定期間の後、前記第2のスイッチの開放と前記第2の定電流源のオンが行われるものであり、該設定周波数は前記VCOの発振周波数範囲の略中間に当たる周波数であり。

20

前記第1、第2の定電流源の出力電流値が等しいことを特徴とするPLL回路。

**【請求項5】**

第1の周波数変調された入力信号と第2の入力信号の位相差に比例した信号を出力する電流出力型位相比較器と、前記電流出力型位相比較器の出力端に接続された低域通過フィルタと、前記低域通過フィルタの出力端に接続されたVCOと、前記VCOの出力端に接続され前記VCOの出力周波数を周波数変換し前記第2の入力信号を出力するミキサと、前記電流出力型位相比較器の出力端に接続された可変電流源と定電流源と、前記電流出力型位相比較器と基準電位との間に接続されたスイッチとを有し、前記可変電流源のオンオフ及び出力電流値と前記定電流源のオンオフと前記スイッチの短絡、開放を制御する手段を有し。

30

前記基準電位は0Vであり、前記可変電流源は前記電流出力型位相比較器の出力端に電流を出力し、前記定電流源は前記電流出力型位相比較器の出力端から定電流を吸収し、

非動作状態では、前記可変電流源と前記定電流源がオフで前記スイッチは短絡されており、前記非動作状態から動作状態への移行には第1と第2の手段が存在し、前記PLL回路の収束周波数が、前記第1のスイッチの短絡時の前記VCOの出力周波数と設定周波数との間の周波数であるという条件を満たす場合には前記第1の手段が用いられ、前記条件を満たさない場合には前記第2の手段が用いられるPLL回路であって、前記第1の手段においては、前記スイッチの開放と前記可変電流源のオンが行われ、前記可変電流源は第1の定電流値を出力し、前記第2の手段においては、まず前記スイッチの開放と前記可変電流源のオンが行われ、前記可変電流源は第2の定電流値を出力し、その一定期間の後、前記可変電流源のオフと前記定電流源のオンが行われるものであり、該設定周波数は前記VCOの発振周波数範囲の略中間に当たる周波数であり。

40

前記第1の定電流値と前記定電流の出力電流値は等しく、前記第2の定電流値は前記第1の定電流値と前記定電流の出力電流値の少なくとも2倍以上であることを特徴とするPLL回路。

**【請求項6】**

第1の周波数変調された入力信号と第2の入力信号の位相差に比例した信号を出力する電流出力型位相比較器と、前記電流出力型位相比較器の出力端に接続された低域通過フィルタと、前記低域通過フィルタの出力端に接続されたVCOと、前記VCOの出力端に接続され前記VCOの出力周波数を周波数変換し前記第2の入力信号を出力するミキサと、前記電流出力型位相比較器の出力端に接続された可変電流源と定電流源と、前記電流出力型位相比較器と基準電位との間に接続されたスイッチとを有し、前記可変電流源のオンオフ及び出力電流値と前記定電流源のオンオフと前記スイッチの短絡、開放を制御する手段を有し、

前記基準電位は電源電位であり、前記可変電流源は前記電流出力型位相比較器の出力端から電流を吸収し、前記定電流源は前記電流出力型位相比較器の出力端に定電流を出力し

10

、非動作状態では、前記可変電流源と前記定電流源がオフで前記スイッチは短絡されており、前記非動作状態から動作状態への移行には第1と第2の手段が存在し、前記PLL回路の収束周波数が、前記第1のスイッチの短絡時の前記VCOの出力周波数と設定周波数との間の周波数であるという条件を満たす場合には前記第1の手段が用いられ、前記条件を満たさない場合には前記第2の手段が用いられるPLL回路であって、前記第1の手段においては、前記スイッチの開放と前記可変電流源のオンが行われ、前記可変電流源は第1の定電流値を出力し、前記第2の手段においては、まず前記スイッチの開放と前記可変電流源のオンが行われ、前記可変電流源は第2の定電流値を出力し、その一定期間の後、前記可変電流源のオフと前記定電流源のオンが行われるものであり、該設定周波数は前記VCOの発振周波数範囲の略中間に当たる周波数であり、

20

前記第1の定電流値と前記定電流の出力電流値は等しく、前記第2の定電流値は前記第1の定電流値と前記定電流の出力電流値の少なくとも2倍以上であることを特徴とするPLL回路。

#### 【請求項7】

ベースバンド回路と、前記ベースバンド回路から第1のベースバンド信号が入力される変調器と、前記変調器の出力に接続されたPLL回路と、前記PLL回路の出力に接続された電力増幅器と、前記ベースバンド回路に第2のベースバンド信号を出力する受信回路と、アンテナと、前記アンテナと前記受信回路の入力と前記電力増幅器の出力とが接続されるセレクタとを有する無線通信端末機器であって、

30

前記ベースバンド回路は前記無線通信端末機器の動作の制御信号を出力し、

前記PLL回路が、第1の周波数変調された入力信号と第2の入力信号の位相差に比例した信号を出力する電流出力型位相比較器と、前記電流出力型位相比較器の出力端に接続された低域通過フィルタと、前記低域通過フィルタの出力端に接続されたVCOと、前記VCOの出力端に接続され前記VCOの出力周波数を周波数変換し前記第2の入力信号を出力するミキサと、前記電流出力型位相比較器の出力端に接続された第1、第2の定電流源と、前記電流出力型位相比較器と第1の基準電位との間に接続された第1のスイッチと、前記電流出力型位相比較器の出力端と第2の基準電位との間に接続された第2のスイッチとを有し、前記第1、第2の定電流源のオンオフと前記第1と第2のスイッチの短絡、開放を制御する手段を有するPLL回路からなり、

40

前記PLL回路において、前記第1の基準電位は0Vであり、前記第2の基準電位は電源電位であり、前記第1の定電流源は前記電流出力型位相比較器の出力端に定電流を出力し、前記第2の定電流源は前記電流出力型位相比較器の出力端から定電流を吸収し、

前記PLL回路において、非動作状態では、前記第1、第2の定電流源がオフで前記第1のスイッチは短絡され、前記第2のスイッチは開放されており、前記非動作状態から動作状態への移行には第1と第2の手段が存在し、前記PLL回路の収束周波数が、前記第1のスイッチの短絡時の前記VCOの出力周波数と設定周波数との間の周波数であるという条件を満たす場合には前記第1の手段が用いられ、前記条件を満たさない場合には前記第2の手段が用いられるPLL回路であって、前記第1の手段においては、前記第1のスイッチの開放と前記第1の定電流源のオンが行われ、前記第2の手段においては、まず前

50

記第1のスイッチの開放と前記第2のスイッチの短絡が行われ、その一定期間の後、前記第2のスイッチの開放と前記第2の定電流源のオンが行われるものであり、該設定周波数は前記VCOの発振周波数範囲の略中間に当たる周波数であり、

前記PLL回路において、前記第1、第2の定電流源の出力電流値が等しいことを特徴とする無線通信端末機器。

**【請求項8】**

ベースバンド回路と、前記ベースバンド回路から第1のベースバンド信号が入力される変調器と、前記変調器の出力に接続されたPLL回路と、前記PLL回路の出力に接続された電力增幅器と、前記ベースバンド回路に第2のベースバンド信号を出力する受信回路と、アンテナと、前記アンテナと前記受信回路の入力と前記電力増幅器の出力とが接続されるセレクタとを有する無線通信端末機器であって、

前記ベースバンド回路は前記無線通信端末機器の動作の制御信号を出力し、

前記PLL回路が、第1の周波数変調された入力信号と第2の入力信号の位相差に比例した信号を出力する電流出力型位相比較器と、前記電流出力型位相比較器の出力端に接続された低域通過フィルタと、前記低域通過フィルタの出力端に接続されたVCOと、前記VCOの出力端に接続され前記VCOの出力周波数を周波数変換し前記第2の入力信号を出力するミキサと、前記電流出力型位相比較器の出力端に接続された第1、第2の定電流源と、前記電流出力型位相比較器と第1の基準電位との間に接続された第1のスイッチと、前記電流出力型位相比較器の出力端と第2の基準電位との間に接続された第2のスイッチとを有し、前記第1、第2の定電流源のオンオフと前記第1と第2のスイッチの短絡、開放を制御する手段を有するPLL回路からなり、

前記PLL回路において、前記第1の基準電位は電源電圧であり、前記第2の基準電位は0Vであり、前記第1の定電流源は前記電流出力型位相比較器の出力端から定電流を吸収し、前記第2の定電流源は前記電流出力型位相比較器の出力端に定電流を出力し、

前記PLL回路において、非動作状態では、前記第1、第2の定電流源がオフで前記第1のスイッチは短絡され、前記第2のスイッチは開放されており、前記非動作状態から動作状態への移行には第1と第2の手段が存在し、前記PLL回路の収束周波数が、前記第1のスイッチの短絡時の前記VCOの出力周波数と設定周波数との間の周波数であるという条件を満たす場合には前記第1の手段が用いられ、前記条件を満たさない場合には前記第2の手段が用いられるPLL回路であって、前記第1の手段においては、前記第1のスイッチの開放と前記第1の定電流源のオンが行われ、前記第2の手段においては、まず前記第1のスイッチの開放と前記第2のスイッチの短絡が行われ、その一定期間の後、前記第2のスイッチの開放と前記第2の定電流源のオンが行われるものであり、該設定周波数は前記VCOの発振周波数範囲の略中間に当たる周波数であり、

前記PLL回路において、前記第1、第2の定電流源の出力電流値が等しいことを特徴とする無線通信端末機器。

**【請求項9】**

第1の周波数変調された入力信号と第2の入力信号の位相差に比例した信号を出力する電流出力型位相比較器と、前記電流出力型位相比較器の出力端に接続された低域通過フィルタと、前記低域通過フィルタの出力端に接続されたVCOと、前記VCOの出力端に接続され前記VCOの出力周波数を周波数変換し前記電流出力型位相比較器の前記第2の入力信号を出力するミキサと、前記電流出力型位相比較器の出力端に接続された第1、第2の定電流源と、前記電流出力型位相比較器と第1の基準電位との間に接続された第1のスイッチと、前記電流出力型位相比較器の出力端と第2の基準電位との間に接続された第2のスイッチとを有し、前記第1、第2の定電流源のオンオフと前記第1と第2のスイッチの短絡、開放を制御するコントローラを有し、

前記第1の基準電位は0Vであり、前記第2の基準電位は電源電位であり、前記第1の定電流源は前記電流出力型位相比較器の出力端に定電流を出力し、前記第2の定電流源は前記電流出力型位相比較器の出力端から定電流を吸収し、

非動作状態では、前記第1、第2の定電流源がオフで前記第1のスイッチは短絡され、

10

20

30

40

50

前記第2のスイッチは開放されており、前記非動作状態から動作状態への移行には第1と第2の手段が存在し、前記PLL回路の収束周波数が、前記第1のスイッチの短絡時の前記VCOの出力周波数と設定周波数との間の周波数であるという条件を満たす場合には前記第1の手段が用いられ、前記条件を満たさない場合には前記第2の手段が用いられるPLL回路であって、前記第1の手段においては、前記第1のスイッチの開放と前記第1の定電流源のオンが行われ、前記第2の手段においては、まず前記第1のスイッチの開放と前記第2のスイッチの短絡が行われ、その一定期間の後、前記第2のスイッチの開放と前記第2の定電流源のオンが行われるものであり、該設定周波数は前記VCOの発振周波数範囲の略中間に当たる周波数であり、

前記第1、第2の定電流源の出力電流値が等しいことを特徴とするPLL回路。 10

#### 【請求項10】

第1の周波数変調された入力信号と第2の入力信号の位相差に比例した信号を出力する電流出力型位相比較器と、前記電流出力型位相比較器の出力端に接続された低域通過フィルタと、前記低域通過フィルタの出力端に接続されたVCOと、前記VCOの出力端に接続され前記VCOの出力周波数を周波数変換し前記電流出力型位相比較器の前記第2の入力信号を出力するミキサと、前記電流出力型位相比較器の出力端に接続された第1、第2の定電流源と、前記電流出力型位相比較器と第1の基準電位との間に接続された第1のスイッチと、前記電流出力型位相比較器の出力端と第2の基準電位との間に接続された第2のスイッチとを有し、前記第1、第2の定電流源のオンオフと前記第1と第2のスイッチの短絡、開放を制御するコントローラを有し、 20

前記第1の基準電位は電源電圧であり、前記第2の基準電位は0Vであり、前記第1の定電流源は前記電流出力型位相比較器の出力端から定電流を吸収し、前記第2の定電流源は前記電流出力型位相比較器の出力端に定電流を出し、

非動作状態では、前記第1、第2の定電流源がオフで前記第1のスイッチは短絡され、前記第2のスイッチは開放されており、前記非動作状態から動作状態への移行には第1と第2の手段が存在し、前記PLL回路の収束周波数が、前記第1のスイッチの短絡時の前記VCOの出力周波数と設定周波数との間の周波数であるという条件を満たす場合には前記第1の手段が用いられ、前記条件を満たさない場合には前記第2の手段が用いられるPLL回路であって、前記第1の手段においては、前記第1のスイッチの開放と前記第1の定電流源のオンが行われ、前記第2の手段においては、まず前記第1のスイッチの開放と前記第2のスイッチの短絡が行われ、その一定期間の後、前記第2のスイッチの開放と前記第2の定電流源のオンが行われるものであり、該設定周波数は前記VCOの発振周波数範囲の略中間に当たる周波数であり、 30

前記第1、第2の定電流源の出力電流値が等しいことを特徴とするPLL回路。

#### 【請求項11】

請求項9または10のいずれかに記載のPLL回路において、

前記第1のスイッチは、前記VCOの入力電位に依存しない信号によって制御され、前記第2のスイッチは、前記VCOの入力電位に依存しない信号によって制御されることを特徴とするPLL回路。 40

#### 【請求項12】

第1の周波数変調された入力信号と第2の入力信号の位相差に比例した信号を出力する電流出力型位相比較器と、前記電流出力型位相比較器の出力端に接続された低域通過フィルタと、前記低域通過フィルタの出力端に接続されたVCOと、前記VCOの出力端に接続され前記VCOの出力周波数を周波数変換し前記電流出力型位相比較器の前記第2の入力信号を出力するミキサと、前記電流出力型位相比較器の出力端に接続された可変電流源と定電流源と、前記電流出力型位相比較器と基準電位との間に接続されたスイッチとを有し、前記可変電流源のオンオフ及び出力電流値と前記定電流源のオンオフと前記スイッチの短絡、開放を制御するコントローラを有し、

前記基準電位は0Vであり、前記可変電流源は前記電流出力型位相比較器の出力端に電流を出し、前記定電流源は前記電流出力型位相比較器の出力端から定電流を吸収し、 50

非動作状態では、前記可変電流源と前記定電流源がオフで前記スイッチは短絡されており、前記非動作状態から動作状態への移行には第1と第2の手段が存在し、前記PLL回路の収束周波数が、前記第1のスイッチの短絡時の前記VCOの出力周波数と設定周波数との間の周波数であるという条件を満たす場合には前記第1の手段が用いられ、前記条件を満たさない場合には前記第2の手段が用いられるPLL回路であって、前記第1の手段においては、前記スイッチの開放と前記可変電流源のオンが行われ、前記可変電流源は第1の定電流値を出力し、前記第2の手段においては、まず前記スイッチの開放と前記可変電流源のオンが行われ、前記可変電流源は第2の定電流値を出力し、その一定期間の後、前記可変電流源のオフと前記定電流源のオンが行われるものであり、該設定周波数は前記VCOの発振周波数範囲の略中間に当たる周波数であり、

10

前記第1の定電流値と前記定電流の出力電流値は等しく、前記第2の定電流値は前記第1の定電流値と前記定電流の出力電流値の少なくとも2倍以上であることを特徴とするPLL回路。

#### 【請求項13】

第1の周波数変調された入力信号と第2の入力信号の位相差に比例した信号を出力する電流出力型位相比較器と、前記電流出力型位相比較器の出力端に接続された低域通過フィルタと、前記低域通過フィルタの出力端に接続されたVCOと、前記VCOの出力端に接続され前記VCOの出力周波数を周波数変換し前記電流出力型位相比較器の前記第2の入力信号を出力するミキサと、前記電流出力型位相比較器の出力端に接続された可変電流源と定電流源と、前記電流出力型位相比較器と基準電位との間に接続されたスイッチとを有し、前記可変電流源のオンオフ及び出力電流値と前記定電流源のオンオフと前記スイッチの短絡、開放を制御するコントローラを有し、

20

前記基準電位は電源電位であり、前記可変電流源は前記電流出力型位相比較器の出力端から電流を吸収し、前記定電流源は前記電流出力型位相比較器の出力端に定電流を出力し、

非動作状態では、前記可変電流源と前記定電流源がオフで前記スイッチは短絡されており、前記非動作状態から動作状態への移行には第1と第2の手段が存在し、前記PLL回路の収束周波数が、前記第1のスイッチの短絡時の前記VCOの出力周波数と設定周波数との間の周波数であるという条件を満たす場合には前記第1の手段が用いられ、前記条件を満たさない場合には前記第2の手段が用いられるPLL回路であって、前記第1の手段においては、前記スイッチの開放と前記可変電流源のオンが行われ、前記可変電流源は第1の定電流値を出力し、前記第2の手段においては、まず前記スイッチの開放と前記可変電流源のオンが行われ、前記可変電流源は第2の定電流値を出力し、その一定期間の後、前記可変電流源のオフと前記定電流源のオンが行われるものであり、該設定周波数は前記VCOの発振周波数範囲の略中間に当たる周波数であり、

30

前記第1の定電流値と前記定電流の出力電流値は等しく、前記第2の定電流値は前記第1の定電流値と前記定電流の出力電流値の少なくとも2倍以上であることを特徴とするPLL回路。

#### 【請求項14】

請求項12または13のいずれかに記載のPLL回路において、

40

前記スイッチは前記VCOの入力電位に依存しない信号によって制御されることを特徴とするPLL回路。

#### 【発明の詳細な説明】

##### 【0001】

##### 【発明の属する技術分野】

本発明は、IF(中間周波数)信号をRF(無線周波数)信号に周波数変換するPLL回路の収束の高速化に適用して有効な技術に関する。

##### 【0002】

##### 【従来の技術】

移動体通信端末に用いられる送信機にはいくつかの方式が存在する。もっとも一般的なも

50

のは、ベースバンド信号を変調器で I F ( 中間周波数 ) 信号に変換し、それをアンテナから送信すべき周波数にミキサで変換するミキサ方式である。この他に、該方式のミキサの替わりに P L L 回路を用いて周波数変換する P L L 方式がある。P L L 方式は、定振幅変調しか扱えないという欠点はあるものの、送信雑音をミキサ方式に比べて大幅に低減できるという特長があり、主に G S M ( Global System for Mobile communications ) システムの無線通信端末機器に用いられている。その動作原理の詳細は、例えば、 IEEE journal of solid-state circuits Vol. 32, No. 12, pp. 2089 - 2096, "A 2.7-V GSM RF Transceiver IC" に記されている。

#### 【 0 0 0 3 】

図 1 2 は、該 P L L 方式で用いられる P L L 回路の一例を示した図である。該 P L L 回路は、電流出力型位相比較器 1 0 0 と、定電流源 1 0 1 と、ミキサ 1 0 5 と、低域通過フィルタ ( L P F ) 1 0 3 と、電圧制御発振器 1 0 4 と、スイッチ ( S W ) 1 0 2 とから構成される。以下の説明において、 V C O 1 0 4 は正の感度をもつものと仮定する。L P F 1 0 3 には、一般に、図 1 2 に示す様な受動素子から成る 2 次 L P F が使用される。また、 S W 1 0 2 には制御信号 L O G I C 1 が与えられる。L O G I C 1 が 0 の場合に S W 1 0 2 は開放状態となり、 L O G I C 1 が 1 の場合に S W 1 0 2 はグランドに短絡する。

#### 【 0 0 0 4 】

電流出力型位相比較器 1 0 0 には、位相周波数比較器ではなく、高速動作可能なミキサ型の位相比較器が用いられる。これにより、送信機の周波数構成の自由度を上げることができる。位相比較器の欠点は、2つの入力の周波数差が大きい場合に、出力電圧が L P F 1 0 3 によって抑圧され V C O 1 0 4 に伝わらないということである。つまり、収束初期段階での V C O 1 0 4 の出力周波数によっては該 P L L 回路が収束することができない。この欠点を解消するために、定電流源 1 0 1 と S W 1 0 2 が接続されている。該 P L L 回路が収束する前に必ず S W 1 0 2 をグランドに接続し V C O 1 0 4 の入力電位をグランド電位に設定する。その後、 S W 1 0 2 を開放して収束を開始する。電流出力型位相比較器 1 0 0 の出力が V C O 1 0 4 に伝わらない場合でも、定電流源 1 0 1 が L P F 1 0 3 の容量を充電することにより、 V C O 1 0 4 の入力電位が上昇する。これにより、電流出力型位相比較器 1 0 0 の2つの入力周波数は近づいていくことができる。該入力周波数が十分近くと、電流出力型位相比較器 1 0 0 の出力が V C O 1 0 4 の入力に伝わり、収束が可能となる。

#### 【 0 0 0 5 】

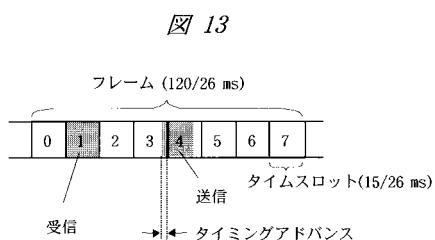

G S M システムには T D M A ( Time Division Multiple Access ) 方式が用いられている。1 フレームは 1 2 0 / 2 6 m s で、 1 5 / 2 6 m s の 8 つのタイムスロットから構成される。1 スロットを受信に、他の 1 スロットを送信に使用する。図 1 3 は、端末の送受信タイミングを示した一例である。この例では、タイムスロット 1 を受信に、タイムスロット 4 を送信に割り当てている。送受信間隔は 2 つのタイムスロット分である。ただし、端末から基地局への伝播遅延を考慮に入れ、送信は最大 3 0 2 4 / 1 3 μ s のタイミングアドバンス分早く行われる。

#### 【 0 0 0 6 】

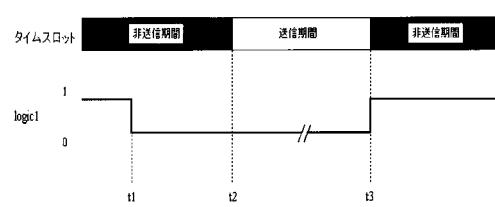

前記 P L L 方式が、前述の G S M の T D M A 動作に従いどのように動作するかを、前記の従来の P L L 回路と、図 1 4 に示すタイミングチャートを用いて説明する。説明の便宜のため、電流出力型位相比較器 1 0 0 の入力の中心周波数を 2 7 0 M H z 、ミキサ 1 0 5 に入力される局発信号 L O の周波数を 1 1 8 0 M H z とする。また、 V C O 1 0 4 の入力感度は正であり、入力電位が 0 V の時の出力周波数を 8 5 0 M H z とする。端末が送信タイミングにない場合、 L O G I C 1 には 1 が入力され、電流出力型位相比較器 1 0 0 の出力が 0 V となる。これにより、 L P F 1 0 3 の容量に蓄積された電荷が放電され、 V C O 1 0 4 の入力電位もまた 0 V となる。したがって、 V C O 1 0 4 の出力周波数は 8 5 0 M H z となる。時刻 t 1 になると、 L O G I C 1 には 0 が入力され、 S W 1 0 2 は開放状態となる。この時のミキサ 1 0 5 の出力周波数は、 8 5 0 M H z と 1 1 8 0 M H z の和と差、すなわち、 2 0 3 0 M H z と 3 3 0 M H z である。和成分は、 L P F 1 0 3 で抑圧され收

10

20

30

40

50

束に寄与しないので、ここでは差成分のみを考える。したがって、電流出力型位相比較器 100 の出力周波数は、 $330 - 270 = 60 \text{ MHz}$  となる。GSM システムに用いる場合、一般に該 PLL 回路の帯域は約 1 MHz に設計されるので、ミキサ 105 の出力信号は LPF 103 で十分抑圧され、前記容量への電荷蓄積に寄与しない。つまり、フィードバックが切れた状態となる。しかし、定電流源 101 からの定電流により該容量に電荷が蓄積され、VCO 104 の入力電位は上昇する。その結果、VCO 104 の出力周波数は 850 MHz から上昇していく。VCO 104 の出力周波数が、例えば、908 MHz に上昇した場合を考える。この時、電流出力型位相比較器 100 の出力周波数は 2 MHz となる。したがって、LPF 103 での抑圧度が減少し、前記容量への電荷蓄積に寄与することができる。すなわち、フィードバックが回復する。フィードバックが回復したことにより、該 PLL 回路は最終的に収束し、VCO 104 の出力周波数は、 $1180 - 270 = 910 \text{ MHz}$  となる。収束は、送信期間の始まる時刻  $t_2$  よりも早く完了しなければならない。送信期間が終了する時刻  $t_3$  に、LOGIC 1 には 1 が入力され、再び VCO 104 の入力電位を 0 V とし、次の送信期間に備える。

#### 【0007】

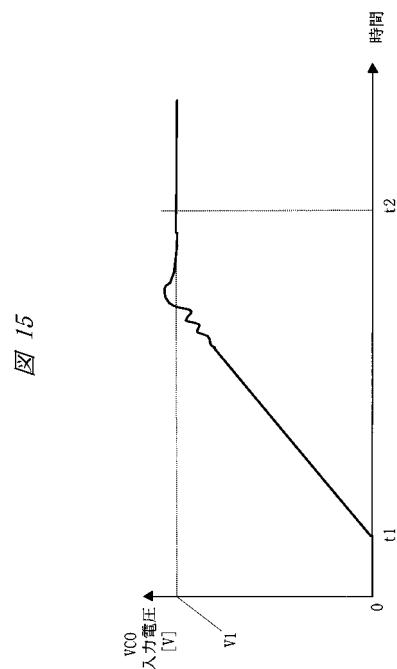

図 15 は、上記収束過程における VCO 104 の入力電位の変化を示した一例である。時刻  $t_1$  までは、該入力電位は 0 V である。時刻  $t_1$  に SW 102 が開放となり、該入力電位が直線的に上昇を始める。該上昇の傾きは、主に定電流源 101 の出力電流  $I_1$  と、LPF 103 の総容量  $C$  により決まり、 $I_1 / C$  で与えられる。その後、フィードバックを回復し収束を完了する。VCO 104 の感度を  $K_V$ 、該入力電位が 0 V 時の VCO 104 の出力周波数を  $f_0$ 、収束時の VCO 104 の出力周波数を  $f_1$  とすると、収束時の該入力電位  $V_1$  は数式 1 で与えられる。

#### 【0008】

$$V_1 = (f_1 - f_0) / K_V \quad \dots \quad (\text{数式 } 1)$$

該 PLL 回路の収束時間  $t_s$  は、該出力電流  $I_1$  によって該総容量  $C$  が  $V_1$  に充電される時間で近似できるので、 $t_s$  は数式 2 で与えられる。

#### 【0009】

$$t_s = (f_1 - f_0) / K_V \cdot C / I_1 \quad \dots \quad (\text{数式 } 2)$$

したがって、 $f_1$  が高いほど収束時間が長くなる。例えば GSM システムでは、送信周波数の最高周波数 915 MHz に収束するときにもっとも収束時間が長くなる。

#### 【0010】

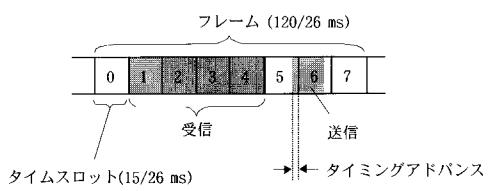

近年、高速データ通信サービスの要求が急速に高まってきた。それに伴い、GSM システムにおいても従来のデータレートを改善する方式がいくつか提案され、実用に向け検討が行われている。その一つが GPRS (General Packet Radio Service) である。GPRS は、図 16 に示すように複数のタイムスロットを送信または受信に割り当てることでデータレートを高める方式である。図 13 と図 16 を比較すれば明らかのように、GPRS では前記 PLL 回路が収束に使える時間が従来の GSM に比べ約半分である。そこで、前記 PLL 回路の収束時間を短縮する必要がでてきた。

#### 【0011】

##### 【発明が解決しようとする課題】

前述の様に、従来の PLL 回路の収束時間  $t_s$  は数式 2 で与えられる。 $t_s$  を短縮するには、数式 2 に含まれるパラメータを変更する必要がある。一般に、VCO 104 はモジュール部品として供給されるため、その特性値、 $f_0$  と  $K_V$  は固定値である。また、 $I_1 / C$  は以下の 1 ) 2 ) に示す制限により自由に変更することが困難である。1) 電流出力型位相比較器 100 の出力電流と  $C$  の比は、システムパラメータである変調帯域幅や許容雜音量によって決定される。2) 該出力電流と  $I_1$  の比により該 PLL 回路の収束安定性が決まる。つまり、従来の PLL 回路の場合、前述の制限を満たしながら、収束時間を短縮することは困難である。

#### 【0012】

そこで、本発明の目的は、前述の制限を満たしながら、従来の PLL 回路の最大収束時間

10

20

30

40

50

を短縮することである。

【0013】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【0014】

【課題を解決するための手段】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

【0015】

上記目的を達成するために、本発明のPLL回路は、少なくとも電流出力型位相比較器と、低域通過フィルタと、VCOとを含むPLL回路であって、収束開始前には該VCOの入力電位を0Vとし、該PLL回路の収束周波数が設定周波数よりも低い場合には、該入力電位を0Vから収束電位までPLLフィードバックループにより収束させ、該収束周波数が該設定周波数よりも高い場合には、まず該入力電位を0Vから電源電圧まで該PLLフィードバックループを使わずに上昇させ、その後、該入力電位を該電源電圧から収束電位まで該PLLフィードバックループにより収束させるものである。 10

【0016】

また、上記目的を達成するための他の動作として、本発明のPLL回路は、少なくとも電流出力型位相比較器と、低域通過フィルタと、VCOとを含むPLL回路であって、収束開始前に該VCOの入力電位を電源電圧とし、該PLL回路の収束周波数が設定周波数よりも高い場合には、該入力電位を該電源電圧から収束電位までPLLフィードバックループにより収束させ、該収束周波数が該設定周波数よりも低い場合には、まず該入力電位を該電源電圧から0Vまで該PLLフィードバックループを使わずに下降させ、その後、該入力電位を0Vから収束電位まで該PLLフィードバックループにより収束させるものである。 20

【0017】

また、上記目的を達成するために、本発明のPLL回路の構成は、第1の入力信号と第2の入力信号の位相差に比例した信号を出力する電流出力型位相比較器と、該電流出力型位相比較器の出力端に接続されたLPFと、該LPFの出力端に接続されたVCOと、該VCOの出力端に接続され第2の信号を出力するミキサと、該電流出力型位相比較器の出力端に定電流を出力する第1と第2の定電流源と、該電流出力型位相比較器の出力端から定電流を吸収する第3の定電流源と、該電流出力型位相比較器とグランドとの間に接続された第1のスイッチとを有し、該第1、第2、第3の定電流源のオンオフと該第1のスイッチの開放、短絡を制御する手段を有するものである。 30

【0018】

また、上記目的を達成するための他の構成として、該本発明のPLL回路において、該第2の定電流源を該電流出力型位相比較器の出力端と電源電位との間に接続された第2のスイッチに置き換え、該第2のスイッチのオンオフを制御する手段を追加するものである。

【0019】

また、上記目的を達成するための他の構成として、該本発明のPLL回路において、該第1と第2の定電流源を可変電流源に置き換え、該可変電流源のオンオフと出力電流値を制御する手段を追加するものである。 40

【0020】

また、本発明の無線通信端末機器は、ベースバンド回路と、該ベースバンド回路から第1のベースバンド信号が入力される変調器と、該変調器の出力に接続されたPLL回路と、該PLL回路の出力に接続された電力増幅器と、該ベースバンド回路に第2のベースバンド信号を出力する受信回路と、アンテナと、該アンテナと該受信回路の入力と該電力増幅器の出力とが接続されるアンテナスイッチとを有し、該ベースバンド回路は該無線通信端末機器の動作の制御信号を出力する無線通信端末機器において、該PLL回路が、前記記載のPLL回路からなることを特徴とするものである。また、該セレクタはアンテナスイ 50

ツチまたはデュプレクサである。

**【0021】**

**【発明の実施の形態】**

以下、本発明の実施の形態を図面を用いて詳細に説明する。なお、実施の形態を説明するための全図において、同一部材には同一の符号を付し、その繰り返しの説明は省略する。さらに、従来の技術で説明した内容と重複する部分についての説明も省略する。

**【0022】**

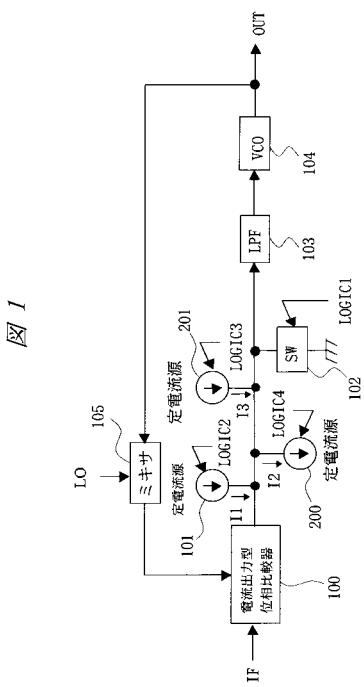

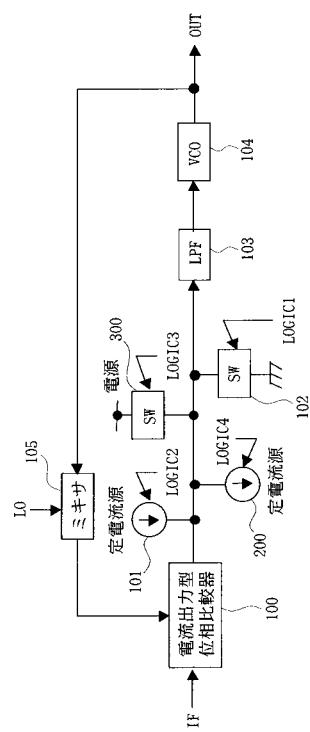

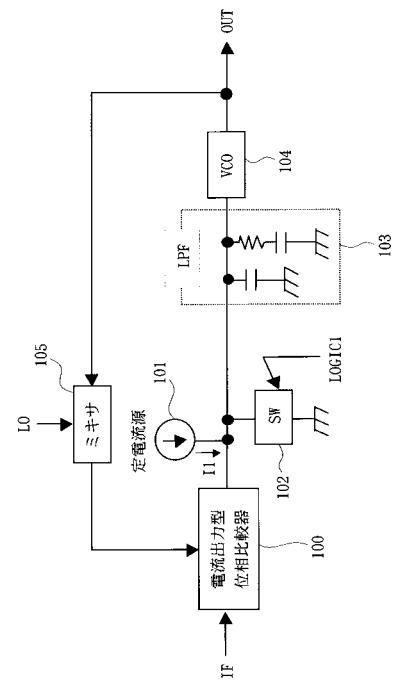

図1は、本発明のPLL回路の第1の実施の形態を示した構成図である。

**【0023】**

本発明に係るPLL回路は、電流出力型位相比較器100と、定電流源101, 200, 201と、ミキサ105と、LPF103と、VCO104と、SW102とから構成される。定電流源101と200の出力電流は同じ値である( $I_1 = I_2$ )。また、定電流源201の出力電流 $I_3$ は、定電流源101と200よりも大きな値、例えば50倍の値である。以下の説明において、VCO104は正の感度をもつものと仮定する。SW102には制御信号LOGIC1が与えられる。LOGIC1が0の場合にSW102は開放状態となり、LOGIC1が1の場合にSW102はグランドに短絡する。また、定電流源101, 200, 201にはそれぞれ制御信号LOGIC2, 3, 4が与えられる。LOGIC2, 3, 4が0の場合に該LOGICが入力される定電流源はそれぞれオフとなり、1の場合にそれぞれオンとなる。

**【0024】**

電流出力型位相比較器100、ミキサ105、SW102、LPF103、VCO104の動作は、前述の従来のPLL回路と同様である。

**【0025】**

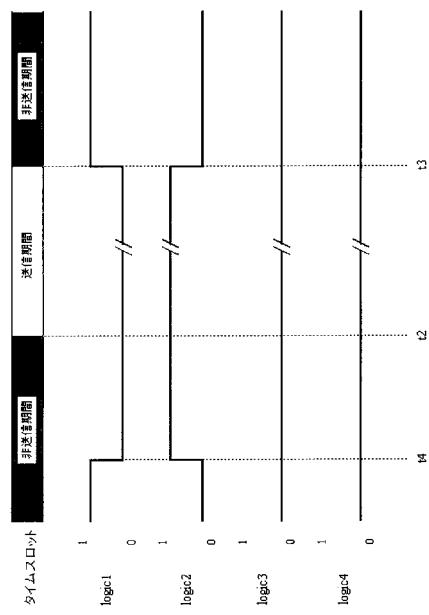

該PLL回路には2つの動作モードがある。該動作モードの一例を図2, 3, 4, 5及び6を用いて説明する。図2は、定電流源200と201を用いない動作モード1のタイミングチャートである。非送信期間の時刻 $t_4$ において、LOGIC1を1から0にしてSW102を短絡状態から開放状態にする。また、LOGIC2を0から1にして定電流源101をオフからオンにする。LOGIC3と4は常に0であり、定電流源200と201は常にオフにする。動作モード1における該PLL回路の動作は、前述の従来のPLL回路の動作と同様であり、収束周波数が高いほど収束時間が長くなる。送信期間が終了すると、LOGIC1は0から1にしてSW102を開放状態から短絡状態にする。また、LOGIC2は1から0にして定電流源101をオンからオフにして、次の送信期間に備える。

**【0026】**

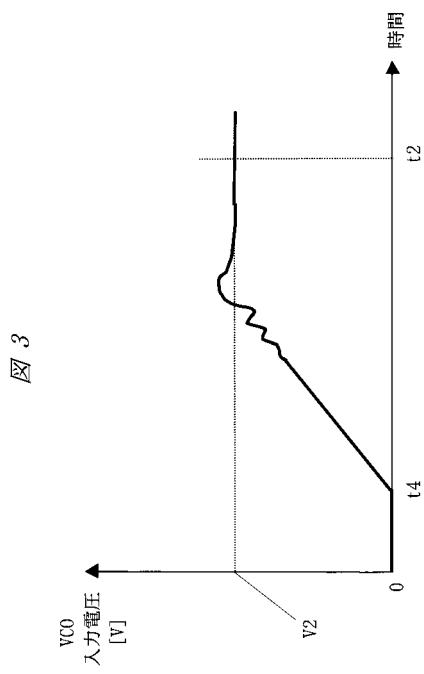

図3は、動作モード1におけるVCO104の入力電位の変化を示した一例である。収束過程は従来のPLL回路と同様である。

**【0027】**

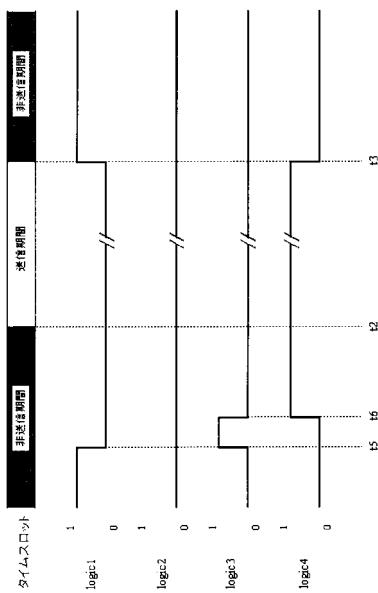

図4は、定電流源101を用いない動作モード2のタイミングチャートである。LOGIC2は常に0として、定電流源101を常にオフにする。非送信期間の時刻 $t_5$ において、LOGIC1を1から0にしてSW102を短絡状態から開放状態にする。また、LOGIC3を0から1にして定電流源201をオフからオンにする。定電流源201の出力大電流によりLPF103の容量が高速充電されVCO104の入力電位が最大電位まで急上昇する。該最大電位は、定電流源201の電源電圧によって決定される。その後、時刻 $t_6$ においてLOGIC3を1から0にして、定電流源201をオンからオフにする。また、LOGIC4を0から1にして、定電流源200をオフからオンにする。定電流源200によってLPF103に蓄積された電荷が放電され、VCO104の入力電位は該最大電位から下降していき、最終的に収束周波数に収束する。この場合、収束周波数が高いほど収束時間が短くなる。送信期間が終了すると、LOGIC1は0から1にしてSW102を開放状態から短絡状態にする。また、LOGIC4は1から0にして定電流源200をオンからオフにして、次の送信期間に備える。

10

20

30

40

50

## 【0028】

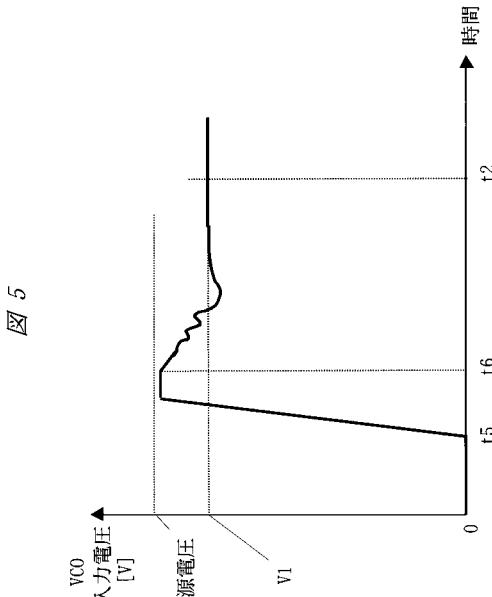

図5は、動作モード2におけるVCO104の入力電位の変化を示した一例である。時刻t5までは、該入力電位は0Vである。時刻t5にSW102が開放となり、該入力電位が直線的に上昇を始める。該上昇の傾きは、主に定電流源201の出力電流I3と、LPPF103の総容量Cにより決まり、 $I_3 / C$ で与えられる。前述の様にI3はI1の、例えば50倍、と大きいため、該上昇の傾きは該動作モード1におけるI1によって決まる傾き $I_1 / C$ の50倍となる。つまり、非常に高速に該入力電位が最大電位まで上昇する。時刻t6になると、定電流源201がオフとなり定電流源200が動作を始める。定電流源200により該入力電位は直線的に下降を始める。該下降の傾きは、主に定電流源200の出力電流I2と、該Cにより決まり、 $I_2 / C$ で与えられる。その後、該PLL回路はフィードバックを回復し収束を完了する。動作モード1における収束時間 $t_{s1}$ は、従来のPLL回路と同様に与えられる。動作モード2における収束時間 $t_{s2}$ は、 $t_d = t_6 - t_5$ 、該入力電位が最大電位の時のVCO104の出力周波数を $f_2$ とすると数式3で与えられる。

## 【0029】

$$t_{s2} = (f_2 - f_1) / K_V \cdot C / I_2 + t_d \quad \dots \quad (\text{数式3})$$

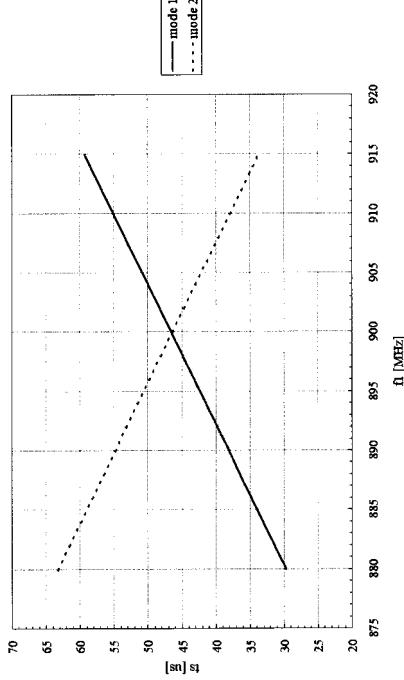

図6は、 $K_V = 35\text{MHz/V}$ 、 $C = 16\text{nF}$ 、 $I_1 = I_2 = 0.54\text{mA}$ 、 $f_0 = 845\text{MHz}$ 、 $f_2 = 943\text{MHz}$ 、 $t_d = 10\mu\text{s}$ の場合の、収束時間 $t_{s2}$ の収束周波数 $f_1$ 依存性を動作モード1と2について示したものである。GSMシステムの場合を想定し、 $f_1$ は $880\text{MHz}$ から $915\text{MHz}$ で計算を行った。また、収束時間の計算には、数式2と3を用いた。図から分かるように、動作モード1のみを用いる従来のPLL回路の最大収束時間は約 $60\mu\text{s}$ である。しかし、 $f_1$ が $900\text{MHz}$ 以下では動作モード1を、 $900\text{MHz}$ 以上では動作モード2を用いれば、最大収束時間は約 $47\mu\text{s}$ に短縮が可能である。

## 【0030】

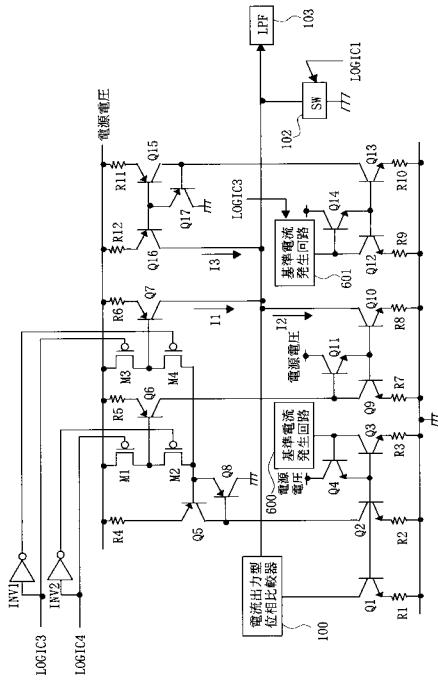

図7は、定電流源101、200、201の実施例を示す回路図である。該回路は、基準電流発生回路600、601、5つのカレントミラー回路、PMOSトランジスタM1-M4及びインバーターINV1、INV2とから構成される。5つのカレントミラー回路はそれぞれ(Q1-Q4, R1-R3)、(Q5-Q8, R4-R6)、(Q9-Q11, R7-R8)、(Q12-Q14, R9-R10)、(Q15-Q17, R11-R12)から構成される。基準電流発生回路600、601は、バンドギャップリファレンス(BGR)回路で発生する温度補償された基準電位から定電流を生成し出力する回路である。

## 【0031】

基準電流発生回路600の出力電流から、図1のI1とI2が生成される。また、基準電流発生回路601からはI3が生成される。I1、I2のオンオフ制御は、M1-M4、INV1、INV2からなるスイッチ回路によって実現される。例えば、LOGIC3が1の場合、M3のソース・ドレイン間はオープンとなり、M4のソース・ドレイン間はショートとなる。したがって、Q5とQ7のベース間がショートされるのでQ7のコレクタからI1が出力される。LOGIC3が0の場合は、Q7のベースが電源電圧となるのでQ7のコレクタ電流はほぼ0となる。I3のオンオフ制御は、基準電流発生回路601のオンオフによって行われる。

## 【0032】

電流出力型位相比較器100のバイアス電流もまた、基準電流発生回路600から生成される。前述の様に、電流出力型位相比較器100の出力電流とI1、I2との比によって該PLL回路の収束安定性を決定する。I1、I2及び該バイアス電流を同一の基準電流から生成することで、該出力電流とI1、I2との比のばらつきを低減することができる。

## 【0033】

たとえば、図7において、LOGIC3で制御されるI3は、I1、I2に比べて8倍の

10

20

30

40

50

電流を流している。この8倍は、カレントミラー回路のエミッタ抵抗比に基準電流源から出力される電流値をかけたものの比である。具体的には、

$(R_{11}/R_{12}) \times (R_9/R_{10}) \times 601$  の発生する電流値と、

$(R_4/R_6) \times (R_2/R_3) \times 600$  の発生する電流値との比が8:1になっている。

#### 【0034】

以上のような構成において、 $0.35\mu\text{m BiCMOS}$ プロセスを用いた例では、前記従来のPLL回路に比べ約6%の回路面積の増加だけで本発明に係るPLL回路の第1の実施の形態を実現できている。

#### 【0035】

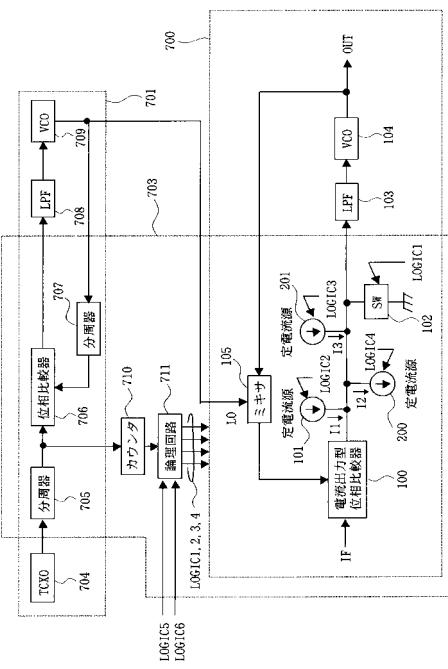

図8は、LOGIC1, 2, 3, 4の生成回路の実施例を示す回路図である。該回路は、第1の実施の形態のPLL回路700と、第1の実施の形態のミキサ105に入力されるLO信号を生成するためのPLL回路701と、カウンタ710と、論理回路711とから構成される。また、PLL回路701は、温度補償型水晶発振器(TXCO)704と、分周器705, 707と、位相比較器706と、LPF708と、VCO709とから構成される。点線703で囲まれた回路は同一IC内に製造される回路である。TCXO704は、温度補償された周波数精度の高い基準信号源として用いられ、例えば、13MHzの信号を出力する。分周器705はTCXO704の出力信号を分周し、位相比較器706に信号を出力する。分周比は、例えば1/65で、200kHzの信号を出力する。分周器705の出力信号がカウンタ710に入力されるので、カウンタ710の入力と出力の間には、分周器705の出力信号の周期の整数倍の遅延が生じる。したがって、該遅延を用いて図4におけるt5からt6への遅延を実現することができる。論理回路711は、カウンタ710の出力信号と該IC外部から入力されるLOGIC5, 6とからLOGIC1, 2, 3, 4を生成し、PLL回路700へと出力する。LOGIC5は、図2, 4におけるt4, t5を決めるための信号であり、LOGIC6は、前述の動作モードを決めるための信号である。

#### 【0036】

次に、本発明に係るPLL回路の第2の実施の形態を説明する。

#### 【0037】

図9は、本発明のPLL回路の第2の実施の形態を示した構成図である。該PLL回路は、第1の実施の形態において、定電流源201を電源電圧に接続されたSW300に置き換えたことを特徴とする回路である。SW300とLOGIC3以外の回路の動作は第1の実施の形態と同様である。SW300は、図4の時刻t5からt6の間にのみオンになる。これにより、LPF103の入力端子と電源が短絡され、LPF103の容量が電源からの電流で最大電位まで高速充電される。

#### 【0038】

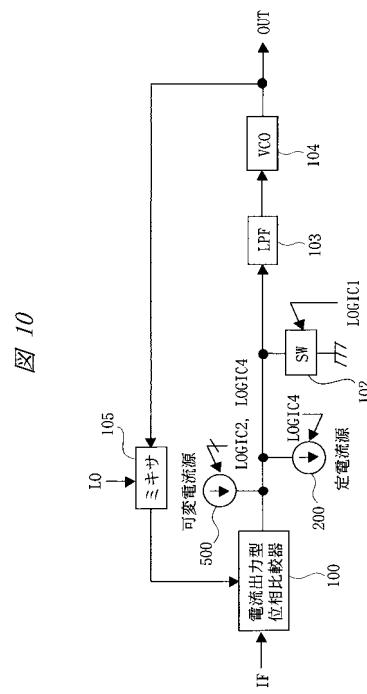

次に、本発明に係るPLL回路の第3の実施の形態を説明する。

#### 【0039】

図10は、本発明のPLL回路の第3の実施の形態を示した構成図である。該PLL回路は、第1の実施の形態において、定電流源101と201を可変電流源500に置き換えたことを特徴とする回路である。可変電流源500は、LOGIC2と4によりオンオフ制御と出力電流値制御が可能である。可変電流源500、LOGIC2と4により、第1の実施の形態の定電流源101, 201とLOGIC2と3と同じ機能を実現する。

#### 【0040】

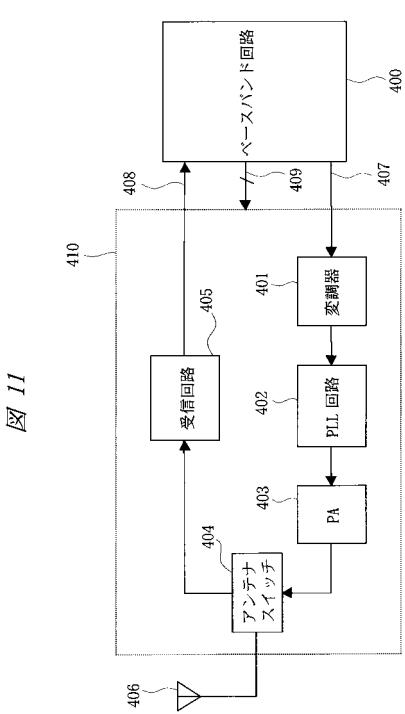

本発明にかかる無線通信端末機器の一例を図11に示す。該無線通信端末機器は、ベースバンド回路400と、変調器401と、本発明に係るPLL回路402と、電力増幅器(PA)403とから構成される送信系と、アンテナスイッチ404と、アンテナ406と、受信回路405とから構成される。

#### 【0041】

ベースバンド回路400は、音声信号やデータ信号に基づいて変調器401にベースバン

10

20

30

40

50

ド信号 407 を出力し、受信回路 405 から入力されるベースバンド信号 408 に基づいて音声信号やデータ信号を再生する。また、該無線通信端末機器を構成する回路 410 を制御するための制御信号 409 を出力する。変調器 401 において、ベースバンド信号 407 に基づき I F 帯の変調信号が生成される。変調器 401 の出力信号は PLL 回路 402 に入力され、周波数変換が施された後、PA 403 に出力される。PA 403 において、信号は電力を増幅され、アンテナスイッチ 404 を通ってアンテナ 406 から送信される。アンテナスイッチ 404 により、送信時にはアンテナ 406 と PA 403 が接続され、受信時にはアンテナ 406 と受信回路 405 が接続される。アンテナ 406 で受信された信号は、受信回路 405 に入力され、復調が行われ、ベースバンド信号 408 が出力される。

10

#### 【0042】

したがって、本実施の形態によれば、PLL 回路の電流出力型位相比較器 100 の出力に、L P F 103 充電用の定電流源 101 と、放電用の定電流源 200 と、高速充電用の定電流源 201 を接続することで、該 PLL 回路の収束周波数が低い場合には、定電流源 101 を用いて VCO 104 の入力電位を 0V から上昇させて収束させ、該収束周波数が高い場合には、定電流源 201 を用いて該入力電位を一旦最大電位にし、その後、定電流源 200 を用いて該入力電位を最大電圧から下降させて収束させるように、収束周波数により上記動作を選択することで該 PLL 回路の最大収束時間を短縮することができる。

#### 【0043】

以上、本発明者によってなされた発明をその実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

20

#### 【0044】

##### 【発明の効果】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば、以下のとおりである。

#### 【0045】

本発明によれば、従来の PLL 回路に 2 つの定電流源を追加するだけで、最大収束時間を約半分に短縮できるという効果がある。

##### 【図面の簡単な説明】

30

【図 1】本発明の PLL 回路の第 1 の実施の形態を示す構成図である。

【図 2】本発明の PLL 回路の動作モード 1 を示すタイミングチャートである。

【図 3】本発明の PLL 回路の動作モード 1 における VCO 入力電位を示す特性図である。

【図 4】本発明の PLL 回路の動作モード 2 を示すタイミングチャートである。

【図 5】本発明の PLL 回路の動作モード 2 における VCO 入力電位を示す特性図である。

【図 6】本発明と従来の PLL 回路の収束時間比較を示す特性図である。

【図 7】本発明の PLL 回路の定電流源の実施例を示す回路図である。

【図 8】本発明の PLL 回路の L O G I C の生成回路の実施例を示す回路図である。

40

【図 9】本発明の PLL 回路の第 2 の実施の形態を示す構成図である。

【図 10】本発明の PLL 回路の第 3 の実施の形態を示す構成図である。

【図 11】本発明の PLL 回路を用いた無線通信端末機器の一例を示す構成図である。

【図 12】従来の PLL 回路を示す構成図である。

【図 13】GSM システム用無線通信端末機器の送受信タイミングを示す説明図である。

【図 14】従来の PLL 回路の動作を示すタイミングチャートである。

【図 15】従来の PLL 回路の VCO 入力電位を示す特性図である。

【図 16】GPRS システム用無線通信端末機器の送受信タイミングを示す説明図である。

##### 【符号の説明】

50

1 0 0 電流出力型位相比較器

1 0 1 , 2 0 0 , 2 0 1 定電流源

1 0 2 , 3 0 0 スイッチ ( S W )

1 0 3 低域通過フィルタ ( L P F )

1 0 4 電圧制御発振器 ( V C O )

1 0 5 ミキサ

4 0 0 ベースバンド回路

4 0 1 変調器

4 0 2 P L L 回路

4 0 3 電力増幅器 ( P A )

4 0 4 アンテナスイッチ

4 0 5 受信回路

4 0 6 アンテナ

4 0 7 , 4 0 8 ベースバンド信号

4 0 9 制御信号

5 0 0 可変電流源

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

図7

【図8】

図8

【図9】

図9

【図10】

【図 1 1】

【図 1 2】

【図 1 3】

【図 1 4】

【図 1 5】

【図 16】

図 16

---

フロントページの続き

(72)発明者 田中 聰

東京都国分寺市東恋ヶ窪一丁目280番地 株式会社日立製作所 中央研究所内

(72)発明者 林 範雄

東京都小平市上水本町5丁目22番1号 株式会社日立超エル・エス・アイ・システムズ内

(72)発明者 渡辺 一雄

東京都小平市上水本町五丁目20番1号 株式会社日立製作所 半導体グループ内

(72)発明者 ロバート・アストル・ヘンシャウ

イギリス国、ハートフォードシャー エスジー8 6イーイー、ロイストン、メルボルン、ケンブリッジ ロード、メルボルン サイエンス パーク、ティーティーピー コム リミテッド内

審査官 崎間 伸洋

(56)参考文献 特開平10-215171(JP,A)

特開平08-139599(JP,A)

英国特許第02338127(GB,B)

特開平11-284508(JP,A)

(58)調査した分野(Int.Cl., DB名)

H03L 7/06-7/23