(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6360175号

(P6360175)

(45) 発行日 平成30年7月18日(2018.7.18)

(24) 登録日 平成30年6月29日(2018.6.29)

(51) Int.Cl.

F 1

|              |           |

|--------------|-----------|

| HO1L 21/8234 | (2006.01) |

| HO1L 27/088  | (2006.01) |

| HO1L 21/822  | (2006.01) |

| HO1L 27/04   | (2006.01) |

| HO1L 21/82   | (2006.01) |

|      |        |

|------|--------|

| HO1L | 27/088 |

| HO1L | 27/04  |

| HO1L | 21/82  |

|   |

|---|

| C |

| A |

| B |

請求項の数 15 (全 22 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2016-540885 (P2016-540885)  |

| (86) (22) 出願日 | 平成26年7月30日 (2014.7.30)        |

| (65) 公表番号     | 特表2016-534574 (P2016-534574A) |

| (43) 公表日      | 平成28年11月4日 (2016.11.4)        |

| (86) 國際出願番号   | PCT/US2014/048944             |

| (87) 國際公開番号   | W02015/034602                 |

| (87) 國際公開日    | 平成27年3月12日 (2015.3.12)        |

| 審査請求日         | 平成29年7月4日 (2017.7.4)          |

| (31) 優先権主張番号  | 14/017,635                    |

| (32) 優先日      | 平成25年9月4日 (2013.9.4)          |

| (33) 優先権主張国   | 米国(US)                        |

|           |                                                                                       |

|-----------|---------------------------------------------------------------------------------------|

| (73) 特許権者 | 507364838<br>クアルコム、インコーポレイテッド<br>アメリカ合衆国 カリフォルニア 921<br>21 サンディエゴ モアハウス ドラ<br>イブ 5775 |

| (74) 代理人  | 100108453<br>弁理士 村山 靖彦                                                                |

| (74) 代理人  | 100163522<br>弁理士 黒田 晋平                                                                |

| (72) 発明者  | ミン・チャイ<br>アメリカ合衆国・カリフォルニア・921<br>21-1714・サン・ディエゴ・モアハ<br>ウス・ドライブ・5775                  |

最終頁に続く

(54) 【発明の名称】複数のコアのゲート長を変動させるシステムおよび方法

## (57) 【特許請求の範囲】

## 【請求項 1】

第1のトランジスタの第1のゲートを形成するステップであって、前記第1のゲートが第1の長さを有し、前記第1のトランジスタが半導体ダイの第1のコア内に配置される、ステップと、

第2のトランジスタの第2のゲートを形成するステップであって、前記第2のゲートが、前記第1の長さよりも短い第2の長さを有し、前記第2のトランジスタが前記半導体ダイの第2のコア内に配置され、前記第1のコアが、前記第2のコアと比較して、前記半導体ダイのより中心近くに配置され、前記第2のトランジスタと前記第1のトランジスタとが対応するトランジスタである、ステップと、

を含む方法。

## 【請求項 2】

前記第1のコアが、トランジスタレイアウトで配置される第1の複数のトランジスタを含み、前記第2のコアが、前記トランジスタレイアウトで配置される第2の複数のトランジスタを含み、前記対応するトランジスタが、前記トランジスタレイアウトにおいて対応する位置でそれぞれのコアに配置される一対のトランジスタを含む、請求項1に記載の方法。

## 【請求項 3】

前記第1の複数のトランジスタの各トランジスタの第1の対応するゲート長が、前記第2の複数のトランジスタの対応する各トランジスタの第2の対応するゲート長よりも実質

的に同量だけ長い、請求項2に記載の方法。

**【請求項4】**

前記半導体ダイの第3のコアの第3のトランジスタの第3のゲートを形成するステップであって、前記第3のゲートが前記第1の長さを有する、ステップと、

前記半導体ダイの第4のコアの第4のトランジスタの第4のゲートを形成するステップであって、前記第4のゲートが前記第2の長さを有し、前記第3のコアが、前記第4のコアと比較して、前記半導体ダイのより中心近くに配置される、ステップと、

をさらに含む、請求項1に記載の方法。

**【請求項5】**

第3のトランジスタの第3のゲートを形成するステップをさらに含み、前記第3のゲートが、前記第1の長さとは異なる第3の長さを有し、前記第3のトランジスタが、第2の半導体ダイの第3のコア内に配置される、請求項1に記載の方法。 10

**【請求項6】**

第4のトランジスタの第4のゲートを形成するステップをさらに含み、前記第4のゲートが前記第2の長さを有し、前記第4のトランジスタが、第2の半導体ダイの第4のコア内に配置される、請求項5に記載の方法。

**【請求項7】**

前記第3のコアが、前記第4のコアと比較して、前記第2の半導体ダイの第2の中心のより近くに配置される、請求項6に記載の方法。

**【請求項8】**

前記第1の長さおよび前記第3の長さが、ウェハ上の前記半導体ダイの第1の位置に基づいて、および前記ウェハ上の前記第2の半導体ダイの第2の位置に基づいて求められる、請求項6に記載の方法。 20

**【請求項9】**

前記第1の長さおよび前記第3の長さが、ウェハ上の半導体ダイの位置に対応する、又は、製造プロセス変動データを含む実験データに基づいて求められる、請求項6に記載の方法。

**【請求項10】**

前記半導体ダイの第3のコア内に配置される第3のトランジスタの第3のゲートを形成するステップであって、前記第3のゲートが第3の長さを有する、ステップと、 30

前記半導体ダイの第4のコア内に配置される第4のトランジスタの第4のゲートを形成するステップであって、前記第4のゲートが第4の長さを有する、ステップと、をさらに含み、

前記第1の長さが、前記第2の長さを第1の量だけ増大させることによって求められ、前記第3の長さが、前記第4の長さを第2の量だけ増大させることによって求められ、前記第1の量が前記第2の量とは異なり、前記第3のトランジスタと前記第4のトランジスタとが対応するトランジスタである、請求項1に記載の方法。

**【請求項11】**

前記第1の長さを使用して前記第1のゲートを形成する前に、

前記第2の長さを使用して前記第1のテストコアおよび前記第2のテストコアを形成するステップと、 40

前記第1のテストコアに関連する第1の性能パラメータを測定するステップと、

前記第2のテストコアに関連する第2の性能パラメータを測定するステップと、

前記第1の性能パラメータと前記第2の性能パラメータとの間の差に基づいて前記第1の長さを求めるステップと、

をさらに含む、請求項1に記載の方法。

**【請求項12】**

前記第1の性能パラメータが、前記第1のテストコアの漏れ電流の第1の量であり、前記第2の性能パラメータが、前記第2のテストコアの漏れ電流の第2の量である、請求項11に記載の方法。 50

**【請求項 1 3】**

前記第1の性能パラメータが、前記第1のテストコアの第1のクロック速度であり、前記第2の性能パラメータが、前記第2のテストコアの第2のクロック速度である、請求項1\_1に記載の方法。

**【請求項 1 4】**

前記第1のテストコアが前記第1の長さを使用して形成され、前記第2のテストコアが前記第2の長さを使用して形成されるとき、前記差が、前記第1の性能パラメータと前記第2の性能パラメータとの間の第2の差よりも大きい、請求項1\_1に記載の方法。

**【請求項 1 5】**

第1のトランジスタを含む半導体ダイの第1のコアであって、前記第1のトランジスタが第1のゲートを含み、前記第1のゲートが第1の長さを有する、第1のコアと、

第2のトランジスタを含む前記半導体ダイの第2のコアであって、前記第2のトランジスタが、前記第1の長さよりも短い第2の長さを有する第2のゲートを含み、前記第1のコアが、前記第2のコアよりも半導体ダイの中心近くに配置され、前記第2のトランジスタと前記第1のトランジスタとが対応するトランジスタである、第2のコアと、

を備える装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

関連出願の相互参照

10

本願は、参照によりその内容全体が本明細書に明確に組み込まれる、同一出願人が所有する2013年9月4日出願の米国非仮特許出願第14/017635号の優先権を主張する。

**【0002】**

本開示は、一般にはプロセッサコアに関する。

**【背景技術】****【0003】**

技術の進歩の結果、コンピューティングデバイスはより小型でより強力になっている。たとえば、小型、軽量であり、ユーザによる持ち運びが容易な、ポータブルワイヤレス電話、携帯情報端末（PDA）、ページングデバイスなどのワイヤレスコンピューティングデバイスを含む様々なポータブルパーソナルコンピューティングデバイスが現在存在している。より具体的には、セルラー電話、インターネットプロトコル（IP）電話などのポータブルワイヤレス電話は、ワイヤレスネットワークを介して音声およびデータパケットを通信し得る。さらに、多くのそのようなワイヤレス電話は、その中に組み込まれる他のタイプのデバイスを含む。たとえばワイヤレス電話は、デジタルスチルカメラ、デジタルビデオカメラ、デジタルレコーダ、およびオーディオファイルプレーヤをも含み得る。さらに、そのようなワイヤレス電話は、インターネットにアクセスするために使用され得る、ウェブブラウザアプリケーションなどのソフトウェアアプリケーションを含む実行可能命令を処理し得る。したがって、これらのワイヤレス電話は、著しいコンピューティング能力を含み得る。

30

**【0004】**

電子デバイス（たとえば、ワイヤレス電話、ラップトップコンピュータ、タブレットなど）は、シングルコアプロセッサと比較して処理能力を向上させるためにマルチコアプロセッサを利用し得る。マルチコアプロセッサは、複数の中央演算処理装置（「コア」）を含み、マルチコアプロセッサの各コアは同一の設計を有し得る。しかしながら、従来型マルチコアプロセッサは、製造プロセス変動やマルチコアプロセッサにわたる様々なエッチ／ローディング効果などによる、コア間漏れ電流変動（たとえば、2つのコアが著しく異なる漏れ電流を有し得る）およびコア間クロック速度変動（たとえば、2つのコアが著しく異なるクロック速度を有し得る）を受ける。品質スクリーニングがしばしば最低の性能のコア（たとえば、最大の漏れ電流を有するコア）によって決定されるので、コア間漏れ

40

50

電流変動は、マルチコアプロセッサの製造歩留まりを低下させ得る。許容しきい値を超えるコア間クロック速度変動のために特定のマルチコアプロセッサに欠陥があることが判明し得るので、コア間クロック速度変動はまた、製造歩留まりを低下させる。

#### 【発明の概要】

#### 【課題を解決するための手段】

#### 【0005】

コア間漏れ電流変動および／またはコア間性能変動を低減するシステムおよび方法が開示される。マルチコアプロセッサが製造されるとき、記載の技法は、マルチコアプロセッサの異なるコアのトランジスタの多結晶シリコンゲートを選択的に形成し得、それによって、選択されたコアの多結晶シリコンゲートが、選択されないコアと比較して増大したゲート長を有する。10

#### 【0006】

たとえば、半導体ダイ（たとえば、マルチコアプロセッサ）は複数のコアを含み得る。複数のコアは、第1のコア、第2のコア、第3のコア、および第4のコアを含み得る。第1のコアは、第2のコアよりも半導体ダイの中心近くに配置され得る。第3のコアは、第4のコアよりも半導体ダイの中心近くに配置され得る。第1のコアおよび第3のコアは内部コアであり得、第2のコアおよび第4のコアは外部コアであり得る。内部コアのトランジスタの多結晶シリコンゲートは、第1の長さを有し得る。外部コアの対応するトランジスタの多結晶シリコンゲートは、第1の長さよりも短い第2の長さを有し得る。第1の長さは、半導体ダイに関する実験データに基づいて決定され得る。20

#### 【0007】

特定の実施形態では、方法が、第1のトランジスタの第1の多結晶シリコンゲートを形成することを含み、第1の多結晶シリコンゲートは第1の長さを有する。第1のトランジスタは第1のコア内に配置される。方法はまた、第2のトランジスタの第2の多結晶シリコンゲートを形成することをも含み、第2の多結晶シリコンゲートは、第1の長さよりも短い第2の長さを有する。第2のトランジスタは第2のコア内に配置され、第1のコアは、第2のコアと比較して、半導体ダイのより中心近くに配置される。

#### 【0008】

別の特定の実施形態では、装置が、第1のトランジスタを含む第1のコアを含む。第1のトランジスタは第1の多結晶シリコンゲートを含み、第1の多結晶シリコンゲートは第1の長さを有する。装置はまた、第2のトランジスタを含む第2のコアをも含む。第2のトランジスタは、第1の長さよりも短い第2の長さを有する第2の多結晶シリコンゲートを含む。第1のコアは、第2のコアよりも半導体ダイの中心近くに配置される。30

#### 【0009】

開示される実施形態のうちの少なくとも1つによってもたらされる1つの特定の利点は、マルチコアプロセッサの1つまたは複数のコア（たとえば、内部コア）を、マルチコアプロセッサの1つまたは複数の他のコア（たとえば、外部コア）と比較して増大した多結晶シリコンゲート長を使用して製造することによって、マルチコアプロセッサのコア間漏れ電流変動および／またはコア間クロック速度変動を低減できることである。以下の節を含む本願全体を検討した後、本開示の他の態様、利点、および特徴が明らかとなるであろう：図面の簡単な説明、発明を実施するための形態、および特許請求の範囲。40

#### 【図面の簡単な説明】

#### 【0010】

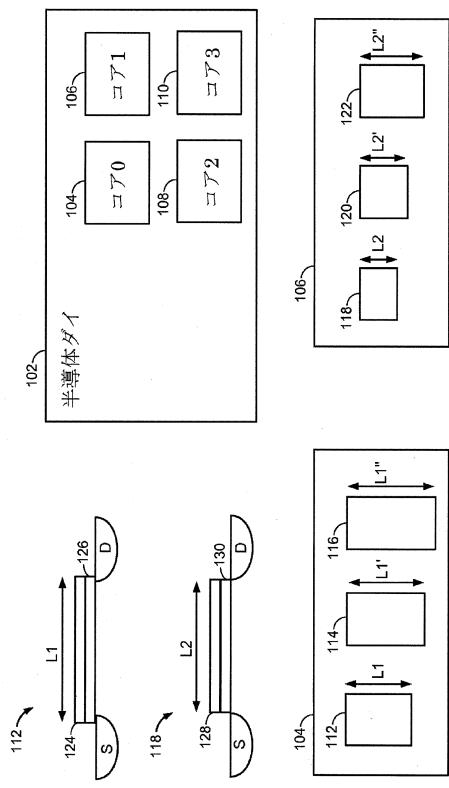

【図1】異なるゲート長を使用して製造されたマルチコアプロセッサの特定の例示的実施形態の図である。

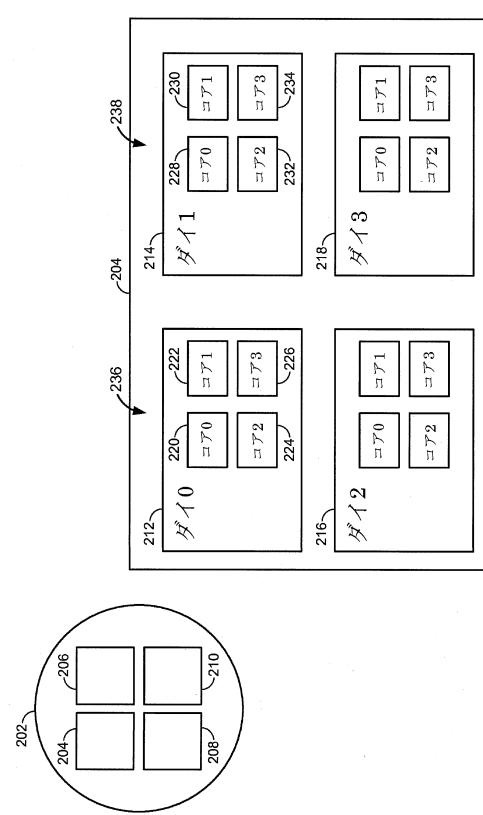

【図2】異なるゲート長を使用して製造されたマルチコアプロセッサの別の特定の例示的実施形態の図である。

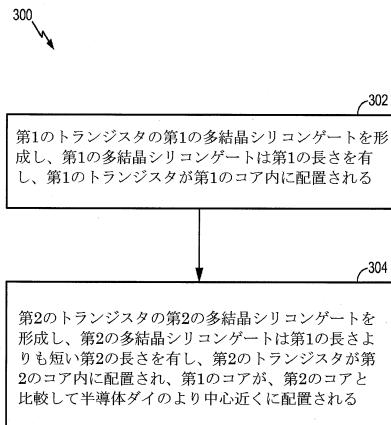

【図3】異なるゲート長を使用してマルチコアプロセッサを製造する方法の特定の例示的実施形態の流れ図である。

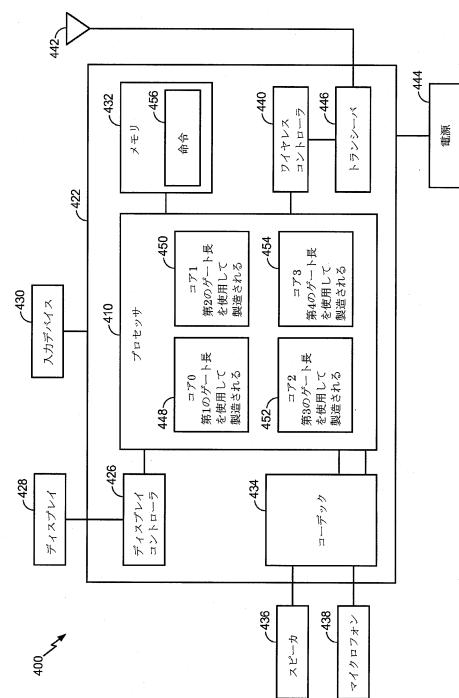

【図4】異なるゲート長を使用して製造されたマルチコアプロセッサを含むポートブルデ50

バイスのブロック図である。

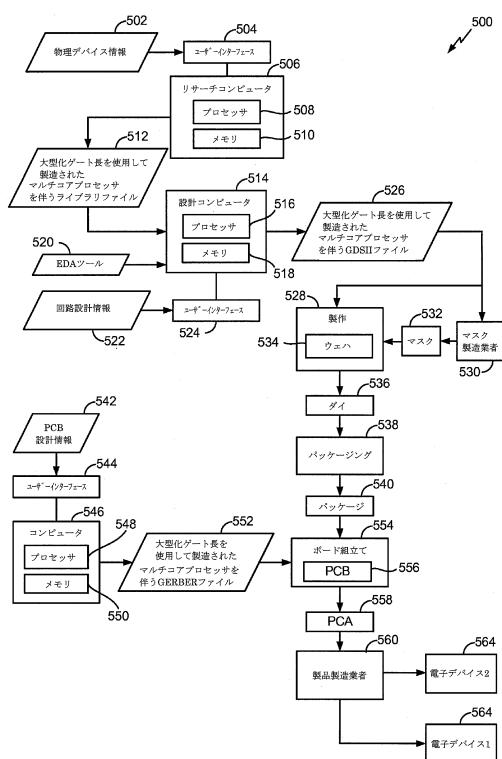

【図5】異なるゲート長を使用して製造されたマルチコアプロセッサを含む電子デバイスを製造するための製造プロセスの特定の例示的実施形態のデータ流れ図である。

【発明を実施するための形態】

【0011】

図1は、異なる多結晶シリコンゲート長を使用して製造されたマルチコアプロセッサの特定の例示的実施形態を示す。マルチコアプロセッサは、複数のコアを含む半導体ダイ102として製造され得る。たとえば、半導体ダイ102は、第1のコア104、第2のコア106、第3のコア108、および第4のコア110を含み得る。各コア104～110は複数のトランジスタを含み得る。第1のコア104および第3のコア108は、それぞれ第2のコア106および第4のコア110と比較して、半導体ダイ102のより中心近くに配置され得る。第1のコア104および第3のコア108は内部コアと呼ばれ得、第2のコア106および第4のコア110は外部コアと呼ばれ得る。

10

【0012】

例示的な非限定的例として、半導体ダイ102は、28ナノメートル(nm)プロセスを使用して製造され得る。実験データは、内部コア104、108は、外部コア106、110よりも高いクロック速度および高い漏れ電流を有することを示し得る。したがって、ゲート長以外のデバイス寸法を修正することなく、コア104～110間の漏れ電流変動およびクロック速度変動を低減するために、コア104および108が、コア106および110と比較して、特定の量だけ「大型化」され得る。

20

【0013】

たとえば、第1のコア104は、第1のトランジスタ112、第2のトランジスタ114、および第3のトランジスタ116を含み得る。各トランジスタ112～116は、異なるゲート長(たとえば、トランジスタの多結晶シリコンゲート長)を有し得る。一例として、第1のトランジスタ112はゲート長L1を有し得る。第2のトランジスタ114は、ゲート長L1よりも長いゲート長L1'を有し得る。第3のトランジスタ116は、ゲート長L1'よりも長いゲート長L1''を有し得る。第2のコア106は、第4のトランジスタ118、第5のトランジスタ120、および第6のトランジスタ122を含み得る。各トランジスタ118～122は異なるゲート長を有し得る。たとえば、第4のトランジスタ118はゲート長L2を有し得る。第5のトランジスタ120は、ゲート長L2よりも長いゲート長L2'を有し得る。第6のトランジスタ122は、ゲート長L2'よりも長いゲート長L2''を有し得る。第3のコア108のトランジスタのゲート長は、第1のコア104の対応するトランジスタ(たとえば、トランジスタ112～116)のゲート長と同一のゲート長(たとえば、ゲート長L1～L1'')を有し得る。第4のコア110のトランジスタのゲート長は、第2のコア106の対応するトランジスタ(たとえば、トランジスタ118～122)のゲート長と同一のゲート長(たとえば、ゲート長L2～L2'')を有し得る。

30

【0014】

第1のコア104のトランジスタは、漏れ電流変動および/またはクロック速度変動を低減するために、第2のコア106の対応するトランジスタと比較して大型化され得る。たとえば、第1のトランジスタ112と第4のトランジスタ118が、対応するトランジスタであり得る。第1のトランジスタ112は、ソース(S)と、ドレイン(D)と、ゲート長L1を有する第1の多結晶シリコンゲート層124とを含み得る。第1のトランジスタ112はまた、ゲート長L1を有する第1の酸化物層126をも含み得る。第4のトランジスタ118は、ゲート長L2を有する第2の多結晶シリコンゲート層128を含み得る。第4のトランジスタ118はまた、ゲート長L2を有する第2の酸化物層130をも含み得る。ゲート長L1は、ゲート長L2と比較して1nmだけ大型化され得る(すなわち、L1 = L2 + 1nm)。

40

【0015】

第1のコア104のトランジスタは、第2のコア106の対応するトランジスタと比較

50

して同じ量だけ大型化され得る。たとえば、ゲート長  $L_1$  と  $L_2$  との間の差がゲート長  $L_1'$  と  $L_2'$  との間の差とほぼ同じとなり、ゲート長  $L_1''$  と  $L_2''$  との間の差とほぼ同じとなるように、ゲート長  $L_1$ 、 $L_1'$ 、および  $L_1''$  が大型化され得る。特定の実施形態では、ゲート長  $L_1$ 、 $L_1'$ 、および  $L_1''$  はそれぞれ  $1\text{ nm}$  だけ大型化される（すなわち、 $L_1 = L_2 + 1\text{ nm}$ 、 $L_1' = L_2' + 1\text{ nm}$ 、 $L_1'' = L_2'' + 1\text{ nm}$ ）。別の特定の実施形態では、ゲート長  $L_1$ 、 $L_1'$ 、および  $L_1''$  はそれぞれ、 $2\text{ nm}$  または別の量だけ大型化される。ゲート長  $L_2$ 、 $L_2'$ 、および / または  $L_2''$  は、多結晶シリコンゲート層および / または酸化物層の標準長さに対応し得、ゲート長  $L_1$ 、 $L_1'$ 、および / または  $L_1''$  は、標準長さと比較して増大した長さに対応し得る。特定の実施形態では、製造中にコア 104 および 108 を  $1\text{ nm}$  だけ大型化すること（すなわち、コア 106 および 110 のゲート長と比較してコア 104 および 108 のゲート長 ( $L_1$ 、 $L_1'$ 、および  $L_1''$ ) を  $1\text{ nm}$  だけ増大させること）は、そのような大型化なしにコア 104 および 108 を製造することと比較して、コア 104 および 108 の漏れ電流を 5% 低減し得る。

10

#### 【0016】

大型化ゲート長（たとえば、ゲート長  $L_1$ 、ゲート長  $L_1'$ 、および / またはゲート長  $L_1''$ ）を求めるために、内部コア（たとえば、第 1 のコア 104 および第 3 のコア 108）および外部コア（たとえば、第 2 のコア 106 および第 4 のコア 110）が第 1 の半導体ダイ上に製造され得、したがって、対応する内部コアのトランジスタの多結晶シリコンゲートおよび外部コアの多結晶シリコンゲートが標準長さを有する（たとえば、第 1 のトランジスタ 112 および第 4 のトランジスタ 118 がゲート長  $L_2$  を有し、第 2 のトランジスタ 114 および第 5 のトランジスタ 120 がゲート長  $L_2'$  を有し、第 3 のトランジスタ 116 および第 6 のトランジスタ 122 がゲート長  $L_2''$  を有する）。性能変動を求めるために、第 1 の半導体ダイのコアに関連する性能パラメータが比較され得る。たとえば、コア間漏れ電流変動を求めるために、内部コアの漏れ電流と外部コアの漏れ電流とが比較され得る（たとえば、第 2 のコア 106 の漏れ電流と比較した第 1 のコア 104 の漏れ電流、または第 4 のコア 110 の漏れ電流と比較した第 3 のコア 108 の漏れ電流）。別の例として、コア間クロック速度変動を求めるために、内部コアのクロック速度と外部コアのクロック速度とが比較され得る。漏れ電流変動および / またはクロック速度変動は、温度効果および / またはプロセス変動によるものであり得る。コア間漏れ電流変動および / またはコア間クロック速度変動に基づいて、大型化されたゲート長が求められ得る。たとえば、コア間漏れ電流変動および / またはコア間クロック速度変動が第 1 の範囲以内（たとえば、5% 以下）にあるとき、大型化ゲート長は、標準長さに比べて  $1\text{ nm}$  の増大である。コア間漏れ電流変動および / またはコア間クロック速度変動が第 2 の範囲以内（たとえば、5% 超）にあるとき、大型化ゲート長は、標準長さに比べて  $2\text{ nm}$  の増大であり得る。大型化ゲート長は、漏れ電流変動および / またはクロック速度変動を低減するように求められ得る。

20

30

#### 【0017】

たとえば、第 1 のコア 104 と第 2 のコア 106 との間の漏れ電流変動は  $6\text{ ミリアンペア (mA)}$  であり得、第 1 のコア 104 と第 2 のコア 106 との間のクロック速度変動は  $40\text{ メガヘルツ (MHz)}$  であり得る。第 3 のコア 108 と第 4 のコア 110 との間の漏れ電流変動は  $4\text{ mA}$  であり得、第 3 のコア 108 と第 4 のコア 110 との間のクロック速度変動は  $30\text{ MHz}$  であり得る。漏れ電流変動および / またはクロック速度変動に基づいて、漏れ電流変動および / またはクロック速度変動を低減するために、大型化ゲート長が、対応する標準長さよりも  $1\text{ ナノメートル (nm)}$  だけ長くなるように求められ得る。したがって、内部コアおよび外部コアが第 2 の半導体ダイ上に製造されるとき、内部コアのトランジスタの多結晶シリコンゲートが、 $1\text{ nm}$  の長さだけ普遍的に増大（「大型化」）され得る。別の例では、あらゆる内部コア内で大型化ゲート長を有するように内部コア内のゲートを同じ量（たとえば、 $1\text{ nm}$ ）だけ大型化する代わりに、各内部コアが、異なる量だけ個々に大型化され得る。たとえば、第 1 のコア 104 が  $1\text{ nm}$  だけ大型化され得（

40

50

たとえば、第1のコア104内のゲートが1nmの長さだけ増大される)、第3のコア108が2nmだけ大型化され得る。

#### 【0018】

内部コアの対応するトランジスタの多結晶シリコンゲートの長さを増大させることによって、短チャネル効果による内部コアの漏れ電流が低減され得る。したがって、内部コアと外部コアとの間の漏れ電流変動が低減され得る。さらに、内部コアの対応するトランジスタの多結晶シリコンゲートの長さを増大させることによって、内部コアのトランジスタの送信時間(トランジスタがソースからドレインに電荷を移送するのにかかる時間量)が増大し得る。したがって、トランジスタのスイッチング能力が低減され得、内部コアのクロック速度が低減され、内部コアと外部コアとの間のクロック速度変動が低減され得る。10

#### 【0019】

半導体ダイ102は、ウェハ上に製造される複数の半導体ダイのうちの1つであり得る。特定の実施形態では、複数の半導体ダイの各々の中の対応する半導体ダイのより中心近くに配置されるコアが、ウェハにわたって同量またはほぼ同量だけ大型化される。たとえば、複数の半導体ダイの各々の中の対応する半導体ダイのより中心近くに配置されるコアが、1nmだけ大型化され得る。別の特定の実施形態では、図2で説明されるように、第1の半導体ダイのコアと、第2の半導体ダイの対応するコアとが、ウェハ上の第1の半導体ダイおよび第2の半導体ダイの位置に基づいて、異なる量だけ大型化され得る。図1は、第1のコア104のトランジスタ112、114、および116が3つの異なるゲート長を有し、第2のコア106のトランジスタ114、120、および122が異なるゲート長を有することを示すが、別の実施形態では第1のコア104および第2のコア106のトランジスタが4つ以上の異なるゲート長または2つ以下の異なるゲート長を有し得ることを理解されたい。20

#### 【0020】

増大したゲート長は漏れ電流およびスイッチング速度を低減し得るので、半導体ダイの1つまたは複数の他のコアを大型化することなく、半導体ダイの1つまたは複数のコアを大型化することによって、半導体ダイのコア間漏れ電流変動および/またはコア間クロック速度変動が低減され得る。コア間漏れ電流変動および/またはコア間クロック速度変動が低減されて、半導体ダイの歩留まりが高まり得る。大型化は、半導体ダイのゲートを製造するために単一マスク修正を使用することによって実施され得る。単一マスクの修正は、半導体ダイの製造プロセスの比較的小さい変更である。したがって、コア大型化を実施するために単一マスク修正を使用することは、製造プロセスの完全な再設計と比較して、製造の複雑さを低減し得る。30

#### 【0021】

図2は、第1のレチクル204、第2のレチクル206、第3のレチクル208、および第4のレチクル210を含む複数のレチクルを含むウェハ202を示す。各レチクル204～210は、ウェハ202の特定の部分に対応し得る。マルチコアプロセッサなどの半導体デバイスが、各レチクル204～210内の半導体ダイとして形成され得る。たとえば、第1の半導体ダイ212、第2の半導体ダイ214、第3の半導体ダイ216、および第4の半導体ダイ218を含む複数の半導体ダイが、マスクを使用して第1のレチクル204内に製造され得る。半導体ダイ212～218のコピーが、レチクル206～210内に形成され得る。図2はレチクル204内に4つの半導体ダイを示すが、任意の数の半導体ダイがレチクル204内に製造され得ることを理解されたい。40

#### 【0022】

各半導体ダイ204～210は複数のコアを含み得る。たとえば、第1の半導体ダイ212は、第1のコア220、第2のコア222、第3のコア224、および第4のコア226を含み得る。第2の半導体ダイ214は、第5のコア228、第6のコア230、第7のコア232、および第8のコア234を含み得る。

#### 【0023】

各半導体ダイ212～218の各コアの大型化(それが行われる場合)の量は、ウェハ50

202の製造プロセスに関する実験データによって個々に決定され得る。実験データは、製造プロセス変動の対象となるプロセス変動データおよび／またはコアの性能データ（たとえば、コアの漏れ電流、コアのクロック速度など）を含み得る。例示のために、第1の半導体ダイ212のコアが、第2の半導体ダイ214のコア、第3の半導体ダイ216のコア、および／または第4の半導体ダイ218のコアとは異なる量だけ大型化され得る。たとえば、レチクル204内に半導体ダイ212～218を含むウェハ202の第1の反復が製造され得る。半導体ダイ212～218のコアのトランジスタの多結晶シリコンゲート層および／または酸化物層が、第1の反復では単一の長さ（たとえば、ゲート長L1）に従って製造され得る。第1の反復での各半導体ダイ212～218のコア間漏れ電流変動および／またはコア間クロック速度変動が測定され、実験データが生成され得る。コア間漏れ電流変動および／またはコア間クロック速度変動は、製造プロセス変動によるものであり得る。

10

#### 【0024】

実験データに基づいて、各半導体ダイ212～218の各コアの大型化の量が個々に決定され得る。実験データは、コア間漏れ電流変動および／またはコア間クロック速度変動がレチクル204内の半導体ダイ212～218の位置に依存することを示し得る。たとえば、レチクル204の左側のレチクルフィールド236上の半導体ダイ（たとえば、第1の半導体ダイ212および第3の半導体ダイ216）のコアは、レチクル204の右側のレチクルフィールド238上の半導体ダイ（たとえば、第2の半導体ダイ214および第4の半導体ダイ218）のコアとは異なるコア間漏れ電流変動および／またはコア間クロック速度変動を有し得る。

20

#### 【0025】

一例として、実験データは、左側のレチクルフィールド236上で、第1の半導体ダイ212の内部コア（たとえば、第1のコア220および第3のコア224）が第1の半導体ダイ212の外部コア（たとえば、第2のコア222および第4のコア226）よりも6mA高い漏れ電流を有し得ることを示し得る。実験データはまた、右側のレチクルフィールド238上で、第2の半導体ダイ214の内部コア（たとえば、第5のコア228および第7のコア232）が外部コア（たとえば、第6のコア230および第8のコア234）よりも10mA高い漏れ電流を有し得ることを示し得る。実験データに基づいて、ウェハ202の第2の反復の製造中に、第1の半導体ダイ212の内部コアが1nmだけ大型化され得、第2の半導体ダイ214の内部コアが2nmだけ大型化され得、第1の半導体ダイ212および第2の半導体ダイ214の外部コアが、異なるコア間漏れ電流変動を低減し、かつ／またはコア間クロック速度変動を低減するために、標準長さ（たとえば、図1のL2～L2'のゲート長）を使用して形成され得る。別の例では、第2の半導体ダイ214の内部コアがウェハ202の第2の反復で大型化され得、一方、第1の半導体ダイ212の内部コアが第2の反復で不变のままであり得、またはその逆である。

30

#### 【0026】

別の例では、半導体ダイのいくつかまたはすべてのコア（内部コアおよび／または外部コア）が、コア間漏れ電流変動および／またはコア間クロック速度変動をさらに低減するために、実験データに基づいて異なる量だけ個々に大型化され得る。たとえば、実験データは、第1のコア220が第2のコア222よりも4mA高い漏れ電流を有し得ること、および第3のコア224が第4のコア226よりも8mA高い漏れ電流を有し得ることを示し得る。実験データに基づいて、第1のコア220が1nmだけ大型化され得（たとえば、第1のコア220のトランジスタのゲート長が、第2のコア222の対応するトランジスタのゲート長に比べて1nmだけ増大される）、第3のコア224が2nmだけ大型化され得る（たとえば、第3のコア224のトランジスタのゲート長が、第4のコア226の対応するトランジスタのゲート長に比べて2nmだけ増大される）。第2のコア222および／または第4のコア226も実験データに基づいて大型化され得る。

40

#### 【0027】

図1～図2は、半導体ダイの内部コア（たとえば、図1の第1のコア104、図2の第

50

1 のコア 220 など) の多結晶シリコンゲート長が半導体ダイの対応する外部コア(たとえば、第2のコア106、第2のコア222など)の多結晶シリコンゲート長に比べて大型化され得ることを示すが、外部コアが内部コアよりも高い漏れ電流および/または高速のクロック速度を有するとき、外部コアの多結晶シリコンゲート長が内部コアの多結晶シリコンゲート長に比べて大型化され得ることを理解されたい。

#### 【0028】

図3は、異なる多結晶シリコンゲート長を使用してマルチコアプロセッサを製造する方法300の特定の例示的実施形態の流れ図を示す。方法300は、302において、第1のトランジスタの第1の多結晶シリコンゲートを形成することを含む。第1の多結晶シリコンゲートは第1の長さを有し、第1のトランジスタが第1のコア内に配置される。たとえば、図1を参照すると、第1のトランジスタ112は、ゲート長L1を有する第1の多結晶シリコンゲート層124を含み得る。

10

#### 【0029】

方法300はまた、304において、第2のトランジスタの第2の多結晶シリコンゲートを形成することを含む。第2の多結晶シリコンゲートは第1の長さよりも短い第2の長さを有する。第2のトランジスタが第2のコア内に配置され、第1のコアが、第2のコアと比較して半導体ダイのより中心近くに配置される。たとえば、図1を参照すると、第4のトランジスタ118は、ゲート長L2を有する第2の多結晶シリコンゲート層128を含み得る。ゲート長L1は、ゲート長L2と比較して1nmだけ大型化され得る。したがって、方法300は、大型化ゲート長を使用して複数のコアを含む半導体ダイを製造することを可能にし得る。大型化ゲート長の使用は、コア間漏れ電流変動および/またはコア間クロック速度変動を低減し得る。

20

#### 【0030】

特定の実施形態では、方法300は、第3のコアの第3のトランジスタの第3の多結晶シリコンゲートを形成することを含む。第3の多結晶シリコンゲートは第1の長さを有する。たとえば、図1を参照すると、第3のコア108のトランジスタのゲート長は、第1のコア104の対応するトランジスタ(たとえば、トランジスタ112～116)のゲート長と同一のゲート長(たとえば、ゲート長L1～L1')を有し得る。方法300はまた、第4のコアの第4のトランジスタの第4の多結晶シリコンゲートを形成することをも含み得る。第4の多結晶シリコンゲートは第2の長さを有する。第3のコアは、第4のコアと比較して半導体ダイのより中心近くに配置される。たとえば、図1を参照すると、第4のコア110のトランジスタのゲート長は、第2のコア106の対応するトランジスタ(たとえば、トランジスタ118～122)のゲート長と同一のゲート長(たとえば、ゲート長L2～L2')を有し得る。第3のコア108は、第4のコア110と比較して半導体ダイ102のより中心近くに配置され得る。

30

#### 【0031】

別の特定の実施形態では、方法300は、第3のコア内に配置される第3のトランジスタの第3の多結晶シリコンゲートを形成すること、および第4のコア内に配置される第4のトランジスタの第4の多結晶シリコンゲートを形成することを含む。第3の多結晶シリコンゲートは第3の長さを有し、第4の多結晶シリコンゲートは第4の長さを有する。第1の長さは、第2の長さを第1の量だけ増大させることによって求められる。第3の長さは、第4の長さを第2の量だけ増大させることによって求められる。第1の量は第2の量とは異なる。第1のトランジスタと第2のトランジスタとは対応するトランジスタであり、第3のトランジスタと第4のトランジスタとは対応するトランジスタである。たとえば、図2を参照すると、実験データに基づいて、第1のコア220が1nmだけ大型化され得(たとえば、第1のコア220のトランジスタのゲート長が、第2のコア222の対応するトランジスタのゲート長に比べて1nmだけ増大される)、第3のコア224が2nmだけ大型化され得る(たとえば、第3のコア224のトランジスタのゲート長が、第4のコア226の対応するトランジスタのゲート長に比べて2nmだけ増大される)。

40

#### 【0032】

10

20

30

40

50

別の特定の実施形態では、方法 300 は、第 1 の長さを使用して第 1 の多結晶シリコンゲートを形成する前に、第 2 の長さを使用して第 1 のコアおよび第 2 のコアを形成することを含む。たとえば、図 1 を参照すると、内部コア（たとえば、第 1 のコア 104 および第 3 のコア 108）および外部コア（たとえば、第 2 のコア 106 および第 4 のコア 110）が、第 1 の半導体ダイ上に製造され得、したがって、対応する内部コアのトランジスタの多結晶シリコンゲートおよび外部コアの多結晶シリコンゲートが標準長さを有する（たとえば、第 1 のトランジスタ 112 および第 4 のトランジスタ 118 がゲート長 L2 を有し、第 2 のトランジスタ 114 および第 5 のトランジスタ 120 がゲート長 L2' を有し、第 3 のトランジスタ 116 および第 6 のトランジスタ 122 がゲート長 L2'' を有する）。

10

#### 【0033】

方法 300 はまた、第 1 の長さを使用して第 1 の多結晶シリコンゲートを形成する前に、第 1 のコアに関連する第 1 の性能パラメータを測定すること、および第 2 のコアに関連する第 2 の性能パラメータを測定することをも含み得る。たとえば、図 1 を参照すると、内部コアの漏れ電流と、外部コアの漏れ電流とが比較され、コア間漏れ電流変動が求められ得る（たとえば、第 2 のコア 106 の漏れ電流と比較した第 1 のコア 104 の漏れ電流、または第 4 のコア 110 の漏れ電流と比較した第 3 のコア 108 の漏れ電流）。別の例として、内部コアのクロック速度と、外部コアのクロック速度とが比較され、コア間クロック速度変動が求められ得る。

#### 【0034】

20

方法 300 は、第 1 の長さを使用して第 1 の多結晶シリコンゲートを形成する前に、第 1 の性能パラメータと第 2 の性能パラメータとの間の差に基づいて第 1 の長さを求めるることをさらに含み得る。たとえば、図 1 を参照すると、コア間漏れ電流変動および／またはコア間クロック速度変動に基づいて、差が第 1 のしきい値未満であるときに第 1 の値を有し、差が第 2 のしきい値以上であるときに第 2 の値を有することなどによって、大型化ゲート長が求められ得る。

#### 【0035】

30

図 4 に、異なるゲート長の複数のコアを有するプロセッサ（たとえば、図 1 の半導体ダイ 102、図 2 の半導体ダイ 212～218 のいずれか）を含む通信デバイス 400 を示す。図 3 で説明した方法、またはそのいくつかの部分が、通信デバイス 400 の構成要素を製造するのに使用され得る。

#### 【0036】

通信デバイス 400 は、メモリ 432 に結合された、デジタル信号プロセッサ（DSP）やマルチコアプロセッサなどのプロセッサ 410 を含む。メモリ 432 は、命令 456 を格納する非一時的有形コンピュータ可読および／またはプロセッサ可読記憶デバイスであり得る。命令 456 は、プロセッサ 410 によって実行可能であり得る。プロセッサ 410 は、第 1 のゲート長（たとえば、図 1 のゲート長 L1、ゲート長 L1'、ゲート長 L1''、またはそれらの組合せ）を使用して製造された第 1 のコア 448 と、第 2 のゲート長（たとえば、ゲート長 L2、ゲート長 L2'、ゲート長 L2''、またはそれらの組合せ）を使用して製造された第 2 のコア 450 と、第 3 のゲート長を使用して製造された第 3 のコア 452 と、第 4 のゲート長を使用して製造された第 4 のコア 454 とを含む複数のコアを含み得る。

40

#### 【0037】

第 1 のコア 448 および／または第 3 のコア 452 は、プロセッサ 410 の内部コア（たとえば、図 1 の第 1 のコア 104 および／または第 3 のコア 108、図 2 の第 1 のコア 220 および／または第 3 のコア 224、図 2 の第 5 のコア 228 および／または第 7 のコア 232）に対応し得る。第 2 のコア 450 および／または第 4 のコア 454 は、プロセッサ 410 の外部コア（たとえば、第 2 のコア 106 および／または第 4 のコア 110、第 2 のコア 222 および／または第 4 のコア 226、第 6 のコア 230 および／または第 8 のコア 234）に対応し得る。特定の実施形態では、第 1 のゲート長は、第 2 のゲー

50

ト長に比べて増大したゲート長に対応する。別の特定の実施形態では、第3のゲート長は、第4のゲート長に比べて増大したゲート長に対応する。別の特定の実施形態では、第1のコア448および第3のコア452が同量だけ大型化される。別の特定の実施形態では、第1のコア448および第3のコア452が異なる量だけそれぞれ大型化される。

#### 【0038】

図4は、通信デバイス400がプロセッサ410およびディスプレイデバイス428に結合されたディスプレイコントローラ426をも含み得ることを示す。コーダ/デコーダ(コーデック)434もプロセッサ410に結合され得る。スピーカ436およびマイクロフォン438が、コーデック434に結合され得る。図4はまた、プロセッサ410に結合されたワイヤレスコントローラ440をも示す。ワイヤレスコントローラ440は、トランシーバ446を介してアンテナ442と通信している。ワイヤレスコントローラ440、トランシーバ446、およびアンテナ442は、通信デバイス400によるワイヤレス通信を可能にするワイヤレスインターフェースを表し得る。通信デバイス400は多数のワイヤレスインターフェースを含み得、異なるワイヤレスネットワークは、異なるネットワーキング技術またはネットワーキング技術の組合せ(たとえば、Bluetooth低エネルギー、近距離場通信、Wi-Fi、セルラーなど)をサポートするように構成される。

10

#### 【0039】

特定の実施形態では、プロセッサ410、ディスプレイコントローラ426、メモリ432、コーデック434、ワイヤレスコントローラ440、およびトランシーバ446が、システムインパッケージまたはシステムオンチップデバイス422内に含まれる。特定の実施形態では、入力デバイス430および電源444が、システムオンチップデバイス422に結合される。その上、特定の実施形態では、図4に示されるように、ディスプレイデバイス428、入力デバイス430、スピーカ436、マイクロフォン438、アンテナ442、および電源444が、システムオンチップデバイス422の外部にある。しかしながら、ディスプレイデバイス428、入力デバイス430、スピーカ436、マイクロフォン438、アンテナ442、および電源444の各々が、インターフェースやコントローラなどのシステムオンチップデバイス422の構成要素に結合され得る。

20

#### 【0040】

記載の実施形態と共に、装置が、処理のための第1の手段を含む。処理のための第1の手段は第1のトランジスタを含む。第1のトランジスタは第1の多結晶シリコンゲートを含み、第1の多結晶シリコンゲートは第1の長さを有する。たとえば、処理のための第1の手段は、図1の第1のコア104、第3のコア108、図2の第1のコア220、第3のコア224、第5のコア228、第7のコア232、第3の半導体ダイ216のコア(たとえば、内部コア、対応するコアに比べて多い漏れ電流および/または高速のクロック速度を有するコア)、第4の半導体ダイ218のコア(たとえば、内部コア、対応するコアに比べて多い漏れ電流および/または高速なクロック速度を有するコア)、プロセッサによって実行可能なデータおよび/または命令を処理するように構成された1つまたは複数のデバイス、あるいはそれらの組合せを含み得る。

30

#### 【0041】

装置はまた、処理のための第2の手段をも含む。処理のための第2の手段は第2のトランジスタを含む。第2のトランジスタは、第1の長さよりも短い第2の長さを有する第2の多結晶シリコンゲートを含む。処理のための第1の手段は、処理のための第2の手段よりも半導体ダイの中心近くに配置される。たとえば、処理のための第2の手段は、図1の第2のコア106、第4のコア110、図2の第2のコア222、第4のコア226、第6のコア230、第8のコア234、第3の半導体ダイ216のコア(たとえば、外部コア、対応するコアに比べて少ない漏れ電流および/または低速なクロック速度を有するコア)、第4の半導体ダイ218のコア(たとえば、外部コア、対応するコアに比べて少ない漏れ電流および/または低速なクロック速度を有するコア)、プロセッサによって実行可能なデータおよび/または命令を処理するように構成された1つまたは複数のデバイス

40

50

、あるいはそれらの組合せを含み得る。

#### 【0042】

上記の開示されるデバイスおよび機能は、コンピュータ可読媒体上に格納されたコンピュータファイル（たとえばR T L、G D S I I、G E R B E Rなど）内に設計および構成され得る。いくつかの、またはすべてのそのようなファイルが、そのようなファイルに基づいてデバイスを製作する製作ハンドラに提供され得る。得られる製品は半導体ウェハを含み、次いで半導体ウェハが半導体ダイに切断され、半導体チップ内にパッケージングされる。次いでチップが、前述のデバイスで利用される。図5は、電子デバイス製造プロセス500の特定の例示的実施形態を示す。

#### 【0043】

物理デバイス情報502が、リサーチコンピュータ506などの製造プロセス500において受信される。物理デバイス情報502は、図1の半導体ダイ102、図2の半導体ダイ212～218のいずれか、図4のプロセッサ410、またはそれらの組合せなどの半導体デバイスの少なくとも1つの物理的性質を表す設計情報を含み得る。たとえば、物理デバイス情報502は、リサーチコンピュータ506に結合されたユーザインターフェース504を介して入力される物理パラメータ、材料特性、および構造情報を含み得る。リサーチコンピュータ506は、メモリ510などのコンピュータ可読媒体に結合された、1つまたは複数の処理コアなどのプロセッサ508を含む。メモリ510は、プロセッサ508に、物理デバイス情報502をファイルフォーマットに準拠するように変換させ、ライブラリファイル512を生成させるように実行可能なコンピュータ可読命令を格納し得る。

10

#### 【0044】

特定の実施形態では、ライブラリファイル512は、変換された設計情報を含む少なくとも1つのデータファイルを含む。たとえば、ライブラリファイル512は、電子設計自動化（E D A : e l e c t r o n i c d e s i g n a u t o m a t i o n ）ツール520と共に使用するために提供される、図1の半導体ダイ102、図2の半導体ダイ212～218、図4のプロセッサ410、またはそれらの任意の組合せを含むデバイスを含む半導体デバイスのライブラリを含み得る。

20

#### 【0045】

ライブラリファイル512は、メモリ518に結合された、1つまたは複数の処理コアなどのプロセッサ516を含む設計コンピュータ514において、E D Aツール520と共に使用され得る。E D Aツール520は、設計コンピュータ514のユーザが、ライブラリファイル512の、図1の半導体ダイ102、図2の半導体ダイ212～218のいずれか、図4のプロセッサ410、またはそれらの組合せを含む回路を設計することを可能にするために、プロセッサ実行可能命令としてメモリ518に格納され得る。たとえば、設計コンピュータ514のユーザは、設計コンピュータ514に結合されたユーザインターフェース524を介して回路設計情報522を入力し得る。回路設計情報522は、図1の半導体ダイ102、図2の半導体ダイ212～218のいずれか、図4のプロセッサ410、またはそれらの任意の組合せなどの半導体デバイスの少なくとも1つの物理的性質を表す設計情報を含み得る。例示のために、回路設計特性は、特定の回路の識別および回路設計内の他の要素に対する関係、位置決め情報、フィーチャサイズ情報、相互接続情報、または半導体デバイスの物理的性質を表す他の情報を含み得る。

30

40

#### 【0046】

設計コンピュータ514は、ファイルフォーマットに準拠するように、回路設計情報522を含む設計情報を変換するように構成され得る。例示のために、ファイル形成は、回路レイアウトについての平面幾何形状、テキストラベル、および他の情報をグラフィックデータシステム（G D S I I ）ファイルフォーマットなどの階層フォーマットで表すデータベースバイナリファイルフォーマットを含み得る。設計コンピュータ514は、他の回路または情報に加えて、図1の半導体ダイ102、図2の半導体ダイ212～218のいずれか、図4のプロセッサ410、またはそれらの組合せについて記述する情報を含むG

50

D S I I ファイル 5 2 6 などの変換された設計情報を含むデータファイルを生成するように構成され得る。例示のために、データファイルは、図 1 の半導体ダイ 1 0 2 、図 2 の半導体ダイ 2 1 2 ~ 2 1 8 のいずれか、図 4 のプロセッサ 4 1 0 、またはそれらの組合せを含み、S O C 内の追加の電子回路および構成要素をも含むシステムオンチップ ( S O C ) に対応する情報を含み得る。

#### 【 0 0 4 7 】

図 1 の半導体ダイ 1 0 2 、図 2 の半導体ダイ 2 1 2 ~ 2 1 8 のいずれか、図 4 のプロセッサ 4 1 0 、またはそれらの組合せを G D S I I ファイル 5 2 6 内の変換された情報に従って製造するために、G D S I I ファイル 5 2 6 が製作プロセス 5 2 8 において受信され得る。製作プロセス 5 2 8 は、メモリ内に格納されたプロセッサ実行可能命令にアクセスするプロセッサによって制御され得る。命令は、製作プロセス 5 2 8 の異なる段階を実施するようにプロセッサによって実行可能であり得る。プロセッサは、通信デバイス、セル 10 フォン、スマートフォン、タブレットコンピュータ、ラップトップコンピュータ、携帯情報端末 ( P D A ) 、およびコンピュータからなるグループから選択されたデバイス内に統合され得る。

#### 【 0 0 4 8 】

たとえば、製作プロセス 5 2 8 は、第 1 のトランジスタの第 1 の多結晶シリコンゲートと、第 2 のトランジスタの第 2 の多結晶シリコンゲートの形成を含み得る。第 1 の多結晶シリコンゲートは第 1 の長さを有し、第 1 のコア内に配置される。第 2 の多結晶シリコンゲートは、第 1 の長さよりも短い第 2 の長さを有し、第 2 のコア内に配置される。第 1 のコアは、第 2 のコアと比較して半導体ダイのより中心近くに配置される。プロセッサ実行可能命令に基づいて、プロセッサは、( たとえば、化学気相堆積プロセスを介して ) 第 1 のトランジスタおよび第 2 のトランジスタの多結晶シリコンゲートとなるべき基板上に多結晶シリコン層を堆積せしめるように半導体製作マシンに命令するように、堆積段階中に半導体製作マシンにコマンドを送り得る。プロセッサは、エッチングを実施して、第 1 のトランジスタの多結晶シリコンゲートが大型化された長さ ( たとえば、図 1 のゲート長 L 1 ~ L 1 ' ) を有し、第 2 のトランジスタの多結晶シリコンゲートが標準長さ ( たとえば、ゲート長 L 2 ~ L 2 ' ) を有するような多結晶シリコンゲートを形成するように、パターニング段階中に半導体製作マシンにコマンドを送り得る。

#### 【 0 0 4 9 】

製作プロセス 5 2 8 はまた、第 1 の長さを使用して第 1 の多結晶シリコンゲートを形成する前に、第 2 の長さを使用して第 1 のコアおよび第 2 のコアを形成することをも含み得る。たとえば、プロセッサ実行可能命令に基づいて、プロセッサは、( 堆積プロセス、エッチングプロセスなどを介して ) 標準長さを使用して第 1 のコアおよび第 2 のコアを製作するように、半導体製作マシンにコマンドを送り得る。

#### 【 0 0 5 0 】

製作プロセス 5 2 8 は、第 1 の長さを使用して第 1 の多結晶シリコンゲートを形成する前に、第 1 のコアに関連する第 1 の性能パラメータを測定することをさらに含み得る。たとえば、プロセッサ実行可能命令に基づいて、プロセッサは、第 1 のコアの 1 つまたは複数の性能パラメータ ( たとえば、漏れ電流、クロック速度など ) を測定するように、半導体製作マシンまたは測定マシンにコマンドを送り得る。測定された 1 つまたは複数の性能パラメータは、メモリ、半導体製作マシンのメモリ、測定マシンのメモリ、またはそれらの組合せの中に格納され得る。

#### 【 0 0 5 1 】

製作プロセス 5 2 8 は、第 1 の長さを使用して第 1 の多結晶シリコンゲートを形成する前に、第 2 のコアに関連する第 2 の性能パラメータを測定することをさらに含み得る。たとえば、プロセッサ実行可能命令に基づいて、プロセッサは、第 2 のコアの 1 つまたは複数の性能パラメータ ( たとえば、漏れ電流、クロック速度など ) を測定するように、半導体製作マシンまたは測定マシンにコマンドを送り得る。測定された 1 つまたは複数の性能パラメータは、メモリ、半導体製作マシンのメモリ、測定マシンのメモリ、またはそれら

10

20

30

40

50

の組合せの中に格納され得る。

**【0052】**

製作プロセス528は、第1の長さを使用して第1の多結晶シリコンゲートを形成する前に、第1の性能パラメータと第2の性能パラメータとの間の差に基づいて第1の長さを求ることをさらに含み得る。たとえば、プロセッサ実行可能命令に基づいて、プロセッサは、第1のコアの測定された1つまたは複数の性能パラメータと、第2のコアの対応する測定された1つまたは複数の性能パラメータとの間の差を計算し得る。あるいは、プロセッサは、差を計算するように半導体製作マシンまたは測定マシンにコマンドを送り得る。差を使用して、プロセッサは、対応する標準長さ（たとえば、ゲート長L2、ゲート長L2'、ゲート長L2''、または組合せ）にオフセットを加えることによって、第1の長さ（たとえば、ゲート長L1、ゲート長L1'、ゲート長L1''、またはそれらの組合せ）を求め得る。プロセッサは、ルックアップテーブル内のオフセットをルックアップし得、またはモデルに従ってオフセットを計算し得る。あるいは、プロセッサは、（たとえば、ルックアップテーブルを使用することによって）第1の長さを求めるように半導体製作マシンまたは測定マシンに命令し得る。10

**【0053】**

製作プロセス528の別の例として、デバイス製造プロセスは、代表的マスク532として示される、フォトリソグラフィ処理と共に使用されるマスクなどの1つまたは複数のマスクを作成するために、マスク製造業者530にGDSI Iファイル526を提供することを含み得る。マスク532は、1つまたは複数のウェハ534を生成するために、製作プロセス528中に使用され得、1つまたは複数のウェハ534は試験され、代表的ダイ536などのダイに分離され得る。ダイ536は、図1の半導体ダイ102、図2の半導体ダイ212～218のいずれか、図4のプロセッサ410、またはそれらの組合せを含むデバイスを含む回路を含む。20

**【0054】**

デバイス製造プロセスは、大型化ゲート長を決定するためにダイ536の複数の反復を製造し得る。たとえば、マスク製造業者530は、マスク532の2つの反復を作成し得る。マスク532の第1の反復は、ダイ536のコアが標準長さ（たとえば、ゲート長L2～L2''）を有するように作成され得る。ダイ536の第1の反復は、マスク532の第1の反復を使用して製造され得る。ダイ536の第1の反復のコアの性能パラメータが、性能パラメータ変動（たとえば、コア間漏れ電流変動、コア間クロック速度変動など）を求めるように測定され得る。性能パラメータ変動に基づいて、大型化ゲート長が求められ得る。たとえば、性能パラメータ変動に基づいて、ルックアップテーブル内のオフセット値をルックアップすることによって、またはモデルに従ってオフセット値を計算することによって大型化ゲート長が求められ得る（たとえば、コア間漏れ電流変動が5%未満であるとき、オフセット値は1nmである）。30

**【0055】**

マスク532の第2の反復は、ダイ536の1つまたは複数のコア（たとえば、内部コア）が大型化ゲート長を使用して作成され得、ダイ536の1つまたは複数のコア（たとえば、外部コア）が標準ゲート長を使用して作成され得るように作成され得る。ダイ536の第2の反復は、マスク532の第2の反復を使用して製造され得る。40

**【0056】**

ダイ536（たとえば、ダイ536の第2の反復）がパッケージングプロセス538に供給され、ダイ536が代表的パッケージ540内に組み込まれる。たとえば、パッケージ540は、システムインパッケージ（SIP）構成などの、単一のダイ536または複数のダイを含み得る。パッケージ540は、電子デバイスエンジニアリング連合評議会（JEDDEC）規格などの1つまたは複数の規格または仕様に準拠するように構成され得る。

**【0057】**

パッケージ540に関する情報が、コンピュータ546に格納される構成要素ライブラ50

リなどを介して、様々な製品設計者に配布され得る。コンピュータ 546 は、メモリ 550 に結合された、1つまたは複数の処理コアなどのプロセッサ 548 を含み得る。プリント回路板 (PCB) ツールが、ユーザインターフェース 544 を介してコンピュータ 546 のユーザから受信された PCB 設計情報 542 を処理するために、プロセッサ実行可能命令としてメモリ 550 に格納され得る。PCB 設計情報 542 は、回路板上のパッケージングされる半導体デバイスの物理的位置決め情報を含み得、パッケージ 540 に対応するパッケージングされる半導体デバイスは、図 1 の半導体ダイ 102、図 2 の半導体ダイ 212～218 のいずれか、図 4 のプロセッサ 410、またはそれらの組合せを含む。

#### 【0058】

コンピュータ 546 は、PCB 設計情報 542 を変換して、回路板上のパッケージングされる半導体デバイスの物理的位置決め情報、ならびにトレースやバイアなどの電気的接続のレイアウトを含むデータを伴う、GERBER ファイル 552 などのデータファイルを生成するように構成され得、パッケージングされる半導体デバイスは、図 1 の半導体ダイ 102、図 2 の半導体ダイ 212～218 のいずれか、図 4 のプロセッサ 410、またはそれらの組合せを含むパッケージ 540 に対応する。別の実施形態では、変換された PCB 設計情報によって生成されるデータファイルは、GERBER フォーマット以外のフォーマットを有し得る。

#### 【0059】

GERBER ファイル 552 は、ボード組立てプロセス 554 において受信され、GERBER ファイル 552 内に格納される設計情報に従って製造される、代表的 PCB 556 などの PCB を作成するのに使用され得る。たとえば、GERBER ファイル 552 は、PCB 製造プロセスの様々なステップを実施するために1つまたは複数のマシンにアップロードされ得る。PCB 556 には、パッケージ 540 を含む電子構成要素が実装され、代表的プリント回路アセンブリ (PCA) 558 が形成され得る。

#### 【0060】

PCA 558 が製品製造プロセス 560 において受信され、第 1 の代表的電子デバイス 562 および第 2 の代表的電子デバイス 564 などの1つまたは複数の電子デバイス内に統合され得る。例示的な非限定的な例として、第 1 の代表的電子デバイス 562、第 2 の代表的電子デバイス 564、またはその両方は、図 1 の半導体ダイ 102、図 2 の半導体ダイ 212～218 のいずれか、図 4 のプロセッサ 410、またはそれらの組合せがその中に統合される、携帯電話、スマートフォン、タブレットコンピュータ、ラップトップコンピュータ、ハンドヘルドパーソナル通信システム (PCS) ユニット、携帯情報端末などのポータブルデータユニット、全地球測位システム (GPS) 対応デバイス、ナビゲーションデバイス、メータ読み取り機器などの固定位置データユニット、またはデータまたはコンピュータ命令を格納または検索する任意の他のデバイス、またはそれらの任意の組合せのグループから選択され得る。別の例示的な非限定的な例として、電子デバイス 562 および 564 のうちの1つまたは複数は、図 1 の半導体ダイ 102、図 2 の半導体ダイ 212～218 のいずれか、図 4 のプロセッサ 410、またはそれらの組合せがその中に統合される、セットトップボックス、音楽プレーヤ、ビデオプレーヤ、エンターテイメントユニット、ナビゲーションデバイス、通信デバイス、携帯情報端末 (PDA)、固定位置データユニット、コンピュータ、またはそれらの組合せなどのリモートユニットであり得る。図 5 は本開示の教示によるリモートユニットを示すが、本開示はこれらの図示されるユニットに限定されない。本開示の実施形態は、メモリおよびオンチップ回路を含む能動集積回路を含む任意のデバイス内で適切に利用され得る。

#### 【0061】

例示的プロセス 500 で説明されるように、図 1 の半導体ダイ 102、図 2 の半導体ダイ 212～218 のいずれか、図 4 のプロセッサ 410、またはそれらの組合せを含むデバイスが製作され、処理され、電子デバイス内に組み込まれ得る。図 1～4 に関する開示される実施形態の1つまたは複数の態様が、ライブラリファイル 512、GDSII ファイル 526、GERBER ファイル 552 内などの様々な処理段階で含められ、リサー

10

20

30

40

50

チコンピュータ 506 のメモリ 510、設計コンピュータ 514 のメモリ 518、コンピュータ 546 のメモリ 550、ボード組立てプロセス 554などの様々な段階において使用される1つまたは複数の他のコンピュータもしくはプロセッサ(図示せず)のメモリに格納され、マスク 532、ダイ 536、パッケージ 540、PCA 558、プロトタイプ回路やデバイス(図示せず)などの他の製品、またはそれらの任意の組合せなどの1つまたは複数の他の物理的実施形態にも組み込まれ得る。物理デバイス設計から最終的製品までの製造の様々な代表的段階が示されるが、別の実施形態では、より少ない段階が使用され得、または追加の段階が含まれ得る。同様に、プロセス 500 は、プロセス 500 の様々な段階を実施する単一のエンティティあるいは1つまたは複数のエンティティによって実施され得る。

10

#### 【0062】

本明細書で「第1の」、「第2の」などの名称を使用する要素へのいかなる参照も、それらの要素の量または順序を全般的に限定するものではないことを理解されたい。むしろ、これらの名称は、2つ以上の要素または要素の例を区別する便利な方法として本明細書で使用され得る。したがって、第1および第2の要素への参照は、ただ2つの要素が利用され得ること、または何らかの形で第1の要素が第2の要素に先行しなければならないことを意味するわけではない。さらに、別段に明記されていない限り、要素のセットは1つまたは複数の要素を含み得る。

#### 【0063】

本明細書では、「求める、決定する(determining)」という用語は、多種多様な動作を包含する。たとえば、「求める、決定する」ことは、計算すること、処理すること、導出すること、調査すること、ルックアップすること(たとえば、テーブル、データベース、または別のデータ構造をルックアップすること)、確認することなどを含み得る。さらに、「求める、決定する」ことは、受信すること(たとえば、情報を受信すること)、アクセスすること(たとえば、メモリ内のデータにアクセスすること)などを含み得る。さらに、「求める、決定する」ことは、解決すること、選択すること、選ぶこと、確立することなど含み得る。

20

#### 【0064】

本明細書では、項目のリストの「少なくとも1つ」を指す語句は、単一の部材を含む、それらの項目の任意の組合せを指す。一例として、「a、b、またはcのうちの少なくとも1つ」は、a、b、c、a-b、a-c、b-c、およびa-b-cを包含するものとする。

30

#### 【0065】

様々な例示的構成要素、ブロック、構成、モジュール、回路、およびステップが、その機能に関して上記で全般的に説明された。そのような機能がハードウェアとして実装されるか、それともプロセッサ実行可能命令として実装されるかは、特定の応用例と、システム全体に課される設計制約とに依存する。さらに、前述の方法の様々な動作(たとえば、図3および図5に示される任意の動作)は、様々なハードウェアおよび/またはプロセッサ実行可能ソフトウェア構成要素、回路、および/またはモジュールなどの、動作を実施することができる任意の適切な手段によって実施され得る。当業者は記載の機能を特定の応用例ごとに様々な方式で実装し得るが、そのような実装決定が本開示の範囲からの逸脱を引き起こすと解釈されるべきではない。

40

#### 【0066】

本開示に関連して説明される様々な例示的な論理ブロック、構成、モジュール、回路、およびアルゴリズムステップは、汎用プロセッサ、デジタル信号プロセッサ(DSP)、特定用途向け集積回路(AVIC)、フィールドプログラマブルゲートアレイ(FPGA)、プログラマブル論理デバイス(PLD)、ディスクリートゲートもしくはトランジスタロジック、ディスクリートハードウェア構成要素(たとえば、電子ハードウェア)、プロセッサによって実行されるコンピュータソフトウェア、または本明細書で説明される機能を実行するように設計されたそれらの任意の組合せを用いて実装または実施され得るこ

50

とを、当業者はさらに理解されよう。汎用プロセッサはマイクロプロセッサであり得るが、代替として、プロセッサは、任意の市販のプロセッサ、コントローラ、マイクロコントローラ、または状態機械であり得る。プロセッサはまた、コンピューティングデバイスの組合せ、たとえばDSPとマイクロプロセッサの組合せ、複数のマイクロプロセッサ、1つまたは複数のマイクロプロセッサとDSPコア、または任意の他のそのような構成として実装され得る。

#### 【0067】

1つまたは複数の態様では、記載の機能は、ハードウェア、ソフトウェア、ファームウェア、またはそれらの任意の組合せで実装され得る。ソフトウェアで実装される場合、機能は、コンピュータ可読媒体上に1つまたは複数のコンピュータ実行可能命令またはコードとして格納され得る。コンピュータ可読媒体は、ある場所から別の場所へのコンピュータプログラムデータの転送を容易にする任意の媒体を含む、コンピュータ可読記憶媒体および通信媒体を含む。記憶媒体は、コンピュータによってアクセスし得る任意の入手可能な媒体であり得る。限定ではなく例として、そのようなコンピュータ可読記憶媒体は、ランダムアクセスメモリ(RAM)、読み取り専用メモリ(ROM)、プログラマブル読み取り専用メモリ(PROM)、消去可能PROM(E PROM)、電気消去可能PROM(EEPROM)、レジスタ、ハードディスク、リムーバブルディスク、コンパクトディスク読み取り専用メモリ(CD-ROM)、他の光学ディスクストレージ、磁気ディスクストレージ、磁気記憶デバイス、または、命令もしくはデータの形態でプログラムコードを記憶するために使用され得、コンピュータによってアクセスされ得る任意の他の媒体を含み得る。代替として、コンピュータ可読媒体(たとえば、記憶媒体)は、プロセッサと一緒にあり得る。プロセッサおよび記憶媒体は、特定用途向け集積回路(ASIC)内にあり得る。ASICは、コンピューティングデバイスまたはユーザ端末内にあり得る。代替として、プロセッサおよび記憶媒体は、コンピューティングデバイスまたはユーザ端末内に別個の構成要素としてあり得る。

#### 【0068】

さらに、任意の接続がコンピュータ可読媒体と適切に呼ばれる。たとえば、ソフトウェアが、同軸ケーブル、光ファイバケーブル、撲線対、デジタル加入者線(DSL)、または赤外線、無線、マイクロ波などのワイヤレス技術を使用して、ウェブサイト、サーバ、または他のリモートソースから送信される場合、同軸ケーブル、光ファイバケーブル、撲線対、DSL、または赤外線、無線、マイクロ波などのワイヤレス技術が、媒体の定義に含まれる。本明細書では、ディスク(disk)およびディスク(disc)は、コンパクトディスク(disc)(CD)、レーザディスク(disc)、光ディスク(disc)、デジタルバーサタイルディスク(disc)(DVD)、フロッピィディスク(disk)を含み、ディスク(disk)は通常、データを磁気的に再現し、一方、ディスク(disc)は、データをレーザで光学的に再現する。したがって、いくつかの態様では、コンピュータ可読媒体は、非一時的コンピュータ可読媒体(たとえば、有形媒体)を含み得る。上記の組合せもコンピュータ可読媒体の範囲内に含まれるべきである。

#### 【0069】

本明細書で開示される方法は、1つまたは複数のステップまたは動作を含む。方法ステップおよび/または動作は、特許請求の範囲から逸脱することなく、互いに交換され得る。言い換えれば、ステップまたは動作の特定の順序が指定されない限り、特定のステップおよび/または動作の順序および/または使用は、本開示の範囲から逸脱することなく修正され得る。

#### 【0070】

いくつかの態様は、本明細書で提示された動作を実行するためのコンピュータプログラム製品を含み得る。たとえば、コンピュータプログラム製品は、その上に格納(および/または符号化)された命令を有するコンピュータ可読記憶媒体を含み得、命令は、本明細書で説明される動作を実行するために1つまたは複数のプロセッサによって実行可能である。コンピュータプログラム製品は、パッケージング材料を含み得る。

10

20

30

40

50

## 【0071】

さらに、本明細書で説明される方法および技法を実施するためのモジュールおよび／または他の適切な手段が、ユーザ端末および／または基地局によって適切にダウンロードおよび／または取得され得ることを理解されたい。あるいは、本明細書で説明される様々な方法は、記憶手段（たとえば、RAM、ROM、またはコンパクトディスク（CD）などの物理的記憶媒体）を介して提供され得る。その上、本明細書に記載された方法および技法を提供するための任意の他の適切な技法が利用され得る。本開示の範囲は、上記で示される厳密な構成および構成要素に限定されないことを理解されたい。

## 【0072】

開示される実施形態の前の説明は、開示される実施形態を当業者が作成または使用することを可能にするために提供される。上記は本開示の態様を対象とするが、本開示の他の態様は、それらの基本的な範囲から逸脱することなく考案され得、範囲は、以下の特許請求の範囲によって決定される。本開示または特許請求の範囲から逸脱することなく、本明細書で説明される実施形態の構成、動作、および細部に様々な修正、変更、および変形が行われ得る。したがって、本開示は、本明細書の実施形態に限定されるものではなく、以下の特許請求の範囲およびその均等物によって定義される原理および新規な特徴に適合する、可能な最大の範囲が与えられるべきである。

10

## 【符号の説明】

## 【0073】

|     |                |    |

|-----|----------------|----|

| 102 | 半導体ダイ          | 20 |

| 104 | 第1のコア          |    |

| 106 | 第2のコア          |    |

| 108 | 第3のコア          |    |

| 110 | 第4のコア          |    |

| 112 | 第1のトランジスタ      |    |

| 114 | 第2のトランジスタ      |    |

| 116 | 第3のトランジスタ      |    |

| 118 | 第4のトランジスタ      |    |

| 120 | 第5のトランジスタ      |    |

| 122 | 第6のトランジスタ      | 30 |

| 124 | 第1の多結晶シリコンゲート層 |    |

| 126 | 第1の酸化物層        |    |

| 128 | 第2の多結晶シリコンゲート層 |    |

| 130 | 第2の酸化物層        |    |

| 202 | ウェハ            |    |

| 204 | 第1のレチクル        |    |

| 206 | 第2のレチクル        |    |

| 208 | 第3のレチクル        |    |

| 210 | 第4のレチクル        |    |

| 212 | 第1の半導体ダイ       | 40 |

| 214 | 第2の半導体ダイ       |    |

| 216 | 第3の半導体ダイ       |    |

| 218 | 第4の半導体ダイ       |    |

| 220 | 第1のコア          |    |

| 222 | 第2のコア          |    |

| 224 | 第3のコア          |    |

| 226 | 第4のコア          |    |

| 228 | 第5のコア          |    |

| 230 | 第6のコア          |    |

| 232 | 第7のコア          | 50 |

|       |                        |    |

|-------|------------------------|----|

| 2 3 4 | 第 8 のコア                |    |

| 2 3 6 | 左側のレチクルフィールド           |    |

| 2 3 8 | 右側のレチクルフィールド           |    |

| 4 0 0 | 通信デバイス                 |    |

| 4 1 0 | プロセッサ                  |    |

| 4 2 6 | ディスプレイコントローラ           |    |

| 4 2 8 | ディスプレイデバイス             |    |

| 4 3 0 | 入力デバイス                 |    |

| 4 3 2 | メモリ                    |    |

| 4 3 4 | コーダ / デコーダ ( コーデック )   | 10 |

| 4 3 6 | スピーカ                   |    |

| 4 3 8 | マイクロフォン                |    |

| 4 4 0 | ワイヤレスコントローラ            |    |

| 4 4 2 | アンテナ                   |    |

| 4 4 4 | 電源                     |    |

| 4 4 6 | トランシーバ                 |    |

| 4 4 8 | 第 1 のコア                |    |

| 4 5 0 | 第 2 のコア                |    |

| 4 5 2 | 第 3 のコア                |    |

| 4 5 4 | 第 4 のコア                | 20 |

| 4 5 6 | 命令                     |    |

| 5 0 0 | 電子デバイス製造プロセス           |    |

| 5 0 2 | 物理デバイス情報               |    |

| 5 0 4 | ユーザインターフェース            |    |

| 5 0 6 | リサーチコンピュータ             |    |

| 5 0 8 | プロセッサ                  |    |

| 5 1 0 | メモリ                    |    |

| 5 1 2 | ライブラリファイル              |    |

| 5 1 4 | 設計コンピュータ               |    |

| 5 1 6 | プロセッサ                  | 30 |

| 5 1 8 | メモリ                    |    |

| 5 2 0 | 電子設計自動化 ( E D A ) ツール  |    |

| 5 2 2 | 回路設計情報                 |    |

| 5 2 4 | ユーザインターフェース            |    |

| 5 2 6 | G D S I I ファイル         |    |

| 5 2 8 | 製作プロセス                 |    |

| 5 3 0 | マスク製造業者                |    |

| 5 3 2 | 代表的マスク                 |    |

| 5 3 4 | ウェハ                    |    |

| 5 3 6 | 代表的ダイ                  | 40 |

| 5 3 8 | パッケージングプロセス            |    |

| 5 4 0 | 代表的パッケージ               |    |

| 5 4 2 | プリント回路板 ( P C B ) 設計情報 |    |

| 5 4 4 | ユーザインターフェース            |    |

| 5 4 6 | コンピュータ                 |    |

| 5 4 8 | プロセッサ                  |    |

| 5 5 0 | メモリ                    |    |

| 5 5 2 | G E R B E R ファイル       |    |

| 5 5 4 | ボード組立てプロセス             |    |

| 5 5 6 | 代表的 P C B              | 50 |

- 5 5 8 代表的プリント回路アセンブリ ( P C A )

5 6 0 製品製造プロセス

5 6 2 第 1 の代表的電子デバイス

5 6 4 第 2 の代表的電子デバイス

【図 1】

【図 2】

【図3】

【 四 4 】

( 5 )

---

フロントページの続き

(72)発明者 サミット・セングブタ

アメリカ合衆国・カリフォルニア・92121-1675・サン・ディエゴ・モアハウス・ドライ

ヴ・5775

(72)発明者 チョック・ヒン・ガン

アメリカ合衆国・カリフォルニア・92121-1675・サン・ディエゴ・モアハウス・ドライ

ヴ・5775

(72)発明者 ブル・チダムバラム

アメリカ合衆国・カリフォルニア・92121-1675・サン・ディエゴ・モアハウス・ドライ

ヴ・5775

審査官 宇多川 勉

(56)参考文献 特表2012-533827(JP,A)

特開2012-059932(JP,A)

特開2011-253931(JP,A)

特開2010-004003(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/8234

H01L 21/82

H01L 21/822

H01L 27/04

H01L 27/088