(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2017-522645

(P2017-522645A)

(43) 公表日 平成29年8月10日(2017.8.10)

(51) Int.Cl.

**G06F 13/10 (2006.01)**

**G06F 13/12 (2006.01)**

**G06F 3/06 (2006.01)**

**G06F 12/00 (2006.01)**

**G06F 3/08 (2006.01)**

F 1

G06F 13/10 330C

G06F 13/12 340B

G06F 3/06 340D

G06F 12/00 301F

G06F 3/08 597U

テーマコード(参考)

5B060

審査請求 未請求 予備審査請求 未請求 (全 24 頁) 最終頁に続く

(21) 出願番号 特願2016-569591 (P2016-569591)

(86) (22) 出願日 平成27年6月3日 (2015.6.3)

(85) 翻訳文提出日 平成28年11月25日 (2016.11.25)

(86) 國際出願番号 PCT/US2015/033953

(87) 國際公開番号 WO2015/187810

(87) 國際公開日 平成27年12月10日 (2015.12.10)

(31) 優先権主張番号 62/007,136

(32) 優先日 平成26年6月3日 (2014.6.3)

(33) 優先権主張国 米国(US)

(31) 優先権主張番号 14/728,343

(32) 優先日 平成27年6月2日 (2015.6.2)

(33) 優先権主張国 米国(US)

(71) 出願人 507364838

クアルコム、インコーポレイテッド

アメリカ合衆国 カリフォルニア 921

21 サンディエゴ モアハウス ドラ

イブ 5775

(74) 代理人 100108453

弁理士 村山 靖彦

(74) 代理人 100163522

弁理士 黒田 晋平

(72) 発明者 アサフ・シャチャム

アメリカ合衆国・カリフォルニア・921

21・サン・ディエゴ・モアハウス・ドラ

イブ・5775

最終頁に続く

(54) 【発明の名称】フラッシュメモリベースのストレージデバイスの入力／出力仮想化 (I/OV) ホストコントローラ (HC) (I/OV-HC)

## (57) 【要約】

フラッシュメモリベースのストレージデバイスの入力／出力仮想化 (I/OV) ホストコントローラ (HC) (I/OV-HC) を開示する。一態様では、I/OV-HCは、対応するクライアントレジスタインターフェース (CRI) を介して入力／出力 (I/O) クライアントに結合され、またフラッシュメモリベースのストレージデバイスに結合される。I/OV-HCは、CRI の各々に基本スロットとして割り当てられる共有転送要求リスト (TRL) のスロットを示す、TRLスロットオフセットレジスタを含む。I/OV-HCは、共有TRLのいくつのスロットがCRIの各々に割り当てられるかを示す、TRLスロットカウントレジスタさらに含む。フラッシュメモリベースのストレージデバイスに宛てられた転送要求 (TR) がCRIから受け取られるとき、I/OV-HCは、TRLスロットオフセットレジスタおよびCRIに対応する複数のTRLスロットカウントレジスタのうちのあるTRLスロットカウントレジスタに基づいて、TRを共有TRLのスロットにマッピングするように構成される。

FIG. 3

## 【特許請求の範囲】

## 【請求項 1】

対応する複数のクライアントレジスタインターフェース(CRI)を介して複数の入力/出力(I/O)クライアントに、およびフラッシュメモリベースのストレージデバイスに通信可能に結合された、入力/出力仮想化(IOV)ホストコントローラ(HC)(IOV-HC)であって、

前記IOV-HCが、

前記複数のCRIの各CRIに基本スロットとして割り当てられる共有転送要求リスト(TRL)のスロットを各々示す、複数のTRLスロットオフセットレジスタと、

前記複数のCRIの各CRIに割り当てられる前記共有TRLのスロットの数を各々示す、複数のTRLスロットカウントレジスタと

10

を含み、

前記IOV-HCが、

前記複数のCRIのうちのあるCRIから前記フラッシュメモリベースのストレージデバイスに宛てられた転送要求(TR)を受け取り、

前記CRIに対応する、前記複数のTRLスロットオフセットレジスタのうちのあるTRLスロットオフセットレジスタおよび前記複数のTRLスロットカウントレジスタのうちのあるTRLスロットカウントレジスタに基づいて、前記IOV-HCのTRフェッチ回路によって、前記TRを前記共有TRLのスロットにマッピングする

ように構成される、IOV-HC。

20

## 【請求項 2】

前記TRのスロット識別子および前記TRLスロットオフセットレジスタのTRLスロットオフセットレジスタ値の和に基づいて、前記TRを前記共有TRLの前記スロットにマッピングする

ように構成される、請求項1に記載のIOV-HC。

## 【請求項 3】

前記フラッシュメモリベースのストレージデバイスから、前記TRへの応答を受け取り、

前記IOV-HCによって、前記CRIに対応する前記TRLスロットオフセットレジスタおよび前記TRLスロットカウントレジスタに基づいて前記CRIへ前記応答をルーティングする

ようにさらに構成される、請求項1に記載のIOV-HC。

## 【請求項 4】

前記IOV-HCの初期化に応答して、前記複数のCRIの各CRIに対するTRLスロットオフセットレジスタ値およびTRLスロットカウントレジスタ値を、仮想マシンマネージャ(VMM)から受け取るようにさらに構成される、請求項1に記載のIOV-HC。

30

## 【請求項 5】

VMMによる新しいI/Oクライアントの作成に応答して、前記新しいI/Oクライアントに対応する新しいCRIに対するTRLスロットオフセットレジスタ値およびTRLスロットカウントレジスタ値を、前記VMMから受け取るようにさらに構成される、請求項1に記載のIOV-HC。

## 【請求項 6】

前記複数のCRIの各CRIに基本スロットとして割り当てられる共有タスク管理要求リスト(TMRL)のスロットを各々示す、複数のTMRLスロットオフセットレジスタと、

前記複数のCRIの各CRIに割り当てられる前記共有TMRLのスロットの数を各々示す、複数のTMRLスロットカウントレジスタと

をさらに含み、

40

前記複数のCRIのうちのあるCRIからタスク管理要求(TMR)を受け取り、

前記CRIに対応する、前記複数のTMRLスロットオフセットレジスタのうちのあるTMRLスロットオフセットレジスタおよび前記複数のTMRLスロットカウントレジスタのうちのあるTMRLスロットカウントレジスタに基づいて、前記IOV-HCの前記TRフェッチ回路によって

、前記TMRを前記共有TMRLのスロットにマッピングする

ようにさらに構成される、請求項1に記載のIOV-HC。

## 【請求項 7】

組み込み用マルチメディアカード(eMMC)規格に従って前記フラッシュメモリベースのス

50

トレージデバイスに通信可能に結合される、請求項1に記載のIOV-HC。

【請求項8】

ユニバーサルフラッシュストレージ(UFS)規格に従って前記フラッシュメモリベースのストレージデバイスに通信可能に結合される、請求項1に記載のIOV-HC。

【請求項9】

集積回路(IC)に組み込まれる、請求項1に記載のIOV-HC。

【請求項10】

セットトップボックス、エンターテインメントユニット、ナビゲーションデバイス、通信デバイス、固定ロケーションデータユニット、モバイルロケーションデータユニット、モバイルフォン、セルラーフォン、コンピュータ、ポータブルコンピュータ、デスクトップコンピュータ、携帯情報端末(PDA)、モニタ、コンピュータモニタ、テレビジョン、チューナ、ラジオ、衛星ラジオ、音楽プレーヤ、デジタル音楽プレーヤ、ポータブル音楽プレーヤ、デジタルビデオプレーヤ、ビデオプレーヤ、デジタルビデオディスク(DVD)プレーヤ、およびポータブルデジタルビデオプレーヤからなる群から選択されるデバイスに組み込まれる、請求項1に記載のIOV-HC。

10

【請求項11】

複数のホストに仮想転送要求リスト(TRL)を提供するための方法であって、

複数のクライアントレジスタインターフェース(CRI)のうちのあるCRIからフラッシュメモリベースのストレージデバイスに宛てられた転送要求(TR)を、入力/出力仮想化(IOV)ホストコントローラ(HC)(IOV-HC)によって受け取るステップと、

20

前記CRIに対応する、複数のTRLスロットオフセットレジスタのうちのあるTRLスロットオフセットレジスタおよび複数のTRLスロットカウントレジスタのうちのあるTRLスロットカウントレジスタに基づいて、前記IOV-HCのTRフェッチ回路によって、前記TRを共有TRLのスロットにマッピングするステップと

を含み、

前記複数のTRLスロットオフセットレジスタが各々、前記複数のCRIのうちの対応するCRIに基本スロットとして割り当てられる前記共有TRLのスロットを示し、

前記複数のTRLスロットカウントレジスタが各々、前記複数のCRIのうちの前記対応するCRIに割り当てられる前記共有TRLのスロットの数を示す、

方法。

30

【請求項12】

前記TRを前記共有TRLの前記スロットにマッピングするステップが、前記TRのスロット識別子および前記TRLスロットオフセットレジスタのTRLスロットオフセットレジスタ値の和に基づいている、請求項11に記載の方法。

【請求項13】

前記フラッシュメモリベースのストレージデバイスから、前記TRへの応答を受け取るステップと、

前記CRIに対応する前記TRLスロットオフセットレジスタおよび前記TRLスロットカウントレジスタに基づいて前記CRIへ前記応答をルーティングするステップと

をさらに含む、請求項11に記載の方法。

40

【請求項14】

前記IOV-HCの初期化に応答して、前記複数のCRIの各CRIに対するTRLスロットオフセットレジスタ値およびTRLスロットカウントレジスタ値を、仮想マシンマネージャ(VMM)から受け取るステップをさらに含む、請求項11に記載の方法。

【請求項15】

VMMによる新しい入力/出力(I/O)クライアントの作成に応答して、前記新しいI/Oクライアントに対応する新しいCRIに対するTRLスロットオフセットレジスタ値およびTRLスロットカウントレジスタ値を、前記VMMから受け取るステップをさらに含む、請求項11に記載の方法。

【請求項16】

50

前記IOV-HCによって、前記複数のCRIのうちのあるCRIからタスク管理要求(TMR)を受け取るステップと、

前記CRIに対応する、複数のタスク管理要求リスト(TMRL)スロットオフセットレジスタのうちのあるTMRLスロットオフセットレジスタおよび複数のTMRLスロットカウントレジスタのうちのあるTMRLスロットカウントレジスタに基づいて、前記IOV-HCの前記TRフェッチ回路によって、前記TMRを共有TMRLのスロットにマッピングするステップとをさらに含み、

前記複数のTMRLスロットオフセットレジスタが各々、前記複数のCRIのうちの前記対応するCRIに基本スロットとして割り当てられる前記共有TMRLのスロットを示し、

前記複数のTMRLスロットカウントレジスタが各々、前記複数のCRIのうちの前記対応するCRIに割り当てられる前記共有TMRLのスロットの数を示す、

請求項11に記載の方法。

10

【請求項17】

前記フラッシュメモリベースのストレージデバイスが、組み込み用マルチメディアカード(eMMC)デバイスを含む、請求項11に記載の方法。

【請求項18】

前記フラッシュメモリベースのストレージデバイスが、ユニバーサルフラッシュストレージ(UFS)デバイスを含む、請求項11に記載の方法。

【請求項19】

入力/出力仮想化(IOV)ホストコントローラ(HC)(IOV-HC)であって、

複数のクライアントレジスタインターフェース(CRI)のうちのあるCRIからフラッシュメモリベースのストレージデバイスに宛てられた転送要求(TR)を受け取るための手段と、

前記CRIに対応する、複数の転送要求リスト(TRL)スロットオフセットレジスタのうちのあるTRLスロットオフセットレジスタおよび複数のTRLスロットカウントレジスタのうちのあるTRLスロットカウントレジスタに基づいて、前記TRを共有TRLのスロットにマッピングするための手段と

を含み、

前記複数のTRLスロットオフセットレジスタが各々、前記複数のCRIのうちの対応するCRIに基本スロットとして割り当てられる前記共有TRLのスロットを示し、

前記複数のTRLスロットカウントレジスタが各々、前記複数のCRIのうちの前記対応するCRIに割り当てられる前記共有TRLのスロットの数を示す、

IOV-HC。

20

【請求項20】

前記フラッシュメモリベースのストレージデバイスから、前記TRへの応答を受け取るための手段と、

前記CRIに対応する前記TRLスロットオフセットレジスタおよび前記TRLスロットカウントレジスタに基づいて前記CRIへ前記応答をルーティングするための手段と

をさらに含む、請求項19に記載のIOV-HC。

【請求項21】

前記IOV-HCの初期化に応答して、前記複数のCRIの各CRIに対するTRLスロットオフセットレジスタ値およびTRLスロットカウントレジスタ値を、仮想マシンマネージャ(VMM)から受け取るための手段をさらに含む、請求項19に記載のIOV-HC。

40

【請求項22】

VMMによる新しい入力/出力(I/O)クライアントの作成に応答して、前記新しいI/Oクライアントに対応する新しいCRIに対するTRLスロットオフセットレジスタ値およびTRLスロットカウントレジスタ値を、前記VMMから受け取るための手段をさらに含む、請求項19に記載のIOV-HC。

【請求項23】

前記複数のCRIのうちのあるCRIからタスク管理要求(TMR)を受け取るための手段と、

前記CRIに対応する、複数のタスク管理要求リスト(TMRL)スロットオフセットレジスタ

50

のうちのあるTMRLスロットオフセットレジスタおよび複数のTMRLスロットカウントレジスタのうちのあるTMRLスロットカウントレジスタに基づいて、前記TMRを共有TMRLのスロットにマッピングするための手段と

をさらに含み、

前記複数のTMRLスロットオフセットレジスタが各々、前記複数のCRIのうちの対応するCRIに基本スロットとして割り当てられる前記共有TMRLのスロットを示し、

前記複数のTMRLスロットカウントレジスタが各々、前記複数のCRIのうちの前記対応するCRIに割り当てられる前記共有TMRLのスロットの数を示す、

請求項19に記載のIOV-HC。

【発明の詳細な説明】

【技術分野】

【0001】

優先権主張

本出願は、その内容全体が参考により本明細書に組み込まれる、2014年6月3日に出願した、「MULTI-HOST UNIVERSAL FLASH STORAGE (UFS)」という名称の米国仮特許出願第62/007,136号の優先権を主張する。

【0002】

本出願は、その内容全体が参考により本明細書に組み込まれる、2015年6月2日に出願した、「AN INPUT/OUTPUT VIRTUALIZATION (IOV) HOST CONTROLLER (HC) (IOV-HC) OF A FLASH-MEMORY-BASED STORAGE DEVICE」いう名称の米国特許出願第14/728,343号の優先権もまた主張する。

【0003】

本開示の技術は、一般に、モバイルコンピューティングデバイス内のフラッシュメモリベースのストレージに関する。

【背景技術】

【0004】

フラッシュメモリは、データを電子的に書き込み、消去することができる不揮発性データ記憶媒体である。フラッシュメモリは、現在、メモリカード、ソリッドステートドライブ、およびユニバーサルシリアルバス(USB)フラッシュドライブなど、様々なフラッシュメモリベースのストレージデバイスに使用されている。フラッシュメモリベースのストレージデバイスは、ダイナミックランダムアクセスメモリ(RAM)に匹敵する速い読み取りおよび書き込み時間を提供するとともに、従来のハードディスクよりも高い耐久性および耐衝撃性をもたらすことができる。

【0005】

フラッシュメモリベースのストレージデバイスの普及を促進するために、いくつかの規格が開発された、または現在開発中である。1つのそのような規格が、スマートフォンおよびタブレットコンピュータなどのモバイルコンピューティングデバイス内のフラッシュメモリベースのストレージのために、電子デバイス技術合同協議会(JEDEC:Joint Electron Device Engineering Council)によって開発された、ユニバーサルフラッシュストレージ(UFS)である。UFSは、小型コンピュータシステムインターフェース(SCSI:Small Computer System Interface)アーキテクチャモデル、およびコマンドキューイング機能を用いて複数のコマンドをサポートするコマンドプロトコルを採用し、したがってマルチスレッドプログラミングパラダイムを可能にする。JEDECによって開発された別の規格は、組み込み用マルチメディアカード(eMMC:Embedded MultiMediaCard)規格であり、これは、簡略化されたアプリケーションインターフェース設計、小型パッケージサイズ、および低電力消費を提供する。eMMCフラッシュメモリベースのストレージデバイスは、現在、モバイルデバイス内のストレージの基本的形態の1つである。

【0006】

UFSおよびeMMCなど、従来のフラッシュメモリベースのストレージデバイス規格は、現在のところ、単一の入力/出力(I/O)クライアントによる管理および使用のために設計され

ている。しかしながら、多くの最新のコンピューティングデバイスは、仮想化環境を使用して複数のI/Oクライアント(たとえば、ホストまたは他のプロセッササブシステム)を同時にサポートすることができる。そのような仮想化環境では、複数のI/Oクライアントは各々、それがフラッシュメモリベースのストレージデバイスの唯一のホストであるかのように、単一のフラッシュメモリベースのストレージデバイスと対話する必要がある場合がある。同様に、フラッシュメモリベースのストレージデバイスは、実際には複数のI/Oクライアントと通信しているときに、単一のI/Oクライアントのみと通信しているかのように動作する必要がある場合がある。

#### 【0007】

特に、フラッシュメモリベースのストレージデバイス用の従来のホストコントローラ(HC)が、複数の「スロット」から構成される転送要求リスト(TRL)(いくつかの規格の下では、複数のタスクディスクリプタ(TD)を含むタスクディスクリプタリスト(TDL)とも呼ぶ)を提供することがある。スロットは、フラッシュメモリベースのストレージデバイスに、読み取り/書き込みトランザクションなどの転送要求(TR)を発行するためにI/Oクライアントによって使用されてよい。しかしながら、マルチホスト環境でフラッシュメモリベースのストレージデバイスへのアクセスを提供するには、HCは、単一ホストとは対照的に、複数のI/OクライアントがTRLにアクセスすることを可能にする必要がある場合がある。

10

#### 【発明の概要】

#### 【課題を解決するための手段】

#### 【0008】

詳細な説明に開示する態様は、フラッシュメモリベースのストレージデバイスの入力/出力仮想化(10V)ホストコントローラ(HC)(10V-HC)を含む。この点について、一態様では、10V-HCが、システムオンチップ(SoC)上の单一システム内の複数の入力/出力(I/O)クライアントに対してフラッシュメモリベースのストレージデバイスへのアクセスを提供する。特に、10V-HCは、読み取り/書き込みトランザクションなどの転送要求(TR)を発行するための物理「スロット」を含む共有転送要求リスト(TRL)を、フラッシュメモリベースのストレージデバイスに提供することによって複数のI/Oクライアントに対してストレージアクセスを提供する。10V-HCは、いくつかのクライアントレジスタインターフェース(CRI)を実装し、CRIの各々が、共有TRLのスロットのサブセットから構成される、その独自の仮想TRLを提供される。仮想TRLは、10V-HCによって管理されるTRLスロットオフセットレジスタおよびTRLスロットカウントレジスタによって定義される。仮想TRLを使用して、10V-HCは、複数のI/OデバイスからフラッシュメモリベースのストレージデバイスへのTR、およびフラッシュメモリベースのストレージデバイスによって複数のI/Oクライアントに提供される応答を、複数のI/Oクライアントにトランスペアレントな方法で、効率的に処理することができる。

20

30

#### 【0009】

別の態様では、10V-HCが提供される。10V-HCは、複数の入力/出力(I/O)クライアントに、対応する複数のクライアントレジスタインターフェース(CRI)を介して通信可能に結合され、またフラッシュメモリベースのストレージデバイスにも通信可能に結合される。10V-HCは、複数のCRIの各CRIに基本スロットとして割り当てる共有転送要求リスト(TRL)のスロットを各々示す、複数のTRLスロットオフセットレジスタを含む。10V-HCは、複数のCRIの各CRIに割り当てる共有TRLのスロットの数を各々示す、複数のTRLスロットカウントレジスタをさらに含む。10V-HCは、複数のCRIのうちのあるCRIからフラッシュメモリベースのストレージデバイスに宛てられた転送要求(TR)を受け取るように構成される。10V-HCは、このCRIに対応する、複数のTRLスロットオフセットレジスタのうちのあるTRLスロットオフセットレジスタおよび複数のTRLスロットカウントレジスタのうちのあるTRLスロットカウントレジスタに基づいて、10V-HCのTRフェッチ回路によって、TRを共有TRLのスロットにマッピングするようにさらに構成される。

40

#### 【0010】

別の態様では、複数のホストに仮想TRLを提供するための方法が提供される。この方法

50

は、複数のCRIのうちのあるCRIからフラッシュメモリベースのストレージデバイスに宛てられたTRを、IOV-HCによって受け取るステップを含む。この方法は、このCRIに対応する、複数のTRLスロットオフセットレジスタのうちのあるTRLスロットオフセットレジスタおよび複数のTRLスロットカウントレジスタのうちのあるTRLスロットカウントレジスタに基づいて、IOV-HCのTRフェッチ回路によって、TRを共有TRLのスロットにマッピングするステップをさらに含む。複数のTRLスロットオフセットレジスタは各々、複数のCRIのうちの対応するCRIに基本スロットとして割り当てられる共有TRLのスロットを示す。複数のTRLスロットカウントレジスタは各々、複数のCRIのうちの対応するCRIに割り当てられる共有TRLのスロットの数を示す。

## 【0011】

10

別の態様では、IOV-HCが提供される。IOV-HCは、複数のCRIのうちのあるCRIからフラッシュメモリベースのストレージデバイスに宛てられたTRを受け取るための手段を含む。IOV-HCは、このCRIに対応する、複数のTRLスロットオフセットレジスタのうちのあるTRLスロットオフセットレジスタおよび複数のTRLスロットカウントレジスタのうちのあるTRLスロットカウントレジスタに基づいて、TRを共有TRLのスロットにマッピングするための手段をさらに含む。複数のTRLスロットオフセットレジスタは各々、複数のCRIのうちの対応するCRIに基本スロットとして割り当てられる共有TRLのスロットを示す。複数のTRLスロットカウントレジスタは各々、複数のCRIのうちの対応するCRIに割り当てられる共有TRLのスロットの数を示す。

## 【図面の簡単な説明】

20

## 【0012】

【図1】例示的なフラッシュメモリベースのストレージデバイス、および複数のホストおよび入力/出力仮想化(IOV)ホストコントローラ(HC)(IOV-HC)を用いた例示的なシステムオンチップ(SoC)のブロック図である。

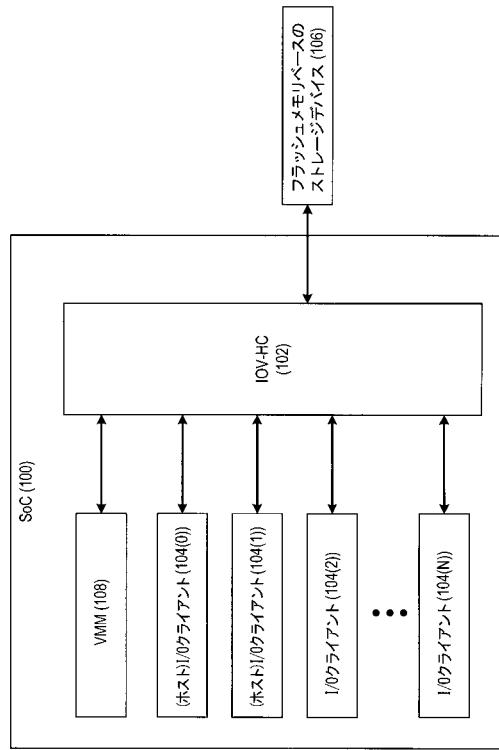

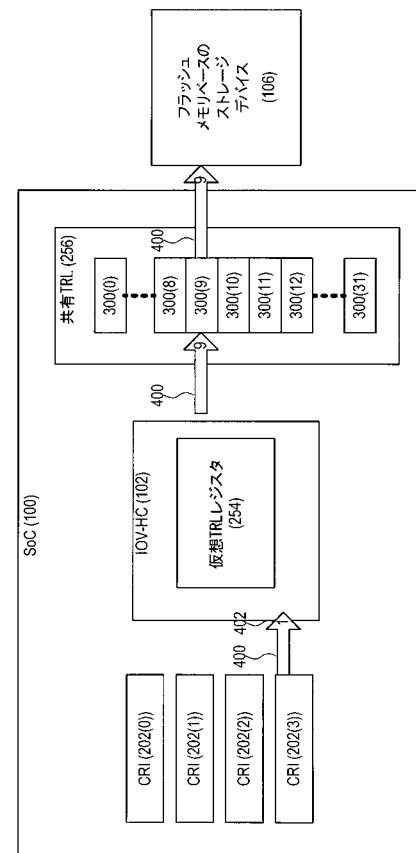

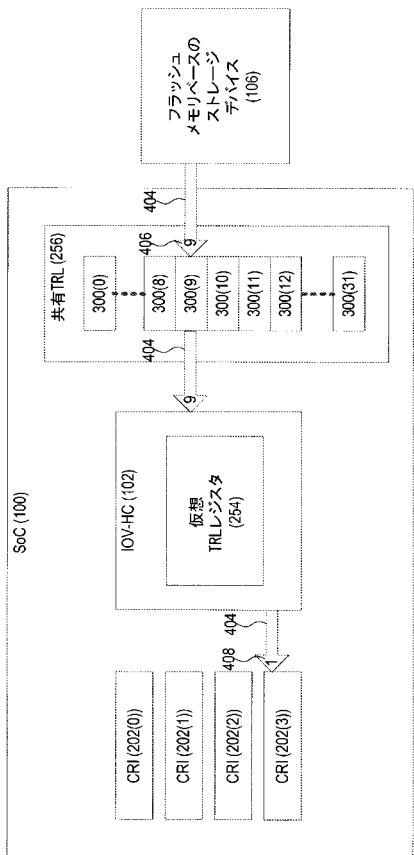

【図2】仮想転送要求リスト(TRL)レジスタを用いた例示的なIOV-HCのブロック図である。

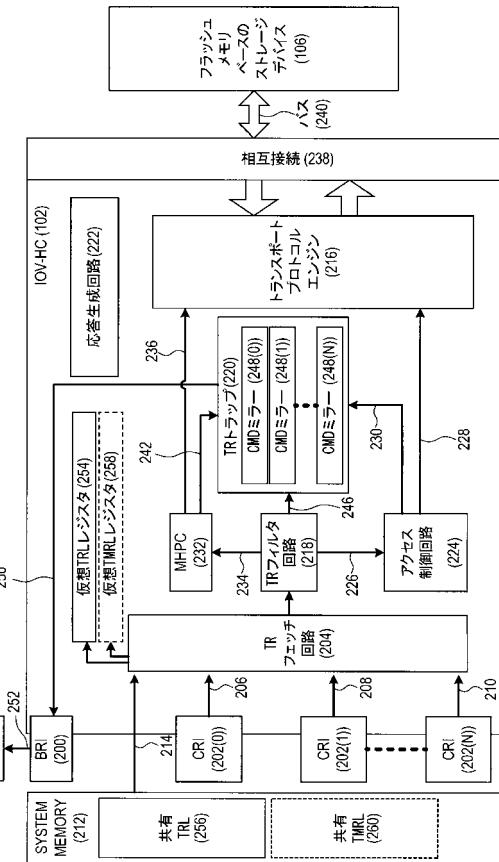

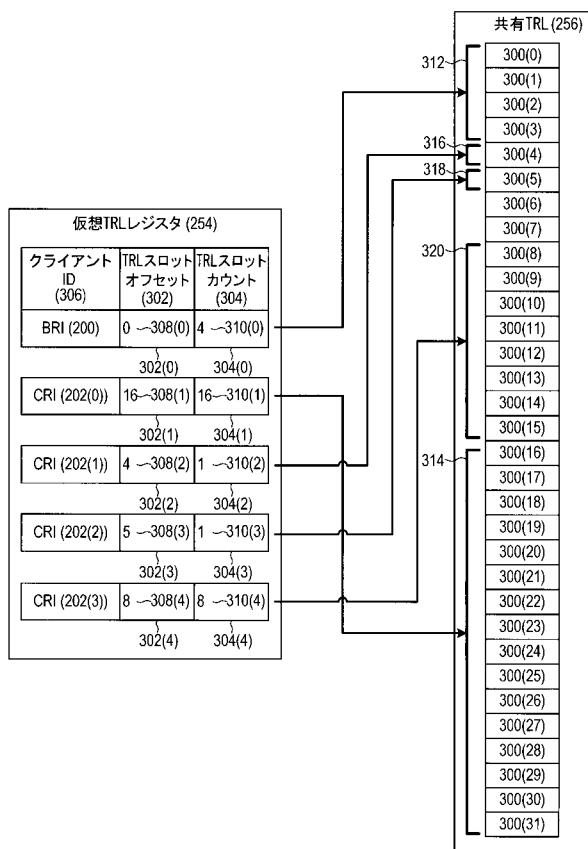

【図3】仮想TRLレジスタを使用する図2のIOV-HCによる複数のクライアントレジスタインターフェース(CRI)への共有TRL内のスロットの例示的な割振りを示すブロック図である。

【図4 A】転送要求(TR)を受け取り、図2の仮想TRLレジスタを使用して共有TRLのスロットにTRをマッピングし、応答を返すための、図2のIOV-HCの例示的な動作を示すブロック図である。

【図4 B】転送要求(TR)を受け取り、図2の仮想TRLレジスタを使用して共有TRLのスロットにTRをマッピングし、応答を返すための、図2のIOV-HCの例示的な動作を示すブロック図である。

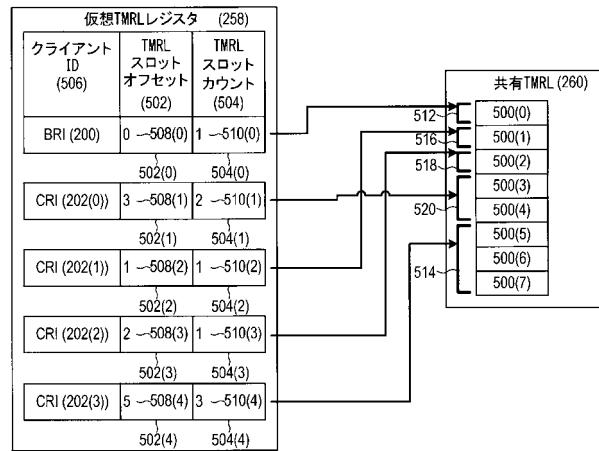

【図5】仮想TMRLレジスタを使用する図2のIOV-HCのいくつかの態様による複数のCRIへの共有タスク管理要求リスト(TMRL)内のスロットの例示的な割振りを示すブロック図である。

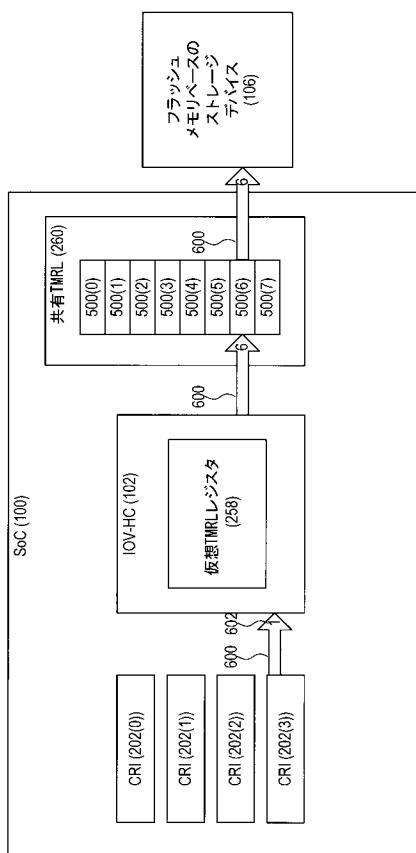

【図6】タスク管理要求(TMR)を受け取り、図5の仮想TMRLレジスタを使用して共有TMRLのスロットにTMRをマッピングし、応答を返すための、図2のIOV-HCの例示的な動作を示すブロック図である。

【図7 A】仮想TRLレジスタを使用して共有TRLのスロットを割り振るための図2のIOV-HCの例示的な動作を示すフローチャートである。

【図7 B】仮想TRLレジスタを使用して共有TRLのスロットを割り振るための図2のIOV-HCの例示的な動作を示すフローチャートである。

【図8】IOV-HC内に図2および図3の仮想TRLレジスタを用いるSoCを組み込むことができる例示的なコンピューティングデバイスのブロック図である。

## 【発明を実施するための形態】

## 【0013】

ここで図面を参照しながら、本開示のいくつかの例示的な態様について説明する。「例示的」という語は、本明細書では「一例、事例、または例示としての役割を果たすこと」

50

を意味するために使用される。「例示的」として本明細書において説明されるいずれの態様も、必ずしも他の態様よりも好ましいか、または有利であると解釈されるとは限らない。

#### 【0014】

詳細な説明に開示する態様は、フラッシュメモリベースのストレージデバイスの入力/出力仮想化(10V)ホストコントローラ(HC)(10V-HC)を含む。この点について、一態様では、10V-HCが、システムオンチップ(SoC)上の単一システム内の複数の入力/出力(I/O)クライアントに対してフラッシュメモリベースのストレージデバイスへのアクセスを提供する。特に、10V-HCは、読み取り/書き込みトランザクションなどの転送要求(TR)を発行するための物理「スロット」を含む共有転送要求リスト(TRL)を、フラッシュメモリベースのストレージデバイスに提供することによって複数のI/Oクライアントに対してストレージアクセスを提供する。10V-HCは、いくつかのクライアントレジスタインターフェース(CRI)を実装し、CRIの各々が、共有TRLのスロットのサブセットから構成される、その独自の仮想TRLを提供される。仮想TRLは、10V-HCによって管理されるTRLスロットオフセットレジスタおよびTRLスロットカウントレジスタによって定義される。仮想TRLを使用して、10V-HCは、複数のI/OデバイスからフラッシュメモリベースのストレージデバイスへのTR、およびフラッシュメモリベースのストレージデバイスによって複数のI/Oクライアントに提供される応答を、複数のI/Oクライアントにトランスペアレントな方法で、効率的に処理することができる。

10

#### 【0015】

この点において、図1は、10V-HC102を含んだ例示的なシステムオンチップ(SoC)100のブロック図である。図1の例では、10V-HC102は、複数のI/Oクライアント104(0)～104(N)が単一のフラッシュメモリベースのストレージデバイス106にアクセスできるようにするために提供される。いくつかの態様では、フラッシュメモリベースのストレージデバイス106は、非限定的な例として、ユニバーサルフラッシュストレージ(UFS)デバイスまたは組み込み用マルチメディアカード(eMMC)デバイスを含むことができる。特に、フラッシュメモリベースのストレージデバイス106は、この態様ではモバイルデバイス内のSoC100に隣接して組み込まれるが、他の態様は、フラッシュメモリベースのストレージデバイス106をリムーバブルメモリデバイスとして用いるとき、同様の機能を得ることができる。

20

#### 【0016】

SoC100はまた、I/Oクライアント104(0)～104(N)に仮想化機能および管理を提供する、仮想マシンマネージャ(VMM)108を含む。VMM108は、SoC100のプロセッサ(図示せず)によって実行され、SoC100のシステムメモリまたは必要もしくは要望に応じて他のメモリ位置にある、ソフトウェアモジュールであってよい。I/Oクライアント104(0)～104(N)の各々は、SoC100のプロセッサ上および/またはSoC100のプロセッササブシステム(図示せず)上で実行される、ホストソフトウェアエンティティ(図1のI/Oクライアント104(0)およびI/Oクライアント104(1)など)を含むことができる。10V-HC102は、I/Oクライアント104(0)～104(N)とフラッシュメモリベースのストレージデバイス106との間の仲介の役目を果たすことができる。このようにして、10V-HC102は、I/Oクライアント104(0)～104(N)が各々、あたかもそれがフラッシュメモリベースのストレージデバイス106と通信している唯一のI/Oクライアント104(0)～104(N)であるかのようにフラッシュメモリベースのストレージデバイス106と対話するように、I/Oクライアント104(0)～104(N)とフラッシュメモリベースのストレージデバイス106との間の対話を制御することができる。同様に、10V-HC102は、フラッシュメモリベースのストレージデバイス106が、実際には複数のI/Oクライアント104(0)～104(N)と通信しているときに、単一のI/Oクライアント104(0)～104(N)のみと通信しているかのように動作することを可能にするように構成することができる。

30

40

#### 【0017】

いくつかの態様による図1の10V-HC102の例示的な構成要素をよりよく示すために、図2を提供する。10V-HC102は、使用されているフラッシュメモリベースのストレージデバイス規格(たとえば、非限定的な例として、UFSまたはeMMC)の必要に従って、図2に示すより

50

も多いためは少ない要素を含む場合があることを理解されたい。図2に見られるように、IOV-HC102は、ベースレジスタインターフェース(BRI)200を含み、これを介して図1のVMM108はIOV-HC102と通信することができる。IOV-HC102はまた、クライアントレジスタインターフェース(CRI)202(0)～202(N)を含む。CRI202(0)～202(N)の各々は、図1のI/Oクライアント104(0)～104(N)のうちの対応するクライアントがIOV-HC102にTR(図示せず)を送信するためのインターフェースを表す。CRI202(0)～202(N)は、クエリまたはノーオペレーション(NOP)命令など、他の、非TR要求を送信するために使用されることもある。

#### 【0018】

図2に見られるように、CRI202(0)～202(N)は、それぞれ矢印206、208、および210で示すように、IOV-HC102のTRフェッチ回路(TR FETCH CIRC)204に通信可能に結合される。いくつかの態様では、TRフェッチ回路204は、UFSトランSPORTプロトコル(UTP)転送要求ディスクリプタ(UTRD)(図示せず)などのトランSPORTプロトコルディスクリプタをシステムメモリからフェッチすることと、UTPコマンドディスクリプタ(UCD)(図示せず)などのコマンドディスクリプタの位置を決定するためにトランSPORTプロトコルディスクリプタを復号することとを担当してよい。TRフェッチ回路204は、次いで、矢印214で示すように、システムメモリ212からコマンドディスクリプタのTRセクション(図示せず)をフェッチしてよい。

#### 【0019】

従来のホストコントローラでは、TRフェッチ回路204は、次いでTRからパラメータを取り出し、処理のためにTR全体をトランSPORTプロトコルエンジン216(たとえば、UTPエンジンまたはeMMCトランSPORTプロトコルエンジン)に転送する。しかしながら、マルチクライアント環境では、TRのさらなる検査および処理が必要とされる場合がある。たとえば、様々なタイプのTRにカスタム処理を提供すること、またはTRをトラップするもしくは終了することが望ましい場合がある。したがって、IOV-HC102は、コマンドトラッピング機能を提供するように構成される。IOV-HC102はしたがって、TR検査および処理のためのTRフィルタ回路218と、コマンドトラッピングのためのTRトラップ220と、トラップされたコマンドから生じる応答の、I/Oクライアント104(0)～104(N)(図示せず)への送信を容易にするための応答生成回路222とを含む。TRフィルタ回路218、TRトラップ220、および応答生成回路222の動作については、以下でさらに詳細に説明する。

#### 【0020】

引き続き図2を参照すると、TRフェッチ回路204によってフェッチされるすべてのTRの検査および処理は、IOV-HC102のTRフィルタ回路218によって行われる。TRフィルタ回路218は、TRがその内容に基づいてどのように処理されるかを決定する。TRの内容が、TRが読み取りまたは書き込みコマンドに対応することを示す場合、TRは、矢印226で示すように、TRフィルタ回路218によってアクセス制御回路224に転送されてよい。アクセス制御回路224は、論理ユニット(図示せず)に読み取り/書き込みアクセスルールのハードウェア実施を提供する。TRがアクセス制御回路224によって確認される場合、TRは、矢印228で示すように、トランSPORTプロトコルエンジン216に伝えられる。アクセス制御回路224によって拒否されるTRは、矢印230で示すように、ソフトウェア処理のためにトラップされる。TRの内容が、TRが電力モード変更コマンドに対応することを示す場合、TRは、矢印234で示すように、TRフィルタ回路218によってマルチホスト電力コントローラ(MHPC)232に送られる。

#### 【0021】

図2のMHPC232は、I/Oクライアント104(0)～104(N)からの電力モード変更要求(図示せず)に基づいてフラッシュメモリベースのストレージデバイス106の電力モードを制御するハードウェア状態機械である。TRがMHPC232によって正常に処理される場合、TRは、矢印236で示すように、トランSPORTプロトコルエンジン216に伝えられてよい。トランSPORTプロトコルエンジン216は次いで、相互接続238およびバス240により、フラッシュメモリベースのストレージデバイス106と電力モード変更コマンドおよび応答を通信する。場合によっては、MHPC232は、暗黙のうちにTRを破棄することがある、または、矢印242で示すように、ソフトウェア処理のためにTRをトラップすることがある。MHPC232は、要求さ

10

20

30

40

50

れた電力モード変更が不成功であったという、フラッシュメモリベースのストレージデバイス106による通知の際に、エラー割込み(図示せず)を生成することもある。TRが他のコマンドを含む場合、TRは、矢印246で示すように、TRフィルタ回路218によってインターceptされ、トラップされてよい。

#### 【0022】

図2に見られるように、TRトラップ220は、トラップされたTRを記憶するために、IOV-HC102によって提供される。TRトラップ220内には、コマンド(CMD)ミラー248(0)～248(N)があり、各々がCRI202(0)～202(N)のうちの1つと関連付けられる。トラップされたTRは、TRを受け取ったCRI202(0)～202(N)のCMDミラー248(0)～248(N)に記憶される。TRがトラップされることを示すために、割込み(矢印250および矢印252で表す)が、BRI200を介してVMM108に生成される。VMM108は、次いで、情報を取り出すために適切なCMDミラー248(0)～248(N)の内容を読み取り、発信元のCRI202(0)～202(N)への応答を生成することによって、TRをさらに処理することができる。

10

#### 【0023】

TRがトラップされると、TRフェッチ回路204はその処理を完了し、別のCRI202(0)～202(N)のための次のTRをフェッチすることに移ることができる。トラップされたTRがVMM108によって処理されるまで、トラップされたTRと関連付けられるCRI202(0)～202(N)は、TRフェッチ調停(図示せず)から除去される。VMM108がIOV-HC102にTRを転送または破棄するよう命令することによってTRを処理するときに限り、同じCRI202(0)～202(N)からの後続のTRが、TRフェッチ回路204によってフェッチされてよい。

20

#### 【0024】

図1および図2に関して上記で説明した態様は、複数のホスト(たとえば、I/Oクライアント104(0)～104(N))によってフラッシュメモリベースのストレージデバイス106を使用するために多くの機能を有効にすることができますが、IOV-HC102によってTRを処理することに関するさらなる問題が依然としてある。特に、従来のホストコントローラ(HC)は、いくつかの「スロット」(いくつかの態様では、UFS-HCI(UFSホストコントローラインターフェース)規格およびeMMC規格に従って、最高32個の(32)スロット)を含んだTRL(図示せず)を提供することができる。TRLスロットは、TRを発行し、フラッシュメモリベースのストレージデバイス106から応答を受け取るためにソフトウェアプロセッサによって使用される。しかしながら、図1のSoC100などの複数のI/Oクライアント環境では、IOV-HC102は、複数のI/Oクライアント104(0)～104(N)の間でスロットを割り振り、追跡する必要がある。いくつかの態様では、同じ問題は、タスク管理要求リスト(TMRL)(図示せず)のスロットの割振りに関して発生することがある。

30

#### 【0025】

この点について、IOV-HC102は、I/Oクライアント104(0)～104(N)に対応するCRI202(0)～202(N)に共有TRL256のスロットを仮想TRL(図示せず)として割り振るために仮想TRLレジスタ254を提供する。いくつかの態様は、I/Oクライアント104(0)～104(N)に対応するCRI202(0)～202(N)に共有TMRL260のスロットを仮想TMRL(図示せず)として割り振るために仮想TMRLレジスタ258を提供することもある。仮想TRLレジスタ254の使用については、図3、図4A、および図4Bに関して以下でより詳細に説明し、仮想TMRLレジスタ258の使用については、図5および図6に関して以下で説明する。

40

#### 【0026】

図3は、図2の共有TRL256および仮想TRLレジスタ254のより詳細な説明を提供する。図3の例では、共有TRL256は、32個の(32)スロット300(0)～300(31)を含んでいる。いくつかの態様では、共有TRL256は、ここに示す32個の(32)スロット300(0)～300(31)を上回るスロット数を含む場合があることを理解されたい。図3の仮想TRLレジスタ254は、複数のTRLスロットオフセットレジスタ302(0)～302(4)と、複数のTRLスロットカウントレジスタ304(0)～304(4)とを含んでいる。TRLスロットオフセットレジスタ302(1)～302(4)およびTRLスロットカウントレジスタ304(1)～304(4)の各々は、クライアントID列306で示す、CRI202(0)～202(3)に対応する。説明のために、TRLスロットオフセットレジスタ302(0)およびT

50

RLスロットカウントレジスタ304(0)は、BRI200と関連付けられる。いくつかの態様では、仮想TRLレジスタ254は、図2のBRI200を介してVMM108によってアクセス可能であってよい。特に、共有TRL256のサイズは、BRI200を介してVMM108にアドバタイズされてよい。

#### 【0027】

図3に見られるように、共有TRL256の部分が、対応するTRLスロットカウントレジスタ302(0)～302(4)およびTRLスロットカウントレジスタ304(0)～304(4)を使用して、IOV-HC102によってBRI200およびCRI202(0)～202(3)の各々に割り振られてよい。TRLスロットオフセットレジスタ302(0)～302(4)のTRLスロットオフセットレジスタ値308(0)～308(4)は各々、それぞれBRI200およびCRI202(0)～202(3)に対する基本スロット(すなわち、第1の割り当てられたスロット)のインデックスを表す。したがって、BRI200は、TRLスロットオフセットレジスタ値308(0)で示されるように、基本スロットとしてスロット300(0)を割り当てられ、CRI202(0)は、TRLスロットオフセットレジスタ値308(1)で示されるように、基本スロットとしてスロット300(16)を割り当てられる。CRI202(1)～202(3)は、それぞれのTRLスロットオフセットレジスタ値308(2)～308(4)で示される、それぞれスロット300(4)、300(5)、および300(8)を割り当てられる。いくつかの態様によれば、TRLスロットオフセットレジスタ値308(0)～308(4)は各々、2の整数乗(たとえば、1、2、4、8、など)であり、特定のCRI202(0)～202(3)のための設定は、対応するI/Oクライアント104(0)～104(3)が有効にされる前に構成されなければならず、CRI202(0)～202(3)がアクティブである限り変更されるべきではない。

10

#### 【0028】

引き続き図3を参照すると、TRLスロットカウントレジスタ304(0)～304(4)は、対応するTRLスロットカウントレジスタ値310(0)～310(4)を記憶する。TRLスロットカウントレジスタ値310(0)～310(4)は各々、BRI200およびCRI202(0)～202(3)にそれぞれ割り当てられる共有TRL256のスロット300(0)～300(31)の数を示す。図3に見られるように、BRI200は、TRLスロットカウントレジスタ値310(0)で示される、4スロットを割り当てられる。BRI200は、したがって、共有TRL256内のスロット300(0)～300(3)から構成される仮想TRL312を割り振られる。同様に、CRI202(0)～202(3)は、対応するTRLスロットカウントレジスタ値310(1)～310(4)で示される、それぞれ16スロット、1スロット、1スロット、および8スロットを割り振られる。CRI202(0)～202(3)は、したがって、対応するスロット300(16)～300(31)、300(4)、300(5)、および300(8)～300(15)から構成されるそれぞれの仮想TRL314、316、318、および320を割り振られる。例示的な態様では、TRLスロットカウントレジスタ値310(0)～310(4)の各々は、対応するTRLスロットオフセットレジスタ値308(0)～308(4)にそろえられ、特定のCRI202(0)～202(3)のための設定は、対応するI/Oクライアント104(0)～104(3)が有効にされる前に構成されなければならず、CRI202(0)～202(3)がアクティブである限り変更されるべきではない。これらの要件もまた、オプションである。

20

#### 【0029】

いくつかの態様では、IOV-HC102の初期化時に、IOV-HC102は、スロット300(0)～300(31)の割振りを担当することができるVMM108からTRLスロットオフセットレジスタ値308(0)～308(4)およびTRLスロットカウントレジスタ値310(0)～310(4)を受け取ることができる。いくつかの態様は、静的構成(図示せず)に、または発見的アルゴリズムの結果(図示せず)に基づいて、スロット300(0)～300(31)が割り振られることを規定することができる。いくつかの態様によれば、IOV-HC102は、CRI202(3)などの新しいCRIがVMM108によって作成されるとき、VMM108からTRLスロットオフセットレジスタ値308(4)などのTRLスロットオフセットレジスタ値、およびTRLスロットカウントレジスタ値310(4)などのTRLスロットカウントレジスタ値を受け取ることができる。いくつかの態様は、VMM108がI/Oクライアント104(0)～104(3)に提示される仮想TRL312、314、316、318、320のパラメータを制御することを規定することができる。いくつかの態様では、割り振られるスロット300(0)～300(31)の数および位置は、IOV-HC102内の機能レジスタ(capability register)(図示せず)に、特に、BRI200を通してVMM108によってアクセスされるレジスタに、書き込まれてよい。

30

#### 【0030】

40

50

UFS-HCIに基づく従来のコントローラでは、ハードウェア定数(hardware constant)として実装され、NUTRSおよび/またはNUTMRSと呼ばれる機能フィールドが、それぞれTRLおよび/またはTMRLのサイズを示すために使用される。本開示のいくつかの態様では、これらのフィールドは、CRI202(0)～202(N)の各々に組み込まれてよい。そのような態様では、VMM108は、I/Oクライアント104(0)～104(3)の各々にスロット300(0)～300(31)のうちのいくつかが割り振られるかを通知するために、初期化または仮想マシン作成時にこれらのフィールドを書き込むことができる。

#### 【0 0 3 1】

TRを受け取り、図2および図3の仮想TRLレジスタ254を使用して共有TRL256のスロットにTRをマッピングし、応答を返すための、図2のIOV-HC102の例示的な動作を示すために、図4Aおよび図4Bを提供する。明快にするために、図4Aおよび図4Bについて説明する際に図1～図3の要素が参照される。図4Aでは、IOV-HC102は、CRI202(3)からTR400を受け取る。TR400は、スロット識別子402を含み、この例ではスロット識別子402は、1(1)という値を有し、CRI202(3)に割り振られた図3の仮想TRL320内の第2のスロットへのインデックスを表す。IOV-HC102(特に、IOV-HC102のTRフェッチ回路204)は次いで、CRI202(3)に対応するTRLスロットオフセットレジスタ302(4)およびTRLスロットカウントレジスタ304(4)を使用して、共有TRL256のスロット300(9)にTR400をマッピングする。たとえば、マッピングは、スロット識別子402を、CRI202(3)に対応するTRLスロットオフセットレジスタ値308(4)と足すことによって実現されてよい。図3に見られるように、TRLスロットオフセットレジスタ値308(4)は8(8)であり、これは、1(1)という値を有するスロット識別子402と足されるとき、9(9)というスロットインデックスを生じる。再計算されたスロットインデックスは、次いで、フラッシュメモリベースのストレージデバイス106に送信されるTR400内にIOV-HC102によって符号化される。非限定的な例として、UFSに基づく態様では、再計算されたスロットインデックスは、TR400のタスクタグフィールドに符号化されてよく、eMMCに基づく態様では、再計算されたスロットインデックスは、TR400のタスクIDフィールドに符号化されてよい。IOV-HC102はしたがって、TR400を共有TRL256のスロット300(9)に宛て、そこからTR400は、順次に処理され、フラッシュメモリベースのストレージデバイス106に渡される。いくつかの態様は、TR400が仮想TRL320の有効スロット300(0)～300(31)に宛てられることを確保するために、TRLスロットカウントレジスタ304(4)が、スロット識別子402の境界チェックをする(bounds-checking)ために使用されることを規定することができる。そのような態様では、TR400が対応するCRI202(0)～202(3)に割り当てられた範囲外のスロット300(0)～300(31)に宛てられる場合、TR400はトラップされる。

#### 【0 0 3 2】

図4Bでは、IOV-HC102は、フラッシュメモリベースのストレージデバイス106から応答404を受け取る。応答404は、TR400を送った同じスロット300(9)に宛てられる。したがって、IOV-HC102は、CRI202(3)に対応するTRLスロットオフセットレジスタ302(4)およびTRLスロットカウントレジスタ304(4)を使用して、CRI202(3)へ応答404をルーティングする。非限定的な例として、IOV-HC102は、応答404のスロット識別子406(9(9))から、CRI202(3)に対応するTRLスロットオフセットレジスタ値308(4)(すなわち、8(8))を引くことができる。非限定的な例として、UFSに基づく態様では、スロット識別子406は、応答404のタスクタグフィールドから検索されてよく、eMMCに基づく態様では、スロット識別子406は、応答404のタスクIDフィールドから検索されてよい。応答404は次いで、1(1)というスロット識別子408とともにCRI202(3)に提供される。

#### 【0 0 3 3】

本開示のいくつかの態様は、複数のI/Oクライアント104(0)～104(N)のためのTMRLにおけるスロットの割振りが、上記で説明した共有TRL256におけるスロット300(0)～300(31)の割振りと同様の方法でIOV-HC102によって管理されることをさらに規定することができる。したがって、図5は、図2の仮想TMRLレジスタ258および共有TMRL260の例示的な態様を示すために提供される。図5の例では、共有TMRL260は、8個の(8)スロット500(0)～500(7)

10

20

30

40

50

を含むが、いくつかの態様は、ここに示すよりも多いまたは少ないスロットを提供することがある。図5の仮想TMRLレジスタ258は、複数のTMRLスロットオフセットレジスタ502(0)～502(4)と、複数のTRLスロットカウントレジスタ504(0)～504(4)とを提供する。TMRLスロットオフセットレジスタ502(1)～502(4)およびTMRLスロットカウントレジスタ504(1)～504(4)の各々は、クライアントID列506で示す、CRI202(0)～202(3)に対応する。説明のために、TMRLスロットオフセットレジスタ502(0)およびTMRLスロットカウントレジスタ504(0)は、BRI200と関連付けられる。

#### 【0 0 3 4】

図5に見られるように、IOV-HC102は、対応するTMRLスロットオフセットレジスタ502(0)～502(4)およびTMRLスロットカウントレジスタ504(0)～504(4)を使用して、共有TMRL260の部分をBRI200およびCRI202(0)～202(3)の各々に割り振ることができる。TMRLスロットオフセットレジスタ502(0)～502(4)のTMRLスロットオフセットレジスタ値508(0)～508(4)が各々、それぞれBRI200およびCRI202(0)～202(3)に対する基本スロット(すなわち、第1の割り当てられたスロット)のインデックスを表す。BRI200はしたがって、TMRLスロットオフセットレジスタ値508(0)で示されるように、基本スロットとしてスロット500(0)を割り当てられ、CRI202(0)は、TMRLスロットオフセットレジスタ値508(1)で示されるように、基本スロットとしてスロット500(3)を割り当てられる。CRI202(1)～202(3)は、それぞれのTMRLスロットオフセットレジスタ値508(2)～508(4)で示される、それぞれスロット500(1)、500(2)、および500(5)を割り当てられる。いくつかの態様によれば、TMRLスロットオフセットレジスタ値508(0)～508(4)は各々、2の整数乗(たとえば、1、2、4、8、など)であってよく、特定のCRI202(0)～202(3)のための設定は、対応するI/Oクライアント104(0)～104(3)が有効にされる前に構成されなければならず、CRI202(0)～202(3)がアクティブである限り変更されるべきではない。

#### 【0 0 3 5】

引き続き図5を参照すると、TMRLスロットカウントレジスタ504(0)～504(4)は、対応するTMRLスロットカウントレジスタ値510(0)～510(4)を記憶する。TMRLスロットカウントレジスタ値510(0)～510(4)は各々、BRI200およびCRI202(0)～202(3)にそれぞれ割り当てられる共有TMRL260のスロット500(0)～500(31)の数を示す。図5に見られるように、BRI200は、TMRLスロットカウントレジスタ値510(0)で示されるように、1個の(1)スロットを割り当てられる。BRI200は、したがって、共有TMRL260内のスロット500(0)から構成される仮想TMRL512を割り振られる。同様に、CRI202(0)～202(3)は、対応するTMRLスロットカウントレジスタ値510(1)～510(4)で示されるように、それぞれ2スロット、1スロット、1スロット、および3スロットを割り振られる。CRI202(0)～202(3)は、したがって、それぞれスロット500(6)～500(7)、500(1)、500(2)、および500(3)～500(4)から構成されるそれぞれの仮想TMRL514、516、518、および520を割り振られる。例示的な態様では、TMRLスロットカウントレジスタ値510(0)～510(4)の各々は、対応するTMRLスロットオフセットレジスタ値508(0)～508(4)にそろえられるべきであり、特定のCRI202(0)～202(3)のための設定は、対応するI/Oクライアント104(0)～104(3)が有効にされる前に構成されなければならず、CRI202(0)～202(3)がアクティブである限り変更されるべきではない。これらの要件もまた、オプションである。

#### 【0 0 3 6】

TMRを受け取り、図2および図5の仮想TMRLレジスタ258を使用して共有TMRL260のスロットにTMRをマッピングするための、図2のIOV-HC102の例示的な動作を示すために、図6を提供する。明快にするために、図6について説明する際に図1、図2、および図5の要素が参照される。図6では、IOV-HC102は、CRI202(3)からTMR600を受け取る。TMR600は、スロット識別子602を含み、この例ではスロット識別子602は、1(1)という値を有し、CRI202(3)に割り振られた図5の仮想TMRL520内の第2のスロットへのインデックスを表す。IOV-HC102(特に、IOV-HC102のTRフェッチ回路204)は次いで、CRI202(3)に対応するTMRLスロットオフセットレジスタ502(4)およびTMRLスロットカウントレジスタ504(4)を使用して、共有TMRL260のスロット500(6)にTMR600をマッピングする。たとえば、マッピングは、スロット識

10

20

30

40

50

別子602を、CRI202(3)に対応するTMRLスロットオフセットレジスタ値508(4)と足すことによって実現されてよい。図5に見られるように、TMRLスロットオフセットレジスタ値508(4)は5(5)であり、これは、1(1)という値を有するスロット識別子602と足されるとき、6(6)というスロットインデックスを生じる。再計算されたスロットインデックスは、次いで、フラッシュメモリベースのストレージデバイス106に送信されるTMR600内にIOV-HC102によって符号化される。非限定的な例として、UFSに基づく態様では、再計算されたスロットインデックスは、TMR600のタスクタグフィールドに符号化されてよく、eMMCに基づく態様では、再計算されたスロットインデックスは、TMR600のタスクIDフィールドに符号化されてよい。IOV-HC102はしたがって、TMR600を共有TMRL260のスロット500(6)に宛て、そこからTMR600は、順次に処理され、フラッシュメモリベースのストレージデバイス106に渡される。いくつかの態様では、TMR600が仮想TMRL520の有効スロット500(1)～500(31)に宛てられることを確保するために、TMRLスロットカウントレジスタ504(4)は、スロット識別子602の境界チェックをするために使用されてよい。

10

#### 【0037】

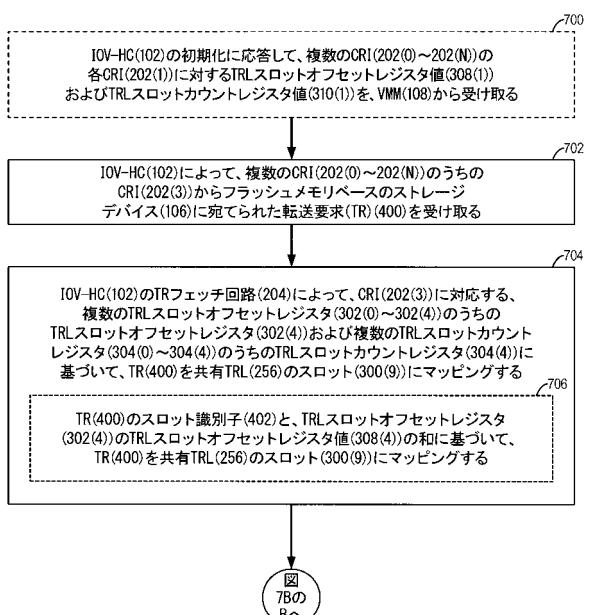

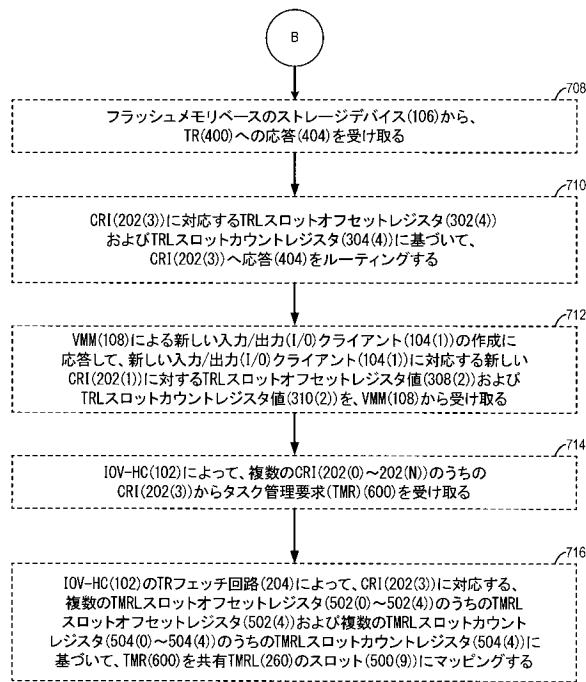

図7Aおよび図7Bは、図2の仮想TRLレジスタ254を使用して共有TRL256のスロットを割り振るための図1のIOV-HC102の例示的な動作を示すために提供される。明快にするために、図7Aおよび図7Bについて説明する際に、図1～図6の要素が参照される。図7Aでは、いくつかの態様による動作は、IOV-HC102が、IOV-HC102の初期化に応答して、複数のCRI202(0)～202(N)の各CRI202(1)に対するTRLスロットオフセットレジスタ値(TRLスロットオフセットレジスタ値308(1)など)およびTRLスロットカウントレジスタ値(TRLスロットカウントレジスタ値310(1)など)を、VMM108から受け取ることから始まることがある(ブロック700)。IOV-HC102はしたがって、本明細書では、「IOV-HCの初期化に応答して、複数のCRIの各CRIに対するTRLスロットオフセットレジスタ値およびTRLスロットカウントレジスタ値を、VMMから受け取るための手段」と呼ぶことができる。IOV-HC102は次いで、複数のCRI202(0)～202(N)のうちのCRI202(3)からフラッシュメモリベースのストレージデバイス106に宛てられたTR400を受け取る(ブロック702)。この点について、IOV-HC102は、本明細書では「CRIからフラッシュメモリベースのストレージデバイスに宛てられたTRを受け取るための手段」と呼ぶことができる。

20

#### 【0038】

IOV-HC102(および特に、IOV-HC102のTRフェッチ回路204)は、次に、複数のTRLスロットオフセットレジスタ302(0)～302(4)のうちのTRLスロットオフセットレジスタ302(4)および複数のTRLスロットカウントレジスタ304(0)～304(4)のうちのTRLスロットカウントレジスタ304(4)に基づいて、TR400を共有TRL256のスロット300(9)にマッピングする(ブロック704)。したがって、TRフェッチ回路204は、本明細書では、「複数のTRLスロットオフセットレジスタのうちのあるTRLスロットオフセットレジスタおよび複数のTRLスロットカウントレジスタのうちのあるTRLスロットカウントレジスタに基づいて、TRを共有TRLのスロットにマッピングするための手段」と呼ぶことができる。TRLスロットオフセットレジスタ302(4)およびTRLスロットカウントレジスタ304(4)は、ともにCRI202(3)に対応する。いくつかの態様では、TR400をスロット300(9)にマッピングするためのブロック704の動作は、TR400のスロット識別子402と、TRLスロットオフセットレジスタ302(4)のTRLスロットオフセットレジスタ値308(4)の和に基づいてよい(ブロック706)。次いで、処理は図7Bのブロック708において継続する。

30

40

#### 【0039】

次に図7Bを参照すると、いくつかの態様によるIOV-HC102は、フラッシュメモリベースのストレージデバイス106から、TR400への応答404を受け取ることができる(ブロック708)。IOV-HC102はしたがって、本明細書では、「フラッシュメモリベースのストレージデバイスから、TRへの応答を受け取るための手段」と呼ぶことができる。CRI202(3)に対応するTRLスロットオフセットレジスタ302(4)およびTRLスロットカウントレジスタ304(4)に基づいて、IOV-HC102は、CRI202(3)へ応答404をルーティングすることができる(ブロック710)。この点について、IOV-HC102は、本明細書では、「CRIに対応するTRLスロットオフセ

50

ットレジスタおよびTRLスロットカウントレジスタに基づいてCRIへ応答をルーティングするための手段」と呼ぶことができる。いくつかの態様では、IOV-HC102は、VMM108による新しいI/Oクライアント104(1)の作成に応答して、新しいI/Oクライアント104(1)に対応する新しいCRI202(1)に対するTRLスロットオフセットレジスタ値(TRLスロットオフセットレジスタ値308(2)など)およびTRLスロットカウントレジスタ値(TRLスロットカウントレジスタ値310(2)など)を、VMM108から受け取ることができる(ロック712)。したがって、IOV-HC102は、本明細書では、「I/Oクライアントに対応する新しいCRIに対するTRLスロットオフセットレジスタ値およびTRLスロットカウントレジスタ値を、VMMから受け取るための手段」と呼ぶことができる。

## 【0040】

10

上述のように、いくつかの態様では、複数のI/Oクライアント104(0)～104(N)のためのスロット500(0)～500(31)の割振りが、上記で説明した共有TRL256におけるスロット300(0)～300(31)の割振りと同様の方法でIOV-HC102によって管理されることが可能である。したがって、そのような態様では、IOV-HC102は、複数のCRI202(0)～202(N)のうちのCRI202(3)からTMR600を受け取ることができる(ロック714)。IOV-HC102はしたがって、本明細書では、「複数のCRIのうちのあるCRIからTMRを受け取るための手段」と呼ぶことができる。IOV-HC102(特に、IOV-HC102のTRフェッチ回路204)は、次いで、CRI202(3)に対応する、複数のTMRLスロットオフセットレジスタ502(0)～502(4)のうちのTMRLスロットオフセットレジスタ502(4)および複数のTMRLスロットカウントレジスタ504(0)～504(4)のうちのTMRLスロットカウントレジスタ504(4)に基づいて、TMR600を共有TMRL260のスロット500(9)にマッピングすることができる(ロック716)。この点について、TRフェッチ回路204は、本明細書では、「複数のTMRLスロットオフセットレジスタのうちのあるTMRLスロットオフセットレジスタおよび複数のTMRLスロットカウントレジスタのうちのあるTMRLスロットカウントレジスタに基づいて、TMRを共有TMRLのスロットにマッピングするための手段」と呼ぶことができる。

## 【0041】

20

本明細書で開示する態様によるフラッシュメモリベースのストレージデバイスのIOV-HCは、任意のプロセッサベースのデバイスで提供されるか、それに統合されてよい。例として、限定はしないが、セットトップボックス、エンターテインメントユニット、ナビゲーションデバイス、通信デバイス、固定位置データユニット、モバイル位置データユニット、モバイルフォン、セルラーフォン、コンピュータ、ポータブルコンピュータ、デスクトップコンピュータ、携帯情報端末(PDA)、モニタ、コンピュータモニタ、テレビジョン、チューナ、ラジオ、衛星ラジオ、音楽プレーヤ、デジタル音楽プレーヤ、ポータブル音楽プレーヤ、デジタルビデオプレーヤ、ビデオプレーヤ、デジタルビデオディスク(DVD)プレーヤ、およびポータブルデジタルビデオプレーヤが含まれる。

30

## 【0042】

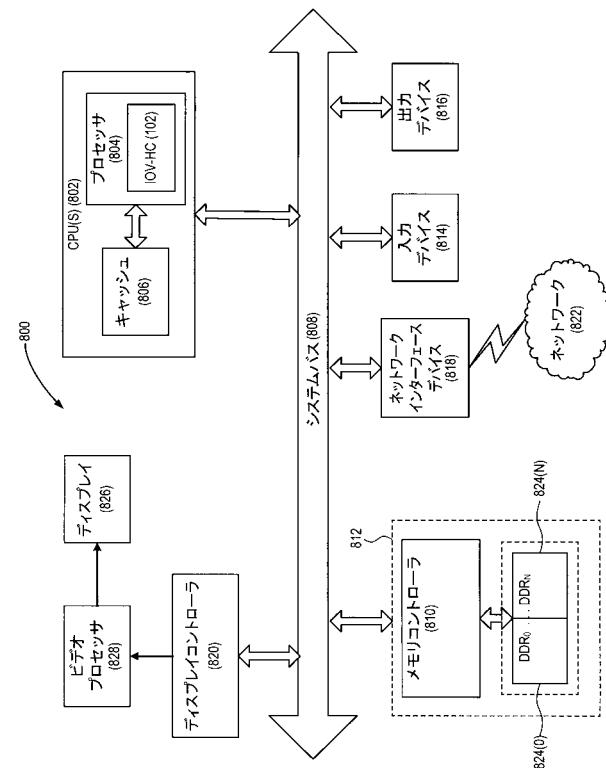

この点について、図8は、図2に示すIOV-HC102で図2のSoC100を用いることができる、プロセッサベースのシステム800の一例を示す。この例では、プロセッサベースのシステム800は、1つまたは複数の中央処理ユニット(CPU)802を含み、各々が1つまたは複数のプロセッサ804を含む。CPU802は、一時的に記憶されたデータへの高速アクセスのためにプロセッサ804に結合されたキャッシュメモリ806を有することができる。CPU802は、システムバス808に結合され、プロセッサベースのシステム800中に含まれるデバイスを相互結合することができる。よく知られているように、CPU802は、システムバス808を通じてアドレス情報、制御情報、およびデータ情報を交換することによって、これらの他のデバイスと通信する。たとえば、CPU802は、スレーブデバイスの一例として、メモリコントローラ810にバストランザクション要求を通信することができる。図8に示されていないが、複数のシステムバス808を設けることができる。

40

## 【0043】

他のデバイスをシステムバス808に接続することができる。図8に示すように、これらのデバイスは、実施例として、メモリシステム812、1つまたは複数の入力デバイス814、1つ

50

または複数の出力デバイス816、1つまたは複数のネットワークインターフェースデバイス818、および1つまたは複数のディスプレイコントローラ820を備えることができる。入力デバイス814は、これに限定されないが、入力キー、スイッチ、音声プロセッサ等を含む、任意のタイプの入力デバイスを備えることができる。出力デバイス816は、限定はしないが、オーディオインジケータ、ビデオインジケータ、他の視覚インジケータなどを含む、任意のタイプの出力デバイスを含むことができる。ネットワークインターフェースデバイス818は、ネットワーク822との間のデータの交換を可能にするように構成された任意のデバイスとすることができます。ネットワーク822は、限定はしないが、ワイヤードまたはワイヤレスネットワーク、プライベートまたは公共ネットワーク、ローカルエリアネットワーク(LAN)、ワイヤローカルエリアネットワーク(WLAN)、ワイヤレスローカルエリアネットワーク、BLUETOOTH(登録商標)(BT)、およびインターネットを含む、任意のタイプのネットワークとすることができます。ネットワークインターフェースデバイス818は、所望の任意のタイプの通信プロトコルをサポートするように構成することができます。メモリシステム812は、1つまたは複数のメモリユニット824(0)～824(N)を含むことができる。

10

#### 【0044】

また、CPU802は、1つまたは複数のディスプレイ826に送られる情報を制御するために、システムバス808を通じてディスプレイコントローラ820にアクセスするように構成されてもよい。ディスプレイコントローラ820は、1つまたは複数のビデオプロセッサ828を介して表示される情報をディスプレイ826に送り、ビデオプロセッサ828は、表示される情報を、ディスプレイ826に適したフォーマットとなるように処理する。ディスプレイ826は、限定はしないが、陰極線管(CRT)、液晶ディスプレイ(LCD)、発光ダイオード(LED)ディスプレイ、プラズマディスプレイなどを含む、任意のタイプのディスプレイを含むことができる。

20

#### 【0045】

本明細書で開示する態様に関して説明する様々な例示的な論理ブロック、モジュール、回路、およびアルゴリズムは、電子ハードウェア、メモリもしくは別のコンピュータ可読媒体に記憶され、プロセッサもしくは他の処理デバイスによって実行される命令、または両方の組合せとして実装され得ることを当業者はさらに諒解されよう。本明細書において説明されるデバイスは、例として、任意の回路、ハードウェア構成要素、集積回路(IC)、またはICチップ内で用いることができる。本明細書において開示されるメモリは、任意のタイプおよびサイズのメモリとすることでき、所望の任意のタイプの情報を記憶するように構成することができる。この互換性を明確に説明するために、様々な例示的な構成要素、ブロック、モジュール、回路、およびステップについて、上記では概してそれらの機能について説明した。そのような機能がどのように実装されるかは、特定の適用例、設計上の選定、および/または全体的なシステムに課された設計制約に依存する。当業者は、説明した機能を特定の適用例ごとに様々な方法で実施することができるが、そのような実施態様の決定は、本開示の範囲からの逸脱を引き起こすものと解釈されるべきではない。

30

#### 【0046】

本明細書において開示される態様に関して説明される様々な例示的な論理ブロック、モジュール、および回路は、プロセッサ、デジタルシグナルプロセッサ(DSP)、特定用途向け集積回路(ASIC)、フィールドプログラマブルゲートアレイ(FPGA)もしくは他のプログラマブル論理デバイス、個別ゲートもしくはトランジスタ論理、個別ハードウェア構成要素、または本明細書において説明される機能を実行するように設計されたそれらの任意の組合せにおいて実現または実行することができる。プロセッサは、マイクロプロセッサとすることができるが、代替形態では、プロセッサは、任意の従来のプロセッサ、コントローラ、マイクロコントローラ、または状態機械とすることができます。プロセッサはまた、コンピューティングデバイスの組合せ、(たとえば、DSPとマイクロプロセッサの組合せ、複数のマイクロプロセッサ、DSPコアと連携した1つもしくは複数のマイクロプロセッサ、または任意の他のそのような構成)として実装される場合もある。

40

#### 【0047】

50

本明細書において開示される態様は、ハードウェアにおいて、また、ハードウェアに記憶された命令において具現される場合があり、命令は、たとえば、ランダムアクセスメモリ(RAM)、フラッシュメモリ、読み取り専用メモリ(ROM)、電気的プログラマブルROM(EPROM)、電気的消去可能プログラマブルROM(EEPROM)、レジスタ、ハードディスク、リムーバブルディスク、CD-ROM、または当技術分野において知られている任意の他の形態のコンピュータ可読媒体内に存在することができる。例示的な記憶媒体は、プロセッサが記憶媒体から情報を読み取り、記憶媒体に情報を書き込むことができるようプロセッサに結合される。代替形態では、記憶媒体は、プロセッサと一緒に構成される場合がある。プロセッサおよび記憶媒体はASICに存在してもよい。ASICはリモート局に存在してもよい。代替として、プロセッサおよび記憶媒体は、個別構成要素として、リモート局、基地局、またはサーバに存在してもよい。

10

#### 【0048】

本明細書の例示的な態様のいずれかで説明した動作ステップは、例および議論を提供するために説明されていることにも留意されたい。説明される動作は、図示されるシーケンス以外の多数の異なるシーケンスにおいて実行することができる。さらに、単一の動作ステップで説明される動作は、実際にはいくつかの異なるステップで実施される場合がある。加えて、例示的な態様において論じた1つまたは複数の動作ステップは、組み合わされてもよい。当業者には容易に明らかになるように、フローチャート図に示す動作ステップは、多数の異なる修正を受ける場合があることを理解されたい。当業者はまた、情報および信号が様々な異なる技術および技法のいずれかを使用して表され得ることを理解されよう。たとえば、上記の説明全体にわたって参照される場合があるデータ、命令、コマンド、情報、信号、ビット、シンボル、およびチップは、電圧、電流、電磁波、磁場もしくは磁性粒子、光場もしくは光学粒子、またはそれらの任意の組合せによって表すことができる。

20

#### 【0049】

本開示についての先の説明は、いかなる当業者でも本開示を作製または使用できるようにするために提供されている。本開示に対する様々な修正は、当業者に容易に明らかになり、本明細書で定義する一般原理は、本開示の趣旨または範囲を逸脱することなく、他の変形形態に適用される場合がある。したがって、本開示は、本明細書において説明する例および設計に限定されるものではなく、本明細書で開示する原理および新規の特徴と一致する最も広い範囲を与えられるべきである。

30

#### 【符号の説明】

#### 【0050】

- 100 システムオンチップ(SoC)

- 102 IOV-HC

- 104 I/Oクライアント

- 106ストレージデバイス

- 108仮想マシンマネージャ(VMM)

- 200ベースレジスタインターフェース(BRI)

- 202クライアントレジスタインターフェース(CRI)

- 204TRフェッチ回路(TR FETCH CIRC)

- 212システムメモリ

- 216トランスポートプロトコルエンジン

- 218TRフィルタ回路

- 220TRトラップ

- 222応答生成回路

- 224アクセス制御回路

- 232マルチホスト電力コントローラ(MHPC)

- 238相互接続

- 240バス

40

50

|     |                   |    |

|-----|-------------------|----|

| 248 | コマンド(CMD)ミラー      |    |

| 254 | 仮想TRLレジスタ         |    |

| 256 | 共有TRL             |    |

| 258 | 仮想TMRLレジスタ        |    |

| 260 | 共有TMRL            |    |

| 300 | スロット              |    |

| 302 | TRLスロットオフセットレジスタ  | 10 |

| 304 | TRLスロットカウントレジスタ   |    |

| 306 | クライアントID列         |    |

| 308 | TRLスロットオフセットレジスタ値 |    |

| 310 | TRLスロットカウントレジスタ値  |    |

| 312 | 仮想TRL             |    |

| 314 | 仮想TRL             |    |

| 316 | 仮想TRL             |    |

| 318 | 仮想TRL             |    |

| 320 | 仮想TRL             |    |

| 400 | 転送要求(TR)          |    |

| 402 | スロット識別子           |    |

| 404 | 応答                |    |

| 500 | スロット              | 20 |

| 502 | TMRLスロットオフセットレジスタ |    |

| 504 | TMRLスロットカウントレジスタ  |    |

| 506 | クライアントID          |    |

| 600 | TMR               |    |

| 602 | スロット識別子           |    |

| 800 | プロセッサベースのシステム     |    |

| 802 | CPU               |    |

| 804 | プロセッサ             |    |

| 806 | キャッシュメモリ          |    |

| 808 | システムバス            | 30 |

| 810 | メモリコントローラ         |    |

| 812 | メモリシステム           |    |

| 814 | 入力デバイス            |    |

| 816 | 出力デバイス            |    |

| 818 | ネットワークインターフェース    |    |

| 820 | ディスプレイコントローラ      |    |

| 822 | ネットワーク            |    |

| 824 | メモリユニット           |    |

【図1】

【図2】

【図3】

【図4 A】

【図 4 B】

【図 5】

【図 6】

【図 7 A】

【図 7 B】

【図 8】

## 【国際調査報告】

## INTERNATIONAL SEARCH REPORT

International application No

PCT/US2015/033953

A. CLASSIFICATION OF SUBJECT MATTER

INV. G06F13/16 G06F3/06 G11C7/00

ADD.

According to International Patent Classification (IPC) or to both national classification and IPC

## B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)

G06F G11C

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)

EPO-Internal, WPI Data

## C. DOCUMENTS CONSIDERED TO BE RELEVANT

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                          | Relevant to claim No. |

|-----------|-----------------------------------------------------------------------------------------------------------------------------|-----------------------|

| A         | EP 2 492 916 A1 (HUAWEI TECH CO LTD [CN])<br>29 August 2012 (2012-08-29)<br>figures 2,3,6<br>-----                          | 1-23                  |

| A         | US 2012/030408 A1 (FLYNN DAVID [US] ET AL)<br>2 February 2012 (2012-02-02)<br>paragraphs [0127] - [0133]; figure 4<br>----- | 1-23                  |

| A         | US 2013/275656 A1 (TALAGALA NISHA [US] ET AL) 17 October 2013 (2013-10-17)<br>figure 1B<br>-----                            | 1-23                  |

Further documents are listed in the continuation of Box C.

See patent family annex.

## \* Special categories of cited documents :

- "A" document defining the general state of the art which is not considered to be of particular relevance

- "E" earlier application or patent but published on or after the international filing date

- "L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

- "O" document referring to an oral disclosure, use, exhibition or other means

- "P" document published prior to the international filing date but later than the priority date claimed

"T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

"X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

"Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art

"&" document member of the same patent family

Date of the actual completion of the international search

Date of mailing of the international search report

30 July 2015

11/08/2015

Name and mailing address of the ISA/

European Patent Office, P.B. 5818 Patentlaan 2

NL - 2280 HV Rijswijk

Tel. (+31-70) 340-2040,

Fax: (+31-70) 340-3016

Authorized officer

Albert, Jozsef

## INTERNATIONAL SEARCH REPORT

Information on patent family members

International application No

PCT/US2015/033953

| Patent document cited in search report | Publication date | Patent family member(s) |  | Publication date |

|----------------------------------------|------------------|-------------------------|--|------------------|

| EP 2492916                             | A1 29-08-2012    | CN 101833989 A          |  | 15-09-2010       |

|                                        |                  | EP 2492916 A1           |  | 29-08-2012       |

|                                        |                  | KR 20120087980 A        |  | 07-08-2012       |

|                                        |                  | RU 2012128534 A         |  | 20-01-2014       |

|                                        |                  | US 2012233386 A1        |  | 13-09-2012       |

|                                        |                  | WO 2011147324 A1        |  | 01-12-2011       |

| -----                                  |                  |                         |  |                  |

| US 2012030408                          | A1 02-02-2012    | CN 103098034 A          |  | 08-05-2013       |

|                                        |                  | EP 2598996 A2           |  | 05-06-2013       |

|                                        |                  | US 2012030408 A1        |  | 02-02-2012       |

|                                        |                  | US 2013205097 A1        |  | 08-08-2013       |

|                                        |                  | WO 2012016089 A2        |  | 02-02-2012       |

| -----                                  |                  |                         |  |                  |

| US 2013275656                          | A1 17-10-2013    | NONE                    |  |                  |

| -----                                  |                  |                         |  |                  |

## フロントページの続き

|              |         |               |

|--------------|---------|---------------|

| (51) Int.Cl. | F I     | テーマコード(参考)    |

|              | G 0 6 F | 3/08 H        |

|              | G 0 6 F | 12/00 5 7 1 A |

(81)指定国 AP(BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, ST, SZ, TZ, UG, ZM, ZW), EA(AM, AZ, BY, KG, KZ, RU, T J, TM), EP(AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, R O, RS, SE, SI, SK, SM, TR), OA(BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, KM, ML, MR, NE, SN, TD, TG), AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, H N, HR, HU, ID, IL, IN, IR, IS, JP, KE, KG, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SA, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US

(72)発明者 ドレヴ・ラヴィヴ

アメリカ合衆国・カリフォルニア・92121・サン・ディエゴ・モアハウス・ドライブ・577

5

(72)発明者 デイヴィッド・テブ

アメリカ合衆国・カリフォルニア・92121・サン・ディエゴ・モアハウス・ドライブ・577

5

F ターム(参考) 5B060 AC10