(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2008-176453

(P2008-176453A)

(43) 公開日 平成20年7月31日(2008.7.31)

(51) Int.Cl.

G06F 9/455 (2006.01)

F 1

G 06 F 9/44 3 1 O D

テーマコード (参考)

(21) 出願番号

特願2007-7888 (P2007-7888)

(22) 出願日

平成19年1月17日 (2007.1.17)

審査請求 未請求 請求項の数 19 O L (全 21 頁)

(71) 出願人 302062931

NECエレクトロニクス株式会社

神奈川県川崎市中原区下沼部1753番地

(74) 代理人 100102864

弁理士 工藤 実

(72) 発明者 吉永 恵美

神奈川県川崎市中原区下沼部1753番地

NECエレクトロニクス株式会社内

(54) 【発明の名称】シミュレーション装置

## (57) 【要約】

【課題】複数のパイプラインを考慮したプロセッサの動作をシミュレートすることができるシミュレーション装置を提供する。

【解決手段】シミュレーション装置は、命令処理部(11)と、同時実行条件判定部(31)と、実行マシンサイクル補正部(41)と、を具備している。命令処理部(11)は、プロセッサ(70)上で実行可能な命令群で構成された解析対象プログラムを読み込んで各命令処理を行う。同時実行条件判定部(31)は、解析対象プログラムが有する命令群のそれぞれが複数のパイプライン(71、72)で同時に処理可能かどうかを判断する。実行マシンサイクル補正部(41)は、同時実行条件判定部(31)の結果と、実行マシンサイクル数格納部(42)に予め記憶された複数の命令の各自の実行マシンサイクル数に基づいて、命令群の実行マシンサイクル数を算出する。

【選択図】図4

**【特許請求の範囲】****【請求項 1】**

複数のパイプライン構造を有するプロセッサの動作を模擬するシミュレーション装置であって、

前記プロセッサ上で実行可能な命令群で構成された解析対象プログラムを読み込んで各命令処理を行う命令処理部と、

前記解析対象プログラムが有する命令群のそれぞれが前記複数のパイplineで同時に処理可能かどうかを判断する同時実行条件判定部と、

前記同時実行条件判定部の結果と、実行サイクル数格納部に予め記憶された複数の命令の各々の実行マシンサイクル数に基づいて、前記命令群の実行マシンサイクル数を算出する実行マシンサイクル補正部と、

を具備するシミュレーション装置。

**【請求項 2】**

前記同時実行条件判定部は、同時実行条件格納部に予め記憶された同時実行条件に基づいて、前記解析対象プログラム中の連続する命令群が前記複数のパイplineで同時に処理可能かどうかを判断し、

前記同時実行条件は、前記複数のパイplineのそれぞれが処理可能な命令に基づいて定義されている、

請求項 1 に記載のシミュレーション装置。

**【請求項 3】**

前記実行マシンサイクル補正部は、前記命令群のうちの、前記同時実行条件判定部によって同時実行可能と判断された実行命令群の実行マシンサイクル数を、前記実行命令群のそれぞれの実行マシンサイクル数の中で最も大きい実行マシンサイクル数とする、

請求項 2 に記載のシミュレーション装置。

**【請求項 4】**

前記複数のパイplineのそれぞれに対応するパイpline状態記憶部群を更に具備し、

前記同時実行条件判定部は、前記同時実行条件格納部を参照して、1命令ずつ処理される1番目から最終番目までの前記命令群を1番目から最終番目までの複数の前記実行命令群に分割し、前記実行命令群をそれぞれ前記パイpline状態記憶部群に格納し、

前記実行マシンサイクル補正部は、前記パイpline状態記憶部群と実行サイクル数格納部とを参照して、前記実行命令群の実行マシンサイクル数の中から、前記最大実行マシンサイクル数を検索し、前記実行命令群の実行マシンサイクル数を前記最も大きい実行マシンサイクル数である最大実行マシンサイクル数に変更する、

請求項 3 に記載のシミュレーション装置。

**【請求項 5】**

前記パイpline状態記憶部群に格納された実行命令の実行マシンサイクル数の合計値を含む実行結果を出力装置に出力する実行サイクル数計測部を更に具備する請求項 4 に記載のシミュレーション装置。

**【請求項 6】**

前記同時実行条件判定部は、前記パイpline状態記憶部群に格納された前記実行命令群が、同一のレジスタを用いて演算を行う演算実行命令群を表す場合、前記演算実行命令群を1番目から最終番目までの複数のハザード実行命令群に分割し、

前記複数のハザード実行命令群の各々は、同一のレジスタを用いていない命令の組を表し、

前記同時実行条件判定部は、前記パイpline状態記憶部群に格納された前記演算実行命令群に代えて、前記ハザード実行命令群を前記実行命令群として1番目から最終番目までこの順に前記パイpline状態記憶部群のうちの1つのパイpline状態記憶部に格納する、

請求項 4 又は 5 に記載のシミュレーション装置。

10

20

30

40

50

**【請求項 7】**

前記命令群のうちの、演算命令を識別する識別子と、前記プロセッサが前記演算命令を実行するときに用いるレジスタのレジスタ名とが格納された使用レジスタ情報記憶部を更に具備し、

前記同時実行条件判定部は、前記パイプライン状態記憶部群と前記使用レジスタ情報記憶部とを参照して、前記パイプライン状態記憶部群に格納された前記実行命令群が、同一のレジスタを用いて演算を行う演算実行命令群を表す場合、前記演算実行命令群を1番目から最終番目までの複数のハザード実行命令群に分割し、

前記複数のハザード実行命令群の各々は、同一のレジスタを用いていない命令の組を表し、

前記同時実行条件判定部は、前記パイプライン状態記憶部群に格納された前記演算実行命令群に代えて、前記ハザード実行命令群を前記実行命令群として1番目から最終番目までこの順に前記パイプライン状態記憶部群のうちの1つのパイプライン状態記憶部に格納する、

請求項4又は5に記載のシミュレーション装置。

**【請求項 8】**

複数のパイプライン構造を有するプロセッサの動作をコンピュータを用いて模擬するシミュレーション方法であって、

前記プロセッサ上で実行可能な命令群で構成された解析対象プログラムを読み込んで各命令処理を行う命令処理ステップと、

前記解析対象プログラムが有する命令群のそれぞれが前記複数のパイプラインで同時に処理可能かどうかを判断する同時実行条件判定ステップと、

前記同時実行条件判定部の結果と、実行サイクル数格納部に予め記憶された複数の命令の各々の実行マシンサイクル数に基づいて、前記命令群の実行マシンサイクル数を算出する実行マシンサイクル補正ステップと、

を具備するシミュレーション方法。

**【請求項 9】**

前記同時実行条件判定ステップは、同時実行条件格納ステップに予め記憶された同時実行条件に基づいて、前記解析対象プログラム中の連続する命令群が前記複数のパイプラインで同時に処理可能かどうかを判断し、

前記同時実行条件は、前記複数のパイプラインのそれぞれが処理可能な命令に基づいて定義されている、

請求項8に記載のシミュレーション方法。

**【請求項 10】**

前記実行マシンサイクル補正ステップは、前記命令群のうちの、前記同時実行条件判定ステップによって同時実行可能と判断された実行命令群の実行マシンサイクル数を、前記実行命令群のそれぞれの実行マシンサイクル数の中で最も大きい実行マシンサイクル数とする、

請求項9に記載のシミュレーション方法。

**【請求項 11】**

前記同時実行条件判定ステップは、前記同時実行条件格納部を参照して、1命令ずつ処理される1番目から最終番目までの前記命令群を1番目から最終番目までの複数の前記実行命令群に分割し、前記実行命令群をそれぞれ前記複数のパイプラインに対応する前記パイプライン状態記憶部群に格納し、

前記実行マシンサイクル補正ステップは、前記パイプライン状態記憶部群と実行サイクル数格納部とを参照して、前記実行命令群の実行マシンサイクル数の中から、前記最大実行マシンサイクル数を検索し、前記実行命令群の実行マシンサイクル数を前記最も大きい実行マシンサイクル数である最大実行マシンサイクル数に変更する、

請求項10に記載のシミュレーション方法。

**【請求項 12】**

10

20

30

40

50

前記パイプライン状態記憶部群に格納された実行命令の実行マシンサイクル数の合計値を含む実行結果を出力装置に出力する実行サイクル数計測ステップを更に具備する請求項11に記載のシミュレーション方法。

**【請求項13】**

前記同時実行条件判定ステップは、前記パイプライン状態記憶部群に格納された前記実行命令群が、同一のレジスタを用いて演算を行う演算実行命令群を表す場合、前記演算実行命令群を1番目から最終番目までの複数のハザード実行命令群に分割し、

前記複数のハザード実行命令群の各々は、同一のレジスタを用いていない命令の組を表し、

前記同時実行条件判定ステップは、前記パイプライン状態記憶部群に格納された前記演算実行命令群に代えて、前記ハザード実行命令群を前記実行命令群として1番目から最終番目までこの順に前記パイプライン状態記憶部群のうちの1つのパイプライン状態記憶部に格納する、

請求項11又は12に記載のシミュレーション方法。

**【請求項14】**

コンピュータにインストールされ、複数のパイプライン構造を有するプロセッサの動作を前記コンピュータを用いて模擬するためのコンピュータプログラムであるシミュレーションプログラムであって、

前記プロセッサ上で実行可能な命令群で構成された解析対象プログラムを読み込んで各命令処理を行う命令処理ステップと、

前記解析対象プログラムが有する命令群のそれぞれが前記複数のパイプラインで同時に処理可能かどうかを判断する同時実行条件判定ステップと、

前記同時実行条件判定部の結果と、実行サイクル数格納部に予め記憶された複数の命令の各々の実行マシンサイクル数に基づいて、前記命令群の実行マシンサイクル数を算出する実行マシンサイクル補正ステップと、

の各ステップを前記コンピュータに実行させるシミュレーションプログラム。

**【請求項15】**

前記同時実行条件判定ステップは、同時実行条件格納ステップに予め記憶された同時実行条件に基づいて、前記解析対象プログラム中の連続する命令群が前記複数のパイプラインで同時に処理可能かどうかを判断し、

前記同時実行条件は、前記複数のパイプラインのそれぞれが処理可能な命令に基づいて定義されている、

請求項14に記載のシミュレーションプログラム。

**【請求項16】**

前記実行マシンサイクル補正ステップは、前記命令群のうちの、前記同時実行条件判定ステップによって同時実行可能と判断された実行命令群の実行マシンサイクル数を、前記実行命令群のそれぞれの実行マシンサイクル数の中で最も大きい実行マシンサイクル数とする、

請求項15に記載のシミュレーションプログラム。

**【請求項17】**

前記同時実行条件判定ステップは、前記同時実行条件格納部を参照して、1命令ずつ処理される1番目から最終番目までの前記命令群を1番目から最終番目までの複数の前記実行命令群に分割し、前記実行命令群をそれぞれ前記複数のパイプラインに対応する前記パイプライン状態記憶部群に格納し、

前記実行マシンサイクル補正ステップは、前記パイプライン状態記憶部群と実行サイクル数格納部とを参照して、前記実行命令群の実行マシンサイクル数の中から、前記最大実行マシンサイクル数を検索し、前記実行命令群の実行マシンサイクル数を前記最も大きい実行マシンサイクル数である最大実行マシンサイクル数に変更する、

請求項16に記載のシミュレーションプログラム。

**【請求項18】**

10

20

30

40

50

前記パイプライン状態記憶部群に格納された実行命令の実行マシンサイクル数の合計値を含む実行結果を出力装置に出力する実行サイクル数計測ステップ

を更に前記コンピュータに実行させる請求項17に記載のシミュレーションプログラム。

【請求項19】

前記同時実行条件判定ステップは、前記パイプライン状態記憶部群に格納された前記実行命令群が、同一のレジスタを用いて演算を行う演算実行命令群を表す場合、前記演算実行命令群を1番目から最終番目までの複数のハザード実行命令群に分割し、

前記複数のハザード実行命令群の各々は、同一のレジスタを用いていない命令の組を表し、

前記同時実行条件判定ステップは、前記パイプライン状態記憶部群に格納された前記演算実行命令群に代えて、前記ハザード実行命令群を前記実行命令群として1番目から最終番目までこの順に前記パイプライン状態記憶部群のうちの1つのパイプライン状態記憶部に格納する、

請求項17又は18に記載のシミュレーションプログラム。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、プロセッサの動作をシミュレートするシミュレーション装置、シミュレーション方法及びシミュレーションプログラムに関する。

【背景技術】

【0002】

プロセッサ上で動作させるプログラムの解析やデバックのためにシミュレーション装置が利用されている。シミュレーション装置は、プロセッサの動作と同じ動作か、あるいは、それを簡略化した動作を行うように設計される。このようなシミュレーション装置としては、命令セットシミュレータ(ISS; Instruction Set Simulator)といったものが広く知られている。ISSは、パーソナルコンピュータやワークステーションなどのコンピュータ上で動作し、プロセッサの命令の動作や、その実行結果、レジスタの状態などを模擬するものである。ISSを用いることにより、プログラムの解析やデバックのために専用のハードウェアを用意する必要がないというメリットがある。

【0003】

ISSなどを用いたプログラムの解析においては、プログラムの動作の正当性を表す情報だけでなく、プログラムの実行速度を表す情報が得られると有益である。より具体的には、後者の情報として、プログラム中にある命令の処理にプロセッサが何サイクル要するか、ということである。例えば、特開2001-290857号公報には、パイプライン構造を有するハードウェアと同等の動作を行うシミュレーション手法に関する技術が記載されており、1命令毎の実行におけるパイプラインの状態を命令毎のタイミングテーブルを参照することで、パイプラインを考慮した実行マシンサイクル数を算出している。

【0004】

【特許文献1】特開2001-290857号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

近年のプロセッサでは、命令の処理速度を上げるために、1つのプロセッサ内に複数のパイプラインを有するようになってきた。従って、このようなプロセッサで動作させるプログラムを開発する場合においても、複数のパイプラインを考慮したシミュレーション手法が望まれる。

【0006】

しかしながら、特開2001-290857号公報には、複数のパイプラインを有するプロセッサをシミュレートする技術に関しては何ら記載されていない。複数のパイプラ

10

20

30

40

50

ンを有するプロセッサに対してこの従来技術を適用した場合、個々のパイプラインで実行されるマシンサイクル数を算出することは出来たとしても、複数のパイプラインを組み合わせて動作するプロセッサ全体のマシンサイクル数を算出することは困難である。

#### 【課題を解決するための手段】

##### 【0007】

以下に、[発明を実施するための最良の形態]で使用する番号・符号を用いて、課題を解決するための手段を説明する。これらの番号・符号は、[特許請求の範囲]の記載と[発明を実施するための最良の形態]の記載との対応関係を明らかにするために付加されたものであるが、[特許請求の範囲]に記載されている発明の技術的範囲の解釈に用いてはならない。

10

##### 【0008】

本発明のシミュレーション装置(4)は、複数のパイプライン構造(71、72)を有するプロセッサ(70)の動作を模擬するシミュレーション装置(4)であって、

前記プロセッサ(70)上で実行可能な命令群(“ADD、MOV、SUB、SUB、JMP、LD、LD、ADD、MOV”)で構成された解析対象プログラムを読み込んで各命令処理を行う命令処理部(11)と、

前記解析対象プログラムが有する命令群(“ADD、MOV、SUB、SUB、JMP、LD、LD、ADD、MOV”)のそれぞれが前記複数のパイプライン(71、72)で同時に処理可能かどうかを判断する同時実行条件判定部(31)と、

前記同時実行条件判定部(31)の結果と、実行マシンサイクル数格納部(42)に予め記憶された複数の命令(LD、ADD、SUB、JMP、MOV、...)の各々の実行サイクル数(1、2、2、6、4,...)とに基づいて、前記命令群(“ADD、MOV、SUB、SUB、JMP、LD、LD、ADD、MOV”)の実行マシンサイクル数(“4”)(“2”)(“6”)(“1”)(“2”)(“4”)を算出する実行マシンサイクル補正部(41)と、

20

を具備している。

##### 【発明の効果】

##### 【0009】

以上により、本発明のシミュレーション装置(4)によれば、複数のパイプラインを考慮したプロセッサ(70)の動作をシミュレートすることができる。

30

##### 【0010】

その理由として、本発明のシミュレーション装置(4)では、命令群(“ADD、MOV、SUB、SUB、JMP、LD、LD、ADD、MOV”)に対して、プロセッサ(70)がパイプライン群(71、72)により同時実行可能な命令の組として実行命令群(“ADD、MOV”、“SUB、SUB”、“JMP、\_”、“LD、\_”、“LD、ADD”、“MOV、\_”)を検索し、命令群(“ADD、MOV、SUB、SUB、JMP、LD、LD、ADD、MOV”)が処理される順番を考慮して、実行命令群(“ADD、MOV”、“SUB、SUB”、“JMP、\_”、“LD、\_”、“LD、ADD”、“MOV、\_”)の実行マシンサイクル数(“2、4”、“2、2”、“6、\_”、“1、\_”、“1、2”、“4、\_”)を最大実行マシンサイクル数(“4”、“2”、“6”、“1”、“2”、“4”)に変更する。このように、本発明のシミュレーション装置(4)では、プロセッサ(70)がパイプライン群(71、72)により同時実行可能な実行命令群を検索し、その実行マシンサイクル数を最大実行マシンサイクル数に変更することにより、複数のパイプライン{パイプライン群(71、72)}を考慮したプロセッサ(70)の動作をシミュレートすることができる。

40

##### 【発明を実施するための最良の形態】

##### 【0011】

以下に添付図面を参照して、本発明のシミュレーション装置について詳細に説明する。

##### 【0012】

50

(第1実施形態)

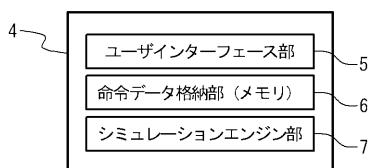

図1は、本発明の第1実施形態によるシミュレーション装置4の構成を示している。そのシミュレーション装置4は、ユーザインターフェース部5と、メモリである命令データ格納部6と、シミュレーションエンジン部(シミュレーションプログラム)7とを具備している。ユーザインターフェース部5は、入力装置による入力、及び、出力装置に出力する制御を行う。命令データ格納部6には、デバック対象のプログラムが格納されている。シミュレーションエンジン部7は、デバック対象のプログラムを命令データ格納部6から読み出し、デバック対象のプログラムに記述されている命令群を処理する。

【0013】

シミュレーションエンジン部7は、コンピュータにインストールされるコンピュータプログラム(シミュレーションプログラム)としても実現可能である。図2は、コンピュータの構成を示している。コンピュータは、入力装置2と、出力装置3と、コンピュータ本体1とを具備している。入力装置2と出力装置3は、コンピュータ本体1に接続されている。入力装置2は、キーボード、ポインティングデバイスを含み、出力装置3は、表示装置、プリンタを含んでいる。

【0014】

上記のコンピュータ本体1は、図示しない記憶装置と、図示しないCPU(Central Processing Unit)とを具備している。シミュレーションエンジン部7は、記憶装置にインストールされる。この場合、命令データ格納部6に格納されたデバック対象のプログラムも記憶装置にインストールされる。シミュレーションエンジン部7(シミュレーションプログラム)は、デバック対象のプログラムを記憶装置から読み出し、デバック対象のプログラムに記述されている命令群をCPU上で処理する。

【0015】

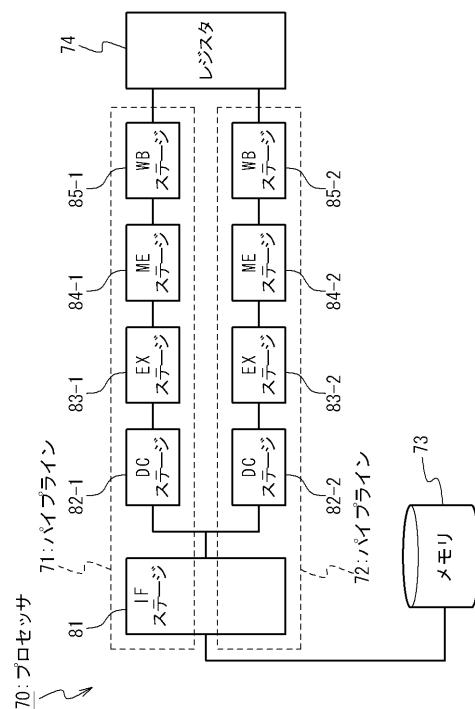

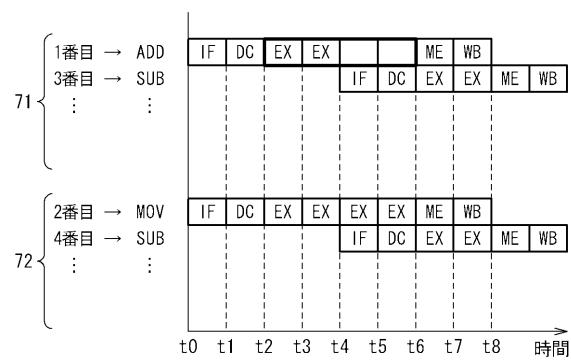

シミュレーションエンジン部7は、プロセッサ上で動作させるプログラムの解析やデバックのためのソフトウェアとして、設計者に利用される。図3は、本発明でシミュレートを実行しようとしているプロセッサ70のパイプライン部分の概略図である。プロセッサ70は、命令群とデータとが格納されたメモリ73と、複数の汎用レジスタを含むレジスタ74と、2つのパイプライン71、72とを具備している。

【0016】

プロセッサ70は、クロックに応じて動作し、更に、命令群をフェッチするIF(命令フェッチ)ステージ81と、フェッチされた命令をデコードするDC(デコード)ステージ82-1、82-2と、デコードされた命令を実行するEX(実行)ステージ83-1、83-2と、命令(メモリアクセス命令)に対してメモリ73のアクセスを行うME(メモリアクセス)ステージ84-1、84-2と、命令の実行結果をレジスタ74に書き込むWB(ライトバック)ステージ85-1、85-2とを具備している。プロセッサ70は、IFステージ81とDCステージ82-1とEXステージ83-1とMEステージ84-1とWBステージ85-1によりパイプライン71を構成し、IFステージ81とDCステージ82-2とEXステージ83-2とMEステージ84-2とWBステージ85-2によりパイプライン72を構成する。

【0017】

プロセッサ70により実行される命令群nは、例えば、“ADD、MOV、SUB、JMP、LD”といったものがあるとする。ニーモニック表記の“LD”、“ADD”、“SUB”、“JMP”、“MOV”は、それぞれ、メモリ73からレジスタ74にデータを書き込むロード命令、加算命令、減算命令、ジャンプ命令、ムーブ命令を表している。プロセッサ70上で動作するプログラムはこれらの命令で構成されることになる。

【0018】

図3に示されるプロセッサ70の場合、2つのパイプライン71、72を具備しているため、フェッチした各命令は2つのパイプライン71、72を使って並列に処理することにより1つのパイプライン71の場合よりも処理速度を上げることができる。ただし、2つのパイプライン71、72により処理される加算器、減算器といった演算器は同じ構成

10

20

20

30

40

50

にはならない場合がある。これは各演算器をパイプラインの数だけ用意してしまうと、処理速度を上げることはできるが、プロセッサ70が巨大になってしまうというデメリットが生じるためである。大型コンピュータに搭載されるプロセッサであれば問題にはならないが、小型コンピュータ用や、家電・車両用のマイコンに搭載されるプロセッサでは、重要な要素となる。具体的には、例えば、命令“LD”、“JMP”、“MOV”を処理するための演算器が一方のパイプライン71にしか配置されていない、というプロセッサ70が想定される。この場合、例えば、プロセッサ70上で動作させようとするプログラム中に、命令“JMP、MOV”という連続する命令があった場合、プロセッサ70は、パイプラインの制約上、これらの命令を2つのパイプライン71、72で並列に実行することはできない。このため、プロセッサ70は、命令“JMP”をパイプライン71で実行した後に、命令“MOV”をパイプライン71で実行するという逐次処理となる。本実施例では、このようなプロセッサ70をシミュレートする場合の手法について述べる。なお、上記の命令“LD”、“JMP”、“MOV”を処理するための演算器が一方のパイプライン71にしか配置されていないプロセッサ70、というものは、単に説明を簡略化するために挙げたものに過ぎない。

10

20

30

40

50

#### 【0019】

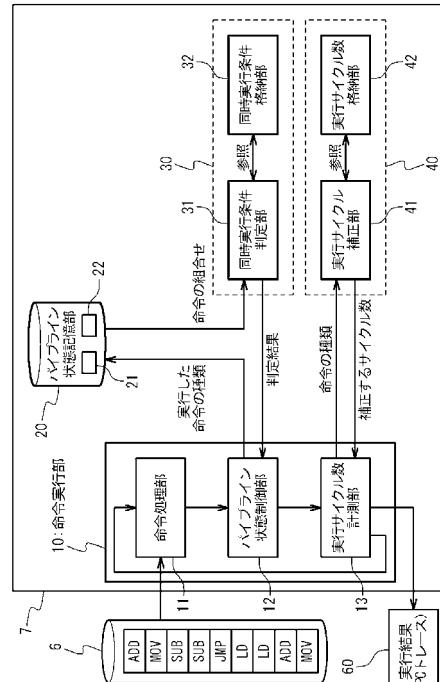

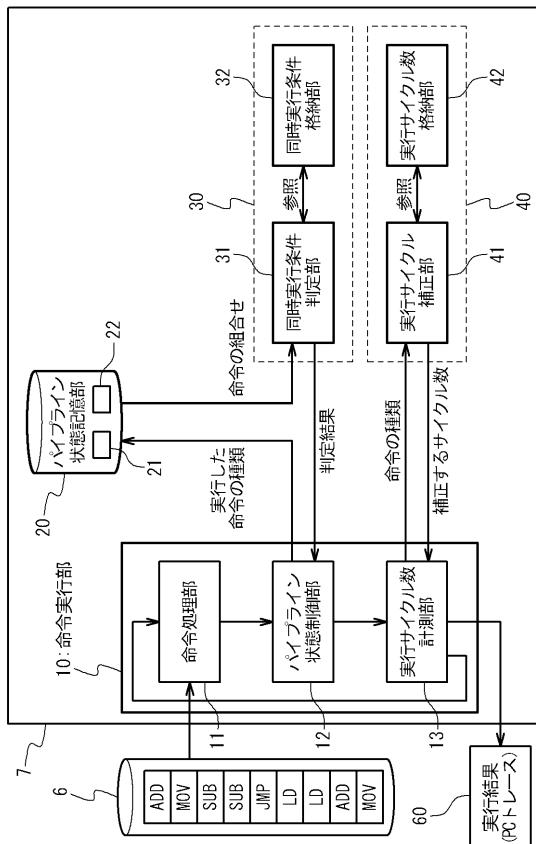

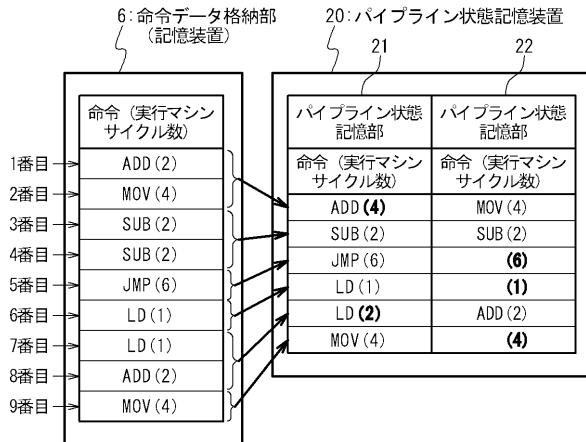

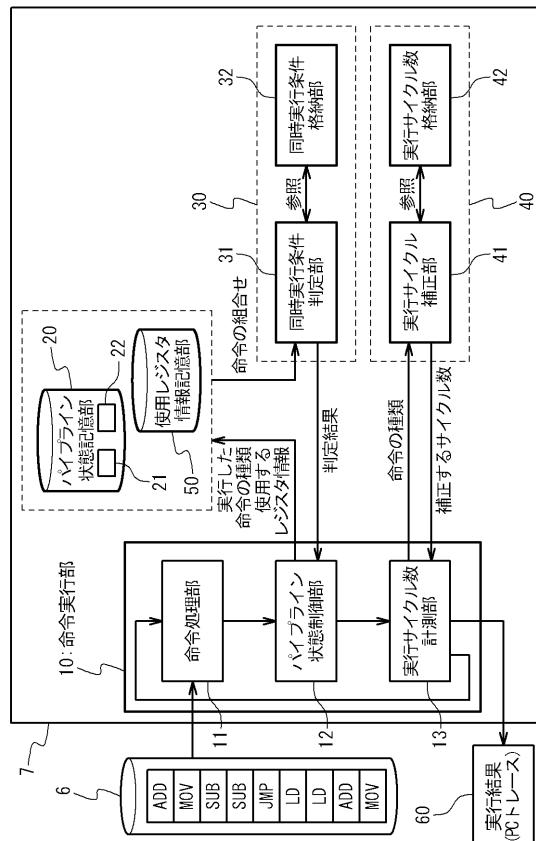

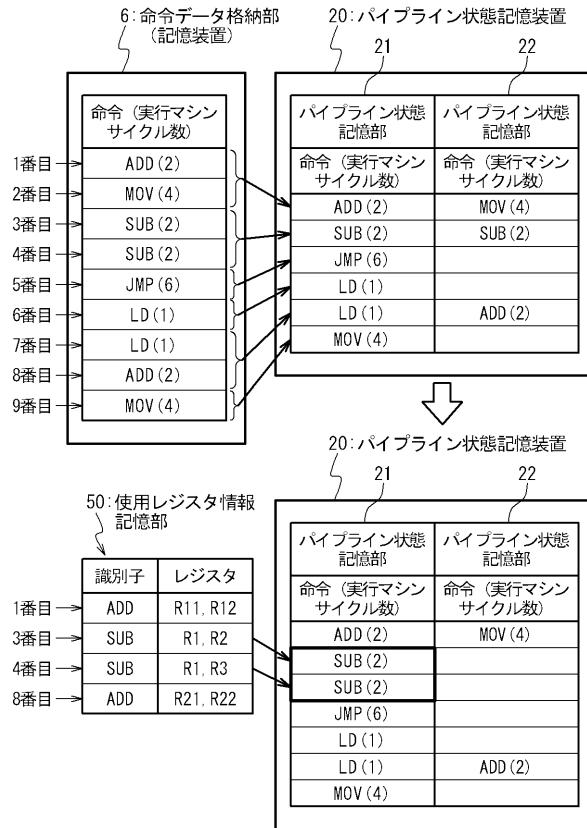

図4は、シミュレーションエンジン部7の構成を示している。シミュレーションエンジン部7は、命令実行部10と、パイプライン状態記憶装置20と、同時実行命令検索部30と、実行サイクル変更部40とを具備している。命令実行部10は、命令処理部11と、パイプライン状態制御部12と、実行サイクル数計測部13とを具備している。パイプライン状態記憶装置20は、パイプライン状態記憶部群21、22を具備している。パイプライン状態記憶部群21、22は、それぞれ、上記のパイプライン群71、72に対応している。同時実行命令検索部30は、同時実行条件判定部31と、同時実行条件格納部32とを具備している。実行サイクル変更部40は、実行サイクル補正部41と、実行サイクル数格納部42とを具備している。命令実行部10において、命令処理部11は、前述のISSが有している機能と同等のものであるため、その説明を省略する。パイプライン状態制御部12と実行サイクル数計測部13は、本発明の特徴部分であり、以下はこれらを中心に説明する。

#### 【0020】

図5は、同時実行条件格納部32を示している。同時実行条件格納部32には、プロセッサ70がパイプライン群71、72により同時実行可能な命令の組を表す同時実行条件が予め格納されている。同時実行条件は、パイプラインの制約として予め決められている。例えば、命令の組として“ADD、MOV”、“LD、MOV”、…と、それに対して同時実行を許可することを表す判定“OK”とが同時実行条件格納部32に格納されている。また、命令の組として“JMP、MOV”、“LD、LD”、…と、それに対して同時実行を許可しないことを表す判定“NG”とが同時実行条件格納部32に格納されている。

#### 【0021】

図6は、実行サイクル数格納部42を示している。実行サイクル数格納部42には、複数の命令と、複数の命令の各々に対してEXステージが実行されるときのマシンサイクル（クロック）の数を表す実行マシンサイクル数とが予め格納されている。例えば、複数の命令として“LD、ADD、SUB、JMP、MOV、…”と、それに対する実行マシンサイクル数として“1、2、2、6、4、…”とが実行サイクル数格納部42に格納されている。ここで、実行マシンサイクル数については、本実施形態を説明する便宜上、実際よりも極端に大きい値を記載している。これらの値は、実際のプロセッサ70の処理速度によって決定される。その決定方法としては、プロセッサ70を用いて予め測定して決定する場合や、プロセッサ70の設計仕様に基づいて予め決定する場合などが挙げられる。

#### 【0022】

命令処理部11は、設計者の入力装置2の操作により、記憶装置（命令データ格納部6に対応）からデバック対象のプログラムを読み出す。図4では、説明の簡略化のためにデ

バック対象のプログラム中の命令群だけを記載しており、デバック対象のプログラムが、“ADD、MOV、SUB、SUB、JMP、LD、LD、ADD、MOV”の順番で命令群を処理するようなプログラムであるものとする。命令処理部11は、記憶装置（命令データ格納部6に対応）から命令群“ADD、MOV、SUB、SUB、JMP、LD、LD、ADD、MOV”を順次読み出して、パイプライン状態制御部12に出力するとともに各命令に応じた処理を実行する。パイプライン状態制御部12は、同時実行可能な命令の組を検索する同時実行命令検索処理を実行させるために、その命令群を同時実行条件判定部31に出力する。

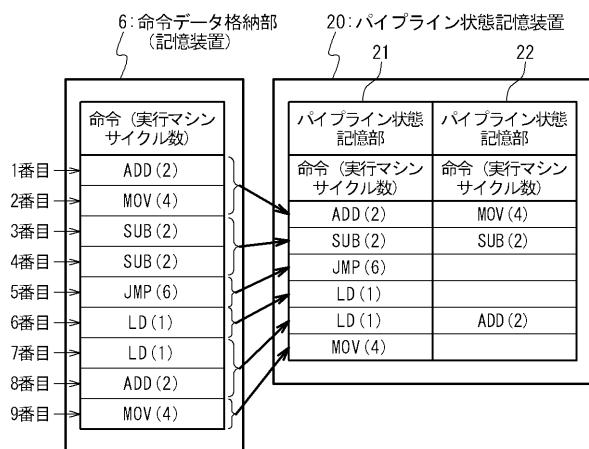

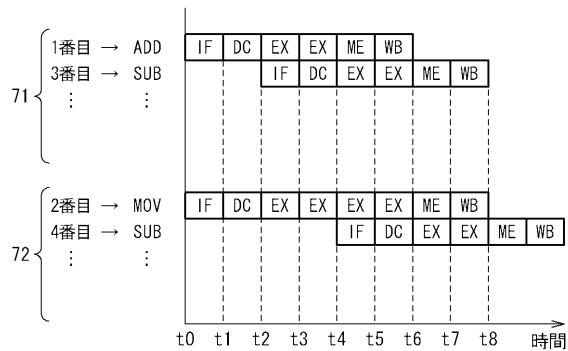

#### 【0023】

同時実行命令検索処理において、図7Aに示されるように、同時実行条件判定部31は、同時実行条件格納部32を参照して、1命令ずつ処理される1番目から最終番目までの命令群“ADD、MOV、SUB、SUB、JMP、LD、LD、ADD、MOV”を1番目から最終番目までの複数の実行命令群“ADD、MOV”、“SUB、SUB”、“JMP、\_\_”、“LD、\_\_”、“LD、ADD”、“MOV、\_\_”に分割する。“\_\_”は、同時実行条件により実行されない命令を表している。複数の実行命令群“ADD、MOV”、“SUB、SUB”、“JMP、\_\_”、“LD、\_\_”、“LD、ADD”、“MOV、\_\_”の各々は、プロセッサ70がパイプライン群71、72により同時実行可能な命令の組を表している。同時実行条件判定部31は、1番目から最終番目までこの順に実行命令群“ADD、MOV”、“SUB、SUB”、“JMP、\_\_”、“LD、\_\_”、“LD、ADD”、“MOV、\_\_”をパイプライン状態記憶装置20に格納する。このとき、同時実行条件判定部31は、実行命令群“ADD、MOV”、“SUB、SUB”、“JMP、\_\_”、“LD、\_\_”、“LD、ADD”、“MOV、\_\_”をそれぞれパイプライン状態記憶部群21、22に格納し、同時実行命令検索処理の終了をパイプライン状態制御部12に通知する。

#### 【0024】

実行命令群“ADD、MOV”、“SUB、SUB”、“JMP、\_\_”、“LD、\_\_”、“LD、ADD”、“MOV、\_\_”の実行マシンサイクル数は、それぞれ、“2、4”、“2、2”、“6、\_\_”、“1、\_\_”、“1、2”、“4、\_\_”である。例えば、実行命令群“ADD、MOV”、“SUB、SUB”、“JMP、\_\_”、“LD、\_\_”、“LD、ADD”、“MOV、\_\_”に対して、それぞれプロセッサ70のパイプライン群71、72によってIFステージ81、DCステージ82-1、82-2、EXステージ83-1、83-2、MEステージ84-1、84-2、WBステージ85-1、85-2が実行される。このとき、プロセッサ70が1番目の実行命令“ADD”と2番目の実行命令“MOV”とを同時実行した場合、実行命令“ADD”、“MOV”に対してEXステージ83-1、83-2が実行されるときの実行マシンサイクル数は“2”、“4”である。図7Bに示されるように、1番目の実行命令“ADD”と2番目の実行命令“MOV”が実行されるときの時間をt0とした場合、2番目の実行命令“MOV”が実行されているときに、時間t6において1番目の実行命令“ADD”的実行が先に終了し、時間t8において2番目の実行命令“MOV”と3番目の実行命令“SUB”的実行が同時に終了する。即ち、1命令ずつ処理される1番目から最終番目までの命令群“ADD、MOV、SUB、SUB、JMP、LD、LD、ADD、MOV”に対して、3番目の実行命令“SUB”が2番目の実行命令“MOV”よりも先に実行されてしまう可能性がある。そこで、実行マシンサイクル数を補正する必要がある。

#### 【0025】

パイプライン状態制御部12は、実行マシンサイクル数を補正する実行サイクル検索処理を実行させるために、パイプライン状態記憶部群21、22に格納された実行命令群“ADD、MOV”、“SUB、SUB”、“JMP、\_\_”、“LD、\_\_”、“LD、ADD”、“MOV、\_\_”を読み出し、実行サイクル数計測部13に出力する。実行サイクル数計測部13は、その実行命令群を実行サイクル補正部41に出力する。

#### 【0026】

10

20

30

40

50

実行サイクル検索処理において、実行サイクル補正部41は、実行サイクル数計測部13からの実行命令群“ADD、MOV”、“SUB、SUB”、“JMP、\_\_”、“LD、\_\_”、“LD、ADD”、“MOV、\_\_”を受け取る。又は、実行サイクル補正部41は、実行サイクル検索処理を実行させる通知を実行サイクル数計測部13から受け取ったとき、パイプライン状態記憶部群21、22を参照してもよい。実行サイクル補正部41は、実行マシンサイクル数格納部42を参照して、パイプライン群71、72によって実行される実行命令群“ADD、MOV”、“SUB、SUB”、“JMP、\_\_”、“LD、\_\_”、“LD、ADD”、“MOV、\_\_”の実行マシンサイクル数“2、4”、“2、2”、“6、\_\_”、“1、\_\_”、“1、2”、“4、\_\_”の中から、最も大きい実行マシンサイクル数である最大実行マシンサイクル数“4”、“2”、“6”、“1”、“2”、“4”を検索する。検索の結果、図8Bに示されるように、実行マシンサイクル補正部41は、実行命令群“ADD、MOV”、“SUB、SUB”、“JMP、\_\_”、“LD、\_\_”、“LD、ADD”、“MOV、\_\_”の実行マシンサイクル数“2、4”、“2、2”、“6、\_\_”、“1、\_\_”、“1、2”、“4、\_\_”を最大実行マシンサイクル数“4”、“2”、“6”、“1”、“2”、“4”に変更する。実行マシンサイクル補正部41は、その最大実行マシンサイクル数“4”、“2”、“6”、“1”、“2”、“4”を命令実行部10に出力し、実行サイクル検索処理の終了を通知する。

10

## 【0027】

このとき、図8Aに示されるように、命令実行部10のパイプライン状態制御部12は、パイプライン状態記憶部群21、22に格納された実行命令群“ADD、MOV”、“SUB、SUB”、“JMP、\_\_”、“LD、\_\_”、“LD、ADD”、“MOV、\_\_”の実行マシンサイクル数“2、4”、“2、2”、“6、\_\_”、“1、\_\_”、“1、2”、“4、\_\_”を最大実行マシンサイクル数“4”、“2”、“6”、“1”、“2”、“4”に更新し、命令実行部10の実行サイクル数計測部13に出力する。

20

## 【0028】

実行サイクル数計測部13は、図9に示されるような実行結果60を出力装置3に出力する。実行結果60は、パイプライン状態記憶部群21、22に格納された実行命令“ADD、SUB、JMP、LD、LD、MOV”、“MOV、SUB、\_\_、\_\_、ADD、\_\_”と、その実行マシンサイクル数“4、2、6、1、2、4”的合計値“19”を含んでいる。この場合、命令群“ADD、MOV、SUB、SUB、JMP、LD、LD、ADD、MOV”的実行マシンサイクル数“2、4、2、2、6、1、1、2、4”的合計値“24”よりも小さい。また、1クロックの周期を10[nsec]とした場合、上記の合計値“19”は、処理時間[nsec]に対応し、実行命令“ADD、SUB、JMP、LD、LD、MOV”、“MOV、SUB、\_\_、\_\_、ADD、\_\_”に対する処理時間[nsec]は、“40、60、120、130、150、190”[nsec]により表される。ここで、1クロックの周期については、本実施形態を説明する便宜上、実際よりも極端に大きい値を記載している。

30

## 【0029】

プロセッサ70では、命令の処理速度を上げるために、1つのプロセッサ70内に複数のパイプラインとしてパイプライン群71、72を有している。従って、このようなプロセッサ70で動作させるプログラムを開発する場合においても、パイプライン群71、72を考慮したシミュレーション手法が望まれる。しかしながら、パイプライン群71、72がまったく同じ構成ではなく、それぞれのパイプライン71、72に実装されている演算器が異なる場合は、特開2001-290857号公報に記載されている技術を単純にパイプライン群71、72に適用することは困難である。

40

## 【0030】

そこで、本発明の第1実施形態によるシミュレーション装置4では、命令群“ADD、MOV、SUB、SUB、JMP、LD、LD、ADD、MOV”に対して、プロセッサ70がパイプライン群71、72により同時実行可能な命令の組として実行命令群“ADD、MOV”、“SUB、SUB”、“JMP、\_\_”、“LD、\_\_”、“LD、ADD”

50

、 “MOV、\_”を検索し、命令群“ADD、MOV、SUB、SUB、JMP、LD、LD、ADD、MOV”が処理される順番を考慮して、実行命令群“ADD、MOV”、“SUB、SUB”、“JMP、\_”、“LD、\_”、“LD、ADD”、“MOV、\_”の実行マシンサイクル数“2、4”、“2、2”、“6、\_”、“1、\_”、“1、2”、“4、\_”を最大実行マシンサイクル数“4”、“2”、“6”、“1”、“2”、“4”に変更する。このように、本発明の第1実施形態によるシミュレーション装置4では、プロセッサ70がパイプライン群71、72により同時実行可能な実行命令群を検索し、その実行マシンサイクル数を最大実行マシンサイクル数に変更することにより、複数のパイプライン（パイプライン群71、72）を考慮したプロセッサ70の動作をシミュレートすることができる。

10

## 【0031】

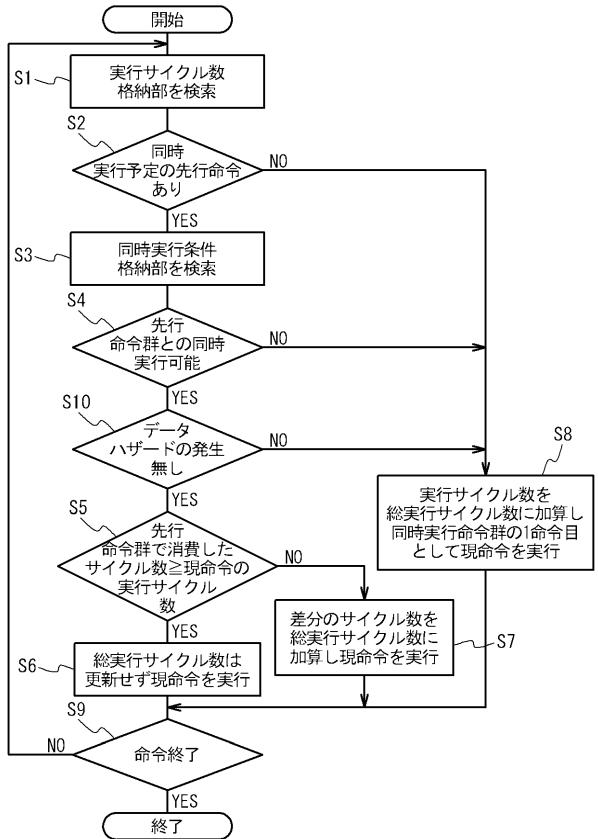

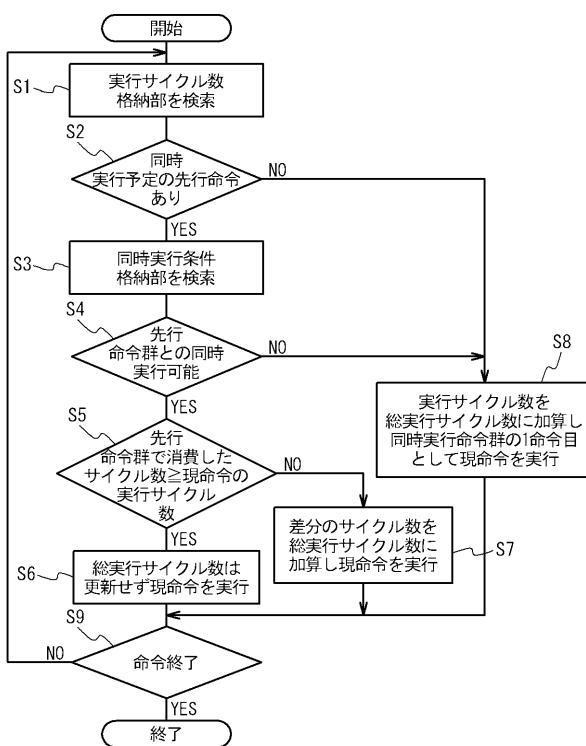

図10は、シミュレーションエンジン部7の動作を示すフローチャートである。

## 【0032】

まず、命令処理部11は、1番目の命令“ADD”を命令データ格納部6から読み出す。同時に、実行サイクル数計測部13は、実行サイクル数格納部42を参照して、1番目の命令“ADD”的実行マシンサイクル数“2”を取得するように、実行サイクル補正部41を制御する（ステップS1）。パイプライン状態制御部12は、同時実行命令検索処理として、1番目の命令“ADD”をパイプライン状態記憶部群21の1レコード目に格納するように、同時実行条件判定部31を制御する（ステップS2-N0）。このとき、実行サイクル数計測部13は、実行結果60として、1番目の命令“ADD”的実行マシンサイクル数“2”を、1番目の実行命令群の総実行マシンサイクル数“0”に加算する（ステップS8）。

20

## 【0033】

次に、命令処理部11は、2番目の命令“MOV”を命令データ格納部6から読み出す（ステップS9-N0）。同時に、実行サイクル数計測部13は、実行サイクル数格納部42を参照して、2番目の命令“MOV”的実行マシンサイクル数“4”を取得するように、実行サイクル補正部41を制御する（ステップS1）。ここで、パイプライン状態記憶部群21の1レコード目には、1番目の命令“ADD”が格納されている（ステップS2-YE5）。パイプライン状態制御部12は、同時実行命令検索処理として、同時実行条件格納部32を参照するように、同時実行条件判定部31を制御する（ステップS3）。検索の結果、1番目の命令（先行命令群）“ADD”と2番目の命令“MOV”は、同時実行可能である（ステップS4-YE5）。この場合、同時実行条件判定部31は、1番目の実行命令群“ADD、MOV”として、パイプライン状態記憶部群21に格納された1番目の命令“ADD”に対応付けて、2番目の命令“MOV”をパイプライン状態記憶部群21の1レコード目に格納する。1番目の命令（先行命令群）“ADD”的実行マシンサイクル数“2”は、2番目の命令（現命令）“MOV”的実行マシンサイクル数“4”よりも小さい（ステップS5-N0）。即ち、2番目の命令“MOV”的実行マシンサイクル数“4”は、最大実行マシンサイクル数“4”となる。このとき、実行サイクル数計測部13は、実行サイクル検索処理として、1番目の命令“ADD”的実行マシンサイクル数“2”を最大実行マシンサイクル数“4”に変更するように、実行マシンサイクル補正部41を制御する。同時に、実行サイクル数計測部13は、実行結果60として、最大実行マシンサイクル数“4”と1番目の命令“ADD”的実行マシンサイクル数“2”との差分“2”を、1番目の実行命令群“ADD、MOV”的総実行マシンサイクル数“2”に加算する（ステップS7）。

30

## 【0034】

一方、先行命令群の実行マシンサイクル数は、現命令の実行マシンサイクル数以上である（ステップS5-YE5）。この場合、実行マシンサイクル補正部41は、先行命令群の実行マシンサイクル数を変更しない。同時に、実行サイクル数計測部13は、実行結果60として、先行命令群と現命令とを含む実行命令群の総実行マシンサイクル数を更新しない（ステップS6）。

40

50

## 【0035】

シミュレーションエンジン部7は、1番目から最終番目(9番目)の命令“ADD、MOV、SUB、SUB、JMP、LD、LD、ADD、MOV”が終了するまで(ステップS9-YES)、上記の動作を実行する。

## 【0036】

以上の説明により、本発明の第1実施形態によるシミュレーション装置4では、プロセッサ70がパイプライン群71、72により同時実行可能な実行命令群を検索し、その実行マシンサイクル数を最大実行マシンサイクル数に変更することにより、複数のパイプライン(パイプライン群71、72)を考慮したプロセッサ70の動作をシミュレートすることができる。

10

## 【0037】

## (第2実施形態)

本発明の第2実施形態によるシミュレーション装置4では、第1実施形態と重複する説明を省略する。

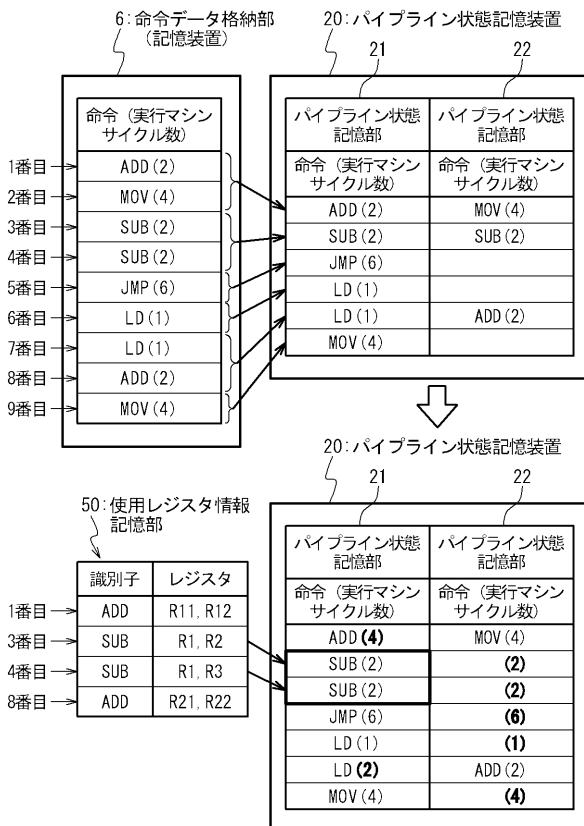

## 【0038】

図11は、シミュレーションエンジン部7の構成を示している。シミュレーションエンジン部7は、更に、使用レジスタ情報記憶部50を具備している。

## 【0039】

図12は、使用レジスタ情報記憶部50を示している。使用レジスタ情報記憶部50には、演算命令を識別する識別子と、各演算命令を実行するときに用いるレジスタ名とが格納されている。レジスタ名は、シミュレート対象のプロセッサ70が備えているレジスタ74であり、デバッグ対象のプログラムで各演算命令を実行するときに用いるものである。例えば、デバッグ対象のプログラムが命令“ADD、MOV、SUB、SUB、JMP、LD、LD、ADD、MOV”という様に構成されている場合に、“ADD、SUB、SUB、ADD”の演算が“ADD R11、R12 (R11=R11+R12の意味)、SUB R1、R2 (R1=R1-R2の意味)、SUB R3、R1 (R3=R3-R1の意味)、ADD R21、R22 (R21=R21+R22の意味)”となっている場合、それぞれの演算を識別する識別子とレジスタ名が使用レジスタ情報記憶部50に格納される。

20

## 【0040】

命令処理部11は、設計者の入力装置2の操作により、命令群“ADD、MOV、SUB、SUB、JMP、LD、LD、ADD、MOV”を記憶装置(命令データ格納部6に対応)から読み出して、パイプライン状態制御部12に出力するとともに、各命令で使用するレジスタ名と各命令を識別するための識別子とを使用レジスタ情報記憶部50に出力する。パイプライン状態制御部12は、同時実行可能な命令の組を検索する同時実行命令検索処理を実行させるために、その命令群を同時実行条件判定部31に出力する。

30

## 【0041】

同時実行命令検索処理において、図13に示されるように、同時実行条件判定部31は、同時実行条件格納部32を参照して、1命令ずつ処理される1番目から最終番目までの命令群“ADD、MOV、SUB、SUB、JMP、LD、LD、ADD、MOV”を1番目から最終番目までの複数の実行命令群“ADD、MOV”、“SUB、SUB”、“JMP、\_”、“LD、\_”、“LD、ADD”、“MOV、\_”に分割する。“\_”は、同時実行条件により実行されない命令を表している。複数の実行命令群“ADD、MOV”、“SUB、SUB”、“JMP、\_”、“LD、\_”、“LD、ADD”、“MOV、\_”の各々は、プロセッサ70がパイプライン群71、72により同時実行可能な命令の組を表している。同時実行条件判定部31は、1番目から最終番目までこの順に実行命令群“ADD、MOV”、“SUB、SUB”、“JMP、\_”、“LD、\_”、“LD、ADD”、“MOV、\_”をパイプライン状態記憶装置20に格納する。このとき、同時実行条件判定部31は、実行命令群“ADD、MOV”、“SUB、SUB”、“JMP、\_”、“LD、\_”、“LD、ADD”、“MOV、\_”をそれぞれパイプライン

40

50

状態記憶部群 21、22 に格納する。

#### 【0042】

次に、同時実行条件判定部 31 は、パイプライン状態記憶部群 21、22 と使用レジスタ情報記憶部 50 を参照して、実行命令群 “ADD、MOV”、“SUB、SUB”、“JMP、\_\_”、“LD、\_\_”、“LD、ADD”、“MOV、\_\_”が、同一のレジスタを用いて演算を行う演算実行命令群であるか否かを検索する。検索の結果、実行命令群 “SUB、SUB” が、同一のレジスタ “R1” を用いて演算 “R1 = R1 - R2”、“R3 = R3 - R1” を行う演算実行命令群である。即ち、演算実行命令群 “SUB、SUB” は、同一のレジスタ “R1” を用いるため、同時に実行することができない。この同一のレジスタを用いることにより同時に実行することができない命令をハザード実行命令と呼ぶ。10

#### 【0043】

そこで、図 13 に示されるように、同時実行条件判定部 31 は、演算実行命令群 “SUB、SUB” を 1 番目から最終番目までの複数のハザード実行命令群 “SUB、\_\_”、“SUB、\_\_” に分割する。複数のハザード実行命令群 “SUB、\_\_”、“SUB、\_\_” の各々は、同一のレジスタ “R1” を用いていない命令の組を表し、“\_\_” は、同時実行条件により実行されない命令を表している。同時実行条件判定部 31 は、パイプライン状態記憶部群 21、22 に格納された演算実行命令群 “SUB、SUB” に代えて、ハザード実行命令群 “SUB、\_\_”、“SUB、\_\_” を実行命令群として 1 番目から最終番目までこの順にパイプライン状態記憶部群 21、22 のうちの 1 つのパイプライン状態記憶部（例えばパイプライン状態記憶部 21）に格納する。この場合、パイプライン状態記憶部群 21、22 には、実行命令群として、“ADD、MOV”、“SUB、\_\_”、“SUB、\_\_”、“JMP、\_\_”、“LD、\_\_”、“LD、ADD”、“MOV、\_\_” が格納されている。同時実行条件判定部 31 は、同時実行命令検索処理の終了をパイプライン状態制御部 12 に通知する。20

#### 【0044】

パイプライン状態制御部 12 は、実行マシンサイクル数を補正する実行サイクル検索処理を実行させるために、パイプライン状態記憶部群 21、22 に格納された実行命令群 “ADD、MOV”、“SUB、\_\_”、“SUB、\_\_”、“JMP、\_\_”、“LD、\_\_”、“LD、ADD”、“MOV、\_\_” を読み出し、実行サイクル数計測部 13 に出力する。実行サイクル数計測部 13 は、その実行命令群を実行サイクル補正部 41 に出力する。30

#### 【0045】

実行サイクル検索処理において、実行サイクル補正部 41 は、実行サイクル数計測部 13 からの実行命令群 “ADD、MOV”、“SUB、\_\_”、“SUB、\_\_”、“JMP、\_\_”、“LD、\_\_”、“LD、ADD”、“MOV、\_\_” を受け取る。又は、実行サイクル補正部 41 は、実行サイクル検索処理を実行させる通知を実行サイクル数計測部 13 から受け取ったとき、パイプライン状態記憶部群 21、22 を参照してもよい。実行サイクル補正部 41 は、実行マシンサイクル数格納部 42 を参照して、パイプライン群 71、72 によって実行される実行命令群 “ADD、MOV”、“SUB、\_\_”、“SUB、\_\_”、“JMP、\_\_”、“LD、\_\_”、“LD、ADD”、“MOV、\_\_” の実行マシンサイクル数 “2、4”、“2、\_\_”、“2、\_\_”、“6、\_\_”、“1、\_\_”、“1、2”、“4、\_\_” の中から、最も大きい実行マシンサイクル数である最大実行マシンサイクル数 “4”、“2”、“2”、“6”、“1”、“2”、“4” を検索する。検索の結果、実行マシンサイクル補正部 41 は、実行命令群 “ADD、MOV”、“SUB、\_\_”、“SUB、\_\_”、“JMP、\_\_”、“LD、\_\_”、“LD、ADD”、“MOV、\_\_” の実行マシンサイクル数 “2、4”、“2、\_\_”、“2、\_\_”、“6、\_\_”、“1、\_\_”、“1、2”、“4、\_\_” を最大実行マシンサイクル数 “4”、“2”、“2”、“6”、“1”、“2”、“4” に変更する。実行マシンサイクル補正部 41 は、その最大実行マシンサイクル数 “4”、“2”、“2”、“6”、“1”、“2”、“4” を命令実行部 10 に出力し、実行サイクル検索処理の終了を通知する。4050

## 【0046】

このとき、図14に示されるように、命令実行部10のパイプライン状態制御部12は、パイプライン状態記憶部群21、22に格納された実行命令群“ADD、MOV”、“SUB、\_\_”、“SUB、\_\_”、“JMP、\_\_”、“LD、\_\_”、“LD、ADD”、“MOV、\_\_”の実行マシンサイクル数“2、4”、“2、\_\_”、“2、\_\_”、“6、\_\_”、“1、\_\_”、“1、2”、“4、\_\_”を最大実行マシンサイクル数“4”、“2”、“2”、“6”、“1”、“2”、“4”に更新し、命令実行部10の実行サイクル数計測部13に出力する。

## 【0047】

実行サイクル数計測部13は、図15に示されるような実行結果60を出力装置3に出力する。実行結果60は、パイプライン状態記憶部群21、22に格納された実行命令“ADD、SUB、SUB、JMP、LD、LD、MOV”、“MOV、\_\_、\_\_、\_\_、\_\_、ADD、\_\_”と、その実行マシンサイクル数“4、2、2、6、1、2、4”的合計値“21”を含んでいる。この場合、命令群“ADD、MOV、SUB、SUB、JMP、LD、LD、ADD、MOV”的実行マシンサイクル数“2、4、2、2、6、1、1、2、4”的合計値“24”よりも小さい。また、1クロックの周期を10[nsec]とした場合、上記の合計値“21”は、処理時間[nsec]に対応し、実行命令“ADD、SUB、SUB、JMP、LD、LD、MOV”、“MOV、\_\_、\_\_、\_\_、\_\_、ADD、\_\_”に対する処理時間[nsec]は、“40、60、120、130、150、190”[nsec]により表される。ここで、1クロックの周期については、本実施形態を説明する便宜上、実際よりも極端に大きい値を記載している。

## 【0048】

本発明の第2実施形態によるシミュレーション装置4では、命令群“ADD、MOV、SUB、SUB、JMP、LD、LD、ADD、MOV”に対して、プロセッサ70がパイプライン群71、72により同時実行可能な命令の組として実行命令群“ADD、MOV”、“SUB、SUB”、“JMP、\_\_”、“LD、\_\_”、“LD、ADD”、“MOV、\_\_”を検索する。上述のように、順番の規定があり、実行命令群“SUB、SUB”が、同一のレジスタ“R1”を用いて演算“R1 = R1 - R2”、“R3 = R3 - R1”を行う場合、同時に実行することができない。

## 【0049】

そこで、本発明の第2実施形態によるシミュレーション装置4では、実行命令群（演算実行命令群）“SUB、SUB”に対して同一のレジスタ“R1”を用いていない命令の組として実行命令群（ハザード実行命令群）“SUB、\_\_”、“SUB、\_\_”を検索する。シミュレーション装置4は、命令群“ADD、MOV、SUB、SUB、JMP、LD、LD、ADD、MOV”が処理される順番を考慮して、実行命令群“ADD、MOV”、“SUB、\_\_”、“SUB、\_\_”、“JMP、\_\_”、“LD、\_\_”、“LD、ADD”、“MOV、\_\_”の実行マシンサイクル数“2、4”、“2、\_\_”、“2、\_\_”、“6、\_\_”、“1、\_\_”、“1、2”、“4、\_\_”を最大実行マシンサイクル数“4”、“2”、“2”、“6”、“1”、“2”、“4”に変更する。このように、本発明の第2実施形態によるシミュレーション装置4では、プロセッサ70がパイプライン群71、72により実行命令群と、同一のレジスタ“R1”を用いていない実行命令群とを検索し、その実行マシンサイクル数を最大実行マシンサイクル数に変更することにより、複数のパイプライン（パイプライン群71、72）を考慮したプロセッサ70の動作をシミュレートすることができる。

## 【0050】

図16は、シミュレーションエンジン部7の動作を示すフローチャートである。

## 【0051】

例えば、1番目の実行命令群“ADD、MOV”として、パイプライン状態記憶部群21の1レコード目に1番目の命令“ADD”が格納され、パイプライン状態記憶部群21の1レコード目に2番目の命令“MOV”が格納されている。

10

20

30

40

50

## 【0052】

次に、命令処理部11は、3番目の命令“SUB”を命令データ格納部6から読み出す(ステップS9-N0)。同時に、実行サイクル数計測部13は、実行サイクル数格納部42を参照して、3番目の命令“SUB”的実行マシンサイクル数“2”を取得するように、実行サイクル補正部41を制御する(ステップS1)。パイプライン状態制御部12は、同時実行命令検索処理として、3番目の命令“SUB”をパイプライン状態記憶部群21の2レコード目に格納するように、同時実行条件判定部31を制御する(ステップS2-N0)。このとき、実行サイクル数計測部13は、実行結果60として、3番目の命令“SUB”的実行マシンサイクル数“2”を、2番目の実行命令群の総実行マシンサイクル数“0”に加算する(ステップS8)。

10

## 【0053】

次に、命令処理部11は、4番目の命令“SUB”を命令データ格納部6から読み出す(ステップS9-N0)。同時に、実行サイクル数計測部13は、実行サイクル数格納部42を参照して、4番目の命令“SUB”的実行マシンサイクル数“2”を取得するように、実行サイクル補正部41を制御する(ステップS1)。ここで、パイプライン状態記憶部群21の2レコード目には、3番目の命令“SUB”が格納されている(ステップS2-YE5)。パイプライン状態制御部12は、同時実行命令検索処理として、同時実行条件格納部32を参照するように、同時実行条件判定部31を制御する(ステップS3)。検索の結果、3番目の命令(先行命令群)“SUB”と2番目の命令“SUB”は、同時実行可能である(ステップS4-YE5)。この場合、同時実行条件判定部31は、2番目の実行命令群“SUB、SUB”として、パイプライン状態記憶部群21に格納された3番目の命令“SUB”に対応付けて、4番目の命令“SUB”をパイプライン状態記憶部群21の2レコード目に格納する。

20

## 【0054】

この同時実行命令検索処理において、同時実行条件判定部31は、パイプライン状態記憶部群21、22と使用レジスタ情報記憶部50とを参照して、3番目の命令(先行命令群)“SUB”と4番目の命令(現命令)“SUB”とが同一のレジスタを用いて演算を行うか否かを検索する(ステップS10)。検索の結果、3番目の命令“SUB”と4番目の命令“SUB”は、同一のレジスタ“R1”を用いて演算“R1=R1-R2”、“R3=R3-R1”を行うため、同時に実行することができない(ステップS10-N0)。この場合、同時実行条件判定部31は、パイプライン状態記憶部群21、22の2レコード目に格納された実行命令群“SUB、SUB”に代えて、2番目の実行命令群“SUB、\_”として、3番目の命令“SUB”をパイプライン状態記憶部群21の2レコード目に格納し、3番目の実行命令群“SUB、\_”として、4番目の命令“SUB”をパイプライン状態記憶部群21の3レコード目に格納する。このとき、実行サイクル数計測部13は、実行結果60として、4番目の命令“SUB”的実行マシンサイクル数“2”を、3番目の実行命令群の総実行マシンサイクル数“0”に加算する(ステップS8)。

30

## 【0055】

一方、先行命令群と現命令とが同一のレジスタを用いて演算を行わない場合(ステップS10-YE5)、上記のステップS5以降が実行される。

40

## 【0056】

以上の説明により、本発明の第2実施形態によるシミュレーション装置4では、プロセッサ70がパイプライン群71、72により同時実行可能な実行命令群と、同一のレジスタ“R1”を用いていない実行命令群とを検索し、その実行マシンサイクル数を最大実行マシンサイクル数に変更することにより、複数のパイプライン(パイプライン群71、72)を考慮したプロセッサ70の動作をシミュレートすることができる。

## 【0057】

本発明の第1及び第2実施形態では、その特徴を明確に説明するために2つのパイプライン間で同時に実行できない命令がある場合について説明したが、シミュレートする対象のプロセッサが複数のパイプラインを有し、各パイプライン間で同時に実行できない命令

50

がない場合であっても、すなわち、同時実行条件にNGのものがなくても、問題なく処理できることは言うまでもない。

【図面の簡単な説明】

【0058】

【図1】図1は、本発明のシミュレーション装置4の構成を示している。（第1実施形態、第2実施形態）

【図2】図2は、コンピュータの構成を示している。（第1実施形態、第2実施形態）

【図3】図3は、本発明でシミュレートを実行しようとしているプロセッサ70のパイプライン部分の概略図を示している。

【図4】図4は、シミュレーションエンジン部7の構成を示している。（第1実施形態）

【図5】図5は、同時実行条件格納部32を示している。（第1実施形態、第2実施形態）

【図6】図6は、実行サイクル数格納部42を示している。（第1実施形態、第2実施形態）

【図7A】図7Aは、本発明のシミュレーション装置4の動作を説明するための図である。（第1実施形態）

【図7B】図7Bは、本発明のシミュレーション装置4の動作を説明するための図である。（第1実施形態）

【図8A】図8Aは、本発明のシミュレーション装置4の動作を説明するための図である。（第1実施形態）

【図8B】図8Bは、本発明のシミュレーション装置4の動作を説明するための図である。（第1実施形態）

【図9】図9は、実行結果60を示している。（第1実施形態）

【図10】図10は、シミュレーションエンジン部7の動作を示すフローチャートである。（第1実施形態）

【図11】図11は、シミュレーションエンジン部7の構成を示している。（第2実施形態）

【図12】図12は、使用レジスタ情報記憶部50を示している。（第2実施形態）

【図13】図13は、本発明のシミュレーション装置4の動作を説明するための図である。（第2実施形態）

【図14】図14は、本発明のシミュレーション装置4の動作を説明するための図である。（第2実施形態）

【図15】図15は、実行結果60を示している。（第2実施形態）

【図16】図16は、シミュレーションエンジン部7の動作を示すフローチャートである。（第2実施形態）

【符号の説明】

【0059】

1 コンピュータ本体、

2 入力装置、

3 出力装置、

4 シミュレーション装置、

5 ユーザインターフェース部、

6 命令データ格納部、

7 シミュレーションエンジン部、

10 命令実行部、

11 命令処理部、

12 パイプライン状態制御部、

13 実行サイクル数計測部、

20 パイプライン状態記憶装置、

21、22 パイプライン状態記憶部、

10

20

30

40

50

3 0 同時実行命令検索部、

3 1 同時実行条件判定部、

3 2 同時実行条件格納部、

4 0 実行サイクル変更部、

4 1 実行サイクル補正部、

4 2 実行サイクル数格納部、

5 0 使用レジスタ情報記憶部、

6 0 実行結果、

7 0 プロセッサ、

7 1 、 7 2 パイプライン、

7 3 メモリ、

7 4 レジスタ、

8 1 I F (命令フェッチ)ステージ、

8 2 - 1 、 8 2 - 2 D C (デコード)ステージ、

8 3 - 1 、 8 3 - 2 E X (実行)ステージ、

8 4 - 1 、 8 4 - 2 M E (メモリアクセス)ステージ、

8 5 - 1 、 8 5 - 2 W B (ライトバック)ステージ、

10

【図 1】

【図 2】

【図 3】

【図4】

【図5】

32

| 同時実行条件 |     |

|--------|-----|

| 命令の組   | 判定  |

| ADD    | MOV |

| LD     | MOV |

| ...    | ... |

| JMP    | MOV |

| LD     | LD  |

| ...    | ... |

【図6】

42

| 命令  | 実行サイクル数 |

|-----|---------|

| LD  | 1       |

| ADD | 2       |

| SUB | 2       |

| JMP | 6       |

| MOV | 4       |

| ... | ...     |

【図7A】

【図7B】

【図 8 A】

【図 8 B】

【図 9】

60

| 処理時間 [nsec] | パイプライン71 により実行される命令 | パイプライン72 により実行される命令 |

|-------------|---------------------|---------------------|

| 40          | ADD                 | MOV                 |

| 60          | SUB                 | SUB                 |

| 120         | JMP                 |                     |

| 130         | LD                  |                     |

| 150         | LD                  | ADD                 |

| 190         | MOV                 |                     |

【図 10】

【図 11】

【図12】

50

| 識別子       | レジスタ                   |

|-----------|------------------------|

| 1番目の命令ADD | R11, R12 (R11=R11+R12) |

| 3番目の命令SUB | R1, R2 (R1=R1-R2)      |

| 4番目の命令SUB | R3, R1 (R3=R3-R1)      |

| 8番目の命令ADD | R21, R22 (R21=R21+R22) |

【図13】

【図14】

【図15】

| 60  | バイブライン71<br>により実行される命令 | バイブライン72<br>により実行される命令 |

|-----|------------------------|------------------------|

| 40  | ADD                    | MOV                    |

| 60  | SUB                    |                        |

| 80  | SUB                    |                        |

| 140 | JMP                    |                        |

| 150 | LD                     |                        |

| 170 | LD                     | ADD                    |

| 210 | MOV                    |                        |

【図16】