(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6665100号

(P6665100)

(45) 発行日 令和2年3月13日(2020.3.13)

(24) 登録日 令和2年2月21日(2020.2.21)

(51) Int.Cl.

HO3C 3/00 (2006.01)

F 1

HO3C 3/00

Z

請求項の数 15 (全 25 頁)

(21) 出願番号 特願2016-548641 (P2016-548641)

(86) (22) 出願日 平成27年1月28日 (2015.1.28)

(65) 公表番号 特表2017-507568 (P2017-507568A)

(43) 公表日 平成29年3月16日 (2017.3.16)

(86) 國際出願番号 PCT/US2015/013245

(87) 國際公開番号 WO2015/116655

(87) 國際公開日 平成27年8月6日 (2015.8.6)

審査請求日 平成30年1月5日 (2018.1.5)

(31) 優先権主張番号 14/167,972

(32) 優先日 平成26年1月29日 (2014.1.29)

(33) 優先権主張国・地域又は機関

米国(US)

(73) 特許権者 595020643

クアルコム・インコーポレイテッド

QUALCOMM INCORPORATED

アメリカ合衆国、カリフォルニア州 92

121-1714、サン・ディエゴ、モア

ハウス・ドライブ 5775

(74) 代理人 100108855

弁理士 蔵田 昌俊

(74) 代理人 100158805

弁理士 井関 守三

(74) 代理人 100112807

弁理士 岡田 貴志

前置審査

最終頁に続く

(54) 【発明の名称】差動遅延されたクロックによる変調

## (57) 【特許請求の範囲】

## 【請求項 1】

第1のクロック信号および第1のベースバンド信号を受信し、データストリームを表すために前記第1のベースバンド信号に含まれるデータ値に基づいて第1の遅延されたクロック信号を生成するように構成された第1の構成可能遅延ユニットと、

前記第1のクロック信号および前記第1のベースバンド信号を受信し、前記第1のベースバンド信号に含まれる前記データ値に基づいて第2の遅延されたクロック信号を生成するように構成された第2の構成可能遅延ユニット、ここにおいて、前記第2の遅延されたクロック信号は前記第1の遅延されたクロック信号と異なり、前記第1の遅延されたクロック信号を生成するための第1の遅延量は、前記第2の遅延されたクロック信号を生成するための第2の遅延量と異なる、と。

10

変調されたクロック信号を生成するために、前記第1の遅延されたクロック信号と前記第2の遅延されたクロック信号とを合成するように構成された合成器、ここにおいて、前記変調されたクロック信号に含まれるパルスのパルス幅は、前記第1のベースバンド信号に含まれる前記データ値が増加すると増加し、前記第1のベースバンド信号に含まれる前記データ値が減少すると減少し、前記パルス幅は、前記第1の遅延量と前記第2の遅延量との差に基づき、前記変調されたクロック信号は、正パルスと負パルスを含む、と、を備えるデバイス。

## 【請求項 2】

前記第1の構成可能遅延ユニットは、前記第1の遅延されたクロック信号を生成するた

めに、前記第1の遅延量だけ前記第1のクロック信号を遅延させるようにさらに構成され、前記第1の遅延量は、前記第1のベースバンド信号に含まれる各データ値に基づく、請求項1に記載のデバイス。

【請求項3】

前記第2の構成可能遅延ユニットは、前記第2の遅延されたクロック信号を生成するためには、前記第2の遅延量だけ前記第1のクロック信号を遅延させるようにさらに構成され、前記第2の遅延量は、前記第1のベースバンド信号に含まれる各データ値に基づく、請求項1または請求項2に記載のデバイス。

【請求項4】

前記合成功器は、前記第1のベースバンド信号に含まれる各データ値に基づくパルス幅を有するパルスを含む前記変調されたクロック信号を生成するようにさらに構成される、請求項1に記載のデバイス。 10

【請求項5】

前記第1の遅延量および前記第2の遅延量は、前記第1のベースバンド信号に含まれる各データ値に基づく、請求項4に記載のデバイス。

【請求項6】

前記第1の遅延されたクロック信号を受信し、第1の増幅された遅延されたクロック信号を生成するように構成された第1のドライバと、

前記第2の遅延されたクロック信号を受信し、第2の増幅された遅延されたクロック信号を生成するように構成された第2のドライバと 20

をさらに備え、

前記合成功器は、前記変調されたクロック信号を生成するために、前記第1の増幅された遅延されたクロック信号と前記第2の増幅された遅延されたクロック信号とを合成するようにさらに構成される、請求項1に記載のデバイス。

【請求項7】

前記第1の構成可能遅延ユニットと結合されたデジタルアナログ変換器をさらに備え、前記デジタルアナログ変換器は、前記第1のベースバンド信号を受信し、前記第1の構成可能遅延ユニットにアナログ信号を与えるように構成され、前記第1の構成可能遅延ユニットは、前記アナログ信号に少なくとも部分的に基づいて前記第1の遅延されたクロック信号を生成するようにさらに構成される、請求項1に記載のデバイス。 30

【請求項8】

前記合成功器が、前記変調されたクロック信号を生成するために、前記第2の遅延されたクロック信号から前記第1の遅延されたクロック信号を減算することによって前記第1の遅延されたクロック信号と前記第2の遅延されたクロック信号とを合成するようにさらに構成される、請求項1に記載のデバイス。

【請求項9】

第2のクロック信号および第2のベースバンド信号を受信し、前記第2のベースバンド信号に含まれるデータ値に基づいて第3の遅延されたクロック信号を生成するように構成された第3の構成可能遅延ユニットと、

前記第2のクロック信号および前記第2のベースバンド信号を受信し、前記第2のベースバンド信号に含まれる前記データ値に基づいて第4の遅延されたクロック信号を生成するように構成された第4の構成可能遅延ユニットと 40

をさらに備え、

前記合成功器は、前記変調されたクロック信号を生成するために、前記第1の遅延されたクロック信号と、前記第2の遅延されたクロック信号と、前記第3の遅延されたクロック信号と、前記第4の遅延されたクロック信号とを合成するようにさらに構成される、請求項1に記載のデバイス。

【請求項10】

方法であって、

第1のクロック信号を受信することと、 50

第 1 のベースバンド信号を受信することと、

データストリームを表すために前記第 1 のベースバンド信号に含まれるデータ値と、前記第 1 のクロック信号と、に基づいて第 1 の遅延されたクロック信号を生成することと、

前記第 1 のベースバンド信号に含まれる前記データ値と前記第 1 のクロック信号とにに基づいて第 2 の遅延されたクロック信号を生成すること、ここにおいて、前記第 1 の遅延されたクロック信号は前記第 2 の遅延されたクロック信号と異なり、前記第 1 の遅延されたクロック信号を生成するための第 1 の遅延量は、前記第 2 の遅延されたクロック信号を生成するための第 2 の遅延量と異なる、と、

変調されたクロック信号を生成するために、前記第 1 の遅延されたクロック信号と前記第 2 の遅延されたクロック信号とを合成すること、ここにおいて、前記変調されたクロック信号に含まれるパルスのパルス幅は、前記第 1 のベースバンド信号に含まれる前記データ値が増加すると増加し、前記第 1 のベースバンド信号に含まれる前記データ値が減少すると減少し、前記パルス幅は、前記第 1 の遅延量と前記第 2 の遅延量との差に基づき、前記変調されたクロック信号は、正パルスと負パルスを含む、と、

を備える方法。

#### 【請求項 1 1】

前記変調されたクロック信号は、前記第 1 のベースバンド信号に含まれる前記データ値が変動すると変動するパルス幅を有するパルスを含む、請求項 1 0 に記載の方法。

#### 【請求項 1 2】

前記合成することは、前記変調されたクロック信号を生成するために、前記第 2 の遅延されたクロック信号から前記第 1 の遅延されたクロック信号を減算することをさらに備える、請求項 1 0 に記載の方法。

#### 【請求項 1 3】

第 2 のクロック信号を受信することと、

第 2 のベースバンド信号を受信することと、

前記第 2 のベースバンド信号に含まれるデータ値と前記第 2 のクロック信号とにに基づいて第 3 の遅延されたクロック信号を生成することと、

前記第 2 のベースバンド信号に含まれる前記データ値と前記第 2 のクロック信号とにに基づいて第 4 の遅延されたクロック信号を生成することと

をさらに備え、

前記合成することは、前記変調されたクロック信号を生成するために、前記第 1 の遅延されたクロック信号と、前記第 2 の遅延されたクロック信号と、前記第 3 の遅延されたクロック信号と、前記第 4 の遅延されたクロック信号とを合成することをさらに備える、請求項 1 0 に記載の方法。

#### 【請求項 1 4】

変調されたクロック信号を生成するための変調器を備えるシステムであって、前記変調器は、請求項 1 ~ 請求項 9 のうちのいずれか一項に記載のデバイスを備える、システム。

#### 【請求項 1 5】

コンピュータシステム上で実行されると、前記コンピュータシステムに、請求項 1 0 ~ 請求項 1 3 のいずれか一項に記載の方法を実行させるための命令を備える、コンピュータプログラム。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0 0 0 1】

関連出願

[0001]本出願は、2014年1月29日に出願された米国出願第 14 / 167,972 号の優先権の利益を主張する。

##### 【0 0 0 2】

[0002]本発明の主題の実施形態は、一般に通信の分野に関し、より詳細には、差動遅延クロック信号を使用して、変調された信号を生成することに関する。

10

20

30

40

50

**【背景技術】****【0003】**

[0003]変調技法は、一般に、ベースバンド信号およびキャリア信号を伴う。ベースバンド信号は、媒体を通じた送信を対象とする情報を含むことができる信号である。ベースバンド信号は、キャリア信号を変調して変調信号を生成するために使用され得る。ベースバンド信号からの情報を搬送する変調信号は、受信機に送信され得る。ベースバンド信号を用いてキャリア信号を変調するために、いくつかの変調技法が使用され得る。たとえば、アクセスポイントなどのワイヤレスデバイスは、IEEE 802.11仕様による直交周波数分割多重(O F D M)変調技法を使用して信号を変調することができる。ワイヤレスデバイスは、変調信号を生成するためのO F D M変調器と、媒体を通じて変調信号を送信するための送信機とを含むことができる。

10

**【0004】**

[0004]変調信号を送信することは、特に、変調器をもつデバイス中に含まれ得る他の回路および構成要素と比較して、大量の電力を消費することがある。電力消費を低減するために、スイッチモード送信機など、より電力効率的である送信機設計がしばしば使用される。しかしながら、スイッチモード送信機のスイッチング性質は、本質的に複雑であり、一般的な信号変調技法を用いた容易な実装に向いていない。

**【発明の概要】****【0005】**

[0005]クロック変調器の様々な実施形態が開示される。いくつかの実施形態では、クロック変調器は、第1のクロック信号および第1のベースバンド信号を受信することができる。第1のクロック信号は、第1の遅延されたクロック信号および第2の遅延されたクロック信号を生成するために遅延され得る。各遅延されたクロック信号のための遅延量は、第1のベースバンド信号に基づき得る。第1の遅延されたクロック信号と第2の遅延されたクロック信号とは、変調されたクロック信号を生成するために合成され得る。

20

**【0006】**

[0006]いくつかの実施形態では、クロック変調器は、第1のクロック信号と、第2のクロック信号と、第1のベースバンド信号と、第2のベースバンド信号とを受信することができます。第2のクロック信号は、第1のクロック信号の位相シフトされたバージョンであり得る。第1のクロック信号は、第1および第2の遅延されたクロック信号を生成するために遅延され得、第2のクロック信号は、第3の遅延されたクロック信号および第4の遅延されたクロック信号を生成するために遅延され得る。第1の遅延されたクロック信号と、第2の遅延されたクロック信号と、第3の遅延されたクロック信号と、第4の遅延されたクロック信号とは、直交変調クロック信号を生成するために合成され得る。

30

**【0007】**

[0007]いくつかの実施形態では、デバイスは、第1のクロック信号および第1のベースバンド信号を受信し、第1のベースバンド信号に少なくとも部分的に基づいて第1の遅延されたクロック信号を生成するように構成された第1の構成可能遅延ユニットと、第1のクロック信号および第1のベースバンド信号を受信し、第1のベースバンド信号に少なくとも部分的に基づいて第2の遅延されたクロック信号を生成するように構成された第2の構成可能遅延ユニットと、ここにおいて、第2の遅延されたクロック信号は第1の遅延されたクロック信号と異なる、変調されたクロック信号を生成するために、第1の遅延されたクロック信号と第2の遅延されたクロック信号とを合成するように構成された合成器とを備える。

40

**【0008】**

[0008]いくつかの実施形態では、第1の構成可能遅延ユニットは、第1の遅延されたクロック信号を生成するために、第1の遅延量だけ第1のクロック信号を遅延させるようにさらに構成され、第1の遅延量は、第1のベースバンド信号に少なくとも部分的に基づく。

**【0009】**

50

[0009]いくつかの実施形態では、第2の構成可能遅延ユニットは、第2の遅延されたクロック信号を生成するために、第2の遅延量だけ第1のクロック信号を遅延させるようさらに構成され、第2の遅延量は、第1のベースバンド信号に少なくとも部分的に基づく。

#### 【0010】

[0010]いくつかの実施形態では、合成器は、第1のベースバンド信号に少なくとも部分的に基づくパルス幅を有するパルスを含む変調されたクロック信号を生成するようにさらに構成される。

#### 【0011】

[0011]いくつかの実施形態では、パルス幅は、第1の遅延量と第2の遅延量との和に少なくとも部分的に基づき、第1の遅延量および第2の遅延量は、第1のベースバンド信号に少なくとも部分的に基づく。 10

#### 【0012】

[0012]いくつかの実施形態では、本デバイスは、第1の遅延されたクロック信号を受信し、第1の増幅された遅延されたクロック信号を生成するように構成された第1のドライバと、第2の遅延されたクロック信号を受信し、第2の増幅された遅延されたクロック信号を生成するように構成された第2のドライバとをさらに備え、合成器は、変調されたクロック信号を生成するために、第1の増幅された遅延されたクロック信号と第2の増幅された遅延されたクロック信号とを合成するようにさらに構成される。

#### 【0013】

[0013]いくつかの実施形態では、第1のドライバおよび第2のドライバは、スイッチモードドライバである。 20

#### 【0014】

[0014]いくつかの実施形態では、本デバイスは、第1の構成可能遅延ユニットと結合されたデジタルアナログ変換器をさらに備え、デジタルアナログ変換器は、第1のベースバンド信号を受信し、第1の構成可能遅延ユニットにアナログ信号を与えるように構成され、第1の構成可能遅延ユニットは、アナログ信号に少なくとも部分的に基づいて第1の遅延されたクロック信号を生成するようにさらに構成される。

#### 【0015】

[0015]いくつかの実施形態では、合成器は、変調されたクロック信号を生成するために、第2の遅延されたクロック信号から第1の遅延されたクロック信号を減算することによって第1の遅延されたクロック信号と第2の遅延されたクロック信号とを合成するようにさらに構成される。 30

#### 【0016】

[0016]いくつかの実施形態では、本デバイスは、第2のクロック信号および第2のベースバンド信号を受信し、第2のベースバンド信号に少なくとも部分的に基づいて第3の遅延されたクロック信号を生成するように構成された第3の構成可能遅延ユニットと、第2のクロック信号および第2のベースバンド信号を受信し、第2のベースバンド信号に少なくとも部分的に基づいて第4の遅延されたクロック信号を生成するように構成された第4の構成可能遅延ユニットとをさらに備え、合成器は、変調されたクロック信号を生成するために、第1の遅延されたクロック信号と、第2の遅延されたクロック信号と、第3の遅延されたクロック信号と、第4の遅延されたクロック信号とを合成するようにさらに構成される。 40

#### 【0017】

[0017]いくつかの実施形態では、第2のクロック信号は、位相シフトによって第1のクロック信号に関係付けられる。

#### 【0018】

[0018]いくつかの実施形態では、方法は、第1のクロック信号を受信することと、第1のベースバンド信号を受信することと、第1のベースバンド信号と第1のクロック信号とに少なくとも部分的に基づいて第1の遅延されたクロック信号を生成することと、第1の 50

ベースバンド信号と第1のクロック信号とに少なくとも部分的に基づいて第2の遅延されたクロック信号を生成することと、ここにおいて、第1の遅延されたクロック信号は第2の遅延されたクロック信号と異なる、変調されたクロック信号を生成するために、第1の遅延されたクロック信号と第2の遅延されたクロック信号とを合成することとを備える。

**【0019】**

[0019]いくつかの実施形態では、第1の遅延されたクロック信号を生成することは、第1の遅延量だけ第1のクロック信号を遅延させることをさらに備え、第1の遅延量は、第1のベースバンド信号に少なくとも部分的に基づく。

**【0020】**

[0020]いくつかの実施形態では、第2の遅延されたクロック信号を生成することは、第2の遅延量だけ第1のクロック信号を遅延させることをさらに備え、第2の遅延量は、第1のベースバンド信号に少なくとも部分的に基づく。

10

**【0021】**

[0021]いくつかの実施形態では、変調されたクロック信号は、第1のベースバンド信号に少なくとも部分的に基づくパルス幅を有するパルスを含む。

**【0022】**

[0022]いくつかの実施形態では、パルス幅は、第1の遅延量と第2の遅延量との和に少なくとも部分的に基づき、ここにおいて、第1の遅延量および第2の遅延量は、第1のベースバンド信号に少なくとも部分的に基づく。

**【0023】**

[0023]いくつかの実施形態では、本方法は、第1の遅延されたクロック信号を増幅することと、第2の遅延されたクロック信号を増幅することとをさらに備え、第1の遅延されたクロック信号と第2の遅延されたクロック信号とを合成することは、変調されたクロック信号を生成するために、第1の増幅された遅延されたクロック信号と第2の増幅された遅延されたクロック信号とを合成することをさらに備える。

20

**【0024】**

[0024]いくつかの実施形態では、第1の遅延されたクロック信号を増幅することは、スイッチモードドライバを通じて増幅することをさらに備える。

**【0025】**

[0025]いくつかの実施形態では、合成することは、変調されたクロック信号を生成するために、第2の遅延されたクロック信号から第1の遅延されたクロック信号を減算することをさらに備える。

30

**【0026】**

[0026]いくつかの実施形態では、本方法は、第2のクロック信号を受信することと、第2のベースバンド信号を受信することと、第2のベースバンド信号と第2のクロック信号とに少なくとも部分的に基づいて第3の遅延されたクロック信号を生成することと、第2のベースバンド信号と第2のクロック信号とに少なくとも部分的に基づいて第4の遅延されたクロック信号を生成することとをさらに備え、合成することは、変調されたクロック信号を生成するために、第1の遅延されたクロック信号と、第2の遅延されたクロック信号と、第3の遅延されたクロック信号と、第4の遅延されたクロック信号とを合成することをさらに備える。

40

**【0027】**

[0027]いくつかの実施形態では、第2のクロック信号は、位相シフトによって第1のクロック信号に関係付けられる。

**【0028】**

[0028]いくつかの実施形態では、システムは、変調されたクロック信号を生成するための変調器を備え、この変調器は、第1のクロック信号および第1のベースバンド信号を受信し、第1のベースバンド信号に少なくとも部分的に基づいて第1の遅延されたクロック信号を生成するように構成された第1の構成可能遅延ユニットと、第1のクロック信号および第1のベースバンド信号を受信し、第1のベースバンド信号に少なくとも部分的に基

50

づいて第2の遅延されたクロック信号を生成するように構成された第2の構成可能遅延ユニットと、ここでいて、第2の遅延されたクロック信号は第1の遅延されたクロック信号と異なる、第1の遅延されたクロック信号と第2の遅延されたクロック信号とに少なくとも部分的に基づいて、変調されたクロック信号を生成するように構成された合成器とを備える。

【0029】

[0029]いくつかの実施形態では、本システムは、第1のベースバンド信号を受信し、第1の構成可能遅延ユニットに変更された第1のベースバンド信号を与えるように構成されたプリプロセッサをさらに備える。

【0030】

[0030]いくつかの実施形態では、プリプロセッサは、第1のベースバンド信号に予歪を与えるように構成される。

【0031】

[0031]いくつかの実施形態では、本システムは、第1の遅延されたクロック信号を受信し、第1の増幅された遅延されたクロック信号を生成するように構成された第1のドライバと、第2の遅延されたクロック信号を受信し、第2の増幅された遅延されたクロック信号を生成するように構成された第2のドライバとをさらに備え、合成器は、変調されたクロック信号を生成するために、第1の増幅された遅延されたクロック信号と第2の増幅された遅延されたクロック信号とを合成するようにさらに構成される。

【0032】

[0032]いくつかの実施形態では、変調器は、第2のクロック信号および第2のベースバンド信号を受信し、第2のベースバンド信号に少なくとも部分的に基づいて第3の遅延されたクロック信号を生成するように構成された第3の構成可能遅延ユニットと、第2のクロック信号および第2のベースバンド信号を受信し、第2のベースバンド信号に少なくとも部分的に基づいて第4の遅延されたクロック信号を生成するように構成された第4の構成可能遅延ユニットとをさらに備え、合成器は、変調されたクロック信号を生成するために、第1の遅延されたクロック信号と、第2の遅延されたクロック信号と、第3の遅延されたクロック信号と、第4の遅延されたクロック信号とを合成するようにさらに構成される。

【0033】

[0033]いくつかの実施形態では、本システムは、変調されたクロック信号を送信するように構成されたアンテナと、アンテナに変調されたクロック信号を選択的に結合するように構成されたスイッチとをさらに備える。

【0034】

[0034]いくつかの実施形態では、本システムは、変調器から変調されたクロック信号を受信し、スイッチにフィルタ処理された変調されたクロック信号を与えるように構成されたフィルタをさらに備える。

【0035】

[0035]いくつかの実施形態では、フィルタは、ローパスフィルタプロファイル、バンドパスフィルタプロファイルおよびハイパスフィルタプロファイルのうちの少なくとも1つを有する。

【0036】

[0036]いくつかの実施形態では、非一時的機械可読記憶媒体は、機械実行可能命令を記憶し、機械実行可能命令は、第1のクロック信号を受信することと、第1のベースバンド信号を受信することと、第1のベースバンド信号と第1のクロック信号とに少なくとも部分的に基づいて第1の遅延量をもつ第1の遅延されたクロック信号を生成することと、第1のベースバンド信号と第1のクロック信号とに少なくとも部分的に基づいて第2の遅延量をもつ第2の遅延されたクロック信号を生成することと、ここにおいて、第1の遅延量は第2の遅延量と異なる、変調されたクロック信号を生成するために、第1の遅延されたクロック信号と第2の遅延されたクロック信号とを合成することとを行うための命令を備

10

20

30

40

50

える。

**【0037】**

[0037]添付の図面を参照することによって、本実施形態はより良く理解されることができ、多数の目的、特徴、および利点が当業者に明らかになり得る。

**【図面の簡単な説明】**

**【0038】**

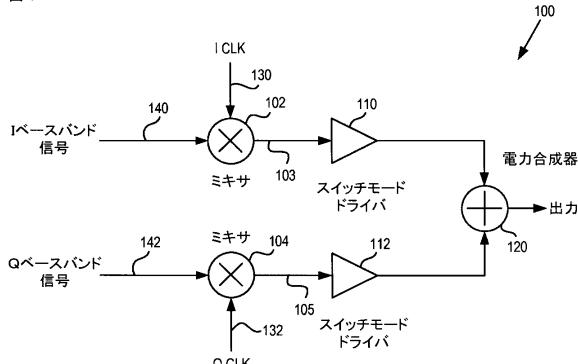

**【図1】クロック変調器の簡略図。**

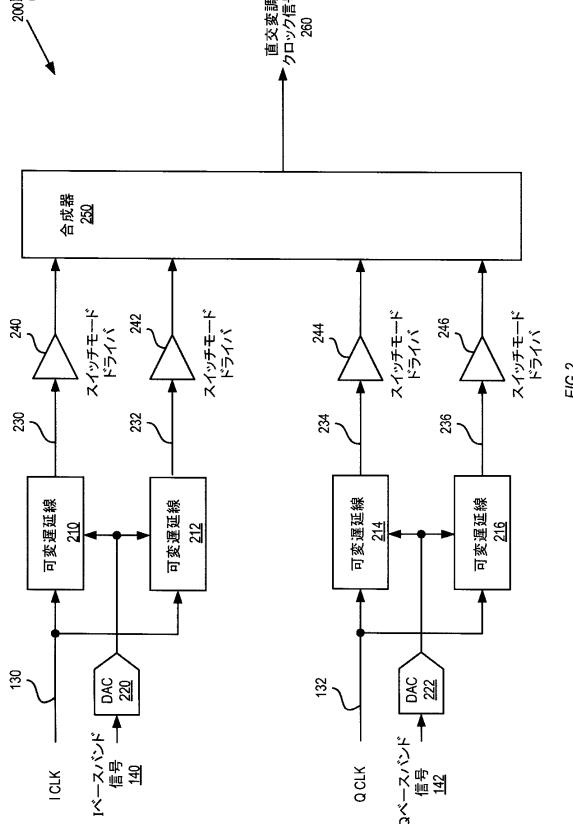

**【図2】直交クロック変調器の一実施形態のブロック図。**

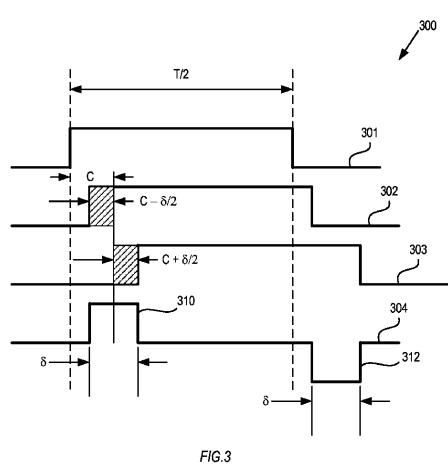

**【図3】クロック信号の例示的な波形形状およびタイミング関係を示す波形図。**

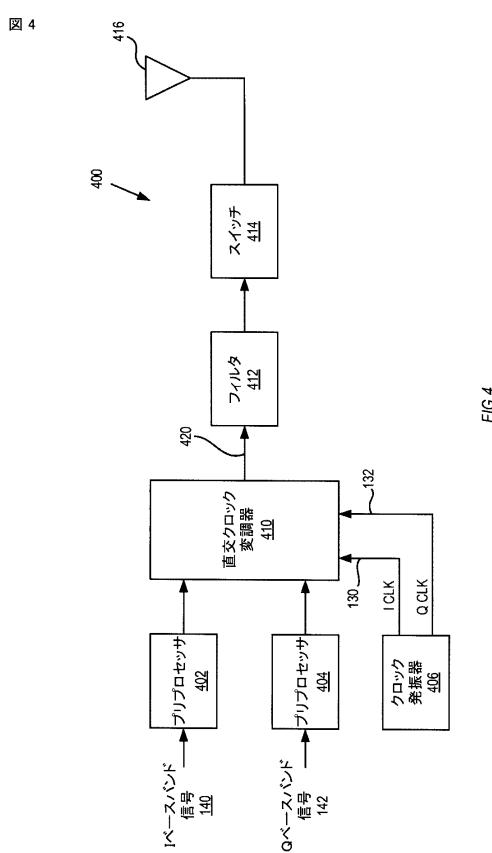

**【図4】直交クロック変調器を含む送信機の一実施形態を示すブロック図。**

10

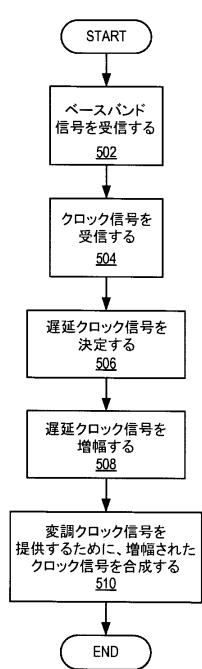

**【図5】変調されたクロック信号を与えるための例示的な動作を示す流れ図。**

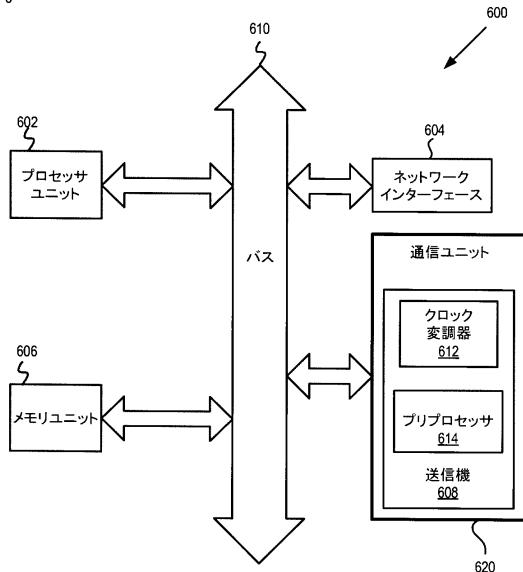

**【図6】直交クロック変調器を含む電子デバイスの例示的な実施形態のブロック図。**

**【発明を実施するための形態】**

**【0039】**

[0044]以下の説明は、本発明の主題の技法を実施する例示的なシステム、方法、技法、命令シーケンスおよびコンピュータプログラム製品を含む。ただし、説明する実施形態は、これらの具体的な詳細なしに実施され得ることを理解されたい。たとえば、例は IEE802.11 仕様に従って動作するデバイスに言及するが、他の規格または仕様に従って動作する他のワイヤレス、ワイヤード（たとえば、イーサネット（登録商標）、電力線通信（PLC）など）、またはハイブリッドデバイスが使用され得る。ハイブリッドデバイスは、ワイヤレスシステムとワイヤードシステムの両方のための構成要素を含むことができる。たとえば、ハイブリッドデバイスは、IEE802.11 仕様に従って通信するためのワイヤレス構成要素と、PLC 仕様に従う通信のためのワイヤード構成要素とを含むことができる。他の事例では、説明を不明瞭にしないために、よく知られている命令インスタンス、プロトコル、構造、および技法を詳細に図示していない。

20

**【0040】**

[0045]通信ネットワークにおける第1のデバイスは、変調器と送信機とを含むことができる。第1のデバイスは、第2のデバイス中の受信機に変調された信号を送信することによって、第2のデバイスと通信することができる。変調器によって生成された変調された信号は、ネットワークの通信媒体を介して送信機から受信機に情報を搬送することができる。送信のための情報は、ベースバンド信号中に含まれ得る。たとえば、1つの変調方式では、変調された信号を生成するために、キャリア信号がベースバンド信号によって変調される。変調された信号は、増幅器に結合され、送信される前に、（フィルタ処理などの）さらなる処理を受けることがある。

30

**【0041】**

[0046]増幅器は、一般に、送信範囲および信頼性を増加させるために、変調されたキャリア信号にエネルギーを追加する（たとえば、変調されたキャリア信号を増幅する）。変調されたキャリア信号が増幅されるとき、増幅器によってひずみがもたらされ得る。位相ひずみ、利得ひずみおよび周波数ひずみなどの一般的なひずみは、送信された変調されたキャリア信号を受信し、復調するために使用される処理ステップの数を増加させことがある。線形利得をもつ増幅器は、本質的に、低い量のひずみを有する。クラス A またはクラス A / B 増幅器設計は、線形利得をもつ増幅器の例である。しかしながら、クラス A またはクラス A / B 増幅器は、電力非効率的であり得る。場合によっては、クラス A またはクラス A / B 增幅器は、デバイスの大量の電力消費の原因であり得る。クラス D（スイッチモード）増幅器は、それらが一般により電力効率的であるので、クラス A またはクラス A / B 増幅器よりも好ましいことがある。しかしながら、クラス D 増幅器は、一般に、線形利得を有しない。その結果、クラス D 増幅器からの変調されたキャリア信号を受信および復調することは、増幅器からの追加されたひずみに部分的にによって、より線形の増幅器と比較して、より多くの処理ステップを必要とすることがある。

40

**【0042】**

50

[0047]いくつかの実施形態では、クロック変調器は、2つの構成可能遅延ユニット (configurable delay unit) と合成器とを含むことができる。各構成可能遅延ユニットは、ベースバンド信号およびクロック信号を受信することができる。各構成可能遅延ユニットは、ベースバンド信号に少なくとも部分的に基づくある遅延量だけクロック信号を遅延させることができる。各構成可能遅延ユニットによって与えられる遅延量は、異なり得る。第1の構成可能遅延ユニットは、第1の遅延されたクロック信号を生成するために、第1の遅延量だけクロック信号を遅延させることができる。第2の構成可能遅延ユニットは、第2の遅延量だけクロック信号を遅延させることができる。一実施形態では、全体的遅延量は、第1の遅延されたクロック信号と第2の遅延されたクロック信号との間の時間差によって決定される。第1の遅延されたクロック信号および第2の遅延されたクロック信号は、差動遅延クロック信号 (differentially delayed clock signal) と呼ばれる。差動遅延クロック信号は、変調されたクロック信号を生成するために合成され得る。

#### 【0043】

[0048]別の実施形態では、クロック変調器は、2つのベースバンド信号および2つのクロック信号を受信することができる。一実施形態では、クロック信号は、約90度の位相シフトによって互いに関係付けられ得る。約90度の位相シフト関係をもつクロック信号は、直交クロックと呼ばれる。この実施形態では、クロック変調器は、4つの構成可能遅延ユニットと合成器とを含むことができる。第1のクロック信号および第1のベースバンド信号は、第1の構成可能遅延ユニットと第2の構成可能遅延ユニットとに結合される。上記で説明したように、構成可能遅延ユニットは、第1の遅延されたクロック信号および第2の遅延されたクロック信号を生成する。第2のクロック信号および第2のベースバンド信号は、第3の構成可能遅延ユニットと第4の構成可能遅延ユニットとに結合される。第3の構成可能遅延ユニットおよび第4の構成可能遅延ユニットは、上記で説明した他の構成可能遅延ユニットと同様である。第3の構成可能遅延ユニットおよび第4の構成可能遅延ユニットは、それぞれ、第3の遅延されたクロック信号および第4の遅延されたクロック信号を生成する。第1、第2、第3および第4の遅延されたクロック信号は、直交変調クロック信号とも呼ばれる変調されたクロック信号を生成するために、合成器によって合成される。

#### 【0044】

[0049]図1は、クロック変調器100の簡略図である。簡略図は、クロック変調器100の概念動作をハイライトする。クロック変調器100は、第1のベースバンド信号と、第2のベースバンド信号と、第1のクロック信号と、第2のクロック信号とを受信することができる。2つのクロック信号は、位相シフトによって互いに関係付けられ得る。位相シフトが約90度であるとき、クロック信号は直交関係にあると言われる。クロック信号が直交関係にあるとき、クロック変調器100は直交クロック変調器である。

#### 【0045】

[0050]第1のクロック信号は、ICLK信号130（同相クロック）と呼ばれることがあり、第2のクロック信号は、QCLK信号132（直交クロック）と呼ばれことがある。一実施形態では、ICLK信号130およびQCLK信号132は、約2.4GHzであり得る。他の実施形態では、他の周波数が使用され得る。たとえば、ICLK信号130およびQCLK信号132は1.2GHzであり得るか、またはICLK信号130およびQCLK信号132は5.4GHzであり得る。第1および第2のベースバンド信号は、データを搬送することができる。たとえば、ベースバンド信号は、データを搬送するために時間変動され得る。時間変動するが、ベースバンド信号は所定の帯域幅に制限され得る。たとえば、ベースバンド信号は50MHzに制限され得る。一実施形態では、ICLK信号130およびQCLK信号132の周波数は、ベースバンド信号の帯域幅よりも少なくとも10倍大きくなり得る。ICLK信号130およびQCLK信号132に関してベースバンド信号の帯域幅を制限することは、ICLK信号130およびQCLK信号132の非線形変調を低減することができる。これらのクロック信号の変調について、

10

20

30

40

50

以下でより詳細に説明する。第1のベースバンド信号は、Iベースバンド信号140と呼ばれることがあり、第2のベースバンド信号は、Qベースバンド信号142と呼ばれることがある。

#### 【0046】

[0051] ICLK信号130およびIベースバンド信号140はミキサ102に結合される。ミキサ102は信号を互いに乗算（または「混合」）することができる。概念的に、2つの信号を混合することは、少なくとも2つの成分、「和」成分と「差」成分とをもつ信号を作成する。たとえば、2つの信号F1およびF2を混合することの結果は、F1 + F2（和）成分とF1 - F2（差）成分とをもつ信号を生成する。信号F1が、第1の周波数をもつ信号であり、信号F2が、第2の周波数をもつ信号であるとき、信号F1と信号F2とを混合することは、第1の周波数と第2の周波数とを足したものに基づく周波数を有する第1の成分と、第1の周波数から第2の周波数を引いたものに基づく第2の成分とをもつ信号を生成する。しばしば、ミキサの出力は、2つの成分のうちの1つを除去するためにフィルタ処理される。混合演算は、アナログ乗算器またはデジタル乗算器を用いて実行され得る。ミキサに与えられた2つの信号のうちの1つは、可変信号（たとえば、時間変動または周波数変動信号）であるとき、ミキサの出力は、変調された信号であると言われる。可変信号は、ミキサを通じて非変動信号を変調すると言われる。非変動信号は、ICLK信号130などのクロック信号であり得る。ICLK信号130の周波数は、一定であり得る。可変信号は、Iベースバンド信号140またはQベースバンド信号142などの時間変動データ信号であり得る。

10

20

#### 【0047】

[0052] Iベースバンド信号140およびICLK信号130は、第1の変調されたクロック信号103を生成するために、ミキサ102を用いて互いに混合され得る。すなわち、ICLK信号130は、第1の変調されたクロック信号103を生成するために、Iベースバンド信号140によって変調される。同様にして、ミキサ104は、第2の変調されたクロック信号105を生成するために、Qベースバンド信号142とQCLK信号132とを互いに混合することができる。すなわち、QCLK信号132は、第2の変調されたクロック信号105を生成するために、Qベースバンド信号142によって変調される。一実施形態では、Iベースバンド信号140およびQベースバンド信号142は可変信号（時間変動または周波数変動）であり、ICLK信号130およびQCLK信号132は非変動信号である。

30

#### 【0048】

[0053] ミキサ102は、スイッチモードドライバ(switched mode driver)110に結合される。スイッチモードドライバ110は、ミキサ102から受信された第1の変調されたクロック信号103を増幅することができる。同様に、ミキサ104は、ミキサ104から受信された第2の変調されたクロック信号105を増幅することができるスイッチモードドライバ112に結合される。スイッチモードドライバ110および112の出力は、電力合成器120に結合される。電力合成器120は、スイッチモードドライバ110の出力およびスイッチモードドライバ112の出力を互いに加算（すなわち、合成）することができる。ICLK信号130およびQCLK信号132が直交関係を有するので、電力合成器120の出力は、（増幅された）第2の変調されたクロック信号105と直交位相にある（増幅された）第1の変調されたクロック信号103を含むことができる。電力合成器120の出力は、直交変調クロック信号と呼ばれることがある。

40

#### 【0049】

[0054] 図2は、直交クロック変調器200の一実施形態のブロック図である。直交クロック変調器200は、ICLK信号130と、QCLK信号132と、Iベースバンド信号140と、Qベースバンド信号142とを受信し、直交変調クロック信号260を生成することができる。

#### 【0050】

[0055] 一実施形態では、直交クロック変調器200は、ICLK信号130およびIベ

50

ースバンド信号 140 を処理するために、2つの構成可能遅延ユニットを含む。この実施形態では、構成可能遅延ユニットは可変遅延線として実装される。他の実施形態では、構成可能遅延ユニットは、タップ付き遅延線、プログラマブル遅延線または他の技術的に実現可能な遅延ユニットとして実装され得る。第1の可変遅延線 210 および第2の可変遅延線 212 は、それぞれ、I C L K 信号 130 を受信することができる。この実施形態では、Iベースバンド信号 140 は、第1のデジタルアナログ変換器 (D A C) 220 を通じて第1の可変遅延線 210 および第2の可変遅延線 212 に結合される。第1のD A C 220 は、デジタル信号からアナログ信号にIベースバンド信号 140 を変換することができる。たとえば、第1のD A C 220 は、アナログ電圧信号またはアナログ電流信号を生成することができる。第1のD A C 220 は、第1の可変遅延線 210 および第2の可変遅延線 212 への結合のために、Iベースバンド信号 140 をアナログ信号に変換することができる。

10

#### 【 0 0 5 1 】

[0056] 第1の可変遅延線 210 および第2の可変遅延線 212 は I C L K 信号 130 を遅延させる。第1の可変遅延線 210 は、第1の遅延量をもつ第1の遅延されたクロック信号 230 を生成するように構成される。同様に、第2の可変遅延線 212 は、第2の遅延量をもつ第2の遅延されたクロック信号 232 を生成する。第1および第2の遅延量は、第1の遅延されたクロック信号 230 が遅延量 だけ第2の遅延されたクロック信号 232 とは異なるように決定される。

#### 【 0 0 5 2 】

[0057] 遅延量 は Iベースバンド信号 140 に少なくとも部分的に基づき得る。一実施形態では、遅延量 は Iベースバンド信号値に基づき得る。たとえば、Iベースバンド信号 140 は、任意のデータストリームを表すように構成され得る。Iベースバンド信号 140 は、データストリーム値を表すために、数値など、値を含むことができる。Iベースバンド信号 140 の値の他の例としては、整数および浮動小数点数、英数字データ、シンボルデータまたは他の技術的に実現可能な値があり得る。Iベースバンド信号 140 の値が増加する場合、遅延量 は比例して増加することがある。逆に、Iベースバンド信号 140 の値が減少する場合、遅延量 は比例して減少することがある。第1の可変遅延線 210 と第2の可変遅延線 212 とから第1の遅延されたクロック信号 230 および第2の遅延されたクロック信号 232 を生成することの動作について、図3に関連して以下により詳細に説明する。

20

30

#### 【 0 0 5 3 】

[0058] 遅延量 は、第1の可変遅延線 210 と第2の可変遅延線 212 とによって生成され得る。一実施形態では、遅延量 は、第1の可変遅延線 210 と第2の可変遅延線 212との間で分割され得る。第1の可変遅延線 210 によって生成された遅延量と第2の可変遅延線 212 によって生成された遅延量とは、合成器 250 中で合成される。すなわち、合成器 250 は、第1の可変遅延線 210 と第2の可変遅延線 212 との間で分割された遅延量を合成することができる。遅延量 を与えるための第1の可変遅延線 210 および第2の可変遅延線 212 の構成ならびに合成器 250 の動作に関する詳細について、図3に関連して以下により詳細に説明する。一実施形態では、遅延量 は、第1の可変遅延線 210 と第2の可変遲延線 212 との間で均等に分割される。他の実施形態では、遅延量 は、第1の可変遅延線 210 と第2の可変遲延線 212 との間で不均等に分割され得る。

40

#### 【 0 0 5 4 】

[0059] 上記で説明したように、遅延量 は、固定されないが、Iベースバンド信号 140 に応じて変動することがある。たとえば、Iベースバンド信号 140 は、時間変動データストリームを表すために、数値を含むことができる。遅延量 が Iベースバンド信号 140 に応じて変動するがあるので、この例では、遅延量 は時間変動遅延量であり得る。

#### 【 0 0 5 5 】

10

20

30

40

50

[0060]第1の遅延されたクロック信号230および第2の遅延されたクロック信号232は、それぞれ、第1のスイッチモードドライバ240および第2のスイッチモードドライバ242に結合される。第1のスイッチモードドライバ240および第2のスイッチモードドライバ242は、第1の遅延されたクロック信号230および第2の遅延されたクロック信号232のエネルギーを増加させることができる。一実施形態では、第1のスイッチモードドライバ240および第2のスイッチモードドライバ242は、クラスD出力ドライバであり得る。別の実施形態では、第1のスイッチモードドライバ240および第2のスイッチモードドライバ242は、高電流出力をもつインバータであり得る。第1のスイッチモードドライバ240および第2のスイッチモードドライバ242の出力は、合成器250に結合され得る。第1のスイッチモードドライバ240および第2のスイッチモードドライバ242は第1の可変遅延線210および第2の可変遅延線212の出力に結合されるが、他の実施例では、增幅は、異なる構成要素に結合された異なるデバイスによって与えられ得る。たとえば、第1の遅延されたクロック信号230および第2の遅延されたクロック信号232は、合成器250の出力に結合された増幅器によって増幅され得る。

10

#### 【0056】

[0061]合成器250は、第1のスイッチモードドライバ240からの出力と第2のスイッチモードドライバ242からの出力を合成することができる。一実施形態では、合成器250は、第1のスイッチモードドライバ240の第2の出力から、第2のスイッチモードドライバ242からの第1の出力を減算することができる。第1のスイッチモードドライバ240の出力と第2のスイッチモードドライバ242の出力を合成することの動作について、図3に関連して以下でより詳細に説明する。

20

#### 【0057】

[0062]QCLK信号132は、それぞれ、第3の可変遅延線214と第4の可変遅延線216とに結合される。Qベースバンド信号142は、第3の可変遅延線214および第4の可変遅延線216に第2のDAC222を通じて結合される。第3の可変遅延線214は、第3の遅延量をもつ第3の遅延されたクロック信号234を生成する。同様に、第4の可変遅延線216は、第4の遅延量をもつ第4の遅延されたクロック信号236を生成する。第3の遅延量および第4の遅延量は、第3の遅延されたクロック信号234が、Qベースバンド信号142に少なくとも部分的に基づく遅延量だけ第4の遅延されたクロック信号236とは異なるように決定される。たとえば、Qベースバンド信号142の値が増加または減少する場合、Qベースバンド信号142に基づく遅延量は比例して増加または減少することがある。

30

#### 【0058】

[0063]第3の遅延されたクロック信号234および第4の遅延されたクロック信号236は、それぞれ、第3のスイッチモードドライバ244および第4のスイッチモードドライバ246に結合される。第3のスイッチモードドライバ244および第4のスイッチモードドライバ246は、第3の遅延されたクロック信号234および第4の遅延されたクロック信号236のエネルギーを増加させることができる。合成器250は、第3のスイッチモードドライバ244および第4のスイッチモードドライバ246からの出力を受信することができ、これらの出力を第1のスイッチモードドライバ240および第2のスイッチモードドライバ242からの出力と合成することができる。合成器250の出力は、直交変調クロック信号260である。

40

#### 【0059】

[0064]上記で説明したように、QCLK信号132の処理は、ICLK信号130の処理と同様である。しかしながら、Qベースバンド信号142はIベースバンド信号140とは無関係であり得る。したがって、Qベースバンド信号142に基づく遅延量は、Iベースバンド信号140に基づく遅延量とは無関係であり得る。一実施形態では、直交クロック変調器200の要素は対称であり得る。すなわち、ICLK信号130およびIベースバンド信号140を処理する際に使用される要素は、QCLK信号132およびQベー

50

スバンド信号 142 を処理する際に使用される対応する要素と同様であり得る。たとえば、第1のスイッチモードドライバ 240 は、QCLK 信号 132 と Q ベースバンド信号 142 とに関係する信号を増幅するために使用される第3のスイッチモードドライバ 244 によって使用される利得の同様の量を用いて ICLK 信号 130 と I ベースバンド信号 140 とに関係する信号を増幅する（それらの信号のエネルギーを増加させる）ことができる。別の実施形態では、直交クロック変調器 200 の要素は非対称であり得る。

#### 【0060】

[0065] 図 3 は、クロック信号の例示的な波形形状およびタイミング関係を示す波形図 300 である。特に、波形図 300 は、図 2 の直交クロック変調器 200 中で見つけられ得る、クロック信号と、遅延されたクロック信号と、遅延されたクロック信号の合成との間の関係を示す。部分クロック波形 301 が波形図 300 の上部に示されている。クロック波形 301 は、期間 T を有することができ、約 50 パーセントのデューティサイクルを有することができる。したがって、破線の間に示されているクロック波形 301 の部分は、クロック波形 301 の期間 T の約 1 / 2 である。 ICLK 信号 130 および QCLK 信号 132 は、クロック波形 301 と同様の波形を有することができる。

10

#### 【0061】

[0066] ICLK 信号 130 などのクロック信号が第1の可変遅延線 210 と第2の可変遅延線 212 とによって遅延されると、第1の遅延されたクロック信号 230 および第2の遅延されたクロック信号 232 がそれぞれ生成される。上記で説明したように、I ベースバンド信号 140 は、第1の可変遅延線 210 と第2の可変遅延線 212 とに結合される。一実施形態では、I ベースバンド信号 140 に応答する遅延量 は、第1の可変遅延線 210 と第2の可変遅延線 212 との間で分散され得る。たとえば、- ( / 2 ) の遅延が第1の可変遅延線 210 によって与えられ得、+ ( / 2 ) の遅延が第2の可変遅延線 212 によって与えられ得る。負の遅延量は生成することが困難であり得るので、一実施形態では、固定時定数 C が第1の可変遅延線 210 と第2の可変遅延線 212 の両方によって導入され得る。固定時定数 C は、正の遅延量を生成するように第1の可変遅延線 210 および第2の可変遅延線 212 を構成するのを助けることができる。たとえば、固定時間定数 C が遅延量 よりも大きい場合、( ( / 2 ) などの) 遅延量の一部分の減算により、正の遅延量が第1の可変遅延線 210 または第2の可変遅延線 212 のいずれかによって生成されることになる。

20

#### 【0062】

[0067] 図 3 に戻ると、波形 302 は、第1の可変遅延線 210 からの第1の遅延されたクロック信号 230 を表すことができる。この例では、第1の可変遅延線 210 は C - ( / 2 ) の遅延量を与える。波形 302 中の影付き領域は C - ( / 2 ) の遅延量をハイライトする。波形 303 は、第2の可変遅延線 212 からの第2の遅延されたクロック信号 232 を表すことができる。図示のように、第2の可変遅延線 212 は C + ( / 2 ) の遅延量を与える。波形 303 中の影付き領域は C + ( / 2 ) の遅延量をハイライトする。波形 302 および 303 は、変調されたクロック信号を形成するために合成され得る。一実施形態では、波形 302 および 303 は図 2 の合成器 250 において合成され得る。合成された波形の一実施形態が波形 304 に示されている。波形 304 は、波形 302 から波形 303 を減算することによって生成され得る。一実施形態では、合成された波形 304 は正パルス 310 と負パルス 312 を含むことができることに留意されたい。正パルス 310 および負パルス 312 は、それぞれ、図示のように のパルス幅を有する。

30

#### 【0063】

[0068] 波形図 300 は、ベースバンド信号に応答する遅延量 を実装するための 1 つの手法を示す。別の実施形態では、遅延量 は第1の可変遅延線 210 と第2の可変遅延線 212 との間で均等に分散される必要はなく、代わりに、遅延量 は不均等に分割され得る。

40

#### 【0064】

[0069] 波形 304 は 2 つのクロック信号（波形 302 および 303 ）の合成を示す。波

50

形 3 0 2 に示されているクロック信号および波形 3 0 3 に示されているクロック信号は、それぞれ、2つのクロック信号の間の遅延量が 10 になるように遅延されている。上記で説明したように、遅延量 10 は、Iベースバンド信号 140 または Qベースバンド信号 142 などの信号に少なくとも部分的に基づき得る。すなわち、遅延量 10 は、Iベースバンド信号 140 または Qベースバンド信号 142 が変動するにつれて変動することがある。

#### 【0065】

[0070]図 4 は、直交クロック変調器 410 を含む送信機 400 の一実施形態を示すプロック図である。直交クロック変調器 410 は図 2 の直交クロック変調器 200 と同様に動作することができる。送信機 400 は、ICLK 信号 130 および QCLK 信号 132 を生成することができるクロック発振器 406 を含むことができる。ICLK 信号 130 および QCLK 信号 132 は、直交クロック変調器 410 に結合され得る。一実施形態では、QCLK 信号 132 は ICLK 信号 130 の位相シフトされたバージョンであり得る。たとえば、ICLK 信号 130 は QCLK 信号 132 に対して約 90 度だけ位相シフトされ得る。他の実施形態では、他の位相シフトが可能である。たとえば、ICLK 信号 130 は 180 度だけ QCLK 信号 132 から位相シフトされ得る。

#### 【0066】

[0071]送信機 400 は、Iベースバンド信号 140 および Qベースバンド信号 142 を受信することができる。Iベースバンド信号 140 は、第 1 のプリプロセッサ 402 を通じて直交クロック変調器 410 に結合される。同様に、Qベースバンド信号 142 は、第 2 のプリプロセッサ 404 を通じて直交クロック変調器 410 に結合される。第 1 のプリプロセッサ 402 および第 2 のプリプロセッサ 404 は、送信機 400 の動作に対して調整または補正を行うことができる。たとえば、第 1 のプリプロセッサ 402 および第 2 のプリプロセッサ 404 は、送信機 400 中の処理によってもたらされたひずみを補償または補正するために、Iベースバンド信号 140 および / または Qベースバンド信号 142 に予歪 (pre-distortion) を適用することができる。一実施形態では、第 1 のプリプロセッサ 402 および / または第 2 のプリプロセッサ 404 は、ルックアップテーブルを含むことができる。第 1 のプリプロセッサ 402 および / または第 2 のプリプロセッサ 404 は、ベースバンド信号を受信し、ルックアップテーブル中に含まれる情報に基づいて、補正されたベースバンド信号を生成するように構成され得る。たとえば、ルックアップテーブル中の情報は、予歪または補正関数を記述することができる。

#### 【0067】

[0072]図 2 に関して上記で説明したように、直交クロック変調器 410 は、直交変調クロック信号 420 を生成することができる。直交クロック変調器 410 は、第 1、第 2、第 3 および第 4 のスイッチモードドライバ 240 ~ 246 など、1つまたは複数のドライバを含むことができる。第 1、第 2、第 3 および第 4 のスイッチモードドライバ 240 ~ 246 は、直交クロック変調器 410 内の信号にエネルギーを加えることができ、それにより通信媒体による直交変調クロック信号 420 の送信が可能になり得る。

#### 【0068】

[0073]直交変調クロック信号 420 はフィルタ 412 に結合される。フィルタ 412 は、ハイパスフィルタプロファイル、ローパスフィルタプロファイルまたはバンドパスフィルタプロファイルを有することができる。いくつかの実施形態では、フィルタ 412 は 2 つまたはそれ以上のフィルタプロファイルの組合せを含むことができる。フィルタ 412 の出力はスイッチ 414 に結合され得る。スイッチ 414 はアンテナ 416 からフィルタ 412 の出力を結合または切断することができる。一実施形態では、スイッチ 414 は、アンテナ 416 から受信機（図示せず）を分離するために使用される送信 / 受信スイッチであり得る。

#### 【0069】

[0074]図 5 は、変調クロック信号を与えるための例示的な動作を示す流れ図 500 である。例示的な動作は、直交クロック変調器 200 または送信機 400 中の 1 つまたは複数の構成要素によって実行され得る。フローは、ベースバンド信号を受信したとき、プロツ

ク 5 0 2において開始する。一実施形態では、受信されたベースバンド信号は、Iベースバンド信号140またはQベースバンド信号142であり得る。別の実施形態では、受信されたベースバンド信号は、Iベースバンド信号140とQベースバンド信号142の両方を含むことができる。ロック504に進むと、クロック信号を受信する。一実施形態では、受信されたクロック信号はICLK信号130またはQCLK信号132であり得る。別の実施形態では、受信されたクロック信号はICLK信号130とQCLK信号132の両方を含むことができる。

#### 【0070】

[0075] ブロック506に進むと、遅延されたクロック信号を決定する。一実施形態では、第1の遅延されたクロック信号230および第2の遅延されたクロック信号232が決定される。別の実施形態では、第1の遅延されたクロック信号230および第2の遅延されたクロック信号232に加えて、第3の遅延されたクロック信号234および第4の遅延されたクロック信号236が決定され得る。上記で説明したように、クロック信号のための遅延量は、ベースバンド信号に少なくとも部分的に基づき得る。一実施形態では、第1の遅延されたクロック信号230および第2の遅延されたクロック信号232のための遅延量はIベースバンド信号140に基づき得、第3の遅延されたクロック信号234および第4の遅延されたクロック信号236のための遅延量はQベースバンド信号142に基づき得る。第1の遅延されたクロック信号230中の遅延量は、第2の遅延されたクロック信号232中の遅延量とは異なり得る。第3の遅延されたクロック信号234のための遅延量は、第4の遅延されたクロック信号236のための遅延量とは異なり得る。

10

#### 【0071】

[0076] ブロック508に進むと、遅延されたクロック信号を増幅する。一実施形態では、第1の遅延されたクロック信号230および第2の遅延されたクロック信号232が増幅され得る。別の実施形態では、第1の遅延されたクロック信号230および第2の遅延されたクロック信号232に加えて、第3の遅延されたクロック信号234および第4の遅延されたクロック信号236が増幅され得る。一実施形態では、遅延されたクロック信号は、クラスD出力ドライバなど、スイッチモードドライバを介して増幅され得る。他の実施形態では、遅延されたクロック信号は、インバータを用いて増幅され得る。さらに他の実施形態では、任意の技術的に実現可能な増幅器が使用され得る。

20

#### 【0072】

[0077] ブロック510に進むと、変調されたクロック信号を生成するために、増幅された遅延されたクロック信号を合成し、フローを終了する。一実施形態では、合成器250は、第1のスイッチモードドライバ240からの増幅された遅延されたクロック信号と、第2のスイッチモードドライバ242からの増幅された遅延されたクロック信号とを合成することができる。別の実施形態では、合成器250は、第1のスイッチモードドライバ240からの増幅された遅延されたクロック信号と、第2のスイッチモードドライバ242からの増幅された遅延されたクロック信号と、第3のスイッチモードドライバ244からの増幅された遅延されたクロック信号と、第4のスイッチモードドライバ246からの増幅された遅延されたクロック信号とを合成することができる。一実施形態では、増幅された遅延されたクロック信号は、第2の増幅された遅延されたクロック信号から第1の増幅された遅延されたクロック信号を減算することによって合成され得る。別の実施形態では、増幅された遅延されたクロック信号は、第1の差分信号を生成するために、第2の増幅された遅延されたクロック信号から第1の増幅された遅延されたクロック信号を減算することによって合成され得る。第3の増幅された遅延されたクロック信号は、第2の差分信号を生成するために、第4の増幅された遅延されたクロック信号から減算され得る。第1の差分信号と第2の差分信号とは互いに合成され、それにより、すべての4つの増幅された遅延されたクロック信号を合成することができる。

30

#### 【0073】

[0078] 図1から図5および本明細書で説明した動作は、実施形態の理解を助けるための例であり、実施形態の範囲または特許請求の範囲を限定するために使用されるべきでない

40

50

。実施形態は、追加の動作を実行し、より少ない動作を実行し、異なる順序で動作を実行し、並列に動作を実行し、別様にいくつかの動作を実行し得る。たとえば、クロック信号は、ベースバンド信号がブロック 502において受信される前に、ブロック 504において受信され得る。

#### 【0074】

[0079]当業者によって諒解されるように、本発明の主題の態様は、システム、方法、またはコンピュータプログラム製品として実施され得る。したがって、本発明の主題の態様は、完全にハードウェアの実施形態、(ファームウェア、常駐ソフトウェア、マイクロコードなどを含む)ソフトウェアの実施形態、またはソフトウェアの態様とハードウェアの態様とを組み合わせた実施形態の形態をとり得、本明細書では、それらすべてを概して「回路」、「モジュール」または「システム」と呼ぶことがある。さらに、本発明の主題の態様は、コンピュータ可読プログラムコードを組み込む1つまたは複数のコンピュータ可読媒体中で実施されたコンピュータプログラム製品の形態をとり得る。10

#### 【0075】

[0080]1つまたは複数のコンピュータ可読媒体の任意の組合せが使用され得る。コンピュータ可読媒体はコンピュータ可読記憶媒体であり得る。コンピュータ可読記憶媒体は、たとえば、電子的、磁気的、光学式、電磁的、赤外線式、または半導体式のシステム、装置、またはデバイス、あるいは上記の任意の好適な組合せであり得る。コンピュータ可読記憶媒体のより具体的な例としては、ポータブルコンピュータディスクケット、ハードディスク、ランダムアクセスメモリ(RAM)、読み取り専用メモリ(ROM)、消去可能プログラマブル読み取り専用メモリ(E PROMまたはフラッシュメモリ)、ポータブルコンパクトディスク読み取り専用メモリ(CD-ROM)、光記憶デバイス、磁気記憶デバイス、または上記の任意の好適な組合せがあり得る。本明細書のコンテキストでは、コンピュータ可読記憶媒体は、命令実行システム、装置、またはデバイスによってあるいはそれらに関連して使用するためのプログラムを包含または記憶することができる任意の有形媒体であり得る。20

#### 【0076】

[0081]コンピュータ可読媒体上で実施されるプログラムコードは、限定はしないが、ワイヤレス、ワイヤライン、光ファイバーケーブル、RFなど、または上記の任意の好適な組合せを含む、任意の好適な媒体を使用して送信され得る。30

#### 【0077】

[0082]コンピュータ可読媒体は、本発明の主題の態様のための動作を行うための命令を含むことができ、1つまたは複数のプログラミング言語の任意の組合せで書かれ得る。プログラミング言語の例としては、Java(登録商標)、Smalltalk、C++などのオブジェクト指向プログラミング言語、および「C」プログラミング言語などの従来の手続き型プログラミング言語があり得る。プログラムコードは、完全にユーザのコンピュータ上で実行するか、部分的にユーザのコンピュータ上で実行するか、スタンドアロンソフトウェアパッケージとして実行するか、部分的にユーザのコンピュータ上と部分的にリモートコンピュータ上で実行するか、あるいは完全にリモートコンピュータまたはサーバ上で実行し得る。後者のシナリオでは、リモートコンピュータは、ローカルエリアネットワーク(LAN)またはワイドエリアネットワーク(WAN)を含む、任意のタイプのネットワークを通じてユーザのコンピュータに接続され得、あるいは接続は、(たとえば、インターネットサービスプロバイダを使用してインターネットを通じて)外部コンピュータに対して行われ得る。40

#### 【0078】

[0083]本発明の主題の態様について、方法、装置(システム)およびコンピュータプログラム製品のフローチャート図および/またはブロック図を参照しながら説明した。フローチャート図および/またはブロック図の各ブロック、ならびにフローチャート図および/またはブロック図中のブロックの組合せは、コンピュータプログラム命令によって実装され得ることが理解されよう。これらのコンピュータプログラム命令は、実行されるため50

に、汎用コンピュータ、専用コンピュータ、または他のプログラマブルデータ処理装置のプロセッサに与えられ得る。

#### 【0079】

[0084]これらのコンピュータプログラム命令は、フローチャートおよび／またはブロック図の1つまたは複数のブロックにおいて指定された機能／行為を実装する命令を含む製造品を生成するために、コンピュータ、他のプログラマブルデータ処理装置、または他のデバイスに特定の様式で機能するように指示するために実行され得る。

#### 【0080】

[0085]コンピュータプログラム命令はまた、コンピュータ、他のプログラマブルデータ処理装置、または他のデバイス上にロードされ得る。コンピュータプログラム命令は、実行された命令が、フローチャートおよび／またはブロック図の1つまたは複数のブロックにおいて指定された機能／行為を実装するためのプロセスを与えることができるようコンピュータ実装プロセスを生成するために、一連の動作ステップが実行されるように実行され得る。10

#### 【0081】

[0086]図6は、クロック変調器612を含む電子デバイス600の例示的な実施形態のブロック図である。いくつかの実装形態では、電子デバイス600は、ラップトップコンピュータ、タブレットコンピュータ、モバイルフォン、電力線通信デバイス、スマートアプライアンス(PDA)、アクセスポイント、ワイヤレス局または他の電子システムのうちの1つであり得る。電子デバイス600は、(場合によっては、複数のプロセッサ、複数のコア、複数のノードを含む、および／またはマルチスレッドを実装するなどの)プロセッサユニット602を含むことができる。電子デバイス600はまた、メモリユニット606を含むことができる。メモリユニット606は、システムメモリ(たとえば、キャッシュ、SRAM、DRAM、ゼロキャパシタRAM、ツイントランジスタRAM、eDRAM、EDO RAM、DDR RAM、EEPROM(登録商標)、NRAM、RRAM(登録商標)、SONOS、PRAMなどのうちの1つまたは複数)、あるいは機械可読媒体の上記すでに説明した可能な実現形態のうちのいずれか1つまたは複数であり得る。電子デバイス600は、バス610(たとえば、PCI、ISA、PCI-Express、HyperTransport(登録商標)、InfiniBand(登録商標)、NuBus、AHB、AXIなど)を含むことができる。電子デバイス600は、ワイヤレスネットワークインターフェース(たとえば、WLANインターフェース、Bluetooth(登録商標)インターフェース、WiMAX(登録商標)インターフェース、ZigBee(登録商標)インターフェース、ワイヤレスUSBインターフェースなど)およびワイヤードネットワークインターフェース(たとえば、イーサネットインターフェース、電力線通信インターフェースなど)のうちの少なくとも1つを含むネットワークインターフェース604を含むことができる。いくつかの実装形態では、電子デバイス600は、複数のネットワークインターフェースをサポートし得、それらのインターフェースの各々は、異なる通信ネットワークに電子デバイス600を結合するように構成される。20

#### 【0082】

[0087]電子デバイス600は通信ユニット620を含むことができる。通信ユニット620は、無線機、またはワイヤードおよびワイヤレスネットワーキングのための送信機と受信機とをもつハイブリッド無線機を含むことができる。たとえば、通信ユニット620は送信機608を含むことができる。送信機608は、上記で説明した送信機400と同様であり得る。送信機608は、クロック変調器612を含むことができる。送信機608は、変調クロック信号を送信することができる。クロック変調器612は、上記で説明した直交クロック変調器200と同様であり得る。送信機608は、1つまたは複数のプリプロセッサ614をも含むことができる。プリプロセッサ614は、上記で説明した第1のプリプロセッサ402および第2のプリプロセッサ404と同様であり得る。プリプロセッサ614は、クロック変調器612によって引き起こされたひずみを補償するため30

40

50

に、ベースバンド信号などの信号を補正する、または信号に予歪を与える（pre-distort）ことができる。いくつかの実施形態では、送信機 608 の他の部分は、プロセッサユニット 602、メモリユニット 606 およびバス 610 内に分散され得る。

#### 【0083】

[0088] メモリユニット 606 は、上記の図 1 から図 5 で説明した実施形態を実装するための機能を実施することができる。一実施形態では、メモリユニット 606 は、2つまたはそれ以上の遅延されたクロック信号を与えることを可能にする 1 つまたは複数の機能を含むことができ、ここで、遅延されたクロック信号の遅延量はベースバンド信号に少なくとも部分的に基づく。他の実施形態では、メモリユニット 606 は、プリプロセッサ 614 の機能の少なくとも一部分を与えることができるルックアップテーブルを実装するため 10 に使用され得る。

#### 【0084】

[0089] これらの機能のうちの任意の 1 つは、ハードウェアおよび / またはプロセッサユニット 602 上に部分的に（または完全に）実装され得る。たとえば、機能は、特定用途向け集積回路を用いて実装され、プロセッサユニット 602、周辺デバイスまたはカード上のコプロセッサなどの中に論理的に実装され得る。さらに、実現形態は、より少数の構成要素、または図 6 に示されない追加の構成要素（たとえば、ビデオカード、オーディオカード、追加のネットワークインターフェース、周辺デバイスなど）を含み得る。プロセッサユニット 602、メモリユニット 606、ネットワークインターフェース 604 は、バス 610 に結合される。バス 610 に結合されるものとして示されているが、メモリユニット 606 はプロセッサユニット 602 に結合され得る。 20

#### 【0085】

[0090] 本実施形態について、様々な実装形態および活用を参照しながら説明したが、これらの実施形態は例示的なものであり、本発明の主題の範囲はそれらに限定されないことを理解されよう。概して、本明細書で説明した、遅延されたクロック信号を与え、遅延されたクロック信号を合成するための技法は、任意の 1 つまたは複数のハードウェアシステムに一致する設備で実装され得る。多くの変形、修正、追加、および改善が可能である。 30

#### 【0086】

[0091] 単一の事例として本明細書で説明した構成要素、動作、または構造について、複数の事例が与えられ得る。最後に、様々な構成要素と、動作と、データストアとの間の境界はいくぶん恣意的であり、特定の動作が、特定の例示的な構成の文脈において示されている。機能の他の割振りが想定され、本発明の主題の範囲内に入り得る。概して、例示的な構成において別個の構成要素として提示された構造および機能は、組み合わされた構造または構成要素として実装され得る。同様に、単一の構成要素として提示された構造および機能は、別個の構成要素として実装され得る。これらおよび他の変形、修正、追加、および改善は、本発明の主題の範囲内に入り得る。 30

以下に、本願出願の当初の特許請求の範囲に記載された発明を付記する。

#### [C1]

第 1 のクロック信号および第 1 のベースバンド信号を受信し、前記第 1 のベースバンド信号に少なくとも部分的に基づいて第 1 の遅延されたクロック信号を生成するように構成された第 1 の構成可能遅延ユニットと、

前記第 1 のクロック信号および前記第 1 のベースバンド信号を受信し、前記第 1 のベースバンド信号に少なくとも部分的に基づいて第 2 の遅延されたクロック信号を生成するように構成された第 2 の構成可能遅延ユニットと、ここにおいて、前記第 2 の遅延されたクロック信号は前記第 1 の遅延されたクロック信号と異なる、

変調されたクロック信号を生成するために、前記第 1 の遅延されたクロック信号と前記第 2 の遅延されたクロック信号とを合成するように構成された合成器とを備えるデバイス。

#### [C2]

前記第 1 の構成可能遅延ユニットは、前記第 1 の遅延されたクロック信号を生成するた

10

20

30

40

50

めに、第1の遅延量だけ前記第1のクロック信号を遅延せるようにさらに構成され、前記第1の遅延量は、前記第1のベースバンド信号に少なくとも部分的に基づく、C1に記載のデバイス。

## [ C 3 ]

前記第2の構成可能遅延ユニットは、前記第2の遅延されたクロック信号を生成するため、第2の遅延量だけ前記第1のクロック信号を遅延せるようにさらに構成され、前記第2の遅延量は、前記第1のベースバンド信号に少なくとも部分的に基づく、C2に記載のデバイス。

## [ C 4 ]

前記合成功器は、前記第1のベースバンド信号に少なくとも部分的に基づくパルス幅を有するパルスを含む前記変調されたクロック信号を生成するようにさらに構成される、C1に記載のデバイス。 10

## [ C 5 ]

前記パルス幅は、第1の遅延量と第2の遅延量との和に少なくとも部分的に基づき、前記第1の遅延量および前記第2の遅延量は、前記第1のベースバンド信号に少なくとも部分的に基づく、C4に記載のデバイス。

## [ C 6 ]

前記第1の遅延されたクロック信号を受信し、第1の増幅された遅延されたクロック信号を生成するように構成された第1のドライバと、

前記第2の遅延されたクロック信号を受信し、第2の増幅された遅延されたクロック信号を生成するように構成された第2のドライバと 20

をさらに備え、

前記合成功器は、前記変調されたクロック信号を生成するために、前記第1の増幅された遅延されたクロック信号と前記第2の増幅された遅延されたクロック信号とを合成するようにさらに構成される、C1に記載のデバイス。

## [ C 7 ]

前記第1のドライバおよび前記第2のドライバはスイッチモードドライバである、C6に記載のデバイス。

## [ C 8 ]

前記第1の構成可能遅延ユニットと結合されたデジタルアナログ変換器をさらに備え、前記デジタルアナログ変換器は、前記第1のベースバンド信号を受信し、前記第1の構成可能遅延ユニットにアナログ信号を与えるように構成され、前記第1の構成可能遅延ユニットは、前記アナログ信号に少なくとも部分的に基づいて前記第1の遅延されたクロック信号を生成するようにさらに構成される、C1に記載のデバイス。 30

## [ C 9 ]

前記合成功器が、前記変調されたクロック信号を生成するために、前記第2の遅延されたクロック信号から前記第1の遅延されたクロック信号を減算することによって前記第1の遅延されたクロック信号と前記第2の遅延されたクロック信号とを合成するようにさらに構成される、C1に記載のデバイス。

## [ C 10 ]

第2のクロック信号および第2のベースバンド信号を受信し、前記第2のベースバンド信号に少なくとも部分的に基づいて第3の遅延されたクロック信号を生成するように構成された第3の構成可能遅延ユニットと、

前記第2のクロック信号および前記第2のベースバンド信号を受信し、前記第2のベースバンド信号に少なくとも部分的に基づいて第4の遅延されたクロック信号を生成するように構成された第4の構成可能遅延ユニットと

をさらに備え、

前記合成功器は、前記変調されたクロック信号を生成するために、前記第1の遅延されたクロック信号と、前記第2の遅延されたクロック信号と、前記第3の遅延されたクロック信号と、前記第4の遅延されたクロック信号とを合成するようにさらに構成される、C1 50

に記載のデバイス。

[ C 1 1 ]

前記第2のクロック信号は、位相シフトによって前記第1のクロック信号に関係付けられる、C 1 0 に記載のデバイス。

[ C 1 2 ]

第1のクロック信号を受信することと、

第1のベースバンド信号を受信することと、

前記第1のベースバンド信号と前記第1のクロック信号とに少なくとも部分的に基づいて第1の遅延されたクロック信号を生成することと、

前記第1のベースバンド信号と前記第1のクロック信号とに少なくとも部分的に基づいて第2の遅延されたクロック信号を生成することと、ここにおいて、前記第1の遅延されたクロック信号は前記第2の遅延されたクロック信号と異なる、

変調されたクロック信号を生成するために、前記第1の遅延されたクロック信号と前記第2の遅延されたクロック信号とを合成することとを備える方法。

[ C 1 3 ]

前記第1の遅延されたクロック信号を生成することは、第1の遅延量だけ前記第1のクロック信号を遅延させることをさらに備え、前記第1の遅延量は、前記第1のベースバンド信号に少なくとも部分的に基づく、C 1 2 に記載の方法。

[ C 1 4 ]

前記第2の遅延されたクロック信号を生成することは、第2の遅延量だけ前記第1のクロック信号を遅延させることをさらに備え、前記第2の遅延量は、前記第1のベースバンド信号に少なくとも部分的に基づく、C 1 3 に記載の方法。

[ C 1 5 ]

前記変調されたクロック信号は、前記第1のベースバンド信号に少なくとも部分的に基づくパルス幅を有するパルスを含む、C 1 2 に記載の方法。

[ C 1 6 ]

前記パルス幅は、第1の遅延量と第2の遅延量との和に少なくとも部分的に基づき、前記第1の遅延量および前記第2の遅延量は、前記第1のベースバンド信号に少なくとも部分的に基づく、C 1 5 に記載の方法。

[ C 1 7 ]

前記第1の遅延されたクロック信号を増幅することと、

前記第2の遅延されたクロック信号を増幅することとをさらに備え、

前記第1の遅延されたクロック信号と前記第2の遅延されたクロック信号とを前記合成することは、前記変調されたクロック信号を生成するために、第1の増幅された遅延されたクロック信号と第2の増幅された遅延されたクロック信号とを合成することをさらに備える、C 1 2 に記載の方法。

[ C 1 8 ]

前記第1の遅延されたクロック信号を増幅することは、スイッチモードドライバを通じて増幅することをさらに備える、C 1 7 に記載の方法。

[ C 1 9 ]

前記合成することは、前記変調されたクロック信号を生成するために、前記第2の遅延されたクロック信号から前記第1の遅延されたクロック信号を減算することをさらに備える、C 1 2 に記載の方法。

[ C 2 0 ]

第2のクロック信号を受信することと、

第2のベースバンド信号を受信することと、

前記第2のベースバンド信号と前記第2のクロック信号とに少なくとも部分的に基づいて第3の遅延されたクロック信号を生成することと、

10

20

30

40

50

前記第2のベースバンド信号と前記第2のクロック信号とに少なくとも部分的に基づいて第4の遅延されたクロック信号を生成することと

をさらに備え、

前記合成することは、前記変調されたクロック信号を生成するために、前記第1の遅延されたクロック信号と、前記第2の遅延されたクロック信号と、前記第3の遅延されたクロック信号と、前記第4の遅延されたクロック信号とを合成することをさらに備える、C

12に記載の方法。

[ C 2 1 ]

前記第2のクロック信号は、位相シフトによって前記第1のクロック信号に関係付けられる、C

20に記載の方法。

10

[ C 2 2 ]

変調されたクロック信号を生成するための変調器を備え、

前記変調器は、

第1のクロック信号および第1のベースバンド信号を受信し、前記第1のベースバンド信号に少なくとも部分的に基づいて第1の遅延されたクロック信号を生成するように構成された第1の構成可能遅延ユニットと、

前記第1のクロック信号および前記第1のベースバンド信号を受信し、前記第1のベースバンド信号に少なくとも部分的に基づいて第2の遅延されたクロック信号を生成するように構成された第2の構成可能遅延ユニットと、ここにおいて、前記第2の遅延されたクロック信号は前記第1の遅延されたクロック信号と異なる、

20

前記第1の遅延されたクロック信号と前記第2の遅延されたクロック信号とに少なくとも部分的に基づいて、前記変調されたクロック信号を生成するように構成された合成器と

を備える、システム。

[ C 2 3 ]

前記第1のベースバンド信号を受信し、前記第1の構成可能遅延ユニットに変更された第1のベースバンド信号を与えるように構成されたプリプロセッサをさらに備える、C

22に記載のシステム。

30

[ C 2 4 ]

前記プリプロセッサは、前記第1のベースバンド信号に予歪を与えるように構成される、C

23に記載のシステム。

[ C 2 5 ]

前記第1の遅延されたクロック信号を受信し、第1の増幅された遅延されたクロック信号を生成するように構成された第1のドライバと、

前記第2の遅延されたクロック信号を受信し、第2の増幅された遅延されたクロック信号を生成するように構成された第2のドライバと

をさらに備え、

前記合成器は、前記変調されたクロック信号を生成するために、前記第1の増幅された遅延されたクロック信号と前記第2の増幅された遅延されたクロック信号とを合成するようにさらに構成される、C

22に記載のシステム。

40

[ C 2 6 ]

前記変調器は、

第2のクロック信号および第2のベースバンド信号を受信し、前記第2のベースバンド信号に少なくとも部分的に基づいて第3の遅延されたクロック信号を生成するように構成された第3の構成可能遅延ユニットと、

前記第2のクロック信号および前記第2のベースバンド信号を受信し、前記第2のベースバンド信号に少なくとも部分的に基づいて第4の遅延されたクロック信号を生成するように構成された第4の構成可能遅延ユニットと

をさらに備え、

前記合成器は、前記変調されたクロック信号を生成するために、前記第1の遅延された

50

クロック信号と、前記第2の遅延されたクロック信号と、前記第3の遅延されたクロック信号と、前記第4の遅延されたクロック信号とを合成するようにさらに構成される、C22に記載のシステム。

[ C 2 7 ]

前記変調されたクロック信号を送信するように構成されたアンテナと、

前記アンテナに前記変調されたクロック信号を選択的に結合するように構成されたスイッチと

をさらに備えるC22に記載のシステム。

[ C 2 8 ]

前記変調器から前記変調されたクロック信号を受信し、前記スイッチにフィルタ処理された変調されたクロック信号を与えるように構成されたフィルタをさらに備えるC27に記載のシステム。

10

[ C 2 9 ]

前記フィルタは、ローパスフィルタプロファイル、バンドパスフィルタプロファイルおよびハイパスフィルタプロファイルのうちの少なくとも1つを有する、C28に記載のシステム。

[ C 3 0 ]

機械実行可能命令を記憶した非一時的機械可読記憶媒体であって、

前記機械実行可能命令は、

第1のクロック信号を受信することと、

第1のベースバンド信号を受信することと、

前記第1のベースバンド信号と前記第1のクロック信号とに少なくとも部分的に基づく第1の遅延量をもつ第1の遅延されたクロック信号を生成することと、

前記第1のベースバンド信号と前記第1のクロック信号とに少なくとも部分的に基づく第2の遅延量をもつ第2の遅延されたクロック信号を生成することと、ここにおいて、

前記第1の遅延量は前記第2の遅延量と異なる、

変調されたクロック信号を生成するために、前記第1の遅延されたクロック信号と前記第2の遅延されたクロック信号とを合成することと

を行うための命令を備える、非一時的機械可読記憶媒体。

20

【 図 1 】

図 1

FIG.1

【 四 2 】

四

卷之二

FIG 2

【 四 3 】

FIG.3

【 义 4 】

FIG. 4

【図5】

図5

【図6】

図6

FIG. 6

FIG.5

---

フロントページの続き

(72)発明者 タルワルカ、ニランジャン・アナンド

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775

(72)発明者 カスツリア、サンジャイ

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775

審査官 高 橋 徳浩

(56)参考文献 米国特許出願公開第2009/0149151(US, A1)

米国特許出願公開第2011/0044404(US, A1)

特開2013-115700(JP, A)

米国特許出願公開第2009/0146754(US, A1)

特表2010-507965(JP, A)

米国特許出願公開第2007/0273436(US, A1)

特開平05-083502(JP, A)

(58)調査した分野(Int.Cl., DB名)

H04B 1/04

H03C3/00 - H03C99/00

H04B1/38 - H04B1/40

H04L27/00 - H04L27/38