(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2016년08월08일

(11) 등록번호 10-1646614

(24) 등록일자 2016년08월02일

- (51) 국제특허분류(Int. Cl.)

*G06F 17/50* (2006.01) *H03H 9/46* (2006.01)

- (21) 출원번호 10-2014-7037093

(22) 출원일자(국제) 2014년02월27일

심사청구일자 2014년12월31일

(85) 번역문제출일자 2014년12월31일

(65) 공개번호 10-2015-0023564

(43) 공개일자 2015년03월05일

(86) 국제출원번호 PCT/US2014/019106

(87) 국제공개번호 WO 2014/149507

국제공개일자 2014년09월25일

(30) 우선권주장

61/802,114 2013년03월15일 미국(US)

13/939,763 2013년07월11일 미국(US)

(56) 선행기술조사문헌

KR1020100037116 A

JP2003243966 A

US20040044971 A1

- (73) 특허권자

**데저넌트 인크.**

미국 93117 캘리포니아주 산타 바바라 스위트 100

캐스틸리안 드라이브 110

(72) 발명자

**펜지, 닐**

미국 93111 캘리포니아주 산타 바바라 버티스 스

트리트 650

**라인, 커트**

미국 93117 캘리포니아주 골레타 에이피티. 지 캐

는 그린 드라이브 487

(74) 대리인

**양영준, 백만기, 정은진**

전체 청구항 수 : 총 19 항

심사관 : 박승철

## (54) 발명의 명칭 마이크로웨이브 필터들에서의 소자 제거 설계

**(57) 요약**

컴퓨터화된 필터 최적화기를 이용하여 마이크로웨이브 필터를 설계하는 방법은, 복수의 공진 소자들 및 하나 이상의 비공진 소자들을 갖는 복수의 회로 소자들을 포함하는 필터 회로 DIP(design in process)를 생성하는 단계와, 상기 DIP를 상기 컴퓨터화된 필터 최적화기에 입력함으로써 상기 DIP를 최적화하는 단계와, 상기 DIP에서 복수의 회로 소자들 중 하나가 중요하지 않다고(significant) 결정하는 단계와, 상기 DIP로부터 상기 하나의 중요하지 않은 회로 소자를 제거하는 단계와, 상기 DIP로부터 최종 필터 회로 설계를 도출하는 단계와, 상기 최종 필터 회로 설계를 기반으로 상기 마이크로웨이브 필터를 제조하는 단계를 포함한다.

**대 표 도**

## 명세서

### 청구범위

#### 청구항 1

컴퓨터화된 필터 최적화기(300)를 이용하여 마이크로웨이브 필터를 설계하는 방법으로서,

(a) 복수의 공진 소자들(202) 및 하나 이상의 비공진 소자들(204)을 갖는 복수의 회로 소자들을 포함하는 필터 회로 DIP(design in process)(200)를 생성하는 단계(단계 102);

(b) 상기 DIP(200)를 상기 컴퓨터화된 필터 최적화기(300)에 입력함으로써 상기 DIP(200)를 최적화하는 단계(단계 104);

(c) 상기 DIP(200)가 최적화된 후 상기 DIP(200)에서 상기 복수의 회로 소자들 중 하나가 중요하지 않다고 (insignificant) 결정하는 단계(단계 106, 114);

(d) 상기 DIP(200)로부터 상기 하나의 중요하지 않은 회로 소자를 제거하는 단계(단계 110);

(e) 상기 DIP(200)로부터 최종 필터 회로 설계를 도출하는 단계(단계 118); 및

(f) 상기 최종 필터 회로 설계를 기반으로 상기 마이크로웨이브 필터를 제조하는 단계(단계 120)

를 포함하는 방법.

#### 청구항 2

제1항에 있어서, 상기 하나의 중요하지 않은 회로 소자는 인덕턴스 및 커패시턴스 중 하나를 초기에 포함하는 비공진 소자(204)이며, 상기 방법은, 상기 비공진 소자를 제거하기 이전에,

상기 인덕턴스 및 커패시턴스 중 하나에서 상기 인덕턴스 및 커패시턴스 중 다른 하나로 상기 하나의 중요하지 않은 회로 소자를 변환함에 의해 변환된 필터 회로 설계를 생성하는 단계(단계 112);

상기 변환된 필터 회로 설계를 상기 컴퓨터화된 필터 최적화기(300)에 입력함에 의해 상기 DIP(200)를 다시 최적화하는 단계(단계 104); 및

상기 DIP(200)에서 상기 하나의 중요하지 않은 회로 소자가 중요하지 않음을 확인하는 단계(단계 106)

를 더 포함하는 방법.

#### 청구항 3

제1항에 있어서, 상기 하나의 중요하지 않은 회로 소자는 초기에 공진 소자(202)이며, 상기 방법은, 상기 하나의 중요하지 않은 회로 소자를 제거하기 이전에,

상기 공진 소자(202)에서 정적 커패시턴스로 상기 하나의 중요하지 않은 회로 소자를 변환함에 의해 변환된 필터 회로 설계를 생성하는 단계(단계 116);

상기 변환된 필터 회로 설계를 상기 컴퓨터화된 필터 최적화기(300)에 입력함에 의해 상기 DIP(200)를 다시 최적화하는 단계; 및

상기 DIP(200)에서 상기 하나의 중요하지 않은 회로 소자가 중요하지 않음을 확인하는 단계(단계 106)

를 더 포함하는 방법.

#### 청구항 4

제1항에 있어서, 상기 DIP(200)로부터 상기 하나의 중요하지 않은 회로 소자를 제거하는 것은 감소된 필터 회로 설계를 가져오며, 상기 방법은,

(g) 상기 감소된 필터 회로 설계를 상기 컴퓨터화된 필터 최적화기(300)에 입력함으로써 상기 DIP(200)를 다시 최적화하는 단계(단계 104);

- (h) 상기 DIP(200)가 다시 최적화된 후 상기 DIP(200)에서 상기 복수의 회로 소자들 중 다른 하나가 중요하지 않다고 결정하는 단계(단계 106, 114); 및

- (i) 상기 DIP(200)로부터 상기 다른 하나의 중요하지 않은 회로 소자를 제거하는 단계(단계 110)를 더 포함하는 방법.

#### 청구항 5

제4항에 있어서, 상기 하나의 중요하지 않은 회로 소자는 비공진 소자(204)이며, 상기 다른 중요하지 않은 회로 소자는 공진 소자(202)인, 방법.

#### 청구항 6

제4항에 있어서, 상기 DIP(200)에서의 회로 소자들 중 중요하지 않다고 결정되는 것이 없을 때까지 상기 단계(g)-(i)를 반복하여 적어도 하나의 부가된 감소 필터 회로 설계를 생성하는 단계를 더 포함하며, 상기 최종 필터 회로 설계는 최종 최적화된 DIP(200)와 동일한, 방법.

#### 청구항 7

제1항에 있어서, 상기 하나의 중요하지 않은 회로 소자는 비공진 소자(204)인, 방법.

#### 청구항 8

제7항에 있어서, 상기 비공진 소자(204)가 중요하지 않은지를 결정하는 단계는 상기 비공진 소자의 값을 임계치와 비교하는 단계를 포함하는, 방법.

#### 청구항 9

제8항에 있어서, 상기 비공진 소자(204)의 값은 임피던스 절대치인, 방법.

#### 청구항 10

제9항에 있어서, 상기 비공진 소자(204)는 상기 임피던스 절대치가 상기 임계치보다 작은 경우 중요하지 않다고 결정되는 직렬 인덕터 또는 션트 커패시터 중 하나인, 방법.

#### 청구항 11

제9항에 있어서, 상기 비공진 소자(204)는 상기 임피던스 절대치가 상기 임계치보다 큰 경우 중요하지 않다고 결정되는 션트 인덕터 또는 직렬 커패시터 중 하나인, 방법.

#### 청구항 12

제8항에 있어서, 상기 비공진 소자(204)의 값은 상대치인, 방법.

#### 청구항 13

제12항에 있어서, 상기 비공진 소자(204)는 직렬 회로 소자이며, 상기 상대치는 상기 DIP(200)에서 다른 직렬 회로 소자의 절대치에 대한 상기 직렬 회로 소자의 절대치의 퍼센티지이고, 상기 직렬 회로 소자는 상기 상대치가 상기 임계치보다 작은 경우 중요하지 않다고 결정되는, 방법.

#### 청구항 14

제12항에 있어서, 상기 비공진 소자(204)는 션트 회로 소자이며, 상기 상대치는 상기 DIP(200)에서 다른 션트 회로 소자의 절대치에 대한 상기 션트 회로 소자의 절대치의 퍼센티지이고, 상기 션트 회로 소자는 상기 상대치가 상기 임계치보다 작은 경우 중요하지 않다고 결정되는, 방법.

#### 청구항 15

제12항에 있어서, 상기 비공진 소자(204)는 직렬 회로 소자이며, 상기 상대치는 상기 직렬 회로 소자로부터의 어느 한 방향에서 본 임피던스에 대한 상기 직렬 회로의 절대치의 퍼센티지이고, 상기 직렬 회로 소자는 상기

상대치가 상기 임계치보다 작은 경우 중요하지 않다고 결정되는, 방법.

#### 청구항 16

제12항에 있어서, 상기 비공진 소자(204)는 션트 회로 소자이며, 상기 상대치는 상기 션트 회로 소자로부터의 어느 한 방향에서 본 서셉턴스(susceptance)에 대한 상기 션트 회로 소자의 절대치의 퍼센티지이고, 상기 션트 회로 소자는 상기 상대치가 상기 임계치보다 작은 경우 중요하지 않다고 결정되는, 방법.

#### 청구항 17

제7항에 있어서, 상기 비공진 소자(204)가 중요하지 않은지 결정하는 단계는, 상기 최적화된 회로 설계로부터 상기 비공진 소자를 제거하는 단계, 및 상기 비공진 소자(204)가 없는 최적화된 회로 설계에서의 성능 파라미터의 값을 상기 비공진 소자(204)를 갖는 최적화된 회로 설계에서의 성능 파라미터의 값과 비교하는 단계를 포함하는, 방법.

#### 청구항 18

제1항에 있어서, 상기 하나의 중요하지 않은 회로 소자는 공진 소자(202)인, 방법.

#### 청구항 19

제18항에 있어서, 상기 DIP(200)는 통과대역 및 저지대역 중 하나 또는 모두를 갖는 주파수 응답을 가지며, 상기 공진 소자(202)가 중요하지 않은지를 결정하는 단계는, 상기 공진 소자와 연관된 송신 제로를 상기 통과대역 및 상기 저지대역 중 하나 또는 모두의 에지 주파수와 비교하는 단계를 포함하는, 방법.

#### 청구항 20

삭제

#### 청구항 21

삭제

#### 청구항 22

삭제

#### 청구항 23

삭제

### 발명의 설명

#### 기술 분야

[0001] 본 발명은 일반적으로 마이크로웨이브 필터들에 관한 것으로, 특히 협대역 어플리케이션으로 설계된 음파 마이크로웨이브 필터들에 관한 것이다.

#### 배경 기술

[0002] 전기 필터는 전기 신호의 처리에 오랫동안 사용되었다. 특히, 이런 전기 필터는 원하는 신호 주파수를 통과시키면서 다른 원치않는 전기 신호 주파수를 차단 또는 감쇄함으로써, 입력 신호로부터 원하는 전기 신호 주파수를 선택하는데 사용된다. 필터는 저역 통과 필터, 고역 통과 필터, 대역 통과 필터, 대역 저지 필터를 포함하며, 필터에 의해 선택적으로 통과되는 주파수의 타입을 나타내는 일부 범용 카테고리로 분류될 수 있다. 더욱이, 필터는 대역형상 주파수 응답의 타입(주파수 컷오프 특성)을 나타내는 버터워스(Butterworth), 체비체브(Chebyshev), 인버스 체비체브(Inverse Chebyshev) 및 엘립틱(Elliptic)과 같은 타입으로 분류될 수 있다.

[0003] 필터의 타입은 종종 사용 목적에 따라 달라진다. 통신 어플리케이션에서, 대역 통과 및 대역 저지 필터들은, 하나 이상의 미리 정의된 대역을 제외한 모든 대역들에서 RF 신호를 걸러내거나 차단하기 위해 셀룰러 기지국, 셀폰 핸드셋, 및 다른 통신 설비에서 종래에 사용되었다. 특히 중요한 것은 대략 500-3,500MHz의 주파수 범위

이다.

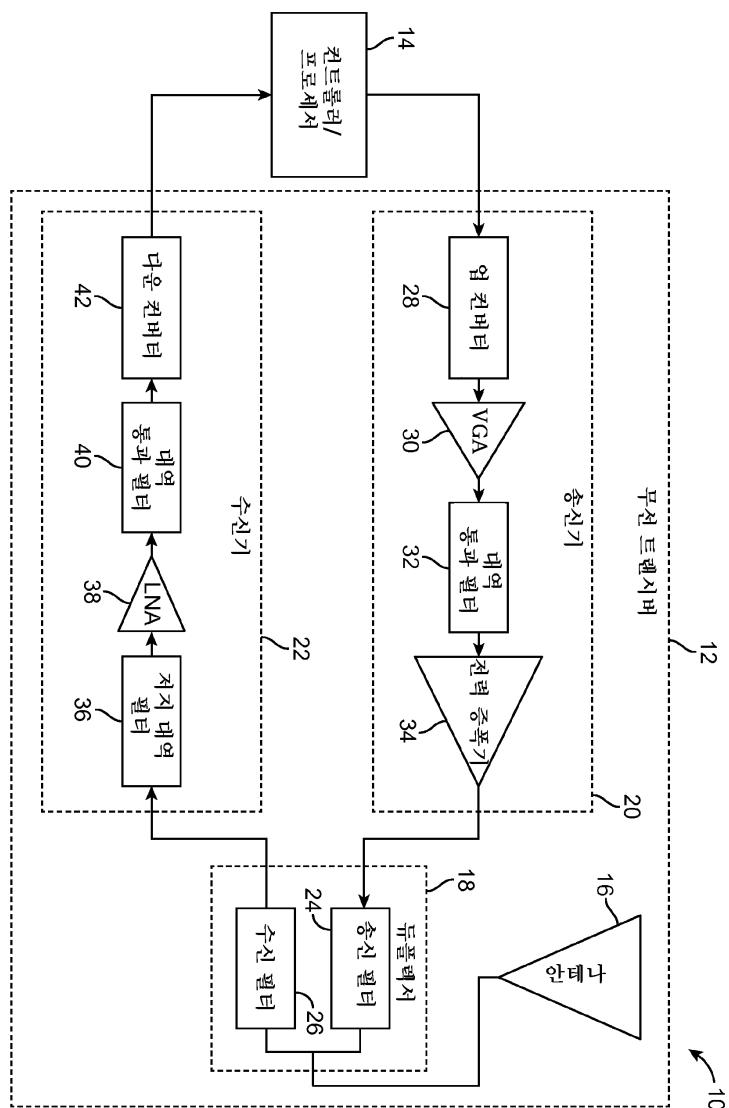

[0004] 도 1을 참고하면, 종래의 통신 시스템(10)은 무선 신호를 송신 및 수신할 수 있는 트랜시버(12), 및 트랜시버(12)의 기능을 제어할 수 있는 컨트롤러/프로세서(14)를 포함한다.

[0005] 트랜시버(12)는 일반적으로 광대역 안테나(16), 송신 필터(24) 및 수신 필터(26)를 갖는 듀플렉서(18), 듀플렉서(18)의 송신 필터(24)를 통해 안테나(16)에 결합된 송신기(20), 및 듀플렉서(18)의 수신 필터(26)를 통해 안테나(16)에 결합된 수신기(22)를 포함한다.

[0006] 송신기(20)는 컨트롤러/프로세서(14)에 의해 제공된 대역통과 신호를 무선 주파수(RF) 신호로 변환하도록 구성된 업컨버터(28), RF 신호를 증폭하도록 구성된 가변 이득 증폭기(VGA)(30), RF 신호를 컨트롤러/프로세서(14)에 의해 선택된 동작 주파수에서 출력하도록 구성된 대역통과 필터(32), 및 필터링된 RF 신호를 증폭하도록 구성된 전력 증폭기(34)를 포함하고, 증폭된 RF 신호는 듀플렉서(18)의 송신 필터(24)를 통해 안테나(16)에 제공된다.

[0007] 수신기(22)는 수신 필터(26)를 통해 안테나(16)로부터 입력된 RF 신호로부터 송신 신호 간섭을 소거하도록 구성된 노치(notch) 또는 저지대역 필터(36), 저지대역 필터(36)로부터의 RF 신호를 비교적 낮은 노이즈로 증폭하도록 구성된 LNA(low noise amplifier)(38), 컨트롤러/프로세서(14)에 의해 선택된 주파수에서 증폭된 RF 신호를 출력하도록 구성된 조정가능한 대역통과 필터(40), 및 RF 신호를 컨트롤러/프로세서(14)에 제공되는 기저대역 신호로 다운컨버팅하도록 구성된 다운컨버터(42)를 포함한다. 대안적으로, 저지대역 필터(36)에 의해 수행되는 송신 신호 간섭을 제거하는 기능은 듀플렉서(18)에 의해 대신 수행될 수 있다. 또는, 송신기(20)의 전력 증폭기(34)는 송신 신호 간섭을 감소시키도록 설계될 수 있다.

[0008] 도 1에 도시된 블록도는 본질적으로 기능도이며, 여러 기능들이 하나의 전자 컴포넌트에 의해 수행될 수 있거나 하나의 기능이 여러 전자 컴포넌트들에 의해 수행될 수 있음을 이해해야 한다. 예컨대, 업 컨버터(28), VGA(30), 대역통과 필터(40), 다운컨버터(42), 및 컨트롤러/프로세서(14)에 의해 수행되는 기능들은 종종 단일 트랜시버 칩에 의해 수행된다. 대역통과 필터(32)의 기능은 전력 증폭기(34) 및 듀플렉서(18)의 송신 필터(24)에 있을 수 있다.

[0009] 마이크로웨이브 필터는 일반적으로 2개의 회로 빌딩 블록들, 즉 공진 주파수(기본 공진 주파수  $f_0$  또는 여러 고차 공진 주파수들  $f_1-f_n$  중 어느 하나일 수 있음)에서 에너지를 매우 효율적으로 저장하는 복수의 공진기들, 및 공진기들 사이에서 전자기 에너지를 커플링하여 넓은 스펙트럼 응답을 제공하는 다수의 반사 제로들(reflection zeros)을 형성하는 커플링(coupling)들을 이용하여 구축된다. 예컨대, 4-공진기 필터는 4개의 반사 제로들을 포함한다. 본 명세서에서 반사 제로란 인더턴스 및 커페시턴스가 소거되고 최소량의 전력이 반사되는 필터 반사 함수의 루트(root)들을 말한다. 소정 커플링의 강도는 그 리액턴스(즉, 인더턴스 및/또는 커페시턴스)에 의해 결정된다. 커플링의 상태 강도는 필터 형상을 결정하며, 커플링의 토플로지는 필터가 대역 통과를 수행하는지 대역 저지 기능을 수행하는지를 결정한다. 공진 주파수  $f_0$ 는 각각의 공진기의 인더턴스 및 커페시턴스에 의해 주로 결정된다. 종래의 필터 설계에서, 필터가 활성인 주파수는 필터를 형성하는 공진기의 공진 주파수에 의해 결정된다. 각각의 공진기는 전술한 이유로 필터의 응답이 첨예(sharp)하고 매우 선택적인 것이 가능하도록 매우 낮은 내부 저항을 가져야만 한다. 이런 낮은 저항의 요건은 소정 기술에 대해 공진기의 크기 및 비용을 드라이브하는 경향이 있다.

[0010] 전단 수신 필터(예컨대, 도 1에 도시된 수신 필터(26))는 바람직하게 원하는 수신 신호 주파수 근방의 주파수에서의 강한 간섭 주파수에 기인하는 여러 역효과를 제거하기 위하여 첨예하게(sharply) 정의된 대역 통과 필터의 형태를 취한다. 안테나 입력에서 전단 수신기 필터의 위치 때문에, 삽입 손실은 노이즈 수치를 저하시키지 않도록 매우 낮아야 한다. 대부분의 필터 기술에서, 낮은 삽입 손실을 달성하려면 필터 첨예도(steepleness) 또는 선택성에서 대응하는 타협점을 요구한다. 실제로, 셀폰 핸드셋용의 대부분의 필터들은 음파 공진기 기술, 예컨대 SAW(surface acoustic wave), BAW(bulk acoustic wave), 및 FBAR(film bulk acoustic resonator) 기술을 이용하여 구성된다. 이런 음파 공진기 필터들은 균등한 인더터/커페시터 공진기에 비해 낮은 삽입 손실, 컴팩트한 크기 및 저 비용의 이점을 가진다.

[0011] 실제 마이크로웨이브 필터의 설계는 예컨대 이미지 설계 또는 네트워크 합성 설계를 이용하여 생성되는 초기 회로의 설계에서 출발한다. 이런 접근법들은 일반적으로 시초부터 가능한 가장 적은 수의 회로 소자를 갖는 회로만을 고려한다. 이는 일반적으로 최종 필터에서 손실을 최소화하려는 요구에서 수행되고, 모든 타입의 마이크로웨이브 필터 설계에서 공통적인 관행이다. 초기 설계는 단순화된 이상적인 회로 소자 모델들을 이용해 생성

될 수 있고, 이러한 모델들은 최종 필터를 만들기 위해 사용된 물리적 회로 소자들의 손실 및 다른 원치않는 특성을 전형적으로 무시할 수 있다. 실제 마이크로웨이브 필터의 설계에서 컴퓨터 최적화는 결정적이고 필수적인 단계이다. 무엇보다도, 애질런트(Agilent) ADS(Advanced Design System)를 포함하는 설계 툴은 "초기 회로 설계"를 개선하기 위하여 몬테카를로(Monte Carlo), 그래디언트(gradient) 등과 같은 수치 최적화 방법을 이용할 수 있다. 이런 컴퓨터 최적화 단계는 점점 더 현실적이고 정확한 회로 소자 모델들을 사용할 수 있고, 회로 소자 값을 최종 필터 설계에 따라 제조될 수 있는 값으로 제한할 수 있다. 최적화는 원하는 필터 응답에 가장 잘 정합하는 회로 소자 값의 조합을 찾을 수 있다. 이런 타입의 컴퓨터 최적화는 마이크로웨이브 필터 설계에서 종종 사용될 수 있다. 최적화는 일반적으로 물리 회로 소자로 구현될 수 있는 크게 개선된 설계를 생성할 수 있기는 하지만, 최적화는 일반적으로 최종 회로 설계에서의 회로 소자의 수를 초기 회로 설계에서의 회로 소자들의 수로부터 감소시킬 수 있으며, 또한 최적화는 회로 소자의 한 타입을 다른 타입으로 변경할 수도 없다.

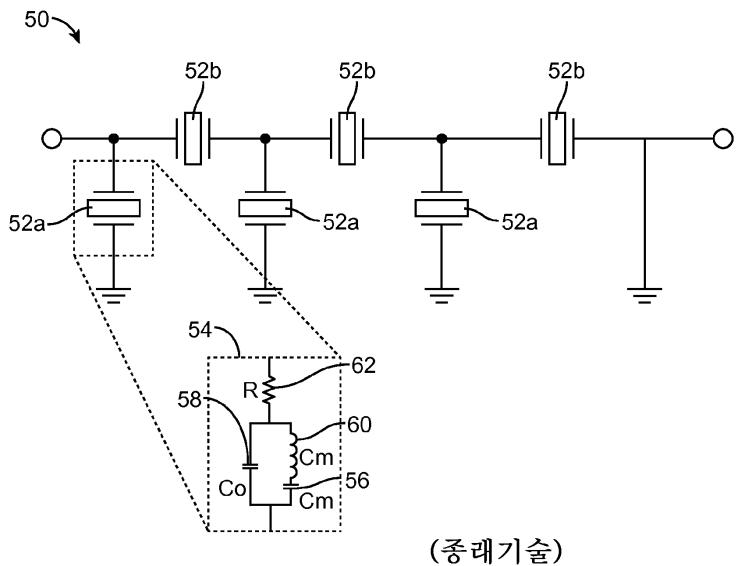

[0012] 예컨대, 음파 대역 통과 필터의 설계에 전형적으로 사용되는 하나의 초기 회로는 도 2에 도시된 바와 같이 다수의 교변하는 션트(shunt) 공진기들(52a) 및 직렬 공진기들(52b)을 포함하는 래더(ladder) 필터(50)이다. 필터(50)는 N개의 공진기 래더 토플로지로 고려될 수 있다(N은 공진기의 수이며, 이 경우 6이다). 본 명세서에서, 음파 래더 필터란 교변하는 직렬 및 션트 음파 공진기들을 포함하는 메이슨-타입(Mason-type) 음파 래더 회로 구조를 이용하는 하나 이상의 필터를 말한다.

[0013] 각각의 음파 공진기(52)는 MBVD(modified Butterworth-Van Dyke) 모델(54)로 표현될 수 있다. MBVD 모델(54)은 결정 석영, 리튬 니오베이트(LiNbO<sub>3</sub>), 리튬 탄탈레이트(LiTaO<sub>3</sub>) 결정 또는 BAW 공진기와 같은, 압전 기판상에 인터디지털 트랜스듀서(interdigital transducer)(IDT)들을 배치함으로써 만들어질 수 있는 SAW 공진기를 또한 표현할 수 있다. 각각의 MBVD 모델(54)은 운동 커페시턴스(motional capacitance) C<sub>m</sub>(56), 정적 커페시턴스(static capacitance) C<sub>o</sub>(58), 운동 인덕턴스 L<sub>m</sub>(60) 및 저항 R(62)을 포함한다. 운동 커페시턴스 C<sub>m</sub>(56) 및 운동 인덕턴스 L<sub>m</sub>(60)는 전기 음파 행위의 상호작용으로부터 유발될 수 있으며, 그 결과 MBVD 모델(54)의 운동 암(arm)으로서 언급될 수 있다. 정적 커페시턴스 C<sub>o</sub>(58)는 구조의 고유 커페시턴스로부터 유발될 수 있으며, 그 결과 MBVD 모델(54)의 정적(비운동) 커페시턴스로서 언급될 수 있다. 저항 R(62)은 음파 공진기(52)의 전기 저항으로부터 유발될 수 있다. 파라미터들은 다음의 수학식들에 의해 관련된다:

### 수학식 1

$$\omega_R = \frac{1}{\sqrt{L_m C_m}}$$

[0014]

### 수학식 2

$$\frac{\omega_A}{\omega_R} = \sqrt{1 + \frac{1}{\gamma}}$$

[0015]

[0016] 여기서  $\omega_R$  및  $\omega_A$ 는 어느 주어진 음파 공진기에 대한 각각의 공진 및 반공진 주파수들이며, 감마  $\gamma$ 는 다음의 수학식 3에 의해 더 정의될 수 있는 물질 속성에 따라 달라질 수 있다.

### 수학식 3

$$\frac{C_0}{C_m} = \gamma$$

[0017]

[0018] 전형적인  $\gamma$  값은 42도 X Y 컷 LiTaO<sub>3</sub>에 대해 약 12 내지 약 18의 범위에 있다.

[0019] 수학식 1로부터 각각의 음파 공진기(52)의 공진 주파수는 MBVD 모델(54)의 운동 암에 따라 달라질 것이며, 반면에 필터 특성(예컨대, 대역폭)은 수학식 2에서의  $\gamma$ 에 의해 결정될 수 있음을 이해할 수 있다. 음파 공진기(52)에 대한 품질 팩터(Q)는 필터 내의 소자의 손실에 관련하여, 음파 필터 설계에서 중요한 성능 지수일 수 있다. 회로 소자의 Q는 사이클당 저장된 에너지와 사이클당 소실되는 에너지의 비율을 나타낸다. Q 팩터는 각각의 음파 공진기(52)에서의 실제 손실을 모델링하며, 일반적으로 둘 이상의 Q 팩터들이 음파 공진기(52)의 손실을 기술하는데 요구될 수 있다. Q 팩터는 필터 예들에 대해 다음과 같이 정의될 수 있다. 운동 커패시턴스  $C_m$ (56)는  $QC_m=1.0E+8$ 로서 정의되는 연관된 Q를 가질 수 있으며, 정적 커패시턴스  $C_o$ (58)는  $QC_o=200$ 으로서 정의되는 연관된 Q를 가질 수 있고, 운동 인덕턴스  $L_m$ (60)은  $QL_m=1000$ 으로서 정의되는 연관된 Q를 가질 수 있다. 회로 설계자는 전형적으로 SAW 공진기를, 공진 주파수  $\omega_R$ , 정적 커패시턴스  $C_o$ , 감마  $\gamma$  및 품질 팩터  $QL_m$ 으로 특징화할 수 있다. 상용 어플리케이션에서,  $QL_m$ 은 SAW 공진기에서는 약 1000이며, BAW 공진기에서는 약 3000일 수 있다.

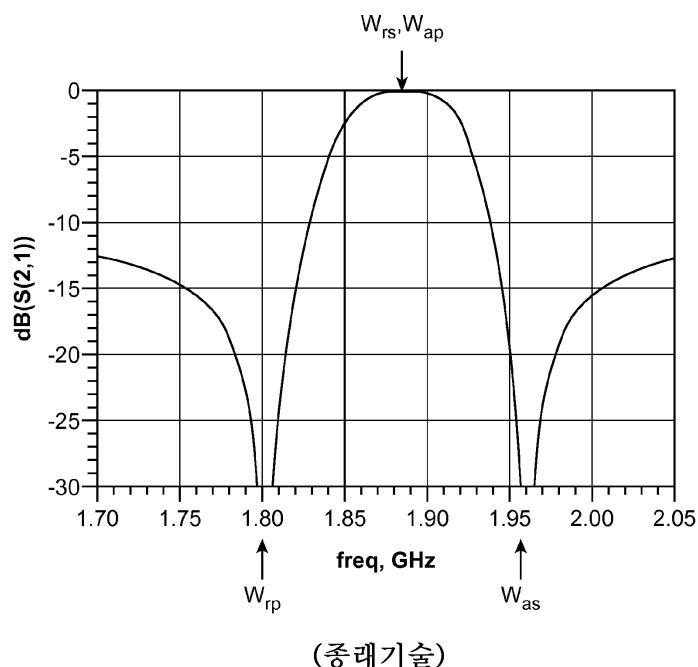

[0020] 도 3에 도시된 필터(50)에 대한 주파수 응답은 데시벨(dB) 대 주파수  $f$ 의 대수 단위로 필터 응답에 대한 산란 매트릭스(scattering matrices)  $|S21|^2$  (삽입 손실) 및  $|S11|^2$  (복귀 손실)을 나타낸다. 각각의 션트 공진기(52a)의 공진 및 반공진 주파수들을  $\omega_{rp}$  및  $\omega_{ap}$ 로 명명하고, 각각의 직렬 공진기(52b)의 공진 및 반공진 주파수들을  $\omega_{rs}$  및  $\omega_{as}$ 로 명명한다. 도 3에 예시된 필터 응답에 도시된 바와 같이,  $\omega_{rs}$  및  $\omega_{ap}$ 가 서로 대략 동일한 경우,  $\omega=\omega_{rs}$ ,  $\omega_{ap}$  근처에 중심을 둔 통과대역이 생성되고, 통과 대역 예지를 정의하는  $\omega=\omega_{rp}$ ,  $\omega_{as}$ 에서의 송신 제로들이 생성된다. 본 명세서에서, 송신 제로란 최대 전력량이 반사되는 필터의 송신 함수의 루트를 말한다. 통과대역 중심 주파수  $\omega_p$ 로부터 먼 주파수  $f$ 에서, 공진기는 대략 커패시터로 작용하여, 큰  $|\omega-\omega_p|$ 에 대해 점근적으로 일정하게 되는 윙(wing)을 형성하는  $|S21|^2$  필터 응답을 가져오며 대역외 저지(out-of-band rejection)를 제공한다.

[0021] 대역 통과 필터 응답은 복귀 손실(즉, 중심 통과대역 주파수  $\omega_p$ 에서의  $|S11|^2$ 의 값), 삽입 손실(즉, 중심 통과대역 주파수  $\omega_p$ 에서의  $|S21|^2$ 의 값), 통과대역 폭(PBW), 및 대역외 저지  $\varepsilon$  (즉, 큰  $|\omega-\omega_p|$ 에서  $1/|S21|$ )로 특징화될 수 있다. 대역 통과 래더 필터는 이를 파라미터들의 제한된 액세스 가능한 범위에 대해서만 설계될 수 있고, 그 범위는 물질 파라미터 값  $\gamma$  및 공진기의 수(필터 차수로 명명)에 따라 달라진다. SAW 및 BAW 필터용의 물질에 현재 널리 사용되는 물질 파라미터 값  $\gamma$ 는 12-14의 범위에 있으면서, 공진 주파수 및 공진방지 주파수가 통과대역 중심 주파수  $\omega_p$ 에 근접하는 것을 허용하여,  $|S21|^2$  필터 응답에서 비교적 좁은 통과대역을 생성한다. 4의 물질 파라미터 값  $\gamma$ 를 갖는 물질이 현재 개발중이다. 보다 작은 물질 파라미터 값  $\gamma$ 는 넓은 통과대역 폭(PBW)을 가능케 하여 복귀 손실(RL)을 감소시키거나, 대역외 저지  $\varepsilon$ 를 개선할 것이다.

[0022] 고정 통과대역 폭(PBW)에서, 대역외 저지  $\varepsilon$ 가 증가함에 따라, 복귀 손실(RL)은 감소한다. 일부 경우에, 수동 회로 소자가 필터 성능을 개선하기 위해 래더 구조에 결합된다. 예컨대, 인덕터의 추가는 유효 물질 파라미터 값  $\gamma$ 를 감소시킬 수 있고, 이는 통과대역 폭(PBW)을 증가시키거나, 복귀 손실(RL)을 감소시키거나 대역외 저지  $\varepsilon$ 를 개선할 수 있다. 그러나, 인덕터의 추가로부터 얻는 이점은 증가된 삽입 손실, 크기 및 비용의 대가로 온다. 대역 통과 필터 파라미터들은 성능을 최대화하기 위하여 액세스 가능한 범위의 한계로 떠밀리는데, 파라미터들 사이의 트레이드오프(tradeoff)는 시스템 어플리케이션 및 요건에 따라 변한다. 더 고차인 필터는 소정의 통과대역 복귀 손실(RL) 및 통과대역 폭(PBW)에서 더 큰 대역외 저지  $\varepsilon$ 를 달성할 수 있다.

[0023]

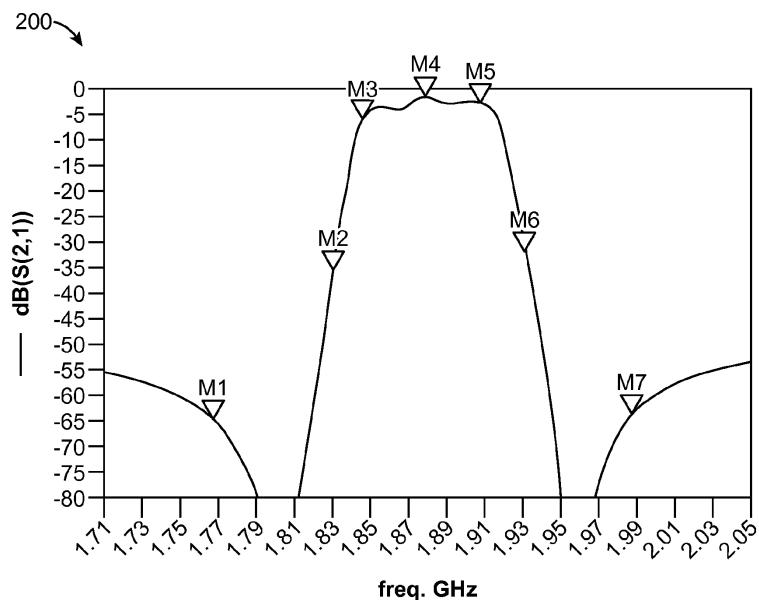

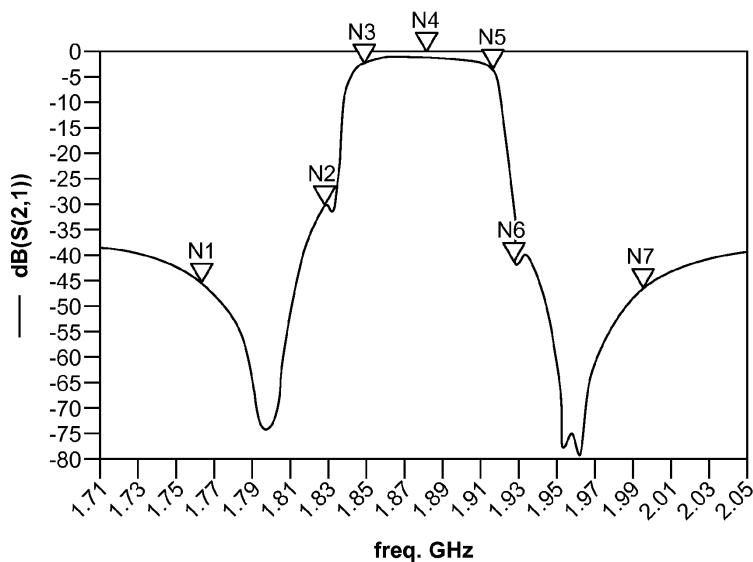

간략히 전술한 바와 같이, 필터(50)는 최종 회로 설계를 생성하기 위해 적당한 컴퓨터 최적화 기술(예컨대, 애질런트(Agilent) ADS 소프트웨어)를 통해 최적화될 수 있는 초기 회로 설계를 가질 수 있다. 예컨대, 필터(50)는 처음에 도 4a에 도시된 바와 같은 각각의 공진기(52)에 대한 공진 주파수  $\omega_R$  및 정적 커패시턴스  $C_0$ 를 갖고 설계될 수 있으며, 시뮬레이션시 도 4b에 도시된 바와 같은 주파수 응답을 가져온다. 이런 주파수 응답은 다음의 표시(marker)들로 특징화되어 나타난다: 주파수 = 1.770GHz에서 Mag S21 = -65.71dB의 M1; 주파수 = 1.830GHz에서 Mag S21 = -36.735dB의 M2; 주파수 = 1.850GHz에서 Mag S21 = -4.367dB의 M3; 주파수 = 1.879GHz에서 Mag S21 = -1.444dB의 M4; 주파수 = 1.910GHz에서 Mag S21 = -2.680dB의 M5; 주파수 = 1.930GHz에서 Mag S21 = -30.118dB의 M6; 및 주파수 = 1.990GHz에서 Mag S21 = -62.874dB의 M7.

[0024]

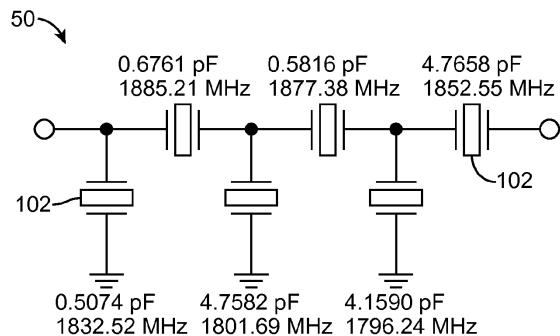

최적화 후, 필터(50)는 도 5a에 도시된 바와 같이 각각의 공진기(52)에 대한 공진 주파수  $\omega_R$  및 정적 커패시턴스  $C_0$ 를 가질 수 있으며, 시뮬레이션시 도 5b에 도시된 바와 같은 주파수 응답을 가져온다. 이런 주파수 응답은 다음의 표시들로 특징화되어 나타난다: 주파수 = 1.770GHz에서 Mag S21 = -46.943dB의 N1; 주파수 = 1.829GHz에서 Mag S21 = -29.865dB의 N2; 주파수 = 1.851GHz에서 Mag S21 = -1.479dB의 N3; 주파수 = 1.875GHz에서 Mag S21 = -0.833dB의 N4; 주파수 = 1.910GHz에서 Mag S21 = -1.898dB의 N5; 주파수 = 1.929GHz에서 Mag S21 = -41.977dB의 N6; 및 주파수 = 1.990GHz에서 Mag S21 = -47.182dB의 N7.

[0025]

전술한 내용으로부터, 공진기(52)에 대한 MBVD 모델(54)의 값이 주파수 응답에서의 개선으로 최적화되게 변경되었음을 이해할 것이다. 그러나, 회로 소자의 타입 및 수는 변하지 않고, 따라서 최종 회로의 풋프린트 또는 비용은 감소하지 않는다. 따라서, 일반적으로 마이크로웨이브 필터에서, 그리고 특히, 수동 소자들을 포함하며 및/또는 더욱 복잡한 셕션들을 가진 현대의 네트워크 이론 또는 이미지 이론과 같은 더욱 복잡한 설계 기술을 이용하는 필터 설계에서는, 개선된 최적화 방법이 요구된다.

### 도면의 간단한 설명

[0026]

본 발명의 바람직한 실시예들의 설계 및 활용을 도시한 도면에서는 유사한 구성요소가 공통 도면부호로 언급된다. 본 발명의 전술한 또한 다른 이점 및 목적들이 얻어질 수 있는 방법을 잘 이해할 수 있도록, 간략하게 전술한 본 발명의 보다 상세한 설명이, 첨부된 도면에 예시되어 있는 특정 실시예들을 참고하여 설명될 것이다. 이들 도면이 본 발명의 하나의 전형적인 실시예만을 도시하며 이에 따라 본 발명의 범위를 제한하는 것으로 여겨서는 안 되는 것을 이해하면서, 본 발명은 첨부 도면을 사용해 보다 상세히 후술될 것이다.

도 1은 종래의 무선 통신 시스템을 도시한 블록도이다.

도 2는 종래의 무선 통신 시스템에서 사용될 수 있는 종래의 음파 래더 필터를 도시한 개요도이다.

도 3은 도 2의 종래의 음파 래더 필터의 주파수 응답도이다.

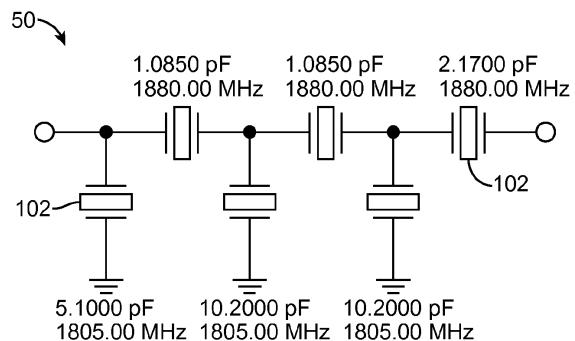

도 4a는 종래의 필터 최적화 기술을 이용하여 최적화될 수 있는 도 2의 음파 래더 필터의 초기 회로 설계를 도시한 개요도이다.

도 4b는 도 4a의 초기 회로 설계의 주파수 응답도이다.

도 5a는 종래의 필터 최적화 기술을 이용하여 도 4a의 초기 필터 회로 설계의 최적화로부터 얻어진 도 2의 음파 래더 필터의 최적화된 최종 회로 설계를 도시한 개요도이다.

도 5b는 도 5a의 최종 회로 설계의 주파수 응답도이다.

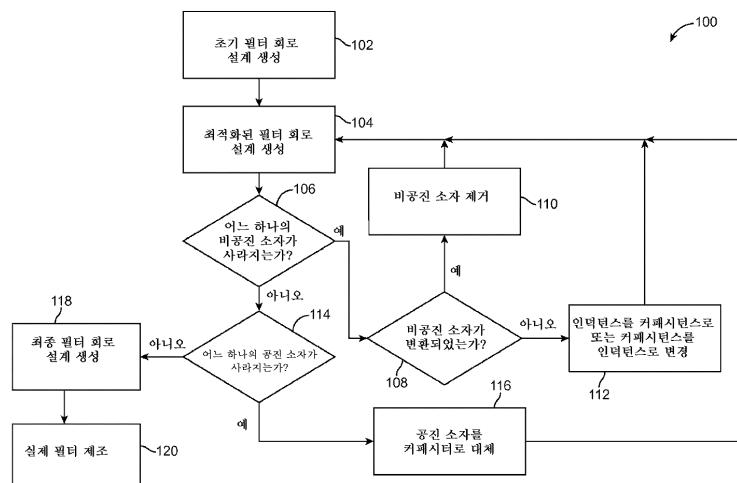

도 6은 본 발명의 일 방법에 따르는 음파 래더 필터를 최적화하는데 사용되는 ERD(Element Removal Design) 기술을 도시한 흐름도이다.

도 7a는 도 6의 ERD 기술을 이용하여 최적화될 수 있는 음파 래더 필터의 초기 회로 설계를 도시한 개요도이다.

도 7b는 도 7a의 초기 회로 설계의 주파수 응답도이다.

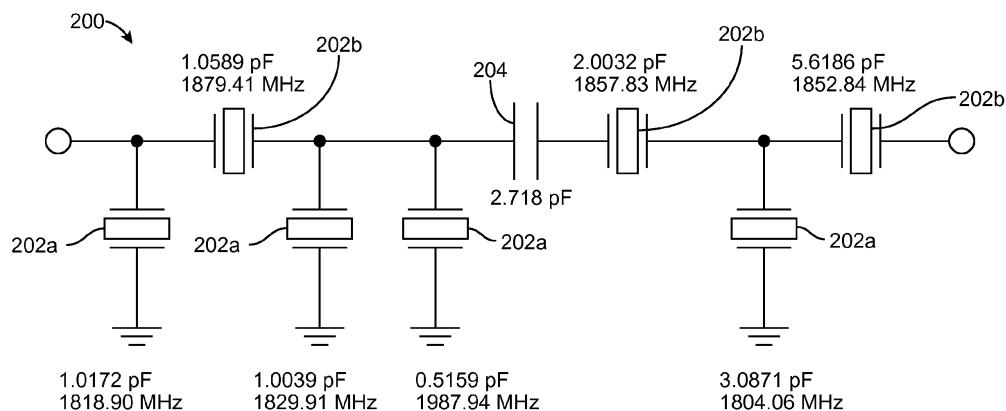

도 8a는 도 6의 ERD 기술을 이용하여 도 7a의 초기 필터 회로 설계의 최적화로부터 얻어진 최적화된 최종 회로 설계를 도시한 개요도이다.

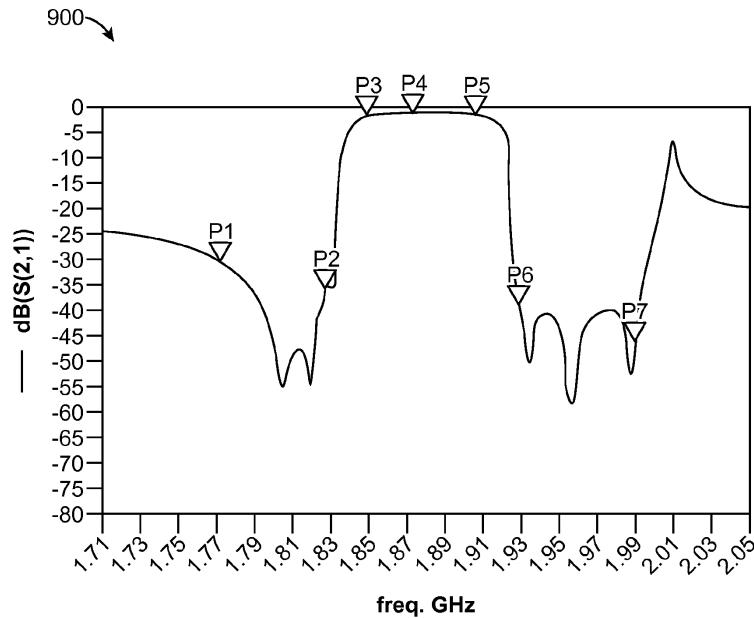

도 8b는 도 8a의 최종 회로 설계의 주파수 응답도이다.

도 9는 도 6의 ERD 기술의 컴퓨터화된 단계들을 구현할 수 있는 컴퓨터화된 필터 설계를 도시한 블록도이다.

## 발명을 실시하기 위한 구체적인 내용

[0027]

마이크로웨이브 필터 설계는 AW(acoustic wave) 마이크로웨이브 필터(예컨대, SAW(surface acoustic wave), BAW(bulk acoustic wave), FBAR(film bulk acoustic resonator) 필터들)를, 회로 소자 값을 변경하고, 회로 소자 탑입을 변경하고, 그리고/또는 여분의 또는 불필요한 회로 소자를 따로 제거함에 의해 최적화한다. 이들 소자들은 인덕터, 커패시터, 및 음파 공진기(예컨대 MBVD(modified Butterworth-Van Dyke) 모델을 이용하여 모델링된)를 포함한다.

[0028]

최적화 기술은 종래에 가능할 수 있는 초기 설계에서 더욱 복잡한 회로의 개선된 최적화가 가능하도록 여러 전통적인 컴퓨터 최적화 방법을 활용한다. 이들 초기 필터 회로 설계는 임의의 설계 방법, 예컨대 이미지 설계 또는 네트워크 합성을 이용하여 이루어진다. 이 최적화 기술은 초기 필터 회로 설계와 비교해 감소한 수의 소자들을 가지면서 동시에 필터의 주파수 응답을 개선한 최종 필터 회로 설계를 가져온다. 본 명세서에서, 주파수 응답 개선이란 필터의 원하는 마이크로웨이브 성능의 개선(예컨대, 더 낮은 삽입 손실, 더 급격한 저지 기울기, 더 높은 대역 외 저지, 더 낮은 노드 전압, 보다 선형의 그룹 지연 등)을 말한다. 따라서, 더 적은 풋프린트, 더 낮은 비용, 더 낮은 삽입 손실, 및 더 큰 선택성의 필터가 달성되면서, 전통적인 제조 프로세스 및 기반 시설의 사용을 허용한다.

[0029]

마이크로웨이브 필터 설계 최적화 기술이 AW 필터를 참고로 이하 설명된다 할지라도, 이 기술은 공진 소자가 MBVD 모델을 이용해 일정 레벨의 정확성으로 모델링될 수 있는 다른 타입의 마이크로웨이브 필터에서 활용될 수 있음을 이해해야 한다. 최적화 기술은 복잡한 공진기 소자(예컨대, 멀티모드 유전체 공진기 및 다른 유사한 기술)를 갖는 다른 기술에도 적용 가능하다.

[0030]

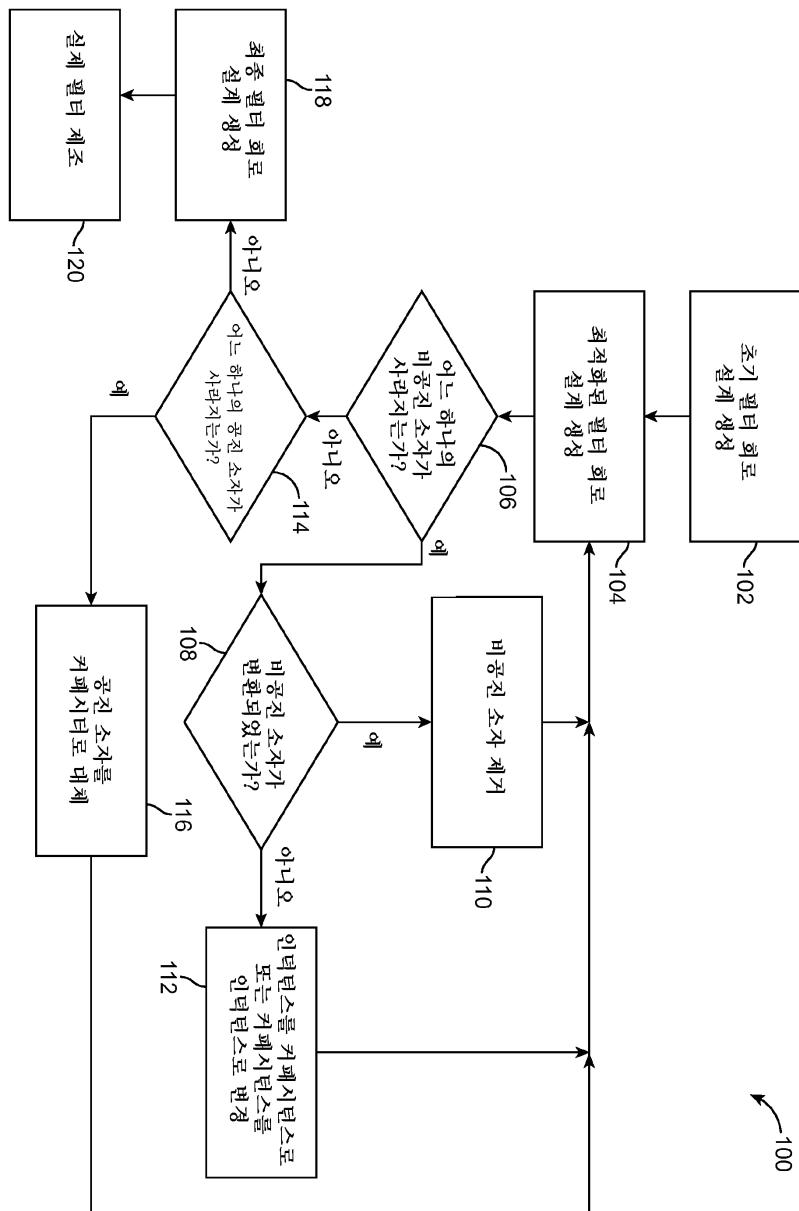

도 6을 참고하면서, 음파 필터를 설계하는데 사용될 수 있는 하나의 ERD(Element Removal Design) 기술(100)을 설명한다. ERD 기술(100)의 구현 동안, DIP(design in process)는 초기 설계로부터 개선된 최종 설계로 변경된다. 이 방법은, DIP를 점증적으로 개선하여 회로 소자 카운트를 감소시키고 성능 메트릭을 개선하기 위해 컴퓨터 최적화 및 결정 단계를 사용한다.

[0031]

이런 목적을 위해, ERD 기술(100)은 먼저, 성능 사양, 예컨대 이미지 필터 기술 또는 네트워크 합성 기술을 이용하여 생성될 수 있는 중심 통과대역 주파수, 통과대역폭, 복귀 손실, 및 대역 외 저지에 기초하여, 초기 필터 회로 설계를 생성한다(단계 102). 본 명세서에서, 회로 소자란 회로 상호접속부의 네트워크 내의 인덕터, 커패시터, 공진기, 스위치 또는 저항을 말한다.

[0032]

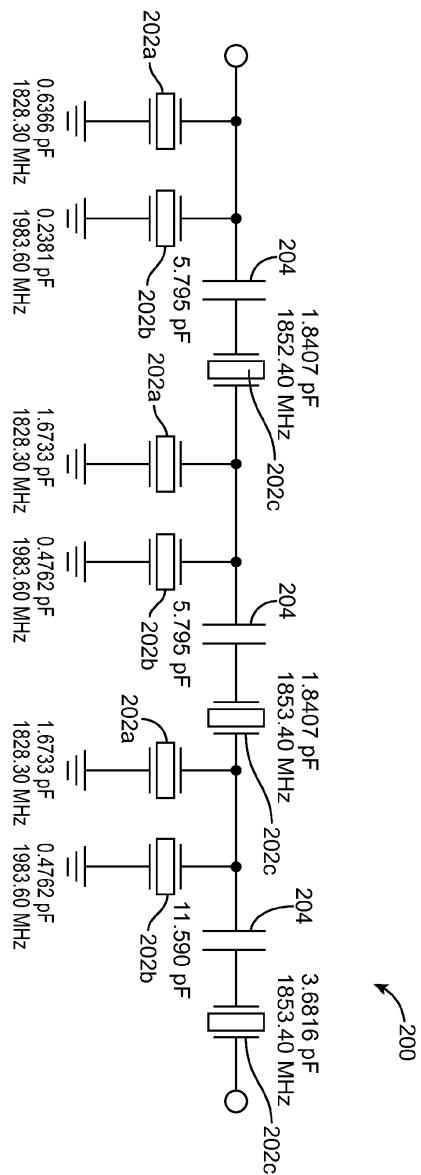

예컨대, 도 7a에 도시된 바와 같이, 초기 필터 회로 설계는 다수의 교번하는 션트 공진 소자들(202a 및 202b) 및 직렬 공진 소자(202c)를 포함하는 대역 통과 래더(200)일 수 있다. 예시된 실시예에서, 래더 필터(200)의 각각의 션트 레그는 다른 주파수들에서 공진할 수 있는 2개의 병렬 션트 공진 소자들(202a 및 202b)을 포함한다. 공진 소자들(202) 각각은 도 2에 도시된 MBVD 모델(54)로 모델링될 수 있다. 래더 필터(200)는 또한 직렬 공진 소자들(202c)과 각각 연관된 커패시터들 형태의 복수의 비공진 소자들(204)을 포함한다. 본 명세서에서, 비공진 소자란 회로에서 수동 컴포넌트를 말한다. 예시적인 비공진 소자는 인덕터, 커패시터, 스위치 또는 저항을 포함한다. 비공진 소자는 관심 주파수로부터 면 공진을 가질 수 있다. 예컨대, 인덕터는 통과대역 주파수의 50%보다 큰 공진을 가질 수 있다. 따라서, 필터(200)는 9개의 공진 소자들 및 3개의 비공진 소자들을 포함한다.

[0033]

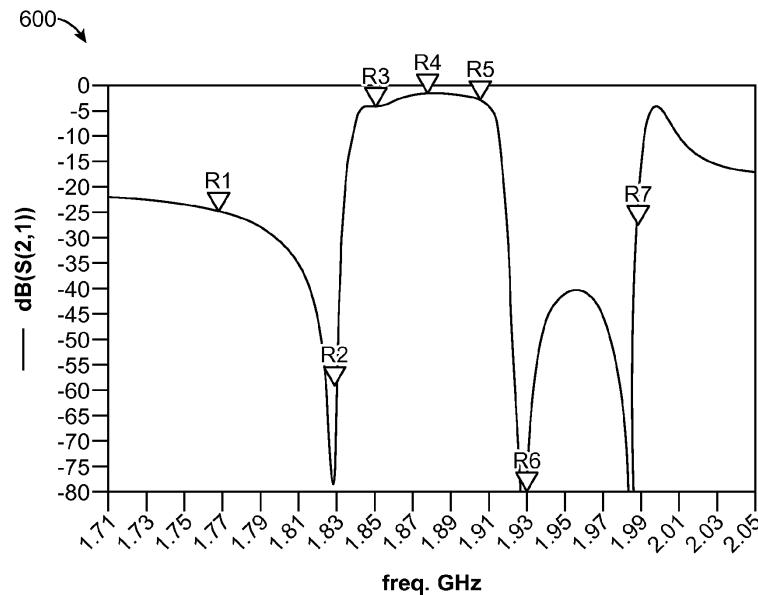

필터(200)는 도 7a에 도시된 바와 같이 각각의 공진기(202)에 대한 공진 주파수  $\omega_R$  및 정적 커패시턴스  $C_0$ 를 갖고 초기에 설계될 수 있으며, 시뮬레이션시 도 7b에 도시된 바와 같은 주파수 응답을 가져온다. 이런 주파수 응답은 다음의 표시들로 특징화되어 나타난다: 주파수 = 1.770GHz에서 Mag S21 = -24.627dB의 R1; 주파수 = 1.830GHz에서 Mag S21 = -64.652dB의 R2; 주파수 = 1.850GHz에서 Mag S21 = -3.857dB의 R3; 주파수 = 1.881GHz에서 Mag S21 = -0.987dB의 R4; 주파수 = 1.910GHz에서 Mag S21 = -3.039dB의 R5; 주파수 = 1.930GHz에서 Mag S21 = -87.468dB의 R6; 및 주파수 = 1.990GHz에서 Mag S21 = -28.429dB의 R7. 초기 필터 회로 설계(200)의 회로 소자들이 다음의 파라미터들, 즉 감마  $\gamma=12$ ,  $QC_0=200$ ,  $Qcap=200$ ,  $QL_m=1000$  및  $Rs=0.5\Omega$ 을 가진다고 가정한다.

[0034]

다음으로, ERD 기술(100)은 DIP(이 경우 초기 필터 설계)를 컴퓨터화된 필터 최적화기(예컨대, 애질런트 ADS)에 입력한다(단계 104). 본 명세서에서, DIP의 컴퓨터 최적화란 컴퓨터 기반 회로 시뮬레이터에서 회로 소자들의 값들을 변경함에 의해 주파수 응답을 개선하는 것을 말할 수 있다. 회로 시뮬레이터는 시뮬레이트된 응답을 원

하는 결과에 비교하기 위해 목표들을 사용할 수 있다. 컴퓨터 최적화될 DIP는 이 시점에서 초기 회로 설계이며, ERD 기술(100)이 필터 설계 프로세스의 어느 시점 동안 DIP를 개선하기 위해 구현될 수 있음을 이해해야 한다. 임의의 이벤트에서, 최종 DIP는 입력 DIP에서의 회로 소자의 수와 동일한 수의 회로 소자를 가진다.

[0035] ERD 기술(100)은 그 후 DIP에서 비공진 소자(204) 중 어느 하나가 중요하지 않게 되는(사라지는)지를 결정한다(단계 106). 본 명세서에서, 회로 소자는, 직렬 소자 리액턴스(reactance) 값 및/또는 션트 소자 서셉턴스(susceptance) 값이 단계 104에서 컴퓨터 최적화 동안 매우 작게 된다면 사라지는 경향이 있고, 그리고/또는 회로 소자는 필터 성능에 큰 영향을 끼치지 않고 필터 설계로부터 제거될 수 있다. 비공진 소자(204)는 필터 회로 설계 내의 그것의 종류 및 배치에 따라 사라지는 경향이 있을 수 있다.

[0036] 예컨대, 비공진 소자(204)가 직렬 인덕터 또는 션트 커패시터인 경우, 그것의 임피던스 절대치가 작아짐에 따라; 예컨대  $0.1nH$ (인덕터) 또는  $0.1pH$ (커패시터)보다 작아짐에 따라 사라지는 경향이 있을 수 있다. 이 경우, 비공진 소자(204)는 임피던스 절대치가 임계치보다 작다면 중요하지 않다고 결정될 것이다. 반대로, 비공진 소자(204)가 션트 인덕터 또는 직렬 커패시터인 경우, 그것의 임피던스 절대치가 커짐에 따라; 예컨대  $100nH$ (인덕터) 또는  $50pH$ (커패시터)보다 커짐에 따라 사라지는 경향이 있을 수 있다. 이 경우, 비공진 소자(204)는 그것의 임피던스 절대치가 임계치보다 커진다면 중요하지 않다고 결정될 것이다.

[0037] 또 다른 예에서, 비공진 소자(204)는 그것의 상대값(임피던스 또는 서셉턴스)이 이들에 연결된 동일 타입(직렬 또는 션트)의 다른 회로 소자와 비교해 작게(예컨대, 10% 미만)될 때 사라지는 경향이 있을 것이다. 따라서, 비공진 소자(204)가 직렬 회로 소자인 경우, DIP에서 다른 직렬 비공진 소자(204)의 절대치에 대한 그 비공진 소자의 절대치의 퍼센티지가 임계치 미만인 경우 중요하지 않다고 결정될 것이다. 유사하게, 비공진 소자(204)가 션트 회로 소자인 경우, DIP에서 다른 션트 비공진 소자(204)의 절대치에 대한 션트 그 비공진 소자의 절대치의 퍼센티지가 임계치 미만인 경우 중요하지 않다고 결정될 것이다.

[0038] 또 다른 예로서, 비공진 소자(204)가 직렬 회로 소자인 경우, 그 임피던스가 비공진 소자(204)로부터의 어느 한 방향에서 본 임피던스의 퍼센티지(예컨대, 10%)보다 작을 때 사라지는 경향이 있을 것이다. 이 경우, 비공진 소자(204)는, 비공진 소자(204)로부터의 어느 한 방향에서 본 임피던스에 대한 비공진 소자(204)의 임피던스 절대치의 퍼센티지가 임계치보다 작다면 중요하지 않다고 결정될 것이다. 반대로, 비공진 소자(204)가 션트 회로 소자인 경우, 그 서셉턴스가 비공진 소자(204)로부터의 어느 한 방향에서 본 서셉턴스의 퍼센티지(예컨대, 10%)보다 작을 때 사라지는 경향이 있을 것이다. 이 경우, 비공진 소자(204)는, 비공진 소자(204)로부터의 어느 한 방향에서 본 서셉턴스에 대한 비공진 소자(204)의 서셉턴스 절대치의 퍼센티지가 임계치보다 작을 때 중요하지 않다고 결정될 것이다.

[0039] 또 다른 예로서, 비공진 소자(204)는 그것을 제거함으로써 필터 회로의 성능 파라미터(예컨대, 삽입 순실, 저지 기울기, 대역 외 저지, 노드 전압, 그룹 지연 평편도(flatness) 등)에서 열화 변화 퍼센티지(percentage degradation change)(예컨대, 10%)보다 작은 결과로 나타날 때 사라지는 경향이 있을 수 있다. 이 경우, 비공진 소자(204)는, 비공진 소자(204)가 없는 성능 파라미터의 값이 비공진 소자(204)를 갖는 성능 파라미터의 값을 임계치 미만으로 열화시킨다면, DIP로부터 비공진 소자(204)를 제거함에 의해 중요하지 않다고 결정될 것이다.

[0040] DIP에서 비공진 소자(204) 중 하나가 단계 106에서 중요하지 않게 되었다고 결정되면, ERD 기술(100)은 중요하지 않은 비공진 소자(204)의 부호가 이전에 변경되었는지(즉, 비공진 소자(204)가 인덕턴스에서 커패시턴스로, 또는 커패시턴스로부터 인덕턴스로 변환되었는지)를 결정한다(단계 108). 물론, DIP가 처음 발생되는 경우에는 이 같은 이전 변환이 없을 것이다. 특히, ERD 기술(100)은 중요하지 않은 비공진 소자(204)의 제거가 비공진 소자(204)의 변환에 비하여 바람직함을 보장하기 위해 이런 질의를 한다.

[0041] 중요하지 않은 비공진 소자(204)가 단계 108에서 이전에 변환되었다면(비공진 소자(204)가 커패시터 및 인덕터 모두로서 사라졌음을 나타냄), ERD 기술(100)은 DIP로부터 중요하지 않은 비공진 소자(204)를 제거함에 의해 감소된 필터 회로 설계를 생성한다(단계 110). 비공진 소자(204)가 단계 108에서 이전에 변환되지 않았다면(비공진 소자(204)가 커패시턴 및 인덕턴스 중 하나로서 사라졌으나, 아직 커패시턴스 및 인덕턴스 중 다른 하나로서는 사라지지 않았음을 나타냄), ERD 기술(100)은 비공진 소자(204)의 부호를 변경(즉, 그것을 커패시턴스에서 인덕턴스로 변경)(비공진 소자(204)가 초기에 커패시턴스인 정도로), 또는 인덕턴스에서 커패시턴스로 변경(비공진 소자(204)가 초기인 커패시턴스인 정도로)함에 의해 DIP를 수정한다(단계 112).

- [0042] ERD 기술(100)은 그 후 단계 104로 복귀하여, 단계 110에서 생성된 감소된 필터 회로 설계 또는 단계 112에서 생성된 변환된 필터 회로 설계 중 어느 하나를 컴퓨터화된 필터 최적화기에 입력함에 의해 DIP를 다시 최적화하고, 그 후 DIP에서 남아있는 비공진 소자(204) 중 어느 하나가 단계 108에서 중요하지 않게 되었는지를 결정한다. DIP에서 비공진 소자(204) 중 하나가 중요하지 않게 되었다고 결정되면, ERD 기술은 중요하지 않은 비공진 소자(204)가 단계 108에서 이전에 변환되었는지 다시 결정한다. 중요하지 않은 비공진 소자(204)가 이전에 변환된 경우, 중요하지 않은 비공진 소자(204)는 이전 DIP로부터 제거되어야 한다고 여겨지고, 그 결과 단계 110에서 그것이 제거된다. 중요하지 않은 비공진 소자(204)가 이전에 변환되지 않은 경우, ERD 기술(100)은 단계 112에서 중요하지 않은 비공진 소자(204)를 변경한다.

- [0043] DIP(처음 또는 후에 생성된 DIP인지에 상관없이)에서 비공진 소자(204) 중 어느 것도 단계 106에서 중요하지 않게 되었다고 결정되지 않는다면, ERD 기술은 DIP에서 공진 소자(202) 중 어느 하나가 중요하지 않게 되었는지(사라지는지)를 결정한다(단계 114). 공진 소자(202)는, 공진 소자(202)와 연관된 송신 제로가 모든 통과대역 및 저지대역으로부터 비교적 멀리 있는 경우, 예컨대 수학식 1 및 2에 주어진 바와 같이 공진 주파수  $\omega_R$  및 반공진 주파수  $\omega_A$ 가 가장 근접한 통과대역 또는 저지대역의 에지 주파수로부터 10%보다 많이 이동한 경우, 사라지는 경향이 있을 수 있다.

- [0044] DIP에서 공진 소자(202) 중 하나가 단계 114에서 중요하지 않게 되었다고 결정되면, ERD 기술은, 중요하지 않는 공진 소자(202)를, 바람직하게는 중요하지 않은 공진 소자(202)의 정적 커패시턴스의 값과 동일한 값을 갖는 정적 커패시턴스  $C_0$ 로 대체함에 의해 DIP를 수정한다(단계 116). 특히, 중요하지 않게 되는 공진 소자(202)는 그 정적 커패시턴스 때문에 회로에 여전히 영향을 미칠 것이며, 따라서 제거되기보다는 커패시터로 대체되는 편이 낫다.

- [0045] ERD 기술(100)은 그 후 단계 104로 복귀하여 DIP를 다시 최적화하고, 그 후 DIP에서 비공진 소자(204) 중 어느 하나(중요하지 않은 공진 소자(202)로부터 변환된 임의의 정적 커패시턴스  $C_0$ 를 포함함)가 단계 106에서 중요하지 않게 되었는지 결정한다.

- [0046] DIP에서 비공진 소자(204) 중 하나가 중요하지 않게 되었다고 결정되면, ERD 기술은, 중요하지 않은 비공진 소자(204)가 단계 108에서 이전에 변환되었는지를 다시 결정하고, 전술한 바와 같이 진행한다. 중요하지 않은 비공진 소자(204)가 중요하지 않은 공진 소자(202)를 대체한 정적 커패시턴스  $C_0$ 인 경우, 중요하지 않은 회로 소자(이전에는 공진 소자(202)였으나 지금은 비공진 소자(204)임)는 완전히 제거되어야 하며, 그 결과 단계 110에서 제거된다.

- [0047] DIP에서 비공진 소자(204) 중 어느 것도 중요하지 않게 되었다고 단계 106에서 결정되지 않는다면, ERD 기술(100)은, DIP에서 공진 소자(202) 중 어느 하나가 단계 114에서 중요하지 않게 되었는지를 다시 결정한다. DIP에서 공진 소자(202) 중 하나가 중요하지 않게 되었다고 결정되면, ERD 기술은, 단계 116에서 중요하지 않은 공진 소자(202)를 정적 커패시턴스  $C_0$ 로 대체하고, 전술한 바와 같이 진행한다.

- [0048] DIP에서 공진 소자(202) 중 어느 것도 중요하지 않게 되었다고 결정되지 않는다면, ERD 기술(100)은 DIP가, 예시적인 실시예에서 도 8a에 도시된 바와 같은 남아있는 공진 소자(202) 및 비공진 소자(204)에 대한 공진 주파수  $\omega_R$  및 정적 커패시턴스  $C_0$ 를 가지며, 시뮬레이션시 도 8b에 도시된 바와 같은 주파수 응답을 가져오는 개선된 최종 필터 회로 설계인 것으로 간주한다(단계 118). 이런 주파수 응답은 다음의 표시들로 특징화되어 나타난다: 주파수 = 1.770GHz에서 Mag S21 = -30.080dB의 P1; 주파수 = 1.830GHz에서 Mag S21 = -34.193dB의 P2; 주파수 = 1.850GHz에서 Mag S21 = -1.394dB의 P3; 주파수 = 1.872GHz에서 Mag S21 = -0.761dB의 P4; 주파수 = 1.910GHz에서 Mag S21 = -1.406dB의 P5; 주파수 = 1.930GHz에서 Mag S21 = -45.227dB의 P6; 및 주파수 = 1.990GHz에서 Mag S21 = -45.227dB의 P7.

- [0049] 도 7a와 도 8a 간의 비교로부터 알 수 있듯이, 개선된 최종 회로 설계는 보다 적은 수의 회로 소자들을 포함하며, 특히 2개 적은 공진 소자(202) 및 1개 적은 비공진 소자(204)를 포함한다. 도 8a와 도 8b 간의 비교로부터 알 수 있듯이, 최종 필터 회로 설계는 통과 대역에서 보다 평편한 주파수 응답과 순실을 가져온다. 종래의 최적화 기술(즉, 회로 소자가 제거 안 된)이 도 7a에 도시된 바와 같이, 초기 필터 회로(200)에서 수행되어, 도 8b에 도시된 ERT 기술에 의해 산출된 주파수 응답 성능만큼 좋지 않은 주파수 응답 성능을 갖는 최종 필터 회로를 가져옴에 유의해야 한다. 따라서, 종래 기술과는 달리, ERT 기술을 이용하여 회로 소자를 제거하는 것은 마이크로웨이브 필터의 비용 및 크기만을 감소시키는 것이 아니고, 많은 수의 회로 소자를 갖는 종래의 마이크로

웨이브 필터에 비해 마이크로웨이브 필터의 주파수 응답 성능을 개선한다.

- [0050] 특히, ERD 기술(100)은 이전 단계가 행해지지 않거나 다시 행해져야 하는지를 결정하기 위해 단계 104로부터 생기는 DIP의 주파수 응답을 분석할 수 있다.

- [0051] 예컨대, DIP의 주파수 응답 성능이 초기 필터 회로 설계의 주파수 응답 성능 보다 좋지 않은 경우, 이는 초기 필터 회로 설계가 수용가능하지 않다는 것을 의미하고, 이에 따라 다른 초기 필터 회로 설계가 고려될 수 있고, 이를 단계 104에서 컴퓨터화된 필터 최적화기에 입력할 수 있다.

- [0052] 다른 예에서, 비공진 소자(204)가 변환된 후(커패시턴스에서 인더턴스로, 또는 인더턴스에서 커패시턴스로) 존재하는 DIP의 주파수 응답 성능이 비공진 소자(204)가 변환되기 전에 존재하는 DIP의 주파수 응답 성능에 대해 임계량 만큼 악화하는 경우, ERD 기술(100)은 이전 DIP로 간단히 복귀하며, 그 설계로부터 비공진 소자(204)를 제거할 수 있다.

- [0053] 또 다른 예에서, 공진 소자(202)가 정적 커패시턴스  $C_0$ 로 변환된 후 존재하는 DIP의 주파수 응답 성능이 공진 소자(202)가 변환되기 전에 존재하는 DIP의 주파수 응답 성능에 대해 임계량 만큼 악화하는 경우, ERD 기술(100)은 이전 DIP로 간단히 복귀하며, 공진 소자(204)를 다시 그 설계로 복원할 수 있다.

- [0054] 개선된 최종 필터 회로 설계가 달성되는 경우, ERD 기술(100)은 최종 필터 회로 설계에 기반한 실제 마이크로웨이브 필터를 제조한다(단계 120). 바람직하게, 실제 마이크로웨이브 필터의 회로 소자값은 개선된 최종 필터 회로 설계에서의 대응하는 회로 소자값에 매칭할 것이다.

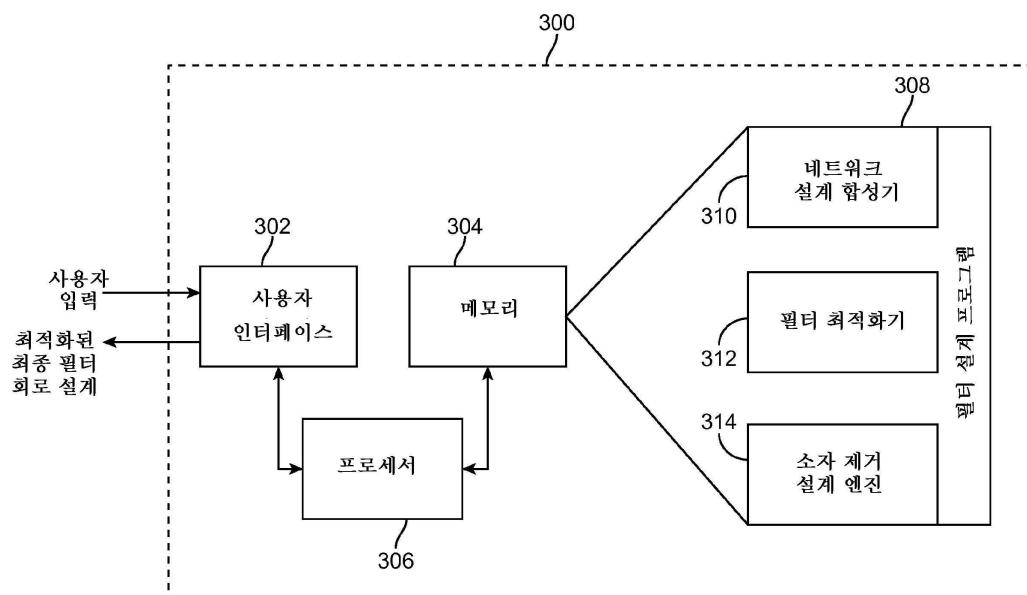

- [0055] 먼저 도 9를 참고하면, 컴퓨터화된 필터 설계 시스템(300)이 ERD 기술(100)을 이용하여 마이크로웨이브 필터를 설계하는데 이용된다. 컴퓨터화된 필터 설계 시스템(300)은, 사용자로부터 정보 및 데이터(예컨대, 파라미터값 및 필터 사양)을 수신하고 최적화된 필터 회로 설계를 사용자에게 출력하도록 구성된 사용자 인터페이스(302)와, 필터 설계 소프트웨어(308)(특정 기능을 수행하거나 특정 추상 데이터 타입을 구현하는, 루틴, 프로그램, 오브젝트, 컴포넌트, 데이터 구조, 프로시저, 모듈, 기능 등을 제한적이지 않게 포함할 수 있는 소프트웨어 명령어의 형태를 가질 수 있음) 뿐만 아니라, 사용자 인터페이스(302)를 통해 사용자로부터 입력된 정보 및 데이터를 저장하도록 구성된 메모리(304)와, 필터 설계 소프트웨어를 실행하도록 구성된 프로세서(306)를 포함한다. 필터 설계 소프트웨어 프로그램(308)은 서브 프로그램들, 특히, 종래의 네트워크 설계 합성기(310)(단계 102에서 초기 필터 회로 설계를 생성하는데 사용될 수 있는), 종래의 필터 최적화기(312)(단계 104에서 DIP를 생성하는데 사용될 수 있는), 및 최적화된 최종 회로 설계를 생성하기 위하여 ERD 기술(100)의 필터 회로 설계 측면에 따라 네트워크 설계 합성기(88) 및 필터 최적화기(90)를 제어하는 소자 제거 설계 엔진(314)으로 구분된다.

- [0056] 본 발명의 특정 실시예가 도시되고 설명되었다 할지라도, 이들 설명이 본 발명을 이들 실시예로 제한하는 것이 아님을 이해해야 한다. 당업자에게는 본 발명의 정신 및 범위를 벗어남이 없이 다양한 변경 및 수정이 행해질 수 있음이 자명할 것이다. 예컨대, 본 발명은 단일 입력 및 출력을 갖는 필터를 훨씬 넘어서 어플리케이션을 가지며, 본 발명의 특정 실시예는 낮은 손실의 선택적인 회로들이 사용될 수 있는 듀플렉서, 멀티플렉서, 채널라이저, 리액티브 스위치 등을 형성하는데 사용될 수 있다. 따라서, 본 발명은 특허청구범위에 정의된 본 발명의 정신 및 범위 내에 있는 대안들, 수정들 및 균등물들을 커버한다.

도면

도면1

(중래기술)

## 도면2

## 도면3

## 도면4a

(종래기술)

## 도면4b

(종래기술)

## 도면5a

(종래기술)

## 도면5b

(종래기술)

도면6

도면7a

도면7b

도면8a

도면8b

도면9