(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6773274号

(P6773274)

(45) 発行日 令和2年10月21日(2020.10.21)

(24) 登録日 令和2年10月5日(2020.10.5)

(51) Int.Cl.

F 1

H O 1 L 41/312 (2013.01)

H O 1 L 41/187 (2006.01)H O 1 L 41/312

H O 1 L 41/187

請求項の数 18 (全 9 頁)

(21) 出願番号 特願2019-504705 (P2019-504705)

(86) (22) 出願日 平成29年8月1日 (2017.8.1)

(65) 公表番号 特表2019-527937 (P2019-527937A)

(43) 公表日 令和1年10月3日 (2019.10.3)

(86) 國際出願番号 PCT/EP2017/069470

(87) 國際公開番号 WO2018/024743

(87) 國際公開日 平成30年2月8日 (2018.2.8)

審査請求日 平成31年3月19日 (2019.3.19)

(31) 優先権主張番号 1657494

(32) 優先日 平成28年8月2日 (2016.8.2)

(33) 優先権主張国・地域又は機関

フランス (FR)

(73) 特許権者 598054968

ソイテック

S o i t e c

フランス国, 38190 ベルナン,

パルク テクノロジーク デ フォンテー

ヌ, シュマン デ フランク

P a r c T e c h n o l o g i q u e

d e s f o n t a i n e s c h e m i

n D e s F r a n q u e s 3819

O B e r n i n, F r a n c e

(74) 代理人 100107456

弁理士 池田 成人

(74) 代理人 100162352

弁理士 酒巻 順一郎

最終頁に続く

(54) 【発明の名称】ドナー基板から圧電層を剥離するための電界の使用

## (57) 【特許請求の範囲】

## 【請求項 1】

支持基板上に圧電層を転写する方法であって、

a ) 圧電ドナー基板(3)内に所定の分割領域(1)を設けるステップと、

b ) 前記圧電ドナー基板(3)を支持基板(11)に取り付けて複合体(13)を形成するステップと、

c ) 電界(15)を印加することを含む、前記圧電ドナー基板(3)から前記圧電層(21)を剥離するステップと、

を含む、方法。

## 【請求項 2】

前記圧電ドナー基板がパルク圧電基板から作られている、請求項1に記載の方法。 10

## 【請求項 3】

前記圧電ドナー基板がハンドル基板上に設けられた圧電材料の層から作られている、請求項1に記載の方法。

## 【請求項 4】

ステップb)が最大100℃の温度での熱処理を含む、請求項1～3のいずれか一項に記載の方法。

## 【請求項 5】

ステップb)が10Pa未満の圧力で行なわれる、請求項1～4のいずれか一項に記載の方法。

10

20

**【請求項 6】**

ステップ c ) が 100 未満の温度で行なわれる、請求項 1 ~ 5 のいずれか一項に記載の方法。

**【請求項 7】**

前記電界 ( 15 ) が少なくとも 1 つの電極を備えるチャックを使用して印加される、請求項 1 ~ 6 のいずれか一項に記載の方法。

**【請求項 8】**

前記複合体の前記圧電ドナー基板の表面が前記チャック上に配置されている、請求項 7 に記載の方法。

**【請求項 9】**

前記チャックが電気的絶縁体によって分離された互いにかみ合わされた複数の電極を備える、請求項 8 に記載の方法。

**【請求項 10】**

前記チャックに印加される電圧が最大 10 kV である、請求項 9 に記載の方法。

**【請求項 11】**

前記複合体が前記チャックと、第 2 の電極との間に挟まれている、請求項 7 又は 8 に記載の方法。

**【請求項 12】**

前記チャックに印加される電圧が最大 5 kV である、請求項 11 に記載の方法。

**【請求項 13】**

前記電界 ( 15 ) の電界線が前記圧電ドナー基板 ( 3 ) の分極方向 ( 17 ) と平行である、請求項 1 ~ 12 のいずれか一項に記載の方法。

**【請求項 14】**

前記圧電ドナー基板 ( 3 ) が LiTaO<sub>3</sub> ( LTO )、AlN、ZnO、Pb [ Zr<sub>x</sub> Ti<sub>1-x</sub> ] O<sub>3</sub> ( 0 < x < 1 ) ( PZT )、及び LiNbO<sub>3</sub> ( LNO ) のうちの 1 つである、請求項 1 ~ 13 のいずれか一項に記載の方法。

**【請求項 15】**

前記支持基板 ( 11 ) が半導体基板、又は絶縁体、又は金属である、請求項 1 ~ 14 のいずれか一項に記載の方法。

**【請求項 16】**

圧電層に電界を印加するための第 1 及び / 又は第 2 の電極を含む 1 つ或いは 2 つのチャックを備える、請求項 1 ~ 15 のいずれか一項に記載のステップ c ) を行うための剥離チャンバ。

**【請求項 17】**

前記チャックのうちの少なくとも 1 つが保持手段を備える、請求項 16 に記載の剥離チャンバ。

**【請求項 18】**

前記第 1 及び / 又は第 2 の電極が前記保持手段から独立している、請求項 17 に記載の剥離チャンバ。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、支持基板上に圧電層を転写する方法に関する。また、本発明は、本方法の少なくとも一部を実行するための剥離チャンバに関する。

**【背景技術】****【0002】**

薄い圧電層が取り付けられたシリコン又はサファイアのような支持基板を備える複合構造体への関心が高まっている。そのような複合構造体を得るために、シリコンオンインシユレータ基板から知られている、スマートカット ( Smart Cut ) ( 商標 ) タイプのプロセスを使用することが提案されている。

10

20

30

40

50

**【 0 0 0 3 】**

本プロセスは、ドナー基板内部に所定の分割領域を有する圧電ドナー基板を利用することができる。所定の分割領域は、ドナー基板にイオンを注入することによって得ることができる。その後、ドナー基板は、支持基板に取り付けられ、ドナーと支持基板との間の接合を強化するために、及び所定の分割領域においてドナー基板の残りの部分を剥離するために熱処理にかけられ、以て支持基板上に圧電ドナー基板の層を転写する。

**【 0 0 0 4 】**

熱処理中により高い温度の影響下で、注入されたイオンによって所定の分割領域に生成されたデフォルトが成長し、局部的なひずみをもたらし、このひずみが所与の熱収支において剥離をもたらし、以て支持基板上への層転写をもたらす。

10

**【発明の概要】****【 0 0 0 5 】**

しかしながら、圧電ドナー基板の場合は、層を破損せずに転写することは困難である。これは、圧電ドナー基板と支持基板との間の熱膨張係数の大きな差（CTE不整合）に起因する。したがって、熱処理中にドナーと支持基板の界面にひずみが現われ、このひずみが剥離の瞬間に突然緩和され、転写された層の破損につながる。

**【 0 0 0 6 】**

したがって、本発明の目的は、CTE不整合に起因する転写された圧電層の破損を低減するために特に重要である代替の層転写方法を提供することである。

**【 0 0 0 7 】**

本目的は、本発明による支持基板上に圧電層を転写する方法によって達成され、本方法は、a) 圧電ドナー基板内に所定の分割領域を設けるステップと、b) 圧電ドナー基板を支持基板に取り付けて複合体を形成するステップと、c) 電界を印加することを含む、圧電ドナー基板から圧電層を剥離するステップと、を含む。電界を印加することによって、電界が圧電ドナー基板内に変形をもたらし、補完的なひずみを構築することに起因して所定の分割領域のデフォルトの領域をさらに脆弱化するため、ドナー基板の圧電特性を用いて所定の分割領域を脆弱化する。結果として、剥離される圧電層を完全に剥離するのに必要な熱収支を下げることができる。

20

**【 0 0 0 8 】**

ある特定の実施形態によると、圧電ドナー基板は、単一の圧電材料、いわゆるバルク圧電基板から作られてもよい。他の実施形態によると、圧電ドナー基板は、ハンドル基板上に設けられた圧電材料の層から作られてもよい。第2の場合は、支持基板と同様のCTEを有するハンドル基板を選択することができる。ハンドル基板と支持基板との間のCTEの差が10%未満であることは、2つのCTEのうちの大きい方に対して、より大きなCTE差と比較して、及び/又は支持基板よりも大きなCTE差を有するバルク圧電基板の使用と比較して、上述の方法を支援する熱処理のための熱収支をより大きくすることを可能にする。

30

**【 0 0 0 9 】**

一実施形態によると、本方法は、所定の分割領域を形成するためのイオン注入ステップと、イオン注入された圧電ドナー基板の熱処理ステップと、をさらに含むことができ、熱処理ステップは、0 ~ 200 の温度範囲で1時間~24時間の間行うことができる。熱処理ステップは、以て、所定の分割領域の欠陥を成長させることができる。

40

**【 0 0 1 0 】**

好みしい変形形態によると、ステップb)は、最大100 若しくは最大50 の温度での熱処理を含むことができ、又は一変形形態では、15 ~ 25 の室温で行うことができる。剥離が熱処理のみによって達成される製造プロセスでは、剥離ステップの前に接合界面を安定化させて、剥離の瞬間の望ましくない接合欠陥を防止する必要がある。従来技術では、接合の強化は、剥離前に複合体を加熱することによって得られる。既に上述したように、そのような熱処理は、圧電ドナー基板の場合は熱膨張係数の差に関連する問題を引き起こす。剥離中に電界を用いることによって、ドナー基板と支持基板との間の接合

50

エネルギーを、熱誘起剥離のみに必要な接合エネルギーと比較して低くすることができる。これは、電界の存在に起因する機械的ひずみの影響が圧電ドナー基板に非常に限定されており、支持基板との界面への影響が少ないという事実による。

#### 【0011】

好ましい変形形態によると、ステップb)は、 $10^{-2}$  mbar未満の圧力で行なうことができる。

#### 【0012】

ステップc)は、100未満、より特に50未満の温度で、さらにより特に15~25の室温で行なうことができるのが好ましい。したがって、電界によって支援されない剥離プロセスと比較して、剥離を低温で得ることができる。

10

#### 【0013】

好ましい実施形態によると、電界は、少なくとも1つの電極を備えるチャックを使用して印加することができる。そのようなチャックを使用することによって、電界を簡単なやり方で利用可能にすることができる。チャックは、そのような電極から独立した、例えば、真空又は静電特性によって実施される保持手段を備えててもよい。

#### 【0014】

複合体の圧電ドナー基板の表面は、チャック上に配置することができるのが有利である。この構成では、プロセスを支持基板の電気的特性と無関係に行なうことができる。

#### 【0015】

一変形形態によると、チャックは、電気的絶縁体、特にセラミックによって分離された互いにかみ合わされた複数の電極を備えることができる。この形状では、1つの電極のみを使用して適切な電界を生成することが可能である。これにより、処理チャンバの設計が簡単になる。

20

#### 【0016】

一実施形態によると、チャックに印加される電圧は、最大10kV、特に1kV~5kVの範囲にある。この電圧範囲では、圧電ドナー基板を変形させるのに十分に強力な電界が形成され、これにより剥離がより低い熱収支で起こり得る。

#### 【0017】

一変形形態によると、ドナー基板-支持基板複合体は、チャックと、特に第2のチャックに含まれている第2の電極との間に挟まれていてもよい。複合体の両側に電極を使用する設計では、第1及び第2の電極に印加される電圧は、1つの電極のみの場合よりも低くすることができます。

30

#### 【0018】

本発明のこの変形形態では、静電チャックに印加される電圧は、最大5kV、特に200V~1kVの範囲とすることができるのが好ましい。

#### 【0019】

一実施形態によると、電界線は、圧電ドナー基板の分極方向と本質的に平行にすることができる。電界を圧電ドナー基板の分極方向に整列させることによって、結果として生じるひずみの大きさを高めることができ、剥離ステップを容易にする。

#### 【0020】

40

圧電ドナー基板は、LiTaO<sub>3</sub>(LTO)、AlN、ZnO、Pb[Zr<sub>x</sub>Ti<sub>1-x</sub>]O<sub>3</sub>(0<x<1)(PZT)、及びLiNbO<sub>3</sub>(LNO)のうちの1つとすることができるのが好ましい。支持基板は、半導体基板、特にSiウェーハ、絶縁体、特にサファイアウェーハ、又は金属、特にMoウェーハとすることができるのが好ましい。

#### 【0021】

また、本発明の目的は、上述したようなステップc)を実行するための、圧電層に電界を印加するための1つ又は2つのチャックを備える剥離チャンバによって達成される。剥離チャンバは、一変形形態によると、ステップb)を実行するためにも使用することができる。チャックの使用により、圧電基板の変形をもたらす電界を生成することができ、以て所定の分割領域を脆弱化することができる。結果として、剥離ステップに熱エネルギー

50

のみを使用するプロセスと比較して、ドナー基板の残りの部分からの圧電層の剥離を実行するのに必要な熱収支を下げる事ができる。したがって、ドナー基板と支持基板との間の熱膨張係数の大きな差の悪影響を低減させることができる。

#### 【0022】

また、本発明の目的は、複合体を保持するための保持手段、特に真空及び／又は静電保持手段を備えるチャックと、複合体内部の所定の分割領域を脆弱化するために電界を印加するための電極とによって達成される。一変形形態によると、静電保持手段と電界を印加するための電極とは、互いに独立していてもよい。このようにして、本方法に関して上述したような保持作用及び脆弱化作用を互いに対して最適化することができる。

#### 【0023】

10

本発明は、添付の図面と併せて有利な例示的な実施形態を使用して、以下でより詳細に説明される。

#### 【図面の簡単な説明】

#### 【0024】

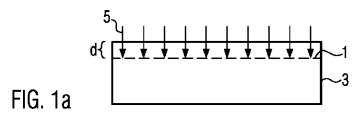

【図1a】支持基板上に圧電層を転写する方法の実施形態を示す概略図である。

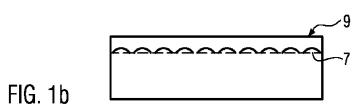

【図1b】支持基板上に圧電層を転写する方法の実施形態を示す概略図である。

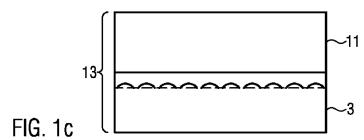

【図1c】支持基板上に圧電層を転写する方法の実施形態を示す概略図である。

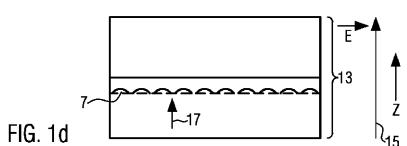

【図1d】支持基板上に圧電層を転写する方法の実施形態を示す概略図である。

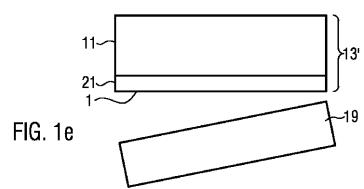

【図1e】支持基板上に圧電層を転写する方法の実施形態を示す概略図である。

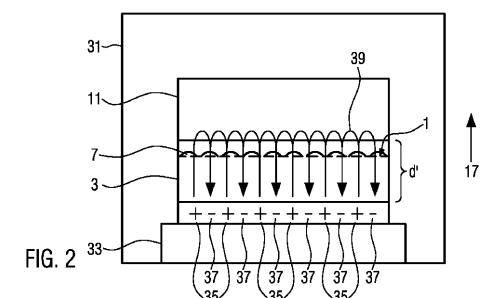

【図2】本発明の第2の実施形態による構成を示す概略図である。

20

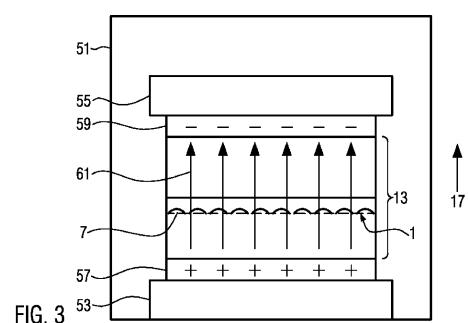

【図3】本発明の第3の実施形態による構成を示す概略図である。

#### 【発明を実施するための形態】

#### 【0025】

図1a～図1eは、支持基板上に圧電層を転写する方法の実施形態を示す。

#### 【0026】

本発明による方法のステップa)に対応する図1aに示すプロセスステップでは、イオン5を注入することによって圧電ドナー基板3内に所定の分割領域1が生成される。

#### 【0027】

圧電ドナー基板3は、例えば、 $\text{LiTaO}_3$ (LTO)、 $\text{AlN}$ 、 $\text{ZnO}$ 、 $\text{Nb}[Zr_{x}\text{Ti}_{1-x}]O_3$ ( $\text{PZT}$ )、及び $\text{LiNbO}_3$ (LNO)とすることが可能である。以下では、単に本発明による一例として、圧電ドナー基板は、LTOから作られたバルク圧電基板である。一変形形態によると、ドナー基板は、上部に圧電層を有するハンドル基板を備えることができる。

30

#### 【0028】

圧電ドナー基板3内部に所定の分割領域1を得るために、 $5 * 10^{16} \sim 2 * 10^{17}$ の $\text{H}^+$ 若しくは $\text{He}^+$ 又は $\text{H}^+/\text{He}^+$ の混合物のイオン/ $\text{cm}^2$ が、所定の分割領域1の所望の深さdに応じて約 $10\text{ keV} \sim 1\text{ MeV}$ のエネルギーで注入される。上述した注入条件下では、深さdは、 $60\text{ nm} \sim 6\mu\text{m}$ 程度である。

#### 【0029】

図1bに示す次のステップは、イオン注入によって生成された所定の分割領域1を形成する欠陥7を成長させる第1の熱処理ステップである。表面9の粗さは、 $5\text{ nm RMS}$ 未満である。本発明によると、この第1の熱処理ステップは、 $0 \sim 200$ の温度で約1～24時間の間行われる。

40

#### 【0030】

本発明によるステップb)を図1cに示す。このステップは、圧電ドナー基板3を支持基板11に、特に接合によって取り付け、以て複合体13を形成することとなる。支持基板11は、シリコンウェーハのような半導体基板、又はサファイアのような絶縁体、或いはMoのような金属とすることができます。

#### 【0031】

接合ステップは、大気圧又は真空中で、典型的には、 $10^{-2}\text{ mbar}$ 未満、特に $10^{-3}\text{ mbar}$ 未満で行われる。

50

$\sim 10^{-4}$  mbar 程度の一次真空下で行われる。2つの基板 3 と 11との間の接合を強化するために、接合は、最大 100 の温度で行われる。

#### 【0032】

図 1 d は、製造プロセスの次のステップを示す。このステップは、本発明によるステップ c ) に対応する。電界が複合体 13 に印加され、電界線 15 は、所定の分割領域 1 に対して本質的に垂直である。本発明の一態様によると、電界線 15 は、圧電効果を最適化するために圧電ドナー基板 3 の分極軸 17 ( 又はポーリング軸 ( poling axis ) ) と本質的に平行である。圧電特性のために、電界 15 の存在は、圧電支持基板 3 内部で z 方向に機械的変形をもたらす。この変形は、所定の分割領域 1 をさらに脆弱化する。所望の電界を得るために、最大 10 kV の電圧が印加される ( 図 2 及び図 3 に関する以下の記載をさらに参照 ) 。

10

#### 【0033】

電界の強度に応じて、支持基板 11 及び転写された圧電層 21 を含む改質された複合体 13' からの圧電ドナー基板の残りの部分 19 の完全な剥離が、図 1 e に示すように所定の分割領域で起こり得る。

#### 【0034】

一変形形態によると、図 1 e に示すような剥離は、電界 15 の印加中又は印加後に、複合体 13 を加熱することによっても得ることができる。この第 2 の熱処理ステップでは、最大 100 の温度が最終的な剥離に使用される。温度の選択は、第 1 の熱処理ステップの条件及び電界 15 の強度に依存する。

20

#### 【0035】

本発明による方法を用いて、圧電層材料 21 と支持基板 11 との間の熱膨張係数の既存の大きな差にわずらわされることなく、薄い圧電層 21 を支持基板 11 上に転写することが可能になる。

#### 【0036】

次いで、圧電ドナー基板の残りの部分 19 をドナー基板 3 として再利用して、図 1 a ~ 図 1 e に関して記載したようなプロセスを再開することができる。

#### 【0037】

図 2 は、本発明の第 2 の実施形態による構成を概略的に示す。図 2 は、図 1 d に示すような本発明による方法の少なくともステップ c ) を実行するために使用される剥離チャンバ 31 を示す。

30

#### 【0038】

剥離チャンバは、第 1 の実施形態に関して詳細に記載したような圧電ドナー基板 3 及び支持基板 11 を含む複合体 13 に電界 39 を印加することができるよう、正極 35 及び負極 37 を含むチャック 33 を備える。第 1 の実施形態の特徴の記載は、再び繰り返されないが、参照によりここに組み込まれる。チャックは、複合体 13 を保持するためのさらなる手段、例えば、真空又は静電手段を備えることができる。本実施形態では、これらの手段は、電極 35 及び 37 から独立している。

#### 【0039】

複合体 13 は、複合体 13 の圧電ドナー基板 3 がチャック 33 上に配置されるように、チャック 33 上に位置決めされる。

40

#### 【0040】

正極 35 及び負極 37 は、電界 39 が少なくとも圧電ドナー基板 3 の厚さ  $d'$  内でチャック 33 の表面に対して本質的に垂直になるように配置される。圧電ドナー基板の分極軸 17 もチャック 33 に対して垂直であることにより、圧電効果を最適化することができ、以て所定の分割領域 1 に機械的ひずみを生成し、さらに脆弱化をもたらすことができる。

#### 【0041】

一変形形態によると、特に電界が十分に強い場合は、チャック 33 上に配置されるのは、支持基板とすることもできる。しかしながら、絶縁性支持基板 11 については、圧電ドナー基板 3 をチャック 33 上に配置することが好ましい。

50

**【 0 0 4 2 】**

一変形形態では、正極 3 5 及び負極 3 7 は、互いにかみ合わされ、電気的絶縁体（図示せず）、例えば、薄いセラミック層が間に配置される。

**【 0 0 4 3 】**

分割チャンバ 3 1 の制御ユニットは、最大 10 kV、好ましくは 1 kV ~ 5 kV の電圧を電極に印加することができるように構成されている。本実施形態では、1 つの静電チャックのみが必要であり、これによって剥離チャンバ 3 1 の設計が簡略化される。

**【 0 0 4 4 】**

図 3 は、本発明の第 3 の実施形態による構成を概略的に示す。図 3 は、図 1 d に示すような本発明による方法の少なくともステップ c ) を実行するために使用される剥離チャンバ 5 1 の第 2 の実施形態を示す。第 1 及び第 2 の実施形態の特徴の記載は、再び繰り返されないが、参照によりここに組み込まれる。10

**【 0 0 4 5 】**

本実施形態では、2 つのチャック 5 3 及び 5 5 が使用されている。下部チャック 5 3 は、正極 5 7 を含み、上部チャック 5 5 は、負極 5 9 を含む。一変形形態によると、分極は、互いに入れ替えることができる。複合体 1 3 は、2 つのチャック 5 3 と 5 5 との間に挟まれている。

**【 0 0 4 6 】**

また、本構成では、電界線 6 1 は、圧電効果を最適化するために圧電ドナー基板の分極方向 1 7 と平行であり、所定の分割領域 1 において最適化された脆弱化をもたらす。20

**【 0 0 4 7 】**

この電極構成では、最大 5 kV、特に 200 V ~ 1 kV の電圧を電極 5 3 及び 5 5 に印加して、圧電ドナー基板 3 と支持基板 1 1 の界面における剥離を観察することなく、所定の分割領域 1 において所望の効果を得ることができる。

**【 0 0 4 8 】**

第 2 及び第 3 の実施形態の剥離チャンバ 3 1 及び 5 1 は、さらなる変形形態によると、本発明による方法のステップ b ) に使用され、図 1 c に示すような取付けステップを実現することができる。さらに、剥離チャンバは、さらなる変形形態によると、熱処理を行うこと及び / 又は真空下でのプロセスステップを行うことができるように加熱手段及び / 又は真空ポンプを備えることもできる。30

**【 0 0 4 9 】**

第 1 ~ 第 3 の実施形態のいずれか 1 つの特徴は、個々に、又は他の実施形態のいずれか 1 つとグループで組み合わされて、本発明による方法及び / 又は分割チャンバのさらなる変形形態を形成することができる。

【図 1 a】

【図 1 b】

【図 1 c】

【図 1 d】

【図 1 e】

【図 2】

【図 3】

---

フロントページの続き

(74)代理人 100123995

弁理士 野田 雅一

(72)発明者 シャルル・アルフレッド, セドリック

フランス, 38000 グルノーブル, プラース ノートル・ダム 1

審査官 上田 智志

(56)参考文献 特開2012-213244(JP,A)

特表2001-511608(JP,A)

特表2015-529978(JP,A)

特開2010-109909(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 41/312, 41/187,

21/02