(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau

(43) International Publication Date

24 November 2011 (24.11.2011)

(10) International Publication Number

WO 2011/145467 A1

(51) International Patent Classification:

*H01L 29/786* (2006.01)   *H01L 21/336* (2006.01)

*G02F 1/1368* (2006.01)   *H01L 51/50* (2006.01)

*G09F 9/30* (2006.01)   *H05B 33/14* (2006.01)

*H01L 21/316* (2006.01)

(72) Inventors; and

(75) Inventors/Applicants (for US only): **ENDO, Yuta**

[JP/JP]; c/o SEMICONDUCTOR ENERGY LABORATORY CO., LTD., 398, Hase, Atsugi-shi, Kanagawa, 2430036 (JP). **SASAKI, Toshinari**. **NODA, Kosei**. **SATO, Mizuho**.

(21) International Application Number:

PCT/JP2011/060682

(22) International Filing Date:

27 April 2011 (27.04.2011)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

2010-116952   21 May 2010 (21.05.2010)   JP

(71) Applicant (for all designated States except US): **SEMICONDUCTOR ENERGY LABORATORY CO., LTD.**

[JP/JP]; 398, Hase, Atsugi-shi, Kanagawa 2430036 (JP).

(81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PE, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ,

*[Continued on next page]*

(54) Title: SEMICONDUCTOR DEVICE

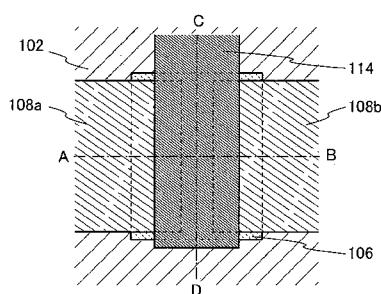

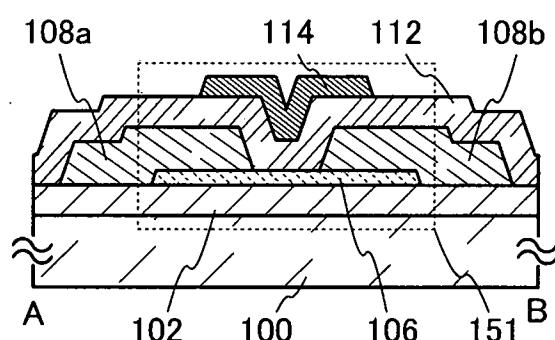

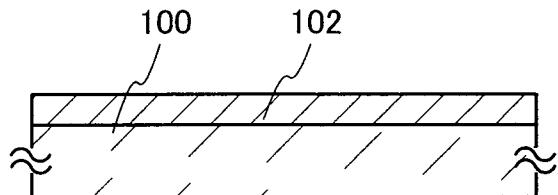

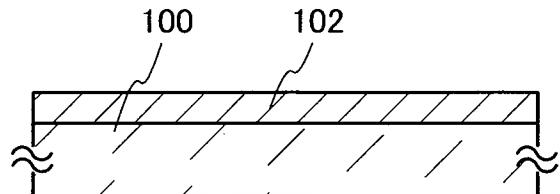

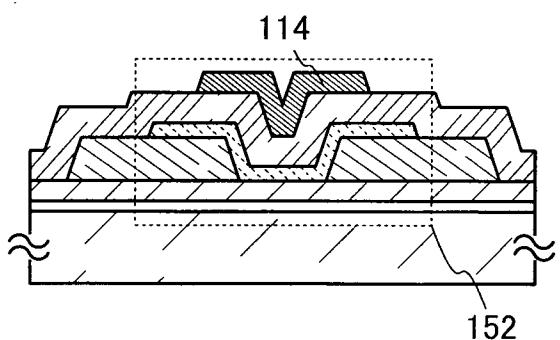

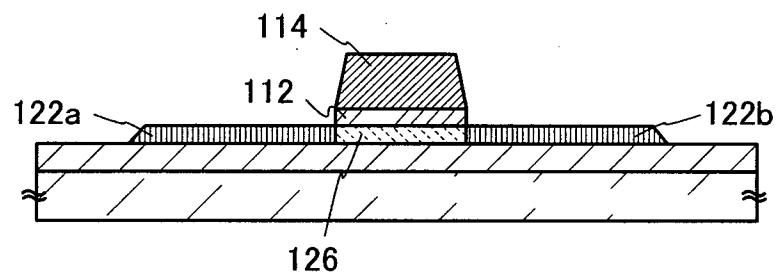

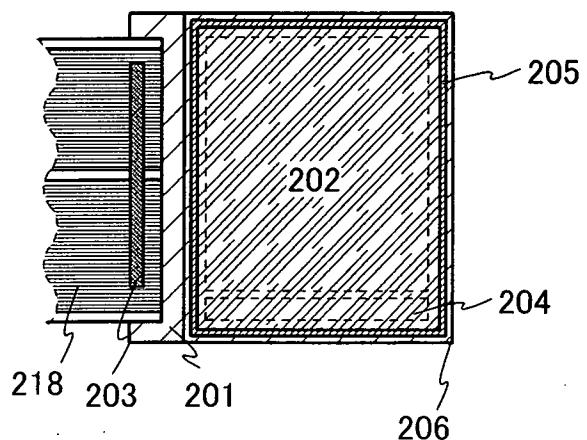

FIG. 1A

(57) Abstract: An object of the present invention is to manufacture a semiconductor device where fluctuation in electrical characteristics is small and reliability is high in a transistor in which an oxide semiconductor is used. An insulating layer from which oxygen is released by heating is used as a base insulating layer of an oxide semiconductor layer which forms a channel. Oxygen is released from the base insulating layer, whereby oxygen deficiency in the oxide semiconductor layer and an interface state between the base insulating layer and the oxide semiconductor layer can be reduced. Thus, a semiconductor device where fluctuation in electrical characteristics is small and reliability is high can be manufactured.

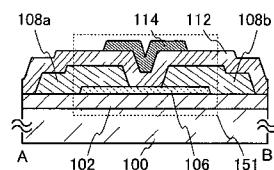

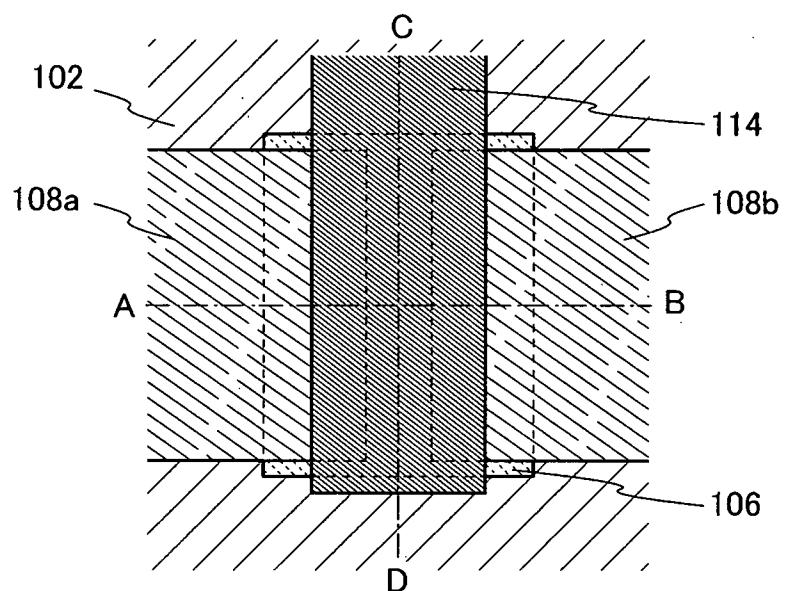

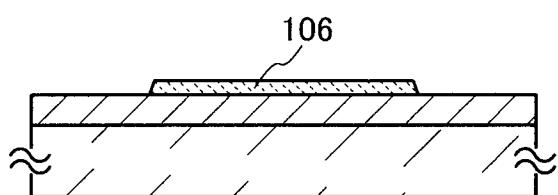

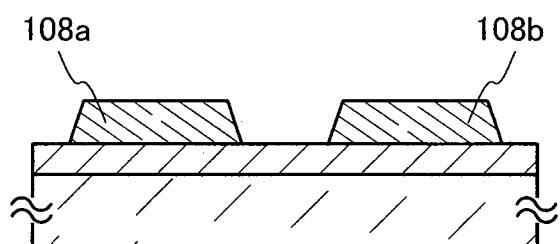

FIG. 1B

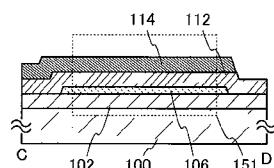

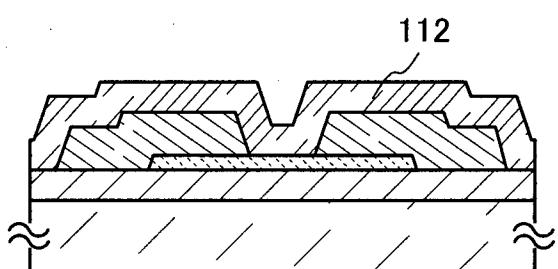

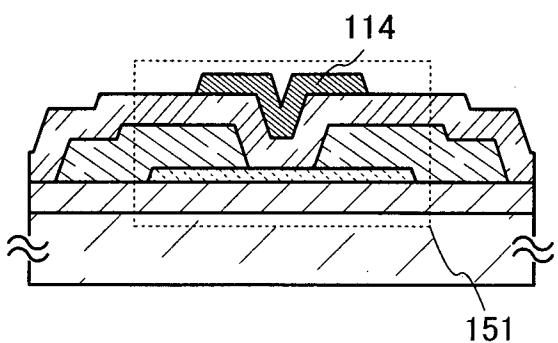

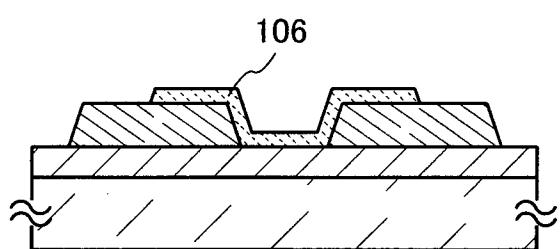

FIG. 1C

TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

**Published:**

— *with international search report (Art. 21(3))*

## DESCRIPTION

## SEMICONDUCTOR DEVICE

## 5 TECHNICAL FIELD

[0001]

The present invention relates to a semiconductor device and a manufacturing method thereof.

[0002]

10 In this specification, a semiconductor device means a general device which can function by utilizing semiconductor characteristics, and an electrooptic device, a semiconductor circuit, and an electronic device are all semiconductor devices.

## BACKGROUND ART

15 [0003]

A technique by which transistors are formed using semiconductor thin films formed over a substrate having an insulating surface has been attracting attention. Such transistors are applied to a wide range of electronic devices such as an integrated circuit (IC) and an image display device (display device). As semiconductor thin films 20 applicable to the transistors, silicon-based semiconductor materials have been widely used, but oxide semiconductors have been attracting attention as alternative materials.

[0004]

For example, disclosed is a transistor whose active layer is formed using an amorphous oxide containing indium (In), gallium (Ga), and zinc (Zn) and having an 25 electron carrier concentration of lower than  $10^{18} / \text{cm}^3$  (see Patent Document 1).

[0005]

A transistor including an oxide semiconductor is known to have a problem of low reliability because of high possibility of fluctuation in electrical characteristics, although the transistor including an oxide semiconductor can be operated at higher 30 speed than a transistor including amorphous silicon and can be manufactured more easily than a transistor including polycrystalline silicon. For example, the threshold voltage of the transistor fluctuates between before and after a bias-temperature stress

test (BT test). Note that in this specification, a "threshold voltage" refers to a gate voltage which is needed to turn on a transistor. "Gate voltage" refers to a potential difference between a source electrode and a gate electrode when the potential of the source electrode is used as a reference potential.

5

[Reference]

[0006]

[Patent Document 1] Japanese Published Patent Application No. 2006-165528

10 DISCLOSURE OF INVENTION

[0007]

Fluctuation in the threshold voltage due to a BT test of the transistor including an oxide semiconductor reduces the reliability of the transistor including an oxide semiconductor. Therefore, an object of one embodiment of the present invention is to

15 improve the reliability of a semiconductor device including an oxide semiconductor.

[0008]

One embodiment of the present invention is a semiconductor device or a method thereof based on the following technical idea: an insulating layer from which oxygen is released by heating is formed as an insulating layer which is a base layer of

20 an oxide semiconductor layer (also referred to as a base insulating layer).

[0009]

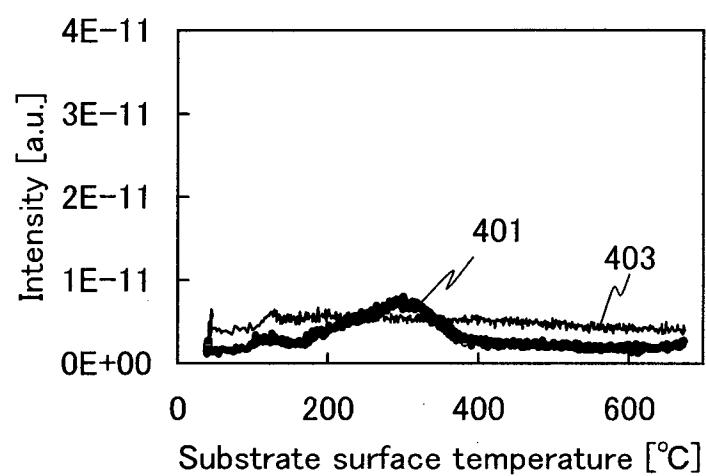

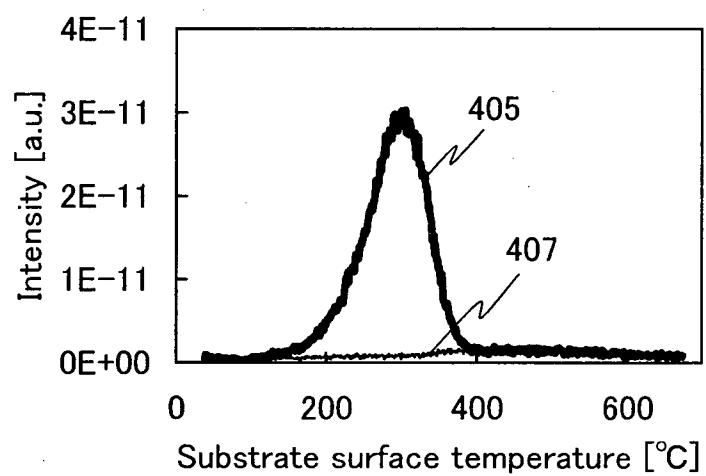

"Being possible to release oxygen by heating" means that the released amount of oxygen molecules (also referred to as  $O_2$ ) is greater than or equal to  $1 \times 10^{18}/cm^3$ , preferably greater than or equal to  $3 \times 10^{20}/cm^3$  in thermal desorption spectroscopy

25 (TDS).

[0010]

By supplying oxygen from the base insulating layer to the oxide semiconductor layer, an interface state between the base insulating layer and the oxide semiconductor layer can be reduced. As a result, it is possible to sufficiently suppress trapping of

30 charge or the like, which can be generated due to the operation of a semiconductor device, or the like, at an interface between the base insulating layer and the oxide

semiconductor layer.

[0011]

Further, charge is generated due to oxygen deficiency in the oxide semiconductor layer in some cases. Oxygen deficiency in the oxide semiconductor 5 layer generally becomes donors and electrons which are carriers are generated. As a result, a threshold voltage of a transistor shifts in a negative direction. Oxygen is sufficiently released from the base insulating layer, whereby oxygen deficiency in the oxide semiconductor layer which causes the shift of the threshold voltage in a negative direction can be compensated by oxygen supplied from the base insulating layer.

10 [0012]

In other words, when oxygen deficiency is generated in the oxide semiconductor layer, it becomes difficult to suppress trapping of charge at the interface between the base insulating layer and the oxide semiconductor layer; however, by providing the insulating layer from which oxygen is released by heating as the base 15 insulating layer, an interface state and oxygen deficiency in the oxide semiconductor layer can be reduced and an adverse effect of trapping of charge at the interface between the oxide semiconductor layer and the base insulating layer can be reduced.

[0013]

Thus, the advantageous effect of one embodiment of the present invention is 20 attributed to the base insulating layer from which oxygen is released by heating.

[0014]

Since the trapping of a charge at the interface between the base insulating layer and the oxide semiconductor layer can be suppressed, which is described above as the 25 advantageous effect, an off-state current of the transistor including an oxide semiconductor can be increased and malfunctions such as fluctuation in the threshold voltage can be suppressed, and further the reliability of the semiconductor device can be improved.

[0015]

Note that the insulating layer from which oxygen is released by heating 30 preferably has an enough thickness with respect to the oxide semiconductor layer. This is because when the thickness of the insulating layer from which oxygen is released by heating is smaller than that of the oxide semiconductor layer, oxygen is not

sufficiently supplied to the oxide semiconductor layer in some cases.

[0016]

Another embodiment of the present invention is a semiconductor device including a base insulating layer, an oxide semiconductor layer over the base insulating layer, a source electrode and a drain electrode which are electrically connected to the oxide semiconductor layer, a gate insulating layer part of which is in contact with the oxide semiconductor layer, and a gate electrode over the gate insulating layer. The base insulating layer is an insulating layer from which oxygen is released by heating. More preferably, an insulating layer from which oxygen is released by heating is used as the gate insulating layer.

[0017]

In the above structure, the base insulating layer can be a single layer or a stacked layer formed using one or more of silicon oxide, silicon oxynitride, silicon nitride oxide, and aluminum oxide. The gate insulating layer can be a single layer or a stacked layer formed using one or more of silicon oxide, silicon oxynitride, aluminum oxide, and hafnium oxide.

[0018]

In this specification, silicon oxynitride refers to a substance that contains more oxygen than nitrogen and for example, silicon oxynitride includes oxygen, nitrogen, silicon, and hydrogen at concentrations ranging from greater than or equal to 50 atomic% and less than or equal to 70 atomic%, greater than or equal to 0.5 atomic% and less than or equal to 15 atomic%, greater than or equal to 25 atomic% and less than or equal to 35 atomic%, and greater than or equal to 0 atomic% and less than or equal to 10 atomic%, respectively. Further, silicon nitride oxide refers to a substance that contains more nitrogen than oxygen and for example, silicon nitride oxide includes oxygen, nitrogen, silicon, and hydrogen at concentrations ranging from greater than or equal to 5 atomic% and less than or equal to 30 atomic%, greater than or equal to 20 atomic% and less than or equal to 55 atomic%, greater than or equal to 25 atomic% and less than or equal to 35 atomic%, and greater than or equal to 10 atomic% and less than or equal to 25 atomic%, respectively. Note that rates of oxygen, nitrogen, silicon, and hydrogen fall within the above ranges in the cases where measurement is performed

using Rutherford backscattering spectrometry (RBS) or hydrogen forward scattering spectrometry (HFS). In addition, the total of the percentages of the constituent elements does not exceed 100 atomic%.

[0019]

5 In the above structure, an insulating layer (also referred to as a protective insulating layer) which covers the gate insulating layer and the gate electrode may be provided. The protective insulating layer is preferably an insulating layer from which oxygen is released by heating. A conductive layer may be provided below the oxide semiconductor layer.

10 [0020]

In the above, the channel length  $L$  of the transistor, which depends on the distance between the source electrode and the drain electrode, can be greater than or equal to 10 nm and less than or equal to 10  $\mu\text{m}$ , for example, 0.1  $\mu\text{m}$  to 0.5  $\mu\text{m}$ . It is needless to say that the channel length  $L$  may be greater than or equal to 1  $\mu\text{m}$ . The 15 channel width  $W$  may be greater than or equal to 10  $\mu\text{m}$ .

[0021]

According to one embodiment of the present invention, by providing an insulating layer from which oxygen is released by heating as a base insulating layer of an oxide semiconductor layer, a transistor which has a small off-state current, small 20 variation in the threshold voltage, and stable electrical characteristics can be provided.

[0022]

Alternatively, according to one embodiment of the present invention, a semiconductor device which includes a transistor having favorable electrical characteristics and high reliability can be provided.

25

## BRIEF DESCRIPTION OF DRAWINGS

[0023]

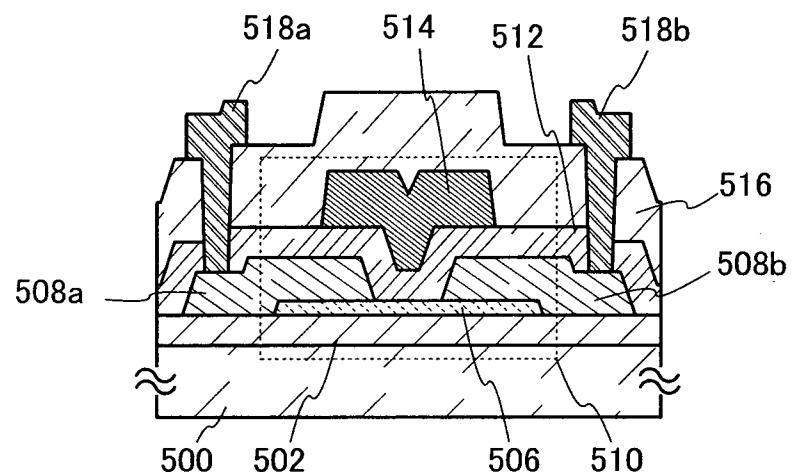

FIGS. 1A to 1C are a top view and cross-sectional views illustrating an example of a semiconductor device according to one embodiment of the present 30 invention.

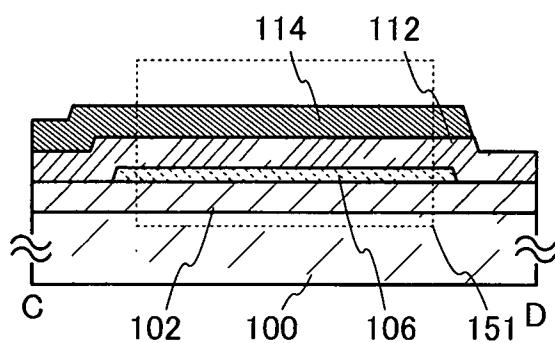

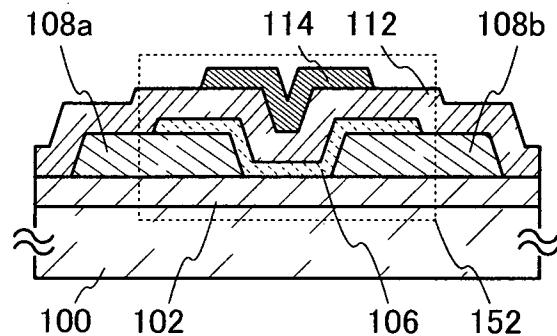

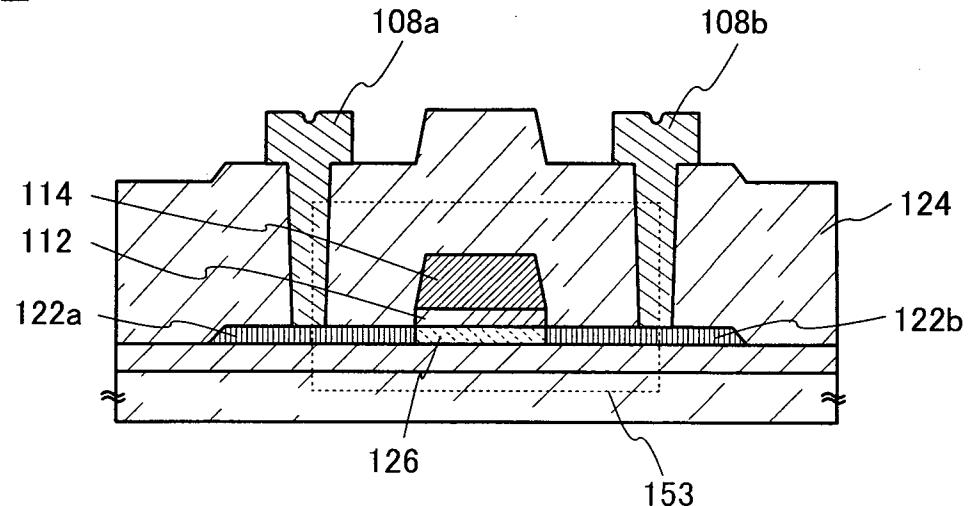

FIGS. 2A and 2B are cross-sectional views each illustrating an example of a

semiconductor device according to one embodiment of the present invention.

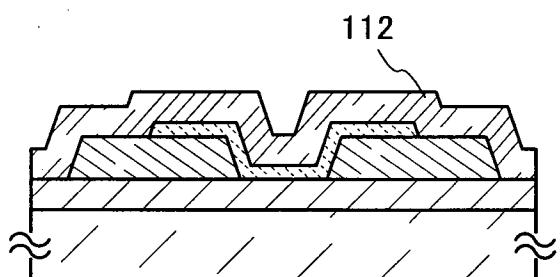

FIGS. 3A to 3E are cross-sectional views illustrating an example of a manufacturing process of a semiconductor device according to one embodiment of the present invention.

5 FIGS. 4A to 4E are cross-sectional views illustrating an example of a manufacturing process of a semiconductor device according to one embodiment of the present invention.

FIGS. 5A to 5E are cross-sectional views illustrating an example of a manufacturing process of a semiconductor device according to one embodiment of the 10 present invention.

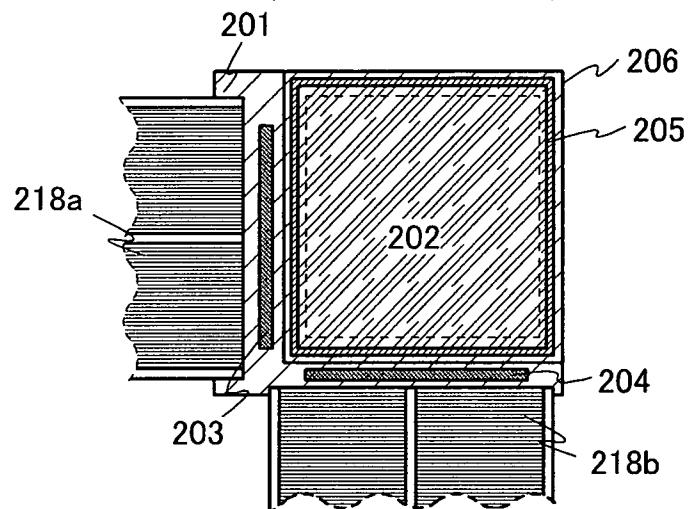

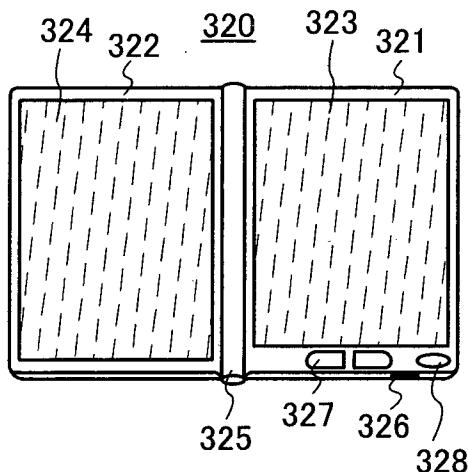

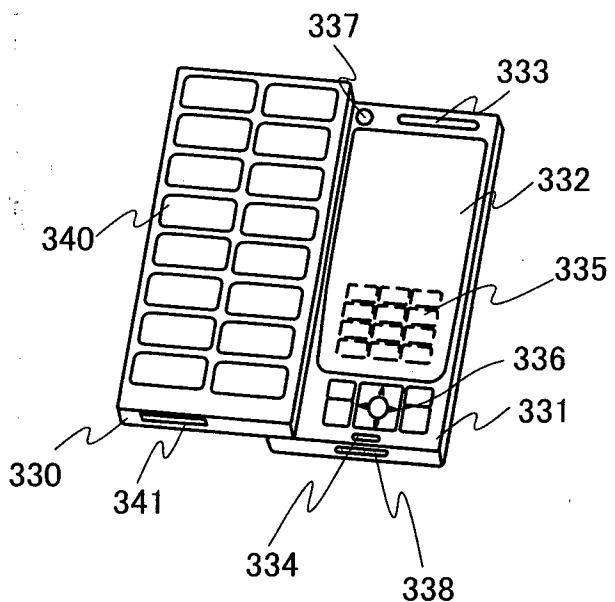

FIGS. 6A to 6C are diagrams each illustrating one mode of a semiconductor device according to one embodiment of the present invention.

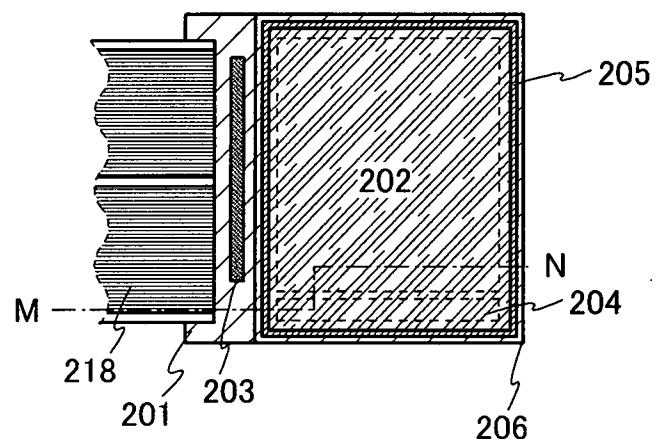

FIG. 7 is a cross-sectional view illustrating one mode of a semiconductor device according to one embodiment of the present invention.

15 FIG. 8 is a cross-sectional view illustrating one mode of a semiconductor device according to one embodiment of the present invention.

FIG. 9 is a cross-sectional view illustrating one mode of a semiconductor device according to one embodiment of the present invention.

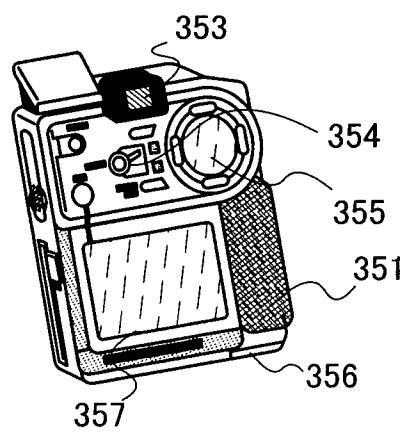

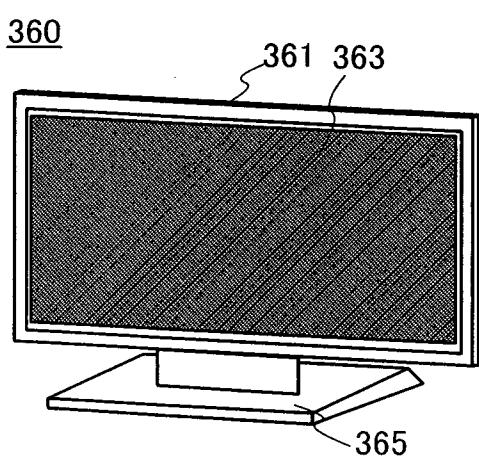

20 FIGS. 10A to 10F are diagrams each illustrating an electronic appliance as a semiconductor device according to one embodiment of the present invention.

FIGS. 11A and 11B are graphs each showing TDS spectra of a silicon oxide layer formed using one embodiment of the present invention.

FIG. 12 is a cross-sectional view illustrating one mode of a semiconductor device according to one embodiment of the present invention.

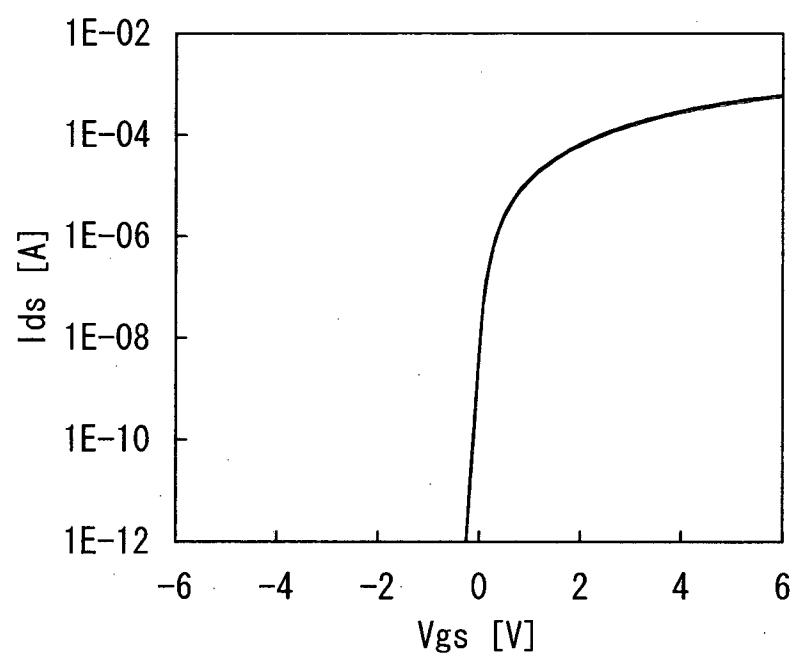

25 FIG. 13 is a graph showing drain current ( $Id_s$ )-gate voltage ( $V_{gs}$ ) measurement results of a semiconductor device manufactured using one embodiment of the present invention.

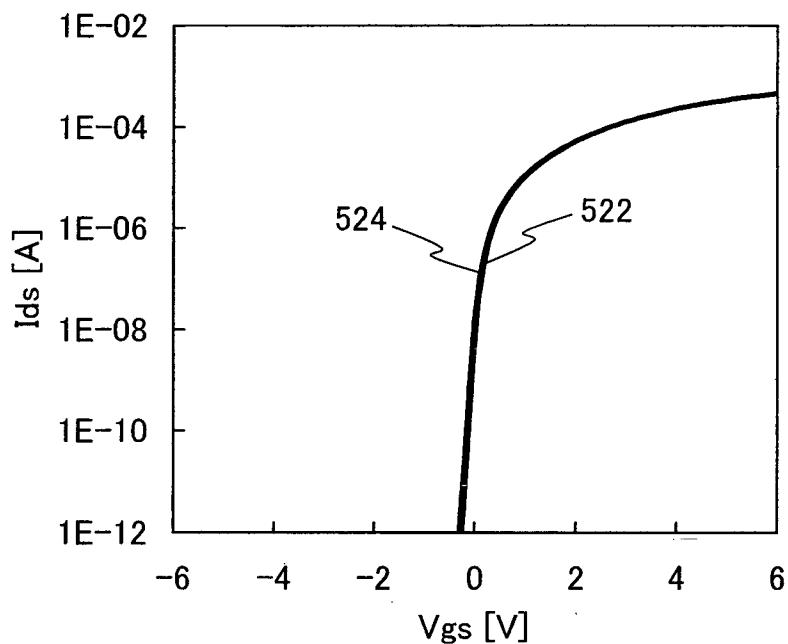

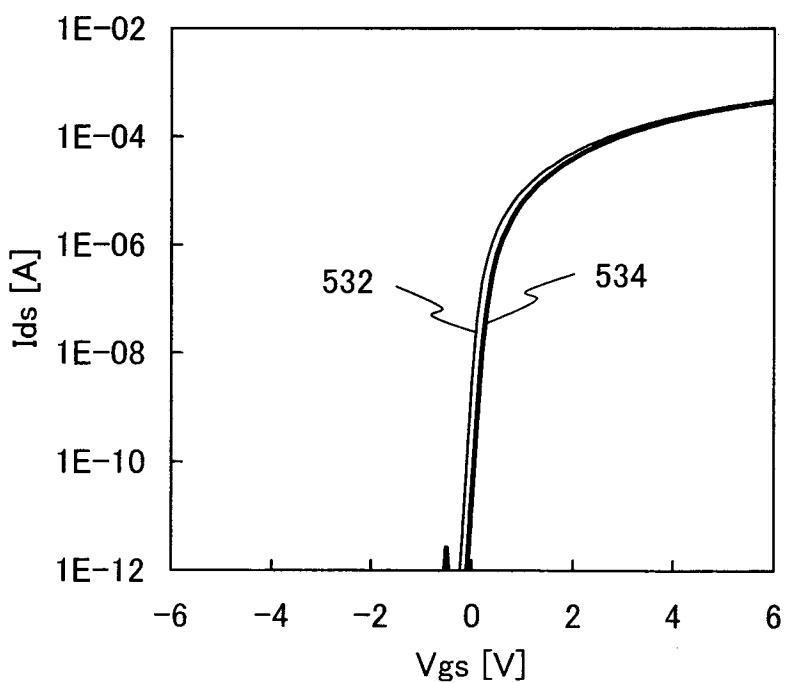

FIGS. 14A and 14B are graphs each showing  $Id_s$ - $V_{gs}$  measurement results before and after a BT test of a semiconductor device manufactured using one 30 embodiment of the present invention.

#### BEST MODE FOR CARRYING OUT THE INVENTION

## [0024]

Hereinafter, embodiments of the present invention will be described in detail with reference to the drawings. Note that the present invention is not limited to the following description, and it will be easily understood by those skilled in the art that 5 modes and details disclosed herein can be modified in various ways without departing from the spirit and the scope of the present invention. Thus, the present invention should not be construed as being limited to the following description of the embodiments. In describing structures of the present invention with reference to the drawings, the same reference numerals are used in common for the same portions in 10 different drawings. Note that the same hatch pattern is applied to similar parts, and the similar parts are not especially denoted by reference numerals in some cases.

## [0025]

Note that the ordinal numbers such as "first" and "second" in this specification are used for convenience and do not denote the order of steps or the stacking order of 15 layers. In addition, the ordinal numbers in this specification do not denote particular names which specify the present invention.

## [0026]

## (Embodiment 1)

In this embodiment, one embodiment of a semiconductor device and a 20 manufacturing method thereof will be described with reference to FIGS. 1A to 1C, FIGS. 2A and 2B, FIGS. 3A to 3E, FIGS. 4A to 4E, and FIGS. 5A to 5E.

## [0027]

FIGS. 1A to 1C are a top view and cross-sectional views of a transistor 151 which is a top-gate top-contact type as an example of a semiconductor device according 25 to one embodiment of the present invention. Here, FIG. 1A is a top view, FIG. 1B is a cross-sectional view along A-B of FIG. 1A, and FIG. 1C is a cross-sectional view along C-D of FIG. 1A. Note that in FIG. 1A, some of components of the transistor 151 (for example, a gate insulating layer 112) are omitted for brevity.

## [0028]

30 The transistor 151 in FIGS. 1A to 1C includes an insulating layer 102, an oxide semiconductor layer 106, a source electrode 108a, a drain electrode 108b, the gate insulating layer 112, and a gate electrode 114 over a substrate 100.

## [0029]

As a material of the insulating layer 102, silicon oxide, silicon oxynitride, aluminum oxide, a mixed material of any of them, or the like may be used. Alternatively, the insulating layer 102 may be formed using a stacked layer of the above 5 material and silicon oxide, silicon nitride, silicon oxynitride, silicon nitride oxide, aluminum oxide, aluminum nitride, a mixed material of any of them, or the like. For example, when the insulating layer 102 has a stacked-layer structure of a silicon nitride layer, a silicon nitride oxide layer, an aluminum oxide layer, or an aluminum nitride layer, and a silicon oxide layer, entry of moisture and hydrogen from the substrate 100 10 or the like to the transistor 151 can be prevented. In the case where the insulating layer 102 is formed to have a stacked-layer structure, an oxide layer of silicon oxide, silicon oxynitride, aluminum oxide, a mixed material of any of them, or the like is preferably formed on a side where the insulating layer 102 is in contact with the oxide semiconductor layer 106. Note that the insulating layer 102 functions as a base layer 15 of the transistor 151. The insulating layer 102 is an insulating layer from which oxygen is released by heating. "Releasing oxygen by heating" means that the released amount of  $O_2$  is greater than or equal to  $1 \times 10^{18}/cm^3$ , preferably greater than or equal to  $3 \times 10^{20}/cm^3$  in TDS analysis.

## [0030]

20 As a material used for the oxide semiconductor layer, a four-component metal oxide material such as an In-Sn-Ga-Zn-O-based material; a three-component metal oxide material such as an In-Ga-Zn-O-based material, an In-Sn-Zn-O-based material, an In-Al-Zn-O-based material, a Sn-Ga-Zn-O-based material, an Al-Ga-Zn-O-based material, or a Sn-Al-Zn-O-based material; a two-component metal oxide material such 25 as an In-Zn-O-based material, a Sn-Zn-O-based material, an Al-Zn-O-based material, a Zn-Mg-O-based material, a Sn-Mg-O-based material, an In-Mg-O-based material, or an In-Ga-O-based material; an In-O-based material; a Sn-O-based material; a Zn-O-based material; or the like can be used. In addition, any of the above materials may contain silicon oxide. Here, for example, an In-Ga-Zn-O-based material means an oxide layer 30 containing indium (In), gallium (Ga), and zinc (Zn), and there is no particular limitation on the composition ratio thereof. Further, the In-Ga-Zn-O-based material may contain

an element other than In, Ga, and Zn. As an example, in the case where an In-Zn-O-based material is used, any of the following is employed: In/Zn is greater than or equal to 0.5 and less than or equal to 50 in an atomic ratio, preferably In/Zn is greater than or equal to 1 and less than or equal to 20 in an atomic ratio, or more preferably 5 In/Zn is greater than or equal to 1.5 and less than or equal to 15 in an atomic ratio. When the atomic ratio of Zn is in the above range, the field effect mobility of the transistor can be improved. Here, when the atomic ratio of the compound is In:Zn:O =  $X:Y:Z$ , the relation of  $Z > 1.5X + Y$  is preferably satisfied.

[0031]

10 For the oxide semiconductor layer, a thin film using a material represented by the chemical formula,  $\text{InMO}_3(\text{ZnO})_m$  ( $m > 0$ ), can be used. Here, M represents one or more metal elements selected from Ga, Al, Mn, and Co. For example, M can be Ga, Ga and Al, Ga and Mn, Ga and Co, or the like.

[0032]

15 An interface state between the insulating layer 102 and the oxide semiconductor layer 106 and oxygen deficiency in the oxide semiconductor layer 106 can be reduced. By the above reduction in the interface state, the fluctuation in threshold voltage before and after a BT test can be reduced.

[0033]

20 The gate insulating layer 112 can have a structure similar to that of the insulating layer 102, and is preferably an insulating layer from which oxygen is released by heating. Note that a material having a high dielectric constant, such as hafnium oxide or aluminum oxide, may be used for the gate insulating layer 112 considering the function of the gate insulating layer of the transistor. Alternatively, a stacked layer of 25 silicon oxide, silicon oxynitride, or silicon nitride and a material having a high dielectric constant, such as hafnium oxide or aluminum oxide, may be used considering a gate withstand voltage and a state of an interface of the oxide semiconductor layer.

[0034]

30 A protective insulating layer may further be provided over the transistor 151. The protective insulating layer can have a structure similar to that of the insulating layer 102. In order to electrically connect the source electrode 108a or the drain electrode

108b and a wiring, an opening may be formed in the insulating layer 102, the gate insulating layer 112, and the like. A second gate electrode may further be provided below the oxide semiconductor layer 106. Note that it is not always necessary but preferable to process the oxide semiconductor layer 106 into an island shape.

5 [0035]

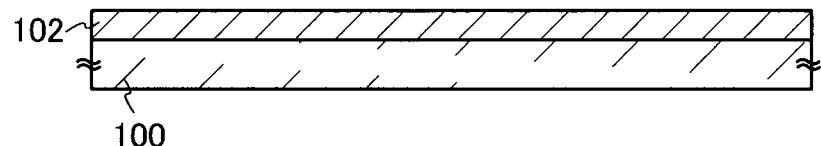

FIGS. 2A and 2B illustrate cross-sectional structures of transistors having different structures from that of the transistor 151.

[0036]

10 A transistor 152 in FIG. 2A is the same as the transistor 151 in that it includes the insulating layer 102, the oxide semiconductor layer 106, the source electrode 108a, the drain electrode 108b, the gate insulating layer 112, and the gate electrode 114. The differences between the transistor 152 and the transistor 151 are the positions where the oxide semiconductor layer 106 is connected to the source electrode 108a and the drain electrode 108b. That is, in the transistor 152, the source electrode 108a and the drain electrode 108b are in contact with bottom portions of the oxide semiconductor layer 106. 15 The other components are similar to those of the transistor 151 in FIGS. 1A to 1C.

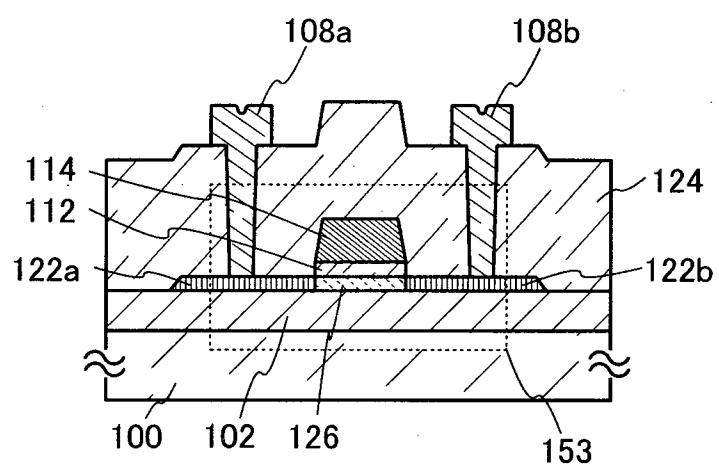

[0037]

20 The transistor 153 in FIG. 2B is the same as the transistor 151 and the transistor 152 in that it includes the insulating layer 102, the gate insulating layer 112, the gate electrode 114, the source electrode 108a, and the drain electrode 108b. The transistor 153 is different from the transistor 151 and the transistor 152 in that a channel region 126, a source region 122a, and a drain region 122b are formed in the oxide semiconductor layer in the same plane. The source region 122a and the drain region 122b are connected to the source electrode 108a and the drain electrode 108b, 25 respectively, with a protective insulating layer 124 interposed therebetween. Note that in FIG. 2B, the gate insulating layer 112 is provided only under the gate electrode 114; however, one embodiment of the present invention is not limited thereto. For example, the gate insulating layer 112 may be provided to cover the oxide semiconductor layer including the channel region 126, the source region 122a, and the drain region 122b.

30 [0038]

Examples of a manufacturing process of the transistor in FIGS. 1A to 1C will be described below with reference to FIGS. 3A to 3E and FIGS. 4A to 4E.

[0039]

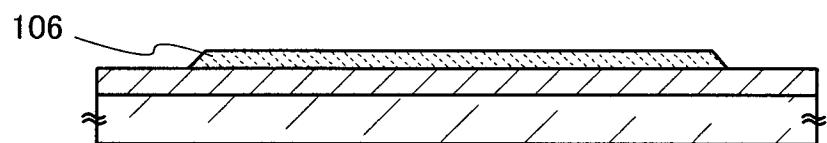

To begin with, an example of a manufacturing process of the transistor 151 in FIGS. 1A to 1C will be described with reference to FIGS. 3A to 3E.

[0040]

5 First, the insulating layer 102 is formed over the substrate 100 (see FIG. 3A). The insulating layer 102 is an insulating layer from which oxygen is released by heating.

[0041]

10 There is no particular limitation on the property of a material and the like of the substrate 100 as long as the material has heat resistance enough to withstand at least heat treatment to be performed later. For example, a glass substrate, a ceramic substrate, a quartz substrate, a sapphire substrate, or the like can be used as the substrate 100. Alternatively, a single crystal semiconductor substrate or a polycrystalline semiconductor substrate made of silicon, silicon carbide, or the like, a compound 15 semiconductor substrate made of silicon germanium or the like, an SOI substrate, or the like may be used as the substrate 100. Still alternatively, any of these substrates further provided with a semiconductor element may be used as the substrate 100.

[0042]

20 A flexible substrate may be used as the substrate 100. In that case, a transistor is formed directly on the flexible substrate. Note that as a method for forming a transistor over a flexible substrate, there is also a method in which, after a non-flexible substrate is used as the substrate 100 and a transistor is formed thereover, the transistor is separated from the substrate and transferred to a flexible substrate. In that case, a separation layer is preferably provided between the substrate 100 and the transistor.

25 [0043]

30 As a formation method of the insulating layer 102, a plasma CVD method or a sputtering method can be employed, for example. The insulating layer from which oxygen is released by heating is preferably formed by a sputtering method. As a material of the insulating layer 102, silicon oxide, silicon oxynitride, aluminum oxide, a mixed material of any of them, or the like may be used. Alternatively, the insulating layer 102 may be formed using a stacked layer of the above material and silicon oxide, silicon nitride, silicon oxynitride, silicon nitride oxide, aluminum oxide, aluminum

nitride, a mixed material of any of them, or the like. In the case where the insulating layer 102 is formed to have a stacked-layer structure, an oxide layer of silicon oxide, silicon oxynitride, aluminum oxide, a mixed material of any of them, or the like is preferably formed on a side where the insulating layer 102 is in contact with the oxide semiconductor layer 106. The total thickness of the insulating layer 102 is preferably 5 20 nm or more, more preferably 100 nm or more. When the thick insulating layer 102 is formed, the amount of oxygen released from the insulating layer 102 can be increased.

[0044]

10 In order to form the insulating layer from which oxygen is released by heating by a sputtering method, in the case where oxygen or a mixed gas of oxygen and a rare gas (such as helium, neon, argon, krypton, or xenon) is used as a film formation gas, the proportion of oxygen is preferably set higher. For example, the concentration of oxygen in the whole gas is preferably set to be higher than or equal to 6 % and lower 15 than 100 %.

[0045]

For example, a silicon oxide film is formed by an RF sputtering method under the following conditions: quartz (preferably synthetic quartz) is used as a target; the substrate temperature is higher than or equal to 30 °C and lower than or equal to 450 °C 20 (preferably higher than or equal to 70 °C and lower than or equal to 200 °C); the distance between the substrate and the target (the T-S distance) is greater than or equal to 20 mm and less than or equal to 400 mm (preferably greater than or equal to 40 mm and less than or equal to 200 mm); the pressure is higher than or equal to 0.1 Pa and lower than or equal to 4 Pa (preferably higher than or equal to 0.2 Pa and lower than or 25 equal to 1.2 Pa); the high-frequency power is higher than or equal to 0.5 kW and lower than or equal to 12 kW (preferably higher than or equal to 1 kW and lower than or equal to 5 kW); and the proportion of  $O_2/(O_2 + Ar)$  in the film formation gas is higher than or equal to 1 % and lower than or equal to 100 % (preferably higher than or equal to 6 % and lower than or equal to 100 %). Note that a silicon target may be used as the target 30 instead of the quartz (preferably synthetic quartz) target. As the film formation gas, oxygen or a mixed gas of oxygen and argon is used.

[0046]

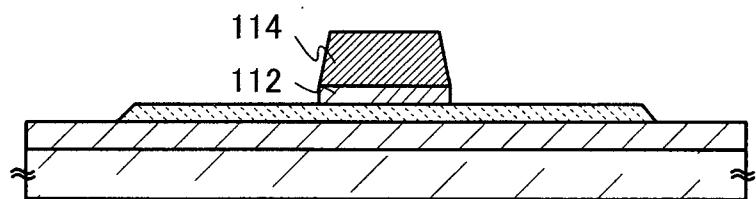

Next, an oxide semiconductor layer is formed over the insulating layer 102 and then is processed to form the oxide semiconductor layer 106 having an island shape (see FIG. 3B).

5 [0047]

For example, the oxide semiconductor layer can be formed by a sputtering method, a vacuum evaporation method, a pulse laser deposition method, a CVD method, or the like. The thickness of the oxide semiconductor layer is preferably greater than or equal to 3 nm and less than or equal to 50 nm. This is because when the oxide semiconductor layer is too thick (e.g., 100 nm or more), there is a possibility that the short channel effect has a large influence and the transistor with a small size is normally on. Here, "normally on" means a state where a channel exists without applying voltage to a gate electrode and current flows through the transistor. Note that the insulating layer 102 and the oxide semiconductor layer are preferably formed 10 successively without exposure to the air.

15

[0048]

For example, the oxide semiconductor layer is formed by a sputtering method using an In-Ga-Zn-O-based oxide target.

[0049]

20 As the In-Ga-Zn-O-based oxide target, for example, an oxide target having a composition ratio of  $\text{In}_2\text{O}_3:\text{Ga}_2\text{O}_3:\text{ZnO} = 1:1:1$  [molar ratio] can be used. Note that it is not necessary to limit the material and the composition ratio of the target to the above. For example, an oxide target having a composition ratio of  $\text{In}_2\text{O}_3:\text{Ga}_2\text{O}_3:\text{ZnO} = 1:1:2$  [molar ratio] can be used.

25 [0050]

The relative density of the oxide target is higher than or equal to 90 % and lower than or equal to 100 %, preferably higher than or equal to 95 % and lower than or equal to 99.9 %. This is because, with the use of the oxide target with a high relative density, the dense oxide semiconductor layer can be formed.

30 [0051]

The film formation may be performed in a rare gas atmosphere, an oxygen

atmosphere, a mixed atmosphere containing a rare gas and oxygen, or the like. Moreover, it is preferably an atmosphere using a high-purity gas in which impurities such as hydrogen, water, a hydroxyl group, and hydride are sufficiently removed so that entry of hydrogen, water, a hydroxyl group, and hydride into the oxide semiconductor 5 layer can be prevented.

[0052]

For example, the oxide semiconductor layer can be formed as follows.

[0053]

An example of the film formation conditions is as follows: the distance 10 between the substrate and the target is 60 mm; the pressure is 0.4 Pa; the direct-current (DC) power is 0.5 kW; and the film formation atmosphere is a mixed atmosphere containing argon and oxygen (the proportion of the oxygen flow is 33 %). Note that a pulse DC sputtering method is preferable because powder substances (also referred to as particles or dust) generated in film formation can be reduced and the film thickness can 15 be uniform.

[0054]

In this case, when the substrate temperature is higher than or equal to 100 °C and lower than or equal to 450 °C, preferably higher than or equal to 150 °C and lower than or equal to 250 °C, oxygen is released from the insulating layer 102, whereby 20 oxygen deficiency in the oxide semiconductor layer and an interface state between the insulating layer 102 and the oxide semiconductor layer can be reduced.

[0055]

Note that before the oxide semiconductor layer 106 is formed by a sputtering method, a substance attached to a surface where the oxide semiconductor layer is to be 25 formed (e.g., a surface of the insulating layer 102) may be removed by reverse sputtering in which a rare gas is introduced and plasma is generated. Here, the reverse sputtering is a method by which ions collide with a surface to be processed so that the surface is modified, in contrast to normal sputtering by which ions collide with a sputtering target. An example of a method for making ions collide with a surface to be 30 processed is a method in which high-frequency voltage is applied to the surface side in an argon atmosphere so that plasma is generated near an object to be processed. Note

that an atmosphere of nitrogen, helium, oxygen, or the like may be used instead of an argon atmosphere.

[0056]

The oxide semiconductor layer 106 can be processed by etching after a mask 5 having a desired shape is formed over the oxide semiconductor layer. The mask can be formed by a method such as photolithography. Alternatively, the mask may be formed by an ink-jet method or the like.

[0057]

For the etching of the oxide semiconductor layer, either wet etching or dry 10 etching may be employed. It is needless to say that both of them may be employed in combination.

[0058]

After that, heat treatment (first heat treatment) is preferably performed on the oxide semiconductor layer. By the first heat treatment, excessive hydrogen (including 15 water and a hydroxyl group) in the oxide semiconductor layer can be removed and a structure of the oxide semiconductor layer can be ordered. The temperature of the first heat treatment is higher than or equal to 100 °C and lower than or equal to 650 °C or lower than the strain point of the substrate, preferably higher than or equal to 250 °C and lower than or equal to 600 °C. The atmosphere of the first heat treatment is an 20 oxidizing gas atmosphere or an inert gas atmosphere.

[0059]

Note that an inert gas atmosphere is preferably an atmosphere that contains nitrogen or a rare gas as its main component and does not contain water, hydrogen, and the like. For example, the purity of nitrogen or a rare gas such as helium, neon, or 25 argon introduced into a heat treatment apparatus is set to 6N (99.9999 %) or more, preferably 7N (99.99999 %) or more (i.e., the impurity concentration is 1 ppm or lower, preferably 0.1 ppm or lower). The inert gas atmosphere is an atmosphere that contains an inert gas as its main component and contains a reactive gas of 10 ppm or lower.

[0060]

30 Note that the oxidizing gas is oxygen, ozone, nitrous oxide, or the like, and it is preferable that the oxidizing gas does not contain water, hydrogen, and the like. For

example, the purity of oxygen, ozone, or nitrous oxide introduced into a heat treatment apparatus is set to 6N (99.9999 %) or higher, preferably 7N (99.99999 %) or higher (i.e., the impurity concentration is 1 ppm or lower, preferably 0.1 ppm or lower). As the oxidizing gas atmosphere, an atmosphere in which an oxidizing gas is mixed with an inert gas may be used, and the oxidizing gas of at least 10 ppm is contained.

5 [0061]

By the first heat treatment, oxygen is released from the insulating layer 102, whereby the oxygen deficiency in the oxide semiconductor layer 106 and the interface state between the insulating layer 102 and the oxide semiconductor layer 106 can be reduced. By the above reduction in the interface state, the fluctuation in threshold voltage before and after a BT test can be reduced. Further, in general, it is known that the oxygen deficiency in the oxide semiconductor layer becomes donors and the source for generating electrons which are carriers. By the generation of electrons in the oxide semiconductor layer 106, the threshold voltage of the transistor 151 shifts to a negative direction, so that the transistor 151 tends to be normally on. By embedding the oxygen deficiency in the oxide semiconductor layer 106, the shift of the threshold voltage in a negative direction can be suppressed.

10 [0062]

The heat treatment can be performed in such a manner that, for example, an object to be processed is introduced into an electric furnace in which a resistance heating element or the like is used and heated at 350 °C in a nitrogen atmosphere for an hour. During the heat treatment, the oxide semiconductor layer is not exposed to the air to prevent the entry of water and hydrogen.

15 [0063]

20 Note that a heat treatment apparatus is not limited to an electric furnace, and may include a device for heating an object to be processed by heat conduction or heat radiation from a medium such as a heated gas. For example, a rapid thermal anneal (RTA) apparatus such as a gas rapid thermal anneal (GRTA) apparatus or a lamp rapid thermal anneal (LRTA) apparatus can be used. An LRTA apparatus is an apparatus for heating an object to be processed by radiation of light (electromagnetic waves) emitted from a lamp such as a halogen lamp, a metal halide lamp, a xenon arc lamp, a carbon

arc lamp, a high pressure sodium lamp, or a high pressure mercury lamp. A GRTA apparatus is an apparatus for heat treatment using a high temperature gas. As the high temperature gas, used is an inert gas which does not react with an object to be processed in heat treatment, such as nitrogen or a rare gas like argon.

5 [0064]

For example, as the first heat treatment, GRTA treatment may be performed as follows. The object to be processed is put in an inert gas atmosphere that has been heated, heated for several minutes, and then taken out of the inert gas atmosphere. GRTA treatment enables high-temperature heat treatment in a short time. Moreover, 10 GRTA treatment can be employed even when the temperature exceeds the upper temperature limit of the object. Note that the inert gas atmosphere may be switched to an atmosphere containing an oxidizing gas during the treatment. This is because by performing the first heat treatment in an atmosphere containing the oxidizing gas, oxygen deficiency in the oxide semiconductor layer 106 can be embedded and defect 15 levels in an energy gap due to oxygen deficiency can be reduced.

[0065]

The above heat treatment (first heat treatment) can be referred to as dehydration treatment, dehydrogenation treatment, or the like because of its advantageous effect of removing hydrogen, water, and the like. In addition, the above 20 heat treatment can also be referred to as treatment for supplying oxygen because of its advantageous effect of supplying oxygen from the insulating layer, a heat treatment atmosphere, or the like. The dehydration treatment, dehydrogenation treatment, or treatment for supplying oxygen can be performed at the timing, for example, after the oxide semiconductor layer is processed to have an island shape. Such dehydration 25 treatment, dehydrogenation treatment, or treatment for supplying oxygen may be performed once or plural times.

[0066]

Note that the case is described here in which after the oxide semiconductor layer 106 is processed to have an island shape, the first heat treatment is performed; 30 however, one embodiment of the present invention is not limited thereto. The oxide semiconductor layer 106 may be processed after the first heat treatment.

[0067]

Next, a conductive layer for forming the source electrode and the drain electrode (including a wiring formed in the same layer as the source electrode and the drain electrode) is formed over the insulating layer 102 and the oxide semiconductor layer 106 and processed to form the source electrode 108a and the drain electrode 108b 5 (see FIG. 3C). The channel length  $L$  of the transistor depends on the minimum distance between the edges of the source electrode 108a and the drain electrode 108b which are formed here.

[0068]

As the conductive layer used for the source electrode 108a and the drain electrode 108b, for example, a metal layer containing an element selected from Al, Cr, Cu, Ta, Ti, Mo, and W, or a metal nitride layer containing any of the above elements as its component (e.g., a titanium nitride layer, a molybdenum nitride layer, or a tungsten nitride layer) can be used. A high-melting-point metal layer of Ti, Mo, W, or the like or a metal nitride layer of any of these elements (a titanium nitride layer, a molybdenum nitride layer, or a tungsten nitride layer) may be stacked on one of or both a bottom side 15 and a top side of a low-melting point and low-resistance metal layer of Al, Cu, or the like.

[0069]

Alternatively, the conductive layer used for the source electrode 108a and the drain electrode 108b may be formed using a conductive metal oxide. As the conductive metal oxide, an indium oxide ( $In_2O_3$  or the like), a tin oxide ( $SnO_2$  or the like), a zinc oxide ( $ZnO$  or the like), an indium oxide-tin oxide alloy ( $In_2O_3-SnO_2$  or the like, which is abbreviated to ITO), an indium oxide-zinc oxide alloy ( $In_2O_3-ZnO$  or the like), or any of these metal oxide materials containing a silicon oxide can be used.

25 [0070]

The conductive layer can be processed by etching with the use of a resist mask. Ultraviolet, a KrF laser light, an ArF laser light, or the like is preferably used for light exposure for forming a resist mask for the etching.

[0071]

30 In the case where light exposure is performed so that the channel length  $L$  is less than 25 nm, the light exposure at the time of forming the resist mask is preferably performed using, for example, extreme ultraviolet having an extremely short

wavelength of several nanometers to several tens of nanometers. In the light exposure using extreme ultraviolet, the resolution is high and the focus depth is large. Thus, the channel length  $L$  of the transistor formed later can be reduced, whereby the operation speed of a circuit can be increased.

5 [0072]

Etching may be performed with the use of a resist mask formed using a so-called multi-tone mask. A resist mask formed using a multi-tone mask has a plurality of thicknesses and can be further changed in shape by ashing; thus, such a resist mask can be used in a plurality of etching steps for different patterns. Therefore, 10 a resist mask for at least two kinds of patterns can be formed using a multi-tone mask, resulting in simplification of the process.

[0073]

Note that in etching of the conductive layer, part of the oxide semiconductor layer 106 is etched, so that the oxide semiconductor layer having a groove (a recessed portion) is formed in some cases.

[0074]

After that, by plasma treatment using a gas such as oxygen, ozone, or nitrous oxide, a surface of an exposed portion of the oxide semiconductor layer 106 may be oxidized and oxygen deficiency may be embedded. In the case where plasma 20 treatment is performed, the gate insulating layer 112 which is to be in contact with part of the oxide semiconductor layer 106 is preferably formed without being exposed to the air, following the plasma treatment.

[0075]

Next, the gate insulating layer 112 is formed so as to cover the source electrode 25 108a and the drain electrode 108b and to be in contact with part of the oxide semiconductor layer 106 (see FIG. 3D).

[0076]

The gate insulating layer 112 can have a structure similar to that of the insulating layer 102. Note that a material having a high dielectric constant, such as 30 hafnium oxide or aluminum oxide, may be used for the gate insulating layer 112 considering the function of the gate insulating layer of the transistor. Alternatively, a stacked layer of silicon oxide, silicon oxynitride, or silicon nitride and a material having

a high dielectric constant, such as hafnium oxide or aluminum oxide, may be used considering a gate withstand voltage and a state of an interface of the oxide semiconductor layer. The total thickness of the gate insulating layer 112 is preferably greater than or equal to 1 nm and less than or equal to 300 nm, more preferably greater 5 than or equal to 5 nm and less than or equal to 50 nm. The larger the thickness of the gate insulating layer is, the more easily a short channel effect occurs; thus, the threshold voltage tends to shift to a negative direction. In addition, it is found that when the thickness of the gate insulating layer is less than or equal to 5 nm, leakage due to a tunnel current is increased.

10 [0077]

Second heat treatment is preferably performed after the gate insulating layer 112 is formed. The second heat treatment is performed at a temperature of higher than or equal to 250 °C and lower than or equal to 700 °C, preferably higher than or equal to 350 °C and lower than or equal to 600 °C or lower than the strain point of the substrate.

15 [0078]

The second heat treatment may be performed in an atmosphere of an oxidizing gas or an inert gas. Note that it is preferable that water, hydrogen, and the like be not contained in the atmosphere of an oxidizing gas or an inert gas. Further, the purity of the gas introduced into a heat treatment apparatus is preferably 6N (99.9999 %) or 20 higher, more preferably 7N (99.99999 %) or higher (that is, the impurity concentration is 1 ppm or lower, preferably 0.1 ppm or lower).

[0079]

The second heat treatment is performed while the oxide semiconductor layer 106 and the gate insulating layer 112 are in contact with each other. Thus, oxygen 25 which is one of main components of the oxide semiconductor can be supplied from the gate insulating layer 112 containing oxygen to the oxide semiconductor layer 106. Accordingly, oxygen deficiency in the oxide semiconductor layer 106 and the interface state between the oxide semiconductor layer and the gate insulating layer 112 can be reduced. At the same time, defects in the gate insulating layer 112 can also be 30 reduced.

[0080]

Note that there is no particular limitation on the timing of the second heat treatment as long as it is after the gate insulating layer 112 is formed. For example, the second heat treatment may be performed after the gate electrode 114 is formed.

[0081]

5 Then, the gate electrode 114 is formed (see FIG. 3E). The gate electrode 114 can be formed using a metal material such as molybdenum, titanium, tantalum, tungsten, aluminum, copper, neodymium, or scandium, nitride of any of these metal materials, or an alloy material which contains any of these metal materials as its main component. Note that the gate electrode 114 may have a single-layer structure or a stacked-layer

10 structure.

[0082]

Through the above process, the transistor 151 is formed.

[0083]

15 Next, an example of a manufacturing process of the transistor 152 in FIG. 2A will be described with reference to FIGS. 4A to 4E.

[0084]

First, the insulating layer 102 is formed over the substrate 100 (see FIG. 4A). As the insulating layer 102 of the transistor 151, the insulating layer 102 is an insulating layer from which oxygen is released by heating.

20 [0085]

Next, a conductive layer for forming the source electrode and the drain electrode (including a wiring formed in the same layer as the source electrode and the drain electrode) is formed over the insulating layer 102 and processed to form the source electrode 108a and the drain electrode 108b (see FIG. 4B).

25 [0086]

Next, an oxide semiconductor layer is formed over the insulating layer 102 so as to be connected to the source electrode 108a and the drain electrode 108b and then is processed to form the oxide semiconductor layer 106 having an island shape (see FIG. 4C). After that, first heat treatment similar to that performed on the transistor 151 may 30 be performed.

[0087]

Next, the gate insulating layer 112 is formed so as to be in contact with the

oxide semiconductor layer 106 and part of the source electrode 108a and the drain electrode 108b and cover the source electrode 108a, the drain electrode 108b, and the oxide semiconductor layer 106 (see FIG. 4D). After that, second heat treatment similar to that performed on the transistor 151 may be performed.

5 [0088]

Then, the gate electrode 114 is formed (see FIG. 4E).

[0089]

Through the above-described process, the transistor 152 is formed.

[0090]

10 When charge is trapped at the interface of the oxide semiconductor layer, the threshold voltage of the transistor shifts. For example, when positive charge is trapped on the back channel side, the threshold voltage of the transistor shifts in a negative direction. As one of factors of such charge trapping, the model where cations (or atoms which are sources of the cations) travel and are trapped can be supposed. In one 15 embodiment of the present invention, the interface states between the oxide semiconductor layer and the insulating layer 102 and between the oxide semiconductor layer and the gate insulating layer 112 are reduced by the insulating layer from which oxygen is released by heating, so that it is possible to reduce charge trapping which may be caused in the above model; therefore, the shift of the threshold voltage of the 20 transistor can be suppressed.

[0091]

An example of a manufacturing process of the transistor 153 in FIG. 2B will be described with reference to FIGS. 5A to 5E.

[0092]

25 First, the insulating layer 102 is formed over the substrate 100 (see FIG. 5A). The insulating layer 102 is an insulating layer from which oxygen is released by heating.

[0093]

30 Next, an oxide semiconductor layer is formed over the insulating layer 102 and processed to form the oxide semiconductor layer 106 having an island shape (see FIG. 5B). After that, first heat treatment similar to that performed on the transistor 151 may be performed.

[0094]

Next, the gate insulating layer 112 and the gate electrode 114 are formed and processed to have similar patterns by photolithography (see FIG. 5C). At this time, the gate electrode 114 may be processed and then the gate insulating layer 112 may be 5 processed using the gate electrode 114 as a mask. After that, second heat treatment similar to that performed on the transistor 151 may be performed.

[0095]

Next, the resistance of the oxide semiconductor layer 106 is reduced using the 10 gate electrode 114 as a mask, so that the source region 122a and the drain region 122b are formed. A region under the gate electrode where the resistance is not reduced becomes the channel region 126 (see FIG. 5D). As a method for reducing the resistance, argon plasma treatment, hydrogen plasma treatment, ammonia plasma treatment, and the like can be given. At this time, the channel length  $L$  of the transistor 15 is determined by the width of the gate electrode. By patterning using the gate electrode as the mask in this manner, the source region and the drain region do not overlap with the gate electrode and parasitic capacitance is not generated; therefore, the operation speed of the transistor can be increased.

[0096]

Next, the protective insulating layer 124 is formed and an opening is provided 20 in a region of the protective insulating layer 124, which is overlapped with the source region 122a and the drain region 122b. A conductive layer for forming the source electrode and the drain electrode (including a wiring formed in the same layer as the source and drain electrodes) is formed and processed to form the source electrode 108a and the drain electrode 108b (see FIG. 5E).

25 [0097]

Through the above process, the transistor 153 is formed.

[0098]

Thus, a semiconductor device including an oxide semiconductor and having 30 stable electrical characteristics can be provided. Therefore, a semiconductor device with high reliability can be provided.

[0099]

The structures, the methods, and the like described in this embodiment can be

combined as appropriate with any of the structures, the methods, and the like described in the other embodiments.

[0100]

(Embodiment 2)

5 A semiconductor device (also referred to as a display device) having a display function can be manufactured using the transistor an example of which is described in Embodiment 1. Some or all driver circuits including the transistors can be formed over a substrate where a pixel portion is formed, whereby a system-on-panel can be obtained.

10 [0101]

In FIG. 6A, a sealant 205 is provided to surround a pixel portion 202 provided over a first substrate 201, and the pixel portion 202 is sealed with the sealant 205 and a second substrate 206. In FIG. 6A, a scan line driver circuit 204 and a signal line driver circuit 203 each are formed using a single crystal semiconductor layer or a polycrystalline semiconductor layer over a substrate prepared separately, and mounted in a region different from the region surrounded by the sealant 205 over the first substrate 201. Various signals and potentials are supplied to the signal line driver circuit 203 and the scan line driver circuit 204 each of which is separately formed, and the pixel portion 202, from flexible printed circuits (FPCs) 218a and 218b.

15 [0102]

In FIGS. 6B and 6C, the sealant 205 is provided to surround the pixel portion 202 and the scan line driver circuit 204 which are provided over the first substrate 201. The second substrate 206 is provided over the pixel portion 202 and the scan line driver circuit 204. Thus, the pixel portion 202 and the scan line driver circuit 204 are sealed together with a display element, by the first substrate 201, the sealant 205, and the second substrate 206. In FIGS. 6B and 6C, the signal line driver circuit 203 is formed using a single crystal semiconductor layer or a polycrystalline semiconductor layer over a substrate prepared separately, and mounted in a region different from the region surrounded by the sealant 205 over the first substrate 201. In FIGS. 6B and 6C, various signals and potentials are supplied to the signal line driver circuit 203 which is separately formed, the scan line driver circuit 204, and the pixel portion 202, from an FPC 218.

[0103]

Although FIGS. 6B and 6C each show the example in which the signal line driver circuit 203 is formed separately and mounted on the first substrate 201, the present invention is not limited to this structure. The scan line driver circuit may be 5 separately formed and then mounted, or only part of the signal line driver circuit or part of the scan line driver circuit may be separately formed and then mounted.

[0104]

Note that a method for connecting a separately formed driver circuit is not particularly limited, and a chip on glass (COG) method, a wire bonding method, a tape 10 automated bonding (TAB) method, or the like can be used. FIG. 6A shows an example in which the signal line driver circuit 203 and the scan line driver circuit 204 are mounted by a COG method. FIG. 6B shows an example in which the signal line driver circuit 203 is mounted by a COG method. FIG. 6C shows an example in which the signal line driver circuit 203 is mounted by a TAB method.

15 [0105]

The display device includes in its category a panel in which a display element is sealed, and a module in which an IC such as a controller is mounted on the panel.

[0106]

Note that a display device in this specification means an image display device, 20 a display device, or a light source (including a lighting device). The display device also includes the following modules in its category: a module to which a connector such as an FPC, a TAB tape, or a TCP is attached; a module having a TAB tape or a TCP at the tip of which a printed wiring board is provided; and a module in which an IC is directly mounted on a display element by a COG method.

25 [0107]

The pixel portion and the scan line driver circuit provided over the first substrate include a plurality of transistors and any of the transistors, the examples of which are described in Embodiment 1, can be applied.

[0108]

30 As the display element provided in the display device, a liquid crystal element (also referred to as a liquid crystal display element) or a light-emitting element (also referred to as a light-emitting display element) can be used. The light-emitting

element includes, in its category, an element whose luminance is controlled by a current or voltage, and specifically includes, in its category, an inorganic electroluminescent (EL) element, an organic EL element, and the like. Furthermore, a display medium whose contrast is changed by an electric effect, such as electronic ink, can be used.

5 [0109]

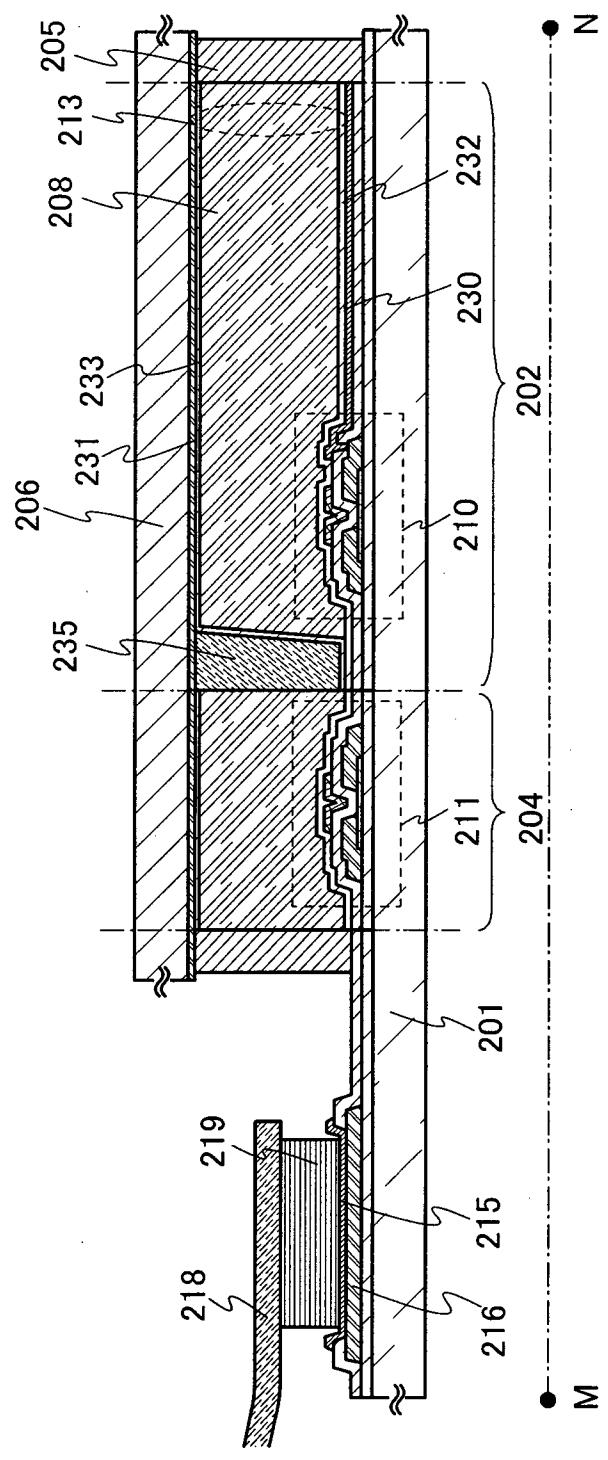

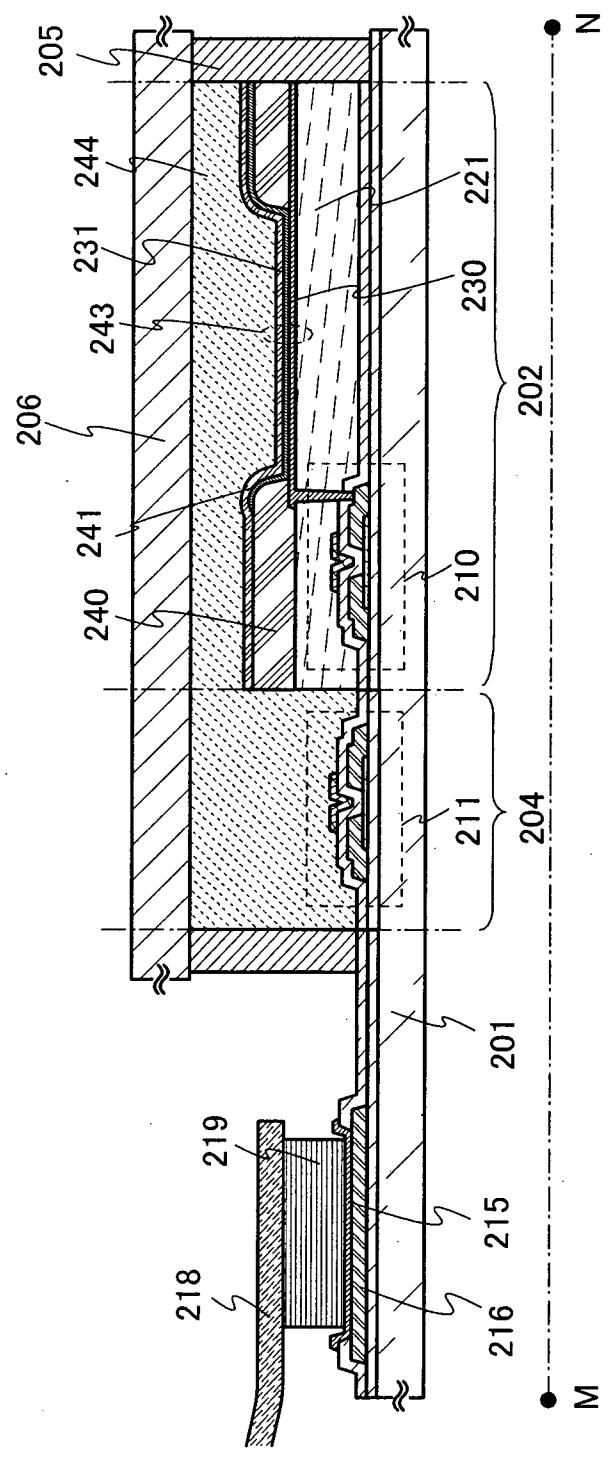

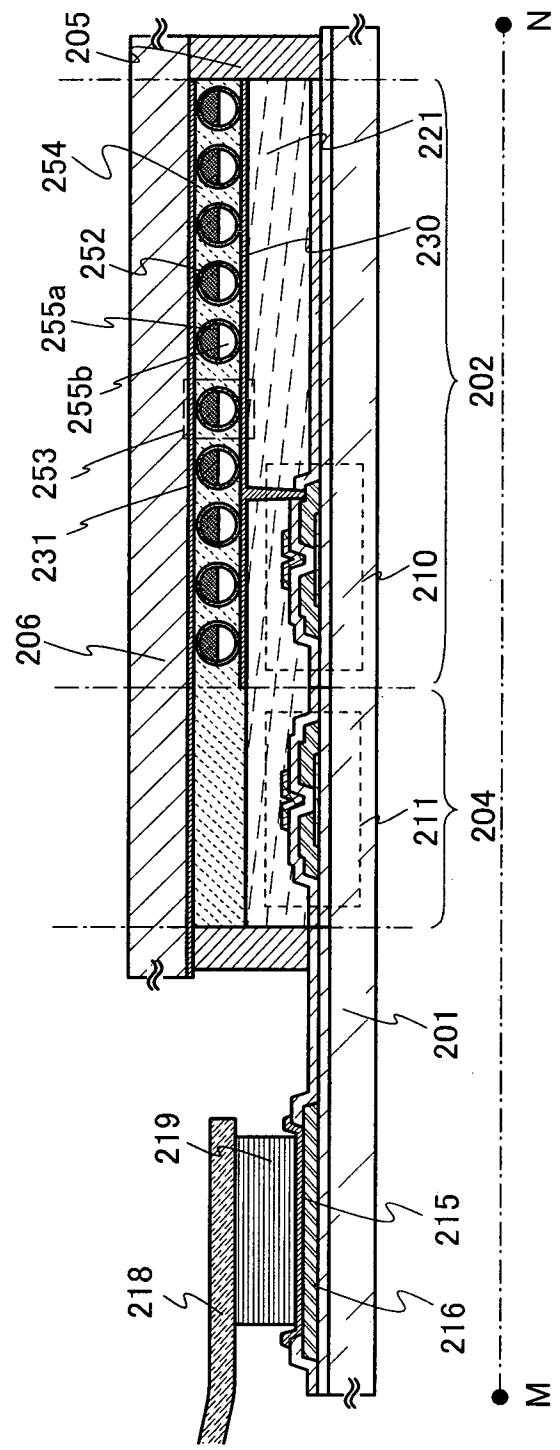

One embodiment of the semiconductor device is described with reference to FIG. 7, FIG. 8, and FIG. 9. FIG. 7, FIG. 8, and FIG. 9 correspond to cross-sectional views taken along line M-N in FIG. 6B.

[0110]

10 As illustrated in FIG. 7, FIG. 8, and FIG. 9, the semiconductor device includes a connection terminal electrode 215 and a terminal electrode 216. The connection terminal electrode 215 and the terminal electrode 216 are electrically connected to a terminal included in the FPC 218 through an anisotropic conductive layer 219.

[0111]

15 The connection terminal electrode 215 is formed of the same conductive layer as a first electrode layer 230. The terminal electrode 216 is formed of the same conductive layer as a source electrode and a drain electrode of transistors 210 and 211.

[0112]

20 Each of the pixel portion 202 and the scan line driver circuit 204 provided over the first substrate 201 includes a plurality of transistors. In FIG. 7, FIG. 8, and FIG. 9, the transistor 210 included in the pixel portion 202 and the transistor 211 included in the scan line driver circuit 204 are shown as an example.

[0113]

25 In this embodiment, any of the transistors described in Embodiment 1 can be applied to the transistors 210 and 211. Fluctuation in the electrical characteristics of the transistors 210 and 211 is suppressed and the transistors 210 and 211 are electrically stable. As described above, a semiconductor device with high reliability as the semiconductor devices in this embodiment in FIG. 7, FIG. 8, and FIG. 9 can be obtained.

[0114]

30 The transistor 210 provided in the pixel portion 202 is electrically connected to the display element to form a display panel. A variety of display elements can be used as the display element as long as display can be performed.

## [0115]

An example of a liquid crystal display device using a liquid crystal element as a display element is illustrated in FIG. 7. In FIG. 7, a liquid crystal element 213 is a display element including the first electrode layer 230, a second electrode layer 231, and 5 a liquid crystal layer 208. Note that insulating layers 232 and 233 serving as alignment layers are provided so that the liquid crystal layer 208 is interposed therebetween. The second electrode layer 231 is formed on the second substrate 206 side. The first electrode layer 230 and the second electrode layer 231 are stacked with the liquid crystal layer 208 interposed therebetween.

## 10 [0116]

A spacer 235 is a columnar spacer obtained by selective etching of an insulating layer and is provided in order to control the thickness (a cell gap) of the liquid crystal layer 208. Alternatively, a spherical spacer may be used.

## [0117]

15 In the case where a liquid crystal element is used as the display element, a thermotropic liquid crystal, a low-molecular liquid crystal, a high-molecular liquid crystal, a polymer dispersed liquid crystal, a ferroelectric liquid crystal, an anti-ferroelectric liquid crystal, or the like can be used. Such a liquid crystal material exhibits a cholesteric phase, a smectic phase, a cubic phase, a chiral nematic phase, an 20 isotropic phase, or the like depending on conditions.

## [0118]

25 Alternatively, a liquid crystal exhibiting a blue phase for which an alignment layer is unnecessary may be used. A blue phase is one of liquid crystal phases generated just before a cholesteric phase changes into an isotropic phase while the temperature of cholesteric liquid crystal is increased. Since the blue phase appears only in a narrow temperature range, a liquid crystal composition in which a chiral material is mixed is used for the liquid crystal layer in order to improve the temperature range. The liquid crystal composition which includes a liquid crystal exhibiting a blue 30 phase and a chiral agent has a short response time of 1 msec or less, has optical isotropy, which makes the alignment process unneeded, and has a small viewing angle dependence. In addition, since an alignment layer does not need to be provided and rubbing treatment is unnecessary, electrostatic discharge damage caused by the rubbing

treatment can be prevented and defects and damage of the liquid crystal display device can be reduced in the manufacturing process. Thus, productivity of the liquid crystal display device can be increased.

[0119]

5 The specific resistivity of the liquid crystal material is  $1 \times 10^9 \Omega\text{-cm}$  or more, preferably  $1 \times 10^{11} \Omega\text{-cm}$  or more, more preferably  $1 \times 10^{12} \Omega\text{-cm}$  or more. Note that the specific resistivity in this specification is measured at 20 °C.

[0120]

10 The size of a storage capacitor provided in the liquid crystal display device is set considering the leakage current of the transistor provided in the pixel portion or the like so that charge can be held for a predetermined period. Since the transistor including a high-purity oxide semiconductor layer is used, a storage capacitor having capacitance which is 1/3 or less, preferably 1/5 or less with respect to a liquid crystal capacitance of each pixel is sufficient to be provided.

15 [0121]

In the transistor used in this embodiment, which uses a highly-purified oxide semiconductor layer, the off-state current can be made small. Therefore, an electrical signal such as an image signal can be held for a long period, and a writing interval can be set long when the power is on. Consequently, frequency of refresh operation can be 20 reduced, which leads to an effect of suppressing power consumption.

[0122]

25 The field-effect mobility of the transistor including a highly-purified oxide semiconductor layer used in this embodiment can be high, whereby high-speed operation is possible. Thus, by using the transistor in a pixel portion of the liquid crystal display device, a high-quality image can be provided. In addition, since the transistors can be separately provided in a driver circuit portion and a pixel portion over one substrate, the number of components of the liquid crystal display device can be reduced.

[0123]

30 For the liquid crystal display device, a twisted nematic (TN) mode, an in-plane-switching (IPS) mode, a fringe field switching (FFS) mode, an axially

symmetric aligned micro-cell (ASM) mode, an optical compensated birefringence (OCB) mode, a ferroelectric liquid crystal (FLC) mode, an antiferroelectric liquid crystal (AFLC) mode, or the like can be used.

[0124]

5       A normally black liquid crystal display device such as a transmissive liquid crystal display device utilizing a vertical alignment (VA) mode is preferable. The vertical alignment mode is one of methods of controlling alignment of liquid crystal molecules of a liquid crystal display panel. The vertical alignment mode is a mode in which liquid crystal molecules are aligned vertically to a panel surface when voltage is

10      not applied. Some examples are given as the vertical alignment mode. For example, a multi-domain vertical alignment (MVA) mode, a patterned vertical alignment (PVA) mode, an ASV mode, and the like can be given. Moreover, it is possible to use a method called domain multiplication or multi-domain design, in which a pixel is divided into some regions (subpixels) and molecules are aligned in different directions

15      in their respective regions.

[0125]

20       In the display device, a black matrix (a light-blocking layer), an optical member (an optical substrate) such as a polarizing member, a retardation member, or an anti-reflection member, and the like are provided as appropriate. For example, circular polarization may be employed by using a polarizing substrate and a retardation substrate. In addition, a backlight, a side light, or the like may be used as a light source.

[0126]

25       In addition, with the use of a plurality of light-emitting diodes (LEDs) as a backlight, a time-division display method (a field-sequential driving method) can be employed. With the field-sequential driving method, color display can be performed without using a color filter.

[0127]

30       As a display method in the pixel portion, a progressive method, an interlace method, or the like can be employed. Color elements controlled in a pixel at the time of color display are not limited to three colors: R, G, and B (R, G, and B correspond to red, green, and blue respectively). For example, R, G, B, and W (W corresponds to white), or R, G, B, and one or more of yellow, cyan, magenta, and the like can be used.

The sizes of display regions may be different between respective dots of color elements.

Note that the present invention is not limited to the application to a display device for color display but can also be applied to a display device for monochrome display.

[0128]

5        Alternatively, as the display element included in the display device, a light-emitting element utilizing an EL element can be used.

[0129]

10      In an organic EL element, by application of voltage to a light-emitting element, electrons and holes are separately injected from a pair of electrodes into a layer containing a light-emitting organic compound, and current flows. The carriers (electrons and holes) are recombined, and thus the light-emitting organic compound is excited. The light-emitting organic compound returns to a ground state from the excited state, thereby emitting light. Owing to such a mechanism, such a light-emitting element is referred to as a current-excitation light-emitting element.

15 [0130]

20      The inorganic EL elements are classified according to their element structures into a dispersion-type inorganic EL element and a thin-film inorganic EL element. A dispersion-type inorganic EL element has a light-emitting layer where particles of a light-emitting material are dispersed in a binder, and its light emission mechanism is donor-acceptor recombination type light emission that utilizes a donor level and an acceptor level. A thin-film inorganic EL element has a structure where a light-emitting layer is sandwiched between dielectric layers, which are further sandwiched between electrodes, and its light emission mechanism is localized type light emission that utilizes inner-shell electron transition of metal ions. Note that an example of an organic EL 25 element as a light-emitting element is described here.

[0131]

30      In order to extract light emitted from the light-emitting element, it is acceptable as long as at least one of a pair of electrodes is transparent. Then a transistor and a light-emitting element are formed over a substrate. The light-emitting element can have any of the following structure: a top emission structure in which light is extracted through the surface opposite to the substrate; a bottom emission structure in which light is extracted through the surface on the substrate side; or a dual emission structure in

which light is extracted through the surface opposite to the substrate and the surface on the substrate side.

[0132]

An example of a light-emitting device using a light-emitting element as a display element is illustrated in FIG. 8. A light-emitting element 243 which is a display element is electrically connected to the transistor 210 provided in the pixel portion 202. The structure of the light-emitting element 243 is not limited to the stacked-layer structure including the first electrode layer 230, an electroluminescent layer 241, and the second electrode layer 231, which is illustrated in FIG. 8. The structure of the light-emitting element 243 can be changed as appropriate depending on a direction in which light is extracted from the light-emitting element 243, or the like.

[0133]

A partition wall 240 can be formed using an organic insulating material or an inorganic insulating material. It is particularly preferable that the partition wall 240 be formed using a photosensitive resin material to have an opening portion over the first electrode layer 230 so that a sidewall of the opening portion is formed as a tilted surface with continuous curvature.

[0134]

The electroluminescent layer 241 may be formed with either a single layer or a stacked layer of a plurality of layers.

[0135]

A protective layer may be formed over the second electrode layer 231 and the partition wall 240 in order to prevent entry of oxygen, hydrogen, moisture, carbon dioxide, or the like into the light-emitting element 243. As the protective layer, a silicon nitride layer, a silicon nitride oxide layer, a diamond-like carbon (DLC) layer, an aluminum oxide layer, an aluminum nitride layer, or the like can be formed. In a space sealed with the first substrate 201, the second substrate 206, and the sealant 205, a filler 244 is provided and tightly sealed. It is preferable that the light-emitting element be packaged (sealed) with a protective film (such as a laminate film or an ultraviolet curable resin film) or a cover material with high air-tightness and little degasification so that the light-emitting element is not exposed to the outside air, in this manner.

[0136]

As the filler 244, an ultraviolet curable resin or a thermosetting resin can be used as well as an inert gas such as nitrogen or argon, and polyvinyl chloride (PVC), acrylic, polyimide, an epoxy resin, a silicone resin, polyvinyl butyral (PVB), ethylene vinyl acetate (EVA), or the like can be used. For example, nitrogen may be used for

5 the filler.

[0137]

If needed, an optical film, such as a polarizing plate, a circularly polarizing plate (including an elliptically polarizing plate), a retardation plate (a quarter-wave plate or a half-wave plate), or a color filter, may be provided as appropriate on a

10 light-emitting surface of the light-emitting element. Further, the polarizing plate or the circularly polarizing plate may be provided with an anti-reflection layer. For example, anti-glare treatment by which reflected light can be diffused by projections and depressions on the surface so as to reduce the glare can be performed.

[0138]

15 An electronic paper in which electronic ink is driven can be provided as the display device. The electronic paper is also called an electrophoretic display device (electrophoretic display) and has advantages in that it has the same level of readability as regular paper, it has less power consumption than other display devices, and it can be set to have a thin and light form.

20 [0139]

An electrophoretic display device can have various modes. An

25 electrophoretic display device contains a plurality of microcapsules dispersed in a solvent or a solute, each microcapsule containing first particles which are positively charged and second particles which are negatively charged. By applying an electric field to the microcapsules, the particles in the microcapsules move in opposite directions to each other and only the color of the particles gathering on one side is displayed. Note that the first particles and the second particles each contain pigment and do not move without an electric field. Moreover, the first particles and the second particles have different colors (which may be colorless).

30 [0140]

Thus, an electrophoretic display device is a display that utilizes a so-called dielectrophoretic effect by which a substance having a high dielectric constant moves to

a high-electric field region.

[0141]

A solution in which the above microcapsules are dispersed in a solvent is referred to as electronic ink. This electronic ink can be printed on a surface of glass, 5 plastic, cloth, paper, or the like. Furthermore, by using a color filter or particles that have a pigment, color display can also be achieved.

[0142]

Note that the first particles and the second particles in the microcapsules may each be formed of a single material selected from a conductive material, an insulating 10 material, a semiconductor material, a magnetic material, a liquid crystal material, a ferroelectric material, an electroluminescent material, an electrochromic material, and a magnetophoretic material, or formed of a composite material of any of these.

[0143]

As the electronic paper, a display device using a twisting ball display method 15 can be used. The twisting ball display method refers to a method in which spherical particles each colored in white and black are arranged between a first electrode layer and a second electrode layer which are electrode layers used for a display element, and a potential difference is generated between the first electrode layer and the second electrode layer to control orientation of the spherical particles, so that display is 20 performed.

[0144]

FIG. 9 shows an active matrix electronic paper as one embodiment of a semiconductor device. The electronic paper in FIG. 9 is an example of a display device using a twisting ball display method.

25 [0145]

Between the first electrode layer 230 connected to the transistor 210 and the second electrode layer 231 provided on the second substrate 206, spherical particles 253 each of which includes a black region 255a, a white region 255b, and a cavity 252 around the regions which is filled with liquid, are provided. A space around the 30 spherical particles 253 is filled with a filler 254 such as a resin. The second electrode layer 231 corresponds to a common electrode (counter electrode). The second electrode layer 231 is electrically connected to a common potential line.

[0146]

Note that in FIG. 7, FIG. 8, and FIG. 9, a flexible substrate as well as a glass substrate can be used as the first substrate 201 and the second substrate 206. For example, a plastic substrate having light-transmitting properties can be used. For 5 plastic, a fiberglass-reinforced plastics (FRP) plate, a polyvinyl fluoride (PVF) film, a polyester film, or an acrylic resin film can be used. A sheet with a structure in which an aluminum foil is sandwiched between PVF films or polyester films can also be used.

[0147]

An insulating layer 221 can be formed using an organic insulating material or 10 an inorganic insulating material. Note that an organic insulating material having heat resistance, such as an acrylic resin, a polyimide, a benzocyclobutene-based resin, a polyamide, or an epoxy resin is preferably used as a planarizing insulating layer. Other than such organic insulating materials, it is possible to use a low-dielectric 15 constant material (a low-k material), a siloxane-based resin, phosphosilicate glass (PSG), borophosphosilicate glass (BPSG), or the like. The insulating layer 221 may be formed by stacking a plurality of insulating layers formed of these materials.

[0148]

There is no particular limitation on the method for forming the insulating layer 221, and the insulating layer 221 can be formed, depending on a material thereof, by a 20 sputtering method, a spin coating method, a dipping method, a spray coating method, a droplet discharging method (e.g., an ink jet method, a screen printing method, or an offset printing method), a roll coating method, a curtain coating method, a knife coating method, or the like.

[0149]

25 The display device performs display by transmitting light from a light source or a display element. Thus, the substrates and the thin films such as insulating layers and conductive layers provided in the pixel portion where light is transmitted have light-transmitting properties with respect to light in the visible-light wavelength range.

[0150]

30 The first electrode layer 230 and the second electrode layer 231 (each of which may be called a pixel electrode layer, a common electrode layer, a counter electrode layer, or the like) for applying voltage to the display element may have

light-transmitting properties or light-reflecting properties, which depends on the direction in which light is extracted, the position where the electrode layer is provided, and the pattern structure of the electrode layer.

[0151]

5       A light-transmitting conductive material such as indium oxide containing tungsten oxide, indium zinc oxide containing tungsten oxide, indium oxide containing titanium oxide, indium tin oxide containing titanium oxide, indium tin oxide (hereinafter referred to as ITO), indium zinc oxide, or indium tin oxide to which silicon oxide is added, can be used for the first electrode layer 230 and the second electrode

10      layer 231.

[0152]

The first electrode layer 230 and the second electrode layer 231 can be formed using one kind or plural kinds selected from metal such as tungsten (W), molybdenum (Mo), zirconium (Zr), hafnium (Hf), vanadium (V), niobium (Nb), tantalum (Ta),

15      chromium (Cr), cobalt (Co), nickel (Ni), titanium (Ti), platinum (Pt), aluminum (Al), copper (Cu), or silver (Ag); an alloy thereof; and a nitride thereof.

[0153]

A conductive composition containing a conductive high molecule (also referred to as a conductive polymer) can be used for the first electrode layer 230 and the second