(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2004-538648

(P2004-538648A)

(43) 公表日 平成16年12月24日(2004.12.24)

(51) Int.Cl.<sup>7</sup>

H01L 29/78

H01L 21/336

F 1

H01L 29/78 653A

H01L 29/78 652K

H01L 29/78 658F

テーマコード(参考)

審査請求 未請求 予備審査請求 未請求 (全 40 頁)

|               |                                                                                                        |          |                                                                                                             |

|---------------|--------------------------------------------------------------------------------------------------------|----------|-------------------------------------------------------------------------------------------------------------|

| (21) 出願番号     | 特願2003-520004 (P2003-520004)                                                                           | (71) 出願人 | 591077450<br>シリコニックス・インコーポレイテッド<br>SILICONIX INCORPORATED<br>アメリカ合衆国カリフォルニア州95054・サンタクララ・ローレルウッドロード<br>2201 |

| (86) (22) 出願日 | 平成14年7月19日 (2002.7.19)                                                                                 | (74) 代理人 | 100104499<br>弁理士 岸本 達人                                                                                      |

| (85) 翻訳文提出日   | 平成16年2月5日 (2004.2.5)                                                                                   | (74) 代理人 | 100101203<br>弁理士 山下 昭彦                                                                                      |

| (86) 國際出願番号   | PCT/US2002/022937                                                                                      | (74) 代理人 | 100108800<br>弁理士 星野 哲郎                                                                                      |

| (87) 國際公開番号   | W02003/015179                                                                                          |          |                                                                                                             |

| (87) 國際公開日    | 平成15年2月20日 (2003.2.20)                                                                                 |          |                                                                                                             |

| (31) 優先権主張番号  | 09/927,320                                                                                             |          |                                                                                                             |

| (32) 優先日      | 平成13年8月10日 (2001.8.10)                                                                                 |          |                                                                                                             |

| (33) 優先権主張國   | 米国(US)                                                                                                 |          |                                                                                                             |

| (81) 指定国      | EP(AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE, SK, TR), JP, KR |          |                                                                                                             |

最終頁に続く

(54) 【発明の名称】トレンチゲート電極を有するMISデバイス及びその製造方法

## (57) 【要約】

厚い絶縁層をトレンチの底部に備えたトレンチMISデバイスおよびその製造方法を開示している。トレンチMOSFETの典型的な実施形態においては、厚い酸化膜をトレンチの底部に備え、前記トレンチの底部に沿って基板中の応力は殆ど変化しない。前記厚い絶縁層によって、トレンチゲートとドレイン領域はトレンチの底部において隔てられ、その結果、ゲート-ドレイン間キャパシタンスが小さくなる。これにより、MOSFETは、高周波の用途に適するようになる。製造方法の典型的な実施形態においては、厚い絶縁層がトレンチの底部上に堆積される。薄いゲート誘電体が露出された側壁上に形成され、前記厚い絶縁層に接続される。トレンチの残留部にはゲートが形成される。該製造工程は、本体およびソースの埋め込み、表面安定化処理、金属化を経て終了する。

**【特許請求の範囲】****【請求項 1】**

トレンチが表面から内部に向かって延在する半導体基板と、前記トレンチの側壁と前記表面とに隣接した第1の導電型のソース領域と、前記ソース領域と前記側壁とに隣接した前記第1の導電型と電荷が反対の第2の導電型の本体領域と、前記本体領域と前記側壁とに隣接した前記第1の導電型のドレイン領域とを備え、前記トレンチの底部に沿って前記基板中の応力が殆ど変化せず、前記本体領域と隣接する前記トレンチの側壁の一部に沿って第1の絶縁層が設けられ、前記トレンチの底部に沿って第2の絶縁層が設けられ、該第2の絶縁層は、前記第1の絶縁層に接続され、前記第1の絶縁層よりも厚いことを特徴とする金属-絶縁体-半導体(MIS)デバイス。

10

**【請求項 2】**

前記トレンチ内部において、前記第1の絶縁層と前記第2の絶縁層とに接続されたゲート領域を更に備えることを特徴とする請求項1に記載のMISデバイス。

**【請求項 3】**

前記ゲート領域がポリシリコンを含むことを特徴とする請求項2に記載のMISデバイス。

**【請求項 4】**

前記トレンチの少なくとも前記底部に隣接する前記ドレイン領域に形成された前記第1の導電型の高導電領域を更に有することを特徴とする請求項1に記載のMISデバイス。

20

**【請求項 5】**

前記第1の絶縁層が酸化物を含むことを特徴とする請求項1に記載のMISデバイス。

**【請求項 6】**

前記第2の絶縁層が酸化物を含むことを特徴とする請求項1に記載のMISデバイス。

**【請求項 7】**

前記第2の絶縁層が多層絶縁層を構成していることを特徴とする請求項1に記載のMISデバイス。

**【請求項 8】**

前記MISデバイスがMOSFETを含むことを特徴とする請求項1に記載のMISデバイス。

30

**【請求項 9】**

トレンチが表面から内部に向かって延在する半導体基板と、前記トレンチの側壁と前記表面とに隣接した第1の導電型のソース領域と、前記ソース領域と前記側壁とに隣接した前記第1の導電型と電荷が反対の第2の導電型の本体領域と、前記本体領域と前記側壁とに隣接した前記第1の導電型のドレイン領域と、前記トレンチ内部において前記第1の絶縁層と前記第2の絶縁層とに接続されたゲート領域とを備え、前記トレンチの底部に沿って前記基板中の応力が殆ど変化せず、前記本体領域と隣接する前記トレンチの側壁の一部に沿って第1の絶縁層が設けられ、前記トレンチの底部に沿って第2の絶縁層が設けられ、該第2の絶縁層は、前記第1の絶縁層に接続され、前記第1の絶縁層よりも厚いことを特徴とするトレンチゲートMOSFET。

40

**【請求項 10】**

前記ゲート領域がポリシリコンを含むことを特徴とする請求項9に記載のトレンチゲートMOSFET。

**【請求項 11】**

前記トレンチの少なくとも前記底部に隣接する前記ドレイン領域に形成された前記第1の導電型の高導電領域を更に有することを特徴とする請求項9に記載のトレンチゲートMOSFET。

**【請求項 12】**

前記第1の絶縁層が酸化物を含むことを特徴とする請求項9に記載のトレンチゲートMOSFET。

**【請求項 13】**

50

前記第2の絶縁層が酸化物を含むことを特徴とする請求項9に記載のトレンチゲートMOSFET。

【請求項14】

前記第2の絶縁層が多層絶縁層を構成していることを特徴とする請求項9に記載のトレンチゲートMOSFET。

【請求項15】

トレンチが表面から内部に向かって延在する半導体基板と、前記トレンチの側壁と前記表面とに隣接した第1の導電型のソース領域と、前記ソース領域と前記側壁とに隣接した前記第1の導電型と電荷が反対の第2の導電型の本体領域と、前記本体領域と前記側壁とに隣接した前記第1の導電型のドレイン領域と、前記本体領域と隣接する前記トレンチの側壁の一部に沿って設けられた第1の絶縁層と、前記トレンチの底部に沿って前記第1の絶縁層よりも厚く設けられ、前記第1の絶縁層に接続された第2の絶縁層と、前記トレンチ内部において前記第1の絶縁層と前記第2の絶縁層とに接続されたゲート領域を備え、前記第1の絶縁層と前記第2の絶縁層との接続部に存在する移行絶縁層の厚さが、前記第1の絶縁層の厚さ以上であることを特徴とするトレンチゲートMOSFET。10

【請求項16】

前記トレンチの少なくとも前記底部に隣接する前記ドレイン領域に形成された前記第1の導電型の高導電領域を更に有することを特徴とする請求項15に記載のトレンチゲートMOSFET。20

【請求項17】

トレンチが表面から内部に向かって延在する半導体基板と、前記トレンチの側壁と前記表面とに隣接した第1の導電型のソース領域と、前記ソース領域と前記側壁とに隣接した前記第1の導電型と電荷が反対の第2の導電型の本体領域と、前記本体領域と前記側壁とに隣接した前記第1の導電型のドレイン領域と、前記本体領域と隣接する前記トレンチの側壁の一部に沿って設けられた第1の絶縁層と、前記トレンチの底部に沿って前記第1の絶縁層よりも厚く設けられ、前記第1の絶縁層に接続された第2の絶縁層と、前記トレンチ内部において前記第1の絶縁層と前記第2の絶縁層とに接続されたゲート領域を備え、前記第2の絶縁層の垂直方向の中心点でとった前記トレンチの第1の直径が、前記本体領域との隣接部でとった前記トレンチの第2の直径以下であることを特徴とするトレンチゲートMOSFET。30

【請求項18】

前記トレンチの少なくとも前記底部に隣接する前記ドレイン領域に形成された前記第1の導電型の高導電領域を更に有することを特徴とする請求項17に記載のトレンチゲートMOSFET。40

【請求項19】

半導体基板を準備する工程と、側壁と底部とを有するトレンチを前記基板中に形成する工程と、前記側壁上および底部上に厚い絶縁層を堆積させる工程と、マスク層を前記トレンチ内に堆積させる工程と、前記マスク層をエッチングすることにより、前記側壁上の厚い絶縁層の一部を露出させるとともに、前記トレンチの底部に前記マスク層の一部を残す工程と、前記厚い絶縁層をエッチングすることにより、前記側壁の露出部を形成するとともに、前記トレンチの底部に前記厚い絶縁層の一部を残す工程と、前記側壁の前記露出部上に薄い絶縁層を形成する工程、前記厚い絶縁層の一部の上側に、前記トレンチ内の前記薄い絶縁層に隣接してゲートを形成する工程とを有するMISデバイスの製造方法。

【請求項20】

前記薄い絶縁層を形成する工程は、前記側壁を熱酸化する工程を含むことを特徴とする請求項19に記載の方法。

【請求項21】

前記薄い絶縁層を形成する工程の前に、前記側壁上に薄い犠牲酸化膜を成長させる工程と、前記薄い絶縁層を形成する工程の前に、前記犠牲酸化膜を除去する工程とを更に含むことを特徴とする請求項20に記載の方法。50

**【請求項 2 2】**

前記ゲートを形成する工程は、ドープしたポリシリコンを前記トレンチ内に堆積させる工程と、前記ドープしたポリシリコンを前記基板の表面とほぼ等しい高さまでエッティングする工程とを含むことを特徴とする請求項 1 9 に記載の方法。

**【請求項 2 3】**

前記厚い絶縁層を堆積させる工程の前に、前記側壁上および底部上に薄い絶縁層を成長させる工程を更に含むことを特徴とする請求項 1 9 に記載の方法。

**【請求項 2 4】**

前記基板中に前記側壁に隣接して本体領域を形成する工程と、前記本体領域中に、前記側壁と前記基板の上面とに隣接してソース領域を形成する工程を更に含むことを特徴とする請求項 1 9 に記載の方法。 10

**【請求項 2 5】**

前記トレンチの少なくとも前記底部に隣接して前記基板中に高導電領域を形成する工程を更に含むことを特徴とする請求項 1 9 に記載の方法。

**【請求項 2 6】**

半導体基板を準備する工程と、側壁と底部とを有するトレンチを前記基板中に形成する工程と、厚い絶縁層を前記底部上に堆積させる工程と、前記厚い絶縁層に接続する薄い絶縁層を前記側壁上に形成する工程と、前記厚い絶縁層の上側に、前記薄い絶縁層に隣接して、ゲートを前記トレンチ内に形成する工程を有する M I S デバイスの製造方法。

**【請求項 2 7】**

前記厚い絶縁層を堆積させる工程は、前記厚い絶縁層を前記側壁上および底部上に堆積させる工程と、マスク層を前記トレンチ内に堆積させる工程と、前記マスク層をエッティングすることにより、前記側壁上の厚い絶縁層の一部を露出させるとともに、前記トレンチの底部に前記マスク層の一部を残す工程と、前記厚い絶縁層をエッティングすることにより、前記側壁の露出部を形成するとともに、前記厚い絶縁層の一部を前記トレンチの底部に残す工程を含むことを特徴とする請求項 2 6 に記載の方法。 20

**【請求項 2 8】**

前記基板中に前記側壁に隣接して本体領域を形成する工程と、前記本体領域中に、前記側壁と前記基板の上面とに隣接してソース領域を形成する工程を更に含むことを特徴とする請求項 2 6 に記載の方法。 30

**【請求項 2 9】**

前記トレンチの少なくとも前記底部に隣接して高導電領域を前記基板中に形成する工程を更に含むことを特徴とする請求項 2 6 に記載の方法。

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

本発明は、トレンチ金属 - 絶縁体 - 半導体 ( M I S ) デバイスに関し、特に、高周波動作に適したトレンチ M O S F E T に関する。

**【背景技術】****【0 0 0 2】**

一部の金属 - 絶縁体 - 半導体 ( M I S ) デバイスは、半導体基板 ( 例えはシリコン ) の表面から下方に延在するトレンチ内に位置するゲートを有している。このようなデバイスにおける電流の流れは主に垂直であり、そのため、セルを密に組み込むことができる。つまり、他の条件が同じであれば、セルを密に組むことによって電流を流す能力が増大するとともに、デバイスのオン抵抗が減少する。 M I S デバイスの一般的なカテゴリーに含まれるデバイスとしては、金属酸化膜半導体電界効果トランジスタ ( M O S F E T ) と、絶縁ゲート型バイポーラトランジスタ ( I G B T ) と、 M O S ゲート型サイリスタが挙げられる。

**【0 0 0 3】**

例えば、トレンチ M O S F E T は、最適なリニア信号の増幅および切換えにおいて重要で 50

ある高い相互コンダクタンス ( $g_m$ ,  $m_{ax}$ ) および特定の低いオン抵抗 ( $R_{on}$ ) をもって製造することができる。しかし、高周波動作における最も重要な問題の1つとして、MOSFETの内部キャパシタンスの低減がある。内部キャパシタンスとしては、フィードバックキャパシタンス ( $C_{rss}$ ) とも呼ばれるゲート - ドレイン間キャパシタンス ( $C_{gd}$ ) と、入力キャパシタンス ( $C_{iss}$ ) と、出力キャパシタンス ( $C_{oss}$ ) を挙げることができる。

#### 【0004】

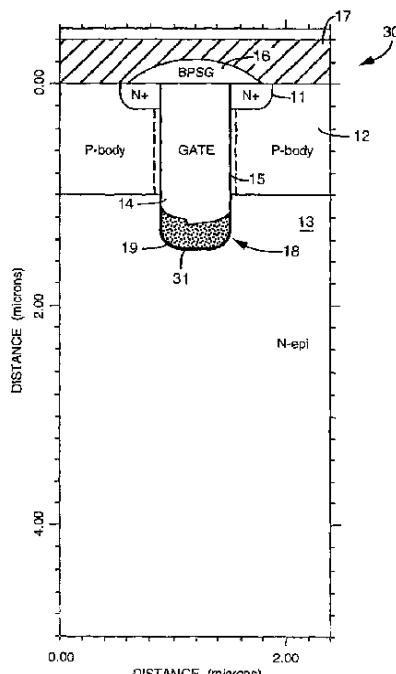

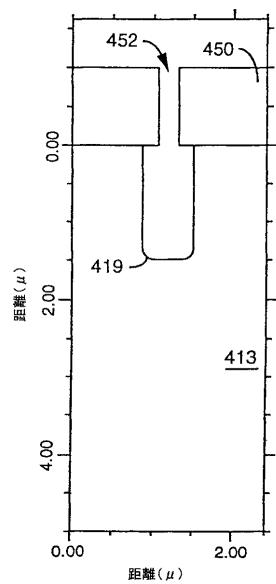

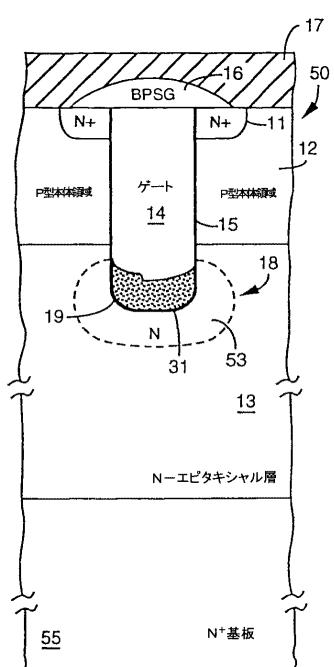

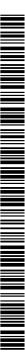

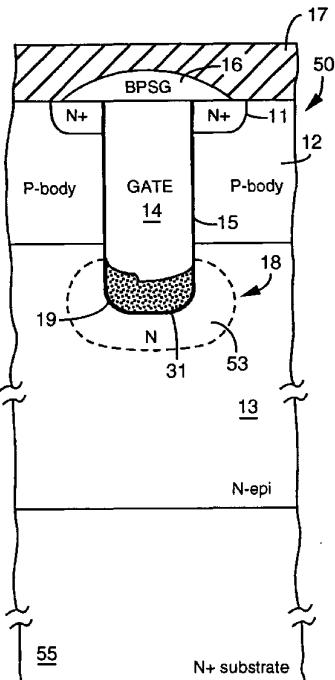

図1は、従来のn型トレンチMOSFET10の断面図である。MOSFET10においては、一般に $N^+$ 基板(図示せず)上に成長させられるn型エピタキシャル(「N-e pi」)層13がドレインである。N-エピタキシャル層13は、軽くドープされた層、すなわち、N-層であっても良い。N-エピタキシャル層13と $N^+$ ソース領域11は、p型本体領域12によって隔てられている。電流は、トレンチ19の側壁に沿って、チャネル(破線で示されている)を通じて垂直に流れる。トレンチ19の側壁および底部に沿って薄いゲート絶縁体15(例えば、二酸化ケイ素)が延在している。トレンチ19は、ドープされたポリシリコン等の導電材料で満たされ、該導電材料はゲート14を形成している。内部にゲート14を有するトレンチ19は、ボロホスホシリケートガラス(BPSG)等の絶縁層16によって覆われている。ソース領域11および本体領域12への電気接点は、一般に金属または金属合金である導体17によって形成されている。ゲート14は、図1の面の外側で3次元的に接触している。

#### 【0005】

MOSFET10の重大な欠点は、ゲート14とN-エピタキシャル層13との間に形成される大きなオーバーラップ領域18である。このオーバーラップ領域18は、薄いゲート絶縁体15の一部をドレイン作動電圧に晒してしまう。この大きなオーバーラップによって、MOSFET10のドレイン定格電圧は制限され、薄いゲート絶縁体15における長期的な信頼性が問題になり、MOSFET10のゲート - ドレイン間キャパシタンス  $C_{gd}$  は大きく増大する。トレンチ構造においては、従来の横方向デバイスよりも  $C_{gd}$  が大きい為、MOSFET10の切換速度が制限され、したがって、高周波用途におけるMOSFETの使用が制限される。

#### 【0006】

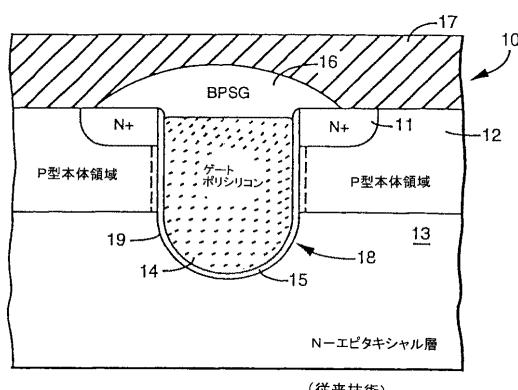

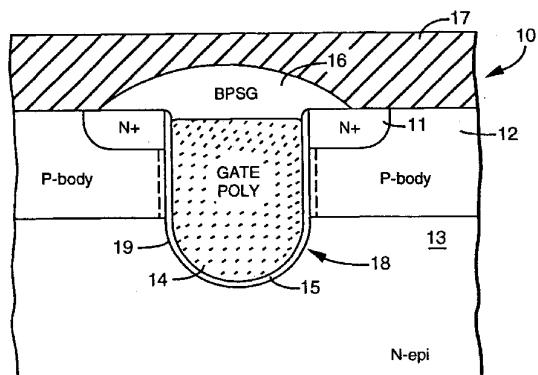

この欠点を解決する方法の一つは、前記米国特許出願第09/591,179号に記載されており、図2に示す。図2は、トレンチ19の底部近傍にドープされていないポリシリコンプラグ22を有するトレンチMOSFET20の断面図である。MOSFET20は、酸化膜21によってトレンチ19の底部から絶縁され且つ酸化膜23によってゲート14から絶縁されたポリシリコンプラグ22を除き、図1のMOSFET10に類似している。酸化膜21、ポリシリコンプラグ22、酸化膜23のサンドイッチ構造によって、ゲート14とN-エピタキシャル層13の距離が大きくなり、 $C_{gd}$  が小さくなる。

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0007】

しかしながら、ある状況下において、高周波用途には、ドープされていないポリシリコンよりも絶縁性が高い材料をトレンチ19の底部に設け、 $C_{gd}$  を最小限に抑えることが好ましい場合がある。したがって、ゲート - ドレイン間キャパシタンス  $C_{gd}$  が小さく且つ高周波性能が良好なトレンチMOSFETが望ましい。

#### 【0008】

本発明において、金属 - 絶縁体 - 半導体(MIS)デバイスは、トレンチが表面から内部に向かって延在する半導体基板を有している。第1の導電型のソース領域は、前記トレンチの側壁と前記基板の表面とに隣接している。第1の導電型と電荷が反対の第2の導電型の本体領域は、前記ソース領域と前記側壁とに隣接している。第1の導電型のドレイン領域は、前記本体領域と前記側壁に隣接している。前記トレンチは、前記本体領域と隣接する前記側壁の一部に沿って第1の絶縁層を設けている。また、前記トレンチは、前記ト

10

20

30

40

50

ンチの底部に沿って第2の絶縁層を設けている。前記第2の絶縁層は、第1の絶縁層に接続され、第1の絶縁層よりも厚い。前記トレンチの底部に沿って前記基板中の応力は殆ど変化しない。

【課題を解決するための手段】

【0009】

このようなMISデバイスの製造方法の典型的な実施形態においては、側壁と底部とを有するトレンチが基板中に形成される。前記トレンチの底部上には厚い絶縁層が堆積される。前記側壁上には薄い絶縁層が形成され、前記厚い絶縁層に接続される。トレンチ内部において、前記厚い絶縁層の一部の上側および前記薄い絶縁層に隣接してゲートが形成される。

10

【0010】

前記厚い絶縁層によって、トレンチゲートとドレイン導電領域はトレンチの底部において隔てられ、その結果、ゲート-ドレイン間キャパシタンスが小さくなる。これにより、トレンチMOSFET等の本発明に係るMISデバイスは、高周波の用途に適するようになる。

【0011】

本発明は、以下の説明および図面を参照することにより更に理解できる。図中、同様の又は類似の特徴的構成には、主に同じ参照符号が付されている。

【発明を実施するための最良の形態】

【0012】

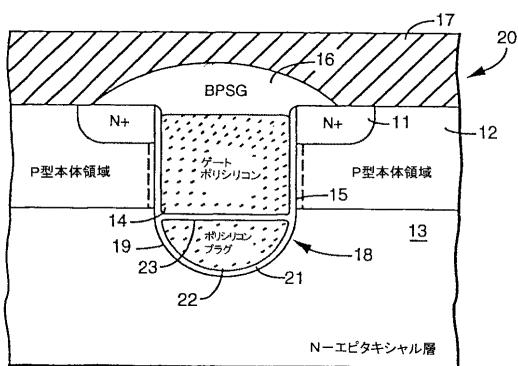

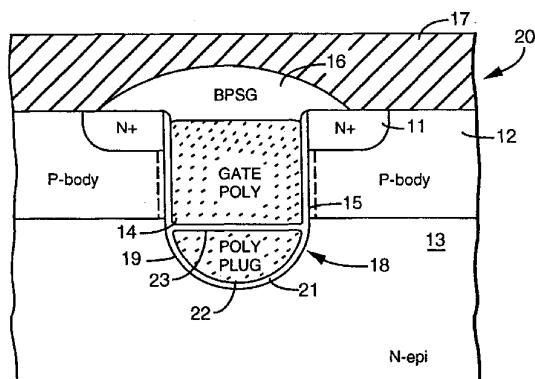

図3は、本発明に係るトレンチMOSFET30の一実施形態の断面図である。MOSFET30は、その一部が図1のMOSFET10と類似している。MOSFET30のトレンチ19の外側にある要素は、図1のMOSFET10のそれと同じであっても良い。しかし、MOSFET30においては、トレンチ19の側壁だけに沿って薄いゲート絶縁体15（例えば、二酸化ケイ素）が設けられている。図1のMOSFET10とは異なり、図3のMOSFET30のトレンチ19の底部に沿って、厚い絶縁層31（例えば、二酸化ケイ素）が設けられている。ゲート14とN-エピタキシャル層13（N<sup>-</sup>層であっても良い）は、厚い絶縁層31によって隔てられている。これにより、図1の場合のようなゲート14とN-エピタキシャル層13（ドレイン）が薄いゲート絶縁体15だけによって隔てられている際に生じる問題が回避される。また、厚い絶縁層31は、図2に示されるようなポリシリコンプラグ22を用いて達成しえる絶縁体よりも有効な絶縁体を形成する。すなわち、厚い絶縁体31は、ゲート-ドレイン間キャパシタンスC<sub>g-d</sub>を最小限に抑え、高周波の用途において有用なトレンチMOSFET30を形成することができる。

20

【0013】

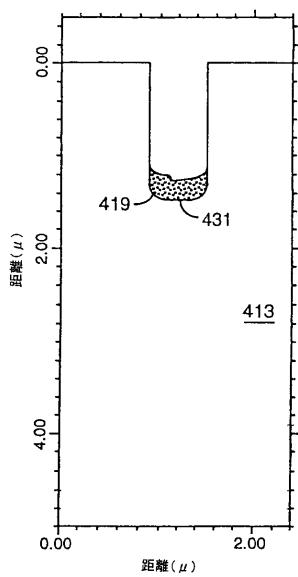

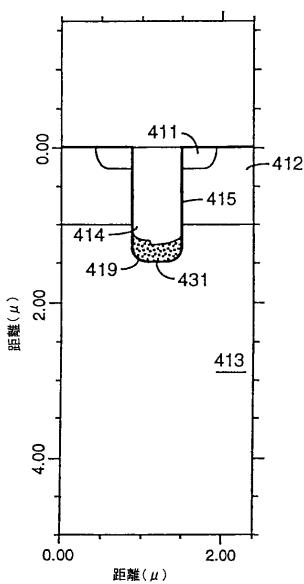

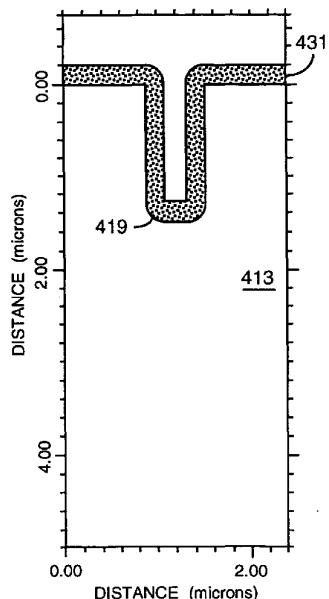

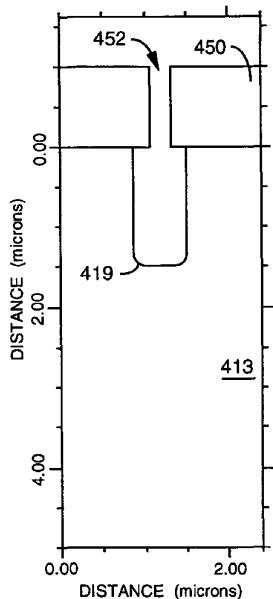

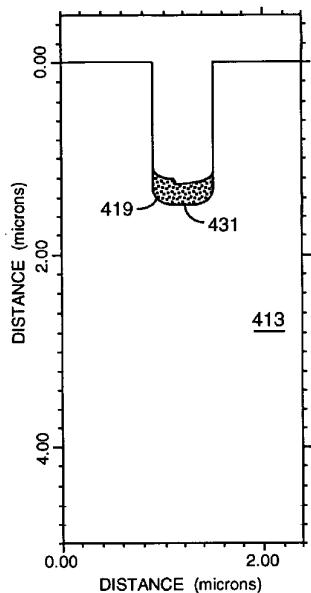

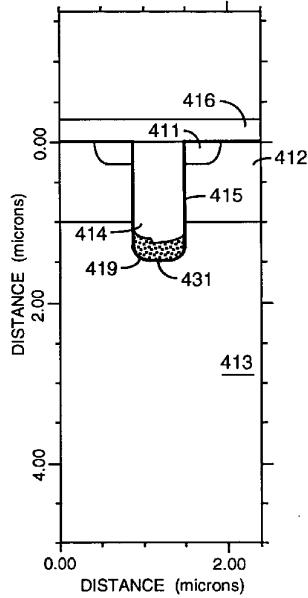

図4A～図4Kは、図3のMOSFET30等の本発明に係るトレンチMOSFETの製造方法の一実施形態を示す断面図である。図4Aに示されるように、工程は、濃密にドープしたN<sup>+</sup>基板（図示せず）上に成長させた、軽くドープしたN-エピタキシャル層413（一般に、約8μmの厚さ）から始まる。フォトレジストまたは酸化物等のトレンチマスク450がN-エピタキシャル層413上に堆積されてパターン化され、これにより、トレンチ419が位置される開口452が形成される。一般にドライプラズマエッティング、例えば反応性イオンエッティング（RIE）を使用し、トレンチ419を開口452を通じてエッティングする。トレンチ419は、幅が約0.5～1.2μm、深さが約1～2μmであっても良い。

30

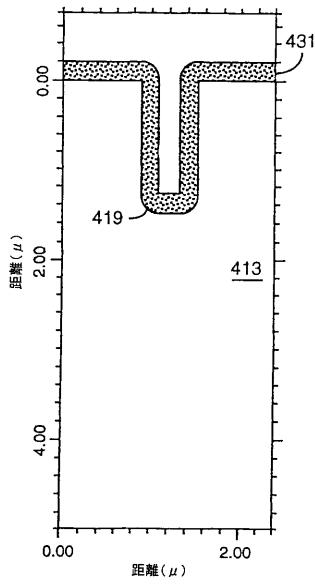

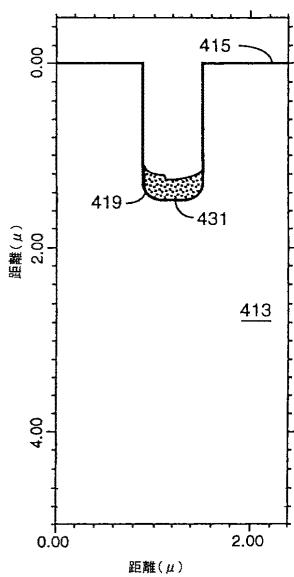

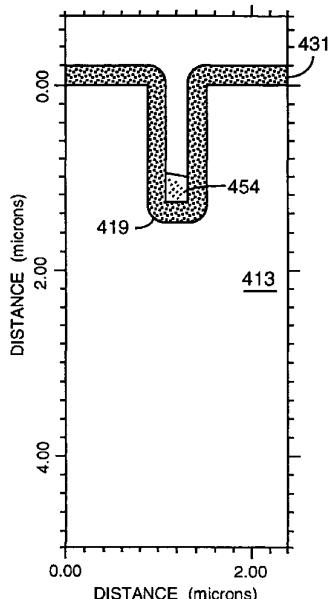

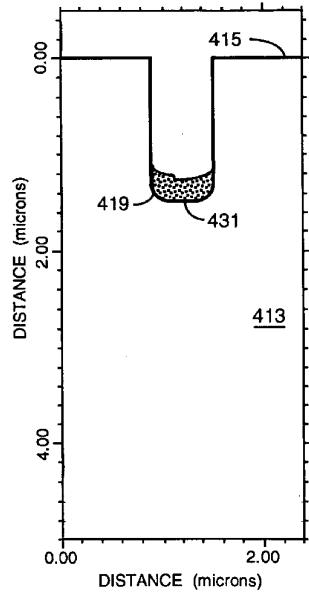

【0014】

図4Bに示されるように、マスク450が除去され、厚い絶縁層431（例えば約0.1～0.3μm）がN-エピタキシャル層413上に堆積される。この堆積工程は、化学気相成長法（CVD）等の従来の堆積技術にしたがって選択され、トレンチ419の側壁上および底部上とN-エピタキシャル層413の上面に、絶縁層431となる絶縁保護堆積物（conformal deposition）が形成される。厚い絶縁層431は、

40

50

例えば、低温酸化物（LTO）、ホスホシリケートガラス（PSG）、BPSG、または、他の絶縁材料であっても良い。幾つかの実施形態においては、厚い絶縁層431を堆積する前に、例えば950で10分間、良く知られたドライ酸化処理を使用して、薄い絶縁層（例えば、100～200の二酸化ケイ素）を熱的に成長させても良い。

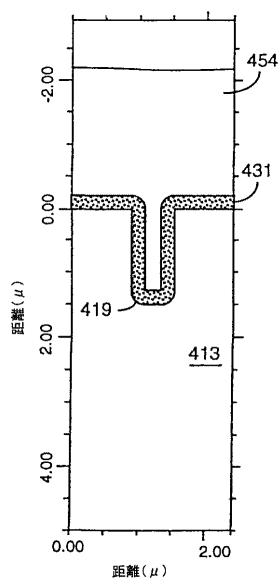

【0015】

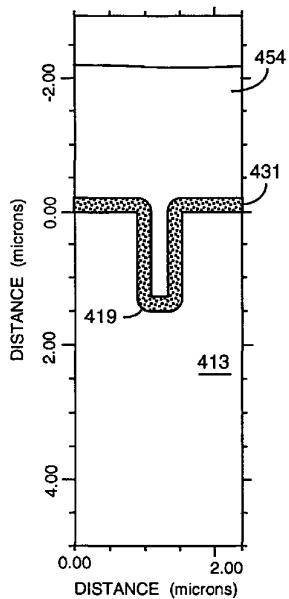

その後、図4Cに示すように、バリア層454がCVDによって堆積される。この堆積物は、絶縁保護しない（non-conformal）状態であってもよく、トレンチ419を充填し、厚い絶縁層431の最上面から溢れるように成される。バリア層454は、例えば、窒化ケイ素（Si<sub>3</sub>N<sub>4</sub>）であっても良く、また、厚さが2～4μmであっても良い。バリア層454は、一般的にはドライエッティングの後にウェットエッティングが行なわれ、厚い絶縁層431上のバリア層454に関して高い選択性を有するエッティング液を用いてエッチバックされる。図4Dに示されるように、バリア層454は、約0.1～0.2μmだけがトレンチ419内に残るまで、トレンチ419内へとエッチバックされる。

10

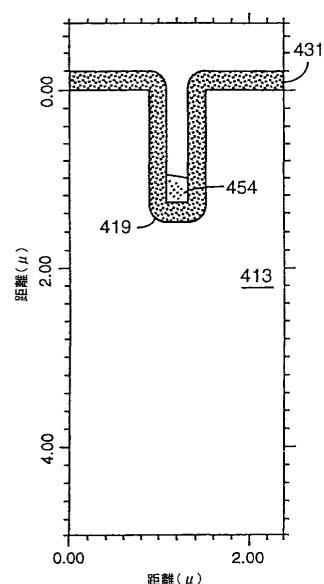

【0016】

その後、厚い絶縁層431は、一般にウェットエッティング技術により、バリア層454およびN-エピタキシャル層413の上側にある絶縁層431に関して高い選択性を有するエッティング液を用いて、エッティングされる。絶縁層431は、絶縁層431がトレンチ431の底部のみに残るまで、N-エピタキシャル層413の上面およびトレンチ419の側壁からエッティング除去される。バリア層454の残留物を除去することにより、図4Eに示される構造体が残る。

20

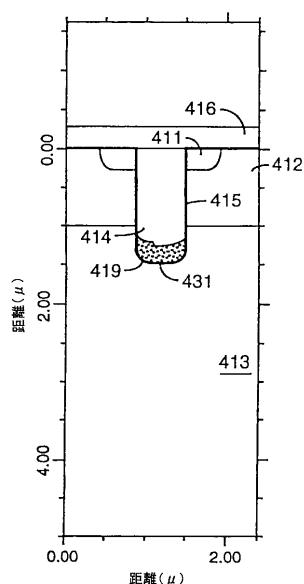

【0017】

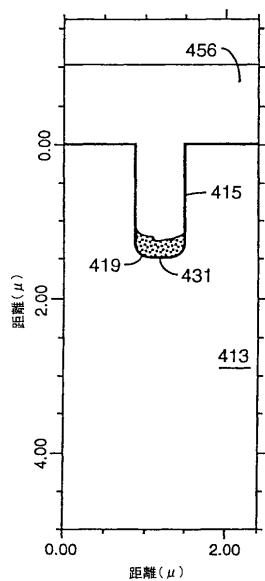

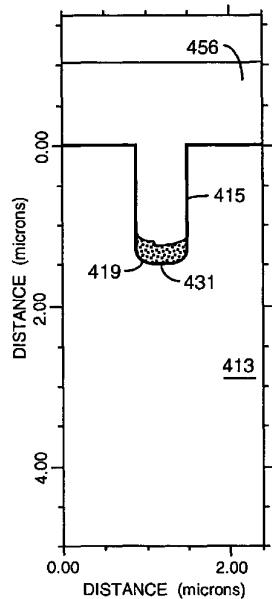

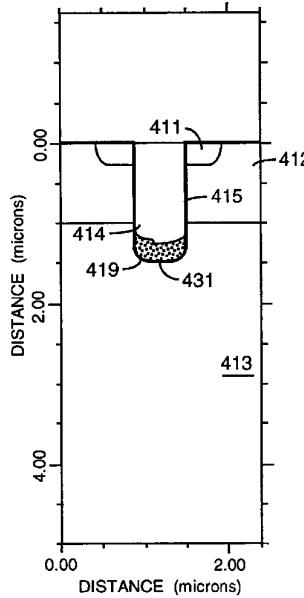

図4Fに示されるように、薄いゲート絶縁体415（例えば、厚さが約100～1000）がN-エピタキシャル層413の上面およびトレンチ419の側壁上に形成される。薄いゲート絶縁体415は、例えば、1050で20分間、ドライ酸化技術を用いて熱的に成長された二酸化ケイ素層であっても良い。幾つかの実施形態においては、薄いゲート絶縁体415を成長させる前に、犠牲ゲート酸化膜（図示せず）を熱的に成長させ、ウェットエッティングによって除去し、トレンチ419の側壁を洗浄しても良い。そのような犠牲ゲート酸化膜のウェットエッティングは、厚い絶縁層431がエッティングされるのを最小限に抑えるため、短時間のみ行なわれる。

30

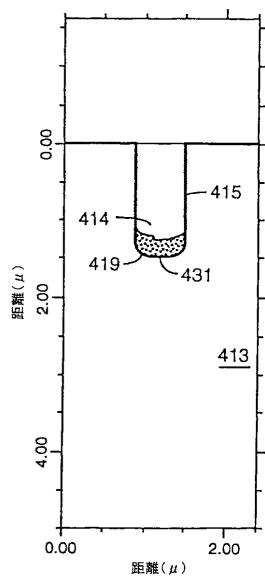

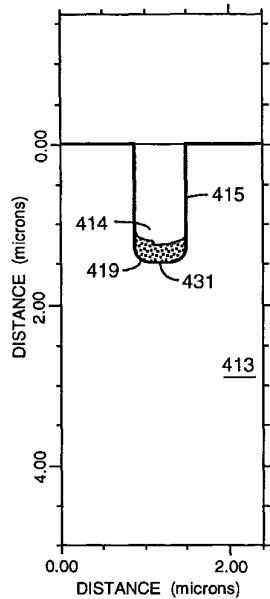

【0018】

図4Gに示すように、CVDによって、可能であれば低圧CVD（LPCVD）によって、導電材料456を堆積させる。これにより、トレンチ419に導電材料456が充填されるとともに、薄いゲート絶縁体415の最上面から導電材料456が溢れる。導電材料456は、例えば、現場でドープされたポリシリコン、または、後に注入（implanted）されてアニール処理されるドープされていないポリシリコン層、または、他の導電材料であっても良い。図4Hに示されるように、導電材料456は、一般に反応性イオンエッティングを用いて、導電材料456の上面がN-エピタキシャル層413の上面と略面一になるまでエッティングされ、これによりゲート414が形成される。n型MOSFETにおいて、ゲート414は、例えば、ドーピング濃度が10<sup>20</sup>cm<sup>-3</sup>のポリシリコン層であっても良い。幾つかの実施形態においては、トレンチ419の上端を過ぎてもさらに導電材料456をエッティングすることにより、ゲート414を凹状に窪ませて、ゲート-ソース間のオーバーラップキャパシタンスを最小限に抑えても良い。

40

【0019】

公知の注入処理および拡散処理を用いて、図4Iに示されるように、p型本体領域412およびN<sup>+</sup>ソース領域411がN-エピタキシャル層413中に形成される。p型本体領域412とN-エピタキシャル層413の残存部分との間のPN接合部は、厚い絶縁層431と薄いゲート絶縁体415との間の界面よりも上側の深さに位置する。

【0020】

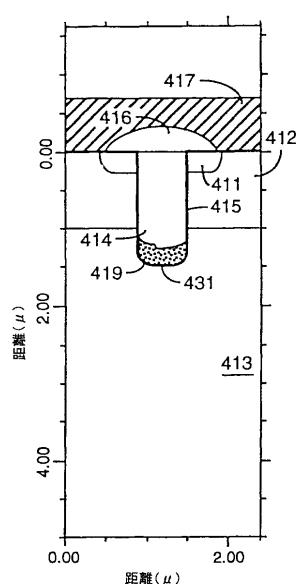

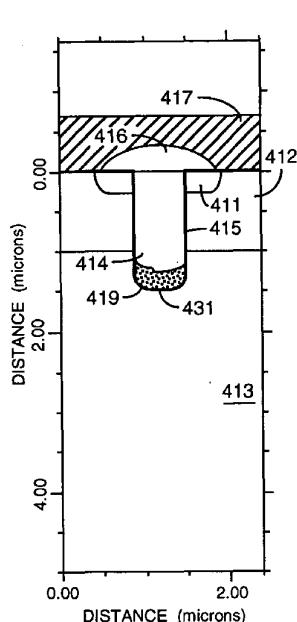

図4Jに示すように、ボロホスホシリケートガラス（BPSG）等の絶縁層416が、C

50

V D によって N - エピタキシャル層 4 1 3 およびゲート 4 1 4 の表面上に堆積される。絶縁層 4 1 6 は、一般にドライエッティングを用いてエッティングされ、これにより、図 4 K に示されるように、p 型本体領域 4 1 2 および N<sup>+</sup> ソース領域 4 1 1 の一部が露出する。一般に堆積された（例えば、物理気相成長法、メッキ、スパッタリング、または、蒸発によって）金属または金属合金である導体 4 1 7 を用いて、本体領域 4 1 2 およびソース領域 4 1 1 への電気接点が形成される。ゲート 4 1 4 への電気接点は、図 4 K の面の外側に 3 次元的に形成される。ドレイン（図示せず）への電気接点は、N<sup>+</sup> 基板（図示せず）の N - エピタキシャル層 4 1 3 が成長した面とは反対側の面に形成される。

## 【0021】

したがって、この方法によれば、トレンチ 4 1 9 の底部に厚い絶縁層 4 3 1 を組み込んでも、C<sub>g\_d</sub> を最小限に抑えることができ、厚い絶縁層 4 3 1 を熱的に成長させることによって引き起こされる虞がある望ましくない影響または製造上の問題を最小に留めることができる。例えば、酸化物を熱的に成長させるのではなく、酸化物を堆積することにより、厚い酸化物をトレンチ 4 1 9 の凹状の底部内に成長させることによって生じる応力の影響が回避される。厚い絶縁層 4 3 1 を堆積することにより、厚い絶縁層 4 3 1 の熱的な成長中に「鳥のくちばし（bird's beak）」が形成されることによって生じる可能性がある厚い絶縁層 4 3 1 と薄いゲート絶縁体 4 1 5 の接続部での絶縁層の薄層化が回避される。また、厚い絶縁層 4 3 1 を堆積することにより、エッティングされたトレンチ 4 1 9 の側壁の外形の変化も避けられる。尚、厚い絶縁層 4 3 1 を成長させてそのような外形の変化が起こることも可能性は少ないとあり、後にトレンチ 4 1 9 の側壁上に薄いゲート絶縁体 4 1 5 を成長させても補えない「バルブ」作用がトレンチ 4 1 9 の底部に起きる。

## 【0022】

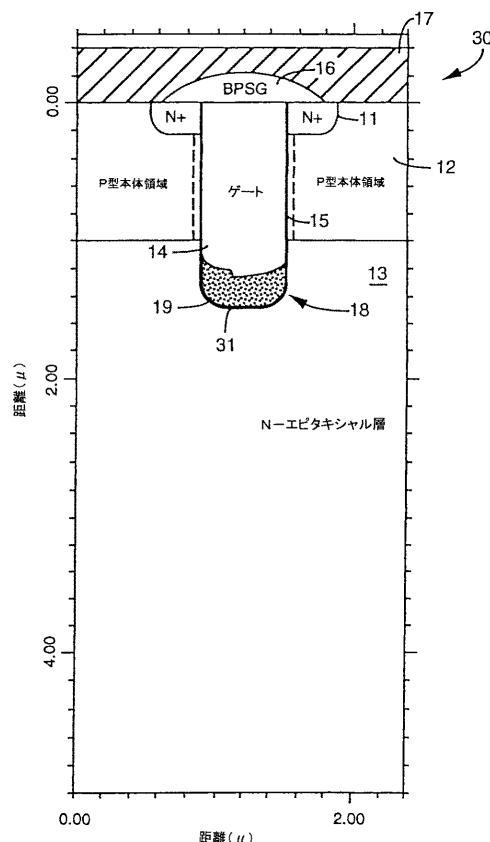

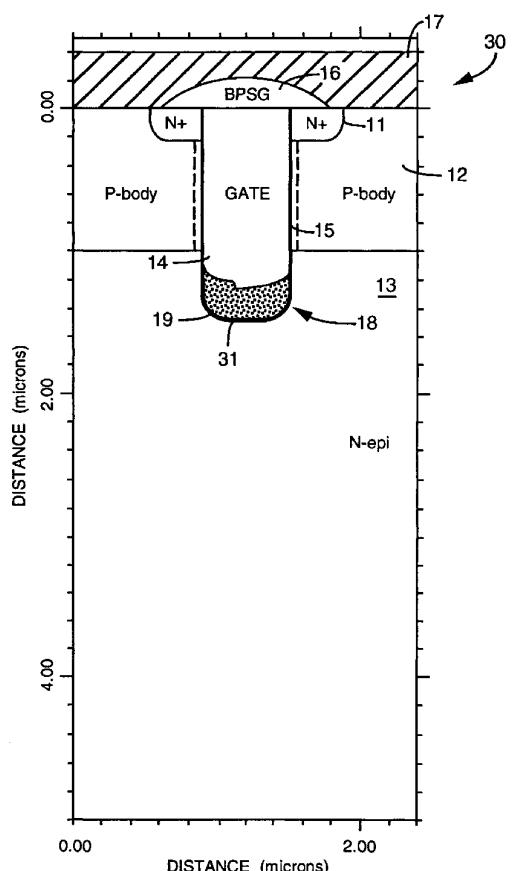

図 5 は、本発明に係る他の実施形態であるトレンチ MOSFET 5 0 の断面図である。MOSFET 5 0 は、多くの点で図 3 の MOSFET 3 0 と類似している。特に、トレンチ 1 9 の側壁だけに沿って薄いゲート絶縁体 1 5 が延び、一方、厚い絶縁層 3 1 がトレンチ 1 9 の底部に沿って延在している。図 3 の MOSFET 3 0 においては、トレンチ 1 9 の底部で積層中に広がる抵抗が増大することに起因して、厚い絶縁層 3 1 が MOSFET 3 0 のオン抵抗 (R<sub>on</sub>) を大きくする可能性がある。しかし、図 5 の MOSFET 5 0 は、電流がより効果的に拡散することを助ける高ドーピング領域 5 3 をトレンチ 1 9 の底部に有している。高ドーピング領域 5 3 は、N<sup>+</sup> 基板 5 5 上にある N - エピタキシャル層 1 3 中に形成されている。高ドーピング領域 5 3 は、図 4 A に示されるようにトレンチがエッティングされた後、マスク 4 5 0 が除去される前に、ヒ素またはリン等の n 型ドーパントを注入することにより形成されても良い。このように、厚い絶縁層 3 1 がゲート - ドレイン間キャパシタンス C<sub>g\_d</sub> を最小限に抑えるとともに、高ドーピング領域 5 3 がオン抵抗 (R<sub>on</sub>) を最小にすることで、高周波の用途に十分適したトレンチ MOSFET 5 0 が形成される。

## 【0023】

前述した実施形態は、一例にすぎず、この発明の広い原理を限定するものではない。当業者であれば分かるように、多くの他の実施形態も考えられる。例えば、この発明の構造および方法は、トレンチゲートとトレンチの外側の領域との間に絶縁層を形成することが望ましい任意のタイプの金属 - 絶縁体 - 半導体 (MIS) デバイスにおいて使用することができる。適切な場合には、様々な絶縁材料または導電材料を使用することもでき、また、本発明は p 型 MOSFET にも適している。本発明は、以下の請求の範囲によってのみ限定される。

## 【図面の簡単な説明】

## 【0024】

【図 1】従来のトレンチ MOSFET の断面図である。

【図 2】トレンチの底部にポリシリコンプラグを有するトレンチ MOSFET の断面図である。

【図 3】本発明に係るトレンチ MOSFET の一実施形態の断面図である。

10

20

30

40

50

【図4A】図4Aから図4Kは、本発明に係るトレンチMOSFETの製造方法の一実施形態を示す断面図である。

【図4B】図4Aから図4Kは、本発明に係るトレンチMOSFETの製造方法の一実施形態を示す断面図である。

【図4C】図4Aから図4Kは、本発明に係るトレンチMOSFETの製造方法の一実施形態を示す断面図である。

【図4D】図4Aから図4Kは、本発明に係るトレンチMOSFETの製造方法の一実施形態を示す断面図である。

【図4E】図4Aから図4Kは、本発明に係るトレンチMOSFETの製造方法の一実施形態を示す断面図である。

10

【図4F】図4Aから図4Kは、本発明に係るトレンチMOSFETの製造方法の一実施形態を示す断面図である。

【図4G】図4Aから図4Kは、本発明に係るトレンチMOSFETの製造方法の一実施形態を示す断面図である。

【図4H】図4Aから図4Kは、本発明に係るトレンチMOSFETの製造方法の一実施形態を示す断面図である。

【図4I】図4Aから図4Kは、本発明に係るトレンチMOSFETの製造方法の一実施形態を示す断面図である。

【図4J】図4Aから図4Kは、本発明に係るトレンチMOSFETの製造方法の一実施形態を示す断面図である。

20

【図4K】図4Aから図4Kは、本発明に係るトレンチMOSFETの製造方法の一実施形態を示す断面図である。

【図5】本発明に係るトレンチMOSFETの他の実施形態の断面図である。

【図1】

【図2】

【図3】

【図4A】

4A

【図4B】

4B

【図4C】

4C

【図4D】

4D

【図4E】

4E

【図4F】

4F

【図4G】

4G

【図4H】

4H

【図4 I】

4I

【図4 J】

4J

【図4 K】

4K

【図5】

## 【国際公開パンフレット】

(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau(43) International Publication Date

20 February 2003 (20.02.2003)

PCT

(10) International Publication Number

WO 03/015179 A2(51) International Patent Classification\*: H01L 29/78,

29/423, 21/336Princeton Drive, San Jose, CA 95118 (US); LUI, Kam

Hong; 3433 Geneva Drive, Santa Clara, CA 95051 (US);

CHEN, Kuo-In; 1673 Newcastle Drive, Los Altos, CA

94024 (US); TERRILL, Kyle; 3385 Londonderry Drive,

Santa Clara, CA 95050 (US).

(21) International Application Number: PCT/US02/22937

(22) International Filing Date: 19 July 2002 (19.07.2002)

(25) Filing Language: English

(74) Agent: KLIVANS, Norman, R.; Skjerven Morrill I.J.P. 25

Metro Drive, Suite 700, San Jose, CA 95110 (US).

(26) Publication Language: English

(81) Designated States (national): JP, KR.

(30) Priority Data: 09/927,320 10 August 2001 (10.08.2001) US

(84) Designated States (regional): European patent (AT, BE,

BG, CII, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, IE, IT,

LU, MC, NL, PT, SE, SK, TR).(71) Applicant: SILICONIX INCORPORATED [US/US];

2301 Laurewood Road, Santa Clara, CA 95054-1595

(US).(72) Inventors: DARWISH, Mohamed, N.; 675 Regas Drive,

Campbell, CA 95008 (US); GILES, Frederick, P.; 1561

[Continued on next page]

(54) Title: TRENCH MIS DEVICE WITH REDUCED GATE-TO-DRAIN CAPACITANCE

(57) **Abstract:** Trench MIS devices including a thick insulative layer at the bottom of the trench are disclosed, along with methods of fabricating such devices. An exemplary trench MOSFET embodiment includes a thick oxide layer at the bottom of the trench, with no appreciable change in stress in the substrate along the trench bottom. The thick insulative layer separates the trench gate from the drain region at the bottom of the trench yielding a reduced gate-to-drain capacitance making such MOSFETs suitable for high frequency applications. In an exemplary fabrication process embodiment, the thick insulative layer is deposited on the bottom of the trench. A thin insulative gate dielectric is formed on the exposed sidewall and is coupled to the thick insulative layer. A gate is formed in the remaining trench volume. The process is completed with body and source implants, passivation, and metallization.

WO 03/015179 A2

---

**WO 03/015179 A2**

*For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.*

WO 03/015179

PCT/US02/22937

**TRENCH MIS DEVICE WITH REDUCED

GATE-TO-DRAIN CAPACITANCE**

**FIELD OF THE INVENTION**

This invention relates to trench metal-insulator-semiconductor (MIS) devices and 5 in particular to trench MOSFETs that are suitable for high frequency operation.

**BACKGROUND**

Some metal-insulator-semiconductor (MIS) devices include a gate located in a trench that extends downward from the surface of a semiconductor substrate (e.g., silicon). The current flow in such devices is primarily vertical and, as a result, the cells can be more 10 densely packed. All else being equal, this increases the current carrying capability and reduces the on-resistance of the device. Devices included in the general category of MIS devices include metal-oxide-semiconductor field effect transistors (MOSFETs), insulated gate bipolar transistors (IGBTs), and MOS-gated thyristors.

Trench MOSFETs, for example, can be fabricated with a high transconductance 15 ( $g_{m,\max}$ ) and low specific on resistance ( $R_{on}$ ), which are important for optimal linear signal amplification and switching. One of the most important issues for high frequency operation, however, is reduction of the MOSFET internal capacitances. The internal capacitances include the gate-to-drain capacitance ( $C_{gd}$ ), which is also called the feedback capacitance ( $C_{rss}$ ), the input capacitance ( $C_{iss}$ ), and the output capacitance ( $C_{oss}$ ).

20 **Fig. 1** is a cross-sectional view of a conventional n-type trench MOSFET 10. In MOSFET 10, an n-type epitaxial ("N-epi") layer 13, which is usually grown on an  $N^+$  substrate (not shown), is the drain. N-epi layer 13 may be a lightly doped layer, that is, an  $N'$  layer. A p-type body region 12 separates N-epi layer 13 from  $N^+$  source regions 11. Current flows vertically through a channel (denoted by the dashed lines) along the sidewall 25 of a trench 19. The sidewall and bottom of trench 19 are lined with a thin gate insulator 15 (e.g., silicon dioxide). Trench 19 is filled with a conductive material, such as doped polysilicon, which forms a gate 14. Trench 19, including gate 14 therein, is covered with an insulative layer 16, which may be borophosphosilicate glass (BPSG). Electrical contact to source regions 11 and body region 12 is made with a conductor 17, which is typically a 30 metal or metal alloy. Gate 14 is contacted in the third dimension, outside of the plane of **Fig. 1**.

WO 03/015179

PCT/US02/22937

A significant disadvantage of MOSFET 10 is a large overlap region 18 formed between gate 14 and N-epi layer 13, which subjects a portion of thin gate insulator 15 to the drain operating voltage. The large overlap limits the drain voltage rating of MOSFET 10, presents long term reliability issues for thin gate insulator 15, and greatly increases the 5 gate-to-drain capacitance,  $C_{gd}$ , of MOSFET 10. In a trench structure,  $C_{gd}$  is larger than in conventional lateral devices, limiting the switching speed of MOSFET 10 and thus its use in high frequency applications.

One possible method to address this disadvantage is described in the above-referenced Application No. 09/591,179 and is illustrated in **Fig. 2**. **Fig. 2** is a cross-sectional view of a trench MOSFET 20 with an undoped polysilicon plug 22 near the bottom of trench 19. MOSFET 20 is similar to MOSFET 10 of **Fig. 1**, except for polysilicon plug 22, which is isolated from the bottom of trench 19 by oxide layer 21 and from gate 14 by oxide layer 23. The sandwich of oxide layer 21, polysilicon plug 22, and oxide layer 23 serves to increase the distance between gate 14 and N-epi layer 13, thereby 15 decreasing  $C_{gd}$ .

In some situations, however, it may be preferable to have a material even more insulative than undoped polysilicon in the bottom of trench 19 to minimize  $C_{gd}$  for high frequency applications. Accordingly, a trench MOSFET with decreased gate-to-drain capacitance,  $C_{gd}$ , and better high frequency performance is desirable.

20 **SUMMARY**

In accordance with the present invention, a metal-insulator-semiconductor (MIS) device includes a semiconductor substrate including a trench extending into the substrate from a surface of the substrate. A source region of a first conductivity type is adjacent to a sidewall of the trench and to the surface of the substrate. A body region of a second 25 conductivity type opposite to the first conductivity type is adjacent to the source region and to the sidewall. A drain region of the first conductivity type is adjacent to the body region and to the sidewall. The trench is lined with a first insulative layer along a portion of the sidewall that abuts the body region. The trench is also lined with a second insulative layer along a bottom portion of the trench. The second insulative layer is 30 coupled to the first insulative layer, and the second insulative layer is thicker than the first insulative layer. The stress in the substrate along the bottom portion of the trench does not change appreciably.

WO 03/015179

PCT/US02/22937

In an exemplary embodiment of a fabrication process for such an MIS device, a trench including a sidewall and a bottom is formed in a substrate. A thick insulative layer is deposited on the bottom of the trench. A thin insulative layer is formed on the sidewall, and is coupled to the thick insulative layer. A gate is formed above the portion of the thick insulative layer and adjacent to the thin insulative layer in the trench.

5 The thick insulative layer separates the trench gate from the drain conductive region at the bottom of the trench resulting in a reduced gate-to-drain capacitance. This makes MIS devices in accordance with the present invention, such as trench MOSFETs, suitable for high frequency applications.

10 BRIEF DESCRIPTION OF THE DRAWINGS

This invention will be better understood by reference to the following description and drawings. In the drawings, like or similar features are typically labeled with the same reference numbers.

**Fig. 1** is a cross-sectional view of a conventional trench MOSFET.

15 **Fig. 2** is a cross-sectional view of a trench MOSFET with a polysilicon plug at the bottom of the trench.

**Fig. 3** is a cross-sectional view of one embodiment of a trench MOSFET in accordance with the present invention.

20 **Figs. 4A-4K** are cross-sectional views illustrating one embodiment of a process for fabricating a trench MOSFET in accordance with the present invention.

**Fig. 5** is a cross-sectional view of an alternative embodiment of a trench MOSFET in accordance with the present invention.

DETAILED DESCRIPTION OF THE INVENTION

25 **Fig. 3** is a cross-sectional view of one embodiment of a trench MOSFET 30 in accordance with the present invention. MOSFET 30 has some similarities to MOSFET 10 of **Fig. 1**. The elements of MOSFET 30 outside of trench 19 can be the same as those of MOSFET 10 of **Fig. 1**. In MOSFET 30, however, only the sidewall of trench 19 is lined with thin gate insulator 15 (e.g., silicon dioxide). Unlike MOSFET 10 of **Fig. 1**, a thick insulative layer 31 (e.g., silicon dioxide) lines the bottom of trench 19 of MOSFET 30 of

30 **Fig. 3**. Thick insulative layer 31 separates gate 14 from N-epi layer 13 (which may be an N<sup>+</sup> layer). This circumvents the problems that occur when only thin gate insulator 15

WO 03/015179

PCT/US02/22937

separates gate 14 from N-epi layer 13 (the drain) as in **Fig. 1**. Thick insulative layer 31 also provides a more effective insulator than is achievable with polysilicon plug 22 as shown in **Fig. 2**. Thus, thick insulative layer 31 minimizes the gate-to-drain capacitance,  $C_{gd}$ , and yields a trench MOSFET 30 useful for high frequency applications.

5 **Figs. 4A-4K** are cross-sectional views illustrating one embodiment of a process for fabricating a trench MOSFET, such as MOSFET 30 of **Fig. 3**, in accordance with the present invention. As shown in **Fig. 4A**, the process begins with a lightly-doped N-epi layer 413 (typically about 8  $\mu\text{m}$  thick) grown on a heavily doped  $\text{N}^+$  substrate (not shown). A trench mask 450, which may be photoresist or an oxide, is deposited on N-epi layer 413 and patterned to form an opening 452 where a trench 419 is to be located. Trench 419 is etched through opening 452, typically using a dry plasma etch, for example, a reactive ion etch (RIE). Trench 419 may be about 0.5-1.2  $\mu\text{m}$  wide and about 1-2  $\mu\text{m}$  deep.

10 Mask 450 is removed, and a thick insulative layer 431 (e.g., about 0.1-0.3  $\mu\text{m}$ ) is deposited on N-epi layer 413, as shown in **Fig. 4B**. The deposition process is chosen, according to conventional deposition techniques such as chemical vapor deposition (CVD), to yield conformal deposition of insulative layer 431 on the sidewall and bottom of trench 419, as well as on the top surface of N-epi layer 413. Thick insulative layer 431 may be, for example, a low temperature oxide (LTO), a phosphosilicate glass (PSG), a BPSG, or another insulative material. In some embodiments, a thin insulative layer (e.g., 20 100-200  $\text{\AA}$  of silicon dioxide) could be thermally grown, for example, using a well known dry oxidation process at 950  $^{\circ}\text{C}$  for 10 minutes, prior to deposition of thick insulative layer 431.

25 As shown in **Fig. 4C**, a barrier layer 454 is then deposited by CVD. This deposition can be non-conformal, filling trench 419 and overflowing past the topmost surface of thick insulative layer 431. Barrier layer 454 may be, for example, silicon nitride ( $\text{Si}_3\text{N}_4$ ), and may be 2-4  $\mu\text{m}$  thick. Barrier layer 454 is etched back, typically by performing a dry etch followed by a wet etch, using etchants that have high selectivity for barrier layer 454 over thick insulative layer 431. Barrier layer 454 is etched back into trench 419 until only about 0.1-0.2  $\mu\text{m}$  remains in trench 419, as shown in **Fig. 4D**.

30 Thick insulative layer 431 is then etched, typically by a wet etch technique, using an etchant that has high selectivity for insulative layer 431 over barrier layer 454 and over N-epi layer 413. Insulative layer 431 is etched from the top of N-epi layer 413 and from the sidewall of trench 419 until insulative layer 431 remains only in the bottom of trench

WO 03/015179

PCT/US02/22937

431. The remainder of barrier layer 454 is removed, leaving the structure shown in Fig. 4E.

As shown in Fig. 4F, a thin gate insulator 415 (e.g., about 100-1000 Å thick) is then formed on the top surface of N-epi layer 413 and on the sidewall of trench 419. Thin 5 gate insulator 415 may be, for example, a silicon dioxide layer that is thermally grown using a dry oxidation technique at 1050 °C for 20 minutes. In some embodiments, a sacrificial gate oxide (not shown) can be thermally grown and removed by a wet etch to clean the sidewall of trench 419 prior to growing thin gate insulator 415. The wet etch of such a sacrificial gate oxide is kept short to minimize etching of thick insulative layer 431.

10 As shown in Fig. 4G, a conductive material 456 is deposited by CVD, possibly by low pressure CVD (LPCVD), to fill trench 419 and overflow past the topmost surface of thin gate insulator 415. Conductive material 456 may be, for example, an in-situ doped polysilicon, or an undoped polysilicon layer that is subsequently implanted and annealed, or an alternative conductive material. Conductive material 456 is etched, typically using a 15 reactive ion etch, until the top surface of material 456 is approximately level with the top of N-epi layer 413, thereby forming gate 414, as shown in Fig. 4H. In an n-type MOSFET, gate 414 may be, for example, a polysilicon layer with a doping concentration of  $10^{20} \text{ cm}^{-3}$ . In some embodiments, conductive material 456 may be etched past the top of trench 419, thereby recessing gate 414 to minimize the gate-to-source overlap 20 capacitance.

Using known implantation and diffusion processes, p-type body regions 412 and N<sup>+</sup> source regions 411 are formed in N-epi layer 413 as shown in Fig. 4I. The PN junctions between p-type body regions 412 and the remainder of N-epi layer 413 are located at a depth above the interface between thick insulative layer 431 and thin gate 25 insulator 415.

As shown in Fig. 4J, an insulative layer 416, which may be borophosphosilicate glass (BPSG), is deposited by CVD on the surfaces of N-epi layer 413 and gate 414. Insulative layer 416 is etched, typically using a dry etch, to expose portions of p-type body 30 regions 412 and N<sup>+</sup> source regions 411, as shown in Fig. 4K. Electrical contact to body regions 412 and source regions 411 is made with a conductor 417, which is typically a deposited (e.g., by physical vapor deposition, plating, sputtering, or evaporation) metal or metal alloy. Electrical contact to gate 414 is made in the third dimension, outside of the

WO 03/015179

PCT/US02/22937

plane of **Fig. 4K**. Electrical contact to the drain (not shown) is made to the opposite surface of the N<sup>+</sup> substrate (not shown) on which N-epi layer 413 is grown.

This method thus allows incorporation of thick insulative layer 431 at the bottom of trench 419 to minimize  $C_{gd}$  with minimal undesirable effects or manufacturing concerns, which may be caused by thermally growing thick insulative layer 431. For example, stress effects from growing a thick oxide in the concave bottom of trench 419 are avoided by depositing the oxide rather than thermally growing it. Thinning of the insulative layers at the juncture of thick insulative layer 431 and thin gate insulator 415, possibly caused by formation of a "bird's beak" during a thermal growth of thick insulative layer 431, are avoided by depositing thick insulative layer 431. In addition, shifts in the etched sidewall profile of trench 419 are also avoided by depositing thick insulative layer 431. Growing thick insulative layer 431 could cause such shifts, resulting in a "bulb" effect at the bottom of trench 419 that is not compensated by subsequent growth of thin gate insulator 415 on the sidewall of trench 419.

**Fig. 5** is a cross-sectional view of an alternative embodiment of a trench MOSFET 50 in accordance with the present invention. MOSFET 50 has many similarities to MOSFET 30 of **Fig. 3**. In particular, only the sidewall of trench 19 is lined with thin gate insulator 15, while thick insulative layer 31 lines the bottom of trench 19. In MOSFET 30 of **Fig. 3**, thick insulative layer 31 may increase the on-resistance ( $R_{on}$ ) of MOSFET 30 due to an increase in the spreading resistance in the accumulation layer at the bottom of trench 19. MOSFET 50 of **Fig. 5**, however, includes a high doping region 53 at the bottom of trench 19 to help spread current more effectively. High doping region 53 is formed in N-epi layer 13, which overlies an N<sup>+</sup> substrate 55. High doping region 53 may be created by implanting an n-type dopant, such as arsenic or phosphorous, before mask 450 is removed after the trench etch shown in **Fig. 4A**. Thus, thick insulative layer 31 minimizes gate-to-drain capacitance,  $C_{gd}$ , and high doped region 53 minimizes on-resistance,  $R_{on}$ , yielding a trench MOSFET 50 well-suited for high frequency applications.

The foregoing embodiments are intended to be illustrative and not limiting of the broad principles of this invention. Many additional embodiments will be apparent to persons skilled in the art. For example, the structures and methods of this invention can be used with any type of metal-insulator-semiconductor (MIS) device in which it is desirable to form an insulating layer between a trench gate and a region outside the trench. Also, various insulative or conductive materials can be used where appropriate, and the

WO 03/015179

PCT/US02/22937

invention is also applicable to p-type MOSFETs. The invention is limited only by the following claims.

WO 03/015179

PCT/US02/22937

CLAIMS

We claim:

1. A metal-insulator-semiconductor device, comprising:

- a semiconductor substrate including a trench extending into said substrate from a surface of said substrate;

- 5 a source region of a first conductivity type adjacent to a sidewall of said trench and to said surface;

- a body region of a second conductivity type opposite to said first conductivity type adjacent to said source region and to said sidewall; and

- 10 a drain region of said first conductivity type adjacent to said body region and to said sidewall,

wherein a stress in said substrate along a bottom portion of said trench does not change appreciably and wherein said trench is lined with a first insulative layer along a portion of said sidewall that abuts said body region and wherein said trench is lined with a second insulative layer along said bottom portion of said trench, said second insulative layer being coupled to said first insulative layer and said second insulative layer being thicker than said first insulative layer.

2. The MIS device of Claim 1, further comprising a gate region coupled to said first insulative layer and said second insulative layer within said trench.

- 20 3. The MIS device of Claim 2, wherein said gate region comprises polysilicon.

4. The MIS device of Claim 1, further including a high conductivity region of said first conductivity type formed in said drain region adjacent to at least said bottom portion of said trench.

- 25 5. The MIS device of Claim 1, wherein said first insulative layer comprises an oxide.

6. The MIS device of Claim 1, wherein said second insulative layer comprises an oxide.

7. The MIS device of Claim 1, wherein said second insulative layer comprises

- 30 a multi-layer insulative layer.

WO 03/015179

PCT/US02/22937

8. The MIS device of Claim 1, wherein said MIS device comprises a MOSFET.

9. A trench-gate MOSFET, comprising:

- 5 a semiconductor substrate including a trench extending into said substrate from a surface of said substrate;

- a source region of a first conductivity type adjacent to a sidewall of said trench and to said surface;

- a body region of a second conductivity type opposite to said first conductivity type adjacent to said source region and to said sidewall;

- 10 a drain region of said first conductivity type adjacent to said body region and to said sidewall,

- wherein a stress in said substrate along a bottom portion of said trench does not change appreciably and wherein said trench is lined with a first insulative layer along a portion of said sidewall that abuts said body region and wherein said trench is lined with a second insulative layer along said bottom portion of said trench, said second insulative layer being coupled to said first insulative layer and said second insulative layer being thicker than said first insulative layer; and

- 15 a gate region coupled to said first insulative layer and said second insulative layer within said trench.

- 20 10. The trench-gate MOSFET of Claim 9, wherein said gate region comprises polysilicon.

11. The trench-gate MOSFET of Claim 9, further including a high conductivity region of said first conductivity type formed in said drain region adjacent to at least said bottom portion of said trench.

- 25 12. The trench-gate MOSFET of Claim 9, wherein said first insulative layer comprises an oxide.

13. The trench-gate MOSFET of Claim 9, wherein said second insulative layer comprises an oxide.

- 30 14. The trench-gate MOSFET of Claim 9, wherein said second insulative layer comprises a multi-layer insulative layer.

WO 03/015179

PCT/US02/22937

15. A trench-gate MOSFET, comprising:

- a semiconductor substrate including a trench extending into said substrate from a surface of said substrate;

- 5 a source region of a first conductivity type adjacent to a sidewall of said trench and to said surface;

- a body region of a second conductivity type opposite to said first conductivity type adjacent to said source region and to said sidewall;

- 10 a drain region of said first conductivity type adjacent to said body region and to said sidewall;

- a first insulative layer lining said trench along a portion of said sidewall that abuts said body region;

- a second insulative layer lining said trench along a bottom portion of said trench, said second insulative layer being thicker than said first insulative layer and said second insulative layer being coupled to said first insulative layer,

- 15 wherein a thickness of a transition insulative layer at the juncture of said first insulative layer and said second insulative layer is not less than a thickness of said first insulative layer; and

- a gate region coupled to said first insulative layer and said second insulative layer within said trench.

- 20 16. The trench-gate MOSFET of Claim 15, further including a high conductivity region of said first conductivity type formed in said drain region adjacent to at least said bottom portion of said trench.

- 25 17. A trench-gate MOSFET, comprising:

- a semiconductor substrate including a trench extending into said substrate from a surface of said substrate;

- a source region of a first conductivity type adjacent to a sidewall of said trench and to said surface;

- a body region of a second conductivity type opposite to said first conductivity type adjacent to said source region and to said sidewall;

WO 03/015179

PCT/US02/22937

a drain region of said first conductivity type adjacent to said body region and to said sidewall;

5 a first insulative layer lining said trench along a portion of said sidewall that abuts said body region;

10 a second insulative layer lining said trench along a bottom portion of said trench, said second insulative layer being thicker than said first insulative layer and said second insulative layer being coupled to said first insulative layer, wherein a first diameter of said trench taken at a vertical midpoint of said second insulative layer is not greater than a second diameter of said trench taken adjacent to said body region; and

15 a gate region coupled to said first insulative layer and said second insulative layer within said trench.

18. The trench-gate MOSFET of Claim 17, further including a high conductivity region of said first conductivity type formed in said drain region adjacent to at least said bottom portion of said trench.

19. A method of fabricating an MIS device, comprising:

providing a semiconductor substrate;

forming a trench in said substrate, said trench including a sidewall and a bottom;

20 depositing a thick insulative layer on said sidewall and said bottom;

depositing a mask layer in said trench;

etching said mask layer to expose a portion of said thick insulative layer on said sidewall while leaving a portion of said mask layer at said bottom of said trench;

25 etching said thick insulative layer to form an exposed portion of said sidewall while leaving a portion of said thick insulative layer at said bottom of said trench;

forming a thin insulative layer on said exposed portion of said sidewall; and

30 forming a gate above said portion of said thick insulative layer and adjacent said thin insulative layer in said trench.

WO 03/015179

PCT/US02/22937

20. The method of Claim 19, wherein said forming a thin insulative layer includes thermally oxidizing said sidewall.

21. The method of Claim 20, further comprising:

- 5 growing a thin sacrificial oxide layer on said sidewall prior to said forming a thin insulative layer; and

- removing said sacrificial oxide layer prior to said forming a thin insulative layer.

22. The method of Claim 19, wherein said forming a gate comprises:

- 10 depositing doped polysilicon in said trench; and

- etching said doped polysilicon to a level about equal to said surface of said substrate.

23. The method of Claim 19, further comprising growing a thin insulative layer on said sidewall and said bottom prior to said depositing a thick insulative layer.

24. The method of Claim 19, further comprising:

- 15 forming a body region in said substrate adjacent said sidewall; and

- forming a source region in said body region, said source region adjacent said sidewall and a top surface of said substrate.

25. The method of Claim 19, further comprising forming a high conductivity region in said substrate adjacent to at least said bottom of said trench.

26. A method of fabricating an MIS device, comprising:

- 20 providing a semiconductor substrate;

- forming a trench in said substrate, said trench including a sidewall and a bottom;

- depositing a thick insulative layer on said bottom;

- 25 forming a thin insulative layer on said sidewall, said thin insulative layer coupled to said thick insulative layer; and

- forming a gate in said trench above said thick insulative layer and adjacent to said thin insulative layer.

WO 03/015179

PCT/US02/22937

27. The method of Claim 26, wherein said depositing a thick insulative layer comprises:

depositing said thick insulative layer on said sidewall and said bottom;

depositing a mask layer in said trench;

5 etching said mask layer to expose a portion of said thick insulative layer on said sidewall while leaving a portion of said mask layer at said bottom of said trench; and

10 etching said thick insulative layer to form an exposed portion of said sidewall while leaving a portion of said thick insulative layer at said bottom of said trench.

28. The method of Claim 26, further comprising:

forming a body region in said substrate adjacent said sidewall; and

forming a source region in said body region, said source region adjacent said sidewall and a top surface of said substrate.

15 29. The method of Claim 26, further comprising forming a high conductivity region in said substrate adjacent to at least said bottom of said trench.

WO 03/015179

PCT/US02/32937

1/8

FIG. 1 (PRIOR ART)

FIG. 2

SUBSTITUTE SHEET (RULE 26)

2/8

FIG. 3

SUBSTITUTE SHEET (RULE 26)

3/8

SUBSTITUTE SHEET (RULE 26)

SUBSTITUTE SHEET (RULE 26)

FIG. 4E

FIG. 4F

FIG. 4G

FIG. 4H

SUBSTITUTE SHEET (RULE 26)

8/8

FIG. 4K

FIG. 5

SUBSTITUTE SHEET (RULE 26)

## 【国際調査報告】

| INTERNATIONAL SEARCH REPORT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                         | International Filing No.<br>PCT/US 02/22937                                    |          |                                                                                    |                       |   |                                                                                                                                                                                                                                                         |      |   |                                                                                                         |                      |   |                                                                                                                             |             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|----------|------------------------------------------------------------------------------------|-----------------------|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---|---------------------------------------------------------------------------------------------------------|----------------------|---|-----------------------------------------------------------------------------------------------------------------------------|-------------|

| <b>A. CLASSIFICATION OF SUBJECT MATTER</b><br>IPC 7 H01L29/78 H01L29/739 H01L29/423 H01L21/336 H01L21/331                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                         |                                                                                |          |                                                                                    |                       |   |                                                                                                                                                                                                                                                         |      |   |                                                                                                         |                      |   |                                                                                                                             |             |

| <b>According to International Patent Classification (IPC) or to both national classification and IPC</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                         |                                                                                |          |                                                                                    |                       |   |                                                                                                                                                                                                                                                         |      |   |                                                                                                         |                      |   |                                                                                                                             |             |

| <b>B. FIELDS SEARCHED</b><br>Minimum documentation searched (classification system followed by classification symbols)<br>IPC 7 H01L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                         |                                                                                |          |                                                                                    |                       |   |                                                                                                                                                                                                                                                         |      |   |                                                                                                         |                      |   |                                                                                                                             |             |

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                         |                                                                                |          |                                                                                    |                       |   |                                                                                                                                                                                                                                                         |      |   |                                                                                                         |                      |   |                                                                                                                             |             |

| Electronic data base consulted during the international search (name of data base and, where practical, search terms used)<br>EPO-Internal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                         |                                                                                |          |                                                                                    |                       |   |                                                                                                                                                                                                                                                         |      |   |                                                                                                         |                      |   |                                                                                                                             |             |

| <b>C. DOCUMENTS CONSIDERED TO BE RELEVANT</b> <table border="1" style="width: 100%; border-collapse: collapse;"> <thead> <tr> <th style="text-align: left; width: 10%;">Category</th> <th style="text-align: left; width: 80%;">Citation of document, with indication, where appropriate, of the relevant passages</th> <th style="text-align: left; width: 10%;">Relevant to claim No.</th> </tr> </thead> <tbody> <tr> <td>X</td> <td>WO 00 72372 A (WILLIAMS R K ET AL)<br/>30 November 2000 (2000-11-30)<br/>page 17, line 20 -page 21, line 4; figures<br/>2,13A-13N<br/>page 21, line 23 -page 22, line 5; figures<br/>16A-16E<br/>page 27, line 3 - line 21; figures<br/>26A-26B,27A-27D<br/>---</td> <td>1-29</td> </tr> <tr> <td>A</td> <td>US 5 424 231 A (YANG S-H)<br/>13 June 1995 (1995-06-13)<br/>column 4, line 12 - line 58; figure 2L<br/>---</td> <td>4,11,16,<br/>18,25,29</td> </tr> <tr> <td>X</td> <td>DE 199 35 442 C (SIEMENS AG)<br/>21 December 2000 (2000-12-21)<br/>column 5, line 4 -column 6, line 47;<br/>figures 1-7<br/>---</td> <td>1-29<br/>-/-</td> </tr> </tbody> </table>                                                                                                                                                                                             |                                                                                                                                                                                                                                                         |                                                                                | Category | Citation of document, with indication, where appropriate, of the relevant passages | Relevant to claim No. | X | WO 00 72372 A (WILLIAMS R K ET AL)<br>30 November 2000 (2000-11-30)<br>page 17, line 20 -page 21, line 4; figures<br>2,13A-13N<br>page 21, line 23 -page 22, line 5; figures<br>16A-16E<br>page 27, line 3 - line 21; figures<br>26A-26B,27A-27D<br>--- | 1-29 | A | US 5 424 231 A (YANG S-H)<br>13 June 1995 (1995-06-13)<br>column 4, line 12 - line 58; figure 2L<br>--- | 4,11,16,<br>18,25,29 | X | DE 199 35 442 C (SIEMENS AG)<br>21 December 2000 (2000-12-21)<br>column 5, line 4 -column 6, line 47;<br>figures 1-7<br>--- | 1-29<br>-/- |

| Category                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                                                      | Relevant to claim No.                                                          |          |                                                                                    |                       |   |                                                                                                                                                                                                                                                         |      |   |                                                                                                         |                      |   |                                                                                                                             |             |

| X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | WO 00 72372 A (WILLIAMS R K ET AL)<br>30 November 2000 (2000-11-30)<br>page 17, line 20 -page 21, line 4; figures<br>2,13A-13N<br>page 21, line 23 -page 22, line 5; figures<br>16A-16E<br>page 27, line 3 - line 21; figures<br>26A-26B,27A-27D<br>--- | 1-29                                                                           |          |                                                                                    |                       |   |                                                                                                                                                                                                                                                         |      |   |                                                                                                         |                      |   |                                                                                                                             |             |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | US 5 424 231 A (YANG S-H)<br>13 June 1995 (1995-06-13)<br>column 4, line 12 - line 58; figure 2L<br>---                                                                                                                                                 | 4,11,16,<br>18,25,29                                                           |          |                                                                                    |                       |   |                                                                                                                                                                                                                                                         |      |   |                                                                                                         |                      |   |                                                                                                                             |             |

| X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | DE 199 35 442 C (SIEMENS AG)<br>21 December 2000 (2000-12-21)<br>column 5, line 4 -column 6, line 47;<br>figures 1-7<br>---                                                                                                                             | 1-29<br>-/-                                                                    |          |                                                                                    |                       |   |                                                                                                                                                                                                                                                         |      |   |                                                                                                         |                      |   |                                                                                                                             |             |

| <input checked="" type="checkbox"/> Further documents are listed in the continuation of box C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                         | <input checked="" type="checkbox"/> Patent family members are listed in annex. |          |                                                                                    |                       |   |                                                                                                                                                                                                                                                         |      |   |                                                                                                         |                      |   |                                                                                                                             |             |

| * Special categories of cited documents:<br>*A* document defining the general state of the art which is not considered to be of particular relevance<br>*E* earlier document but published on or after the international filing date<br>*L* document which may be of relevance to the priority claim(s) or which is cited to establish the priority date of another claim for other special reason (as specified)<br>*O* document referring to an oral disclosure, use, exhibition or other means<br>*P* document published prior to the international filing date but later than the priority date claimed<br>*T* later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention<br>*X* document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone<br>*Y* document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other prior art documents, such combination being obvious to a person skilled in the art<br>*8* document member of the same patent family |                                                                                                                                                                                                                                                         |                                                                                |          |                                                                                    |                       |   |                                                                                                                                                                                                                                                         |      |   |                                                                                                         |                      |   |                                                                                                                             |             |