## (12)发明专利

(10)授权公告号 CN 103811553 B

(45)授权公告日 2019.02.26

(21)申请号 201310540664.2

(51)Int.CI.

(22)申请日 2013.11.05

H01L 29/78(2006.01)

(65)同一申请的已公布的文献号

H01L 21/336(2006.01)

申请公布号 CN 103811553 A

H01L 21/76(2006.01)

(43)申请公布日 2014.05.21

H01L 23/48(2006.01)

(30)优先权数据

13/671,506 2012.11.07 US

(56)对比文件

(73)专利权人 恩智浦美国有限公司

US 2003/0080381 A1, 2003.05.01,

地址 美国得克萨斯

CN 102593119 A, 2012.07.18,

(72)发明人 H·M·鲍德 陈伟泽

US 5834826 A, 1998.11.10,

R·J·德苏扎 P·M·帕里斯

审查员 郑钰

(74)专利代理机构 中国国际贸易促进委员会专

利商标事务所 11038

代理人 刘倜

权利要求书3页 说明书21页 附图11页

## (54)发明名称

带有通过电阻器电路互连的有源器件和隔

离结构的半导体器件和驱动电路及其制作方法

## (57)摘要

本公开涉及带有通过电阻器电路互连的有源器件和隔离结构的半导体器件和驱动电路及其制作方法。半导体器件和驱动电路的实施例包括有第一导电类型的半导体衬底、隔离结构(包括下沉区域和埋层)、位于包含在所述隔离结构的衬底的区域内的有源器件以及电阻器电路。所述埋层位于顶衬底表面下面，并且有第二导电类型。所述下沉区域延伸于所述顶衬底表面和所述埋层之间，并且有所述第二导电类型。所述有源器件包括体区域，该区域通过有所述第一导电类型的所述半导体衬底的一部分与所述隔离结构分开。所述电阻器电路连接在所述隔离结构和所述体区域之间。所述电阻器电路可以包括一个或多个电阻网络以及可选择地包括肖特基二极管和/或一个或多个与所述电阻网络串联和/或并联的PN结二极管。

CN 103811553 B

## 1. 一种半导体器件,包括:

半导体衬底,有第一导电类型和顶衬底表面;

埋层,位于所述顶衬底表面下面,其中所述埋层有不同于所述第一导电类型的第二导电类型;

下沉区域,位于所述顶衬底表面和所述埋层之间,其中所述下沉区域有所述第二导电类型,并且隔离结构由所述下沉区域和所述埋层形成;

有源器件,位于由所述隔离结构包含的所述半导体衬底的部分内,其中所述有源器件包括:

所述第一导电类型的漂移区域,从所述顶衬底表面延伸到所述半导体衬底中;

所述第一导电类型的漏极区域,从所述顶衬底表面延伸到所述漂移区域中;

所述第二导电类型的体区域,从所述顶衬底表面延伸到位于所述漂移区域和所述隔离结构之间的所述半导体衬底中,其中所述体区域和所述隔离结构通过有所述第一导电类型的所述半导体衬底的一部分分开;和

所述第一导电类型的源极区域,从所述顶衬底表面延伸到所述体区域中;以及

电阻器电路,所述电阻器电路的第一端子耦合于所述体区域,以及所述电阻器电路的第二端子耦合于所述隔离结构。

## 2. 根据权利要求1所述的半导体器件,其中所述电阻器电路包括:

多晶硅电阻器。

## 3. 根据权利要求1所述的半导体器件,其中所述电阻器电路包括:

第一电阻网络;以及

肖特基二极管,耦合于所述第一电阻网络,其中所述肖特基二极管由耦合于所述隔离结构的肖特基接触形成。

## 4. 根据权利要求3所述的半导体器件,其中:

所述肖特基二极管串联耦合于所述第一电阻网络。

## 5. 根据权利要求3所述的半导体器件,其中:

所述肖特基二极管并联耦合于所述第一电阻网络。

## 6. 根据权利要求5所述的半导体器件,其中所述电阻器电路还包括:

第二电阻网络,串联耦合于所述肖特基二极管。

## 7. 根据权利要求3所述的半导体器件,其中所述电阻器电路还包括:

PN结二极管,并联耦合于所述肖特基二极管。

## 8. 根据权利要求1所述的半导体器件,其中所述电阻器电路包括:

第一电阻网络;以及

PN结二极管,耦合于所述第一电阻网络。

## 9. 根据权利要求8所述的半导体器件,其中:

所述PN结二极管串联耦合于所述第一电阻网络。

## 10. 根据权利要求8所述的半导体器件,其中:

所述PN结二极管并联耦合于所述第一电阻网络。

## 11. 根据权利要求10所述的半导体器件,其中所述电阻器电路还包括:

第二电阻网络,串联耦合于所述PN结二极管。

12. 根据权利要求8所述的半导体器件,还包括:

所述第一导电类型的另一区域,延伸到所述下沉区域中,其中所述PN结二极管形成于所述另一区域和所述下沉区域之间。

13. 根据权利要求8所述的半导体器件,其中所述PN结二极管包括多晶硅二极管。

14. 根据权利要求1所述的半导体器件,其中:

所述第一导电类型的漂移区域位于所述有源区域的中心部分内。

15. 一种驱动电路,包括:

第一横向扩散金属氧化物半导体场效应晶体管(LDMOSFET),形成于有第一导电类型和顶衬底表面的半导体衬底上,其中所述第一横向扩散金属氧化物半导体场效应晶体管(LDMOSFET)包括:

埋层,位于所述顶衬底表面下面,其中所述埋层有不同于所述第一导电类型的第二导电类型;

下沉区域,位于所述顶衬底表面和所述埋层之间,其中所述下沉区域有所述第二导电类型,并且隔离结构由所述下沉区域和所述埋层形成;

有源器件,位于由所述隔离结构包含的所述半导体衬底的部分内,其中所述有源器件包括:

所述第一导电类型的漂移区域,从所述顶衬底表面延伸到所述半导体衬底中;

所述第一导电类型的漏极区域,从所述顶衬底表面延伸到所述漂移区域中;

所述第二导电类型的体区域,从所述顶衬底表面延伸到位于所述漂移区域和所述隔离结构之间的所述半导体衬底中,其中所述体区域和所述隔离结构通过有所述第一导电类型的所述半导体衬底的一部分分开;和

所述第一导电类型的源极区域,从所述顶衬底表面延伸到所述体区域中;以及

电阻器电路,所述电阻器电路的第一端子耦合于所述体区域,以及所述电阻器电路的第二端子耦合于所述隔离结构。

16. 根据权利要求15所述的驱动电路,其中所述电阻器电路包括:

多晶硅电阻器。

17. 根据权利要求15所述的驱动电路,其中所述电阻器电路包括:

第一电阻网络;以及

肖特基二极管,耦合于所述第一电阻网络,其中所述肖特基二极管由耦合于所述隔离结构的肖特基接触形成。

18. 根据权利要求17所述的驱动电路,其中所述肖特基二极管并联耦合于所述第一电阻网络,并且所述电阻器电路还包括:

第二电阻网络,串联耦合于所述肖特基二极管。

19. 根据权利要求15所述的驱动电路,其中所述电阻器电路包括:

第一电阻网络;以及

PN结二极管,耦合于所述第一电阻网络。

20. 根据权利要求19所述的驱动电路,还包括:

所述第一导电类型的另一区域,延伸到所述下沉区域中,其中所述PN结二极管形成于所述另一区域和所述下沉区域之间。

21. 根据权利要求19所述的驱动电路,其中所述PN结二极管包括多晶硅二极管。

22. 根据权利要求19所述的驱动电路,其中所述PN结二极管并联耦合于所述第一电阻网络,并且所述电阻器电路还包括:

第二电阻网络,串联耦合于所述PN结二极管。

23. 一种形成半导体器件的方法,所述方法包括以下步骤:

形成位于有第一导电类型的半导体衬底的顶衬底表面下面的埋层,其中所述埋层有不同于所述第一导电类型的第二导电类型;

形成位于所述顶衬底表面和所述埋层之间的下沉区域,其中所述下沉区域有所述第二导电类型,并且由所述下沉区域和所述埋层形成隔离结构;

形成位于由所述隔离结构包含的所述半导体衬底的部分内的有源器件,其中所述有源器件包括:

所述第一导电类型的漂移区域,从所述顶衬底表面延伸到所述半导体衬底中;

所述第一导电类型的漏极区域,从所述顶衬底表面延伸到所述漂移区域中;

所述第二导电类型的体区域,从所述顶衬底表面延伸到位于所述漂移区域和所述隔离结构之间的所述半导体衬底中,其中所述体区域和所述隔离结构通过有所述第一导电类型的所述半导体衬底的一部分分开;和

所述第一导电类型的源极区域,从所述顶衬底表面延伸到所述体区域中;以及

形成电阻器电路,所述电阻器电路的第一端子耦合于所述体区域,以及所述电阻器电路的第二端子耦合于所述隔离结构。

24. 根据权利要求23所述的方法,其中形成所述电阻器电路包括:

形成并且互连多晶硅电阻器作为所述电阻器电路的一部分。

25. 根据权利要求23所述的方法,其中所述电阻器电路包括电阻网络和肖特基二极管,并且形成所述电阻器电路包括:

形成所述电阻网络;

形成所述肖特基二极管,其中所述肖特基二极管包括耦合于所述隔离结构的肖特基接触;以及

将所述电阻网络耦合于所述肖特基接触。

26. 根据权利要求23所述的方法,其中所述电阻器电路包括电阻网络和PN结二极管,并且形成所述电阻器电路包括:

形成所述电阻网络;

形成延伸到所述下沉区域中的所述第一导电类型的另一区域,其中所述PN结二极管形成于所述另一区域和所述下沉区域之间;以及

将所述电阻网络耦合于所述另一区域。

27. 根据权利要求23所述的方法,其中所述电阻器电路包括电阻网络和PN结二极管,并且形成所述电阻器电路包括:

形成所述电阻网络;

形成作为多晶硅二极管的所述PN结二极管;以及

将所述电阻网络耦合于所述多晶硅二极管。

## 带有通过电阻器电路互连的有源器件和隔离结构的半导体器件和驱动电路及其制作方法

### 技术领域

[0001] 实施例通常涉及半导体器件及其制作方法,更具体地说,涉及带有隔离结构的横向扩散金属氧化物半导体(LDMOS)器件。

### 背景技术

[0002] 在某些包括电感负载的片上系统(SOC)应用中,某些节点在切换期间可以会经历负电位,这可以会导致将显著的电流注入到衬底。注入到衬底的载荷子可以干扰相邻电路,从而不利地影响其运行。

[0003] 因此,就不断需要可以克服这一困难和提供改进性能的改进的器件结构、材料以及制作方法。还期望采用的方法、材料以及结构与现今制作能力和材料相容,并且不需要对可用的制作程序进行实质性修改或不需要大幅增加制作成本。此外,结合附图和前述的技术领域和背景,从后续的详细说明书和所附的权利要求中来看,各个实施例的其它有利特征和特性将变得显而易见。

[0004] 附图简要说明

[0005] 结合以下附图,以下的实施例将会得到描述,其中类似的数字表示类似的元素,以及

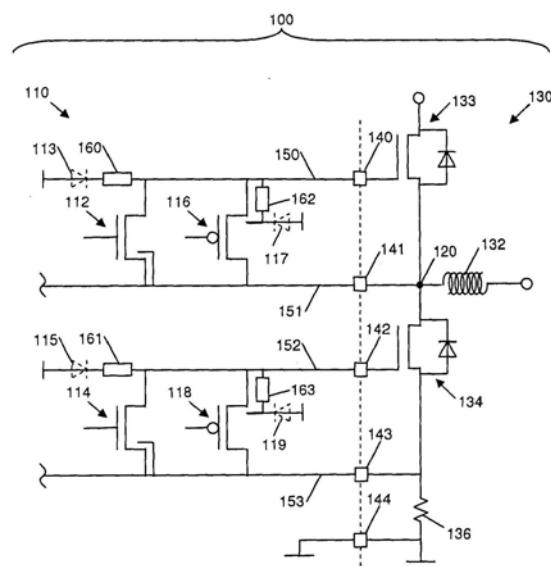

[0006] 图1根据实施例,是包括被配置以驱动包括电感负载的外部电路的驱动电路的电子系统的简化图;

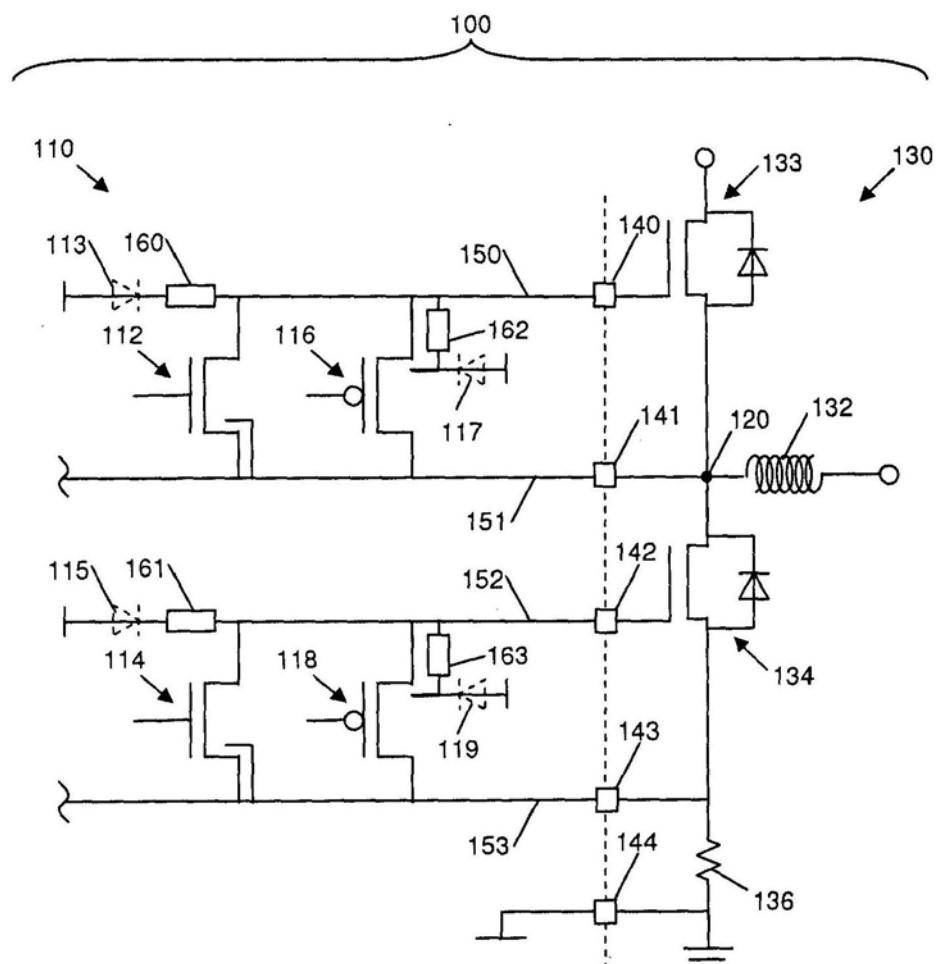

[0007] 图2根据实施例,是N型、横向扩散金属氧化物半导体场效应晶体管(NLDMOSFET)的截面图,带有连接在NLDMOSFET的漏极区域和隔离结构之间的电阻器电路;

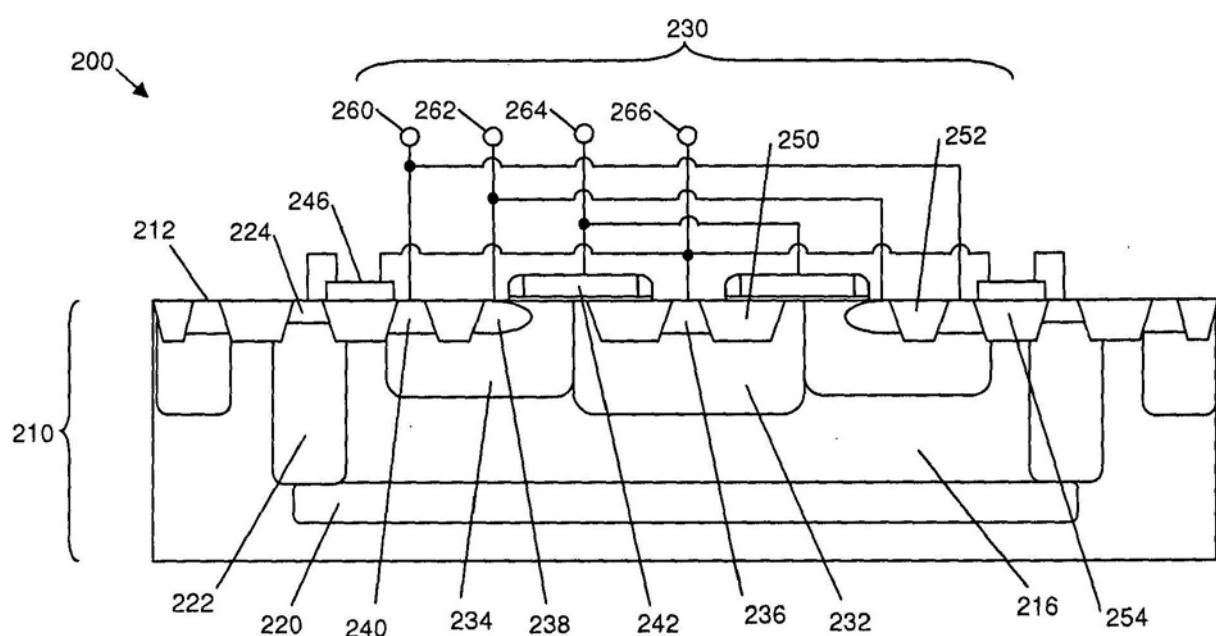

[0008] 图3根据实施例,是图2的N LDMOSFET的简化电路表征;

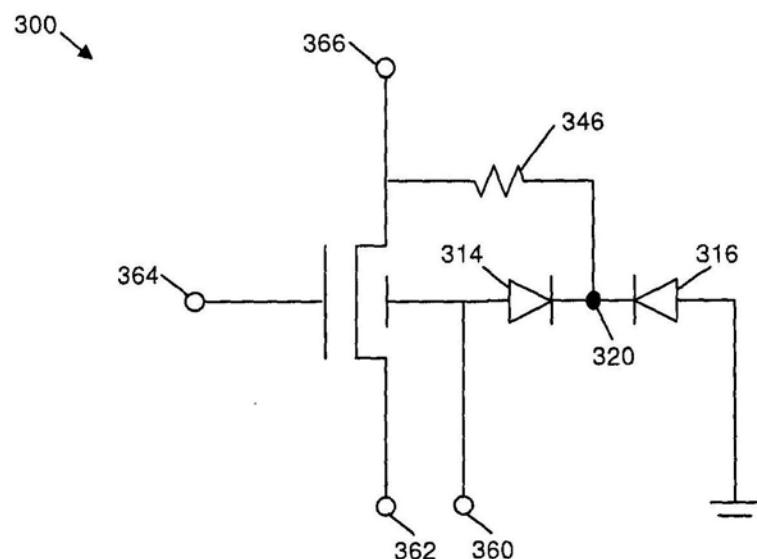

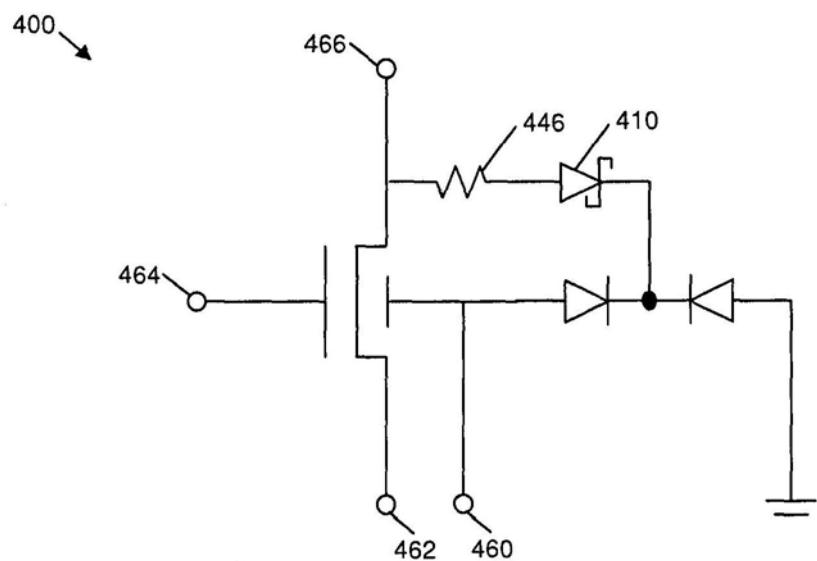

[0009] 图4根据替代实施例,是图2的N LDMOSFET的简化电路表征,带有包括与肖特基二极管串联的电阻网络的电阻器电路;

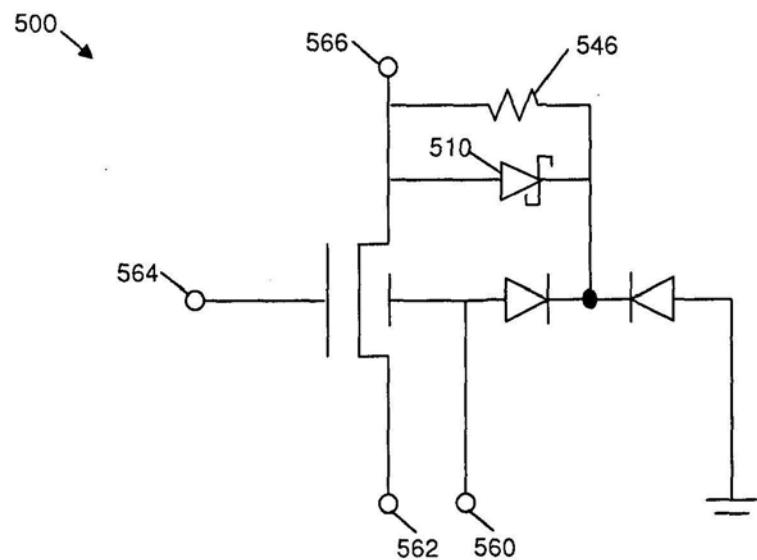

[0010] 图5根据另一替代实施例,是图2的N LDMOSFET的简化电路表征,带有包括与肖特基二极管并联的电阻网络的电阻器电路;

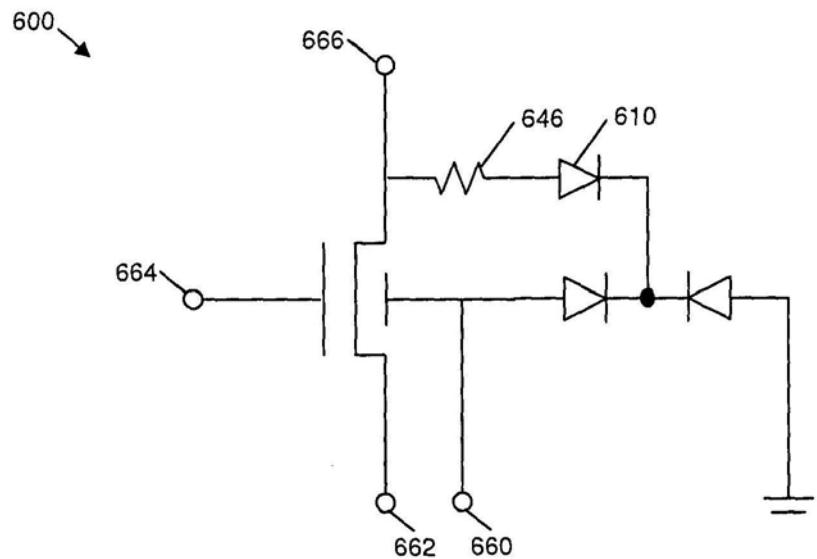

[0011] 图6根据另一替代实施例,是图2的NLDMOSFET的简化电路表征,带有包括与PN结二极管串联的电阻网络的电阻器电路;

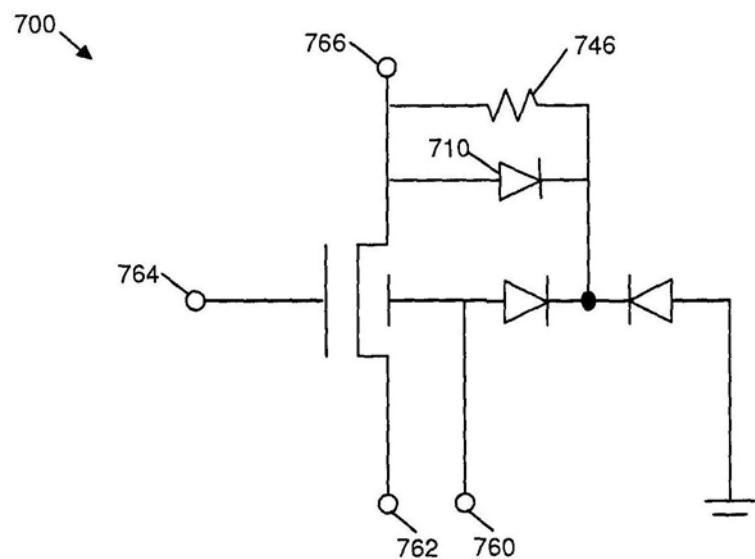

[0012] 图7根据另一替代实施例,是图2的NLDMOSFET的简化电路表征,带有包括与PN结二极管并联的电阻网络的电阻器电路;

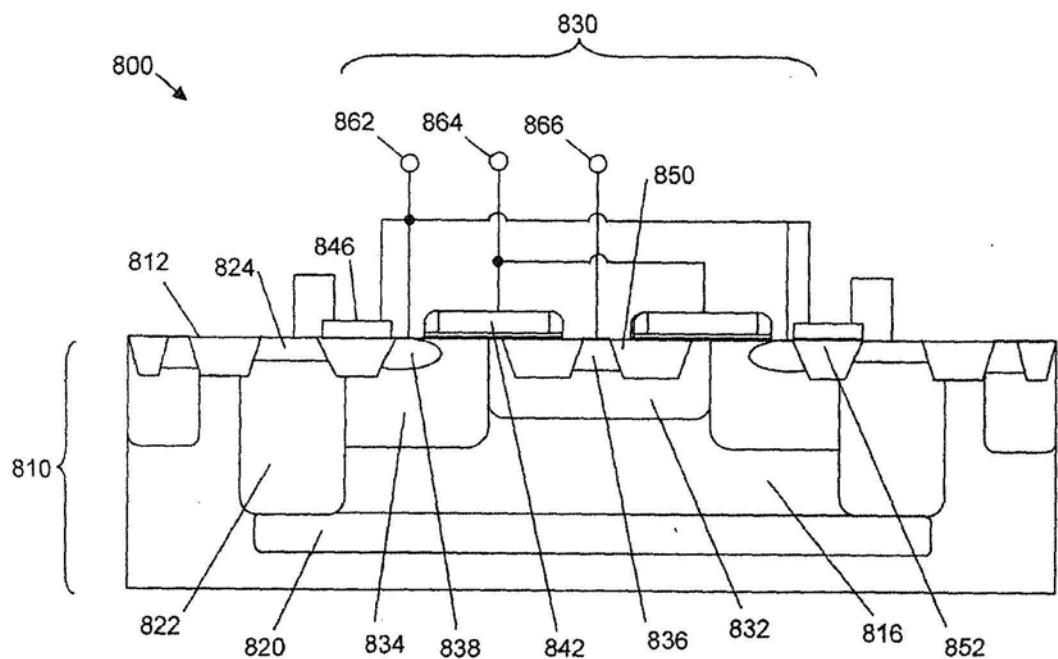

[0013] 图8根据实施例,是P型、横向扩散金属氧化物半导体场效应晶体管(PLDMOSFET)的截面图,带有连接在PLDMOSFET的源极区域和隔离结构之间的电阻器电路;

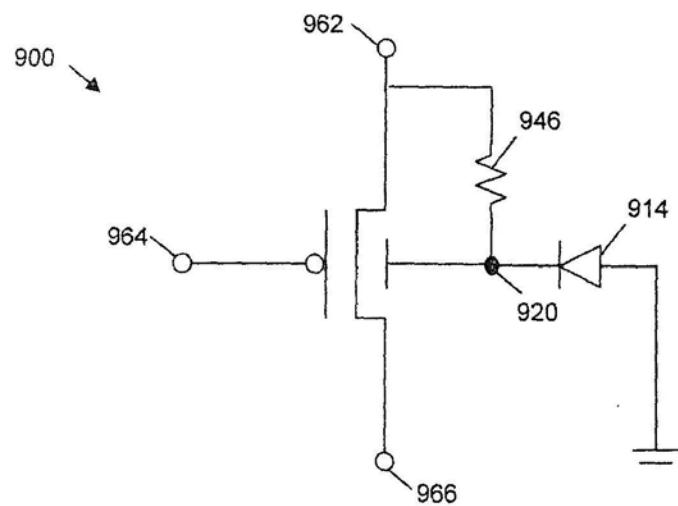

[0014] 图9根据实施例,是图8的PLDMOSFET的简化电路表征;

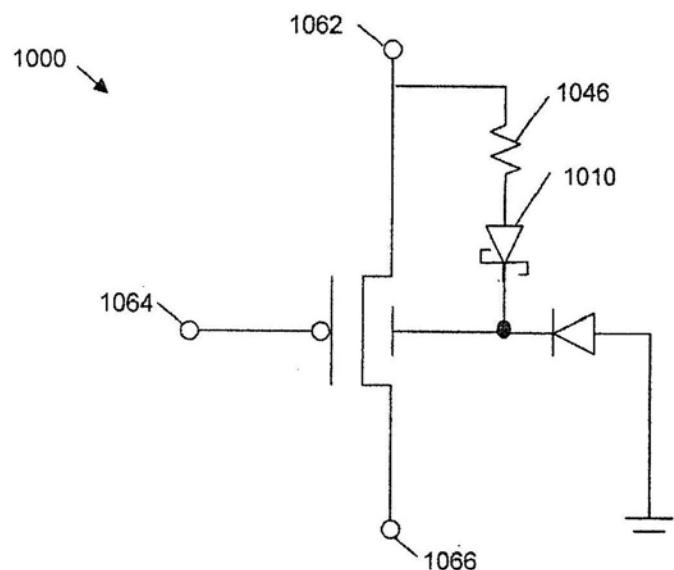

[0015] 图10根据替代实施例,是图8的PLDMOSFET的简化电路表征,带有包括与肖特基二极管串联的电阻网络的电阻器电路;

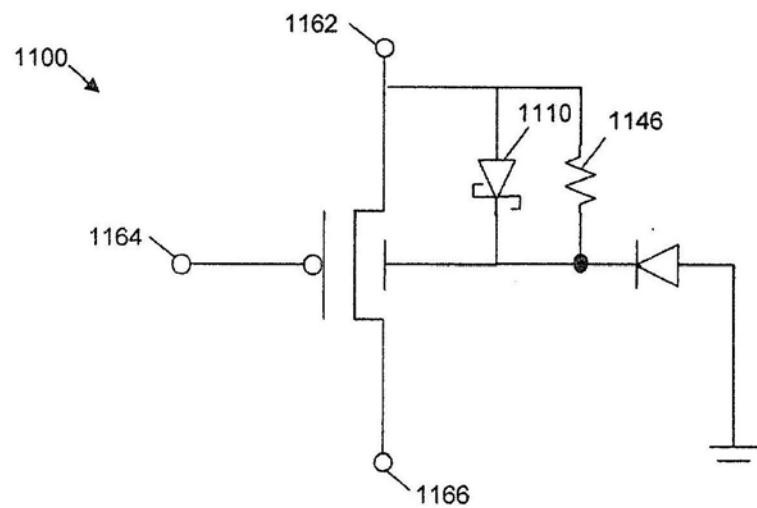

[0016] 图11根据另一替代实施例,是图8的PLDMOSFET的简化电路表征,带有包括与肖特

基二极管并联的电阻网络的电阻器电路；

[0017] 图12根据替代实施例，是图8的PLDMOSFET的简化电路表征，带有包括与PN结二极管串联的电阻网络的电阻器电路；

[0018] 图13根据另一替代实施例，是图8的PLDMOSFET的简化电路表征，带有包括与PN结二极管并联的电阻网络的电阻器电路；

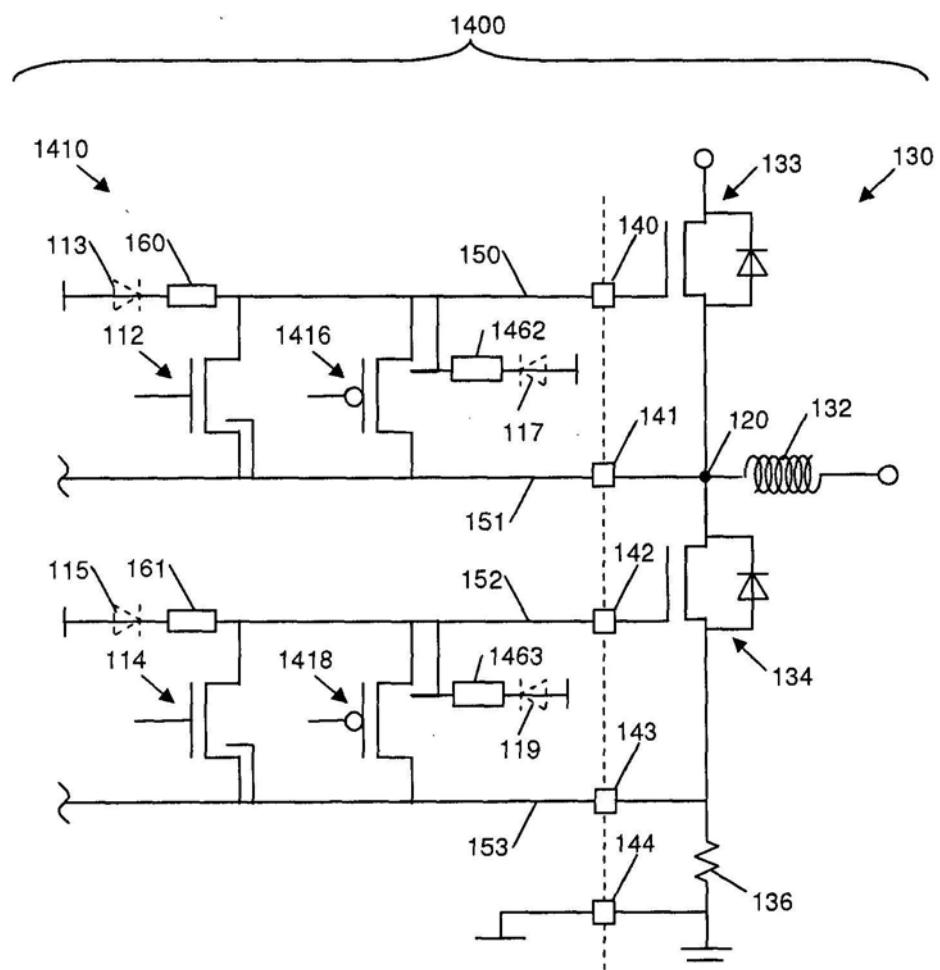

[0019] 图14根据替代实施例，是电子系统的简化图，其中该系统包括了被配置以驱动包括电感负载的外部电路的驱动电路；

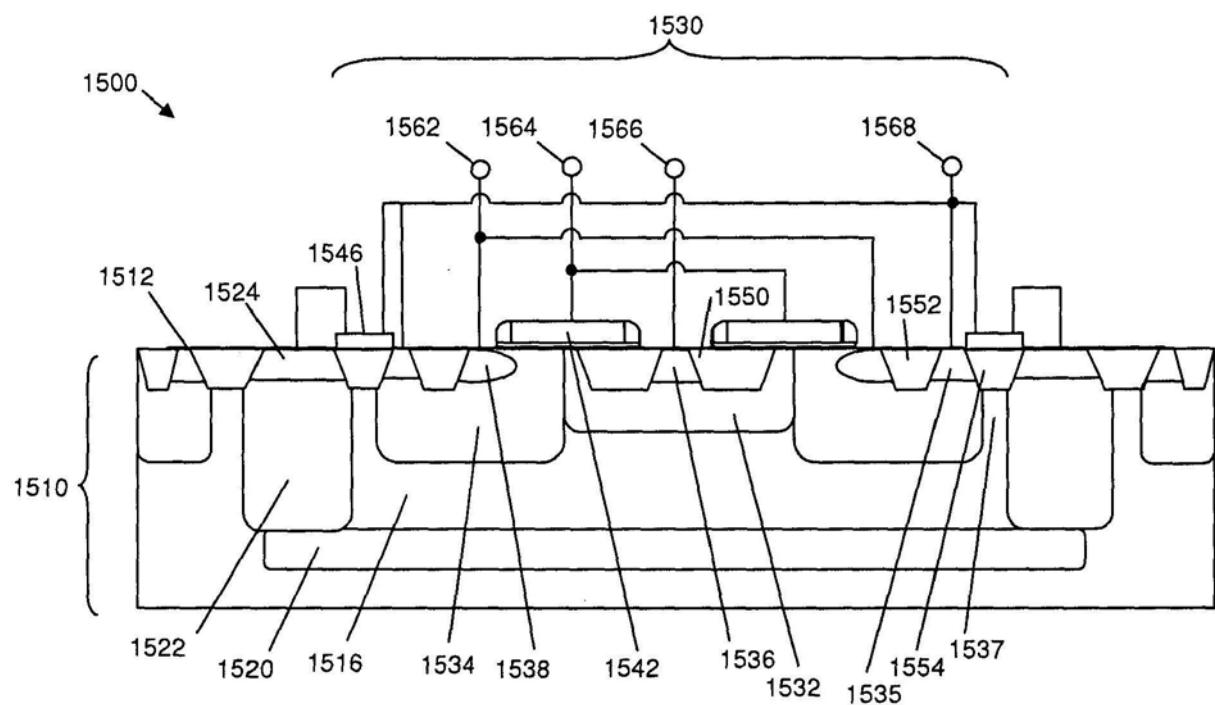

[0020] 图15根据替代实施例，是PLDMOSFET的截面图，带有被连接在PLDMOSFET的体区域和隔离结构之间的电阻器电路；

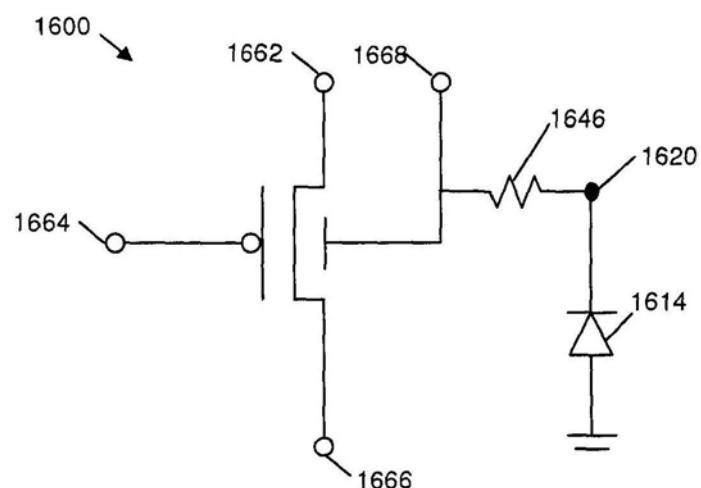

[0021] 图16根据实施例，是图15的PLDMOSFET的简化电路表征；

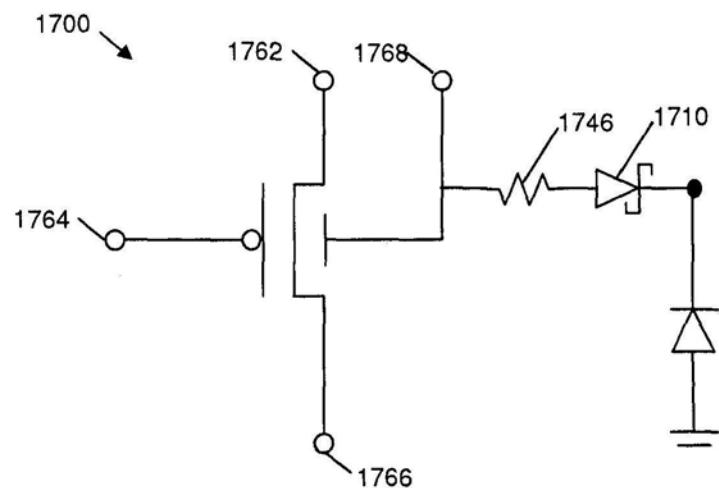

[0022] 图17根据替代实施例，是图15的PLDMOSFET的简化电路表征，带有包括与肖特基二极管串联的电阻网络的电阻器电路；

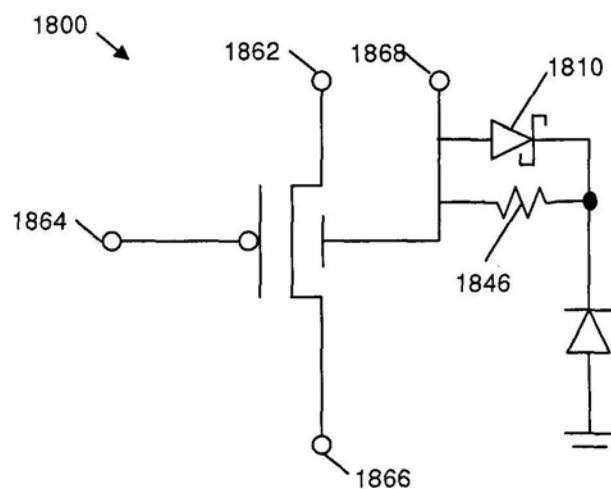

[0023] 图18根据另一替代实施例，是图15的PLDMOSFET的简化电路表征，带有包括与肖特基二极管并联的电阻网络的电阻器电路；

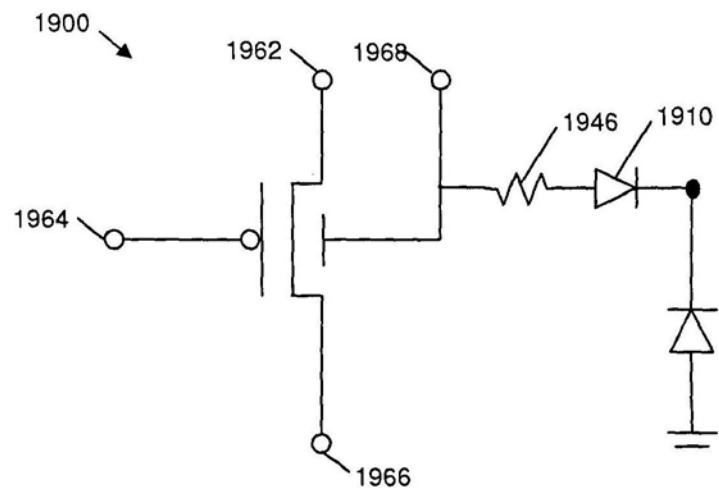

[0024] 图19根据替代实施例，是图15的PLDMOSFET的简化电路表征，带有包括与PN结二极管串联的电阻网络的电阻器电路；

[0025] 图20根据另一替代实施例，是图15的PLDMOSFET的简化电路表征，带有包括与PN结二极管并联的电阻网络的电阻器电路；

[0026] 图21根据各种实施例，是说明了一种形成图2、图8以及图15中所说明的器件的方法，并且将这些器件合并到带有电感负载的系统的简化流程图。

## 具体实施方式

[0027] 以下的详细说明在本质上仅仅是示例的，不旨在限定实施例或本申请以及各个实施例的使用。此外，也不旨在被先前技术领域、背景、或以下详细说明中的任何明示或暗示的理论所限定。

[0028] 为了简便以及清晰的说明，附图说明了构造的一般方式，并且众所周知的特征和技术的说明以及细节可以被忽略以避免不必要地模糊实施例的说明。此外，附图中的元素不一定按比例绘制。例如，附图中的一些元素或区域的尺寸相对于其它元素或区域可以被夸大以帮助提高对各个实施例的理解。

[0029] 说明书以及权利要求中的术语“第一”、“第二”、“第三”、“第四”等等，如果有的话，可以被用于区分相似元素而不一定用于描述特定顺序或时间顺序。应了解术语的这种用法在适当的情况下是可以互换的以便本申请所描述的实施例例如，能够以不是本申请所说明的顺序或不同于本申请所描述的其它方式被使用。此外，术语“包括”、“包含”、“有”或其的任何变化形式旨在涵盖非排他性包含，以便包括一列元素或步骤的过程、方法、物件、或设备不需要被限定于那些元素或步骤，而可以包括其它没有明确列出的或是这个过程、方法、物件、或设备固有的其它元素或步骤。说明书和权利要求中的术语“左边”、“右边”、“里面”、“外面”、“前面”、“后面”、“向上”、“向下”、“底部”、“顶部”、“之上”、“之下”、“上面”、“下面”等等，如果有的话，是被用于描述相对位置而不一定用于描述空间中的固定位置。应了解本申请所描述的实施例可以在其它情况下而不是本发明所说明的或以其它方式所描述的情

况下被使用。本发明所使用的术语“耦合”被定义为以一种电或非电方式直接或间接连接。

[0030] 本发明所描述的各种实施例是通过特定导电类型的半导体器件以及结构被说明的；该半导体器件以及结构有各种适合于导电器件或结构的P和N掺杂区域。但是这仅仅是为了便于解释而不旨在限定。本领域所属技术人员将了解相反导电类型的半导体器件以及结构可以通过互换导电类型被提供以便P型区域变为N型区域，反之亦然。或者，下面所说明的特定区域可以通常被称为是“第一导电类型”和“第二相反导电类型”，其中第一导电类型可以是N型或P型，那么第二相反导电类型可以是P型或N型等等。此外，为了便于解释而不旨在限定，本发明的各种实施例在本申请被针对硅半导体描述，但是本领域所属技术人员将了解本发明不被限定为硅，而是适用于多种半导体材料。非限定性例子是其它IV型半导体材料、III-V和II-VI型半导体材料、有机半导体材料以及它们的组合，而且，无论是块的形式、层的形式、薄膜形式、绝缘硅形式或它们的组合。这些材料可以是单晶或多晶或非晶质，或它们的组合。

[0031] 图1根据实施例，是包括被配置以驱动包括电感负载132的外部电路130的驱动电路110的电子系统100的简化图。系统100可以在一辆汽车或其它车辆内被实施，其中电感负载132表示电动机的部分，或车辆的其它电感分量。或者，系统100或其派生物可以被用于汽车或车辆应用以外的应用。

[0032] 根据实施例，驱动电路110是片上系统(SOC)的一部分，其中驱动器电路110和SOC的其它部分形成于单一半导体衬底(以下被称为“SOC衬底”)上。例如，SOC也可以包括各种处理组件、存储器阵列(例如，闪存阵列、静态随机存取存储器(SRAM)阵列、等等)、以及其它电路。简单起见，SOC的其它部分在图1中未进行说明。正如在下面将要更详细解释的，实施例涉及被配置以减小或消除来自电感负载132或其它来源的不期望的电流注入SOC衬底的系统和半导体组件。

[0033] 驱动电路110和SOC的其它部分至少通过“高边栅极”(HG)管脚140、“高边源极”(HS)管脚141、“低边栅极”(LG)管脚142、“低边源极”(LS)管脚143、以及接地管脚144耦合于外部电路130。虽然在本发明被称为“管脚(pin)”，管脚140-144可以包括管脚、引线、凸块、球、或其它类型的接触件的任意组合。在图1中，穿过管脚140-144的垂直虚线表示了SOC(包括驱动电路110)和外部电路130之间的划分。

[0034] 正如上面所提到的，在实施例中，外部电路130包括电感负载132。此外，外部电路130包括第一“高边”FET133、第二“低边”FET134、以及分流电阻器136。正如在下面将要更详细解释的，在某些情况下，电感负载132可以作为耦合于驱动电路110的注入电流源。正如图1所显示的，高边FET133和低边FET134各自包括体二极管。HS管脚141在节点120耦合于电感负载132的输入端子、高边FET133的源极、以及低边FET134的漏极。低边FET134的源极通过分流电阻器136耦合于LS管脚143和地面。高边FET133的栅极耦合于HG管脚140，并且高边FET133响应于通过HG管脚140从驱动电路110接收到的信号而被开启和关闭。低边FET134的栅极耦合于LG管脚142，并且低边FET134响应于通过LG管脚142从驱动电路110接收到的信号而被开启和关闭。

[0035] 根据实施例，沿着第一电流路径，驱动电路110包括至少一个第一N型LDMOS场效应晶体管(NLDMOSFET)112和至少一个P型LDMOS场效应晶体管(PLDMOSFET)116。节点150将NLDMOSFET112的漏极以及PLDMOSFET116的源极和体耦合于HG管脚140。节点151将

NLDMOSFET112的源极和体以及PLDMOSFET116的漏极耦合于HS管脚141。沿着第二电流路径，驱动电路110也可以包括第二NLDMOSFET114和第二PLDMOSFET118。节点152将NLDMOSFET114的漏极以及PLDMOSFET118的源极和体耦合于LG管脚142。节点153将NLDMOSFET114的源极和体以及PLDMOSFET118的漏极耦合于LS管脚143。SOC衬底通过接地管脚144被连接到系统接地。

[0036] 正如结合其它附图将要被详细描述的，PLDMOSFET116和118的有源区域分别可以形成于隔离结构或隔离“管桶”(例如，N型埋层和围绕有源区域的N型下沉区域)内。此外，NLDMOSFET112和114的有源区域分别可以类似地形成于隔离结构内。隔离结构被配置以将NLDMOSFET112和114的有源区域从SOC衬底的剩余部分中分开。隔离结构可以允许NLDMOSFET112和114以及PLDMOSFET116和118以体偏压进行操作。此外，在正常操作条件下，隔离结构可以有助于防止电流注入SOC衬底。例如，在图1中，二极管113和115表示与NLDMOSFET112和114相关联的埋层-衬底二极管，以及二极管117和119表示与PLDMOSFET116和118相关联的埋层-衬底二极管，其中二极管113、115、117、以及119允许管脚141-143被放置于正电位处而不短接至SOC衬底。

[0037] 在某些系统中，PLDMOSFET116和118的源极区域以及其相关联的隔离结构通过金属化被电短接以便源极区域和隔离结构总是处在相同电位。此外，在PLDMOSFET116和118中，体区域可以与衬底表面处的或衬底表面下的隔离结构合并，在这种情况下，隔离结构(或者更具体说是N型下沉区域)可以被认为是体结。源极区域和体区域通常被保持在高电位(例如，Vdd)，并且通过隔离结构短接源极，同时合并隔离结构和体区域使得位于体区域和N型埋层之间的衬底部分更好地将满反向偏压维持在最大Vdd处。类似地，NLDMOSFET112和114的漏极区域以及其相关联的隔离结构通过金属化被电短接以便漏极区域和隔离结构总是处在相同电位。这样的布置是有利的，因为在NLDMOSFET112和114内，位于漂移区域和每隔离结构埋层之间的衬底材料可以不能够将满反向偏压维持在来自漂移区域和埋层的最大Vdd处。

[0038] 虽然载流区域(例如，NLDMOSFET112和114的漏极区域，以及PLDMOSFET116和118的源极区域)到NLDMOSFET112和114的隔离结构以及到PLDMOSFET116和118的体的短接在很多操作条件下可以很好地工作，然而，在某些其它操作条件下，这种布置可以允许不期望的电流注入到SOC衬底。例如，在驱动电路110关闭高边FET133(例如，通过开启NLDMOSFET112)的那一刻，低边FET134也被关闭(例如，NLDMOSFET114导电)。在这种状态下，电感负载132内的电流可以将HS管脚141推到负，直到低边FET134的体二极管被正向偏置。驱动器电路110可以被控制以开启低边FET134，以在一段时间之后降低低边FET134的功耗。然后，节点120和HS管脚141(从而在NLDMOSFET112的源极和体)处的负电位被电感负载电流乘以分流电阻器136的电阻和低边FET134的RDSON总和定义。在LS管脚143(以及NLDMOSFET114的源极和体)处，较小的负电位被电感负载电流乘以分流电阻器136的电阻定义。在高边FET133被关闭之后的一段时间，NLDMOSFET112和114有正栅极-源极电压(Vgs)，因此引起漏极与NLDMOSFET112和114的源极短接。在NLDMOSFET112和114的漏极电极以及隔离结构仅仅是短接的系统中，HS管脚141和LS管脚143处的负电位可以然后通过NLDMOSFET112和114的导电通道接近节点150、152以及SOC衬底内的至少两个注入点(N型区域)。因为HS管脚141处的负电位大于LS管脚143处的负电位，作为HS管脚141处的负电位的结果的电流注入电位是比作

为LS管脚143上的负电位的结果的电流注入电位大的问题。为了在一段延长的时间避免在低边FET134的体二极管内的高功耗,低边FET134在关闭高边FET133不久之后被开启(即,通过关闭NLDMOSFET114)。然而,节点120处的电位(因此HS管脚141)将仍然为负,并且电流注入问题可以仍然存在,虽然在一个较小的程度。

[0039] 根据各种实施例,驱动电路110包括被配置以减小或消除在上述所描述的或其它操作条件下电流注入SOC衬底的另一(further)电路。更具体地,在实施例中,驱动电路110包括耦合于NLDMOSFET112的漏极区域和隔离结构之间的第一电阻器电路160、耦合于NLDMOSFET114的漏极区域和隔离结构之间的第二电阻器电路161、耦合于PLDMOSFET116的源极区域和隔离结构之间的第三电阻器电路162、以及耦合于PLDMOSFET118的源极区域和隔离结构之间的第四电阻器电路163。通过将电阻器电路160-163插入到这些位置,注入电流可以被减小。更具体地,注射点移动到电阻器电路160-163的后面,从而显著地限制了在HS管脚141和/或LS管脚143处的给定电位可以被注入到SOC衬底的电流。虽然未在图1中被说明,驱动电路110包括可以包括附加的NLDMOSFET和/或PLDMOSFET器件,这些器件也包括耦合于其漏极区域或源极区域和隔离结构之间的电阻器电路,以便减小或消除电流注入SOC衬底。

[0040] 正如本申请所使用的,“电阻器电路”是包括一个或多个电阻器或电阻网络的电路。当本申请提及“电阻网络”的时候,应了解该术语可以包括单一电阻器或串联或并联的电阻器布置。正如在下面将要更详细解释的,本申请所讨论的“电阻器电路”实施例包括至少一个电阻网络,并且也可以包括或多个其它组件(例如,一个或多个二极管或与电阻器电路的电阻网络串联和/或并联在一起的其它组件)。正如结合剩余的附图在下面将要更详细描述的,虽然形成了电阻器电路的一部分的电阻器可以由多晶硅形成,应了解电阻器也可以由其它材料形成。“二极管”可以包括单一二极管或多个串联或并联互连的二极管。在各种实施例中,二极管可以由肖特基接触和掺杂半导体区域、PN结、多晶硅二极管、以及这些或其它二极管组件的组合形成。

[0041] NLDMOSFET(例如,NLDMOSFET112)、PLDMOSFET(例如,PLDMOSFET116)以及相关联电阻器电路(例如,电阻器电路160和162)的实施例在下面被详细描述。更具体地,图2-图7讨论了NLDMOSFET和相关联电阻器电路的各种实施例,以及图8-图13讨论了PLDMOSFET和相关联电阻器电路的各种实施例。应了解NLDMOSFET和PLDMOSFET的各种实施例可以被合并到系统中,例如系统100。

[0042] 图2是NLDMOSFET200(例如,图1的NLDMOSFET112)的截面图,带有耦合于NLDMOSFET200的漏极区域和隔离结构之间的电阻器电路(例如,图1的电阻器电路160)。根据实施例,NLDMOSFET200(以及稍后讨论的图8的PLDMOSFET800)的各个区域有在与图2中所说明的截面垂直的平面内定向的环形配置。虽然本发明的附图和描述特别适用于双栅指配置,本发明主题范围并不限定于这样的配置。根据本发明的描述,本领域所属技术人员将了解如何修改所说明的和所描述的实施例以应用包括多个(即,>2)栅指的应用配置,其中相邻的栅指可以共享位于一边上的漏极(例如,漏极区域236)和位于另一边上的体接触区域(例如,体接触区域240)。在这样的实施例中,体接触区域可以比附图中所描述的从下沉区域(sinker region)(例如,下沉区域222)横向分开更多。

[0043] NLDMOSFET200形成于有顶衬底表面212的半导体衬底210(例如,结合图1所讨论的

SOC衬底)上和内。根据实施例,NLDMOSFET200包括隔离结构,其实质上围绕与NLDMOSFET200的有源区域230(即,在有源器件形成于其内的衬底210内的区域)相关联的衬底的部分216。换句话说,有源器件可以被认为包含在隔离结构中。隔离结构是箱式结构,由N型埋层(NBL)220(位于顶衬底表面212下面的深度)和从顶衬底表面212延伸到NBL220的深度的N型下沉区域222形成。下沉区域222可以通过使用单一注入过程被形成;该过程有足以使得下沉区域222延伸到NBL220的注入能量,或下沉区域222可以通过使用有不同注入能量的多个注入过程被形成,从而在不同深度形成了一系列互连下沉子区域。

[0044] NLDMOSFET200还包括形成于有源区域230内的有源器件。根据实施例,有源器件包括N型漂移区域232、P型体区域234、N型漏极区域236、N型源极区域238、P型体接触区域240(也被称为“体结”)、以及栅极电极242(以及相应的没有编号的栅极介电质)。漏极区域236和源极区域238可以在本发明被称为“载流区域”以将这些区域和不是载流区域的NLDMOSFET200的栅极区分开。关于漏极区域236和源极区域238的术语“载流区域”的使用不意味着暗示NLDMOSFET200的其它区域没有载流。漂移区域232形成于有源区域230的中心部分内,并且从顶衬底表面212延伸到衬底210内小于NBL220的深度的深度。漏极区域236形成于漂移区域232内,并且比漂移区域232重掺杂。漏极区域236从顶衬底表面212延伸到衬底210显著地小于漂移区域232的深度的深度。体区域234形成于漂移区域232和下沉区域222之间,并且从顶衬底表面212延伸到衬底210内小于NBL220的深度的深度,并且可以小于漂移区域232的深度(虽然体区域234也可以延伸到实质上等于或大于漂移区域232的深度的深度)。在实施例中,正如图2中所显示的,体区域234相邻于漂移区域232并且与下沉区域222横向分离。在替代实施例中,体区域234可以与漂移区域232横向分离,或体区域234可以重叠于漂移区域232(生成带有与沟道或漂移区域232内的掺杂分布不同的掺杂分布的区域)。源极区域238和体接触区域240形成于体区域234内,各自从顶衬底表面212延伸到衬底210显著地小于体区域234的深度的深度。源极区域238是与体区域234相反的导电类型,并且可以比漂移区域232更加重掺杂,以及体接触区域240比体区域234更加重掺杂。导电互连将体接触区域240电耦合于体接触端子260,以及附加导电互连将源极区域238电耦合于源极端子262。栅极电极242形成于通常位于漏极区域236和源极区域238之间的顶衬底表面212上的栅氧化物上。导电互连将栅极电极242电耦合于栅极端子264。

[0045] 根据实施例,NLDMOSFET200可以还包括正如图2所显示的各种浅沟槽隔离(STI)结构250、252、254。例如,在顶衬底表面212,STI250在漂移区域232内相邻于漏极区域236,STI252被放置于源极区域238和体接触区域240之间,以及STI254被放置于体接触区域240和隔离结构(或者更具体地,下沉区域222)之间。在替代实施例中,某些或所有STI结构250、252、和/或254可以被排除在外。例如,STI252可以被排除在外,以及源极区域238和体接触区域240可以被短接在一起。此外,STI250可以被排除在外,将NLDMOSFET200做成“有源漂移器件”,而不是图2中所说明的“场漂移器件”。STI250的包含允许高栅极-漏极电位,同时降低了栅氧化物破裂的风险。在另一替代实施例中,某些或所有STI结构可以被替代为防止硅化物在表面形成的硅化物阻挡层,否则会将各个区域短接在一起。

[0046] 根据实施例,NLDMOSFET200还包括被连接在漏极区域236和延伸到下沉区域222内的N型区域224之间的电阻器电路(例如,图1的电阻器电路161),其中N型区域224比下沉区域222更加重掺杂以给下沉区域222提供欧姆接触。例如,电阻器电路可以包括带有一个或

多个电阻器246的电阻网络。虽然只有电阻器246在图2中被显示,应了解电阻网络可以包括多个电阻器。电阻网络的电阻器246可以由多晶硅形成,并且可以位于衬底顶面的一个或多个隔离区域上(例如,位于STI254上)。或者,一个或多个电阻器246可以由其它材料形成和/或位于其它地方。根据实施例,导电互连电耦合漏极区域236、电阻网络的第一端子(例如,电阻网络246的第一端子)、以及漏极端子266。另一导电互连将电阻网络的第二端子(例如,电阻网络246的第二端子)电耦合于隔离结构(例如,N型区域224)。在实施例中,电阻网络有在约10-约500欧姆范围内的电阻,虽然更小或更大的电阻也可以被实现。

[0047] 图3根据实施例,是图2的NLDMOSFET200的简化电路表征300。还参照图2,端子360(例如,端子260)耦合于P型体区域(例如,通过体接触区域240耦合于体区域234)、端子362(例如,端子262)耦合于N型源极区域(例如,源极区域238)、端子364(例如,端子264)耦合于栅极电极(例如,栅极电极242)、以及端子366(例如,端子266)耦合于漏极区域(例如,漏极区域236)。

[0048] 根据实施例,以及正如上面所讨论的,NLDMOSFET还包括电耦合于漏极区域(例如,漏极区域236)和器件的隔离结构之间的电阻网络346。虽然单一电阻器被用于描述图3(以及在附图中描述的其它电路表征中)中的电阻网络346,应了解这仅仅是为了方便,并且正如先前所讨论的,电阻网络可以包括多个电阻器。在实施例中,电阻网络346的第一端子耦合于漏极区域,以及电阻网络346的第二端子耦合于隔离结构(例如,下沉区域222和NBL220的组合)。在节点320处,二极管314表示了由隔离结构和器件有源区域内的部分衬底(例如,隔离结构内的衬底210的部分216)之间的界面形成的二极管,以及二极管316表示了由隔离结构和隔离结构之外的剩余衬底之间的界面形成的二极管。

[0049] 在漏极电位被升高的正常工作期间,隔离结构电位紧密地跟随漏极区域电位,其中电阻网络346两端的电压降取决于流经隔离结构的电流量。另一方面,当漏极电位转换到负电压的时候,隔离结构电位被电阻网络346两端的电压降保持。当漏极电位变为负的时候,通过保持隔离结构电位,如果漏极和隔离结构仅仅是短接则可以会发生的注入到衬底的载流子可以被减少或消除,从而避免了相邻电路块的中断。

[0050] 根据另一实施例,电阻器电路(例如,图1的电阻器电路160)可以包括与肖特基二极管串联的电阻网络。例如,图4根据替代实施例,是图2的NLDMOSFET200的简化电路表征400,带有包括与肖特基二极管410串联的电阻网络446的电阻器电路。与图3的实施例相类似,端子460(例如,端子260)耦合于P型体区域(例如,通过体接触区域240耦合于体区域234)、端子462(例如,端子262)耦合于N型源极区域(例如,源极区域238)、端子464(例如,端子264)耦合于栅极电极(例如,栅极电极242)、以及端子466(例如,端子266)耦合于漏极区域(例如,漏极区域236)。

[0051] 肖特基二极管410和电阻网络446串联电耦合于漏极区域(例如,漏极区域236)和器件的隔离结构之间。肖特基二极管410例如可以由与隔离结构(例如,下沉区域222)接触的肖特基接触(未示出)形成。更具体地,在实施例中,肖特基二极管可以由位于肖特基接触(例如,用硅化物在顶衬底表面上形成)和下沉区域222的顶面之间的金属-半导体结形成。在替代实施例中,肖特基接触可以形成于不与顶衬底表面212共面的侧壁或其它表面上。

[0052] 在操作期间,当漏极电位转换到负电压的时候,隔离结构电位被与肖特基二极管410的反向击穿电压串联的电阻网络446两端的电压降保持。例如,还参照图1,在正常操作

情况下的高边被关闭期间, NLD MOSFET的漏极的电压(例如, 图1的HS管脚141处的电压)可以在约-0.3伏-约-6.0伏(或某些其它正常工作值)之间负性地变动。根据各个实施例, 电阻器电路(例如, 图1的电阻器电路160-163)可以包括带有小于、大于、或等于最低正常负操作电压的击穿电压的二极管, 取决于应用, 以便二极管仅仅在漏极上出现过度负电压时击穿(例如, 肖特基二极管410的反向击穿电压可以位于-0.3伏-约-14.0伏之间, 虽然更小或更大的击穿电压也可以被实现)。肖特基二极管410和电阻网络446的组合可以允许更灵活地建造肖特基二极管410。此外, 在选择电阻网络446的值以实现保持NLD MOSFET的完整性的最佳整体结果时, 静电放电(ESD)的稳健性可以被实现, 同时降低了衬底注入。更具体地, 例如, 在肖特基二极管410碰上击穿(例如, 在ESD应力期间)的条件下, 流过肖特基二极管410的电流被电阻网络446限定到其容量程度, 从而降低了ESD事件可以损坏肖特基二极管410的可能性。

[0053] 根据另一实施例, 电阻器电路(例如, 图1的电阻器电路160)可以包括与肖特基二极管并联的电阻网络。例如, 图5根据替代实施例, 是图2的NLD MOSFET200的简化电路表征500, 带有包括与肖特基二极管510并联的电阻网络546的电阻器电路。与图2的实施例相类似, 端子560(例如, 端子260)耦合于P型体区域(例如, 通过体接触区域240耦合于体区域234)、端子562(例如, 端子262)耦合于N型源极区域(例如, 源极区域238)、端子564(例如, 端子264)耦合于栅极电极(例如, 栅极电极242)、以及端子566(例如, 端子266)耦合于漏极区域(例如, 漏极区域236)。

[0054] 肖特基二极管510(例如, 肖特基接触(未示出)和下沉区域222之间的界面)和电阻网络546并联电耦合于漏极区域(例如, 漏极区域236)和器件的隔离结构之间。在操作期间, 当漏极电位转换到负电压的时候, 隔离结构电位被与肖特基二极管510的反向击穿电压并联的电阻网络546两端的电压降保持。如同结合图4所讨论的电阻器电路, 肖特基二极管510和电阻网络546的组合可以允许更灵活地建造肖特基二极管510。此外, 在某些条件下, 电阻网络546可以运行以保持隔离结构电位更接近NLD MOSFET的漏极电位。例如, 当漏极电位降低的时候(虽然仍是正的), 隔离结构电位仅仅被肖特基二极管510的电容拉下来, 这可能够也可能不够。在这样一种情况下, 电阻网络546可以有助于隔离结构电位朝着漏极电位放电。当漏极电位转换到负的时候, 虽然某些少数载流子注入可以被添加, 但是电阻网络546可以限制载流子注入的量。

[0055] 在结合图4和图5所讨论的实施例中, 电阻器电路(例如, 图1的电阻器电路160)包括与肖特基二极管串联(图4)或并联(图5)的电阻网络(例如, 电阻网络446、546)。在另一替代实施例中, 电阻器电路可以包括肖特基二极管以及与肖特基二极管串联的第一电阻网络以及与肖特基二极管并联的第二电阻网络, 以实现可以被串联耦合和并联耦合电阻网络布置二者提供的优势。

[0056] 在结合图4和图5所讨论的实施例中, 耦合NLD MOSFET(例如, 图1的NLD MOSFET112)的实施例的漏极区域和隔离结构的电阻器电路(例如, 图1的电阻器电路160)包括肖特基二极管。根据另一实施例, 电阻器电路(例如, 图1的电阻器电路160)包括电阻网络和连接在漏极区域(例如, 图2的漏极区域236)和隔离结构之间的PN结二极管(未示出)。例如, 还参照图2, 不是包括N型区域224, NLD MOSFET200也可以包括延伸到下沉区域222的P型区域(未示出)。位于P型区域和下沉区域222之间的PN结形成了可以在电阻器电路中是互连的PN结二

极管。PN结二极管可以被设计以提供期望的依赖于应用的击穿电压(例如,大于、小于或等于正常的、最负的操作电压的击穿电压)。例如,在实施例中,PN结二极管可以被设计以提供在约-0.3伏-约-14.0伏范围内的反向击穿电压,虽然更小或更大的击穿电压也可以被实现。

[0057] 根据另一实施例,电阻器电路(例如,图1的电阻器电路160)可以包括电阻网络和连接在漏极区域(例如,图2的漏极区域236)和隔离结构之间的多晶硅二极管(未示出)。例如,多晶硅二极管可以由被定义了多晶硅二极管的击穿电压的中性间隔区域间隔开的P型区域和N型区域形成。多晶硅二极管可以形成于衬底顶面上的绝缘区域上(例如,在STI254上)。或者,多晶硅二极管可以由其它材料形成和/或位于其它地方。在实施例中,多晶硅二极管可以被设计以提供期望的依赖于应用的、大于、小于或等于正常的、最负的操作电压的击穿电压(例如,在约-0.3伏-约-14.0伏范围内的击穿电压,虽然更小或更大的击穿电压也可以被实现)。

[0058] 例如,图6根据一个替代实施例,是图2的NLDMOSFET200的简化电路表征600,带有包括与PN结二极管610(例如,由位于P型区域和下沉区域222之间的PN结形成的PN结二极管,或多晶硅二极管)串联的电阻网络646的电阻器电路。与图2的实施例相类似,端子660(例如,端子260)耦合于P型体区域(例如,通过体接触区域240耦合于体区域234)、端子662(例如,端子262)耦合于N型源极区域(例如,源极区域238)、端子664(例如,端子264)耦合于栅极电极(例如,栅极电极242)、以及端子666(例如,端子266)耦合于漏极区域(例如,漏极区域236)。

[0059] 电阻网络646和PN结二极管610串联电耦合于漏极区域(例如,漏极区域236)和器件的隔离结构之间。在操作期间,当漏极电位转换到负电压的时候,隔离结构电位被与PN结二极管610的反向击穿电压串联的电阻网络646两端的电压降保持。如同结合图4先前所讨论的实施例,PN结二极管610和电阻网络646的组合可以提供某些有利效用。

[0060] 根据另一实施例,电阻器电路(例如,图1的电阻器电路160)可以包括与PN结二极管并联的电阻网络。例如,图7根据替代实施例,是图2的NLDMOSFET200的简化电路表征700,带有包括与PN结二极管710并联的电阻网络746的电阻器电路。与图2的实施例相类似,端子760(例如,端子260)耦合于P型体区域(例如,通过体接触区域240耦合于体区域234)、端子762(例如,端子262)耦合于N型源极区域(例如,源极区域238)、端子764(例如,端子264)耦合于栅极电极(例如,栅极电极242)、以及端子766(例如,端子266)耦合于漏极区域(例如,漏极区域236)。

[0061] 电阻网络746和PN结二极管710并联电耦合于漏极区域(例如,漏极区域236)和器件的隔离结构之间。在操作期间,当漏极电位转换到负电压的时候,隔离结构电位被与PN结二极管710的反向击穿电压并联的电阻网络746两端的电压降保持。如同结合图5先前所讨论的实施例,PN结二极管710和电阻网络746的组合可以提供某些有利效用。

[0062] 在结合图6和图7所讨论的实施例中,电阻器电路(例如,图1的电阻器电路160)包括PN结二极管(例如,PN结二极管610、710)和与PN结二极管串联耦合的电阻网络(电阻网络646)或与PN结二极管并联耦合的电阻网络(电阻网络746)。在另一替代实施例中,电阻器电路可以包括PN结二极管以及与PN结二极管串联耦合的第一电阻网络和与PN结二极管并联耦合的第二电阻网络,以实现可以由串联耦合和并联耦合电阻网络布置二者提供的优势。

[0063] 在结合图4-图7所讨论的实施例中,例如,根据实施例,耦合NLDMOSFET的实施例(例如,图1的NLDMOSFET112)的漏极区域和隔离结构的电阻器电路(例如,图1的电阻器电路160)包括肖特基二极管或PN结二极管。根据其它实施例,替代地,耦合NLDMOSFET的实施例的漏极区域和隔离结构的电阻器电路可以包括一个或多个肖特基二极管和一个或多个PN结二极管的组合。例如,NLDMOSFET的实施例可以包括肖特基二极管和一个或多个并联连接在漏极区域和隔离结构之间的PN结二极管的组合。更具体地,电阻器电路可以包括由位于肖特基接触和隔离结构(例如,下沉区域222)之间的金属-半导体结形成的肖特基二极管,连同一个或多个P型区域,分别延伸到下沉区域并且部分穿过下沉区域。肖特基接触被连接到电阻网络(即,肖特基二极管的阳极被连接到电阻网络),以及位于P型区域和下沉区域之间的PN结形成了电阻器电路的PN结二极管。根据实施例,将PN结二极管放置于肖特基二极管旁边允许了PN结耗尽肖特基二极管下面的硅,从而降低了肖特基二极管内的反向偏置泄漏。肖特基二极管和PN结二极管可以被设计以提供期望的依赖于应用的击穿电压(例如,大于、小于或等于正常的、最负的操作电压的击穿电压)。例如,在实施例中,肖特基二极管和PN结二极管均可以被设计以提供在约-0.3伏-约-14.0伏范围内的反向击穿电压,虽然更小或更大的击穿电压也可以被实现。

[0064] 在上面所描述的实施例中,NLDMOSFET(例如,图1-图2的NLDMOSFET112、200)的漏极区域和隔离结构通过电阻器电路电耦合。在其它实施例中,PLDMOSFET(例如,图1的PLDMOSFET116)的源极区域和隔离结构通过电阻器电路电耦合。例如,图8根据实施例,是PLDMOSFET800(例如,图1的PLDMOSFET116)的截面图,带有耦合于PLDMOSFET的源极区域和隔离结构之间的电阻器电路(例如,图2的电阻器电路162)。根据实施例,PLDMOSFET800的各个区域有在与图8中所说明的截面垂直的平面内定向的环形配置。再一次,虽然本申请的附图和描述特别适用于双栅指配置,本发明主题范围并不限于这样的配置。根据本发明的描述,本领域所属技术人员将了解如何修改所说明的和所描述的实施例以应用包括多个(即,>2)栅指的应用配置,其中相邻的栅指可以共享漏极(例如,漏极区域836)。

[0065] PLDMOSFET800形成于有顶衬底表面812的P型半导体衬底810(例如,结合图1所讨论的SOC衬底)上和内。根据实施例,PLDMOSFET800包括隔离结构,其实质上围绕与PLDMOSFET800的有源区域830(即,在有源器件形成于其内的衬底810内的区域)相关联的衬底的部分816。换句话说,有源器件可以被认为包含在隔离结构中。隔离结构是箱式结构,由N型埋层(NBL)820(位于顶衬底表面812下面的深度)和从顶衬底表面812延伸到NBL820的深度的N型下沉区域822形成。下沉区域822可以通过使用单一注入过程被形成;该过程有足够的注入能量,或下沉区域822可以通过使用有不同注入能量的多个注入过程被形成,从而在不同深度形成了一系列互连下沉子区域。

[0066] PLDMOSFET800还包括形成于有源区域830内的有源器件。根据实施例,有源器件包括P型漂移区域832、N型体区域834、P型漏极区域836、P型源极区域838、以及栅极电极842(以及相应的没有编号的栅极介电质)。漂移区域832形成于有源区域830的中心部分内,并且从顶衬底表面812延伸到衬底810的小于NBL820的深度的深度。漏极区域836形成于漂移区域832内,并且比漂移区域832重掺杂。漏极区域836从顶衬底表面812延伸到衬底810显著地小于漂移区域832的深度的深度。导电互连将漏极区域836电耦合于漏极端子866。

[0067] 体区域834形成于漂移区域832和下沉区域822之间,并且从顶衬底表面812延伸到

衬底810内小于NBL820的深度的深度,并且该深度可以大于漂移区域832的深度(虽然体区域834也可以延伸到小于或实质上等于漂移区域832的深度的深度)。在实施例中,体区域834相邻于漂移区域832。此外,在实施例中,正如图8中所显示的,体区域834与下沉区域822合并。因此,隔离结构(或更具体地说,下沉区域822)可以被认为是体结。在替代实施例中,体区域834可以与漂移区域832和/或下沉区域822横向分离(例如,正如在图15的实施例中的),或体区域834可以重叠于漂移区域832和/或下沉区域822(生成带有与沟道或漂移区域832和/或下沉区域822内的掺杂分布不同的掺杂分布的区域)。源极区域838形成于体区域834内,从顶衬底表面812延伸到衬底810内显著地小于体区域834的深度的深度。源极区域838比漂移区域832更加重掺杂。栅极电极842形成于通常位于漏极区域836和源极区域838之间的顶衬底表面812上的栅氧化物上。导电互连也将栅极电极842电耦合于栅极端子864。

[0068] 根据实施例,PLDMOSFET800可以还包括正如图8所显示的各种STI结构850、852。例如,在顶衬底表面812,STI850相邻于漂移区域832内的漏极区域836,以及STI852位于源极区域838和隔离结构(或更具体地说,下沉区域822)之间。在替代实施例中,STI结构850和852的其中或两者可以被短接在一起。此外,STI850可以被排除在外,将PLDMOSFET800做成“有源漂移器件”,而不是图8中所说明的“场漂移器件”。STI250的包含允许高栅极-漏极电位,同时降低了栅氧化物破裂的风险。在另一替代实施例中,某些或所有STI结构可以被替代为硅化物阻挡层。

[0069] 根据实施例,PLDMOSFET800还包括被连接在源极区域838和延伸到下沉区域822内的N型区域824之间的电阻器电路(例如,图1的电阻器电路162),其中N型区域824比下沉区域822更加重掺杂以给下沉区域822提供欧姆接触。例如,电阻器电路可以包括带有一个或多个电阻器846的电阻网络。虽然只有电阻器846在图8中被显示,应了解电阻网络可以包括多个电阻器。电阻网络的电阻器846可以由多晶硅形成,并且可以位于衬底顶面的一个或多个隔离区域上(例如,位于STI852上)。或者,一个或多个电阻器846可以由其它材料形成和/或位于其它地方。根据实施例,导电互连电耦合源极区域838、电阻网络的第一端子(例如,电阻网络846的第一端子)、以及源极端子862。另一导电互连将电阻网络的第二端子(例如,电阻网络846的第二端子)电耦合于隔离结构(例如,N型区域824)。在实施例中,电阻网络有在约10-约500欧姆范围内的电阻,虽然更小或更大的电阻也可以被实现。

[0070] 正如上面所提到的,根据替代实施例,体区域(例如,图15的体区域1534)可以横向分离于下沉区域(例如,图15的下沉区域1522)以便P型间隙存在于体区域和下沉区域之间(例如,正如稍后在图15的实施例中讨论的)。此外,STI结构(例如,图15的STI结构1554)或硅化物阻挡层可以在衬底表面被包括以确保区域之间的隔离。P型间隙可以由隔离结构(将向位于体区域和下沉区域之间的顶衬底表面延伸)内的P型衬底(例如,图15的衬底1510的部分1516)的部分(例如,部分1537)形成,或由从顶衬底表面延伸并且位于体区域和下沉区域之间的P型阱区域形成。在这样的实施例中,PLDMOSFET(例如,图15的PLDMOSFET1500)还可以包括形成于体区域(例如,位于源极区域和下沉区域之间,其中体接触区域可以通过STI结构或硅化物阻挡层从源极区域分开)内的N型体接触区域(例如,图15的体接触区域1535)。体接触区域和源极区域(例如,图15的源极区域1538)可以通过导电互连电耦合(短接),以及电阻器电路(例如,图14的电阻器电路1462)可以耦合于隔离结构(例如,图15的下沉区域1522)和短接的源极区域以及体区域之间。在正常操作期间,在体区域、源极区域以

及隔离结构都在高电位时,隔离结构和体区域可以通过其间的P型间隙的横向耗尽(例如,在其间的击穿之前可以被完全耗尽),或通过位于体区域和NBL(例如,图15的NBL1520)之间的P型衬底的部分的垂直耗尽被有效地短接,无论哪种情形先发生。

[0071] 图9根据实施例,是图8的PLDMOSFET800的简化电路表征900。还参照图8,端子962(例如,端子862)耦合于源极区域(例如,源极区域838)、端子964(例如,端子864)耦合于栅极电极(例如,栅极电极842)、以及端子966(例如,端子866)耦合于漏极区域(例如,漏极区域836)。

[0072] 根据实施例,以及正如上面所讨论的,PLDMOSFET还包括电耦合于源极区域(例如,源极区域838)和器件的隔离结构之间的电阻网络946。虽然单一电阻器被用于描述图9(以及在附图中描述的其它电路表征中)中的电阻网络946,应了解这仅仅是为了方便,并且正如先前所讨论的,电阻网络可以包括多个电阻器。在实施例中,电阻网络946的第一端子耦合于源极区域,以及电阻网络946的第二端子耦合于隔离结构(例如,下沉区域822和NBL820的组合)。在节点920处,二极管914表示了由隔离结构和隔离结构之外的剩余衬底之间的界面形成的二极管。

[0073] 在源极电位被升高的正常工作期间,隔离结构电位紧密地跟随源极区域电位,其中电阻网络946两端的电压降取决于流经体区域的电流量。另一方面,当源极电位转换到负电压的时候,隔离结构电位被电阻网络946两端的电压降保持。当源极电位变为负的时候,通过保持隔离结构电位,如果源极和隔离结构仅仅是短接则可以会发生的注入到衬底的载流子可以被减少或消除,从而避免了相邻电路块的中断。

[0074] 根据另一实施例,电阻器电路(例如,图1的电阻器电路162)可以包括与肖特基二极管串联的电阻网络。例如,图10根据替代实施例,是图8的PLDMOSFET800的简化电路表征1000,带有包括与肖特基二极管1010串联的电阻网络1046的电阻器电路。与图8的实施例相类似,端子1062(例如,端子862)耦合于源极区域(例如,源极区域838)、端子1064(例如,端子864)耦合于栅极电极(例如,栅极电极842)、以及端子1066(例如,端子866)耦合于漏极区域(例如,漏极区域836)。

[0075] 肖特基二极管1010和电阻网络1046串联电耦合于源极区域(例如,源极区域838)和器件的隔离结构之间。肖特基二极管1010可以例如由与隔离结构(例如,与下沉区域822接触的肖特基接触(未示出)形成。更具体地,在实施例中,肖特基二极管可以由位于肖特基接触(例如,用硅化物在顶衬底表面上形成)和下沉区域822的顶面之间的金属-半导体结形成。在替代实施例中,肖特基接触可以形成于不与顶衬底表面812共面的侧壁或其它表面上。

[0076] 在操作期间,当源极电位转换到负电压的时候,隔离结构电位被与肖特基二极管1010的反向击穿电压串联的电阻网络1046两端的电压降保持。肖特基二极管1010和电阻网络1046的组合可以允许更灵活地建造肖特基二极管1010。此外,选择电阻网络1046的值以实现保持PLDMOSFET的完整性的最佳整体结果,ESD稳健性可以被实现,同时降低了衬底注入。更具体地说,例如,在肖特基二极管1010碰上击穿(例如,在ESD应力期间)的条件下,流过肖特基二极管1010的电流被电阻网络1046限定到其容量程度,从而降低了ESD事件可以损坏肖特基二极管1010的可能性。

[0077] 根据另一实施例,电阻器电路(例如,图1的电阻器电路162)可以包括与肖特基二

极管并联的电阻网络。例如,图11根据替代实施例,是图8的PLDMOSFET800的简化电路表征1100,带有包括与肖特基二极管1110并联的电阻网络1146的电阻器电路。与图8的实施例相类似,端子1162(例如,端子862)耦合于源极区域(例如,源极区域838)、端子1164(例如,端子864)耦合于栅极电极(例如,栅极电极842)、以及端子1166(例如,端子866)耦合于漏极区域(例如,漏极区域836)。

[0078] 肖特基二极管1110(例如,位于肖特基二极管(未示出)和下沉区域822之间的界面)和电阻网络1146并联电耦合于源极区域(例如,源极区域838)和器件的隔离结构之间。在操作期间,当源极电位转换到负电压的时候,隔离结构电位被与肖特基二极管1110的反向击穿电压并联的电阻网络1146两端的电压降保持。如同结合图10所讨论的电阻器电路,肖特基二极管1110和电阻网络1146的组合可以允许更灵活地建造肖特基二极管1110。此外,在某些条件下,电阻网络1146可以运行以保持隔离结构电位更接近PLDMOSFET的漏极电位。例如,当源极电位降低的时候(虽然仍是正的),隔离结构电位仅仅被肖特基二极管1110的电容拉下来,这可能够有可能不够。在这样一种情况下,电阻网络1146可以有助于隔离结构电位朝着源极电位放电。当源极电位转换到负的时候,虽然某些少数载流子注入可以被添加,但是电阻网络1146可以限制载流子注入的量。

[0079] 在结合图10和图11所讨论的实施例中,电阻器电路(例如,图1的电阻器电路162)包括与肖特基二极管串联(图10)或并联(图11)的电阻网络(例如,电阻网络1046、1146)。在另一替代实施例中,电阻器电路可以包括肖特基二极管以及与肖特基二极管串联的第一电阻网络以及与肖特基二极管并联的第二电阻网络,以实现可以被串联耦合和并联耦合电阻网络布置二者提供的优势。

[0080] 在结合图10和图11所讨论的实施例中,耦合PLDMOSFET的实施例(例如,图1的PLDMOSFET116)的源极区域和隔离结构的电阻器电路(例如,图1的电阻器电路162)包括肖特基二极管。根据另一实施例,电阻器电路(例如,图1的电阻器电路162)包括电阻网络和连接在源极区域(例如,图8的源极区域838)和隔离结构之间的PN结二极管(未示出)。例如,还参照图8,不是包括N型区域824,PLDMOSFET800也可以包括延伸到下沉区域822的P型区域(未示出)。位于P型区域和下沉区域822之间的PN结形成了可以在电阻器电路中是互连的PN结二极管。PN结二极管可以被设计以提供期望的依赖于应用的击穿电压(例如,大于、小于或等于正常的、最负的操作电压的击穿电压)。例如,在实施例中,PN结二极管可以被设计以提供在约-0.3伏-约-14.0伏范围内的反向击穿电压,虽然更小或更大的击穿电压也可以被实现。

[0081] 根据另一实施例,电阻器电路(例如,图1的电阻器电路162)可以包括电阻网络和连接在源极区域(例如,图8的源极区域838)和隔离结构之间的多晶硅二极管(未示出)。例如,多晶硅二极管可以由被定义了多晶硅二极管的击穿电压的中性间隔区域间隔开的P型区域和N型区域形成。多晶硅二极管可以形成于衬底顶面上的绝缘区域上(例如,在STI852上)。或者,多晶硅二极管可以由其它材料形成和/或位于其它地方。在实施例中,多晶硅二极管可以被设计以提供期望的依赖于应用、大于、小于或等于正常的、最负的操作电压的击穿电压(例如,在约-0.3伏-约-14.0伏范围内的击穿电压,虽然更小或更大的击穿电压也可以被实现)。

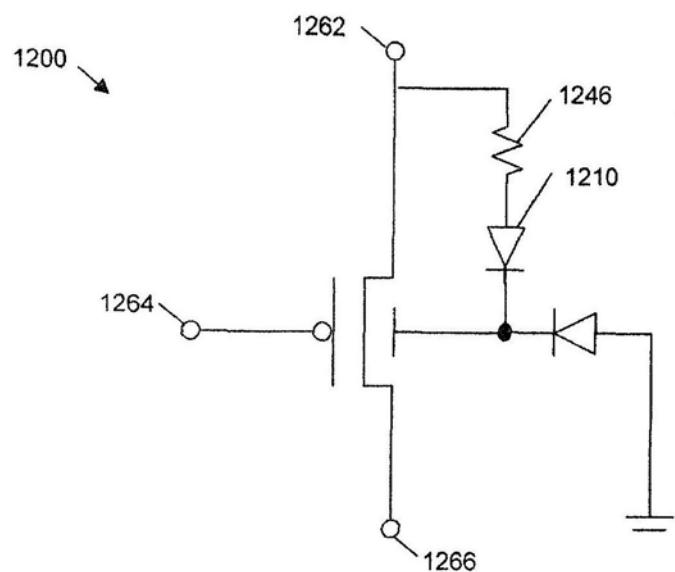

[0082] 图12根据替代实施例,是图8的PLDMOSFET800的简化电路表征1200,带有包括与PN

结二极管1210(例如,由位于P型区域和下沉区域822之间的PN结形成的PN结二极管,或多晶硅二极管)串联的电阻网络1246的电阻器电路。与图8的实施例相类似,端子1262(例如,端子862)耦合于源极区域(例如,源极区域838)、端子1264(例如,端子864)耦合于栅极电极(例如,栅极电极842)、以及端子1266(例如,端子866)耦合于漏极区域(例如,漏极区域836)。

[0083] 电阻网络1246和PN结二极管1210串联电耦合于源极区域(例如,源极区域838)和器件的隔离结构之间。在操作期间,当源极电位转换到负电压的时候,隔离结构电位被与PN结二极管1210的反向击穿电压串联的电阻网络1246两端的电压降保持。如同结合图10先前所讨论的实施例,PN结二极管1210和电阻网络1246的组合可以提供某些有利效用。

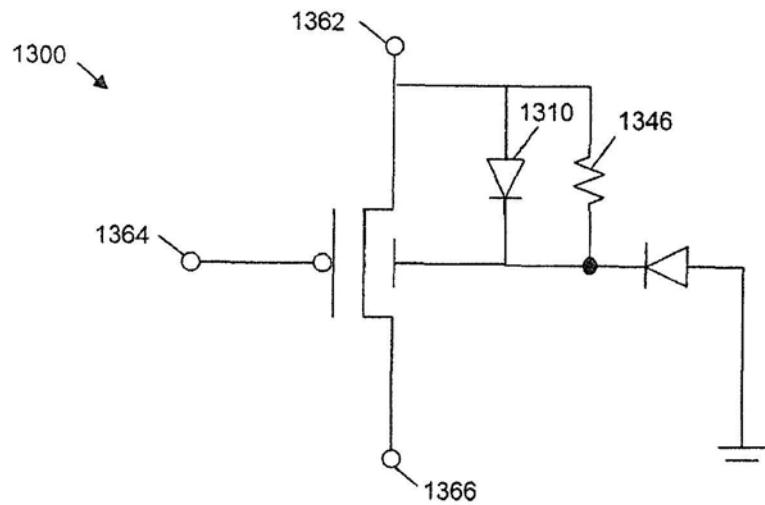

[0084] 根据另一实施例,电阻器电路(例如,图1的电阻器电路162)可以包括与PN结二极管并联的电阻网络。例如,图13根据替代实施例,是图8的PLDMOSFET800的简化电路表征1300,带有包括与PN结二极管1310并联的电阻网络1346的电阻器电路。与图8的实施例相类似,端子1362(例如,端子862)耦合于源极区域(例如,源极区域838)、端子1364(例如,端子864)耦合于栅极电极(例如,栅极电极842)、以及端子1366(例如,端子866)耦合于漏极区域(例如,漏极区域836)。

[0085] 电阻网络1346和PN结二极管1310并联电耦合于源极区域(例如,源极区域836)和器件的隔离结构之间。在操作期间,当源极电位转换到负电压的时候,隔离结构电位被与PN结二极管1310的反向击穿电压并联的电阻网络1346两端的电压降保持。如同结合图12所讨论的电阻器电路,PN结二极管1310和电阻网络1346的组合可以有某些有利效用。

[0086] 在结合图12和图13所讨论的实施例中,电阻器电路(例如,图1的电阻器电路162)包括PN结二极管(例如,PN结二极管1210、1310)和串联耦合于PN结二极管的电阻网络(电阻网络1246)或并联耦合于PN结二极管的电阻网络(电阻网络1346)。在另一替代实施例中,电阻器电路可以包括PN结二极管和串联耦合于PN结二极管的第一电阻网络以及并联耦合于PN结二极管的第二电阻网络,以实现可以被串联耦合和并联耦合电阻网络布置二者提供的优势。

[0087] 在结合图10-图13所讨论的实施例中,耦合PLDMOSFET的实施例(例如,图1的PLDMOSFET116)的源极区域和隔离结构的电阻器电路(例如,图1的电阻器电路162)包括肖特基二极管或PN结二极管。根据其它实施例,替代地,耦合PLDMOSFET的实施例的源极区域和隔离结构的电阻器电路可以包括一个或多个肖特基二极管和一个或多个PN结二极管的组合。例如,PLDMOSFET的实施例可以包括肖特基二极管和一个或多个串联连接在源极区域和隔离结构之间的PN结二极管的组合。更具体地,电阻器电路可以包括由位于肖特基接触和隔离结构(例如,下沉区域822)之间的金属-半导体结形成的肖特基二极管,连同一个或多个P型区域,各自延伸到下沉区域并且部分穿过下沉区域。肖特基接触被连接到电阻网络(即,肖特基二极管的阳极被连接到电阻网络),以及位于P型区域和下沉区域之间的PN结形成了电阻器电路的PN结二极管。根据实施例,将PN二极管放置于肖特基二极管旁边允许了PN结耗尽肖特基二极管下面的硅,因此降低了肖特基二极管内的反向偏置泄漏。肖特基二极管和PN结二极管可以被设计以提供期望的依赖于应用的击穿电压(例如,大于、小于或等于正常的、最负的操作电压的击穿电压)。例如,在实施例中,肖特基二极管和PN结二极管可以被设计以提供在约-0.3伏-约-14.0伏范围内的反向击穿电压,虽然更小或更大的击穿电

压也可以被实现。

[0088] 在上面所描述的PLDMOSFET的实施例中,体区域(例如,图8的体区域834)和隔离结构合并,并且隔离结构(或者更具体地说是下沉区域(例如,图8的下沉区域822)可以被认为是体结。在这种实施例中,当电阻器电路(例如,图1的电阻器电路162)耦合于源极端子的时候,因为源极区域-体区域结可以变为正向偏置,体偏压可以在操作期间被创建。在结合图14-图20所讨论的替代实施例中,体区域和隔离结构可以通过P型材料(例如,与有源器件或P型阱相关联的衬底的一部分)的区域分开,以及不同的体端子可以被提供以有助于电访问体区域。在这样的实施例中,类似于上面所描述的电阻器电路的电阻器电路可以耦合于体区域和隔离结构之间,而不是正如上面实施例中所描述的将电阻器电路耦合于源极区域和隔离结构之间。在体区域和隔离结构被分开的实施例中,当源极/体端子处出现负电位的时候,体区域和源极区域可以被结合(tie)在一起(例如,在正常操作期间,它们可以有相同偏压),并且隔离结构的电位可以被电阻器电路保持。在正常操作期间,在体区域、源极区域以及隔离结构都在高电位时,隔离结构和体区域可以通过其间的P型材料的横向耗尽(例如,在其间的击穿之前可以被完全耗尽),或通过位于体区域和NBL之间的P型衬底的部分的垂直耗尽被有效地短接,无论哪种情形先发生。

[0089] 例如,图14根据另一实施例,是包括了驱动电路1410的电子系统1400的简化图。系统1400的大部分与图1中所描述的系统100类似,并且图1和图14之间的相似参考符号表示类似的系统元件。为了简洁,虽然上面的说明书同样适用于图14的系统,这些相同的系统元件在发明中不进行详细讨论了。

[0090] 系统1400与系统100的不同点在于驱动器电路1410包括耦合于PLDMOSFET1416的体区域和隔离结构之间的电阻器电路1462(而不是耦合于图1的PLDMOSFET116的源极区域和隔离结构之间的电阻器电路162)。此外,驱动器电路1410包括耦合于PLDMOSFET1418的体区域和隔离结构之间的电阻器电路1463(而不是耦合于图1的PLDMOSFET118的源极区域和隔离结构之间的电阻器电路163)。电阻器电路1462、1463被配置以在先前所描述的操作条件下减少或消除至SOC的衬底内的电流注入。

[0091] 在各个实施例中,因为PLDMOSFET1416、1418的体区域和隔离结构没有合并,在PLDMOSFET1416、1418的体区域和隔离结构之间插入电阻器电路1462、1463是可以的。更具体地说,在图14的PLDMOSFET1416、1418中,体区域和隔离结构通过正如前面提到的P型材料的区域分开,并且将结合图15-图20更详细地讨论。在体区域和隔离结构分开的情况下,通过将源极和体区域结合在一起(例如,短接)以及将电阻器电路(例如,电阻器电路1462、1463)放置在隔离结构和被结合在一起的源极/体区域之间,就避免了否则可以在操作期间(例如,在先前所描述的体区域和隔离结构是合并的实施例中)被创建的体偏压。此外,如同先前所描述的实施例,通过在PLDMOSFET1416、1418的体区域和隔离结构之间插入电阻器电路1462、1463,可以被减小或消除系统1400中的注入电流。

[0092] 下面更详细地描述了PLDMOSFET(例如,PLDMOSFET1416)的附加实施例和相关的电阻器电路(例如,电阻器电路1462)。例如,根据实施例,耦合PLDMOSFET1416的体区域和隔离结构的电阻器电路1462包括了电阻网络。这样实施例在图15中被说明,其中图15是PLDMOSFET1500(例如,图1的PLDMOSFET1416)的截面图,带有包括电阻网络的电阻器电路(例如,图14的电阻器电路1462),正如在下面更详细描述的。虽然本发明的附图和描述特别

适用于双栅指配置,本发明主题范围并不限于这样的配置。根据本发明的描述,本领域所属技术人员将了解如何修改所说明的和所描述的实施例以应用包括多个(即,>2)栅指的应用配置,其中一边上相邻的栅指可以共享漏极(例如,漏极区域1536)以及另一边(或极端情况下,位于源极区域1538上)的可以共享体接触区域(例如,体接触区域1535)。在这样的实施例中,体接触区域可以比附图中所描述的更加横向分离于下沉区域(例如,下沉区域1522)。

[0093] PLDMOSFET1500形成于有顶衬底表面1512的半导体衬底1510(例如,结合图1所讨论的SOC衬底)上和内。根据实施例,PLDMOSFET1500包括隔离结构,其实质上围绕与PLDMOSFET1500的有源区域1530(即,在有源器件形成于其内的衬底1510内的区域)相关联的衬底的部分1516。换句话说,有源器件可以被认为包含在隔离结构中。隔离结构是箱式结构,由NBL1520(位于顶衬底表面1512下面的深度)和从顶衬底表面1512延伸到NBL1520的深度的N型下沉区域1522形成。下沉区域1522可以通过使用单一注入过程被形成;该过程有足够的能量使得下沉区域1522延伸到NBL1520的注入能量,或下沉区域1522可以通过使用有不同注入能量的多个注入过程被形成,从而在不同深度形成了一系列互连下沉子区域。

[0094] PLDMOSFET1500还包括形成于有源区域1530内的有源器件。根据实施例,有源器件包括P型漂移区域1532、N型体区域1534、P型漏极区域1536、P型源极区域1538、以及栅极电极1542(以及相应的没有编号的栅极介电质)。漂移区域1532形成于有源区域1530的中心部分内,并且从顶衬底表面1512延伸到衬底1510的小于NBL1520的深度的深度。漏极区域1536形成于漂移区域1532内,并且比漂移区域1532重掺杂。漏极区域1536从顶衬底表面1512延伸到衬底1510显著地小于漂移区域1532的深度的深度。导电互连将漏极区域1536电耦合于漏极端子1566。

[0095] 体区域1534形成于漂移区域1532和下沉区域1522之间,并且从顶衬底表面1512延伸到衬底1510内小于NBL1520的深度的深度,并且该深度可以大于漂移区域1532的深度(虽然体区域1534也可以延伸到小于或实质上等于漂移区域1532的深度的深度)。N型体接触区域1535形成于源极区域1538和下沉区域1522之间的体区域1534内。体接触区域1535可以比体区域1534重掺杂。在实施例中,体区域1534相邻于漂移区域1532。在替代实施例中,体区域1534可以横向分离于漂移区域1532,或体区域1534可以重叠于漂移区域1532(生成带有与沟道或漂移区域1532内的掺杂分布不同的掺杂分布的区域)。

[0096] 根据实施例,体区域1534通过P型材料的区域1537(在本发明被称为“P型间隙”)横向分离于下沉区域1522。根据实施例,P型间隙1537可以由隔离结构所包含的P型衬底的部分形成,其中P型间隙1537在体区域1534和下沉区域1522之间朝着顶衬底表面1512延伸。在替代实施例中,P型间隙1537可以由形成于体区域1534和下沉区域1522之间的P型阱(例如,高压P-阱或低压P-阱)形成。

[0097] 栅极电极1542形成于通常位于漏极区域1536和源极区域1538之间的顶衬底表面1512上的栅氧化物上。导电互连将栅极电极1542电耦合于栅极端子1564。源极区域1538形成于体区域1534内,从顶衬底表面1512延伸到衬底1510内显著小于体区域1534的深度的深度。源极区域1538可以比漂移区域1532重掺杂。导电互连将源极区域1538电耦合于源极端子1562。

[0098] 根据实施例,PLDMOSFET1500可以还包括正如图15所显示的各种STI结构1550、

1552、1554。例如,在顶衬底表面1512,STI1550相邻于漂移区域1532内的漏极区域1536,以及STI1552位于源极区域1538和体接触区域1535之间,以及STI1554位于体区域1534和隔离结构(或更具体地说,下沉区域1522)之间。在替代实施例中,STI结构1550、1552、和/或1554的其中一个或多个可以被排除在外。在其它替代实施例中,某些或所有STI结构可以被替代为硅化物阻挡层,其中该阻挡层阻止了硅化物在表面形成,否则硅化物将短接在一起各个区域。

[0099] 根据实施例,PLDMOSFET1500还包括被连接在源极区域1538和延伸到下沉区域1522内的N型区域1524之间的电阻器电路(例如,图14的电阻器电路1462),其中N型区域1524比下沉区域1522更加重掺杂以给下沉区域1522提供欧姆接触。例如,电阻器电路可以包括带有一个或多个电阻器1546的电阻网络。虽然只有电阻器1546在图15中被显示,应了解电阻网络可以包括多个电阻器。电阻网络的电阻器1546可以由多晶硅形成,并且可以位于衬底顶面的一个或多个隔离区域上(例如,位于STI1552或1544上)。或者,一个或多个电阻器1546可以由其它材料形成和/或位于其它地方。根据实施例,导电互连电耦合体区域1534(通过体接触区域1535)、电阻网络的第一端子(例如,电阻网络1546的第一端子)、以及体端子1568。另一导电互连将电阻网络的第二端子(例如,电阻网络1546的第二端子)电耦合于隔离结构(例如,N型区域1524)。在实施例中,电阻网络有在约10-约20000欧姆范围内的电阻,虽然更小或更大的电阻也可以被实现。

[0100] 正如先前所提到的,以及正如图14中所表示的,体区域1534和源极区域1538可以通过导电互连(未在图15中说明)电耦合(短接的),以及电阻器电路(例如,图14的电阻器电路1462)可以电耦合于隔离结构(例如,下沉区域1522)和短接的源极和体区域之间。换句话说,源极端子1562和体端子1568可以短接在一起。在正常操作期间,在体区域1534、源极区域1538以及隔离结构都在高电位时,隔离结构和体区域1534可以通过其间的P型间隙1537的横向耗尽(例如,在其间的击穿之前可以被完全耗尽),或通过位于体区域1534和NBL1520之间的P型衬底的部分的垂直耗尽被有效地短接,无论哪种情形先发生。

[0101] 图16根据实施例,是图15的PLDMOSFET1500的简化电路表征1600。还参照图15,端子1662(例如,端子1562)耦合于源极区域(例如,源极区域1538)、端子1664(例如,端子1564)耦合于栅极电极(例如,栅极电极1542)、以及端子1666(例如,端子1566)耦合于漏极区域(例如,漏极区域1536)、以及端子1668(例如,端子1568)耦合于体区域(例如,通过体接触区域1535)。

[0102] 根据实施例,以及正如上面所讨论的,PLDMOSFET还包括电耦合于体区域(例如,通过体接触1535的体区域1534)和器件的隔离结构之间的电阻器电路(例如,包括电阻网络1646)。更具体地说,电阻网络1646的第一端子耦合于体区域,以及电阻网络1646的第二端子耦合于隔离结构(例如,下沉区域1522和NBL1520的组合)。在节点1620,二极管1614表示了由隔离结构和隔离结构之外的剩余衬底之间的界面形成的二极管。

[0103] 在体电位等于或高于衬底电压电平(例如,被升高)期间,隔离结构电位紧密地跟随体区域电位,其中电阻网络1646两端的电压降取决于流经体区域的电流量。另一方面,当体电位转换到负电压的时候,隔离结构电位被电阻网络1646两端的电压降保持。当体电位变为负的时候,通过保持隔离结构电位,如果体和隔离结构仅仅是短接则可以会发生的注入到衬底的载流子可以被减少或消除,从而避免了相邻电路块的中断。

[0104] 根据另一实施例,电阻器电路(例如,图14的电阻器电路1462)可以包括与肖特基二极管串联的电阻网络。例如,图17根据替代实施例,是图15的PLDMOSFET1500的简化电路表征1700,带有包括与肖特基二极管1710串联的电阻网络1746的电阻器电路。还参照图15,端子1762(例如,端子1562)耦合于源极区域(例如,源极区域1538)、端子1764(例如,端子1564)耦合于栅极电极(例如,栅极电极1542)、端子1766(例如,端子1566)耦合于漏极区域(例如,漏极区域1536)、以及端子1768(例如,端子1568)耦合于体区域(例如,通过体接触区域1535)。

[0105] 肖特基二极管1710和电阻网络1746串联电耦合于体区域(例如,通过体接触1535的体区域1534)和器件的隔离结构之间。肖特基二极管1710可以例如由与隔离结构(例如,与下沉区域1522)接触的肖特基接触(未示出)形成。更具体地,在实施例中,肖特基二极管可以由位于肖特基接触(例如,用硅化物在顶衬底表面上形成)和下沉区域1522的顶面之间的金属-半导体结形成。在替代实施例中,肖特基接触可以形成于不与顶衬底表面1512共面的侧壁或其它表面上。

[0106] 在操作期间,当体电位转换到负电压的时候,隔离结构电位被与肖特基二极管1710的反向击穿电压串联的电阻网络1746两端的电压降保持。肖特基二极管1710和电阻网络1746的组合可以允许更灵活地建造肖特基二极管1710。此外,选择电阻网络1746的值以实现保持PLDMOSFET的完整性的最佳整体结果,ESD稳健性可以被实现,同时降低了衬底注入。更具体地说,例如,在肖特基二极管1710碰上击穿(例如,在ESD应力期间)的条件下,流过肖特基二极管1710的电流被电阻网络1746限定到其容量程度,从而降低了ESD事件可以损坏肖特基二极管1710的可能性。

[0107] 根据另一实施例,电阻器电路(例如,图14的电阻器电路1462)可以包括与肖特基二极管并联的电阻网络。例如,图18根据替代实施例,是图15的PLDMOSFET1500的简化电路表征1800,带有包括与肖特基二极管1810并联的电阻网络1846的电阻器电路。还参照图15,端子1862(例如,端子1562)耦合于源极区域(例如,源极区域1538)、端子1864(例如,端子1564)耦合于栅极电极(例如,栅极电极1542)、端子1866(例如,端子1566)耦合于漏极区域(例如,漏极区域1536)、以及端子1868(例如,端子1568)耦合于体区域(例如,通过体接触区域1535)。

[0108] 肖特基二极管1810(例如,位于肖特基二极管(未示出)和下沉区域1522之间的界面)和电阻网络1846并联电耦合于体区域(例如,通过图15的体接触1535的体区域1534)和器件的隔离结构之间。在操作期间,当源极电位转换到负电压的时候,隔离结构电位被与肖特基二极管1810的反向击穿电压并联的电阻网络1846两端的电压降保持。如同结合图17所讨论的电阻器电路,肖特基二极管1810和电阻网络1846的组合可以允许更灵活地建造肖特基二极管1810。此外,在某些条件下,电阻网络1846可以运行以保持隔离结构电位更接近PLDMOSFET的体电位。例如,当体电位降低的时候(虽然仍是正的),隔离结构电位仅仅被肖特基二极管1810的电容拉下来,这可能够也可能不够。在这样一种情况下,电阻网络1846可以有助于隔离结构电位朝着体电位放电。当体电位转换到负的时候,虽然某些少数载流子注入可以被添加,但是电阻网络1846可以限制载流子注入的量。

[0109] 在结合图17和图18所讨论的实施例中,电阻器电路(例如,图14的电阻器电路1462)包括与肖特基二极管串联(图17)或并联(图18)的电阻网络(例如,电阻网络1746、

1846)。在另一替代实施例中,电阻器电路可以包括肖特基二极管以及与肖特基二极管串联的第一电阻网络以及与肖特基二极管并联的第二电阻网络,以实现可以被串联耦合和并联耦合电阻网络布置二者提供的优势。

[0110] 在结合图17和图18所讨论的实施例中,耦合PLDMOSFET的实施例(例如,图14的PLDMOSFET1416)的体区域和隔离结构的电阻器电路(例如,图14的电阻器电路1462)包括肖特基二极管。根据另一实施例,电阻器电路(例如,图14的电阻器电路1462)包括电阻网络和连接在体区域(例如,图15的通过体接触1535的体区域1534)和隔离结构之间的PN结二极管(未示出)。例如,还参照图15,不是包括N型区域1524,PLDMOSFET1500也可以包括延伸到下沉区域1522的P型区域(未示出),其中P型区域比P型漂移区域1532重掺杂。位于P型区域和下沉区域1522之间的PN结形成了可以在电阻器电路中是互连的PN结二极管。PN结二极管可以被设计以提供期望的依赖于应用的击穿电压(例如,大于、小于或等于正常的、最负的操作电压的击穿电压)。例如,在实施例中,PN结二极管可以被设计以提供在约-0.3伏-约-14.0伏范围内的反向击穿电压,虽然更小或更大的击穿电压也可以被实现。

[0111] 根据另一实施例,电阻器电路(例如,图14的电阻器电路1462)可以包括电阻网络和连接在体区域(例如,通过图15的体接触1535的体区域1534)和隔离结构之间的多晶硅二极管(未示出)。例如,多晶硅二极管可以由被定义了多晶硅二极管的击穿电压的中性间隔区域间隔开的P型区域和N型区域形成。多晶硅二极管可以形成于衬底顶面上的绝缘区域上(例如,在STI1552或1554上)。或者,多晶硅二极管可以由其它材料形成和/或位于其它地方。在实施例中,多晶硅二极管可以被设计以提供期望的依赖于应用、大于、小于或等于正常的、最负的操作电压的击穿电压(例如,在约-0.3伏-约-14.0伏范围内的击穿电压,虽然更小或更大的击穿电压也可以被实现)。

[0112] 图19根据替代实施例,是图15的PLDMOSFET1500的简化电路表征1900,带有包括与PN结二极管1910(例如,由位于P型区域和下沉区域1522之间的PN结形成的PN结二极管,或多晶硅二极管)串联的电阻网络1946的电阻器电路。与图15的实施例相类似,端子1962(例如,端子1562)耦合于源极区域(例如,源极区域1538)、端子1964(例如,端子1564)耦合于栅极电极(例如,栅极电极1542)、端子1966(例如,端子1566)耦合于漏极区域(例如,漏极区域1536)、以及端子1968(例如,端子1568)耦合于体区域(例如,通过体接触区域1535)。

[0113] 电阻网络1946和PN结二极管1910串联电耦合于体区域(例如,通过体接触1535的体区域1534)和器件的隔离结构之间。在操作期间,当源极电位转换到负电压的时候,隔离结构电位被与PN结二极管1910的反向击穿电压串联的电阻网络1946两端的电压降保持。如同结合图17先前所讨论的实施例,PN结二极管1910和电阻网络1946的组合可以提供某些有利效用。

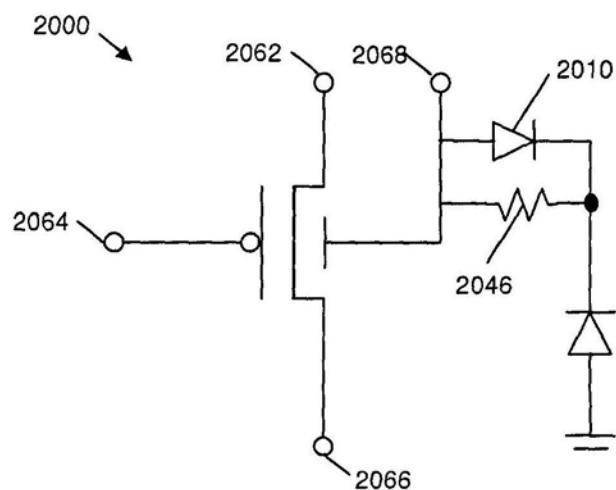

[0114] 根据另一实施例,电阻器电路(例如,图14的电阻器电路1462)可以包括与PN结二极管并联的电阻网络。例如,图20根据替代实施例,是图15的PLDMOSFET1500的简化电路表征2000,带有包括与PN结二极管2010并联的电阻网络2046的电阻器电路。与图15的实施例相类似,端子2062(例如,端子1562)耦合于源极区域(例如,源极区域1538)、端子2064(例如,端子1564)耦合于栅极电极(例如,栅极电极1542)、端子2066(例如,端子1566)耦合于漏极区域(例如,漏极区域1536)、以及端子2068(例如,端子1568)耦合于体区域(例如,通过体接触区域1535)。

[0115] 电阻网络2046和PN结二极管2010并联电耦合于体区域(例如,通过体接触1535的体区域1534)和器件的隔离结构之间。在操作期间,当体电位转换到负电压的时候,隔离结构电位被与PN结二极管2010的反向击穿电压并联的电阻网络2046两端的电压降保持。如同结合图19所讨论的电阻器电路,PN结二极管2010和电阻网络2046的组合可以有某些有利效用。

[0116] 在结合图19和图20所讨论的实施例中,电阻器电路(例如,图14的电阻器电路1462)包括PN结二极管(例如,PN结二极管1910、2010)和串联耦合于PN结二极管的电阻网络(电阻网络1946)或并联耦合于PN结二极管的电阻网络(电阻网络2046)。在另一替代实施例中,电阻器电路可以包括PN结二极管和串联耦合于PN结二极管的第一电阻网络以及并联耦合于PN结二极管的第二电阻网络二者,以实现可以被串联耦合和并联耦合电阻网络布置二者提供的优势。

[0117] 在结合图17-图20所讨论的实施例中,耦合PLDMOSFET的实施例(例如,图14的PLDMOSFET1416)的体区域和隔离结构的电阻器电路(例如,图14的电阻器电路1462)包括肖特基二极管或PN结二极管。根据其它实施例,替代地,耦合PLDMOSFET的实施例的体区域和隔离结构的电阻器电路可以包括一个或多个肖特基二极管和一个或多个PN结二极管的组合。例如,PLDMOSFET的实施例可以包括肖特基二极管和一个或多个并联连接在体区域和隔离结构之间的PN结二极管的组合。更具体地,电阻器电路可以包括由位于肖特基接触和隔离结构(例如,下沉区域1522)之间的金属-半导体结形成的肖特基二极管,连同一个或多个P型区域,各自延伸到下沉区域并且部分穿过下沉区域。肖特基接触被连接到电阻网络(即,肖特基二极管的阳极被连接到电阻网络),以及位于P型区域和下沉区域之间的PN结形成了电阻器电路的PN结二极管。根据实施例,将PN二极管放置于肖特基二极管旁边允许了PN结耗尽肖特基二极管下面的硅,因此降低了肖特基二极管内的反向偏置泄漏。肖特基二极管和PN结二极管可以被设计以提供期望的依赖于应用的击穿电压(例如,大于、小于或等于正常的、最负的操作电压的击穿电压)。例如,在实施例中,肖特基二极管和PN结二极管可以被设计以提供在约-0.3伏-约-14.0伏范围内的反向击穿电压,虽然更小或更大的击穿电压也可以被实现。

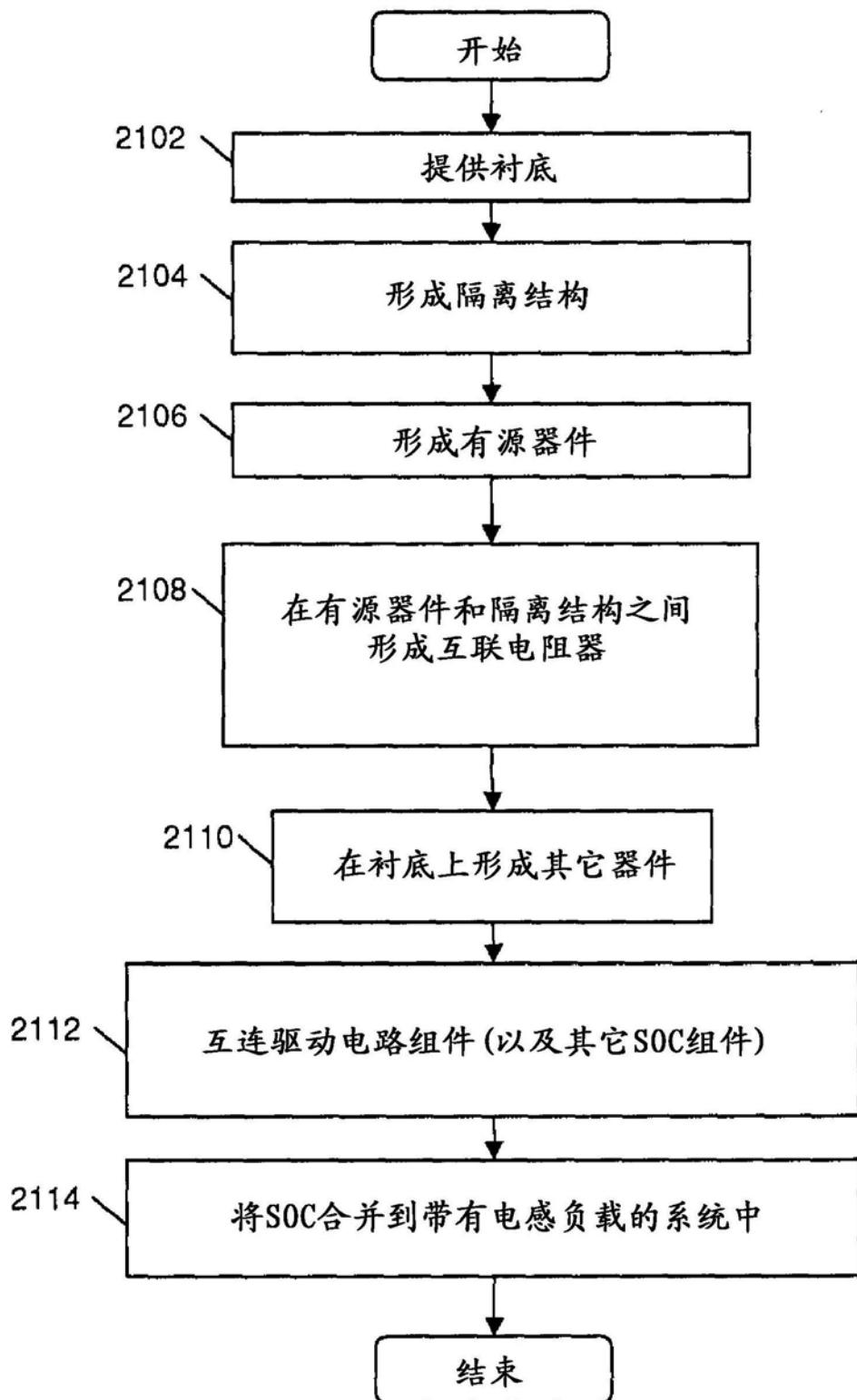

[0118] 图21根据各个实施例,是说明了一种用于形成例如在图2、图8和图15所说明的器件,并且将这些器件合并到SOC和带有电感负载(例如,图1的电感负载132)的系统(例如,图1、图14的系统100、1400)的方法的简化流程图。标准的半导体工艺技术可以被采用以生产SOC,并且为了简洁,本申请没有详细描述这些技术。

[0119] 所述方法通过提供有第一导电类型(例如,P型衬底210、810、1510)的衬底(例如,SOC衬底)在块2102开始。例如,所述衬底可以包括基底衬底和在所述基底衬底上生长的外延层。有源器件(例如,与驱动电路相关联的)可以然后被形成(块2104、2106、2108)。例如,在块2104,隔离结构可以形成于衬底内。正如先前所详细描述的,所述隔离结构可以包括第二导电类型的埋层(例如,NBL220、820、1520)和所述第二导电类型的从衬底顶面延伸到埋层的下沉区域(例如,下沉区域222、822、1522)。由埋层和下沉区域的组合形成的隔离结构可以实质上围绕器件有源区域(例如,有源区域230、830、1530)。在块2106,有源器件可以形成于有源区域内。例如,除了别的之外,形成于有源区域内的有源器件可以包括正如先前所描述的漂移区域、体区域、栅极、以及相邻于器件的沟道区域的相对两端的载流区域(例如,

漏极区域和源极区域)。

[0120] 在块2108, 电阻器电路(例如, 图1的电阻器电路162)可以形成于并且互连在有源器件和隔离结构(或者更具体地说是下沉区域, 例如下沉区域222、822、1522)之间。例如, 在制作NLDMOSFET(例如, 图2的PLDMOSFET200)的情况下, 电阻器电路可以互连在器件的漏极区域和隔离结构之间。相反, 在制作PLDMOSFET(例如, 图8、图15的PLDMOSFET800、1500)的情况下, 电阻器电路可以互连在器件的源极区域(图8)或体区域(图15)和隔离结构之间。正如上述所详细描述的, 电阻器电路的实施例可以包括一个或多个电阻网络、肖特基二极管、和/或PN结二极管。

[0121] 在可以并行于块2104、2106、以及2108被执行的块2110, “其它器件”可以形成于衬底内或衬底上, 包括形成与驱动电路(例如, 图1的驱动电路110)相关联的附加器件和与片上系统(SOC)相关联的附加器件(例如, 处理组件、存储器阵列、以及其它电路)。驱动电路和其它SOC组件在块2112可以互连, SOC的衬底可以被封装, 从而完成SOC的制作。在块2114, 无论封装还是未封装, SOC可以被合并到更大的系统中, 例如包括电感负载(例如, 图1的电感负载132)的系统, 并且所述方法可以结束。

[0122] 正如先前所讨论的, 在块2404、2406和2408中形成的器件被配置以减少或消除在各种操作条件下到SOC衬底的电流注入。更具体地说, 当与不存在这样电阻器电路的其它系统(例如, 在源极区域、体区域以及隔离结构仅仅被短接在一起的系统中)进行比较的时候, 耦合于驱动电路的至少一个有源器件的载流区域(例如, 漏极或源极区域)和隔离结构之间的电阻器电路可以导致减少或消除注入电流。因此, 各个实施例可以产生显著地有利结果。

[0123] 虽然至少一个示例实施例在上述详细描述中已经被提出了, 应认识到还存在大量的变化, 特别是关于器件类型、材料以及掺杂的选择。应认识到示例实施例或一些示例实施例仅仅是例子, 而不旨在以任何方式实施例的限定范围、适用性、或配置。相反, 上述详细描述将给本领域所属技术人员提供一条便捷的路线图以用于实施本发明的一个或多个实施例。应了解在不脱离所附权利要求以及其法律等同物所提出的发明主题的范围的情况下, 在元素的功能和布置方面可以做各种变化。

图1

图2

图3

图4

图5

图6

图7

图8

图9

图10

图11

图12

图13

图14

图15

图16

图17

图18

图19

图20

图21