(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3786575号

(P3786575)

(45) 発行日 平成18年6月14日(2006.6.14)

(24) 登録日 平成18年3月31日(2006.3.31)

(51) Int.C1.

F 1

G 06 F 9/42 (2006.01)

G 06 F 9/42 330 A

請求項の数 4 (全 25 頁)

(21) 出願番号 特願2000-357619 (P2000-357619)

(22) 出願日 平成12年11月20日 (2000.11.20)

(65) 公開番号 特開2002-157115 (P2002-157115A)

(43) 公開日 平成14年5月31日 (2002.5.31)

審査請求日 平成16年3月26日 (2004.3.26)

(73) 特許権者 503121103

株式会社ルネサステクノロジ

東京都千代田区丸の内二丁目4番1号

(74) 代理人 100089071

弁理士 玉村 静世

(74) 代理人 100075096

弁理士 作田 康夫

(72) 発明者 三ツ石 直幹

東京都小平市上水本町五丁目20番1号

株式会社日立製作所半導体グ

ループ内

審査官 後藤 彰

最終頁に続く

(54) 【発明の名称】データ処理装置

## (57) 【特許請求の範囲】

## 【請求項 1】

所定の命令を順次実行するデータ処理装置であって、

プログラムカウンタとスタックとレジスタ番号で指定できる複数のレジスタとを有し、

前記スタックは、データの書き込みと読み出しが可能であって、最後に格納された内容

から順次読み出しを行うことができるデータ記憶手段であり、

前記データ処理装置は、前記プログラムカウンタで指定されるアドレスに格納された命

令を実行し、前記プログラムカウンタの値を更新するものであり、

前記データ処理装置は、前記プログラムカウンタの内容を前記スタックに書き込む第1

の命令と、前記複数のレジスタの中の指定されたレジスタの内容を前記スタックに書き込

む第2の命令と、前記スタックから読み出した内容を前記プログラムカウンタに書き戻す

ことができるとともに前記複数のレジスタのうち前記スタックから内容を書き戻すべきレ

ジスタの数とレジスタ番号を指定することができる第3の命令と、前記スタックから読み

出した内容を前記プログラムカウンタに書き戻すことができるとともに前記複数のレジ

サのうち前記スタックから内容を書き戻すべきレジスタの数とレジスタ番号を指定するこ

とができる第4の命令とを実行可能であり、

前記第3の命令と前記第4の命令は、指定できるレジスタの数の取り得る値が異なるこ

とを特徴とするデータ処理装置。

## 【請求項 2】

請求項1記載のデータ処理装置であって、

10

20

レジスタ選択のための算術演算手段を備え、

前記第3の命令は、前記スタックから順次読み出した複数の内容を、前記レジスタの内、前記第3の命令コード中に指定された値とこの値を用いて前記算術演算手段によって演算された値に基づいて指定される複数のレジスタに書込むことができることを特徴とするデータ処理装置。

【請求項3】

請求項1又は2に記載のデータ処理装置であって、

前記データ処理装置は、さらに第5の命令を実行可能であり、

前記第5の命令は、前記複数のレジスタのうち前記スタックから内容を復帰すべきレジスタ番号を指定することができることを特徴とするデータ処理装置。 10

【請求項4】

請求項1乃至3の何れか1項に記載のデータ処理装置であって、

前記データ処理装置は、さらに復帰命令を実行可能であり、

前記復帰命令は、前記スタックから読み出した内容を前記プログラムカウンタに書き戻すことができることを特徴とするデータ処理装置。 20

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は、データ処理装置に関し、特に、半導体集積回路装置によって構成されるマイクロコンピュータにかかり、これらの中央処理装置(CPU)など、及びこれらを用いたデータ処理システム、更に、この開発装置に利用して有効な技術に関するものである。 20

【0002】

【従来の技術】

半導体集積回路装置の製造技術の高度化に伴って、半導体単結晶からなるシングルチップに、中央演算処理装置(Central Processing Unit; 以下、単にCPUと称する)、プログラムを格納するROM(ReadOnly Memory)、書き替え可能に各種データを格納するRAM(Random Access Memory)等を含む構成素子を集積して製造した、マイクロコンピュータが広範囲に普及してきており、種々の目的のデータ処理装置として使用されてきている。このマイクロコンピュータは、CPUが同時に処理し得る情報の量によって性能が異なり、例えば4ビット、8ビット、16ビット、32ビット等のマイクロコンピュータとして区分されている。 30

【0003】

このようなマイクロコンピュータは、アドレス空間の拡張や、命令セットの拡大、高速化等が図られてきている。また、CPUは、ソフトウェアによってその性能が定義されているから、前記のようにアドレス空間の拡張や、命令セットの拡大、高速化等を図ったマイクロコンピュータにおいても、既存のマイクロコンピュータのソフトウェア資産を有効に利用できることが望ましい。

【0004】

このため、オブジェクトレベルで互換性を保つつつ、アドレス空間の拡張や、命令セットの拡大、高速化等を実現した例として、例えば本発明者が先に提案した特開平6-51981号公報がある。これは16ビット単位の可変長命令で、いわゆる汎用レジスタ型、或いはロードストア型アーキテクチャを採用することが示されている。 40

【0005】

プログラム用のメモリであるROMを内蔵した、シングルチップ型のものにあっては、内蔵ROMの容量が、外部にメモリを接続するのに比較して、少ないから、プログラム容量を削減することが望ましい。

【0006】

16ビット単位の可変長命令を採用した場合、オペレーションコードのみを持ち、実効アドレスの指定を行わず、かつ有意味な命令として、復帰(RTS/RTT)命令がある。かかる復帰命令を16ビット単位の命令に割当てる場合、16ビットの命令コードの全て 50

のビットが利用されていない場合が多い。

【0007】

例えば、命令コードH'5470がサブルーチンからの復帰命令であって、H'5471、H'5472、H'5473が未定義（他の命令として定義されていない）とされているような場合、ビット0、ビット1は利用されていない。

【0008】

一方、本発明者らが先に提案した特開平8-263290号公報に記載のCPUは、命令を実行する実行手段を制御する制御手段に指定可能な複数の汎用レジスタの組合せを固定にし、複数の汎用レジスタのスタックに対する退避／復帰命令を有し、複数の汎用レジスタを順次待避／復帰するようにしている。汎用レジスタの組合せを固定にすることによって、汎用レジスタの指定に要するビット数を節約できる。10

【0009】

かかる退避／復帰命令は、サブルーチンや例外処理などの、処理の切れ目で、それ以前の処理の状態を保存する目的に用いられ、アドレッシングモードは、スタックポインタのブリデクリメント（待避）／ポストインクリメント（復帰）にが使用できる。

【0010】

つまり、かかる汎用レジスタの復帰命令は、前記サブルーチンまたは例外処理からの復帰命令（RTS / RET）の前に置かれることが多い。

【0011】

いわゆるアキュムレータ型アーキテクチャのCPUにおいては、サブルーチンへの分岐／サブルーチンからの復帰時に、PCに加えて、アキュムレータの退避／復帰を行う場合がある。これは、データの処理が少数のアキュムレータ上で行われ、サブルーチンのように処理が変わるとときには、アキュムレータを空ける必要があるためである。換言すれば、アキュムレータを自動的に退避／復帰を行っても、無駄にならないからである。20

【0012】

これに対して、汎用レジスタ型アーキテクチャのCPUにおいては、汎用レジスタのいずれにデータを置くかについて、自由度が高く、また、サブルーチンへの分岐／サブルーチンからの復帰時の引数が、汎用レジスタに割当てられる場合もある。このため、所定の（全部または一部の）汎用レジスタの退避／復帰を自動的に行うと、無駄になりやすい。不所望の汎用レジスタの退避／復帰によって、実行ステート数や、スタックの使用量が増加してしまうからである。30

【0013】

マイクロコンピュータのプログラムはC言語で記述されることが多くなっている。C言語で多く用いられる関数は、サブルーチンとして実現される。

【0014】

【発明が解決しようとする課題】

本発明が解決しようとする問題点は、

マイクロコンピュータなどのデータ処理装置、その論理的規模の増加を最小限にしつつ、使い勝手を向上し、プログラム容量を縮小したり、実行ステート数を短縮したりする手段を提供することにある。40

【0015】

特に、C言語などを使用したプログラムにおいて、関数を多用した場合のプログラム容量の縮小、実行ステート数の短縮を図ることである。

【0016】

また、既存のソフトウェア資産を有效地に利用可能にし、使用者の開発効率を向上するとともに、開発装置を共通に利用可能にし、開発装置の開発効率を向上するとともに、いち早く開発環境を提供可能にすることである。

【0017】

本発明の前記ならびにそのほかの目的と新規な特長は、本発明書の記述及び添付図面から明らかになるであろう。50

## 【0018】

## 【課題を解決するための手段】

本願において開示される発明のうち代表的なものの概要を簡単に説明すれば下記の通りである。

## 【0019】

本発明のデータ処理装置は、サブルーチンから、または例外処理からの復帰命令において、当該命令コードに複数の汎用レジスタを指定する情報を含み、当該命令コードの実行時に、プログラムカウンタの復帰に加えて、前記指定した汎用レジスタの復帰を行うようとする。

## 【0020】

更に、指定する汎用レジスタの組合せを連続したものにする。

10

## 【0021】

同様の指定を可能にした、汎用レジスタの退避命令を実行可能にする。

## 【0022】

上記した手段によれば、

サブルーチンから、または例外処理からの復帰命令と、汎用レジスタの復帰命令を同一の命令（例えば16ビット）とすることにより、使い勝手を向上し、プログラム容量を短縮できる。

## 【0023】

16ビット単位の可変長の命令コード体系を探る場合にも、命令プリフェッヂや命令デコードを簡易にしつつ、命令コードを有効に利用して、全体的なプログラム効率を向上できる。

20

## 【0024】

同様の指定を可能にした、汎用レジスタの退避命令を持ち、これをサブルーチン乃至例外処理ルーチンの先頭で実行し、最後に、本発明の復帰命令を実行することによって、より一層の使い勝手を向上できる。

## 【0025】

指定する汎用レジスタの組合せを固定にすることによって、汎用レジスタを指定する情報を短くでき、限られた命令コード（例えば16ビット）であっても、指定可能にできる。

## 【0026】

30

汎用レジスタの復帰と、プログラムカウンタなどの復帰を連続的に行うことによって、内部の動作を容易にし、高速化できる。

## 【0027】

## 【発明の実施の形態】

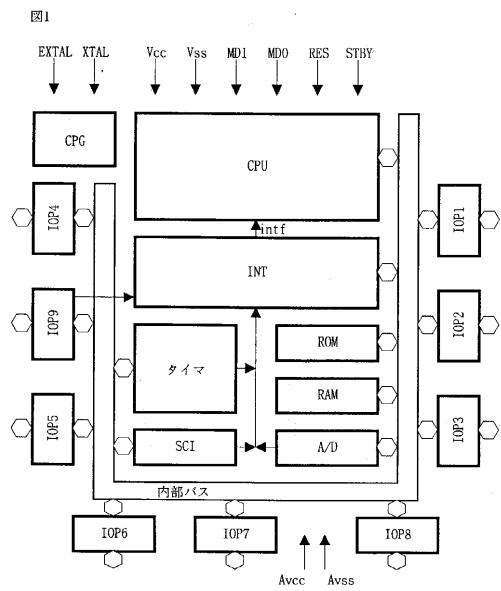

図1に、本発明の適用されたマイクロコンピュータのブロック図を示す。

## 【0028】

マイクロコンピュータは、シングルチップ型であり、全体の制御を司るCPU、割込コントローラ（INT）、CPUの処理プログラムなどを格納するメモリであるROM、CPUの作業領域ならびにデータの一時記憶用及びスタック用のメモリとすることができるRAM、タイマ、シリアルコミュニケーションインターフェース（SCI）、A/D変換器、第1乃至第9入出力ポート（IOP1～IOP9）、クロック発振器（CPG）の機能ブロック乃至はモジュールから構成され、公知の半導体製造技術により1つの半導体基板上に形成される。

40

## 【0029】

かかるマイクロコンピュータは、電源端子として、グランドレベル（Vss）、電源電圧レベル（Vcc）、アナロググランドレベル（AVss）、アナログ電源電圧レベル（AVcc）、アナログ基準電圧（Vref）、の他専用制御端子として、リセット（RES）、スタンバイ（STBY）、モード制御（MD0、MD1）、クロック入力（EXTAL、XTAL）端子を有する。

## 【0030】

50

CPGの端子EXTAL、XTALに接続される水晶発振子またはEXTAL端子に入力される外部クロックに基づいて生成される基準クロック（システムクロック）に同期して、マイクロコンピュータは動作を行う。この基準クロック1周期をステートと呼ぶ。

【0031】

マイクロコンピュータの機能ブロックは、内部バスによって相互に接続される。バスの制御を行う、図示はされないバスコントローラを内蔵している。内部バスはアドレスバス・データバスのほか、リード信号・ライト信号・バスサイズ信号を含み、これらはバスコマンドとしてコード化される。

【0032】

かかる機能ブロックやモジュールは内部バスを介して、CPUによってリード／ライトされる。内部バスのデータバス幅は32ビットとする。内蔵ROM、RAMリード／ライトを1ステートでリード／ライト可能とする。

10

【0033】

タイマ、SCI、A/D変換器、IOP1～IOP9、SYSC、INT、CPGなどがある制御レジスタを総称して、内部I/Oレジスタと呼ぶ。

【0034】

各入出力ポートは、アドレスバス、データバス、バス制御信号或いはタイマ、SCI、A/D変換器の入出力端子と兼用されている。即ち、タイマ、SCI、A/D変換器は、それぞれ入出力信号を有し、入出力ポートと兼用にされた端子介して、外部と入出力されるものである。例えばIOP5、6は、タイマの入出力端子と兼用、IOP7はSCIの入出力端子と兼用にされている。アナログデータの入出力(AIN0～AIN7)端子は、IOP8と兼用にされている。

20

【0035】

外部割込み入力は、IOP9と兼用にされている。

【0036】

かかるマイクロコンピュータにリセット信号RESが与えられると、CPUを始めとし、マイクロコンピュータはリセット状態になる。このリセットが解除されると、モード制御で指定された動作モード（シングルチップ、外部バス拡張、内蔵ROM有効など）とされ、CPUは所定のアドレス（ベクタアドレス）からスタートアドレスをリードして、このスタートアドレスから命令のリードを開始するリセット例外処理を行う。この後、CPUは逐次、ROMなどから命令をリードし、解読して、その解読内容に基づいて、フラグやビットの判定や操作を含む、データの処理或いはRAM、タイマ、SCI、A/D変換器、入出力ポートなどとのデータ転送を行う。即ち、CPUは、タイマ、SCI、A/D変換器、入出力ポートなどから入力されるデータ或いは機器の状態や指示（スイッチ、ボリュームなど）を参照しつつ、ROMなどに記憶されている命令に基づいて処理を行い、その結果に基づいて、入出力ポート、タイマなどを使用しつつ、外部に信号を出力し、機器の制御を行うものである。

30

【0037】

割込みコントローラ(INT)は、タイマ、SCI、A/D変換器、外部入力の各割込み信号を入力して、割込み要求信号をCPUに出力する。

40

【0038】

CPUに割込み要求信号が与えられると、CPUは実行中の処理を中断して、割込み例外処理状態を経て、所定の処理ルーチンに分岐し、所望の処理を行い、割込み要因をクリアしたりする。所定の処理ルーチンの最後には、通常復帰命令がおかれて、この命令を実行することによって前記中断した処理を再開する。

【0039】

割込み例外処理の実行時には、後述のプログラムカウンタ(PC)やコンディションコードレジスタ(CCR)などがRAMなどに退避され、復帰命令実行時に上記プログラムカウンタ(PC)やコンディションコードレジスタ(CCR)などが復帰される。

【0040】

50

更に、割込み処理ルーチンでは所要の処理を行うため、汎用レジスタを使用する必要がある。割込み発生直前の状態を保存するため、割込み処理ルーチンの先頭で、所要の汎用レジスタをスタックに退避する。これは、例えば、

S T M E R 0 - E R 3 , @ - S P

と記述される。割込み処理ルーチンの最後に、退避した汎用レジスタを復帰してから、復帰命令 (R T E) を実行して、割込み発生直前のプログラムを継続する。これは、従来技術では、例えば、

L D M @ S P + , E R 0 - E R 3

R T E

と記述される。

10

【0041】

本発明によれば、上記 L D M と R T E 命令を 1 命令で実行して、

R T E / 4 E R 0 - E R 3

と記述すればよいようにする。

【0042】

同様に、サブルーチンにおいても同様に、所要の処理を行うため、汎用レジスタを使用する。例えば、サブルーチンの先頭で、

S T M E R 0 - E R 1 , @ - S P

と記述し、最後に、

L D M @ S P + , E R 0 - E R 1

20

R T S

と記述される。

【0043】

本発明によれば、上記 L D M と R T E 命令を 1 命令で実行して、

R T S / 2 E R 0 - E R 1

と記述すればよいようにする。

【0044】

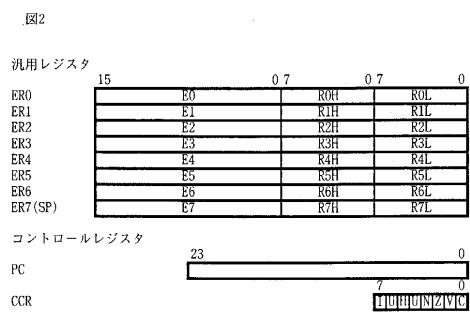

図 2 に、C P U に内蔵されている汎用レジスタ及び制御レジスタの構成例 (プログラミングモデル) を示す。

【0045】

30

C P U は、32 ビット長の汎用レジスタを 8 本持っている。汎用レジスタは、すべて同機能を持っており、アドレスレジスタとしてもデータレジスタとしても使用することができる。

【0046】

40

データレジスタとしては 32 ビット、16 ビット及び 8 ビットレジスタとして使用する。アドレスレジスタ及び 32 ビットレジスタとしては、一括して汎用レジスタ E R ( E R 0 ~ E R 7 ) として使用する。16 ビットレジスタとしては、汎用レジスタ E R を分割して汎用レジスタ E ( E 0 ~ E 7 ) 、汎用レジスタ R ( R 0 ~ R 7 ) として使用する。これらは同等の機能を持っており、16 ビットレジスタを最大 16 本まで使用することができる。なお、汎用レジスタ E ( E 0 ~ E 7 ) を、特に拡張レジスタと呼ぶ場合がある。8 ビットレジスタとしては、汎用レジスタ R を分割して汎用レジスタ R H ( R 0 H ~ R 7 H ) 、汎用レジスタ R L ( R 0 L ~ R 7 L ) として使用する。これらは同等の機能を持っており、8 ビットレジスタを最大 16 本まで使用することができる。各レジスタ独立に使用方法を選択することができる。

【0047】

汎用レジスタ E R 7 には、汎用レジスタとしての機能に加えて、スタックポインタ ( S P ) としての機能が割当てられており、例外処理やサブルーチン分岐などで暗黙的に使用される。例外処理は前記割込み処理を含む。

【0048】

P C は 24 ビットのカウンタで、C P U が次に実行する命令のアドレスを示す。特に制限

50

されないものの C P U の命令は、すべて 2 バイト (ワード) を単位としているため、最下位ビットは無効であり、命令リード時には最下位ビットは 0 とみなされる。

【 0 0 4 9 】

C C R は 8 ビットのレジスタで、割込みマスクビット (I) とハーフキャリ (H)、ネガティブ (N)、ゼロ (Z)、オーバフロー (V)、キャリ (C) の各フラグを含む。ハーフキャリ (H)、ネガティブ (N)、ゼロ (Z)、オーバフロー (V)、キャリ (C) の各フラグは転送命令や演算命令実行時に、データを検査して、その状態を反映する。ハーフキャリ (H) は 10 進補正用にのみ用いられる。

【 0 0 5 0 】

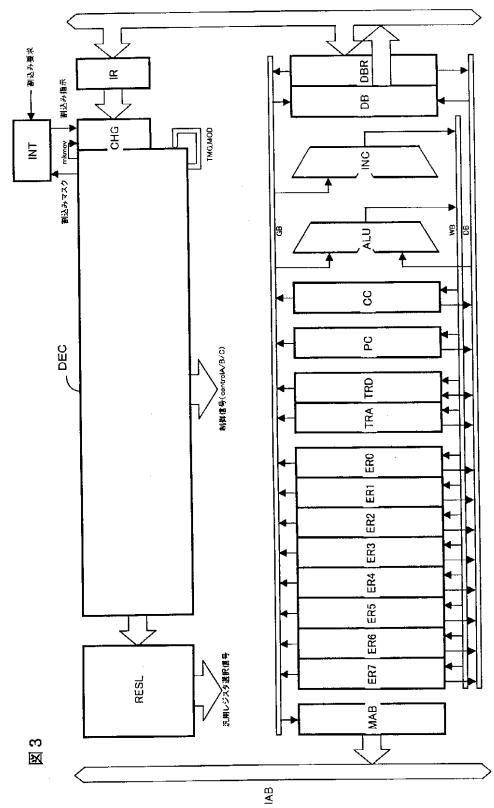

図 3 に、C P U の構成例を示す。

10

【 0 0 5 1 】

C P U は、制御部と、前記汎用レジスタ E R 0 ~ E R 3 1、プログラムカウンタ P C、コンディションコードレジスタ C C R を含む実行部から構成される。

【 0 0 5 2 】

制御部は、命令レジスタ I R、命令デコーダ D E C、レジスタセレクタ R E S L、割込受け付け回路 I N T を含む。命令デコーダ D E C は、例えば、マイクロ R O M 或 P L A ( P r o g r a m m a b l e L o g i c A r r a y ) または布線論理で構成される。命令デコーダ D E C の出力の一部が命令デコーダ D E C にフィードバックされている。これは各命令コード内の遷移に用いるステージコード (T M G) と、命令コード間に用いる制御信号 (M O D) を含む。即ち、前記 S T M 命令の第 1 ワードは汎用レジスタの本数を指定する制御信号を発生し、割込みマスク信号を出力して、割込みの受け付けを禁止する。

20

【 0 0 5 3 】

割込み制御部 I N T は、後述の図 1 の割込みコントローラの出力する割込み要求信号を受け付ける。また、命令デコーダの出力する割込みマスク信号を参照して、割込みがマスクされていなければ、命令変更部 C H G に割込みを指示し、割込み例外処理用の命令コードの実行を行わせる。

【 0 0 5 4 】

実行部には、更に、テンポラリレジスタ T R 、算術論理演算器 A L U 、インクリメンタ I N C 、リードデータバッファ D B R 、ライトデータバッファ D B W 、アドレスバッファ A B を含む。これらのブロックは G B バス、D B バス、W B バスによって相互に接続されている。

30

【 0 0 5 5 】

算術論理演算器 A L U は、命令によって指定される各種の演算や実効アドレスの計算など用いる。

【 0 0 5 6 】

インクリメンタ I N C は、主に P C の加算やアドレス計算に用いられる。

【 0 0 5 7 】

D B R は、R O M 、R A M 、内部 I / O レジスタ、或いは図示はされない外部メモリから、リードした命令コードやデータを一時的に格納する。D B W は R O M 、R A M 、内部 I / O レジスタ、或いは外部メモリへのライトデータを一時的に格納する。D B R 、D B W によって C P U 内部動作と、C P U 外部のリード / ライト動作のタイミングを調整している。

40

【 0 0 5 8 】

アドレスバッファ A B は、C P U がリード / ライトするアドレスを一時的に格納する。

【 0 0 5 9 】

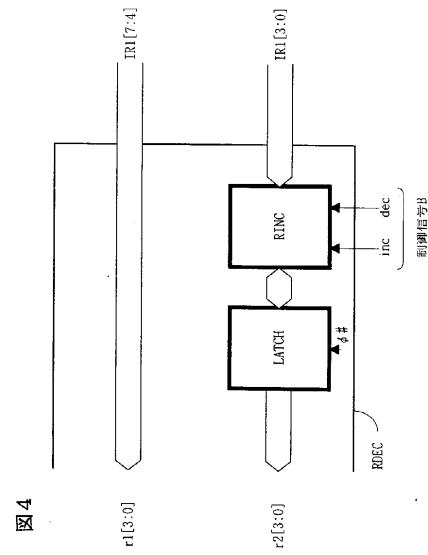

図 4 に、レジスタセレクタ R E S L の一部の詳細なブロック図を示す。

【 0 0 6 0 】

レジスタセレクタ R E S L は、レジスタフィールドを保持する I R から出力されるレジスタフィールド情報と、命令デコーダ D E C の制御信号出力を入力して、各汎用レジスタに対応するレジスタ選択信号を発生する。

50

## 【0061】

レジスタ指定フィールドは2つある(r1、r2)。

## 【0062】

第2のレジスタ指定フィールド(r2)は、IRのビット3～0と、命令デコーダの制御信号出力(in c、dec)から生成される。

## 【0063】

上記を入力したインクリメンタ(RINC)の出力が、システムクロックの反転#でラッピングされ、第2のレジスタ指定フィールド(r2)となる。

## 【0064】

例えば、

STM ER0 - ER3, @ - SP

の場合、r2の初期値として、0が与えられる。その後、後述の所定のタイミングで、インクリメント信号(in c)によって、r2は0 1 2 3とされる。

## 【0065】

また、

LDM @SP+, ER0 - ER1

または、

RTS/2 ER0 - ER1

の場合、r2の初期値として、1が与えられる。その後、後述の所定のタイミングで、インクリメント信号(dec = rd)によって、r2は1 0とされる。

## 【0066】

これによって、レジスタ選択回路自体をそのほかの命令と共通化することが、論理的規模の増加を抑止できる。

## 【0067】

r2のビット3は、これらの命令では使用しないため、インクリメンタ(RINC)は3ビットでよい。インクリメンタ(RINC)を持つことにより、さほど論理規模を大きくすることなく、連続した任意の汎用レジスタの組合せを指定可能にできる。

## 【0068】

なお、その他のRESLの詳細については省略する。

## 【0069】

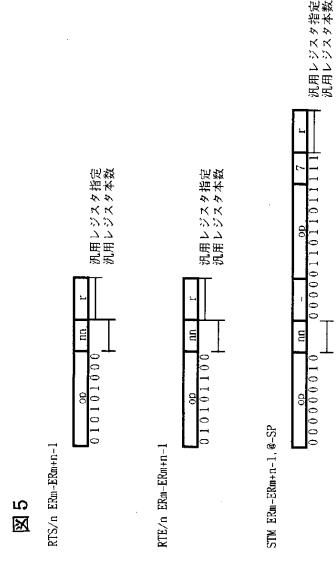

図5に、複数汎用レジスタの復帰を含む第1の復帰命令(RTS/n)、第2の復帰命令(RTE/n)の命令フォーマットを示す。

## 【0070】

第1の復帰命令(RTS/n)は、サブルーチンからの復帰命令であり、第2の復帰命令(RTE/n)は、例外処理ルーチンからの復帰命令である。

## 【0071】

ビット15～7はオペレーションフィールドであり、復帰命令を指定する。

## 【0072】

ビット6が0のときは、ビット5、4によって、汎用レジスタの本数を指定する。01のときは2本、10のときは3本、11のときは4本とする。汎用レジスタの選択は、連続した2、3、4本の選択が可能である。例えば、4本の場合には、ER0 - 3、ER1 - 4、ER2 - 5、ER3 - 6、が指定可能である。ER7は、スタックポインタと兼用であり、対象としない。

## 【0073】

ビット6が1のときは、汎用レジスタの復帰を伴わない。即ち、従来技術の復帰命令と同一であり、共通の命令コード(H'5470)とする。

## 【0074】

ビット3～0で最初に使用する汎用レジスタを指定する。ビット3は予約されているものとし、0とする。

## 【0075】

10

20

30

40

50

例えば、R T S / 4 E R 0 - 3 のときは、E R 3 から復帰されるので、H' 5 4 3 3 の命令コードとなる。

【0076】

第2の復帰命令 (R T E / n) も、オペレーションフィールドが異なるのみであり、前記同様である。

【0077】

S T M 命令の命令フォーマットは、2ワード命令であり、第2ワードのビット3～0で最初に使用する汎用レジスタを指定する。これは上記復帰命令と共通化されている。

【0078】

L D M 命令の命令フォーマットも同様である。

10

【0079】

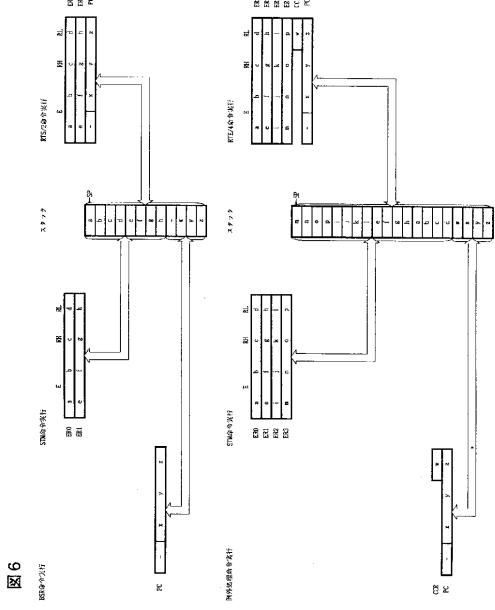

図6に、複数汎用レジスタの復帰を含む第1の復帰命令 (R T S / n)、第2の復帰命令 (R T E / n) のスタックの構成の例を示す。

【0080】

スタックはスタックポインタ (S P : E R 7) によって、スタックされた最後のアドレスが指示されている。

【0081】

サブルーチン分岐命令 (例えば、B S R 命令) によって、プログラムカウンタがスタックに退避される。その後、サブルーチンの先頭で、所要の汎用レジスタが退避される (例えば、S T M E R 0 - E R 1, @ - S P)。

20

【0082】

これに対応して、第1の復帰命令 (例えば、R T S / 2 E R 0 - E R 1) は、まず、指定した汎用レジスタの復帰として、スタックからのリードを行い、指定した汎用レジスタ (E R 1、E R 0) に順次格納する。引続き、プログラムカウンタの復帰として、スタックからのリードを行い、プログラムカウンタに格納し、この内容に従って、命令のリードを行う。

【0083】

同様に、例外処理によって、プログラムカウンタとコンディションコードレジスタがスタックに退避される。プログラムカウンタが24ビットであり、コンディションコードレジスタと組合せて、スタックに退避される。その後、サブルーチンの先頭で、所要の汎用レジスタが退避される (例えば、S T M E R 0 - E R 3, @ - S P)。

30

【0084】

これに対応して、第2の復帰命令 (例えば、R T E / 4 E R 0 - E R 3) は、まず、指定した汎用レジスタの復帰として、スタックからのリードを行い、指定した汎用レジスタ (E R 3、E R 2、E R 1、E R 0) に順次格納する。引続き、プログラムカウンタとコンディションコードレジスタの復帰として、スタックからのリードを行い、プログラムカウンタとコンディションコードレジスタに所定の内容を格納するとともに、命令のリードを行う。

【0085】

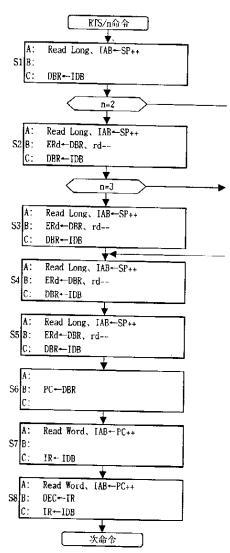

図7に、第1の復帰命令 (R T S / n) の動作フローを示す。

40

【0086】

ステップ1で、制御信号Aで、スタックポインタ (S P) の内容がアドレスバス (I A B) に出力され、ロングワードのリードが指示される。また、S Pの内容のインクリメント (+4) が指示される。制御信号Cで、リードしたデータのD B Rへの格納が指示される。

【0087】

ステップ2～5で、制御信号Bで、前のステップでリードした内容の汎用レジスタへの書き込みが指示される。具体的には、一旦、内部バスG Bに出力し、A L Uを経由して、内部バスW Bに出力し、指定された汎用レジスタに書き込まれる。レジスタセレクタR E S L に対してレジスタフィールドのデクリメント (-1) が指示される。前記同様に、制御信

50

号 A で、スタックポインタ ( S P ) の内容のアドレスバス ( I A B ) への出力と、ロングワードのリードが指示され、 S P の内容のインクリメント ( + 4 ) が指示される。制御信号 C で、リードしたデータの D B R への格納が指示される。ステップ 2 ~ 4 は、指定した汎用レジスタの本数 ( n ) に従って、所定回数が実行される。

#### 【 0 0 8 8 】

ステップ 6 で、制御信号 B で、前のステップでリードした内容のプログラムカウンタ ( P C ) への書込みが指示される。

#### 【 0 0 8 9 】

ステップ 7 で、制御信号 A で、命令リードとして、プログラムカウンタ ( P C ) の内容がアドレスバス ( I A B ) に出力され、メモリワードリードが指示される。また、 P C の内容のインクリメント ( + 2 ) が指示される。制御信号 C で、リードされた命令を I R に格納する。

10

#### 【 0 0 9 0 】

ステップ 8 で、同様に、制御信号 A で、プログラムカウンタ ( P C ) の内容のアドレスバス ( I A B ) への出力と、メモリワードリードが指示され、 P C の内容のインクリメント ( + 2 ) が指示される。制御信号 B で、前のステップでリードした命令 ( I R ) の命令デコーダへの入力が指示される。次の命令の実行が開始される。

#### 【 0 0 9 1 】

P C の復帰時、スタックからリードした内容を、一旦、 P C に格納するものとしたが、これを行わず、ステップ 7 で、 P C の代わりに、 D B R から読み出すようにしてもよい。

20

#### 【 0 0 9 2 】

汎用レジスタの復帰を行わない復帰命令の場合は、ステップ 2 ~ 5 をスキップすればよい。換言すれば、従来技術の復帰命令に、ステップ 2 ~ 5 を追加すればよい。

#### 【 0 0 9 3 】

かかる動作フローに従って、ハードウェア記述言語 ( H D L ) を記述し、命令デコーダ D E C を生成することができる。第 1 の復帰命令 ( R T S / n ) に関する部分は、以下の通りである。

#### 【 0 0 9 4 】

```

c a s e x ( o p c o d e ) (1)

1 6 ' b 0 1 0 1 0 1 0 0 _ 0 0 0 1 ? ? ? ? : b e g i n (2)

c a s e ( t m g ) (3)

4 ' b 0 0 0 1 : b e g i n (4)

n e x t t m g = 4 ' b 0 1 0 0 ; (5)

b c m d = l o n g _ r e a d ; (6)

.

.

.

e n d (7)

4 ' b 0 1 0 0 : b e g i n (8)

n e x t t m g = 4 ' b 0 1 0 1 ; (9)

b c m d = l o n g _ r e a d ; (10)

.

.

.

e n d (11)

.

.

.

e n d (12)

1 6 ' b 0 1 0 1 0 1 0 0 _ 0 0 1 0 ? ? ? ? : b e g i n (13)

c a s e ( t m g ) (14)

4 ' b 0 0 0 1 : b e g i n (15)

n e x t t m g = 4 ' b 0 0 1 0 ; (16)

.

.

.

4 ' b 0 0 1 0 : b e g i n (17) 30

n e x t t m g = 4 ' b 0 1 0 0 ; (18)

.

.

.

```

本記述は、IEEE1364として標準化されているHDL記述言語に従っている。かかるHDL記述言語自体については、1996年7月CQ出版株式会社発行の『入門Verilog-HDL記述』などに記載されている。

#### 【0095】

c a s e x 及び c a s e は、それに続く( )内の変数( o p c o d e 、 t m g )に応じて、後続の値( 1 6 ' b 0 1 0 1 0 1 0 0 \_ 0 0 0 1 ? ? ? ? : 、 4 ' b 0 0 0 1 : など) 40 に一致した動作を実行する。 b e g i n ~ e n d で 1 つの動作が記述される。

#### 【0096】

( 1 ) で、命令デコーダの入力( o p c o d e )による条件を指示する。当該条件で、( 2 ) ~ ( 1 2 ) で R T S / 2 に相当する命令コードの動作が記述される。更に、各命令コード毎に、ステップに相当する命令デコーダの入力( t m g )による条件を指示する。 R T S / 2 の第 1 ステップの動作は、( 4 ) ~ ( 7 ) に記述される。( 5 ) で、次のステップ( n e x t t m g )が第 4 ステップであることが指定される。 n e x t t m g は 1 ステップ後に、 t m g として命令デコーダに入力される。( 6 ) で、バスコマンドがロングワードリードとされる。 l o n g \_ r e a d はパラメータとして、所定のコードが割当てられるようにしておく。この後に、そのほかの制御信号が記述される。同様に、第 4 ステップ 50

ブの動作は、(8)～(11)に記述される。第5～第8ステップの動作は、これ以降(12)までに記述される。

#### 【0097】

同様に、命令デコーダの入力(o p c o d e)による条件で、(13)以降でR T S / 3に相当する命令コードの動作が記述される。第1ステップの動作記述において、(15)で、次のステップ(n e x t t m g)が第2ステップであることが指定される。また、第2ステップの動作は、(17)以降に記述される。更に、第4～第8ステップの動作も記述される。

#### 【0098】

更に、その後、R T S / 4に相当する命令コードの動作が記述され、第2の復帰命令(R T E / n)、複数レジスタの退避命令(S T M)や、その他の命令コードも記述される。

10

#### 【0099】

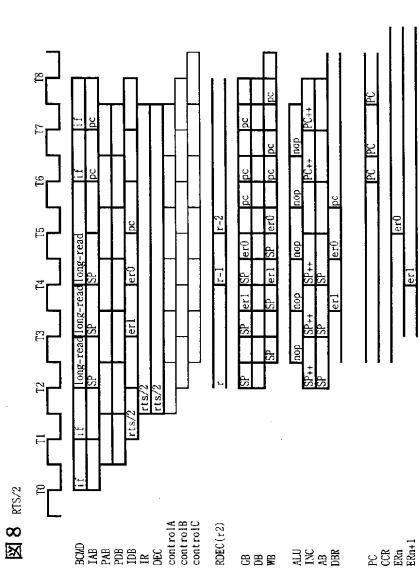

図8に、第1の復帰命令(R T S / n)の実行タイミングを示す。

#### 【0100】

n = 2の場合の例である。

#### 【0101】

特に制限はされないものの、内蔵R O M、R A Mのリード/ライトを1ステートでリード/ライト可能とし、内蔵R O M上にプログラム、内蔵R A M上にスタックを配置した場合のタイミングを示す。

#### 【0102】

20

T 0の # (#は反転論理を示す)で、C P Uのアドレスバッファ(M A B)かアドレスがI A Bに出力される。また、命令デコーダから、命令フェッチ(i f)を示す、バスコマンド(B C M D)が出力される。

#### 【0103】

T 1の #で、I A Bの内容がP A Bに出力され、バスコマンドに基づき、リードサイクルが開始され、P D Bにデータが出力される。#でP D Bのリードデータが内部データバスI D Bに得られ、これをT 2の #でI Rにラッチする。以上の動作は以前の命令の実行の制御によって行われる(プリフェッチ)。ここで、内蔵R O M、R A Mは、P A B及びP D Bに接続されていないが、P A B、P D B相当の動作をモジュール内で行い、本タイミング図には、このモジュール内の動作を示している。

30

#### 【0104】

直前の命令の実行が終了すると、最も早く命令の実行が開始される場合には、T 2の #で命令コードがD E Cに入力されて、命令の内容が解読される。解読結果に従って、制御信号を出力して、各部の制御を行う。命令の一部(レジスタ指定フィード:r)がレジスタセレクトに与えられる。

#### 【0105】

前記のステップ1として、T 2の #で、S Pの内容を内部バスG Bに読み出して、A BとI N Cに入力する。A BからアドレスI A Bが出力される。ロングワードのリードのバスコマンドが出力される。

#### 【0106】

40

T 3の #で、I N Cでインクリメント(+4)された結果が、内部バスW Bを経由してS Pにライトされる。T 3の #から、スタックからリードしたデータがI D Bに出力され、T 4の #で、D B Rに格納される。

#### 【0107】

ステップ4として、T 4の #で、D B Rの内容が内部バスG B、A L U、内部バスW Bを介して、指定(r)した汎用レジスタに書き込まれる。レジスタ指定フィールドがデクリメントされる。前記同様に、T 3の #で、S Pの内容を内部バスG Bに読み出して、A BとI N Cに入力する。A BからアドレスI A Bが出力される。ロングワードのリードのバスコマンドが出力される。T 4の #で、I N Cでインクリメント(+4)された結果が、内部バスW Bを経由してS Pにライトされる。T 4の #から、スタックからリ

50

ードしたデータが I D B に出力され、T 5 の で、D B R に格納される。

【0108】

ステップ5として、T 5 の 及び # で、D B R の内容が内部バスG B、A L U、内部バスW Bを介して、指定(r)した汎用レジスタに書き込まれる。レジスタ指定フィールドがデクリメントされる。前記同様に、T 4 の # で、S P の内容を内部バスG B に読み出して、A B とI N C に入力する。A B からアドレスI A B が出力される。ロングワードのリードのバスコマンドが出力される。T 5 の で、I N C でインクリメント(+4)された結果が、内部バスW B を経由してS P にライトされる。T 5 の # から、スタックからリードしたデータが I D B に出力され、T 6 の で、D B R に格納される。

【0109】

ステップ6として、T 6 の 及び # で、D B R の内容が内部バスG B、A L U、内部バスW Bを介して、P C に書き込まれる。

【0110】

ステップ7として、T 6 の # で、P C の内容を内部バスG B に読み出して、A B とI N C に入力する。A B からアドレスI A B が出力される。T 7 の で、I N C でインクリメント(+2)された結果が、内部バスW B を経由してP C にライトされる。

【0111】

ステップ8として、T 7 の # で、P C の内容を内部バスG B に読み出して、A B とI N C に入力する。A B からアドレスI A B が出力される。T 8 の で、I N C でインクリメント(+2)された結果が、内部バスW B を経由してP C にライトされる。T 8 の でリードした命令コードが、I R を経由して、D E C に入力されて、次の命令が実行される。

【0112】

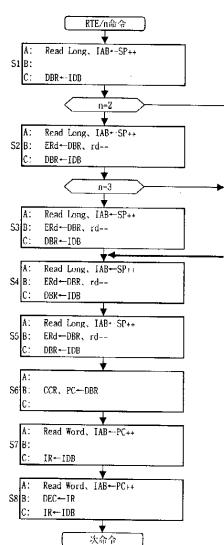

図9に、第2の復帰命令(R T E / n)の動作フローを示す。

【0113】

第1の復帰命令(R T S / n)に対して、ステップ6で、P C とともに、C C Rへの書き込みが行われるようにされる。そのほかの動作は同様にできる。

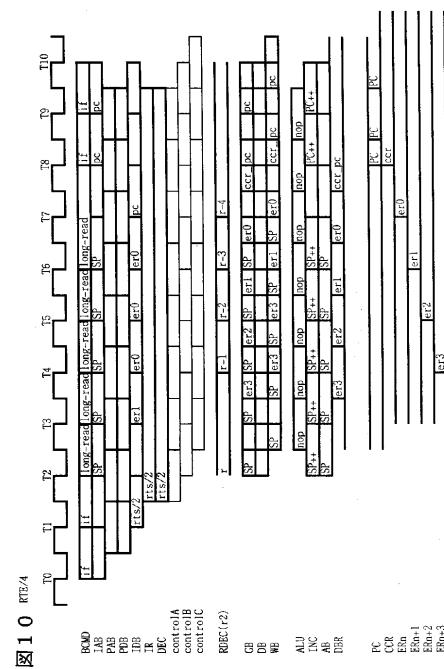

【0114】

図10に、第2の復帰命令(R T E / n)の実行タイミングを示す。

【0115】

n = 4 の場合の例である。

【0116】

前記同様に、T 2 の で命令コードがD E C に入力されて、命令の内容が解読される。解読結果に従って、制御信号を出力して、各部の制御を行う。命令の一部(レジスタ指定フィールド:r)がレジスタセレクトに与えられる。

【0117】

前記のステップ1として、T 2 の # で、S P の内容を内部バスG B に読み出して、A B とI N C に入力する。A B からアドレスI A B が出力される。ロングワードのリードのバスコマンドが出力される。

【0118】

T 3 の で、I N C でインクリメント(+4)された結果が、内部バスW B を経由してS P にライトされる。T 3 の # から、スタックからリードしたデータが I D B に出力され、T 4 の で、D B R に格納される。

【0119】

ステップ2として、T 4 の 及び # で、D B R の内容が内部バスG B、A L U、内部バスW Bを介して、指定(r)した汎用レジスタに書き込まれる。レジスタ指定フィールドがデクリメントされる。前記同様に、T 3 の # で、S P の内容を内部バスG B に読み出して、A B とI N C に入力する。A B からアドレスI A B が出力される。ロングワードのリードのバスコマンドが出力される。T 4 の で、I N C でインクリメント(+4)された結果が、内部バスW B を経由してS P にライトされる。T 4 の # から、スタックからリードしたデータが I D B に出力され、T 5 の で、D B R に格納される。

10

20

30

40

50

## 【0120】

ステップ3として、T5の及び#で、DBRの内容が内部バスGB、ALU、内部バスWBを介して、指定(r)した汎用レジスタに書き込まれる。レジスタ指定フィールドがデクリメントされる。前記同様に、T4の#で、SPの内容を内部バスGBに読み出して、ABとINCに入力する。ABからアドレスIABが outputされる。ロングワードのリードのバスコマンドが outputされる。T5の#で、INCでインクリメント(+4)された結果が、内部バスWBを経由してSPにライトされる。T5の#から、スタックからリードしたデータがIDBに出力され、T6の#で、DBRに格納される。

## 【0121】

ステップ4として、T6の及び#で、DBRの内容が内部バスGB、ALU、内部バスWBを介して、指定(r)した汎用レジスタに書き込まれる。レジスタ指定フィールドがデクリメントされる。前記同様に、T5の#で、SPの内容を内部バスGBに読み出して、ABとINCに入力する。ABからアドレスIABが outputされる。ロングワードのリードのバスコマンドが outputされる。T6の#で、INCでインクリメント(+4)された結果が、内部バスWBを経由してSPにライトされる。T6の#から、スタックからリードしたデータがIDBに出力され、T7の#で、DBRに格納される。

10

## 【0122】

ステップ5として、T7の及び#で、DBRの内容が内部バスGB、ALU、内部バスWBを介して、指定(r)した汎用レジスタに書き込まれる。レジスタ指定フィールドがデクリメントされる。前記同様に、T6の#で、SPの内容を内部バスGBに読み出して、ABとINCに入力する。ABからアドレスIABが outputされる。ロングワードのリードのバスコマンドが outputされる。T7の#で、INCでインクリメント(+4)された結果が、内部バスWBを経由してSPにライトされる。T7の#から、スタックからリードしたデータがIDBに出力され、T6の#で、DBRに格納される。

20

## 【0123】

ステップ6として、T6の及び#で、DBRの内容が内部バスGB、ALU、内部バスWBを介して、CCRとPCに書き込まれる。DBRのビット31~24がCCRに、ビット23~0がPCに書き込まれる。

## 【0124】

ステップ7として、T8の#で、PCの内容を内部バスGBに読み出して、ABとINCに入力する。ABからアドレスIABが outputされる。T9の#で、INCでインクリメント(+2)された結果が、内部バスWBを経由してPCにライトされる。

30

## 【0125】

ステップ8として、T9の#で、PCの内容を内部バスGBに読み出して、ABとINCに入力する。ABからアドレスIABが outputされる。T10の#で、INCでインクリメント(+2)された結果が、内部バスWBを経由してPCにライトされる。T10の#でリードした命令コードが、IRを経由してDECに入力されて、次の命令が実行される。

## 【0126】

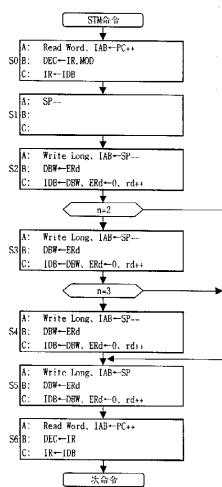

図11に、複数汎用レジスタの退避命令(STM)の動作フローを示す。

40

## 【0127】

ステップ0は、命令コードの第1ワードで制御される。制御信号Aで、プログラムカウンタ(PC)の内容のアドレスバス(IAB)への出力と、メモリワードリードが指示され、PCの内容のインクリメント(+2)が指示される。制御信号Bで、命令コードの第2ワードの命令デコーダへの入力と、第1ワードで指定される汎用レジスタ本数の情報(MOD)が指示される。

## 【0128】

ステップ1で、制御信号Aで、スタックポインタ(SP)の内容のデクリメント(-4)が指示される。ステップ2~5で、制御信号Aで、スタックポインタ(SP)の内容のアドレスバス(IAB)への出力と、ロングワードのライトが指示される。制御信号Bで

50

、汎用レジスタの内容の D B Wへの格納が指示される。制御信号 C で、 D B Wの内容の I D Bへの出力が指示される。レジスタセレクタ R E S L に対してレジスタフィールドのインクリメント ( - 1 ) が指示される。ステップ 2 ~ 4 は、 S P の内容のデクリメント ( - 4 ) が指示される。ステップ 2 ~ 5 は、指定した汎用レジスタの本数 ( n ) に従って、所定回数が実行される。

【 0 1 2 9 】

ステップ 6 で、制御信号 A で、プログラムカウンタ ( P C ) の内容のアドレスバス ( I A B ) への出力と、メモリワードリードが指示され、 P C の内容のインクリメント ( + 2 ) が指示される。制御信号 B で、前のステップでリードした命令 ( I R ) の命令デコーダへの入力が指示される。次の命令の実行が開始される。 10

【 0 1 3 0 】

ステップ 2 ~ 5 において、汎用レジスタの内容を、 D B W に転送後、当該汎用レジスタの内容を 0 にクリアするようにするとよい。汎用レジスタを退避した後、 0 にクリアし、その内容を確定することで、その後の処理を簡略化することができる。

【 0 1 3 1 】

例えば、その後、汎用レジスタに 0 を代入する場合、 M O V 命令を省略できる。また、 1などを代入する場合は、

M O V . L # 1 , E R n

を使用する代わりに、

M O V . B # 1 , R n L

を使用することができる。イミディエイトデータは、そのデータサイズに対応した領域を命令コードに持つから、 M O V . L の命令コード長 ( 例えば 3 ワード ) よりも、 M O V . B の命令コード長 ( 例えば 1 ワード ) の方が短い。これによって、プログラム容量の短縮に寄与できる。 20

【 0 1 3 2 】

なお、プログラム中に使用する定数値は、 0 や 1 などの比較的小さい値が多いことが一般的である。

【 0 1 3 3 】

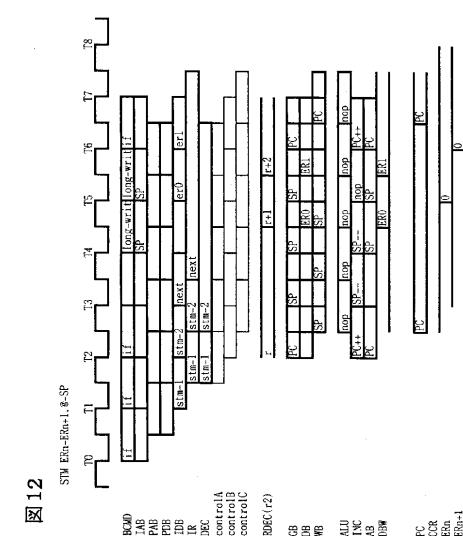

図 12 に、複数汎用レジスタの退避命令 ( S T M ) の実行タイミングを示す。

【 0 1 3 4 】

n = 2 の場合の例である。

【 0 1 3 5 】

T 2 の で命令コードの第 1 ワード ( s t m - 1 ) が D E C に入力されて、命令の内容が解読される。解読結果に従って、制御信号を出力して、各部の制御を行う。命令の一部 ( レジスタ指定フィード : r ) がレジスタセレクトに与えられる。 30

【 0 1 3 6 】

ステップ 0 として、 T 2 の # で、 P C の内容を内部バス G B に読み出して、 A B と I N C に入力する。 A B からアドレス I A B が出力される。 T 2 の で、 I N C でインクリメント ( + 2 ) された結果が、内部バス W B を経由して P C にライトされる。 T 3 の でリードした命令コードが、 I R を経由して、 D E C に入力されて、次の命令が実行される。 40

【 0 1 3 7 】

T 3 の で命令コードの第 2 ワード ( s t m - 2 ) が D E C に入力されて、命令の内容が解読される。解読結果に従って、制御信号を出力して、各部の制御を行う。命令の一部 ( レジスタ指定フィード : r ) がレジスタセレクトに与えられる。

【 0 1 3 8 】

前記のステップ 1 として、 T 3 の # で、 S P の内容を内部バス G B に読み出して、 I N C に入力する。 T 3 の で、 I N C でデクリメント ( - 4 ) された結果が、内部バス W B を経由して S P にライトされる。

【 0 1 3 9 】

ステップ 2 として、 T 4 の # で、 S P の内容を内部バス G B に読み出して、 A B と I N 50

Cに入力する。A Bからアドレス I A Bが出力される。ロングワードのライトのバスコマンドが出力される。T 5の #で、INCでデクリメント(-4)された結果が、内部バスWBを経由してSPにライトされる。また、指定(r)した汎用レジスタの内容が内部バスDBを介してDBWに書込まれる。レジスタ指定フィールドがインクリメントされる。T 5の #から、DBWの内容がIDBに出力される。

【0140】

ステップ5として、T 5の #で、SPの内容を内部バスGBに読み出して、ABを介してアドレス I A Bが出力される。ロングワードのライトのバスコマンドが出力される。T 5の #で、指定(r)した汎用レジスタの内容が内部バスDBを介してDBWに書込まれる。レジスタ指定フィールドがインクリメントされる。T 5の #から、DBWの内容がIDBに出力される。

10

【0141】

ステップ6として、T 6の #で、PCの内容を内部バスGBに読み出して、ABとINCに入力する。ABからアドレス I A Bが出力される。T 7の #で、INCでインクリメント(+2)された結果が、内部バスWBを経由してPCにライトされる。プリフェッヂした命令コード(next)が、IRを経由して、DECに入力されて、次の命令が実行される。

【0142】

前記の通り、ステップ2～5において、T 5、T 6の #で、汎用レジスタの内容を0にクリアする。これは、当該タイミングの内部バスWBを0とし、これを汎用レジスタに書き込むようにするとよい。

20

【0143】

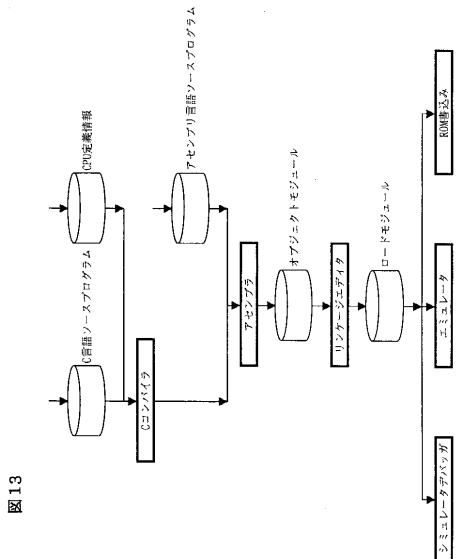

図13に、本発明のCPUの開発環境の概略を示す。

【0144】

使用者は、各種エディタなどを用いて、C言語乃至アセンブリ言語でプログラムを作成する。これは通常、複数のモジュールに分割して作成される。

【0145】

Cコンパイラは、使用者の作成したそれぞれのC言語ソースプログラムを入力し、アセンブリ言語ソースプログラム乃至オブジェクトモジュールを出力する。

【0146】

30

例えば、C言語でプログラムを作成する場合、

```

void seq0 (void)

{

...

}

```

と記述された関数 seq0 は、本発明のCPUに対しては、以下のようにコンパイルされる。

【0147】

40

```

_seq0:

```

```

STM      ER3-4, @-SP

```

```

...

```

```

RTS/2      ER3-4

```

関数内で使用する汎用レジスタ ER3、ER4をSTM命令でスタックに退避し、0にクリアされる。復帰命令時にスタックから回復される。

【0148】

また、メインプログラムで上記関数 seq0 を呼び出す場合は、

50

`s e q 0 ( ) ;`

と記述され、

`J S R @_s e q 0`

とサブルーチン分岐命令にコンパイルされる。

【0149】

アセンブラーは、アセンブリ言語ソースプログラムを入力し、オブジェクトモジュールを出力する。

【0150】

リンクエディタは、上記Cコンパイラやアセンブラーの生成した、複数のオブジェクトモジュールを入力して、各モジュールの外部参照や相対アドレスなどの解決を行い、1つのプログラムに結合して、ロードモジュールを出力する。

10

【0151】

ロードモジュールは、シミュレータ/デバッガに入力して、パーソナルコンピュータなどのシステム開発装置上で、CPUの動作をシミュレーションし、実行結果を表示し、プログラムの解析や評価を行うことができる。また、エミュレータに入力して、実際の応用システム上などで動作する、いわゆるインサーキットエミュレーションを行ない、マイクロコンピュータ全体としての、実動作の解析や評価を行うことができる。

【0152】

更に、ロードモジュールをPROMライタなどのROM書き込み装置に入力して、マイクロコンピュータの内蔵ROMがフラッシュメモリなどの場合や、外部のフラッシュメモリなどに、作成したプログラムをロードすることができる。或いはマイクロコンピュータの製造工程で、内蔵ROMに書込むことも可能である。必要に応じて、オブジェクトコンバータなどによって、所望のフォーマットに変換する。

20

【0153】

このほかに、ライブラリアンとして、汎用的なサブルーチンなどを提供することもできる。

【0154】

CPU定義情報ファイルは、コンパイル対象のCPUを指定し、本発明の復帰命令を持たない(既存の)CPUと、本発明のCPUとを共通の開発環境を利用可能にする。

30

【0155】

例えば、CPU定義情報ファイルに、

`S E T C P U = C P U 1 ;`

と記述することによって、本発明のCPUを選択するようとする。

【0156】

コンパイル時に、かかるCPU定義情報ファイルを参照し、本発明の復帰命令を持たないCPUが選択されていれば、前記関数は、

`_s e q 0 :`

`STM E R 3 - 4, @ - S P`

`M O V . L # 0, E R 3`

`M O V . L # 0, E R 4`

40

`. . .`

`L D M @ S P +, E R 3 - 4`

`R T S`

となる。MOV.Lは、当該関数の処理内容に従って、変更になる場合もある。

【0157】

Cコンパイラ自体には、C言語によるプログラムを、CPUの命令に変換する機能のほか

50

、 C + + 言語によるプログラムのコンパイルや、モジュール間最適化などといった、 C P U の命令セットとは直接関係のない機能の向上が図られているが、 C P U 毎の個別のコンパイラでは、これらの機能向上を全ての個別のコンパイラに適用しなければならない。本発明のように、共通の C コンパイラとしておけば、前記、 C P U の命令セットとは直接関係のない機能向上を図ることが容易になり、また、開発効率などを向上することができる。

#### 【 0 1 5 8 】

上記実施例によれば、以下の作用効果を得るものである。

#### 【 0 1 5 9 】

单一の命令で、複数の汎用レジスタと復帰動作と、サブルーチンまたは例外処理ルーチンからの復帰動作を行うことによって、相対的に、命令コード長を短縮（例えば、2ワード短縮）し、命令のリード回数を低減して、高速化することができる。

10

#### 【 0 1 6 0 】

例えば、 C 言語などで多用される関数はサブルーチンとされるから、この数に対応する数のサブルーチンからの復帰命令が使用されることになる。関数毎に必要なデータが汎用レジスタに割当てられるから、それ以前の汎用レジスタの内容の退避／復帰を伴う。従って、かかる復帰命令による命令コード長の短縮効果も大きくなる。

#### 【 0 1 6 1 】

また、関数毎に、退避／復帰する汎用レジスタ本数も異なるから、レジスタの本数の異なる命令を複数命令サポートすることによって、或いは、汎用レジスタの復帰を伴わない復帰命令もサポートして、プログラムの作成を容易にし、使い勝手を向上することができる。

20

#### 【 0 1 6 2 】

C P U の有する汎用レジスタ本数が多い場合にも、復帰する汎用レジスタを指定可能にしているから、汎用レジスタの使用方法の自由度を損なうことが少ない。また、不所望の汎用レジスタの退避／復帰を行ったりするこがない。

#### 【 0 1 6 3 】

複数の汎用レジスタを指定する固定の組合せにすることによって、命令コード長を短縮でき、更に、各命令の実行ステート数を固定にすることにより、内部の条件分岐を行うことを少なくし（命令デコーダの入力 o p c o d e に応じて、デコーダを記述すればよい）、内部論理を簡潔にし、論理規模を縮小できる。マイクロプログラムによらず、ワイヤードロジックなどでも容易に実現できる。マイクロプログラムによらず、ワイヤードロジックなどとすることにより、論理回路の高速化に寄与することができる。レジスタセレクタにインクリメンタを持つことによって、論理的規模の増加を最小限にして、連続した任意の組合せを指定可能にできる。

30

#### 【 0 1 6 4 】

同様の指定を可能にした、汎用レジスタの退避命令（ S T M ）を持ち、これをサブルーチン乃至例外処理ルーチンの先頭で実行し、最後に、本発明の復帰命令を実行することによって、より一層の使い勝手を向上できる。汎用レジスタの退避命令実行時に、退避後に汎用レジスタをクリアすることにより、更に、命令コード長を短縮し、実行ステート数を短縮できる。

40

#### 【 0 1 6 5 】

また、データのリード／ライトを連続して行うことによって、メモリに対するバースト動作などやバス幅を拡張する場合にも、これらを有効に利用しやすい。

#### 【 0 1 6 6 】

ソースプログラムレベルまたはオブジェクトプログラムレベルで、既存の C P U の命令セットを包含した上で、上記命令を追加することによって、ソフトウェア資産を有効に利用することができ、使用者のソフトウェア開発効率を向上することができる。ソースプログラムレベルまたはオブジェクトプログラムレベルで互換性を保つことによる利点と前記転送命令を追加することの利点の双方を享受することができる。

50

**【0167】**

以上本発明者等によってなされた発明を実施例に限定されるものではなく、その要旨を逸脱しない範囲において種々変更可能である。

**【0168】**

命令コードは一例であり、種々変更が可能である。既存の命令セットに追加するほか、新規の命令セットを開発する場合に適用することが可能であることは言うまでもない。

**【0169】**

例外処理におけるスタックの構造は、CCRとPCを組合せて32ビットとしたが、これらは、16ビットと32ビットに分割したり、そのほかのコントロールレジスタを追加したりすることもできる。PCも32ビットとしてもよい。

10

**【0170】**

汎用レジスタの構成や本数など、或いは復帰命令で復帰する汎用レジスタの本数などは任意に変更できる。復帰する汎用レジスタの本数は1本でもよい。スタックに格納される順序なども任意に変更できる。汎用レジスタを復帰する場合、PC(及びCCR)と連続してリードする方が都合がよい。

**【0171】**

インクリメンタ(RINC)も、インクリメント/デクリメントを行うほか、命令デコーダの出力との加算/減算を行うようにしてもよい。本発明の復帰命令の場合、命令コードのレジスタ指定フィールドに対して、1/2/3を順次減算するようにしてもよい。命令コード中に含まれるレジスタ指定フィールドも、最初に指定する汎用レジスタに対応している必要は必ずしもない。前記加算/減算と組合せて、所望の汎用レジスタを指定できればよい。

20

**【0172】**

復帰する汎用レジスタとして、スタックポインタであるER7が指定された場合は、ER7への書き込みを禁止するとよい。スタックポインタの退避/復帰は意味がなく、所定のポイント動作を行えばよいからである。

**【0173】**

汎用レジスタの退避命令実行時に、退避後に汎用レジスタをクリアする命令と、保持する命令の両方を持ってよい。当該命令コードの第1ワードの所定のビットでこれを指定して、制御信号(MOD)を発生して、第2ワードの動作を変更するようにすればよい。

30

**【0174】**

汎用レジスタのクリアの内容は0に限定されず、他の値にしてもよい。クリアする内容を指定する手段を別に設けてよい。

**【0175】**

命令の基本単位も16ビットに限定されない。8ビット単位、32ビット単位でも、本発明の復帰命令は適用可能である。

**【0176】**

簡単のために、バス幅を32ビットとし、命令リードを16ビット単位としたが、命令リードを32ビット単位にして高速化することができる。このような例は、特願平11-167812に記載されている。また、バス幅を16ビットとして、ロングワードのリード/ライトを、ワード単位の2回のリード/ライトで実行するようにしてもよい。このような例は、特願平11-320518に記載されている。

40

**【0177】**

マイクロコンピュータのその他の機能ブロックについても何等制約されない。

**【0178】**

以上の説明では主として本発明者によってなされた発明をその背景となった利用分野であるマイクロコンピュータに適用した場合について説明したが、それに限定されるものではなく、その他のデータ処理装置にも適用可能であり、本発明は少なくとも、複数のレジスタ手段を有するデータ処理装置に適用することができる。

**【0179】**

50

**【発明の効果】**

本題において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば下記の通りである。

**【0180】**

サブルーチンから、または例外処理からの復帰命令において、当該命令コードに複数の汎用レジスタを指定する情報を含み、当該命令コードの実行時に、プログラムカウンタの復帰に加えて、前記指定した汎用レジスタの復帰を行うようにすることにより、使い勝手を向上し、プログラム容量と実行ステート数を短縮できる。

**【0181】**

更に、指定する汎用レジスタの組合せを連続したものにすることにより、命令コード長を短縮でき、更に、各命令の実行ステート数を固定にすることにより、内部の条件分岐を行うことを少なくし、内部論理を簡潔にし、論理規模を縮小できる。16ビット単位の可変長の命令コード体系を採る場合にも、命令プリフェッчや命令デコードを簡易にしつつ、命令コードを有効に利用して、全体的なプログラム効率を向上できる。

**【0182】**

同様の指定を可能にした、汎用レジスタの退避命令を持ち、これをサブルーチン乃至例外処理ルーチンの先頭で実行し、最後に、本発明の復帰命令を実行することによって、より一層の使い勝手を向上できる。

**【0183】**

汎用レジスタの復帰と、プログラムカウンタなどの復帰を連続的に行うことによって、内部の動作を容易にし、高速化できる。

**【0184】**

レジスタの本数の異なる復帰命令を複数サポートすることによって、また、連続した汎用レジスタの指定を可能にして、更に、プログラムの作成を容易にし、使い勝手を向上することができる。

**【図面の簡単な説明】**

【図1】本発明の適用されたマイクロコンピュータのブロック図。

【図2】CPUに内蔵されている汎用レジスタ及び制御レジスタの構成例の図。

【図3】CPUの構成例の図。

【図4】レジスタセレクタRESLの一部の詳細ブロック図。

【図5】複数汎用レジスタの復帰を含む第1の復帰命令(RTS/n)、第2の復帰命令(RTE/n)の命令フォーマット図。

【図6】複数汎用レジスタの復帰を含む第1の復帰命令(RTS/n)、第2の復帰命令(RTE/n)のスタックの構成例の図。

【図7】第1の復帰命令(RTS/n)の動作フローの図。

【図8】第1の復帰命令(RTS/n)の実行タイミングの図。

【図9】第2の復帰命令(RTE/n)の動作フローの図。

【図10】第2の復帰命令(RTE/n)の実行タイミングの図。

【図11】複数汎用レジスタの退避命令(STM)の動作フローの図。

【図12】複数汎用レジスタの退避命令(STM)の実行タイミングの図。

【図13】本発明のCPUの開発環境の概略図。

10

20

30

40

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

図7

【図8】

【図9】

図9

【図10】

図10

【図11】

図11

【図12】

図12

【図 13】

---

フロントページの続き

(56)参考文献 特開平5 - 6281 (JP, A)

特開平8 - 263290 (JP, A)

特開平2 - 103632 (JP, A)

特開平5 - 127905 (JP, A)

特開昭57 - 105045 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G06F 9/40 - 9/42

G06F 9/30 - 9/355