#### (19) World Intellectual Property Organization

International Bureau

(43) International Publication Date 21 May 2004 (21.05.2004)

**PCT**

# (10) International Publication Number WO 2004/042813 A1

(51) International Patent Classification<sup>7</sup>: H01L 21/311, 21/3213

JONES, Steven; P.O. Box 62468, Sunnyvale, CA 94088 (US).

(21) International Application Number:

PCT/US2003/033217

(74) Agents: BERNADICOU, Michael, A. et al.; Blakeley, Sokoloff, Taylor & Zafman, LLP, 12400 Wilshire Boulevard, 7th Floor, Los Angeles, CA 90025 (US).

(22) International Filing Date: 20 October 2003 (20.10.2003)

English

(81) Designated States (national): CN, JP.

(26) Publication Language: English

(84) Designated States (regional): European patent (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HU, IE, IT, LU, MC, NL, PT, RO, SE, SI, SK, TR).

(30) Priority Data: 10/286,297

(25) Filing Language:

31 October 2002 (31.10.2002) US

**Published:**

(71) Applicant: APPLIED MATERIALS, INC. [US/US];

with international search report

P.O. Box 450A, Santa Clara, CA 95052 (US).

before the expiration of the time limit for amending the claims and to be republished in the event of receipt of amendments

(72) Inventors: DU, Yan; 1505 DeRose Way, Apt. #19, San Jose, CA 95126 (US). DESHMUKH, Shashank, C.; 2168 Pettigrew Drive, San Jose, CA 95148 (US). SHEN, Meihua; 694 Perry Common, Fremont, CA 94539 (US).

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

(54) Title: METHOD OF ETCHING A SILICON-CONTAINING DIELECTRIC MATERIAL

(57) Abstract: Disclosed herein is a method of pattern etching a layer of a silicon-containing dielectric material. The method employs a plasma source gas comprising  $CH_2F_2$  to  $CF_4$  is within the range of about 1:2 to about 3:1, and where  $O_2$  comprises about 2 to about 20 volume % of the plasma source gas. Etching is performed at a process chamber pressure within the range of about 4 mTorr to about 10mTorr. The method provides a selectivity for etching a silicon-containing dielectric layer relative to photoresist of at least 2:1. The method also provides an etch profile sidewall angle ranging from about  $84^{\circ}$  to about  $90^{\circ}$  between the etched silicon-containing dielectric layer and an underlying horizontal layer in a semiconductor structure.

| 1<br>2 | [0001]      | METHOD OF ETCHING A SILICON-CONTAINING DIELECTRIC MATERIAL                              |

|--------|-------------|-----------------------------------------------------------------------------------------|

| 3      | [0002]      | BACKGROUND OF THE INVENTION                                                             |

| 4      | [0003]      | 1. Field of the Invention                                                               |

| 5      | [0004]      | The present invention pertains to a method of etching a silicon-containing              |

| 6      | dielectric  | material. In particular, the invention pertains to a method of pattern etching a        |

| 7      | layer of a  | silicon-containing dielectric material for use as a hard mask for subsequent pattern    |

| 8      | etching o   | f underlying layers in a semiconductor structure.                                       |

|        |             |                                                                                         |

| 9      | [0005]      | 2. Brief Description of the Background Art                                              |

| 10     | [0006]      | Silicon-containing dielectric materials (such as silicon nitride, silicon oxide, and    |

| 11     | silicon ox  | ynitride) are often used as hard masks for pattern etching of underlying layers in      |

| 12     | a semicon   | ductor structure. The silicon-containing dielectric layer itself is typically patterned |

| 13     | using an    | overlying, patterned photoresist. Selectivity for etching the silicon-containing        |

| 14     | dielectric  | layer relative to an overlying, organic photoresist is important during the mask        |

| 15     | patterning  | g step. As used herein, the term "selectivity" or "etch selectivity" refers to a ratio  |

| 16     | of the etc  | h rate of a first material (e.g., a silicon-containing dielectric material) to the etch |

| 17     | rate of a s | econd material (e.g., photoresist) using a given plasma source gas and processing       |

| 18     | condition   | s.                                                                                      |

| 19     | [0007]      | Conventional plasma etch processes for pattern etching silicon-containing               |

dielectric materials utilize a source gas which is a combination of CF<sub>4</sub> and CH<sub>2</sub>F<sub>2</sub>. While

this etch chemistry typically provides good (at least 2:1) selectivity for etching the silicon-

containing dielectric layer relative to the overlying photoresist, the resulting etch profile of

the silicon-containing dielectric layer is typically tapered, as shown with reference to layer

110 in Figure 1B. Because the silicon-containing dielectric layer will be used as a hard

20

21

22

23

24

25

patterned etch profile of the silicon-containing dielectric layer exhibit a sidewall angle, with respect to a horizontal base, which is as close to 90° as possible (typically about 88° to about 92°). Any deviation from a substantially 90° etch profile will be reflected in the etch profiles of the underlying layers.

#### [0008] SUMMARY OF THE INVENTION

[0009] We have discovered a method of pattern etching a layer of a silicon-containing dielectric material which provides both good selectivity for etching the silicon-containing dielectric layer relative to photoresist and excellent etch profile control. The silicon-containing dielectric material is typically silicon nitride, but may alternatively be silicon oxide or silicon oxynitride, for example and not by way of limitation. The method is particularly useful for feature sizes in the range of about 0.13  $\mu$ m to about 0.25  $\mu$ m.

[0010] The source gas used for plasma etching the silicon-containing dielectric material includes CF<sub>4</sub>, CH<sub>2</sub>F<sub>2</sub>, and O<sub>2</sub>. Carbon tetrafluoride (CF<sub>4</sub>) provides an excellent source of fluorine etchant species, while CH<sub>2</sub>F<sub>2</sub> provides polymer generation and passivation of

includes CF<sub>4</sub>, CH<sub>2</sub>F<sub>2</sub>, and O<sub>2</sub>. Carbon tetrafluoride (CF<sub>4</sub>) provides an excellent source of fluorine etchant species, while CH<sub>2</sub>F<sub>2</sub> provides polymer generation and passivation of exposed photoresist surfaces, extending the lifetime of the photoresist. However, as the volumetric ratio of CH<sub>2</sub>F<sub>2</sub> to CF<sub>4</sub> increases, the etch profile of the silicon-containing dielectric layer becomes more tapered. For example, in a pattern of lines and spaces, the width of a trench etched into the silicon-containing dielectric is wider at the top of the line than at the interface with the underlying substrate. As a result, the line produced after etching is wider at the interface with the underlying substrate than at the top of the line. The sidewall angle of the etched line with respect to the horizontal base typically may be 80° or less. The addition of a small amount of O<sub>2</sub> (typically, less than 20 % by volume of the plasma source gas) assists in profile control. However, the presence of O<sub>2</sub> in the plasma source gas reduces the selectivity for etching the silicon-containing dielectric material relative to the photoresist, resulting in more rapid erosion of the photoresist.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

Therefore, it is important to achieve a balance between etch profile of the etched [0011] line and photoresist preservation. We have discovered that a volumetric ratio of CH<sub>2</sub>F<sub>2</sub> to CF<sub>4</sub> in the plasma source gas within the range of about 1:2 to about 3:1 provides a good balance between etching and passivation, when used in combination with oxygen at a plasma source gas concentration of 20 volume % or less. Often, the volumetric ratio of CH<sub>2</sub>F<sub>2</sub> to CF<sub>4</sub> ranges between about 1:2 and about 2:1. More typically, the volumetric ratio of CH<sub>2</sub>F<sub>2</sub> to CF<sub>4</sub> ranges between about 1:1 and about 2:1. We have found that a plasma source gas comprising about 30 to about 70 volume % CH<sub>2</sub>F<sub>2</sub>, about 30 to about 70 volume % CF<sub>4</sub>, and about 2 to about 20 volume % O<sub>2</sub> provides good (at least 2:1) selectivity for etching the silicon-containing dielectric layer relative to an overlying photoresist, as well as excellent etch profile control. More typically, the plasma source gas composition comprises about 50 to about 70 volume % CH<sub>2</sub>F<sub>2</sub>, about 30 to about 50 volume % CF<sub>4</sub>, and about 5 to about 15 volume % O<sub>2</sub>. Typically, the sidewall angle for a patterned line ranges from about 84° to about 90°. The plasma source gas composition may further include a nonreactive diluent gas such as helium, argon, neon, xenon, or krypton, by way of example and not by way of limitation. Often, the nonreactive diluent gas is helium. Helium is typically present in the source gas at a concentration within the range of about 50 to about 70 volume %. Often, the plasma source gas is selected to include about 10 to about 25 volume % CH<sub>2</sub>F<sub>2</sub>, about 10 to about 25 volume % CF<sub>4</sub>, about 2 to about 10 volume % O<sub>2</sub>, and about 50 to about 70 volume % helium. The etch method works particularly well when performed in a semiconductor [0013] processing chamber having a decoupled plasma source. The process chamber pressure during etching in such a processing chamber is typically within the range of about 4 mTorr to about 10 mTorr.

[0014] We have found that the etch method described above works especially well in combination with a photoresist which is sensitive to 248 nm radiation, of the kind commonly used in the art. The method provides a selectivity for etching a silicon-containing dielectric layer relative to the photoresist of about 2:1 or better. The method also provides a line etch profile sidewall angle ranging from 84° to 90° between the etched silicon-containing dielectric layer and an underlying horizontal layer in the semiconductor structure. In addition, the method provides an etched sidewall roughness of about 5 nm or less.

## [0015] BRIEF DESCRIPTION OF THE DRAWINGS

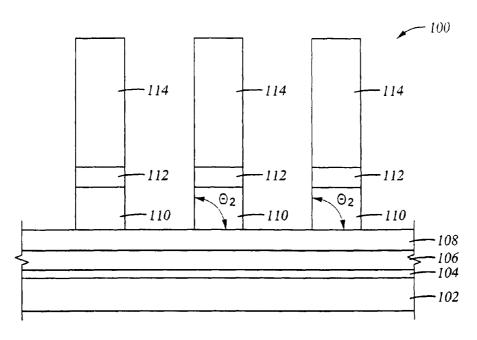

- [0016] Figure 1A shows a typical starting structure 100 which was used in the example embodiments described herein. Structure 100 includes the following layers, from top to bottom: a patterned photoresist layer 114 which is sensitive to 248 nm imaging radiation; a patterned bottom anti-reflective coating (BARC) layer 112; a silicon nitride layer 110; a tungsten layer 108; a polysilicon layer 106; and a gate layer 104, all deposited overlying a substrate 102.

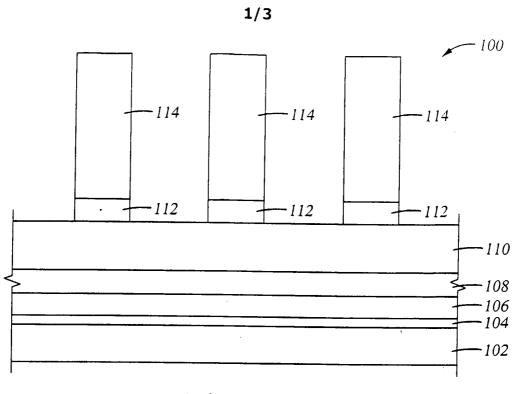

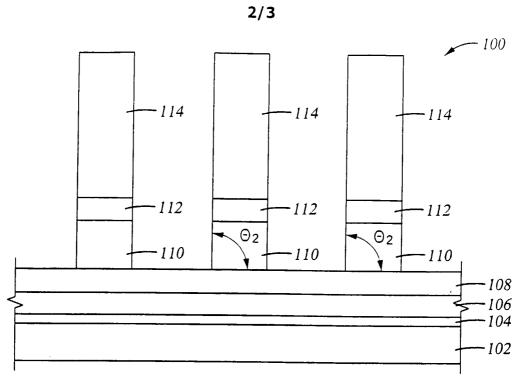

- 15 [0017] Figure 1B shows a schematic cross-sectional front view of structure 100 after 16 pattern etching of silicon nitride layer 110, when a previously known, comparative method 17 is used to etch the silicon nitride layer 110.

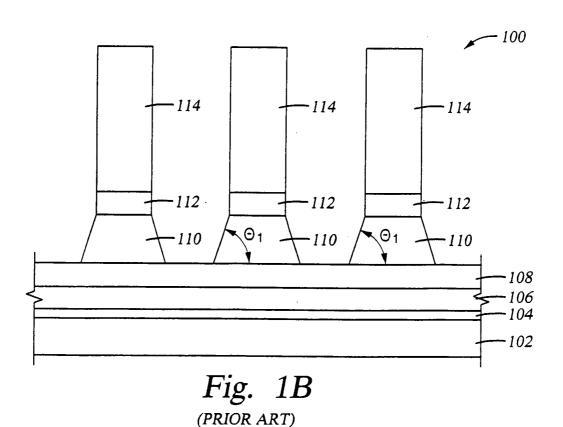

- [0018] Figure 1C shows a schematic front view of structure 100 after pattern etching of silicon nitride layer 110 using an embodiment method of the invention.

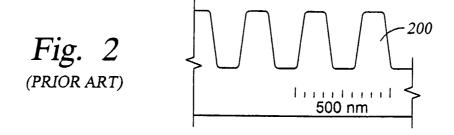

- [0019] Figure 2 shows a schematic cross-sectional front view of a silicon nitride layer 200, etched in a lines and spaces pattern, where the etched trench exhibits a tapered profile.

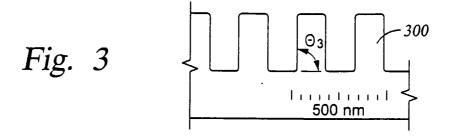

[0020] Figure 3 shows a schematic cross-sectional front view of silicon nitride layer 300 etched in a lines and spaces pattern using an embodiment method of the invention, where the etched line exhibits a more vertical sidewall profile, where the angle between the line sidewall and a horizontal surface at the base of the line sidewall ranges between about 84° and about 90°.

1

2

3

4

5

12

13

14

15

16

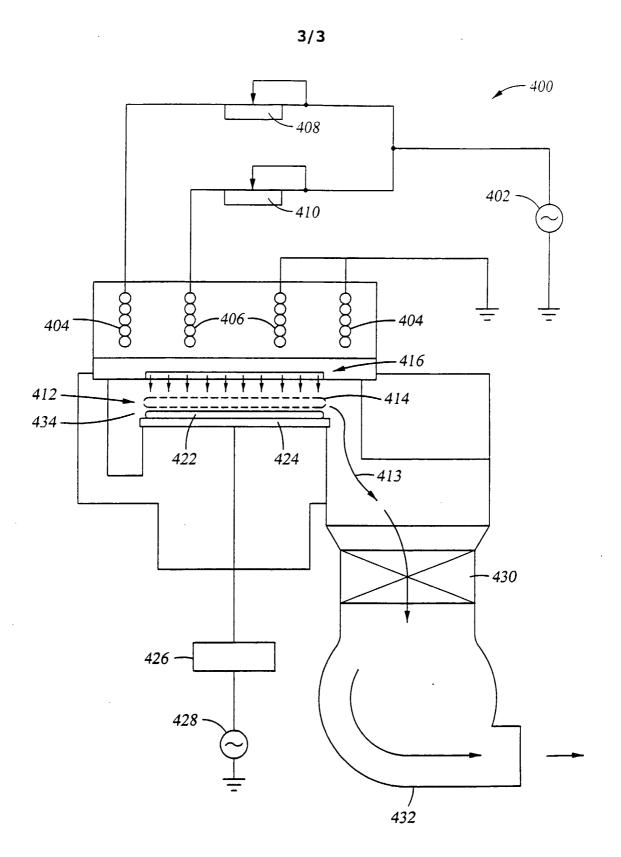

- 6 [0021] Figure 4 is a schematic of a CENTURA® DPS II<sup>TM</sup> (Model of Apparatus) etch 7 chamber of the kind which was used to carry out the experimentation described herein.

- 8 [0022] **DETAILED DESCRIPTION OF EXEMPLARY EMBODIMENTS**

- 9 [0023] Disclosed herein is a method of pattern etching a layer of a silicon-containing 10 dielectric material. Exemplary processing conditions for performing various embodiments 11 of the method of the invention are set forth below.

- [0024] Although the method embodiments described below pertain to the use of a silicon-containing dielectric material as a hard mask in the etching of a gate structure, the etch chemistry and processing conditions described below can be used any time a silicon-containing dielectric material is used as a masking layer, for example, in the etching of a trench or contact via or other semiconductor feature.

- [0025] As a preface to the detailed description, it should be noted that, as used in this specification and the appended claims, the singular forms "a", "an", and "the" include plural referents, unless the context clearly dictates otherwise.

- 20 [0026] I. AN APPARATUS FOR PRACTICING THE INVENTION

- [0027] The embodiment etch methods described herein are typically performed in a plasma etch chamber having a Decoupled Plasma Source (DPS) of the kind described by Yan Ye et al. at the Proceedings of the Eleventh International Symposium of Plasma

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

Processing, May 7, 1996, and as published in the Electrochemical Society Proceedings, Volume 96-12, pp. 222 - 233 (1996). In particular, the embodiment example etch processes described herein were carried out in a CENTURA® DPS IITM plasma etch chamber available from Applied Materials, Inc., of Santa Clara, California. This apparatus used to carry out the etching described herein is discussed in detail below; however, it is contemplated that other plasma etch chamber apparatus known in the industry may be used to carry out the invention. [0028] Figure 4 shows a schematic of a cross-sectional view of a CENTURA® DPS II<sup>TM</sup> plasma etch chamber 400 of the kind which was used to carry out the etching processes described herein. During processing, a substrate 422 is introduced into the chamber 400 through a slit valve 434. The substrate 422 is held in place by means of a static charge generated on the surface of an electrostatic chuck (ESC) cathode 424, by applying a DC voltage to a conductive layer located under a dielectric film on the chuck surface (not shown). Etch gases are introduced into the chamber 400 by means of a gas distribution assembly 416. The etch chamber 400 uses an inductively coupled plasma RF source power 402, which is connected to an outer inductive coil 404 and an inner inductive coil 406 for generating and sustaining a high density plasma 414 in plasma processing region 412. Plasma source power 402 is split off into a first power distribution system 408, which provides power to outer coil 404, and a second power distribution system 410, which provides power to inner coil 406. The substrate 422 is biased by means of an RF source 428 and matching network 426. Power to the plasma source 402 and substrate biasing means 428 are controlled by separate controllers (not shown). Etch byproducts and excess processing gases 413 are exhausted from the chamber through throttle valve 430, by means of pump 432, which maintains the desired process chamber pressure. The temperature of the semiconductor substrate 422 is controlled using the temperature of the electrostatic chuck cathode 424 upon which the substrate 422 rests. Typically, a helium gas flow is used

to facilitate heat transfer between the substrate and the pedestal.

2 [0029] Although the etch process chamber used to process the substrates described in the

- Examples presented herein is shown in schematic in Figure 4, one skilled in the art may use

- 4 any of the etch processors available in the industry, with some readily apparent adjustments.

- For example, the method of the invention may alternatively be performed in an etch

- 6 processing apparatus wherein power to a plasma generation source and power to a substrate

- biasing means are supplied by a single power supply, such as the Applied Materials' MXP

- 8 or MXP+ polysilicon etch chamber.

3

23

24

25

### 9 [0030] II. EXEMPLARY METHODS OF PATTERN ETCHING 10 A SILICON-CONTAINING DIELECTRIC LAYER

11 [0031] Figure 1A shows a typical starting structure 100 for performing the embodiment

12 etching methods described herein. Structure 100 includes the following layers, from top to

13 bottom: a patterned 193 nm photoresist layer 114; a patterned bottom anti-reflective coating

14 (BARC) layer 112; a silicon-containing dielectric layer 110; a tungsten layer 108; a

15 polysilicon layer 106; and a gate oxide layer 104, all overlying a single-crystal silicon

16 substrate 102. However, it is understood that, in practicing the invention, layers underlying

17 the silicon-containing dielectric layer 110 may be different.

- 18 [0032] The various layers in the embodiment example semiconductor structure 100 are deposited using conventional deposition techniques known in the art, as follows.

- [0033] Gate oxide layer 104 was a silicon oxide layer, which was formed by thermal oxidation, according to techniques known in the art. Gate oxide layer 104 had a thickness within the range of about 15 Å to 50 Å.

- [0034] Polysilicon layer 106 was deposited by chemical vapor deposition (CVD), according to techniques known in the art. Polysilicon layer 106 had a thickness within the range of about 500 Å to about 2000 Å.

1

2

3

4

5

6

7

8

9.

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

[0035] Tungsten layer 108 was deposited by CVD, according to techniques known in the art. Tungsten layer 108 had a thickness within the range of about 300 Å to about 1000 Å. In the Examples described below, silicon-containing dielectric layer 110 was silicon nitride. However, silicon-containing dielectric layer 110 may alternatively comprise silicon oxide or silicon oxynitride. Optionally, silicon-containing dielectric layer 110 may be a dual layer, with an upper layer of silicon oxide and a lower layer of silicon nitride, for example, and not by way of limitation. Silicon nitride layer 110 is typically deposited by low pressure CVD (LPCVD) [0037] or plasma-enhanced CVD (PECVD), according to techniques known in the art. Silicon nitride layer 110 typically has a thickness within the range of about 1000 Å to about 2500 Å. Antireflective coatings are used in combination with photoresists to reduce [0038] standing waves and back-scattered light, so that the imaging within the photoresist can be better controlled. When the ARC layer lies beneath the photoresist layer, it is commonly referred to as a bottom antireflective coating (BARC). An organic BARC layer 112 is typically deposited by spin-on techniques known in the art. BARC layer 112 typically has a thickness within the range of about 500 Å to about 1500 Å. Photoresist layer 114 is, in the present instance, a photoresist which is sensitive [0039] to radiation within the range of about 200 nm to about 300 nm. Typically, the photoresist is a chemically amplified version of an organic, polymeric-based composition which is available from a number of manufacturers, including AZ Electronic Materials (Somerville, NJ) and Shipley, Inc. (Marlboro, MA). A typical film thickness for such a photoresist ranges from about 4000 Å to about 6000 Å. The thickness and patterning method for the photoresist layer 114 will depend on the particular photoresist material used and the pattern to be etched in the underlying substrate. In the present instance, for etching a pattern of lines and spaces which are 0.2  $\mu m$  wide lines and 0.2  $\mu m$  wide spaces through a 2000 Å thick

1 layer of silicon nitride, the resist thickness is typically about 5000 Å. The maximum 2 thickness of the photoresist is limited by the aspect ratio of the photoresist being developed and the particular characteristics of the photoresist used. To obtain advantageous results, 3 the aspect ratio of the developed photoresist is typically about 4:1 or less; more typically, 4 5 about 3:1 or less. 6 [0040] Patterned photoresist layer 114 is used as a mask to transfer the pattern to underlying BARC layer 112. Pattern etching of lines and spaces through an organic BARC 7 layer 112 is typically performed using a plasma source gas including CF<sub>4</sub> and argon. 8 Typical process conditions for pattern etching of BARC layer 110 in a decoupled plasma 9 source etch chamber are as follows: 100 sccm of CF<sub>4</sub>; 100 sccm of Ar; 4 mTorr to 20 mTorr 10 process chamber pressure; 300 W to 1000 W plasma source power; 30 W to 100 W substrate 11 bias power (about -60 V to -1000 V substrate bias voltage); and 40°C to 80°C substrate 12 temperature. Etching time will depend on the composition and thickness of the particular 13 BARC layer being etched. For an organic BARC layer having a thickness of 800 Å, the etch 14 time is typically within the range of about 20 seconds to about 30 seconds. 15

## 16 [0041] III. COMPARATIVE SILICON NITRIDE ETCH EXAMPLE

23

24

25

17 [0042] The following comparative example was performed using the starting structure

18 100 shown in Figure 1. Thicknesses of the various layers were as follows: a 5000 Å thick

19 patterned 248 nm photoresist layer 114; a 600 Å thick patterned BARC layer 112; a

20 2000 Å thick silicon nitride layer 110; a 500 Å thick tungsten layer 108; a 1500 Å thick

21 polysilicon layer 106; and a 15 Å thick silicon oxide gate layer, all deposited overlying a

22 single-crystal silicon substrate 102.

[0043] After patterning of BARC layer 112 in the manner described above, the silicon nitride layer 110 was etched. Silicon nitride etching was performed in an Applied Materials' DPS II plasma etch chamber (shown in Figure 4). Plasma etching of silicon nitride layer

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

110 was performed using the following plasma source gas composition and etch process conditions: 30 sccm CF<sub>4</sub>; 60 sccm CH<sub>2</sub>F<sub>2</sub>; 4 mTorr process chamber pressure; 800 W plasma source power; 250 W substrate bias power; and a 60°C substrate temperature. Figure 1B shows a schematic cross-sectional front view of the structure 100 after [0044] pattern etching of silicon nitride layer 108, when etching was performed using the CF<sub>4</sub>/ CH<sub>2</sub>F<sub>2</sub> / He etch chemistry and process conditions set forth above. Note the tapered profile of etched silicon nitride layer 108, where the line sidewall angle  $\theta$ 1 was about 78°. Figure 2 is a schematic drawing based on a photomicrograph taken of a silicon [0045] nitride layer 200, etched in a lines and spaces pattern, where etching was performed using the  $CF_4$  /  $CH_2F_2$  / He etch chemistry and process conditions set forth above. Figure 2 shows a schematic cross-sectional front view of silicon nitride layer 200. The etched line exhibits the tapered profile described above. Because the silicon-containing dielectric layer will be used as a hard mask for [0046] subsequent pattern etching of underlying material layers, it is important that the patterned etch profile of the silicon-containing dielectric layer exhibit a sidewall angle, with respect to a horizontal base, which is as close to 90° as possible. Any non-uniformity in the etch profile of the mask opening will be reflected in the etch profiles of the underlying layers. Therefore, we needed to a develop a method of pattern etching a layer of siliconcontaining dielectric material which provides a vertical (i.e., as close to 90° as possible, and typically ranging between about 88° and about 92°) etch profile. IV. INVENTION EMBODIMENT EXAMPLES [0048] We have found that the addition of a small amount of O<sub>2</sub> (typically, less than [0049] 20 % by volume of the plasma source gas) provides excellent profile control, without significantly suppressing the etch rate of the silicon-containing dielectric material. A

volumetric ratio of CH<sub>2</sub>F<sub>2</sub> to CF<sub>4</sub> in the plasma source gas within the range of about 1:2 to

about 2:1 was found to provide a good balance between etching and passivation, when used in combination with oxygen at a plasma source gas concentration of 20 volume % or less.

[0050] The following examples were performed using the starting structure 100 shown in Figure 1. Thicknesses of the various layers were as follows: a 5000 Å thick patterned 248 nm photoresist layer 114; a 600 Å thick patterned organic BARC layer 112; a 2000 Å thick silicon nitride layer 110; a 500 Å thick tungsten layer 108; a 1500 Å thick polysilicon layer 106; and a silicon oxide gate layer 104, all deposited overlying a single-crystal silicon substrate 102.

[0051] After patterning of BARC layer 112 in the manner previously described, a silicon nitride layer 110 was etched. Silicon nitride etching was performed in the same Applied Materials' DPS II plasma etch chamber referred to with respect to the comparative example. Silicon nitride etch process conditions which were used during each experiment are presented in Table One, below.

[0052] Table One. Process Conditions Used During Etching of Silicon Nitride

| Process Parameter                                                    | Run #1 | Run #2 | Run #3 | Run #4 | Run #5 | Run #6 |

|----------------------------------------------------------------------|--------|--------|--------|--------|--------|--------|

| CH <sub>2</sub> F <sub>2</sub> Flow Rate (sccm)                      | 60     | 60     | 50     | 60     | 30     | 60     |

| CF <sub>4</sub> Flow Rate (sccm)                                     | 30     | 30     | 30     | 30     | 15     | 30     |

| O <sub>2</sub> Flow Rate (sccm)                                      | 15     | 5      | 5      | 5      | 5      |        |

| He Flow Rate (sccm)                                                  |        |        |        |        | 300    |        |

| Process Chamber Pressure (mTorr)                                     | 4      | 4      | 4      | 4      | 4      | 4      |

| Plasma Source Power (W)                                              | 800    | 800    | 800    | 1200   | 1200   | 800    |

| Substrate Bias Power (W)                                             | 250    | 250    | 250    | 250    | 250    | 250    |

| Substrate Temp. (°C)                                                 | 60     | 60     | 60     | 60     | 60     | 60     |

| Etch Time (sec)                                                      | 75     | 70     | 72     | 57     | 65     | 60     |

| Si <sub>x</sub> N <sub>y</sub> : PR Selectivity,<br>no overetch*     | 2.2    | 5.6    | 2.7    | 4      |        | 6.7    |

| Si <sub>x</sub> N <sub>y</sub> : PR Selectivity,<br>w/50% overetch** |        |        | 2      | 2.4    | 1.7    |        |

| Etch Profile Angle (θ)                                               | 88     | 84     | 85     | 86     | 87     | 78     |

\* Silicon nitride: photoresist etch selectivity, with no overetch step.

\*\* Silicon nitride: photoresist etch selectivity, with 50 % overetch. (Overetch process was the same as the main etch.)

[0053] The Run # 6 data are presented as a comparison, to show the tapered etch profile angle which is obtained when the plasma source gas does not include oxygen.

Figure 1C shows a schematic cross-sectional front view of the structure 100 after pattern etching of silicon nitride layer 108 using a method of the invention which provided a nearly vertical etch profile exhibiting etch profile angle  $\theta_2$ . Figure 3 shows a schematic cross-sectional front view of silicon nitride layer 300 etched in a lines and spaces pattern using an embodiment method of the invention, where the etched line exhibits a vertical sidewall profile, where the angle  $\theta_3$  between the line sidewall and a horizontal surface at the

base of the sidewall ranges between about 84° and about 92°.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18 -

19

20

21

22

23

24

25

26

According to the present method embodiment, etching of a silicon-containing dielectric material is typically performed using a plasma generated from a source gas which includes CH<sub>2</sub>F<sub>2</sub>, CF<sub>4</sub>, and O<sub>2</sub>, where a volumetric ratio of CH<sub>2</sub>F<sub>2</sub> to CF<sub>4</sub> is within the range of about 1:2 to about 3:1, and where O2 is comprises about 2 to about 20 volume % of the plasma source gas. Often, the volumetric ratio of CH<sub>2</sub>F<sub>2</sub> to CF<sub>4</sub> ranges between about 1:2 and about 2:1. More typically, the volumetric ratio of CH<sub>2</sub>F<sub>2</sub> to CF<sub>4</sub> ranges between about 1:1 and about 2:1. We have found that a plasma source gas comprising about 30 to about 70 volume % CH<sub>2</sub>F<sub>2</sub>, about 30 to about 70 volume % CF<sub>4</sub>, and about 2 to about 20 volume % O<sub>2</sub> provides good (at least 2:1) selectivity for etching the silicon-containing dielectric layer relative to an overlying photoresist, as well as excellent etch profile control. More typically, the plasma source gas composition comprises about 50 to about 70 volume % CH<sub>2</sub>F<sub>2</sub>, about 30 to about 50 volume % CF<sub>4</sub>, and about 5 to about 15 volume % O<sub>2</sub>. Typically, the sidewall angle for a patterned line ranges from about 84° to about 92°. The plasma source gas composition may further include a nonreactive diluent gas such as helium, argon, neon, xenon, or krypton, by example and not by way of limitation. Often, the nonreactive diluent gas is helium. Helium is typically present in the source gas at a concentration within the range of about 50 to about 70 volume %. Often, the plasma source gas is selected to include about 10 to about 25 volume % CH<sub>2</sub>F<sub>2</sub>, about 10 to about 25 volume % CF<sub>4</sub>, about 2 to about 10 volume % O<sub>2</sub>, and about 50 to about 70 volume % helium. The present etch method works particularly well when performed in a [0057] semiconductor processing chamber having a decoupled plasma source. Typical process conditions for etching of a silicon-containing dielectric material, according to the present embodiment method, in a decoupled plasma chamber (such as a CENTURA® DPS IITM), are provided in Table Two, below:

1 [0058] <u>Table Two. Typical Process Conditions for Etching</u>

2 <u>of a Silicon-Containing Dielectric Material</u>

| Process Parameter                               | Range of<br>Process<br>Conditions | Typical Process<br>Conditions | Advantageous<br>Process<br>Conditions |

|-------------------------------------------------|-----------------------------------|-------------------------------|---------------------------------------|

| CH <sub>2</sub> F <sub>2</sub> Flow Rate (sccm) | 10 - 100                          | 10 - 100                      | 30 - 60                               |

| CF <sub>4</sub> Flow Rate (sccm)                | 30 - 100                          | 30 - 100                      | 30 - 60                               |

| O <sub>2</sub> Flow Rate (sccm)                 | 3 - 30                            | 3 - 30                        | 5 - 20                                |

| He Flow Rate (sccm)                             | 0 - 200                           | 0 - 200                       | 0 - 200                               |

| Process Chamber Pressure (mTorr)                | 3 - 20                            | 4 - 10                        | . 4 - 10                              |

| Plasma Source Power (W)                         | 200 - 1800                        | 300 - 1500                    | 500 - 1000                            |

| Substrate Bias Power (W)                        | 30 - 400                          | 50 - 300                      | 150 - 250                             |

| Substrate Temperature (°C)                      | 20 - 80                           | 20 - 80                       | 40 - 60                               |

| Etch Time Period (sec)*                         | 40 - 100                          | 40 - 100                      | 40 - 100                              |

<sup>\*</sup> For a 2000 Å thick silicon nitride layer.

[0059] The etch method described above works particularly well in combination with a photoresist which is sensitive to 248 nm radiation, of the kind commonly used in the art. Such photoresists are available from AZ Electronic Materials / Clariant (Somerville, NJ) and Shipley, Inc. (Marlboro, MA), by way of example and not by way of limitation.

[0060] The method provides a selectivity for etching a silicon-containing dielectric layer relative to such a photoresist of about 2: 1 or better. The method also provides an etch profile sidewall angle ranging from 84° to 92° between the etched silicon-containing dielectric layer and an underlying horizontal layer in the semiconductor structure. In addition, the method provides an etched sidewall roughness of about 5 nm or less.

[0061] Although the Examples above are described with reference to the use of a siliconcontaining dielectric material as a hard mask in the etching of a gate structure, the etch

chemistry and processing conditions described above can be used any time a siliconcontaining dielectric material is used as a masking layer, for example, in the etching of a

shallow trench or other semiconductor feature.

[0062] The above described exemplary embodiments are not intended to limit the scope

of the present invention, as one skilled in the art can, in view of the present disclosure

expand such embodiments to correspond with the subject matter of the invention claimed

below.

[0063] CLAIMS

We claim:

1 1. A method of pattern etching a layer of a silicon-containing dielectric material on

2 a semiconductor substrate, wherein a patterned photoresist layer overlies said silicon3 containing dielectric layer, said method comprising exposing said silicon-containing

4 dielectric layer to a plasma generated from a source gas comprising CH<sub>2</sub>F<sub>2</sub>, CF<sub>4</sub>, and O<sub>2</sub>,

5 wherein a volumetric ratio of CH<sub>2</sub>F<sub>2</sub> to CF<sub>4</sub> is within the range of about 1: 2 to about 3: 1,

6 and wherein O<sub>2</sub> comprises about 2 to about 20 volume % of the plasma source gas.

- 1 2. The method of Claim 1, wherein said silicon-containing dielectric material is 2 selected from the group consisting of silicon nitride, silicon oxide, silicon oxynitride, and 3 combinations thereof.

- The method of Claim 1, wherein a volumetric ratio of CH<sub>2</sub>F<sub>2</sub> to CF<sub>4</sub> is within the range of about 1: 2 to about 2: 1.

- 1 4. The method of Claim 3, wherein a volumetric ratio of CH<sub>2</sub>F<sub>2</sub> to CF<sub>4</sub> is within the 2 range of about 1:1 to about 2:1.

- The method of Claim 1, wherein said source gas comprises about 30 to about 70 volume % CH<sub>2</sub>F<sub>2</sub>, about 30 to about 70 volume % CF<sub>4</sub>, and about 2 to about 20 volume % O<sub>2</sub>.

1 6. The method of Claim 6, wherein said source gas comprises about 50 to about 70

- 2 volume % CH<sub>2</sub>F<sub>2</sub>, about 30 to about 50 volume % CF<sub>4</sub>, and about 5 to about 15 volume %

- $O_2$ .

- The method of Claim 1, wherein said source gas further includes helium.

- 1 8. The method of Claim 7, wherein said helium is present in said source gas at a

- 2 concentration within the range of about 50 to about 70 volume %.

- 1 9. The method of Claim 8, wherein said source gas comprises about 10 to about 25

- 2 volume % CH<sub>2</sub>F<sub>2</sub>, about 10 to about 25 volume % CF<sub>4</sub>, about 2 to about 10 volume % O<sub>2</sub>,

- and about 50 to about 70 volume % helium.

- 1 10. The method of Claim 1, wherein said photoresist is sensitive to 248 nm radiation.

- 1 11. The method of Claim 1, wherein said silicon-containing dielectric layer is used

- 2 as a hard mask during pattern etching of an underlying semiconductor structure, and wherein

- said semiconductor structure includes features having a feature size of about 0.13  $\mu m$  or

- 4 larger.

- 1 12. The method of Claim 1, wherein said silicon-containing dielectric layer has a

- 2 thickness within the range of about 1000 Å to about 2500 Å.

- 1 13. The method of Claim 1, wherein etching is performed at a process chamber

- pressure within the range of about 4 mTorr to about 10 mTorr.

1 14. The method of Claim 1, wherein said method is performed in a semiconductor

- 2 processing chamber having a decoupled plasma source.

- 1 15. The method of Claim 1, wherein said method provides a selectivity for etching

- 2 said silicon-containing dielectric layer relative to said photoresist of at least 2:1.

- 1 16. The method of Claim 1, wherein said method provides a sidewall etch profile

- 2 angle ranging from 84° to 92° between said etched silicon-containing dielectric layer and

- 3 an underlying horizontal layer.

- 1 17. A method of pattern etching a layer of silicon nitride on a semiconductor

- 2 substrate, wherein a patterned photoresist layer overlies said silicon nitride layer, said

- method comprising exposing said silicon nitride layer to a plasma generated from a source

- gas comprising CH<sub>2</sub>F<sub>2</sub>, CF<sub>4</sub>, and O<sub>2</sub>, wherein a volumetric ratio of CH<sub>2</sub>F<sub>2</sub> to CF<sub>4</sub> is within

- 5 the range of about 1:2 to about 3:1, and wherein O2 comprises about 2 to about 20 volume

- 6 % of the plasma source gas.

- 1 18. The method of Claim 1, wherein a volumetric ratio of CH<sub>2</sub>F<sub>2</sub> to CF<sub>4</sub> is within the

- 2 range of about 1:2 to about 2:1.

- 1 19. The method of Claim 18, wherein a volumetric ratio of CH<sub>2</sub>F<sub>2</sub> to CF<sub>4</sub> is within

- 2 the range of about 1:1 to about 2:1.

- 1 20. The method of Claim 1, wherein said source gas comprises about 30 to about 70

- 2 volume % CH<sub>2</sub>F<sub>2</sub>, about 30 to about 70 volume % CF<sub>4</sub>, and about 2 to about 20 volume %

- $O_2$ .

1 21. The method of Claim 20, wherein said source gas comprises about 50 to about

- 2 70 volume % CH<sub>2</sub>F<sub>2</sub>, about 30 to about 50 volume % CF<sub>4</sub>, and about 5 to about 15 volume

- 3 % O<sub>2</sub>.

- 1 22. The method of Claim 1, wherein said source gas further includes helium.

- 1 23. The method of Claim 22, wherein said helium is present in said source gas at a

- 2 concentration within the range of about 50 to about 70 volume %.

- 1 24. The method of Claim 23, wherein said source gas comprises about 10 to about

- 2 25 volume %  $CH_2F_2$ , about 10 to about 25 volume %  $CF_4$ , about 2 to about 10 volume %  $O_2$ ,

- and about 50 to about 70 volume % helium.

- 1 25. The method of Claim 1, wherein said photoresist is sensitive to 248 nm radiation.

- 1 26. The method of Claim 1, wherein said silicon nitride layer is used as a hard mask

- during pattern etching of an underlying semiconductor structure, and wherein said

- 3 semiconductor structure includes features having a feature size of about 0.13  $\mu m$  or larger.

- 1 27. The method of Claim 1, wherein said silicon nitride layer has a thickness within

- the range of about 1000 Å to about 2500 Å.

- 1 28. The method of Claim 1, wherein etching is performed at a process chamber

- 2 pressure within the range of about 4 mTorr to about 10 mTorr.

1 29. The method of Claim 1, wherein said method is performed in a semiconductor processing chamber having a decoupled plasma source.

- 1 30. The method of Claim 1, wherein said method provides a selectivity for etching said silicon nitride layer relative to said photoresist of at least 2:1.

- The method of Claim 1, wherein said method provides a sidewall etch profile angle ranging from 84° to 92° between said etched silicon nitride layer and an underlying horizontal layer.

Fig. 1A (PRIOR ART)

Fig. 1C

Fig. 4

#### INTERNATIONAL SEARCH REPORT

Internation: lication No PCT/US 03/33217

A. CLASSIFICATION OF SUBJECT MATTER IPC 7 H01L21/311 H01L21/3213

According to International Patent Classification (IPC) or to both national classification and IPC

#### B. FIELDS SEARCHED

$\label{lem:minimum documentation searched (classification system followed by classification symbols)} IPC \ 7 \ \ H01L$

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practical, search terms used)

EPO-Internal, WPI Data, PAJ, INSPEC, CHEM ABS Data

| Category ° | Citation of document, with indication, where appropriate, of the relevant passages                      | Relevant to claim No.                |

|------------|---------------------------------------------------------------------------------------------------------|--------------------------------------|

| Х          | US 6 362 109 B1 (KOMATSU TAKEHIKO ET AL)<br>26 March 2002 (2002-03-26)<br>table 3                       | 1-4,<br>10-19,<br>25-31              |

| X          | US 6 432 832 B1 (MELAKU YOSIAS ET AL) 13 August 2002 (2002-08-13) column 9, line 57 -column 10, line 16 | 1-9,<br>11-16                        |

| X          | US 6 218 309 B1 (MILLER ALAN J ET AL) 17 April 2001 (2001-04-17) column 9                               | 1-9,<br>11-16                        |

| X          | US 6 309 962 B1 (CHAO LI-CHI ET AL)<br>30 October 2001 (2001-10-30)                                     | 1-6,<br>11-14,<br>16-21,<br>26-29,31 |

|            | example 1                                                                                               |                                      |

| X Further documents are listed in the continuation of box C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Patent family members are listed in annex.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Special categories of cited documents:      A' document defining the general state of the art which is not considered to be of particular relevance      E' earlier document but published on or after the international filing date      L' document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)      O' document referring to an oral disclosure, use, exhibition or other means      P' document published prior to the international filing date but later than the priority date claimed | <ul> <li>'T' later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention</li> <li>'X' document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone</li> <li>'Y' document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art.</li> <li>'&amp;' document member of the same patent family</li> </ul> |  |  |  |  |

| Date of the actual completion of the international search                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Date of mailing of the international search report                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| 16 March 2004                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 26/03/2004                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| Name and mailing address of the ISA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Authorized officer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| European Patent Office, P.B. 5818 Patentlaan 2<br>NL - 2280 HV Rijswijk<br>Tel. (+31-70) 340-2040, Tx. 31 651 epo nl,<br>Fax: (+31-70) 340-3016                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Szarowski, A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

## INTERNATIONAL SEARCH REPORT

Internation cation No

PCT/US 03/33217

| C.(Continu | iation) DOCUMENTS CONSIDERED TO BE RELEVANT                                                                                                                                                                                                               |                               |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

| Category ° | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                                                        | Relevant to claim No.         |

| A .        | MIYOSHI S ET AL.: "Pattern transfer processes for 157-nm lithography" PROCEEDINGS OF THE SPIE, 2002, vol. 4690, 2002, pages 221-232, XP001188926 Advances in resist technology and processing XIX, Santa Clara, CA, USA, 4-6 March 2002 paragraph '3.1.4! | 1-31                          |

| A          | US 2001/005636 A1 (NISHIZAWA ATSUSHI)<br>28 June 2001 (2001-06-28)<br>table 2                                                                                                                                                                             | 1,2,13,<br>14,16,<br>17,28,29 |

| A          | EP 0 908 940 A (IBM) 14 April 1999 (1999-04-14) abstract                                                                                                                                                                                                  | 1-6,<br>10-21,<br>25-31       |

| A          | US 6 461 529 B1 (BOYD DIANE C ET AL)<br>8 October 2002 (2002-10-08)<br>column 4 -column 5                                                                                                                                                                 | 1-31                          |

| A          | US 6 335 293 B1 (MANTRIPRAGADA SAI ET AL) 1 January 2002 (2002-01-01) column 13                                                                                                                                                                           | 1-4, 17-19                    |

|            |                                                                                                                                                                                                                                                           |                               |

## INTERNATIONAL SEARCH REPORT

Information on patent family members

Internation: illication No PCT/US 03/33217

|    | itent document<br>I in search report |    | Publication date |          | Patent family member(s) |       | Publication date         |

|----|--------------------------------------|----|------------------|----------|-------------------------|-------|--------------------------|

| US | 6362109                              | B1 | 26-03-2002       | NONE     |                         |       |                          |

| US | 6432832                              | B1 | 13-08-2002       | NONE     |                         |       |                          |

| US | 6218309                              | B1 | 17-04-2001       | US       | 6287974                 |       | 11-09-2001               |

|    |                                      |    |                  | AU       | 5634800                 |       | 31-01-2001               |

|    |                                      |    |                  | EP<br>TW | 1190443<br>451395       |       | 27-03-2002<br>21-08-2001 |

|    |                                      |    |                  | WO       | 0101468                 |       | 04-01-2001               |

|    |                                      |    |                  |          | 0101400                 |       |                          |

| US | 6309962                              | B1 | 30~10~2001       | NONE     |                         |       |                          |

| US | 2001005636                           | A1 | 28-06-2001       | JP       | 2001176842              | A     | 29-06-2001               |

|    |                                      |    |                  | US       | 2003203631              | A1    | 30-10-2003               |

| EP | 0908940                              | Α  | 14-04-1999       | US       | 6051504                 | A     | 18-04-2000               |

|    |                                      |    |                  | EP       | 0908940                 |       | 14-04-1999               |

|    |                                      |    |                  | JP       | 3155513                 |       | 09-04-2001               |

|    |                                      |    |                  | JP<br>   | 11102896                | A<br> | 13-04-1999               |

| US | 6461529                              | B1 | 08-10-2002       | CN       | 1271871                 |       | 01-11-2000               |

|    |                                      |    | 1 60             | JP       | 2000340552              |       | 08-12-2000               |

|    |                                      |    |                  | SG       | 98375                   |       | 19-09-2003               |

|    |                                      |    |                  | TW       | 484185                  |       | 21 <b>-</b> 04-2002      |

| US | 6335293                              | В1 | 01-01-2002       | EP       | 1125002                 |       | 22-08-2001               |

|    |                                      |    |                  | JP       | 3487828                 |       | 19-01-2004               |

|    |                                      |    |                  | JP       | 2002520834              |       | 09-07-2002               |

|    |                                      |    |                  | WO       | 0003059                 |       | 20-01-2000               |

|    |                                      |    |                  | US       | 2002017364              |       | 14-02-2002               |

|    |                                      |    |                  | US       | 2001009177              | ΑI    | 26-07-2001               |