(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6703134号

(P6703134)

(45) 発行日 令和2年6月3日(2020.6.3)

(24) 登録日 令和2年5月11日(2020.5.11)

(51) Int.Cl.

H04L 7/00 (2006.01)

H04L 25/02 (2006.01)

F 1

H04L 7/00

H04L 25/02810

J

請求項の数 8 (全 15 頁)

(21) 出願番号 特願2018-556345 (P2018-556345)

(86) (22) 出願日 平成28年9月21日 (2016.9.21)

(65) 公表番号 特表2019-525507 (P2019-525507A)

(43) 公表日 令和1年9月5日 (2019.9.5)

(86) 國際出願番号 PCT/US2016/052725

(87) 國際公開番号 WO2017/222578

(87) 國際公開日 平成29年12月28日 (2017.12.28)

審査請求日 令和1年9月18日 (2019.9.18)

(31) 優先権主張番号 15/192,287

(32) 優先日 平成28年6月24日 (2016.6.24)

(33) 優先権主張国・地域又は機関

米国(US)

早期審査対象出願

(73) 特許権者 591016172

アドバンスト・マイクロ・ディバイシズ・

インコーポレイテッド

ADVANCED MICRO DEVICES INCORPORATED

アメリカ合衆国 95054 カリフォルニア州、サンタクララ、オーガスティン ドライブ 2485

(54) 【発明の名称】レプリカレーンを使用したチャネルトレーニング

最終頁に続く

(57) 【特許請求の範囲】

【請求項 1】

受信機と、

第1レーンと第2レーンとを少なくとも含む複数のレーンを有する通信チャネルを介して前記受信機に接続された送信機であって、前記第1レーンは、システムデータを伝送するために利用されない、送信機と、

を備えるシステムであって、

前記送信機は、

前記通信チャネルの前記第1レーンでテストパターンを送信し、

前記通信チャネルの第2レーンでシステムデータを送信するのと同時に、前記第1レーンで前記テストパターンを送信する、 10

ように構成されており、

前記受信機は、

前記第2レーンで前記システムデータを受信するのと同時に、前記通信チャネルの前記第1レーンを介してテストパターンを受信し、

受信したテストパターンにおいて検出されたエラーに基づいて、前記第1レーンのサンプリングポイントがミスマライメントであると判別し、

前記テストパターンにおいて前記エラーが検出されたことを示すエラー表示を、前記第1レーンを介して前記送信機に伝える、

ように構成されており、

前記システムは、前記検出されたエラーに応じて、

前記第1レーンのサンプリングポイントに対して第1調整を実行し、

前記通信チャネルの前記第2レーンのサンプリングポイントに対して、前記第1調整と同じ調整である第2調整を実行する、

ように構成されている、

システム。

#### 【請求項2】

前記システムは、前記第1調整及び前記第2調整を実行する前に初期フェーズを実行するように構成されており、前記システムは、前記初期フェーズ中に、前記第1レーン及び前記第2レーンの両方を同時にトレーニングすることに応じて、前記第1レーンのサンプリングポイントと、前記第2レーンのサンプリングポイントと、を設定するように構成されており、10

前記トレーニングは、テストパターンデータを前記第1レーン及び前記第2レーンで伝えることと、前記第1レーン及び前記第2レーンの遅延設定を更新して前記第1レーンのサンプリングポイントと前記第2レーンのサンプリングポイントとを調整することと、を含む、

請求項1のシステム。

#### 【請求項3】

前記送信機は、前記第1レーンで前記エラー表示を受信したことに応じて、前記第1レーンのサンプリングポイントに対して前記第1調整を行うために、前記第1レーンの遅延設定を変更するように構成されている、20

請求項1のシステム。

#### 【請求項4】

前記送信機は、前記第1レーンで前記エラー表示を受信したことに応じて、前記第2レーンのサンプリングポイントに対して前記第2調整を行うために、前記第2レーンの遅延設定を変更するように構成されている、

請求項1のシステム。

#### 【請求項5】

前記第2レーンのサンプリングポイントに対する前記第2調整は、前記第2レーンでテストパターンを送信することなく行われる、30

請求項4のシステム。

#### 【請求項6】

送信機が、通信チャネルの第1レーンでテストパターンを送信することであって、前記第1レーンはシステムデータを伝送するために利用されない、ことと、

前記送信機が、前記通信チャネルの第2レーンでシステムデータを送信するのと同時に、前記第1レーンで前記テストパターンを送信することと、

前記テストパターンにおいて前記エラーが検出されたことを示すエラー表示を、前記第1レーンを介して受信すること、

受信機によって受信された前記テストパターンにおいて検出されたエラーの数に基づいて、前記第1レーンのサンプリングポイントがミスアライメントであると判別したことに応じて、前記第1レーンのサンプリングポイントに対して第1調整を実行し、前記通信チャネルの第2レーンによって利用されるサンプリングポイントに対して、前記第1調整と同じ調整である第2調整を実行することと、を含む、40

方法。

#### 【請求項7】

前記第1調整及び前記第2調整を実行する前に初期フェーズを実行することを含み、前記方法は、前記初期フェーズ中に、前記第1レーン及び前記第2レーンの両方を同時にトレーニングすることに応じて、前記第1レーンのサンプリングポイントと、前記第2レーンのサンプリングポイントと、を設定することを含み、

前記トレーニングは、テストパターンデータを前記第1レーン及び前記第2レーンで伝50

えることと、前記第1レーン及び前記第2レーンの遅延設定を更新して前記第1レーンのサンプリングポイントと前記第2レーンのサンプリングポイントとを調整することと、を含む、

請求項6の方法。

【請求項8】

前記送信機が、前記第1レーンで前記エラー表示を受信したことに応じて、前記第1レーンのサンプリングポイントに対して前記第1調整を行うために、前記第1レーンの遅延設定を変更すること、及び／又は、前記第2レーンのサンプリングポイントに対して前記第2調整を行うために、前記第2レーンの遅延設定を変更することを含む、

請求項6の方法。

10

【発明の詳細な説明】

【技術分野】

【0001】

本明細書に記載される実施形態は、データ通信に関し、より詳細には、ビットシリアルデータリンクのトレーニングを実行することに関する。

【背景技術】

【0002】

集積回路のデータスループットは、アプリケーション需要及びデータ消費が増加するにつれて増加し続けている。例えば、マイクロプロセッサ速度の改善率は、メモリ速度の改善率を超えて続けている。データの送信レートが増加することで、データを送受信するために使用される回路のタイミング要求が増加する。コンピューティングデバイス及びコンピューティングシステムにおいて利用される多くの回路では、これらの回路内でグローバルクロックを使用してデータが転送される。例えば、クロックの立ち上がりエッジは、フリップフロップに入るデータをロードし、その後、データを、フリップフロップを通過させるか又はフリップフロップから処理することができる。いくつかのシナリオでは、複数のデータレーンのデータバスに単一のクロックが使用され、各データレーンは個別のシリアルビットストリームを伝送する。しかしながら、これは、クロックの遷移をデータバス全体に使用する必要があるのでデータバスの速度が制限されるが、一部のデータビットは、他のデータビットと比較してバスを通るのに時間がかかる場合がある。データレーン間のばらつきが大きすぎる場合、データバス全体において正確にクロックするためにクロックエッジを配置する場所が存在しない場合がある。さらに、温度又は電圧の変動により、レーンの位相アライメントが時間とともに変動することがある。このようなばらつきを補正すると、データのフローが中断され、重要な動作が中断され、データの転送が遅れることがある。

20

【発明の概要】

【課題を解決するための手段】

【0003】

ビットシリアルデータリンクのトレーニングを実行するためのシステム、装置及び方法について検討する。

30

【0004】

40

一実施形態では、送信機と受信機との間の遅延設定をテストするために、トレーニングシーケンスが実行される。送信機は、複数のデータレーンの通信チャネルを介して受信機に接続されている。一実施形態では、通信チャネルは、追加のレプリカレーンを含む。この追加のレプリカレーンは、周期的追跡(PT)レーンと呼ばれることもある。様々な実施形態では、レプリカレーンは、システムデータを送らない。むしろ、レプリカレーンは、テストデータの送信用のみに構成されている。送信機は、データレーンが通常のシステムデータを送っている間に、レプリカレーンで一連のトレーニングシーケンスを定期的に実行する。トレーニングシーケンスは、温度変動、電源変動、及び／又は、他の要因によるレプリカレーンの僅かなタイミング変化を検出するために実行される。レプリカレーンの位相タイミングにおける変化が検出されると、制御ロジックは、レプリカレーンと通常

50

のデータレーンとの位相タイミングを更新する。

**【0005】**

一実施形態では、送信機は、レプリカレーンでテストパターンを送信すると同時に、チャネルの少なくとも第2レーンで第1データを送信する。受信機が、レプリカレーンで受信したテストパターンにおいて1つ以上のエラーを検出した場合、送信機及び／又は受信機は、レプリカレーンにおいてサンプリングポイントがミスアライメントであると判別する。送信機及び／又は受信機は、レプリカレーンにおいてサンプリングポイントがミスアライメントであると判別すると、第1レーンのサンプリングポイントに対して第1調整を実行し、第2レーンのサンプリングポイントに対して第1調整を実行する。第2レーンのサンプリングポイントに対する第1調整は、レプリカレーンのサンプリングポイントに対する第1調整に相当する。送信機は、第2レーンのサンプリングポイントに対して第1調整を実行した後に、第2レーンで第2データを送信するように構成されている。10

**【0006】**

これらの特徴及び利点と、他の特徴及び利点とは、本明細書に提示される以下の詳細な説明を考慮して、当業者に明らかとなるであろう。

**【0007】**

方法及びメカニズムの上記の利点と、さらなる利点とは、添付の図面と併せて以下の説明を参照することによって、より良く理解することができる。

**【図面の簡単な説明】**

**【0008】**

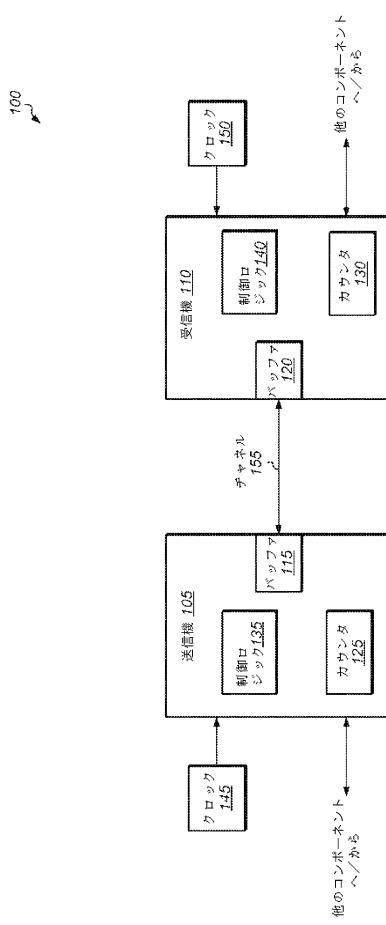

**【図1】**コンピューティングシステムの送信機及び受信機の一実施形態のブロック図である。

20

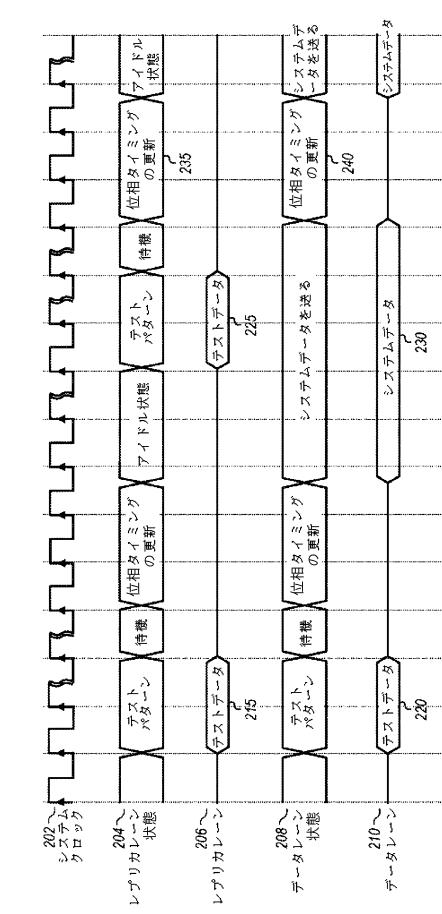

**【図2】**レプリカレーンのトレーニングシーケンスを実行する一実施形態のタイミング図である。

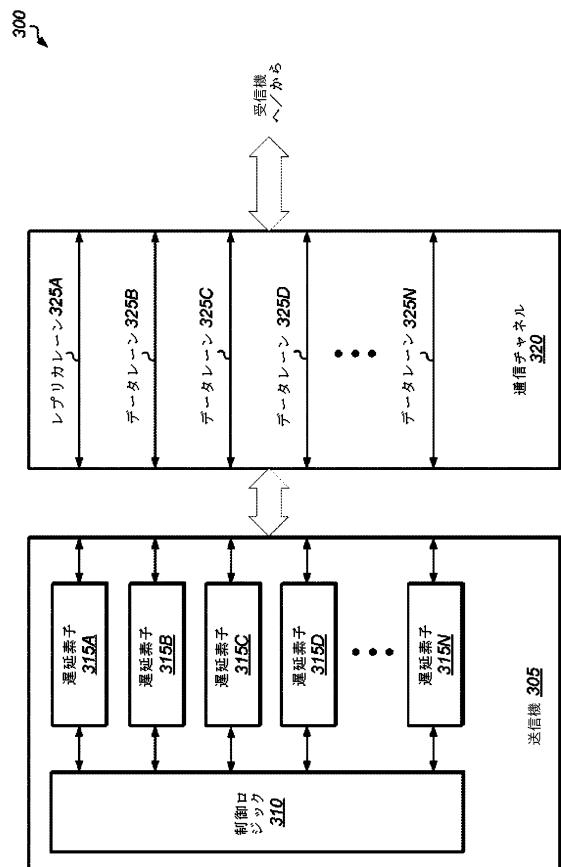

**【図3】**送信機及び通信チャネルを有するシステムの一実施形態のブロック図である。

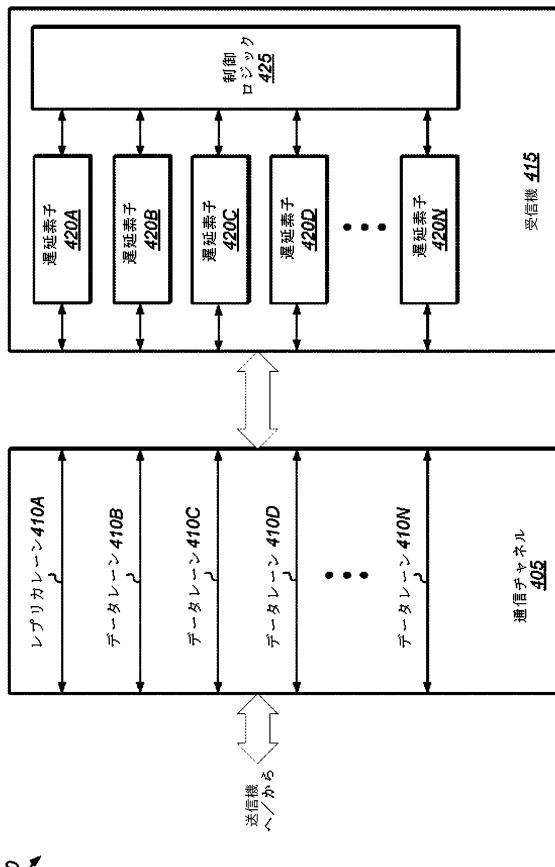

**【図4】**受信機及び通信チャネルを有するシステムの一実施形態のブロック図である。

**【図5】**データアイの一実施形態を示す図である。

**【図6】**複数レーンチャネルの位相タイミングを調整する方法の一実施形態を示す一般化されたフロー図である。

**【図7】**レプリカレーンを利用してチャネルの他のレーンのサンプリングポイントを調整する方法の他の実施形態を示す一般化されたフロー図である。30

**【発明を実施するための形態】**

**【0009】**

下記の説明では、本明細書に提示される方法及びメカニズムを十分に理解してもらうために、多数の具体的な詳細が示されている。しかしながら、当業者であれば、これらの具体的な詳細無しに様々な実施形態を実施可能であることを認識すべきである。いくつかの例では、周知の構造、コンポーネント、信号、コンピュータプログラム命令及び技術は、本明細書で説明するアプローチを不明瞭にするのを避けるために詳細に示されていない。説明を簡単且つ明瞭にするために、図面に示される要素が必ずしも一定の縮尺で描かれていないことを理解されたい。例えば、いくつかの要素の寸法は、他の要素に対して誇張されている。40

**【0010】**

図1を参照すると、コンピューティングシステム100の送信機105及び受信機110の一実施形態を示すブロック図が示されている。送信機105は、チャネル155を介して受信機110に接続されている。チャネル155は、実施形態に応じて、任意の数のデータレーンを含む。また、チャネル155は、レプリカレーン、クロックレーン、及び／又は、1つ以上の他のレーンを含む。コンピューティングシステム100は、クロック145と、クロック150と、図面を不明瞭にするのを避けるために示されていない1つ以上の他のコンポーネントと、を含む。例えば、コンピューティングシステム100は、1つ以上の処理ユニット（例えば、プロセッサ、プロセッサコア、プログラマブルロジック）

50

クデバイス、特定用途向け集積回路等)、1つ以上のメモリデバイス、及び/又は、他のコンポーネントを含む。1つ以上の処理ユニットは、実施形態に応じて、命令を実行し、及び/又は、1つ以上のタイプの計算(例えば、浮動小数点、整数、メモリ、I/O)を実行するように構成されている。様々な実施形態では、コンピューティングシステム100のコンポーネントは、1つ以上の通信バスによって相互接続されている。一実施形態では、送信機105及び受信機110は、プロセッサのメモリバスに存在する。様々な実施形態において、プロセッサに接続されたメモリは、ダブルデータレート同期ダイナミックランダムアクセスメモリ(DDR SDRAM)である。他の実施形態では、メモリは、他のタイプのメモリデバイスを用いて実装される。

## 【0011】

10

送信機105は、チャネル155に接続されたバッファ115を含む。一実施形態では、バッファ115は、トレーニングシーケンスの状態に関して、送信機105が受信機110からのフィードバックを受信するのを待機している場合に、チャネル155の出力を駆動するか、高インピーダンス状態を生成するためのトライステートバッファである。また、送信機105は、トレーニングシーケンスを生成し、チャネル155のレーンの遅延設定を制御し、及び/又は、他の機能を実行する制御ロジック135も含む。さらに、送信機105は、スーパーサイクルをカウントするためのカウンタ125を含む。様々な実施形態では、スーパーサイクルは、長さが「N」クロックサイクルであり、「N」は正の整数である。例えば、一実施形態では、スーパーサイクルは8クロックサイクルの長さであり、他の実施形態では、スーパーサイクルは数クロックサイクルである。一実施形態では、クロック145は、カウンタ125をクロックするためのクロック信号を提供する。

## 【0012】

20

受信機110は、チャネル155に接続するためのバッファ120を含む。一実施形態では、バッファ120は、フィードバック結果をチャネル155に運ぶ、又は、受信機110が送信機105からデータを受信している場合に高インピーダンス状態を生成するためのトライステートバッファである。また、受信機110は、チャネル155上のトレーニングシーケンス指示を検出し、受信したテストパターンを期待値と比較し、チャネル155のレーンの遅延設定を制御し、及び/又は、他の機能を実行する制御ロジック140を含む。さらに、受信機110は、スーパーサイクルをカウントするためのカウンタ130を含む。一実施形態では、クロック150は、カウンタ130をクロックするためのクロック信号を提供する。他の実施形態では、受信機110は、カウンタ130をクロックするためのクロック信号として、チャネル155で受信したクロック信号を使用する。

## 【0013】

30

送信機105は、チャネル155のレプリカレーン及び1つ以上のデータレーンを介してテストパターンを送信するように構成されている。テストパターンは、チャネル155のレプリカレーン及びデータレーンの最適なサンプリングポイントを決定するために利用される。レプリカレーン及びデータレーンの遅延は、テストパターンの結果に基づいて調整され、通常のデータオペレーションが開始される。定期的に、送信機105は、データレーンがシステムデータを送る間に、レプリカレーンを介して追加のテストパターンを送信するように構成されている。システム100が、前回のテスト以来レプリカレーンの最適なサンプリングポイントがドリフトしていると判別した場合に、システム100は、レプリカレーンのサンプリングポイントを調整して、最適なサンプリングポイントにアライメントさせる。また、システム100は、データレーンのサンプリングポイントに対して同等の調整を行う。このようにして、温度変動、電源変動、及び/又は、他の要因によるデータレーンのサンプリングポイントのドリフトが、システムデータのフローを中断することなく補正される。

## 【0014】

40

受信機110は、レプリカレーン及びデータレーンで送信機105によって送信されたテストパターンをキャプチャするように構成されている。次いで、受信機110は、キャプチャされたテストパターンのエラーに関してチェックする。一実施形態では、送信機1

50

05は、トレーニングパターンを送信した後にバッファ115を無効にし、キャプチャされたテストパターンに関するフィードバックを受信機110が送信するのを待機する。受信機110は、バッファ120を有効にし、キャプチャされたテストパターンにおいてエラーが検出されたかどうかを判別した後に、フィードバックを送信機105に送信する。送信機105は、フィードバックをキャプチャし、そのフィードバックを（他の遅延設定を用いた他のテストからのフィードバックと共に）使用して、所定のデータレーンのデータ有効期間（又は、「データアイ」）を決定する。送信機105は、フィードバックをキャプチャした後に、別のテストを実行するかどうか、又は、通常のデータオペレーションに戻るかどうかを決定する。別の実施形態では、受信機110は、キャプチャしたテストパターンにおいて検出されたエラーの数に基づいて、レプリカレーン及びデータレーンの遅延設定を調整する。

#### 【0015】

システム100は、送信機105及び受信機110を含む任意のタイプのコンピューティングシステム又はコンピューティングデバイスを表す。例えば、様々な実施形態では、システム100は、コンピュータ、サーバ、計算ノード、プロセッサ、処理デバイス、プログラマブル論理デバイス、メモリデバイス、プロセッシングインメモリ（PIM）ノード、モバイルデバイス、テレビ、娯楽システム若しくはデバイス、及び／又は、他のタイプのシステム若しくはデバイスを含むことができる。また、システム100は、送信機105及び受信機110に加えて、任意の数の他の送信機及び受信機を含む。

#### 【0016】

次に、図2を参照すると、レプリカレーンでトレーニングシーケンスを実行する一実施形態のタイミング図200が示されている。トレーニングシーケンスは、複数レーンチャネル（例えば、チャネル155）を介して、送信機（例えば、図1の送信機105）と受信機（例えば、図1の受信機110）との間で実行される。複数レーンチャネルは、レプリカレーンと、システムデータを送るための複数のデータレーンと、を含む。

#### 【0017】

システムクロック202のサイクルは、タイミング図200の一番上の行に示されている。一実施形態では、タイミング図200のクロック202行に示されるサイクルは、スーパーサイクルを表している。スーパーサイクルは、「N」システムクロックであり、「N」は1より大きい正の整数であり、「N」はプログラマブルレジスタに記憶されている。一実施形態では、送信機及び受信機の両方は、スーパーサイクルをカウントするカウンタを含む。一実施形態では、スーパーサイクルは、長さが8クロックサイクルであり、カウンタは、モジュロ8カウンタである。他の実施形態では、スーパーサイクルは、他の数のクロックサイクルである。レプリカレーン状態204は、タイミング図200に示すクロックサイクル中のチャネルのレプリカレーン状態を示す。レプリカレーン206は、レプリカレーンで送信されるデータを示す。同様に、データレーン状態208は、データレーンの状態を示し、データレーン210は、タイミング図200に示すクロックサイクル中にデータレーンで送信されるデータを示す。

#### 【0018】

最初のテストフェーズの間、送信機は、レプリカレーン及びデータレーンでテストパターンを受信機に送信する。これは、レプリカレーン206のテストデータ215及びデータレーン210のテストデータ220として示されている。一実施形態では、テストパターンは、擬似ランダムバイナリシーケンスである。送信機は、レプリカレーン及びデータレーンでテストパターンを送信する前に、テストパターンが送信されることを受信機に知らせるためのトレーニングシーケンス指示を送信する。受信機が所定のレーンでトレーニングシーケンス指示を受信すると、受信機は、所定のレーンでテストパターンを受信する準備が整う。テストデータ215及びテストデータ220は、異なる遅延設定で実行される任意の数のテストに対応する。

#### 【0019】

受信機は、レプリカレーン及びデータレーンでテストパターンを受信し、受信したテス

10

20

30

40

50

トパターンにエラーがあるかどうかをチェックする。一実施形態では、受信機は、受信したテストパターンのエラーの有無に関するフィードバックを送信機に送信する。これは、レプリカレーン及びデータレーンの「待機」状態中に発生する。システムは、テストパターンの結果を使用して、レプリカレーン及びデータレーンの各々のデータアイを識別する。次に、システムは、テストデータの結果に基づいて、レプリカレーン及び各データレーンの位相タイミングを更新する。各レーンは、レーンで受信したテストパターンの結果に基づいて、他のレーンとは独立して更新される。所定のレーンが既に最適なサンプリングポイント用に構成されていることを結果が示している場合、所定のレーンの遅延設定は、位相タイミングの更新期間中に調整されないことに留意されたい。

## 【0020】

10

レプリカレーン及びデータレーンの位相タイミングへの最初の更新の後、データレーンがシステムデータ230を送る間、レプリカレーンはアイドル状態になる。一定時間が経過すると、システムは、レプリカレーンをテストして、レプリカレーンの位相タイミングがドリフトしているかどうかを確認する。システムがデータレーンでシステムデータ230を送信し続ける一方で、テストデータ225がレプリカレーンで同時に送信される。次に、システムは、テストデータ225が送信された後に、レプリカレーンの位相タイミングを調整するかどうかを決定する。システムは、レプリカレーンで受信したテストパターンの結果に基づいて、以前のテスト以来最適なサンプリングポイントがドリフトした場合に、レプリカレーンの位相タイミングを更新する。この更新は、レプリカレーン状態204の行の更新235として示されている。また、システムは、レプリカレーンでの如何なるドリフトもデータレーンで発生するという仮定に基づいて、データレーンの更新タイミングに対して同様の更新240を実行する。様々な実施形態において、データレーンのタイミングの更新は、データレーンでデータ送信がアクティブである間に（例えば、システムデータ230を送信する間に）実行される。他の実施形態では、データレーンは、更新フェーズ（例えば、240）中にタイミングパラメータが調整される間、データの送信を一時的に中断する。両方のアプローチが考えられる。システムは、レプリカレーン及びデータレーンの位相タイミングの更新235、240の各々の後に、データレーンでのシステムデータの送信に戻る一方で、レプリカレーンはアイドル状態に戻る。次に、レプリカレーンの位相タイミングがドリフトしている場合、システムは、レプリカレーンを定期的にテストして、レプリカレーン及びデータレーンに変更を加えることを継続して行う。

20

## 【0021】

30

次に、図3を参照すると、送信機305及び通信チャネル320を有する一実施形態のシステム300のブロック図が示されている。通信チャネル320は、送信機305と受信機（図示省略）とを接続する任意のタイプの通信チャネルを表す。通信チャネル320は、実施形態に応じて、レプリカレーン325Aと、任意の数のデータレーン325B～Nと、を含む。レプリカレーン325Aは、以前のテスト以来最適なサンプリングポイントがドリフトしているかどうかを判別するために、テストデータを送るように構成されている。通常のデータオペレーションでは、レプリカレーン325Aは、システムデータを送るために利用されるのではなく、むしろアイドル状態である。各データレーン325B～Nは、システムデータのシリアルビットストリームを送るように構成されている。また、通信チャネル320は、クロックレーン（図示省略）及び／又は1つ以上の他のレーンを含む。

40

## 【0022】

一実施形態では、送信機305は、制御ロジック310及び遅延素子315A～Nを含む。遅延素子315A～Nの個々のセットは、レーン325A～Nのうち対応するレーンの遅延設定を選択するための1つ以上の遅延素子を含む。一実施形態では、1つ以上の遅延素子は、レーン325A～Nのうち単一のレーンに適用される粗い遅延調整及び細かい遅延調整を含む。

## 【0023】

送信機305は、最初のテスト期間中にレーン325A～Nの遅延設定をテストするた

50

めに、レーン 325A～N の全てでテストパターンを送信するように構成されている。例えば、この最初のテスト期間は、起動時又はリセット後に発生する。送信機は、テストパターンを送信した後に、出力バッファ（例えば、図 1 のバッファ 115）を無効にする。出力バッファは、送信機 305 がテストパターンを受信機に送信した後に、送信機 305 によって高インピーダンス状態に切り替えられるトライステートバッファである。受信機は、フィードバックを準備する期間の後に、出力バッファを起動して、フィードバックを送信機に送る。一実施形態では、フィードバックは、受信したテストパターンにエラーがあったかどうかを示す。一実施形態では、フィードバックは、単一のビットである。他の実施形態では、フィードバックは、エラーの数を示すために複数のビットを利用する。送信機は、フィードバックを受信し、フィードバックを利用して、現在の遅延設定がデータアイ内側か外側かを判別する。送信機がフィードバックを受信した後に、別のテストが実行されてもよいし、送信機が通常のデータオペレーションを行ってもよい。

#### 【0024】

一実施形態では、送信機 305 は、各レーンでテストパターンを送信し、受信機（図示省略）は、各テストパターンにおいて検出されたエラーの数と共にフィードバックを送信機 305 に送る。次に、送信機 305 の制御ロジック 310 は、このフィードバックを利用して、各レーン 325A～N のデータアイを決定する。例えば、送信機は、チャネル 320 のレーン 325A～N 毎に、異なる遅延設定を有する複数のテストパターンを送信する。これらのテストパターンに対する受信機からのフィードバックは、制御ロジック 310 によって、各レーンのデータアイの位置を決定するために使用される。制御ロジック 310 は、遅延素子 315A～N の各々を調整して、対応するレーンの受信機のサンプリングポイントを、データアイの位置に基づく最適なサンプリングポイントに対応させる。遅延素子 315A～N の各々に対する調整は、他の遅延素子 315A～N に対する調整とは独立して行われる。

#### 【0025】

次に、システム 300 は、全てのレーン 325A～N について位相テストシーケンスを実行した後に、通常のデータオペレーションを開始する。データレーン 325B～N は、通常のデータオペレーションの間、システムデータを送るために利用される一方で、レプリカレーン 325A は、アイドル状態である。換言すれば、レプリカレーン 325A は、システムデータを送るために使用されない。次に、システム 300 は、通常のデータオペレーションの間、レプリカレーン 325A を周期的に利用して、以前のテストからフェーズタイミングがドリフトしているかどうかを確認するために、位相テストを行う。実施形態に応じて、レプリカレーン 325A の位相タイミングは、温度変動、電源変動、及び／又は、要因に基づいてドリフトする。システム 300 は、データレーン 325B～N がシステムデータを送っている間に、レプリカレーン 325A における位相テストを実行する。このように、システム 300 は、データレーン 325B～N のシステムデータのフローを中断することなく、レプリカレーン 325A の位相タイミングをテストすることができる。

#### 【0026】

システム 300 がレプリカレーン 325A の位相タイミングのドリフトを検出すると、システム 300 は、遅延素子 315A を調整することによって、レプリカレーン 325A のタイミングを補正する。また、システム 300 は、データレーン 325B～N に影響を与える他の遅延素子 315B～N にも同じ調整を行う。多くの場合、レプリカレーン 325A の位相タイミングで発生したドリフトは、データレーン 325B～N においても発生している。したがって、システム 300 は、全てのレーン 325A～N の位相タイミングのドリフトを、单一のレプリカレーン 325A のテストを実行するだけで補正することができる。一実施形態では、システム 300 は、規則的な間隔で、单一のレプリカレーン 325A でこれらのテストを実行するように構成されている。別の実施形態では、システム 300 は、1つ以上の条件（例えば、エラー率の増加、温度変動、電源変動等）の検出に応じて、レプリカレーン 325A に対するテストを実行するように構成されている。

## 【0027】

次に、図4を参照すると、通信チャネル405及び受信機415を備える一実施形態のシステム400のブロック図が示されている。図3のシステム300と同様に、システム400は、レプリカレーン410Aの位相タイミングのドリフトの検出に基づいて、データレーン410B～Nの位相タイミングを補正するように構成されている。しかし、システム300とは対照的に、システム400は、遅延素子420A～Nを用いて、受信機415における位相タイミングの補正を行う。本実施形態では、受信機415の制御ロジック425は、フィードバックを送信機（図示省略）に送信するのではなく、受信したテストパターンに対するフィードバックを利用して、遅延素子420A～Nを調整する。

## 【0028】

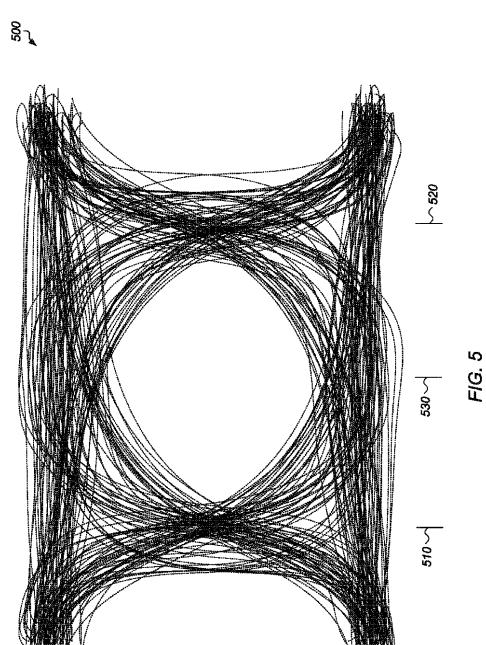

次に、図5を参照すると、データアイ500の一実施形態の図が示されている。データアイ500は、チャネル（例えば、図3の通信チャネル320）のレーンでのビット遷移をキャプチャすることによってモニタリングされるデータ有効期間の一例である。一実施形態では、システム（例えば、システム300）は、データアイ500の境界を検出するために、異なる遅延設定で複数のトレーニングシーケンスを実行するように構成されている。システムは、各テスト結果について受信機（例えば、図1の受信機110）が生成したフィードバックを利用するよう構成されている。

## 【0029】

システムは、複数の遅延設定で複数のテストを実行し、フィードバックが不良（すなわち、1つ以上のエラーがある）から良好（すなわち、エラーがない）になると、その特定の遅延設定がデータアイ500の開始510と一致すると認識する。システムは、僅かな増分で遅延を追加し、追加のテストを実行し、フィードバックが良好から不良になると、これをデータアイ500の終了520と識別する。次に、システムは、データアイ500の中央530を算出するために、開始510及び終了520の平均をもとめる。データアイ500の中央530に対応する遅延設定は、チャネルの所定のレーンに対する最適な遅延設定とみなされる。一実施形態では、システムは、チャネルのレプリカレーンでこれらのテストを実行し、次いで、これらのテストの結果を利用して、チャネルのデータレーンの遅延設定を更新する。

## 【0030】

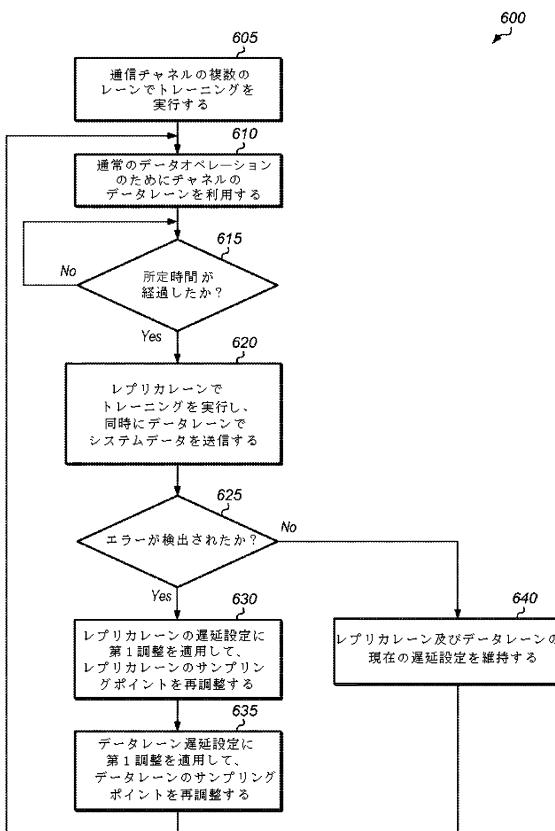

次に、図6を参照すると、マルチレーンチャネルの位相タイミングを調整する方法600の一実施形態が示されている。説明目的のために、本実施形態におけるステップは、順番に示されている。後述する方法の様々な実施形態において、説明する要素のうち1つ以上が同時に実行されてもよいし、図示した順序とは異なる順序で実行されてもよいし、完全に省略されてもよいことに留意されたい。必要に応じて、他の追加の要素を実行してもよい。本明細書において説明する様々なシステム又は装置の何れかは、方法600を実行するように構成されている。

## 【0031】

複数レーン通信チャネルを介して受信機に接続された送信機を有するシステムは、チャネルの複数のレーンでトレーニングシーケンスを同時に実行する（ブロック605）。一実施形態では、通信チャネルは、レプリカレーン及び1つ以上のデータレーンを含む。チャネルの複数のレーンでトレーニングシーケンスを実行する一環として、システムは、レーンの遅延設定を更新して、各レーンが着信データを最適なサンプリングポイントでサンプリングするようにする。

## 【0032】

次に、システムは、通常のデータオペレーションのためにデータレーンを利用することができます（ブロック610）。通常のデータオペレーションの間、チャネルのレプリカレーンはアイドル状態である。次に、システムは、最後のトレーニングシーケンスが実行されてから所定時間が経過したかどうかを判別する（条件ブロック615）。例えば、システムは、所定時間を追跡するタイマを有し、所定時間は、プログラム可能であって、実施形態毎に異なる。

**【 0 0 3 3 】**

システムは、所定時間が経過した場合（条件ブロック 615：「Y e s」）、レプリカレーンで1つ以上のトレーニングシーケンスを実行し、同時にデータレーンでシステムデータを送信する（ブロック 620）。所定時間が経過していない場合（条件ブロック 615：「N o」）、方法 600 は、条件ブロック 615 に留まる。システムは、ブロック 620 の後に、レプリカレーンで実行されたトレーニングシーケンスが、レプリカレーンの最適なサンプリングポイントが以前のテストからドリフトしたことを表しているかどうかを判別する（条件ブロック 625）。

**【 0 0 3 4 】**

レプリカレーンの最適なサンプリングポイントが以前のテストからドリフトしている場合（条件ブロック 625：「Y e s」）、システムは、レプリカレーンの遅延設定に第1調整を適用して、レプリカレーンのサンプリングポイントを再調整する（ブロック 630）。また、システムは、チャネルのデータレーンの遅延設定に第1調整を適用して、データレーンのサンプリングポイントを再調整する（ブロック 635）。このシステムは、レプリカレーンの最適なサンプリングポイントのドリフトがデータレーンで発生することを前提として動作する。したがって、システムは、レプリカレーンの遅延設定に適用されるのと同じ調整を、データレーンの遅延設定に適用する。例えば、第1の量の遅延がレプリカレーンの遅延設定に加えられた場合、第1の量の遅延がデータレーンの遅延設定に加えられる。レプリカレーンの最適なサンプリングポイントが以前のテストからドリフトしていない場合（条件ブロック 625：「N o」）、システムは、レプリカレーン及びデータレーンの現在の遅延設定を維持する（ブロック 640）。ブロック 635, 640 の後に、方法 600 はブロック 610 に戻り、システムは、通常のデータオペレーションのためにデータレーンを利用し続ける。

10

20

30

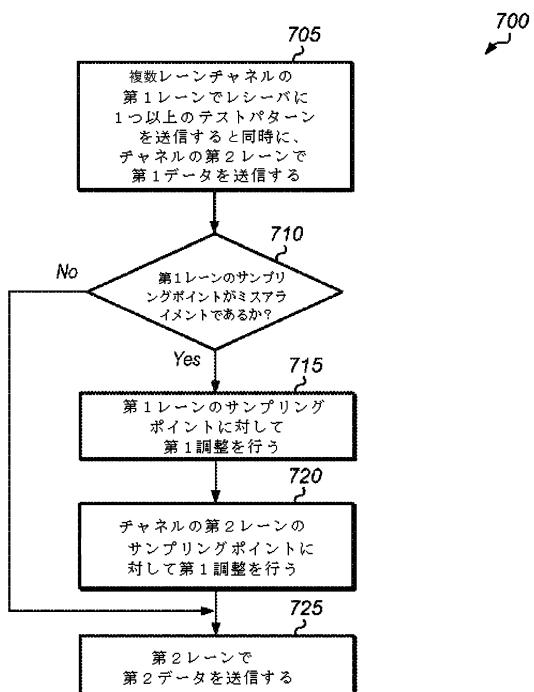

**【 0 0 3 5 】**

次に、図 7 を参照すると、チャネルの他のレーンのサンプリングポイントを調整するためにレプリカレーンを利用する方法 700 の一実施形態が示されている。説明目的のために、本実施形態におけるステップは、順番に示されている。後述する方法の様々な実施形態において、説明する要素のうち1つ以上が同時に実行されてもよいし、図示した順序とは異なる順序で実行されてもよいし、完全に省略されてもよいことに留意されたい。必要に応じて、他の追加の要素を実行してもよい。本明細書において説明する様々なシステム又は装置の何れかは、方法 700 を実行するように構成されている。

30

**【 0 0 3 6 】**

送信機は、複数レーンチャネルの第1レーンで、1つ以上のテストパターンを受信機に送信すると同時に、チャネルの第2レーンで第1データを送信する（ブロック 705）。送信機及び受信機は、ホストシステム内のコンポーネントである。第1レーンは、「レプリカレーン」と呼ぶこともある。1つ以上のテストパターンは、トレーニングシーケンスの一部として第1レーンで受信機に送信され、送信機及び受信機間の第1レーンの遅延設定をテストする。これらのトレーニングシーケンスを使用して、第1レーンのデータアイの位置を決定し、データアイ（及び、対応する最適なサンプリングポイント）が以前のテストからシフトしたかどうかを判別する。

40

**【 0 0 3 7 】**

次に、システムは、受信機によって受信されたテストパターンの結果に基づいて、第1レーンの現在のサンプリングポイントがミスマライメントされているかどうかを判別する（条件ブロック 710）。例えば、システムは、複数の遅延設定で第1レーンの複数のテストを実行し、受信したテストパターンが1つ以上のエラーを有する状態からエラーのない状態になると、その特定の遅延設定がデータアイの開始と一致すると認識する。システムは、僅かな増分で遅延を追加し、追加のテストを実行し、受信したテストパターンがエラーのない状態から1つ以上のエラーを有する状態になると、データアイの終了であると認識する。システムは、データアイの開始及び終了の平均をもとめて、データアイの中央（又は、最適なサンプリングポイント）を計算する。次に、システムは、この新たな最適

50

なサンプリングポイントが第1レーンの実際のサンプリングポイントと一致するかどうかを判別する。他の実施形態では、システムは、最適なサンプリングポイントが第1レーンに対してドリフトしたかどうかを判別するための他の適切な技術を利用する。

#### 【0038】

システムは、受信機によって受信されたテストパターンの結果に基づいて、第1レーンの現在のサンプリングポイントがミスアライメントしていると判別した場合（条件ブロック710：「Y e s」）、第1レーンのサンプリングポイントに対して第1調整を行って、サンプリングポイントを最適なサンプリングポイントにアライメントし直す（ブロック715）。また、システムは、チャネルの第2レーンのサンプリングポイントに対して第1調整を行う（ブロック720）。さらに、システムは、チャネルの1つ以上の他のレーンのサンプリングポイントに対して第1調整を行う。例えば、一実施形態では、システムは、チャネルの全てのデータレーンのサンプリングポイントに対して第1調整を行う。システムが、受信機によって受信されたテストパターンの結果に基づいて、第1レーンのサンプリングポイントが適切にアライメントされていると判別した場合（条件ブロック710：「N o」の分岐）、送信機は、第2レーンで第2データを送信する（ブロック725）。

10

#### 【0039】

温度変動、電源変動、及び／又は、他の要因によって、同様の方法で第1レーン及び他のレーンについて信号遅延の変動が生じる。したがって、第1レーンの最適なサンプリングポイントの変化を検出することは、典型的に、他のレーンがデータアイにおいて同様のドリフトを経験したことと、第1レーンを補正するための変更が、チャネルの他のレーンを補正するのに必要とされる同じ変更であることと、を表す。したがって、チャネルの第2レーン（及び、他のレーン）に対して行われる第1調整は、第1レーンに対して行われる第1調整と同じである。例えば、第1調整が、第1レーンに加える遅延をクロックサイクルの1／4だけ増加させる場合、他のレーンに加わる遅延は、クロックサイクルの1／4だけ増加する。或いは、第1調整が、第1レーンに加える遅延をクロックサイクルの1／8だけ減少させる場合、他のレーンに加わる遅延は、クロックサイクルの1／8だけ減少する。他の実施形態では、他の遅延増分が、第1レーンに対して行われた調整と同等の方法で、レーンに追加又はレーンから削除される。一実施形態では、サンプリングポイントに対する調整は、送信機によって行われる。別の実施形態では、サンプリングポイントに対する調整は、受信機によって行われる。

20

#### 【0040】

ブロック720の後、送信機は、第2レーンで第2データを送信する（ブロック725）。また、送信機は、他のレーンに使用されるサンプリングポイントの調整を行った後に、チャネルの1つ以上の他のレーンで追加のデータを送信する。ブロック725の後に、方法700は終了する。

30

#### 【0041】

様々な実施形態では、ソフトウェアアプリケーションのプログラム命令は、上述した方法及び／又はメカニズムを実施するために使用される。プログラム命令には、C等の高水準プログラミング言語でハードウェアの動作が記述されている。或いは、V e r i l o g等のハードウェア設計言語（H D L）が使用される。プログラム命令は、非一時的なコンピュータ可読記憶媒体に記憶される。多数のタイプの記憶媒体が利用可能である。記憶媒体は、プログラム実行のためにプログラム命令及び付随データをコンピューティングシステムに提供するために、使用中にコンピューティングシステムによってアクセス可能である。コンピューティングシステムは、少なくとも1つ以上のメモリと、プログラム命令を実行するように構成された1つ以上のプロセッサと、を含む。

40

#### 【0042】

上述した実施形態は、実装の非限定的な例に過ぎないことが強調されるべきである。上記の開示を十分に理解することで、多数の変形及び修正が当業者に明らかになるであろう。以下の特許請求の範囲は、このような変形及び修正の全てを包含すると解釈されること

50

が意図される。

【図1】

【図2】

【図3】

【図4】

【図5】

FIG. 5

【図6】

【図7】

---

フロントページの続き

(73)特許権者 508301087

エーティーアイ・テクノロジーズ・ユーエルシー

A T I T E C H N O L O G I E S U L C

カナダ、オンタリオ エル3ティー 7エックス6、マーカム、コマース バリー ドライブ

イースト 1

One Commerce Valley Drive East, Markham, Ontario, L3T 7X6 Canada

(74)代理人 100108833

弁理士 早川 裕司

(74)代理人 100111615

弁理士 佐野 良太

(74)代理人 100162156

弁理士 村雨 圭介

(72)発明者 スタンリー エイムズ ラッキー ジュニア

アメリカ合衆国 01453 マサチューセッツ州、レオミンスター、リッチフィールド パインズ ドライブ 108C

(72)発明者 デイモン トヒディ

カナダ国 L 4 E 4 G 5 オンタリオ州、リッチモンドヒル、ナンタケット ドライブ 115

(72)発明者 ジェラルド アール. タルボット

アメリカ合衆国 01742 マサチューセッツ州、コンコード、ホールデン ウッド ロード 280

(72)発明者 エドアルド プレーテ

アメリカ合衆国 02474 マサチューセッツ州、アーリントン、ワイマン ストリート 24

審査官 谷岡 佳彦

(56)参考文献 特開2014-206971(JP, A)

米国特許第09036757(US, B1)

特表2007-503630(JP, A)

特表2002-523971(JP, A)

米国特許出願公開第2011/0291713(US, A1)

米国特許出願公開第2015/0078495(US, A1)

(58)調査した分野(Int.Cl., DB名)

H 04 L 7 / 00

H 04 L 25 / 02