등록특허 10-2642601

(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2024년03월05일

(11) 등록번호 10-2642601

(24) 등록일자 2024년02월27일

(51) 국제특허분류(Int. Cl.)

*G09G 3/3233* (2016.01) *G09G 3/36* (2006.01)

*H01L 27/12* (2006.01) *H01L 29/786* (2006.01)

*H10K 59/00* (2023.01)

(52) CPC특허분류

*G09G 3/3233* (2013.01)

*G09G 3/3607* (2013.01)

(21) 출원번호 10-2020-7014558

(22) 출원일자(국제) 2018년11월15일

심사청구일자 2021년11월11일

(85) 번역문제출일자 2020년05월21일

(65) 공개번호 10-2020-0080269

(43) 공개일자 2020년07월06일

(86) 국제출원번호 PCT/IB2018/058983

(87) 국제공개번호 WO 2019/102315

국제공개일자 2019년05월31일

(30) 우선권주장

JP-P-2017-225270 2017년11월23일 일본(JP)

(56) 선행기술조사문현

JP2005062794 A\*

JP2014006521 A\*

\*는 심사관에 의하여 인용된 문현

전체 청구항 수 : 총 8 항

심사관 : 윤난영

(54) 발명의 명칭 표시 장치 및 전자 기기

**(57) 요 약**

화상 품질을 향상시킬 수 있는 표시 장치를 제공한다. 각 화소에 기억 노드가 제공되고 기억 노드에 제 1 데이터를 유지할 수 있다. 용량 결합에 의하여 제 1 데이터에 제 2 데이터가 부가되고, 표시 소자에 공급될 수 있다. 따라서 표시 장치는 보정된 화상을 표시할 수 있다. 용량 결합 동작을 하기 위한 기준 전위를 전원선 등으로부터 공급하기 때문에, 제 1 데이터 및 제 2 데이터를 공통의 신호선으로부터 공급할 수 있다.

**대 표 도** - 도1

(52) CPC특허분류

*G09G 3/3648* (2013.01)

*H01L 27/1225* (2013.01)

*H01L 27/1255* (2013.01)

*H01L 29/78648* (2013.01)

*H10K 59/00* (2023.02)

*H10K 59/12* (2023.02)

*H10K 59/40* (2023.02)

*G09G 2300/0819* (2013.01)

*G09G 2300/0842* (2013.01)

---

## 명세서

### 청구범위

#### 청구항 1

표시 장치로서,

제 1 트랜지스터;

제 2 트랜지스터;

제 3 트랜지스터;

제 1 용량 소자;

회로 블록;

제 1 배선; 및

제 2 배선

을 포함하고,

상기 제 1 트랜지스터의 소스 및 드레인 중 한쪽은 상기 제 2 트랜지스터의 소스 및 드레인 중 한쪽에 전기적으로 접속되고,

상기 제 2 트랜지스터의 상기 소스 및 상기 드레인 중 상기 한쪽은 상기 제 1 용량 소자의 제 1 전극에 전기적으로 접속되고,

상기 제 1 용량 소자의 제 2 전극은 상기 제 3 트랜지스터의 소스 및 드레인 중 한쪽에 전기적으로 접속되고,

상기 제 3 트랜지스터의 상기 소스 및 상기 드레인 중 상기 한쪽은 상기 회로 블록에 전기적으로 접속되고,

상기 제 1 트랜지스터의 상기 소스 및 상기 드레인 중 다른 쪽은 상기 제 1 배선에 전기적으로 접속되고,

상기 제 3 트랜지스터의 상기 소스 및 상기 드레인 중 다른 쪽은 상기 제 1 배선에 전기적으로 접속되고,

상기 제 2 트랜지스터의 게이트는 상기 제 2 배선에 전기적으로 접속되고,

상기 제 3 트랜지스터의 게이트는 상기 제 2 배선에 전기적으로 접속되고,

상기 회로 블록은 제 6 트랜지스터, 제 3 용량 소자, 및 액정 소자를 포함하고,

상기 액정 소자의 제 1 전극은 상기 제 3 용량 소자의 제 1 전극에 전기적으로 접속되고,

상기 제 3 용량 소자의 상기 제 1 전극은 상기 제 6 트랜지스터의 소스 및 드레인 중 한쪽에 전기적으로 접속되고,

상기 제 6 트랜지스터의 상기 소스 및 상기 드레인 중 다른 쪽은 상기 제 1 용량 소자의 상기 제 2 전극에 전기적으로 접속되는, 표시 장치.

#### 청구항 2

표시 장치로서,

제 1 트랜지스터;

제 2 트랜지스터;

제 1 회로;

제 2 회로;

제 1 배선; 및

## 제 2 배선

을 포함하고,

상기 제 1 회로 및 상기 제 2 회로는 각각 제 3 트랜지스터, 제 1 용량 소자, 및 회로 블록을 포함하고,

상기 제 3 트랜지스터의 소스 및 드레인 중 한쪽은 상기 제 1 용량 소자의 제 1 전극에 전기적으로 접속되고,

상기 제 1 용량 소자의 상기 제 1 전극은 상기 회로 블록에 전기적으로 접속되고,

상기 제 1 용량 소자의 제 2 전극은 상기 제 1 트랜지스터의 소스 및 드레인 중 한쪽에 전기적으로 접속되고,

상기 제 1 트랜지스터의 상기 소스 및 상기 드레인 중 상기 한쪽은 상기 제 2 트랜지스터의 소스 및 드레인 중 한쪽에 전기적으로 접속되고,

상기 제 1 회로에서의 상기 제 3 트랜지스터의 상기 소스 및 상기 드레인 중 다른 쪽은 상기 제 1 배선에 전기적으로 접속되고,

상기 제 1 트랜지스터의 상기 소스 및 상기 드레인 중 다른 쪽은 상기 제 1 배선에 전기적으로 접속되고,

상기 제 1 회로에서의 상기 제 3 트랜지스터의 게이트는 상기 제 2 배선에 전기적으로 접속되고,

상기 제 2 회로에서의 상기 제 3 트랜지스터의 게이트는 상기 제 2 배선에 전기적으로 접속되고,

상기 제 2 트랜지스터의 게이트는 상기 제 2 배선에 전기적으로 접속되고,

상기 회로 블록은 표시 소자를 포함하는, 표시 장치.

## 청구항 3

제 2 항에 있어서,

상기 회로 블록은 제 4 트랜지스터, 제 5 트랜지스터, 제 2 용량 소자, 및 상기 표시 소자로서 유기 EL 소자를 포함하고,

상기 유기 EL 소자의 제 1 전극은 상기 제 5 트랜지스터의 소스 및 드레인 중 한쪽에 전기적으로 접속되고,

상기 제 5 트랜지스터의 상기 소스 및 상기 드레인 중 다른 쪽은 상기 제 2 용량 소자의 제 1 전극에 전기적으로 접속되고,

상기 제 2 용량 소자의 상기 제 1 전극은 상기 제 4 트랜지스터의 소스 및 드레인 중 한쪽에 전기적으로 접속되고,

상기 제 4 트랜지스터의 게이트는 상기 제 2 용량 소자의 제 2 전극에 전기적으로 접속되고,

상기 제 2 용량 소자의 상기 제 2 전극은 상기 제 1 용량 소자의 상기 제 2 전극에 전기적으로 접속되는, 표시 장치.

## 청구항 4

제 3 항에 있어서,

상기 제 4 트랜지스터의 상기 소스 및 상기 드레인 중 다른 쪽은 상기 제 2 트랜지스터의 상기 소스 및 상기 드레인 중 다른 쪽에 전기적으로 접속되는, 표시 장치.

## 청구항 5

제 2 항에 있어서,

상기 회로 블록은 제 6 트랜지스터, 제 3 용량 소자, 및 상기 표시 소자로서 액정 소자를 포함하고,

상기 액정 소자의 제 1 전극은 상기 제 3 용량 소자의 제 1 전극에 전기적으로 접속되고,

상기 제 3 용량 소자의 상기 제 1 전극은 상기 제 6 트랜지스터의 소스 및 드레인 중 한쪽에 전기적으로 접속되고,

상기 제 6 트랜지스터의 상기 소스 및 상기 드레인 중 다른 쪽은 상기 제 1 용량 소자의 상기 제 2 전극에 전기

적으로 접속되는, 표시 장치.

### 청구항 6

제 5 항에 있어서,

상기 제 3 용량 소자의 제 2 전극은 상기 제 2 트랜지스터의 상기 소스 및 상기 드레인 중 다른 쪽에 전기적으로 접속되는, 표시 장치.

### 청구항 7

제 1 항 또는 제 2 항에 있어서,

상기 제 3 트랜지스터는 채널 형성 영역에 금속 산화물을 포함하고, 상기 금속 산화물은 In, Zn, 및 M(M은 Al, Ti, Ga, Sn, Y, Zr, La, Ce, Nd, 및 Hf 중에서 선택됨)을 포함하는, 표시 장치.

### 청구항 8

전자 기기로서,

제 1 항 또는 제 2 항에 따른 표시 장치와, 카메라를 포함하는, 전자 기기.

## 발명의 설명

### 기술 분야

[0001] 본 발명의 일 형태는 표시 장치에 관한 것이다.

[0002] 또한 본 발명의 일 형태는 상술한 기술분야에 한정되지 않는다. 본 명세서 등에 개시(開示)되는 발명의 일 형태의 기술분야는 물건, 방법, 또는 제작 방법에 관한 것이다. 본 발명의 일 형태는 공정(process), 기계(machine), 제품(manufacture), 또는 조성물(composition of matter)에 관한 것이다. 구체적으로, 본 명세서에 개시되는 본 발명의 일 형태의 기술분야의 예에는 반도체 장치, 표시 장치, 액정 표시 장치, 발광 장치, 조명 장치, 전력 저장 장치, 기억 장치, 활상 장치, 이들의 구동 방법, 및 이들의 제작 방법이 포함된다.

[0003] 본 명세서 등에서 반도체 장치는 일반적으로 반도체 특성을 이용함으로써 기능할 수 있는 장치를 뜻한다. 트랜지스터 및 반도체 회로는 반도체 장치의 일 형태이다. 기억 장치, 표시 장치, 활상 장치, 또는 전자 기기는 반도체 장치를 포함하는 경우가 있다.

### 배경 기술

[0004] 트랜지스터에 사용할 수 있는 반도체 박막의 재료로서 실리콘계 반도체 재료가 널리 알려져 있고, 그 외의 재료로서 산화물 반도체가 주목을 받고 있다. 산화물 반도체의 예에는 산화 인듐 및 산화 아연 등의 1원계 금속 산화물(single-component metal oxide)뿐만 아니라 다원계 금속 산화물(multi-component metal oxide)도 포함된다. 다원계 금속 산화물 중에서도 특히 In-Ga-Zn 산화물(이하 IGZO라고도 함)이 활발히 연구되고 있다.

[0005] IGZO에 관한 연구로부터, 산화물 반도체에서 단결정도 아니고 비정질도 아닌 CAAC(c-axis aligned crystalline) 구조 및 nc(nanocrystalline) 구조가 발견되었다(비특허문헌 1 내지 3 참조). 비특허문헌 1 및 2에서는 CAAC 구조를 가지는 산화물 반도체를 사용하여 트랜지스터를 형성하는 기술이 개시되어 있다. 또한 CAAC 구조 및 nc 구조보다 결정성이 낮은 산화물 반도체에도 미소한 결정이 포함되는 것이 비특허문헌 4 및 5에 개시되어 있다.

[0006] 또한 활성층으로서 IGZO를 포함하는 트랜지스터는 오프 상태 전류가 매우 낮고(비특허문헌 6 참조), 이 특성을 이용한 LSI 및 디스플레이가 보고되었다(비특허문헌 7 및 8 참조).

[0007] 특허문헌 1에는 오프 상태 전류가 매우 낮은 트랜지스터를 메모리 셀에 사용한 기억 장치가 개시되어 있다.

## 선행기술문헌

### 특허문헌

[0008] (특허문현 0001) 일본 공개특허공보 특개2011-119674호

### 비특허문현

[0009] (비특허문현 0001) S. Yamazaki et al., "SID Symposium Digest of Technical Papers", 2012, volume 43, issue 1, pp.183-186.

(비특허문현 0002) S. Yamazaki et al., "Japanese Journal of Applied Physics", 2014, volume 53, Number 4S, pp.04ED18-1-04ED18-10.

(비특허문현 0003) S. Ito et al., "The Proceedings of AM-FPD'13 Digest of Technical Papers", 2013, pp.151-154.

(비특허문현 0004) S. Yamazaki et al., "ECS Journal of Solid State Science and Technology", 2014, volume 3, issue 9, pp.Q3012-Q3022.

(비특허문현 0005) S. Yamazaki, "ECS Transactions", 2014, volume 64, issue 10, pp.155-164.

(비특허문현 0006) K. Kato et al., "Japanese Journal of Applied Physics", 2012, volume 51, pp.021201-1-021201-7.

(비특허문현 0007) S. Matsuda et al., "2015 Symposium on VLSI Technology Digest of Technical Papers", 2015, pp.T216-T217.

(비특허문현 0008) S. Amano et al., "SID Symposium Digest of Technical Papers", 2010, volume 41, issue 1, pp.626-629.

### 발명의 내용

#### 해결하려는 과제

[0010] 표시 장치의 해상도가 높아지고 있으며, 8K4K 해상도(화소수 7680×4320) 또는 그 이상의 해상도의 화상을 표시 할 수 있는 하드웨어가 개발되고 있다. 또한 휙도 조정에 의하여 화상 품질을 향상시키는 HDR(high dynamic range) 표시 기술이 도입되고 있다.

[0011] 표시 장치에 의하여 적절한 표시를 하기 위하여, 화상 데이터는 표시 장치의 해상도에 대응할 필요가 있다. 예를 들어, 표시 장치의 해상도가 8K4K이고 화상 데이터가 4K2K 해상도(화소수 3840×2160)에 대응하는 경우에는, 풀 스크린 표시를 제공하기 위하여 데이터수를 4배로 변환해야 한다. 한편, 표시 장치의 해상도가 4K2K이고 화상 데이터가 8K4K 해상도에 대응하는 경우에는, 데이터수를 4분의 1로 변환해야 한다.

[0012] HDR 처리에서, 화상 데이터의 생성 또는 데이터수의 변환을 하기 위하여 전용의 회로가 필요하므로, 공교롭게도 전력 소비를 증가시킨다. 적어도 원래의 화상 데이터는 그 데이터가 표시 장치의 화소에 입력될 때 변환되지 않는 것이 바람직하다.

[0013] 따라서, 본 발명의 일 형태의 목적은 화상 품질을 향상시킬 수 있는 표시 장치를 제공하는 것이다. 다른 목적은 화상 데이터를 변환하지 않고 적절한 표시를 수행할 수 있는 표시 장치를 제공하는 것이다. 다른 목적은 HDR 표시를 수행할 수 있는 표시 장치를 제공하는 것이다. 다른 목적은 업컨버전 동작을 수행할 수 있는 표시 장치를 제공하는 것이다. 다른 목적은 표시 화상의 휙도를 높일 수 있는 표시 장치를 제공하는 것이다. 다른 목적은 서로 겹쳐진 2개의 화상을 표시할 수 있는 표시 장치를 제공하는 것이다.

[0014] 다른 목적은 저소비전력의 표시 장치를 제공하는 것이다. 다른 목적은 신뢰성이 높은 표시 장치를 제공하는 것이다. 다른 목적은 신규 표시 장치 등을 제공하는 것이다. 다른 목적은 상술한 표시 장치 중 어느 것의 구동 방법을 제공하는 것이다. 다른 목적은 상기 표시 장치 중 어느 것의 구동 방법을 제공하는 것이다. 다른 목적은 신규 반도체 장치 등을 제공하는 것이다.

[0015] 또한 이들 목적의 기재는 다른 목적의 존재를 방해하지 않는다. 본 발명의 일 형태는 목적 모두를 달성할 필요

는 없다. 다른 목적은 명세서, 도면, 및 청구항 등의 기재로부터 명백해질 것이고 추출될 수 있다.

### 과제의 해결 수단

[0016] 본 발명의 일 형태는 화상 품질을 향상시킬 수 있는 표시 장치에 관한 것이다. 본 발명의 다른 일 형태는 화상 처리를 수행할 수 있는 표시 장치에 관한 것이다.

[0017] 본 발명의 일 형태는 제 1 트랜지스터, 제 2 트랜지스터, 제 3 트랜지스터, 제 1 용량 소자, 회로 블록, 제 1 배선, 및 제 2 배선을 포함하는 표시 장치이다. 제 1 트랜지스터의 소스 및 드레인 중 한쪽은 제 2 트랜지스터의 소스 및 드레인 중 한쪽에 전기적으로 접속된다. 제 2 트랜지스터의 소스 및 드레인 중 한쪽은 제 1 용량 소자의 한쪽 전극에 전기적으로 접속된다. 제 1 용량 소자의 다른 쪽 전극은 제 3 트랜지스터의 소스 및 드레인 중 한쪽에 전기적으로 접속된다. 제 3 트랜지스터의 소스 및 드레인 중 한쪽은 회로 블록에 전기적으로 접속된다. 제 1 트랜지스터의 소스 및 드레인 중 다른 쪽은 제 1 배선에 전기적으로 접속된다. 제 3 트랜지스터의 케이트는 제 2 배선에 전기적으로 접속된다. 제 2 트랜지스터의 케이트는 제 2 배선에 전기적으로 접속된다. 회로 블록은 표시 소자를 포함한다.

[0018] 본 발명의 다른 일 형태는 제 1 트랜지스터, 제 2 트랜지스터, 제 1 회로, 제 2 회로, 제 1 배선, 및 제 2 배선을 포함하는 표시 장치이다. 제 1 회로 및 제 2 회로는 각각 제 3 트랜지스터, 제 1 용량 소자, 및 회로 블록을 포함한다. 제 3 트랜지스터의 소스 및 드레인 중 한쪽은 제 1 용량 소자의 한쪽 전극에 전기적으로 접속된다. 제 1 용량 소자의 다른 쪽 전극은 제 1 트랜지스터의 소스 및 드레인 중 한쪽에 전기적으로 접속된다. 제 1 트랜지스터의 소스 및 드레인 중 한쪽은 제 2 트랜지스터의 소스 및 드레인 중 한쪽에 전기적으로 접속된다. 제 1 회로에서의 제 3 트랜지스터의 소스 및 드레인 중 다른 쪽은 제 1 배선에 전기적으로 접속된다. 제 1 트랜지스터의 소스 및 드레인 중 다른 쪽은 제 1 배선에 전기적으로 접속된다. 제 1 회로에서의 제 3 트랜지스터의 케이트는 제 2 배선에 전기적으로 접속된다. 제 2 회로에서의 제 3 트랜지스터의 케이트는 제 2 배선에 전기적으로 접속된다. 제 2 트랜지스터의 케이트는 제 2 배선에 전기적으로 접속된다. 회로 블록은 표시 소자를 포함한다.

[0019] 회로 블록은 제 4 트랜지스터, 제 5 트랜지스터, 제 2 용량 소자, 및 표시 소자로서 유기 EL 소자를 포함하고, 다음 구조를 가질 수 있다. 유기 EL 소자의 한쪽 전극은 제 5 트랜지스터의 소스 및 드레인 중 한쪽에 전기적으로 접속된다. 제 5 트랜지스터의 소스 및 드레인 중 다른 쪽은 제 2 용량 소자의 한쪽 전극에 전기적으로 접속된다. 제 2 용량 소자의 한쪽 전극은 제 4 트랜지스터의 소스 및 드레인 중 한쪽에 전기적으로 접속된다. 제 4 트랜지스터의 케이트는 제 2 용량 소자의 다른 쪽 전극에 전기적으로 접속된다. 제 2 용량 소자의 다른 쪽 전극은 제 1 용량 소자의 한쪽 전극에 전기적으로 접속된다.

[0020] 상술한 구조에서, 제 4 트랜지스터의 소스 및 드레인 중 다른 쪽은 제 2 트랜지스터의 소스 및 드레인 중 다른 쪽에 전기적으로 접속될 수 있다.

[0021] 회로 블록은 제 6 트랜지스터, 제 3 용량 소자, 및 표시 소자로서 액정 소자를 포함하고, 다음 구조를 가질 수 있다. 액정 소자의 한쪽 전극은 제 3 용량 소자의 한쪽 전극에 전기적으로 접속된다. 제 3 용량 소자의 한쪽 전극은 제 6 트랜지스터의 소스 및 드레인 중 한쪽에 전기적으로 접속된다. 제 6 트랜지스터의 소스 및 드레인 중 다른 쪽은 제 1 용량 소자의 한쪽 전극에 전기적으로 접속된다.

[0022] 상술한 구조에서, 제 3 용량 소자의 다른 쪽 전극은 제 2 트랜지스터의 소스 및 드레인 중 다른 쪽에 전기적으로 접속될 수 있다.

[0023] 제 3 트랜지스터는 채널 형성 영역에 금속 산화물을 포함한다. 금속 산화물은 In, Zn, 및 M(M은 Al, Ti, Ga, Sn, Y, Zr, La, Ce, Nd, 또는 Hf임)을 포함하는 것이 바람직하다.

### 발명의 효과

[0024] 본 발명의 일 형태에 따르면, 화상 품질을 향상시킬 수 있는 표시 장치를 제공할 수 있다. 화상 데이터를 변환하지 않고 적절한 표시를 수행할 수 있는 표시 장치를 제공할 수 있다. HDR 표시를 수행할 수 있는 표시 장치를 제공할 수 있다. 업컨버전 동작을 수행할 수 있는 표시 장치를 제공할 수 있다. 표시 화상의 휴도를 높일 수 있는 표시 장치를 제공할 수 있다. 서로 겹쳐진 2개의 화상을 표시할 수 있는 표시 장치를 제공할 수 있다.

[0025] 저소비전력의 표시 장치를 제공할 수 있다. 신뢰성이 높은 표시 장치를 제공할 수 있다. 신규 표시 장치 등을

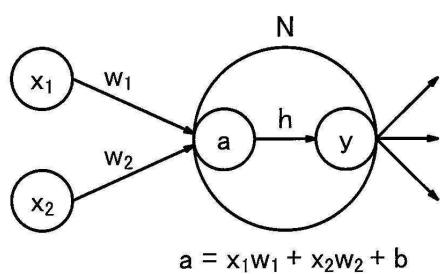

제공할 수 있다. 상기 표시 장치 중 어느 것의 구동 방법을 제공할 수 있다. 신규 반도체 장치 등을 제공할 수 있다.

### 도면의 간단한 설명

[0026]

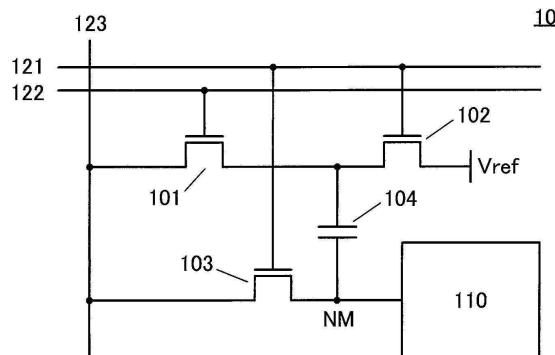

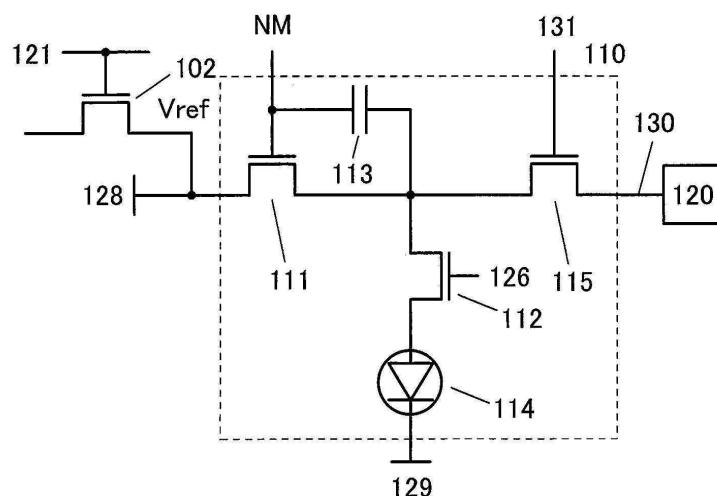

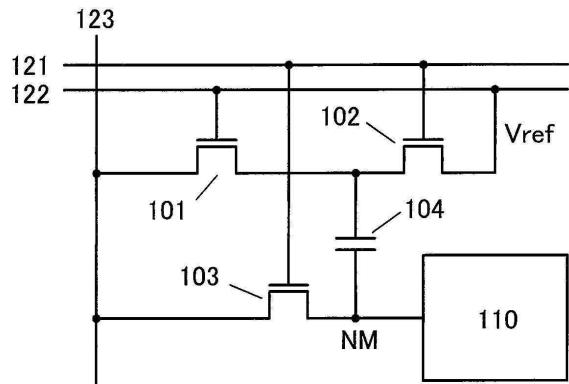

도 1은 화소 회로를 나타낸 것이다.

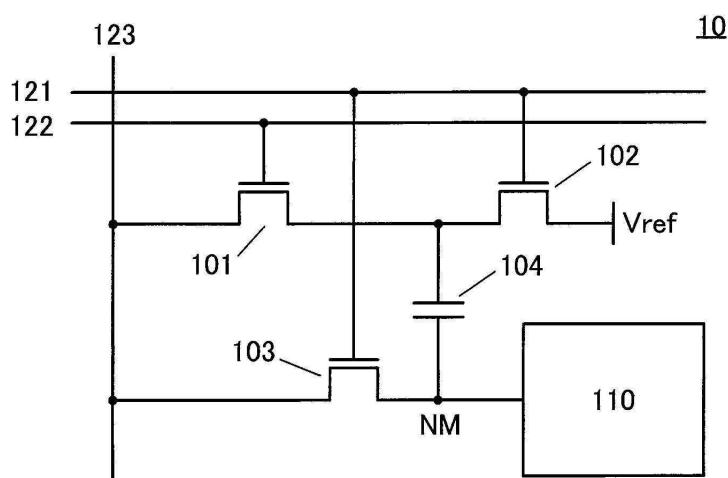

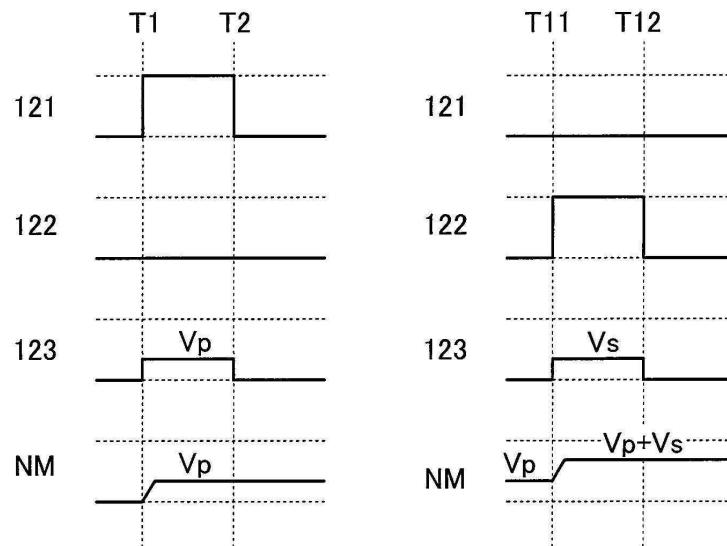

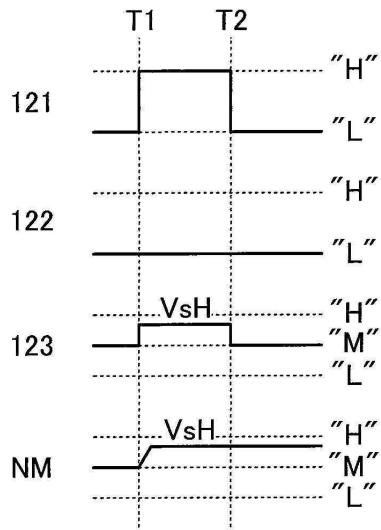

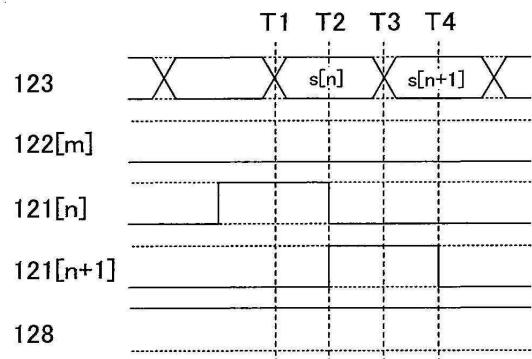

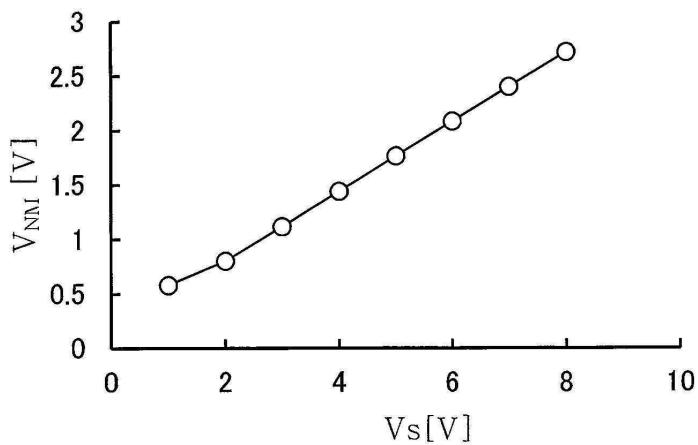

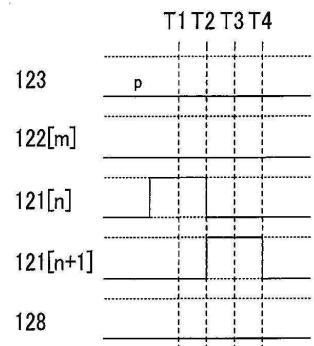

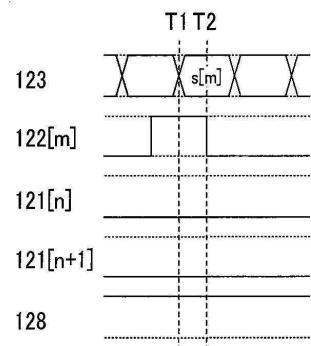

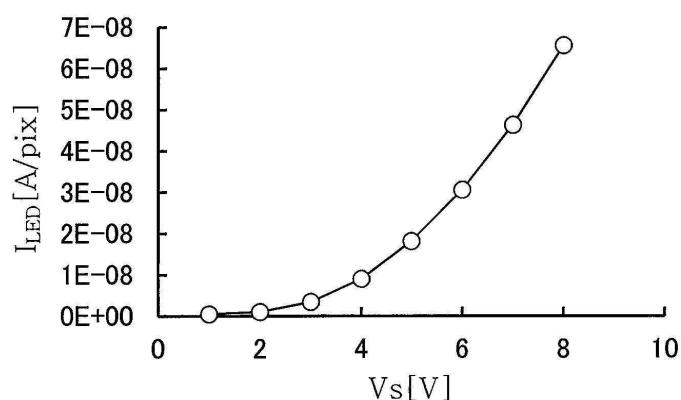

도 2의 (A) 및 (B)는 화소 회로의 동작을 나타내는 타이밍 차트이다.

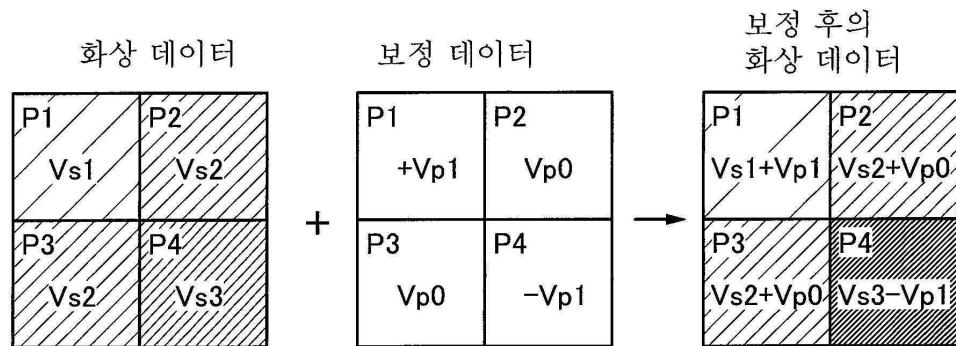

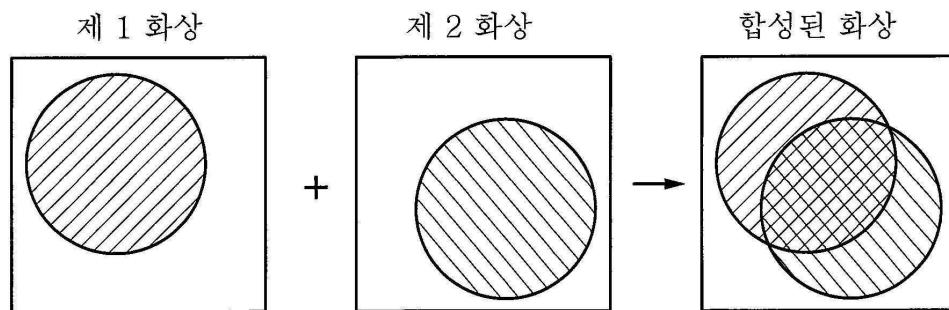

도 3의 (A) 및 (B)는 화상 데이터의 보정 및 화상의 합성을 나타낸 것이다.

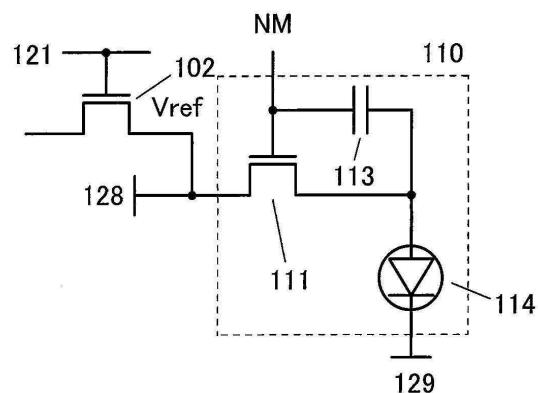

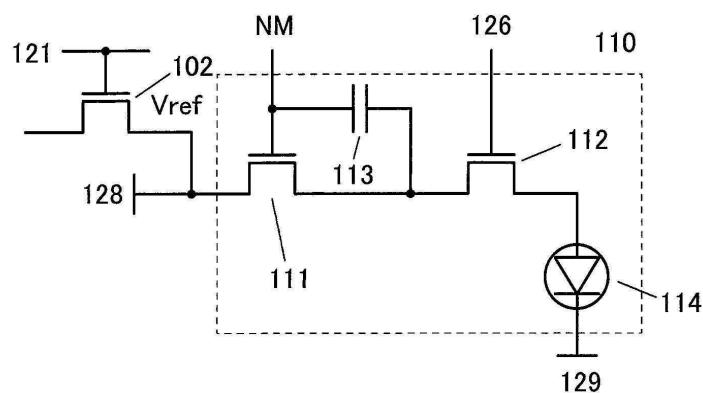

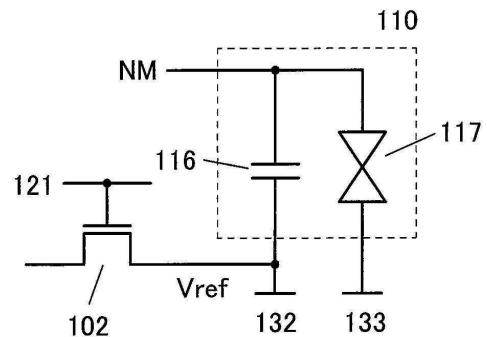

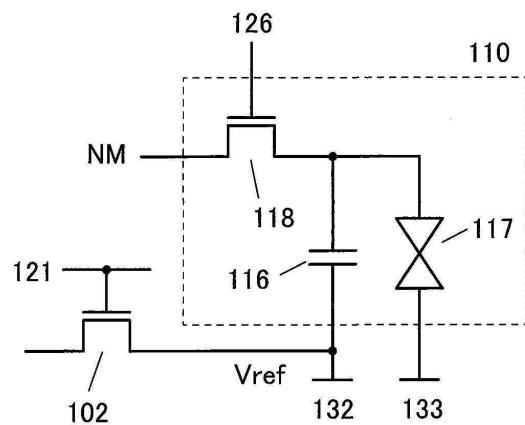

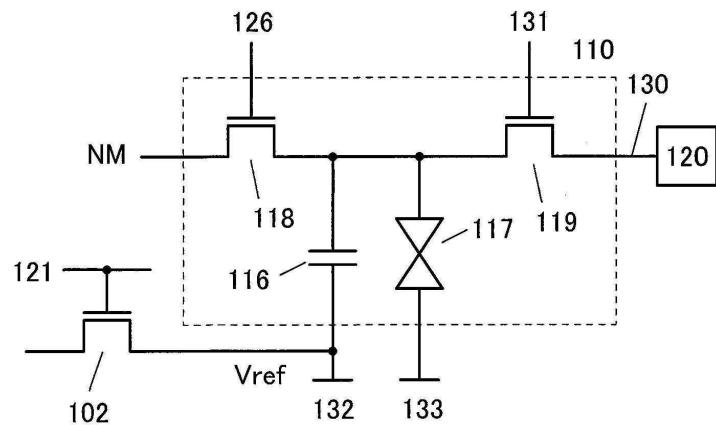

도 4의 (A) 내지 (C)는 각각 회로 블록을 나타낸 것이다.

도 5의 (A) 내지 (C)는 각각 회로 블록을 나타낸 것이다.

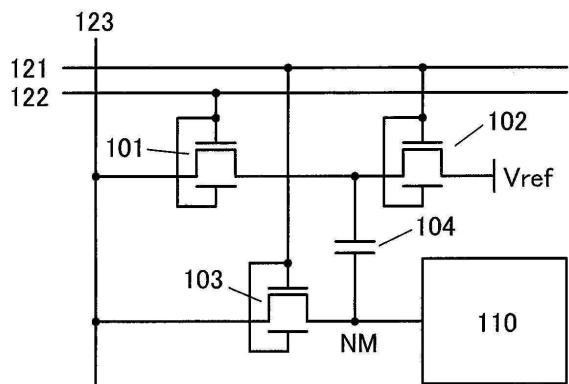

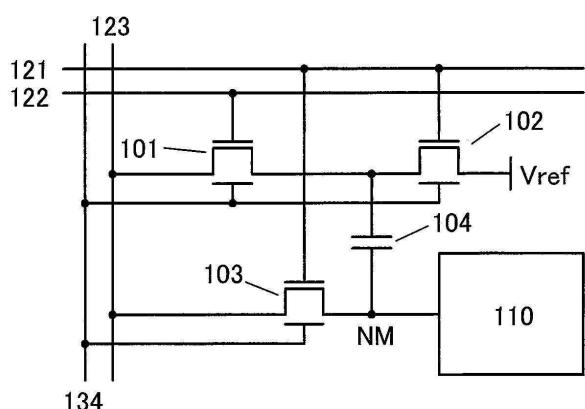

도 6의 (A) 내지 (C)는 각각 화소 회로를 나타낸 것이다.

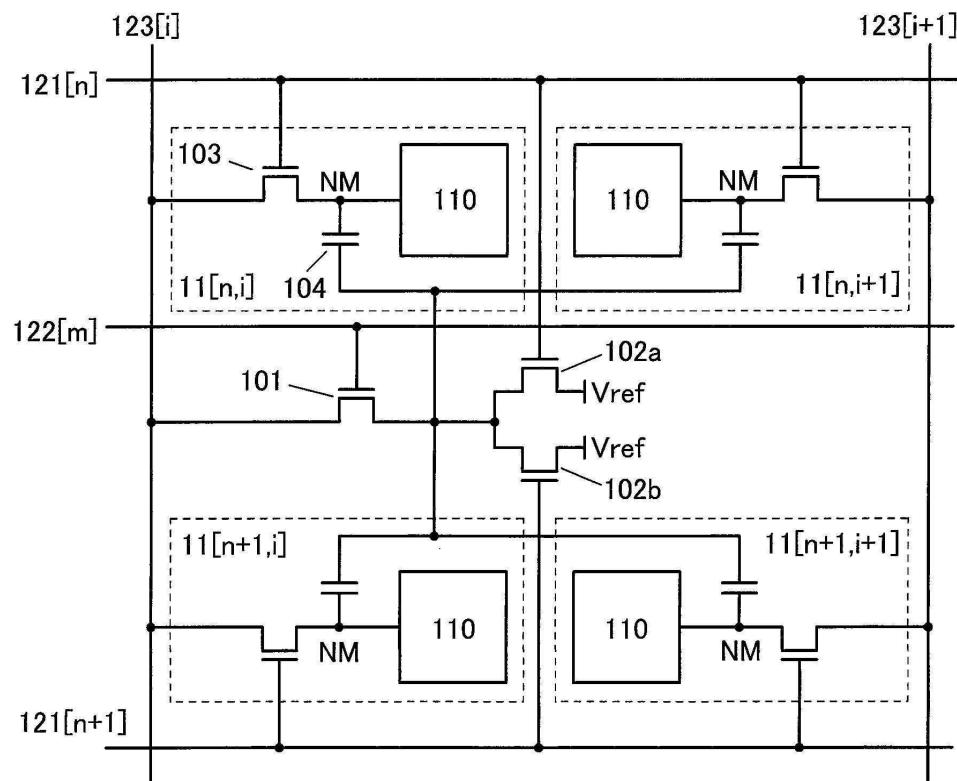

도 7은 화소 어레이를 나타낸 것이다.

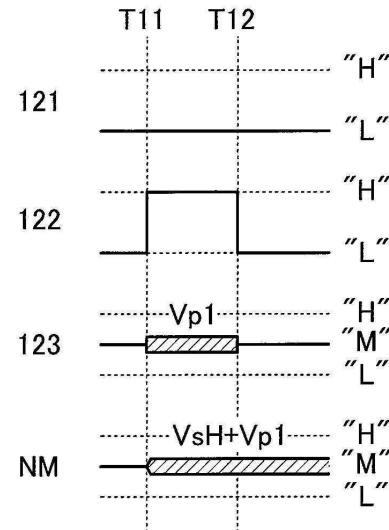

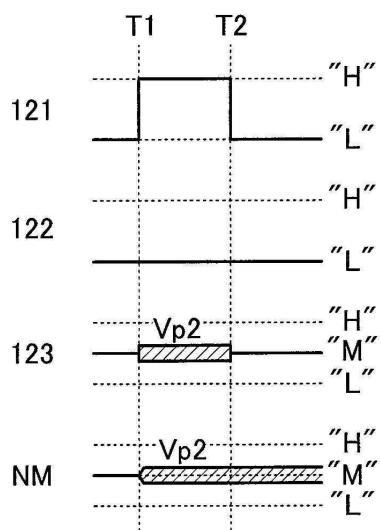

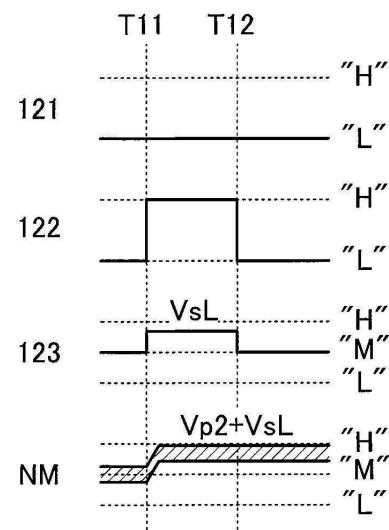

도 8의 (A1), (A2), (B1), 및 (B2)는 화소 어레이의 동작을 나타내는 타이밍 차트이다.

도 9의 (A) 내지 (C)는 표시 장치를 나타내는 블록도이다.

도 10의 (A) 및 (B)는 뉴럴 네트워크의 구조예를 나타낸 것이다.

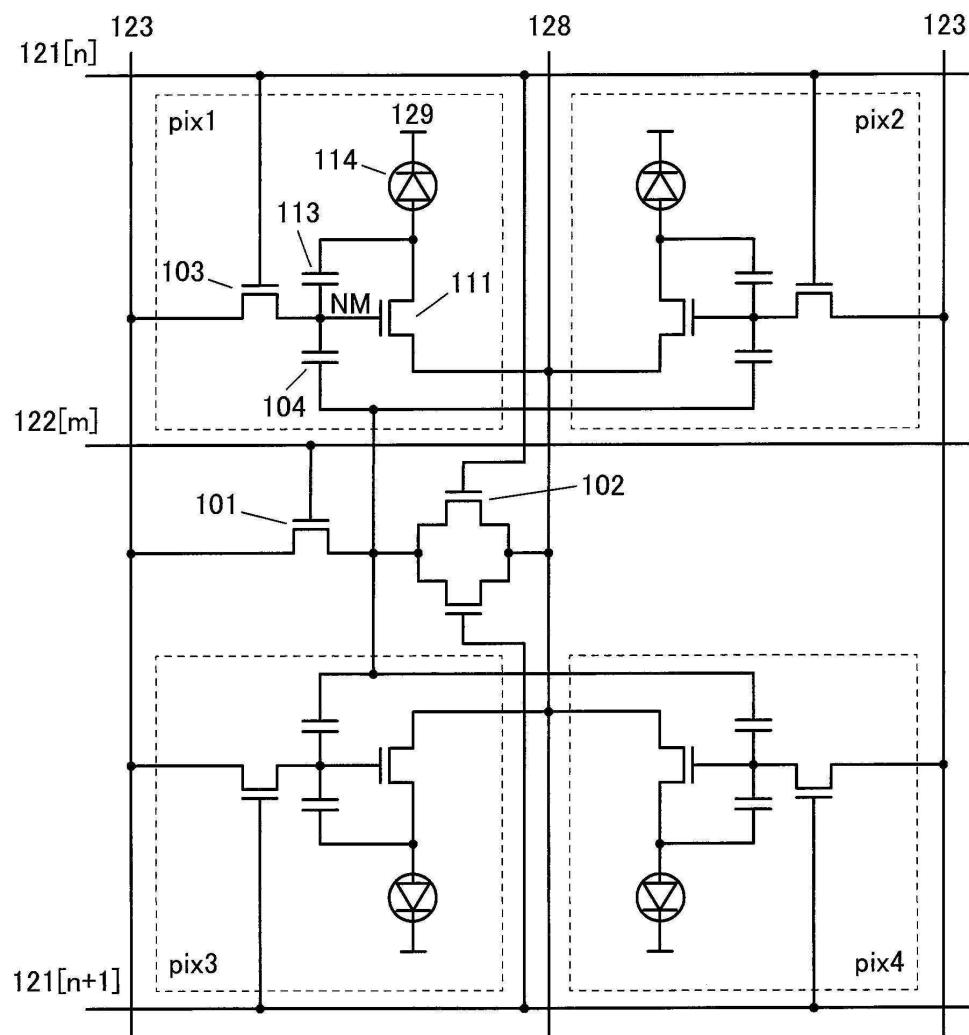

도 11은 시뮬레이션에 사용하는 화소 어레이의 구조를 나타낸 것이다.

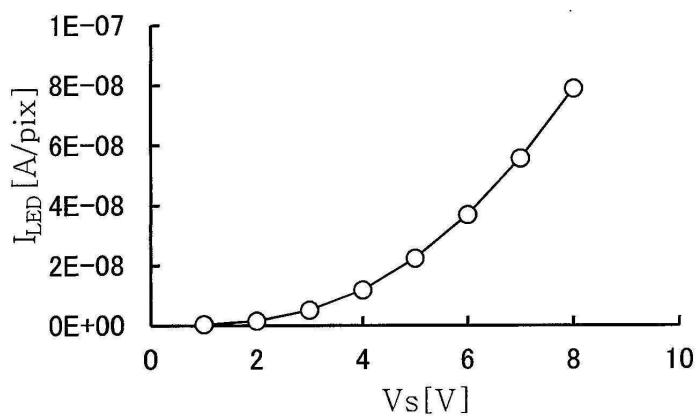

도 12의 (A) 내지 (C)는 시뮬레이션 결과를 나타낸 것이다.

도 13의 (A) 내지 (D)는 시뮬레이션 결과를 나타낸 것이다.

도 14의 (A) 내지 (D)는 시뮬레이션 결과를 나타낸 것이다.

도 15는 화소 구조를 나타낸 것이다.

도 16의 (A) 내지 (C)는 각각 표시 장치를 나타낸 것이다.

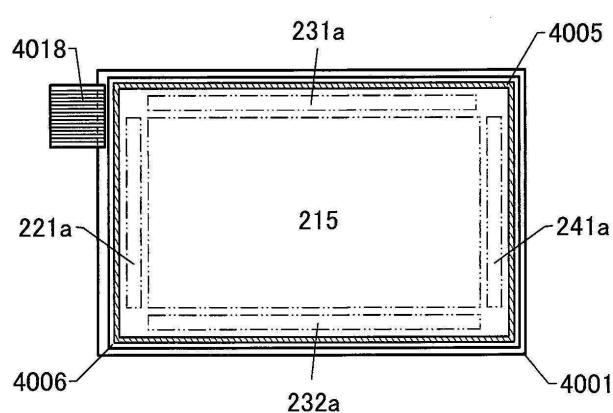

도 17의 (A) 및 (B)는 터치 패널을 나타낸 것이다.

도 18의 (A) 및 (B)는 각각 표시 장치를 나타낸 것이다.

도 19의 (A1), (A2), (B1), (B2), (C1), 및 (C2)는 각각 트랜지스터를 나타낸 것이다.

도 20의 (A1), (A2), (B1), (B2), (C1), 및 (C2)는 각각 트랜지스터를 나타낸 것이다.

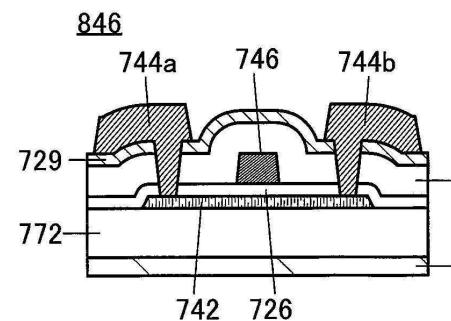

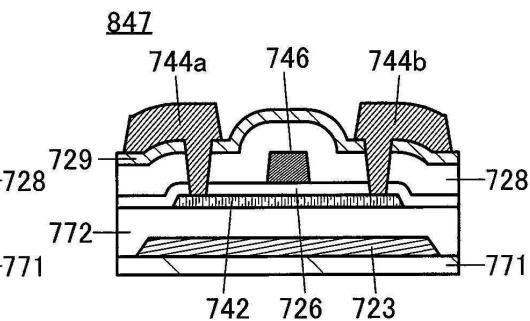

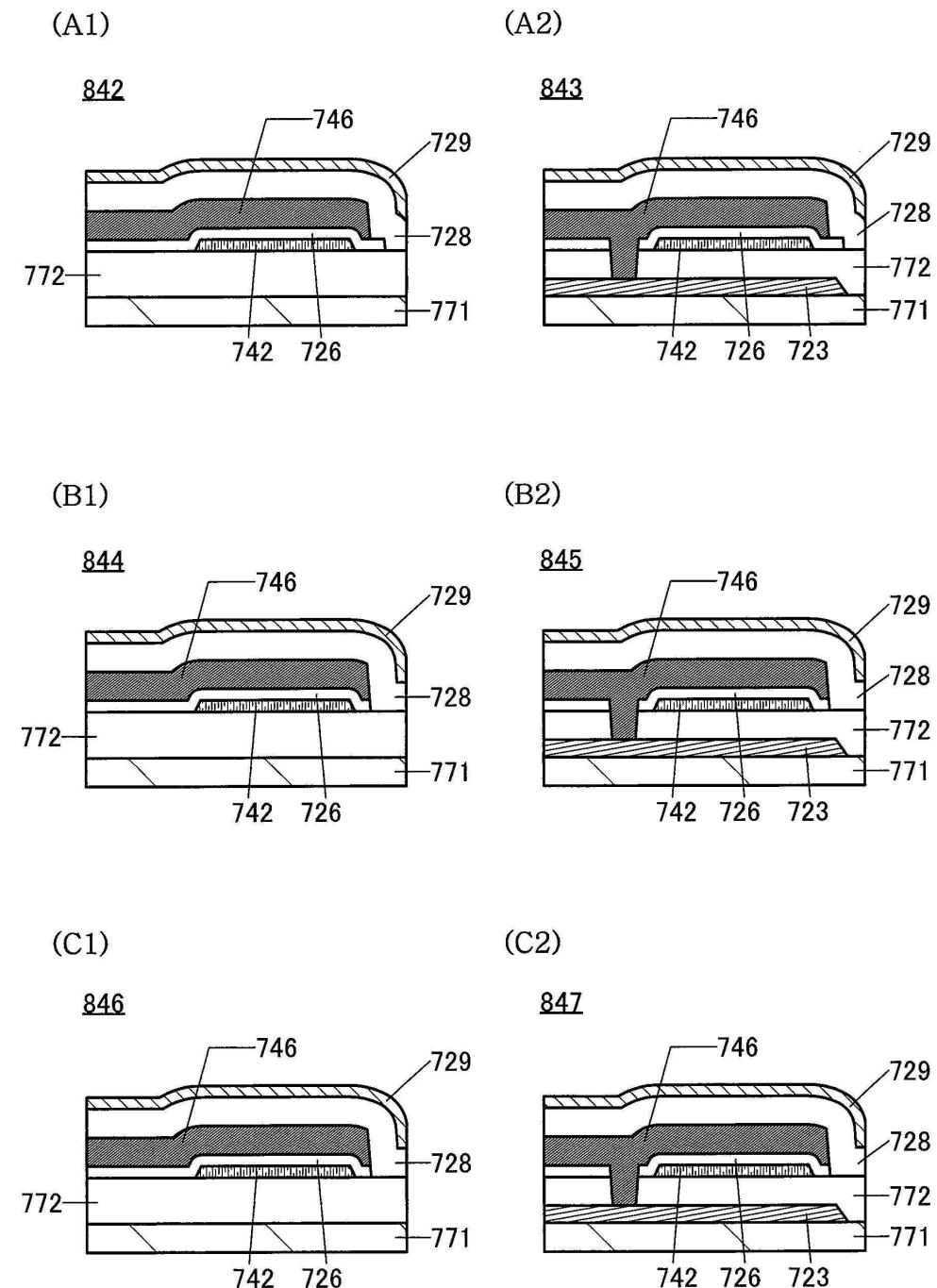

도 21의 (A1), (A2), (B1), (B2), (C1), 및 (C2)는 각각 트랜지스터를 나타낸 것이다.

도 22의 (A1), (A2), (B1), (B2), (C1), 및 (C2)는 각각 트랜지스터를 나타낸 것이다.

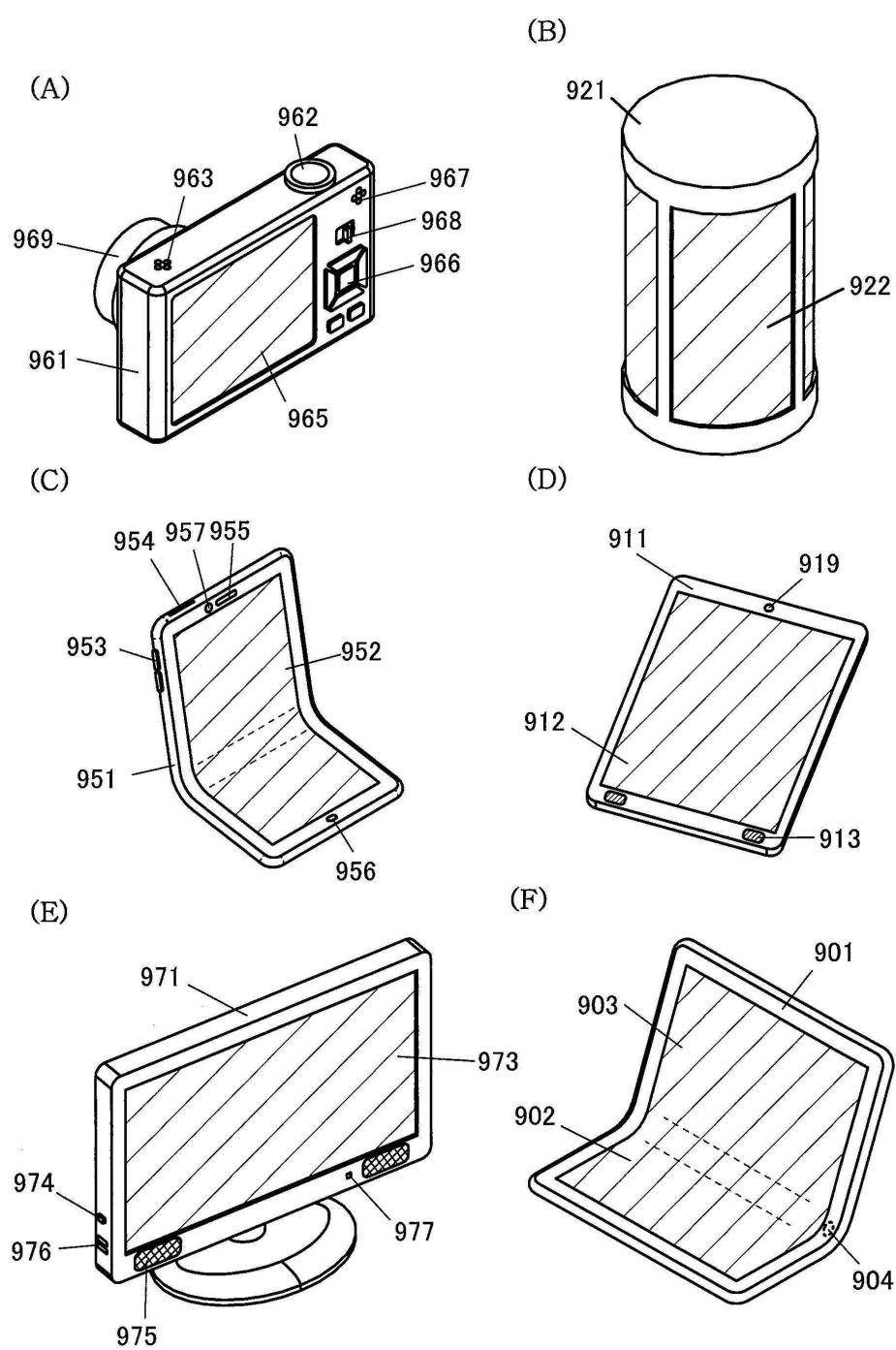

도 23의 (A) 내지 (F)는 각각 전자 기기를 나타낸 것이다.

### 발명을 실시하기 위한 구체적인 내용

[0027]

실시형태에 대하여 도면을 참조하여 자세히 설명한다. 또한 본 발명은 아래의 설명에 한정되지 않고, 본 발명의 취지 및 범위에서 벗어나지 않고 형태 및 자세한 사항을 다양하게 변경할 수 있다는 것은 통상의 기술자에 의하여 쉽게 이해된다. 따라서 본 발명은 아래의 실시형태의 기재에 한정하여 해석되지 말아야 한다. 또한 아래에서 설명하는 발명의 구조에서, 같은 부분 또는 비슷한 기능을 가지는 부분을 다른 도면에서 같은 부호로 나타내며, 그 설명을 반복하지 않는 경우가 있다. 그러나 같은 구성 요소가 다른 도면에서 다른 해칭 패턴으로 나타내어지거나, 해칭 패턴이 생략되는 경우가 있다.

[0028]

(실시형태 1)

[0029]

본 실시형태에서는 본 발명의 일 형태의 표시 장치에 대하여 도면을 참조하여 설명한다.

[0030]

본 발명의 일 형태는 화소에서 화상 데이터를 보정하는 기능을 가지는 표시 장치이다. 각 화소에 기억 노드가 제공되고 기억 노드에 제 1 데이터를 유지할 수 있다. 용량 결합에 의하여 제 1 데이터에 제 2 데이터가 부가 되고, 표시 소자에 공급될 수 있다. 또는 제 2 데이터가 기억 노드에 기록된 후, 용량 결합에 의하여 제 1 데

이터가 부가될 수 있다.

[0031] 따라서 표시 장치는 보정된 화상을 표시할 수 있다. 보정을 통하여 화상의 업컨버전을 수행할 수 있다. 또는 표시부에서의 화상의 일부 또는 전체를 보정함으로써 HDR 표시를 수행할 수 있다. 또는 제 1 데이터 및 제 2 데이터로서 같은 화상 데이터를 사용하면, 표시 화상의 휘도를 현저히 향상시킬 수 있다. 또는 제 1 데이터 및 제 2 데이터로서 상이한 화상 데이터를 사용하면, 서로 겹쳐진 임의의 화상을 표시할 수 있다.

[0032] 또한 본 발명의 일 형태에 따르면, 고해상도용 화상 데이터 및 저해상도용 화상 데이터의 양쪽 모두의 업컨버전 또는 다운컨버전을 하지 않고 적절한 표시를 수행할 수 있다. 고해상도 표시를 하기 위해서는, 각 화소에 포함되는 제 1 트랜지스터를 통하여 각 화소에 개별 데이터를 공급한다. 저해상도 표시를 하기 위해서는, 복수의 화소에 전기적으로 접속되는 제 2 트랜지스터를 통하여 복수의 화소에 동일 데이터를 공급한다.

[0033] 여기서 고해상도용 화상 데이터란 예를 들어 8K4K(화소수  $7680 \times 4320$ )에 대응하는 데이터를 말한다. 저해상도용 화상 데이터란 예를 들어 4K2K(화소수  $3840 \times 2160$ )에 대응하는 데이터를 말한다. 그러므로 고해상도용 화상 데이터수 대 저해상도용 화상 데이터수의 유효한 비율(유효 화소수에 대응함)을 4:1이라고 가정한다.

[0034] 또한 데이터(화소)수의 비율이 4:1이기만 하면, 상술한 예에 한정되지 않고, 고해상도용 화상 데이터가 4K2K에 대응하는 데이터이어도 좋고, 저해상도용 화상 데이터가 풀 HD(화소수  $1920 \times 1080$ )에 대응하는 데이터이어도 좋다. 또는 고해상도용 화상 데이터가 16K8K( $15360 \times 8640$ )에 대응하는 데이터이어도 좋고, 저해상도용 화상 데이터가 8K4K에 대응하는 데이터이어도 좋다.

[0035] 도 1은 본 발명의 일 형태의 표시 장치에 사용될 수 있는 화소(10)를 나타낸 것이다. 화소(10)는 트랜지스터(101), 트랜지스터(102), 트랜지스터(103), 용량 소자(104), 및 회로 블록(110)을 포함한다. 회로 블록(110)은 트랜지스터, 용량 소자, 및 표시 소자 등을 포함할 수 있고, 자세한 사항은 나중에 설명한다.

[0036] 트랜지스터(101)의 소스 및 드레인 중 한쪽은 트랜지스터(102)의 소스 및 드레인 중 한쪽에 전기적으로 접속된다. 트랜지스터(102)의 소스 및 드레인 중 한쪽은 용량 소자(104)의 한쪽 전극에 전기적으로 접속된다. 용량 소자(104)의 다른 쪽 전극은 트랜지스터(103)의 소스 및 드레인 중 한쪽에 전기적으로 접속된다. 트랜지스터(103)의 소스 및 드레인 중 한쪽은 회로 블록(110)에 전기적으로 접속된다.

[0037] 여기서, 노드(NM)란 트랜지스터(103)의 소스 및 드레인 중 한쪽, 용량 소자(104)의 다른 쪽 전극, 및 회로 블록(110)이 접속되는 배선을 말한다. 또한 노드(NM)는 노드(NM)에 접속된 회로 블록(110)의 구성 요소에 따라 플로팅이 될 수 있다.

[0038] 트랜지스터(101)의 게이트는 배선(122)에 전기적으로 접속된다. 트랜지스터(102)의 게이트 및 트랜지스터(103)의 게이트는 배선(121)에 전기적으로 접속된다. 트랜지스터(101)의 소스 및 드레인 중 다른 쪽 및 트랜지스터(103)의 소스 및 드레인 중 다른 쪽은 배선(123)에 전기적으로 접속된다. 트랜지스터(102)의 소스 및 드레인 중 다른 쪽은 특정 전위 "Vref"를 공급할 수 있는 배선에 전기적으로 접속된다.

[0039] 배선(121 및 122)은 각각 트랜지스터의 동작을 제어하기 위한 신호선으로서 기능할 수 있다. 배선(123)은 제 1 데이터 또는 제 2 데이터를 공급하는 신호선으로서 기능할 수 있다. "Vref"를 공급할 수 있는 배선으로서 예를 들어 회로 블록(110)의 구성 요소에 전기적으로 접속되는 전원선을 사용할 수 있다.

[0040] 후술하는 용량 결합 동작을 하기 위하여, 같은 기간에서 "Vref" 및 제 1 데이터(예를 들어 보정 데이터)를 화소에 공급할 필요가 있다. 이런 이유로 신호선으로부터 "Vref"를 공급하는 경우에는, 적어도 제 1 데이터를 공급하는 신호선 및 "Vref" 또는 제 2 데이터(예를 들어 화상 데이터)를 공급하는 신호선이 필요하다.

[0041] 그러나 본 발명의 일 형태의 표시 장치에서는 전원선 등으로부터 "Vref"를 공급한다. 이에 의하여, 하나의 신호선(배선(123))이 제 1 데이터와 제 2 데이터를 상이한 타이밍에 공급할 수 있다. 따라서, 표시 장치의 배선 수를 저감할 수 있다.

[0042] 노드(NM)는 기억 노드이다. 트랜지스터(103)를 온으로 하면, 배선(123)에 공급된 데이터를 노드(NM)에 기록할 수 있다. 트랜지스터(103)를 오프로 하면, 상기 데이터를 노드(NM)에 유지할 수 있다. 오프 상태 전류가 매우 낮은 트랜지스터를 트랜지스터(103)로서 사용함으로써, 노드(NM)의 전위를 장시간 유지할 수 있다. 이 트랜지스터로서는, 예를 들어 금속 산화물을 채널 형성 영역에 사용한 트랜지스터(이하 OS 트랜지스터라고 함)를 사용할 수 있다.

[0043] 트랜지스터(103)뿐만 아니라 화소에서의 다른 트랜지스터에도 OS 트랜지스터를 사용하여도 좋다. 트랜지스터

(103)로서는 Si을 채널 형성 영역에 포함한 트랜지스터(이하 Si 트랜지스터라고 함)를 사용하여도 좋다. OS 트랜지스터 및 Si 트랜지스터의 양쪽을 사용하여도 좋다. Si 트랜지스터의 예에는 비정질 실리콘을 포함한 트랜지스터 및 결정성 실리콘(대표적으로는 저온 폴리실리콘 및 단결정 실리콘)을 포함한 트랜지스터가 포함된다.

[0044] OS 트랜지스터에 사용하는 반도체 재료로서는, 에너지 갭이 2eV 이상, 바람직하게는 2.5eV 이상, 더 바람직하게는 3eV 이상인 금속 산화물을 사용할 수 있다. 대표적인 예는 인듐을 포함한 산화물 반도체이고, 예를 들어 후술하는 CAAC-OS 또는 CAC-OS를 사용할 수 있다. CAAC-OS는 안정적인 원자를 포함한 결정 구조를 가져, 높은 신뢰성이 요구되는 트랜지스터 등에 적합하다. CAC-OS는 이동도가 높아, 고속으로 동작하는 트랜지스터 등에 적합하다.

[0045] OS 트랜지스터는 에너지 갭이 크기 때문에, 오프 상태 전류가 매우 낮다. OS 트랜지스터는 Si 트랜지스터와는 달리 충격 이온화(impact ionization), 애벌란시 항복(avalanche breakdown), 또는 단채널 효과 등이 발생하지 않는 특징을 가진다. 그러므로 OS 트랜지스터를 사용하면 신뢰성이 높은 회로를 형성할 수 있다.

[0046] OS 트랜지스터에서의 반도체층은 예를 들어 인듐, 아연, 및 M(알루미늄, 타이타늄, 갈륨, 저마늄, 이트륨, 치르코늄, 란타넘, 세륨, 주석, 네오디뮴, 또는 하프늄 등의 금속)을 포함한 In-M-Zn계 산화물로 나타내어지는 막으로 할 수 있다.

[0047] 반도체층에서의 산화물 반도체가 In-M-Zn계 산화물인 경우, In-M-Zn 산화물의 막을 형성하기 위하여 사용되는 스퍼터링 타깃의 금속 원소의 원자수비는  $In \geq M$  및  $Zn \geq M$ 을 만족시키는 것이 바람직하다. 이와 같은 스퍼터링 타깃의 금속 원소의 원자수비는 예를 들어  $In:M:Zn=1:1:1$ ,  $In:M:Zn=1:1:1.2$ ,  $In:M:Zn=3:1:2$ ,  $In:M:Zn=4:2:3$ ,  $In:M:Zn=4:2:4.1$ ,  $In:M:Zn=5:1:6$ ,  $In:M:Zn=5:1:7$ , 또는  $In:M:Zn=5:1:8$ 인 것이 바람직하다. 또한 형성되는 반도체층의 금속 원소의 원자수비는 상기 스퍼터링 타깃의 금속 원소의 상술한 원자수비로부터  $\pm 40\%$ 의 범위 내에서 변동된다.

[0048] 반도체층에는 캐리어 밀도가 낮은 산화물 반도체를 사용한다. 예를 들어, 반도체층은 캐리어 밀도가  $1 \times 10^{17}/\text{cm}^3$  이하, 바람직하게는  $1 \times 10^{15}/\text{cm}^3$  이하, 더 바람직하게는  $1 \times 10^{13}/\text{cm}^3$  이하, 더욱 바람직하게는  $1 \times 10^{11}/\text{cm}^3$  이하, 더욱더 바람직하게는  $1 \times 10^{10}/\text{cm}^3$  미만이고,  $1 \times 10^{-9}/\text{cm}^3$  이상인 산화물 반도체를 사용할 수 있다. 이와 같은 산화물 반도체를 고순도 진성 또는 실질적으로 고순도 진성인 산화물 반도체라고 한다. 이 산화물 반도체는 결함 준위 밀도가 낮고 안정적인 특성을 가진다고 할 수 있다.

[0049] 또한 상술한 것에 한정되지 않고, 요구되는 트랜지스터의 반도체 특성 및 전기 특성(예를 들어 전계 효과 이동도 및 문턱 전압)에 따라 적절한 조성의 재료를 사용할 수 있다. 요구되는 트랜지스터의 반도체 특성을 얻기 위하여, 반도체층의 캐리어 밀도, 불순물 농도, 결함 밀도, 금속 원소와 산소의 원자수비, 원자간 거리, 및 밀도 등을 적절한 값으로 하는 것이 바람직하다.

[0050] 반도체층에서의 산화물 반도체에 14족에 속하는 원소인 실리콘 또는 탄소가 포함되면, 반도체층에서 산소 결손의 개수가 증가되어, 반도체층이 n형이 된다. 그러므로 반도체층에서의 실리콘 또는 탄소의 농도(이차 이온 질량 분석법에 의하여 측정됨)를  $2 \times 10^{18} \text{ atoms}/\text{cm}^3$  이하, 바람직하게는  $2 \times 10^{17} \text{ atoms}/\text{cm}^3$  이하로 한다.

[0051] 알칼리 금속 및 알칼리 토금속은 산화물 반도체와 결합되면 캐리어를 생성할 수 있고, 이 경우 트랜지스터의 오프 상태 전류가 증가될 수 있다. 그러므로, 반도체층에서의 알칼리 금속 또는 알칼리 토금속의 농도(이차 이온 질량 분석법에 의하여 측정됨)를  $1 \times 10^{18} \text{ atoms}/\text{cm}^3$  이하, 바람직하게는  $2 \times 10^{16} \text{ atoms}/\text{cm}^3$  이하로 한다.

[0052] 반도체층에서의 산화물 반도체에 질소가 포함되면, 캐리어로서 기능하는 전자가 발생하고 캐리어 밀도가 높아지기 때문에, 반도체층이 n형이 되기 쉽다. 따라서 질소를 포함하는 산화물 반도체를 사용한 트랜지스터는 노멀리 온이 되기 쉽다. 그러므로 반도체층에서의 질소의 농도(이차 이온 질량 분석법에 의하여 측정됨)를  $5 \times 10^{18} \text{ atoms}/\text{cm}^3$  이하로 하는 것이 바람직하다.

[0053] 반도체층은 예를 들어 비단결정 구조를 가져도 좋다. 비단결정 구조의 예에는 c축 배향된 결정을 포함한 CAAC-OS(c-axis aligned crystalline oxide semiconductor), 다결정 구조, 미결정 구조, 및 비정질 구조가 포함된다. 비단결정 구조 중, 비정질 구조는 결함 준위 밀도가 가장 높은 한편, CAAC-OS는 결함 준위 밀도가 가장 낮다.

[0054] 비정질 구조를 가지는 산화물 반도체막은 예를 들어, 원자 배열이 무질서하고 결정 성분을 가지지 않는다. 다

른 예에서, 비정질 구조를 가지는 산화물막은 완전한 비정질 구조를 가지고, 결정부를 가지지 않는다.

[0055] 또한 반도체층은 비정질 구조를 가지는 영역, 미결정 구조를 가지는 영역, 다결정 구조를 가지는 영역, CAAC-OS의 영역, 및 단결정 구조를 가지는 영역 중 2개 이상을 포함한 혼합막이어도 좋다. 혼합막은 예를 들어, 상술한 영역 중 2개 이상을 포함한 단층 구조 또는 적층 구조를 가지는 경우가 있다.

[0056] 아래에서는, 비단결정 반도체층의 일 형태인 CAC-OS(cloud-aligned composite oxide semiconductor)의 구성에 대하여 설명한다.

[0057] CAC-OS는 예를 들어 산화물 반도체에 포함되는 원소가 고르지 않게 분포된 구성을 가진다. 고르지 않게 분포된 원소를 포함하는 각 재료는 0.5nm 이상 10nm 이하, 바람직하게는 1nm 이상 2nm 이하, 또는 이와 비슷한 크기를 가진다. 또한 아래에서 설명하는 산화물 반도체에서, 하나 이상의 금속 원소가 고르지 않게 분포되고 이 금속 원소(들)를 포함하는 영역이 혼합된 상태를 모자이크 패턴 또는 패치상 패턴이라고 한다. 영역은 0.5nm 이상 10nm 이하, 바람직하게는 1nm 이상 2nm 이하, 또는 이와 비슷한 크기를 가진다.

[0058] 또한 산화물 반도체는 적어도 인듐을 포함하는 것이 바람직하다. 특히, 인듐 및 아연을 포함하는 것이 바람직하다. 또한 알루미늄, 갈륨, 이트륨, 구리, 바나듐, 베릴륨, 봉소, 실리콘, 타이타늄, 철, 니켈, 저마늄, 지르코늄, 몰리브데늄, 란타늄, 세륨, 네오디뮴, 하프늄, 탄탈럼, 텉스텐, 및 마그네슘 등 중 하나 이상이 포함되어도 좋다.

[0059] 예를 들어 CAC-OS 중, CAC 구성을 가지는 In-Ga-Zn 산화물(이와 같은 In-Ga-Zn 산화물을 특히 CAC-IGZO라고 하여도 좋음)은 인듐 산화물( $In_{X_1}O$ , 여기서  $X_1$ 은 0보다 큰 실수(實數)임) 또는 인듐 아연 산화물( $In_{X_2}Zn_{Y_2}O_{Z_2}$ , 여기서  $X_2$ ,  $Y_2$ , 및  $Z_2$ 는 0보다 큰 실수임)과, 갈륨 산화물( $Ga_{X_3}O$ , 여기서  $X_3$ 은 0보다 큰 실수임) 또는 갈륨 아연 산화물( $Ga_{X_4}Zn_{Y_4}O_{Z_4}$ , 여기서  $X_4$ ,  $Y_4$ , 및  $Z_4$ 는 0보다 큰 실수임)로 재료가 분리되어 모자이크 패턴이 형성되는 구성을 가진다. 그리고 모자이크 패턴을 형성하는  $In_{X_1}O$  또는  $In_{X_2}Zn_{Y_2}O_{Z_2}$ 가 막 내에 고르게 분포되어 있다. 이 구성을 클라우드상 구성이라고도 한다.

[0060] 즉 CAC-OS는  $Ga_{X_3}O$ 를 주성분으로서 포함하는 영역과,  $In_{X_2}Zn_{Y_2}O_{Z_2}$  또는  $In_{X_1}O$ 를 주성분으로서 포함하는 영역이 혼합된 구성을 가지는 복합 산화물 반도체이다. 또한 본 명세서에서는, 예를 들어 제 1 영역에서의 원소 M에 대한 In의 원자수비가 제 2 영역에서의 원소 M에 대한 In의 원자수비보다 클 때, 제 1 영역을 제 2 영역보다 In의 농도가 높은 것으로서 설명한다.

[0061] 또한 IGZO로서는 In, Ga, Zn, 및 O를 포함한 화합물도 알려져 있다. IGZO의 대표적인 예에는  $InGaO_3(ZnO)_{m_1}$  ( $m_1$ 은 자연수임)로 나타내어지는 결정성 화합물 및  $In_{(1+x_0)}Ga_{(1-x_0)}O_3(ZnO)_{m_0}$  ( $-1 \leq x_0 \leq 1$ ,  $m_0$ 은 임의의 수임)으로 나타내어지는 결정성 화합물이 포함된다.

[0062] 상기 결정성 화합물은 단결정 구조, 다결정 구조, 또는 CAAC 구조를 가진다. 또한 CAAC 구조는 복수의 IGZO 나노 결정이 c축 배향을 가지고 a-b면 방향에서는 배향하지 않고 연결된 결정 구조이다.

[0063] CAC-OS는 산화물 반도체의 재료 구성에 관한 것이다. In, Ga, Zn, 및 O를 포함하는 CAC-OS의 재료 구성에서, Ga을 주성분으로서 포함하는 나노 입자 영역이 CAC-OS의 일부에 관찰되고, In을 주성분으로서 포함하는 나노 입자 영역이 그 일부에 관찰된다. 이를 나노 입자 영역은 무작위로 분산되어 모자이크 패턴을 형성한다. 따라서 이 결정 구조는 CAC-OS에서 부차적인 요소이다.

[0064] 또한 CAC-OS에서, 원자수비가 다른 2개 이상의 막을 포함하는 적층 구조는 포함되지 않는다. 예를 들어, In을 주성분으로서 포함하는 막과 Ga을 주성분으로서 포함하는 막의 2층 구조는 포함되지 않는다.

[0065]  $Ga_{X_3}O$ 를 주성분으로서 포함하는 영역과  $In_{X_2}Zn_{Y_2}O_{Z_2}$  또는  $In_{X_1}O$ 를 주성분으로서 포함하는 영역의 경계가 명확하게 관찰되지 않는 경우가 있다.

[0066] CAC-OS에서 갈륨 대신에, 알루미늄, 이트륨, 구리, 바나듐, 베릴륨, 봉소, 실리콘, 타이타늄, 철, 니켈, 저마늄, 지르코늄, 몰리브데늄, 란타늄, 세륨, 네오디뮴, 하프늄, 탄탈럼, 텉스텐, 및 마그네슘 등 중 하나 이상이 포함되는 경우, CAC-OS의 일부에 선택된 금속 원소(들)를 주성분으로서 포함하는 나노 입자 영역이 관찰되고, CAC-OS의 일부에 In을 주성분으로서 포함하는 나노 입자 영역이 관찰되고, 이를 나노 입자 영역은 CAC-OS에서 무작위로 분산되어 모자이크 패턴을 형성한다.

[0067] CAC-OS는 예를 들어, 기판을 의도적으로 가열하지 않는 조건하에서 스퍼터링법에 의하여 형성할 수 있다. 스퍼터링법에 의하여 CAC-OS를 형성하는 경우, 퇴적 가스로서 불활성 가스(대표적으로는 아르곤), 산소 가스, 및 질소 가스 중 하나 이상을 사용할 수 있다. 퇴적 시의 퇴적 가스의 총유량에 대한 산소 가스의 유량은 가능한 한 낮은 것이 바람직하고, 예를 들어 산소 가스의 유량을 0% 이상 30% 미만, 바람직하게는 0% 이상 10% 이하로 한다.

[0068] CAC-OS는 X선 회절(XRD) 측정 방법인, out-of-plane법에 의한  $\Theta/2\Theta$  스캔을 사용하여 측정을 실시한 경우에, 명확한 피크가 관찰되지 않는다는 특징을 가진다. 즉 XRD 측정에 의하여, 측정 영역에서는 a-b면 방향 및 c축 방향의 배향이 없는 것을 알았다.

[0069] CAC-OS에서는, 프로브 직경이 1nm인 전자선(나노빔 전자선이라고도 함)을 조사함으로써 얻어지는 전자 회절 패턴이 링 패턴으로 회도가 높은 영역을 가지고, 상기 링 패턴에 복수의 회절이 나타난다. 그러므로 전자 회절 패턴으로부터, CAC-OS의 결정 구조가 평면 방향 및 단면 방향에서 배향성을 나타내지 않는 nc(nanocrystalline) 구조를 포함하는 것을 알았다.

[0070] 예를 들어 에너지 분산형 X선 분광법(EDX)은 EDX 매팡을 취득하는 데 사용되고, 그 EDX 매팡에 따르면 In-Ga-Zn 산화물의 CAC-OS는  $GaO_{x3}$ 을 주성분으로서 포함하는 영역 및  $In_{x2}Zn_{y2}O_{z2}$  또는  $InO_{x1}$ 을 주성분으로서 포함하는 영역이 고르지 않게 분포되고 혼합된 구성을 가진다.

[0071] CAC-OS는 금속 원소가 고르게 분포된 IGZO 화합물과는 다른 구조를 가지고, IGZO 화합물과는 다른 성질을 가진다. 즉 CAC-OS에서,  $GaO_{x3}$  등을 주성분으로서 포함하는 영역 및  $In_{x2}Zn_{y2}O_{z2}$  또는  $InO_{x1}$ 을 주성분으로서 포함하는 영역은 분리되어 모자이크 패턴을 형성한다.

[0072]  $In_{x2}Zn_{y2}O_{z2}$  또는  $InO_{x1}$ 을 주성분으로서 포함하는 영역의 도전성은  $GaO_{x3}$  등을 주성분으로서 포함하는 영역의 도전성보다 높다. 바꿔 말하면,  $In_{x2}Zn_{y2}O_{z2}$  또는  $InO_{x1}$ 을 주성분으로서 포함하는 영역을 캐리어가 흐를 때, 산화물 반도체의 도전성이 발현된다. 따라서  $In_{x2}Zn_{y2}O_{z2}$  또는  $InO_{x1}$ 을 주성분으로서 포함하는 영역이 산화물 반도체에서 클라우드상으로 분포되는 경우, 높은 전계 효과 이동도( $\mu$ )를 실현할 수 있다.

[0073] 한편,  $GaO_{x3}$  등을 주성분으로서 포함하는 영역의 절연성은  $In_{x2}Zn_{y2}O_{z2}$  또는  $InO_{x1}$ 을 주성분으로서 포함하는 영역의 절연성보다 우수하다. 바꿔 말하면,  $GaO_{x3}$  등을 주성분으로서 포함하는 영역이 산화물 반도체에 분포되면, 누설 전류를 억제할 수 있고 양호한 스위칭 동작을 실현할 수 있다.

[0074] 따라서 CAC-OS를 반도체 소자에 사용한 경우,  $GaO_{x3}$  등에서 유래하는 절연성과  $In_{x2}Zn_{y2}O_{z2}$  또는  $InO_{x1}$ 에서 유래하는 도전성이 서로를 보완함으로써, 높은 온 상태 전류( $I_{on}$ ) 및 높은 전계 효과 이동도( $\mu$ )를 실현할 수 있다.

[0075] CAC-OS를 사용한 반도체 소자는 신뢰성이 높다. 따라서 CAC-OS는 다양한 반도체 장치의 재료로서 적합하게 사용된다.

[0076] 화상 데이터에 보정 데이터를 부가하는 화소(10)의 동작예에 대하여 도 2의 (A) 및 (B)에 나타낸 타이밍 차트를 참조하여 설명한다. 또한 아래의 설명에서, "H"는 고전위를 나타내고, "L"은 저전위를 나타내고, "Vp"는 보정 데이터를 나타내고, "Vs"는 화상 데이터를 나타내고, "Vref"는 특정 전위를 나타낸다. "Vref"로서 예를 들어 0V, GND 전위, 또는 특정의 기준 전위를 사용할 수 있다. 또한 "Vp"는 임의의 제 1 데이터를, "Vs"는 임의의 제 2 데이터를 나타낼 수도 있다.

[0077] 먼저, 보정 데이터 "Vp"를 노드(NM)에 기록하는 동작에 대하여 도 2의 (A)를 참조하여 설명한다. 또한 전위의 분배, 전위의 결합, 또는 전위의 손실에서, 회로 구성 또는 동작 타이밍 등에 기인하는 자세한 변화는 고려하지 않는다. 용량 결합에 기인한 전위의 변화는 전위가 공급되는 측에 대한 전위를 공급하는 측의 용량비에 의존하지만, 명료화를 위하여 노드(NM)의 용량값은 충분히 작은 것으로 가정한다.

[0078] 시각 T1에서, 배선(121)의 전위를 "H"로 하고, 배선(122)의 전위를 "L"로 하고, 배선(123)의 전위를 "Vp"로 함으로써, 트랜지스터(102)가 온이 되고, 용량 소자(104)의 한쪽 전극의 전위는 "Vref"가 된다. 이 동작은 이후의 보정 동작(용량 결합 동작)을 하기 위한 리셋 동작이다.

[0079] 또한 트랜지스터(103)는 온이 되고, 배선(123)의 전위(보정 데이터 "Vp")가 노드(NM)에 기록된다.

[0080] 시각 T2에서, 배선(121)의 전위를 "L"로 하고, 배선(122)의 전위를 "L"로 하고, 배선(123)의 전위를 "L"로 함으

로써, 트랜지스터(102 및 103)는 오프가 되고, 노드(NM)에 보정 데이터 "Vp"가 유지된다. 또한 "Vp-Vref"가 용량 소자(104)에 유지된다.

[0081] 여기까지 보정 데이터 "Vp"의 기록 동작에 대하여 설명하였다. 또한 보정을 수행하지 않는 경우에는, 상술한 동작에서 보정 데이터 "Vp"로서 "Vref"와 같은 전위를 공급한다.

[0082] 다음으로, 화상 데이터 "Vs"의 보정 동작 및 회로 블록(110)에서의 표시 소자의 표시 동작에 대하여 도 2의 (B)를 참조하여 설명한다.

[0083] 도 2의 (A) 및 (B)의 동작은 1수평 기간에서 순차적으로 수행할 수 있다. 또는 도 2의 (A)의 동작은  $k$ 번째 프레임( $k$ 는 자연수임)에서, 도 2의 (B)의 동작은  $k+1$ 번째 프레임에서 수행하여도 좋다. 또는 도 2의 (A)의 동작 후에, 도 2의 (B)의 동작을 복수 회 수행하여도 좋다.

[0084] 시각 T11에서, 배선(121)의 전위를 "L"로 하고, 배선(122)의 전위를 "H"로 하고, 배선(123)의 전위를 "Vs"로 함으로써, 트랜지스터(101)가 온이 되고, 용량 소자(104)의 용량 결합에 의하여 배선(123)의 전위 "Vs"가 노드(NM)의 전위에 부가된다. 이때, 노드(NM)의 전위는 "Vp-Vref+Vs"이다. "Vref"가 0일 때, 노드(NM)의 전위는 "Vp+Vs"가 된다.

[0085] 시각 T12에서, 배선(121)의 전위를 "L"로 하고, 배선(122)의 전위를 "L"로 하고, 배선(123)의 전위를 "L"로 함으로써, 트랜지스터(103)는 오프가 되고, 노드(NM)의 전위는 "Vp+Vs"로 유지된다.

[0086] 그 후, 회로 블록(110)에 포함되는 표시 소자는 노드(NM)의 전위에 대응하는 표시 동작을 수행한다. 또한 회로 블록의 구조에 따라서는, 시각 T1 또는 시각 T11에 표시 동작을 시작하는 경우가 있다.

[0087] 화상 데이터를 보정하는 동작에 대하여 도 3의 (A)를 참조하여 설명한다.

[0088] 도 3의 (A)에 원쪽으로부터 수평 수직 방향의 4개의 화소(P1 내지 P4)의 입력 화상 데이터(Vs1, Vs2, 및 Vs3), 입력 보정 데이터(+Vp1, Vp0, 및 -Vp1), 및 보정 후의 생성 화상 데이터를 나타내었다. 또한 아래의 설명에서, 표시 소자는 화상 데이터의 전위가 비교적 높을 때 휘도가 높아지고, 화상 데이터의 전위가 비교적 낮을 때 휘도가 낮아지도록 표시를 수행할 수 있다.

[0089] 예를 들어 화소(P1)에서, 화상 데이터 "Vs1"을 양의 보정 데이터 "+Vp1"과 조합하면 화상 데이터는 "Vs1+Vp1"이 되고, 휘도가 높아진다. 화소(P2 및 P3)에서, 화상 데이터 Vs2를 실질적으로 보정을 야기하지 않는 보정 데이터 "Vp0"과 조합하면 화상 데이터는 "Vs2+Vp0=Vs2"가 되고, 휘도는 변화하지 않는다. 화소(P4)에서, 화상 데이터 "Vs3"을 음의 보정 데이터 "-Vp1"과 조합하면 화상 데이터는 "Vs1-Vp1"이 되고, 휘도가 낮아진다.

[0090] 화상 데이터와 보정 데이터의 이와 같은 조합에 의하여 예를 들어 업컨버전, HDR 표시, 표시 장치 고유의 표시 불균일의 보정, 또는 화소에 포함되는 트랜지스터의 문턱 전압의 보정이 가능하게 된다.

[0091] 업컨버전 동작에서는, 예를 들어, 4개의 화소 모두에 같은 화상 데이터를 공급한다. 보정이 수행되면, 화소들은 상이한 화상을 표시할 수 있게 된다. 예를 들어 8K4K에 대응하는 화소를 포함하는 표시 장치에서의 특정의 4개의 화소에, 4K2K에 대응하는 화소를 포함하는 표시 장치에서의 특정의 하나의 화소용 데이터를 입력함으로써, 해상도가 높아진 표시를 수행할 수 있다.

[0092] 넓은 의미에서는 화상 데이터의 보정이지만, 상이한 화상들을 서로 겹쳐 표시할 수 있다. 도 3의 (B)는 표시부 전체의 화상, 즉, 원쪽으로부터 화상 데이터 "Vs"로 구성된 제 1 화상, 보정 데이터 "Vp"로 구성된 제 2 화상, 및 제 1 화상과 제 2 화상이 합성된 화상을 나타낸 것이다.

[0093] 화상 데이터와 보정 데이터의 이와 같은 조합에 의하여, 상이한 화상들의 합성 표시 또는 표시부 전체의 휘도 향상 등이 가능하게 된다. 상기 조합은 예를 들어 문자의 삽입 또는 증강 현실(AR) 표시 등에 적용할 수 있다.

[0094] 도 4의 (A) 내지 (C)는 각각 회로 블록(110)에 적용될 수 있는, 표시 소자로서 EL 소자를 포함한 구조의 예를 나타낸 것이다.

[0095] 도 4의 (A)에 나타낸 구조는 트랜지스터(111), 용량 소자(113), 및 EL 소자(114)를 가진다. 트랜지스터(111)의 소스 및 드레인 중 한쪽은 EL 소자(114)의 한쪽 전극에 전기적으로 접속된다. EL 소자(114)의 한쪽 전극은 용량 소자(113)의 한쪽 전극에 전기적으로 접속된다. 용량 소자(113)의 다른 쪽 전극은 트랜지스터(111)의 게이트에 전기적으로 접속된다. 트랜지스터(111)의 게이트는 노드(NM)에 전기적으로 접속된다.

[0096] 트랜지스터(111)의 소스 및 드레인 중 다른 쪽은 배선(128)에 전기적으로 접속된다. EL 소자(114)의 다른 쪽

전극은 배선(129)에 전기적으로 접속된다. 배선(128 및 129)은 전원을 공급하는 기능을 가진다. 예를 들어 배선(128)은 고전위 전원을 공급할 수 있다. 배선(129)은 저전위 전원을 공급할 수 있다.

[0097] 여기서, 도 1에 나타낸 "Vref"를 공급하기 위한 트랜지스터(103)의 소스 및 드레인 중 다른 쪽은 배선(128)에 전기적으로 접속될 수 있다. "Vref"는 OV, GND, 또는 저전위인 것이 바람직하기 때문에, 배선(128)은 적어도 이들 전위 중 어느 것을 공급하는 기능도 가진다. 배선(128)에는, 노드(NM)에 데이터를 기록할 때 "Vref"를 공급하고, EL 소자(114)를 발광시킬 때 고전위 전원을 공급한다.

[0098] 도 4의 (A)에 나타낸 구조에서는, 노드(NM)의 전위가 트랜지스터(111)의 문턱 전압 이상이 될 때 EL 소자(114)를 전류가 흐른다. 그러므로, 도 2의 (A)의 타이밍 차트에 나타낸 시각 T1에서 EL 소자(114)가 발광하기 시작하는 경우가 있어 용도가 한정될 수 있다.

[0099] 도 4의 (B)는 도 4의 (A)에 나타낸 구조에 트랜지스터(112)를 추가한 구조를 나타낸 것이다. 트랜지스터(112)의 소스 및 드레인 중 한쪽은 트랜지스터(111)의 소스 및 드레인 중 한쪽에 전기적으로 접속된다. 트랜지스터(112)의 소스 및 드레인 중 다른 쪽은 EL 소자(114)에 전기적으로 접속된다. 트랜지스터(112)의 게이트는 배선(126)에 전기적으로 접속된다. 배선(126)은 트랜지스터(112)의 도통을 제어하는 신호선의 기능을 가질 수 있다.

[0100] 이 구조에서는, 트랜지스터(112)가 온이 되고 노드(NM)의 전위가 트랜지스터(111)의 문턱 전압 이상이 될 때 EL 소자(114)를 전류가 흐른다. 그러므로 EL 소자(114)는 도 2의 (B)의 타이밍 차트의 시각 T12 이후에 발광을 시작할 수 있기 때문에 보정을 수반하는 동작에 적합하다.

[0101] 도 4의 (C)는 도 4의 (B)에 나타낸 구조에 트랜지스터(115)를 추가한 구조를 나타낸 것이다. 트랜지스터(115)의 소스 및 드레인 중 한쪽은 트랜지스터(111)의 소스 및 드레인 중 한쪽에 전기적으로 접속된다. 트랜지스터(115)의 소스 및 드레인 중 다른 쪽은 배선(130)에 전기적으로 접속된다. 트랜지스터(115)의 게이트는 배선(131)에 전기적으로 접속된다. 배선(131)은 트랜지스터(115)의 도통을 제어하는 신호선의 기능을 가질 수 있다. 또한 트랜지스터(115)의 게이트는 배선(122)에 전기적으로 접속되어도 좋다.

[0102] 배선(130)은 기준 전위 등 특정 전위의 공급원에 전기적으로 접속될 수 있다. 배선(130)으로부터 트랜지스터(111)의 소스 및 드레인 중 한쪽에 특정 전위를 공급함으로써 화상 데이터의 기록이 안정될 수 있다.

[0103] 또한 배선(130)은 회로(120)에 접속될 수 있고 모니터선으로서도 기능할 수 있다. 회로(120)는 상술한 특정 전위 전원을 공급하는 기능, 트랜지스터(111)의 전기 특성을 얻는 기능, 및 보정 데이터를 생성하는 기능 중 하나 이상을 가질 수 있다.

[0104] 배선(130)이 모니터선으로서 기능하는 경우에는, 회로(120)가 보정 데이터 "Vp"로서 트랜지스터(111)의 문턱 전압을 보정하는 전위를 생성할 수 있다.

[0105] 도 5의 (A) 내지 (C)는 각각 회로 블록(110)에 적용될 수 있는, 표시 소자로서 액정 소자를 포함한 구조의 예를 나타낸 것이다.

[0106] 도 5의 (A)에 나타낸 구조는 용량 소자(116) 및 액정 소자(117)를 가진다. 액정 소자(117)의 한쪽 전극은 용량 소자(116)의 한쪽 전극에 전기적으로 접속된다. 용량 소자(116)의 한쪽 전극은 노드(NM)에 전기적으로 접속된다.

[0107] 용량 소자(116)의 다른 쪽 전극은 배선(132)에 전기적으로 접속된다. 액정 소자(117)의 다른 쪽 전극은 배선(133)에 전기적으로 접속된다. 배선(132 및 133)은 전원을 공급하는 기능을 가진다. 예를 들어 배선(132 및 133)은 GND 또는 OV 등의 기준 전위 또는 임의의 전위를 공급할 수 있다.

[0108] 도 1에 나타낸 "Vref"를 공급하기 위한 트랜지스터(103)의 소스 및 드레인 중 다른 쪽은 배선(132)에 전기적으로 접속될 수 있다.

[0109] 이 구조에서는, 노드(NM)의 전위가 액정 소자(117)의 동작 문턱 이상이 될 때, 액정 소자(117)의 동작이 시작한다. 그러므로, 도 2의 (A)의 타이밍 차트의 시각 T1에서 표시 동작이 시작되어 용도가 한정되는 경우가 있다. 그러나, 투과형 액정 표시 장치에서는, 예를 들어 이 구조와 도 2의 (B)의 시각 T12까지 백라이트를 오프시키는 동작을 조합하면, 불필요한 표시 동작을 눈에 덜 띄게 할 수 있다.

[0110] 도 5의 (B)는 도 5의 (A)에 나타낸 구조에 트랜지스터(118)를 추가한 구조를 나타낸 것이다. 트랜지스터(118)의 소스 및 드레인 중 한쪽은 용량 소자(116)의 한쪽 전극에 전기적으로 접속된다. 트랜지스터(118)의 소스 및

드레인 중 다른 쪽은 노드(NM)에 전기적으로 접속된다. 트랜지스터(118)의 게이트는 배선(126)에 전기적으로 접속된다. 배선(126)은 트랜지스터(118)의 도통을 제어하는 신호선의 기능을 가질 수 있다.

[0111] 이 구조에서는, 트랜지스터(118)가 온이 될 때, 노드(NM)의 전위가 액정 소자(117)에 인가된다. 그러므로 액정 소자의 동작은 도 2의 (B)의 타이밍 차트에 나타낸 시각 T12 이후에 시작할 수 있기 때문에 보정을 수반하는 동작에 적합하다.

[0112] 트랜지스터(118)가 오프 상태에 있는 동안에는, 용량 소자(116) 및 액정 소자(117)에 공급된 전위는 계속 유지된다. 화상 데이터가 재기록되기 전에, 용량 소자(116) 및 액정 소자(117)에 공급된 전위는 리셋되는 것이 바람직하다. 이 리셋을 하기 위하여, 예를 들어, 배선(123)에 리셋 전위를 공급하여 트랜지스터(103 및 118)를 동시에 온으로 한다.

[0113] 도 5의 (C)는 도 5의 (B)에 나타낸 구조에 트랜지스터(119)를 추가한 구조를 나타낸 것이다. 트랜지스터(119)의 소스 및 드레인 중 한쪽은 액정 소자(117)의 한쪽 전극에 전기적으로 접속된다. 트랜지스터(119)의 소스 및 드레인 중 다른 쪽은 배선(130)에 전기적으로 접속된다. 트랜지스터(119)의 게이트는 배선(131)에 전기적으로 접속된다. 배선(131)은 트랜지스터(119)의 도통을 제어하는 신호선의 기능을 가질 수 있다. 또한 트랜지스터(119)의 게이트는 배선(122)에 전기적으로 접속되어도 좋다.

[0114] 배선(130)에 전기적으로 접속된 회로(120)는 도 4의 (C)를 사용하여 상술한 바와 같고, 또한 용량 소자(116) 및 액정 소자(117)에 공급된 전위를 리셋하는 기능을 가져도 좋다.

[0115] "Vref"를 전원선으로부터 공급하는 예를 도 4의 (A) 내지 (C) 및 도 5의 (A) 내지 (C)에 나타내었지만, "Vref"를 주사선으로부터 공급할 수 있다. 예를 들어 도 6의 (A)에 나타낸 바와 같이, 배선(122)으로부터 "Vref"를 공급하여도 좋다. 도 6의 (A)에 나타낸 바와 같이, 보정 데이터가 기록될 때(트랜지스터(103)가 온일 때) 배선(122)에 "L"에 대응하는 전위가 공급되기 때문에 이 전위를 "Vref"로서 사용할 수 있다.

[0116] 도 6의 (B) 및 (C)에 나타낸 바와 같이, 트랜지스터(101, 102, 및 103)는 각각 백 게이트를 가져도 좋다. 도 6의 (B)는 백 게이트가 각 프런트 게이트에 전기적으로 접속된 구조를 나타낸 것이고, 온 상태 전류를 증가시키는 효과를 가진다. 도 6의 (C)는 백 게이트가 정전위를 공급할 수 있는 배선(134)에 전기적으로 접속되어, 트랜지스터의 문턱 전압을 제어할 수 있는 구조를 나타낸 것이다. 또한 도 4의 (A) 내지 (C) 및 도 5의 (A) 내지 (C)의 회로 블록(110)에 포함되는 트랜지스터에도 백 게이트가 제공되어도 좋다.

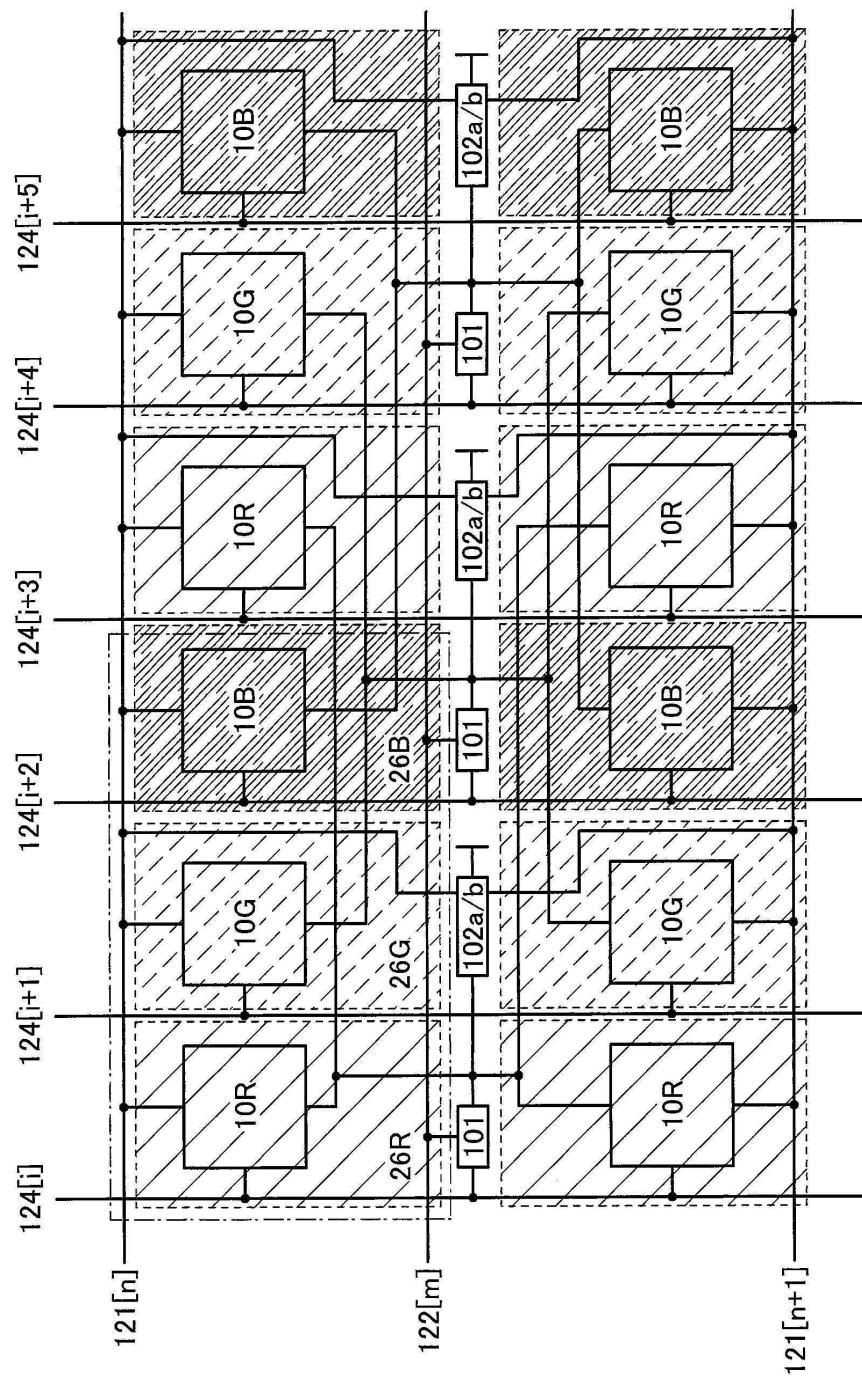

[0117] 도 7은 화소(10)의 기본 구조를 체용한 화소(11)를 포함한 화소 어레이의 일부(4개의 화소에 대응함)를 나타낸 것이다. 화소(11)는 트랜지스터(103), 용량 소자(104), 및 회로 블록(110)을 포함한다. 또한 부호에 붙여진 꺾쇠괄호에서,  $n$  및  $m$ 은 각각 특정의 행을 나타내고,  $i$ 는 특정의 열( $n, m$ , 및  $i$ 는 자연수임)을 나타낸다.

[0118] 화소(11)는 매트릭스로, 즉  $n$ 행  $i$ 열,  $n$ 행  $(i+x)$ 열( $x$ 는 자연수임),  $(n+1)$ 행  $i$ 열, 및  $(n+1)$ 행  $(i+x)$ 열에 배치될 수 있다. 또한 도 7은  $x$ 이 1인 경우의 배치를 나타낸 것이다.

[0119] 화소 어레이에는 4개의 화소(11)에 전기적으로 접속된 트랜지스터(101, 102a, 및 102b)가 제공된다. 트랜지스터(102a 및 102b)는 화소(10)에 포함되는 트랜지스터(102)의 기능을 가진다.

[0120] 트랜지스터(101)는 각 화소(11)의 구성 요소이고, 즉 4개의 화소가 공유한다. 트랜지스터(102a)는 화소(11[n,  $i$ ] 및 11[n,  $i+1$ ])의 구성 요소이고, 즉 2개의 화소가 공유한다. 트랜지스터(102b)는 화소(11[n+1,  $i$ ] 및 11[n+1,  $i+1$ ])의 구성 요소이고, 즉 2개의 화소가 공유한다. 또한 트랜지스터(101, 102a, 및 102b)는 화소 영역 중 어느 것에 분산되어도 좋다.

[0121] 각 화소(11)에서, 트랜지스터(103)의 소스 및 드레인 중 한쪽은 용량 소자(104)의 한쪽 전극에 전기적으로 접속된다. 용량 소자(104)의 한쪽 전극은 회로 블록(110)에 전기적으로 접속된다. 용량 소자(104)의 다른 쪽 전극은 트랜지스터(101)의 소스 및 드레인 중 한쪽에 전기적으로 접속된다. 트랜지스터(101)의 소스 및 드레인 중 한쪽은 트랜지스터(102a)의 소스 및 드레인 중 한쪽에 전기적으로 접속된다. 트랜지스터(101)의 소스 및 드레인 중 한쪽은 트랜지스터(102b)의 소스 및 드레인 중 한쪽에 전기적으로 접속된다.

[0122] 이 화소 어레이에서는, 일부의 같은 동작에 대해서는, 화소(10)가 단순히 매트릭스로 배치된 구조보다 요구되는 배선수 및 트랜지스터수를 적게 할 수 있다.

[0123] 표시 장치와 화상 데이터의 해상도가 서로 상이한 경우에도, 화상 데이터 및 보정 데이터의 입력 패스를 변경함으로써, 업컨버전도 다운컨버전도 하지 않고, 적절한 표시를 수행할 수 있다.

[0124] 각 화소(11)에 상이한 데이터를 기록하는 동작에 대하여 도 8의 (A1) 및 (A2)의 타이밍 차트를 참조하여 설명한다. 이 동작은 예를 들어 8K4K에 대응하는 화소를 포함하는 표시 장치에 고해상도용 화상 데이터(8K4K 데이터)를 입력하는 경우에 대응한다. 하나의 화소(11)의 동작에 대하여 설명하지만, 다른 화소(11)에도 같은 동작이 적용된다.

[0125] 아래의 설명에서, "H"는 고전위를 나타내고 "L"은 저전위를 나타내고, "M"은 고전위와 저전위 사이의 특정 전위를 나타낸다. 또한 "M"은 OV 또는 GND 등의 기준 전위일 수 있지만, 다른 전위이어도 좋다. 또한 "VsH"는 고해상도용 화상 데이터를 나타내고, "Vp1"은 고해상도용 보정 데이터를 나타낸다. 바꿔 말하면, "Vp1"은 임의의 제 1 데이터를 나타낼 수도 있고, "VsH"는 임의의 제 2 데이터를 나타낼 수도 있다.

[0126] 먼저, 화상 데이터 "VsH"를 노드(NM)에 기록하는 동작에 대하여 도 8의 (A1)를 참조하여 설명한다. 또한 전위의 분배, 전위의 결합, 또는 전위의 순서에서, 회로 구성 또는 동작 타이밍 등에 기인하는 자세한 변화는 고려하지 않는다.

[0127] 시각 T1에서, 배선(121)의 전위를 "H"로 하고, 배선(122)의 전위를 "L"로 하고, 배선(123)의 전위를 "VsH"로 함으로써, 트랜지스터(102)는 온이 되고, 용량 소자(104)의 다른 쪽 전극의 전위는 "Vref"가 된다. 이 동작은 이후의 보정 동작(용량 결합 동작)을 하기 위한 리셋 동작이다.

[0128] 또한 트랜지스터(103)는 온이 되고, 배선(123)의 전위(화상 데이터 "VsH")가 노드(NM)에 기록된다.

[0129] 시각 T2에서, 배선(121)의 전위를 "L"로 하고, 배선(122)의 전위를 "L"로 하고, 배선(123)의 전위를 "M"으로 함으로써, 트랜지스터(102) 및 트랜지스터(103)는 오프가 되고, 노드(NM)에 화상 데이터 "VsH"가 유지된다. 또한 "VsH-Vref"가 용량 소자(104)에 유지된다.

[0130] 여기까지 화상 데이터 "VsH"의 기록 동작에 대하여 설명하였다. 다음으로, 화상 데이터 "VsH"의 보정 동작 및 회로 블록(110)에서의 표시 소자의 표시 동작에 대하여 도 8의 (A2)를 참조하여 설명한다.

[0131] 도 8의 (A1) 및 (A2)의 동작은 1수평 기간에서 순차적으로 수행할 수 있다. 또는 도 8의 (A1)의 동작은  $k$ 번째 프레임( $k$ 는 자연수임)에서, 도 8의 (A2)의 동작은  $k+1$ 번째 프레임에서 수행하여도 좋다. 또는 도 8의 (A1)의 동작 후에, 도 8의 (A2)의 동작을 복수 회 수행하여도 좋다.

[0132] 시각 T11에서, 배선(121)의 전위를 "L"로 하고, 배선(122)의 전위를 "H"로 하고, 배선(123)의 전위를 "Vp1"로 함으로써, 트랜지스터(101)가 온이 되고, 용량 소자(104)의 용량 결합에 의하여 배선(123)의 전위 "Vp1"이 노드(NM)의 전위에 부가된다. 이때, 노드(NM)의 전위는 "VsH-Vref+Vp1"이다. "Vref"가 0일 때, 노드(NM)의 전위는 "VsH+Vp1"이 된다. 또한 보정을 수행하지 않는 경우에는, 상술한 동작에서 보정 데이터 "Vp1"로서 "Vref"와 같은 전위를 공급한다.

[0133] 시각 T12에서, 배선(121)의 전위를 "L"로 하고, 배선(122)의 전위를 "L"로 하고, 배선(123)의 전위를 "M"으로 함으로써, 트랜지스터(101)는 오프가 되고, 노드(NM)의 전위는 "VsH+Vp1"로 유지된다.

[0134] 그 후, 회로 블록(110)에 포함되는 표시 소자는 노드(NM)의 전위에 대응하는 표시 동작을 수행한다. 또한 회로 블록의 구조에 따라, 시각 T1 또는 시각 T11에 표시 동작을 시작하는 경우가 있다.

[0135] 선택된 화소에서 이와 같이 보정을 수행하여, HDR 표시 등을 수행할 수 있다. 또한 4개의 화소 각각에 대한 보정 데이터 "Vp1"의 값은 같지만, 시각적 콘트라스트 효과를 얻는 데 충분히 효과적이다. 보정을 수행하지 않는 경우에는, 시각 T11 동안 배선(123)의 전위를 "M"으로 유지한다. 또는 배선(122)의 전위를 "L"로 하여 트랜지스터(101)가 온이 되는 것을 방지한다.

[0136] 다음으로, 4개의 화소(11)에 대하여 같은 데이터를 기록하는 동작에 대하여 도 8의 (B1) 및 (B2)의 타이밍 차트를 참조하여 설명한다. 이 동작은 예를 들어 8K4K에 대응하는 화소를 포함하는 표시 장치에 저해상도용 화상 데이터(4K2K 데이터)를 입력하는 경우에 대응한다.

[0137] 먼저, 보정 데이터 "Vp2"를 노드(NM)에 기록하는 동작에 대하여 도 8의 (B1)를 참조하여 설명한다. 아래의 설명에서는, "VsL"은 저해상도용 화상 데이터를 나타내고, "Vp2"는 저해상도용 보정 데이터를 나타낸다. 또한 "Vp2"는 임의의 제 1 데이터를 나타낼 수도 있고, "VsL"은 임의의 제 2 데이터를 나타낼 수도 있다.

[0138] 시각 T1에서, 배선(121)의 전위를 "H"로 하고, 배선(122)의 전위를 "L"로 하고, 배선(123)의 전위를 "Vp2"로 함으로써, 트랜지스터(102)는 온이 되고, 용량 소자(104)의 다른 쪽 전극의 전위는 "Vref"가 된다. 이 동작은 이

후의 보정 동작(용량 결합 동작)을 하기 위한 리셋 동작이다.

[0139] 또한 트랜지스터(103)는 온이 되고, 배선(123)의 전위(보정 데이터 "Vp2")가 노드(NM)에 기록된다.

[0140] 시각 T2에서, 배선(121)의 전위를 "L"로 하고, 배선(122)의 전위를 "L"로 하고, 배선(123)의 전위를 "M"으로 함으로써, 트랜지스터(102) 및 트랜지스터(103)는 오프가 되고, 노드(NM)에 보정 데이터 "Vp2"가 유지된다. 또한 "Vp2-Vref"가 용량 소자(104)에 유지된다.

[0141] 여기까지 보정 데이터 "Vp2"의 기록 동작에 대하여 설명하였다. 또한 보정을 수행하지 않는 경우에는, 상술한 동작에서 보정 데이터 "Vp2"로서 "Vref"와 같은 전위를 공급한다.

[0142] 다음으로, 화상 데이터 "VsL"의 보정 동작 및 회로 블록(110)에서의 표시 소자의 표시 동작에 대하여 도 8의 (B2)를 참조하여 설명한다.

[0143] 도 8의 (B1) 및 (B2)의 동작은 1수평 기간에서 순차적으로 수행할 수 있다. 또는 도 8의 (B1)의 동작은  $k$ 번째 프레임에서, 도 8의 (B2)의 동작은  $k+1$ 번째 프레임에서 수행하여도 좋다. 또는 도 8의 (B1)의 동작 후에, 도 8의 (B2)의 동작을 복수 회 수행하여도 좋다.

[0144] 시각 T11에서, 배선(121)의 전위를 "L"로 하고, 배선(122)의 전위를 "H"로 하고, 배선(123)의 전위를 "VsL"로 함으로써, 트랜지스터(101)는 온이 되고, 용량 소자(104)의 용량 결합에 의하여 노드(NM)의 전위에 배선(123)의 전위 "VsL"이 부가된다. 이때, 노드(NM)의 전위는 "Vp2-Vref+VsL"이다. "Vref"가 0일 때, 노드(NM)의 전위는 "Vp2+VsL"이 된다.

[0145] 시각 T12에서, 배선(121)의 전위를 "L"로 하고, 배선(122)의 전위를 "L"로 하고, 배선(123)의 전위를 "M"으로 함으로써, 트랜지스터(101)는 오프가 되고, 노드(NM)의 전위는 "Vp2+VsL"로 유지된다.

[0146] 그 후, 회로 블록(110)에 포함되는 표시 소자는 노드(NM)의 전위에 대응하는 표시 동작을 수행한다. 또한 회로 블록의 구조에 따라, 시각 T11에 표시 동작을 시작하는 경우가 있다.

[0147] 각 화소(11)에 보정 데이터 "Vp2"로서 다른 값을 입력할 수 있다. 그래서, 같은 화상 데이터 "VsL"을 사용하여도 각 화소(11)는 상이한 화상을 표시할 수 있다. 즉 업컨버전을 수행할 수 있다. 또한 보정을 수행하지 않는 경우, 4개의 화소 각각에 의하여 같은 화상이 표시된다.

[0148] 상술한 동작에 의하여, 원래의 화상 데이터를 업컨버전하지 않고 표시 장치에 입력할 수 있어 적절한 표시를 수행할 수 있다. 또는 화상 표시에 적절한 보정을 수행할 수 있다.

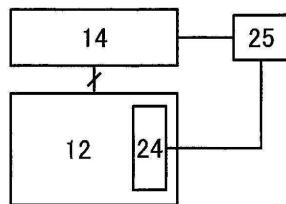

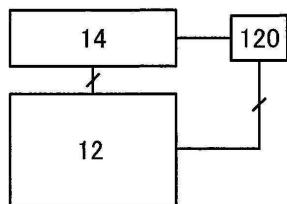

[0149] 도 9의 (A)는 본 발명의 일 형태의 표시 장치를 나타내는 블록도의 예이다. 표시 장치는 화소(11)가 매트릭스로 배치된 화소 어레이(12), 행 드라이버(13), 열 드라이버(14), 회로(15), 및 선택 회로(16)를 포함한다. 또한 도 9의 (A)에서는, 트랜지스터(102a 및 102b)를 하나의 블록으로서 나타내고, 전위 "Vref"를 공급하는 배선에 접속된 부분을 생략하였다.

[0150] 행 드라이버(13)는 예를 들어 시프트 레지스터(20) 및 버퍼 회로(21)를 조합한 구조를 가질 수 있다. 버퍼 회로(21)의 도통을 제어함으로써, 배선(121) 또는 배선(122)에 데이터를 출력할 수 있다.

[0151] 열 드라이버(14)는 예를 들어 시프트 레지스터(22) 및 버퍼 회로(23)를 조합한 구조를 가질 수 있다. 버퍼 회로(23)의 도통을 제어함으로써, 배선(123)에 데이터를 출력할 수 있다.

[0152] 회로(15)는 보정 데이터를 생성하는 기능을 가진다. 회로(15)는 보정 데이터를 생성하기 위한 외부 기기라고 할 수도 있다.

[0153] 행 드라이버(13)는 트랜지스터(101, 102a, 및 102b)의 도통을 제어할 수 있다. 열 드라이버(14)는 배선(123)에 보정 데이터 또는 화상 데이터를 공급할 수 있다.

[0154] 저해상도용 화상 데이터 "VsH"(예를 들어 8K4K 데이터) 또는 저해상도용 화상 데이터 "VsL"이 회로(15)에 입력된다. 화상 데이터 "VsH"가 입력되면, 보정 데이터 "Vp1"이 생성된다. 화상 데이터 "VsL"이 입력되면, 보정 데이터 "Vp2"가 생성된다.

[0155] 선택 회로(16)는 회로(15)에서 생성된 보정 데이터 "Vp1" 및 "Vp2"뿐만 아니라 외부에서 생성된 보정 데이터 "Vp1" 및 "Vp2" 또는 화상 데이터 "VsH" 및 "VsL"을 열 드라이버(14)에 출력할 수 있다.

[0156] 도 9의 (A)에 나타낸 구조에서는, 예를 들어 보정하지 않고 저해상도 표시 동작을 함으로써 각 드라이버의 출력

단(output stage)을 절반으로 줄일 수 있어 소비전력을 저감할 수 있다.

[0157] 또한 회로(15)는 신경망을 포함하여도 좋다. 예를 들어, 방대한 화상을 교사 데이터로서 학습한 심층 신경망을 사용함으로써, 정확도가 높은 보정 데이터를 생성할 수 있다.

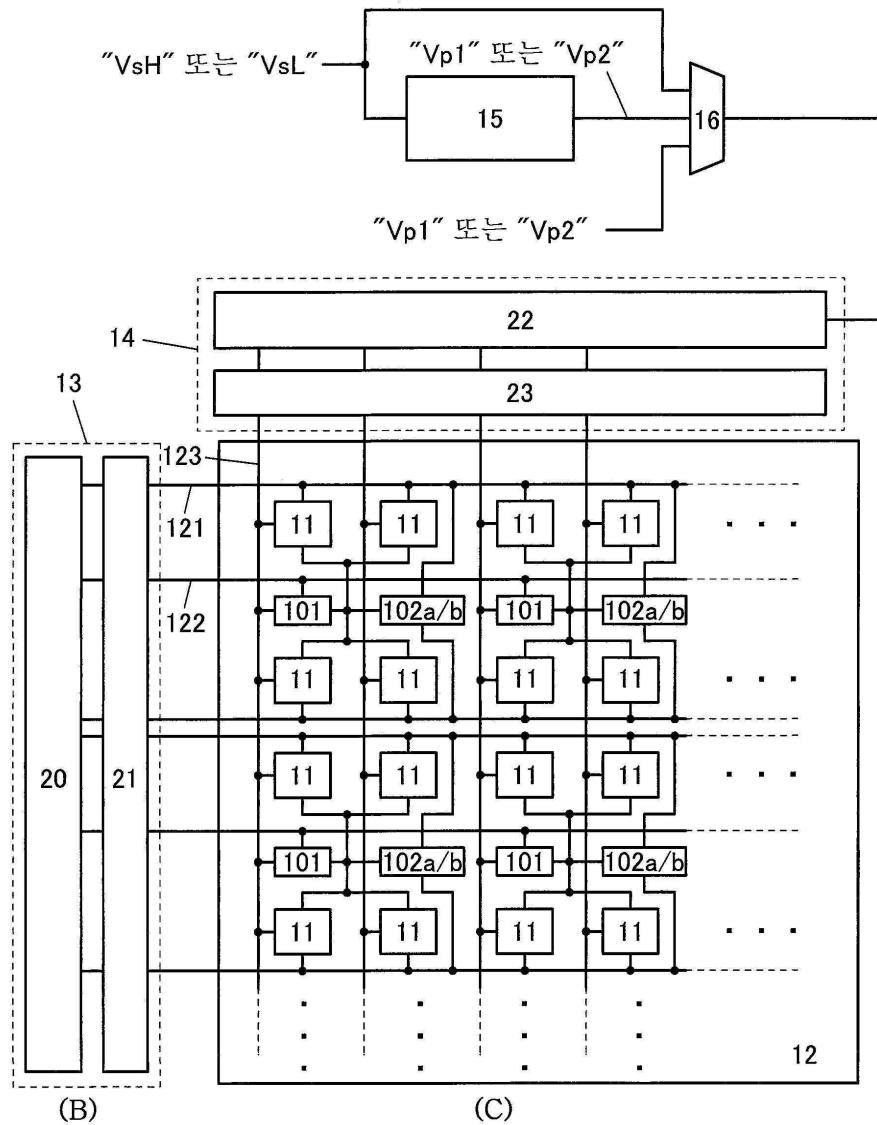

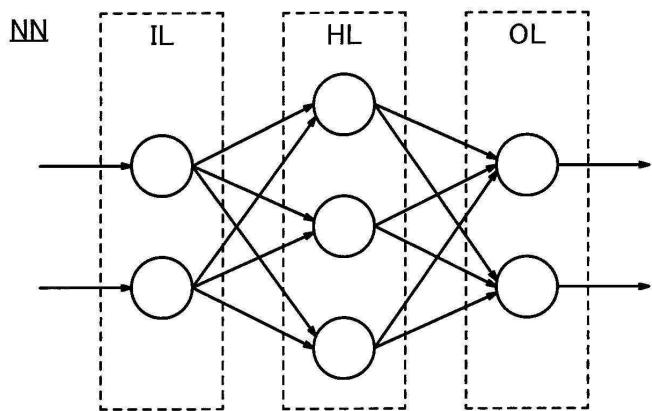

[0158] 도 10의 (A)에 나타낸 바와 같이, 뉴럴 네트워크(NN)는 입력층(IL), 출력층(OL), 및 중간층(은닉층)(HL)으로 형성될 수 있다. 입력층(IL), 출력층(OL), 및 중간층(HL)은 각각 하나 이상의 뉴런(유닛)을 포함한다. 또한 중간층(HL)은 하나의 층 또는 2개 이상의 층으로 구성되어도 좋다. 2개 이상의 중간층(HL)을 포함한 신경망을 DNN(deep neural network)이라고 할 수도 있고, DNN을 사용한 학습을 심층 학습이라고 할 수도 있다.

[0159] 입력층(IL)의 뉴런에는 입력 데이터가 입력되고, 중간층(HL)의 뉴런에는 앞의 층 또는 다음의 층의 뉴런의 출력신호가 입력되고, 출력층(OL)의 뉴런에는 앞의 층의 뉴런의 출력신호가 입력된다. 또한 각 뉴런은 앞의 층 및 다음의 층의 모든 뉴런과 결합되어도 좋고(전(全)결합), 일부 뉴런과 결합되어도 좋다.

[0160] 도 10의 (B)는 뉴런에 의한 연산의 예를 나타낸 것이다. 여기서는, 뉴런 N과, 뉴런 N에 신호를 출력하는 앞의 층의 2개의 뉴런을 나타내었다. 뉴런 N에는 앞의 층의 뉴런의 출력  $x_1$  및 앞의 층의 뉴런의 출력  $x_2$ 가 입력된다. 그 후, 뉴런 N에서, 출력  $x_1$ 과 가중치  $w_1$ 의 곱셈 결과( $x_1w_1$ )와, 출력  $x_2$ 와 가중치  $w_2$ 의 곱셈 결과( $x_2w_2$ )의 총합  $x_1w_1+x_2w_2$ 가 계산된 후, 필요에 따라 바이어스  $b$ 가 가산되어 값  $a=x_1w_1+x_2w_2+b$ 가 얻어진다. 그리고 값  $a$ 는 활성화 함수  $h$ 에 의하여 변환되고, 뉴런 N으로부터 출력 신호  $y=h(a)$ 가 출력된다.

[0161] 이런 식으로, 뉴런에 의한 연산에는 앞의 층의 뉴런의 출력과 가중치의 곱을 합하는 연산, 즉 적화 연산(product-sum operation)이 포함된다(상술한  $x_1w_1+x_2w_2$ ). 이 적화 연산은 프로그램을 사용하여 소프트웨어상에서 수행되어도 좋고 하드웨어를 사용하여 수행되어도 좋다. 적화 연산을 하드웨어에 의하여 수행하는 경우에는, 적화 연산 회로를 사용할 수 있다. 이 적화 연산 회로로서는 디지털 회로 및 아날로그 회로의 어느 쪽이든 사용할 수 있다.

[0162] 적화 연산 회로는 Si 트랜지스터를 사용하여 형성되어도 좋고 OS 트랜지스터를 사용하여 형성되어도 좋다. OS 트랜지스터는 오프 상태 전류가 매우 낮기 때문에, 적화 연산 회로의 아날로그 메모리에 포함되는 트랜지스터로서 사용되는 것이 특히 바람직하다. 또한 적화 연산 회로에는 Si 트랜지스터 및 OS 트랜지스터의 양쪽이 포함되어도 좋다.

[0163] 또한 회로(15)뿐만 아니라 상술한 회로(120)에서도 보정 데이터를 생성할 수 있다(도 9의 (B) 참조). 표시부의 그레이스케일 표시의 휘도를 휘도계에 의하여 판독하여 얻은 데이터, 또는 상기 표시의 사진을 판독하여 얻은 데이터에 기초하여 보정 데이터를 생성하여도 좋다. 표시의 휘도를 검출할 수 있는 센서(24) 및 표시 소자의 열화를 검출하여 보정 데이터를 생성할 수 있는 회로(25)를 제공하여도 좋다(도 9의 (C) 참조).

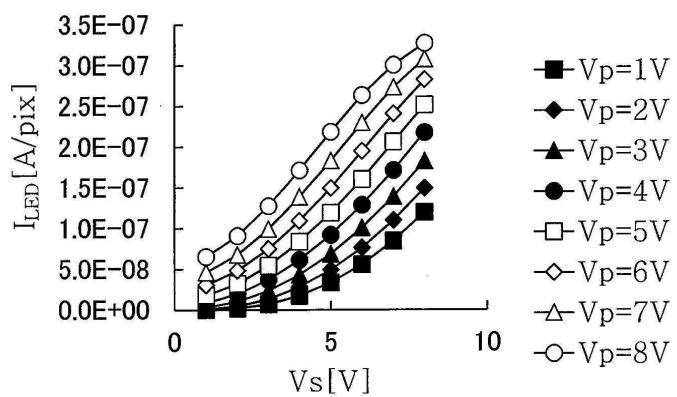

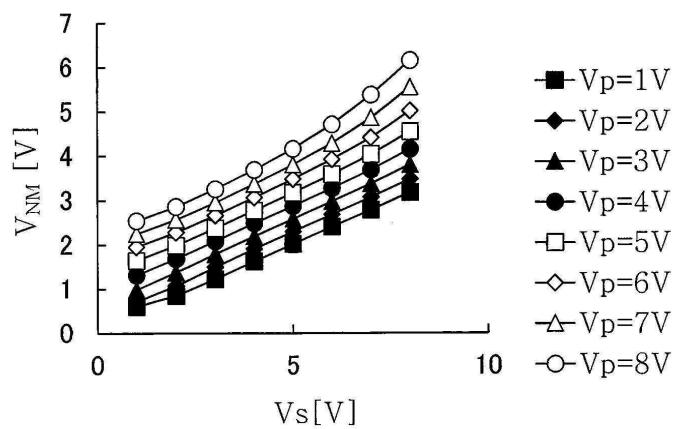

[0164] 다음으로, 도 7에 나타낸 화소 어레이에 도 4의 (A)에 나타낸 회로 블록을 적용한 구조의 시뮬레이션 결과에 대하여 설명한다(도 11 참조). 파라미터는 다음과 같다: 트랜지스터(111)의 크기는  $6\mu\text{m}/6\mu\text{m}$ (L/W)이고, 그 이외의 트랜지스터의 크기는  $4\mu\text{m}/4\mu\text{m}$ (L/W)이고, 용량 소자(104)의 용량은  $150\text{fF}$ 이고, 용량 소자(113)의 용량은  $50\text{fF}$ 이고, EL 소자(114)는 FN 다이오드 모델이고, 배선(128)은 애노드 전위  $+10\text{V}$ 로 하고, "Vref"는  $+1\text{V}$ 로 하고, 배선(129)은 캐소드 전위  $-5\text{V}$ 로 하고, 화상 데이터 및 보정 데이터의 최솟값은  $+1\text{V}$ 로 하고, 최댓값은  $+8\text{V}$ 로 하였다. 또한 회로 시뮬레이션 소프트웨어에는 SPICE를 사용하였다.

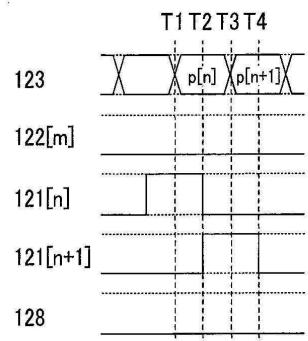

[0165] 도 12의 (A) 내지 (C)는 고해상도 표시(보정 없음)를 검증하기 위한 시뮬레이션 결과를 나타낸 것이다. 도 12의 (A)는 검증에 사용한 타이밍 차트이다. 도 12의 (A)에 나타낸 시각 T1 내지 시각 T2에서 트랜지스터(103)를 온으로 하여 배선(123)으로부터 화상 데이터 "Vs"(s[n])를 기록한다. 또한 시각 T3 내지 시각 T4에서 화상 데이터 "Vs"(s[n+1])를 기록한다. 이때, 배선(128)은 애노드 전위이다.

[0166] 도 12의 (B)는 화상 데이터 "Vs"에 대한 EL 소자(114)를 흐르는 전류( $I_{\text{LED}}$ )의 시뮬레이션 결과를 나타낸 것이다. 하나의 화소의 시뮬레이션 결과를 도 12의 (B)에 나타내었지만, 모든 화소(pix1 내지 pix4)에서 그레이스케일 표시가 확인된다.

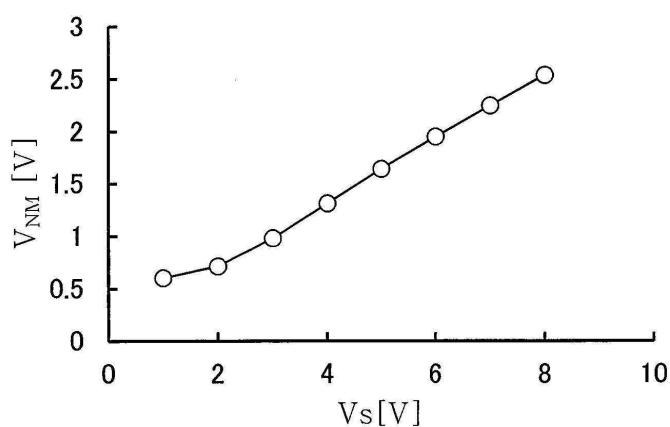

[0167] 도 12의 (C)는 화상 데이터 "Vs"에 대한 노드(NM)의 전위 " $V_{\text{NM}}$ "의 변화의 시뮬레이션 결과를 나타낸 것이다. 모든 화소에서 노드(NM)의 전위 " $V_{\text{NM}}$ "이 화상 데이터 "Vs"에 비례하는 것이 확인된다.

[0168] 따라서, 배선(123)으로부터 공급되는 고해상도용 화상 데이터 "Vs"를 표시할 수 있는 것이 확인된다.

[0169] 도 13의 (A) 내지 (D)는 저해상도 표시(보정 없음)를 검증하기 위한 시뮬레이션 결과를 나타낸 것이다. 도 13의 (A) 및 (B)는 검증에 사용한 타이밍 차트이다. 먼저, 배선(123)의 전위를 최솟값(+1V)으로 하고, 도 13의 (A)에 나타낸 시각 T1 내지 시각 T4에서 모든 화소에 보정 데이터 "Vp"(p)를 기록한다. 이때, 배선(128)을 전위 "Vref"(+1V)로 하기 때문에 용량 소자(104)에 유지된 차분 전위는 0이다. 즉 보정이 수행되지 않는다.

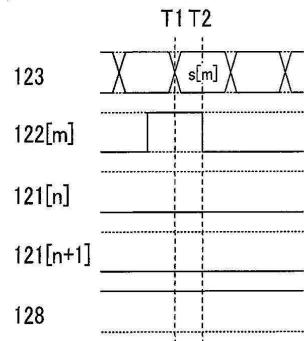

[0170] 그 후, 도 13의 (B)에 나타낸 시각 T1 내지 시각 T2에서 트랜지스터(101)를 온으로 하여 배선(123)으로부터 화상 데이터 "Vs"(s[m])를 기록한다.

[0171] 도 13의 (C)는 화상 데이터 "Vs"에 대한 EL 소자(114)를 흐르는 전류( $I_{LED}$ )의 시뮬레이션 결과를 나타낸 것이다. 하나의 화소의 시뮬레이션 결과를 도 13의 (C)에 나타내었지만, 모든 화소(pix1 내지 pix4)에서 그레이스케일 표시가 확인된다.

[0172] 도 13의 (D)는 화상 데이터 "Vs"에 대한 노드(NM)의 전위 " $V_{NM}$ "의 변화의 시뮬레이션 결과를 나타낸 것이다. 모든 화소에서 노드(NM)의 전위 " $V_{NM}$ "이 화상 데이터 "Vs"에 비례하는 것이 확인된다.

[0173] 따라서, 배선(123)으로부터 공급되는 저해상도용 화상 데이터 "Vs"를 표시할 수 있는 것이 확인된다.

[0174] 도 14의 (A) 내지 (D)는 저해상도 표시(보정 있음)를 검증하기 위한 시뮬레이션 결과를 나타낸 것이다. 도 14의 (A) 및 (B)는 검증에 사용한 타이밍 차트이다. 먼저, 배선(123)에 원하는 보정 데이터 "Vp"를 공급하고, 도 14의 (A)에 나타낸 시각 T1 내지 시각 T2에서 보정 데이터 "Vp"(p[n])를 기록한다. 또한 시각 T3 내지 시각 T4에서 보정 데이터 "Vp"(p[n+1])를 기록한다. 이때, 배선(128)을 전위 "Vref"(+1V)로 하기 때문에 용량 소자(104)에 유지된 차분 전위는 "Vp-1"이다.

[0175] 그 후, 도 14의 (B)에 나타낸 시각 T1 내지 시각 T2에서 트랜지스터(101)를 온으로 하여 배선(123)으로부터 화상 데이터 "Vs"를 기록하고 화상 데이터에 보정 데이터를 부가한다. 이때, 배선(128)은 애노드 전위이다.

[0176] 도 14의 (C)는 화상 데이터 "Vs"에 대한 EL 소자(114)를 흐르는 전류( $I_{LED}$ )의 시뮬레이션 결과를 나타낸 것이다. 보정 데이터 "Vp"로서 1V 내지 8V를 기록한 경우 및 화상 데이터 "Vs"와 조합시킨 경우 각각에서 그레이스케일 표시가 확인된다.

[0177] 도 14의 (D)는 화상 데이터 "Vs"에 대한 노드(NM)의 전위 " $V_{NM}$ "의 변화의 시뮬레이션 결과를 나타낸 것이다. 보정 데이터 "Vp"로서 1V 내지 8V를 기록한 경우 및 화상 데이터 "Vs"와 조합시킨 경우 각각에서, 노드(NM)의 전위 " $V_{NM}$ "이 화상 데이터 "Vs"에 비례하는 경향이 있는 것이 확인된다.

[0178] 상기에 의하여, 배선(123)으로부터 공급되는 보정 데이터 "Vp" 및 저해상도용 화상 데이터 "Vs"를 조합함으로써 유효한 표시가 가능한 것이 확인된다.

[0179] 도 15는 본 발명의 일 형태의 화소가 채용된, 컬러 표시가 가능한 EL 표시 장치의 예를 나타낸 것이다. 컬러 표시가 가능한 표시 장치의 화소는 일반적으로 적색(R), 녹색(G), 및 청색(B)의 광을 방출하는 부화소의 조합을 포함한다. 도 15에는 수평 방향으로 배치된 3개의 부화소(10R, 10G, 및 10B)로 각각 구성된 수평 수직 방향의 4개의 화소를 나타내었다. 또한 도 15에서는 트랜지스터(102a 및 102b)를 하나의 블록으로서 나타내었다.

[0180] 상술한 바와 같이, 본 발명의 일 형태에서는, 트랜지스터(101)를 개재(介在)하여 매트릭스로 배치된 4개의 화소(같은 색의 광을 방출하는 4개의 부화소에 대응함)에 보정 데이터 "Vp1" 또는 화상 데이터 "VsL"을 입력할 수 있다. 트랜지스터(102a 및 102b)를 개재하여 수평 방향으로 배치된 2개의 화소(같은 색의 광을 방출하는 2개의 부화소에 대응함)에 전위 "Vref"를 공급할 수 있다.

[0181] 스트라이프 배열에서, 부화소는 규칙적인 간격으로 배치되는 것이 바람직하지만, 부화소가 배선 또는 트랜지스터를 공유하는 경우, 부화소 간(같은 기능을 가지는 구성 요소 간)에서 일정 간격을 확보하기 어려운 경우가 있다.

[0182] 따라서 전극(26R, 26G, 및 26B)이 부화소(10R, 10G, 및 10B)에 각각 접속된 화소 전극인 경우에는, 전극(26R, 26G, 및 26B)은 도 15에 나타낸 바와 같이, 규칙적인 간격으로 배치되는 것이 바람직하다. 또한 화소 전극을 대응하는 부화소의 구성 요소라고 가정할 수도 있지만, 여기서는 명료화를 위하여 다른 구성 요소라고 가정한다. 이 구조는 톱 이미션 EL 표시 장치 또는 반사형 액정 표시 장치에 유효하다.

[0183] 본 실시형태는 다른 실시형태 등에서 설명하는 구조 중 임의의 것과 적절히 조합하여 실시할 수 있다.

[0184] (실시형태 2)

[0185] 본 실시형태에서는 액정 소자를 포함한 표시 장치 및 EL 소자를 포함한 표시 장치의 구조예에 대하여 설명한다. 또한 본 실시형태에서는 실시형태 1에서 설명한 표시 장치의 구성 요소, 동작, 및 기능에 대해서는 반복하여 설명하지 않는다.

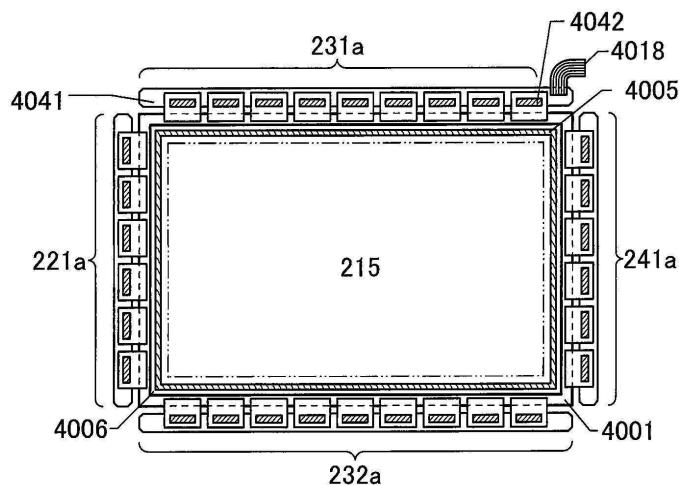

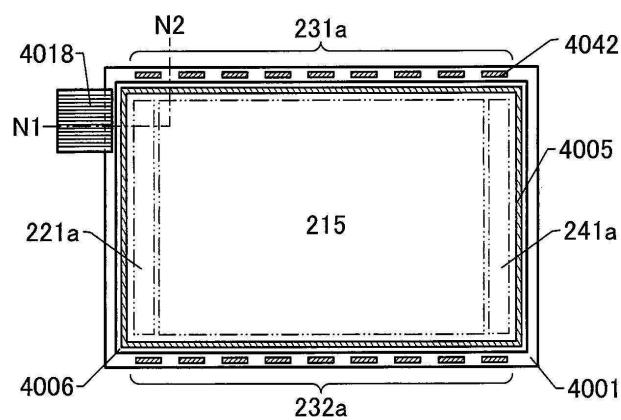

[0186] 도 16의 (A) 내지 (C)는 각각 본 발명의 일 형태를 사용할 수 있는 표시 장치의 구조를 나타낸 것이다.

[0187] 도 16의 (A)에서는, 제 1 기판(4001) 위에 제공된 표시부(215)를 둘러싸도록 실재(4005)가 제공된다. 표시부(215)가 실재(4005) 및 제 2 기판(4006)으로 밀봉되어 있다.

[0188] 표시부(215)에는 실시형태 1의 도 7에 나타낸 화소 어레이를 제공할 수 있다. 또한 아래에서 설명하는 주사선 구동 회로는 행 드라이버에, 신호선 구동 회로는 열 드라이버에 대응한다.

[0189] 도 16의 (A)에서, 주사선 구동 회로(221a), 신호선 구동 회로(231a), 신호선 구동 회로(232a), 및 공통선 구동 회로(241a)는 각각 인쇄 회로 기판(4041) 위에 제공된 복수의 접적 회로(4042)를 포함한다. 접적 회로(4042)는 각각 단결정 반도체 또는 다결정 반도체를 사용하여 형성되어 있다. 신호선 구동 회로(231a) 및 신호선 구동 회로(232a)는 각각 실시형태 1에서 설명한 열 드라이버로서 기능한다. 주사선 구동 회로(221a)는 실시형태 1에서 설명한 행 드라이버로서 기능한다. 공통선 구동 회로(241a)는 실시형태 1에서 설명한, 전원을 공급하는 배선 또는 Vref를 공급하는 배선에 소정의 전위를 공급하는 기능을 가진다.

[0190] 주사선 구동 회로(221a), 공통선 구동 회로(241a), 신호선 구동 회로(231a), 및 신호선 구동 회로(232a)에는 FPC(flexible printed circuit)(4018)를 통하여 신호 및 전위가 공급된다.

[0191] 주사선 구동 회로(221a) 및 공통선 구동 회로(241a)에 포함되는 접적 회로(4042)는 각각 표시부(215)에 선택 신호를 공급하는 기능을 가진다. 신호선 구동 회로(231a) 및 신호선 구동 회로(232a)에 포함되는 접적 회로(4042)는 각각 표시부(215)에 화상 데이터를 공급하는 기능을 가진다. 접적 회로(4042)는 제 1 기판(4001) 위의 실재(4005)로 둘러싸인 영역과는 다른 영역에 실장되어 있다.

[0192] 또한 접적 회로(4042)의 접속 방법은 한정되지 않고, 와이어 본딩법, COG(chip on glass)법, TCP(tape carrier package)법, 또는 COF(chip on film)법 등을 사용할 수 있다.

[0193] 도 16의 (B)는 신호선 구동 회로(231a) 및 신호선 구동 회로(232a)에 포함되는 접적 회로(4042)를 COG법에 의하여 실장하는 예를 나타낸 것이다. 구동 회로의 일부 또는 모두를 표시부(215)가 형성되는 기판 위에 형성함으로써, 시스템 온 패널(system-on-panel)을 얻을 수 있다.

[0194] 도 16의 (B)에 나타낸 예에서는, 표시부(215)가 형성되는 기판 위에 주사선 구동 회로(221a) 및 공통선 구동 회로(241a)가 형성되어 있다. 구동 회로를 표시부(215) 내의 화소 회로와 동시에 형성하면, 부품의 개수를 줄일 수 있으므로 생산성을 높일 수 있다.

[0195] 도 16의 (B)에서는, 제 1 기판(4001) 위의 표시부(215), 주사선 구동 회로(221a), 및 공통선 구동 회로(241a)를 둘러싸도록 실재(4005)가 제공되어 있다. 표시부(215), 주사선 구동 회로(221a), 및 공통선 구동 회로(241a) 위에 제 2 기판(4006)이 제공되어 있다. 따라서 표시부(215), 주사선 구동 회로(221a), 및 공통선 구동 회로(241a)는 제 1 기판(4001), 실재(4005), 및 제 2 기판(4006)을 사용하여 표시 소자와 함께 밀봉되어 있다.

[0196] 도 16의 (B)에 나타낸 예에서는 신호선 구동 회로(231a) 및 신호선 구동 회로(232a)가 별도로 형성되고 제 1 기판(4001)에 실장되어 있지만, 본 발명의 일 형태는 이 구조에 한정되지 않는다. 주사선 구동 회로를 별도로 형성한 다음 실장하여도 좋고, 신호선 구동 회로의 일부 또는 주사선 구동 회로의 일부를 별도로 형성한 다음 실장하여도 좋다. 도 16의 (C)에 나타낸 바와 같이, 신호선 구동 회로(231a) 및 신호선 구동 회로(232a)를 표시부(215)가 형성되는 기판 위에 형성하여도 좋다.

[0197] 표시 장치는 표시 소자가 밀봉된 패널, 및 상기 패널에 컨트롤러를 포함한 IC 등이 실장된 모듈을 포함하는 경우가 있다.

[0198] 제 1 기판 위의 표시부 및 주사선 구동 회로는 각각 복수의 트랜지스터를 포함한다. 위의 실시형태에서 설명한 트랜지스터를 상기 트랜지스터로서 사용할 수 있다.

[0199] 주변 구동 회로에 포함되는 트랜지스터 및 표시부의 화소 회로에 포함되는 트랜지스터는 같은 구조를 가져도 좋고 다른 구조를 가져도 좋다. 주변 구동 회로에 포함되는 트랜지스터는 같은 구조를 가진 트랜지스터이어도 좋

고 2종류 이상의 구조를 가진 트랜지스터이어도 좋다. 마찬가지로, 화소 회로에 포함되는 트랜지스터는 같은 구조를 가진 트랜지스터이어도 좋고 2종류 이상의 구조를 가진 트랜지스터이어도 좋다.

[0200] 제 2 기판(4006) 위에는 입력 장치(4200)를 제공할 수 있다. 도 16의 (A) 내지 (C) 중 어느 것에 나타낸 표시 장치에 입력 장치(4200)를 추가한 구조에서는 터치 패널 기능을 얻을 수 있다.

[0201] 본 발명의 일 형태의 터치 패널에 포함되는 센서 소자에 특별한 한정은 없다. 손가락 또는 스타일러스 등의 검지 대상의 근접 또는 접촉을 검지할 수 있는 다양한 센서를 센서 소자로서 사용할 수 있다.

[0202] 예를 들어 센서에는 정전 용량 방식, 저항막 방식, 표면 탄성파 방식, 적외선 방식, 광학 방식, 및 감압 방식 등 다양한 방식을 사용할 수 있다.

[0203] 본 실시형태에서는 정전 용량 방식의 센서 소자를 포함한 터치 패널을 예로서 설명한다.

[0204] 정전 용량 방식의 센서 소자의 예에는 표면형 정전 용량 방식의 센서 소자 및 투영형 정전 용량 방식의 센서 소자가 포함된다. 투영형 정전 용량 방식의 센서 소자의 예에는 자기 용량 방식의 센서 소자 및 상호 용량 방식의 센서 소자가 포함된다. 상호 용량 방식의 센서 소자를 사용하면 여러 지점을 동시에 검지할 수 있으므로 바람직하다.

[0205] 본 발명의 일 형태의 터치 패널은, 따로따로 형성된 표시 장치와 센서 소자를 서로 접착하는 구조, 및 표시 소자를 지지하는 기판 및 대향 기판 중 한쪽 또는 양쪽 모두에 센서 소자에 포함되는 전극 등을 제공하는 구조를 포함한 다양한 구조 중 임의의 것을 가질 수 있다.

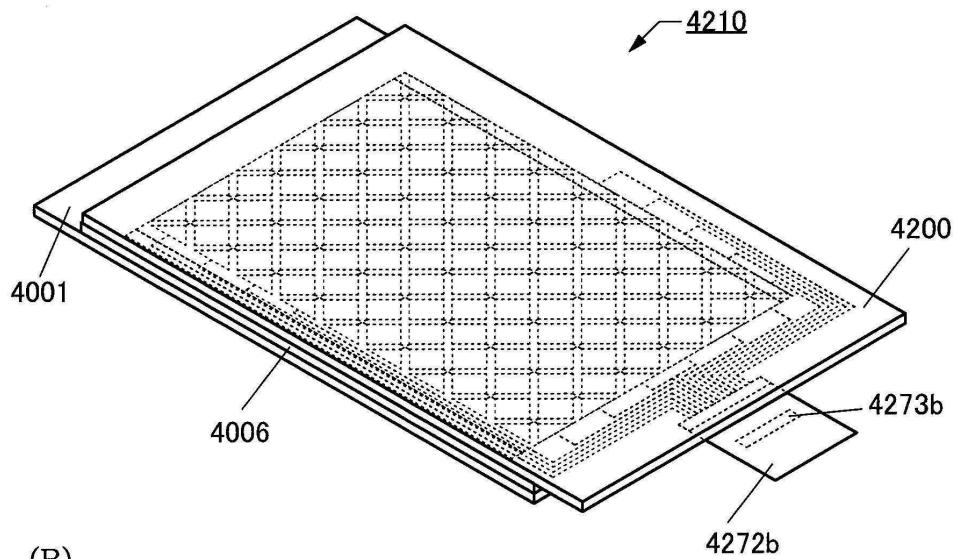

[0206] 도 17의 (A) 및 (B)는 터치 패널의 예를 나타낸 것이다. 도 17의 (A)는 터치 패널(4210)의 사시도이다. 도 17의 (B)는 입력 장치(4200)의 사시 개략도이다. 또한 명료화를 위하여 도 17의 (A) 및 (B)에는 주요한 구성 요소만을 나타내었다.

[0207] 터치 패널(4210)은 따로따로 형성된 표시 장치와 센서 소자를 서로 접합시킨 구조를 가진다.

[0208] 터치 패널(4210)은 서로 중첩하여 제공된 입력 장치(4200) 및 표시 장치를 포함한다.

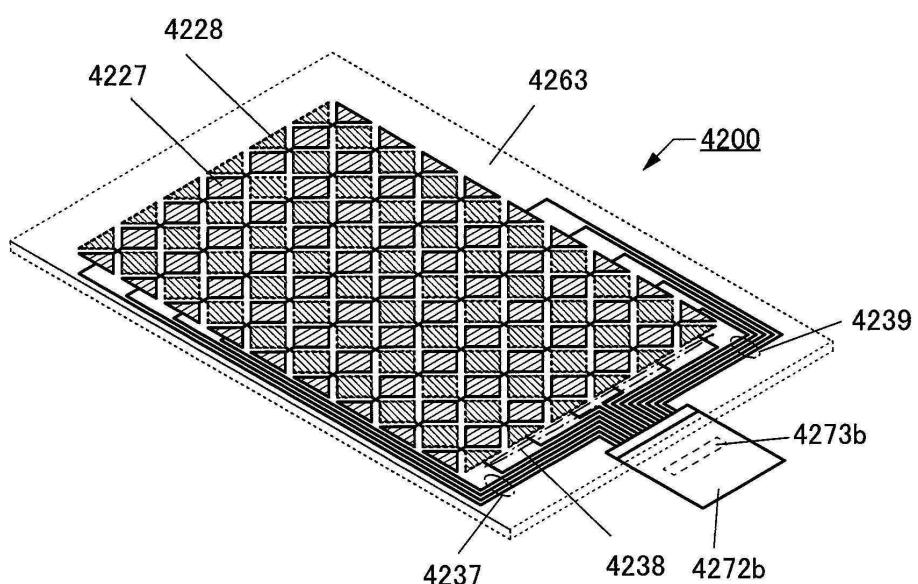

[0209] 입력 장치(4200)는 기판(4263), 전극(4227), 전극(4228), 복수의 배선(4237), 복수의 배선(4238), 및 복수의 배선(4239)을 포함한다. 예를 들어, 전극(4227)은 배선(4237) 또는 배선(4239)에 전기적으로 접속될 수 있다. 또한 전극(4228)은 배선(4239)에 전기적으로 접속될 수 있다. FPC(4272b)는 복수의 배선(4237) 및 복수의 배선(4238)의 각각에 전기적으로 접속된다. FPC(4272b)에는 IC(4273b)를 제공할 수 있다.

[0210] 표시 장치의 제 1 기판(4001)과 제 2 기판(4006) 사이에 터치 센서를 제공하여도 좋다. 제 1 기판(4001)과 제 2 기판(4006) 사이에 터치 센서를 제공하는 경우에는, 정전 용량 방식의 터치 센서 및 광학 변환 소자를 포함한 광학 터치 센서의 어느 쪽이든 사용할 수 있다.

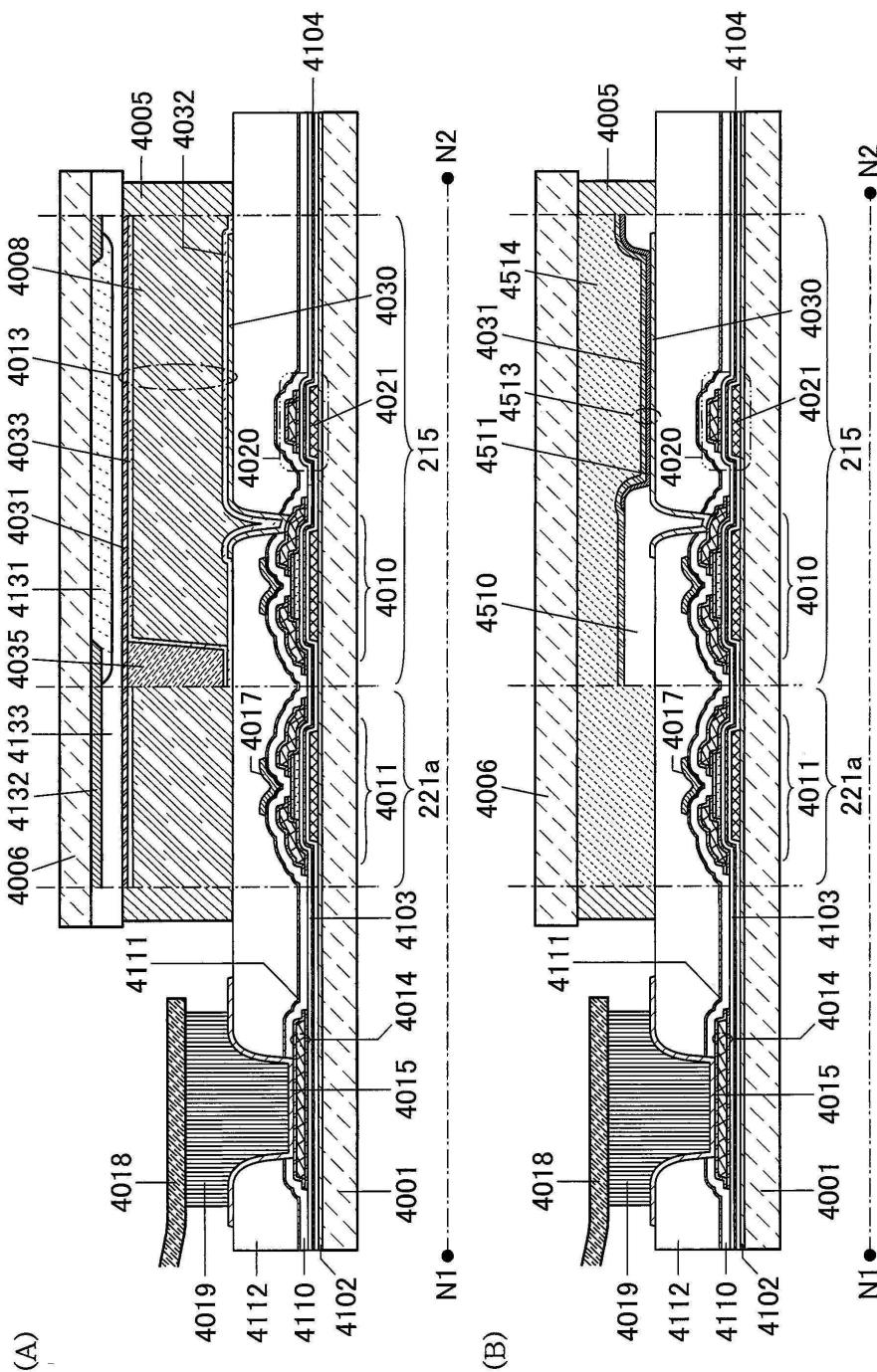

[0211] 도 18의 (A) 및 (B)는 각각 도 16의 (B)의 쇄선 N1-N2를 따라 자른 단면도이다. 도 18의 (A) 및 (B)에 나타낸 표시 장치는 각각 전극(4015)을 포함하고, 전극(4015)은 FPC(4018)에 포함되는 단자에 이방성 도전층(4019)을 통하여 전기적으로 접속되어 있다. 도 18의 (A) 및 (B)에서, 전극(4015)은 절연층(4112, 4111, 및 4110)에 형성된 개구에서 배선(4014)에 전기적으로 접속되어 있다.

[0212] 전극(4015)은 제 1 전극층(4030)과 같은 도전층으로 형성되고, 배선(4014)은 트랜지스터(4010 및 4011)의 소스 전극 및 드레인 전극과 같은 도전층으로 형성되어 있다.

[0213] 제 1 기판(4001) 위에 제공된 표시부(215) 및 주사선 구동 회로(221a)는 각각 복수의 트랜지스터를 포함한다. 도 18의 (A) 및 (B)에는, 표시부(215)에 포함되는 트랜지스터(4010) 및 주사선 구동 회로(221a)에 포함되는 트랜지스터(4011)를 예로서 나타내었다. 도 18의 (A) 및 (B)에 나타낸 예에서, 트랜지스터(4010 및 4011)는 보텀 게이트 트랜지스터이지만 톱 게이트 트랜지스터이어도 좋다.

[0214] 도 18의 (A) 및 (B)에서는, 트랜지스터(4010 및 4011) 위에 절연층(4112)이 제공되어 있다. 도 18의 (B)에서는, 절연층(4112) 위에는 격벽(4510)이 제공되어 있다.

[0215] 트랜지스터(4010 및 4011)는 절연층(4102) 위에 제공되어 있다. 트랜지스터(4010 및 4011)는 각각 절연층(4111) 위에 형성된 전극(4017)을 포함한다. 전극(4017)은 백 게이트 전극으로서 기능할 수 있다.

[0216] 도 18의 (A) 및 (B)에 나타낸 표시 장치는 각각 용량 소자(4020)를 포함한다. 용량 소자(4020)는 트랜지스터(4010)의 게이트 전극과 같은 단계에서 형성된 전극(4021), 및 트랜지스터(4010)의 소스 전극 및 드레인 전극과

같은 단계에서 형성된 전극을 포함한다. 이들 전극은 절연층(4103)을 개재하여 서로 중첩되어 있다.

[0217] 일반적으로, 표시 장치의 화소부에 제공되는 용량 소자의 용량은, 화소부에 제공되는 트랜지스터의 누설 전류 등을 고려하여, 소정 기간 전하를 유지할 수 있도록 설정된다. 용량 소자의 용량은 트랜지스터의 오프 상태 전류 등을 고려하여 설정된다.

[0218] 표시부(215)에 제공되는 트랜지스터(4010)는 표시 소자에 전기적으로 접속된다. 도 18의 (A)는 표시 소자로서 액정 소자를 사용하는 액정 표시 장치의 예를 나타낸 것이다. 도 18의 (A)에서 표시 소자로서 기능하는 액정 소자(4013)는 제 1 전극층(4030), 제 2 전극층(4031), 및 액정층(4008)을 포함한다. 배향막으로서 기능하는 절연층(4032 및 4033)이 액정층(4008)을 개재하도록 제공된다. 제 2 전극층(4031)은 제 2 기판(4006) 측에 제공되고, 제 1 전극층(4030)과 제 2 전극층(4031)은 액정층(4008)을 개재하여 서로 중첩된다.

[0219] 스페이서(4035)는 절연층의 선택적 에칭에 의하여 얻어지는 기동형 스페이서이고 제 1 전극층(4030)과 제 2 전극층(4031) 사이의 거리(셀 갭)를 제어하기 위하여 제공된다. 또한 구상 스페이서를 대신에 사용하여도 좋다.

[0220] 블랙 매트릭스(차광층), 착색층(컬러 필터), 혹은 편광 부재, 위상차 부재, 또는 반사 방지 부재 등의 광학 부재(광학 기판) 등을 적절히 제공하여도 좋다. 예를 들어, 편광 기판 및 위상차 기판을 사용함으로써, 원 편광을 채용하여도 좋다. 또한 광원으로서 백라이트 또는 사이드라이트 등을 사용하여도 좋다. 백라이트 또는 사이드라이트로서 마이크로 LED 등을 사용하여도 좋다.

[0221] 도 18의 (A)에 나타낸 표시 장치에서는, 제 2 기판(4006)과 제 2 전극층(4031) 사이에 차광층(4132), 착색층(4131), 및 절연층(4133)이 제공된다.

[0222] 차광층에 사용할 수 있는 재료의 예에는 카본 블랙, 타이타늄 블랙, 금속, 금속 산화물, 및 복수의 금속 산화물의 고용체를 포함한 복합 산화물이 포함된다. 차광층은 수지 재료를 포함한 막이여도 좋고, 금속 등의 무기 재료의 박막이여도 좋다. 착색층의 재료를 포함하는 적층막을 차광층에 사용할 수도 있다. 예를 들어, 어느 색의 광을 투과시키는 착색층의 재료를 포함하는 막과, 다른 색의 광을 투과시키는 착색층의 재료를 포함하는 막의 적층 구조를 채용할 수 있다. 착색층 및 차광층을 같은 재료를 사용하여 형성하면, 같은 제조 장치를 사용할 수 있고 공정을 간략화할 수 있기 때문에 바람직하다.

[0223] 착색층에 사용할 수 있는 재료의 예에는, 금속 재료, 수지 재료, 및 안료 또는 염료를 포함한 수지 재료가 포함된다. 차광층 및 착색층은 예를 들어 잉크젯법에 의하여 형성할 수 있다.

[0224] 도 18의 (A) 및 (B)에 나타낸 표시 장치 각각은 절연층(4111) 및 절연층(4104)을 포함한다. 절연층(4104 및 4111)으로서는, 불순물 원소가 쉽게 통과하지 않는 절연층을 사용한다. 절연층들(4104 및 4111) 사이에 트랜지스터의 반도체층을 끼워으로써, 외부로부터의 불순물의 침입을 방지할 수 있다.

[0225] 표시 장치에 포함되는 표시 소자로서, 일렉트로루미네센스를 이용하는 발광 소자(EL 소자)를 사용할 수 있다. EL 소자는 한 쌍의 전극 사이에 발광성 화합물을 포함한 층("EL층"이라고도 함)을 포함한다. 한 쌍의 전극 사이에서 EL 소자의 문턱 전압보다 큰 전위차를 발생시키면, EL층에 양극 측으로부터 정공이 주입되고, EL층에 음극 측으로부터 전자가 주입된다. 주입된 전자와 정공은 EL층에서 재결합되고, EL층에 포함되는 발광 화합물이 광을 방출한다.

[0226] EL 소자는 발광 재료가 유기 화합물인지 또는 무기 화합물인지에 따라 분류된다. 일반적으로, 전자(前者)를 유기 EL 소자라고 하고, 후자(後者)를 무기 EL 소자라고 한다.

[0227] 유기 EL 소자에서는, 전압을 인가함으로써, 한쪽 전극으로부터 EL층에 전자가 주입되고, 다른 쪽 전극으로부터 EL층에 정공이 주입된다. 캐리어(전자 및 정공)가 재결합됨으로써, 발광성 유기 화합물이 여기된다. 발광성 유기 화합물은 여기 상태로부터 기저 상태로 되돌아감으로써 광을 방출한다. 이와 같은 메커니즘 때문에, 이 발광 소자를 전류 여기형 발광 소자라고 한다.

[0228] 발광성 화합물에 더하여, EL층은 정공 주입성이 우수한 물질, 정공 수송성이 우수한 물질, 정공 블로킹 재료, 전자 수송성이 우수한 물질, 전자 주입성이 우수한 물질, 및 바이폴러성을 가지는 물질(전자 수송성 및 정공 수송성이 우수한 물질) 등 중 임의의 것을 더 포함하여도 좋다.

[0229] EL층은 증착법(진공 증착법을 포함함), 전사법(transfer method), 인쇄법, 잉크젯법, 또는 도포법 등에 의하여 형성할 수 있다.

[0230] 무기 EL 소자는 그 소자 구조에 따라, 분산형 무기 EL 소자 및 박막형 무기 EL 소자로 분류된다. 분산형 무기

EL 소자는 발광 재료의 입자를 바인더 내로 분산시킨 발광층을 포함하고, 그 발광 메커니즘은 도너 준위와 억셉터 준위를 이용하는 도너-억셉터 재결합형 발광이다. 박막형 무기 EL 소자는 발광층을 유전체층들 사이에 끼우고, 이들을 전극들 사이에 더 끼운 구조를 가지고, 그 발광 메커니즘은 금속 이온의 내각(inner-shell) 전자 전이(electron transition)를 이용하는 국재(局在)형 발광이다. 또한 여기서는 발광 소자로서 유기 EL 소자를 사용하는 경우에 대하여 설명한다.

[0231] 발광 소자로부터 방출되는 광을 추출하기 위해서는, 한 쌍의 전극 중 적어도 한쪽이 투명할 필요가 있다. 기판 위에 트랜지스터 및 발광 소자를 형성한다. 발광 소자는, 상기 기판과는 반대쪽의 면으로부터 발광을 추출하는 톱 이미션 구조, 기판의 면으로부터 발광을 추출하는 보텀 이미션 구조, 또는 기판과는 반대쪽의 면과 기판의 면의 양쪽으로부터 발광을 추출하는 듀얼 이미션 구조를 가질 수 있다.

[0232] 도 18의 (B)는 표시 소자로서 발광 소자를 사용한 발광 표시 장치("EL 표시 장치"라고도 함)의 예를 나타낸 것이다. 표시 소자인 발광 소자(4513)는 표시부(215)에 제공된 트랜지스터(4010)에 전기적으로 접속되어 있다. 발광 소자(4513)의 구조는 제 1 전극층(4030), 발광층(4511), 및 제 2 전극층(4031)의 적층 구조이지만, 본 실시형태는 이 구조에 한정되지 않는다. 발광 소자(4513)로부터 광을 추출하는 방향 등에 따라 발광 소자(4513)의 구조를 적절히 변경할 수 있다.

[0233] 격벽(4510)은 유기 절연 재료 또는 무기 절연 재료를 사용하여 형성된다. 격벽(4510)은 감광성 수지 재료를 사용하여 제 1 전극층(4030) 위에 개구를 가지도록 형성되어, 그 개구의 측면이 연속한 곡률을 가지고 경사지는 것이 특히 바람직하다.

[0234] 발광층(4511)은 하나의 층을 사용하여 형성되어도 좋고 적층된 복수의 층을 사용하여 형성되어도 좋다.

[0235] 발광 소자(4513)의 발광색은 발광층(4511)의 재료에 따라 백색, 적색, 녹색, 청색, 시안, 마젠타, 또는 황색 등으로 할 수 있다.

[0236] 컬러 표시 방법으로서는, 백색광을 방출하는 발광 소자(4513)를 착색층과 조합하는 방법과, 화소마다 다른 발광색의 광을 방출하는 발광 소자(4513)를 제공하는 방법이 있다. 전자의 방법은 후자의 방법보다 생산적이다. 후자의 방법은, 화소마다 발광층(4511)을 따로따로 형성할 필요가 있기 때문에 전자의 방법보다 생산성이 떨어지지만, 후자의 방법은 전자의 방법보다 색 순도가 높은 발광색을 제공할 수 있다. 후자의 방법에서, 발광 소자(4513)가 마이크로캐비티 구조를 가지면, 색 순도를 더 높일 수 있다.

[0237] 발광층(4511)은 퀀텀닷(quantum dot) 등의 무기 화합물을 포함하여도 좋다. 예를 들어, 퀀텀닷은 발광층에 사용되면 발광 재료로서 기능할 수 있다.

[0238] 발광 소자(4513) 내에 산소, 수소, 수분, 또는 이산화 탄소 등이 들어가는 것을 방지하기 위하여, 제 2 전극층(4031) 및 격벽(4510) 위에 보호층을 형성하여도 좋다. 보호층에는 질화 실리콘, 질화산화 실리콘, 산화 알루미늄, 질화 알루미늄, 산화질화 알루미늄, 질화산화 알루미늄, 또는 DLC(diamond like carbon) 등을 사용할 수 있다. 제 1 기판(4001), 제 2 기판(4006), 및 실재(4005)로 형성된 공간에는 밀봉하기 위하여 충전재(4514)가 제공되어 있다. 이런 식으로, 발광 소자가 외기에 노출되지 않도록, 기밀성이 높고 탈가스가 적은 보호 필름(접합 필름 또는 자외선 경화 수지 필름 등) 또는 커버 부재를 사용하여 발광 소자가 패키징(밀봉)되는 것이 바람직하다.

[0239] 충전재(4514)로서는, 질소 또는 아르곤 등의 불활성 가스 외에, 자외선 경화 수지 또는 열경화 수지를 사용할 수 있고, 폴리바이닐클로라이드(PVC), 아크릴계 수지, 폴리이미드, 에폭시계 수지, 실리콘(silicone)계 수지, 폴리바이닐뷰티랄(PVB), 또는 에틸렌바이닐아세테이트(EVA) 등을 사용할 수 있다. 충전재(4514)에는 건조제가 포함되어도 좋다.

[0240] 실재(4005)에는 유리 프레트 등의 유리 재료, 또는 실온에서 경화될 수 있는 수지(예를 들어, 2성분 혼합형 수지), 광경화성 수지, 또는 열경화성 수지 등의 수지 재료를 사용할 수 있다. 실재(4005)에는 건조제가 포함되어도 좋다.

[0241] 필요하다면, 발광 소자의 발광면에 편광판, 원 편광판(타원 편광판을 포함함), 위상차판(1/4 파장판 또는 1/2 파장판), 또는 컬러 필터 등의 광학 필름을 적절히 제공하여도 좋다. 또한 편광판 또는 원 편광판에 반사 방지막을 제공하여도 좋고, 예를 들어, 표면의 요철에 의하여 반사광을 확산시켜 눈부심을 저감할 수 있는 안티글레어 처리를 수행할 수 있다.

[0242] 발광 소자가 마이크로캐비티 구조를 가지면, 색 순도가 높은 광을 추출할 수 있다. 또한 마이크로캐비티 구조

와 컬러 필터를 조합하여 사용하면, 눈부심을 저감하고 표시 화상의 시인성을 높일 수 있다.

[0243] 표시 소자에 전압을 인가하는 제 1 전극층 및 제 2 전극층(각각을 화소 전극층, 공통 전극층, 또는 대향 전극층 등이라고도 함) 각각은 광을 추출하는 방향, 전극층이 제공되는 위치, 및 전극층의 패턴 구조에 따라 투광성 또는 광 반사성을 가진다.

[0244] 제 1 전극층(4030) 및 제 2 전극층(4031)의 각각은 산화 텅스텐을 포함하는 인듐 산화물, 산화 텅스텐을 포함하는 인듐 아연 산화물, 산화 타이타늄을 포함하는 인듐 산화물, 인듐 주석 산화물, 산화 타이타늄을 포함하는 인듐 주석 산화물, 인듐 아연 산화물, 또는 산화 실리콘의 첨가된 인듐 주석 산화물 등의 투광성의 도전성 재료를 사용하여 형성할 수 있다.

[0245] 제 1 전극층(4030) 및 제 2 전극층(4031)의 각각은 텅스텐(W), 몰리브데넘(Mo), 지르코늄(Zr), 하프늄(Hf), 바나듐(V), 나이오븀(Nb), 탄탈럼(Ta), 크로뮴(Cr), 코발트(Co), 니켈(Ni), 타이타늄(Ti), 백금(Pt), 알루미늄(Al), 구리(Cu), 또는 은(Ag) 등의 금속, 이들의 합금, 및 이들의 금속 질화물 중에서 선택된 1종류 이상을 사용하여 형성할 수도 있다.

[0246] 제 1 전극층(4030) 및 제 2 전극층(4031)에는 도전성 고분자(도전성 폴리머라고도 함)를 포함하는 도전성 조성물을 사용할 수 있다. 도전성 고분자로서는, π전자 공액 도전성 고분자를 사용할 수 있다. 예를 들어, 폴리아닐린 또는 그 유도체, 폴리피롤 또는 그 유도체, 폴리싸이오펜 또는 그 유도체, 아닐린, 피롤, 및 싸이오펜 중 2개 이상으로 이루어진 공중합체 또는 그 유도체가 있다.

[0247] 트랜지스터는 정전기 등에 의하여 파괴되기 쉽기 때문에, 구동 회로를 보호하기 위한 보호 회로를 제공하는 것이 바람직하다. 보호 회로는 비선형 소자를 사용하여 형성되는 것이 바람직하다.

[0248] 본 실시형태는 다른 실시형태 등에서 설명하는 구조 중 임의의 것과 적절히 조합하여 실시할 수 있다.

[0249] (실시형태 3)

[0250] 본 실시형태에서는, 위의 실시형태에서 설명한 트랜지스터로서 사용할 수 있는 트랜지스터의 예에 대하여 도면을 참조하여 설명한다.

[0251] 본 발명의 일 형태의 표시 장치는 보텀 게이트 트랜지스터 또는 틉 게이트 트랜지스터 등 다양한 구조를 가지는 트랜지스터를 사용하여 제작할 수 있다. 그러므로 기존의 생산 라인에 따라 반도체층의 재료 또는 트랜지스터의 구조를 쉽게 변경할 수 있다.

[0252] [보텀 게이트 트랜지스터]

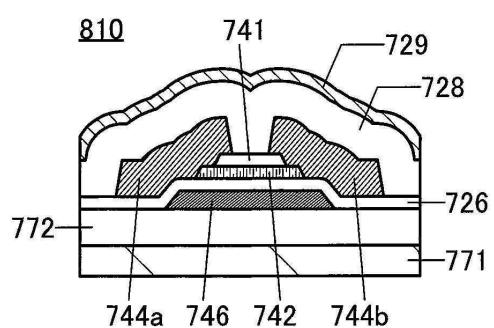

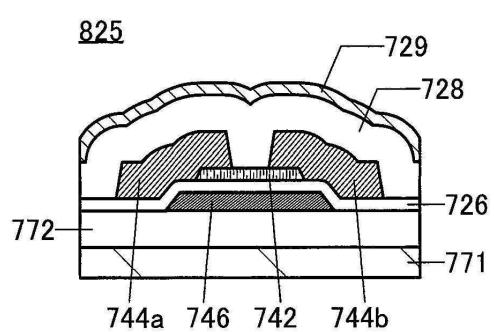

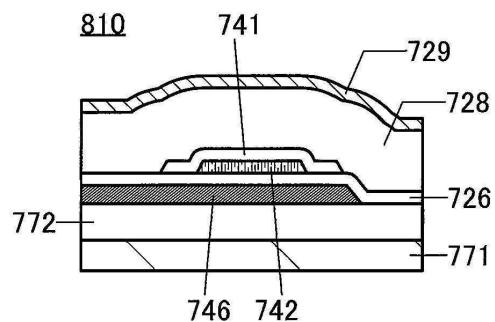

[0253] 도 19의 (A1)은 보텀 게이트 트랜지스터의 일종인 채널 보호 트랜지스터(810)의 채널 길이 방향에서의 단면도이다. 도 19의 (A1)에서 트랜지스터(810)는 기판(771) 위에 형성되어 있다. 트랜지스터(810)는 절연층(772)을 개재하여 기판(771) 위에 전극(746)을 포함한다. 또한 트랜지스터(810)는 절연층(726)을 개재하여 전극(746) 위에 반도체층(742)을 포함한다. 전극(746)은 게이트 전극으로서 기능할 수 있다. 절연층(726)은 게이트 절연층으로서 기능할 수 있다.

[0254] 트랜지스터(810)는 반도체층(742)의 채널 형성 영역 위에 절연층(741)을 포함한다. 또한 트랜지스터(810)는 절연층(726) 위에 있고 반도체층(742)과 부분적으로 접촉하는 전극(744a) 및 전극(744b)을 포함한다. 전극(744a)은 소스 전극 및 드레인 전극 중 한쪽으로서 기능할 수 있다. 전극(744b)은 소스 전극 및 드레인 전극 중 다른 쪽으로서 기능할 수 있다. 전극(744a)의 일부 및 전극(744b)의 일부는 절연층(741) 위에 형성된다.

[0255] 절연층(741)은 채널 보호층으로서 기능할 수 있다. 채널 형성 영역 위에 절연층(741)을 제공하면, 전극(744a 및 744b)을 형성할 때 반도체층(742)이 노출되는 것을 방지할 수 있다. 그러므로 전극(744a 및 744b)을 형성할 때 반도체층(742)의 채널 형성 영역이 예상되는 것을 방지할 수 있다. 본 발명의 일 형태에 따르면, 전기 특성이 양호한 트랜지스터를 제공할 수 있다.

[0256] 트랜지스터(810)는 전극(744a), 전극(744b), 및 절연층(741) 위에 절연층(728)을 포함하고, 절연층(728) 위에 절연층(729)을 더 포함한다.

[0257] 반도체층(742)에 산화물 반도체를 사용하는 경우에는, 전극(744a 및 744b)에서 적어도 반도체층(742)과 접촉하는 영역에, 반도체층(742)의 일부로부터 산소를 제거하여 산소 결손을 발생시킬 수 있는 재료를 사용하는 것이 바람직하다. 반도체층(742)에서 산소 결손이 발생한 영역의 캐리어 농도가 증가되므로, 상기 영역은 n형 영역

(n<sup>+</sup>층)이 된다. 이로써, 상기 영역은 소스 영역 및 드레인 영역으로서 기능할 수 있다. 반도체층(742)에 산화물 반도체를 사용하는 경우, 반도체층(742)으로부터 산소를 제거하여 산소 결손을 발생시킬 수 있는 재료의 예에는 텅스텐 및 타이타늄이 포함된다.

[0258] 반도체층(742)에 소스 영역 및 드레인 영역을 형성함으로써, 반도체층(742)과 각 전극(744a 및 744b) 사이의 접촉 저항을 저감할 수 있다. 이로써, 전계 효과 이동도 및 문턱 전압 등의 트랜지스터의 전기 특성을 향상시킬 수 있다.

[0259] 반도체층(742)에 실리콘 등의 반도체를 사용하는 경우에는, 반도체층(742)과 전극(744a) 사이, 및 반도체층(742)과 전극(744b) 사이에 n형 반도체 또는 p형 반도체로서 기능하는 층을 제공하는 것이 바람직하다. n형 반도체 또는 p형 반도체로서 기능하는 층은 트랜지스터의 소스 영역 또는 드레인 영역으로서 기능할 수 있다.

[0260] 절연층(729)은 외부로부터 트랜지스터로 불순물이 확산되는 것을 방지하거나 저감할 수 있는 재료를 사용하여 형성되는 것이 바람직하다. 또한 절연층(729)을 반드시 제공할 필요는 없다.

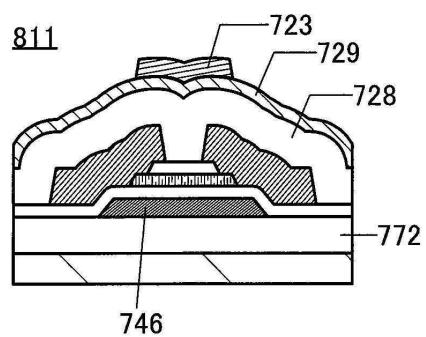

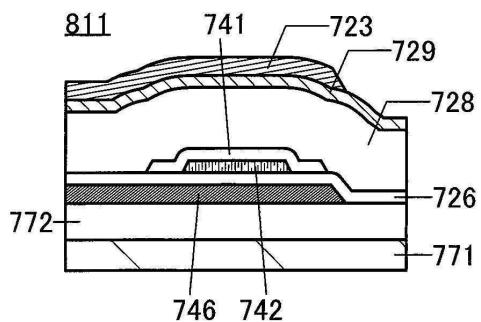

[0261] 도 19의 (A2)에 나타낸 트랜지스터(811)는 백 게이트 전극으로서 기능할 수 있는 전극(723)이 절연층(729) 위에 제공된다는 점에서 트랜지스터(810)와 다르다. 전극(723)은 전극(746)과 비슷한 재료 및 방법을 사용하여 형성할 수 있다.

[0262] 일반적으로, 백 게이트 전극은 도전층을 사용하여 형성되고, 반도체층의 채널 형성 영역이 게이트 전극과 백 게이트 전극 사이에 위치하도록 배치된다. 그러므로 백 게이트 전극은 게이트 전극과 비슷한 식으로 기능할 수 있다. 백 게이트 전극의 전위는 게이트 전극과 같게 하여도 좋고, 접지(GND) 전위 또는 임의의 전위로 하여도 좋다. 백 게이트 전극의 전위를 게이트 전극의 전위와는 독립적으로 변화시킴으로써, 트랜지스터의 문턱 전압을 변화시킬 수 있다.

[0263] 전극(746 및 723)은 각각 게이트 전극으로서 기능할 수 있다. 따라서 절연층(726, 728, 및 729)은 각각 게이트 절연층으로서 기능할 수 있다. 전극(723)을 절연층들(728 및 729) 사이에 제공하여도 좋다.

[0264] 전극(746 및 723) 중 한쪽을 "게이트 전극"이라고 하는 경우, 다른 쪽을 "백 게이트 전극"이라고 한다. 예를 들어, 트랜지스터(811)에서 전극(723)을 "게이트 전극"이라고 하는 경우, 전극(746)을 "백 게이트 전극"이라고 한다. 전극(723)을 "게이트 전극"으로서 사용하는 경우, 트랜지스터(811)를 톱 게이트 트랜지스터의 일종으로 간주할 수 있다. 전극(746 및 723) 중 한쪽을 "제 1 게이트 전극"이라고 하고, 다른 쪽을 "제 2 게이트 전극"이라고 하는 경우가 있다.

[0265] 반도체층(742)을 개재하여 전극(746 및 723)을 제공하고, 전극(746) 및 전극(723)의 전위를 같은 전위로 함으로써, 반도체층(742)에서 캐리어가 흐르는 영역이 막 두께 방향에서 확대된다. 따라서 이동하는 캐리어의 개수가 증가된다. 이 결과, 트랜지스터(811)의 온 상태 전류 및 전계 효과 이동도가 높아진다.

[0266] 그러므로 트랜지스터(811)는 그 면적에 대하여 온 상태 전류가 높다. 즉 요구되는 온 상태 전류에 대하여 트랜지스터(811)의 면적을 축소할 수 있다. 본 발명의 일 형태에 따르면, 트랜지스터의 면적을 축소할 수 있다. 그러므로 본 발명의 일 형태에 따르면, 접도도가 높은 반도체 장치를 제공할 수 있다.

[0267] 게이트 전극 및 백 게이트 전극은 도전층을 사용하여 형성되기 때문에, 트랜지스터의 외부에서 발생하는 전계가, 채널이 형성되는 반도체층에 영향을 미치는 것을 방지하는 기능(특히, 정전기 등에 대한 전계 차폐 기능)을 각각 가진다. 백 게이트 전극을 반도체층보다 크게 형성하여 반도체층을 백 게이트 전극으로 덮음으로써, 전계 차폐 기능을 향상시킬 수 있다.

[0268] 차광성 도전막을 사용하여 백 게이트 전극을 형성하면, 백 게이트 전극 층으로부터 반도체층에 광이 들어가는 것을 방지할 수 있다. 그러므로 반도체층의 광 열화를 방지하고, 문턱 전압이 변동되는 등의 트랜지스터의 전기 특성의 저하를 방지할 수 있다.

[0269] 본 발명의 일 형태에 따르면, 신뢰성이 높은 트랜지스터를 제공할 수 있다. 또한 신뢰성이 높은 반도체 장치를 제공할 수 있다.

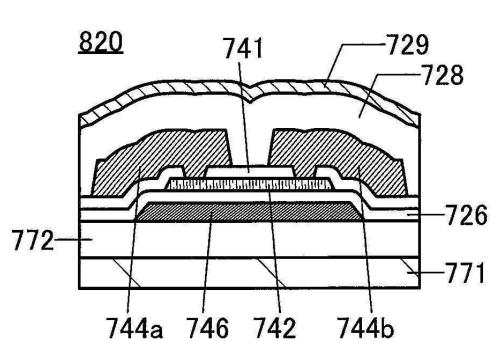

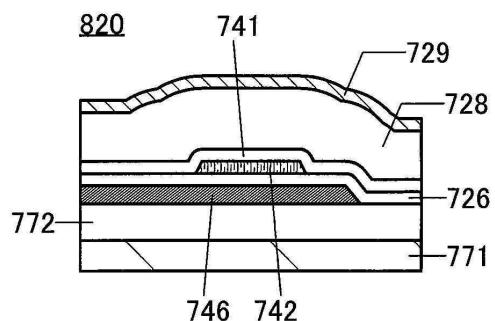

[0270] 도 19의 (B1)은 도 19의 (A1)의 트랜지스터의 구조와는 다른 구조를 가지는 채널 보호 트랜지스터(820)의 채널 길이 방향에서의 단면도이다. 트랜지스터(820)는 트랜지스터(810)와 실질적으로 같은 구조를 가지지만, 절연층(741)이 반도체층(742)의 단부를 덮는다는 점에서 트랜지스터(810)와 다르다. 반도체층(742)과 중첩되는 절연층(741)의 일부를 선택적으로 제거함으로써 형성된 개구를 통하여 반도체층(742)이 전극(744a)에 전기적으로 접

속되어 있다. 반도체층(742)과 중첩되는 절연층(741)의 일부를 선택적으로 제거함으로써 형성된 다른 개구를 통하여 반도체층(742)이 전극(744b)에 전기적으로 접속되어 있다. 절연층(741)에서 채널 형성 영역과 중첩되는 영역은 채널 보호층으로서 기능할 수 있다.

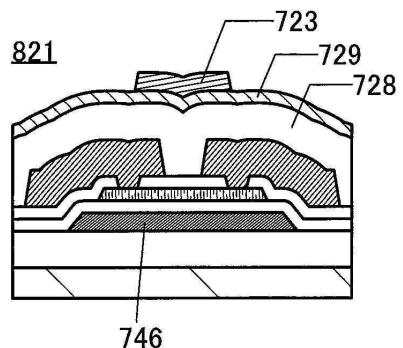

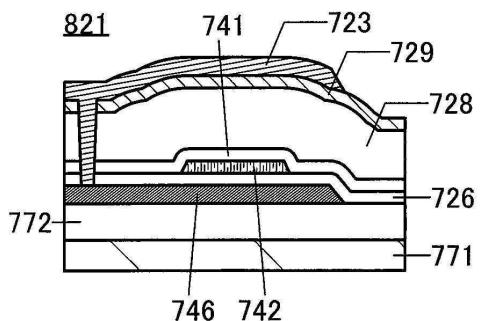

[0271] 도 19의 (B2)에 나타낸 트랜지스터(821)는, 백 게이트 전극으로서 기능할 수 있는 전극(723)이 절연층(729) 위에 제공된다는 점에서 트랜지스터(820)와 다르다.

[0272] 절연층(741)에 의하여, 전극(744a 및 744b)을 형성할 때 반도체층(742)이 노출되는 것을 방지할 수 있다. 그러므로 전극(744a 및 744b)을 형성할 때 반도체층(742)의 두께가 얇아지는 것을 방지할 수 있다.

[0273] 트랜지스터(820 및 821)에서는 트랜지스터(810 및 811)에서보다 전극(744a)과 전극(746) 사이의 길이, 및 전극(744b)과 전극(746) 사이의 길이가 같다. 그러므로 전극(744a)과 전극(746) 사이, 및 전극(744b)과 전극(746) 사이에서 발생하는 기생 용량을 트랜지스터(810 및 811)에서보다 트랜지스터(820 및 821)에서 더 작게 할 수 있다. 본 발명의 일 형태에 따르면, 전기 특성이 양호한 트랜지스터를 제공할 수 있다.

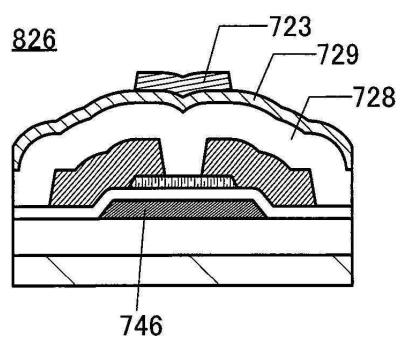

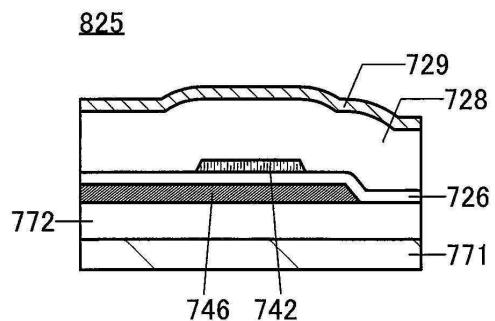

[0274] 도 19의 (C1)은 보텀 게이트 트랜지스터의 일종인 채널 에치 트랜지스터(825)의 채널 길이 방향에서의 단면도이다. 트랜지스터(825)에서는, 절연층(741)을 사용하지 않고 전극(744a 및 744b)을 형성한다. 그러므로 전극(744a 및 744b)을 형성할 때 노출되는 반도체층(742)의 일부가 에칭되는 경우가 있다. 또한 절연층(741)을 제공하지 않기 때문에, 트랜지스터의 생산성을 높일 수 있다.

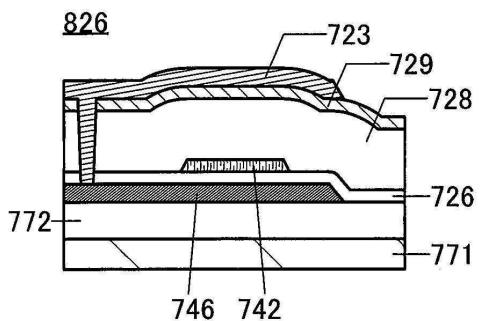

[0275] 도 19의 (C2)에 나타낸 트랜지스터(826)는 백 게이트 전극으로서 기능할 수 있는 전극(723)이 절연층(729) 위에 제공된다는 점에서 트랜지스터(825)와 다르다.

[0276] 도 20의 (A1), (A2), (B1), (B2), (C1), 및 (C2)는 각각 트랜지스터(810, 811, 820, 821, 825, 및 826)의 채널 폭 방향에서의 단면도이다.

[0277] 도 20의 (B2) 및 (C2)에 나타낸 구조 각각에서, 게이트 전극이 백 게이트 전극에 접속되고, 게이트 전극과 백 게이트 전극은 전위가 같다. 또한 반도체층(742)이 게이트 전극과 백 게이트 전극 사이에 끼워진다.

[0278] 게이트 전극 및 백 게이트 전극 각각의 채널 폭 방향에서의 길이는 반도체층(742)의 채널 폭 방향에서의 길이보다 길다. 채널 폭 방향에서, 반도체층(742) 전체는 절연층(726, 741, 728, 및 729)을 개재하여 게이트 전극 및 백 게이트 전극으로 덮인다.

[0279] 이 구조에서, 트랜지스터에 포함되는 반도체층(742)을 게이트 전극 및 백 게이트 전극의 전계에 의하여 둘러쌓 수 있다.

[0280] 트랜지스터(821) 또는 트랜지스터(826)에서와 같이, 채널 형성 영역이 형성되는 반도체층(742)이 게이트 전극 및 백 게이트 전극의 전계에 의하여 둘러싸이는 트랜지스터 디바이스 구조를 S-channel(surrounded channel) 구조라고 할 수 있다.

[0281] S-channel 구조에 의하여, 게이트 전극 및/또는 백 게이트 전극이 채널을 유발시키기 위한 전계를 반도체층(742)에 효과적으로 인가할 수 있어, 트랜지스터는 전류 구동 능력이 향상되고 온 상태 전류 특성이 우수하다. 또한 트랜지스터는 온 상태 전류를 증가시킬 수 있기 때문에 미소화할 수 있다. 또한 S-channel 구조에 의하여 트랜지스터의 기계적 강도를 향상시킬 수 있다.

[0282] [톱 게이트 트랜지스터]

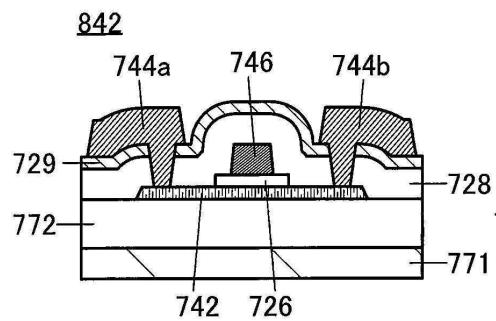

[0283] 도 21의 (A1)에 나타낸 트랜지스터(842)는 톱 게이트 트랜지스터의 일종이다. 전극(744a 및 744b)은 절연층(728 및 729)에 형성된 개구를 통하여 반도체층(742)에 전기적으로 접속된다.

[0284] 전극(746)과 중첩되지 않는 절연층(726)의 일부를 제거하고, 전극(746) 및 잔존한 절연층(726)을 마스크로서 사용하여 불순물(755)을 반도체층(742)에 도입하면, 반도체층(742) 내에 자기 정합(self-aligned)적으로 불순물 영역을 형성할 수 있다. 트랜지스터(842)는 절연층(726)이 전극(746)의 단부를 넘어 연장되는 영역을 포함한다. 반도체층(742)에서 절연층(726)을 통하여 불순물(755)이 도입되는 영역의 불순물 농도는 반도체층(742)에서 절연층(726)을 통하여 않고 불순물(755)이 도입되는 영역의 불순물 농도보다 낮다. 그러므로 반도체층(742)에서 전극(746)과 중첩되지 않는 영역에 LDD(lightly doped drain) 영역이 형성된다.

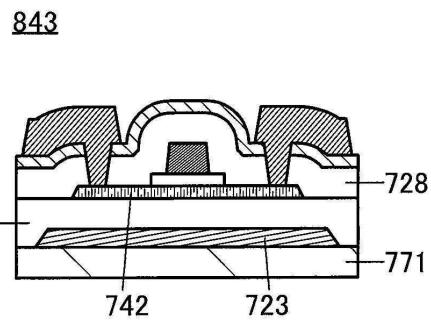

[0285] 도 21의 (A2)에 나타낸 트랜지스터(843)는 전극(723)이 포함된다는 점에서 트랜지스터(842)와 다르다. 트랜지스터(843)는 기판(771) 위에 형성된 전극(723)을 포함한다. 전극(723)은 절연층(772)을 개재하여 반도체층

(742)과 부분적으로 중첩되어 있다. 전극(723)은 백 게이트 전극으로서 기능할 수 있다.

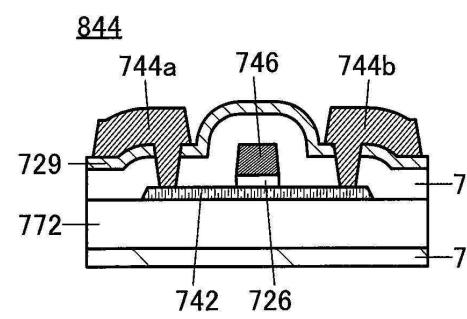

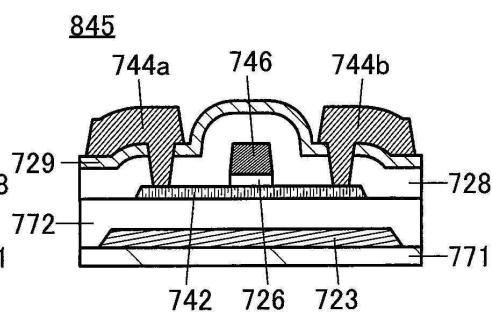

[0286] 도 21의 (B1)에 나타낸 트랜지스터(844) 및 도 21의 (B2)에 나타낸 트랜지스터(845)에서와 같이, 전극(746)과 중첩되지 않는 영역의 절연층(726)을 완전히 제거하여도 좋다. 또는 도 21의 (C1)에 나타낸 트랜지스터(846) 및 도 21의 (C2)에 나타낸 트랜지스터(847)에서와 같이, 절연층(726)을 남겨도 좋다.

[0287] 트랜지스터(842 내지 847)에서는, 전극(746)을 형성한 후에 전극(746)을 마스크로서 사용하여 반도체층(742)에 불순물(755)을 도입함으로써, 반도체층(742)에 불순물 영역을 자기 정합적으로 형성할 수 있다. 본 발명의 일 형태에 따르면, 전기 특성이 양호한 트랜지스터를 제공할 수 있다. 또한 본 발명의 일 형태에 따르면, 집적도가 높은 반도체 장치를 제공할 수 있다.

[0288] 도 22의 (A1), (A2), (B1), (B2), (C1), 및 (C2)는 각각 트랜지스터(842, 843, 844, 845, 846, 및 847)의 채널 폭 방향에서의 단면도이다.

[0289] 트랜지스터(843, 845, 및 847) 각각은 상술한 S-channel 구조를 가지지만, 본 발명의 일 형태는 이에 한정되지 않고, 트랜지스터(843, 845, 및 847)는 반드시 S-channel 구조를 가질 필요는 없다.

[0290] 본 실시형태는 다른 실시형태 등에서 설명하는 구조 중 임의의 것과 적절히 조합하여 실시할 수 있다.

[0291] (실시형태 4)

[0292] 본 발명의 일 형태에 따른 표시 장치를 사용할 수 있는 전자 기기의 예에는, 표시 장치, 퍼스널 컴퓨터, 기록 매체가 제공된 화상 기억 장치 또는 화상 재생 장치, 휴대 전화기, 게임기(휴대용 게임기를 포함함), 휴대 정보 단말기, 전자책 리더, 비디오 카메라 및 디지털 스틸 카메라 등의 카메라, 고글형 디스플레이(헤드 마운티드 디스플레이), 내비게이션 시스템, 음향 재생 장치(예를 들어 카 오디오 플레이어 및 디지털 오디오 플레이어), 복사기, 팩시밀리, 프린터, 프린터 복합기, 현금 자동 입출금기(ATM), 및 자동 판매기가 포함된다. 도 23의 (A) 내지 (F)는 이를 전자 기기의 구체적인 예를 나타낸 것이다.

[0293] 도 23의 (A)는 하우징(961), 셔터 버튼(962), 마이크로폰(963), 스피커(967), 표시부(965), 조작 키(966), 줌 레버(968), 및 렌즈(969) 등을 포함하는 디지털 카메라를 나타낸 것이다. 본 발명의 일 형태의 표시 장치를 표시부(965)에 사용함으로써, 다양한 화상의 표시를 할 수 있다.

[0294] 도 23의 (B)는 대형 표시부(922)를 가지는 디지털 사이니지를 나타낸 것이다. 이 디지털 사이니지는 예를 들어 기동(921)의 측면에 설치할 수 있다. 본 발명의 일 형태의 표시 장치를 표시부(922)에 사용함으로써, 다양한 화상의 표시를 할 수 있다.

[0295] 도 23의 (C)는 하우징(951), 표시부(952), 조작 버튼(953), 외부 접속 포트(954), 스피커(955), 마이크로폰(956), 및 카메라(957) 등을 포함하는 휴대 전화기를 나타낸 것이다. 이 휴대 전화기의 표시부(952)는 터치 센서를 포함한다. 손가락 또는 스타일러스 등으로 표시부(952)를 터치함으로써, 전화 걸기 및 문자 입력 등의 조작을 수행할 수 있다. 하우징(951) 및 표시부(952)는 가요성을 가지고 도면에 나타낸 바와 같이 구부러진 상태로 사용할 수 있다. 본 발명의 일 형태의 표시 장치를 표시부(952)에 사용함으로써, 다양한 화상의 표시를 할 수 있다.

[0296] 도 23의 (D)는 하우징(911), 표시부(912), 스피커(913), 및 카메라(919) 등을 포함하는 휴대 정보 단말기를 나타낸 것이다. 표시부(912)의 터치 패널 기능에 의하여 정보의 입출력을 할 수 있다. 본 발명의 일 형태의 표시 장치를 표시부(912)에 사용함으로써, 다양한 화상의 표시를 할 수 있다.

[0297] 도 23의 (E)는 하우징(971), 표시부(973), 조작 키(974), 스피커(975), 통신용 접속 단자(976), 및 광 센서(977) 등을 포함하는 텔레비전을 나타낸 것이다. 표시부(973)는 입력 조작이 가능한 터치 센서를 포함한다. 본 발명의 일 형태의 표시 장치를 표시부(973)에 사용함으로써, 다양한 화상의 표시를 할 수 있다.

[0298] 도 23의 (F)는 하우징(901), 표시부(902), 표시부(903), 및 센서(904) 등을 포함하는 정보 처리 단말기를 나타낸 것이다. 표시부(902 및 903)는 하나의 표시 패널을 사용하여 형성되고 가요성을 가진다. 하우징(901)도 가요성을 가지고, 도면에 나타낸 바와 같이 구부러진 상태로 사용할 수 있으며, 태블릿 단말기와 같이 평판 형상으로 사용할 수 있다. 센서(904)는 하우징(901)의 형상을 감지할 수 있고, 예를 들어 하우징(901)이 구부러진 경우에 표시부(902 및 903)의 표시를 전환할 수 있다. 본 발명의 일 형태의 표시 장치를 표시부(902 및 903)에 사용함으로써, 다양한 화상의 표시를 할 수 있다.

[0299] 본 실시형태는 다른 실시형태 및 실시예 등에서 설명하는 구조 중 임의의 것과 적절히 조합하여 실시할 수

있다.

### 부호의 설명

[0300]

10: 화소, 10B: 부화소, 10R: 부화소, 11: 화소, 11B: 부화소, 11G: 부화소, 11R: 부화소, 12: 화소 어레이, 13: 행 드라이버, 14: 열 드라이버, 15: 회로, 16: 선택 회로, 20: 시프트 레지스터, 21: 버퍼 회로, 22: 시프트 레지스터, 23: 버퍼 회로, 24: 센서, 25: 회로, 26B: 전극, 26G: 전극, 26R: 전극, 101: 트랜지스터, 102: 트랜지스터, 102a: 트랜지스터, 102b: 트랜지스터, 103: 트랜지스터, 104: 용량 소자, 110: 회로 블록, 111: 트랜지스터, 112: 트랜지스터, 113: 용량 소자, 114: EL 소자, 115: 트랜지스터, 116: 용량 소자, 117: 액정 소자, 118: 트랜지스터, 119: 트랜지스터, 120: 회로, 121: 배선, 122: 배선, 123: 배선, 126: 배선, 128: 배선, 129: 배선, 130: 배선, 131: 배선, 132: 배선, 133: 배선, 134: 배선, 215: 표시부, 221a: 주사선 구동 회로, 231a: 신호선 구동 회로, 232a: 신호선 구동 회로, 241a: 공통선 구동 회로, 723: 전극, 726: 절연층, 728: 절연층, 729: 절연층, 741: 절연층, 742: 반도체층, 744a: 전극, 744b: 전극, 746: 전극, 755: 불순물, 771: 기판, 772: 절연층, 810: 트랜지스터, 811: 트랜지스터, 820: 트랜지스터, 821: 트랜지스터, 825: 트랜지스터, 826: 트랜지스터, 842: 트랜지스터, 843: 트랜지스터, 844: 트랜지스터, 845: 트랜지스터, 846: 트랜지스터, 847: 트랜지스터, 901: 하우징, 902: 표시부, 903: 표시부, 904: 센서, 911: 하우징, 912: 표시부, 913: 스피커, 919: 카메라, 921: 기동, 922: 표시부, 951: 하우징, 952: 표시부, 953: 조작 버튼, 954: 외부 접속 포트, 955: 스피커, 956: 마이크로폰, 957: 카메라, 961: 하우징, 962: 셔터 버튼, 963: 마이크로폰, 965: 표시부, 966: 조작 키, 967: 스피커, 968: 줌 레버, 969: 렌즈, 971: 하우징, 973: 표시부, 974: 조작 키, 975: 스피커, 976: 통신용 접속 단자, 977: 광 센서, 4001: 기판, 4005: 실재, 4006: 기판, 4008: 액정층, 4010: 트랜지스터, 4011: 트랜지스터, 4013: 액정 소자, 4014: 배선, 4015: 전극, 4017: 전극, 4018: FPC(flexible printed circuit), 4019: 이방성 도전층, 4020: 용량 소자, 4021: 전극, 4030: 전극층, 4031: 전극층, 4032: 절연층, 4033: 절연층, 4035: 스페이서, 4041: 인쇄 회로 기판, 4042: 접착 회로, 4102: 절연층, 4103: 절연층, 4104: 절연층, 4110: 절연층, 4111: 절연층, 4112: 절연층, 4131: 쟁색층, 4132: 차광 층, 4133: 절연층, 4200: 입력 장치, 4210: 터치 패널, 4227: 전극, 4228: 전극, 4237: 배선, 4238: 배선, 4239: 배선, 4263: 기판, 4272b: FPC, 4273b: IC, 4510: 격벽, 4511: 발광층, 4513: 발광 소자, 4514: 충전재.

본 출원은 2017년 11월 23일에 일본 특허청에 출원된 일련 번호 2017-225270의 일본 특허 출원에 기초하고, 본 명세서에 그 전문이 참조로 통합된다.

### 도면

#### 도면1

## 도면2

(A) (B)

## 도면3

(A)

(B)

## 도면4

(A)

(B)

(C)

## 도면5

(A)

(B)

(C)

## 도면6

(A)

(B)

(C)

도면7

## 도면8

(A1)

(A2)

(B1)

(B2)

## 도면9

(A)

## 도면10

(A)

(B)

## 도면11

## 도면12

(A)

(B)

(C)

## 도면13

(A)

(B)

(C)

(D)

## 도면14

(A)

(B)

(C)

(D)

도면 15

## 도면16

(A)

(B)

(C)

도면17

(A)

(B)

도면18

## 도면19

(A1)

(A2)

(B1)

(B2)

(C1)

(C2)

## 도면20

(A1)

(A2)

(B1)

(B2)

(C1)

(C2)

## 도면21

(A1)

(A2)

(B1)

(B2)

(C1)

(C2)

## 도면22

## 도면23