(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2013-0135404

(43) 공개일자 2013년12월10일

- (51) 국제특허분류(Int. Cl.)

*H01L 21/302* (2006.01) *H01L 21/20* (2006.01)

- (21) 출원번호 10-2013-7031794(분할)

- (22) 출원일자(국제) 2008년07월08일

심사청구일자 空

- (62) 원출원 특허 10-2011-7022788

원출원일자(국제) 2008년07월08일

심사청구일자 2011년09월28일

- (85) 번역문제출일자 2013년11월29일

- (86) 국제출원번호 PCT/US2008/069430

- (87) 국제공개번호 WO 2009/014894

국제공개일자 2009년01월29일

- (30) 우선권주장

12/146,177 2008년06월25일 미국(US)

60/952,230 2007년07월26일 미국(US)

- (71) 출원인

애플라이드 머티어리얼스, 인코포레이티드

미국 95054 캘리포니아 산타 클라라 바우어스 애브뉴 3050

- (72) 별명자

산체즈, 에를 안토니오 씨.

미국 95377 캘리포니아 트레이시 질 드라이브 324

스웬버그, 요하네스

미국 95032 캘리포니아 로스 가토스 메리 웨이 128

(뒷면에 계속)

- (74) 대리인

특허법인 남앤드남

전체 청구항 수 : 총 9 항

(54) 발명의 명칭 기판 표면을 세정하기 위한 방법 및 장치

**(57) 요 약**

본 발명은 반도체 기판 상에 깨끗하고 손상 없는 표면을 형성하기 위한 장치 및 방법을 일반적으로 제공한다. 본 발명의 일 실시예는 위에 에피택셜층을 형성하기 이전에 플라즈마 세정 프로세스로 기판의 표면을 노출시키도록 이루어진 세정 챔버를 포함한 시스템을 제공한다. 일 실시예에서, 기판 상에서 세정 프로세스를 수행하기 이전에 세정 챔버의 내부면 상에 게터링 물질을 증착시킴에 의해 세정 챔버에서 처리된 기판의 오염을 감소시키는 방법이 이용된다. 일 실시예에서, 그 위에 위치한 에피택셜을 가질 수 있는 기판 상에 깨끗한 표면을 생성하거나 또는 노출시키도록 세정 챔버의 기판 상에서 산화 및 에칭 단계가 반복적으로 수행된다. 일 실시예에서, 낮은 에너지 플라즈마가 세정 단계 동안 이용된다.

**대 표 도** - 도3

(72) 발명자

칼슨, 레이비드 케이.

미국 95132 캘리포니아 샌어제이 클라이터 웨이

4054

도허티, 로이신 엘.

미국 94110 캘리포니아 샌프란시스코 윈필드 스트

리트 15

---

## 특허청구의 범위

### 청구항 1

프로세싱 챔버의 프로세싱 영역에 기판을 위치시키는 단계;

상기 프로세싱 챔버에 배치된 상기 기판의 표면을 산소 함유 가스에 노출시켜서 상기 표면 상에 제 1 산소 함유층을 형성하는 단계;

상기 제 1 산소 함유층의 적어도 일부분을 제거시켜서 상기 기판의 표면의 적어도 일부분을 노출시키는 단계;

및

상기 기판의 표면을 산소 함유 가스에 노출시켜서 상기 표면 상에 제 2 산소 함유층을 형성하는 단계를 포함하는

반도체 기판을 프로세싱하기 위한 방법.

### 청구항 2

제 1 항에 있어서,

상기 제 1 산소 함유층을 형성하는 단계, 상기 제 1 산소 함유층의 적어도 일부분을 제거하는 단계 및 상기 제 2 산소 함유층을 형성하는 단계가 모두 상기 프로세싱 챔버에서 수행되는

반도체 기판을 프로세싱하기 위한 방법.

### 청구항 3

제 1 항 또는 제 2 항에 있어서,

상기 제 2 산소 함유층의 적어도 일부분을 제거하여서 상기 기판의 표면을 노출시키는 단계; 및

상기 기판의 노출된 표면의 적어도 일부분 상에 에피택셜층을 증착시키는 단계를 더 포함하는

반도체 기판을 프로세싱하기 위한 방법.

### 청구항 4

제 3 항에 있어서,

상기 제 1 산소 함유층을 형성하는 단계, 상기 제 1 산소 함유층의 적어도 일부분을 제거하는 단계, 상기 제 2 산소 함유층을 형성하는 단계 및 상기 제 2 산소 함유층의 적어도 일부분을 제거하는 단계가 모두 상기 프로세싱 챔버로부터 상기 기판을 제거하기 전에 수행되는

반도체 기판을 프로세싱하기 위한 방법.

### 청구항 5

제 1 항 내지 제 4 항 중 어느 한 항에 있어서,

상기 프로세싱 챔버의 프로세싱 영역에 상기 기판을 위치시키기 전에 상기 프로세싱 영역에 배치된 챔버 구성요소의 표면 상에 게터링층을 형성하는 단계를 더 포함하는

반도체 기판을 프로세싱하기 위한 방법.

#### 청구항 6

제 5 항에 있어서,

상기 게터링층이 실리콘 및 게르마늄으로 구성된 그룹으로부터 선택된 물질을 포함하는

반도체 기판을 프로세싱하기 위한 방법.

#### 청구항 7

제 1 항 내지 제 6 항 중 어느 한 항에 있어서,

상기 산소 함유 가스가 2원자 산소( $O_2$ )를 포함하는

반도체 기판을 프로세싱하기 위한 방법.

#### 청구항 8

제 1 항 내지 제 6 항 중 어느 한 항에 있어서,

상기 산소 함유 가스가 오존( $O_3$ )을 포함하는

반도체 기판을 프로세싱하기 위한 방법.

#### 청구항 9

제 1 항 내지 제 6 항 중 어느 한 항에 있어서,

상기 제 1 산소 함유층을 형성하는 단계 또는 상기 제 2 산소 함유층을 형성하는 단계가 상기 기판을 자외선(UV) 광에 노출시키는 단계를 포함하는

반도체 기판을 프로세싱하기 위한 방법.

### 명세서

#### 기술분야

[0001]

본 발명의 실시예들은 일반적으로 반도체 기판을 프로세싱하기 위한 방법 및 장치에 관한 것이다. 더욱 구체적으로, 본 발명의 실시예들은 실리콘 기판의 표면을 세정하기 위한 방법 및 장치에 관한 것이다.

#### 배경기술

[0002]

집적 회로는 실리콘 및 다른 반도체 기판 내에 그리고 기판 상에 형성된다. 단결정 실리콘의 경우에, 기판은 용해된 실리콘 배스(bath)로부터 잉곳(ingot)을 성장시키고 이후 고형화된 잉곳을 다수의 웨이퍼로 소우잉(sawing)함에 의해 만들어진다. 에피택셜 실리콘층(epitaxial silicon layer)은 이후 단결정 실리콘 웨이퍼 상에 형성될 수 있고, 이에 의해 도핑되거나 또는 도핑되지 아니할 수 있는 결합 없는 실리콘층을 형성한다. 트랜ジ스터와 같은 반도체 소자는 에피택셜 실리콘층으로 제조된다. 형성된 에피택셜 실리콘층의 전기적 성질은 일반적으로 단결정 실리콘 기판의 성질보다 뛰어날 것이다.

[0003]

단결정 실리콘의 표면 및 에피택셜 실리콘층의 표면은 일반적인 대기 환경에 노출될 때 오염에 민감하다. 따라서, 기판은 에피택셜층의 형성과 같은 다양한 반도체 프로세스를 수행하기 이전에 실리콘 웨이퍼 표면 상에서

발견된 불순물 및 입자를 제거하도록 세정될 필요가 있다.

[0004] 종래에는 반도체 기판은 습식 세정 프로세스 또는 종래의 플라즈마 세정 프로세스를 이용하여 세정되었다. 그러나, 습식 세정 프로세스는 "대기열 시간(queue time)" 문제를 갖고, 이는 로트 내의(in a lot) 서로 상이한 웨이퍼들에 대한 아이들 시간(idle times)을 변경시킴에 의해 웨이퍼 로트에서 웨이퍼마다 차이를 야기할 수 있다. 종래의 원격 또는 인시츄 플라즈마 세정 프로세스에서는 세정 프로세스 동안 또는 가스상에서 형성된 원하지 않는 종들의 생성에 의한 챔버에서 처리되는 기판 및 챔버의 오염물질에 의해, 매우 많은 문제가 발생될 수 있다. 이러한 원하지 않는 종은 원하는 종의 세정 작용을 제한하거나 또는 세정 프로세스에 다른 복잡함을 유도한다.

[0005] 따라서, 특히 에피택셜 증착 프로세스를 수행하기 이전에 기판 표면을 세정하기 위한, 기판 표면 세정 방법 및 장치에 대한 요구가 있다.

### 발명의 내용

[0006] 본 발명은 기판을 프로세싱하기 위한 장치를 일반적으로 제공하고, 이 장치는: 프로세싱 영역을 형성하는 하나 이상의 벽을 포함한 낮은 에너지 세정 챔버; 프로세싱 영역으로 전자기 에너지를 전달하도록 이루어진 플라즈마 생성 소스; 프로세싱 영역으로 실리콘 함유 가스를 전달하도록 이루어진 제 1 가스 소스; 프로세싱 영역으로 산화 가스를 전달하도록 이루어진 제 2 가스 소스; 에피택셜층 증착 챔버 그리고 낮은 에너지 세정 챔버 내의 제 1 위치와 에피택셜층 증착 챔버의 제 1 위치 사이에서 기판을 전달하도록 이루어진 로봇; 및 전달 영역을 에워싸는 하나 이상의 벽을 가진 전달 챔버;를 포함한다.

[0007] 또한, 본 발명의 실시예는 프로세싱 영역을 형성하는 하나 이상의 벽; 프로세싱 영역으로 전자기 에너지를 전달하도록 이루어진 플라즈마 생성 소스; 프로세싱 영역 내에 위치한 월드로서, 상기 월드가 실리콘, 이트륨, 이트륨 산화물, 게르마늄, 붕소, 인 및 실리콘 게르마늄 화합물로 이루어진 그룹으로부터 선택된 물질로 제조되는, 월드; 기판 지지면 및 RF 전력 서플라이에 의해 바이어스되도록 이루어진 바이어싱 전극을 가지는 기판 지지대; 프로세싱 영역으로 산화 가스를 전달하도록 이루어진 제 1 가스 소스; 프로세싱 영역으로 비활성 가스를 전달하도록 이루어진 제 2 가스 소스; 및 프로세싱 영역으로 실리콘 함유 가스를 전달하도록 이루어진 제 3 가스 소스를 포함하는, 낮은 에너지 세정 프로세스를 수행하기 위한 장치를 제공한다.

[0008] 또한, 본 발명의 실시예는 에피택셜층을 형성하는 방법을 제공하고, 이러한 방법은 세정 챔버의 프로세싱 영역에 위치한 챔버 구성요소의 표면 상에 게터링층을 증착시키는 단계, 세정 챔버의 프로세싱 영역 내에 위치한 기판 지지대 상에 기판을 위치시키는 단계, 기판 지지대 상에 위치한 기판의 표면을 산화시키는 단계, 기판 지지대 상에 위치한 기판의 산화 표면의 적어도 일부분을 제거하는 단계, 수소 함유 가스에 표면을 노출시킴에 의해 산화 표면의 적어도 일부분을 제거한 이후 기판의 표면을 패시베이트하는 단계, 세정 챔버로부터 에피택셜층 증착 챔버로 기판을 전달하는 단계, 및 패시베이트된 표면의 적어도 일부분 상에 에피택셜층을 증착시키는 단계를 포함한다.

[0009] 또한, 본 발명의 일 실시예는 낮은 에너지 세정 프로세스를 수행하기 위한 장치를 제공하고, 그러한 장치는: 프로세싱 영역을 형성하는 하나 이상의 벽으로서, 상기 하나 이상의 벽 중 적어도 하나는 하나 이상의 벽의 적어도 하나의 온도를 제어하도록 열교환 소자를 포함하는, 하나 이상의 벽; 프로세싱 영역으로 전자기 에너지를 전달하도록 이루어진 플라즈마 생성 소스; 프로세싱 영역 내에 위치한 월드; 기판 지지면, RF 전력 서플라이에 의해 바이어스 되도록 이루어진 바이어싱 전극 및 기판 지지면의 온도를 제어하기 위한 기판 지지 열교환 소자를 갖는 기판 지지대; 프로세싱 영역으로 산화 가스를 전달하도록 이루어진 제 1 가스 소스; 및 프로세싱 영역으로 에칭 가스를 전달하도록 이루어진 제 2 가스 소스를 포함한다.

### 도면의 간단한 설명

[0010] 본 발명의 상기 언급된 특징들을 더욱 자세하게 이해할 수 있도록, 상기에서 간략히 요약된 본 발명의 보다 상세한 설명은 실시예를 참고로 하여 설명될 수 있고, 이 중 일부는 첨부된 도면에서 도시된다. 그러나, 첨부된 도면들은 본 발명의 오직 전형적인 실시예들 만을 도시하는 것이고 따라서 그 범위를 제한하려는 의도는 아니며 본 발명은 다른 동등하게 효과적인 실시예를 허용할 수 있음을 주의해야 한다.

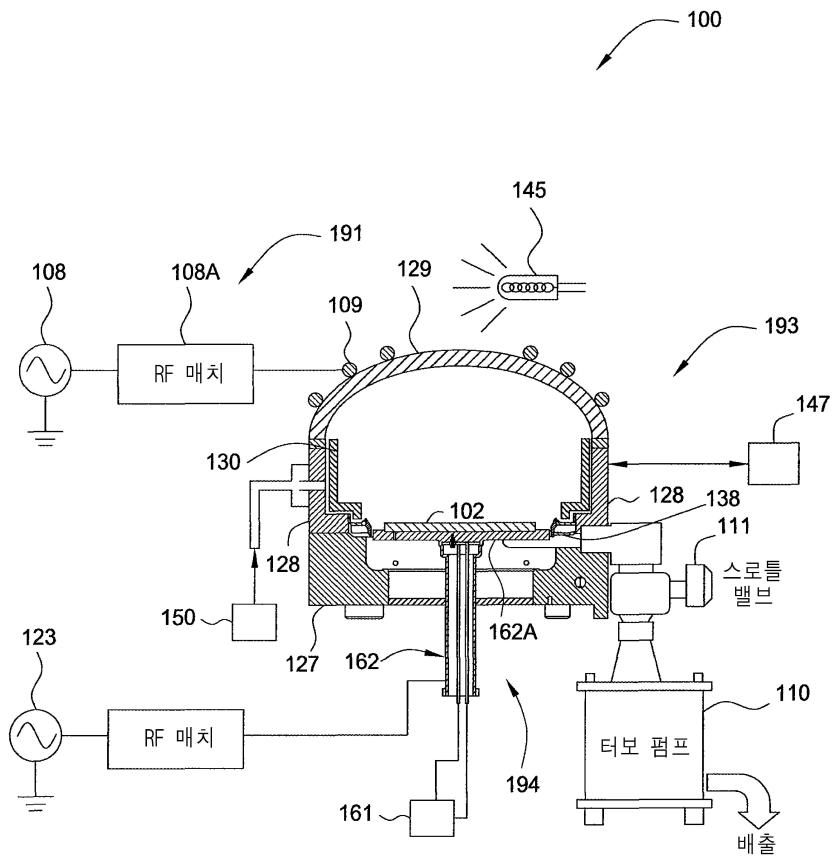

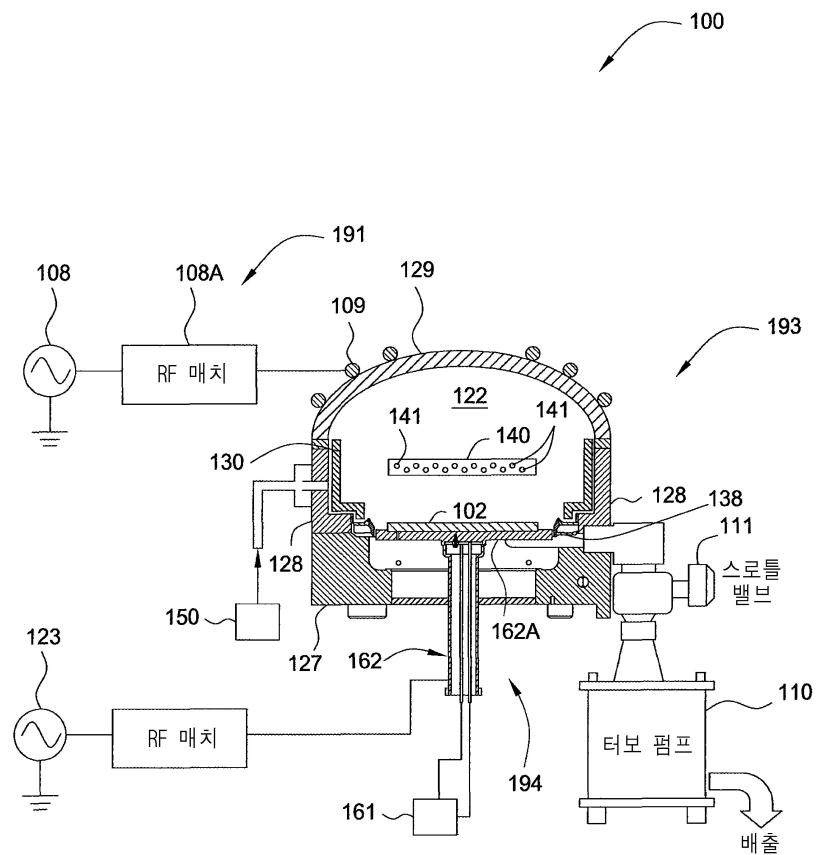

도 1은 본 발명의 일 실시예에 따른 세정 챔버의 측단면도를 개략적으로 도시한다.

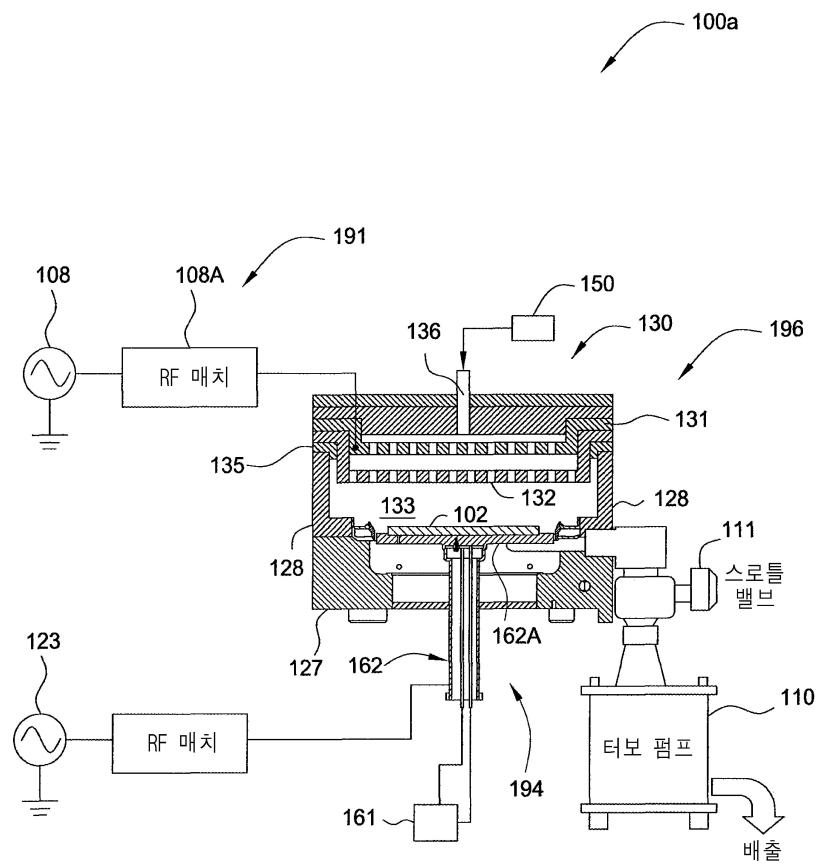

도 2a는 본 발명의 다른 실시예에 따른 세정 챔버의 측단면도를 개략적으로 도시한다.

도 2b는 본 발명의 일 실시예에 따른 세정 챔버의 측단면도를 개략적으로 도시한다.

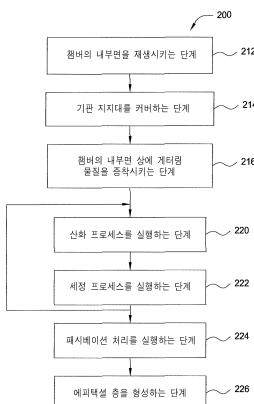

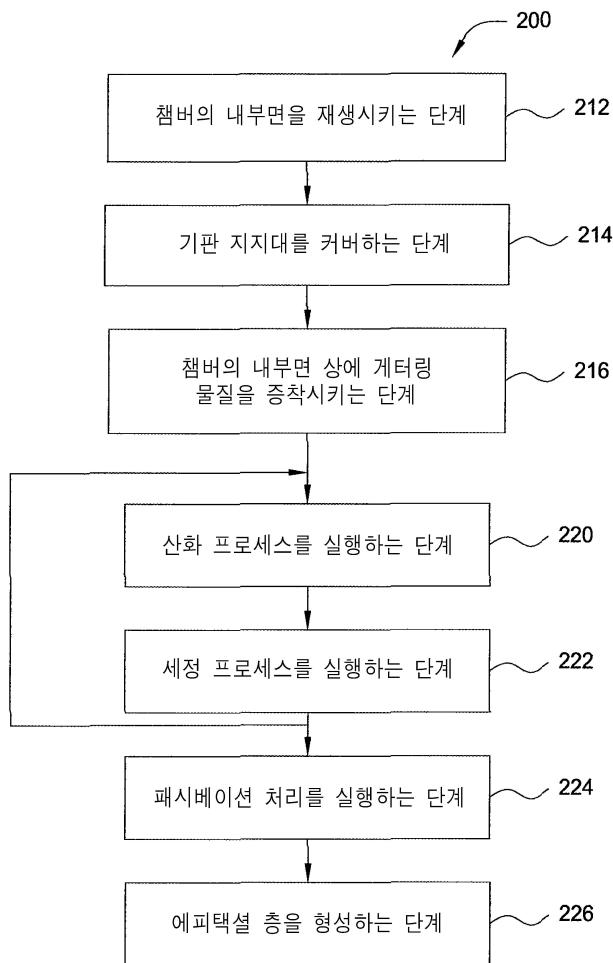

도 3은 본 발명의 일 실시예에 따른 반도체 기판을 세정하기 위한 방법의 순서도를 도시한다.

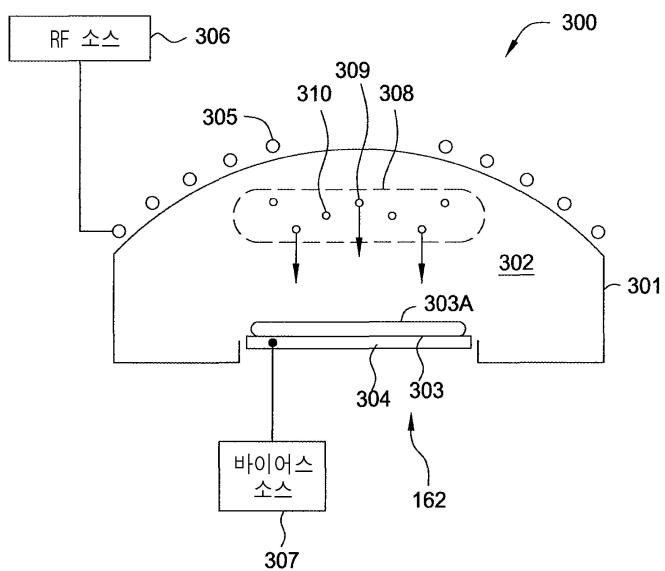

도 4는 세정 챔버의 부분적 측단면도를 개략적으로 도시한다.

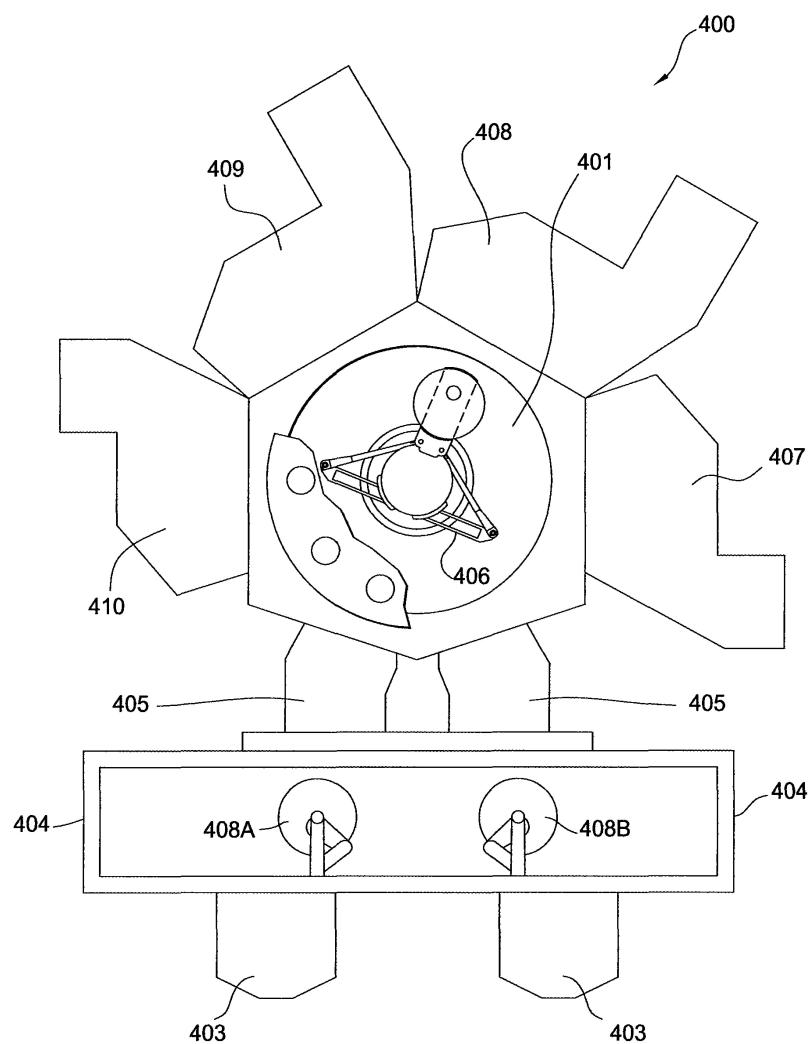

도 5는 본 발명의 일 실시예에 따른 클러스터 툴의 평면도를 개략적으로 도시한다.

이해를 돋기 위해, 동일한 도면 부호가 가능한 도면에서 공통적인 동일한 요소들을 지칭하도록 이용되었다. 일 실시예에서 개시된 요소들은 특별한 언급이 없이 다른 실시예 상에서 이롭게 이용될 수 있음을 고려해야 한다.

### 발명을 실시하기 위한 구체적인 내용

[0011]

본 발명은 반도체 기판(또는 웨이퍼) 상에 깨끗하고 손상 없는 표면을 형성하기 위한 장치 및 방법을 일반적으로 제공한다. 본 발명의 일 실시예에는 에피택셜층을 위에 형성하기 이전에 플라즈마 세정 프로세스에 기판 표면을 노출시키도록 이루어진 세정 챔버를 포함한 시스템을 제공한다. 일 실시예에서, 기판 상의 세정 프로세스를 수행하기 이전에 세정 챔버의 내부면 상에 게터링 물질(gettering material)을 증착함에 의해 세정 챔버에서 프로세스된 기판의 오염을 감소시키는 방법이 이용된다. 게터링 물질은 세정 챔버에서 발견된 오염 물질을 포획하는 경향이 있을 것이고, 따라서 프로세스된 기판이 깨끗한 것을 보장하며 챔버에서 프로세스되는 추후의 기판들이 동일한 원하는 세정 결과를 가질 것이라는 것을 보장한다. 일 실시예에서, 산화 및 에칭 단계들은 세정 챔버에서 기판 상에서 반복적으로 수행되고, 이에 의해 기판 상에 깨끗한 표면을 만들거나 또는 노출시키며, 이러한 깨끗한 표면은 이후 그 위에 위치된 에피택셜 필름을 가질 수 있다. 일 실시예에서, 낮은 에너지 플라즈마가 에칭 단계 동안 이용된다. 플라즈마의 낮은 에너지는 기판 RF 바이어스 전력을 낮추는 단계, 기판을 가로질러 가해진 바이어스 포텐셜을 조절하는 단계, 프로세싱 챔버에서 플라즈마를 생성하는데 이용된 RF 전력을 펠스하는 단계, 기판 RF 바이어스 전력을 펠스하는 단계, 가벼운 원자핵종(light atomic species)을 포함한 플라즈마를 형성하는 단계, 플라즈마를 한정하도록 플라즈마 쉴드를 이용하는 단계, 플라즈마에 대해 기판의 프로세싱 위치를 조절하는 단계, 및/또는 이의 조합에 의해 이루어질 수 있다.

[0012]

### 세정 챔버

[0013]

도 1은 본 발명의 일 실시예에 따른 세정 챔버(100)의 측단면도를 개략적으로 도시한다. 세정 챔버(100)는 프로세싱 영역(122)에서 기판(102)을 세정할 수 있는 유도적으로 커플링된 플라즈마 프로세싱 챔버이다. 일 실시예에서, 세정 챔버(100)는 유도적으로 커플링된 라디오 주파수(RF) 소스를 이용하는 산타 클라라의 어플라이드 머티어리얼스사로부터 구입 가능한 변경된 디커플된 플라즈마 질화(Decoupled Plasma Nitridation; DPN) 챔버이다. DPN 챔버의 상세한 설명은 여기서 설명된 프로세스들 중 하나 이상을 수행하도록 이루어질 수 있고, 이는 여기서 전체가 참조로서 통합된 "기판을 프로세싱하기 위한 플라즈마 방법 및 장치"라는 명칭의 미국 특허 제 6,660,659호 및 "플라즈마 질화된 게이트 유전체층에서 질소 프로파일을 향상시키기 위한 방법"이라는 명칭의 미국 특허 제 7,122,454호에서 찾을 수 있다.

[0014]

세정 챔버(100)는 일반적으로 RF 소스 어셈블리(191), 프로세스 챔버 어셈블리(193) 및 기판 지지 어셈블리(194)를 포함한다. 프로세스 챔버 어셈블리(193)는 프로세싱 영역(122)에서 진공을 형성하는데 이용되는 다수의 구성요소를 일반적으로 포함하고, 이에 의해 플라즈마 프로세스는 그 안에서 수행될 수 있다. 일반적으로 프로세스 챔버 어셈블리(193)는 프로세싱 영역(122)을 밀봉 가능하게 예워싸는 챔버 베이스(127), 챔버 벽(128) 및 챔버 뚜껑(129)을 포함한다. 프로세싱 영역(122)은 챔버 벽(128) 및/또는 챔버 베이스(127)를 통해 프로세싱 영역(122)에 연결된 진공 펌프(110)를 이용함에 의해 원하는 진공 압력으로 비워질 수 있다. 일반적으로, 챔버 벽(128) 및 챔버 베이스(127)는 알루미늄과 같은 금속 또는 다른 적절한 물질로 형성될 수 있다.

[0015]

일 실시예에서, 챔버 벽(128) 및 챔버 뚜껑(129)은 온도 제어될 수 있다. 종래의 방법들 및/또는 열교환 소자들은 다양한 챔버 구성요소를 가열하고 냉각하는데 이용될 수 있다. 예를 들면, 챔버 벽(128) 및 챔버 뚜껑(129)은 프로세스 챔버 어셈블리(193)의 외부에 위치한 램프 배열과 같은 히터(미도시)에 의해 가열될 수 있다. 다른 예에서, 냉각 가스들은 프로세스 챔버 어셈블리(193) 외부에서 순환될 수 있고, 이에 의해 챔버 벽(128) 및 챔버 뚜껑(129)을 냉각시킨다. 다른 예에서, 챔버 벽(128) 및 챔버 뚜껑(129)에 내장될(embedded) 수 있는

가열 및/또는 냉각 도관은 온도를 제어하기 위해 유체 가열기/냉각기 소자에 연결될 수 있다. 프로세스 챔버 어셈블리(193)의 온도를 제어하는데 이용될 수 있는 방법 및 장치는 여기서 참조로서 통합된 "프로세싱 동안 반응 챔버의 벽의 온도를 제어하기 위한 방법"이라는 명칭의 미국 특허 제 6,083,323호에서 찾을 수 있다.

[0016] 일 실시예에서, RF 소스 어셈블리(191)는 코일(109)에 연결된 RF 매치 회로(108A) 및 RF 생성기(RF generator; 108)를 일반적으로 포함한 유도성 유형의 RF 소스이다. 코일(109)은 챔버 뚜껑(129)에 인접하여 위치한다. 일 실시예에서, RF 생성기(108)는 약 400kHz 내지 약 60MHz의 주파수에서 약 0 내지 약 3000W에서 작동할 수 있다. 일례에서, RF 생성기(108)는 13.56MHz의 주파수에서 작동한다. 일 실시예에서, RF 생성기(108)는 코일(109)에 RF 에너지의 펄스를 제공할 수 있고, 이에 의해 감소된 에너지 레벨 및/또는 플라즈마 밀도를 갖는 플라즈마를 생성한다.

[0017] 챔버 뚜껑(129)은 일반적으로 유도성 RF 소스 어셈블리(191)로부터 전달된 RF 에너지가 프로세싱 영역(122)에서 플라즈마를 형성하는 것을 가능하게 하도록 이루어진 유전체 구성요소(예를 들어 석영, 세라믹 물질(예를 들어 알루미나))이다.

[0018] 일 실시예에서, 프로세스 챔버 어셈블리(193)는 또한, 챔버 베이스(127), 챔버 벽(128) 및 챔버 뚜껑(129)에 의해 형성된 프로세싱 영역(122)으로 하나 이상의 프로세스 가스를 전달하도록 이루어진 가스 전달 시스템(150)을 포함한다. 일 실시예에서, 프로세싱 영역(122)은 챔버에서 수행된 준비 프로세스 및 생성된 플라즈마로부터 챔버 벽(128) 및/또는 챔버 뚜껑(129)을 보호하는 것으로 의도된 하나 이상의 쉴드(shield; 130)로 둘러싸인다. 일 실시예에서, 가스 전달 시스템(150)은 높은 농도 오존( $O_3$ )을 함유한 가스의 흐름을 생성하도록 구성된 오존 발생기(ozonator)를 포함한다. 일 실시예에서, 가스 전달 시스템은 실리콘 함유 가스(예를 들어 실란), 수소 함유 가스(예를 들어  $H_2$ ), 게르마늄 함유 가스, 염소 함유 가스, 산소 함유 가스(예를 들어  $O_2$ ), 트리플루오르화 질소( $NF_3$ ), 붕소 함유 가스(예를 들어 디보란), 및/또는 인 함유 가스(예를 들어 포스핀)와 같은 반응성 가스를 전달하도록 이루어지고, 이러한 반응성 가스들의 소수만 열거하였다. 일 실시예에서, 가스 전달 시스템은 아르곤(Ar), 헬륨(He), 크립톤(Kr) 및/또는 질소( $N_2$ )와 같은 비활성 가스를 전달하도록 이루어진다. 프로세싱 영역(122)에서의 압력은 진공 펌프(110)의 펌프 속도 및 가스 전달 시스템(150)에 의해 전달된 가스의 유량(flow rate)을 조절함에 의해 제어될 수 있다. 스로틀 밸브(throttle valve; 111)는 진공 펌프(110)의 펌프 속도를 조절하는데 이용될 수 있다.

[0019] 기판 지지 어셈블리(194)는 기판 지지 부재(162A)를 포함한 기판 지지대(162)를 일반적으로 포함한다. 기판 지지 부재(162A)는 프로세싱 동안 기판을 능동적(actively)으로 지지하는데 이용될 수 있는 종래의 정전기적 쳐크 일 수 있거나 또는 간단한 기판 지지대를 포함할 수 있다. 온도 제어기(161)는 일반적으로 종래의 열 교환기(미도시)에 커플링된 내장된 저항성 가열 요소 또는 유체 냉각 채널과 같은 열교환 소자 및 온도 제어기(161)를 이용하여 원하는 온도로 기판 지지 부재(162A)를 가열 및/또는 냉각시키도록 이루어진다. 일 실시예에서, 온도 제어기(161)는 약 20°C 내지 약 800°C의 온도로 기판 지지 부재(162A) 상에 위치한 기판(102)을 작동시키고 가열하도록 이루어진다.

[0020] 프로세싱 동안, 기판 지지대(162)는 RF 생성기(123)에 연결될 수 있고, 이에 의해 RF 바이어스가 기판 지지대(162)의 일부분 내에 배치된 전도성 요소에 가해질 수 있으며 이로써 프로세싱 영역(122)에 형성된 플라즈마 내에 존재하는 이온을 기판(102)의 표면으로 끌어당긴다. 일 실시예에서, RF 생성기(123)는 기판 세정 프로세스의 하나 이상의 부분 동안 기판 상의 캐소딕 또는 애노딕 바이어스를 생성하도록 이루어지고, 이에 의해 기판 표면의 이온 및 플라즈마 충돌의 양을 제어하고 및/또는 기판 상에 존속하는 전하를 조절한다. 일 실시예에서, 기판 지지 부재(162A)는 접지되거나 또는 DC(직류) 바이어스된다. 다른 실시예에서, 기판 지지 부재(162A) 및 기판은 플라즈마 프로세스 동안 전기적으로 플로팅(floating) 상태이고 이에 의해 기판(102)의 이온 충돌 손상을 최소화한다.

[0021] 도 1을 참고하면, RF 생성기(108)로부터 프로세싱 영역(122)으로 RF 에너지를 전달함에 의해 프로세싱 영역(122)의 가스 원자들을 이온화시킨다. 기판이 세정 프로세스 동안 프로세싱 영역(122)에서 생성된 플라즈마에 노출될 때, 기판(102)의 표면을 때리는 플라즈마의 이온화된 원자들에 의해 전달된 에너지에 의해 기판(102) 표면 상의 오염 물질이 표면으로부터 제거(desorb)되거나 또는 떨어져나갈 수 있다. 일 실시예에서, 플라즈마 내의 이온화된 가스 원자들은 기판 지지 부재(162A)를 통해 기판(102)에 가해진 바이어스에 의해 기판(102)의 표면으로 당겨질 수 있다.

[0022] 일 실시예에서, RF 생성기(108)에 의해 코일(109)로 전달된 RF 전력은 낮은 에너지 플라즈마를 형성하도록 펄스

된다. 일 실시예에서, 펠스된 플라즈마 프로세스는 일반적으로 RF 생성기(108)에 의한 코일(109)을 이용하여 시간의 함수로서 프로세싱 영역(122)으로 전달되는 일련의 순차적 에너지 펠스이다. 프로세싱 영역(122)에서 형성된 플라즈마를 여기시키기 위해 유도성 RF 소스를 펠스하는 것은 종래의 플라즈마 프로세싱 챔버에서 공통적으로 형성되는 플라즈마 포텐셜에 의해 기판 표면으로 야기되는 손상의 양을 최소화할 것이다. 세정 프로세스에 의해 기판 표면에 야기된 어떠한 손상을 최소화하거나 또는 제거하는데에 대한 요구는 에피택셜층을 그 위에 형성하기 위해 준비되는 단결정 기판에 있어서 특히 중요하다. 기판의 표면에 대한 손상은 형성된 에피택셜층에서의 결함 및 응력의 수를 줄이기 위해 최소화될 필요가 있다. 따라서, 유도성 RF 소스 전력을 펠스하는 것은 낮은 전자 온도 및 낮은 이온 에너지 플라즈마를 생성하고 유지시키는 것을 가능하게 한다. 일반적으로, 펠스된 RF 유도성 플라즈마에 의해 생성된 이온은 낮은 이온 에너지(예를 들어 < 10eV)를 가진 이온을 만들고, 이는 플라즈마 내에 위치한 기판에 손상을 입히지 않을 것이다. 여기서 설명된 하나 이상의 실시예를 유의하게 하도록 이루어질 수 있는 RF 전력을 펠스하는 방법의 예는 여기서 참조로서 통합된 2003년 6월 12일 출원되고 공통으로 양도된 미국 특허 제 6,831,021호에서 추가적으로 논의된다.

[0023] 도 2a는 본 발명의 다른 실시예에 따른 세정 챔버(100a)의 측단면도를 개략적으로 도시한다. 세정 챔버(100a)는 용량성으로 커플링된 플라즈마 챔버이다. 세정 챔버(100a)는 프로세스 영역(133)을 형성하고 프로세스 챔버 어셈블리(196)에 밀봉 가능하게 커플링된 챔버 뚜껑(129)을 포함한다. 이러한 구성에서, 챔버 뚜껑 어셈블리(130)는 가스 분배 플레이트(132)(또한 샤워 헤드라고도 알려져 있음) 및 상기 가스 분배 플레이트(132)에 거의 평행한 블로커 플레이트(blocker plate; 134)를 가진 베이스 플레이트(131)를 포함한다. 가스 분배 플레이트(132)는 전기적 절연체(135)를 이용하여 챔버벽(128)으로부터 절연된다. 챔버 뚜껑 어셈블리(130)는 가스 전달 어셈블리(150)에 연결된다. 가스 전달 시스템(150)으로부터의 세정 가스 및/또는 반응 물질은 가스 통로(136)를 통해 프로세스 영역(133)으로 유동할 수 있다. RF 소스 어셈블리(191)는 플라즈마 생성을 위해 RF 전력 소스를 제공하는 베이스 플레이트(131)에 커플링된다. 용량성 플라즈마 생성을 위한 RF 소스는 일반적으로 예를 들어 13.56MHz RF 생성기와 같은 라디오 주파수(RF) 전력원을 포함한다. 프로세싱 동안, 기판 지지 부재(162 A)는 접지될 수 있다. 기판 지지 부재(162A) 및 베이스 플레이트(131) 사이의 바이어스 포텐셜은 프로세스 영역(133)에서 플라즈마를 점화할 수 있다. 플라즈마에서 활성화된 좋은 기판(102)을 프로세스하는데 이용될 수 있다. 프로세싱 동안 기판 지지대(162A)는 RF 생성기(123)에 연결될 수 있고, 이에 의해 RF 바이어스가 기판 지지 부재(162A)의 부분들에 배치된 전도성 요소에 가해질 수 있으며, 이에 의해 기판(102)의 표면으로 프로세싱 영역(122)에서 생성되었던 플라즈마에 존재하는 이온들을 끌어당긴다. 용량성으로 커플링된 플라즈마 반응기의 더욱 구체적인 설명은 여기서 참조로서 통합된 "화학 기상 증착 시스템에서 가스를 분배하기 위한 장치"라는 명칭의 미국 특허 제 6,495,233호에서 찾을 수 있다.

[0024] 상기 설명된 세정 챔버(100 및 100a)(도 1 및 2)는 반도체 기판을 세정하는데 이용될 수 있다. 특히, 본 발명의 세정 챔버(100 및 100a)는 실리콘 표면에 대해 손상 없는 세정을 수행하는데 이용될 수 있다.

[0025] 다른 실시예에서, 세정 챔버는 마이크로파 에너지 소스(미도시)를 이용할 수 있고, 이에 의해 여기서 논의된 세정 프로세스를 수행하는데 이용되는 플라즈마를 생성한다.

#### 기판 표면을 세정하기 위한 방법

[0026] 도 3은 본 발명의 일 실시예에 따른 반도체 기판을 세정하기 위한 방법(200)의 흐름도를 도시한다. 일 실시예에서, 상기 방법(200)은 상기 설명된 세정 챔버(100 또는 100a)에서 수행될 수 있다. 일 실시예에서, 세정 프로세스는 일반적으로 플라즈마 세정 프로세스를 이용하여 반도체 기판 상에 깨끗하고 손상 없는 표면을 형성하는 방법을 제공한다.

[0027] 단계(212)에서, 세정 챔버(100) 또는 세정 챔버(100a)와 같은 세정 챔버의 내부면이 재생될 수 있다. 일 실시예에서, 단계(212)는 세정 챔버의 다양한 내부면에서 발견된 어느 원하지 않는 잔류 물질 및/또는 오염 물질을 제거하는 에칭 프로세스를 수행하는 단계를 포함한다. 종래의 스퍼터 에칭 및/또는 화학적으로 보조되는 에칭 프로세스는 챔버벽 또는 쉴드(130)와 같은 세정 챔버의 내부면을 재생하도록 수행될 수 있다.

[0028] 일 실시예에서, 반응성 가스의 원격 또는 인시츄 플라즈마는 세정 챔버의 내부면 상에서 오염 물질을 제거하는데 이용될 수 있다. 반응성 가스는 일반적으로 이용되는 할로겐 및 할로겐 화합물을 포함한 넓은 범위의 가스들로부터 선택될 수 있다. 예를 들면, 반응성 가스는 염소, 플루오르 또는 이의 화합물일 수 있고, 이는 예를 들어 제거되는 증착 물질에 따라 트리플루오르화 질소( $NF_3$ ), 테트라플루오르화 탄소( $CF_4$ ), 헥사플루오르화 황

(SF<sub>6</sub>), 헥사플루오로에탄(C<sub>2</sub>F<sub>6</sub>), 테트라클로로화 탄소(CC<sub>14</sub>), 헥사클로로에탄(C<sub>2</sub>C<sub>16</sub>), 또는 이의 조합물이다.

- [0030] 일 실시예에서, 아르곤, 질소, 헬륨, 수소 또는 산소 등과 같은 캐리어 가스는 세정 챔버의 프로세싱 영역으로 전달될 수 있고, 이에 의해 원하지 않는 종의 제거를 돋고 및/또는 에칭 프로세스를 돋거나, 또는 세정 챔버에서 플라즈마를 개시하고 및/또는 안정화하는 것을 돋는다.

- [0031] 일 실시예에서, 세정 가스는 세정 챔버내로 전달될 수 있고, 이에 의해 세정 챔버의 내부면 상의 실리콘(Si)과 같은 게터링 물질(이하에서 논의됨)을 포함한 코팅을 에칭한다. 세정 가스는 가열된 트리플루오르화 질소(NF<sub>3</sub>), 염화 수소(HCl) 또는 이의 조합을 포함할 수 있다. 일 실시예에서, 종래의 원격 플라즈마 소스(RPS)는 프로세스 챔버의 프로세싱 영역에 커플링될 수 있다. RPS는 일반적으로 분해된 플루오르와 같은 반응성 세정제를 제공하고, 이는 진공 펌프(110)에 의해 비워진 증착물 및 다른 프로세스 부산물을 챔버 구성요소로부터 제거한다.

- [0032] 단계(214)에서, 셔터 디스크(shutter disk) 또는 더미 기판(dummy substrate)은 도 1 및 2a의 기판 지지 부재(162A)와 같은 기판 지지 부재의 상부면을 커버하는데 이용될 수 있다. 셔터 디스크 또는 더미 기판은 단계(216)와 같은 후속 증착 동안 기판 지지 부재 상에 어떠한 증착도 방지시키는데 이용되고, 이에 의해 처리되는 기판은 세정 챔버의 내부에 형성된 어떠한 코팅과도 접촉하지 않을 것이다. 또한, 기판 지지 부재를 커버하는 것은 기판 지지 부재가 프로세싱 동안 기판을 지지하도록 구성된 정전기적 쳐크일 때 쳐킹 문제를 피할 수 있다.

- [0033] 단계(216)에서, 일 실시예에서, 챔버벽(128), 쉴드(130), 쇠도우 링(shadow ring; 138), 챔버 뚜껑(129)과 같은 세정 챔버 구성요소의 하나 이상은 그 위에 게터링 코팅을 증착함에 의해 조절(conditioning)될 수 있다. 게터링 코팅은 하나 이상의 게터링 물질을 포함할 수 있다. 게터링 물질이란 용어는 세정 프로세스 이전에 또는 세정 프로세스 동안 세정 챔버에서 발견되는 어떠한 이물질을 흡수(물리적 흡수 또는 화학적 흡수) 및/또는 부동화시키는데 이용되는 임의 물질을 일반적으로 지칭한다. 게터링 물질은 새로운 부산물의 생성, 입자 생성, RF 전력의 원하지 않는 소산 또는 프로세싱 영역(122)에서 발견되는 바람직한 종들의 제거와 같은 다른 문제점들을 유발하지 않으면서 세정 챔버에서 원하지 않는 부산물을 제거하도록 선택된다. 단계(216) 동안 형성된 증착된 게터링 코팅의 두께는 약 10Å 내지 약 1μm일 수 있다. 내부면 상의 코팅은 순차적으로 프로세스된 기판의 오염을 막거나 또는 감소시키는데 이용될 수 있다. 코팅은 순수한 실리콘 물질(예를 들어 에피택셜 Si 층, 다결정 Si 층, 비정질 Si 층), 실리콘 함유층, 게르마늄 함유층 및/또는 하나 이상의 공통 도연트 물질(예를 들어 붕소(B), 인(P))의 원하는 레벨을 함유한 실리콘 또는 게르마늄층, 또는 이의 조합을 포함할 수 있다. 순수 실리콘으로 형성된 코팅은 에피택셜층이 위에 형성될 수 있는 실리콘 기판 상에서 공통적으로 발견되는 가장 많은 오염 물질에 대해 강한 게터링 영향을 가질 것이라 여겨진다. 실리콘의 이용은 또한 소자 수율에 미치는 입자 오염의 영향을 최소화시키는 것에서 유리할 수 있고, 그러한 영향은 기판의 세정된 표면 상에 후속하여 형성되는 에피택셜층의 금속 오염 또는 포이즌(poisoning)에 의해 야기될 것이다. 일례에서, 게터링 코팅은 약 200W 내지 약 2kW의 RF 전력 및 약 0.1 내지 약 5.0Torr의 압력으로 프로세싱 챔버의 프로세싱 영역 내로 전달된 실란(SiH<sub>4</sub>) 함유 가스를 이용하여 증착되고, 이 경우 챔버 구성요소 온도는 약 200°C 내지 약 500°C의 범위에서 유지된다.

- [0034] 일 실시예에서, 게터 산소로 구성된 게터링 물질로 된 층은 세정 챔버의 내부면 상에 증착될 수 있다. 일 실시예에서, 코팅은 약 10Å 내지 약 1μm의 두께의 실리콘(Si) 층을 포함한다. 실리콘 코팅은 일반적인 CVD 또는 ALD 유형의 프로세스를 이용하여 증착될 수 있고, 그러한 프로세스는 실리콘 함유 전구체를 챔버의 프로세싱 영역에 위치한 가열된 구성요소로 전달한다. 게터링 물질을 수용하는 구성요소는 외부 펌프, 내장된 저항성 가열 요소를 이용하여 가열될 수 있고 및/또는 RF 플라즈마를 이용하여 가열될 수 있다.

- [0035] 단계(216)에서 증착된 게터링 물질로 된 코팅은 세정 프로세스 동안 생성된 바람직하지 못한 종들을 부동화시키거나, 흡수하거나 또는 흡착할 수 있다. 궁극적으로, 코팅의 게터링 능력은 활성 표면이 커버되거나 또는 반응성이 작아짐으로써, 감소될 것이다. 이러한 문제점을 보상하기 위해, 게터링 물질의 프레쉬(새로운) 코팅(fresh coating)이 단계들(212, 214, 216)의 반복에 의해 프로세싱 영역(122)의 구성요소들 상에 형성될 수 있다. 일 실시예에서, 단계들(212, 214, 216)은 세정 챔버 내의 각각의 기판을 프로세싱하기 이전에 반복될 수 있다. 다른 실시예에서, 단계들(212, 214, 216)은 세정 챔버에서 다수의 기판들을 프로세싱한 이후 반복될 수 있다.

- [0036] 게터링 물질로 된 층을 증착한 이후, 셔터 디스크, 더미 디스크 또는 더미 기판은 세정 챔버로부터 제거된다. 다음으로, 세정되어야 하는 기판이 세정 챔버에 배치된다. 세정 챔버는 진공 상태에서 일반적으로 유지되기 때

문에, 산소, 탄소, 플루오르, 실리콘 및 염소와 같이 기판 표면 상에서 발견되는 오염 물질 및 입자는 제거되거나 또는 이동될 수 있고, 이에 의해 이들은 세정 챔버의 내부면 상에 형성된 코팅에 의해 게터링될 수 있다.

[0037] 기판은 이후 이하에서 논의되는 하나 이상의 산화 및 에칭 단계들을 수행함에 의해 세정된다. 산화 프로세스는 기판의 표면 상에서 발견되는 오염된 또는 손상된 실리콘을 소비하는데 이용된다. 이후 형성된 산화층은 새롭고 세정된 실리콘 표면을 노출하기 위해 제거된다. 산화 프로세스는 단계(220)에서 설명되고, 에칭 단계는 단계(222)에서 설명된다.

[0038] 단계(220)에서, 산화제는 세정 챔버로 전달되고 이에 의해 세정되는 기판의 상부층 상에 산화물을 생성한다. 일 실시예에서, 산화제는 오존( $O_3$ )을 포함하고, 이는 비교적 저온에서 실리콘의 산화를 가능하게 한다. 일 실시 예에서, 오존은 산소를 플라즈마, 자외선(UV) 에너지, 또는 플라즈마 및 UV 에너지의 조합에 노출시킴으로써 오존 생성기에서 생성될 수 있다. 일 실시예에서, UV 램프(145)는 프로세싱 동안 기판의 표면에 에너지를 전달하도록 위치한다. 일 실시예(미도시)에서, UV 램프는 챔버벽들(128) 중 하나에 형성된 포트를 통해 UV 광을 전달 할 수 있도록 위치한다. 산화를 위한 방법의 상세한 설명은 여기서 모두 참조로서 통합된 "기판 상에 에피택셜 실리콘층을 밀봉하기 위한 방법 및 시스템"이라는 명칭의 미국 특허출원 공보 제 2002/0115266호 및 "오존을 이용하여 열적으로 산화되는 실리콘"이라는 명칭의 미국 특허출원 공보 제 2006/0223315호에서 찾을 수 있다.

[0039] 일 실시예에서, 기판 표면은 고온 산화 프로세스를 이용하여 산화된다. 이러한 경우에, 기판은 도 1의 기판 지지 부재(162A)와 같은 기판 지지 부재 상에서 약 400°C 내지 약 700°C의 온도로 가열될 수 있다. 산화 동안, 세정 챔버는 기판 보다 낮은 온도에서 유지된다. 예를 들면, 가스 전달 경로를 포함한 세정 챔버 구성요소(예를 들어 벽, 쉴드)는 400°C 미만의 온도 또는 400°C보다 상당히 낮은 온도에서 유지된다. 일 실시예에서, 기판 지지 부재/히터는 약 700°C에서 유지되고, 세정 챔버는 약 350°C에서 유지된다. 일 실시예에서, 벽들은 프로세싱 챔버의 벽에서 형성된 채널들을 통해 유동하는 유체를 이용하여 온도 제어된다.

[0040] 단계(222)에 있어서, 뒤 이어 에칭 프로세스는 단계(220)에서 형성된 산화물을 제거하도록 수행된다. 에칭 프로세스는 물리적, 화학적 또는 물리적 및 화학적 에칭 기술의 조합을 이용하여 이루어질 수 있다.

[0041] 화학적 에칭의 경우에, 에칭 가스는 세정 챔버 내로 전달될 수 있고, 플라즈마는 기판 상의 물질과 화학적으로 반응하는 반응종을 생성하도록 점화될 수 있다. 반응의 휘발성 부산물은 세정 챔버에 연결된 진공 시스템에 의해 제거되고 및/또는 단계(216)에서 챔버 구성요소의 표면 상에 형성된 코팅에 의해 게터링된다. 에칭 가스는 염소, 플루오르 또는 단계(220) 동안 기판 표면 상에 형성된 산화물의 제거에 적절한 다른 화합물을 포함할 수 있다. 일 실시예에서, 에칭 가스는 트리플루오르화 질소( $NF_3$ ), 염소 이온( $Cl^-$ ) 및 아르곤과 같은 캐리어 가스를 포함한다.

[0042] 물리적 에칭은 기판 표면으로부터 물질을 제거하도록 기판 표면을 충돌시키는데 이용되는 에너지 종들을 제공하는 플라즈마를 생성함에 의해 수행된다. 일부 경우에, 기판 표면을 향해 플라즈마에서 형성된 이온들을 가속시키도록 기판 지지대로 바이어스를 가하는 것이 바람직하다. 충돌 이온은 스퍼터링 에칭 작용에 의해 기판 표면 상에서 물질을 물리적으로 제거한다. 기판 표면의 저에너지 물리적 충돌은 일반적으로 기판 표면에서 실리콘 격자에 대한 손상의 양을 감소시키는데 있어서 바람직하다. 낮은 전력의 바이어스는 산화된 층을 제거하고 기판 표면에 대한 손상을 최소화하는데 이용될 수 있다. 종래의 건식 에칭 프로세스는 플라즈마 보조 물질 제거 프로세스에 의해 생성된 기판 물질 격자 손상에 대해 염려할 필요 없이 물질을 빠르게 제거하는데 일반적으로 이용된다. 종래의 스퍼터 에칭 기술은 충돌 이온 및/또는 부산물의 높은 에너지에 의해 에피택셜 층 단계를 수행하기 이전에 기판을 세정하는데 일반적으로 바람직하지 못하다. 특히, 본 발명의 에칭 프로세스는 단계(222) 동안 기판 표면에서 노출된 결정질 물질에 대한 손상을 최소화하기 위해 에칭 프로세스 동안 형성된 이온들의 에너지를 조절하는 단계를 포함한다. 일 실시예에서, 내부에 배치된 게터링층을 가진 챔버에서 낮은 RF 전력 물질 제거 프로세스를 이용함에 의해, 단계(222)에서 수행된 물질 제거 프로세스는 기판 상에 손상이 없고 깨끗한 표면을 형성할 것이고, 이는 고품질의 에피택셜층이 이후의 증착 프로세스 단계(들) 동안 형성되는 것을 보장하는데 중요하다. 일 실시예에서, RF 생성기(123)는 약 25W 내지 약 500W의 평균 RF 바이어스 전력을 기판 지지대(162)에 배치된 전도성 요소로 전달하도록 이루어지고, 이에 의해 에칭 프로세스를 수행한다.

[0043] 상기 방법(200)의 대안적인 실시예에서, 단계(216)는 단계(220) 이후에, 하지만 단계(222)를 수행하기 이전에 수행된다. 이러한 대안적인 실시예의 일 태양에서, 단계(220, 222)는 상이한 챔버들에서 수행되고, 이에 의해

게터링 물질은 단계(222)를 수행하기 이전에 산화된 기판의 표면 상에 증착되지 않는다(단계 216). 단일 세정 챔버가 이용되는 대안적인 실시예의 다른 태양에서, 단계(220)는 기판 상에서 수행되고, 이후 기판은 세정 챔버로부터 제거되며, 이에 의해 더미 기판이 삽입될 수 있고 이에 의해 산화된 기판의 표면을 게터링 물질로 코팅하지 아니한 채로 단계(216)가 수행될 수 있으며, 이후 더미 기판은 제거되고 산화된 기판이 채삽입되면 이에 의해 단계(222)가 수행될 수 있다.

[0044] 도 4는 물리적 예칭 프로세스를 일으킬 수 있는 메커니즘을 일반적으로 도시하는 세정 챔버(300)의 부분적 측면도를 개략적으로 도시한다. 세정 챔버(300)는 프로세스 영역(302)을 형성하는 챔버 바디(301)를 갖는다. 세정되는 기판(303)은 기판 지지대(304) 상의 프로세스 영역(302)에 배치될 수 있다. 코일(305)은 프로세스 영역(302)의 상부에서 플라즈마(308)를 생성하도록 챔버 바디(301)의 상부 외부에 위치한다. RF 소스(306)는 플라즈마 생성을 위한 RF 에너지를 제공하기 위해 코일(305)에 연결될 수 있다. 바이어스 소스(307)는 기판 지지대(304)에 커플링될 수 있고, 이에 의해 기판(303) 및/또는 기판 지지대(304)로 바이어스 포텐셜을 제공한다. 플라즈마(308)에서 생성된 활성화 종(309) 또는 이온(310)은 기판(303)의 상부면(303A)으로 끌어당겨질 수 있고, 이에 의해 그 위의 물질을 제거한다.

[0045] 일 실시예에서, 활성화 종(309) 및/또는 이온(310)의 에너지는 조절될 수 있고, 이에 의해 물질 제거 동안 물리적 손상은 상부면(303A)에서 일어나지 않을 것이다. 이러한 조절은 기판 RF 바이어스 전력을 낮추는 단계, 기판에 가로질러 가해진 바이어스 포텐셜을 조절하는 단계, 플라즈마 생성 구성요소(예를 들어 유도적으로 커플링된 소자(예를 들어 코일), 용량성으로 커플링된 소자(예를 들어 샤워헤드, 마이크로파 소스))로 전달되는 RF 전력을 펠스하는 단계, 기판 RF 바이어스 전력을 펠스하는 단계, 예칭 가스에서 가벼운 원자종을 포함한 플라즈마를 형성하는 단계, 플라즈마를 한정하기 위해 플라즈마 쉴드를 이용하는 단계, 플라즈마에 대해 기판의 프로세싱 위치를 조절하는 단계, 및/또는 이의 조합에 의해 이루어질 수 있다.

[0046] 일 실시예에서, 활성화 종의 에너지는 기판 지지대로 전달된 낮아진 RF 바이어스 전력을 이용함에 의해 감소될 수 있다. 일 실시예에서, 도 4의 바이어스 소스(307)와 같은 바이어스 소스의 전력은 기판의 상부면으로부터 실리콘 디옥사이드를 제거하기 위해 약 50W로 설정될 수 있다.

[0047] 일 실시예에서, 도 4의 바이어스 소스(307)와 같은 바이어스 소스의 포텐셜은 더 적게 음극성을 갖도록(less cathodic) 조절될 수 있고, 이에 의해 기판 상의 바이어스를 감소시킨다. 일 실시예에서, 바이어스 소스는 제거될 수 있고, 기판은 접지된 기판 지지대 상에 위치한다. 다른 실시예에서, 역(reversed) 바이어스가 가해질 수 있고, 이에 의해 플라즈마에서 이온 및 반응성 이온종에 반발력을 가하도록 인가될 수 있다. 예를 들면, 역 바이어스는 실리콘-온-인슐레이터(silicon-on-insulator) 기판을 세정할 때 이용될 수 있다.

[0048] 일 실시예에서, 플라즈마 에너지는 RF 소스 및/또는 기판 바이어스 소스를 펠스함에 의해 감소될 수 있다. 에너지 감소의 정도는 플라즈마 생성 구성요소(예를 들어 코일, 샤워 헤드, 마이크로파 소스)로 전달된 RF 펠스의 뉘티 사이클(duty cycle)을 조절함에 의해 제어될 수 있다. RF 소스를 펠스함으로써 RF 소스에 의해 생성된 플라즈마에서의 활성화 종의 밀도를 감소시킨다. 일 실시예에서, RF 소스는 세정 프로세스 동안 세정 챔버에서 낮은 에너지 플라즈마를 유지시키도록 펠스된다. RF 소스를 펠스함으로써 플라즈마 프로세싱 영역에서의 전체 플라즈마 및 활성화 종 밀도를 감소시키고, 따라서 기판에 대한 손상을 피하도록 충돌 종의 수 및 에너지를 감소시킨다. 펠스된 플라즈마 프로세스에 대한 상세한 논의는 여기서 참조로서 통합된 "낮은 에너지 플라즈마 장치를 이용하여 높은 유전 상수 트랜지스터 게이트를 제작하기 위한 방법 및 장치"라는 명칭으로 2007년 12월 20일 출원된 미국 특허출원 제 11/614,019(Docket No. APPM 10983)호에서 찾을 수 있다.

[0049] 일 실시예에서, 예칭 가스는 하나 이상의 보다 가벼운 종을 포함하고, 이 종은 물리적 예칭 프로세스에 의해 기판 표면 상에 생성되는 어떠한 손상이라도 최소화하거나 또는 감소시키도록 낮은 에너지 플라즈마를 생성하는데 이용된다. 일 실시예에서, 헬륨(He), 네온(Ne), 수소(H<sub>2</sub>) 또는 이의 조합과 같은 보다 가벼운 가스 종은 아르곤(Ar)과 같은 다른 프로세스 가스를 포함한 예칭 가스에 첨가될 수 있다. 일 실시예에서, 예칭 가스는 아르곤 및 헬륨을 포함한다. 다른 실시예에서, 예칭 가스는 실질적으로 아르곤, 헬륨 및 수소 가스를 포함한다. 다른 실시예에서, 예칭 가스는 아르곤 및 수소를 포함한다. 다른 실시예에서, 예칭 가스는 아르곤 및 질소를 포함한다. 또 다른 실시예에서, 예칭 가스는 실질적으로 헬륨(He), 네온(Ne), 또는 수소(H<sub>2</sub>)를 포함한다.

[0050] 다른 실시예에서, 플라즈마 쉴드(140)(도 2b)는 프로세싱 동안 기판의 표면 근처에 위치할 수 있다. 도 2b는 플라즈마 쉴드(140)를 포함한 세정 챔버(100)의 일 실시예의 측면도를 개략적으로 도시한다. 플라즈마 쉴드는 기판의 표면 근처에 충돌 종의 에너지 및/또는 양을 최소화하거나 또는 감소시키는데 이용된다. 플라즈마

쉴드(140)는 천공 또는 다공성 물질일 수 있고, 이에 의해 프로세싱 동안 플라즈마 및/또는 프로세스 가스의 일부가 통과하는 것이 가능하다. 일 실시예에서, 천공은 플라즈마 쉴드를 통과하는 다수의 홀(141)이다. 일 실시예에서, 플라즈마 쉴드는 유전체 물질로 만들어지거나 또는 유전체 물질로 코팅되고, 이러한 물질은 플라즈마 및 프로세스 가스와 양립성이 있다(compatible)(예를 들어 석영,  $\text{SiO}_2$ ). 일 실시예에서, 플라즈마 쉴드는 챔버 뚜껑(129) 또는 챔버벽(128)이 만들어지는 물질과 같은 챔버의 다른 구성요소와 동일한 물질로 만들어진다. 일 실시예에서, 플라즈마 쉴드는 실리콘, 이트륨, 이트륨 산화물, 게르마늄, 붕소, 인, 및 실리콘 게르마늄 화합물로 이루어진 그룹으로부터 선택된 물질로 만들어진다.

[0051] 다른 실시예에서, 세정 챔버에서 생성된 플라즈마 및 처리되는 기판의 상대적 위치는 플라즈마의 이온 또는 활성 중에 의한 기판 표면의 충돌의 양을 조절하도록 조절될 수 있다. 유사한 조절은 여기서 참조로서 통합된 "저온 폴리실리콘 TFT를 위한 다중층 고품질 게이트 유전체"라는 명칭의 공통으로 양도된 미국 특허출원 공보 제2006/0105114호에서 설명된다.

[0052] 도 3으로 다시 돌아가면, 단계(222)의 예시적 예칭 프로세스가 도 1의 세정 챔버(100)와 유사한 세정 챔버에서 수행될 수 있고, 이에 의해 기판의 상부면 상에 형성된 실리콘 산화물을 제거한다. 프로세싱 동안, 챔버 압력은 약 1mTorr 내지 약 1Torr에서 유지될 수 있다. 일 실시예에서, 챔버 압력은 약 20mTorr 내지 약 800mTorr에서 유지될 수 있다. 헬륨 및 아르곤을 포함한 예칭 가스는 프로세스 영역에 제공될 수 있다. 일 실시예에서, 챔버 압력은 약 5mTorr 내지 약 20mTorr일 수 있고, 예칭 가스는 주로 헬륨을 포함한다. 처리되는 기판은 또한 최대 약 700°C의 온도로 가열될 수 있다. 세정 챔버는 약 20°C 내지 약 400°C의 온도에서 유지될 수 있다. 일 실시예에서, 챔버는 약 30°C의 온도에서 유지된다. 챔버벽을 낮은 온도에서 유지시키는 것은 챔버벽의 부식을 감소시키는 데 도움이 된다고 여겨진다.

[0053] 도 3으로 돌아가면, 단계(220, 222)는 기판이 세정될 때까지 한번 이상 반복될 수 있다. 일단 기판 표면이 세정되면, 이어서 단계(224) 및/또는 단계(226)는 깨끗한 기판 표면 상에서 수행될 수 있다.

[0054] 단계(224)에서, 패시베이션 처리(passivation treatment)가 세정된 기판에 대해서 수행되고, 이에 의해 기판은 이후의 에피택셜 증착 프로세스 때까지 깨끗한 채로 남아 있다. 일 실시예에서, 패시베이션 처리는 패시베이션 가스를 유동시키는 단계 및 패시베이션 가스로 된 플라즈마를 생성시키는 단계를 포함한다. 일 실시예에서, 패시베이션 가스는 수소로 세정된 실리콘 표면을 마무리짓는데(terminate) 이용되는 짙은 농도의 수소 가스( $\text{H}_2$ )를 포함한다. 일 실시예에서, 패시베이션 처리는 기판이 약 50 내지 약 500°C의 온도에서 유지되는 동안 약 1%의 수소 가스를 포함한 수소 함유 가스를 전달하는 단계를 포함한다.

[0055] 단계(226)에서, 에피택셜 실리콘층은 에피택셜 챔버에서 세정된 기판 상에서 성장될 수 있다. CVD 프로세스를 이용하여 실리콘 에피택셜층을 성장시키기 위해, 기판은 예를 들어 약 500°C 내지 약 800°C의 상승 온도로 그리고 감소된 압력 상태 또는 대기 압력 상태로 설정된 에피택셜 챔버에 위치한다. 상승 온도 및 감소된 압력 상태에서 유지하는 동안, 모노실란 가스 또는 디클로로실란 가스와 같은 실리콘 함유 가스가 에피택셜 챔버로 공급되고, 실리콘 에피택셜층은 증기 상 성장(vapor phase growth)에 의해 성장하여 성장이 이루어지는 기판과 동일한 결정 배향을 갖는 반도체층을 형성한다. 프로세스는 약 0.1Torr 내지 약 760Torr의 압력의 범위에서 작동할 수 있다. 실리콘 함유 필름을 증착시키는데 이용될 수 있는 하드웨어는 미국 캘리포니아 산타클라라에 위치한 어플라이드 머티어리얼스사로부터 구입 가능한 Epi Centura RTM 시스템 및 Poly Gen RTM 시스템을 포함한다. 에피택셜 챔버의 상세한 설명은 여기서 참조로서 통합된, 2007년 6월 25일에 출원된 "모듈형 CVD EPI 300mm 반응기"라는 명칭의 미국 특허출원 제 11/767,619호(Docket No.10394)에서 찾을 수 있다.

[0056] 상기 방법(200)은 세정 챔버 및 에피택셜 챔버를 포함한 클러스터 틀에서 수행될 수 있다. 종래의 구성에서, 기판은 에피택셜층을 형성하도록 에피택셜 증착 챔버내로 이동되기 이전에 종래의 세정 프로세스(예를 들어 습식 세정 프로세스)를 수행한 이후 일정한 주기의 시간을 기다릴 수 있다. 기다리는 프로세스는 기판 표면의 청결성에 영향을 미칠 수 있고, 이는 웨이퍼마다의 프로세스 결과에 영향을 미칠 수 있다. 일 실시예에서, 단계(224)의 완료 및 이후의 에피택셜층 증착 프로세스(즉, 단계(226)) 사이의 타이밍은, 패시베이션 프로세스가 완료된 직후 기판이 에피택셜 챔버로 이동되도록, 스케줄된다. 프로세스 타이밍 또는 스케줄링을 제어하는 제어기(147)의 이용은 프로세스 반복성 및 소자 수율을 향상시킬 수 있다. 일 실시예에서, 대기열 단계(queuing step)는 단계(224) 이전에 추가될 수 있고, 이에 의해 패시베이션 이후의 기다림을 제거한다. 다른 실시예에서, 단계(222) 및/또는 단계(224)는 그러한 단계(222) 및/또는 단계(224)가 완료된 때 에피택셜 증착

챔버가 기판을 수용할 준비가 되어있을지를 제어기(147)가 확인할 때까지 시작되지 아니한다.

[0057] 일 실시예에서, 단계(220)는 제 1 세정 챔버(100)에서 수행되고, 단계(222)는 제 2 세정 챔버(100)에서 수행되며, 이에 의해 단계(220)가 단계(222)에 영향을 미치는 또는 그 반대로 영향을 미치는 임의 프로세스를 감소시킨다. 일 실시예에서, 제 1 세정 챔버(100)는 단계(212-220)를 수행할 수 있고, 제 2 세정 챔버(100)는 단계(212-216) 및 단계(222-224)를 수행할 수 있다.

[0058] 제어기(147)는 일반적으로 제 1 세정 챔버(100) 및 시스템(400)의 제어 및 자동화를 촉진시키도록 설계되고(도 5), 일반적으로 중앙 처리 유닛(CPU)(미도시), 메모리(미도시) 및 지원 회로(또는 I/O)(미도시)를 포함할 수 있다. CPU는 다양한 챔버 프로세스들 및 하드웨어(예를 들어 탐지기, 모터, 유체 전달 하드웨어 등)를 제어하기 위한 산업적 설정에서 이용되는 컴퓨터 프로세서들의 임의의 형태들 중 하나일 수 있고, 시스템 및 챔버 프로세스들(예를 들어 기판 위치, 프로세스 타임, 탐지기 신호 등)을 모니터한다. 메모리는 CPU에 연결되고, 랜덤 액세스 메모리(RAM), 리드 온리 메모리(ROM), 플로피 디스크, 하드 디스크, 또는 로컬 또는 원격의 디지털 저장의 다른 어떠한 형태와 같은 쉽게 이용가능한 메모리의 하나 이상일 수 있다. 소프트웨어 명령 및 데이터는 CPU에 명령하기 위한 메모리 내에 코드화되고 저장될 수 있다. 지원 회로는 또한 종래의 방식으로 프로세서를 지원하기 위해 CPU에 연결된다. 지원 회로는 캐쉬, 전력 서플라이, 클럭 회로, 입력/출력 회로, 하위 시스템 및 이와 유사한 것을 포함할 수 있다. 제어기(147)에 의해 판독 가능한 프로그램(또는 컴퓨터 명령)은 어떠한 작업이 기판 상에서 수행 가능한지를 결정한다. 바람직하게, 프로그램은 제어기(147)에 의해 판독 가능한 소프트웨어이고, 이는 적어도 프로세스 레시피 순서(process recipe sequencing), 기판 위치 정보, 다양하게 제어된 구성 요소의 이동 순서, 프로세스 제어, 프로세스 타이밍, 스케줄링, 대기열 단계, 및 이의 조합을 생성하고 저장하기 위한 코드를 포함한다.

#### 클러스터 툴

[0059] 도 5는 본 발명의 일 실시예에 따른 반도체 프로세싱을 위한 클러스터 툴(400)의 평면도를 도시한다. 클러스터 툴은 반도체 제조 프로세스에서 다양한 기능을 수행하는 다수의 챔버를 포함한 모듈형 시스템이다. 클러스터 툴(400)은 한 쌍의 로드락(405)을 통해 전방 단부 환경(404)에 연결된 중앙 전달 챔버(401)를 포함한다. 팩토리 인터페이스 로봇(factory interface robot; 408A, 408B)은 전방 단부 환경(404)에 배치되고, 전방 단부 환경(404) 상에 장착된 다수의 포드(pods; 403) 및 로드락(loadlocks; 405) 사이에서 기판을 셔틀하도록(shuttle) 구성된다.

[0060] [0061] 다수의 챔버(407, 408, 409, 및 410)가 원하는 프로세스를 수행하기 위해 중앙 전달 챔버(401)에 장착된다. 중앙 전달 챔버(401)에 배치된 중앙 로봇(406)은 로드락(405) 및 챔버(407, 408, 409, 410) 사이에서 또는 챔버들(407, 408, 409, 410) 사이에서 기판을 전달하도록 구성된다.

[0062] 일 실시예에서, 클러스터 툴(400)은 도 1의 세정 챔버(100)와 같은 세정 챔버 및 두 개의 에피택셜 챔버(407, 408)를 포함한다. 챔버(410)는 도 1에서 설명된 세정 챔버(100)와 같은 세정 챔버일 수 있다. 챔버(410)는 에피택셜 성장 프로세스 이전에 기판을 세정하도록 구성된다. 챔버(407, 408)는 에피택셜 성장 프로세스를 수행할 수 있는 에피택셜 챔버일 수 있다. 예시적인 에피택셜 챔버는 여기서 참조로서 통합된 2007년 6월 25일에 "모듈형 CVD EPI 300mm 반응기"라는 명칭으로 출원된 미국 특허출원 제 11/767,619(Docket No.10394)호에서 찾을 수 있다.

[0063] 클러스터 툴(400)은 상기 설명된 방법(200)을 수행하는데 이용될 수 있다. 프로세싱 동안, 프로세스되는 기판은 포드(403)에서 클러스터 툴(400)에 도달할 수 있다. 기판은 팩토리 인터페이스 로봇(408A 또는 408B)에 의해 포드(403)로부터 진공 양립형 로드락(405)으로 전달된다. 이후 기판은 진공 상태에서 일반적으로 유지되는 전달 챔버(401)에서 중앙 로봇(406)에 의해 집어진다. 이후 중앙 로봇(406)은 세정 챔버(410) 안으로 기판을 로드하고, 그 내부면은 상기 방법(200)의 단계(212, 214, 216)에서 설명된 것처럼 재생되고 코팅되었다. 상기 방법(200)의 단계(220, 222, 224)를 포함한 세정 프로세스는 세정 챔버(410)에서 기판에 대해 수행될 수 있다. 이후 중앙 로봇(406)은 세정 챔버(410)로부터 기판을 집고, 기판을 에피택셜 챔버(407 또는 408) 중 이용가능한 어느 것으로 로드한다. 에피택셜층은 에피택셜 챔버(407 또는 408)에서 세정된 기판 상에서 성장될 수 있다.

[0064] 일 실시예에서, 클러스터 툴(400)은 챔버(409) 및 챔버(410) 위치에 위치한 두 개의 세정 챔버(100)(또는 100a)(도 5) 및 챔버(407) 또는 챔버(408) 위치에 위치한 두 개의 에피택셜 챔버를 포함하도록 구성된다. 상기에서 언급된 것처럼, 에피택셜 챔버(407, 408) 중 어느 하나에서 에피택셜층 증착 단계(226)를 수행하기

이전에, 이러한 구성에서 하나의 세정 챔버(예를 들어 챔버(410))에서 단계(220)를 수행하고, 나머지 세정 챔버(예를 들어 챔버(409))에서 단계(222, 224)를 수행하는 것이 바람직할 수 있다.

다른 실시예에서, 클러스터 툴은 플라즈마 침지형 이온 주입(plasma immersion ion implantation)(P3I) 챔버를 포함한다. 예를 들면, 챔버(409)는 기판 상에서 에피택셜층으로 하나 이상의 도편트를 주입하도록 구성된 P3I 챔버일 수 있다. 예시적인 P3I 챔버는 여기서 참조로서 통합된 "플라즈마 침지형 이온 주입을 이용한 실리콘-온-인슐레이터 구조의 제작"이라는 명칭의 미국 특허 제 6,893,907호 및 "이온 분배의 자기적 제어를 가진 외부로 활성화된 토로이달 플라즈마 소스"라는 명칭의 미국 특허 제 6,939,434호에서 찾을 수 있다.

이전의 내용은 본 발명의 실시예에 관한 것이지만, 본 발명의 다른 그리고 추가적인 실시예들이 본 발명의 기본적 범위로부터 벗어나지 아니한 채로 고안될 수 있으며, 그 범위는 이하의 청구 범위에 의해 결정된다.

도면

## 도면1

도면2a

도면2b

## 도면3

도면4

도면5