(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2005-509282

(P2005-509282A)

(43) 公表日 平成17年4月7日(2005.4.7)

(51) Int.CI.<sup>7</sup>

H01L 27/105

H01L 21/3205

H01L 27/10

F 1

H01L 27/10 444Z

H01L 27/10 451

H01L 21/88 B

テーマコード(参考)

5FO33

5FO83

審査請求 有 予備審査請求 未請求 (全 30 頁)

(21) 出願番号 特願2003-543032 (P2003-543032)

(86) (22) 出願日 平成14年11月8日 (2002.11.8)

(85) 翻訳文提出日 平成16年5月7日 (2004.5.7)

(86) 國際出願番号 PCT/N02002/000414

(87) 國際公開番号 WO2003/041084

(87) 國際公開日 平成15年5月15日 (2003.5.15)

(31) 優先権主張番号 20015509

(32) 優先日 平成13年11月9日 (2001.11.9)

(33) 優先権主張国 ノルウェー(N0)

(71) 出願人 500034413

シン・フィルム エレクトロニクス エイ

エスエイ

ノルウェー国、オスロ、バイカ、ビー、

オー、ボックス 1872

(74) 代理人 100066692

弁理士 浅村皓

(74) 代理人 100072040

弁理士 浅村肇

(74) 代理人 100087217

弁理士 吉田裕

(74) 代理人 100080263

弁理士 岩本行夫

最終頁に続く

(54) 【発明の名称】メモリ構造体用電極、方法および装置

## (57) 【要約】

平行帶状導電体の形態の電極を各層に有する第1および第2の薄膜電極層L1、L2を有する電極手段において、電極は電極幅の何分の一かの厚さを有し、少なくともその側縁に沿って延在し、その間に絶縁壁6aを作る電気絶縁材料の薄膜6によってのみ離隔されている。薄膜電極層L1、L2を平坦化して、極めて平坦な表面を得る。1または複数の電極手段EMを有する装置において、好ましくは受動マトリックス・アドレス指定可能な装置が得られ、例えば、個々にアドレス指定可能な機能素子5を、例えばそれぞれ論理セルまたはメモリ・セルの形態で含むマトリックス・アドレス指定可能なデータ処理デバイスまたはマトリックス・アドレス指定可能なデータ記憶デバイスとしての使用に適したものとなるように、角電極1、2が或る角度で交差、好ましくは直交し、機能媒体3がその間に挟まれて全域に設けられ、全域機能媒体3におけるその充填率が1に近づき、装置における最大セル数が約A/f<sup>2</sup>になる。ただし、Aは、薄膜電極層L1とL2の間に挟まれた全域機能媒体3の面積、fはプロセスで制限される最小輪郭である。

**【特許請求の範囲】**

**【請求項 1】**

平行帯状導電体の形態の電極( )を各層に有する第1および第2の薄膜電極層( L 1、 L 2 )を含み、

前記第2の薄膜電極層( L 2 )の前記電極( )は、前記第1の薄膜電極層( L 1 )の前記電極( )と交差する方向、または、実質的に直交する方向に指向しており、

前記第1および第2の薄膜電極層( L 1、 L 2 )の少なくとも1つが、基板または背面体( 7、 7' )の絶縁表面に設けられ、

前記第1および第2の薄膜電極層( L 1、 L 2 )は、平行離隔平面に形成したものであり、両者の間の機能媒体である全域形成層( 3 )に接している電極手段( E M )において

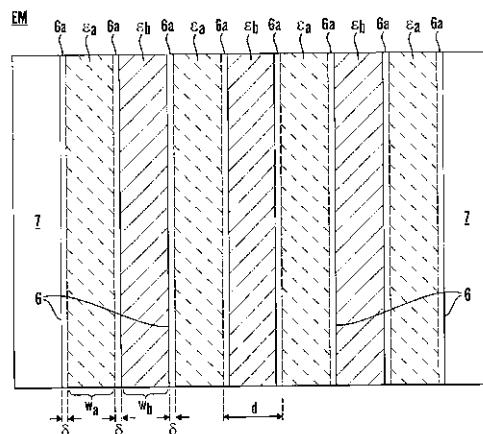

、前記第1および第2の薄膜電極層( L 1、 L 2 )の各々が、幅 w<sub>a</sub> 、厚さ h<sub>a</sub> を有する、第1組( E<sub>a</sub> )の前記帯状電極( a )と、幅 w<sub>b</sub> 、厚さ h<sub>b</sub> を有する第2組( E<sub>b</sub> )の前記帯状電極( b )とを含み、

前記第1組( E<sub>a</sub> )の前記電極( a )は、w<sub>a</sub> と同等以上の距離 d だけ互いに離れており、

前記第2組( E<sub>b</sub> )の前記電極( b )は、前記第1組( E<sub>a</sub> )の前記電極( a )の間の間隔部に設けられて、電気絶縁材料から成る薄膜( 6 )によって前記第1組の電極から電気的に絶縁され、該電気絶縁材料が、厚さ を有するとともに、少なくとも前記平行電極( a 、 b )の側縁に沿って延在し、両組の前記電極間に厚さ の絶縁壁( 6a )を作っており、前記 の大きさは w<sub>a</sub> または w<sub>b</sub> の大きさに比べて小さく、前記第1組( E<sub>a</sub> )の前記電極( a )の間の間隔距離が w<sub>b</sub> + 2 であり、

また、前記電極( )を有する前記電極層( L 1、 L 2 )および前記絶縁性薄膜( 6 )が、それぞれ、前記電極手段( E M )に全域平面層を作っていることを特徴とする電極手段( E M )。

**【請求項 2】**

前記第1および第2の薄膜電極層( L 1、 L 2 )のうちの少なくとも1つの前記電極( )の導電材料が、前記基板( 7、 7' )の表面に直接付与されていることを特徴とする請求項1に記載された電極手段( E M )。

**【請求項 3】**

第1および第2の薄膜電極層( L 1、 L 2 )のうちの1つの層の前記電極( )が、他方の前記薄膜電極層( L 2、 L 1 )とは反対側の表面で外部に露出していることを特徴とする請求項1に記載された電極手段( E M )。

**【請求項 4】**

前記他方の薄膜電極層( L 2、 L 1 )とは反対側の、前記薄膜電極層( L 1、 L 2 )のうちの1つの薄膜電極層の表面が、背面体( 7' )によって覆われていることを特徴とする請求項1に記載された電極手段( E M )。

**【請求項 5】**

両組( E<sub>a</sub> 、 E<sub>b</sub> )の前記電極( a 、 b )の断面積が等しく、 w<sub>a</sub> · h<sub>a</sub> = w<sub>b</sub> · h<sub>b</sub> であることを特徴とする請求項1に記載された電極手段( E M )。

**【請求項 6】**

前記第1組( E<sub>a</sub> )の電極( a )の断面積が、前記第2組( E<sub>b</sub> )の前記電極( b )の断面積と相違し、 w<sub>a</sub> · h<sub>a</sub> ≠ w<sub>b</sub> · h<sub>b</sub> であることを特徴とする請求項1に記載された電極手段( E M )。

**【請求項 7】**

両組( E<sub>a</sub> 、 E<sub>b</sub> )の前記電極( a 、 b )を成す導電材料が同一である請求項1に記載された電極手段( E M )。

**【請求項 8】**

前記第2組( E<sub>b</sub> )の前記電極( b )を成す導電材料が、前記第1組( E<sub>a</sub> )の前記電極( a )を成す導電材料と異なることを特徴とする請求項1に記載された電極手段( E M )。

10

20

30

40

50

EM)。

**【請求項 9】**

第1組(E<sub>a</sub>)の前記電極( a )を成す導電材料および第2組(E<sub>b</sub>)の前記電極( b )を成す導電材料が、それぞれ、導電率<sub>a</sub>、<sub>b</sub>を有し、下記関係式を満たして、

**【数1】**

$$\frac{w_a \cdot h_a}{w_b \cdot h_b} = \frac{\sigma_b}{\sigma_a}$$

前記第1および第2組(E<sub>a</sub>およびE<sub>b</sub>)の各電極( a 、 b )の導電容量を、いずれの場合も等しくしていることを特徴とする請求項8に記載された電極手段(EM)。 10

**【請求項 10】**

前記第1組(E<sub>a</sub>)の前記電極( a )と、前記第2組(E<sub>b</sub>)の前記電極( b )との間の前記絶縁壁(6a)が、前記第1組(E<sub>a</sub>)の前記電極( a )を覆う連続層に設けた、および、前記第1組の電極の間隔部内で基板(7および7')にも設けた、前記絶縁性薄膜(6)の部分(6a)を作っており、

また、前記第2組(E<sub>b</sub>)の前記電極( b )が、前記絶縁性薄膜(6)の前記壁部分(6a)の間の凹所(8)に形成され、および、前記基板を覆う前記絶縁性薄膜の部分(6b)の上にも形成されており、

前記第2組(E<sub>b</sub>)の前記電極( b )の上面が、前記第1組(E<sub>a</sub>)の前記電極( a )の上面を覆う前記絶縁性薄膜(6)の部分(6c)の表面と面一であり、もって 20

前記第1および第2組(E<sub>a</sub>、E<sub>b</sub>)の前記電極( a 、 b )が等しい高さh<sub>a</sub>=h<sub>b</sub>を有し、かつ

前記電極( a 、 b )および前記絶縁性薄膜(6)を有する前記薄膜電極層(L1、L2)が、前記電極手段(EM)における全域平面層を作っていることを特徴とする請求項1に記載された電極手段(EM)。 25

**【請求項 11】**

前記第1組(E<sub>a</sub>)の前記電極( a )と、前記第2組(E<sub>b</sub>)の前記電極( b )との間の前記絶縁壁(6a)が、第1組(E<sub>a</sub>)の前記電極( a )の側縁をその上面まで覆う層に設けた、および、前記第1組の電極の間の間隔部内で前記基板(7、7')にも設けた、前記絶縁性薄膜(6)の部分(6a、6b)を作っており、また 30

前記第2組(E<sub>b</sub>)の前記電極( b )が、前記絶縁性薄膜の壁部(6a)間の凹所(8)に形成され、および、前記基板(7)を覆う部分(6b)の上にも形成されており、

前記第2組(E<sub>b</sub>)の前記電極( b )は、前記絶縁壁(6a)の上縁、および、前記第1組(E<sub>a</sub>)の前記電極( a )の上面と面一になっており、

前記第2組(E<sub>b</sub>)の前記電極( b )は、高さh<sub>b</sub>=h<sub>a</sub>-を有しており、また電極( a 、 b )を有する前記薄膜電極層(L1、L2)と、絶縁材料(6)とが、電極手段(EM)における厚さh<sub>a</sub>の全域平面層を作っていることを特徴とする請求項1に記載された電極手段(EM)。 40

**【請求項 12】**

前記第1組(E<sub>a</sub>)の前記電極( a )と、前記第2組(E<sub>b</sub>)の前記電極( b )との間の前記絶縁壁(6a)が、前記第1組(E<sub>a</sub>)の前記電極( a )を前記基板(7、7')位置まで覆う層に設けた前記絶縁性薄膜(6)の部分を作っており、また

前記第2組の前記電極( b )が、前記絶縁性薄膜(6)の前記壁部分(6a)の間の凹所(8)に形成され、および、露出した前記基板(7、7')の上にも直接形成され、かつ前記第1組(E<sub>a</sub>)の前記電極( a )の上面を覆う前記絶縁性薄膜(6)の部分(6a)の上面と面一になっており、もって

前記第1組(E<sub>a</sub>)の電極が、高さh<sub>a</sub>=h<sub>b</sub>-を有し、かつ電極( a 、 b )を有する前記少なくとも1つの薄膜電極層(L1、L2)と前記絶縁性薄膜(6)とが、前記電極手段(EM)における、厚さh<sub>b</sub>の全域平面層を作つてい 50

ることを特徴とする請求項 1 に記載された電極手段 ( E M )。

**【請求項 1 3】**

平行帯状導電体の形態の電極 ( ) を各層に有する第 1 および第 2 の薄膜電極層 ( L 1 、 L 2 ) を含む電極手段 ( E M ) に電極層 ( L 1 、 L 2 ) を形成する方法であり、

前記第 2 の電極層 ( L 2 ) の前記電極 ( ) が、第 1 の電極層 ( L 1 ) の前記電極 ( ) と交差方向、または、実質的に直交する方向に指向し、また

前記薄膜電極層 ( L 1 、 L 2 ) のうちの少なくとも 1 つが、基板または背面体 ( 7 、 7' ) の絶縁表面に形成され、また

前記薄膜電極層 ( L 1 、 L 2 ) は、平行離隔平面に形成したものであって、該薄膜電極層の間の機能媒体である全域形成層 ( 3 ) に接触している、電極手段に電極層を形成する方法において、

厚さ  $h_a$  を有する導電材料から成る平面層を基板上に被着する段階と、

導電材料から成る前記平面層をパターン化して、幅  $w_a$  、厚さ  $h_a$  を有する第 1 組の前記帯状電極を形成する段階であり、パターン化処理で形成される電極間の凹所によって相互に離隔した前記電極となる前記段階と、

前記導電材料の部分を除去し、第 1 組の前記帯状電極の間の前記基板の表面を露出させる段階であって、前記第 1 組の平行電極は、前記電極間の凹所の幅に等しく、かつ、  $w_a$  と同等以上の距離  $d$  だけ離れている前記段階と、

前記第 1 組の電極の少なくとも側縁を覆う電気絶縁材料から成る薄膜を形成する段階と、

前記第 1 組の電極の前記側縁を覆う前記絶縁性薄膜の間の凹所に導電材料を被着させて、電極層が前記電極手段における全域平面層として得られるように、幅  $w_b$  、厚さ  $h_b$  を有する第 2 組の電極を形成する段階とによって特徴づけられる電極手段に電極層を形成する方法。

**【請求項 1 4】**

前記第 1 組の電極と、前記基板の露出面の両者を覆う全域層として前記絶縁性薄膜を形成する段階と、

前記第 2 組の電極に対する導電材料を、前記第 1 組の電極の間の前記凹所内、および、前記絶縁性薄膜の上に被着させる段階と、

前記第 2 組の電極の上面が、前記第 1 組の電極を覆う前記絶縁性薄膜と面一になるよう前に前記薄膜電極層を平坦化する段階とによって特徴づけられる請求項 1 3 に記載された電極手段に電極層を形成する方法。

**【請求項 1 5】**

前記第 1 組の電極および前記基板の露出面を覆う全域層として前記絶縁性薄膜を形成する段階と、

前記第 2 組の電極に対する導電材料を、前記第 1 組の電極の間の前記凹所内、および、前記絶縁性薄膜の上に被着させる段階と、

前記第 1 組の電極を覆う前記絶縁性薄膜が除去されて、前記電極の上面を露出し、両組の前記電極の上面、および、前記絶縁性薄膜の上縁が、全て、前記薄膜電極層の上面と面一になるように、前記薄膜電極層を平坦化する段階とによって特徴づけられる請求項 1 3 に記載された電極手段に電極層を形成する方法。

**【請求項 1 6】**

前記第 1 組の電極と、前記基板の露出面の両者を覆う全域層として前記絶縁性薄膜を形成する段階と、

前記凹所の底部にある前記絶縁性薄膜を除去する段階と、

前記第 1 組の電極を基板位置まで覆う前記絶縁性薄膜のみを残し、前記基板の表面を露出させる段階と、

前記第 2 組の電極の導電材料を前記凹所内に被着させる段階と、

前記第 2 組の薄膜電極層の上面、および、前記第 1 組の電極を覆う前記絶縁性薄膜の表面が、全て、前記薄膜電極層の上面と面一になるように、前記薄膜電極層を平坦化する段

10

20

30

40

50

階とによって特徴づけられる請求項 1 3 に記載された電極手段に電極層を形成する方法。

**【請求項 17】**

前記薄膜電極層 (L 1、L 2) のうちの 1 つのみが基板上に形成される方法であり、基板上に形成した 1 つの前記薄膜電極層を覆うとともに、前記薄膜電極層の電極に接触する、機能媒体から成る全域層を被着させ、次いで、前記基板上に電極層を形成するために用いる段階と同様な段階によって、第 2 の電極層を機能媒体から成る全域層に、直接、形成することを特徴とする請求項 1 3 に記載された電極手段に電極層を形成する方法。

**【請求項 18】**

機能媒体の前記全域層に形成された前記薄膜電極層を覆う、基板または背面体を設けることを特徴とする請求項 1 7 に記載された電極手段に電極層を形成する方法。 10

**【請求項 19】**

電極手段の電極を成す導電材料および / または基板材料を、表面酸化に適する材料として選択し、かつ、適宜少なくとも 1 つの酸化プロセスでいずれかの表面を酸化することによって前記絶縁性薄膜を形成することを特徴とする請求項 1 3 に記載された電極手段に電極層を形成する方法。

**【請求項 20】**

平行帯状導電体の形態の電極 ( ) を各層に有する第 1 および第 2 の薄膜電極層 (L 1、L 2) を含む少なくとも 1 つの電極手段 (EM) を有する装置であり、

前記第 2 の薄膜電極層 (L 2) の前記電極 ( ) が、前記第 1 の薄膜電極層 (L 1) の前記電極 ( ) と交差する方向、または、実質的に直交する方向に指向しており、 20

前記薄膜電極層 (L 1、L 2) のうちの少なくとも 1 つが、基板または背面体 (7、7') の絶縁表面に形成され、

前記薄膜電極層 (L 1、L 2) が、該薄膜電極層の間の機能媒体である全域形成層 (3) に接触する平行離隔平面に形成され、

前記第 1 の薄膜電極層 (L 1) の電極 ( ) と、前記第 2 の薄膜電極層 (L 2) の電極 ( ) との間の各重なり合い部分で定まる前記機能媒体 (3) の塊体に機能素子 (5) が形成されて、マトリックス・アドレス指定可能な配列をなし、

機能素子 (5) が、該機能素子 (5) を規定する前記交差電極 (1、2) に電圧を加えることによって機能素子 (5) を活性化されて、該交差電極間に電位が生じ、もって前記機能素子 (5) の物理的状態を一時的または永久的に変化させ、または、識別可能な物理的状態の間の切り換えを行なうことができ、前記電圧の印加は、前記機能素子の書き込みまたは読み取り動作のための前記機能素子 (5) のアドレス指定に相当し、また 30

データ処理装置の切換可能論理要素、データ記憶装置のメモリ・セル、または、情報表示装置におけるピクセルのうちの少なくとも 1 つとして、選択された機能材料 (3) の特性に応じて前記機能素子が動作せしめられ、もって、いずれの場合も、前記機能素子、セルまたはピクセルのアドレス指定がマトリックス・アドレス指定計画で行われる、前記少なくとも 1 つの電極手段を有する装置において、

前記電極手段の前記電極 (1、2) が、各電極層 (L 1、L 2) に形成されていること、

前記電極手段 (EM) の前記電極 (1、2) が、全て、ほぼ同じ幅 w を有すること、各手段の電極 (1、2) が、幅 w の何分の一かの大きさである厚さ  $w/f$  の絶縁性薄膜 (6) によって互いに電気的に絶縁されていること、および 40

w の最小値が、プロセスで制限される最小輪郭サイズ  $f$  と同程度であり、それによって、機能媒体 (3) における機能素子 (5) の充填率が 1 に近づき、機能素子 (5) の数が、前記電極層 (L 1、L 2) の間に挟まれた前記機能媒体 (3) の全面積 A、および、前記プロセスで制限される最小輪郭サイズ  $f$  によって定まる最大値に近づき、前記最大値が  $A/f^2$  で定義されることを特徴とする少なくとも 1 つの電極手段を有する装置。

**【請求項 21】**

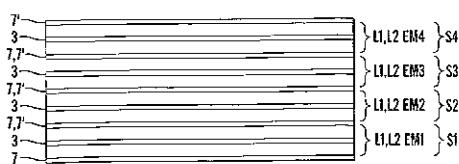

積層配列で形成された複数の電極手段 (EM<sub>1</sub> . . . EM<sub>n</sub>) を含み、その各々が、各全域層 (3<sub>1</sub> . . . 3<sub>n</sub>) を含むとともに、これに接触し、もって、容積構成体が実現さ 50

れて成ることを特徴とする請求項 20 に記載された少なくとも 1 つの電極手段を有する装置。

**【請求項 22】**

電極手段 ( $EM_k$ ) の第 2 の電極層における前記電極が、以下の電極手段 ( $EM_{k+1}$ ) における前記機能媒体 (3) に直接接触して、電極手段の第 1 の電極層 ( $L$ ) を作り、もって、 $n$  個の電極手段 ( $EM_1 \dots EM_n$ ) から成る積層体が、合計  $n + 1$  個の電極層 ( $L$ ) で実現されて成ることを特徴とする請求項 21 に記載された少なくとも 1 つの電極手段を有する装置。

**【請求項 23】**

前記装置のマトリックス・アドレス指定可能な配列を構成する前記機能素子に対する受動マトリックス・アドレス指定を実行するための、請求項 16 に記載された装置における、請求項 1 に記載された電極手段の使用。

**【請求項 24】**

前記装置のマトリックス・アドレス指定可能な配列を構成する前記機能素子に対する能動マトリックス・アドレス指定を実行するために、各機能素子が少なくとも 1 つの能動切換構成部品に接続される請求項 16 に記載された装置における、請求項 1 に記載された電極手段の使用。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、平行帯状導電体の形態の電極を各層に有する第 1 および第 2 の薄膜電極層を含み、第 2 の電極層の電極は、第 1 の薄膜電極層の電極と交差する方向、または、実質的に直交する方向に指向しており、第 1 および第 2 の薄膜電極層の少なくとも 1 つが、基板または背面体の絶縁表面に設けられ、第 1 および第 2 の薄膜電極層は、平行離隔平面に形成したものであり、両者の間の機能媒体である全域形成層に接している電極手段、および、この種の電極手段を製造する方法に関するものである。

**【0002】**

また、本発明は、平行帯状導電体の形態の電極を各層に有する第 1 および第 2 の薄膜電極層を含む少なくとも 1 つの電極手段を有する装置に係わり、この装置では、

第 2 の薄膜電極層の電極が、第 1 の薄膜電極層の前記電極と交差する方向、または、実質的に直交する方向に指向しており、

前記薄膜電極層のうちの少なくとも 1 つが、基板または背面体の絶縁表面に形成され、前記薄膜電極層が、該薄膜電極層の間の機能媒体である全域形成層に接する平行離隔平面に形成され、

第 1 の薄膜電極層の電極と、第 2 の薄膜電極層の電極との間の各重なり合い部分で定まる前記機能媒体の塊体に機能素子が形成されて、マトリックス・アドレス指定可能な配列をなし、

機能素子が、該機能素子を規定する前記交差電極に電圧を加えることによって機能素子を活性化されて、該交差電極間に電位が生じ、もって前記機能素子の物理的状態を一時的または永久的に変化させ、または、識別可能な物理的状態の間の切り換えを行なうことができ、前記電圧の印加は、前記機能素子の書き込みまたは読み取り動作のための前記機能素子のアドレス指定に相当し、また

データ処理装置の切換可能論理要素、データ記憶装置のメモリ・セル、または、情報表示装置におけるピクセルのうちの少なくとも 1 つとして、選択された機能材料の特性に応じて前記機能素子が動作せしめられ、もって、いずれの場合も、前記機能素子、セルまたはピクセルのアドレス指定がマトリックス・アドレス指定計画で行われる。

**【0003】**

最後に、本発明は、本発明装置における本発明電極手段の使用にも係わるものである。

**【0004】**

本発明は、特に、装置およびデバイスに使用され、平面配列の機能素子を備え、機能素

10

20

30

40

50

子は、それぞれ、その片側で機能素子に接触して配置される平行帯状電極を有する第1の電極手段と、同様の電極であるが、第1の手段の電極に垂直に配置され、機能素子の反対側に接触して設けられる電極を有する他の電極手段とを介してアドレスされる電極手段に関する。これによって、マトリックス・アドレス指定可能なデバイスと呼ばれるものが構成される。当該マトリックス・アドレス指定可能なデバイスは、例えば、論理セルの形態またはメモリ・セルの形態の機能素子を含むことができる。機能素子は、1つまたは複数の能動切換手段を含むことができ、その場合は、マトリックス・アドレス指定可能なデバイスは能動マトリックス・アドレス指定可能なデバイスと呼ばれ、あるいは機能素子は受動手段のみ、例えば抵抗性または容量性手段のみから構成することができ、その場合は、マトリックス・アドレス指定可能なデバイスは受動マトリックス・アドレス指定可能なデバイスと呼ばれる。

10

#### 【0005】

後者は、最も効率的なアドレス指定手段を提供するものと見なされ、例えば記憶デバイスの場合は、メモリ・セルに切換素子、すなわちトランジスタを必要としない。次いで、可能な限り高い記憶密度を達成することが望ましいが、セルに下限を設定する現行の設計規則は、その充填率、すなわち記憶を目的として実際に使用できるマトリックス・アドレス指定可能なメモリ・デバイスのメモリ材料の面積をも制限する。

#### 【背景技術】

#### 【0006】

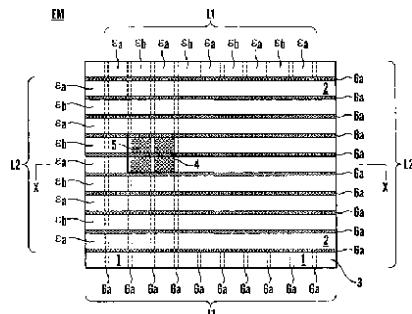

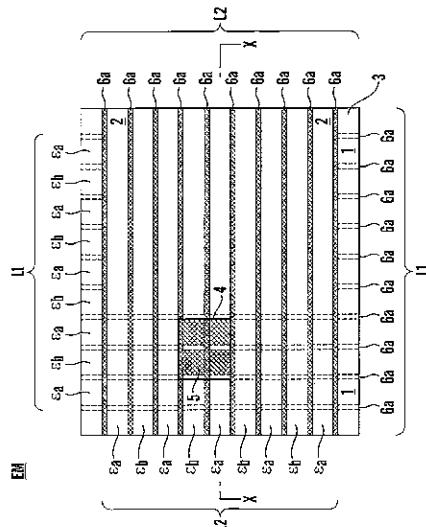

従来技術の受動マトリックス・アドレス指定可能なデバイスが図1aに示されており、幅wを有し、距離dだけ離れて配置された平行帯状電極1を含む第1の電極手段と、同一幅wを有するが、電極1に直角に配列された平行帯状電極2を含む同様な第2の電極手段との間に挟まれた機能材料から成る実質的に平坦な全域層3を含む。機能材料から成る全域層3では、それぞれの電極手段の電極1、2間の重複部分が、全域層3の機能材料における機能素子5を定める。この箇所で交差する電極に電圧を印加することによって、例えば論理セルまたはメモリ・セルでありうる機能素子の物理的状態を変化、または切り換えることができる。

20

#### 【0007】

図1bは、電極1、2、および挟まれた機能材料3の配置、ならびに機能素子5の場所を明らかにする、線X-Xに沿って截断した図1aの従来技術に係わるデバイスの断面を示す図である。全域層3の機能材料は、交差電極1、2に対する電圧の印加が、その交差部分における機能素子5のみに影響し、近隣の機能素子、または前者に近接する電極交差部分におけるセルに影響しないような特性を通常有する。全域層の機能材料が、例えば導電性である場合は、機能材料に直角方向で、かつ重複電極の間でのみ通電が生じ、全域層を通じて他の機能素子に電流が流れないように、異方性導電特性を与えることによって達成できる。しかし、多くの用途に対しては、全域層の機能材料を非導電性、すなわち誘電性とすることができる、機能素子を高度な抵抗性を有するもの、またはコンデンサのような挙動を示すような誘電体と見なすことができる。誘電体は分極性無機または有機材料で、ヒステリシスを示すものであってもよい。当該材料としては、強誘電性かつエレクトレット材料が挙げられ、それらが極性を帶びヒステリシスを示す能力は、例えば、デバイス構成が図1に示されるものと類似している強誘電性マトリックス・メモリまたはエレクトレット・マトリックス・メモリに利用される。当該デバイスでは、それらの重複分においてメモリ・セル5を定める電極に電圧を正しく印加することによってメモリ・セル、すなわち機能素子5での極性状態を設定することができ、メモリ・セルに対する書き込みおよび読み取り動作に従う動作によって極性を切り換え、またはセルを初期状態に戻すことができる。当該マトリックス・デバイスの機能は、勿論、選択される機能性材料ばかりでなく、メモリ・デバイスの構成的かつ構造的制約条件に依存する。全域層3におけるメモリ媒体の記憶容量は、メモリ・セル5のサイズおよび密度に依存し、これは、今度は製造工程で生成されうる最小工程限定特徴に依存することになる。当該特徴は、例えば、後にフォトリソグラフィ・マスクを利用し、例えばエッチングを行うフォトミクロリソグラフィ法でパ

30

40

50

ターン化される金属蒸着として電極を配置するときは、マスクによって定めることのできる最小工程限定特徴  $f$  に依存し、その値は、今度は、使用される光の波長に依存することになる。換言すれば、この特徴  $f$  は、今日の技術の範囲内では通常、例えば 0.15 から 0.2  $\mu\text{m}$  であるため、電極 1 および 2 の幅  $w$ 、ならびにその間隔もほぼこの大きさになる。

#### 【0008】

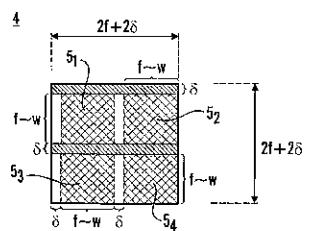

ちなみに、値  $2f$  は通常ピッチと呼ばれ、従来の製造技術で得ることができる単位長さ当たりの最大線数は、係数  $1/2f$  で与えられ、これに相応して、単位面積当たりの最大特徴数は係数  $1/4f^2$  で与えられる。したがって、図 1 に示される領域 4 について考えると、領域 4 をより詳細に示す図 1c からわかるように、セルのサイズが  $f^2$  で与えられることは明らかである。各セルは、その大きさが  $4f^2$ 、言い換えればセルの面積  $f^2$  の 4 倍である領域 4 に対応する固定領域を必要とする。このことは、図 1a のマトリックスが 0.25 の係数、すなわち  $f^2/4f^2$  を有することを示している。したがって、層 3 によって提供される領域の利用度は低い。全域層 3 における機能素子またはセル 5 のより高い充填率またはより高い密度に到達するために、充填率を高めるか、またはマトリックスの工程限定特徴におけるより高い解像度、例えば 0.1  $\mu\text{m}$  以下の範囲までの解像度を得ることが望ましい。しかし、これは、同様の領域におけるセルの全数を増加させることができると、より高い充填率を補償することはできない。

#### 【0009】

能動タイプのマトリックス・デバイス、すなわち各々の機能素子またはセルに関連する少なくとも 1 つの能動切換要素をも備えたマトリックス・デバイスの場合は、充填率はさらに低く、典型的には  $1/6$  のオーダ、すなわちわずか 1.6 . 7 % の充填率になる。

#### 【0010】

米国特許第 5 0 1 7 5 1 5 号 (Gill, テキサス・インスツルメント社に譲渡) より、集積回路における要素間にサブリソグラフィ距離を形成する方法が知られている。この公報の図 1 に示されるように、この方法は、フォトミクロリソグラフィ法の使用によって課される寸法的制約を受けず、実際に導電体または電極の寸法に比べても非常に薄くすることができる絶縁特徴  $14$  によって互いに絶縁された高密度の平行帯状電極 13 および 19 を有する電極層を形成するのに適している。該公報は、集積回路、すなわちそれぞれ切換および記憶トランジスタ構造体を備えたメモリ・セルを有する半導体メモリ・デバイスにおける帯状浮遊ゲート電極を形成するのに、この種の電極手段をどのようにして使用できるかということを開示している。明らかに、高密度電極層を形成する方法に用いられるドーピング法の同じフォトマスクを使用して、基板を好適にドーピングすることによってビット線が形成される。ビット線およびワード線 / 制御ゲート電極 42 は、浮遊ゲート 13 および 19 から絶縁体によって分離して形成され、得られる構造体は、トランジスタを備えた多端末メモリ・セルを有する半導体メモリの配列になる。しかし、米国特許第 5 0 1 7 5 1 5 号には、それぞれ高密度配列の電極を備えた 2 つの電極層を有し、2 つの電極層の電極が、電極層の間に配置され、その電極に接触する機能媒体から成る全域形成層における機能素子をアドレス指定するのに適した電極マトリックスをともに形成するよう配置された電極手段を形成するためのヒントまたは指示が示されていない。機能媒体の全域層のマトリックス・アドレス指定を効率的に利用することは、この種のマトリックス・アドレス指定可能なデバイスの層に固有の高度な平面性をも前提とするが、基板上で直交して伸びる組織構造体を形成すると、表面特徴にこの構造体の輪郭が再現されるため、これは従来技術では容易に達成されない。また、従来技術は、複数の当該マトリックス・アドレス指定可能な配列を積層して、容量デバイス、例えば当該技術分野で知られている複数のマトリックス・アドレス指定可能なメモリ・デバイスの積層体を形成する場合は不適切である。

#### 【0011】

電極が直交電極マトリックスを形成するように、電極層が機能媒体のいずれかの側に配置された受動マトリックス・アドレス指定可能なデータ処理またはメモリ・デバイスの例

10

20

30

40

50

が、例えば、公開国際特許出願WO 98 / 58383号に開示されている。明らかに、この種の装置は、いずれの場合も例えばメモリ・セルに対応しうるマトリックスにおける機能素子が、いずれの場合も、それぞれ第1の電極層と第2の電極層の電極の間の交差によって形成される重複領域によって定められるため、各電極層における電極の充填率を高めることによりマトリックスの機能素子の密度を高めることに関しては有益である。

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0012】

上記問題に鑑み、本発明の主たる目的は、上記種類のマトリックス・デバイスにおける充填率を1に近い値まで高めることを可能にし、充填率は $f$ の減少に影響されないが、当該減少は、勿論、全域層3において得られる機能素子またはセルの最大数をさらに増加させる役割を果たすため、最小工程限定特徴 $f$ の実際または実質的なサイズによって実際に制約されることなく当該デバイスにおける機能材料の全域層3によって提供される固定領域の最大利用を達成することである。10

#### 【0013】

図1aに示されている種類のマトリックス・デバイスをそれぞれの上面に積層して容量デバイスを形成することができ、その場合は、単一のデバイスを分離または絶縁層によって積層体における次のデバイスから隔離して、デバイスの1つにおける電極への電圧の印加、およびその中の機能素子の切換が、積層体における近隣デバイスに影響するのを防ぐ。当該容量デバイスは、勿論、大容量の容量メモリ・デバイスに対応するが、充填率を1または100%まで高めることが可能であれば、単一のマトリックス・デバイスの全容量は、容量デバイスを形成するために積層された4つの同様の従来のマトリックス・デバイスの容量に近づくであろうことが容易にわかる。20

#### 【0014】

理論上では、積層体を形成するデバイスの数に制限はないが、例えば、様々なデバイスにおける機能素子の大量平行アドレス指定に応じて、積層体内のデバイス間に望ましくない種類の電気的、物理的かつ熱的結合が導入されうるという短所がある。さらなる短所は、積層体の各々の單一デバイスにおける固有の不均一性である。デバイスは実質的に平面であると見なすことができるが、デバイスが積層体に付加され、デバイスが次々に積層されるに従って積層体の凹凸が大きくなるにつれて不均一性が広がっていく。当該凹凸も、実質的に平面の回路技術では極めて望ましくない。30

#### 【0015】

これに鑑み、本発明の二次的な目的は、マトリックス・デバイスで得ることができる機能素子の数に関して全容量を増加させることで、多層または容量デバイス、すなわち多数の層を有する積層体を開発する必要性を低減させ、従来技術で必要とされるデバイスまたは層の数のわずか4分の1デバイスまたは層を含む積層体で同等の容量を達成することができる。

#### 【0016】

最後に、容易に処理して高度な平面性を与えることで、表面不均一性または凹凸を防ぎ、電極手段を積層容量デバイスの用途により適したものとすることができる電極手段を提供することである。40

#### 【課題を解決するための手段】

#### 【0017】

前記目的、および、その他の利点と特徴は、本発明による以下の電極手段によって達成される。すなわち、この電極手段は、

第1および第2の薄膜電極層の各々が、幅 $w_a$ 、厚さ $h_a$ を有する、第1組の帯状電極と、幅 $w_b$ 、厚さ $h_b$ を有する第2組の前記帯状電極とを含み、

第1組の前記電極は、 $w_a$ と同等以上の距離 $d$ だけ互いに離れており、

第2組の電極は、第1組の電極の間の間隔部に設けられて、電気絶縁材料から成る薄膜によって第1組の電極から電気的に絶縁され、該電気絶縁材料が、厚さ $h_c$ を有するととも50

に、少なくとも平行電極の側縁に沿って延在し、両組の前記電極間に厚さの絶縁壁を作つてあり、の大きさは $w_a$ または $w_b$ の大きさに比べて小さく、第1組の電極の間の間隔距離が $w_b + 2$ であり。

また、電極を有する電極層および絶縁性薄膜が、それぞれ、電極手段に全域平面層を作つていることを特徴とするものである。

#### 【0018】

好適には、第1および第2の薄膜電極層のうちの少なくとも1つの電極の導電材料が、基板の表面に直接付与される。

#### 【0019】

また、好適には、第1および第2の薄膜電極層のうちの1つの層の電極が、他方の薄膜電極層とは反対側の表面で外部に露出するか、または、他方の薄膜電極層とは反対側の、薄膜電極層のうちの1つの薄膜電極層の表面が、背面体によって覆われる。 10

#### 【0020】

本発明電極手段の好適例では、両組の電極の断面積が等しく、 $w_a \cdot h_a = w_b \cdot h_b$ である。

#### 【0021】

本発明電極手段の他の好適例では、第1組の電極の断面積が、第2組の電極の断面積と相違し、 $w_a \cdot h_a \neq w_b \cdot h_b$ である。

#### 【0022】

本発明電極手段の他の好適例では、両組の電極を成す導電材料が同一である。 20

#### 【0023】

本発明電極手段の他の好適例では、第2組の電極を成す導電材料が、第1組の電極を成す導電材料と異なる。

#### 【0024】

後者の場合は、第1組の電極を成す導電材料および第2組の電極を成す導電材料が、それぞれ、導電率 $\sigma_a$ 、 $\sigma_b$ を有し、下記関係式を満たし、第1および第2組の各電極の導電容量を、いずれの場合も等しくしている。

#### 【0025】

#### 【数1】

$$\frac{w_a \cdot h_a}{w_b \cdot h_b} = \frac{\sigma_b}{\sigma_a}$$

#### 【0026】

本発明電極手段の好適例では、第1組の電極と、第2組の電極との間の絶縁壁が、第1組の電極を覆う連続層に設けた、および、第1組の電極の間隔部内で基板にも設けた、絶縁性薄膜の部分を作つており、

また、第2組の電極が、絶縁性薄膜の壁部分の間の凹所に形成され、および、基板を覆う絶縁性薄膜の部分の上にも形成されており、

第2組の電極の上面が、第1組の電極の上面を覆う絶縁性薄膜の部分の表面と面一であり、もって

第1および第2組の電極が等しい高さ $h_a = h_b$ を有し、かつ

電極および絶縁性薄膜を有する薄膜電極層が、電極手段における全域平面層を作つてゐる。

#### 【0027】

電極手段の他の好適例では、第1組の電極と、第2組の電極との間の絶縁壁が、第1組の電極の側縁をその上面まで覆う層に設けた、および、第1組の電極の間の間隔部内で基板にも設けた、絶縁性薄膜の部分を作つており、また

第2組の電極が、絶縁性薄膜の壁部間の凹所に形成され、および、基板を覆う部分の上にも形成されており、

第2組の電極は、絶縁壁の上縁、および、第1組の電極の上面と面一になつてあり、

10

20

30

40

50

第2組の電極は、高さ  $h_b = h_a -$  を有しており、また電極を有する薄膜電極層と、絶縁材料とが、電極手段における厚さ  $h_a$  の全域平面層を作っている。

#### 【0028】

本発明電極手段の他の好適例では、第1組の電極と、第2組の電極との間の絶縁壁が、第1組の電極を基板位置まで覆う層に設けた絶縁性薄膜の部分を作っており、また

第2組の電極が、絶縁性薄膜の壁部分の間の凹所に形成され、および、露出した基板の上にも直接形成され、かつ第1組の電極の上面を覆う絶縁性薄膜の部分の上面と面一になつてあり、もつて

第1組の電極が、高さ  $h_a = h_b -$  を有し、かつ

電極を有する少なくとも1つの薄膜電極層と絶縁性薄膜とが、電極手段における、厚さ  $h_b$  の全域平面層を作っている。 10

#### 【0029】

本発明の目的、および、その他の利点と特徴は、本発明による、以下の電極手段の製造方法によって達成される。すなわち、この製造方法は、

厚さ  $h_a$  を有する導電材料から成る平面層を基板上に被着する段階と、

導電材料から成る平面層をパターン化して、幅  $w_a$  、厚さ  $h_a$  を有する第1組の帯状電極を形成する段階であり、パターン化処理で形成される電極間の凹所によって相互に離隔した電極となる前記段階と、

導電材料の部分を除去し、第1組の帯状電極の間の基板の表面を露出させる段階であつて、第1組の平行電極は、電極間の凹所の幅に等しく、かつ、 $w_a$  と同等以上の距離  $d$  だけ離れている段階と、 20

第1組の電極の少なくとも側縁を覆う電気絶縁材料から成る薄膜を形成する段階と、

第1組の電極の側縁を覆う絶縁性薄膜の間の凹所に導電材料を被着させて、電極層が電極手段における全域平面層として得られるように、幅  $w_b$  、厚さ  $h_b$  を有する第2組の電極を形成する段階とによって特徴づけられる。 30

#### 【0030】

本発明方法の好適例では、第1組の電極と、基板の露出面の両者を覆う全域層として絶縁性薄膜が形成され、第2組の電極に対する導電材料が、第1組の電極の間の凹所内、および、絶縁性薄膜の上に被着され、第2組の電極の上面が、第1組の電極を覆う絶縁性薄膜と面一になるように薄膜電極層が平坦化される。

#### 【0031】

本発明方法のその他の好適例では、第1組の電極および基板の露出面を覆う全域層として前記絶縁性薄膜が形成され、第2組の電極に対する導電材料が、第1組の電極の間の凹所内、および、絶縁性薄膜の上に被着され、第1組の電極を覆う絶縁性薄膜が除去されて、電極の上面を出し、両組の電極の上面、および、絶縁性薄膜の上縁が、全て、薄膜電極層の上面と面一になるように、薄膜電極層が平坦化される。 40

#### 【0032】

本発明方法のその他の好適例では、第1組の電極と、基板の露出面の両者を覆う全域層として絶縁性薄膜を形成し、凹所の底部にある絶縁性薄膜を除去し、第1組の電極を基板位置まで覆う絶縁性薄膜のみを残して、基板の表面を露出させ、第2組の電極の導電材料を凹所内に被着させ、第2組の薄膜電極層の上面、および、第1組の電極を覆う絶縁性薄膜の表面が、全て、薄膜電極層の上面と面一になるように、薄膜電極層を平坦化する。 40

#### 【0033】

本発明方法の好適例では、基板上に形成された1つの薄膜電極層を覆って、薄膜電極層に接触する、機能媒体から成る全域層を被着させ、次いで、基板上に電極層を形成するために用いる操作と同様な操作によって、第2の電極層を機能媒体から成る全域層に、直接、形成する。次いで、好適には、機能媒体の全域層に形成された薄膜電極層を覆う、基板または背面体を設けることができる。

#### 【0034】

50

本発明方法では、電極手段の電極を成す導電材料および／または基板材料を、表面酸化に適する材料として選択し、かつ、適宜少なくとも1つの酸化プロセスでいずれかの表面を酸化することによって絶縁性薄膜を形成するのが好ましい。

### 【0035】

最後に、上記目的、ならびにさらなる利点および特徴は、各電極手段の電極がそれぞれの電極層に設けられ、電極手段の電極がすべてほぼ同じ幅wを有し、各手段の電極は、厚さの絶縁性薄膜によって互いに電気的に絶縁され、の大きさは幅wの数分の一であり、wの最小値がプロセスで制限される最小輪郭サイズfと同程度になることによって、それに対する機能媒体の機能素子の充填率が1に近づき、機能素子の数が、電極手段の間に挟持された機能媒体の全面積A、および前記プロセスで制限される最小輪郭サイズfによって定められる最大値に近づき、前記最大値は $a / f^2$ によって定められることを特徴とする装置による本発明によって達成される。10

### 【0036】

最後に、前記目的、および、その他の利点と特徴は、前記装置のマトリックス・アドレス指定可能な配列を構成する機能素子に対する受動マトリックス・アドレス指定を実行するための本発明装置における本発明電極手段の使用、および、前記装置のマトリックス・アドレス指定可能な配列を構成する機能素子に対する能動マトリックス・アドレス指定を実行するために、各機能素子が少なくとも1つの能動切換構成部品に接続される、本発明装置における本発明電極手段の使用による本発明によって達成される。20

### 【実施例】

### 【0037】

本発明は、添付の図面を併用し、電極手段およびその製造方法の以下の例示的な実施例の説明、ならびに装置の実施例の説明を読むことによって、より深く理解されるであろう。。

### 【0038】

次に、本発明による電極手段における電極層の様々な実施例の製造を例示する図1から5を参照しながら、本発明による電極手段を説明する。これらの図は極めて概略的で、本発明による電極手段における電極層の製造段階および構造を説明するのに必要とされる十分な数の帯状電極を示しているにすぎないことに留意されたい。

### 【0039】

本発明による電極手段は、勿論、この種のものであって、電極が、その間にあり、その中の電極に接触する機能媒体の全域層3に直面する2つの電極層L1およびL2を備える。第2の電極層2は、勿論、前述したのと同様の段階および実施例で製造することができ、適切に配置し、適切な方法で、第1の電極層L1および機能媒体の全域層3により組み立てることができる。これについては、電極手段EMの2つの好ましい実施例と、どのようにして電極手段の当該実施例を積層して、本発明による複数の電極手段を備えた容量構造体を形成できるかということを参考しながら、以下にさらに説明する。30

### 【0040】

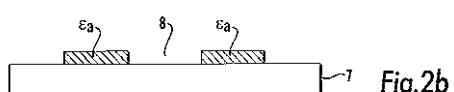

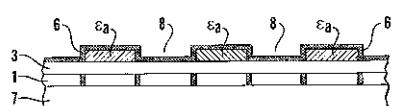

図2aにおいて、任意の材料で構成することができるが、いずれの場合も絶縁性であるか、または少なくとも1つの絶縁性表面を有する必要がある基板に導電材料の層を設ける。この層を、場合によっては、基板7の絶縁性表面に設けることが可能である。図2bに示される第2の段階において、基板7を覆う全域層として設けられた導電材料が、その間に凹所8を形成するように距離dだけ離された第1組E<sub>a</sub>の電極を形成する平行帯状電極<sub>a</sub>にパターン化される。例えば、従来のフォトミクロリソグラフィを用いたり、フォトマスクを使用し、続くエッチングでパターン化する場合は、パターン化処理で得ることができる電極<sub>a</sub>の幅wは、大きさfのプロセスで制限される最小輪郭に限定されることが理解されるであろう。次いで、fの値は、0.15μm以下の範囲になり、これは電極<sub>a</sub>の最小幅、ならびにその間の凹所8の幅に対応する。40

### 【0041】

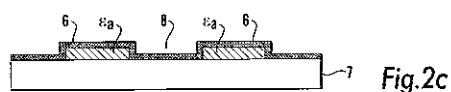

図2cに示される第3の処理段階において、帯状電極<sub>a</sub>、および基板7の露出部が、50

任意の好適な処理、例えば化学蒸着、吹付けなどによって被着または形成される絶縁材料の薄膜6によって被覆される。当業者に知られているように、次いで、この絶縁層6を、極端に薄く、例えば数ナノメートルの範囲の厚さにし、実際、電極<sub>a</sub>の幅w<sub>a</sub>に比べて非常に小さい厚さとすることができる。

#### 【0042】

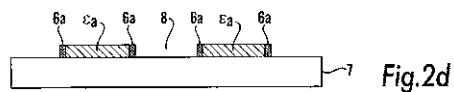

図2dに示される第4の処理段階において、電極<sub>a</sub>および基板7を被覆する絶縁層6を除去し、この除去を、電極<sub>a</sub>のパターン化に用いた処理と異なる処理によって、あるいは好適な処理の組合せによって行うことができるが、従来、好ましい処理は、続くエッティングを伴うフォトマスクを使用することが可能であり、フォトマスクは電極<sub>a</sub>の幅w<sub>a</sub>、および適宜その間の凹所8の幅dに合わせられる。第4の処理段階の後で、図2dに示されるような構造体が得られる。薄膜層のなかで残っている唯一の部分は、帯状電極<sub>a</sub>の側方に沿って伸びるその壁部6aである。10

#### 【0043】

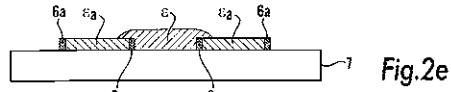

図2eに示される第5の処理段階において、いずれの場合も電極組E<sub>a</sub>に使用されるものと同じでありうる他の導電材料を、電極<sub>a</sub>間の凹所8に設ける。勿論、電極<sub>a</sub>と凹所8の両方を覆う全域層にこの導電材料を設けることも可能であるが、ここに示される図では、主に凹所のみを充たすために被着する。この被着は、図2aにおける層の被着と同様の方法、すなわち蒸気蒸着、吹付けなどによって行うことができる。

#### 【0044】

最後に、図2fは、第1組E<sub>a</sub>の電極<sub>a</sub>の間にあり、絶縁性薄膜6の絶縁壁部6aによってそれから電気的に絶縁される第2の電極組E<sub>b</sub>の帯状電極<sub>b</sub>を形成するように、導電材料を絶縁壁部6aの高さまで除去する平坦化段階を示す図である。図2eに例示される処理段階に対する凹所8aは、ケーシング型と見なすことが可能で、任意の好適なケーシング法により導電材料をそのなかに設けることが可能である。20

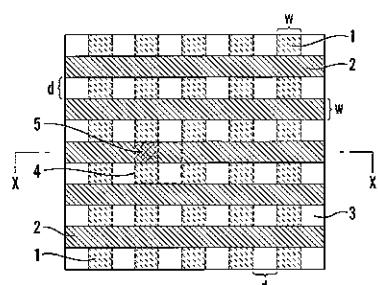

#### 【0045】

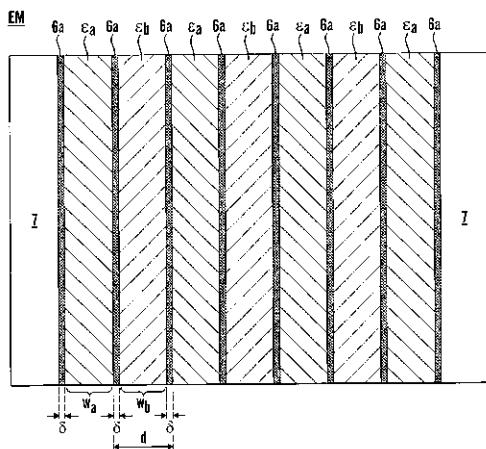

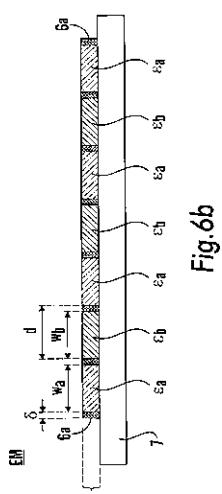

本発明による電極手段に使用され、図2fに概略的に例示されている電極層の得られる実施例を図6aの平面図に示す。ここで、電極層Lは、基板7に設けられた複数の帯状平行電極<sub>a</sub>、<sub>b</sub>を備える。電極<sub>a</sub>は、図2bのパターン化段階から得られる電極<sub>a</sub>の第1組E<sub>a</sub>に属するものと考えることができ、前者間の電極<sub>b</sub>は、図2eおよび2fに示される処理段階から得られる電極の第2組E<sub>b</sub>に属するものと見なすことができる。ここで、2つの電極<sub>a</sub>間の距離をd、電極<sub>a</sub>の幅をw<sub>a</sub>、電極<sub>b</sub>の幅をw<sub>b</sub>とする。ここで、w<sub>a</sub>、w<sub>b</sub>およびdの値はすべて同程度で、ほぼ同様の大きさを有し、その最小値は、図2bの構造体を得るためにパターン化処理で得ることができるプロセスで制限される最小輪郭fの値によって与えられることになる。同時に、電極<sub>b</sub>と<sub>a</sub>の間の絶縁壁部6aの厚さは、fによって制約されず、ナノメートル・スケールまでの厚さを有することができ、唯一の制約は、電極<sub>a</sub>と<sub>b</sub>の間の電気的故障および絶縁破壊を防ぐ絶縁性薄膜を設けることである。すなわち、必要に応じて電極を整合する基板7の表面も電気絶縁性を有するとすれば、すべての平行帯状電極<sub>a</sub>、<sub>b</sub>は、互いに電気的に絶縁されることになる。図6bに示される図6aの平面図の断面は、さらなる説明は不要であるが、両電極<sub>a</sub>、<sub>b</sub>、および絶縁壁部6aの高さがhであること、また式d = w<sub>b</sub> + 2が成立することに留意すべきである。電極間の距離dをw<sub>a</sub> + 2に選定すれば、電極<sub>a</sub>、<sub>b</sub>の幅が同じで、値wに等しくなり、すべての電極<sub>a</sub>、<sub>b</sub>は、同じ断面積を有し、同一の導電材料で構成されれば、同じ導電特性を有する。3040

#### 【0046】

達成可能な充填率に関して説明した、電極層Lを含む電極手段EMの利点を、図10aに示される本発明による装置の説明と併せて以下に説明する。

#### 【0047】

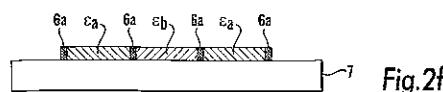

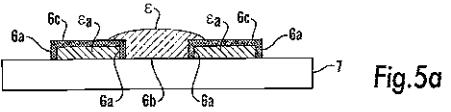

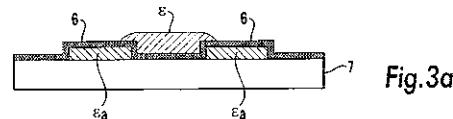

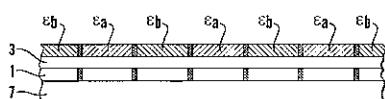

図3aおよび3bは、本発明による電極手段EMにおける電極層Lの第2の実施例を製造するための処理段階を示す図である。図3aに示される処理段階は、すでに所定の位置50

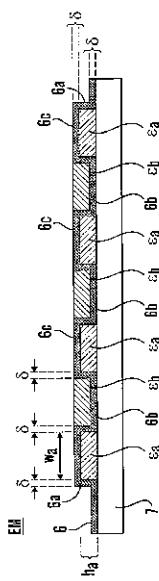

にある絶縁性薄膜6を有する、図2cに示される構造体を開始点とする。図3aに示されるように、ここでも電極<sub>a</sub>の導電材料と同じでありうる導電材料<sub>b</sub>を、任意の好適な方法によって図2cの凹所8に被着し、次いで平坦化段階を実施して、本発明による電極層Lの第2の実施例に符合する、図3bに例示される構造体を得る。この実施例において、第1組の電極<sub>a</sub>は、電極<sub>a</sub>の側縁に沿う部分6a、その上面の部分6c、ならびに凹所8の底部の部分6bを形成する絶縁性薄膜6によって被覆され、次に、その上面が、電極<sub>a</sub>を覆う絶縁性薄膜6の部分6cと面一になる導電材料<sub>b</sub>によって被覆される。図7の断面に示されるこの第2の実施例に関し、電極6aは、その上に設けられる任意の接触材料とオーム接觸していないが、絶縁性薄膜6は、電極<sub>b</sub>と接触材料の間の容量性結合を防ぐものではないことに留意すべきである。したがって、本発明による電極層Lのこの実施例は、電極<sub>a</sub>および<sub>b</sub>が、容量性結合のみを必要とする雰囲気で使用される用途に適することになる。さらに、電極<sub>b</sub>の高さ<sub>hb</sub>は、絶縁性薄膜6の厚さ<sub>h</sub>に対応する量だけ、電極<sub>a</sub>の高さ<sub>ha</sub>より小さくなることに留意すべきである。電極<sub>a</sub>および<sub>b</sub>の両方に対して同じ電極断面を得るためにには、これらの電極の高さ<sub>hb</sub>が、平坦化段階の後にわずか<sub>ha</sub>-になり、その上面が絶縁薄膜部6cと面一になる(図7参照)ことに対応して、電極<sub>b</sub>の幅<sub>wb</sub>を相応に大きくする必要がある。

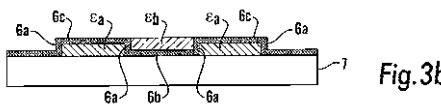

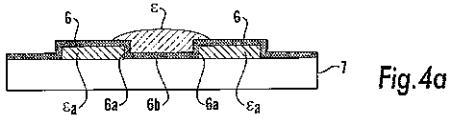

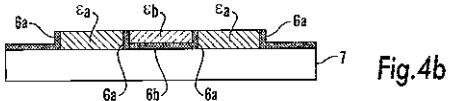

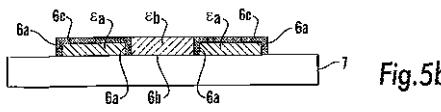

## 【0048】

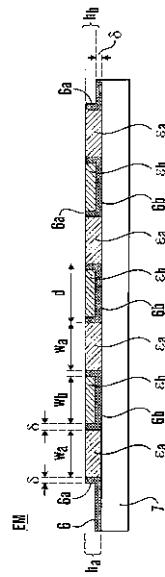

本発明による電極層Lの第3の実施例を製造するための処理段階を図4aおよび4bに示す。図4aは、図2cに示される構造体を開始点とし、基板7および電極<sub>a</sub>を全体に覆う絶縁性薄膜6が設けられる。ここで、図2cの凹所8を充たして覆う導電材料<sub>b</sub>が被着され、図4bに示される電極を形成することを目的とする図4aの構造体が得られる。導電材料<sub>b</sub>は、勿論、先述の電極<sub>a</sub>に使用されるものと同じでありうる。ここで、平坦化段階を行い、電極<sub>a</sub>を覆う絶縁性薄膜6の部分、ならびに過剰の電極材料を除去し、図4bに示されるように、すべて互いに面一で、かつ絶縁性薄膜6の壁部6aの上面と面一になる電極層の表面に露出された電極<sub>a</sub>および<sub>b</sub>を残す。ここで、この第3の実施例は、図8の断面に例示されているものに対応し、すべての電極<sub>a</sub>および<sub>b</sub>が上面を露出しているため、その上に設けられる接触子または機能材料に対する容量性かつオーム結合に好適であることがわかる。電極<sub>a</sub>、<sub>b</sub>の最小幅<sub>wa</sub>および<sub>wb</sub>に関する考慮もここでは有効である。さらに、電極<sub>a</sub>の高さ<sub>ha</sub>は、薄膜6の部分6bの厚さ<sub>h</sub>に対応する量だけ、電極<sub>b</sub>の高さ<sub>hb</sub>と異なることがわかる。これは、先述のように、例えば、電極<sub>a</sub>およびBGA同じ導電性を有する導電材料で構成される場合に、同じ導電容量を得るためにそうすることが望ましい場合に、断面が等しい電極<sub>a</sub>、<sub>b</sub>を得るために、パターン化処理において電極<sub>a</sub>間の距離を大きくしなければならないことを示している。任意の好適な手段、例えば化学的機械的研磨、制御エッティングまたは制御ミクロ研磨処理によって平坦化を容易に行うことができる。

## 【0049】

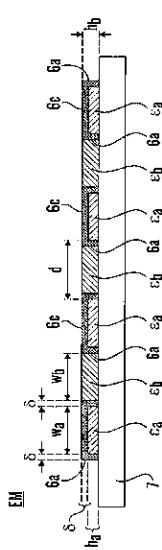

最後に、図5aおよび5bは、本発明による電極層の第4の実施例を製造するための、図2bまたは図2cの処理段階から導かれる処理段階を示す図である。出発点が図2bであれば、これは、電極構造体<sub>a</sub>が好適な特性の導電材料、例えばチタニウムまたはアルミニウムのような金属から構成される場合は、それらを選択的に酸化して、図5aに示すように、縁部または壁部6aおよび上面部6cで電極を覆う絶縁性薄膜6を形成できることを示すものである。しかし、図5aに示される処理段階も、図2cに示される状況から出発することが可能で、絶縁性薄膜層の基板を被覆している箇所、すなわち凹所8内をエッティング除去し、絶縁性薄膜6の部分6aおよび6cによって被覆される電極<sub>a</sub>のみを残す必要があることを示す。しかし、第2のマスキング・段階の使用を伴い、処理コストを増加させることになる。電極<sub>b</sub>に対する導電材料<sub>b</sub>を被着する前に電極<sub>a</sub>の選択的酸化を利用することによって、電極<sub>a</sub>を覆う絶縁性薄膜6を設けるより安価な方法が得られる。導電材料<sub>b</sub>を電極<sub>a</sub>の間の凹所8に被着し、次いで、勿論、前述のように絶縁壁部6aによってそこから隔離させた後、図5bに示される平坦化段階で過剰の導電材料<sub>b</sub>を除去して、図5bに示される壁部6aの間の凹所8に電極<sub>b</sub>を形成し、直接接觸す

10

20

30

40

50

る基板 7 の絶縁表面をそれによって覆う。

#### 【0050】

この第4の実施例は、図9aの平面図および図9bの断面に示されるものに対応し、そこからは、電極<sub>a</sub>が高さ<sub>ha</sub>を有し、電極<sub>b</sub>が異なる高さ<sub>hb</sub>を有することによって、電極<sub>a</sub>、<sub>b</sub>の断面積は、それぞれ<sub>wa</sub>·<sub>ha</sub>および<sub>wb</sub>·<sub>hb</sub>となり、これは、同じ幅<sub>wa</sub>=<sub>wb</sub>=<sub>w</sub>を有する電極<sub>a</sub>、<sub>b</sub>を形成するためには、第1組E<sub>a</sub>の電極<sub>a</sub>の間の距離<sub>d</sub>を図2bに示されるパターン化段階で調整しなければならないことを示している。ここで、絶縁性薄膜6は、部分6cで電極<sub>b</sub>の上面をも覆うため、これは、勿論、図9aに示される電極層Lの第4の実施例を拘束して、その上に被着される任意の接触材料との容量性結合を生成することを示すものである。図9aの平面図は、勿論、前者における電極<sub>a</sub>が絶縁性薄膜部6cによって被覆されることを除いては、図6aの平面図に示される実施例と類似している。

#### 【0051】

すでに上述したように、任意の好適な手段、例えば化学蒸着、吹付けまたはスパッタリングによって絶縁性薄膜6を被着することができるが、電極材料および基板材料が酸化に適するものであれば、例えば熱酸化法によって絶縁性薄膜を形成して、図2cに示される構造体を得ることが可能である。これは、電極デバイスにおける電極材料に広く使用されるチタニウム、アルミニウムおよび銅のような材料を使用して金属材料として被着される電極材料に適用可能である。ここで、基板7が例えばシリコンで構成される場合は、電極<sub>a</sub>で被覆されていない基板の箇所を同時に酸化して、その上にSiO<sub>2</sub>の絶縁層を形成することが可能である。また、すでに上述したように、これらの電極間の凹所に導電材料を被着する前に、電極<sub>a</sub>の選択的酸化によって、図5aに示される絶縁性薄膜部を形成することが可能である。当該酸化法については当業者によく知られているため、ここではそれ以上の説明を行わない。

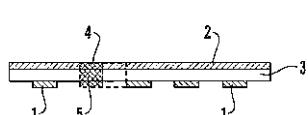

#### 【0052】

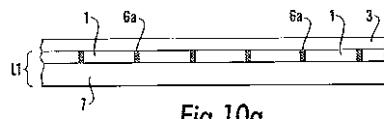

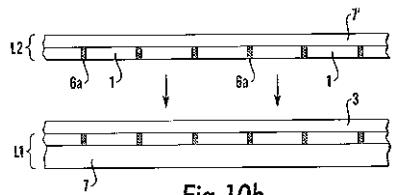

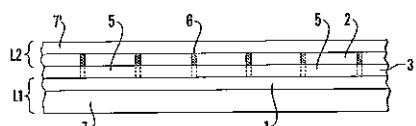

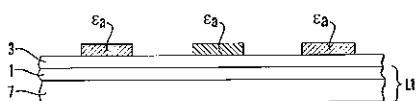

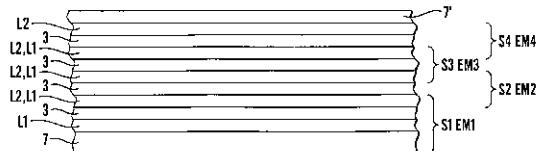

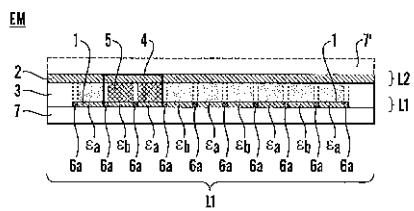

図10aは、本発明による電極手段における第1の電極層L1の実施例で、電極1を被覆し、それと接触して設けられる機能媒体の全域層で被覆された実施例の断面を示す図である。図10bは、第1の電極層の基板7に対応する背面体7'に設けられた電極を有する第2の電極層L2を示す図である。この電極層は、勿論、あらゆる点において、第1の電極層L1に類似し、第1の電極層L1および機能媒体である全域層を備えた機構に接合されて、本発明による集成電極手段EMを形成する。その結果得られる後者の実施例が図10cの断面に示されているが、ここでは第1の電極層L1が90°回転し、第2の電極層は、その電極2が電極層L1の電極に交差または直交して配置されるように設けられる。得られる構造体は、機能媒体である全域層に接触し、それぞれの電極層L1、L2の交差電極1、2が重なる箇所に機能素子が定められる密な電極マトリックスを形成する。電極マトリックスの形態の電極手段の配置は、例えば、第1の電極層L2における選択電極1および第2の電極層における選択電極2に電圧を印加することによって、全域機能媒体の機能素子のマトリックス・アドレス指定を可能にする。これらの選択電極が電場を交差し、または機能媒体3に対して電位差を加えることができ、アドレスされた機能素子におけるその物理的パラメータの、例えばそのインピーダンスの変化という形態の変化を含む。機能媒体が、以下に説明する分極性強誘電材料またはエレクトレット材料体であれば、図10cに示されるデバイスを受動マトリックス・アドレス指定可能なメモリと見なすことができ、次いで第1および第2の電極層それぞれの電極に電圧を印加すると、交差電極1と2の間に形成された機能素子5が極性化され、それが、勿論、強誘電性体またはエレクトレット・メモリにおけるメモリ・セルになる。機能媒体がメモリ材料であるときのメモリ・セルに対するアドレス指定動作、例えば書き込みおよび読み取り動作と併用して駆動および制御については、当業者が容易に理解するように、電極を周辺ドライバおよび制御回路に接続しなければならないことを理解すべきである。図10dは、電極手段を含むいくつかの当該デバイスをどのように積層して、機能媒体を有する複数の電極手段を形成し、容量デバイスを実現できるかを示す図である。ここで、不図示の周辺回路に適切に接続さ

れているときに、それぞれ電極手段であるこの種のデバイスを個別に平行にアドレスすることができる今や容易である。

#### 【0053】

本発明による電極手段の第2の実施例が図11a～11dに示されており、ここでは、その製造における各種段階が示されている。図11aは、図2fに示されたものに対応し、基板7に設けられた第1の電極層L1の実施例を示す図である。ここで、機能媒体3の全域層を第1の電極層L1に塗布し、その電極に接触させる。この全域層を平坦化し、次いで、その上に第2の電極層L2が設けられているときの基板として使用する。これを行うための処理は、図2aからfに示される段階に類似し、得られる電極層L2は、背面体で覆われていないが、機能媒体3の第2の層がその上に被着される前に平坦化され、第3の電極層L3の被着に向けた基板を形成する。この処理を繰り返すことができ、ここで、図11cに示すように、複数の電極手段EM1およびEM2を有する積層構造体がどのようにして得られるかがわかる。しかし、本発明による電極手段を有するデバイスのこの容量実施例は、ここでは第1の電極手段の第2の電極層L2が、第2の電極手段EM2の第1の電極層L1を形成すること等の点において、図10dに示されるものとは異なる。結果は、n個の電極手段EM1からEMnを有する積層デバイスにおいて、電極層の総数は、積層構造体における電極手段が基板または背面体7および7'によって互いに隔離されているときのように2nにならず、n+1になる。これにより、この種の容量実施例における完成構造体の寸法(厚さ)が低減されることになる。しかし、第2の電極手段から、最後から2番目の電極手段までの電極層は、すべてそのいずれかの側で機能媒体層3に接続することが可能であるため、この実施例ではすべての第2の電極手段のみ、例えば第1および第3の電極手段などにみをアドレスすることができる。

#### 【0054】

第2の電極層L2を機能媒体に直接被着すると、例えば機能媒体の材料が融点の低い有機材料であり、第2の電極層L2が、ある種類の無機または金属材料の導体として被着されるとときに特定の問題を生じるおそれがある。例えば、機能媒体が、ポリマーまたはコポリマーで構成された強誘電またはエレクトレット・メモリであるときは、この材料は200付近の融点を有することになり、その金属蒸着、すなわちこの種の材料に金属被膜を設けると、その表層の材料が溶融するおそれがある。また、平行帯状電極形成するパターン化段階における次のエッティングは、この種の材料の特性にとって好ましくない。しかし、例えばポリマー材料の形態の機能的媒体に悪影響を与えるほど高い熱応力を引き起こすことなく金属蒸着層を設けるための蒸着法を用いることが可能であることがわかった。例えば電子またはイオン・ビームを使用する様々な吹付けおよびスパッタリング法を、機能媒体に課さなければならぬ熱的制約条件に適合可能な熱量域で行うことができ、パターン化段階において特別な注意を払う場合も、例えば金属蒸着層をパターン化するためのイオン反応処理に高度に選択性を有する反応物質を使用することによって、機能媒体の材料の機能特性の劣化を避けることができる。すなわち、これには、第2の層L2の電極を形成するのに用いられる同材料の金属蒸着、およびそれに続くエッティングが必要であっても、機能媒体の層3を、続く第2の電極層の被着およびパターン化に向けた基板として採用することができる。

#### 【0055】

次に、図12a、12bおよび12cに関連して、本発明に係わり、本発明の電極手段を含む装置について説明する。この説明から、いかにして本発明による電極手段が、この種の装置において、充填率を1に近づけることが可能であるかということも明らかになる。

#### 【0056】

機能媒体が全域層3に設けられ、本発明による電極手段EMを形成する2つの電極層L1とL2の間に挟持される、マトリックス・アドレス指定可能なデバイスに限定される実施例における図12aの平面図に本発明による装置が示されている。使用される機能材料の種類に応じて、図6から9に示される実施例のいずれかでありうる第1の電極層L1は

10

20

30

40

50

、電極層 L 2 と同一であるが、それには、ここに示されるように、電極層 L 1 の対応する電極 1 に対してある角度で、好ましくは垂直に配置された平行帯状電極 2 が設けられる。電極 1 および 2 が重なる場合は、機能素子 5 は、その間の機能媒体 3 に定められる。機能素子 5 は、半導電性無機または有機材料、または好ましくは有機物、例えばポリマーまたはコポリマーでありうる強誘電体またはエレクトレット体の如き、極性を帶び、ヒステリシスを示すことが可能な誘電体でありうる。後者の場合は、結合は容量性になり、図 7 または図 9 の断面に示される電極層 L の実施例の使用を可能にする。本発明による装置の実施例の以下の説明は、簡略化するために、好ましくはポリマーおよびコポリマーの形態の有機材料として選択される機能媒体を有するデータ記憶デバイス、特に強誘電データ記憶デバイスの実施例に限定される。しかし、本発明による装置の実施態様は、これに限定されず、他の可能性があることを当業者であればわかるであろう。さらに、理解しやすいように、図 12 a には、すべての駆動、感知および制御回路を示していないが、実用的な実施例において、シリコンをベースとした CMOS 技術で実装し、これが同じ材料で構成される場合は基板 7 に設けることが可能である。次いで、すべての電極 1 および 2 を、当業者が十分に理解する方法で、ルーティングし、前記回路に接続することになる。

10

20

30

## 【0057】

すでに記載したように、線 X - X に沿ってとらえた図 12 a の装置の断面を示す図 12 b を見ればよくわかるように、機能材料 3 は、電極層 L 1 と L 2 の間に挟持されている。電極 1 と 2 の重複部分または交差部分では、機能媒体 3、すなわち強誘電体にメモリ・セル 5 が定められ、それぞれ第 1 の電極層 L 1 および第 2 の電極層 L 2 の重複電極 1 および 2 に電圧を印加すると、メモリ・セル 5 におけるこの材料を初期状態から極性化することができる。勿論、ヒステリシスを示すことが可能である強誘電性メモリ材料 3 の極性状態を、そこに論理値を記憶するために永久的に設定することができ、かつ / または極性の符合（方向）を逆に切り換えることができ、その現象は、メモリ・セルの論理状態、すなわち二進 0 または二進 1 を検出するために、いわゆる破壊的読み取り処理で生じさせることができる。しかし、読み取りは、例えばメモリ・セル 5 を定める電極 1 および 2 に電圧を印加することによって読み取りを行った後もセルの論理状態が変化せず、その極性を切り換えるほどの規模でないような非破壊的な場合もある。物理的な観点では、電極層 L 1 および L 2 の電極 1、2 の重複部分、ならびにその間に挟持され、メモリ・セル 5 を形成する強誘電体 3 をコンデンサ構造と見なすことができ、この種の強誘電メモリは、一般に容量性データ記憶デバイスの種類として分類される。いずれの場合も、それぞれの電極層 L 1 および L 2 は、厚さ  $a$  が電極  $a$  および  $b$  の幅  $w$  のわずか数分の一で、最も好ましくは最小工程限界または工程規定特徴  $f$  に対応する絶縁材料の非常に薄い膜 6 によってのみ分離されるため、本発明による電極手段 EM は、充填率を 1 まで増加させることができることがわかるであろう。いずれの場合も、電極  $a$  および  $b$  の幅  $w_a$  および  $w_b$  は異なっていてもよいが、 $w_a \sim w_b$  として、実用的な幅は同じ値  $w$  を有するものと見なすことができることに留意されたい。

40

50

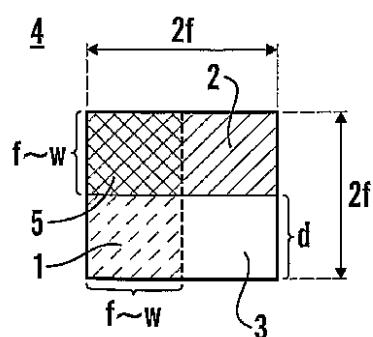

## 【0058】

これは、図 12 c に示されるように、4 つのメモリ・セル 5<sub>1</sub> から 5<sub>4</sub> を含む平面部 4 を考えればよくわかる。電極間の絶縁壁 6 a が占める領域は、セル 5<sub>1</sub> から 5<sub>4</sub> の領域を定め、電極層 L 1、L 2 における電極自体は、 $4f^2 + 8f + 4$ <sup>2</sup> になる。これは、

が  $f$ 、または電極 1、2 の幅  $w$  の数分の一にすぎないため、本発明による装置において充填率が 1 に近づくことを示し、電極層 L 1 と L 2 の間に挟持される機能媒体 3 の領域のほぼ 100% が機能素子またはセルによって占められ、その最小サイズが  $f^2$  になることを意味する。例えば、 $f \sim w$  を 1 に設定し、 $= 0.01f$  とすれば、平面部の領域が  $4 + 8 \cdot 0.01 + 0.0004 \sim 4.08$  になり、充填率が  $4 / 4.08 = 0.98$ 、すなわち 89% になる。アクセス可能な機能媒体の面積を A とした場合のマトリックスにおける機能素子またはセル 5 の最大数は、本発明による装置においては  $A / f^2$  に近くなる。例えば、適用される設計規則が  $f$  を  $0.2 \mu m$  に設定し、機能媒体 3 の面積 A を  $10^6 \mu m^2$ 、すなわち  $0.98 \cdot 10^6 / 0.2^2 = 24.5 \cdot 10^6$  に設定する場合は、1 ピ

50

ットを記憶するメモリ・セルとしてアドレス指定可能な機能素子3を設けることが可能であり、記憶密度が約25Mビット/mm<sup>2</sup>であることが示される。従来技術で知られる電極を最小工程限定特徴fによって定められる距離dだけ離す場合は、図10cに示される平面部4は、1つのセル5のみを含むため、充填率が0.25から25%になるが、勿論、達成可能なセルの最大数は、本発明による電極手段EMを使用したときに達成することができる数の1/4になる。

#### 【0059】

このことは、本発明による装置では、2つの電極層L1およびL2、ならびにその間に挟持された機能媒体3を有する單一デバイスは、従来技術における4つの当該デバイスと同じ能力を有し、積層されて容量データ記憶装置を形成する。しかし、図12bに示されるようなデバイスを積層して、容量が大きく記憶密度が高い容量データ記憶デバイス、例えば電極層L2の上面の基板7を、積層体における第1のデバイスと次のデバイスの間の隔離および/または絶縁層として機能するように設けた容量データ記憶デバイスを製造できることを回避するものではない。その結果は、勿論、いずれにせよ、積層容量データ記憶装置において本発明を採用するデバイスの数のわずか1/4で同じ容量を達成することができる。したがって、同じデータ記憶容量を得るために従来の技術で必要とされるような多数の積層デバイスを使用することに特有の問題が回避される。

#### 【0060】

特に、電極層を形成するための最終段階に適用することができる平坦化処理を極めて高い精度で行い、本発明による大面積電極手段においても、ナノメートル・スケールまでの全体平面性を達成できる。例えば、すでに述べたように、機能材料への直接的な金属蒸着としても受けられる従来技術の電極手段を阻害する凹凸または不均一性を伴うことなく、化学的機械的研磨を適用して、完成電極手段を提供することができる。

#### 【0061】

したがって、より多くのデバイスが積層されると、積層デバイスの不均一性の増加を避けることが不可能になる。加えて、各々の個別的なメモリ・デバイスにおける機能媒体のセルに対するデータの書き込みおよび読み取りを行うために電圧を印加するときに導入される熱的、機械的応力による問題を回避することもできる。

#### 【0062】

本発明による電極手段EMにおける用途は、データ記憶装置に限定されるものではないが、この種の装置は、積層メモリ・デバイスで形成されてもいいなくても、特に有益である。当該装置の一般的な配置および構造、ならびに機能媒体に対するいくつかの可能な材料または材料の組合せについては、米国特許および欧州特許として授与され、本発明の出願人に属する前述の公開国際特許出願第WO98/58383号を参照することができる。この出願は、ケース・メモリにおけるデータ処理デバイスに対するアキテクチャを開示しているが、特に強誘電メモリ・デバイスに向けられているものではない。加えて、この公報は、例えば情報表示デバイスに適用される同様のアキテクチャをも開示している。

#### 【0063】

メモリ・デバイスの如き様々なデバイスに使用される電極手段EMに対する電極材料に関しては、すでに述べたように、任意の好適な導電材料、例えば電子デバイスで広く使用されるチタニウムまたはアルミニウムのような金属でありうる。電極材料は、無機材料、例えば導電性ポリマーであってもよいが、絶縁性薄膜を形成するのに用いられる処理、またはその部分を除去するのに用いられる処理に適合するものでなくてはならない。

#### 【0064】

本発明による電極手段EMの電極の幅は、相応して、最小工程限定特徴fによって定められる最小値を有することを理解すべきであるが、それは、勿論、第1の場合において、被着され、パターン化される第1組の電極<sub>a</sub>の幅、ならびにそのように制限されるその間の距離のみである。電極<sub>b</sub>は、パターン化処理に適用される設計規則によって制限されない方法によって被着することができる。これは、得られる特徴に対する最小の寸法的制約が、fの値よりはるかに小さい可能性があることを示している。勿論、例えば酸化、

10

20

30

40

50

蒸発蒸着または吹付けまたはスパッタリングによってほぼ単元素の寸法で行うことができる絶縁性薄膜の成膜にも同じことが当てはまる。唯一の要件は、電極層における電極のそれぞれの組  $E_a$  および  $E_b$  における隣接電極  $a$  と  $b$  の間に必要な電気的絶縁を与える必要があることである。また、従来のフォトミクロリソグラフィ法における  $f$  は、通常  $0 \sim 2 \mu m$ 、またはそれより幾分小さいのに対して、現在確立されている、または開発中の他の技術は、ナノスケールの特徴、すなわち数十ナノメートルまでの電極幅が可能とし、例えばナノスケール・レンジの化学的機械的処理を用いて必要な平坦性を達成することを可能として、いずれの場合も平面性の高い上面を有し、すべての構成部品、すなわち  $a$  および  $b$ 、ならびに絶縁性薄膜  $6$  がその上面と面一になる電極層  $L$  が製造される。

## 【0065】

10

一般に、平行帯状電極を有し、それぞれマトリックス・アドレス指定可能なデバイスを形成するように互いにある角度、好ましくは垂直に配置された一対の電極層に機能媒体が挟持された装置またはデバイスに、本発明による電極手段を使用すると、充填率を 1 に近づけ、電極のパターン化処理に対する適用可能な設計規則によってのみ制約される確定可能な機能素子またはセルの数を最大にすることが可能になる。特に魅力的なのは、例えば巻返し処理で本発明による電極層を作製した後に電極手段の連続帯を所望の寸法に切断することが可能な点である。ここで、機能媒体を電極層の 1 つの電極側に塗布することが可能で、その後に、本発明による第 2 の電極層が、その個々の電極を第 1 の電極層の電極に対して垂直にし、その電極を直面させて配置され、機能媒体に対して直接金属蒸着、すなわち上述したように、特に、例えば強誘電マトリックス・アドレス指定可能なデバイスを提供するのに使用されるポリマーまたはコポリマーの如き有機材料の場合は機能媒体の材料にとって好ましくないといえる処理で少なくとも第 2 の電極手段の電極を設けることを必要とせずに、本発明による電極手段  $E_M$  を形成するように、すでに塗布された第 1 の電極層の機能媒体と整合関係をもって設けられる。しかし、概略的な作製手順を能動マトリックス・アドレス指定可能なデバイスに容易に適用できないが、最近の開発に鑑みれば、これらは、例えばマトリックス・アドレス指定可能な強誘電メモリ・デバイスに対して特に魅力的な提案に思われる。能動マトリックス・アドレス指定可能な強誘電メモリ・デバイスは、複雑で電力消費量が大きいばかりでなく、本発明による電極手段で実現しても、その充填率は 1 よりはるかに小さくなる。例えば、I<sub>T</sub> および I<sub>C</sub> (一方はトランジスタ、一方はコンデンサ) の能動強誘電メモリ・セルの場合は、達成可能な充填率は、良くても  $0.67$  を超えることはない。

20

## 【0066】

30

あるいは、連続的または半連続的巻返し動作で電極手段を平坦化した後の最終的な処理段階でも、慎重に制御した厚さにより、または第 2 の平坦化を伴って機能媒体を塗布することが可能である。次いで、それぞれの電極を互いに垂直関係に保ちながら、機能媒体がすでに所定位置にある 2 つの電極層を適切に配置させて、個々の電極層を所望の寸法に切断した後に、本発明による電極手段を形成し、各電極手段の所定位置の機能媒体と整合関係をもって接合させることができる。この作製手順を繰り返して、例えば、所定の数だけ積層した本発明による複数の電極手段を含む容量データ記憶デバイスを形成し、本発明による装置を容量構成で実現することが可能である。

40

## 【0067】

高度に平面化された電極層を有する本発明による電極手段は、電極寸法、すなわちこれらの電流導電容量に対して均一であることが必要とされる電極の断面積の慎重な制御を可能にする。これは、つまりは、機能媒体における機能素子に対するアドレス指定は、測定されたインピーダンス(抵抗性または容量性)状態に要素を誘導または設定するために、これらの要素に同じ電位差を生じさせることを示している。また、例えば強誘電メモリ材料の切換電圧の一部である電圧による書き込みおよび読み取りプロトコルを使用するときは、より高い信頼性が得られるが、受動マトリックス・アドレス指定体系における非活動的ワード・ビット線に加えられる静的電位を慎重に制御し、例えばマトリックスにおける非アドレス・メモリの容量性結合および妨害を回避することが可能になる。

50

【図面の簡単な説明】

【0068】

【図1a】従来技術の受動マトリックス・アドレス指定可能なデバイスを示し、当該デバイスにおける従来の方法で達成可能な充填率を例示する図である。

【図1b】従来技術の受動マトリックス・アドレス指定可能なデバイスを示し、当該デバイスにおける従来の方法で達成可能な充填率を例示する図である。

【図1c】従来技術の受動マトリックス・アドレス指定可能なデバイスを示し、当該デバイスにおける従来の方法で達成可能な充填率を例示する図である。

【図2a】本発明による電極層の第1の実施例を製造するための処理段階を模式的に示す図である。

10

【図2b】本発明による電極層の第1の実施例を製造するための処理段階を模式的に示す図である。スにおける従来の方法で達成可能な充填率を例示する図である。

【図2c】本発明による電極層の第1の実施例を製造するための処理段階を模式的に示す図である。

【図2d】本発明による電極層の第1の実施例を製造するための処理段階を概略的に示す図である。

【図2e】本発明による電極層の第1の実施例を製造するための処理段階を概略的に示す図である。

【図2f】本発明による電極層の第1の実施例を製造するための処理段階を模式的に示す図である。

20

【図3a】本発明による電極層の第2の実施例を製造するための処理段階で、図2cの処理段階から導かれる処理段階を模式的に示す図である。

【図3b】本発明による電極層の第2の実施例を製造するための処理段階で、図2cの処理段階から導かれる処理段階を模式的に示す図である。

【図4a】本発明による電極層の第3の実施例を製造するための処理段階で、図2cの処理段階から導かれる処理段階を模式的に示す図である。

【図4b】本発明による電極層の第3の実施例を製造するための処理段階で、図2cの処理段階から導かれる処理段階を模式的に示す図である。

30

【図5a】本発明による電極層の第4の実施例を製造するための処理段階で、図2bまたは図2cの処理段階から導かれる処理段階を模式的に示す図である。

【図5b】本発明による電極層の第4の実施例を製造するための処理段階で、図2bまたは図2cの処理段階から導かれる処理段階を模式的に示す図である。

【図6a】本発明による電極手段における電極層の第1の実施例の平面図を模式的に示す図である。

【図6b】図6aにおける実施例の断面図を模式的に示す図である。

【図7】本発明による電極手段における電極層の第2の実施例の断面を模式的に示す図である。

【図8】本発明による電極手段における電極層の第3の実施例の断面を模式的に示す図である。

【図9a】本発明による電極手段における電極層の第4の実施例の平面図を模式的に示す図である。

40

【図9b】図9aにおける実施例の断面を模式的に示す図である。

【図10a】本発明による電極手段における第1の電極層で、機能媒体の全域層により被覆された第1の電極層の断面を示す図である。

【図10b】第1の電極層の1つとしての類似の実施例における第2の電極層で、本発明による電極手段を形成するように配置された第2の電極層を示す図である。

【図10c】本発明による電極手段の好ましい実施例を示す図である。

【図10d】どのようにして複数の電極手段を積層して容量デバイスを形成できるかを示す図である。

【図11a】本発明による電極手段の他の実施例の製造における段階を示す図である。

50

【図11b】本発明による電極手段の他の実施例の製造における段階を示す図である。

【図11c】本発明による電極手段の他の実施例の製造における段階を示す図である。

【図11d】本発明による電極手段の他の実施例の製造における段階を示す図である。

【図11e】どのようにして本実施例による複数の電極手段を積層して容量デバイスを形成できるかを示す図である。

【図12a】本発明による装置の実施例における受動マトリックス・アドレス指定可能なデバイスで、本発明による電極手段を有する受動マトリックス・アドレス指定可能なデバイスの平面図である。

【図12b】図12aの線X-Xに沿ってとらえた断面を示す図である。

【図12c】図12aの詳細を示し、本発明によって達成可能な充填率を例示する図である。 10

【図1a】

Fig. 1a (Prior art)

【図1b】

Fig. 1b (Prior art)

【図1c】

Fig. 1c (Prior art)

【図2a】

Fig. 2a

【図2b】

Fig. 2b

【図 2 c】

Fig.2c

【図 2 d】

Fig.2d

【図 2 e】

Fig.2e

【図 2 f】

Fig.2f

【図 3 b】

Fig.3b

【図 4 a】

Fig.4a

【図 4 b】

Fig.4b

【図 5 a】

Fig.5a

【図 5 b】

Fig.5b

【図 3 a】

Fig.3a

【図 6 a】

Fig.6a

【図 6 b】

Fig.6b

【 四 7 】

Fig. 7

【 四 8 】

Fig. 8

【図 9 b】

Fig. 9b

【図 9 a】

Fig.9a

【 図 1 0 a 】

Fig. 10a

【図 1 0 b】

Fig. 10b

【図 1 0 c】

Fig. 10c

【図 1 0 d】

Fig. 10d

【図 1 1 a】

Fig. 11a

【図 1 1 b】

Fig. 11b

【図 1 1 c】

Fig. 11c

【図 1 1 d】

Fig. 11d

【図 1 2 a】

Fig. 12a

【図 1 1 e】

Fig. 11e

【図 1 2 b】

Fig. 12b

【図 1 2 c】

Fig. 12c

## 【国際調査報告】

## INTERNATIONAL SEARCH REPORT

International application No.

PCT/NO 02/00414

## A. CLASSIFICATION OF SUBJECT MATTER

**IPC7: G11C 11/22, H01L 21/8239**

According to International Patent Classification (IPC) or to both national classification and IPC

## B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)

**IPC7: G02F, G11C, H01L**

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

**SE,DK,FI,NO classes as above**

Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)

**WPI DATA, EPO-INTERNAL, PAJ**

## C. DOCUMENTS CONSIDERED TO BE RELEVANT

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                  | Relevant to claim No. |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| A         | EP 0902465 A1 (STMICROELECTRONICS S.R.L.),<br>17 March 1999 (17.03.99), abstract<br><br>--                                                                                          | 1-5,7,9-24            |

| A         | US 4952031 A (ICHIRO TSUNODA ET AL),<br>28 August 1990 (28.08.90), abstract<br><br>--                                                                                               | 1-5,7,9-24            |

| A         | PATENT ABSTRACTS OF JAPAN<br>Vol 1999, No. 07<br>31 March 1999 (1999-03-31)<br>& JP 7106450 A (OLYMPUS CO LTD; SYMMETRICS CORP)<br>21 April 1995 (1995-04-21)<br>abstract<br><br>-- | 1-5,7,9-24            |

Further documents are listed in the continuation of Box C. See patent family annex.

\* Special categories of cited documents:

- "A" document defining the general state of the art which is not considered to be of particular relevance

- "E" earlier application or patent but published on or after the international filing date

- "L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

- "O" document referring to an oral disclosure, use, exhibition or other means

- "P" document published prior to the international filing date but later than the priority date claimed

"T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

"X" document of particular relevance: the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

"Y" document of particular relevance: the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art

"&" document member of the same patent family

Date of the actual completion of the international search

13 February 2003

Date of mailing of the international search report

19 -02- 2003

Name and mailing address of the ISA/

Swedish Patent Office

Box 5055, S-102 42 STOCKHOLM

Facsimile No. + 46 8 666 02 86

Authorized officer

Erik Miliander/MN

Telephone No. + 46 8 782 25 00

## INTERNATIONAL SEARCH REPORT

|                               |

|-------------------------------|

| International application No. |

| PCT/NO 02/00414               |

## C (Continuation). DOCUMENTS CONSIDERED TO BE RELEVANT

| Category* | Citation of document, with indication, where appropriate, of the relevant passages          | Relevant to claim N°. |

|-----------|---------------------------------------------------------------------------------------------|-----------------------|

| A         | US 6072716 A (JOSEPH M. JACOBSON ET AL),<br>6 June 2000 (06.06.00), abstract<br><br>--      | 1-5,7,9-24            |

| P,A       | EP 1187123 A2 (HEWLETT-PACKARD COMPANY),<br>13 March 2002 (13.03.02), abstract<br><br>----- | 1-5,7,9-24            |

**INTERNATIONAL SEARCH REPORT**

|                                             |

|---------------------------------------------|

| International application No.<br>NO02/00414 |

|---------------------------------------------|

**Box I Observations where certain claims were found unsearchable (Continuation of item 1 of first sheet)**

This international search report has not been established in respect of certain claims under Article 17(2)(a) for the following reasons:

1.  Claims Nos.: because they relate to subject matter not required to be searched by this Authority, namely:

2.  Claims Nos.: 6, 8 because they relate to parts of the international application that do not comply with the prescribed requirements to such an extent that no meaningful international search can be carried out, specifically:

**Contain disclaimers**

3.  Claims Nos.: because they are dependent claims and are not drafted in accordance with the second and third sentences of Rule 6.4(a).

**Box II Observations where unity of invention is lacking (Continuation of item 2 of first sheet)**

This International Searching Authority found multiple inventions in this international application, as follows:

1.  As all required additional search fees were timely paid by the applicant, this international search report covers all searchable claims.

2.  As all searchable claims could be searched without effort justifying an additional fee, this Authority did not invite payment of any additional fee.

3.  As only some of the required additional search fees were timely paid by the applicant, this international search report covers only those claims for which fees were paid, specifically claims Nos.:

4.  No required additional search fees were timely paid by the applicant. Consequently, this international search report is restricted to the invention first mentioned in the claims; it is covered by claims Nos.:

**Remark on Protest**

- The additional search fees were accompanied by the applicant's protest.

No protest accompanied the payment of additional search fees.

**INTERNATIONAL SEARCH REPORT**

Information on patent family members

30/12/02

International application No.

PCT/NO 02/00414

| Patent document cited in search report | Publication date | Patent family member(s) |              | Publication date |

|----------------------------------------|------------------|-------------------------|--------------|------------------|

| EP 0902465 A1                          | 17/03/99         | US                      | 6326266 B    | 04/12/01         |

| US 4952031 A                           | 28/08/90         | JP                      | 63316085 A   | 23/12/88         |

|                                        |                  | US                      | 5064275 A    | 12/11/91         |

|                                        |                  | JP                      | 1931691 C    | 12/05/95         |

|                                        |                  | JP                      | 6061022 B    | 10/08/94         |

|                                        |                  | JP                      | 63316086 A   | 23/12/88         |

|                                        |                  | JP                      | 1013527 A    | 18/01/89         |

|                                        |                  | JP                      | 1889401 C    | 07/12/94         |

|                                        |                  | JP                      | 6017954 B    | 09/03/94         |

| US 6072716 A                           | 06/06/00         | NONE                    |              |                  |

| EP 1187123 A2                          | 13/03/02         | CN                      | 1340861 A    | 20/03/02         |

|                                        |                  | JP                      | 2002109794 A | 12/04/02         |

|                                        |                  | US                      | 6473388 B    | 29/10/02         |

---

フロントページの続き

(81)指定国 AP(GH,GM,KE,LS,MW,MZ,SD,SL,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,MD,RU,TJ,TM),EP(AT,BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,IE,IT,LU,MC,NL,PT,SE,SK,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AT,AU,AZ,BA,BB,BG,BR,BY,BZ,CA,CH,CN,CO,CR,CU,CZ,DE,DK,DM,DZ,EC,EE,ES,FI,GB,GD,GE,GH,GM,HR,HU,ID,IL,IN,IS,JP,KE,KG,KP,KR,KZ,LC,LK,LR,LS,LT,LU,LV,MA,MD,MG,MK,MN,MW,MX,MZ,N0,NZ,OM,PH,PL,PT,RO,RU,SD,SE,SG,SI,SK,SL,TJ,TM,TN,TR,TT,TZ,UA,UG,US,UZ,VN,YU,ZA,ZM,ZW

(72)発明者 ゲデセン、ハンス、ゲデ

ベルギー国、ブリュッセル、リュ フルトン 17

(72)発明者 レイスタッド、ゲイール、アイ。

ノルウェー国、ザンドヴィカ、ヨングストゥベン 19

F ターム(参考) 5F033 HH08 HH18 MM01 QQ08 QQ09 QQ77 RR03 SS08 SS11 SS26

TT08 VV10 VV16

5F083 FR01 FZ10 GA09 JA36 JA37 JA39 KA20 LA11 NA08 PR10

PR12 PR22