(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7127066号

(P7127066)

(45)発行日 令和4年8月29日(2022.8.29)

(24)登録日 令和4年8月19日(2022.8.19)

(51)国際特許分類

|         |                  |     |         |        |   |

|---------|------------------|-----|---------|--------|---|

| G 0 1 T | 1/24 (2006.01)   | F I | G 0 1 T | 1/24   |   |

| H 0 1 L | 27/144 (2006.01) |     | H 0 1 L | 27/144 | K |

| H 0 1 L | 27/146 (2006.01) |     | H 0 1 L | 27/146 | D |

| H 0 1 L | 31/10 (2006.01)  |     | H 0 1 L | 31/10  | A |

| H 0 4 N | 5/32 (2006.01)   |     | H 0 4 N | 5/32   |   |

請求項の数 15 (全22頁) 最終頁に続く

(21)出願番号 特願2019-563170(P2019-563170)

(86)(22)出願日 平成30年5月8日(2018.5.8)

(65)公表番号 特表2020-521953(P2020-521953

A)

(43)公表日 令和2年7月27日(2020.7.27)

(86)国際出願番号 PCT/SE2018/050475

(87)国際公開番号 WO2018/212698

(87)国際公開日 平成30年11月22日(2018.11.22)

審査請求日 令和3年3月29日(2021.3.29)

(31)優先権主張番号 15/595,087

(32)優先日 平成29年5月15日(2017.5.15)

(33)優先権主張国・地域又は機関

米国(US)

(73)特許権者 512120638

プリズマティック、センサーズ、アクチ

ボラグ

PRISMATIC SENSORS AB

スウェーデン国ストックホルム、ロスラ

グストゥルスパッケン、21

(74)代理人 100091982

弁理士 永井 浩之

(74)代理人 100091487

弁理士 中村 行孝

(74)代理人 100105153

弁理士 朝倉 悟

(74)代理人 100107582

弁理士 関根 賀

(74)代理人 100118843

最終頁に続く

(54)【発明の名称】 X線撮像のための検出器

## (57)【特許請求の範囲】

## 【請求項1】

半導体基板を備えるエッジオン光子計数検出器であって、前記半導体基板は、

- X線源に対向するように構成された第1の端部と、入射X線の方向において、前記

第1の端部の反対側にある第2の端部と、

- N-2とするN個の深度セグメントを有し、前記深度セグメントのそれぞれが、電

荷収集金属電極を備える、少なくとも1つのストリップと、

- ドープ領域と絶縁領域とを備えた電荷収集側と、を備え

前記電荷収集金属電極のそれぞれは、対応するドープ領域の上に配置され、前記絶縁領域上に配置された、それぞれのルーティングトレースに接続され、それぞれの前記ルーティングトレースは、前記電荷収集金属電極から、前記第2の端部に配置されたフロントエンド電子回路に接続可能な読み出しパッドへと信号を伝達するように構成され、

前記ストリップの数は、少なくとも2つであり、

前記電荷収集金属電極の幅寸法は、ストリップピッチに対する前記電荷収集金属電極幅の比率が0.8未満であり、キャパシタンスを減少させるような寸法である、エッジオン光子計数検出器。

## 【請求項2】

前記半導体基板はシリコンを含む、請求項1に記載のエッジオン検出器。

## 【請求項3】

前記電荷収集金属電極および前記ルーティングトレースは、同じ金属から製造される、

請求項 1 または 2 に記載のエッジオン検出器。

【請求項 4】

前記電荷収集金属電極および前記ルーティングトレースは、单一金属層内に設けられる、請求項 3 に記載のエッジオン検出器。

【請求項 5】

前記金属はアルミニウムである、請求項 4 に記載のエッジオン検出器。

【請求項 6】

前記絶縁領域は、二酸化シリコンの領域を備える、請求項 1 から 5 のいずれか 1 項に記載のエッジオン検出器。

【請求項 7】

前記ストリップの数は、少なくとも 2 つであり、

前記ルーティングトレースの幅寸法は、ストリップピッチに対する前記ルーティングトレース幅の比率が 0.05 未満であり、キャパシタンスを減少させるような寸法である、請求項 1 から 6 のいずれか 1 項に記載のエッジオン検出器。

【請求項 8】

前記半導体基板には、前記第 2 の端部に配置された前記読み出しパッドに隣接する領域内にドープ領域が設けられている、請求項 1 から 7 のいずれか 1 項に記載のエッジオン検出器。

【請求項 9】

前記読み出しパッドに隣接する前記領域に、絶縁領域がさらに設けられ、これにより、前記ドープ領域と前記絶縁領域とが配置されて、前記ルーティングトレースが前記絶縁領域上を前記読み出しパッドまで延びるようなパターンを形成する、請求項 8 に記載のエッジオン検出器。

【請求項 10】

前記半導体基板は、テーパ形状を有し、これにより、前記半導体基板の第 1 の端部は、第 1 の幅を有し、前記半導体基板の第 2 の端部は、前記第 1 の端部よりも大きな第 2 の幅を有する、請求項 1 から 9 のいずれか 1 項に記載のエッジオン検出器。

【請求項 11】

前記半導体基板は、電荷収集金属電極の少なくとも 2 つのストリップを備え、前記ストリップは、前記電荷収集金属電極が、前記基板のテーパ形状に適合されたテーパパターン内の前記電荷収集側に設けられるように、互いに対し角度をなしている、請求項 10 に記載のエッジオン検出器。

【請求項 12】

前記半導体基板の前記第 2 の端部は、少なくとも 1 つの面取り角部を備える、請求項 1 から 1 のいずれか 1 項に記載のエッジオン検出器。

【請求項 13】

エッジオン検出器のための電荷収集面を製造するための方法であって、

- X 線源に対向するように構成された第 1 の端部と、前記第 1 の端部の反対側にある第 2 の端部と、を有する半導体基板を供給するステップ (S 1) と、

- 電荷収集面と称される、前記半導体基板の表面に、ドープ領域を設けるステップ (S 2) と、

- ドープ領域が設けられていない第 2 の表面の領域に、絶縁層を設けるステップ (S 3) と、

- 前記半導体基板の前記第 2 の端部に、読み出しパッドを配置するステップ (S 4) と、

- 前記ドープ領域と、前記絶縁層とを備える前記電荷収集面の上に、单一金属層を成膜するステップ (S 5) と、

- 前記单一金属層をパターニングして、

i ) 前記ドープ領域の上に、電荷収集金属電極を形成し、

i i ) 前記絶縁層の上に、前記電荷収集金属電極を前記読み出しパッドと接続するル

10

20

30

40

50

ーティングトレースを形成するステップ (S 6) と、

を含み、

ドープ領域 (R) が設けられていない前記第 2 の表面の領域に、絶縁層 F を設けるステップ (S 3) は、二酸化シリコン層を設けることを含み、

前記金属層をパターニングする前記ステップ (S 6) は、電荷収集金属電極の少なくとも 2 つのストリップを形成することを含み、前記電荷収集金属電極のそれぞれは、ストリップピッチに対する電荷収集金属電極幅の比率が、0.8 未満であるような幅寸法を有する方法。

【請求項 14】

半導体基板 B を供給する前記ステップ (S 1) は、シリコン基板を供給することを含み、

前記電荷収集面の上に单一金属層を成膜する前記ステップ (S 5) は、物理蒸着法 (PVD)、めっき法および / または化学蒸着法 (CVD) を使用して单一アルミニウム層を成膜することを含み、

前記单一金属層をパターニングするステップ (S 6) は、フォトリソグラフィの使用を含む、請求項 1\_3 に記載の方法。

【請求項 15】

前記金属層をパターニングする前記ステップ (S 6) は、ストリップピッチに対するルーティングトレース幅の比率が、0.05 未満であるような幅寸法を有するルーティングトレースを形成することをさらに含む、請求項 1\_3 に記載の方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、概して、X線撮像のための検出器に関し、特に、光子計数X線撮像のための半導体ストリップ検出器、および検出器を製造する方法に関する。

【背景技術】

【0002】

シリコン検出器などの半導体検出器は、X線撮像に広く使用されており、X線光子を検出し、相互作用する各光子によって放出された電荷キャリアを収集することにより、X線光子をデジタル信号またはデジタル画像に変換する。低エネルギーX線に関しては、検出器表面をX線に向けて、検出器面を複数の画素に分割することにより、半導体検出器を画素化するのが一般的である。各画素は、印加電界を通した画素内のX線相互作用によって生成された電荷を収集し、対応するフロントエンド電子回路に電荷を供給する。しかし、低い原子番号と低い密度のため、X線コンピュータ断層撮影などの高エネルギーX線による撮像では、例えばシリコン検出器の画素化構成は、0.5ミリメートル未満の基板厚さでは、全ての高エネルギーX線を捕捉することはできず、低い検出効率をもたらす。また、シリコンの原子番号が低いということは、検出器内のコンプトン散乱X線光子の一部が、光吸収光子よりも支配的であることを意味し、これは、散乱光子が検出器内の他の画素に信号を誘発することがあり、この信号はこれらの画素内ではノイズに等しいため、問題を生じさせる。

【0003】

シリコンの低吸収率の問題を解決する1つの方法は、シリコンの深度を、大幅に増加できるように、シリコン検出器のエッジを、入射X線に向けることにより、検出器のエッジオン構成を採用することである。X線検出器として、エッジオンジオメトリ (edge on geometry) の結晶シリコンストリップ検出器を最初に言及したのは、R. ノヴォトニー (R. Nowotny)、“医学および構造解析における Si マイクロストリップ検出器の応用 (Application of Si-microstrip-detectors in medicine and structural analysis) ”、物理学研究における核計器および方法 (Nuclear Instruments and Methods in Physics Research) 226 (1984) 、34~39である。シリコンは、胸部撮影用など、低エネルギーで動作するが、主に、

10

20

30

40

50

コンプトン散乱のより大きな部分およびこれに関連する問題のため、コンピュータ断層撮影などのより高エネルギー用ではないと結論づけている。

【 0 0 0 4 】

半導体検出器のエッジオンジオメトリは、米国特許第4,937,453号、ロバート・ネルソン (Robert Nelson) “放射線撮像用X線検出器 (X-ray detector for radiographic imaging)”、米国特許第5,434,417号、デイビッド・ナイグレン (David Nygren) “高解像度エネルギーに敏感なデジタルX線 (High resolution energy-sensitive digital X-ray)” および米国特許第7,291,841号B2、ロバート・ネルソン (Robert Nelson) ら、“核医学における強化されたSPECT、PET、およびコンプトン散乱撮像のための装置およびシステム (Device and system for enhanced SPECT, PET, and Compton scatter imaging in nuclear medicine)” でも提案されている。米国特許第5,434,417号では、セグメント化されたシリコンストリップ検出器の概念が説明されているが、電荷収集電極が、どのようにフロントエンド電子回路に接続されているか、およびルーティングトレースの配置が示されていない。米国特許第7,291,841号B2では、エッジオン検出器は、本発明には関わらない、いわゆるコンプトン撮像に使用される。ショウイチ・ヨシダ (Showichi Yoshida)、タカシ・オオスギ (Takashi Ohsugi) の論文 “シリコンストリップ検出器のX線コンピュータ断層撮影への応用 (Application of silicon strip detectors to X-ray computed tomography)”、物理学研究における核計器および方法 (Nuclear Instruments and Methods in Physics Research)、A 541 (2005)、412~420において、エッジオンコンセプトの実施が概説されている。この実施では、エッジオンシリコンストリップ検出器の間に配置された薄いタングステンプレートが、散乱X線の背景を減らし、低線量で画像コントラストを改善する。

【 0 0 0 5 】

エッジオンシリコンストリップ検出器の実装は、米国特許第8,183,535号B2

、マツ・ダニエルソン(Mats Danielsson)ら、“X線撮像用のシリコン

検出器アセンブリ(Silicon detector assembly for x-

ray imaging)”、チェン・シュウ(Cheng Xu)ら、“光子計数スペクトル

CT用のセグメント化シリコンストリップ検出器のエネルギー分解能(Energy

resolution of a segmented silicon strip de-

tector for photon-counting spectral CT)”、物

理学研究における核計器および方法(Nuclear Instruments and

Methods in Physics Research)、715(2013)、11

～17およびスジン・リウ(Xuejin Liu)ら、“マルチビン光子計数スペクトル

コンピューター断層撮影検出器用のスペクトル応答モデルとその応用(Spectral

response model for a multibin photon-counting spectral computed tomography detector

and its applications)”、医用画像ジャーナル(Journal

of Medical Imaging)2(3)(2015)033502に、さらに説

明されている。そして、説明されるように、各ストリップは、深度セグメントにさらに分

割され、X線コンピュータ断層撮影などの、X線撮像の高フラックス適用下でのフロント

エンド電子回路の負荷を軽減する。各深度セグメントで検出された光子変換信号は、深度

セグメントの対応する電荷収集電極と、フロントエンド電子回路のチャネルでの入力とを

接続するルーティングトレースを介して、フロントエンド電子回路の個々の処理チャネル

に伝達される。チェン・シュウ(Cheng Xu)らにより説明された、“光子計数スペ

クトルCT用のセグメント化シリコンストリップ検出器のエネルギー分解能(Energ

y resolution of a segmented silicon strip de-

tector for photon-counting spectral CT)”、物理

学研究における核計器および方法(Nuclear Instruments and

Methods in Physics Research)、715(2013)、11

～17

y resolution of a segmented silicon strip detector for photon-counting spectral CT)"、物理学研究における核計器および方法(Nuclear Instruments and Methods in Physics Research)、715(2013)、11~17には、2つの異なる金属層が、電荷収集電極用の1つの金属層と、ルーティングトレース用の他の層とを有するシリコン基板の電荷収集側に実装されている。マツ・ダニエルソン(Mats Danielsson)の、スウェーデン特許出願第9801677-7号には、放射線療法の監視のために電荷収集電極間に延びるルーティングトレースを有するシリコン検出器が記載されている。E.ベラウ(E. BELAU)ら、"Silicon strip detectors"、物理学研究における核計器および方法(Nuclear Instruments and Methods in Physics Research)214(2-3)(1983)、253~260は、電荷収集電極と同じ層にルーティングトレースを有する粒子物理学に使用される望遠鏡検出器を説明している。マツ・ダニエルソン(Mats Danielsson)ら、米国特許第8,183,535号B2の、コンプトン散乱が他のシリコン検出器に到達した結果としての散乱光子を部分的に止めるために、シリコン検出器のサブセットに取り付けられる"X線撮像用のシリコン検出器アセンブリ"では、薄くて重い金属シートが提案されている。

#### 【0006】

キャパシタンスは、検出器に関する最も重要なパラメータの1つであり、フロントエンド電子回路の電子ノイズのレベルに直接関連する。ノイズレベルは、任意の撮像検出器が満足のいく品質で画像を取得するために、可能な限り低くする必要がある。検出された光子が特定の時間間隔にわたって統合されるエネルギー統合検出器の場合、電子ノイズが読み出し信号に吸収され、結果として画質の低下をもたらす。光子計数検出器の場合、ノイズによって誘発される偽の計数を拒絶するには、最低エネルギー閾値を、ノイズフロアのレベルよりも高く設定する必要がある。したがって、新しい検出器を設計する場合、フロントエンド電子回路への入力容量を下げるることは、重要なタスクである。

#### 【0007】

シリコン検出器などの半導体検出器の場合、片面シリコンストリップ検出器を特定の例とすると、次の2つの寄与が、主なキャパシタンス源であり、それは、電荷収集電極とシリコン基板の裏面との間のキャパシタンスである裏面キャパシタンス、および隣接する電荷収集電極間のキャパシタンスであるストリップ間キャパシタンスである。電荷収集電極とフロントエンド電子回路の入力とを接続するルーティングトレースを有する検出器の場合、トレースキャパシタンスも重要な役割を果たし、トレースキャパシタンスには、隣接するルーティングトレース間のキャパシタンスと、ルーティングトレースと電荷収集電極との間のキャパシタンスと、が含まれまる。X線に敏感な領域の範囲外では、シリコン基板は注入層の大きな領域によって覆われていることがあり、その上に延びるルーティングトレースが存在する場合、これもキャパシタンスに寄与する。

#### 【0008】

特に高エネルギーX線による撮像のための医療撮像用のエッジオンシリコン検出器に、大きな関心が寄せられている。しかし、深度セグメントの数が1よりも大きい場合、フロントエンド電子回路へのルーティングに関連して、問題が発生する。チェン・シュウ(Cheng Xu)ら、"光子計数スペクトルCT用のセグメント化シリコンストリップ検出器のエネルギー分解能(Energy resolution of a segmented silicon strip detector for photon-counting spectral CT)"、物理学研究における核計器および方法(Nuclear Instruments and Methods in Physics Research)、715(2013)、11~17に、2つの金属層を有する設計が説明されているが、ルーティングトレースは、電荷収集金属電極のものとは異なる金属層上で動作しており、より高いキャパシタンスと実装の複雑さを示している。そして、2つの金属

10

20

30

40

50

層間の絶縁体材料によって、より多くのデッドスペースが追加され、これは、幾何学的効率の損失をもたらしている。また、米国特許第8,183,535号B2、マツ・ダニエルソン (Mats Danielsson) ら、"X線撮像用のシリコン検出器アセンブリ (Silicon detector assembly for x-ray imaging)" では、フロントエンド電極を、センサの領域またはセンサの上部に展開することが提案されているが、そうした場合、フロントエンド電子回路が、放射線にさらされ、フロントエンド電子回路も、スペースを取り、非常に高密度の梱包を不可能にする。したがって、実装の複雑さを低下させ、フロントエンド電子回路への最適なキャパシタンスで、ルーティングトレースをフロントエンド電子回路に導通する方法を提供することが望ましい。

10

【発明の概要】

【発明が解決しようとする課題】

【0009】

提案技術は、電荷収集電極をフロントエンド電子回路の入力に接続するルーティングトレースを有する検出器に関連する、キャパシタンス関連の問題のいくつかを少なくとも軽減する、エッジオン半導体検出器を提供することを目的とする。

【0010】

提案技術の特定の目的は、改善されたキャパシタンス特性を有する光子計数エッジオン半導体検出器を提供することである。特に、低いキャパシタンスを有する光子計数エッジオン半導体検出器を提供することである。

20

【0011】

もう1つの目的は、改善されたキャパシタンス特性、特に低いキャパシタンス特性を有する光子計数エッジオン半導体検出器を製造する方法を提供することである。

【課題を解決するための手段】

【0012】

提案技術の第1の態様によれば、エッジオン光子計数検出器が提供される。検出器は、X線源に対向するように構成された第1の端部と、入射X線の方向において、第1の端部の反対側にある第2の端部と、を備えた半導体基板を備える。半導体基板は、N-2とするN個の深度セグメントを有する少なくとも1つのストリップを備える。深度セグメントのそれぞれが、電荷収集金属電極を備える。半導体基板は、また、ドープ領域と絶縁領域とを備えた電荷収集側を備える。電荷収集金属電極のそれぞれは、対応するドープ領域の上に配置され、絶縁領域上に配置された、それぞれのルーティングトレースに接続される。それぞれのルーティングトレースは、電荷収集金属電極から、第2の端部に配置されたフロントエンド電子回路に接続可能な読み出しパッドEへと信号を伝達するように構成されている。

30

【0013】

提案技術の第2の態様によれば、エッジオン検出器のための電荷収集面を製造するための方法が提供される。

【0014】

方法は、半導体基板を供給するステップを含み、半導体基板は、X線源に対向するように構成された第1の端部と、第1の端部の反対側にある第2の端部と、を有する。方法は、また、電荷収集面と称される、半導体基板の表面に、ドープ領域を設けるステップを含み、ドープ領域は、第1の種類のドーピングを有する。方法は、また、ドープ領域が設けられていない第2の表面の領域に、絶縁層を設けるステップを含む。方法は、また、半導体基板の第2の端部に、読み出しパッドを配置するステップを含む。方法は、さらに、ドープ領域と、絶縁層とを備える電荷収集面の上に、単一金属層を成膜するステップを含む。方法は、さらに、単一金属層をパターニングして、i) ドープ領域の上に、電荷収集金属電極を形成し、ii) 絶縁層の上に、電荷収集金属電極を読み出しパッドと接続するルーティングトレースを形成するステップを含む。

40

【0015】

50

提案技術の実施形態は、優れたキャパシタンス特性を有するエッジオン検出器を提供する。このような検出器は、フロントエンド電子回路でノイズレベルが減少することを確保し、これは、取得画像の質を高める。さらなる利点は、後のセクションを読むことにより、明らかとなる。

【図面の簡単な説明】

【0016】

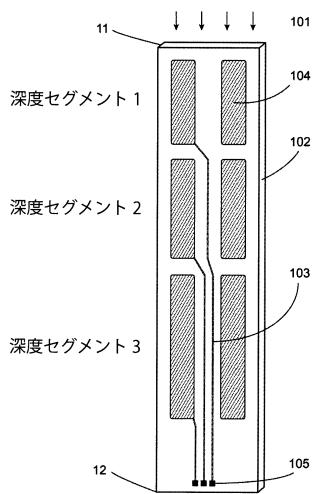

【図1】センサの一部の模式図。

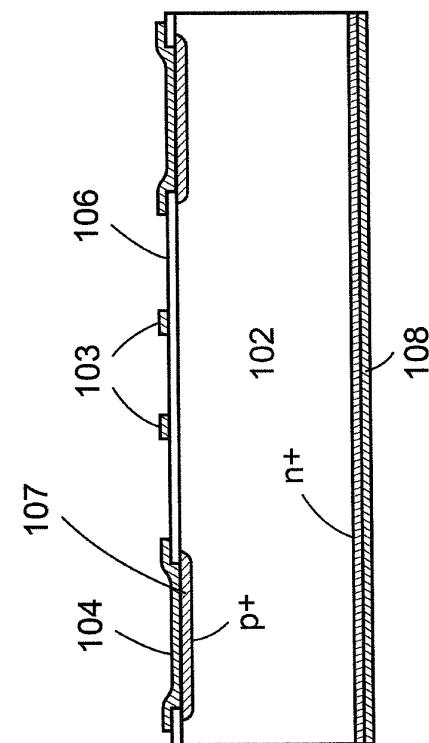

【図2】センサの断面の模式図。

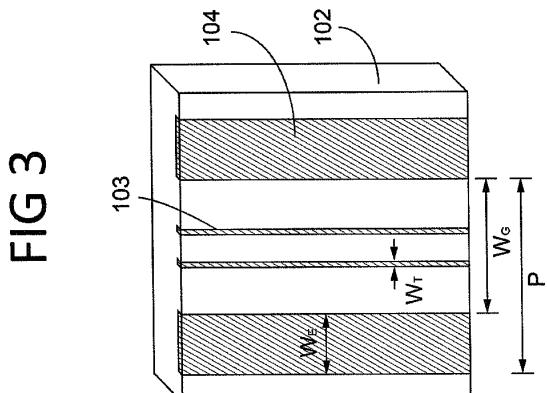

【図3】電荷収集電極およびルーティングトレースの幅を示す模式図。

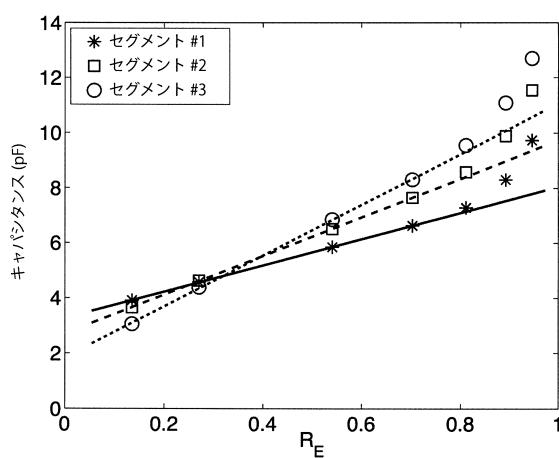

【図4】ストリップピッチに対する電極幅の比率の関数として、キャパシタンスを示す図。

10

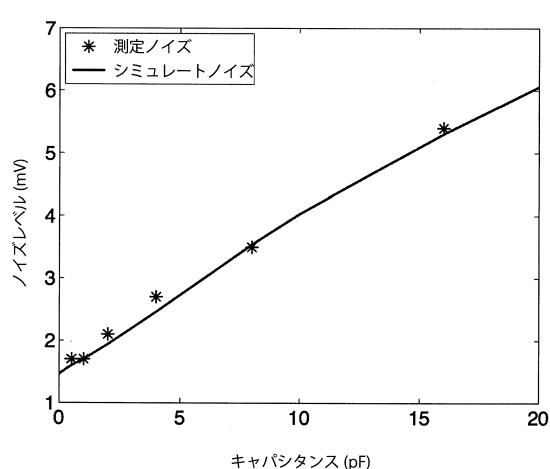

【図5】キャパシタンスの関数としてのノイズレベルを示す図。

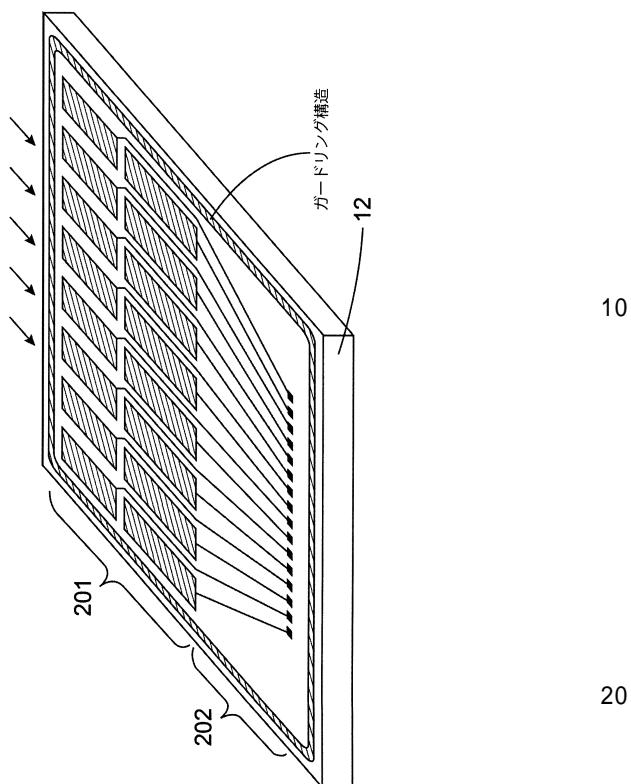

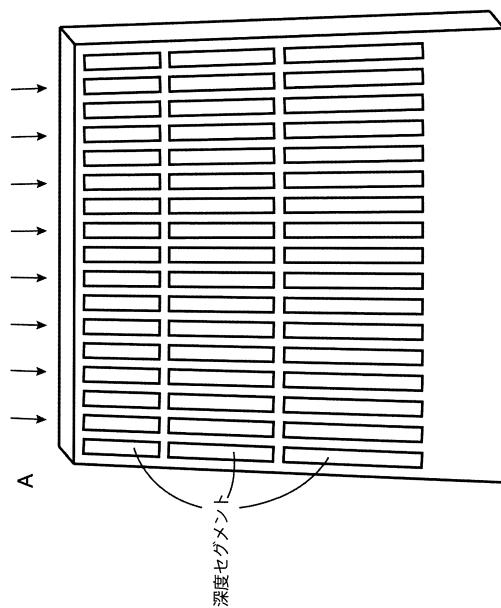

【図6】2つの深度セグメントを有するセンサと、どのようにしてルーティングトレースが読み出しパッドに接続されているかとを示す模式図。

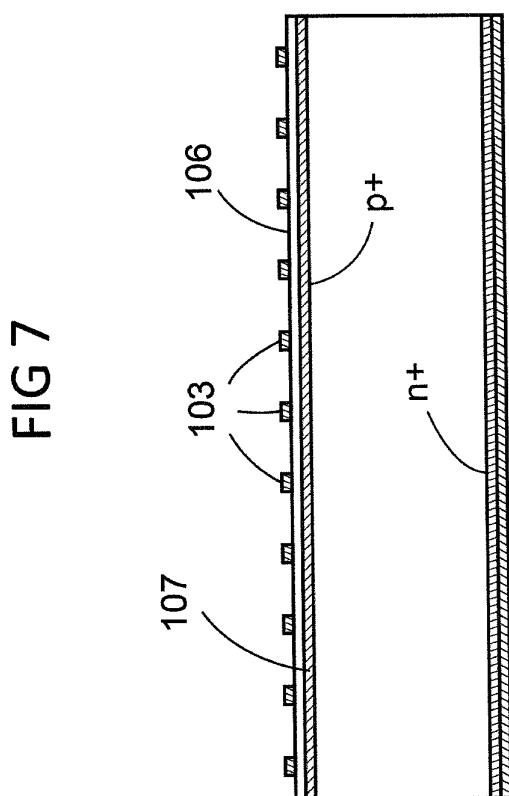

【図7】シリコン基板の底部領域の断面を示す模式図。

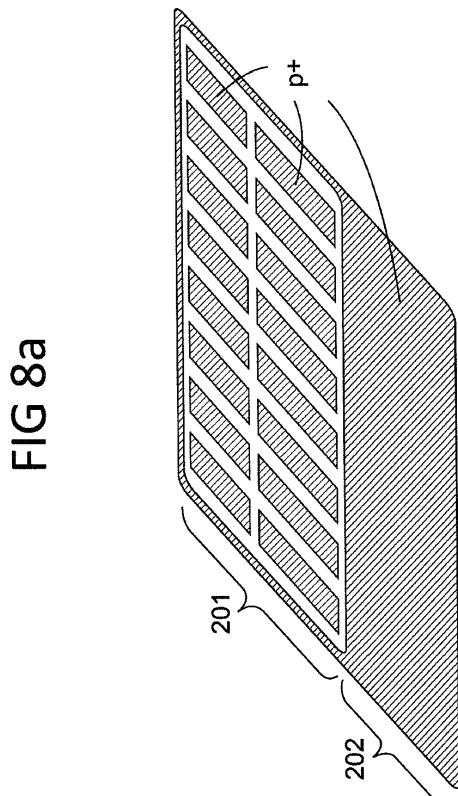

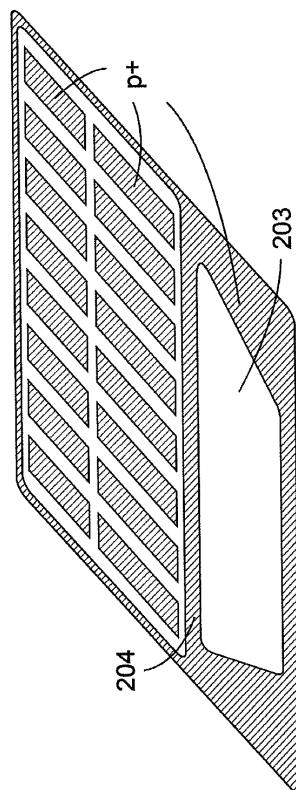

【図8a】完全なP+注入部を有するセンサ底部における、ルーティング領域を示す模式図。

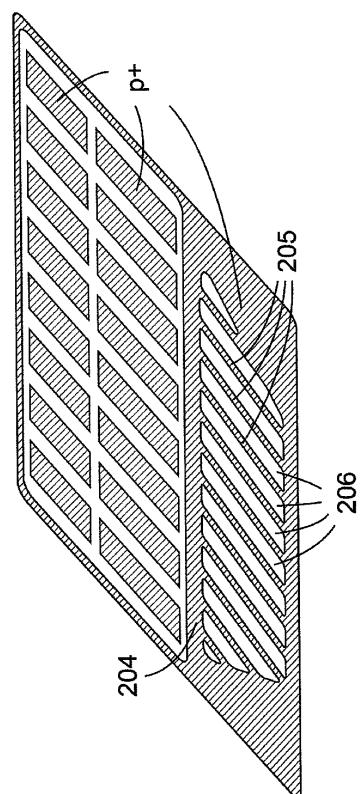

【図8b】ルーティングトレースの下にP+注入部がないセンサ底部における、ルーティング領域を示す模式図。

【図8c】ストリップ状に注入されたP+であるセンサ底部における、ルーティング領域を示す模式図。

20

【図9】台形形状のセンサの模式図。

【図10】面取りされた角部を有するセンサの模式図。

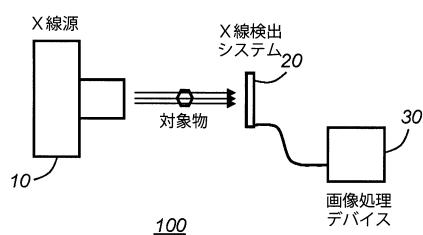

【図11】提案技術に係るエッジオン検出器を用いることが可能なX線撮像システムを示す図。

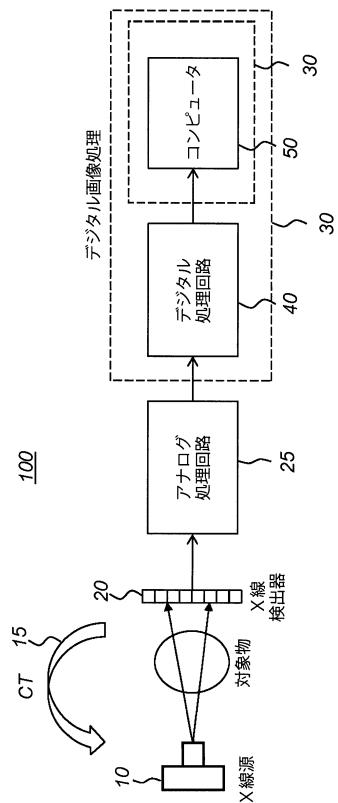

【図12】提案技術に係るエッジオン検出器を用いることが可能なX線撮像システムを示す別の図。

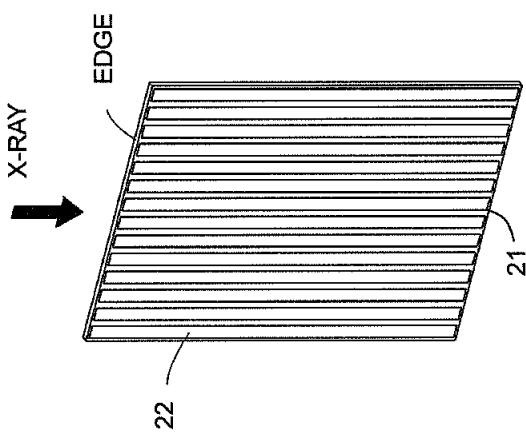

【図13】複数のストリップを有するエッジオン検出器を示す模式図。

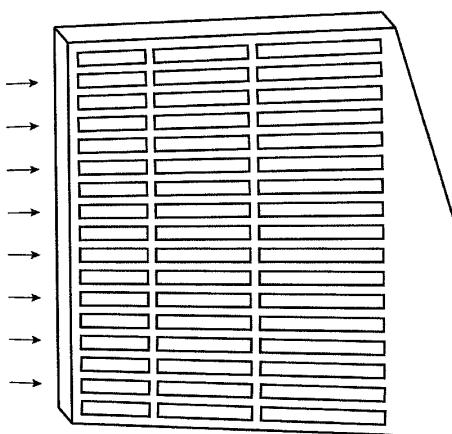

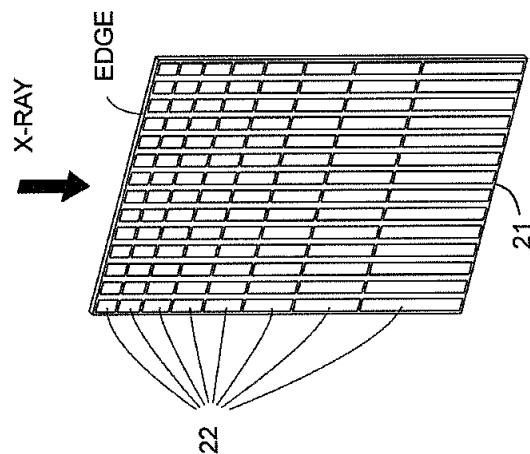

【図14】複数のストリップと複数の深度セグメントとを有するエッジオン検出器を示す模式図。

【図15】どのようにしてルーティングトレースがエッジオン検出器上のフロントエンド電子回路に接続されるかを示す模式図。

30

【図16】エッジオン検出器の電荷収集側を製造する方法を示すフロー図。

【発明を実施するための形態】

【0017】

本発明は、改善されたキャパシタンス特性を有するエッジオン半導体ストリップ検出器を、提供することを目的とする。提供されるストリップ検出器は、40 keV ~ 250 keVのエネルギー範囲内でのX線撮像における使用に適している。この目的を達成するために、金属層を、検出器の電荷収集側に実装して、電荷収集電極と同じ金属層に延びる導電ルーティングトレースを得るようにもよい。さらに、ストリップ検出器に関連するキャパシタンスを減少させるための方法および方策が提供される。

40

【0018】

提案技術の様々な実施形態を説明する前に、エッジオン半導体ストリップ検出器が用いられる技術の概要から始めるのが、有用であろう。このために、図11を参照する。この非限定の例において、X線撮像システム100は、基本的には、X線源10と、X線検出システム20と、関連する画像処理デバイス30と、を備える。一般に、X線検出システム20は、任意のX線光学素子により焦点を合わされ、物体または被験者あるいはその一部を通過した可能性がある、X線源10からの放射を記録するように構成されている。X線検出システム20は、適切なアナログ処理および読み出し電子部品(X線検出システム20に一体化してもよい)を介して、画像処理デバイス30に接続可能であり、画像処理デバイス30による画像処理および/または画像再構築を可能にする。

50

## 【0019】

図12に示すように、X線撮像システム100の別の例は、X線を放射するX線源10と、物体を通過した後のX線を検出するX線検出システム20と、検出器からの生電気信号を処理し、デジタル化するアナログ処理回路25と、補正を適用する、測定データを一時保存する、またはフィルタリングするなどのさらなる処理動作を、測定データに対して実行することが可能なデジタル処理回路40と、処理データを保存し、さらなる後処理および/または画像再構築を行うことが可能なコンピュータ50と、を備える。

## 【0020】

全体的な検出器を、X線検出システム20とみなしてもよく、または、X線検出システム20を、関連するアナログ処理回路25と組み合わせてもよい。

10

## 【0021】

デジタル処理回路40および/またはコンピュータ50を含むデジタル部は、X線検出器からの画像データに基づき画像再構築を行う、デジタル画像処理システム30とみなしてもよい。画像処理システム30は、よって、コンピュータ50、または代替案としてデジタル処理回路40とコンピュータ50との複合システムとして、あるいは場合によっては、デジタル処理回路をさらに画像処理および/または再構築に専用のものとする場合は、デジタル処理回路40自体として考えてもよい。

## 【0022】

一般的に用いられるX線撮像システムの例は、コンピュータ断層撮影(CT)システムであり、このシステムは、X線のファンまたはコーンビームを生成するX線源と、患者または物体を通過したX線の部分を記録するための対向するX線検出システムと、を含んでもよい。X線源および検出システムは、通常、撮像される物体の周りを回転するガントリーに搭載される。

20

## 【0023】

このため、図12に示されるX線源10と、X線検出システム20とは、CTシステムの一部として配置してもよく、例えば、CTガントリーに搭載可能であってもよい。

## 【0024】

X線撮像検出器に関する課題は、検出されたX線から最大の情報を抽出し、物体または被験者が密度、組成および構造に関して描写される、物体または被験者の画像に対する入力を供給することである。検出器として、フィルム画像を用いることが、なお一般的であるが、今日の検出器は、最も一般的には、デジタル画像を提供する。

30

## 【0025】

提案技術は、一部は、半導体エッジオン検出器の特定の設計に関する。半導体エッジオン検出器は、任意の適切な半導体材料を備えてよい。提案技術の特定の実施形態は、シリコンの検出器基板に関する。しかし、他の材料も可能である。光子計数X線検出器のための将来有望な材料は、テルル化カドミウム(CdTe)、テルル化亜鉛カドミウム(CZT)およびシリコン(Si)である。CdTeおよびCZTは、臨床CTで用いられる高エネルギーX線の高い吸収効率のため、いくつかの光子計数スペクトルCTプロジェクトで採用されている。しかし、これらのプロジェクトは、CdTe/CZTのいくつかの欠点のため進行が遅い。CdTe/CZTは、低い電荷キャリア移動度を有し、これは、臨床診療で見られるものよりも、10分の1のフラックスレートで、いくつかのパルスパイルアップを引き起こす。この問題を軽減する1つのやり方は、画素サイズを減少させることであるが、電荷共有およびKエスケープの結果として、スペクトル歪みの増加をもたらす。また、CdTe/CZTは、電荷トラッピングを受け、これは、光子フラックスが特定レベルを上回ると、出力計数率の急激な降下を起こす極性化をもたらす。

40

## 【0026】

対照的に、シリコンは、より高い電荷キャリア移動度を有し、極性化の問題もない。成熟した製造過程と、比較的低いコストも、その利点である。しかし、シリコンは、CdTe/CZTが持たない制限も有する。これに応じて、シリコンセンサは、その低い阻止能を補償するために、非常に厚くしなければならない。典型的には、シリコンセンサは、入

50

射する光子のほとんどを吸収するために、数センチメートルの厚さを必要とするのに対し、CdTe/CZTは、数ミリメートルのみを必要とする。他方で、シリコンの長い減衰経路は、検出器を、以下に述べるように、異なる深度セグメントに分割することを可能にする。これは、一方で、シリコンベースの光子計数検出器が、CT内の高いフラックスを正しく処理することを可能にする。

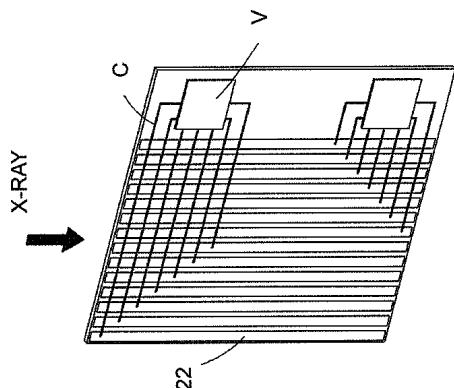

#### 【0027】

図13は、半導体検出モジュールの例を示す模式図を提供する。これは、センサ部21を、検出素子または画素22に分割した半導体検出モジュールの例であり、各検出素子（または画素）は、通常、主要な構成要素として、電荷収集電極を有するダイオードに基づく。X線は、半導体検出器のエッジから入る。図16に見られるように、検出素子は、検出器の表面に沿って、個別のストリップ状に配置してもよい。

10

#### 【0028】

図14は、別の例示的な実施形態に係る半導体検出モジュールの例を示す模式図である。この例では、半導体センサ部21は、深度方向で、いわゆる深度セグメント22に分割されており、再び、X線はエッジから入るものとしている。検出素子のそれぞれは、電荷収集電極と、電荷収集電極からの信号を、フロントエンド電子回路に伝達するように構成されている、対応するルーティングトレースと、を備えることに留意すべきである。通常、このような検出素子は、検出器の個別のX線検知サブ素子である。一般に、光子相互作用は、検出素子内で起こり、よって、生成される電荷は、検出素子の対応電極によって収集される。各検出素子は、典型的には、フレームの連続として、入射X線フラックスを測定する。フレームは、フレーム時間と呼ばれる特定の時間間隔内で測定されたデータである。

20

#### 【0029】

図15は、別の例示的な実施形態に係る半導体検出モジュールの模式図である。ルーティングトレースCは、検出器の電荷収集電極を、フロントエンド電子回路Vの入力に接続する。読み出しパッドは、図15では開示されず、代わりに、ルーティングトレースを、検出器に取り付けられたフロントエンド電子回路または回路に、どのようにして接続するかを示している。読み出しパッドは、この図では、フロントエンド電子回路の下に配置されている。

30

#### 【0030】

検出器トポロジーに応じて、検出素子は、特に検出器がフラットパネル検出器である場合、画素に対応してもよい。深度セグメント化された検出器は、各ストリップが複数の深度セグメントを有する、複数の検出ストリップを有するものとみなしてもよい。このような深度セグメント化された検出器に関して、各深度セグメントは、特に深度セグメントのそれぞれが、それ自体の個別の電荷収集電極と関連する場合、個別の検出素子とみなしてもよい。

30

#### 【0031】

深度セグメント化された検出器の検出ストリップは、通常、一般的なフラットパネル検出器の画素に対応する。しかし、深度セグメント化された検出器を、個別の深度/検出素子に対応する各画素（時にはボクセルと称される）である、3次元画素アレイとみなすことも可能である。

40

#### 【0032】

エッジオン検出器を用いることが可能な包括的システムを説明したが、以下、改善されたキャパシタンス特性を提供する特定のエッジオン検出器を説明する。

#### 【0033】

提案技術は、半導体基板102を備えるエッジオン光子計数検出器を提供し、半導体基板102は、

- ・X線源に対向するように構成された第1の端部11と、入射X線の方向において、第1の端部11の反対側にある第2の端部12と、

- ・N-2とするN個の深度セグメントを有し、深度セグメントのそれぞれが、電荷収集金

50

属電極 104 を備える、少なくとも 1 つのストリップと、

ドープ領域 107 と絶縁領域 106 とを備えた電荷収集側と、を備える。電荷収集金属電極 104 のそれぞれは、対応するドープ領域 107 の上に配置され、絶縁領域 106 上に配置された、それぞれのルーティングトレース 103 に接続され、それぞれのルーティングトレース 103 は、電荷収集金属電極から、第 2 の端部に配置されたフロントエンド電子回路に接続可能な読み出しパッド 105 へと信号を伝達するように構成されている。

#### 【0034】

図 1 は、このような検出器の一部の例を示す模式図である。この実施形態では、半導体基板は、N 型の結晶シリコンを含んでもよく、検出器は、検出器のエッジから衝突する入射 X 線 101 に対して、エッジオンで配向されてもよい。検出器の半導体基板 102 は、ストリップに分割され、各ストリップは、続いて、X 線入射方向でもある深度方向内の複数の深度セグメントに分割される。各深度セグメントは、全体積が X 線用の検出器として機能するように、完全に空乏化する必要がある、逆バイアスダイオードによって形成されてもよい。本実施形態において、ストリップ内の各深度セグメントは、ドープ領域 107 の上、例えば P+ 注入部の上に金属コンタクトが成膜された電荷収集側に、個別の電荷収集電極を有し、ドープ領域 107 は、ルーティングトレース 103 を介して、関連するフロントエンド電子回路に接続されている。電荷収集電極の金属コンタクトは、図 1 では、符号 104 が付与されている。金属の電荷収集電極の左列用のルーティングトレースのみが、図 1 に示されている。フロントエンド電子回路の一例は、特定用途向け集積回路、ASIC である。ASIC は、対応する電荷収集電極にそれぞれ接続された、複数の信号処理チャネルを含む。本実施形態において、電荷収集電極からフロントエンド電子回路まで信号を伝達するために用いられるルーティングトレース 103 は、図 1 に示される電荷収集電極の間の領域に延びるようにして配置される。検出器の電荷収集側は、本実施形態においては、したがって、単一金属層として設けられる。この特定の特徴は、ルーティングトレースのための余分な層の使用を不要にする。単一金属層のみを有する注入部の利点としては、より低いキャパシタンス、より高い形状効率性、および実施の複雑さを低下させることが挙げられる。図 1 からは、また、フロントエンド電子回路の入力が、検出器上の読み出しパッド 105 に取り付けられることが分かる。これは、ワイヤボンディング、バンプボンディング、または他の任意のマルチチップモジュール技術によって行うことができる。好適な実施形態において、フロントエンド電子回路は、ルーティングトレースが集まる検出器の底部エッジ 12 に取り付けられてもよい。

#### 【0035】

提案技術の特定の実施形態によれば、半導体基板が、シリコンを含む、エッジオン検出器が提供される。

#### 【0036】

提案技術の別の実施形態によれば、電荷収集金属電極 104 およびルーティングトレース 103 が、同じ金属から製造されたエッジオン検出器が提供される。すなわち、電荷収集金属電極 104 およびルーティングトレース 103 は、基板 102 の電荷収集側の単一金属層内に設けられる。電荷収集電極およびルーティングトレースに用いられる金属は、特定の実施形態において、アルミニウムであってもよい。

#### 【0037】

例として、提案技術に係るエッジオン検出器は、二酸化シリコンの絶縁領域 106 を備えてよい。

#### 【0038】

図 2 は、提案技術の例示的な実施形態に係る半導体基板、例えばシリコン基板、102 の断面を示す模式図である。断面は、2 つのストリップを有するエッジオン検出器を示しており、各ストリップは、2 つの電荷収集電極と、その間の 2 つのルーティングトレース 103 とを有する。電荷収集電極の金属コンタクト 104 は、例えば、ルーティングトレースと同じ金属層上に延びるようにして、P+ 注入部上に形成されてもよい。薄い絶縁層、例えば二酸化シリコン層、106 は、シリコン基板の表側でパシベーションとして用い

10

20

30

40

50

られる。本実施形態において、バイアスが、N+注入部を通して裏面コンタクト108から供給され、検出器を完全に空乏化する。図2は、単なる例示であり、検出器は、より多くの詳細を含んでもよく、例えば、電荷収集側により多くのパシベーション層を含んでもよいことを、認識すべきである。

#### 【0039】

幅狭の電荷収集電極は、キャパシタンスの観点から好適である。幅狭の電荷収集電極で得られる別の利点は、電荷収集電極間のルーティングトレースの適合を容易にすることである。

#### 【0040】

図3は、半導体基板、例えばシリコン基板、102の一部の模式図である。図3に示されているのは、図1の第3の深度セグメントの拡大図であり、電荷収集電極の金属コンタクト104と、ルーティングトレース103とが、同じ金属層で延びている。Pは、ストリップのピッチを表し、WEは、電荷収集電極の幅を表し、WTは、ルーティングトレースの幅を表すとすると、ストリップピッチに対する電極幅の比率は、次式により与えられる。

$$R_E = W_E / P$$

#### 【0041】

ストリップピッチに対するルーティングトレース幅の比率は、次式により与えられる。

$$R_T = W_T / P$$

#### 【0042】

提案技術の特定の実施形態によれば、ストリップの数は、少なくとも2つであり、電荷収集金属電極の幅寸法は、ストリップピッチに対する電荷収集金属電極幅の比率が0.8未満であり、キャパシタンスを減少させるような寸法である、エッジオン検出器が提供される。

#### 【0043】

図4は、厚さ0.6mmのシリコン基板と、0.37mmのストリップピッチと、幅5μmのルーティングトレースとを有する検出器のためのストリップピッチに対する、電極幅の比率の関数としてシミュレートされたキャパシタンスを示している。3つの深度セグメントは、それぞれ10mm、15mmおよび20mmの深度セグメントの長さでシミュレートされている。その間に30%の接着剤および70%の空気を有する、シミュレートされた検出器の電荷収集側に対して20μm離れた、散乱防止シートとしての別の金属表面、あるいは別の電極の表面がある。比率が0.8未満の場合、キャパシタンスは比率に対してほぼ線形に比例するが、比率が0.8よりも大きい場合、キャパシタンスの大幅な増加がある。この結果は、他のストリップピッチに関して確認されている。

#### 【0044】

提案技術のさらに別の実施形態によれば、ストリップの数は、少なくとも2つであり、ルーティングトレースの幅寸法は、ストリップピッチに対するルーティングトレースの幅の比率が0.05未満であるような寸法である、エッジオン検出器が提供される。この実施形態は、改善されたキャパシタンス特性を有する、すなわち、減少されたキャパシタンスを示すエッジオン検出器を提供する。

#### 【0045】

図5は、検出器のノイズレベルと、検出器キャパシタンスとの間のほぼ線形の関係を示している。したがって、比率REは、好ましくは、キャパシタンスおよび信号対ノイズ比の観点からの電荷収集電極の幅に関して、0.8未満であると結論づけられる。さらに、比率RTは、好ましくは、本実施形態におけるルーティングトレースの幅に関して、0.05未満であると結論づくことができる。

#### 【0046】

より多くのルーティングトレースがその間で延びる、底部の深度セグメントに関して、隣接する電荷収集電極の間にルーティングトレースを適合させるために、より多くのスペースが必要とされる。ストリップピッチに対する、隣接する電荷収集電極の間の間隔の比

10

20

30

40

50

率は、 $R_G = W_G / P$  として定義されるが、この比率は、好ましくは、深度セグメントの数を  $N - 2$  として、 $0.05 \times (N + 1)$  よりも大きくすべきである。

【0047】

シリコンと二酸化シリコンの間の界面の露出した領域は、注入部カバーなしでは放射線に感應するため、電荷収集電極は、極度に細くできないことを認識すべきである。したがって、キャパシタンスと検出器の放射線耐性との間に、トレードオフがある。

【0048】

開示されたエッジオン検出器の別の実施形態によれば、半導体基板 102 には、第 2 の端部に配置された読み出しパッドに隣接した領域において、ドープ領域が設けられる。図 8a は、この実施形態の模式図を提供する。読み出しパッドに隣接するドープ領域は、202 で示され、一方で電荷収集電極が設けられるドープ領域を有する領域は、201 で示される。ドープ領域は、この特定の図では、P+ドープ領域である。これはしかし、単なる例であり、他の種類のドーピングを用いてもよい。

【0049】

図 1 に示されるように、検出器の第 2 の端部において、ルーティングトレースは、読み出しパッドに接続されており、読み出しパッドは、その後、フロントエンド電子回路に接続されている。フロントエンド電子回路の入力に対するキャパシタンスを最小化するために、ルーティングトレースの長さを減少させ、ルーティングトレースをまばらに分散させるという必要条件がある。最後の電荷収集電極の端部で、検出器の大部分または検出器全体を覆うフロントエンド電子回路を有することが考えられる。しかし、フロントエンド電子回路の集積回路は、高速、低電力および低い製造コストのために、小型となる傾向があり、これは多くの場合、フロントエンド電子回路は、検出器の小さな部分しか覆うことができないことを意味する。小さな画素ピッチを有する検出器があり、この画素ピッチは、フロントエンド電子回路、例えば数十マイクロメートルの画素ピッチを有するマンモグラフィーの入力ピッチに相当する。このような検出器に対して、フロントエンド電子回路は、ルーティングトレースの最小長さを有し、よって最小のキャパシタンスを有する電荷収集電極に、非常に近接して接合することができる。しかし、大きな画素ピッチを有するいくつかの X 線撮像検出器、例えば X 線コンピュータ断層撮影もあり、ここでは、画素ピッチは、フロントエンド電子回路の入力ピッチよりもずっと大きい。このようなケースが、図 6 に示されており、ルーティングトレースは、検出器の X 線検知部 201 のうちの一領域を占め、検出器の領域 202 内の読み出しパッドに集まり、扇形を形成する可能性が高い。ガードリング構造は、電荷収集側の特徴であり、この構造は、エッジ効果を最小化し、全てのストリップおよび深度セグメントに対して、定義された均質な電位の確保をもたらすために、特別に提供される。ガードリング構造は、図 6 に示されている。常にではないが、通常は、1 つまたは複数のガードリングが、検出器のアクティブ部と検出器のエッジとの間に配置される。第 1 のリングは、特定の電位、通常はグランドに直接接続され、検出器のエッジに生成されるリーク電流のための排流を提供する。1 つまたは複数の浮動リングがあり、電位を個別に適合させ、外部からの電圧効果を平滑にしてもよい。リングは、通常、ストリップおよび深度セグメントと同じ構造を、同じ種類の金属およびドーピングで有する。図 6 では、1 つのリングの金属部分のみが示されている。

【0050】

図 7 は、例示的な実施形態に係る、シリコン基板の読み出しパッドに隣接する領域の例示的な断面を示す模式図である。ルーティングトレース C は、二酸化シリコンを含む絶縁層 106 の上を延びている。常にではないが、通常は、絶縁層 106 は、読み出しパッドに隣接する領域全体を覆う。請求される本発明の一実施形態においては、二酸化シリコンの下で、N 型結晶シリコンを用いて、検出器のガードリングから延びる P+注入部 203 は、通常、底部領域全体を覆うが、しかしこれは、ルーティングトレースと、二酸化シリコンの典型的な厚さを与えられた P+注入部の層との間に、高いキャパシタンスを生じる。

【0051】

開示されたエッジオン検出器の別の実施形態によれば、半導体基板 B には、第 2 の端部

10

20

30

40

50

に配置された読み出しパッドに隣接する領域に、ドープ領域が設けられる。図 8 a は、この実施形態の模式図を提供する。この実施形態においては、ドープ領域は、読み出しパッドに隣接する領域全体を覆う。ドープ領域は、この特定の図では、P + ドープ領域である。しかしこれは、これは単なる例であり、他の種類のドーピングを用いてもよい。

#### 【 0 0 5 2 】

別の実施形態は、読み出しパッドに隣接する領域に、絶縁領域がさらに設けられ、これにより、ドープ領域と絶縁領域とが配置されて、ルーティングトレースが絶縁領域上を読み出しパッドまで延びるようなパターンを形成する、エッジオン検出器を提供する。このようなパターンの特定の例が、図 8 b および図 8 c に与えられている。図 8 b では、絶縁領域 203 の領域が、どのようにしてドープ領域 204 に囲まれているかを示している。不図示のルーティングトレース 103 は、絶縁領域の上に配置されることを意図している。図 8 c では、絶縁領域を、どのようにして読み出しパッドに隣接する領域に配置して、ルーティングトレースを、扇状のやり方で読み出しパッドに接続し得るかを示している。

10

#### 【 0 0 5 3 】

図 8 a ~ 図 8 c は、図 6 に示されるセンサのための注入層の異なる実施に対応する模式図であり、検出器の読み出しパッドに隣接する領域で延びる、ルーティングトレースからのキャパシタンスに対処する異なる方策を示している。X 線検知部 201 は、電荷収集電極の P + 注入部、図 2 の P + を含み、検出器の第 2 の端部に近い領域 202 も、P + 注入領域、図 7 の P + を含む。

20

#### 【 0 0 5 4 】

請求される本発明の一実施形態において、図 8 a に示すように、非注入領域に囲まれる、注入層上の電荷収集電極の注入部がある。ガードリングの注入部から延びる注入領域は、センサの第 2 の端部の読み出しパッドに隣接する領域全体を覆い、これは結果として、本実施形態において、比較的高いキャパシタンスをもたらす。ガードリング構造の 1 つのリングのみが、図示されている。

#### 【 0 0 5 5 】

請求される本発明の別の実施形態において、図 8 b に示すように、センサの底部領域で、注入領域は、ガードリングから、最も外側のトレースのみに近接してさらに延びており、これにより、203 で示される、トレースの下の領域に対しては、注入部はない。電荷収集電極の近くに、長いストリップ注入領域 204 があり、センサのガードリングに接続されて、センサのガードリングに対する、センサの第 2 の端部の領域内で生成されたリーク電流をガイドし、センサの第 2 の端部の領域内で生じた障害が X 線検知部に達することを防止する。本実施形態は、センサの第 2 の端部の領域内で延びるルーティングトレースにより誘発されるキャパシタンスを、少なくとも有するものとしている。

30

#### 【 0 0 5 6 】

センサの第 2 の端部の領域内で、ルーティングトレースと P + 注入部との間で誘発されるキャパシタンスを減少させ、リーク電流、ブレーカダウン電圧などの、センサの他の側面を、前の実施形態と比較して高信頼かつ制御下に保つために、別の実施形態が提供される。図 8 c は、読み出しパッドに隣接する領域内で、非注入領域 206 により分離される P + 注入部 205 のストリップパターンを示す模式図である。P + 注入ストリップは、センサのガードリングに接続される。この例では、注入ストリップは、センサ深度方向に沿って電荷収集電極に対して平行であるが、注入ストリップは、他の方向、例えば、電荷収集電極に垂直、またはグリッドパターンを形成する両方向、あるいは他の任意のパターンに沿うこともできる。センサの第 2 の端部で読み出しパッドに隣接する領域内で、ルーティングトレースにより誘発されるキャパシタンスは、P + 注入部の領域を減少させることにより、相応に減少される。注入ストリップの幅を a で表し、非注入部間隔の幅を b で表すと、キャパシタンスは、これにより、ほぼ、b / ( a + b ) に減少させることができる。さらにキャパシタンスを減少させるために、本発明の特定の実施形態では、注入ストリップ間の非注入領域を、ルーティングトレースの経路を追うように配置することができ、これは、ルーティングトレースと P + 注入部との間のより少ない重複と、よってより少な

40

50

いキャパシタンスとをもたらす。

【 0 0 5 7 】

1列のみの読み出しパッドを、上述の実施形態にて示したが、複数列の読み出しパッドも、当業者には明らかであろう。

【 0 0 5 8 】

提案技術は、また、半導体基板が、テーパ形状を有し、これにより、半導体基板の第1の端部11が、第1の幅を有し、半導体基板の第2の端部12が、第1の端部よりも大きな第2の幅を有する、エッジオン検出器を提供する。このようなエッジオン検出器は、電荷収集金属電極の少なくとも2つのストリップを備えた半導体基板を含んでもよく、ストリップは、電荷収集電極が、基板のテーパ形状に適合されたテーパパターン内の電荷収集側に設けられるように、互いにに対して角度をなしている。

10

【 0 0 5 9 】

これらのような設計は、大型のセンサが利用される場合に、特に有用となり得る。図9に示されるように、設計の図が提供される。図9において、各個別の深度セグメントは、X線101の入射方向に沿って、X線源を指すように傾けて配置されることが分かる。センサの台形形状は、例示的な実施形態を形成する。このようなセンサの台形形状は、センサの四角形状と比べて最小のデッドスペースを有してセンサを並べて搭載することにより、検出器の幅を延ばすことを容易にするが、その理由は、X線源を指すように各センサを配置する必要もあるためである。しかし、大型のセンサの四角形状も、請求される本発明によってカバーされることを、認識すべきである。

20

【 0 0 6 0 】

提案技術は、また、基板の第2の端部が、少なくとも1つの面取り角部を備えた、エッジオン検出器を提供する。図10は、1つの角部を取り除いてセンサの面取り形状を生成した、センサの別の例を示す模式図であり、このセンサは、最も近いセンサから誘発されるキャパシタンスを減少させ、かつ、回路のボンディング接続のためにより多くのスペースを割り当てることによって、フロントエンド電子回路の搭載も容易にする。フロントエンド電子回路を、ワイヤボンディング、フリップフロップ技術を用いたバンプボンディング、または他の任意のボンディング技術によりセンサに接続して、マルチチップモジュールを形成することができる。

30

【 0 0 6 1 】

上述したように、提案技術は、キャパシタンス特性を改善したエッジオン半導体ストリップ検出器を提供する。ストリップ検出器は、40keV～250keVのエネルギー範囲内でのX線撮像における使用に適している。このような検出器の特定の特徴は、単一金属層を、検出器の電荷収集側に実装可能であることである。この単一層は、導電ルーティングトレースと、電荷収集電極とを備える。この特定の特徴は、改善されたキャパシタンス特性を有する検出器を提供する。提案技術は、したがって、このようなエッジオン検出器の電荷収集側を製造する方法を提供する。

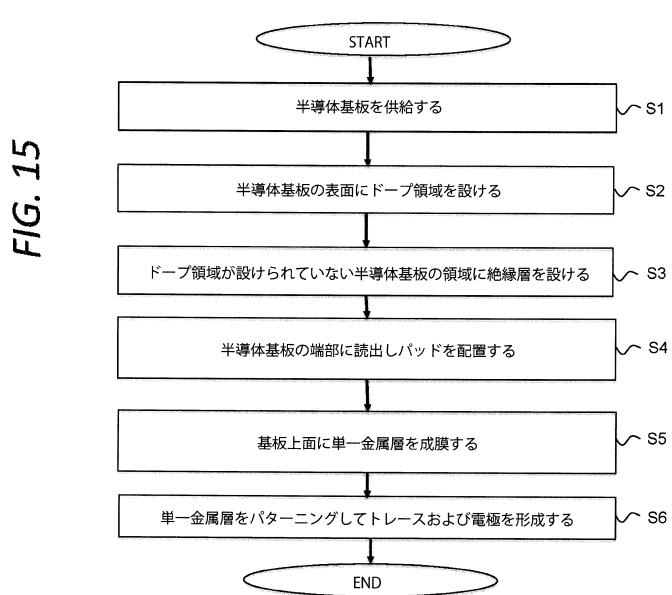

【 0 0 6 2 】

このために、エッジオン検出器のための電荷収集面を製造するための方法が提供され、この方法は、

40

- X線源に対向するように構成された第1の端部と、第1の端部の反対側の第2の端部と、を有する半導体基板102を供給するステップS1と、

- 電荷収集面と称される、半導体基板102の表面に、ドープ領域107を設けるステップS2と、

- ドープ領域107が設けられていない第2の表面の領域の上に、絶縁層106を設けるステップS3と、

- 半導体基板の第2の端部に、読み出しパッド105を配置するステップS4と、

- ドープ領域107と、絶縁層とを備える電荷収集面の上に、単一金属層を成膜するステップS5と、

- 単一金属層をパターニングして、

50

i ) ドープ領域 107 の上に、電荷収集金属電極を形成し、

ii ) 絶縁層 106 の上に、電荷収集金属電極を読み出しパッド 105 と接続するルーティングトレース 103 を形成するステップ S6 と、

を含む。

【0063】

提案された方法は、図 16 のフロー図に、模式的に示されている。

【0064】

提案された方法の特定の実施形態によれば、単一金属層を成膜するステップ S5 は、物理蒸着法 (PVD) 、めっき法および / または化学蒸着法 (CVD) を使用することを含む。

10

【0065】

提案された方法の別の特定の実施形態によれば、単一金属層をパターニングするステップ S6 は、フォトリソグラフィの使用を含む。

【0066】

提案技術のさらに別の実施形態は、半導体基板 102 を供給するステップ S1 は、シリコン基板を供給することを含む。

【0067】

提案技術のさらに別の実施形態は、電荷収集面の上に、単一金属層を成膜するステップ S5 は、単一アルミニウム層を成膜することを含む方法を提供する。いくつかの金属層を、第 1 の金属層の上に成膜してもよいことに留意すべきである。例えば、提案された方法を行い、初回は、パターニングされてルーティングトレースと電荷収集電極とを形成した第 1 の金属層を有する電荷収集側を得、次いで、成膜ステップを 1 または複数回繰り返し、互いの上に配置された電荷収集電極とルーティングトレースとを形成するいくつかの金属層を得てもよい。

20

【0068】

提案技術の任意の実施形態によれば、ドープ領域 107 が設けられていない第 2 の表面の領域上に、絶縁層 106 を設けるステップ S3 は、二酸化シリコン層を設けることを含む方法が提供される。

【0069】

提案技術の特定の実施形態によれば、金属層をパターニングするステップ S6 は、電荷収集電極の少なくとも 2 つのストリップを形成することを含み、電荷収集電極のそれぞれは、ストリップピッチに対する電荷収集金属電極幅の比率が、0.8 未満であるような幅寸法を有する方法が提供される。

30

【0070】

提案技術の別の実施形態は、金属層をパターニングするステップ S6 は、ストリップピッチに対するルーティングトレース幅の比率が、0.05 未満であるような幅寸法を有するルーティングトレースを形成することをさらに含む方法を提供する。

【0071】

提案技術は、また、上述の方法に従って製造された電荷収集面を備えるエッジオン検出器を提供する。

40

【0072】

本開示に示される実施形態は、N 型結晶シリコンによる例を示しているが、提案技術は、N+ ドープ電極を有する P 型結晶シリコンにも適用できることを認識すべきである。センサ形状の変形は、当業者に対して直ちに明らかとなることを、認識すべきである。したがって、添付の特許請求の範囲は、例えば、センサの三角形形状または 2 つの面取りされた角部を有するセンサなど、すべてのこののような変形および修正を含むように、可能な限り広く解釈されることを意図している。加えて、深度セグメントの異なる数およびセグメント長さの異なる変更例が、請求される本発明の範囲に含まれる。

【0073】

参考文献

50

- ・ R. ノヴォトニー (R. Nowotny)、"医学および構造解析における Si マイクロストリップ検出器の応用 (Application of Si-microstrip-detectors in medicine and structural analysis)"、物理学研究における核計器および方法 (Nuclear Instruments and Methods in Physics Research) 226 (1984) 34~39

- ・ 米国特許第4,937,453号、ロバート・ネルソン (Robert Nelson) "放射線撮像用X線検出器 (X-ray detector for radiographic imaging)"

- ・ 米国特許第5,434,417号、デイビッド・ナイグレン (David Nygren) "高解像度エネルギーに敏感なデジタルX線 (High resolution energy-sensitive digital X-ray)" 10

- ・ 米国特許第7,291,841号B2、ロバート・ネルソン (Robert Nelson) ら、"核医学における強化されたSPECT、PET、およびコンプトン散乱撮像のための装置およびシステム (Device and system for enhanced SPECT, PET, and Compton scatter imaging in nuclear medicine)"

- ・ ショウイチ・ヨシダ (Shoichi Yoshiida)、タカシ・オオスギ (Takashi Ohsugi)、"シリコンストリップ検出器のX線コンピュータ断層撮影への応用 (Application of silicon strip detectors to X-ray computed tomography)"、物理学研究における核計器および方法 (Nuclear Instruments and Methods in Physics Research)、A 541 (2005)、412~420 20

- ・ 米国特許第8,183,535号B2、マツ・ダニエルソン (Mats Danielsson) ら、"X線撮像用のシリコン検出器アセンブリ (Silicon detector assembly for x-ray imaging)"

- ・ チェン・シュウ (Cheng Xu) ら、"光子計数スペクトルCT用のセグメント化シリコンストリップ検出器のエネルギー分解能 (Energy resolution of a segmented silicon strip detector for photon-counting spectral CT)"、物理学研究における核計器および方法 (Nuclear Instruments and Methods in Physics Research)、A 715 (2013)、11~17 30

- ・ スジン・リウ (Xuejin Liu) ら、"マルチビン光子計数スペクトルコンピューター断層撮影検出器用のスペクトル応答モデルとその応用 (Spectral response model for a multibin photon-counting spectral computed tomography detector and its applications)"、医用画像ジャーナル (Journal of Medical Imaging) 2(3) (2015) 033502

- ・ スウェーデン特許出願第9801677-7号、マツ・ダニエルソン (Mats Danielsson) 40

- ・ "シリコンストリップ検出器での電荷収集 (Charge collection in silicon strip detectors)"、物理学研究における核計器および方法 (Nuclear Instruments and Methods in Physics Research) 214 (2-3) (1983)、253~260

【図面】

【図 1】

【図 2】

FIG 2

【図 3】

FIG 3

【図 4】

10

20

30

40

50

【図 5】

【図 6】

【図 7】

FIG 7

【図 8 a】

FIG 8a

【図 8 b】

FIG 8b

【図 8 c】

FIG 8c

10

20

【図 9】

【図 10】

FIG 10

30

40

50

### 【図11】

【図12】

### 【図13】

FIG. 13

【図14】

FIG. 14

【図15】

【図16】

## フロントページの続き

## (51)国際特許分類

H 0 4 N 5/369(2011.01)

F I

H 0 4 N

5/369

弁理士 赤岡 明

## (74)代理人

弁理士 三並 大悟

## (72)発明者

マツ、ダニエルソン

スウェーデン国タビー、グルドグランド、5

## (72)発明者

スタファン、カールソン

スウェーデン国ブロンマ、ストルトロドスベーゲン、34

## (72)発明者

トールビヨルン、ヤルン

スウェーデン国バックスホルム、ダルスティーゲン、19

## (72)発明者

チエン、シユ

スウェーデン国タビー、オーケルビベーゲン、268

審査官 大門 清

## (56)参考文献

米国特許第05434417(US, A)

特開2007-007407(JP, A)

米国特許第06546075(US, B1)

特開2011-145292(JP, A)

CHENG,Xu et al. , Energy resolution of a segmented silicon strip detector for photon-counting spectral CT , Nuclear Instruments &amp; Methods in Physics Research, Section A. , 米国 , 2013年 , A715 , p.11-17

## (58)調査した分野 (Int.Cl. , DB名)

G 0 1 T 1 / 2 4

H 0 1 L 2 7 / 1 4 4

H 0 1 L 2 7 / 1 4 6

H 0 1 L 3 1 / 1 0

H 0 4 N 5 / 3 2

H 0 4 N 5 / 3 6 9