(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4996938号

(P4996938)

(45) 発行日 平成24年8月8日(2012.8.8)

(24) 登録日 平成24年5月18日(2012.5.18)

(51) Int.Cl.

H01L 33/34 (2010.01)

G02B 6/42 (2006.01)

F 1

H01L 33/00 188

G02B 6/42

請求項の数 9 (全 49 頁)

(21) 出願番号 特願2007-36328 (P2007-36328)

(22) 出願日 平成19年2月16日 (2007.2.16)

(65) 公開番号 特開2008-205006 (P2008-205006A)

(43) 公開日 平成20年9月4日 (2008.9.4)

審査請求日 平成21年7月23日 (2009.7.23)

(73) 特許権者 000005108

株式会社日立製作所

東京都千代田区丸の内一丁目6番6号

(74) 代理人 110000350

ポレール特許業務法人

(72) 発明者 久本 大

東京都国分寺市東恋ヶ窪一丁目280番地

株式会社日立製作所中央研究所内

(72) 発明者 斎藤 慎一

東京都国分寺市東恋ヶ窪一丁目280番地

株式会社日立製作所中央研究所内

(72) 発明者 木村 紳一郎

東京都国分寺市東恋ヶ窪一丁目280番地

株式会社日立製作所中央研究所内

最終頁に続く

(54) 【発明の名称】半導体発光素子

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体基板上に設けられた絶縁層と、

前記絶縁層上にそれぞれ設けられた電子を注入するための第1の電極と、正孔を注入するための第2の電極と、前記第1の電極及び前記第2の電極と電気的に接続された発光部とを有し、

前記第1の電極、前記第2の電極、及び前記発光部は、それぞれ第1の単結晶材料から構成され、

前記発光部は、前記半導体基板の基板面に対して垂直方向に形成され、10nm以下の膜厚を有する薄膜であるフィンからなり、前記第1の単結晶材料の酸化膜で覆われており

10

前記発光部の前記フィンの材料はIV族半導体であることを特徴とする半導体発光素子。

## 【請求項 2】

前記発光部は、複数の前記フィンを有していることを特徴とする請求項1に記載の半導体発光素子。

## 【請求項 3】

複数の前記フィンは、導波路で覆われていることを特徴とする請求項2に記載の半導体発光素子。

## 【請求項 4】

複数の前記フィンは、前記発光部の発光波長の半波長間隔で並んでいることを特徴とす

20

る請求項 2 に記載の半導体発光素子。

【請求項 5】

前記薄膜の材料は、間接遷移型半導体であることを特徴とする請求項 1 または 2 に記載の半導体発光素子。

【請求項 6】

前記 I V 族半導体がシリコンであり、かつ、前記シリコンの表面の面方位が (100) 面、もしくはこれと等価な面方位であることを特徴とする請求項 1 に記載の半導体発光素子。

【請求項 7】

前記導波路がシリコン窒化膜によって形成されていることを特徴とする請求項 3 に記載の半導体発光素子。

10

【請求項 8】

前記導波路が、前記導波路を構成する材料の屈折率に比べて低い屈折率を有する材料により覆われていることを特徴とする請求項 7 に記載の半導体発光素子。

【請求項 9】

前記半導体基板上に設けられた受光素子と、

前記発光部と前記受光素子とを接続する前記導波路とを有し、

前記導波路は、シリコン窒化膜で構成されていることを特徴とする請求項 3 に記載の半導体発光素子。

【発明の詳細な説明】

20

【技術分野】

【0001】

本発明は、半導体発光素子、それを用いた光電子集積回路およびその製造方法に関するものであり、特に、電気的な信号処理を行う半導体集積回路と混載した、高輝度の発光ダイオード、ゲート電圧で光強度・波長を制御可能な光トランジスタ、シリコンレーザー素子、受光素子および導波路を集積した集積半導体素子及びそれらの製造方法に関する。

【背景技術】

【0002】

インターネット産業を支えるブロード・バンド・ネットワークでは、光通信が採用されている。この光通信における光の送受信には、III-V族やII-VI族などの化合物半導体を用いたレーザーが使用されている。

30

【0003】

化合物半導体レーザーには、様々な構造が提唱されているが、ダブル・ヘテロ構造が一般的である。ダブル・ヘテロ構造は、2種類の異なる化合物半導体を用いて、バンド・ギャップの小さい化合物半導体をバンド・ギャップの大きい化合物半導体で挟んだ構造をしている。ダブル・ヘテロ構造を作製するには、基板上に導電型がn型、ドーピングしていないi型、そしてp型の各化合物半導体を連続的にエピタキシャル成長させ、垂直方向に積層する。その際、間に挟まれているドーピングしていないi型の化合物半導体のバンド構造に注意をする必要があり、n型とp型の各化合物半導体よりもバンドギャップが小さく、i型の伝導帯レベルがn型の伝導帯レベルよりも低く、i型の価電子帯レベルがp型の価電子レベルよりも高いことが重要である。つまり、電子及び正孔がともに、i型の領域に閉じ込められる構造となっている。そのため、電子と正孔が同じ領域に居やすくなるため、電子と正孔が衝突して対消滅する確率が高まり、結果として、発光効率をあげる事ができる。また、屈折率はバンド・ギャップが小さくなるほど大きくなる傾向があるため、i型の化合物半導体の屈折率がn型やp型の各化合物半導体の屈折率よりも小さい材料を選ぶ事によって、光もi型の化合物半導体に閉じ込められることになる。閉じ込められた光は、反転分布をつくっている電子と正孔の再結合を効率よく誘導するため、レーザー発振することにつながる。

40

【0004】

このように効率よく発光する化合物半導体を用いた光通信によって、長距離情報通信が

50

瞬時の間に大量に行われている。すなわち、情報処理や記憶はシリコンを基幹としたLSI上で行われており、情報の送信は化合物半導体を基幹としたレーザーによって行われている。

シリコンを高効率で発光させる事ができれば、シリコン・チップ上に電子デバイスと発光素子をともに集積化させる事ができるため、その産業的価値は甚大である。そこで、シリコンを発光させるという研究は膨大に行われている。

#### 【0005】

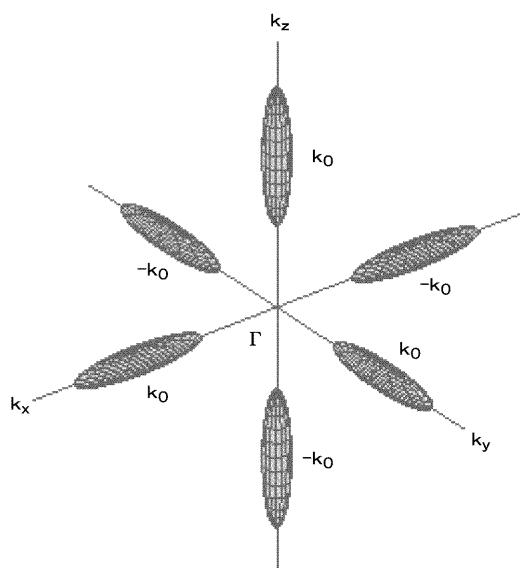

しかしながら、シリコンを高効率に発光させる事は難しい。それは、シリコンが間接遷移型のバンド構造を有しているからである。間接遷移型のバンド構造とは、伝導帯のエネルギーが最低になる運動量または価電子帯のエネルギーが最低になる運動量のどちらか0でないバンド構造を指す。シリコンの場合には、価電子帯の最小エネルギー点は、運動量が0になる点であるが、伝導帯の最小エネルギー点は点ではなく点とX点の間にあり、より具体的には、格子定数をaとして、 $k_0=0.85^*/a$ と定義するならば、(0, 0, ± $k_0$ )、(0, ± $k_0$ , 0)、(± $k_0$ , 0, 0)の6点に縮退して存在する。この様子を、図1Aに示す。

これに対して、化合物半導体の多くは、伝導帯も価電子帯も点に最小エネルギー点があるため直接遷移型の半導体と呼ばれる。

#### 【0006】

次に、何故、間接遷移型の半導体では発光効率が悪く、直接遷移型の半導体では発光効率が良いか説明する。

上述のように、半導体素子で発光させるためには、電子と正孔が衝突して対消滅し、両者のエネルギーの差を光として抽出しなければならない。その際、エネルギーと運動量の保存則が共に満足されなければならない。電子は伝導帯の中にエネルギー準位をもっており、正孔は価電子帯の中で電子がない部分のエネルギー準位をもっている。両者の差が光の持っているエネルギーになり、エネルギーによって波長が異なるため、伝導帯と価電子帯のエネルギー差、すなわちバンドギャップの大きさが光の波長、すなわち色を決める事になる。こうして考えると、エネルギーの保存則が成立する事に格段の困難さは見いだせられない。

#### 【0007】

一方、発光には電子と正孔の衝突現象が関与するため、運動量も保存されなければならない。微視的な世界を支配する法則である量子力学によると、電子、正孔、光子（光の量子）は共に、波でもあるが粒子として散乱されるため、運動量の保存則が成立する。運動量とは、定性的には、衝突の際に粒子をどの位の勢いで弾き飛ばすかという事を定量化する尺度である。光の分散関係（ $=ck$ 、ここで $c$ は光の角振動数、 $c$ は高速、 $k$ は光子の運動量）やエネルギーから、結晶中の光子の運動量を見積もるとほとんどゼロとなる事がわかる。これは、光が衝突する事によって物質を弾き飛ばすという現象があるとしても、それによって物質が散乱される影響は非常に少ないという事を意味しており、我々の直感とも一致する。

#### 【0008】

一方、正孔もエネルギーの最小点が点にあるため、ほとんど運動量を有していない。しかしながら、間接遷移型の半導体であるシリコン中では、電子が点にほとんど存在せず、X点付近のエネルギー最小点に存在するため、大きさで $k_0=0.85^*/a$ もの大きな運動量を有している。

#### 【0009】

従って、シリコン中では、単純に電子と正孔が衝突する課程では、運動量保存則とエネルギー保存則を同時に満足させる事ができない。そこで、結晶中の光子振動の量子であるフォノンを吸収または放出するなどして、運動量保存則とエネルギー保存則をなんとか同時に満足できた電子・正孔対のみが光に変換されることになる。このような過程は、物理的に存在しないわけではないが、電子・正孔・光子・フォノンが同時に衝突するような高次の散乱課程であるため、そのような現象がおこる確率は少ない。従って、間接遷移型の

10

20

30

40

50

半導体であるシリコンは極めて発光効率が悪いということが知られている。

【0010】

これに対して、直接遷移型の化合物半導体の多くは、伝導帯も価電子帯も一点にエネルギーの最小点が存在するため、運動量の保存則とエネルギーの保存則を共に満たす事ができる。従って、化合物半導体では発光効率が高い。

非特許文献1には、発光効率の高い化合物半導体を用いたレーザーを化合物半導体で作られたバイポーラ・トランジスタで駆動するトランジスタ・レーザー素子が報告されている。

【0011】

上述したようにバルクの状態では極めて発光効率が悪いシリコンであるが、ポーラス状態、あるいは、ナノ粒子状態にすることで発光効率が上がる事が知られている。 10

たとえば、非特許文献2では、フッ酸溶液中で陽極酸化したシリコンがポーラス状態になることによって、室温でなおかつ可視光波長帯で発光することが報告されている。そのメカニズムに関しては、完全には解明されていないものの、多孔質の形成によって、狭い領域に閉じ込められたシリコンが存在するために生ずる量子サイズ効果が重要ではないかと考えられている。サイズの小さいシリコン中では、電子の位置がその領域内に閉じ込められるため、量子力学の不確定性原理により、逆に運動量が定まらなくなるため、電子と正孔の再結合が生じやすくなっているのではないかと考えられている。

【0012】

シリコンを用いた別 の方法として、たとえば非特許文献3には、Si基板に形成されたpn接合中にErイオンを注入する事によって、発光素子となる発光ダイオード(Light Emitting Diode)をつくることができたと記載されている。ErイオンをSi基板中に注入すると、Erが不純物準位をつくり、不純物準位は空間的に局在した準位であるため、Siの伝導帯にある電子がErイオンのつくる不純物準位に捕獲されると運動量は実効的にゼロとなり、価電子帯の正孔と再結合ができるようになり発光すると考えられる。Erイオンを介在した発光は、 $1.54 \mu m$ の波長であるため、周囲のシリコンに吸収されること無く光を伝搬させることができ。また、既存の光ファイバーを用いた場合に損失が少なくなる波長でもあるため、将来の技術革新によって、Erイオンを用いたSiベースのLEDが実用化された場合にも、既存の光ファイバー網を利用する事ができるため、大規模な設備投資を必要する事が無いのではないかと、期待されている。 30

【0013】

さらに、シリコンを用いた別 の方法として、たとえば非特許文献4や非特許文献5には、上述の量子サイズ効果とErイオンのアイディアを組み合わせて、シリコン・ナノ粒子中にErイオンを注入する事によって、効率を上げて発光させる事ができたと記載されている。

【0014】

従来技術では、シリコンを発光させるために、シリコンの伝導帯のバンド構造をバルクのバンド構造と変えて、不確定性原理によって、運動量を $k_0$ の点から離すためには、量子サイズ効果によって、シリコンを多孔質状態か、または、ナノ粒子状態などにすれば良いと考えられていた。しかしながら、たとえば、ナノ粒子のような構造のシリコンを形成すると、シリコン表面は極めて酸化されやすいという特徴から、シリコン・ナノ粒子の表面が酸化されて、表面に二酸化シリコンが形成されるという問題がある。二酸化シリコンはバンドギャップが極めて大きい絶縁体であるため、表面に二酸化シリコンが形成されると効率よく電子や正孔を注入することができないという問題が生じる。従って、従来のシリコン発光素子では、フォトルミネッセンスでは高い強度が得られたとしても、エレクトロルミネッセンスでは極めて効率が落ちてしまうという問題が生じる。また、発光の際には、発光層となる物質の結晶性が重要になるが、CVD (Chemical Vapor Deposition) 法で形成したナノ粒子や陽極酸化によって表面に不規則かつ多量の穴を開けた構造では、単結晶と比べて結晶性が悪くなるという問題がある。結晶性が悪いと欠陥準位を介した発光が発生するという事態が生ずるが、欠陥を利用した発光では、効率が悪いため、情報通信 40

などの実用に耐える素子は作製できないという問題がある。

上述のように、ポーラスシリコンやナノ粒子やErドープなど、様々な技術によってシリコンを発光させるという努力は行われているが、発光効率は実用レベルまで高くなかった。我々は、電子を注入する第1の電極部と、正孔を注入する第2の電極部と、第1の電極部及び第2の電極部と電気的に接続された発光部を備え、発光部を単結晶のシリコンとし、発光部が第1の面（上面）と第1の面に対向する第2の面（下面）を有し、第1及び第2の面の面方位を（100）面とし、第1及び第2の面に直交する方向の発光部の厚さを薄くすることで、シリコンなどの基板上に通常のシリコン・プロセスを用いて容易に形成可能で、かつ、高効率に発光する発光素子を得られることを見出した。まず、発光の原理およびその実証結果を示し、次に、実用化における本発明にとっての課題を明らかにする。

シリコンやそれに順ずるゲルマニウムなどのIV族半導体を効率良く光らせるための原理について、図面に基づいて説明する。

シリコンなどの結晶中の電子の状態を表す波動関数  $\psi(r)$  は大変良い近似で（式1）のように表すことができる。

【0015】

【数1】

$$\psi(r) = \phi_{k_0}(r) \xi(r) \quad \dots \quad (\text{式1})$$

【0016】

ここで、 $k_0$ は伝導帯のバンドの谷底（valley）を与える運動量であり、 $r=(x, y, z)$ は空間上での位置を表し、 $\phi_{k_0}(r)$ は伝導帯のバンドの谷でのBloch関数を与える、 $\xi(r)$ は包絡線関数を表す。 $\phi_{k_0}(r)$ は、結晶中の単位格子ベクトル $a$ に対する周期性を反映した周期関数 $u_{k_0}(r+a)=u_{k_0}(r)$ を用いて（式2）と表せる。

【0017】

【数2】

$$\phi_{k_0}(r) = u_{k_0}(r) e^{ik_0 \cdot r} \quad \dots \quad (\text{式2})$$

【0018】

このことからも明らかのように、原子スケールの距離の関数として激しく振動する。これに対して、包絡線関数  $\xi(r)$  は原子スケールでは緩やかな変化をする成分を表しており、半導体の物理的な形状や周囲から印加されている外場に対する応答を表す。ここで、 $\xi(r)$  が、必ずしもバルク結晶ではない、有限の大きさを有した半導体構造中の波動関数である場合も含めて考えると、 $\xi(r)$  の満足すべき式を（式3）と導く事ができる。

【0019】

【数3】

$$[\varepsilon(k_0 - i\nabla) + V(r)] \xi(r) = E \xi(r) \quad \dots \quad (\text{式3})$$

【0020】

ここで、 $\varepsilon(k)$  は、運動量  $k$  を有する伝導帯電子のバルクにおけるバンド構造を表しており、運動量  $k$  に微分演算子  $-i\nabla$  と運動量  $k_0$  の和を代入したものを  $(k_0 - i\nabla)$  と示している。また、 $V=V(r)$  は、電子の感じるポテンシャルで、たとえば、半導体の境界部に絶縁体や別の種類の半導体が接触している場合には、ポテンシャル障壁を与えるし、外部から電界効果によって電場を印加することによって、 $V=V(r)$  の値を調整する事もできる。ここでは簡単のために、 $V$  の  $z$  方向に対する変化のみに注目する。

【0021】

ここで、理解を容易にするため、具体的に、たとえば、半導体として（100）面上でのシリコンを想定すると、上述のようにバルクでは、図1Aに示したようなバンド構造をしているため、 $k_z$  方向の  $(0, 0, \pm k_0)$  に存在する伝導帯の谷は、（式4）と近似することができる。

【0022】

10

20

30

40

50

【数4】

$$\varepsilon(k) = \frac{\hbar^2}{2m_t^*} (k_x^2 + k_y^2) + \frac{\hbar^2}{2m_l^*} (k_z \mp k_0)^2 \quad \dots \quad (\text{式4})$$

【0023】

ここで、 $m_t^*$  及び  $m_l^*$  は、回転楕円体形状をしている伝導帯の谷の短軸及び長軸方向の曲率から求めたシリコン結晶中の有効質量を表している。

なお、(式4)を代入すると(式3)は、(式5)と表される。

【0024】

【数5】

$$\left[ -\frac{\hbar^2}{2m_t^*} (\partial_x^2 + \partial_y^2) - \frac{\hbar^2}{2m_l^*} \partial_z^2 + V(r) \right] \xi(r) = E \xi(r) \quad \dots \quad (\text{式5})$$

【0025】

なお、(100)面に平行な方向を(x, y)とし、幅をW、長さをLとして、包絡線関数を(式6)と置くことによって、(式5)は、(式7)となる。

【0026】

【数6】

$$\xi(r) = \frac{e^{i(k_x x + k_y y)}}{\sqrt{LW}} \chi(z) \quad \dots \quad (\text{式6})$$

【0027】

【数7】

$$\left[ -\frac{\hbar^2}{2m_l^*} \partial_z^2 + V(z) \right] \chi(z) = \Delta E \chi(z) \quad \dots \quad (\text{式7})$$

【0028】

ここで、Eは、z方向のエネルギーを表し、伝導帯の底から測った電子の全エネルギーは、(式8)と表される。

【0029】

【数8】

$$E = \frac{\hbar^2 k_x^2}{2m_t^*} + \frac{\hbar^2 k_y^2}{2m_t^*} + \Delta E \quad \dots \quad (\text{式8})$$

【0030】

まず、(式7)がバルクの電子状態を再現する事を確かめる。そのためには、 $V(r)=0$ とおいた時の連続状態の解を求めれば良い。それは、z方向の厚さをtとして、包絡線波動関数が(式9)となり、Eが(式10)となる事から確かめられる。

【0031】

【数9】

$$\chi(z) = \frac{1}{\sqrt{t}} e^{ik_z z} \quad \dots \quad (\text{式9})$$

【0032】

10

20

40

【数10】

$$\Delta E = \frac{\hbar^2 (k_z \mp k_0)^2}{2m_l^*} \quad \dots \quad (\text{式10})$$

【0033】

すなわち、波動関数は、バルク結晶全体に連続的に広がった状態で、波動関数は激しく振動している。この時、z方向の運動量の量子力学的期待値は、z方向の運動量演算子を  $k_z$  として(式11)となる事は当然である。

【0034】

【数11】

$$\langle \hat{k}_z \rangle = \int d^3r \psi^*(r) (-i \partial_z) \psi(r) \quad \dots \quad (\text{式11})$$

$$= k_z \pm k_0$$

【0035】

すなわち、シリコンなどの間接遷移型の半導体では、電子の多くは、運動量空間で、点から遠く離れた点にいる確率が圧倒的に高いため、非常に大きい運動量を持って動いているという事を数式の上からも示している。

本発明は、このz方向の厚さであるtが非常に小さい極薄膜の場合、量子閉じ込め効果によって、バルクでは間接遷移型の半導体が、実効的に直接遷移型に変わるという事を基本原理として使う。以下、この点について詳しく説明する。

【0036】

話を具体的にわかりやすく説明するために、引き続き、シリコンを例にとり、z方向の厚さtが非常に小さく、z方向の上下には、隣接して、 $SiO_2$ などのバンドギャップの大きい絶縁体か、さらにエネルギー障壁が大きい真空または大気に接していると想定する。同様の効果が期待できる系としては、たとえば、電界効果などによって、電子を狭い領域に閉じ込めれば同様の効果が期待できる。これらの場合、シリコン中の電子の波動関数は、z方向の上下の界面でゼロになる。もちろん、厳密には量子力学的な波動関数のしみ出しが存在するが、エネルギー障壁が大きいため、z方向の距離に対して指数関数的にしみ出しあるため、界面でゼロになるという近似はほぼ厳密に正しい。従って、外部から印加されるポテンシャル  $V(r)=0$  であったとしても、包絡線波動関数の様子はtが厚い場合と全く異なる。実際、このような量子井戸中に閉じ込められた電子及び正孔の包絡線波動関数は、離散的エネルギー準位を表す指数をnとして、n=0, 2, 4, ...と偶数の場合には、(式12)と解けるし、n=1, 3, 5, ...と奇数の場合には、(式13)となり、エネルギー準位の値は、nが偶数か奇数かによらず、(式14)と表す事ができる。

【0037】

【数12】

$$\chi_n(z) = \sqrt{\frac{2}{t}} \cos\left(\pi \frac{z}{t} (n+1)\right) \quad \dots \quad (\text{式12})$$

【0038】

【数13】

$$\chi_n(z) = \sqrt{\frac{2}{t}} \sin\left(\pi \frac{z}{t} (n+1)\right) \quad \dots \quad (\text{式13})$$

【0039】

【数14】

$$\Delta E = \frac{\hbar^2}{2m_l^*} \frac{\pi^2}{t^2} (n+1)^2 \quad \dots \quad (\text{式14})$$

10

20

30

40

50

## 【0040】

最もエネルギーが低い状態がn=0である事は言うまでもない。包絡線波動関数を示すにあたって、z軸の原点を薄膜シリコンの中心にし設定し、 $z=\pm t/2$ にエネルギー障壁の高い界面が存在するとした。ここで、この包絡線波動関数  $\chi_n(z)$  の性質について説明する。nが0または偶数であった場合、波動関数は、zの符号変化に対して対称的であり、 $\chi_n(z) = \chi_n(-z)$  という性質を有している。これをパリティが偶であるという。一方、nが奇数であった場合には、 $\chi_n(z) = -\chi_n(-z)$  という性質を有しており、パリティが奇であるという。このような対称性を反映した構造をもっているため、包絡線波動関数による運動量への寄与を評価すると、(式15)となる。

## 【0041】

10

## 【数15】

$$\langle \chi_n | \hat{k}_z | \chi_n \rangle = \int dz \chi_n^*(z) (-i \partial_z) \chi_n(z) = 0 \quad \dots \dots \dots \text{(式15)}$$

## 【0042】

これは、 $\chi_n(z)$  をz方向に対して微分をとると、もともと  $\chi_n(z)$  が有していたパリティと変わるため、z方向に対して積分をとるとゼロになるというきわめて一般的な性質を示している。つまり、電子がz軸方向に強く束縛されているため、包絡線波動関数が定在波となり、電子が動かなくなる性質があることがわかる。これは、バルク状態での包絡線波動関数が(式9)で与えられるように指数関数的であり、電子が運動量をもってバルク結晶全体を動きまわっているのと全く対照的である。ただし、Bloch関数の存在まで考慮した全波動関数は、(式1)の中に、(式2)及び(式6)及び(式13)または(式14)を代入したものであるため、z方向の運動量の量子力学的期待値は、(式16)となる事に注意が必要である。

20

## 【0043】

## 【数16】

$$\langle \hat{k}_z \rangle = \int d^3r \psi^*(r) (-i \partial_z) \psi(r) = \pm k_0 \quad \dots \dots \dots \text{(式16)}$$

30

## 【0044】

つまり、もともとの半導体材料の性質としてバルクのときには、一点に伝導帯の谷底があるわけではなく、 $(0, 0, \pm k_0)$  に谷底があるため、全体としての波動関数は、その性質を反映している。このようにしてみると、薄膜にしても、運動量  $\pm k_0$  を持つ、電子が動き回っているように見えるが、そこには注意が必要である事に気付いた。つまり、たとえば、シリコンのように結晶として反転対称性を有している物質では、 $(0, 0, +k_0)$  の谷と $(0, 0, -k_0)$  の谷がエネルギー的に等しく、縮退している事に注意が必要である。このように、極めて一般的に縮退したエネルギー準位を有する量子力学的な状態が空間的に同じ領域に閉じ込められると、それらの状態間に混成が生じる。つまり、 $(0, 0, +k_0)$  の谷と $(0, 0, -k_0)$  の谷の間を結ぶエネルギー的な結合が非常にわずかでも存在すれば、2つの離散準位は、結合軌道と反結合軌道を形成する。たとえば、バンド計算には十分に含まれていない電子間のクーロン相互作用などは、狭い領域に閉じ込められている電子間には強く働く事が考えられる。電子間に働く相互作用は電子相関と呼ばれ、高温超伝導をはじめとする多くの遷移金属酸化物などで大問題になっているが、バルクのシリコンでは、もともとのシリコン原子でのsp軌道が大きな軌道をもっていることを反映してこれまで大きな問題とはなってこなかった。しかしながら、量子力学的な効果が重要となるような非常に狭い領域に閉じ込めた場合には、クーロン相互作用が強く働くために、このような電子間のクーロン相互作用を無視する事ができなくなる。クーロン相互作用をきちんと取り入れて、ハミルトニアンの行列要素を計算すれば、そこには $(0, 0, +k_0)$  の谷と $(0, 0, -k_0)$  の

40

50

谷を結ぶ混成がある。そして、そのハミルトニアンを対角化すれば、結合軌道と反結合軌道に分裂していることがわかる。これは、ふたつの水素原子を近づけていった場合に、水素分子が形成されるプロセスと似ており、そのような系を評価する方法はHeitler-Londonによって量子力学が形成された70年位前から理解されていた。我々は、Heitler-Londonによって理解された結合状態の形成が、シリコンなどのIV族半導体が狭い領域に閉じ込められている場合において、谷間の結合にも重要なことにはじめて気がついた。また、たとえ、もし、そのようなエネルギー的な結合が全くなかったとしても、2つの状態のユニタリー変換から、z軸方向に運動していない定在波を構成できる。これをもう少し具体的に説明する。Bloch状態は、結晶の有する反転対称性から $u_{-k_0}(r)=u_{k_0}(r)$ という性質があるため、 $(0, 0, +k_0)$ の谷と $(0, 0, -k_0)$ の谷のBloch波動関数は、それぞれ、 $u_{k_0}(r)=u_{k_0}(r)e^{ik_0z}$ と $u_{-k_0}(r)=u_{k_0}(r)e^{-ik_0z}$ と表せる。従って、 $e^{\pm ik_0z}$ の部分に着目すればよい事がわかる。これらの波動関数の和と差から新しい基底状態を構成するには、ユニタリー変換Uによって、(式17)と変換してやれば良い。

【0045】

【数17】

$$U \begin{pmatrix} e^{ik_0z} \\ e^{-ik_0z} \end{pmatrix} = \frac{1}{\sqrt{2}} \begin{pmatrix} 1 & 1 \\ -i & i \end{pmatrix} \begin{pmatrix} e^{ik_0z} \\ e^{-ik_0z} \end{pmatrix} \quad \dots \quad (式17)$$

$$= \sqrt{2} \begin{pmatrix} \cos(k_0z) \\ \sin(k_0z) \end{pmatrix}$$

10

20

【0046】

従って、原子レベルの波動関数の変化は、 $2^{1/2}u_{k_0}(r)\cos(k_0z)$ と $2^{1/2}u_{k_0}(r)\sin(k_0z)$ という2つの定在波の波動関数によって記述できることがわかる。そして、波動関数全体を示すと(式18)及び(式19)と表すことができる。

【0047】

【数18】

$$\psi(r) = \sqrt{2}u_{k_0}(r)\cos(k_0z) \xi(z) \quad \dots \quad (式18)$$

30

【0048】

【数19】

$$\psi(r) = \sqrt{2}u_{k_0}(r)\sin(k_0z) \xi(z) \quad \dots \quad (式19)$$

【0049】

(式18)または(式19)の状態での運動量のz軸方向の期待値は、定在波である事を反映して(式20)となる。

【0050】

【数20】

$$\langle \hat{k}_z \rangle = \int dz \psi^*(z) (-i \partial_z) \psi(r) \quad \dots \quad (式20)$$

40

$$= 0$$

【0051】

つまり、電子がz軸方向には、全く動いていない事がわかる。基底を変えるだけで、運動量の期待値が変わって見える事には、誤解が生じかねないので、ここで注意する。実は、(式18)と(式19)のような基底波動関数は、運動量の固有状態ではない。すなわち、運動量演算子の行列要素は、(式18)と(式19)を用いると、(式21)となり、対角行列要素がゼロとなり、非対角行列要素が純虚数となる。

【0052】

50

## 【数21】

$$U \begin{pmatrix} k_0 & 0 \\ 0 & -k_0 \end{pmatrix} U^{-1} = \begin{pmatrix} 0 & ik_0 \\ -ik_0 & 0 \end{pmatrix} \quad \dots \dots \dots \text{ (式21)}$$

## 【0053】

このような基底を取ることが物理的に適切かどうかは、対象としている系の性質に依存する。我々は、極薄の単結晶シリコン膜を想定しているが、そのような場合は、z軸方向に対する並進対称性が崩れかけているので、運動量の固有状態である $u_{k_0}(r)e^{\pm ik_0 z}$ を用いるよりも、むしろ定在波となっている $2u_{k_0}(r)\cos(k_0 z)$ や $2u_{k_0}(r)\sin(k_0 z)$ を用いた方が適切である。逆に、バルクの状態を扱う時には、並進対称性が存在するため、 $u_{k_0}(r)e^{\pm ik_0 z}$ を用いた方が良い。また、バルク状態では、運動量 $\pm k_0$ を有している電子は結晶中を激しく動き回っており、その際に、結晶中の格子振動の量子であるフォノンなどに強く散乱されており、波動関数の位相がダイナミックに変化しているため、運動量 $+k_0$ の状態と運動量 $-k_0$ の状態がコヒーレントに結合した状態を形成する事は期待できない。これとは対称的に、極薄の単結晶シリコン膜などのように、散乱を特長づける長さである平均自由行程よりも薄いような、極めて狭い領域に電子を閉じ込めている場合、室温でも十分波導関数は位相の定まった定在波を形成できる。定性的には、電子の波が狭い領域を高速で行き来しているうちに、その領域の大きさにピッタリあう定常的な波になるという事を意味している。

## 【0054】

上述のように、詳細に簡単な数式を用いて説明したように、極薄の単結晶シリコン膜などに代表される極めて狭い領域に電子を閉じ込めた場合、バルクの電子状態では、伝導帯の電子が点に存在しないシリコンのような物質であったとしても、実効的に薄膜に垂直方向には運動しない事がわかる。これは、定性的には、薄膜に垂直な方向がなくなるため、電子が薄膜に垂直な方向には動けなくなるという極めて当然の事を示している。つまり、バルクでは高速に結晶中を動いていたとしても、薄膜では、そもそも動くべき方向がなくなってしまうため、電子は止まらざるを得ないという事を意味する。

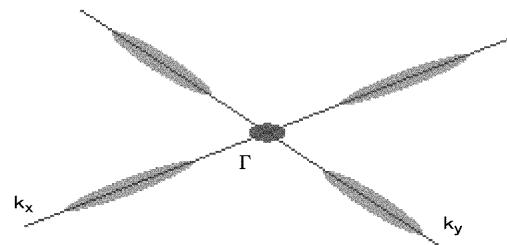

## 【0055】

この様子をバンド図を使って説明したものが、図1Bである。z軸方向への運動ができなくなったため、バルクのバンド構造である図1Aは、 $k_z=0$ の面に射影され、薄膜や電界効果を印加した場合などには、図1Bのようなバンド構造になる。図1Bのようなバンド構造は、シリコンで電界効果トランジスタを設計する際の基本であり、デバイス物理学の基本であると言っても差し支えない。このように2次元に閉じ込められた系は、2次元電子系と呼ばれている。薄膜でなく、細線構造にすれば、更に、次元を低下させた1次元電子系も形成できる。

## 【0056】

図1Bのようなバンド構造を前提とすると、上述のように、バルクでは、図1Aの谷底 $(0, 0, \pm k_0)$ に対応する状態が、図1Bでは点に来ていることがわかる。上述のように、この状態にいる電子は、z軸方向に動いていない。

このようなデバイス物理の基礎に立ち戻るならば、図1Bで点に存在する電子は、正孔と効率よく再結合し、発光素子として使えるはずであるという発想に至った。つまり、電子を閉じ込める事によって、電子は自由に動けなくなるわけであるから、同じく点に存在するため運動量の小さい正孔と衝突した際、やはり運動量の小さい光を運動量とエネルギーの保存則を破ることなく、放出する事ができるわけである。上述のように、運動量とは、粒子が別の粒子に衝突した際に、どの位の衝撃で粒子を散乱するかという尺度である。我々は、電子を狭い領域に閉じ込める事によって、電子を動けなくするようすれば、電子の運動量が失われるという事に気付いた。電子の運動量が小さくなれば、従来の方法では、難しかった散乱の際の運動量の保存則を満たす事ができるようになるため、シリコンなどのIV族半導体であっても効率よく光るようになる。

10

20

30

40

50

## 【0057】

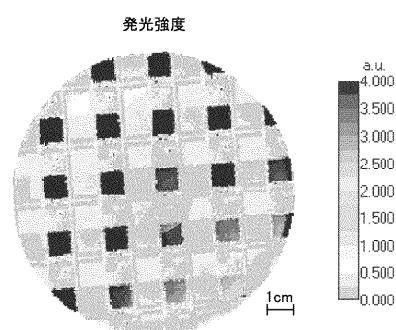

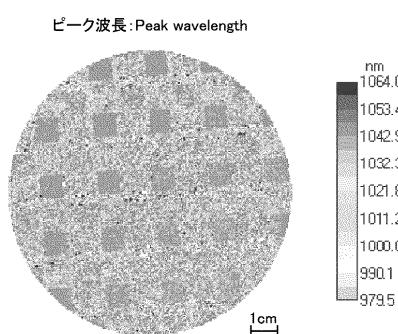

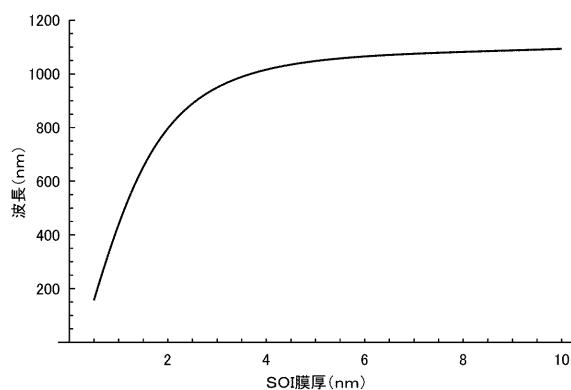

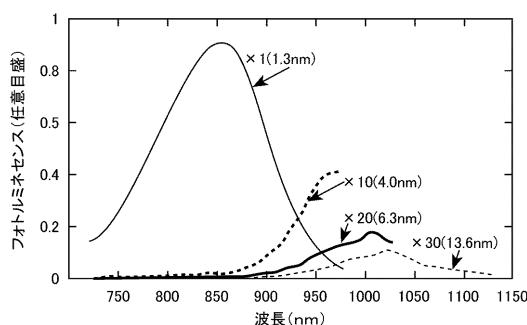

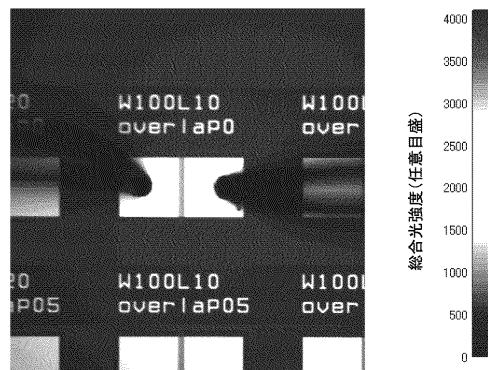

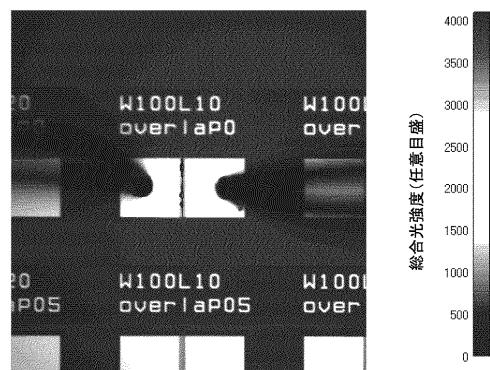

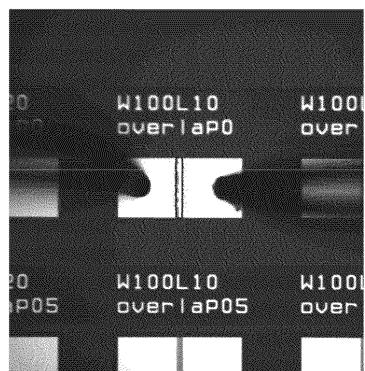

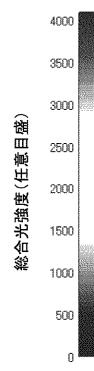

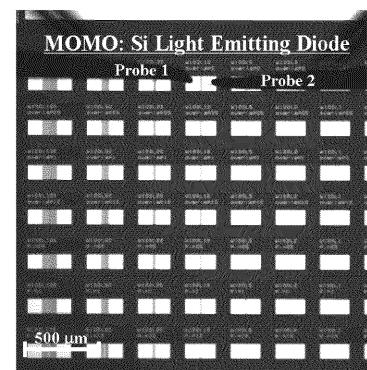

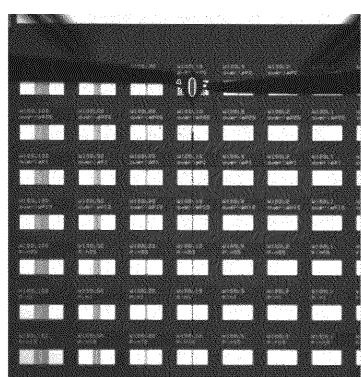

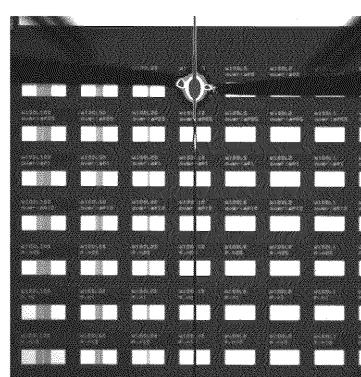

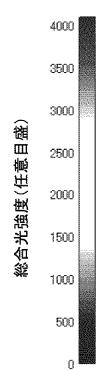

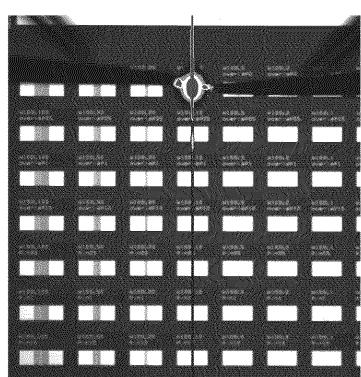

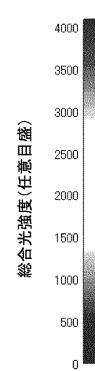

このような発想の元、実際に、極薄のSi膜を1cm角の大きさに基板に部分的に形成し、そのフォトルミネッセンスを測定した結果を図2及び図3及び図4Bに示す。図2及び図4Bには、フォトルミネッセンスによる発光の強度を示してある。ここから、極薄のSi膜から大変強い発光強度が観測された事がわかる。この強度は、バルクのシリコンの間接遷移による発光と比べて数桁大きいものである。つまり、狭い領域に電子を閉じ込める事によって、我々は、シリコンなどのIV族半導体が実効的に直接遷移型へと変化すると考えられる。また、図3には、この実験の際に得られたスペクトルのピークの波長を示してある。ここから、シリコンのバンドギャップより(式14)で示されるエネルギーだけ大きい波長が得られている事が確認できた。これは、量子閉じ込め効果によって、エネルギーが離散的になる分だけ、バンドギャップが大きい事を反映しており、上述の原理が正しい事を示している。バンドギャップが大きくなった結果、どの程度発光波長が変わるかを計算した結果を、図4Aに示した。上述したように、シリコンを高効率に発光させるためには、(100)面を表面とし、シリコンの膜厚を薄くすることによって、実効的にエネルギーの谷を点とする事ができる。10

## 【0058】

そこで、以下の構造を形成することで、エレクトロルミネッセンスの実証実験を行った。。

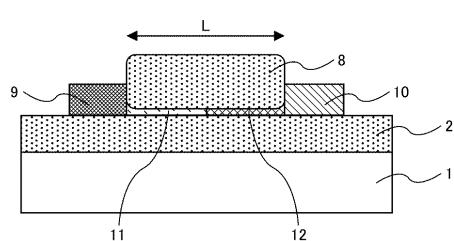

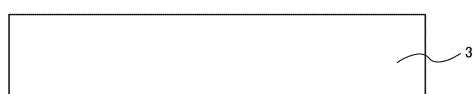

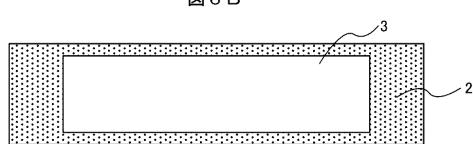

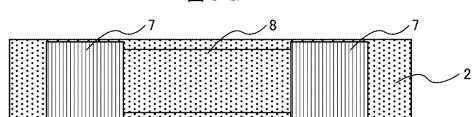

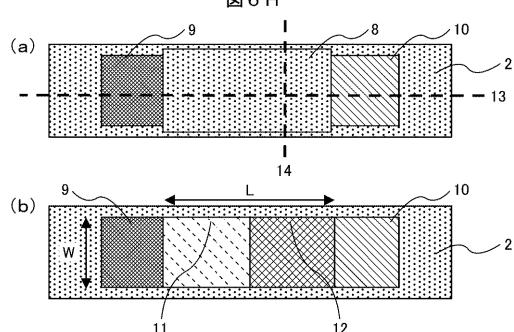

図5A～図5Hには、製造工程順に断面構造を示す。また、図6A～図6Hには、SOI基板の上部から見た製造工程順の模式図を示す。ここで、図5A～図5Hは、それぞれ図6A～図6Hの横方向の断面図であり、例えば図5Hは、図6H(1)における断面13で切り出した時の構造を表している。また、図6H(1)において、断面14で切り出した時の断面構造の模式図を図7に示す。デバイスの完成図は、図5H及び図6H(1)(2)及び図7である。20

## 【0059】

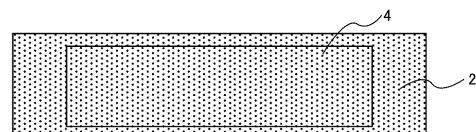

以下、順をおって製造工程を説明する。

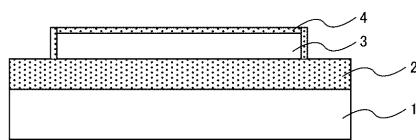

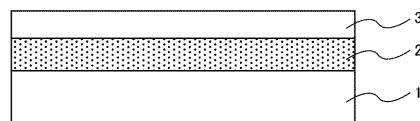

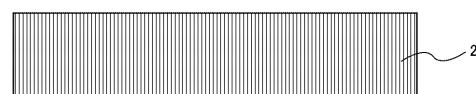

まず、図5Aに示すように、支持基板として、下からシリコン基板1、埋め込み酸化膜2 (Burried Oxide: 以下BOXと略す。) 及びSilicon On Insulator (SOI) 層3が積層されたSOI基板を用意する。図6Aに示すように、基板の上部からみるとSOI層3しか見えないが、SOI基板の厚さが薄い場合には、実際に試作すると下の基板が透過して見えることもある。ここで、Silicon On Insulator (SOI) 層3を構成している単結晶シリコンとしては、表面に(100)面を有している基板を用いた。試作したSOI層3のプロセス前の初期膜厚は55nmであった。また、BOX2の膜厚は約150nmであった。30

## 【0060】

次に、レジストを塗布した後に、フォトリソグラフィーによるマスク露光によって、所望の領域にのみレジストを残した後に、異方性ドライエッティングを施すによって、Silicon On Insulator (SOI) 層3を図5B及び図6Bに示すように、メサ形状に加工した。図では簡略するために、ひとつの素子しか示していないが、基板上に多くの素子を同時に形成している事は言うまでもない。シリコンプロセスを使っているため、歩留まり高く多くの素子を集積化できる。40

図には示していないが、引き続き、等方性ドライエッティングを施すことによって、メサ形状に加工したSilicon On Insulator (SOI) 層3の角を丸める処理を施す。このような角を丸める処理を施すことによって、この後の工程で酸化処理を施した場合に、エッジ部分のみ応力が集中して酸化が進まなくなる事を防止している。すなわち、もし、角を丸める処理を施さないと、角周辺部分のSilicon On Insulator (SOI) 層3が周囲と比べて厚くなるため、電流を流した場合に、この領域に集中して電流が流れてしまい発光効率が落ちるという問題が生じる。

## 【0061】

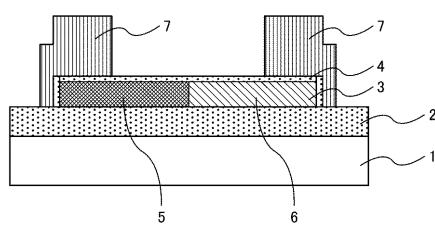

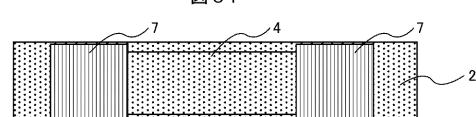

引き続き、表面を保護するために、SOI層3の表面を15 nm程酸化して、図5C及び図6Cに示すように二酸化シリコン膜4を形成した。二酸化シリコン膜4は、この後のプロセス50

で導入されるイオン注入によって基板が受けるダメージを軽減するばかりでなく、活性化熱処理によって不純物が大気中に抜けるのを抑制する役割がある。

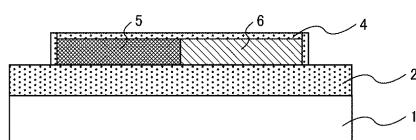

引き続き、フォトリソグラフィーを用いたレジストパターニングによって、所望の領域のみにレジストを残した後に、BF<sub>2</sub>イオンを加速エネルギー：15keV、ドーズ量： $1 \times 10^{15} / \text{cm}^2$ でイオン注入することによって、SOI層3中に、P型不純物注入領域5を形成した。

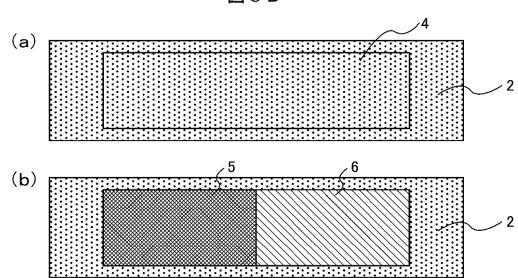

引き続き、レジストを除去した後に、再び、フォトリソグラフィーを用いたレジストパターニングによって、所望の領域のみにレジストを残した後に、Pイオンを加速エネルギー10keV、ドーズ量 $1 \times 10^{15} / \text{cm}^2$ でイオン注入することによって、SOI層3中にN型不純物注入領域6を形成した。この状態を図5Dに示す。上部から見た図は図6D(a)となるが、これではイオン注入した様子がわからないため、二酸化シリコン膜4の下部の様子を示したもののが図6D(b)に示されている。実際に、製造工程中に、光学顕微鏡を使って検査をしたところ、二酸化シリコン膜4はガラスであるため、透けて見え、図6D(2)のように異なる不純物を注入した領域が若干別の色に見える事が確認された。

このイオン注入工程においては、イオンが注入された部分のSOI層3がアモルファス化するため、結晶性が悪くなる。そこで、図には示していないが、SOI層3の表面のみがアモルファス化し、SOI層3がBOX2と隣接している領域には結晶シリコンが残るようにしている事が重要である。イオン注入の加速電圧を高く設定しすぎると、イオン注入した領域のSOI層3のすべてを非晶質化してしまうため、その後のアニール処理を施しても、単結晶性が回復せずに、多結晶となってしまうという問題が生じる。そこでイオン注入後の活性化熱処理などによって、結晶性を回復させる事ができる。上述のように、効率よく発光させるためには、単結晶性が良い事は、極めて重要である。

また、図5Dや図6D(b)では、P型不純物注入領域5に隣接してN型不純物注入領域6が設けられているが、隣接していないくとも差し支えない。マスクを用いたフォトリソグラフィーを製造工程に用いる場合、合わせずれが生じる事があるが、その場合には、P型不純物注入領域5とN型不純物注入領域6が離れたり重なったりする。

ここでは、マスクのパターンを適切に設定することによって、故意に、P型不純物注入領域5とN型不純物注入領域6の間にイオン注入を施していないSOI層3を残したものも同時に作製した。このようにイオン注入されていない領域(i領域)を含むダイオードは、pinダイオードと呼ばれる。極薄のシリコン層からなるpnダイオードとpinダイオードを同時に形成して実験をおこなっている。

#### 【0062】

引き続き、活性化熱処理を施して、不純物を活性化するとともに、イオン注入処理によってダメージを受けたSOI層3の領域の単結晶性を回復させても良い。しかしながら、本実施例では工程数の簡略化のため、ここでは活性化処理を行わずに、以下に示すように酸化処理を行うのと同時に不純物を活性化させるという製造工程をとった。これによって、工程数を削減できるため、製造コストを削減できる。ただし、ここで、活性化と単結晶性の熱処理を施しておいても問題ない。

#### 【0063】

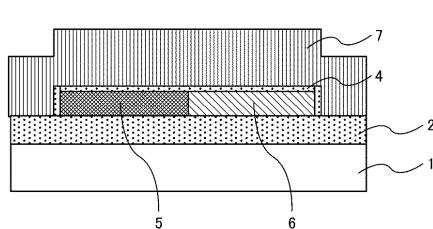

次に、シリコン窒化膜7を全面に100nmの厚さで堆積させ、図5E及び図6Eの状態とした。

引き続き、フォトリソグラフィーを用いたレジスト・パターニングによって、レジストを所望の領域にのみ残した後、異方性ドライエッティングを用いてシリコン窒化膜7を加工することによって、図5F及び図6Fの状態とした。

引き続き、洗浄工程を施した後に、酸化処理を行うことによってSOI層3の所望の領域を極限まで薄くする処理をおこなった。ここで酸化のための条件は極めて重要である。我々は、通常のシリコンプロセスで良く使われる1000以下の温度での酸化処理では、P型不純物注入領域5に形成される二酸化シリコンの膜厚とN型不純物注入領域6に形成される二酸化シリコンの膜厚との間に最大2倍程度の差が出る事を確認した。上述のように、効率よく発光させるためには、SOI層3の膜厚を平均自由行程よりも薄くする必要がある。シリコンでは室温における平均自由行程の大きさはおよそ10nmであるので、SOI層の膜厚は

10

20

30

40

50

10 nm 以下、より望ましくは 5 nm 以下に設定する必要がある。このような極薄膜を均一に形成するためには、不純物イオンの導電型によって酸化レートが異なる事は許されない。なぜならば、酸化レートに差があると、片方の領域を 5 nm 以下にした場合、もう一方の導電型の領域は厚くなりすぎるか、すべてが酸化されてしまい消失しているかの何れかになってしまふからである。我々は、酸化温度 1100 のドライ酸化処理を施せば、100 nm の酸化膜を形成する条件であったとしても、P 型不純物注入領域 5 に形成される二酸化シリコンの膜厚と N 型不純物注入領域 6 を形成される二酸化シリコンの膜厚の差を 1 nm 程度に抑制できる事を見出した。

#### 【0064】

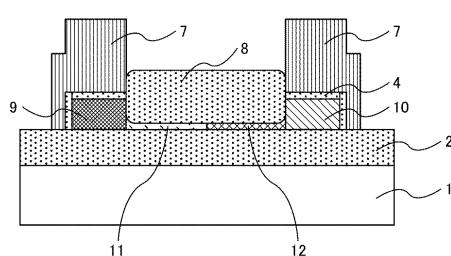

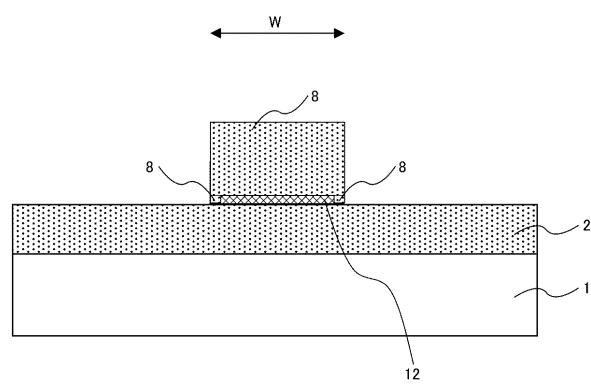

ここでは、酸化温度 1100 のドライ酸化処理によって、二酸化シリコン膜 8 を厚さおよそ 90 nm になるように形成した結果、極薄シリコン層の膜厚を約 5 nm にすることができた。また、その際に、n 型にドーピングした領域と p 型にドーピングした領域の膜厚の差を 1 nm 以下に抑制することができた。この酸化処理の際には、極薄シリコン層の膜厚を 1 nm 以下の精度で分光エリプソメトリーで観察しながら残りのシリコン層の膜厚を詳しく調べる事が求められる。酸化装置の中に、量産のためには、分光エリプソメトリーを内蔵している事が望ましい。また、生産するウェハの中には、あらかじめ、膜厚を検査するためのパターンを用意しておくことが望ましい。ここでは、図 2 または図 3 の発光領域が示すように、ウェハ中に約 1 cm<sup>2</sup> の大きさの検査のためのパターンを用意することで、ウェハ面内での膜厚分布を詳細に調べながら、酸化処理をおこなった。また、1100 という温度はイオンを活性化させるのに十分な温度であるため、この酸化処理によって、イオン注入によって導入された不純物が活性化され、p 型 SOI 領域 9、n 型 SOI 領域 10、p 型極薄シリコン領域 11、及び n 型極薄シリコン領域 12 がそれぞれ形成された。この状態を図 5 G 及び図 6 G に示す。

10

#### 【0065】

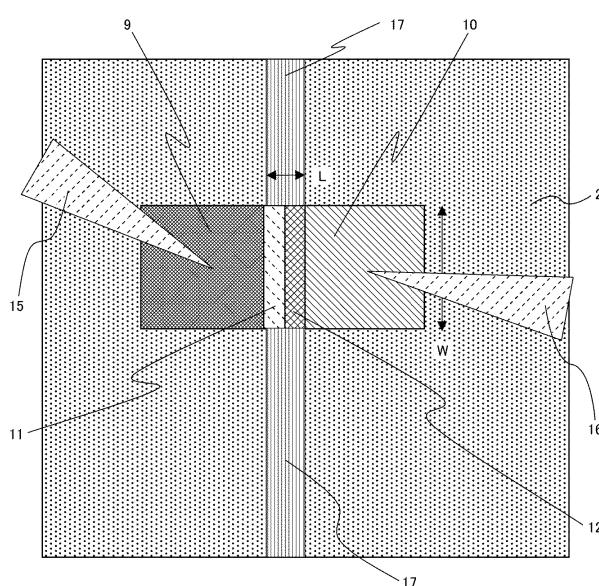

引き続き、洗浄工程と熱磷酸によるウェットエッチングによって、シリコン窒化膜 7 を除去した。その後、400 の温度で水素アニール処理を施し、プロセス中に生じた欠陥を水素終端する処理をおこなった。その結果、完成した発光ダイオードの完成断面図が、図 5 H に示されている。上部から見た図は図 6 H (1) となるが、これでは注入した様子がわからないため、二酸化シリコン膜 8 の下部の様子を示したもののが図 6 H (2) に示されている。また、断面 14 で切った場合の模式図が図 7 に示されている。図 7 では、n 型極薄シリコン領域 12 に隣接した側壁部が酸化され二酸化シリコン膜 8 となっている様子が示されている。

20

この後、所望の配線工程を行うことによって、シリコン基板 1 上に形成された高効率シリコン発光ダイオードが完成した。

30

#### 【0066】

図 8 には、ここで構造による発光ダイオードの特性を調べた時の測定方法を模式的に示した。探針 15 は p 型 SOI 領域 9 に接続されており、探針 16 は n 型 SOI 領域 10 に接続されている。探針 15 と探針 16 の間に電流を流すと、ダイオード特性が得られた。しかも、その電流電圧特性のしきい値は図 4 A で示したバンドギャップの増大分を反映するものであった。また、p 型極薄シリコン領域 11 と n 型極薄シリコン領域 12 の膜厚が 13.6 nm、6.3 nm、4.0 nm、1.3 nm と異なるように設計したものについても測定をおこなったところ、確かに図 4 A で示したバンドギャップ増大の膜厚依存性が観測された。フォトルミネッセンスによるスペクトルを図 4 B に示す。極薄シリコン領域の SOI 膜厚が小さくなるにつれて、発光強度が飛躍的に大きくなる様子がわかる。そして、発光 17 は、図 8 に示すように、p 型極薄シリコン領域 11 と n 型極薄シリコン領域 12 及びそれらの界面から発光する。図 8 では、理解を容易にするため、p 型極薄シリコン領域 11 と n 型極薄シリコン領域 12 の上部に重ねては、発光 17 を示さなかったが、上方にも発光 17 が進むことは言うまでもない。また、図 8 に示すように、発光 17 は基板に平行な方向にも進んでいる。

40

#### 【0067】

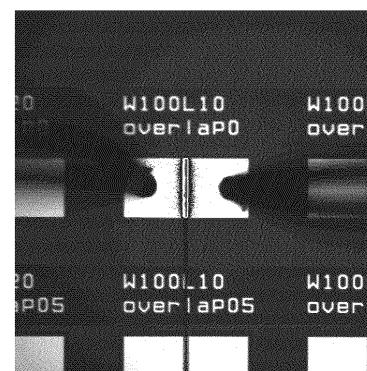

次に、図 9 A ~ 図 9 F に pn 接合に順バイアスをそれぞれ、0、1、2、3、4、5V 印加した

50

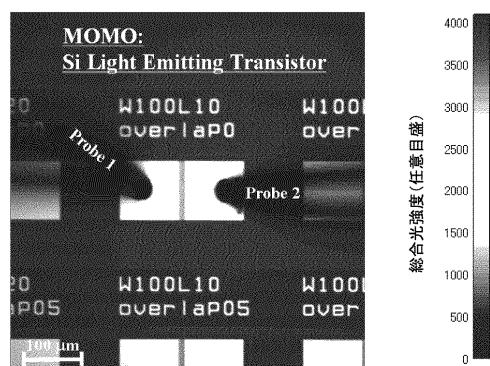

場合の発光像をコントラストによって示し、同時に撮影したデバイス素子の光学像とスーパーインポーズして重ねて表示した写真を示す。この素子の幅Wは100 μmであり、p型極薄シリコン領域11とn型極薄シリコン領域12をあわせた極薄シリコン膜の長さLは10 μmである。尚、図9Aにおいてプローブ1とプローブ2の間で縦方向の灰色の帯状に見える部分が、p型極薄シリコン領域11とn型極薄シリコン領域12が形成されている領域である。発光強度を示してあるが、確かに、p型極薄シリコン領域11とn型極薄シリコン領域12の存在するところからの発光強度が強く、SOI層の膜厚の厚いp型SOI領域9やn型SOI領域10からの発光はほとんどないことがわかる。これは、バルクシリコンでは発光強度が極めて弱く、極薄シリコンにすると発光強度が強くなるという上述の原理に基づき考えられる結果を得ることができることがわかった。実際、発光によってCCDが観測した光子の数をカウントしたところ、極薄シリコンからの発光強度は厚いシリコンからの発光と比べて数桁大きい事が明らかになった。またフィルタを入れて発光の分光をしてみたところ、波長が約1000 nm付近での発光強度が最も高く、波長500 nm付近ではほとんど発光が存在しないこともあわせて明らかになった。これは、発光が極薄シリコンのバンドギャップに起因した再結合による発光であり、運動エネルギーの大きいホットエレクトロンなどによる輻射による発光ではないことを示しており、上述の原理が正しい事が証明された。

#### 【0068】

次に、観察に用いたレンズをより低倍にして、順バイアス条件を0,、5,、10,、20,、30,、40Vにしてそれぞれ撮影した像を図10A～図10Fに示す。発光がやはりp型極薄シリコン領域11とn型極薄シリコン領域12が強く、同心円状に広がっていることがわかる。

この構造を用いれば、シリコンなどの基板上に、歩留り良く、IV族半導体を基本構成要素とした高効率に発光する素子を得られることがわかった。

#### 【0069】

【特許文献1】米国特許(US 6868214B1)

【非特許文献1】R. Chan, M. Feng, N. Holonyak, Jr., A. James, and G. Walter, 「アプライド・フィジックス・レターズ(Appl. Phys. Lett.)」, 2006年, 88巻, pp. 143 508-1～143508-3

【非特許文献2】L. T. Canham, 「アプライド・フィジックス・レターズ(Appl. Phys. Lett.)」, 1990年, 57巻, pp. 1046～1048

【非特許文献3】S. Coffa, G. Franzo, and F. Priolo, 「アプライド・フィジックス・レターズ(Appl. Phys. Lett.)」, 1996年, 69巻, pp. 2077～2079

【非特許文献4】F. Iacona, G. Franzo, E. C. Moreira, and F. Priolo, 「ジャーナル・オブ・アプライド・フィジックス(J. Appl. Phys.)」, 2001年, 89巻, pp. 8354～8356

【非特許文献5】S. Coffa, 「アイ・イー・イー・イー・スペクトラム(IEEE Spectrum)」, 2005年, Oct., pp.44～49

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0070】

上述のように、シリコンによる発光素子を得られるが、光による通信を考えると、そこでの発光を効率よく伝播させる必要がある。これまで、シリコンによる発光素子が得られなかつたため、同一チップ内で発光素子を形成し、その発光を引き出す構造というのを考えられてこなかつた。

#### 【0071】

本発明は、上記従来の課題を鑑みてなされたものであり、そこでその目的は、通常のシリコン・プロセスを用いて容易に形成可能な方法によって、シリコンなどの基板上に、シリコンやそれに順ずるゲルマニウムなどのIV族半導体を基本構成要素とした高効率な発光素子及びその導波路の製造方法を提供する事にある。

また、本発明の別の目的は、導波路をキャビティとし、レーザー発振するIV族半導体を基

10

20

30

40

50

準とした素子及びその製造方法を提供する事にある。

【課題を解決するための手段】

【0072】

本発明において開示される発明のうち、代表的なものの概要を簡単に説明すれば、以下のとおりである。

本発明による発光素子は、電子を注入する第1の電極部と、正孔を注入する第2の電極部と、第1の電極部及び第2の電極部と電気的に接続された発光部を備え、発光部を単結晶のシリコンとし、発光部が第1の面（上面）と第1の面に対向する第2の面（下面）を有し、第1及び第2の面の面方位を（100）面とし、第1及び第2の面に直交する方向の発光部の厚さを薄くし、該薄膜部の周囲に屈折率の高い材料を堆積することで導波路を形成する。

【発明の効果】

【0073】

本発明によれば、シリコンなどの基板上に通常のシリコン・プロセスを用いて容易に形成可能で、かつ、高効率に発光する発光素子および高効率に発光を引き出す導波路を提供する事ができる。

【発明を実施するための最良の形態】

【0074】

以下、本発明の実施例を図面に基づいて詳細に説明する。

なお、実施例を説明するための全図において、同一の機能を有する部材には同一の符号を付し、その繰り返しの説明は省略する。また、本実施例で紹介する方法以外にも、材料や製造工程の組合せを変える等、多くの変更が可能である事は言うまでもない。

【実施例1】

【0075】

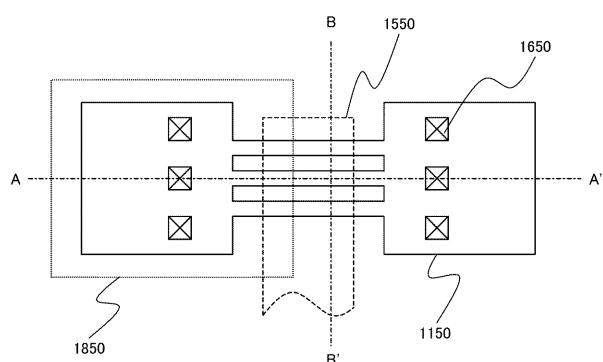

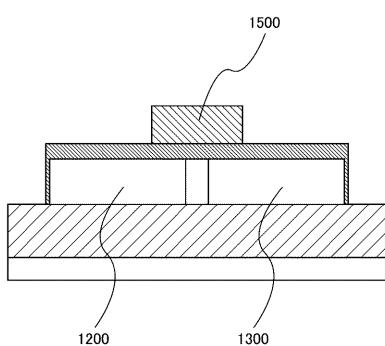

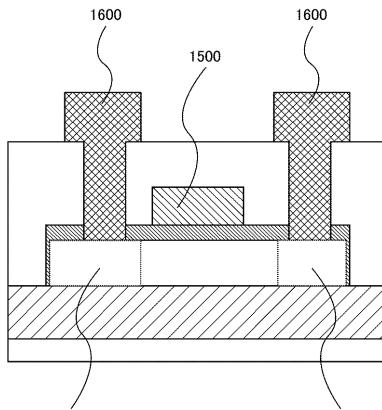

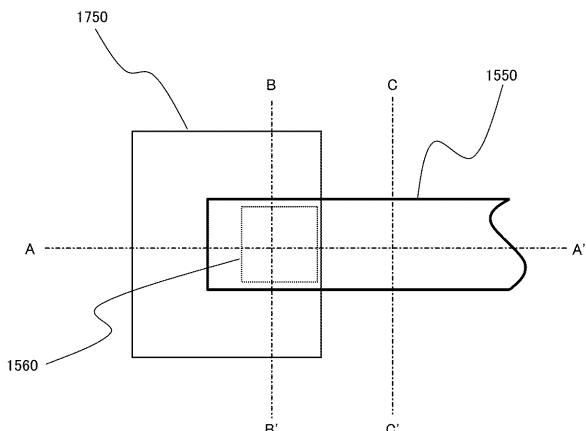

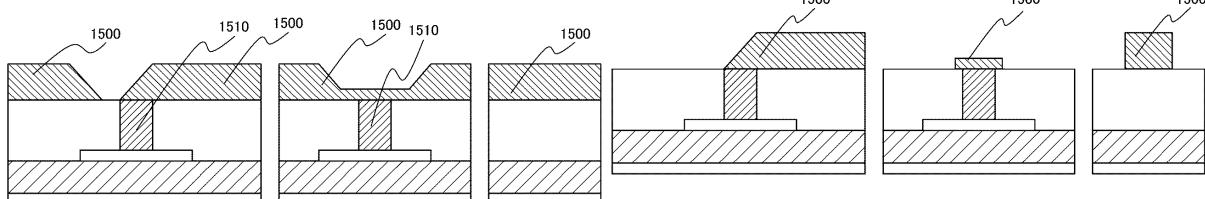

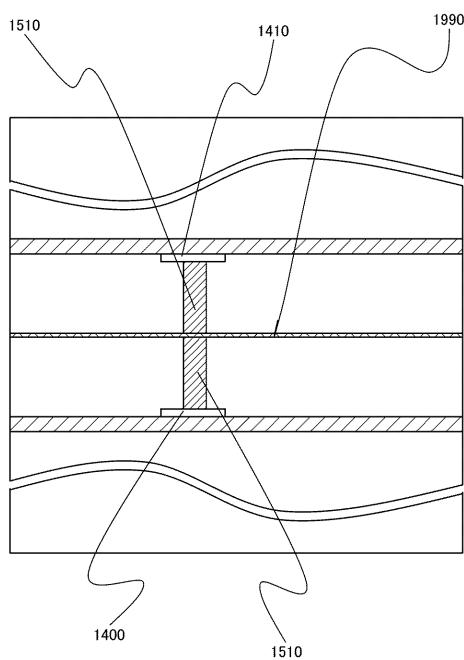

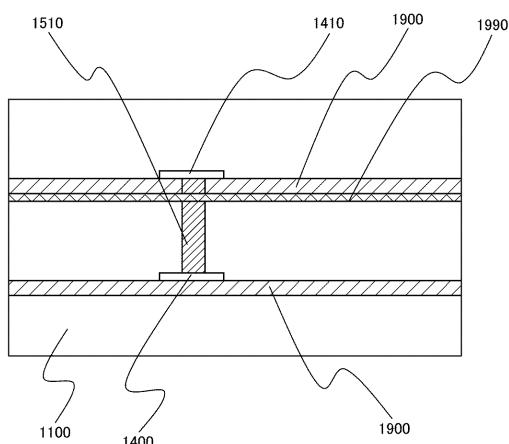

図11は、本発明による集積発光素子を形成する平面レイアウト、図12は本発明による受光素子を形成する平面レイアウトを示したものである。図13から図18は、集積発光素子の形成工程を示す素子断面構造図である。それぞれの図中左側に、平面レイアウト（図11）のA-A'断面、右側には平面レイアウト（図11）のB-B'断面を示した。

【0076】

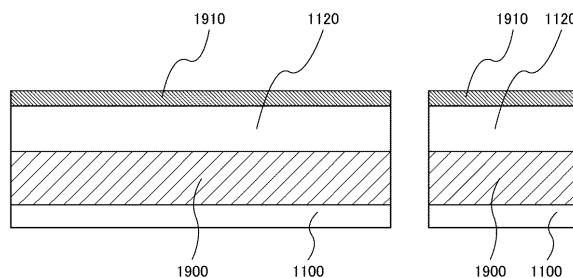

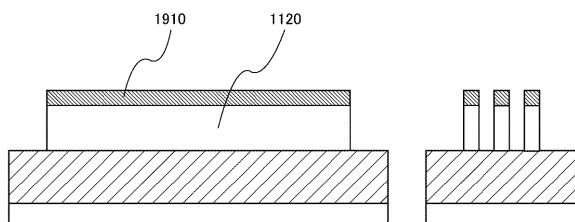

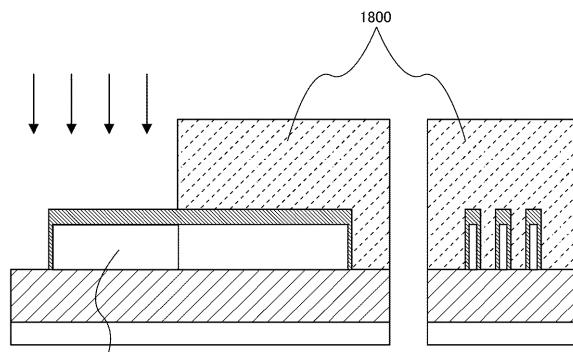

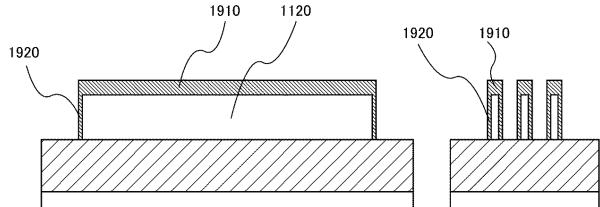

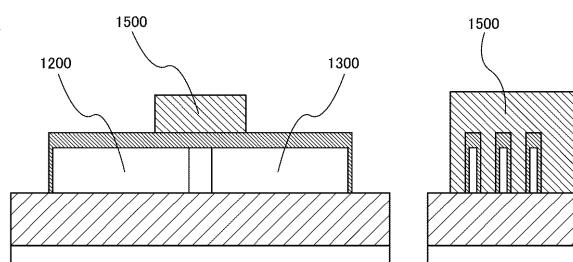

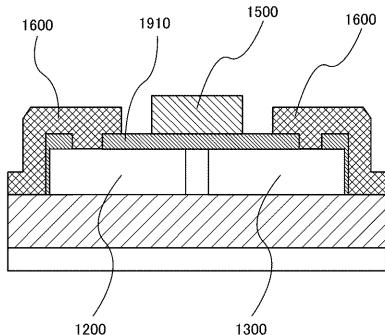

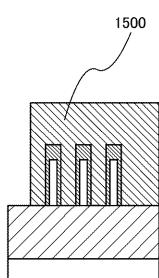

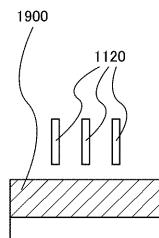

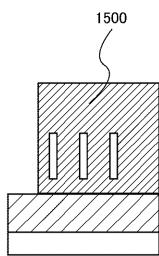

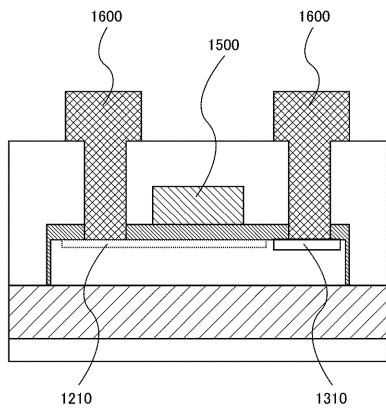

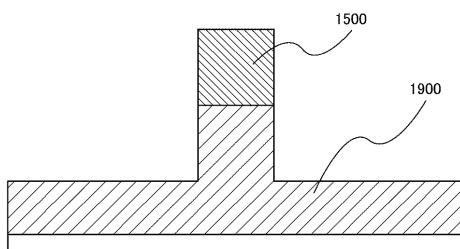

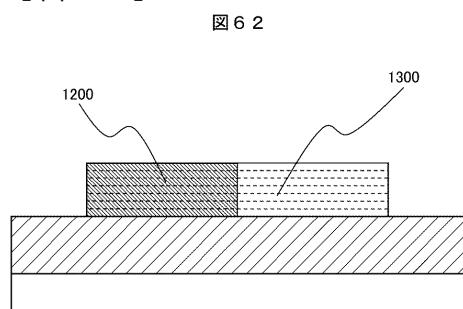

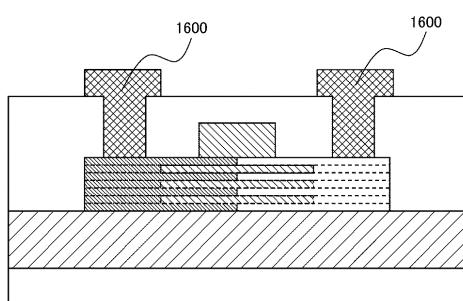

シリコン支持基板(1100)上に厚さ1μmのシリコン酸化膜(1900)と、このシリコン酸化膜上に厚さ100nmの単結晶シリコン(1120)を持ったSOIウエハを熱酸化し、厚さ20nmの酸化膜を形成する（図13）。図11に示した活性領域パターン1150を用いてシリコンの薄膜状領域（フィン）およびコンタクト領域を形成する（図14）。基板面に対して垂直方向に形成された薄膜状の単結晶領域を以下フィンと呼ぶことにする。フィン側面に露出したシリコン表面を熱酸化(1920)することで、フィンにより形成されたシリコン幅を所定（5nm）の厚さに設定する。このとき、露出するシリコン表面が（100）面となるようにSOIウエハの結晶方位を設定する（図15）。図11の1850孔パターンによりレジストマスク（1800）を形成し、イオン打ち込み法により砒素を加速エネルギー25keVで $2 \times 10^{15} \text{ cm}^{-3}$ ドーピングすることでN型不純物拡散層(1200)を形成する（図16）。その後、図示はしないが、パターン1850を反転させたレジストマスクを形成し、イオン打ち込み法でボロンを5keVで $2 \times 10^{15} \text{ cm}^{-3}$ 打ち込むことで、P型不純物拡散層領域(1300)を形成する。これによりPN接合を持つダイオードを形成する。ここでは反転マスクを用いたが、P-N間の距離を調整することで、P-N間に真性領域を設ける等により、電界を所望のものに設定することができる。

【0077】

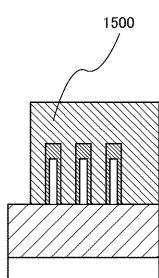

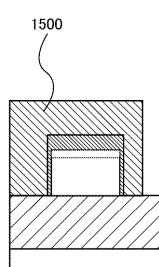

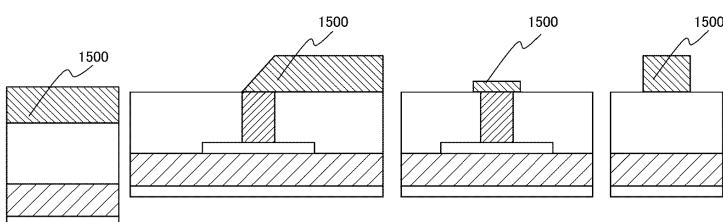

シリコン窒化膜を300nmをCVD法により堆積し、図11の導波路パターン(1550)を用いて導波路1500を加工する。並列配置したフィンが導波路1500により被覆される構成を得ることができる。ここでは、導波路という言葉を、单一波長等に限ることなく、広義の意味として光を伝える経路として用いる（図17）。

10

20

30

40

50

酸化膜1910にコンタクト孔(図11、1650)を開口し、金属配線1600を形成する。(図11では省略)

これにより、PおよびN領域に配線することで、PN接合部を順方向バイアスを印加することができる。これにより、並列配置したフィン内の接合部で発光を得ることができる。複数のフィン配置する場合、半波長間隔でフィンを配置することで、有効に発光を強めることができる。また、この構造を後述する反射膜層で覆うことでレーザー発振させることができる。

#### 【0078】

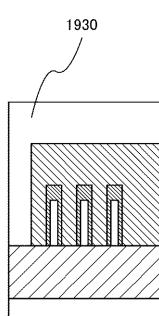

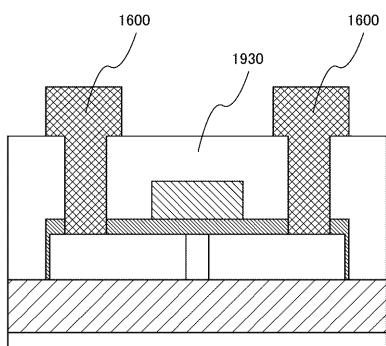

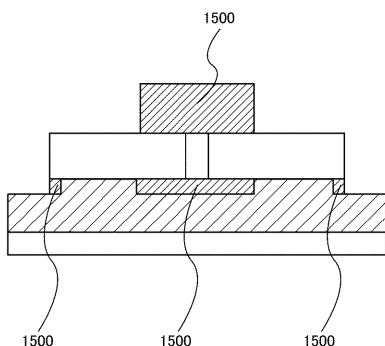

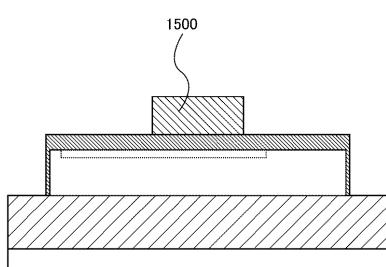

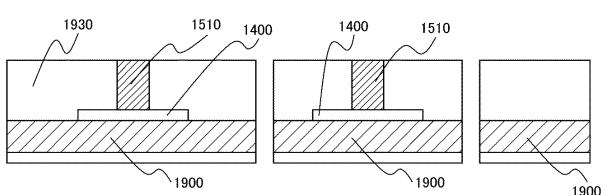

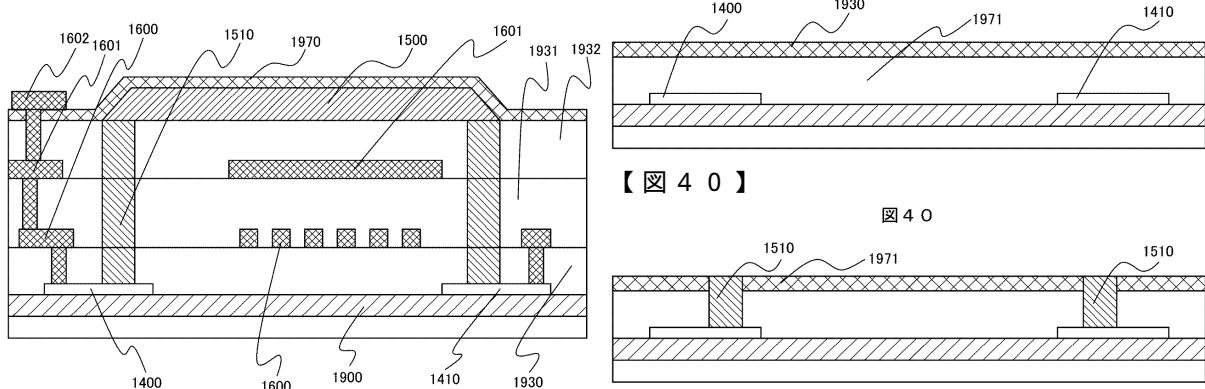

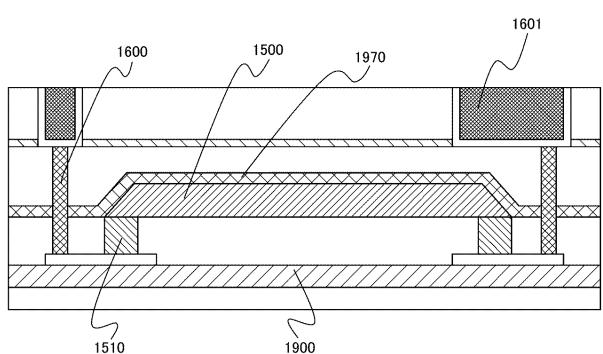

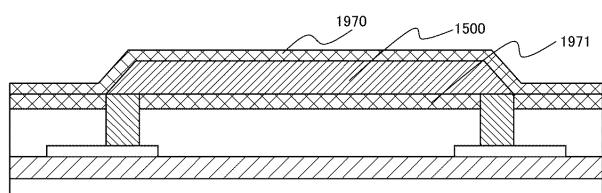

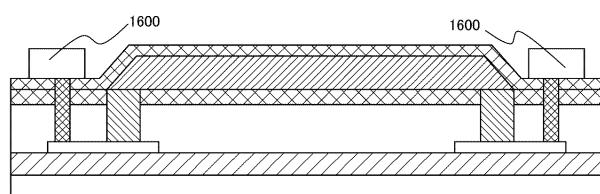

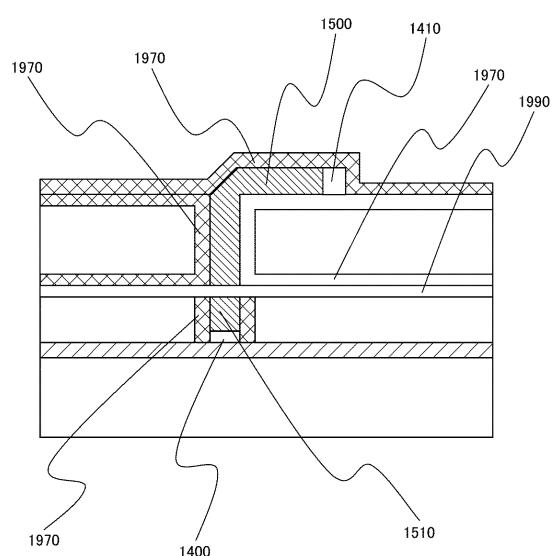

前述では、導波路を大気中に置く構成をとることで、シリコン窒化膜と大気との屈折率差を利用することで、導波路内に光を閉じ込めることができるていた。しかし、ULSIにおいては、多層の金属配線や、チップをパッケージに封入する使用法が広く用いられている。この使用法との整合性をとるため、図19、110に示すような方式をとることが考えられる。図24は、図17の工程で形成されたところを示したものである。その後、シリコン酸化膜1930を1μm堆積したのち、CMP法により研磨を行い平坦化する。このとき導波路はシリコン窒化膜で形成されているため、窒化膜にくらべ屈折率の低いシリコン酸化膜は反射被覆として働くことができる。該酸化膜等にコンタクトを開口し、金属配線1600を形成する。このようにすることで、従来ULSIと互換性をもった集積発光素子および導波路を形成することができる。

10

#### 【0079】

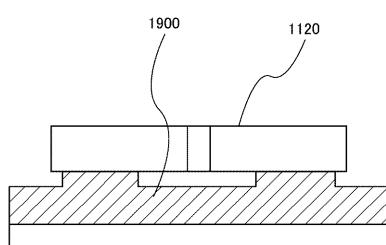

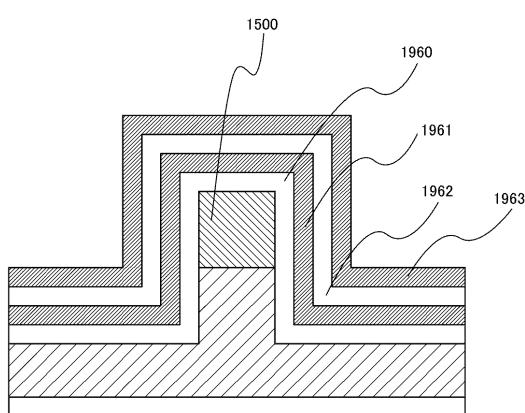

図21、および図22にその他の導波路の接続構成を示した。図16に示した工程の後、シリコン酸化膜をフッ酸系のウェットエッチを用いて、酸化膜1910を除去するとともに、埋め込み酸化膜1900をエッティングすることで、フィン下部の酸化膜を除去する。このとき、右図に示したようにフィン部は酸化膜から離れた構造になっている(図21)。前述と同様にシリコン窒化膜を堆積することで、フィンの全周を導波路1500を覆うことができる(図22)。

20

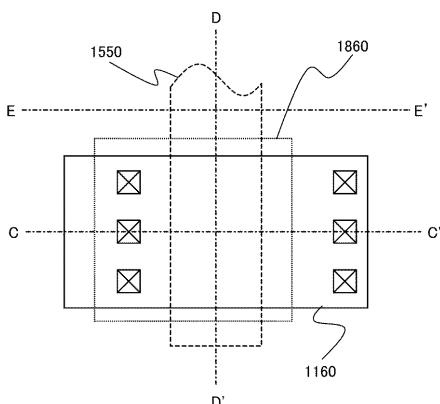

#### 【0080】

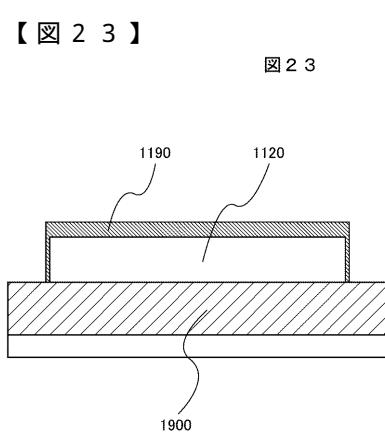

ここで、受光素子の例を示す。受光ダイオードは、これまで用いられてきているものである。平面レイアウトを図12に示している。図23から図26は、その断面構造を用いて製造工程を示したものである。前述した発光素子と、ここで述べる受光素子は、同一ウェハ上に集積されるものであるため、本来、同時に形成される。ここでは、集積発光素子構造を説明するため、別々に述べるものである。P型にドーピングしたSOI層(1120)を図12の活性領域パターン1160を用いて加工する。この工程は、前述図14で示したSOI層の加工に対応したものである(図23)。以下、対応する工程図番を参照として記す。

30

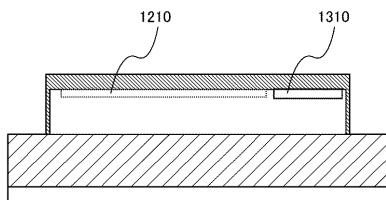

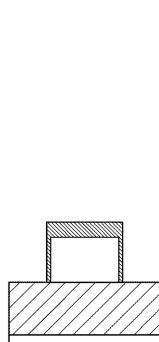

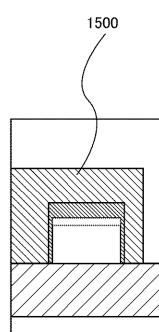

#### 【0081】

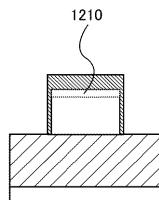

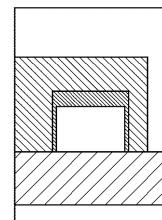

図12の1860パターンを用いてN型拡散層領域1210を形成する。また、P型高濃度不純物領域1310を形成する(図24)。シリコン窒化膜1500導波路を形成する(図25、図17参照)。電極層に対して金属配線を形成して、受光素子を得る(図26、図20参照)。受光素子のPNダイオードは水平方向の配置で形成することができる(図27)。これにより、縦方向に配置した場合には、PN接合による電界領域幅がSOI層の膜厚による制限を受けるのに対してPN接合による電界領域を大きくとることができる。

40

#### 【0082】

ここで説明したSOIウェハを用いた構造では、十分に厚い埋め込み酸化膜1900を持っている特長がある。そこで、導波路1500形成においても、この酸化膜を利用することができる。図28に示したように、導波路1500加工時に、埋め込み酸化膜1900を同時に加工し凸型の形状を得る。CVD法により、シリコン酸化膜層1960、シリコン窒化膜層1961、シリコン酸化膜1962、シリコン窒化膜1963を積層させることで、高反射膜(HR膜)を形成し、導波路1500をコア層とするクラッドを形成する(図29)。これにより、導波路1500に効率よく光を閉じ込めることができる。この場合、HRを構成する積層膜の膜厚を波長の1/4に設定する既知のHR形成法を用いることができる。例えば波長1μmの場合、シリコン窒化膜および酸化膜では、屈折率から約100-200nm程度の厚さになる。こ

50

これは、従来 LSI の配線工程で用いている層間絶縁膜厚と近いオーダーのものため、形成工程は従来のものを応用することが容易である。また反射効率を高めるため屈折率の異なる積層構造を多回繰り返し積層すことも問題なく形成できる。

#### 【 0 0 8 3 】

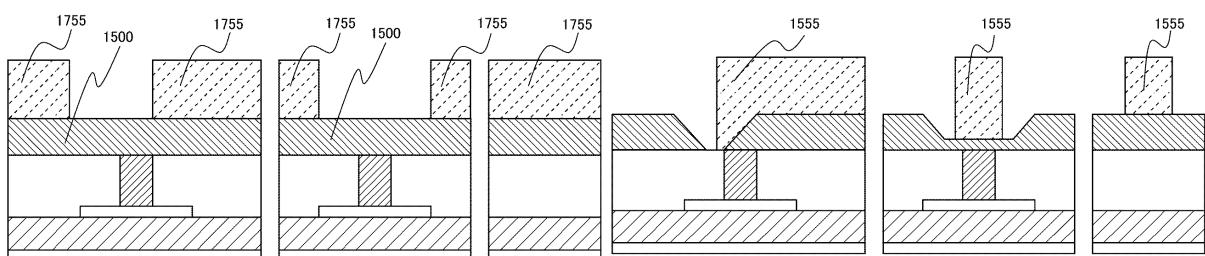

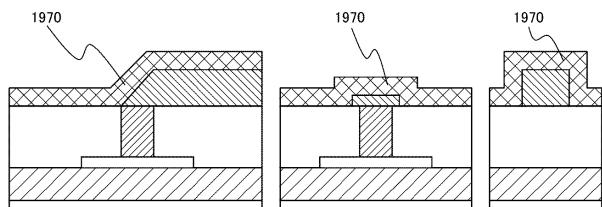

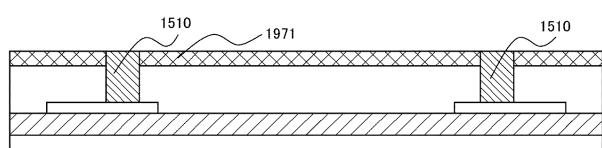

発光素子と受光素子を集積し、導波路により光による信号伝達を行う場合、光の進行方向を変える必要がある。その代表的な部位として、集積発光素子から導波路を基板面に垂直方向に引き出したのち、基板面と平行に引き回す場合にそのつなぎとなる部分が上げられる。受光素子においても同様の構成が求められることになる。図 3 0 に代表的引き出し部の平面レイアウトを示し、図 3 1 から図 4 1 に、図 3 0 A - A'、B - B'、C - C' での断面構造を用いて製造工程を示す。図中左側に A - A'、中央に B - B'、右側に C - C' を示している。断面構造において集積発光素子あるいは受光素子の領域を、1400 により模式的に示した。図 3 1 は、発光素子を形成後、シリコン酸化膜 1930 を堆積し、CMP 法を用いて平坦化した後、図 3 0 の導波路引き出しパターン 1560 により開口し、シリコン窒化膜 1510 を堆積したのちエッチバックすることで、窒化膜プラグを形成したところを示したものである。またこの工程のエッチバックに代えて CMP 法を用いて形成することもできる。CVD 法により導波路となるシリコン窒化膜を堆積した後、図 3 0 に示した 1750 を用いて図 3 2 のレジストパターン 1700 を形成する。レジストパターンを用いて、窒化膜 1500 をドライエッチングにより加工する。この際、反応生成物の堆積雰囲気となるエッチング条件を選ぶことで、加工側面が傾斜形状に加工する(図 3 3)。

#### 【 0 0 8 4 】

図 3 0 の導波路パターン 1550 によりレジスト 1555 を形成する(図 3 4)。これをマスクにシリコン窒化膜 1500 を加工する(図 3 5)。シリコン酸化膜とシリコン窒化膜を積層した高反射膜層 1970 を堆積することで、導波路 1500 を覆うように形成する。シリコン酸化膜とシリコン窒化膜は、それぞれ屈折率約 1.5 および 2 を持っている。またシリコン酸化膜(SiON)とすることで、組成をシリコン酸化膜に窒素を含有したものにすることができるため、シリコン酸化膜からシリコン窒化膜までの屈折率を設計することができる。これにより、垂直方向導波路 1510 と酸化膜 1930 上におかれた水平方向導波路 1500 を 45 度の反射面をもって接続される。集積発光素子から基板面に垂直に伝播した光を基板面に平行な方向に進行方向を変えることができる。ここでは、集積発光素子からの接続として示したが、同じ構造を受光素子部においても形成される。

#### 【 0 0 8 5 】

この導波路形成工程は、ULSI の配線工程を、そのまま行えることに特徴がある。その様子を断面構造を用いて図 3 7 に示した。広く行われている金属多層配線を持った ULSI の配線を模式的に示したものである。埋め込み酸化膜 1900 上に形成された 1400 は集積発光素子、1410 は受光素子をそれぞれ模式的に表したものである。ここでは多層配線例として、金属層 1600、1601 および 1602 の 3 層を持つ場合を示す。それぞれの層間絶縁膜が 1930、1931、1932 になっている。この導波路形成工程で用いている材料は、シリコンの酸化膜および窒化膜の絶縁体であり、これらは、これまでの配線工程で主たる構成材料ということができる。そのため、これまでの多層配線構造中にそのまま導入することができる。層間 1930 の平坦化後、金属配線のコントクト形成と同様に、垂直方向導波路 1510 を形成する。これを多層配線の各層ごとに繰り返すことで垂直方向導波路を形成する。もちろん、金属配線のコントクト形成とは分けて行えるため、2 層あるいは更に多層の層間膜を形成後、一括して垂直方向導波路の孔を開口してもよい。積層高反射膜層 1970 も層間絶縁膜として働かせることができるため、図示したように、金属配線 1602 を 1970 上に配置することができる。

#### 【 0 0 8 6 】

図 3 8 に導波路を金属配線より下層に形成する場合を示した。1600 は金属プラグ層、1601 がいわゆるダマシンプロセスによりけいせいされた金属配線層である。導波路形成時には、金属配線層が作られていない為、導波路として用いるシリコン窒化膜の堆積に、高温を用いた堆積法を使うことができ、屈折率の設定を容易にすることができる。

10

20

30

40

50

ここで用いている導波路および反射膜層は、通常のシリコンプロセスで用いている絶縁物だけで構成されているため、これまでの U L S I と集積した場合、 U L S I の電気特性を損ねることなく、導波路特性を向上させる構造を設計することができる。図 3 9 から図 4 2 に導波路を高反射膜層で覆う構造の形成工程を示している。集積発光素子 1400 および受光素子 1410 を形成し、絶縁膜 1930 およびシリコン酸化膜と窒化膜を組み合わせた積層高反射膜層 1971 を形成する（図 3 9）。垂直方向導波路 1510 を形成する（図 4 0）。前述（図 3 1 から図 3 6 参照）した導波路形成工程を用いて、導波路のコアとなる 1500 およびクラッド 1970 を形成する（図 4 1）。図 4 7 は夫々の素子に金属配線 1600 を形成した様子を示したものである。これにより導波路 1500 は高反射膜 1970、1971 により全周を覆うことができるため、有效地に光を閉じ込めることができる。

10

### 【実施例 2】

#### 【0087】

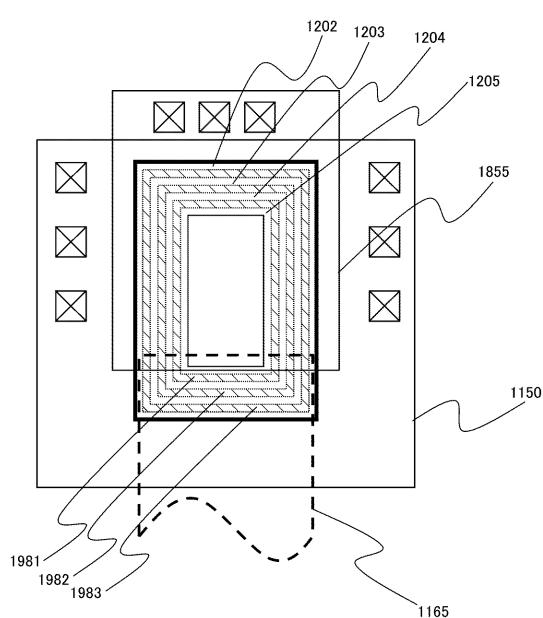

集積発光素子として、複数フィンを形成するものを示した。複数フィンの形成法としては、パターニングに依らずに形成することができる。いわゆるスペーサプロセスを用いた場合を以下に示す。代表的な平面レイアウトを図 4 3 に、また、このときの製造工程を示す素子断面構造図（図 4 3 の A - A' 断面）を図 4 5 から図 6 0 に示した。また、この作成法はダミーパターン 1152 をもとに形成することになるが、ダミーパターンの配置法として、島パターンである場合と孔パターンである場合の 2 通りが考えられる。図 4 3 は島パターンを用いた場合であり、孔パターンを用いた場合を図 4 4 に示した。この製造工程では、図 4 3 および図 4 4 のダミーパターン 1152 を形成した後、スペーサプロセスを用いてダミーパターンに対して自己整合的にフィンを形成される。そのため、フィンおよび形成に用いるスペーサ（1202、1203、1204、1205、1981、1982、1983）は自己整合のため、本来ホトマスクは存在しないが、ここでは、配置関係を示すため、形成後に置かれるパターン位置としてレイアウト図に示した。

20

#### 【0088】

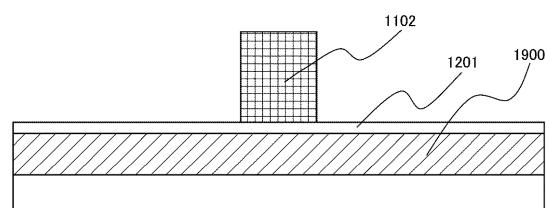

図 4 5 では、厚さ 50 nm の S O I (1201) 上にシリコン窒化膜を 300 nm 堆積し、図 4 3 に示した 1152 により島形状パターンを形成する。ここで島形状とは、図中 1102 に見られるように、断面図において平坦面上に凸型に現れる形状を表すものである。図 4 4 に示した 1152 の孔パターンを用いた場合には、凸ではなく凹形状に形成されることになる。以下の工程は島パターンを用いた場合で説明するが、孔パターンを用いても同様に形成することができる。

30

#### 【0089】

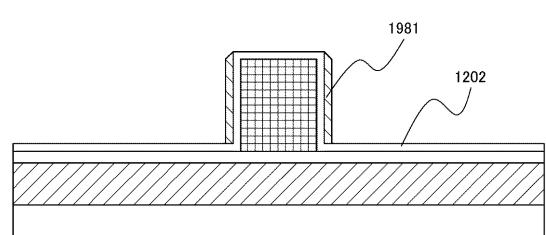

図 4 6 では、非晶質シリコン 1202 を 10 nm 堆積し、熱処理を加えることで、結晶化する。このとき、単結晶シリコン 1201 をシードに結晶成長が起こるため、1102 の側面下部には 1201 の結晶方位を保った単結晶を得ることができる。これによりフィンを得ることができる。ここでシリコン表面を熱酸化することでフィン膜厚を所定の厚さに調整することができる。さらにシリコン窒化膜 1981 を 20 nm 堆積する。異方性ドライエッチングにより堆積膜厚分エッチングすることでシリコン窒化膜 1981 をサイドウォールスペーサ形状にする。

40

#### 【0090】

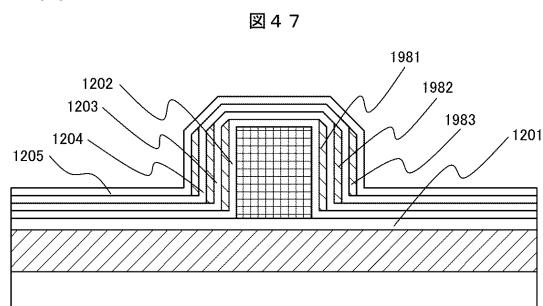

図 4 7 では、前記工程を繰り返すことで、薄膜の非晶質シリコン層 1203、1204、1205 と窒化膜スペーサ 1982、1983 の積層構造を得る。

#### 【0091】

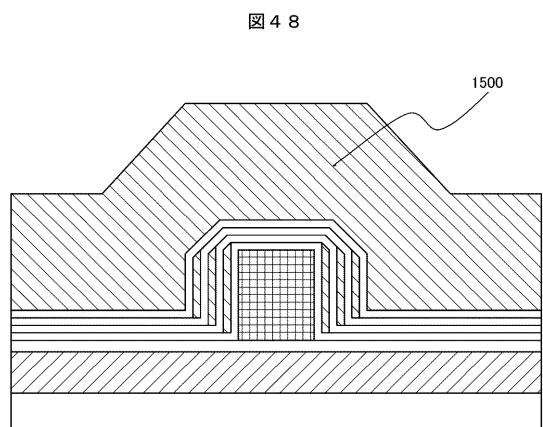

図 4 8 では、図 4 3 に示したパターン 1165 によりホトレジストの孔パターンを形成しシリコン窒化膜とシリコン薄膜の積層膜をエッチングし、埋め込み酸化膜 1900 を露出させる（図示省略）。シリコン窒化膜 1500 を集積発光素子部を覆うように 500 nm 堆積する。

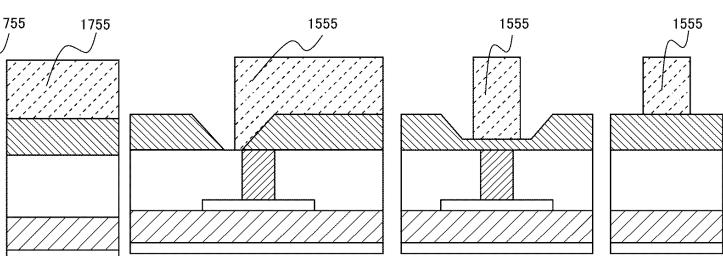

#### 【0092】

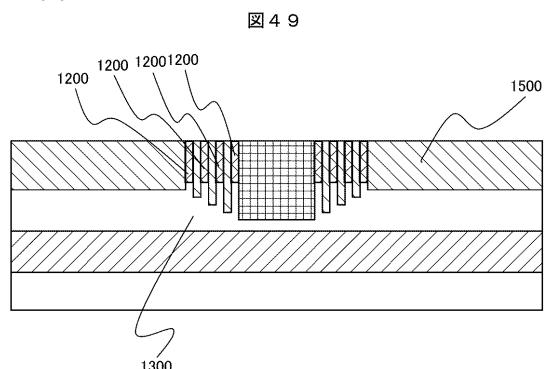

図 4 9 では、C M P 法により、堆積した窒化膜を平坦化し、ダミー 1102 を露出させる。図 4 3 に示したパターン 1150 をマスクに用いてイオン打ち込み法により、フィン下部および平面部 1300 に N 型領域、上部に P 型領域 1200 を形成することで、フィン内部に縦方向に

50

P N 接合を形成する。

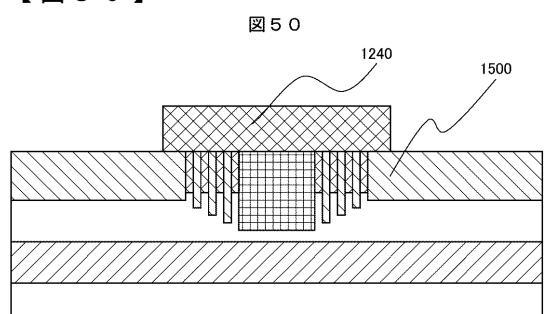

【 0 0 9 3 】

図 5 0 では、 P 型不純物を高濃度にドーピングした多結晶シリコン1240を 5 0 n m 堆積し、図 4 3 の 1855 を用いて加工する。

【 0 0 9 4 】

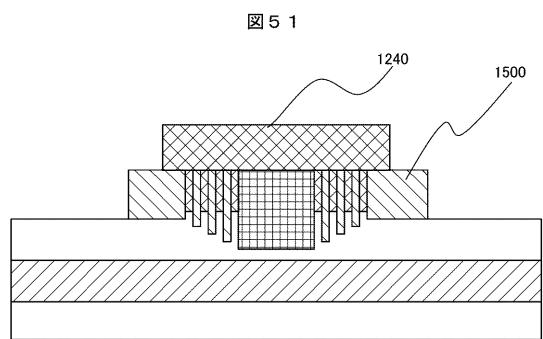

図 5 1 では、導波路 1550 パターンを用いてシリコン窒化膜 1500 を加工することで導波路を形成する。図 4 4 に示したダミー形成に孔パターンを用いた場合、図 5 3 を用いて説明した 1165 による加工と導波路 1500 形成を兼ねることができる。即ち、図 4 4 の 1165 パターンにより溝を形成したのちシリコン窒化膜 1500 を堆積し、 C M P 法を適用することで、溝パターン 1165 のシリコン窒化膜導波路を得ることができる。そのため、この図 5 1 で述べる 1500 形成工程は省略することができる。 10

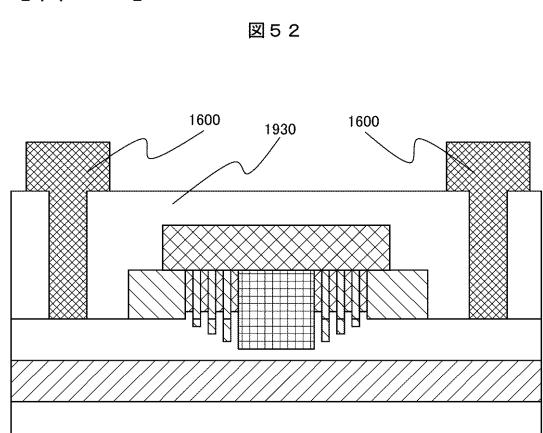

【 0 0 9 5 】

図 5 2 では、層間膜となるシリコン酸化膜を堆積平坦化したのち、各電極に金属配線を行う。

これにより、縦方向に P N 接合を持つ構造を得ることができ高密度で発光させることができる

上述した構造では、縦方向に P N 接合を形成したが、同様のスペーサプロセスを用いて、 S O I 基板よりエッティングによりフィンを形成することができる。

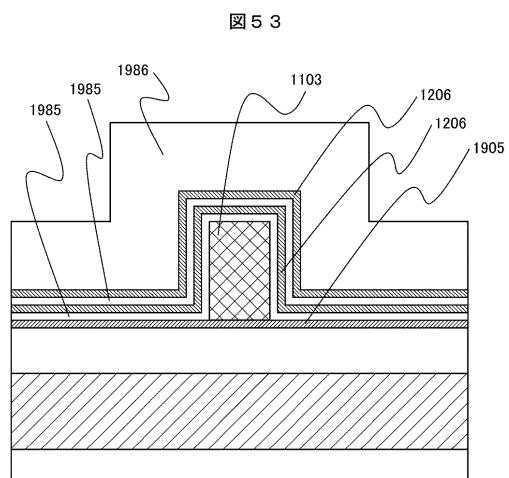

【 0 0 9 6 】

図 5 3 では、 S O I 基板 1120 表面を熱酸化し、厚さ 2 0 n m の酸化膜 1905 を形成する。多結晶シリコンによりダミー 1103 を形成したのち、シリコン窒化膜 1985 と多結晶シリコン 1206 を交互に堆積し、厚い窒化膜 1986 を堆積する。 20

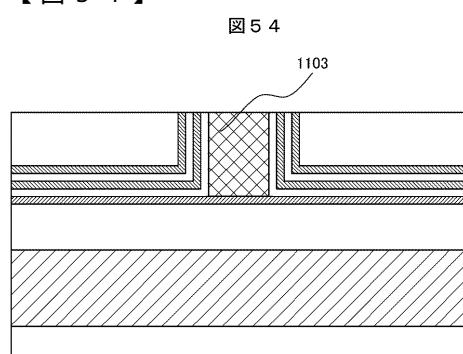

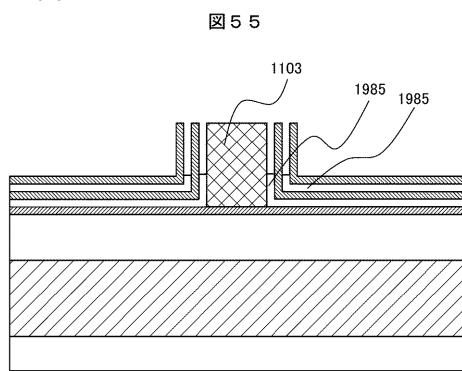

【 0 0 9 7 】

図 5 4 では、 C M P 法により凸部を平坦化し、ダミー パターン 1103 上部を露出させる。

【 0 0 9 8 】

図 5 5 では、ウエットエッティングにより窒化膜をエッティングし、多結晶シリコンによるパターンを形成する。

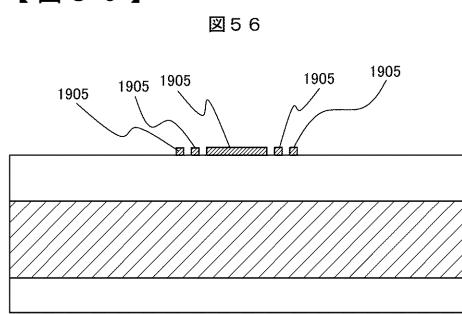

【 0 0 9 9 】

図 5 6 では、該マスクを異方的にエッティングし、酸化膜 1905 にパターンとして転写する。 30

【 0 1 0 0 】

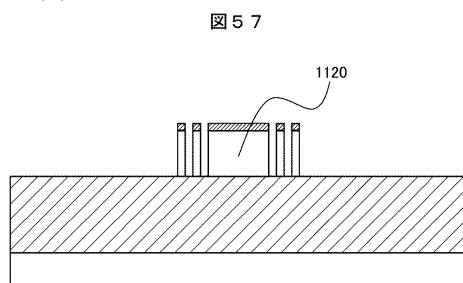

図 5 7 では、酸化膜パターンをマスクに S O I シリコン層をエッティングし、フィンを得ることができる。

【 0 1 0 1 】

以下、このフィンパターンを用いて発光素子を作成すればよい。ここでは、積層した膜により微細なフィンパターンを得たが、図 4 3 以下で述べたように、スペーサプロセスにより、フィン形成のためのマスクパターンを形成してもよい。

ここまで、フィンをもちいることで集積発光素子を形成する例を示したが、シリコン薄膜を基板面と平行方向に積層することで集積発光素子を形成することができる。

【 0 1 0 2 】

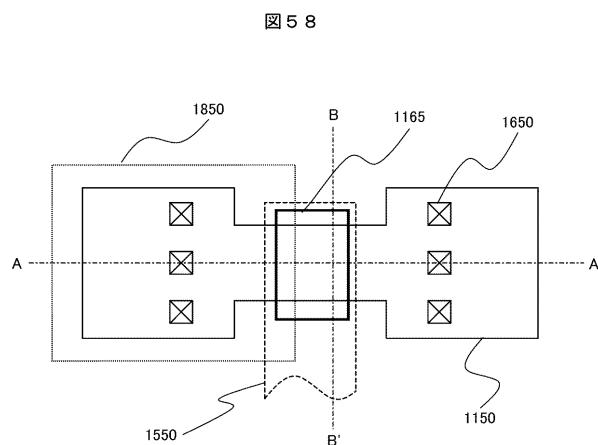

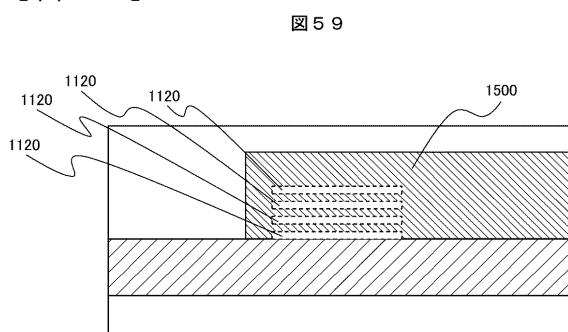

図 5 8 に、平面レイアウトを、図 5 9 は、図 5 8 の B - B ' 素子断面構造である。また、図 5 8 の A - A ' 断面で示した図 6 0 から図 6 5 を用いて、素子製造工程を説明する。

【 0 1 0 3 】

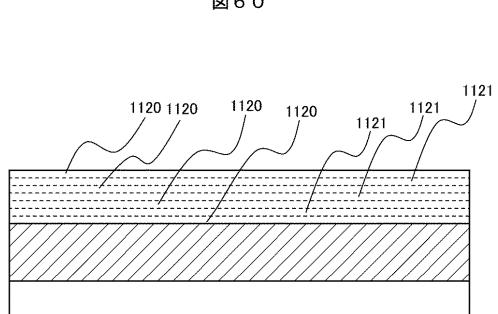

図 6 0 では、 S O I 基板 1120 上に M B E 法を用いてシリコンゲルマニウム 1121 とシリコン 1120 の厚さ 1 0 n m の薄膜を交互にエピ成長させる。

【 0 1 0 4 】

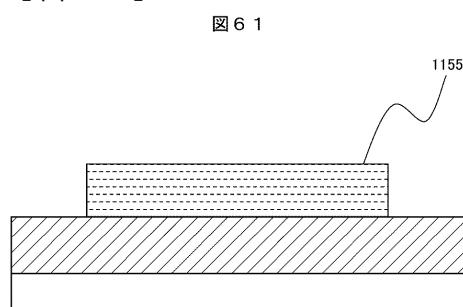

図 6 1 では、図 5 8 の活性領域パターン 1150 を用いて積層膜をエッティングする 1155 。

【 0 1 0 5 】

図 6 2 では、図 5 8 のイオン打ち込みマスク 1850 およびその反転パターンを用いて P N 接合を形成する。 50

## 【0106】

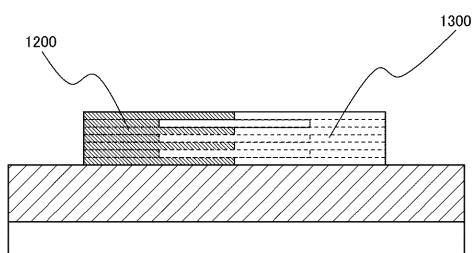

図63では、図58の薄膜化マスクパターン1165を用いて、シリコンゲルマニウム結晶層を選択的にエッチングすることで、P N接合を持ったシリコン薄膜の中空状薄膜構造を得る。

## 【0107】

図64では、シリコン窒化膜を堆積し、導波路パターン(図58、1550)を用いて加工する。このときシリコン薄膜によって形成された中空状領域には、シリコン窒化膜により埋められた構造が形成される。

## 【0108】

図65では、層間絶縁膜および金属配線を形成することで、縦方向に薄膜を集積した集積発光素子を得ることができる。

ここまで、同一チップ上に集積発光素子と受光素子を集積し、その間を導波路により接合することをしめしてきた。本発明は異なるチップ上に形成し、同様の導波路によりつなぐこともできる。

## 【0109】

図66に、2枚のウエハにそれぞれ集積発光素子1400と受光素子1410を形成し、導波路1510を形成する。導波路1510が露出した状態で、シリコン酸化膜とシリコン窒化膜を積層することで、低反射膜(A R膜)1990を形成し、A R膜を挟んで両ウエハを張り合わせることで導波路を接続することができる。

また、図67に示すように、SOIの支持基板を除去し、積層状に上に重ねて貼り付けて行くことで多層構成を得ることができる。この際、張り合わせ界面にA R膜を挟むことができる。

ウエハを積層した構造を導波路でつなぐ場合、導波路1500外周をH R膜1970で覆い、その張り合わせ部にA R膜1990を置く構造にすることで高い光の伝播効率を実現することができる。

## 【実施例3】

## 【0110】

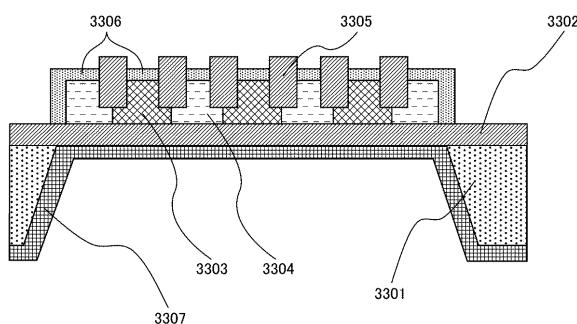

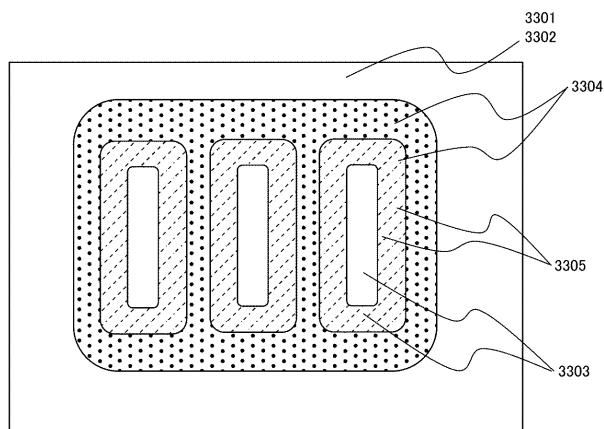

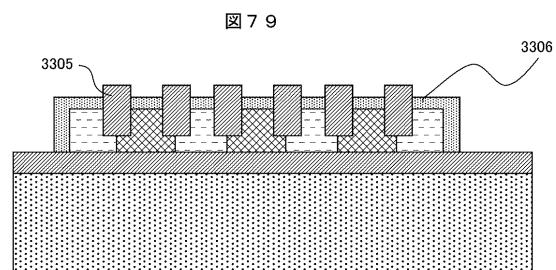

本実施例では、実施例1、2で開示したような、積層膜、もしくは、複数枚の壁状のシリコン薄膜を必要としない、発光領域の拡大法について実施例3として開示する。本実施例の発光素子では、図69に示したように、シリコン基板3301表面に形成したシリコン酸化膜3302に、導電型の異なるシリコン半導体領域3303、3304が、隣接して配置されており、この2つの半導体領域の界面近傍にのみ、シリコンの酸化膜3305が2つの半導体領域の表面の一部を覆うように形成されており、かつ、該酸化膜3305で覆われていない半導体領域の表面には、シリコンと金属の化合物である、シリサイド3306が形成されている。さらには、シリコン基板3301の一部、すなわち、その上に発光素子が形成されている領域のシリコン基板が、シリコン酸化膜3302が露出するように除去されており、この表面には、光の反射膜となる金属3307が堆積膜として形成されている。

## 【0111】

本実施例3の発光素子の平面構造を示したのが、図70である。3301、3302は、シリコン基板、および、その表面のシリコン酸化膜を示している。表面に見ているのは、シリコン酸化膜3302である。3304は、一方の導電型の半導体領域であり、3303は他方の導電型の半導体領域である。3305は、2つの導電型の半導体領域にまたがるようにして形成されたシリコン酸化膜の領域を示している。このように、本実施例3の発光素子においては、一方の導電型のシリコン半導体領域は、他方の導電型の半導体領域から周辺を覆われた平面構造になっているのが特徴である。周辺の接合部分が発光領域となり、これを、所望の数だけ並べることで、発光領域を拡大することができる。このとき、周辺を覆われた半導体領域を、円形あるいは正方形に近い矩形ではなく、細長い形にレイアウトすることで、発光するP N接合長をレイアウト面積に比べ大きなものにすることができます。また、別の特徴として、接合部は全て半導体領域の内部に形成され、端が半導体領域の端面に出ることはないため、この端の存在に起因したリーク電流などの不具合の懸念がない。また、さら

10

20

30

40

50

に別の特徴として、シリコン酸化膜3305で覆われていない2つの導電型の半導体領域の表面がシリサイド膜で覆われていることが上げられる。このシリサイド膜によって、発生した光は、窓となるシリコン酸化膜3305を通して効率的に外に出すことができる。また、シリサイドの存在によって、電圧を均一に印加することが出来るようになり、安定した動作が実現できる。

#### 【0112】

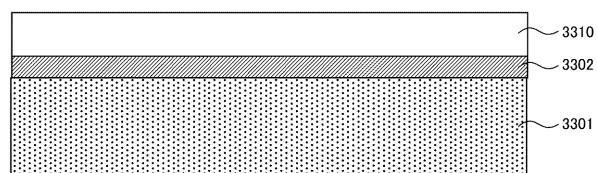

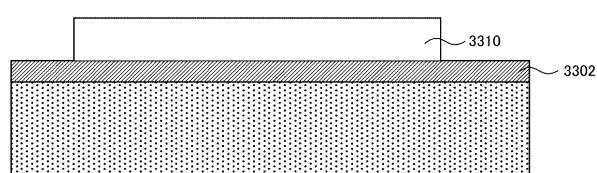

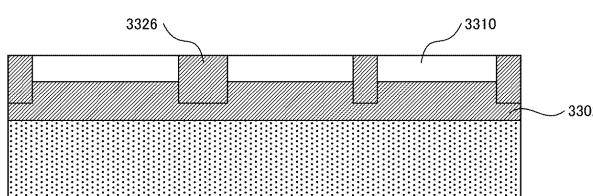

次に、図71以降を使って、本実施例3の発光素子の製造方法を示す。まず、図71に示したように、シリコン基板表面にシリコン酸化膜3302を既知の熱酸化法などを用いて、100-200nmの厚さで成長させる。次に、この酸化膜の表面に既知である貼りあわせ法を用いて、シリコンの単結晶膜3310を貼りあわせる。この構造は、いわゆるSOI(Silicon On Insulator)構造と呼ばれるシリコン基板の一種であり、既に、高性能マイクロプロセッサなどの半導体製品の一部で使われているものである。この実施例においても、このSOI基板は、ウエハーメーカーから購入したものを使っている。ただし、面方位は(100)であり、かつ、膜厚は、50nm程度のものを用意した。

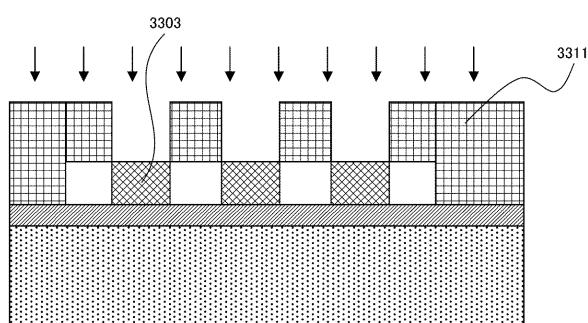

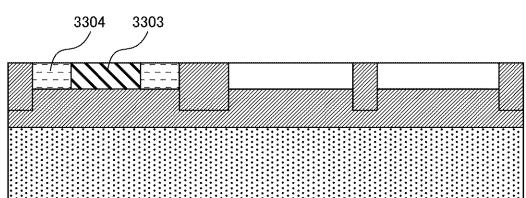

次に、この酸化膜上のシリコン薄膜3310を、所望の形状に、島状に加工する(図72)。シリコン薄膜3310の大きさは、この中に形成する領域の大きさと発光領域の大きさに依存して変化する。次に、シリコン薄膜内に、導電型の異なる2つの半導体領域を形成するために、まず、図73に示したように、イオン注入のマスクとなるフォトレジストパターン3311を、リソグラフィ法を用いて形成し、不純物をイオン注入した領域のみを開口する。この開口部を通して、本実施例では砒素、もしくは、リンを注入する。注入した不純物の量は、 $10^{14} - 10^{15}/\text{cm}^2$ である。

#### 【0113】

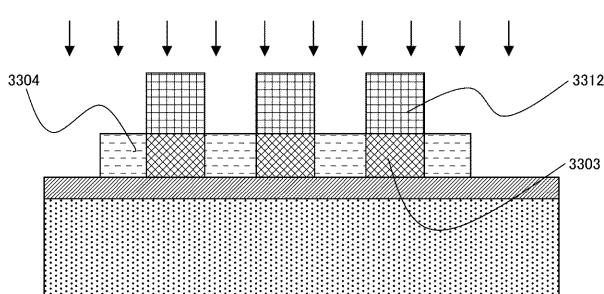

次に、図73においてイオン注入のマスクとなったフォトレジストパターンを洗浄で除去した後に、今度は、既に不純物を注入した領域を覆うためのフォトレジストパターン3312を、リソグラフィ法を用いて形成し、これをマスクとして、ボロンをイオン注入する。注入量は $10^{14} - 10^{15}/\text{cm}^2$ である。

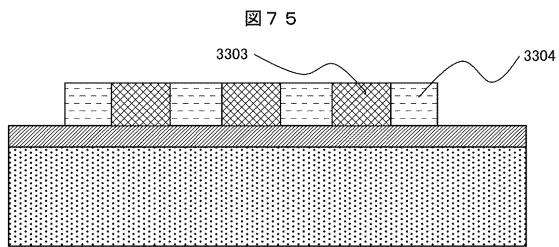

その後に、図75に示したように、フォトレジストパターンを洗浄で除去し、さらに、熱処理を加えることによって、不純物を活性化させる。これらの一連の工程によって、電子が充満したn型の半導体領域3303と、正孔が充満したp型の半導体領域3304を形成する。熱処理温度は900とした。なお、イオン注入に際して、フォトレジストマスクの開口部、もしくは、遮蔽部を調整したものを使い、n型とp型の半導体領域が重なるものや、n型とp型との間に、不純物の含まない、いわゆる、i型と呼ばれる領域を形成することも可能である。

#### 【0114】

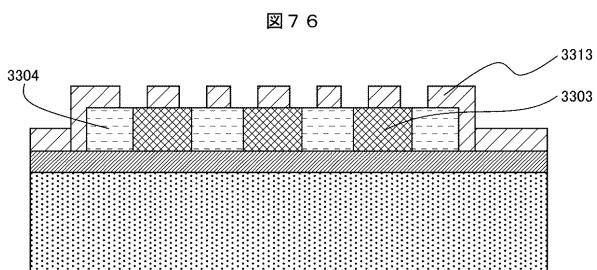

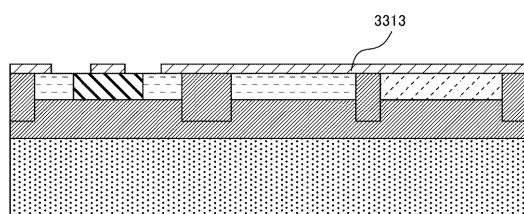

次に、図76に示したように、基板表面上をシリコンの窒化膜3313で覆い、n型半導体領域3303とp型半導体領域3304の界面近傍のシリコン薄膜表面が露出するように、リソグラフィ法とドライエッチ法を用いて、シリコン窒化膜3313を加工する。

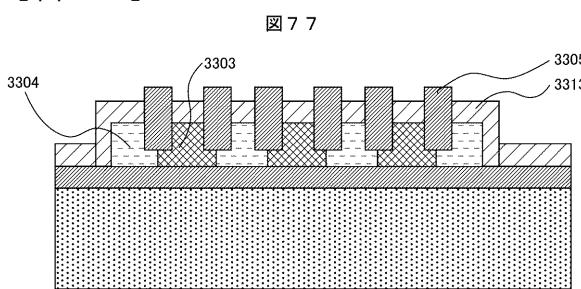

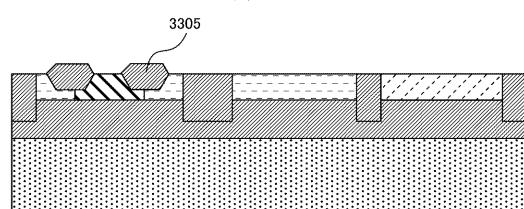

次に、図77に示したように、この基板全体を高温の酸化雰囲気に入れると、シリコン窒化膜3313で覆われていないn型とp型の半導体領域表面にのみ、シリコン酸化膜3305が選択的に成長する。これは、シリコンの選択酸化法と呼ばれるもので、既に使われている方法である。酸化雰囲気は1000程度の水分を含んだ雰囲気である。水分を含んだ雰囲気を用いると、酸素雰囲気に比べて、短時間で比較的厚い酸化膜を成長させることができる。成長させた酸化膜は80nm程度であり、これによって、酸化が進行したシリコン薄膜では、10nm程度のシリコン領域(n型とp型の界面を含んだ)が形成される。

#### 【0115】

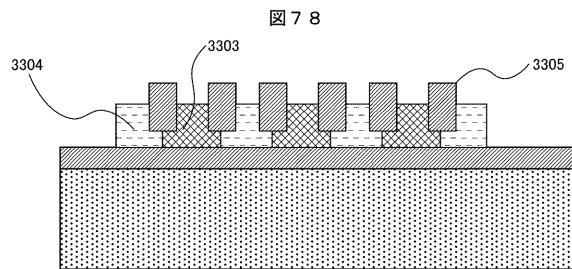

さらに、図77の工程で選択酸化のマスクとなったシリコンの窒化膜3313のみを、選択的に除去する。そのために、加熱したリン酸溶液にこの基板を浸漬する。その結果、図78に示したように、成長した酸化膜を残しながら、半導体領域が露出する。

次に、この表面全体にチタン、コバルト、ニッケルなどの金属を数10nm堆積して、これにまず450程度の熱処理を加え(窒素雰囲気)、酸化膜3305上に堆積した、未反応の金属

10

20

30

40

50

を、過酸化水素を含む溶液で除去する。シリコン薄膜上に堆積した金属は、熱処理によって化学反応を起こしシリサイド化しているために、溶液で除去されることはない。その結果、図79に示したように、酸化膜3305にはシリサイドがない構造が実現される。ただし、このままではシリサイドの抵抗が高いために、さらに700°C程度の熱処理を加え、低抵抗化させる。この手法も、シリコン半導体プロセスでは一般的に使われている手法である。

#### 【0116】

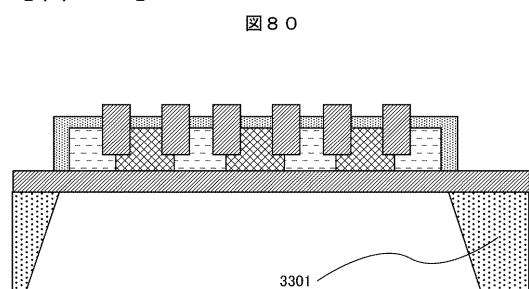

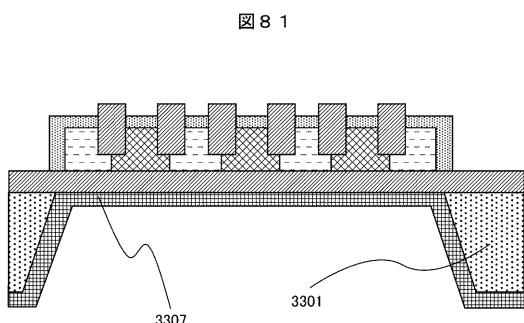

次に、図80に示したように、シリコン基板の一部（発光素子を形成している領域）のみを、選択的に除去する。そして、図313に示したように、光の反射板となる金属を、蒸着法などを用いて形成して、発光素子の製造を終了する。なお、本実施例では、発光素子の製造方法のみを説明しているが、実際には、これに、周辺の半導体素子を作製する工程や、それらの半導体素子と発光素子を電気的、かつ、光学的に接続する工程を行う。そのため、基板の裏面に反射板となる金属を被着させるのは、通常は、工程の最後となる。配線工程を含む場合、発光素子の2つの半導体領域に電流を流すための配線、および、コントラクトの開口を示したのが図82である。

#### 【実施例4】

#### 【0117】

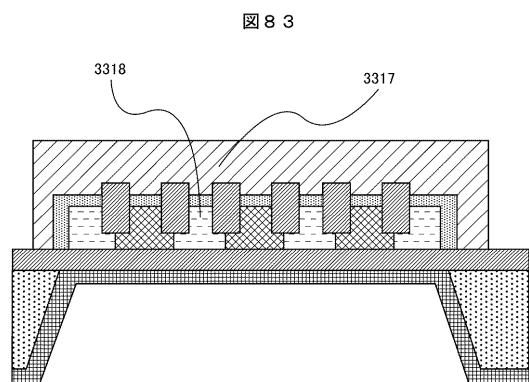

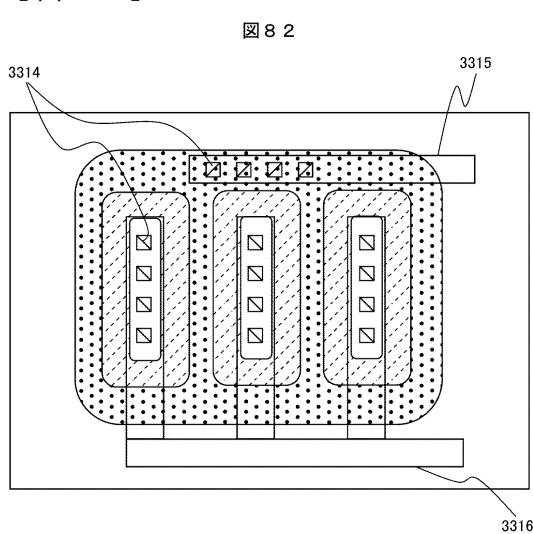

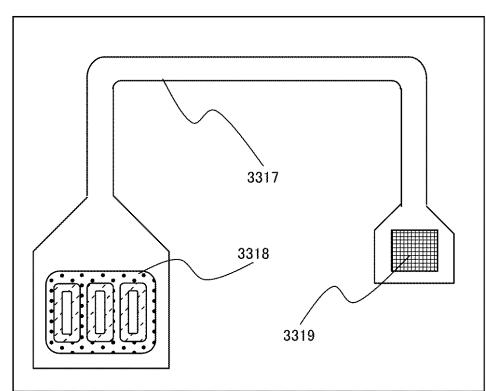

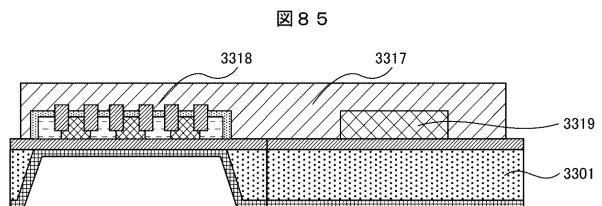

本実施例では、上述した発光素子から発せられた光を、受光素子に導くための導波路を実装している。発光素子から出た光は、波長が約1000nm付近での発光強度が最も高く、これは、発光が極薄シリコンのバンドギャップに起因した再結合に起因している。この光を導波路に閉じ込めるために、発光素子全体3318をシリコンの窒化膜3317で覆い、さらに、このシリコン窒化膜3317を、図84に示したような形状で、基板上に導波路パターンとして配置し、その終端には受光素子3319を配置する。シリコン窒化膜3317からなる導波路は、その周囲をシリコン窒化膜より屈折率の小さなシリコン酸化膜（図83では簡略化のために省略されている）で覆われており、発光素子から出た光は、窒化膜の外に漏れ出ることはない。なお、受光素子としては、公知のシリコンデバイスを用いた。図85は、発光素子3318、受光素子3319、および、シリコン窒化膜3317からなる素子群を一体化したチップの断面図である。受光素子は既知のシリコン受光素子であるが、これも、発光素子と同じように、基板3301表面の酸化膜上に形成された単結晶シリコン薄膜を用い、従来のシリコン半導体プロセスを用いて同時に形成されている。

#### 【実施例5】

#### 【0118】

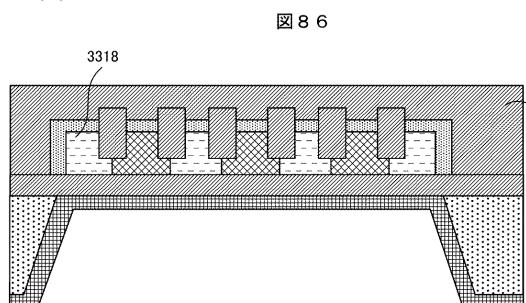

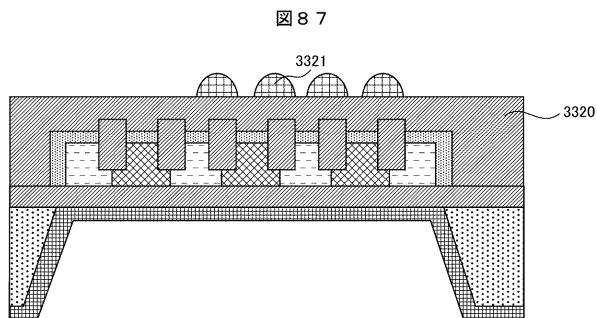

本実施例5は、光の伝播を効率的に行うための導波路に関するものである。まず、図86に示したように、発光素子3318全体を覆うようにシリコン酸化膜3320を、層間絶縁膜として堆積し、これを、公知の化学的機械研磨法などを用いて平坦化する。次に、図87に示したように、2つの導電型の界面近傍（発光領域）の直上に、導波路3321を配置する。導波路は、実施例4と同じように、シリコンの窒化膜で出来ており、光はこの窒化膜の内部に閉じ込められる。そのためには、窒化膜の導波路3321は、それよりも誘電率の小さなシリコン酸化膜などで覆わなければならぬが、ここでは、簡略化のために描いていない。

#### 【0119】

ここで、導波路の断面は、ほぼ半円形の形状をしている。また、発光素子や受光素子が配置される導波路の終端は、球体を1/4にしたような形状をしている。このため、発光素子から出た光は、終端で高率的に反射され、導波路を伝播する。また、一方の端も同様な1/4球の形状をしているので、導波路を伝播してきた光は、導波路端で反射されて、ほぼ垂直に受光素子に届くようになる。このような導波路の形状の効果に関しては、米国特許（U.S. 6868214B1）に詳細に開示されている。

#### 【0120】

このような形状の導波路の作製するために、シリコン半導体プロセスと整合性の高い方法を採用した。まず、導波路として、シリコンの窒化膜を用いる場合について述べる。次

10

20

30

40

50

に、シリコンの酸化膜を用いた場合を開示する。

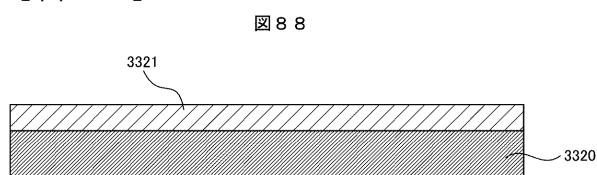

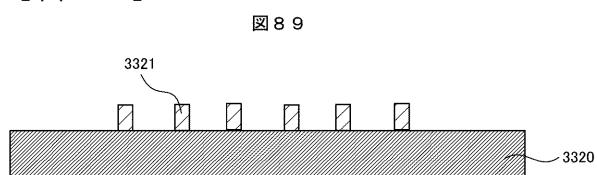

記述を簡単にするために、発光領域などを取り除いた素子断面で説明する。図88のように、層間絶縁膜3320の表面に、シリコン窒化膜3321を堆積する。次に、図89のように、窒化膜を矩形に加工する。この加工に際しては、公知のリソグラフィ法やドライエッチ法を用いる。シリコン窒化膜と層間絶縁膜であるシリコン酸化膜とには、ドライエッティングに際してエッティング速度に差があるため、窒化膜の加工を酸化膜で止めることができる。

#### 【0121】

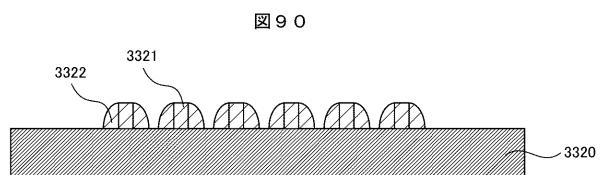

次に、矩形に加工したシリコン窒化膜の表面上、および、層間絶縁膜の表面上のどこにでも同じ厚さの膜が堆積するように、化学的気相成長法を用いて、シリコン窒化膜を堆積し、これに、公知の異方性ドライエッティングを施すと、図90に示したように、矩形に加工されたシリコン窒化膜3321の側壁にのみ、弧を描く周辺を有する側壁膜3322が形成される。この側壁膜を形成する方法では、導波路の断面形状を完全な半円形にすることは難しいが、シリコンの半導体プロセスで頻繁に使われている異方性ドライエッチ法とシリコン窒化膜を使用することができ、シリコン半導体との整合性が高い方法である。また、断面をより半円形に近づけるためには、この側壁膜を形成する工程を複数回繰り返せばよい。次の方法は、導波路にガラスのような、比較的融点の低いガラスを用いる方法である。

#### 【0122】

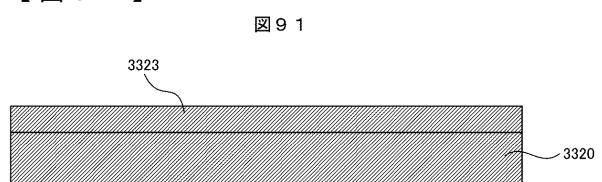

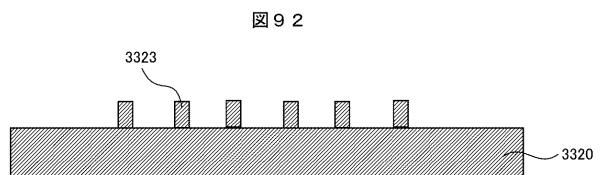

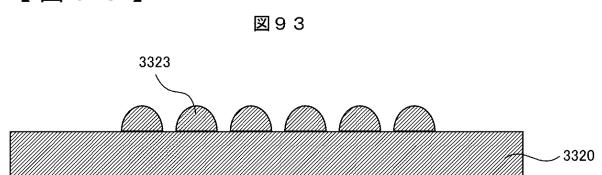

ただし、導波路としての役目を果たすためには、層間絶縁膜であるシリコン酸化膜よりも屈折率が大きく、かつ、後の配線工程での熱処理(500度)に耐える材料でなければならない。このようなガラス3323を図91に示したように、層間絶縁膜3320の表面に形成し、公知のドライエッチ法を用いて、図92に示したように矩形の導波路パターンに加工する。そして、これを600度に加熱して流動化させると、図93のよう、半円形の断面を持つ導波路が形成された。

#### 【実施例6】

#### 【0123】

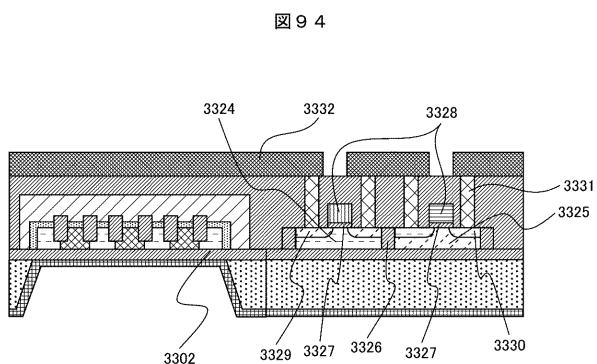

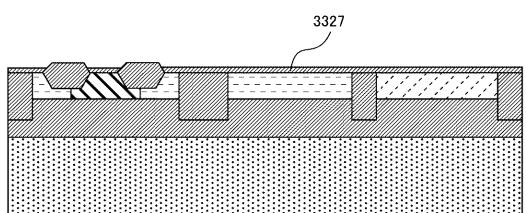

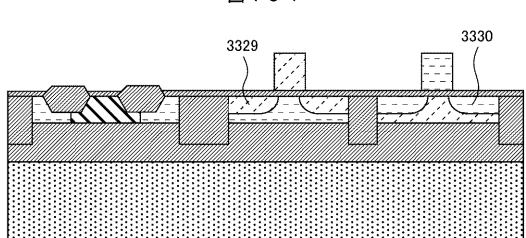

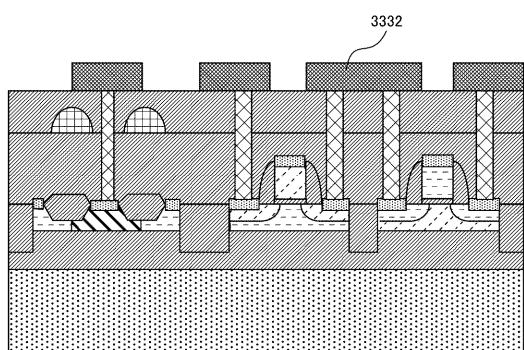

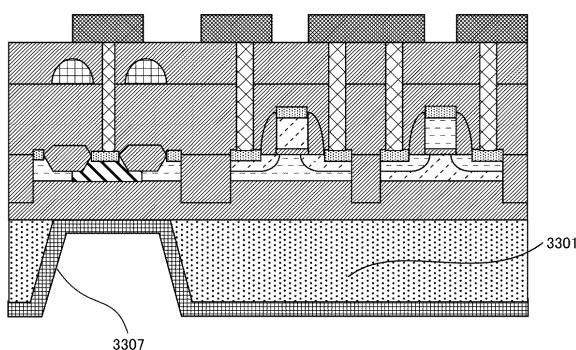

本発光素子は、シリコン薄膜を用いて容易に製造できるため、シリコンを基板とする半導体素子、例えば、MOSFET(Metal Oxide Semiconductor Field Effect Transistor)などとの混在が可能である。図94は、発光素子と半導体素子(CMOS;nMOSFETとpMOSFETから構成されるスイッチング素子)の両方を、基板上のシリコン酸化膜3302に形成した単結晶シリコン薄膜上に形成したものである。いわゆる、SOI(Silicon On Insulator)構造のMOSFETである。ここで、3324は第1導電型のシリコン薄膜、3325は第2導電型のシリコン薄膜、3326は2つのMOSFETを電気的に絶縁分離するためのシリコン酸化膜である素子分離酸化膜、3327はMOSFETのゲート酸化膜、3328はMOSFETのゲート電極、3329は第2導電型の半導体領域、3330は第1導電型の半導体領域、3331は配線と半導体素子とを電気的に接続するためのプラグと呼ばれる埋め込み金属、3332は配線の金属である。これらの半導体素子は、従来のシリコン半導体素子の製造プロセスを用いて、混在する発光素子を作りながら、製造することが可能である。

#### 【0124】

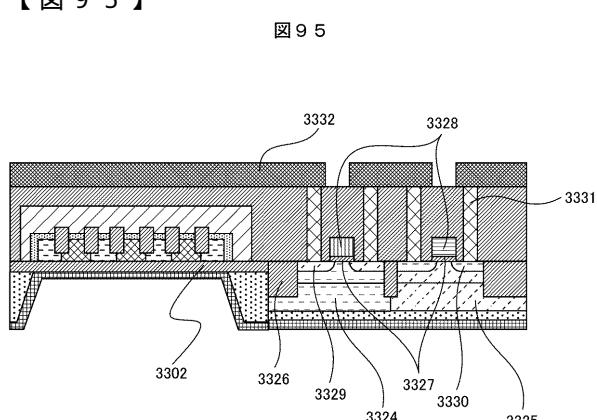

図95は、MOSFETをシリコンの基板上に作ったものである。基板上の酸化膜3302のその上に形成した単結晶シリコン膜を除去し、さらに、その下の酸化膜3302を取り除くと、シリコン基板の表面が露出する。図95に示した例では、このシリコン基板を用いてMOSFETを形成したものである。ただし、酸化膜3302の厚さが100-200nmあるために、そのままでには、発光素子を作るシリコン薄膜と、MOSFETを作る基板とには酸化膜に起因した段差が発生する。そこで、この実施例では、露出したシリコン表面にシリコンの選択的なエピタキシャル成長を施し、100-200nmの単結晶シリコン層を成長させた。その結果、段差が大幅に低減され、発光素子と半導体素子の同時作製が可能となった。

#### 【実施例7】

#### 【0125】

図96以降を用いて、発光素子とMOSFETなどの電気的な素子を同時に集積化する工程を記述する。ここでは、図96に示したように、シリコン酸化膜3302上に単結晶シリコン膜

10

20

30

40

50

3310を形成したSOI基板を用いたが、図95のように、一部を埋め込み酸化膜3302のない、シリコン基板を用いる場合も、製造工程に大きな違いは無い。

まず、図97に示したように、各素子間を電気的に絶縁分離する素子分離酸化膜3326を形成する。この工程には、公知のシリコン溝加工、シリコン酸化、シリコン酸化膜の埋め込み、研磨などのシリコン微細加工技術を用いる。図97では、発光領域が形成される領域（左の単結晶シリコン領域）と、第1導電型のMOSFETが形成される領域（中央の単結晶シリコン領域）、および、第2導電型のMOSFETが形成される領域（右の単結晶シリコン領域）を形成した場合を示した。

#### 【0126】

次に、まず、発光素子の作製を行う、図98に示したように、第1導電型の領域3304を、公知のイオン注入法で形成し、次に、この第1導電型の内部に、第2導電型の領域3303を、これも同様にイオン注入を用いて形成する。具体的には、第1導電型の領域3304には、砒素を $10^{15}/\text{cm}^2$ 程度で、また、第2導電型の領域3304には、ボロンを $10^{15}/\text{cm}^2$ 程度でイオン注入した。

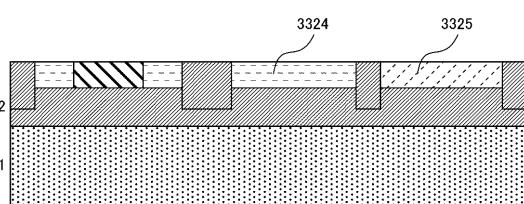

次に、図99に示したように、第1導電型MOSFETの基板となる領域3324をイオン注入で作り、さらに、第2導電型MOSFETの基板となる領域3325をイオン注入で作る。具体的には、第1導電型MOSFETの基板となる領域3324にはリンを $10^{13}/\text{cm}^2$ 程度で、また、第2導電型MOSFETの基板となる領域3325には、ボロンを $10^{13}/\text{cm}^2$ 程度で注入した。

次に、図106に示したように、発光領域となる第1、第2導電型の界面近傍のシリコン膜を薄くするために、シリコンの酸化を行う。この際、酸化した領域だけが開口したシリコン窒化膜3313を堆積する（図100）。これを、1000程度の、水蒸気を含む酸化炉に挿入して、40nm程度だけシリコン薄膜を酸化すると、約80nmの酸化膜が成長し、かつ、10nm程度の単結晶シリコン領域が残る（図101）。

#### 【0127】

次に、MOSFETの製造に入る。図102に示したように、MOSFETのゲート酸化膜3327を、公知のシリコン酸化法を用いて成長させる。膜厚は2nm程度とした。

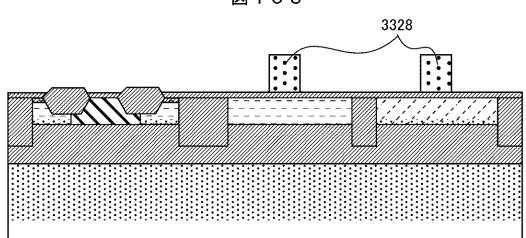

次に、MOSFETのゲート電極を形成するために、まず、基板全面に多結晶シリコンを堆積する。膜厚は250nm程度である。これを、図103に示したように、MOSFETのゲート電極形状に加工する3328。加工寸法は90nm程度である。この際、ゲート電極の加工は、2nm程度の薄いゲート酸化膜上で止まるようにしなければならない。

#### 【0128】

次に、MOSFETのソース・ドレインとなる拡散層を形成するために、それぞれのゲート電極3328をマスクとして、基板とは導電型の異なる不純物を注入する。図104の中央に示したMOSFETの場合、基板はリンを含んでいるので、拡散層にはボロンを注入する。不純物の注入量は $10^{15}/\text{cm}^2$ 程度である。一方、右のMOSFETでは、基板にはボロンが含まれているので、拡散層にはリン、もしくは、砒素を注入する。注入量はこちらも $10^{15}/\text{cm}^2$ 程度である。この際、それぞれの不純物がゲート電極にも注入されて、ゲート電極の低抵抗化、ならびに、仕事関数が決定される。

#### 【0129】

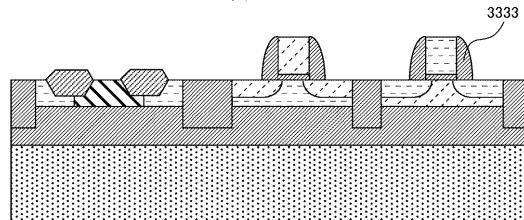

次に、拡散層やゲート電極、さらには、発光素子において、酸化膜で覆われていない領域をシリサイド化する前段階として、図105に示したように、ゲート電極の側壁にのみ、側壁絶縁膜を形成する。このためには、まず、基板全面に公知の化学的気相成長法を用いてシリコン酸化膜もしくはシリコン窒化膜を堆積し、これに、公知の異方性ドライエッティングを施すと、図105に示したように、矩形のゲート電極の側壁にのみ、側壁絶縁膜3333が残る。

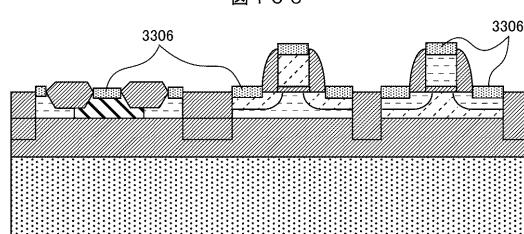

#### 【0130】

側壁絶縁膜の形成工程で露出したシリコン表面を洗浄した後、金属を20-30nm程度堆積する。堆積した金属は、チタン、コバルト、ニッケルなどである。そして、450程度の熱処理を施すと、シリコンと金属の反応が進行し、金属の珪化物（シリサイド）3306が形成される。このシリサイドは、シリコンが露出した部分にのみ形成されるので、側壁絶縁

10

20

30

40

50

膜3333で覆われたゲート電極の側壁や、発光素子において発光部領域を覆うシリコンの酸化膜上には形成されない。これらの部分は、金属のままである。この未反応の金属部分は、過酸化水素を含む溶液で除去するために、最終的には、図106に示したように、シリコンと接する部分にのみ、シリサイドが形成される。ただし、このままではシリサイドの抵抗が高いので、これに、750°C程度の熱処理を施し、低抵抗化する。これによって、抵抗の高かったゲート電極や拡散層が低抵抗化され、MOSFETや発光素子の低電圧動作が可能となる。

### 【0131】

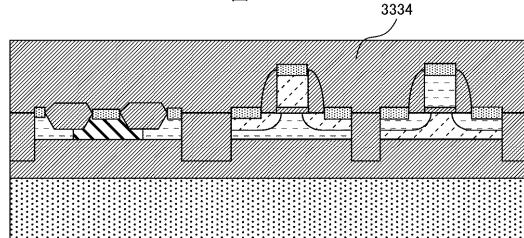

次に、図107に示したように、発光素子とMOSFETを覆うように、層間絶縁膜3334を堆積し、これを、研磨することで平坦化する。

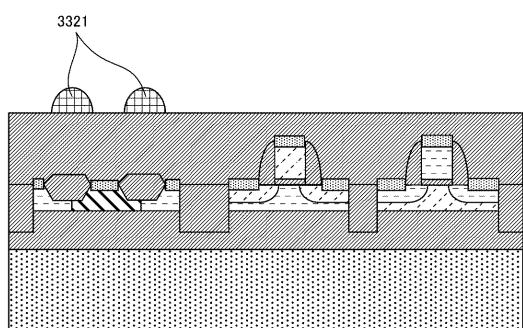

次に、図108に示したように、発光領域の上部に、光の導波路3321を、既に述べたような方法で作製する、そして、その導波路を、より屈折率の小さな絶縁膜で覆い、平坦化した後に、図109に示したように、配線とMOSFETの拡散層やゲート電極、さらには、発光素子のシリコン領域とを接続するための、金属プラグを形成する。金属プラグの形成は、まず、層間膜にコンタクト穴を開口し、これを金属で埋め戻し、さらに、層間絶縁膜の表面に付いた金属膜を研磨で削り落とすという方法で形成できる。

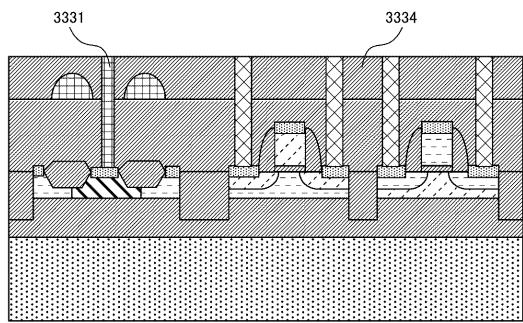

次に、図110に示したように、配線をアルミニュームなどを用いて行い、図111のように、発光部の支持基板に開口部を設けて、光の反射板となる金属を形成して、本光電子集積回路の製造が完了する。

### 【図面の簡単な説明】

#### 【0132】

【図1A】発光素子の原理の説明をするためのシリコンのバルク状態でのバンド構造。

【図1B】発光素子の原理の説明をするためのシリコンの薄膜状態またはゲート電界印加状態でのバンド構造。

【図2】発光素子の原理を実証する実験データ。極薄シリコン層からの発光強度。

【図3】発光素子の原理を実証する実験データ。極薄シリコン層からの発光波長。

【図4A】発光素子の原理にもとづく発光波長の極薄シリコン層膜厚依存性。

【図4B】発光素子の原理にもとづく発光波長・強度の極薄シリコン層膜厚依存性。

【図5A】発光原理を検証する発光ダイオード製造工程順を示す断面図。

【図5B】発光原理を検証する発光ダイオード製造工程順を示す断面図。

【図5C】発光原理を検証する発光ダイオード製造工程順を示す断面図。

【図5D】発光原理を検証する発光ダイオード製造工程順を示す断面図。

【図5E】発光原理を検証する発光ダイオード製造工程順を示す断面図。

【図5F】発光原理を検証する発光ダイオード製造工程順を示す断面図。

【図5G】発光原理を検証する発光ダイオード製造工程順を示す断面図。

【図5H】発光原理を検証する発光ダイオード製造工程順を示す断面図。

【図6A】発光原理を検証する発光ダイオード製造工程順を示す上部からみた図。

【図6B】発光原理を検証する発光ダイオード製造工程順を示す上部からみた図。

【図6C】発光原理を検証する発光ダイオード製造工程順を示す上部からみた図。

【図6D】発光原理を検証する発光ダイオード製造工程順を示す上部からみた図。

【図6E】発光原理を検証する発光ダイオード製造工程順を示す上部からみた図。

【図6F】発光原理を検証する発光ダイオード製造工程順を示す上部からみた図。

【図6G】発光原理を検証する発光ダイオード製造工程順を示す上部からみた図。

【図6H】発光原理を検証する発光ダイオード製造工程順を示す上部からみた図。

【図7】発光原理を検証する発光ダイオードの断面図。

【図8】発光原理を検証する発光ダイオードの発光検証実験の説明図。

【図9A】発光原理を検証する発光ダイオードの発光写真。

【図9B】本発光原理を検証する発光ダイオードの発光写真。

【図9C】発光原理を検証する発光ダイオードの発光写真。

【図9D】発光原理を検証する発光ダイオードの発光写真。

10

20

30

40

50

- 【図 9 E】発光原理を検証する発光ダイオードの発光写真。

- 【図 9 F】発光原理を検証する発光ダイオードの発光写真。

- 【図 10 A】発光原理を検証する発光ダイオードの発光写真。

- 【図 10 B】発光原理を検証する発光ダイオードの発光写真。

- 【図 10 C】発光原理を検証する発光ダイオードの発光写真。

- 【図 10 D】発光原理を検証する発光ダイオードの発光写真。

- 【図 10 E】発光原理を検証する発光ダイオードの発光写真。

- 【図 10 F】発光原理を検証する発光ダイオードの発光写真。

- 【図 11】本発明による実施例 1 の集積発光素子を説明する平面レイアウト。 10

- 【図 12】本発明による実施例 1 の受光素子を説明する平面レイアウト。

- 【図 13】本発明による実施例 1 の集積発光素子の製造工程を説明する素子断面構造図。

- 【図 14】本発明による実施例 1 の集積発光素子の製造工程を説明する素子断面構造図。

- 【図 15】本発明による実施例 1 の集積発光素子の製造工程を説明する素子断面構造図。

- 【図 16】本発明による実施例 1 の集積発光素子の製造工程を説明する素子断面構造図。

- 【図 17】本発明による実施例 1 の集積発光素子の製造工程を説明する素子断面構造図。

- 【図 18】本発明による実施例 1 の集積発光素子の製造工程を説明する素子断面構造図。

- 【図 19】本発明による実施例 1 の集積発光素子のその他の製造工程を説明する素子断面構造図。

- 【図 20】本発明による実施例 1 の集積発光素子のその他の製造工程を説明する素子断面構造図。 20

- 【図 21】本発明による実施例 1 の集積発光素子のその他の製造工程を説明する素子断面構造図。

- 【図 22】本発明による実施例 1 の集積発光素子のその他の製造工程を説明する素子断面構造図。

- 【図 23】本発明による実施例 1 の受光素子の製造工程を説明する素子断面構造図。

- 【図 24】本発明による実施例 1 の受光素子の製造工程を説明する素子断面構造図。

- 【図 25】本発明による実施例 1 の受光素子の製造工程を説明する素子断面構造図。

- 【図 26】本発明による実施例 1 の受光素子の製造工程を説明する素子断面構造図。

- 【図 27】本発明による実施例 1 の受光素子の製造工程を説明する素子断面構造図。

- 【図 28】本発明による実施例 1 の導波路の製造工程を説明する断面構造図。 30

- 【図 29】本発明による実施例 1 の導波路の製造工程を説明する断面構造図。

- 【図 30】本発明による実施例 1 の導波路のその他の製造工程を説明する平面レイアウト図。

- 【図 31】本発明による実施例 1 の導波路のその他の製造工程を説明する断面構造図。

- 【図 32】本発明による実施例 1 の導波路のその他の製造工程を説明する断面構造図。

- 【図 33】本発明による実施例 1 の導波路のその他の製造工程を説明する断面構造図。

- 【図 34】本発明による実施例 1 の導波路のその他の製造工程を説明する断面構造図。

- 【図 35】本発明による実施例 1 の導波路のその他の製造工程を説明する断面構造図。

- 【図 36】本発明による実施例 1 の導波路のその他の製造工程を説明する断面構造図。

- 【図 37】本発明による実施例 1 の集積発光素子、導波路および受光素子と従来多層配線の集積を説明する断面構造図。 40

- 【図 38】本発明による実施例 1 の集積発光素子、導波路および受光素子と従来多層配線の集積を説明する断面構造図。

- 【図 39】本発明による実施例 1 の集積発光素子、導波路および受光素子と従来多層配線を集積する製造工程を説明する断面構造図。

- 【図 40】本発明による実施例 1 の集積発光素子、導波路および受光素子と従来多層配線を集積する製造工程を説明する断面構造図。

- 【図 41】本発明による実施例 1 の集積発光素子、導波路および受光素子と従来多層配線を集積する製造工程を説明する断面構造図。

- 【図 42】本発明による実施例 1 の集積発光素子、導波路および受光素子と従来多層配線 50

【図109】本発明による実施例7の集積発光素子、導波路とCMOSとの集積構造の製造工程を説明する断面構造

【図110】本発明による実施例7の集積発光素子、導波路とCMOSとの集積構造の製造工程を説明する断面構造図。

【図111】本発明による実施例7の集積発光素子、導波路とCMOSとの集積構造の製造工程を説明する断面構造図。

【符号の説明】

【0133】

- 1...シリコン基板、

- 2...埋め込み酸化膜(BOX)、

- 3...Silicon On Insulator (SOI)層、

- 4...酸化シリコン膜、

- 5...P型不純物注入領域、

- 6...N型不純物注入領域、

- 7...シリコン窒化膜、

- 8...二酸化シリコン膜、

- 9...p型SOI領域、

- 10...n型SOI領域、

- 11...p型極薄シリコン領域、

- 12...n型極薄シリコン領域、

- 13...断面、

- 14...断面、

- 15...探針、

- 16...探針、

- 17...発光、

- 18...ノンドープ・シリコン・パッド、

- 19...ノンドープ・シリコン・パッド、

- 20...ノンドープ・シリコン・パッド、

- 21...ノンドープ・シリコン・パッド、

- 22...極薄ノンドープ・シリコン、

- 23...探針、

- 24...探針、

- 1150, 1152, 1160, 1550, 1560, 1650, 1651, 1750, 1850, 1855, 1860、...マスクパターン、

- 1155...活性領域、

- 1100, 1103, 1120...単結晶シリコン、

- 1121...シリコンゲルマニウム結晶、

- 1200, 1300, 1210, 1310...不純物拡散層、

- 1400...集積発光素子、

- 1410...受光素子、

- 1500, 1510...導波路、

- 1201, 1202, 1203, 1204, 1205, 1206, 1240...シリコン、

- 1600、1601、1602...金属層、

- 1555、1800...ホトレジスト、

- 1900, 1905, 1910, 1920, 1930, 1931, 1932, 1960, 1962...シリコン酸化膜、

- 1961, 1963, 1981, 1982, 1983, 1985, 1986...シリコン窒化膜、

- 1970, 1971...H R膜、

- 1990...A R膜、

- 3301, 3310...単結晶シリコン、

- 3302, 3305, 3326, 3327...シリコン酸化膜、

- 3303, 3304, 3329, 3330...半導体領域、

10

20

30

40

50

3306...シリサイド、

3307, 3331, 3332...金属層、

3311, 3312...フォトレジストパターン、

3313、3317...シリコン窒化膜、

3318...発光素子、

3319...受光素子、

3320, 3334...層間絶縁膜、

3321...導波路、

3322...側壁膜、

3323...ガラス、

3324, 3325...シリコン薄膜、

3328...ゲート電極、

3333...側壁絶縁膜。

10

【図1 A】

図1 A

【図1 B】

図1 B

【図2】

図2

【図3】

図3

【図4 A】

図4 A

【図5 C】

図5 C

【図5 D】

図5 D

【図5 E】

図5 E

【図4 B】

図4 B

【図5 A】

図5 A

【図5 B】

図5 B

【図5 F】

図5 F

【図5 G】

図5 G

【図 5 H】

図 5 H

【図 6 A】

図 6 A

【図 6 B】

図 6 B

【図 6 G】

図 6 G

【図 6 H】

図 6 H

【図 6 C】

図 6 C

【図 6 D】

図 6 D

【図 6 E】

図 6 E

【図 6 F】

図 6 F

【図 7】

図 7

【 四 8 】

图 8

【 図 9 A 】

図 9 A

【図9B】

9 B

【図9C】

9 C

【図 9 D】

図 9 D

【図 9 E】

図 9 E

【図 9 F】

図 9 F

【図 10 A】

図 10 A

【図 10 B】

図 10 B

【図 10 C】

図 10 C

【図 10 D】

図 10 D

【図 10 E】

図 10 E

【図 10 F】

図 10 F

【図 11】

図 11

【図 14】

図 14

【図 12】

図 12

【図 13】

図 13

【図 15】

図 15

【図 16】

図 16

【図 17】

【図 17】

【図 17】

図 17

【図18】

図18

【図19】

図19

【図20】

図20

【図21】

図21

【図22】

図22

【図24】

図24

【図25】

図25

【図26】

図26

【図27】

図27

【図28】

図28

【図29】

図29

【図30】

図30

【図31】

図31

【図32】

図32

【図34】

図34

【図33】

図33

【図35】

図35

【図36】

図36

【図37】

図37

【図39】

図39

【図40】

図40

【図38】

図38

【図41】

図41

【図42】

図42

【図43】

図43

【図44】

図44

【図45】

図45

【図46】

図46

【図47】

【図48】

【図49】

【図50】

【図51】

【図52】

【図53】

【図54】

【図 5 5】

【図 5 6】

【図 5 7】

【図 5 8】

【図 5 9】

【図 6 0】

【図 6 1】

【図 6 2】

【図63】

図63

【図64】

図64

【図65】

図65

【図66】

図66

【図67】

図67

【図 6 8】

図 6 8

【図 6 9】

図 6 9

【図 7 0】

図 7 0

【図 7 1】

図 7 1

【図 7 2】

図 7 2

【図 7 3】

図 7 3

【図 7 4】

図 7 4

【図 7 5】

【図 7 8】

【図 7 6】

【図 7 9】

【図 7 7】

【図 8 0】

【図 8 1】

【図 8 3】

【図 8 2】

【図 8 4】

【図 8 5】

【図 8 6】

【図 8 7】

【図 8 8】

【図 8 9】

【図 9 0】

【図 9 1】

【図 9 2】

【図 9 3】

【図 9 4】

【図 9 5】

【図 9 6】

図 9 6

【図 9 9】

図 9 9

【図 9 7】

図 9 7

【図 1 0 0】

図 1 0 0

【図 9 8】

図 9 8

【図 1 0 1】

図 1 0 1

【図 1 0 2】

図 1 0 2

【図 1 0 5】

図 1 0 5

【図 1 0 3】

図 1 0 3

【図 1 0 6】

図 1 0 6

【図 1 0 4】

図 1 0 4

【図 1 0 7】

図 1 0 7

【図 108】

図 108

【図 109】

図 109

【図 110】

図 110

【図 111】

図 111

---

フロントページの続き

審査官 高棕 健司

(56)参考文献 特開平08-046237 (JP, A)

国際公開第02/097894 (WO, A1)

(58)調査した分野(Int.Cl., DB名)

H01L 33/00 - 33/64

H01S 5/00 - 5/50