(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-133754

(P2006-133754A)

(43) 公開日 平成18年5月25日(2006.5.25)

| (51) Int.C1.                 | F 1       | テーマコード (参考)    |

|------------------------------|-----------|----------------|

| <b>G09G 3/36</b> (2006.01)   | G09G 3/36 | 2 H093         |

| <b>G09G 3/34</b> (2006.01)   | G09G 3/34 | J 5 C006       |

| <b>G09G 3/20</b> (2006.01)   | G09G 3/20 | 6 4 1 E 5 C080 |

| <b>H01L 29/786</b> (2006.01) | G09G 3/20 | 6 2 2 R 5 F110 |

| <b>G02F 1/133</b> (2006.01)  | G09G 3/20 | 6 2 4 B        |

審査請求 未請求 請求項の数 15 O L (全 30 頁) 最終頁に続く

|              |                              |            |                                                                                                                                                    |

|--------------|------------------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| (21) 出願番号    | 特願2005-291349 (P2005-291349) | (71) 出願人   | 000153878                                                                                                                                          |

| (22) 出願日     | 平成17年10月4日 (2005.10.4)       |            | 株式会社半導体エネルギー研究所                                                                                                                                    |

| (31) 優先権主張番号 | 特願2004-292010 (P2004-292010) |            | 神奈川県厚木市長谷398番地                                                                                                                                     |

| (32) 優先日     | 平成16年10月4日 (2004.10.4)       | (72) 発明者   | 小山 潤                                                                                                                                               |

| (33) 優先権主張国  | 日本国 (JP)                     |            | 神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内                                                                                                                    |

|              |                              | (72) 発明者   | 山崎 舜平                                                                                                                                              |

|              |                              |            | 神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内                                                                                                                    |

|              |                              | F ターム (参考) | 2H093 NA41 NA65 NC13 NC22 NC23<br>NC34 NC35 ND57 NE03 NE04<br>NE10<br>5C006 AA14 AA22 AB01 AC11 AC24<br>BA19 BB16 BC03 BC06 BC12<br>BF02 FA03 FA04 |

|              |                              |            | 最終頁に続く                                                                                                                                             |

(54) 【発明の名称】表示装置及びその駆動方法

## (57) 【要約】

【課題】 画面の縦横表示の切替が可能な表示装置を提供する。

【解決手段】 第1のゲート信号線駆動回路の走査方向は、ソース信号線駆動回路の走査方向と垂直をなし、第2のゲート信号線駆動回路の走査方向は、第1のゲート信号線駆動回路の走査方向と垂直をなす。通常表示の際は、画面の垂直走査は第1のゲート信号線駆動回路によって行う。一方、縦横表示を切り替える際には、画面の垂直走査は第2のゲート信号線駆動回路によって行う。画素はフィールドシーケンシャルで駆動され、画素内がRGBに分割されないため、縦横切換が容易になる。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

周期的に発光色が変化する発光源と、ソース信号線駆動回路と、第1のゲート信号線駆動回路と、第2のゲート信号線駆動回路と、複数の画素とを有し、

前記第1のゲート信号線駆動回路の走査方向と、前記第2のゲート信号線駆動回路の走査方向とが直交することを特徴とする第1の表示及び第2の表示が可能な表示装置。

**【請求項 2】**

周期的に発光色が変化する発光源と、ソース信号線駆動回路と、第1のゲート信号線駆動回路と、第2のゲート信号線駆動回路と、複数の画素とを有し、

前記複数の画素は、ソース信号線と、第1のゲート信号線と、前記第1のゲート信号線に直交する第2のゲート信号線と、第1のトランジスタと、第2のトランジスタとを有し

、前記第1のトランジスタのゲート電極は、前記第1のゲート信号線と電気的に接続され、前記第1のトランジスタの入力電極は、前記ソース信号線と電気的に接続され、前記第1のトランジスタの出力電極は、前記第2のトランジスタの入力電極と電気的に接続され

、前記第2のトランジスタのゲート電極は、前記第2のゲート信号線と電気的に接続されていることを特徴とする第1の表示及び第2の表示が可能な表示装置。

**【請求項 3】**

請求項1又は請求項2において、

第1の表示を行う際には、前記ソース信号線駆動回路の駆動周波数は、第1のゲート信号線駆動回路の駆動周波数よりも高く、

第2の表示を行う際には、前記ソース信号線駆動回路の駆動周波数は、第1のゲート信号線駆動回路の駆動周波数よりも低いことを特徴とする第1の表示及び第2の表示が可能な表示装置。

**【請求項 4】**

請求項1乃至請求項3のいずれか1項において、

前記ソース信号線駆動回路、前記第1のゲート信号線駆動回路、前記第2のゲート信号線駆動回路の少なくとも1つと、前記複数の画素は同一基板上に形成されていることを特徴とする第1の表示及び第2の表示が可能な表示装置。

**【請求項 5】**

周期的に発光色が変化する発光源と、第1のソース信号線駆動回路と、第2のソース信号線駆動回路と、第1のゲート信号線駆動回路と、第2のゲート信号線駆動回路と、複数の画素とを有し、

前記第1のゲート信号線駆動回路の走査方向と、前記第2のゲート信号線駆動回路の走査方向とが直交することを特徴とする第1の表示及び第2の表示が可能な表示装置。

**【請求項 6】**

周期的に発光色が変化する発光源と、第1のソース信号線駆動回路と、第2のソース信号線駆動回路と、第1のゲート信号線駆動回路と、第2のゲート信号線駆動回路と、複数の画素とを有し、

前記複数の画素は、第1のソース信号線と、第2のソース信号線と、第1のゲート信号線と、前記第1のゲート信号線に直交する第2のゲート信号線と、第1のトランジスタと、第2のトランジスタとを有し、

前記第1のトランジスタのゲート電極は、前記第1のゲート信号線と電気的に接続され、前記第1のトランジスタの入力電極は前記第1のソース信号線と電気的に接続され、

前記第2のトランジスタのゲート電極は、前記第2のゲート信号線と電気的に接続され、前記第2のトランジスタの入力電極は前記第2のソース信号線と電気的に接続されていることを特徴とする第1の表示及び第2の表示が可能な表示装置。

**【請求項 7】**

請求項5又は請求項6において、

10

20

30

40

50

前記第1のソース信号線駆動回路、前記第2のソース信号線駆動回路、前記第1のゲート信号線駆動回路、前記第2のゲート信号線駆動回路の少なくとも1つと、前記複数の画素は同一基板上に形成されていることを特徴とする第1の表示及び第2の表示が可能な表示装置。

**【請求項8】**

請求項1乃至請求項7のいずれか1項において、

第1の表示を行う際には、映像の上下は前記第1のゲート信号線駆動回路の走査方向に従った向きで表示され、

第2の表示を行う際には、映像の上下は前記第2のゲート信号線駆動回路の走査方向に従った向きで表示されることを特徴とする第1の表示及び第2の表示が可能な表示装置。 10

**【請求項9】**

請求項1乃至請求項8のいずれか1項において、

前記複数の画素はそれぞれ、液晶素子を有することを特徴とする第1の表示及び第2の表示が可能な表示装置。

**【請求項10】**

請求項1乃至請求項9のいずれか1項に記載の表示装置を用いることを特徴とする電子機器。

**【請求項11】**

ソース信号線駆動回路と、第1のゲート信号線駆動回路と、第2のゲート信号線駆動回路と、複数の画素とを有し、 20

前記第1のゲート信号線駆動回路の走査方向と、前記第2のゲート信号線駆動回路の走査方向とが直交し、

前記複数の画素はフィールドシーケンシャル駆動されることを特徴とする第1の表示及び第2の表示が可能な表示装置の駆動方法。

**【請求項12】**

請求項11において、

第1の表示を行う際には、前記ソース信号線駆動回路の駆動周波数は、第1のゲート信号線駆動回路の駆動周波数よりも高く、

第2の表示を行う際には、前記ソース信号線駆動回路の駆動周波数は、第1のゲート信号線駆動回路の駆動周波数よりも低いことを特徴とする第1の表示及び第2の表示が可能な表示装置の駆動方法。 30

**【請求項13】**

第1のソース信号線駆動回路と、第2のソース信号線駆動回路と、第1のゲート信号線駆動回路と、第2のゲート信号線駆動回路と、複数の画素とを有し、

前記第1のゲート信号線駆動回路の走査方向と、前記第2のゲート信号線駆動回路の走査方向とが直交し、

前記複数の画素はフィールドシーケンシャル駆動されることを特徴とする第1の表示及び第2の表示が可能な表示装置の駆動方法。

**【請求項14】**

請求項11乃至請求項13のいずれか1項において、 40

第1の表示を行う際には、映像の上下は前記第1のゲート信号線駆動回路の走査方向に従った向きで表示され、

第2の表示を行う際には、映像の上下は前記第2のゲート信号線駆動回路の走査方向に従った向きで表示されることを特徴とする第1の表示及び第2の表示が可能な表示装置の駆動方法。

**【請求項15】**

請求項11乃至請求項14のいずれか1項に記載の表示装置の駆動方法を用いることを特徴とする電子機器。

10

20

30

40

50

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、液晶素子を用いて画素部を構成した表示装置及びその駆動方法、そのような表示装置を表示部に用いた電子機器に関する。特に、フィールドシーケンシャル駆動を用いた表示装置および、そのような表示装置を表示部に用いた電子機器に関する。

## 【背景技術】

## 【0002】

近年、ガラス基板等の絶縁体上に半導体薄膜を形成した表示装置、特に薄膜トランジスタ（以下、TFTと表記）を用いた電子回路が各分野で使用されている。特に、表示装置において使用されることが多く、LCD（液晶ディスプレイ）を始めとするアクティブマトリクス型表示装置は、多くの製品に利用され、普及している。TFTを使用したアクティブマトリクス型表示装置は、マトリクス状に配置された数十万から数百万の画素を有し、各画素に配置されたTFTによって各画素の電荷を制御することによって映像の表示を行っている。

## 【0003】

さらに最近の技術として、画素を構成する画素TFTの他に、画素部の周辺領域にTFTを用いて駆動回路を基板上に同時形成するポリシリコンTFTに関する技術が発展してきており、装置の小型化、低消費電力化に大いに貢献し、それに伴って、近年その応用分野の拡大が著しいモバイル情報端末の表示部等に、表示装置は不可欠なデバイスとなってきた。

## 【0004】

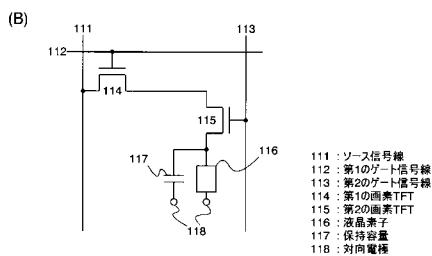

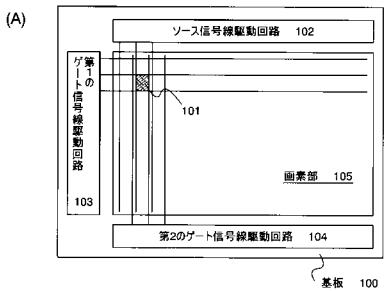

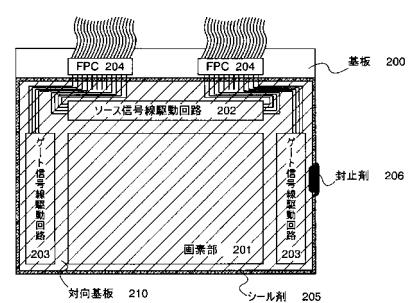

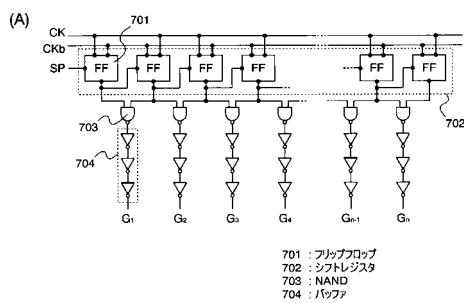

一般的な表示装置の例を図2(A)に示す。図2(A)は、絶縁体上に画素部と駆動回路とが一体形成された液晶表示装置の例である。基板200上の中央部に、画素部201が配置され、画素部201の周辺には、ソース信号線駆動回路202、ゲート信号線駆動回路203等が形成されている。なお、図2(A)においては、ゲート信号線駆動回路203は画素部201の左右両側に対称配置されているが、これは片側のみの配置であっても良い。ただし、回路の動作の信頼性や効率等を考えると、図2(A)のように対称配置とするのが好ましい。

## 【0005】

ソース信号線駆動回路202およびゲート信号線駆動回路203に入力される信号は、外部より、フレキシブルプリント基板(Flexible Print Circuit: FPC)204を介して供給される。

## 【0006】

対向基板210には、対向電極等が形成され、シール材205を介して、ある空隙をもって基板200と貼り合わされる。その後、あらかじめ用意してある注入口より、基板200と対向基板210との空隙に液晶材料を注入し、注入口は封止材206によって密閉される。

## 【0007】

画素部201は、図2(B)に示すように、m本のソース信号線とn本のゲート信号線とが直交配置されている。ソース信号線とゲート信号線の交点にあたる場所(220)に、図2(C)に示すような画素が形成されている。ソース信号線221、ゲート信号線222、画素TFT223、液晶素子224、保持容量225、対向電極226からなる。ここでは、画素数はm×n画素である。

## 【0008】

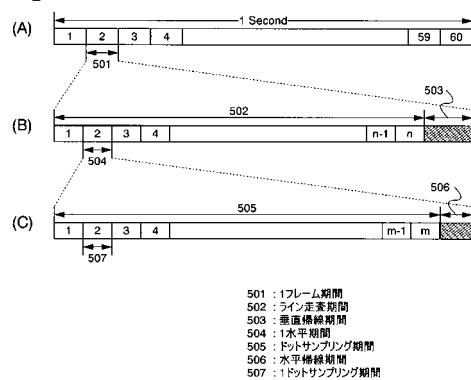

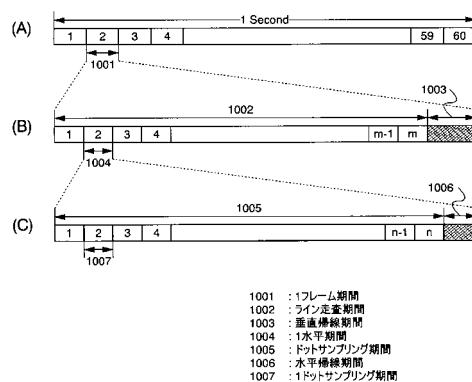

図5を参照し、表示装置の動作について簡単に説明する。一般に、画面のちらつき(フリッカと呼ばれる)が人間の眼に認識されないためには、1秒間に60回程度、画面の描画が行われる。ここで、501で示される期間、すなわち画面を1回描画するのに要する期間を、1フレーム期間と呼ぶ(図5(A))。

## 【0009】

10

20

30

40

50

1 フレーム期間においては、1行目から順にゲート信号線の選択が行われる。1行あたりの選択期間 504 を1水平期間と表記する。最終行( n 行目)の選択が終了するまでの期間 502 を、ライン走査期間と表記する。その後、垂直帰線期間 503 を挟んで、次のフレーム期間で同様の操作が行われる(図 5 (B) )。

【0010】

1 水平期間においては、選択されている行の画素に、ソース信号線より順に映像信号の書き込みが行われる。この期間 505 を、ドットサンプリング期間と表記する。1つの画素に映像信号を書き込むのに要する期間 507 を、1ドットサンプリング期間と表記する。1行分の画素において映像信号の書き込みが完了すると、水平帰線期間 506 を挟んで、次の水平期間で同様の操作が行われる(図 5 (C) )。

10

【0011】

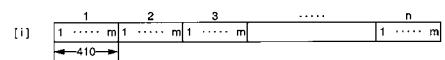

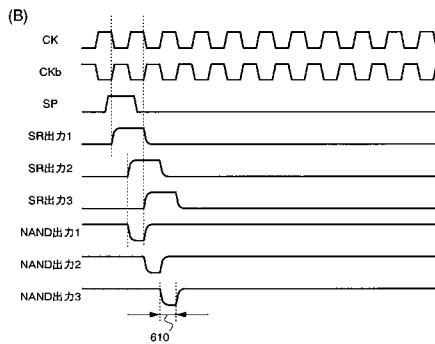

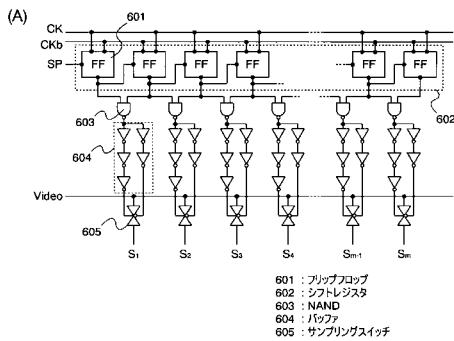

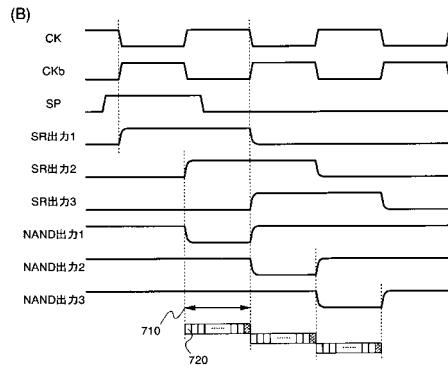

次に、回路の具体的な動作について説明する。図 6 (A) は、表示装置のソース信号線駆動回路の一構成例であり、フリップフロップ回路 601 (FF) を複数段用いてなるシフトレジスタ 602、NAND 603、バッファ 604、サンプリングスイッチ 605 を有している。

【0012】

動作の説明に際し、図 6 (B) を参照する。シフトレジスタ 602 は、クロック信号(CK)、クロック反転信号(CKb)およびスタートパルス(SP)にしたがって、それぞれ1段目から順次パルスを出力する。

20

【0013】

シフトレジスタ 602 から出力されたパルスが隣接段で重なりを持つ場合は、NAND 603 に入力されて、隣接段で重なりを持たないパルスとされる。その後、NAND 出力はバッファ 604 を通り、サンプリングパルスとなる。

【0014】

サンプリングパルスがサンプリングスイッチ 605 に入力されると、サンプリングスイッチ 605 が ON し、その間、映像信号(Video)の電位が、サンプリングスイッチに接続されているソース信号線に充電される。同時に、ゲート信号線が選択されている行の、前述のソース信号線に接続されている一画素に書き込まれる。図 6 (B) において、610 で示される期間が、1ドットサンプリング期間である。

30

【0015】

続いて、図 7 (A) に示すゲート信号線駆動回路について説明する。シフトレジスタ～バッファ間は、ソース信号線駆動回路とほぼ同様であり、フリップフロップ 701 を複数段用いてなるシフトレジスタ 702、NAND 703、バッファ 704 を有する。

【0016】

動作の説明に際し、図 7 (B) を参照する。シフトレジスタ 702 は、ソース信号線駆動回路と同様に、クロック信号(CK)、クロック反転信号(CKb)およびスタートパルス(SP)にしたがって、それぞれ1段目から順次パルスを出力する。

【0017】

シフトレジスタ 702 から出力されたパルスが隣接段で重なりを持つ場合は、NAND 703 に入力されて、隣接段で重なりを持たないパルスとされる。その後、NAND 出力はバッファ 704 を通り、ゲート信号線選択パルスとなる。

40

【0018】

ゲート信号線選択パルスが入力されている行においては、前述のようにソース信号線に書き込まれる映像信号が、それぞれの画素に書き込まれる。図 7 (B) において、710 で示される期間が、1水平期間であり、720 で示される期間が、前述の1ドットサンプリング期間である。

【0019】

ところで、表示装置は、装置に設置された方向に固定されて使用される場合が一般的であるが、パーソナルコンピュータ等のように、その用途が多機能化している場合、ある用途においては横長なレイアウトで、またある用途においては縦長なレイアウトで表示装置

50

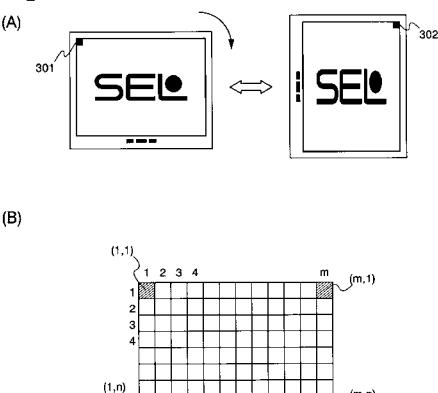

を用いたい場合がある。このような場合、図3(A)に示すように、表示装置の筐体を90°回転させた状態で表示させる方法がある。

【 0 0 2 0 】

この場合の表示装置を駆動するタイミングは図 10 で示される。ここで、1001で示される期間を1フレーム期間と呼ぶ。1フレーム期間においては、1行目から順にゲート信号線の選択が行われる。1行あたりの選択期間1004を1水平期間と表記する。最終行(m行目)の選択が終了するまでの期間1002を、ライン走査期間と表記する。その後、垂直帰線期間1003を挟んで、次のフレーム期間で同様の操作が行われる。1水平期間においては、選択されている行の画素に、ソース信号線より順に映像信号の書き込みが行われる。この期間1005を、ドットサンプリング期間と表記する。1つの画素に映像信号を書き込むのに要する期間1007を、1ドットサンプリング期間と表記する。1行分の画素において映像信号の書き込みが完了すると、水平帰線期間1006を挟んで、次の水平期間で同様の操作が行われる。

【 0 0 2 1 】

また、最近の携帯電話ではテレビ放送受信機能を備えたものもあり、テレビ映像を表示する時には横長に設定し、文字情報を表示する時には縦長に設定できることが望ましい。

【 0 0 2 2 】

アクティブマトリクス型表示装置の画素部は、図2(B)に示すように、 $m \times n$  個の画素がマトリクス状に整列しており、映像信号の書き込みは、座標(1, 1)の画素から順に、(1, 2)、(1, 3)、(1, 4)と行われ、(1, m)に達したところで1水平周期が完了する。これをn回繰り返し、最終的に座標(m, n)の画素への書き込みが完了すると、1画面の書き込みが完了する。

【 0 0 2 3 】

再び、図3(A)に戻る。横長表示(左)と縦長表示(右)の場合、最初に書き込みが行われる座標(1, 1)の画素は、それぞれ301、302で示される。図3(A)に示すように、横長表示と縦長表示において、同様の画面の表示を行う場合を考えると、映像信号の入力が横長表示に対応したものであるとき、その入力の順序は、左上 右上 ... . 右下の順であるが、この映像信号を用いて縦長表示を行う場合、表示装置自体の書き込みの順序は変わらないため、映像信号の入力の順序を、右上 右下 ... 左下の順としなければならない。

( 0 0 2 4 )

しかし、表示装置の縦横表示の切り替えは、フレキシブルに行えることが好ましいため、その都度異なるフォーマットの映像信号を用意するのは効率的ではない。そこで、フレームメモリを用いて、映像信号を一旦メモリに記憶して読み出しを行うことによって表示を行う。

〔 0 0 2 5 〕

フレームメモリは、各画素の映像信号を各メモリセルごとに記憶しているため、書き込みの順序に関係なく、任意のアドレスからの読み出しが可能である。フレームメモリに一旦書き込まれた映像信号の読み出しの順序を変えることによって、前述の縦横表示の切り替えを行うことが出来る。

〔 0 0 2 6 〕

1 フレーム分の映像信号を記憶するフレームメモリは、図 3 ( B ) に示すようにそれぞれの記憶回路がアドレスで管理される。よって、映像信号が入力されると、( 1 , 1 ) ( 2 , 1 ) . . . ( m , 1 ) 、 ( 1 , 2 ) ( 2 , 2 ) . . . ( m , 2 ) 、 . . . 、 ( 1 , n ) ( 2 , n ) . . . ( m , n ) の順に書き込まれ、横長表示の場合は書き込まれた順序と同じ順序で読み出される。

〔 0 0 2 7 〕

一方、縦長表示の場合、図3(A)のように表示したい場合には、(m, 1) (m, 2) ··· (m, n)、(m-1, 1) (m-2, 2) ··· (m-1, n)、···、(1, 1) (1, 2) ··· (1, n)の順に読み出される。

## 【0028】

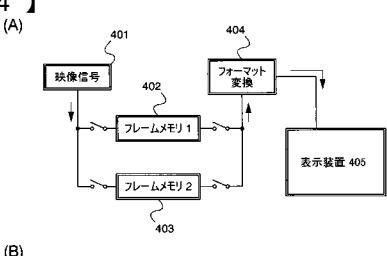

また、フレームメモリは、図4(A)に示すように、一般的には少なくとも2フレーム分設けられ(第1のフレームメモリ402、第2のフレームメモリ403)、一方のフレームメモリに映像信号401の書き込みを行っている間は、他のフレームメモリから読み出しを行い、フォーマット変換404を通じて画面の表示を行う。

## 【0029】

このようにすると、表示装置は通常駆動のままで、画面の縦横切り替えを行うことが出来る。ただし、この方法のみによって正常に画面表示が行えるのは、 $m = n$ 、すなわち縦横の画素数が等しいときに限られる。画面の縦横の画素数が異なる表示装置において縦横の表示変換を行う場合は、フォーマット変換を必要とする。

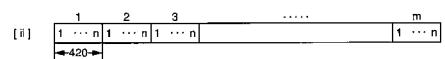

映像信号は、図4(B)の[i]に示すように、1行目の1画素～m画素に書き込まれる映像信号、2行目の1画素～m画素に書き込まれる映像信号、・・・とn本分が集まった構成となっている。この場合、横m×縦n画素に対応している。これを縦横の表示切り替えを行うには、図4(B)の[ii]に示すように、横n×縦m画素に対応した形に変換する必要がある。これをフォーマット変換という。フォーマット変換自体は公知技術を用いて行えればよいので、その詳細は省略する。

## 【0030】

最近、携帯電話等の小型携帯端末においても、様々なソフトウェアが供給され、1つの機器における用途が多様化する傾向にあるため、前述のような縦横表示の切り替え技術が重要となる。しかし、前述したようなフレームメモリを用いて縦横データを入れ替える場合は映像が不連続になりノイズが乗りやすいと言う課題があった。

## 【0031】

よって、本発明者は以前にフレームメモリを用いずに画面の縦横切り替えをおこなう表示装置を発案した。その表示装置は、ソース信号線駆動回路と、第1のゲート信号線駆動回路と、第2のゲート信号線駆動回路とを有する。そして第2のゲート信号線駆動回路の走査方向は、第1のゲート信号線駆動回路の走査方向と直交するような構成とする。

## 【0032】

ここで、走査方向とは、それぞれの駆動回路が制御する信号線の並びに直交する方向であるとする。また、通常表示を第1の表示と表記し、これに対し、画面の縦横を切り替えて表示する場合を、第2の表示と表記する。

## 【0033】

通常表示の際は、画面の垂直走査は第1のゲート信号線駆動回路によって行う。映像は、第1のゲート信号線の走査方向に従った向きで表示される。一方、第2の表示の際には、画面の垂直走査は第2のゲート信号線駆動回路によって行う。映像は、第2のゲート信号線の走査方向に従った向きで表示される。

## 【0034】

詳細は特許文献1に記載されている。特許文献1に記載された内容はフレームメモリ等の追加をすることなく、縦横の表示切り替えが可能な表示装置を提供するものである。

## 【特許文献1】特開2003-76315

## 【発明の開示】

## 【発明が解決しようとする課題】

## 【0035】

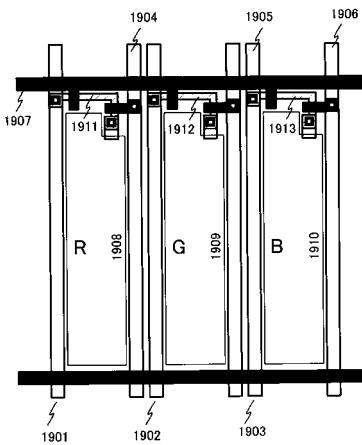

しかし、上述した縦横表示切り替えを用いた表示装置には以下のような課題があった。それは信号線を従来の表示装置に比べて多くする必要があり、特にソース信号線を増やすことは、画素の開口率を低下させることになる。図19に示すように画素には赤色(以下R)、緑色(以下G)、青色(以下B)3つの画素電極があり、ソース信号線を増やすことによって画素は更に縦長になり、開口率を低下させる。図19において画素はRGBそれぞれのソース信号線1901、1902、1903、第1のゲート信号線1907、RGBそれぞれの第2のゲート信号線1904、1905、1906、RGBそれぞれの画素電極1908、1909、1910、RGBそれぞれの画素トランジスタ1911、1

912、1913より構成される。本構成の画素では通常の液晶画素より第2のゲート信号線が多いため、開口率が低下する。

【課題を解決するための手段】

【0036】

本発明の表示装置は第1の表示及び第2の表示が可能であり、ソース信号線駆動回路と、第1のゲート信号線駆動回路と、第2のゲート信号線駆動回路とを有する。ここで、第2のゲート信号線駆動回路の走査方向は、第1のゲート信号線駆動回路の走査方向と直交する。

【0037】

第1の表示の際は、画面の垂直走査は第1のゲート信号線駆動回路によって行う。映像は、第1のゲート信号線の走査方向に従った向きで表示される。一方、第2の表示の際には、画面の垂直走査は第2のゲート信号線駆動回路によって行う。映像は、第2のゲート信号線の走査方向に従った向きで表示される。それに加えて、画素の駆動をフィールドシーケンシャル駆動としている。フィールドシーケンシャル駆動は1フレーム期間を3つのサブフレーム期間に分割し、それぞれの期間にRGBの光を独立に照射し、1つの画素でカラー表示をおこなうものである。

【0038】

本発明の第1の表示及び第2の表示が可能な表示装置の一は、周期的に発光色が変化する発光源と、ソース信号線駆動回路と、第1のゲート信号線駆動回路と、第2のゲート信号線駆動回路と、複数の画素とを有している。第1のゲート信号線駆動回路の走査方向と、第2のゲート信号線駆動回路の走査方向とが直交している。

【0039】

本発明の第1の表示及び第2の表示が可能な表示装置の一は、周期的に発光色が変化する発光源と、ソース信号線駆動回路と、第1のゲート信号線駆動回路と、第2のゲート信号線駆動回路と、複数の画素とを有している。複数の画素は、ソース信号線と、第1のゲート信号線と、第1のゲート信号線に直交する第2のゲート信号線と、第1のトランジスタと、第2のトランジスタとを有している。第1のトランジスタのゲート電極は、第1のゲート信号線と電気的に接続され、前記第1のトランジスタの入力電極は、ソース信号線と電気的に接続され、前記第2のトランジスタの出力電極は、第2のトランジスタの入力電極と電気的に接続されている。第2のトランジスタのゲート電極は、第2のゲート信号線と電気的に接続されている。

【0040】

上記において、第1の表示を行う際には、ソース信号線駆動回路の駆動周波数は、第1のゲート信号線駆動回路の駆動周波数よりも高く、第2の表示を行う際には、ソース信号線駆動回路の駆動周波数は、第1のゲート信号線駆動回路の駆動周波数よりも低くなっている場合が好ましい。

【0041】

また、上記において、前記ソース信号線駆動回路、前記第1のゲート信号線駆動回路、前記第2のゲート信号線駆動回路の少なくとも1つと、前記複数の画素は同一基板上に形成されていると好ましい。

【0042】

本発明の第1の表示及び第2の表示が可能な表示装置の一は、周期的に発光色が変化する発光源と、第1のソース信号線駆動回路と、第2のソース信号線駆動回路と、第1のゲート信号線駆動回路と、第2のゲート信号線駆動回路と、複数の画素とを有している。第1のソース信号線駆動回路と、第2のソース信号線駆動回路と、第1のゲート信号線駆動回路と、第2のゲート信号線駆動回路と、複数の画素とはいずれも同一基板上に形成されている。第1のゲート信号線駆動回路の走査方向と、第2のゲート信号線駆動回路の走査方向とが直交する。

【0043】

本発明の第1の表示及び第2の表示が可能な表示装置の一は、周期的に発光色が変化す

10

20

30

40

50

る発光源と、第1のソース信号線駆動回路と、第2のソース信号線駆動回路と、第1のゲート信号線駆動回路と、第2のゲート信号線駆動回路と、複数の画素とを有している。複数の画素は、第1のソース信号線と、第2のソース信号線と、第1のゲート信号線と、第1のゲート信号線に直交する第2のゲート信号線と、第1のトランジスタと、第2のトランジスタとを有している。第1のトランジスタのゲート電極は、第1のゲート信号線と電気的に接続され、前記第1のトランジスタの入力電極は前記第1のソース信号線と電気的に接続されている。第2のトランジスタのゲート電極は、第2のゲート信号線と電気的に接続され、入力電極は前記第2のソース信号線と電気的に接続されている。

【0044】

上記において、第1の表示を行う際には、映像は前記第1のゲート信号線駆動回路の走査方向に従った向きで表示され、第2の表示を行う際には、映像は前記第2のゲート信号線駆動回路の走査方向に従った向きで表示されることが好ましい。

【0045】

また、上記において、前記第1のソース信号線駆動回路、前記第1のソース信号線駆動回路、前記第1のゲート信号線駆動回路、前記第2のゲート信号線駆動回路の少なくとも1つと、前記複数の画素は同一基板上に形成されていると好ましい。

【0046】

上記において、複数の画素はそれぞれ、液晶素子を有していても良い。

【0047】

本発明の第1の表示及び第2の表示が可能な表示装置の駆動方法の一は、ソース信号線駆動回路と、第1のゲート信号線駆動回路と、第2のゲート信号線駆動回路と、複数の画素とを有している表示装置にあって、第1のゲート信号線駆動回路の走査方向と、第2のゲート信号線駆動回路の走査方向とを交差させ、複数の画素を、フィールドシーケンシャル駆動することを特徴としている。

【0048】

上記駆動方法において、第1の表示を行う際には、ソース信号線駆動回路の駆動周波数は、第1のゲート信号線駆動回路の駆動周波数よりも高く、第2の表示を行う際には、ソース信号線駆動回路の駆動周波数は、第1のゲート信号線駆動回路の駆動周波数よりも低くなるようにすることが好ましい。

【0049】

本発明の第1の表示及び第2の表示が可能な表示装置の駆動方法の一は、第1のソース信号線駆動回路と、第2のソース信号線駆動回路と、第1のゲート信号線駆動回路と、第2のゲート信号線駆動回路と、複数の画素とを有した表示装置にあって、第1のゲート信号線駆動回路の走査方向と、第2のゲート信号線駆動回路の走査方向とを交差させ、複数の画素をフィールドシーケンシャル駆動することを特徴としている。

【0050】

上記駆動方法において、第1の表示を行う際には、映像は前記第1のゲート信号線駆動回路の走査方向に従った向きで表示され、第2の表示を行う際には、映像は前記第2のゲート信号線駆動回路の走査方向に従った向きで表示されることが好ましい。

【発明の効果】

【0051】

本発明によって、画面の縦横切り替えを容易に可能にすることができ、且つ、開口率を向上させ、高画質な表示装置を提供することができる。

【発明を実施するための最良の形態】

【0052】

以下、本発明の実施の形態を図面に基づいて説明する。但し、本発明は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本実施の形態の記載内容に限定して解釈されるものではない。

【0053】

10

20

30

40

50

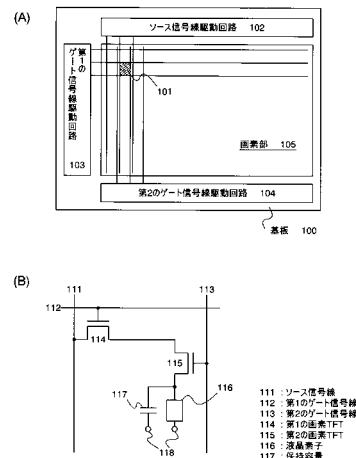

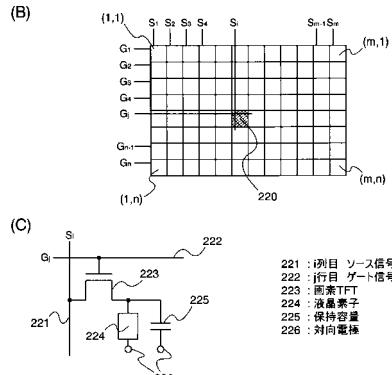

図1(A)は、本発明の一実施形態を示したものである。基板100上には、画素部105、ソース信号線駆動回路102、第1のゲート信号線駆動回路103、および第2のゲート信号線駆動回路104が形成されている。

【0054】

画素部105において、第1のゲート信号線駆動回路103、第2のゲート信号線駆動回路104、ソース信号線駆動回路102のそれぞれから伸びる信号線に囲まれた領域に、一つの画素101が区画されている。画素101の回路構成を図1(B)に示す。一画素は、ソース信号線111、第1のゲート信号線112、第2のゲート信号線113、第1の画素TFT114、第2の画素TFT115、液晶素子116、保持容量117、対向電極118を有している。

【0055】

第1の画素TFT114のゲート電極は、第1のゲート信号線112と電気的に接続され、第1のゲート信号線112に入力されるパルスによってON、OFFが制御される。第2の画素TFT115のゲート電極は、第2のゲート信号線113と電気的に接続され、第2のゲート信号線113に入力されるパルスによってON、OFFが制御される。

【0056】

ソース信号線111より入力される映像信号は、第1の画素TFT114、および第2の画素TFT115が共にONのときに画素に入力され、保持容量117において電荷が保持される。

【0057】

回路の動作について説明する。なお、本実施の形態においては、画素数を $m \times n$ 画素としているが、映像信号のフォーマット変換についてはその手段を問わないで、説明を簡単にするため、フォーマット変換を必要としないように $m = n$ とした場合を例に挙げて説明する。図1および図8を参照する。

【0058】

第1の表示、すなわち通常表示を行う場合、第2のゲート信号線駆動回路104は、第2の画素TFT115が全画面にわたってONとなるようにしておくる。これにより、画素は第1の画素TFT114のON、OFFのみによって制御される。あとは、ソース信号線駆動回路と第1のゲート信号線駆動回路とを従来と同様に駆動することによって映像の表示を行う。図8(A)に示すように、画素の書き込みの順序は、(1, 1) (2, 1) ··· (m, 1)、(1, 2) (2, 2) ··· (m, 2)、···、(1, n) (2, n) ··· (m, n)となる。

【0059】

次に、第2の表示、すなわち画面の縦横を切り替えた場合について説明する。図8(B)は、図8(A)を時計回りに90°回転させた様子を示している。本発明の表示装置は、フレームメモリを用いないため、映像信号の入力順序は変えない。よって、図8(B)に示す状態での画素への書き込みの順序は、(1, n) (1, n-1) ··· (1, 1)、(2, n) (2, n-1) ··· (2, 1)、···、(m, n) (m, n-1) ··· (m, 1)となる。

【0060】

よって、第2の表示を行っている間は、ソース信号線駆動回路801は通常よりも低速で駆動し、1水平期間づつサンプリングパルスを出力する。これにより、サンプリングスイッチは1水平期間の間開きつづけているので、ソース信号線1本ごとに、1水平期間分の映像信号が連続的に書き込まれていく。一方、第1のゲート信号線駆動回路802は、通常よりも高速に駆動し、1ドットサンプリング期間づつ、ゲート信号線選択パルスを出力する。これにより、各画素では、1ドットサンプリング期間だけ第1の画素TFTがONし、そのときの映像信号が書き込まれる。また、第2のゲート信号線駆動回路803は、ソース信号線駆動回路801と同様の動作をする。つまり、ソース信号線駆動回路801からサンプリングパルスが出力されて、ある列のソース信号線に映像信号が入力されているとき、その列の第2のゲート信号線が選択され、選択された第2のゲート信号線に接

続されている第2の画素TFTは全てONとなることにより、その列にのみ映像信号の書き込みが許可される。

【0061】

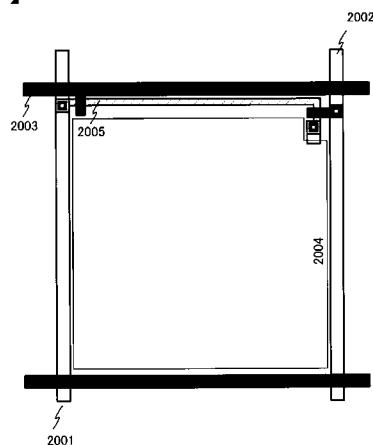

図20に本発明の画素の平面図を示す。フィールドシーケンシャル駆動をおこなうため、RGBに画素を分離する必要はない。したがって必要な信号線も少なくてすみ、開口率を飛躍的に大きくすることができる。図20において、画素はソース信号線2001、第1のゲート信号線2003、第2のゲート信号線2002、画素電極2004、画素TFT2005より構成される。

【0062】

次にフィールドシーケンシャルの実施形態について説明をおこなう。フィールドシーケンシャル駆動は周期的に発光色が変化する光源と、液晶などの光シャッターを用いてカラー表示をおこなうものである。周期的に発光色が変化する光源としては、RGBの冷陰極管やLEDを切り替えて点灯させるものがある。また、カラーフィルタを白色光源の前で回転させ、RGB成分を個別に取り出すものなどがある。携帯用機器などではRGBのLEDを切り替えて点灯させるものを用いるのが好ましい。

【0063】

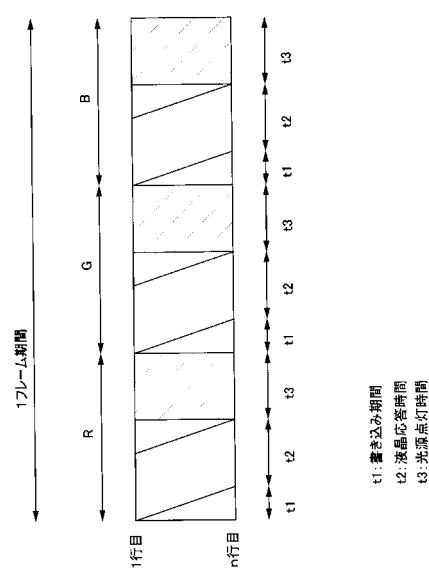

一般にテレビなどの映像において、1フレーム期間は16.6ms程度である。これをRGBそれぞれの3つのサブフレームに分けると5.53ms程度となるが、画素への書き込み時間や、液晶の応答速度などを考慮すると、実際のRGBそれぞれの点灯期間は2ms程度が望ましい。

【0064】

図21にタイミングチャートを示す。以下において、その動作を説明する。ここでは説明上、映像の順番をR、G、Bの順序とする。まず画素にRのデータを書き込んでいく。書き込まれた画素から順次液晶が応答する。書き込みが終了し、液晶の応答が終了した後に、Rの光源を点灯させる。Rの光源を一定時間点灯の後、Rの光源を消灯する。図21において第1行目の書き込み開始から第n行目の書き込み終了までの時間をt1としている。また、液晶の応答時間をt2としている。そして光源(LEDなど)の点灯時間をt3としている。

【0065】

次に、画素にGのデータを書き込んでいく。書き込まれた画素から順次液晶が応答する。書き込みが終了し、液晶の応答が終了した後に、Gの光源を点灯させる。Gの光源を一定時間点灯の後、Gの光源を消灯する。さらに画素にBのデータを書き込んでいく。書き込まれた画素から順次液晶が応答する。書き込みが終了し、液晶の応答が終了した後に、Bの光源を点灯させる。Bの光源を一定時間点灯の後、Bの光源を消灯する。

【0066】

これを繰り返すことによって、フィールドシーケンシャル駆動が可能となる。フィールドシーケンシャル駆動には高速の液晶が必要となるが、本発明においてはOCB(Optical Compensated Bend)、FLC(強誘電性液晶)、AFLC(反強誘電性液晶)などの液晶材料が使用可能であるが、これには限界はない。セルギャップを小さくすることや、過渡状態を使うことによって、TN(ツイストネマチック)液晶を用いても実現することが可能である。

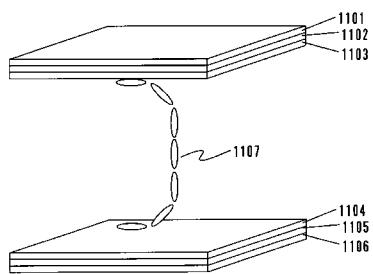

【0067】

図11にOCB液晶の例を示す。OCB液晶は視野角が広く、応答が早い液晶材料であるので、フィールドシーケンシャル駆動に適した液晶材料である。

【0068】

基板1103、1104に位相差フィルム1102、1105、偏光板1101、1106を貼り付ける。基板1103、1104の間に液晶材料1107を挟み込む。OCB液晶は上下対称なBend(弓なり)配向構造をしており、セルの上層部と下層部がそれぞれ補償しあう構成になっている。位相差フィルム1102、1105に液晶層の配列に対応して傾斜角が変化するハイブリッドディスコティックフィルムを組み合わせることに

10

20

30

40

50

より、広い視野角が得られる。

【実施例1】

【0069】

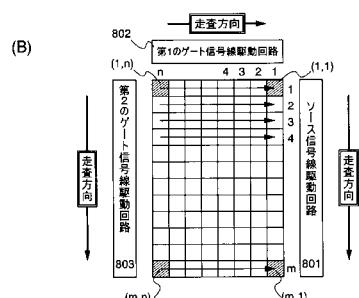

実施形態にて示した方法で縦横表示切り替えを行う場合、第1のゲート信号線駆動回路の走査方向に注目する。通常表示の場合、図8(A)に示したように、第1のゲート信号線駆動回路は、1行目からn行目までのゲート信号線を順に選択、走査していく。これに對して、縦横を切り替えた場合には、図8(B)に示したように、第1のゲート信号線駆動回路は、逆にn行目から1行目までのゲート信号線を順に選択、走査していく。よって、縦横表示切り替えの際は、第1のゲート信号線駆動回路の走査方向の切り替えが必要となる。

10

【0070】

図9に、走査方向切り替え回路を追加した駆動回路の構成を示す。フリップフロップ901を複数段用いてなるシフトレジスタ902、NAND904、バッファ905に関しては、図7(A)に示した従来例と同様である。走査方向切り替え回路903には、走査方向切り替え信号(UD)、走査方向切り替え反転信号(UDb)が入力され、走査方向切り替え信号(UD)がH、走査方向切り替え反転信号(UDb)がLのとき、ゲート信号線の選択は、G<sub>1</sub>、G<sub>2</sub>、…、G<sub>n</sub>の順であり、走査方向切り替え信号(UD)がL、走査方向切り替え反転信号(UDb)がHのとき、ゲート信号線の選択は、G<sub>n</sub>、G<sub>n-1</sub>、…、G<sub>1</sub>の順となる。

20

【0071】

なお、本発明を実施するにあたり、その駆動回路の構成は図6、図7、図9等の構成には限定しない。例えば、シフトレジスタの代わりにデコーダを用いた場合等においても、本発明は実施が可能である。

【実施例2】

【0072】

本実施例では、実施形態とは異なる方法で、簡単に縦横表示の切り替えを行う場合の例を示す。

【0073】

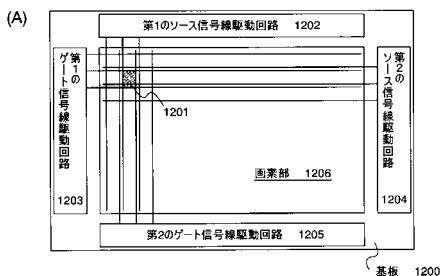

図12(A)に表示装置の構成を示す。基板1200上に画素部1206が形成され、さらに第1のソース信号線駆動回路1202、第1のゲート信号線駆動回路1203、第2のソース信号線駆動回路1204、第2のゲート信号線駆動回路1205が形成されている。ここで、第1のソース信号線駆動回路の走査方向と、第2のソース信号線駆動回路の走査方向とは互いに垂直をなす。また、第1のゲート信号線駆動回路の走査方向と、第2のゲート信号線駆動回路の走査方向とは互いに垂直をなす。

30

【0074】

画素部1206において、1201で示される部分が一画素であり、その構成を図12(B)に示す。一画素は、第1のソース信号線1211、第1のゲート信号線1212、第2のソース信号線1213、第2のゲート信号線1214、第1の画素TFT1215、第2の画素TFT1216、液晶素子1217、保持容量1218、対向電極1219を有する。

40

【0075】

本実施例の場合、ソース信号線、ゲート信号線、画素TFTをそれぞれ2つづつ有するため、液晶素子に映像信号を書き込む経路が独立して2系統ある。第1の表示、すなわち通常表示を行う際には例えば、第1のソース信号線駆動回路、第1のゲート信号線駆動回路を動作させることによって第1の画素TFTを制御し、第1のソース信号線1211に入力される映像信号を画素に書き込む。このとき、第2のソース信号線駆動回路、第2のゲート信号線駆動回路は、いずれも動作しないようにしておく。

【0076】

一方、第2の表示、すなわち画面の縦横を切り替える際には、第2のソース信号線駆動回路、第2のゲート信号線駆動回路を動作させることによって第2の画素TFTを制御し

50

、第2のソース信号線1213に入力される映像信号を画素に書き込む。このとき、第1のソース信号線駆動回路、第1のゲート信号線駆動回路は、いずれも動作しないようにしておく。

【0077】

このように、一画素を2組の駆動回路を交互に用いて制御することにより、容易に縦横の表示切り替えが可能である。

【実施例3】

【0078】

高解像度、大画面の表示装置においては、一定期間内により多くの画素を駆動する必要がある。従来の駆動方法では駆動周波数が高くなるため、分割駆動が採用される場合が多い。

【0079】

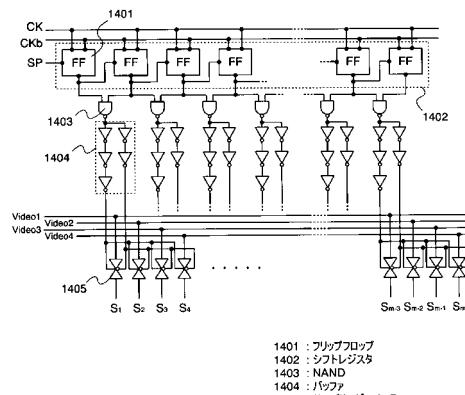

図14は、分割駆動を行う場合のソース信号線駆動回路の構成例を示しており、フリップフロップ1401を複数段用いてなるシフトレジスタ1402、NAND1403、バッファ1404、サンプリングスイッチ1405等を有する。

【0080】

図6に示した回路は、1つのサンプリングパルスによって1度に一画素への映像信号の書き込みが行われるのに対し、図14に示した回路は、映像信号を並列に4本入力し、1つのサンプリングパルスによって1度に4画素への映像信号の書き込みを行う。このようにすると、画素数が同じ従来の表示装置と比較して、ソース信号線駆動回路の駆動周波数を(1/分割数)に抑えることが出来る。図14の場合は、4点同時サンプリングを行うので、分割数は4分割であり、ソース信号線駆動回路の駆動周波数を1/4に抑えることが出来る。

【0081】

本実施例においては、このような分割駆動を行う表示装置において、縦横表示の切り替えを行う方法について説明する。

【0082】

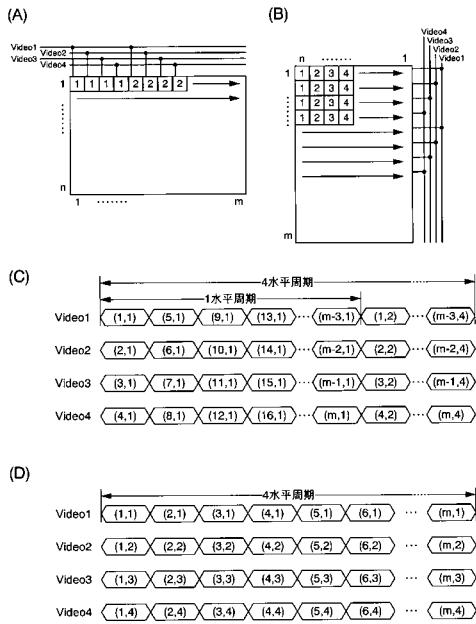

図15を参照する。図15(A)は、4分割駆動を行うソース信号線駆動回路を有する表示装置の、通常表示時の書き込み順序を示している。4本のビデオ信号線から、同時に4画素分のサンプリングを行い、最初のサンプリングパルスで(1, 1)(2, 1)(3, 1)(4, 1)の4画素に同時に書き込まれる。続いて、次のサンプリングパルスで(5, 1)(6, 1)(7, 1)(8, 1)の4画素に同時に書き込まれる。

【0083】

よって、各ビデオ信号線(Video1~Video4)に入力される映像信号の入力順序は図15(C)に示すようになる。

【0084】

図15(B)は、図15(A)に示した表示装置の縦横表示を切り替えた場合の書き込み順序を示している。通常表示の場合、横方向に並んだ4点で同時サンプリングが行われるのに対し、縦横を切り替えた場合、縦方向に並んだ4点で同時サンプリングが行われる。

【0085】

通常表示の場合、最初に同時に書き込まれる画素は、(1, 1)(2, 1)(3, 1)(4, 1)の4画素であったが、縦横を切り替えた場合、最初に同時に書き込まれる画素は、(1, n)(2, n)(3, n)(4, n)の4画素である。

【0086】

このとき、それら4画素に書き込まれるべき映像信号は、通常表示の場合に(1, 1)(1, 2)(1, 3)(1, 4)の4画素に書き込まれるべき映像信号である。

【0087】

よって、縦横の表示を切り替える場合、各ビデオ信号線(Video1~Video4)に入力される映像信号の入力順序は図15(D)に示すようになる。

10

20

30

40

50

## 【0088】

この場合、4水平周期分の映像信号の並べ替えを行う手順が必要なため、4水平周期分の映像信号を記憶するメモリを必要とするが、従来のようにフレームメモリを必要とする場合と比較しても、その記憶容量は極めて小さくて済む。

## 【0089】

以上のようにして、分割駆動を行う表示装置においても、本発明を実施することが可能である。

## 【実施例4】

## 【0090】

本実施例においては、同一基板上に画素部および画素部の周辺に設ける駆動回路のTFT (nチャネル型TFT及びpチャネル型TFT)を同時に作製する方法について詳細に説明する。 10

## 【0091】

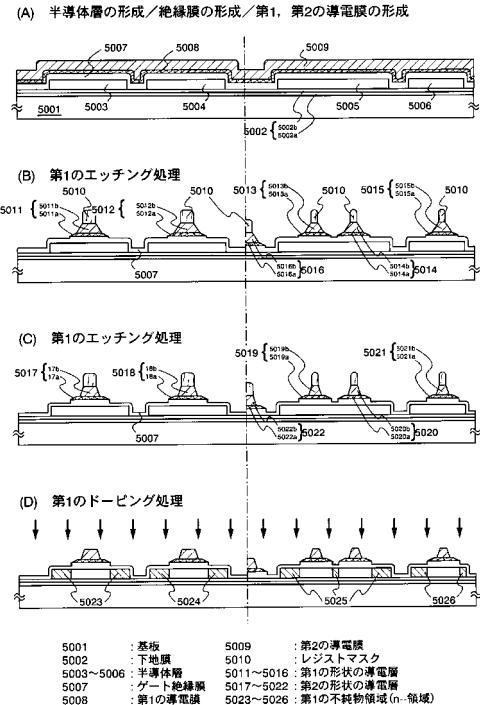

図16を参照する。まず、基板5001上に下地絶縁膜5002を形成し、結晶構造を有する第1の半導体膜を得た後、所望の形状にエッチング処理して島状に分離された半導体層5003～5006を形成する。

## 【0092】

本実施例においては、基板5001としてガラス基板 (#1737基板)を用い、下地絶縁膜5002としては、プラズマCVD法で成膜温度400℃、原料ガスSiH<sub>4</sub>、NH<sub>3</sub>、N<sub>2</sub>Oから作製される酸化窒化シリコン膜5002a (組成比Si = 32%、O = 27%、N = 24%、H = 17%)を50nm (好ましくは10～200nm)形成する。次いで、表面をオゾン水で洗浄した後、表面の酸化膜を希フッ酸 (1/100希釈)で除去する。次いでプラズマCVD法で成膜温度400℃、原料ガスSiH<sub>4</sub>、N<sub>2</sub>Oから作製される酸化窒化水素化シリコン膜5002b (組成比Si = 32%、O = 59%、N = 7%、H = 2%)を100nm (好ましくは50～200nm)の厚さに積層形成し、さらに大気解放せずにプラズマCVD法で成膜温度300℃、成膜ガスSiH<sub>4</sub>で非晶質構造を有する半導体膜 (ここではアモルファスシリコン膜)を54nmの厚さ (好ましくは25～80nm)で形成する。 20

## 【0093】

本実施例では下地膜絶縁膜5002を2層構造として示したが、前記絶縁膜の単層膜または3層以上積層させた構造として形成しても良い。また、半導体膜の材料に限定はないが、好ましくはシリコンまたはシリコンゲルマニウム (Si<sub>x</sub>Ge<sub>1-x</sub> (X = 0.0001～0.02)) 合金などを用い、公知の手段 (スパッタ法、LPCVD法、またはプラズマCVD法等)により形成すればよい。また、プラズマCVD装置は、枚葉式の装置でもよいし、バッチ式の装置でもよい。また、同一の成膜室で大気に触れることなく下地絶縁膜と半導体膜とを連続成膜してもよい。 30

## 【0094】

次いで、非晶質構造を有する半導体膜の表面を洗浄した後、オゾン水で表面に約2nmのごく薄い酸化膜 (図示せず)を形成する。次いで、TFTのしきい値を制御するために微量な不純物元素 (ボロンまたはリン) のドーピングを行う。ここでは、ジボラン (B<sub>2</sub>H<sub>6</sub>)を質量分離しないでプラズマ励起したイオンドープ法を用い、ドーピング条件を加速電圧15kV、ジボランを水素で1%に希釈したガス流量30sccm、ドーズ量2×10<sup>12</sup>atoms/cm<sup>2</sup>で非晶質シリコン膜にボロンを添加する。 40

## 【0095】

次いで、重量換算で10ppmのニッケルを含む酢酸ニッケル溶液をスピナーで塗布する。塗布に代えてスパッタ法でニッケル元素を全面に散布する方法を用いてもよい。

## 【0096】

次いで、加熱処理を行い結晶化させて結晶構造を有する半導体膜を形成する。この加熱処理は、電気炉の熱処理または強光の照射を用いればよい。電気炉の熱処理で行う場合は、500～650℃で4～24時間で行えばよい。ここでは脱水素化のための熱処理 ( 50

500、1時間)の後、結晶化のための熱処理(550、4時間)を行って結晶構造を有するシリコン膜を得る。なお、ここでは炉を用いた熱処理を用いて結晶化を行ったが、ランプアニール装置で結晶化を行ってもよい。なお、ここではシリコンの結晶化を助長する金属元素としてニッケルを用いた結晶化技術を用いたが、他の公知の結晶化技術、例えば固相成長法やレーザー結晶化法を用いてもよい。

#### 【0097】

次いで、結晶構造を有するシリコン膜表面の酸化膜を希フッ酸等で除去した後、結晶化率を高め、結晶粒内に残される欠陥を補修するための第1のレーザー光(XeCl:波長308nm)の照射を大気中、または酸素雰囲気中で行う。レーザー光には波長400nm以下のエキシマレーザー光や、YAGレーザーの第2高調波、第3高調波、またはCWレーザーを用いる。いずれにしても、繰り返し周波数10~1000Hz程度のパルスレーザー光を用い、当該レーザー光を光学系にて100~500mJ/cm<sup>2</sup>に集光し、90~95%のオーバーラップ率をもって照射し、シリコン膜表面を走査させればよい。ここでは、繰り返し周波数30Hz、エネルギー密度393mJ/cm<sup>2</sup>で第1のレーザー光の照射を大気中で行う。なお、大気中、または酸素雰囲気中で行うため、第1のレーザー光の照射により表面に酸化膜が形成される。

#### 【0098】

次いで、第1のレーザー光の照射により形成された酸化膜を希フッ酸で除去した後、第2のレーザー光の照射を窒素雰囲気、或いは真空中で行い、半導体膜表面を平坦化する。このレーザー光(第2のレーザー光)には波長400nm以下のエキシマレーザー光や、YAGレーザーの第2高調波、第3高調波、またはCWレーザーを用いる。第2のレーザー光のエネルギー密度は、第1のレーザー光のエネルギー密度より大きく(好ましくは30~60mJ/cm<sup>2</sup>大きく)する。ここでは、繰り返し周波数30Hz、エネルギー密度453mJ/cm<sup>2</sup>で第2のレーザー光の照射を行い、半導体膜表面における凹凸のP-V値が5nm以下となる。

#### 【0099】

また、本実施例では第2のレーザー光の照射を全面に行ったが、オフ電流の低減は、画素部のTFTに特に効果があるため、少なくとも画素部のみに選択的に照射する工程としてもよい。また、1回のレーザー照射のみによる処理であっても良い。

#### 【0100】

次いで、オゾン水で表面を120秒処理して合計1~5nmの酸化膜からなるバリア層(図示せず)を形成する。

#### 【0101】

次いで、バリア層上にスパッタ法にてゲッタリングサイトとなるアルゴン元素を含む非晶質シリコン膜を膜厚150nmで形成する。本実施例のスパッタ法による成膜条件は、成膜圧力を0.3Paとし、ガス(Ar)流量を50sccmとし、成膜パワーを3kWとし、基板温度を150とする。なお、上記条件での非晶質シリコン膜に含まれるアルゴン元素の原子濃度は、 $3 \times 10^{20} \sim 6 \times 10^{20}$ atoms/cm<sup>3</sup>、酸素の原子濃度は $1 \times 10^{19} \sim 3 \times 10^{19}$ atoms/cm<sup>3</sup>である。その後、ランプアニール装置を用いて500、3分の熱処理を行いゲッタリングする。

#### 【0102】

次いで、バリア層をエッチングストッパーとして、ゲッタリングサイトであるアルゴン元素を含む非晶質シリコン膜を選択的に除去した後、バリア層を希フッ酸で選択的に除去する。なお、ゲッタリングの際、ニッケルは酸素濃度の高い領域に移動しやすい傾向があるため、酸化膜からなるバリア層をゲッタリング後に除去することが望ましい。

#### 【0103】

次いで、得られた結晶構造を有するシリコン膜(ポリシリコン膜とも呼ばれる)の表面にオゾン水で薄い酸化膜を形成した後、レジストからなるマスクを形成し、所望の形状にエッチング処理して島状に分離された半導体層5003~5006を形成する。半導体層を形成した後、レジストからなるマスクを除去する。

10

20

30

40

50

## 【0104】

次いで、フッ酸を含むエッチャントで酸化膜を除去すると同時にシリコン膜の表面を洗浄した後、ゲート絶縁膜5007となる珪素を主成分とする絶縁膜を形成する。本実施例では、プラズマCVD法により115nmの厚さで酸化窒化シリコン膜（組成比Si=32%、O=59%、N=7%、H=2%）で形成する。

## 【0105】

次いで、ゲート絶縁膜5007上に膜厚20~100nmの第1の導電膜5008と、膜厚100~400nmの第2の導電膜5009とを積層形成する。本実施例では、ゲート絶縁膜5007上に膜厚50nmの窒化タンタル（TaN）膜、膜厚370nmのタンゲステン（W）膜を順次積層する（図16（A））。

10

## 【0106】

第1の導電膜及び第2の導電膜を形成する導電性材料としてはTa、W、Ti、Mo、Al、Cuから選ばれた元素、または前記元素を主成分とする合金材料もしくは化合物材料で形成する。また、第1の導電膜及び第2の導電膜としてリン等の不純物元素をドーピングした多結晶シリコン膜に代表される半導体膜や、AgPdCu合金を用いてもよい。また、2層構造に限定されず、例えば、膜厚50nmのタンゲステン膜、膜厚500nmのアルミニウムとシリコンの合金（Al-Si）膜、膜厚30nmの窒化チタン膜を順次積層した3層構造としてもよい。また、3層構造とする場合、第1の導電膜のタンゲステンに代えて窒化タンゲステンを用いてもよいし、第2の導電膜のアルミニウムとシリコンの合金（Al-Si）膜に代えてアルミニウムとチタンの合金膜（Al-Ti）を用いてもよいし、第3の導電膜の窒化チタン膜に代えてチタン膜を用いてもよい。また、単層構造であってもよい。

20

次に、図16（B）に示すように光露光工程によりレジストからなるマスク5010を形成し、ゲート電極及び配線を形成するための第1のエッチャング処理を行う。第1のエッチャング処理では第1及び第2のエッチャング条件で行う。エッチャングにはICP（Inductive Coupled Plasma：誘導結合型プラズマ）エッチャング法を用いると良い。ICPエッチャング法を用い、エッチャング条件（コイル型の電極に印加される電力量、基板側の電極に印加される電力量、基板側の電極温度等）を適宜調節することによって所望のテーパー形状に膜をエッチャングすることができる。なお、エッチャング用ガスとしては、Cl<sub>2</sub>、BCl<sub>3</sub>、SiCl<sub>4</sub>、CCl<sub>4</sub>などを代表とする塩素系ガスまたはCF<sub>4</sub>、SF<sub>6</sub>、NF<sub>3</sub>などを代表とするフッ素系ガス、またはO<sub>2</sub>を適宜用いることができる。

30

## 【0107】

本実施例では、基板側（試料ステージ）にも150WのRF（13.56MHz）電力を投入し、実質的に負の自己バイアス電圧を印加する。この第1のエッチャング条件によりW膜をエッチャングして第1の導電層の端部をテーパー形状とする。第1のエッチャング条件でのWに対するエッチャング速度は200.39nm/min、TaNに対するエッチャング速度は80.32nm/minであり、TaNに対するWの選択比は約2.5である。また、この第1のエッチャング条件によって、Wのテーパー角は、約26°となる。この後、レジストからなるマスク5010を除去せずに第2のエッチャング条件に変え、エッチャング用ガスにCF<sub>4</sub>とCl<sub>2</sub>とを用い、それぞれのガス流量比を30/30sccmとし、1.0Paの圧力でコイル型の電極に500WのRF（13.56MHz）電力を投入してプラズマを生成して約30秒程度のエッチャングを行った。基板側（試料ステージ）にも20WのRF（13.56MHz）電力を投入し、実質的に負の自己バイアス電圧を印加する。CF<sub>4</sub>とCl<sub>2</sub>を混合した第2のエッチャング条件ではW膜及びTaN膜とも同程度にエッチャングされる。第2のエッチャング条件でのWに対するエッチャング速度は58.97nm/min、TaNに対するエッチャング速度は66.43nm/minである。なお、ゲート絶縁膜上に残渣を残すことなくエッチャングするためには、10~20%程度の割合でエッチャング時間を増加させると良い。

40

## 【0108】

上記第1のエッチャング処理では、レジストからなるマスクの形状を適したものとするこ

50

とにより、基板側に印加するバイアス電圧の効果により第1の導電層及び第2の導電層の端部がテーパー形状となる。このテーパー部の角度は15～45°とすればよい。

#### 【0109】

こうして、第1のエッチング処理により第1の導電層と第2の導電層から成る第1の形状の導電層5011～5016（第1の導電層5011a～5016aと第2の導電層5011b～5016b）を形成する。ゲート絶縁膜となる絶縁膜5007において、第1の形状の導電層5011～5016で覆われない領域は10～20nm程度エッチングされて薄くなる。

#### 【0110】

次いで、レジストからなるマスクを除去せずに第2のエッチング処理を行う。ここでは、エッチング用ガスにSF<sub>6</sub>とCl<sub>2</sub>とO<sub>2</sub>とを用い、それぞれのガス流量比を24/12/24sccmとし、1.3Paの圧力でコイル型の電極に700WのRF（13.56MHz）電力を投入してプラズマを生成してエッチングを25秒行った。基板側（試料ステージ）にも10WのRF（13.56MHz）電力を投入し、実質的に負の自己バイアス電圧を印加する。第2のエッチング処理でのWに対するエッチング速度は227.3nm/min、TaNに対するエッチング速度は32.1nm/minであり、TaNに対するWの選択比は7.1であり、ゲート絶縁膜5007であるSiONに対するエッチング速度は33.7nm/minであり、SiONに対するWの選択比は6.83である。このようにエッチングガス用ガスにSF<sub>6</sub>を用いた場合、ゲート絶縁膜5007との選択比が高いので膜減りを抑えることができる。本実施例ではゲート絶縁膜5007において約8nmしか膜減りが起きない。

#### 【0111】

この第2のエッチング処理によりWのテーパー角は70°となった。この第2のエッチング処理により第2の形状の導電層5017～5022を形成する。このとき、第1の導電層はほとんどエッチングされず、第1の導電層5017a～5022aとなる。なお、第1の導電層5017a～5022aは、第1の導電層5011a～5016aとほぼ同一サイズである。実際には第2のエッチング処理によって、第1の導電層の幅は、第2のエッチング処理前に比べて約0.3μm程度、即ち線幅全体で0.6μm程度後退する場合もあるがほとんどサイズに変化がない。

#### 【0112】

また、2層構造に代えて、膜厚50nmのタンゲステン膜、膜厚500nmのアルミニウムとシリコンの合金（Al-Si）膜、膜厚30nmの窒化チタン膜を順次積層した3層構造とした場合、第1のエッチング処理の第1のエッチング条件としては、BCl<sub>3</sub>とCl<sub>2</sub>とO<sub>2</sub>とを原料ガスに用い、それぞれのガス流量比を65/10/5sccmとし、基板側（試料ステージ）に300WのRF（13.56MHz）電力を投入し、1.2Paの圧力でコイル型の電極に450WのRF（13.56MHz）電力を投入してプラズマを生成して117秒のエッチングを行えばよく、第1のエッチング処理の第2のエッチング条件としては、CF<sub>4</sub>とCl<sub>2</sub>とO<sub>2</sub>とを用い、それぞれのガス流量比を25/25/10sccmとし、基板側（試料ステージ）にも20WのRF（13.56MHz）電力を投入し、1.0Paの圧力でコイル型の電極に500WのRF（13.56MHz）電力を投入してプラズマを生成して約30秒程度のエッチングを行えばよく、第2のエッチング処理としてはBCl<sub>3</sub>とCl<sub>2</sub>を用い、それぞれのガス流量比を20/60sccmとし、基板側（試料ステージ）には100WのRF（13.56MHz）電力を投入し、1.2Paの圧力でコイル型の電極に600WのRF（13.56MHz）電力を投入してプラズマを生成してエッチングを行えばよい。

#### 【0113】

次いで、レジストからなるマスクを除去した後、第1のドーピング処理を行って図16（D）の状態を得る。ドーピング処理はイオンドープ法、もしくはイオン注入法で行えば良い。イオンドープ法の条件はドーズ量を $1.5 \times 10^{14}$ atoms/cm<sup>2</sup>とし、加速電圧を60～100keVとして行う。n型を付与する不純物元素として、典型的にはリ

10

20

30

40

50

ン (P) または砒素 (As) を用いる。この場合、第1の導電層及び第2の導電層 5017 ~ 5021 が n 型を付与する不純物元素に対するマスクとなり、自己整合的に第1の不純物領域 5023 ~ 5026 が形成される。第1の不純物領域 5023 ~ 5026 には  $1 \times 10^{16} \sim 1 \times 10^{17}$  atoms/cm<sup>3</sup> の濃度範囲で n 型を付与する不純物元素を添加する。ここでは、第1の不純物領域と同じ濃度範囲の領域を n<sup>-</sup> 領域とも呼ぶ。

#### 【0114】

なお、本実施例ではレジストからなるマスクを除去した後、第1のドーピング処理を行ったが、レジストからなるマスクを除去せずに第1のドーピング処理を行ってもよい。

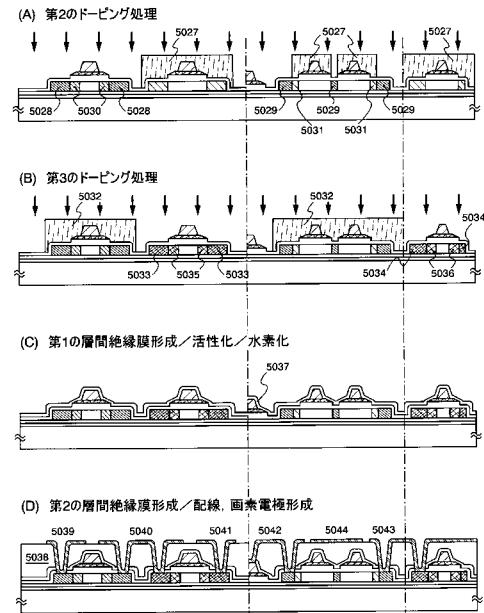

#### 【0115】

次いで、図17 (A) に示すようにレジストからなるマスク 5027 を形成し第2のドーピング処理を行う。第2のドーピング処理におけるイオンドープ法の条件はドーズ量を  $1.5 \times 10^{15}$  atoms/cm<sup>2</sup> とし、加速電圧を 60 ~ 100 keV としてリン (P) をドーピングする。ここでは、第2の導電層 5017b ~ 5021b をマスクとして各半導体層に不純物領域が自己整合的に形成される。勿論、マスク 5027 で覆われた領域には添加されない。こうして、第2の不純物領域 5028、5029 と、第3の不純物領域 5030 が形成される。第2の不純物領域 5028、5029 には  $1 \times 10^{20} \sim 1 \times 10^{21}$  atoms/cm<sup>3</sup> の濃度範囲で n 型を付与する不純物元素を添加されている。ここでは、第2の不純物領域と同じ濃度範囲の領域を n<sup>+</sup> 領域とも呼ぶ。

#### 【0116】

また、第3の不純物領域は第1の導電層 5017a により第2の不純物領域よりも低濃度に形成され、 $1 \times 10^{18} \sim 1 \times 10^{19}$  atoms/cm<sup>3</sup> の濃度範囲で n 型を付与する不純物元素を添加されることになる。なお、第3の不純物領域は、テーパー形状である第1の導電層 5017a の部分を通過させてドーピングを行うため、テーパー部の端部に向かって不純物濃度が増加する濃度勾配を有している。ここでは、第3の不純物領域と同じ濃度範囲の領域を n<sup>-</sup> 領域とも呼ぶ。また、マスク 5027 で覆われた領域 5031 は、第2のドーピング処理で不純物元素が添加されず、第1の不純物領域がそのまま残される。

#### 【0117】

次いで、レジストからなるマスク 5027 を除去した後、新たにレジストからなるマスク 5032 を形成して図17 (B) に示すように第3のドーピング処理を行う。駆動回路において、上記第3のドーピング処理により、Pチャネル型 TFT を形成する半導体層および保持容量を形成する半導体層に P 型の導電型を付与する不純物元素が添加された第4の不純物領域 5033、5034 及び第5の不純物領域 5035、5036 を形成する。

また、第4の不純物領域 5033、5034 には  $1 \times 10^{20} \sim 1 \times 10^{21}$  atoms/cm<sup>3</sup> の濃度範囲で P 型を付与する不純物元素が添加されるようとする。尚、第4の不純物領域 5033、5034 は、当初は先の工程でリン (P) が添加された領域 (n<sup>-</sup> 領域) となっているが、P 型を付与する不純物元素の濃度がその 1.5 ~ 3 倍添加されていて導電型は P 型となっている。ここでは、第4の不純物領域と同じ濃度範囲の領域を P<sup>+</sup> 領域とも呼ぶ。

#### 【0118】

また、第5の不純物領域 5035、5036 は第2の導電層 5018b、5021b のテーパー部と重なる領域に形成されるものであり、 $1 \times 10^{18} \sim 1 \times 10^{20}$  atoms/cm<sup>3</sup> の濃度範囲で P 型を付与する不純物元素が添加されるようとする。ここでは、第5の不純物領域と同じ濃度範囲の領域を P<sup>-</sup> 領域とも呼ぶ。

#### 【0119】

以上までの工程でそれぞれの半導体層に N 型または P 型の導電型を有する不純物領域が形成される。導電層 5017 ~ 5020 は TFT のゲート電極となる。また、導電層 5021 は画素部において保持容量を形成する一方の電極となる。さらに、導電層 5022 は画素部においてソース信号線を形成する。

10

20

30

40

50

## 【0120】

次いで、ほぼ全面を覆う絶縁膜（図示せず）を形成する。本実施例では、プラズマCVD法により膜厚50nmの酸化シリコン膜を形成した。勿論、この絶縁膜は酸化シリコン膜に限定されるものでなく、他のシリコンを含む絶縁膜を単層または積層構造として用いても良い。

## 【0121】

次いで、それぞれの半導体層に添加された不純物元素を活性化処理する工程を行う。この活性化工程は、ランプ光源を用いたラピッドサーマルアニール法（RTA法）、或いはYAGレーザーまたはエキシマレーザーを裏面から照射する方法、或いは炉を用いた熱処理、或いはこれらの方のうち、いずれかと組み合わせた方法によって行う。

10

## 【0122】

また、本実施例では、上記活性化の前に絶縁膜を形成した例を示したが、上記活性化を行った後、絶縁膜を形成する工程としてもよい。

## 【0123】

次いで、窒化シリコン膜からなる第1の層間絶縁膜5037を形成して熱処理（300～550で1～12時間の熱処理）を行い、半導体層を水素化する工程を行う（図17（C））。この工程は第1の層間絶縁膜5037に含まれる水素により半導体層のダングリングボンドを終端する工程である。酸化シリコン膜からなる絶縁膜（図示しない）の存在に關係なく半導体層を水素化することができる。

## 【0124】

次いで、第1の層間絶縁膜5037上に有機絶縁物材料から成る第2の層間絶縁膜5038を形成する。本実施例では膜厚1.6μmのアクリル樹脂膜を形成する。次いで、各電極もしくは不純物領域に達するコンタクトホールを開口する。本実施例では複数のエッチング処理を順次行う。本実施例では第1の層間絶縁膜5037をエッチングストッパーとして第2の層間絶縁膜5038をエッチングした後、絶縁膜（図示しない）をエッチングストッパーとして第1の層間絶縁膜5037をエッチングしてから絶縁膜（図示しない）をエッチングする。

その後、Al、Ti、Mo、Wなどを用いて配線及び画素電極を形成する。これらの電極及び画素電極の材料は、AlまたはAgを主成分とする膜、またはそれらの積層膜等で反射性に優れた材料を用いることが望ましい。こうして、配線5039～5042、画素電極5043、ゲート信号線5044が形成される。

20

## 【0125】

以上の様にして、Nチャネル型TFT、Pチャネル型TFTを有する駆動回路と、Nチャネル型TFTからなる画素TFT、保持容量とを有する画素部とを同一基板上に形成することができる（図17（D））。本明細書中ではこのような基板を便宜上アクティブマトリクス基板と呼ぶ。

## 【0126】

図17（D）に示したアクティブマトリクス基板において、Nチャネル型TFTは2種類の構造を有している。1つは、駆動回路のNチャネル型TFTに見られるような、ゲート電極に重なる第3の不純物領域を有するGOLD構造、もう1つは、画素TFTに見られるような、ゲート電極に重ならない第1の不純物領域を有するLDD構造である。

40

## 【0127】

前者は、ホットキャリア劣化等の抑制に有効な構造であり、特に動作に信頼性が求められる箇所に適している。後者は、オフ電流のリーク低減に有効な構造であり、負のバイアス電圧が印加される機会の多い回路や、画素部を制御する回路等に適している。

## 【0128】

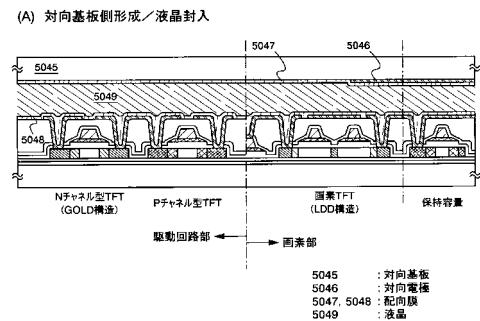

一方、対向基板5045を用意する。対向基板側には、透明導電膜でなる対向電極5046を形成する。

## 【0129】

続いて、アクティブマトリクス基板および対向基板に、それぞれ配向膜5047、50

50

48を形成し、ラビング処理を行う。なお、本実施例においては、配向膜5048をアクティブマトリクス基板側に形成する前に、アクリル樹脂等の有機樹脂膜を用いて、基板間の空隙を確保するための柱状スペーサ(図示せず)を所望の位置に形成した。また、柱状スペーサに代えて、球状のスペーサを基板全面に散布しても良い。

【0130】

そして、画素部と駆動回路が形成されたアクティブマトリクス基板と対向基板とをシール材(図示せず)で貼り合わせる。シール材にはフィラーが混入されていて、このフィラーと柱状スペーサによって均一な空隙を持って2枚の基板が貼り合わせられる。その後、両基板間の空隙に液晶材料5049を注入し、封止材(図示せず)によって完全に封止する。液晶材料5049には公知の液晶材料を用いれば良い。そして、必要があれば、アクティブマトリクス基板または対向基板を所望の形状に分断する。さらに、公知の技術を用いて偏光板等を適宜設けた。そして、公知の技術を用いてFPCを貼り付ける。このようにして図18に示すアクティブマトリクス型液晶表示装置が完成する。

10

【実施例5】

【0131】

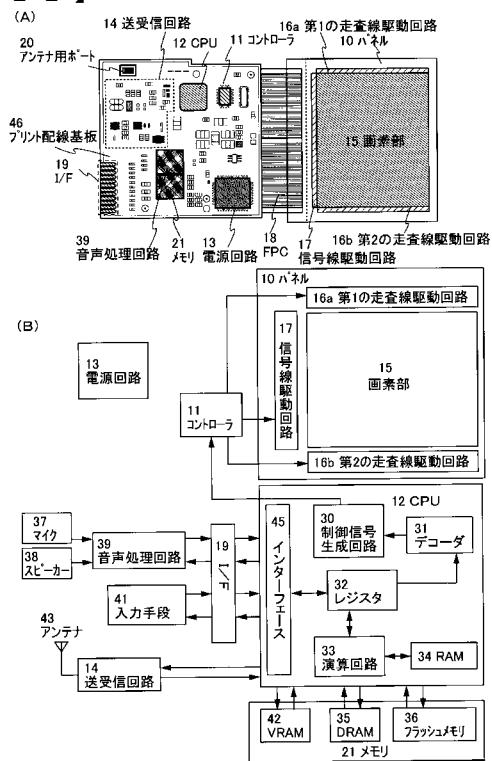

図22(A)に示す液晶表示装置は、プリント配線基板46に、コントローラ11、中央処理装置(CPU)12、メモリ21、電源回路13、音声処理回路39及び送受信回路14や、その他、抵抗、バッファ、容量素子等の素子が実装されている。また、液晶パネル10がフレキシブル配線基板(FPC)18を介してプリント配線基板46に接続されている。

20

【0132】

液晶パネル10には、ソース信号線駆動回路17と、第1のゲート信号線駆動回路16a」と、第2のゲート信号線駆動回路16bとを備えている。第2のゲート信号線駆動回路の走査方向は、第1のゲート信号線駆動回路の走査方向と直交する。この構成は図1(A)と同様なものである。この液晶パネル10は、フィールドシーケンシャル駆動をおこなうため、画素部15における画素をRGBに分離する必要はない。したがって必要な信号線も少なくてすみ、開口率を飛躍的に大きくすることができる。

【0133】

プリント配線基板46に備えられたインターフェース(I/F)19を介して、各種制御信号の入出力が行われる。また、アンテナとの間の信号の送受信を行なうためのアンテナ用ポート20が、プリント配線基板46に設けられている。

30

【0134】

なお、本実施例では液晶パネル10にプリント配線基板46がFPC18を介して接続されているが、必ずしもこの構成に限定されない。COG(Chip on Glass)方式を用い、コントローラ11、音声処理回路39、メモリ21、CPU12または電源回路13を液晶パネル10に直接実装させるようにしても良い。また、プリント配線基板46には、容量素子、バッファ等の各種素子が設けられ、電源電圧や信号にノイズがのったり、信号の立ち上がりが鈍ったりすることを防いでいる。

【0135】

図22(B)は、図22(A)に示した液晶表示装置のブロック図を示す。この液晶表示装置は、メモリ21としてVRAM42、DRAM35、フラッシュメモリ36などが含まれている。VRAM42にはパネルに表示する画像のデータが、DRAM35には画像データまたは音声データが、フラッシュメモリには各種プログラムが記憶されている。

40

【0136】

電源回路13では、液晶パネル10、コントローラ11、CPU12、音声処理回路39、メモリ21、送受信回路14に与える電源電圧が生成される。またパネルの仕様によっては、電源回路13に電流源が備えられている場合もある。

【0137】

CPU12は、制御信号生成回路30、デコーダ31、レジスタ32、演算回路33、RAM34、CPU用のインターフェース45などを有している。インターフェース45

50

を介して C P U 1 2 に入力された各種信号は、一旦レジスタ 3 2 に保持された後、演算回路 3 3、デコーダ 3 1 などに入力される。演算回路 3 3 では、入力された信号に基づき演算を行ない、各種命令を送る場所を指定する。一方デコーダ 3 1 に入力された信号はデコードされ、制御信号生成回路 3 0 に入力される。制御信号生成回路 3 0 は入力された信号に基づき、各種命令を含む信号を生成し、演算回路 3 3 において指定された場所、具体的にはメモリ 2 1、送受信回路 1 4、音声処理回路 3 9、コントローラ 1 1 などに送る。

#### 【 0 1 3 8 】

メモリ 2 1、送受信回路 1 4、音声処理回路 3 9、コントローラ 1 1 は、それぞれ受けた命令に従って動作する。以下その動作について簡単に説明する。

#### 【 0 1 3 9 】

入力手段 4 1 から入力された信号は、インターフェース 1 9 を介してプリント配線基板 4 6 に実装された C P U 1 2 に送られる。制御信号生成回路 3 0 は、ポインティングデバイスやキーボードなどの入力手段 4 1 から送られてきた信号に従い、V R A M 4 2 に格納してある画像データを所定のフォーマットに変換し、コントローラ 1 1 に送付する。

#### 【 0 1 4 0 】

コントローラ 1 1 は、パネルの仕様に合わせて C P U 1 2 から送られてきた画像データを含む信号にデータ処理を施し、液晶パネル 1 0 に供給する。またコントローラ 1 1 は、電源回路 1 3 から入力された電源電圧や C P U 1 2 から入力された各種信号をもとに、H sync 信号、V sync 信号、クロック信号 C L K、交流電圧 ( A C C o n t ) 、切り替え信号 L / R を生成し、液晶パネル 1 0 に供給する。

#### 【 0 1 4 1 】

送受信回路 1 4 では、アンテナ 4 3 において電波として送受信される信号が処理されており、具体的にはアイソレータ、バンドパスフィルタ、V C O ( V o l t a g e C o n t r o l l e d O s c i l l a t o r ) 、L P F ( L o w P a s s F i l t e r ) 、カプラ、バランなどの高周波回路を含んでいる。送受信回路 1 4 において送受信される信号のうち音声情報を含む信号が、C P U 1 2 からの命令に従って、音声処理回路 3 9 に送られる。

#### 【 0 1 4 2 】

C P U 1 2 の命令に従って送られてきた音声情報を含む信号は、音声処理回路 3 9 において音声信号に復調され、スピーカー 3 8 に送られる。またマイク 3 7 から送られてきた音声信号は、音声処理回路 3 9 において変調され、C P U 1 2 からの命令に従って、送受信回路 1 4 に送られる。

#### 【 0 1 4 3 】

コントローラ 1 1 、C P U 1 2 、電源回路 1 3 、音声処理回路 3 9 、メモリ 2 1 を、本実施例のパッケージとして実装することができる。本実施例は、アイソレータ、バンドパスフィルタ、V C O ( V o l t a g e C o n t r o l l e d O s c i l l a t o r ) 、L P F ( L o w P a s s F i l t e r ) 、カプラ、バランなどの高周波回路以外であれば、どのような回路にも応用することができる。

#### 【 0 1 4 4 】

本実施例によれば、画面の縦横切り替えを容易に可能にすことができる、且つ、外部回路を複雑化することなく液晶表示装置を得ることができる。

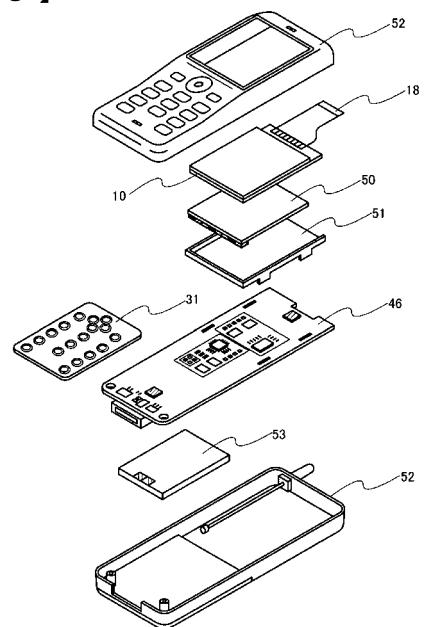

#### 【 0 1 4 5 】

図 2 3 は、この液晶表示装置を含む携帯電話機の一態様を示している。液晶パネル 1 0 はハウジング 5 1 に脱着自在に組み込んで液晶表示装置と容易に一体化できるようにしている。ハウジング 5 1 は組み入れる電子機器に合わせて、形状や寸法を適宜変更することができる。

#### 【 0 1 4 6 】

フィールドシーケンシャル駆動する液晶パネル 1 0 は、周期的に発光色が変化する発光源 5 0 と組み合わせられる。この発光源 5 0 は導光板と発光色の異なる発光ダイオードにより構成されている。また、有機 E L 素子、無機 E L 素子若しくは有機材料と無機材料と

10

20

30

40

50

の相乗効果を利用したコンポジット E L 素子を発光源 5 0 の光源に使っても良い。液晶パネル 1 0 と発光源 5 0 を固定したハウジング 5 1 はプリント配線基板 4 6 に嵌着されモジュールとして組み立てられる。

【 0 1 4 7 】

プリント配線基板 4 6 には、コントローラ、C P U、メモリ、電源回路、その他、抵抗、バッファ、容量素子等の素子が実装されている。さらに、用途に応じて、音声処理回路、送受信回路などが実装されていても良い。液晶パネル 1 0 はF P C 1 8 を介してプリント配線基板 4 6 に接続される。

【 0 1 4 8 】

このような液晶表示装置、入力手段 4 1 、バッテリ 5 3 は筐体 5 2 に収納される。液晶パネル 1 0 の画素部は筐体 5 2 に形成された開口窓から視認できよう配置されている。 10

【 0 1 4 9 】

この液晶パネル 1 0 は、フィールドシーケンシャル駆動をおこなうため、画素部における画素をR G B に分離する必要はない。したがって必要な信号線も少なくてすみ、開口率を飛躍的に大きくすることができます。また、カラーフィルタを省略することができるので、携帯電話機の軽量化と薄型化に寄与する。また、表示の向きを縦横に切り替えることができるので、筐体 5 2 の外形を自在に設計することができる。すなわち、図 2 3 は携帯電話機の外観形状を一例として示しているが、液晶表示装置を備えた電子機器としてさまざまな態様とすることができます。

【 実施例 6 】

【 0 1 5 0 】

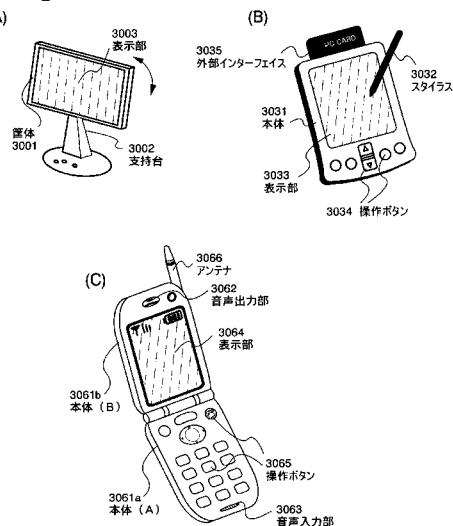

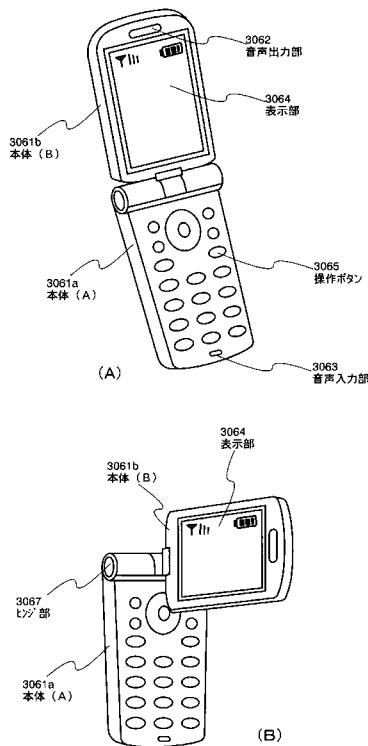

本発明は、実施例 5 で説明したように、様々な電子機器に用いられている表示装置の作製に適用が可能である。このような電子機器には、ディスプレイ装置、携帯情報端末（電子手帳、モバイルコンピュータ等）、携帯電話等が挙げられる。それらの一例を図 1 3 に示す。 20

【 0 1 5 1 】

図 1 3 ( A ) は液晶ディスプレイであり、筐体 3 0 0 1 、支持台 3 0 0 2 、表示部 3 0 0 3 等を有している。本発明は表示部 3 0 0 3 に適用が可能である。また、このような卓上据付型のディスプレイにおいて縦横表示切り替えを行う場合には、支持台 3 0 0 2 への筐体 3 0 0 1 の取り付け部に回転機構を設け、筐体 3 0 0 1 自体を回転可能にすると良い。 30

【 0 1 5 2 】

図 1 3 ( B ) は、携帯情報端末であり、本体 3 0 3 1 、スタイルス 3 0 3 2 、表示部 3 0 3 3 、操作ボタン 3 0 3 4 、外部インターフェース 3 0 3 5 等を有している。本発明は表示部 3 0 3 3 に適用が可能である。この携帯情報端末は、画面に表示するコンテンツに応じて、画像の縦横切り替えを容易にすることができます、且つ、高画質な表示をすることができる。 40

【 0 1 5 3 】

図 1 3 ( C ) は、携帯電話機であり、音声入力部 3 0 6 3 、操作ボタン 3 0 6 5 等が備えられた本体 ( A ) 3 0 6 1 a と、表示部 3 0 6 4 、音声出力部 3 0 6 2 、アンテナ 3 0 6 6 等を備えた本体 ( B ) 3 0 6 1 b を有している。本発明は表示部 3 0 6 4 に適用が可能である。この携帯電話は、画面に表示するコンテンツに応じて、画像の縦横切り替えを容易にすることができます、且つ、高画質な表示をすることができる。例えば、図 2 4 ( A ) ( B ) に示すように、本体 ( A ) 3 0 6 1 a と本体 ( B ) 3 0 6 1 b とを連結するヒンジ部 3 0 6 7 に回転機構を設け、本体 ( B ) 3 0 6 1 b 自体を回転可能にすると良い。ヒンジ部 3 0 6 7 にC C D などの撮像素子とレンズを設けてカメラを組み込んだときに便利に使用することができます。図 2 4 ( B ) に示すように、本体 ( B ) 3 0 6 1 b を回転させ、表示部 3 0 6 4 の画像表示を縦横切り替えることで、撮像しながらその画像を表示部 3 0 6 4 で視認することができます。 50

【 0 1 5 4 】

なお、本実施例に示した例はごく一例であり、これらの用途に限定するものではないことを付記する。

【図面の簡単な説明】

【0155】

【図1】本発明の一実施形態を示す図。

【図2】従来用いられている表示装置の概要を示す図。

【図3】縦横表示の切り替えの様子を説明する図。

【図4】縦横表示の切り替えにフレームメモリを用いる場合の処理の流れ、およびフォーマット変換について示す図。

【図5】表示装置を駆動する際のタイミングについて説明する図。

【図6】ソース信号線駆動回路の構成およびタイミングチャートを示す図。

【図7】ゲート信号線駆動回路の構成およびタイミングチャートを示す図。

【図8】通常表示と縦横切り替え表示における、映像信号の書き込み順を説明する図。

【図9】走査方向切り替え回路を有するゲート信号線駆動回路の構成を示す図。

【図10】縦横表示を切り替えた場合に表示装置を駆動する際のタイミングについて説明する図。

【図11】OCB液晶の構成を示す図。

【図12】本発明の一実施例である、独立した2組の駆動回路を有する表示装置の構成を示す図。

【図13】本発明の適用が可能な電子機器の一例を示す図。

【図14】分割駆動を行う場合のソース信号線駆動回路の構成を示す図。

【図15】分割駆動を行う表示装置において本発明を実施する場合の表示と映像信号の入力順序について説明する図。

【図16】アクティブマトリクス型液晶表示装置の作製工程例を示す図。

【図17】アクティブマトリクス型液晶表示装置の作製工程例を示す図。

【図18】アクティブマトリクス型液晶表示装置の作製工程例を示す図。

【図19】フィールドシーケンシャルを用いない場合の画素を示す図。

【図20】フィールドシーケンシャルを用いた場合の画素を示す図。

【図21】フィールドシーケンシャルのタイミングを示す図。

【図22】液晶表示装置の一態様を示す図。

【図23】液晶表示装置を含む携帯電話機の一態様を示す図。

【図24】携帯電話機の一態様を示す図。

【符号の説明】

【0156】

100 基板

101 画素

102 ソース信号線駆動回路

103 第1のゲート信号線駆動回路

104 第2のゲート信号線駆動回路

105 画素部

111 ソース信号線

112 ゲート信号線

113 ゲート信号線

114 画素 TFT

115 画素 TFT

116 液晶素子

117 保持容量

118 対向電極

10

20

30

40

【図1】

【図2】

【図3】

【図5】

【図4】

(B)

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

OCB (Optically Compensate Bend) モード液晶

【図12】

1211：第1のソース信号線

1212：第1のゲート信号線

1213：第2のソース信号線

1214：第2のゲート信号線

1215：第10画素TFT

1216：第20画素TFT

1217：液晶素子

1218：保持容量

1219：対向電極

【図13】

【図14】

1401：フリップフロップ

1402：シフトレジスタ

1403：NAND

1404：Latch

1405：サンプリングスイッチ

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

## フロントページの続き

(51)Int.Cl.

F I

テーマコード(参考)

G 0 9 G 3/20 6 2 1 K

G 0 9 G 3/20 6 6 0 F

H 0 1 L 29/78 6 1 2 B

G 0 2 F 1/133 5 5 0

F ターム(参考) 5C080 AA10 BB05 DD21 EE19 EE23 EE29 FF01 FF11 JJ02 JJ03

JJ04 JJ06 KK07 KK47

5F110 AA30 BB02 BB04 CC02 DD02 DD12 DD15 DD17 DD25 EE01

EE02 EE03 EE04 EE06 EE14 EE15 EE23 FF04 FF30 FF35

GG01 GG02 GG13 GG32 GG34 GG43 GG45 GG47 GG51 GG58

HJ01 HJ04 HJ12 HJ13 HJ23 HL03 HL04 HL06 HM13 HM15

NN03 NN04 NN23 NN24 NN27 NN35 NN72 NN73 NN78 PP01

PP02 PP03 PP04 PP05 PP10 PP13 PP29 PP34 PP35 QQ04

QQ09 QQ23 QQ28