(12)发明专利

(10)授权公告号 CN 106463505 B

(45)授权公告日 2020.05.08

(21)申请号 201580028026.X

(72)发明人 S·K·海因里希-巴纳

(22)申请日 2015.05.27

D·P·弗雷特 A·J·察奥

(65)同一申请的已公布的文献号

(74)专利代理机构 北京纪凯知识产权代理有限公司 11245

申请公布号 CN 106463505 A

代理人 徐东升 赵蓉民

(43)申请公布日 2017.02.22

(51)Int.Cl.

H01L 27/04(2006.01)

(30)优先权数据

H01C 1/028(2006.01)

14/287,434 2014.05.27 US

(85)PCT国际申请进入国家阶段日

(56)对比文件

2016.11.25

US 2005287756 A1,2005.12.29,

(86)PCT国际申请的申请数据

US 4757368 A,1988.07.12,

PCT/US2015/032690 2015.05.27

US 7141831 B1,2006.11.28,

(87)PCT国际申请的公布数据

US 7403094 B2,2008.07.22,

W02015/183964 EN 2015.12.03

审查员 韩冰

(73)专利权人 德克萨斯仪器股份有限公司

权利要求书3页 说明书8页 附图32页

地址 美国德克萨斯州

(54)发明名称

阱电阻和多晶硅电阻

(57)摘要

在所描述的示例中,包含阱电阻(110)的集成电路(100)具有在阱电阻(110)中的STI场氧化物(108)和电阻虚设有源区(118)。STI沟槽被蚀刻并填充有沟槽填充介电材料。沟槽填充介电材料通过CMP工艺被从有源区(118)的上方去除,留下STI沟槽中的STI场氧化物(108)。随后,掺杂剂被注入阱电阻区中的衬底(102)中以形成阱电阻(110)。

## 1. 一种集成电路,其包含:

衬底,其包含在所述衬底的顶表面处的半导体材料;

场氧化物,其由浅沟槽隔离工艺即STI工艺形成并被设置在所述衬底的所述顶表面处;

阱电阻,其被设置在所述场氧化物下方的所述半导体材料中;

电阻前端有源区,其被设置为穿过所述场氧化物与所述阱电阻两端相邻;以及

电阻虚设有源区,其被设置为穿过在所述阱电阻的区域中的所述场氧化物,所述电阻虚设有源区在所述衬底之上没有电连接,并且所述电阻虚设有源区具有10%至80%的密度;其中,在所述电阻虚设有源区下方的区域中,所述阱电阻的一部分在所述场氧化物之间延伸。

2. 根据权利要求1所述的集成电路,其中所述电阻虚设有源区具有20%至50%的密度。

3. 根据权利要求1所述的集成电路,其进一步包含在所述电阻虚设有源区中的重掺杂虚设扩散区,所述重掺杂虚设扩散区具有为所述阱电阻中的平均掺杂密度的至少10倍的平均掺杂密度,并且所述重掺杂虚设扩散区具有比所述场氧化物小的深度。

4. 根据权利要求3所述的集成电路,其中所述重掺杂虚设扩散区具有与所述阱电阻相反的导电类型。

5. 根据权利要求1所述的集成电路,其进一步包含在所述电阻前端有源区和所述电阻虚设有源区的顶表面上的金属硅化物层。

## 6. 一种集成电路,其包含:

衬底,其包含在所述衬底的顶表面处的半导体材料;

场氧化物,其由浅沟槽隔离工艺即STI工艺形成并被设置在所述衬底的所述顶表面处;

阱电阻,其被设置在所述场氧化物下方的所述半导体材料中;

电阻前端有源区,其被设置为穿过所述场氧化物与所述阱电阻两端相邻;以及

电阻虚设有源区,其被设置为穿过在所述阱电阻的区域中的所述场氧化物,所述电阻虚设有源区在所述衬底之上没有电连接,其中所述电阻虚设有源区被配置为多个矩形,使得每个所述矩形从与所述阱电阻的一侧相邻延伸到与所述阱电阻的相对一侧相邻。

## 7. 一种形成集成电路的方法,所述方法包含:

提供衬底,所述衬底包含在所述衬底的顶表面处的半导体材料;

在所述衬底上方形成化学机械抛光停止层即CMP停止层;

在所述CMP停止层上方形成STI掩膜,所述STI掩膜覆盖所述集成电路的有源区的区域,所述有源区包括在阱电阻的区域中的电阻前端有源区并且包括在所述阱电阻的区域中的电阻虚设有源区,并且所述电阻虚设有源区具有10%至80%的密度;

在由所述STI掩膜暴露的区域中去除所述CMP停止层并去除所述衬底的所述半导体材料的一部分,以便在所述衬底中形成250纳米至500纳米深的STI沟槽;

在所述STI沟槽中和所述有源区上方的所述CMP停止层上方形成一层沟槽填充介电材料,所述沟槽填充介电材料填充所述STI沟槽;

通过CMP工艺将所述沟槽填充介电材料向下平坦化至所述CMP停止层,其中所述CMP工艺从所述CMP停止层上方去除所有的所述沟槽填充介电材料并且不从所述电阻前端有源区和所述电阻虚设有源区去除任何所述半导体材料;

去除所述CMP停止层的剩余部分,其中所述STI沟槽中的所述沟槽填充介电材料形成所

述集成电路的场氧化物；

将阱掺杂剂穿过所述场氧化物注入在所述阱电阻的区域中的所述场氧化物下方的所述衬底的所述半导体材料中；

在阱退火工艺中加热所述衬底来激活所述阱掺杂剂以形成所述阱电阻，其中，在所述电阻虚设有源区下方的区域中，所述阱电阻的一部分在所述场氧化物之间延伸；以及

形成穿过所述电阻前端有源区向所述阱电阻提供电连接的接触件，其中所述电阻虚设有源区在所述衬底之上没有电连接。

8. 根据权利要求7所述的方法，其中所述电阻虚设有源区具有20%至50%的密度。

9. 根据权利要求7所述的方法，其进一步包含：

在所述衬底和所述场氧化物上方形成虚设区域注入掩膜以暴露所述电阻虚设有源区；

当所述虚设区域注入掩膜处于适当位置时在所述电阻虚设有源区中注入源/漏掺杂剂；

随后去除所述虚设区域注入掩膜；以及

执行退火操作来激活所述源/漏掺杂剂以形成所述电阻虚设有源区中的重掺杂虚设扩散区，所述重掺杂虚设扩散区具有为所述阱电阻中的平均掺杂密度的至少10倍的平均掺杂密度并且具有比所述场氧化物的深度小的深度。

10. 根据权利要求9所述的方法，其中所述重掺杂虚设扩散区具有与所述阱电阻相反的导电类型。

11. 根据权利要求7所述的方法，其进一步包含：

在所述电阻前端有源区和所述电阻虚设有源区的顶表面上形成难熔金属层；

加热所述衬底以在所述电阻前端有源区和所述电阻虚设有源区的所述顶表面处形成金属硅化物层；

随后从所述难熔金属层中去除未反应的难熔金属。

12. 根据权利要求7所述的方法，其中所述电阻虚设有源区被配置为多个矩形，使得每个所述矩形从与所述阱电阻的一侧相邻延伸到与所述阱电阻的相对一侧相邻。

13. 一种集成电路，其包含：

衬底，其包含在所述衬底的顶表面处的半导体材料；

场氧化物，其由STI工艺形成并被设置在所述衬底的所述顶表面处；

多晶硅电阻，其被设置在所述场氧化物上方，所述多晶硅电阻从CMP平坦化的多晶硅层形成；以及

电阻虚设有源区，其被设置为穿过所述多晶硅电阻的区域中的所述场氧化物，所述电阻虚设有源区在所述衬底之上没有电连接，并且所述电阻虚设有源区具有10%至80%的密度。

14. 根据权利要求13所述的集成电路，其中所述电阻虚设有源区不在所述多晶硅电阻下方延伸。

15. 根据权利要求13所述的集成电路，其中所述电阻虚设有源区在所述多晶硅电阻下方延伸，并且通过所述电阻虚设有源区的顶表面处的介电层与所述多晶硅电阻分离。

16. 根据权利要求13所述的集成电路，其中所述电阻虚设有源区具有20%至50%的密度。

17. 一种形成集成电路的方法,所述方法包含:

提供衬底,所述衬底包含在所述衬底的顶表面处的半导体材料;

在所述衬底上方形成CMP停止层;

在所述CMP停止层上方形成STI掩膜,所述STI掩膜覆盖所述集成电路的有源区的区域,所述有源区包括在多晶硅电阻的区域中的电阻虚设有源区,并且所述电阻虚设有源区具有10%至80%的密度;

在由所述STI掩膜暴露的区域中去除所述CMP停止层并去除所述衬底的所述半导体材料的一部分以便在所述衬底中形成250纳米至500纳米深的STI沟槽;

在所述STI沟槽中和所述有源区上方的所述CMP停止层上方形成沟槽填充介电材料层,所述沟槽填充介电材料填充所述STI沟槽;

通过CMP工艺将所述沟槽填充介电材料向下平坦化至所述CMP停止层,其中所述CMP工艺从所述CMP停止层上方去除所有所述沟槽填充介电材料并且不从所述电阻虚设有源区去除任何所述半导体材料;

去除所述CMP停止层的剩余部分,其中所述STI沟槽中的所述沟槽填充介电材料形成所述集成电路的场氧化物;

在所述场氧化物和所述电阻虚设有源区上方形成多晶硅层;

使用CMP工艺平坦化所述多晶硅层以形成CMP平坦化的多晶硅层;

在所述CMP平坦化的多晶硅层上方形成多晶硅蚀刻掩膜,所述多晶硅蚀刻掩膜限定所述多晶硅电阻;

在所述多晶硅蚀刻掩膜之外的区域中从所述CMP平坦化的多晶硅层去除多晶硅以形成所述多晶硅电阻;以及

形成向所述多晶硅电阻提供电连接的接触件,其中所述电阻虚设有源区在所述衬底之上没有电连接。

18. 根据权利要求17所述的方法,其中所述电阻虚设有源区不在所述多晶硅电阻下方延伸。

19. 根据权利要求17所述的方法,其中所述电阻虚设有源区在所述多晶硅电阻下方延伸,并且通过在所述电阻虚设有源区的顶表面处的介电层与所述多晶硅电阻分离。

20. 根据权利要求17所述的方法,其中所述电阻虚设有源区具有20%至50%的密度。

## 阱电阻和多晶硅电阻

### 技术领域

[0001] 本申请总体涉及集成电路，并且更具体地涉及集成电路中的电阻。

### 背景技术

[0002] 包含由浅沟槽隔离 (STI) 工艺制造的场氧化物的集成电路包括使用化学机械抛光 (CMP) 工艺的氧化物平坦化步骤。该 CMP 工艺过度抛光具有低有源区密度的大区域，例如电极区，从而在这些区域中产生具有不可预知厚度剖面的薄场氧化物。由于更多的注入掺杂剂穿过薄场氧化物，在过度抛光的场氧化物下制作的阱电阻具有低的不稳定的阻抗。过度抛光的场氧化物上的复晶硅（“多晶硅”）电阻（其中该多晶硅已经通过另一 CMP 工艺平坦化）趋于具有高的不稳定的厚度，其导致低的可变阻抗以及阻抗随温度的非期望变化。

### 发明内容

[0003] 在所描述的示例中，包含阱电阻的集成电路在阱电阻中具有 STI 场氧化物和电阻虚设 (dummy) 有源区。形成 STI 掩膜以覆盖阱电阻的区域中的电阻前端 (head) 有源区和电阻虚设有源区。在由 STI 掩膜暴露的区域蚀刻 STI 沟槽并填充沟槽填充介电材料。通过 CMP 工艺从有源区的上方去除沟槽填充介电材料，留下 STI 沟槽中的 STI 场氧化物。随后，将掺杂剂注入到阱电阻区域中的衬底中以形成阱电阻。

[0004] 在其他示例中，包含多晶硅电阻的集成电路在用于多晶硅电阻的区域中的 STI 场氧化物中具有电阻虚设有源区。在场氧化物上方形成多晶硅层并通过 CMP 工艺平坦化。多晶硅蚀刻工艺去除由多晶硅蚀刻掩膜暴露的区域中的多晶硅，留下多晶硅电阻。

### 附图说明

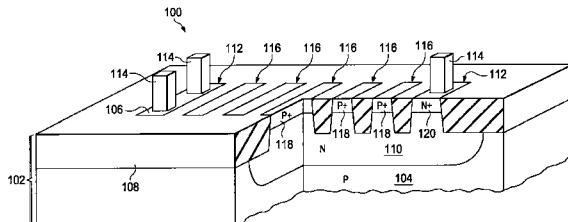

- [0005] 图1是包含阱电阻的示例集成电路的截面图。

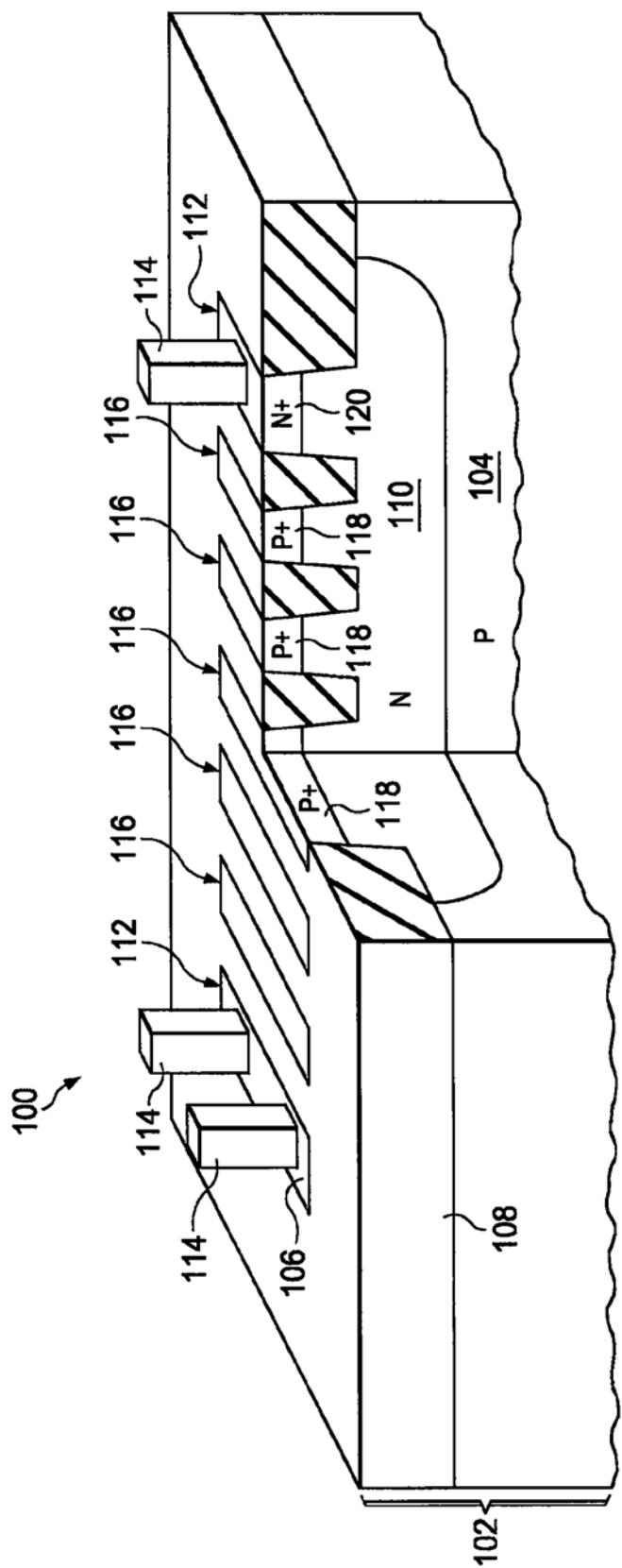

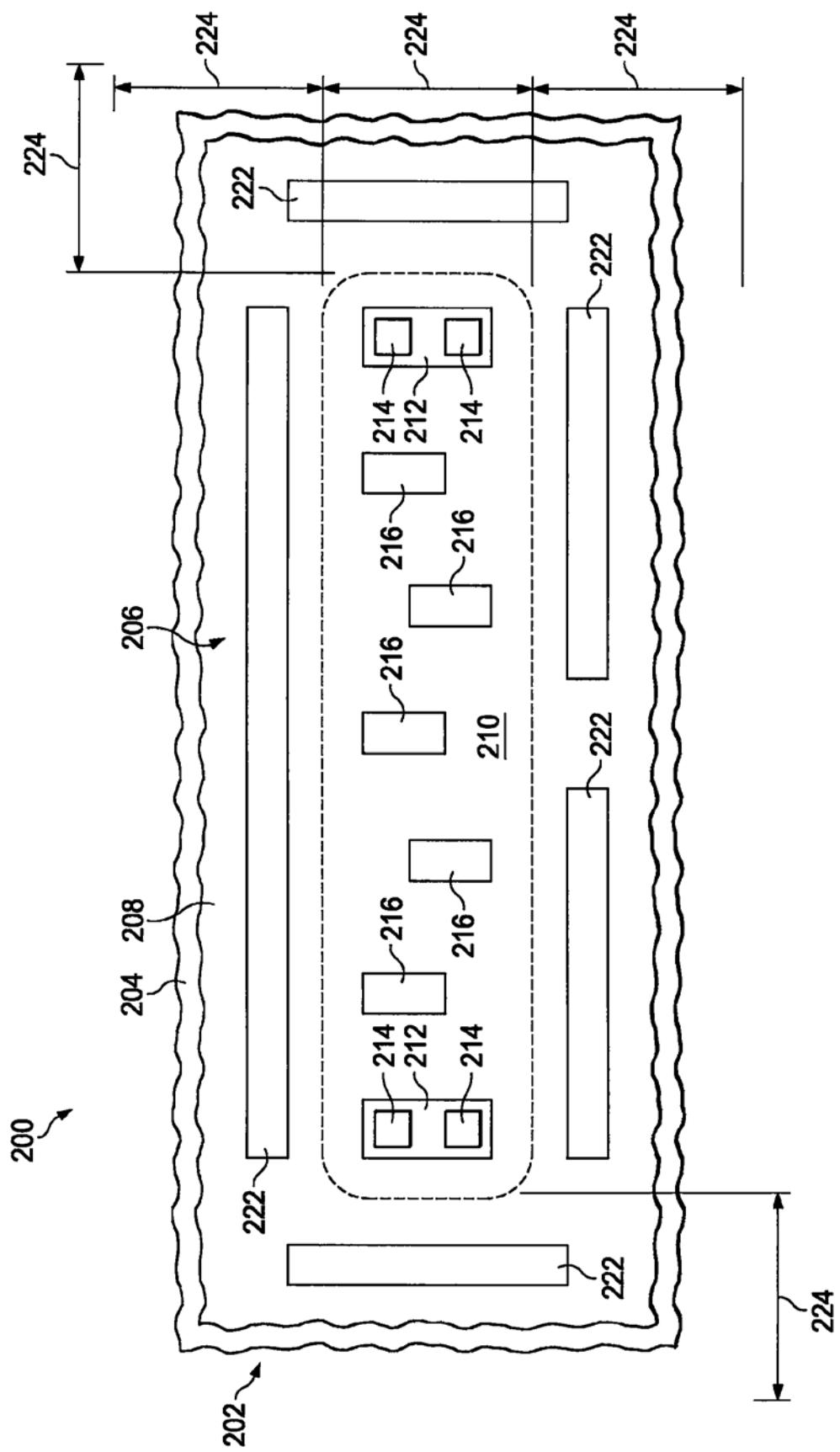

- [0006] 图2和图3是包含阱电阻的示例集成电路的俯视图。

- [0007] 图4A至图4L是以连续的制造阶段描绘的包含阱电阻的示例集成电路的截面图。

- [0008] 图5A至图5D是以连续的制造阶段描绘的包含阱电阻的另一示例集成电路的截面图。

- [0009] 图6A至图6C是以连续的制造阶段描绘的包含阱电阻的又一示例集成电路的截面图。

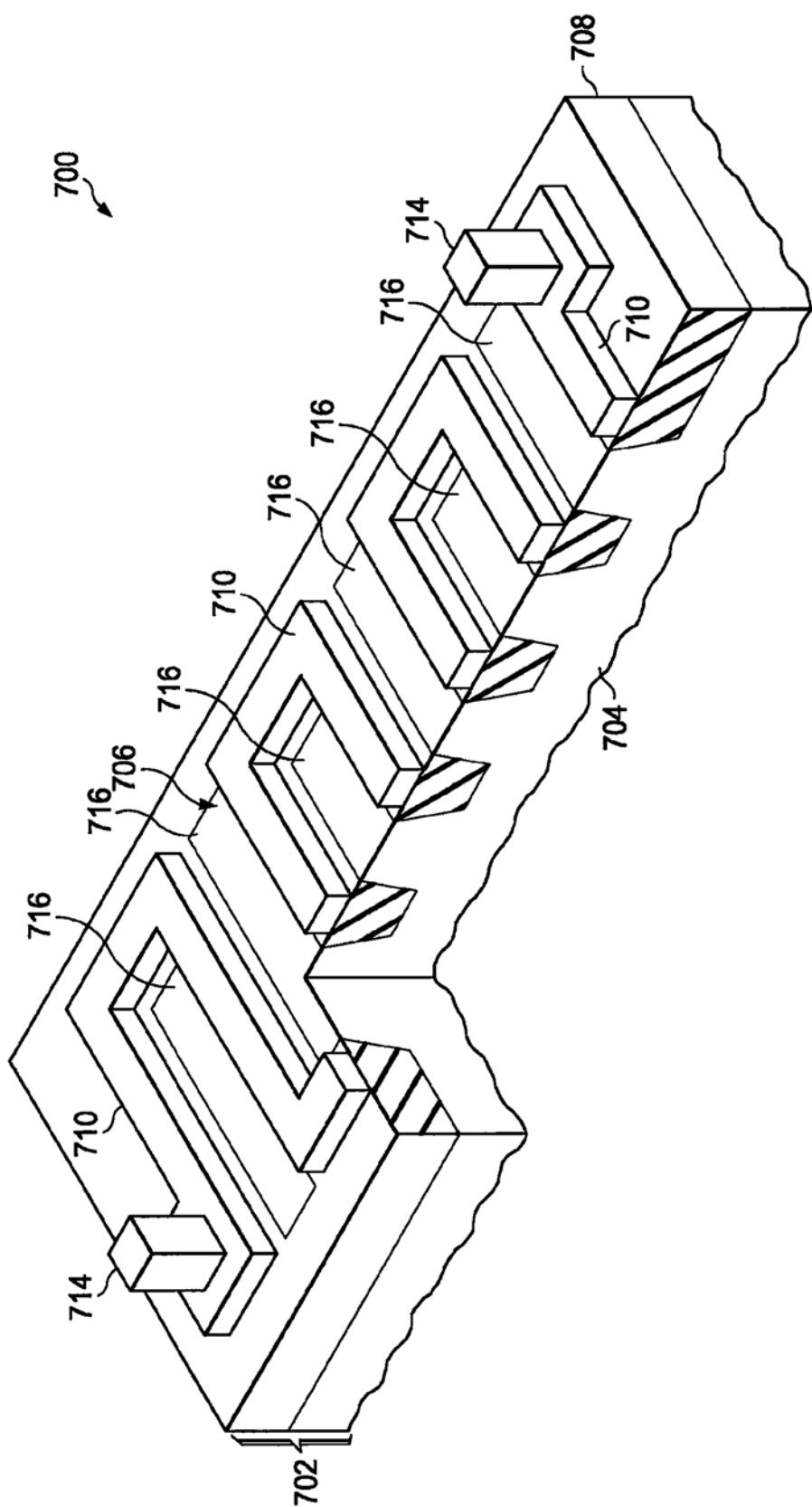

- [0010] 图7描绘包含多晶硅电阻的示例集成电路。图7A是图7的集成电路的截面图。

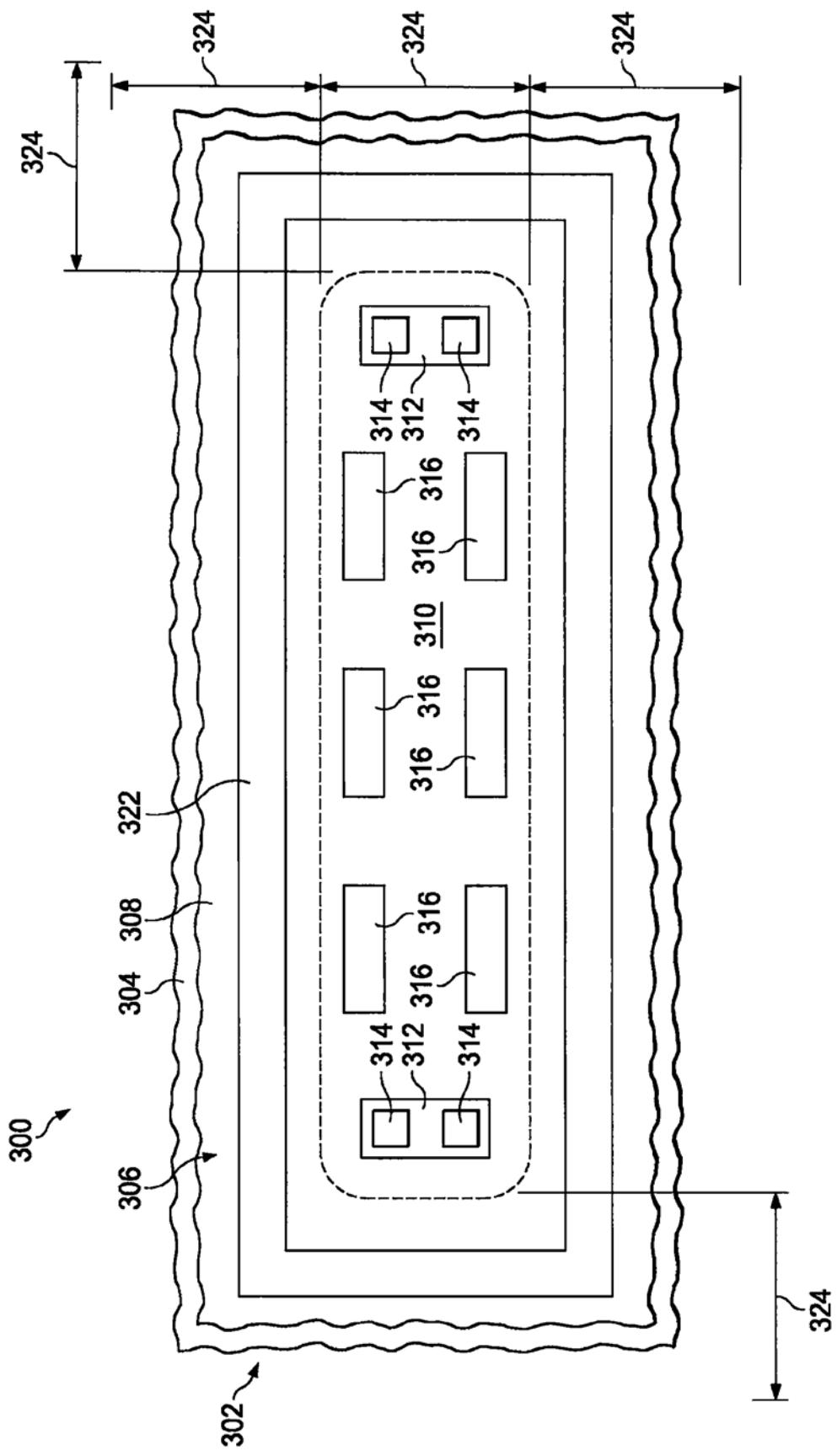

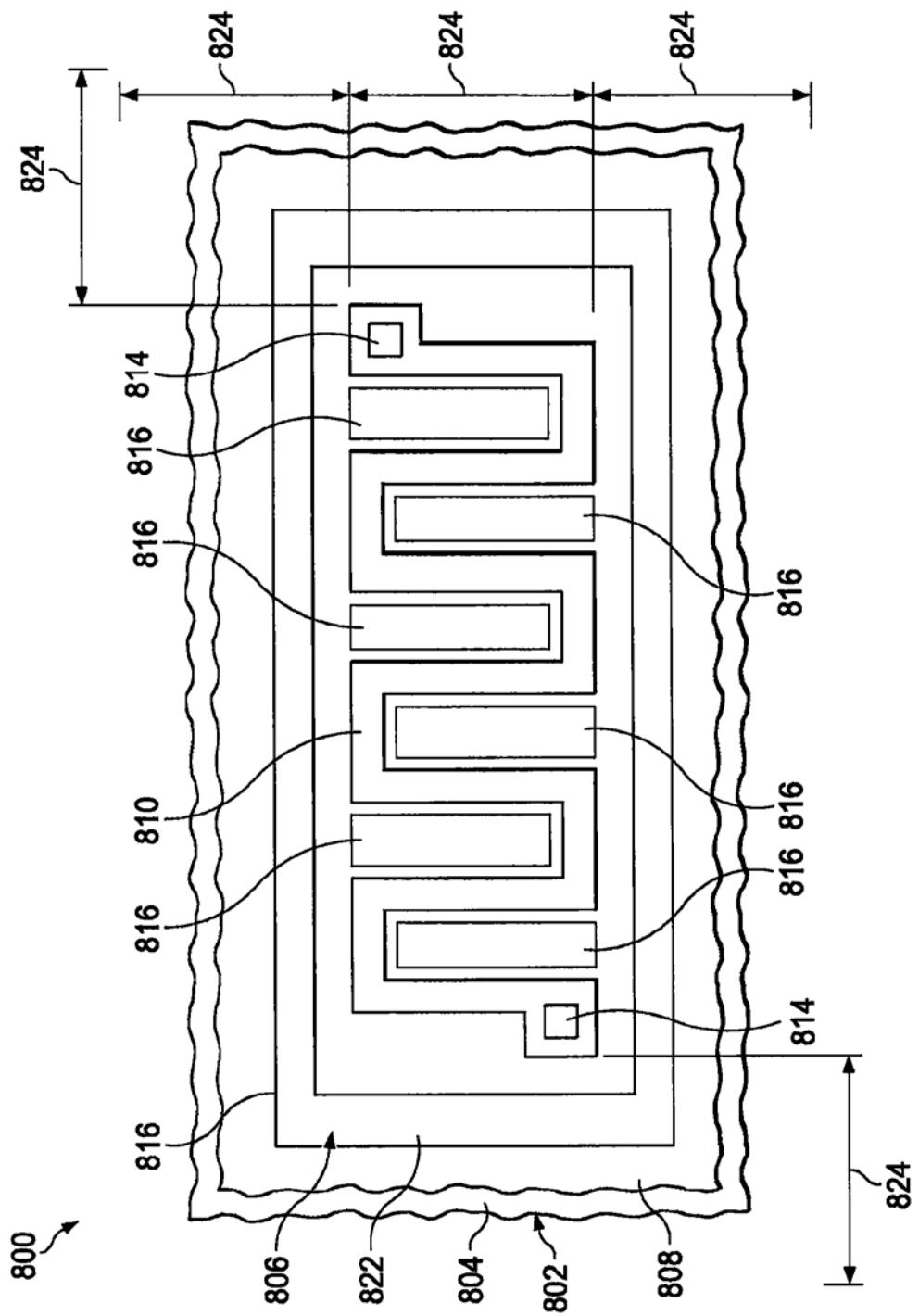

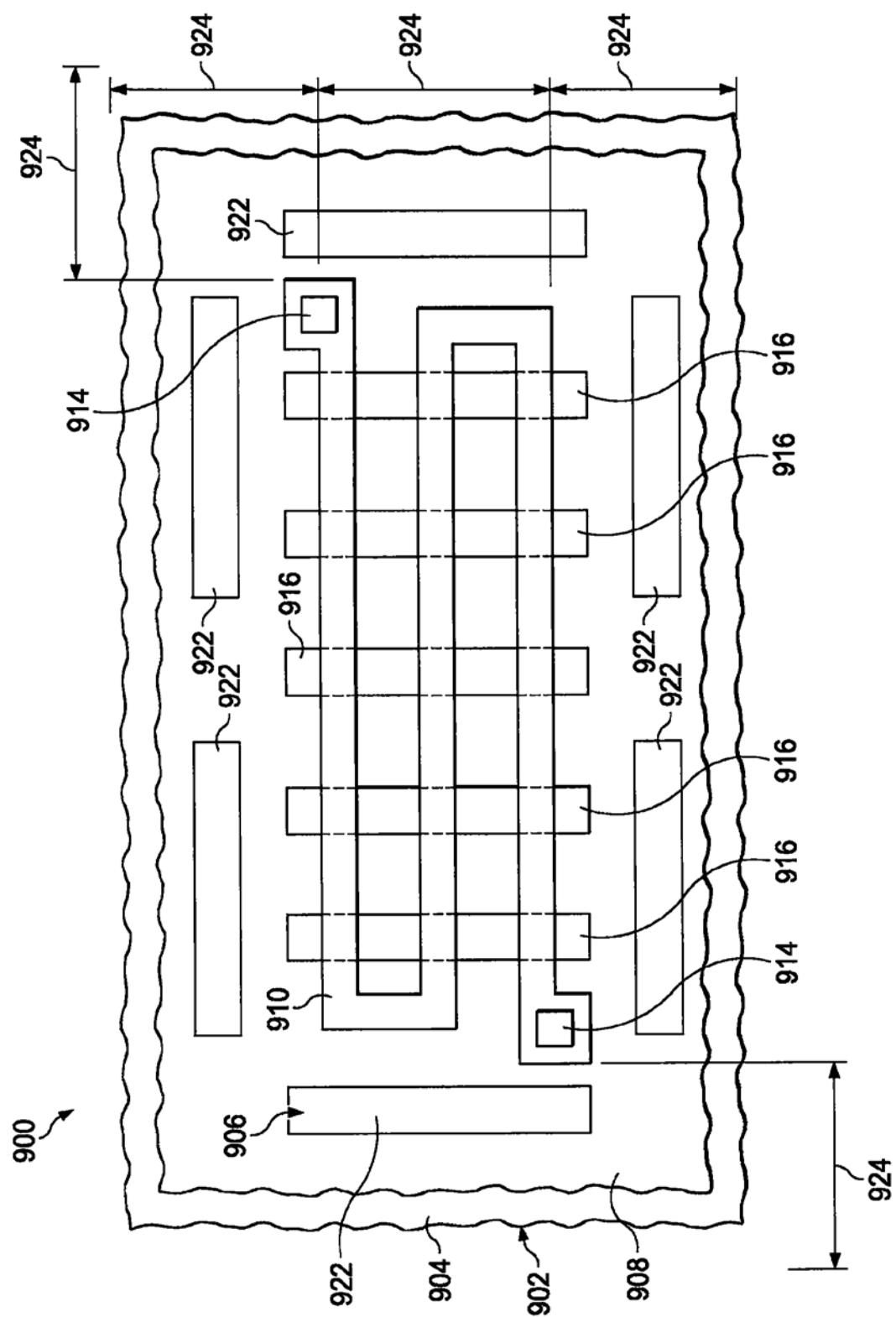

- [0011] 图8和图9是包含多晶硅电阻的示例集成电路的俯视图。

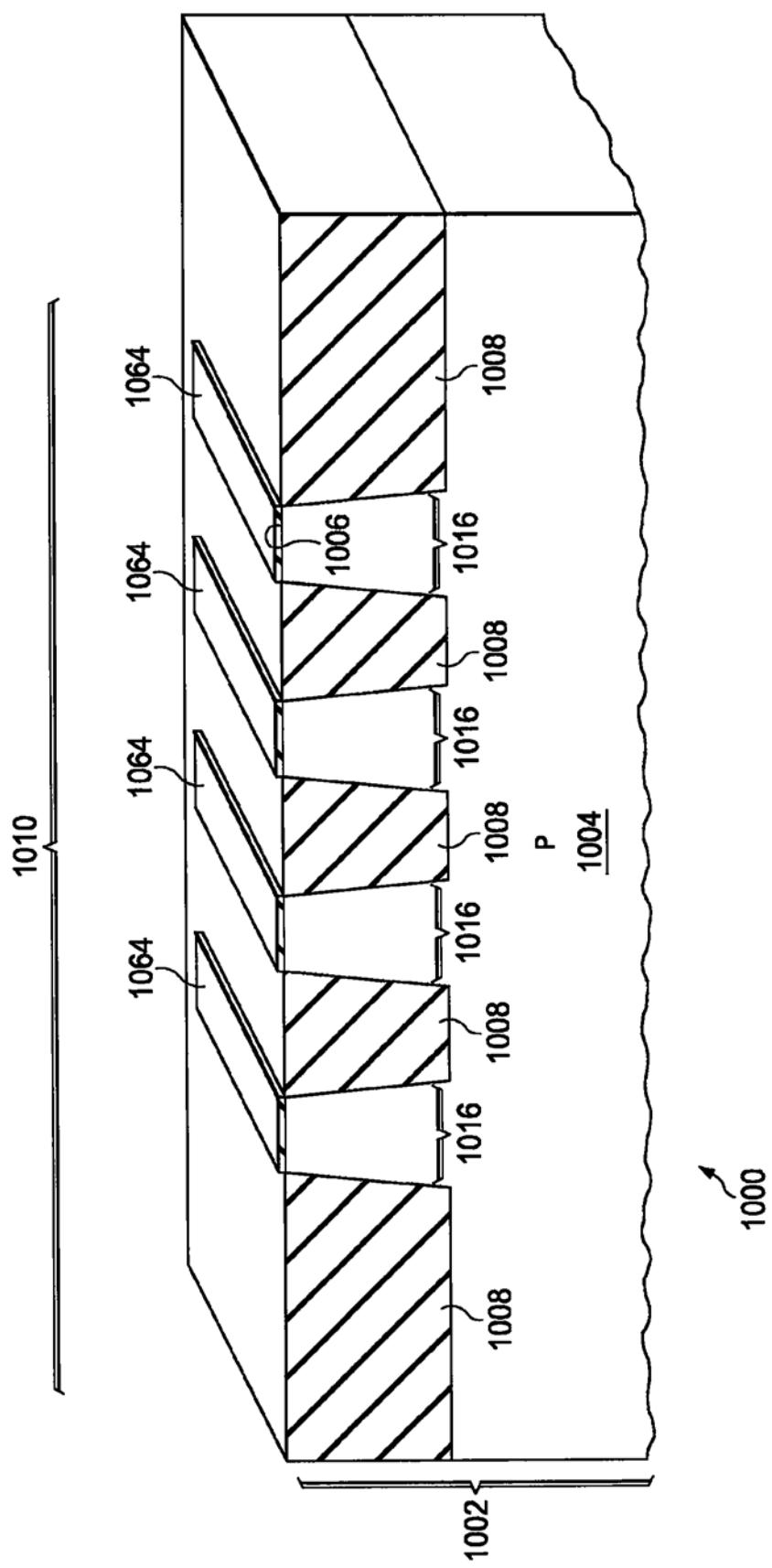

- [0012] 图10A至图10F是以连续的制造阶段描绘的包含多晶硅电阻的示例集成电路的截面图。

### 具体实施方式

[0013] 附图没有按比例绘制。图1是包含阱电阻的示例集成电路的截面图。集成电路100

形成在衬底102上,衬底102包括延伸到衬底102的顶表面106的半导体材料104。该示例将针对p型半导体材料104来描述。由STI工艺形成的场氧化物108被设置在衬底102的顶表面106处。n型阱电阻110被设置在场氧化物108下方的衬底102的半导体材料104中。阱电阻110中的示例平均掺杂密度可以是 $1 \times 10^{17} \text{ cm}^{-3}$ 至 $5 \times 10^{18} \text{ cm}^{-3}$ 。电阻前端有源区112被设置为穿过场氧化物108与阱电阻110的两端相邻。形成接触件114以便制作至电阻前端有源区112的电连接,有可能穿过金属硅化物层(图1中未示出)。形成场氧化物108以使得电阻虚设有源区116被设置为穿过阱电阻110的区域中的场氧化物108。电阻虚设有源区116在衬底102上方没有电连接。在该示例中,电阻虚设有源区被配置为多个矩形,使得每个矩形从与阱电阻的一侧相邻延伸到与阱电阻的相对一侧相邻。电阻虚设有源区116的密度是10%至80%。重掺杂虚设扩散区118可以被可选地形成在电阻虚设有源区116中。虚设扩散区118中的平均掺杂密度是阱电阻110中的平均掺杂密度的至少10倍。在该示例中,虚设扩散区118是p型,因此虚设扩散区118具有与阱电阻110相反的导电类型。重掺杂电阻前端接触区120可以被形成在具有与阱电阻110相同导电类型的电阻前端有源区112中。在阱电阻110的区域中形成具有10%至80%的密度的电阻虚设有源区116可以防止在STI工艺期间过度抛光场氧化物108,以有利地提供场氧化物的期望厚度,因此为阱电阻110提供期望阻抗。在该示例的一个版本中,电阻虚设有源区116的密度是20%至50%,以有利地提供更接近期望厚度的场氧化物108的厚度。在另一版本中,电阻虚设有源区116的密度是30%至35%,以有利地更进一步缩小场氧化物108的厚度范围。阱电阻110的实例的阻抗可以通过调节电阻虚设有源区116的横向尺寸和间距来调整。n型衬底中的p型阱电阻可以根据该示例通过掺杂剂和导电类型的适当变化来形成。此外,p型阱电阻可以通过在p型阱电阻下方形成隔离n型结构(例如,埋入层或深阱)而形成在p型衬底中。n型阱电阻可以类似地使用p型隔离结构形成在n型衬底中。

[0014] 图2和图3是包含阱电阻的示例集成电路的俯视图。参考图2,集成电路200被形成在衬底202上,衬底202包括延伸到衬底202的顶表面206的半导体材料204。由STI工艺形成的场氧化物208被设置在衬底202的顶表面206处。阱电阻210被设置在场氧化物208下方的半导体材料204中。电阻前端有源区212被设置为穿过场氧化物208与阱电阻210的两端相邻。形成接触件214以便制作至电阻前端有源区212的电连接。形成场氧化物208,使得电阻虚设有源区216被设置为穿过阱电阻210的区域中的场氧化物208。在该示例中,电阻虚设有源区216可以被配置为最小化对阱电阻210的阻抗的影响,同时维持电阻虚设有源区216的期望密度以提供场氧化物208的期望厚度。可选的周围虚设有源区222可以被设置为穿过在阱电阻210的区域的所有边上和外部的场氧化物208。周围虚设有源区222(如果有的话)在阱电阻210的宽度224内。如图2所示,周围虚设有源区222可以是分段的。在阱电阻210的宽度224内形成周围虚设有源区222可以有利地为场氧化物208的厚度提供更严格的工艺范围。

[0015] 参考图3,集成电路300被形成在衬底302上,衬底302包括延伸到衬底302的顶表面306的半导体材料304。由STI工艺形成的场氧化物308被设置在衬底302的顶表面306处。阱电阻310被设置在场氧化物308下方的半导体材料304中。电阻前端有源区312被设置为穿过场氧化物308与阱电阻310的两端相邻。形成接触件314以便制作至电阻前端有源区312的电连接。形成场氧化物,使得电阻虚设有源区316被设置为穿过阱电阻310的区域中的场氧化物308。在该示例中,电阻虚设有源区316可以被配置为平行于阱电阻310中的电流以提供对

阱电阻310的阻抗的更大调整能力,同时维持电阻虚设有源区316的期望密度以提供场氧化物308的期望厚度。可选的周围虚设有源区322可以被设置为穿过场氧化物308连续地包围阱电阻310的区域。周围虚设有源区322(如果有的话)在阱电阻310的宽度324内。在阱电阻310的宽度324内形成连续包围阱电阻310的周围虚设有源区322可以有利地为场氧化物308的厚度提供更严格的工艺范围,同时降低电阻虚设有源区316的密度。降低电阻虚设有源区316的密度对于减小阱电阻310的整体面积来说可能是合乎期望的。

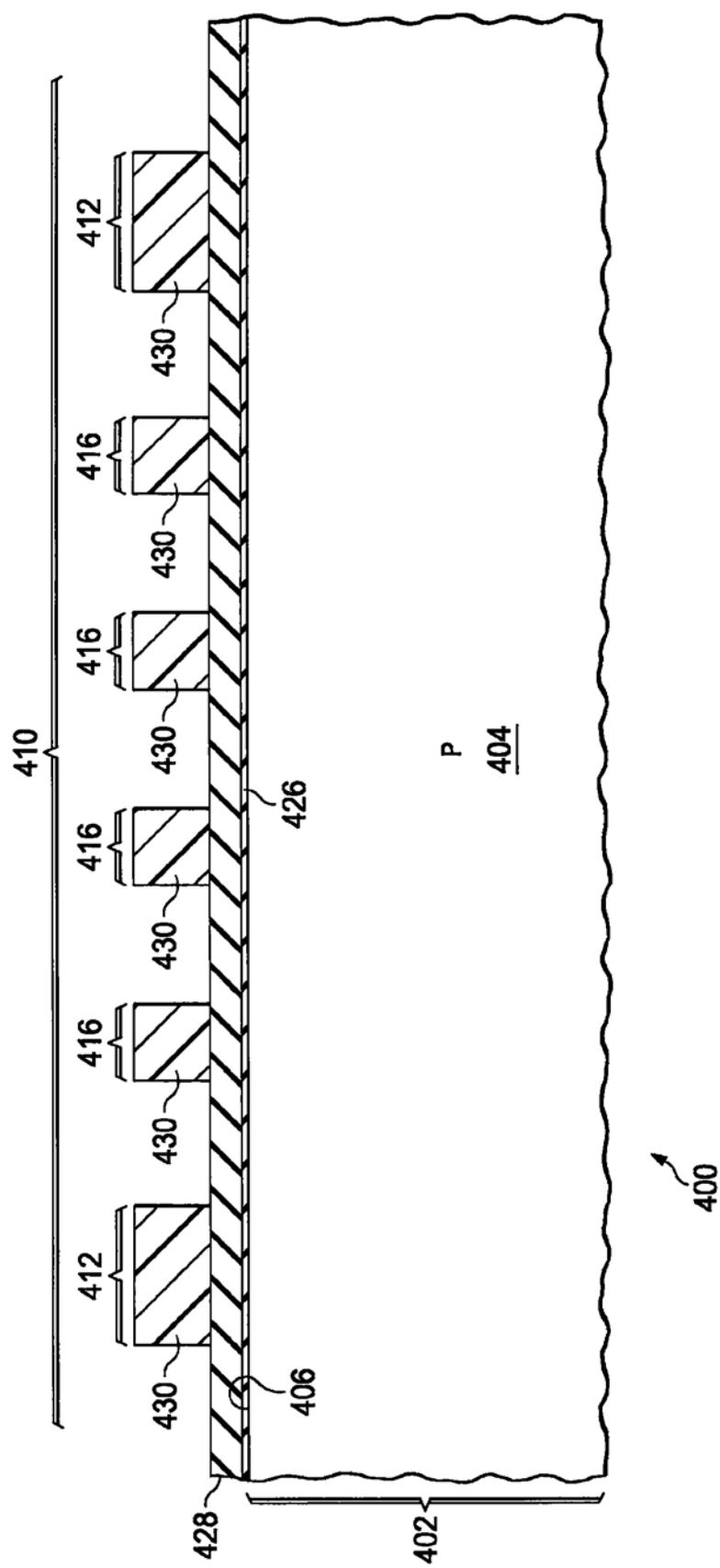

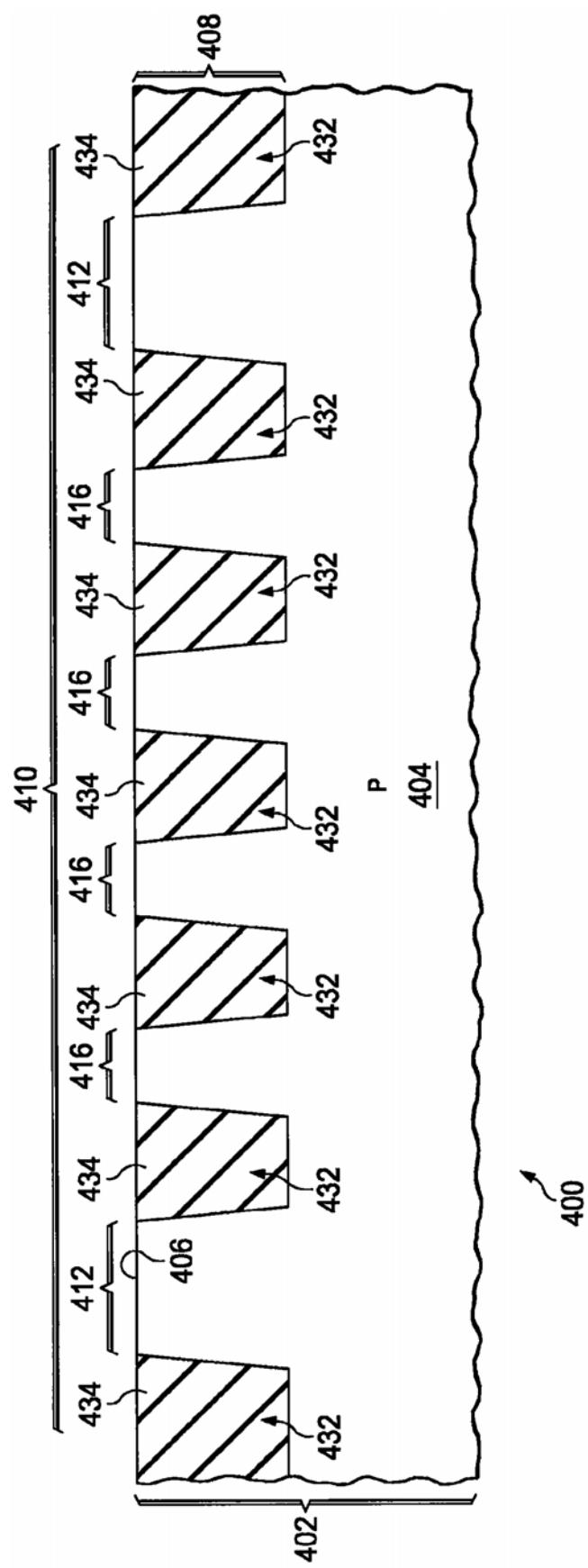

[0016] 图4A至图4L是以连续的制造阶段描绘的具有阱电阻的示例集成电路的截面图。参考图4A,集成电路400被形成在衬底402上,衬底402包括延伸到衬底402的顶表面406的半导体材料404。在该示例中,半导体材料404是p型的。厚度为5纳米至25纳米的二氧化硅的氧化物垫层426通过半导体材料404中硅的热氧化或通过沉积(例如通过使用也被称为四乙氧基硅烷(TEOS)的正硅酸四乙酯的等离子体增强化学气相沉积(PECVD))被形成在衬底402的顶表面406上方。厚度为50纳米到200纳米的氮化硅的CMP停止层428例如通过在700°C下使用硅烷或二氯甲硅烷和氨的低压化学气相沉积(LPCVD)工艺被形成在氧化物垫层426上方。STI掩膜430被形成在CMP停止层428上方以覆盖集成电路400中的有源区的区域,该区域包括阱电阻410的区域中的电阻前端有源区412的区域和电阻虚设有源区416的区域。STI掩膜430可以包括使用光刻工艺形成的光致抗蚀剂,并且可以可选地包括抗反射层和/或硬掩膜层。

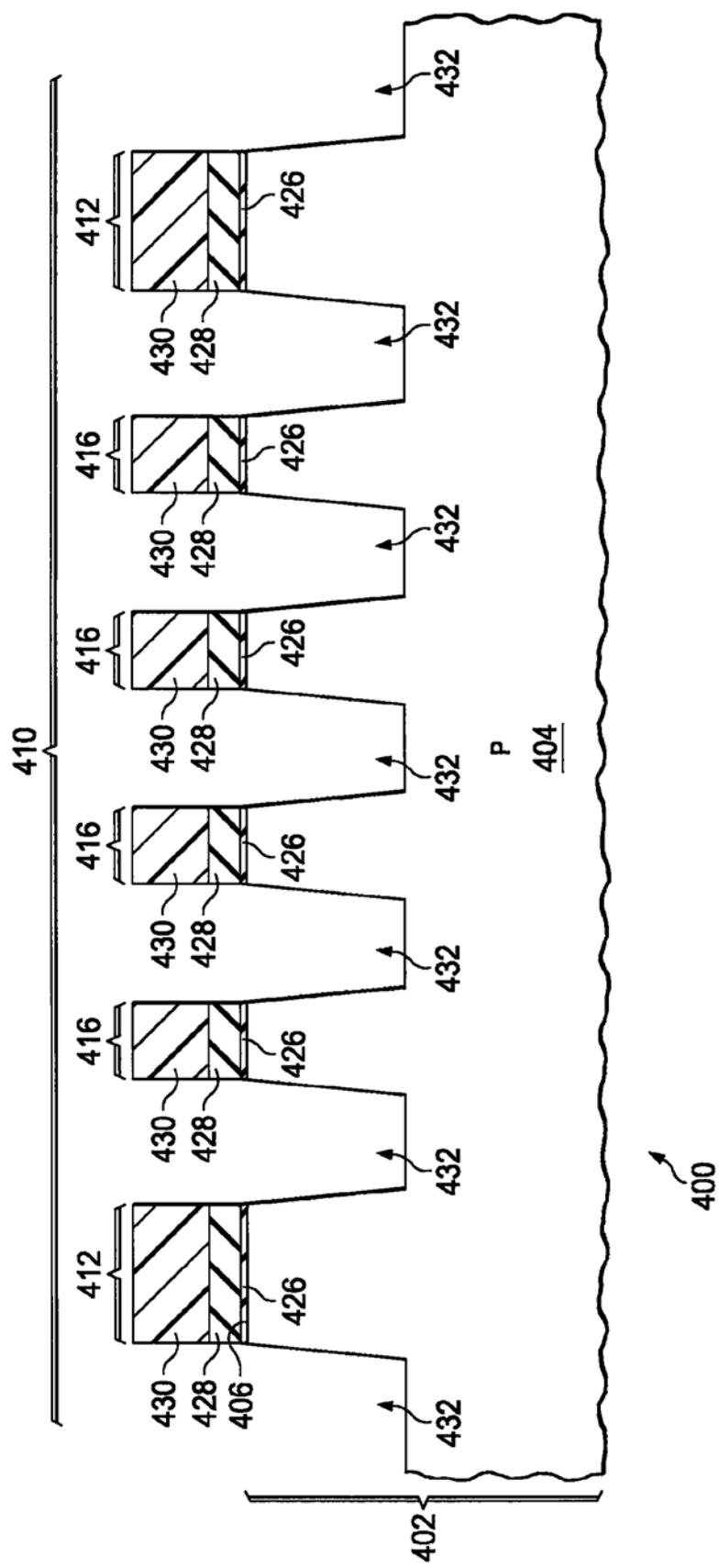

[0017] 参考图4B,STI沟槽蚀刻工艺去除在由STI掩膜430暴露的区域中的CMP停止层428和氧化物垫层426,并且蚀刻到半导体材料404中以在由STI掩膜430暴露的区域中形成深度为250纳米至500纳米的STI沟槽432。随后例如通过灰化工艺之后使用硫酸和过氧化氢的水混合物的湿法清洗步骤来去除STI掩膜430。在STI掩膜430被去除之后,可以通过半导体材料404中的硅的热氧化在STI沟槽432的侧壁上形成二氧化硅层(图4B中未示出)。

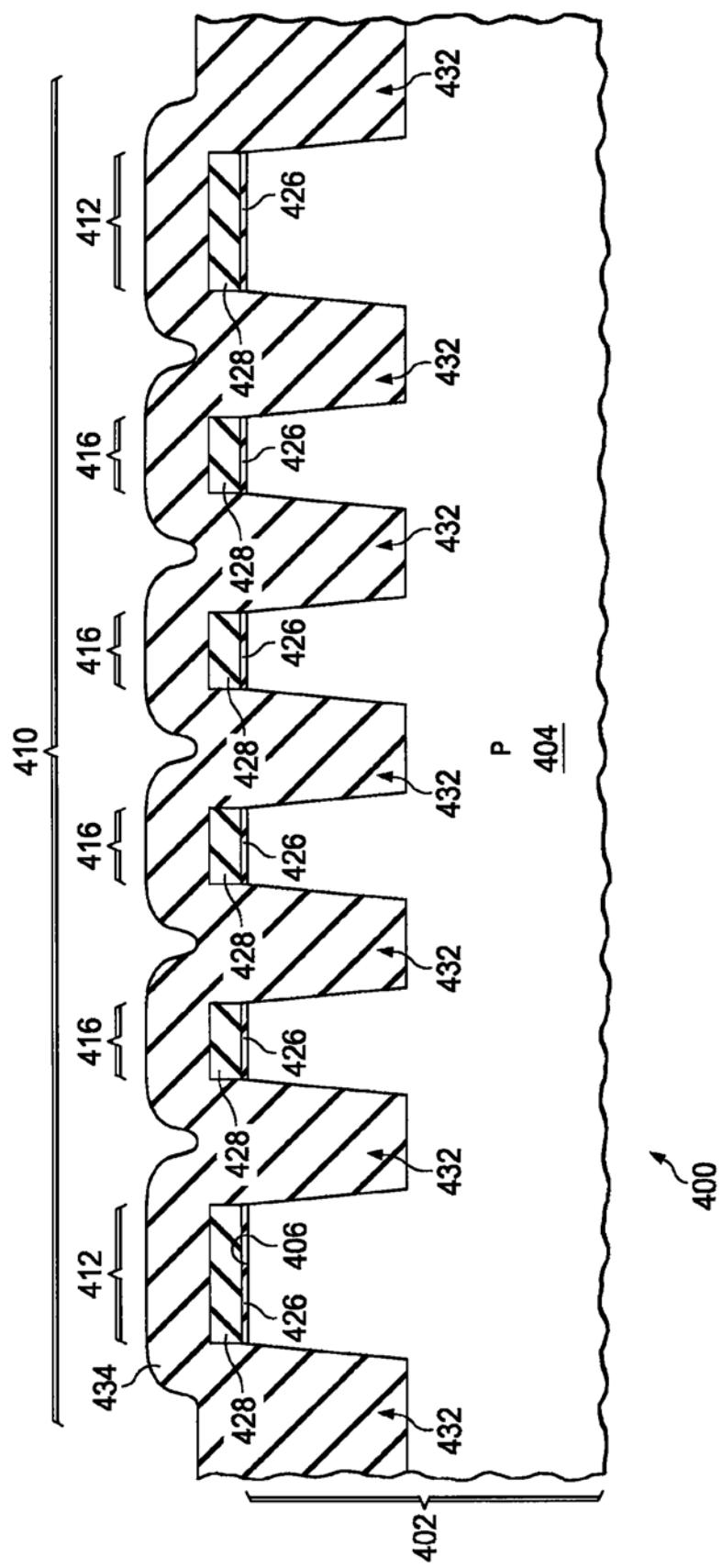

[0018] 参考图4C,沟槽填充介电材料层434被形成在STI沟槽432中以及在电阻前端有源区412的区域和电阻虚设有源区416的区域上方的CMP停止层428上方。沟槽填充介电材料434填充STI沟槽432。沟槽填充介电材料434可以主要包括二氧化硅,并且可以包括氮化硅层或氮氧化硅层。沟槽填充介电材料434可以形成在单个层中或形成在几个层中。可以在几个层的形成之间执行均厚蚀刻(blanket etch)工艺以减小CMP停止层428上方的沟槽填充介电材料434的厚度。沟槽填充介电材料434可以通过多种工艺形成,例如在450°C下使用硅烷和氧气的常压化学气相沉积(APCVD)工艺、在500°C下使用二氯甲硅烷和氧气的低于大气压的化学气相沉积(SAVCD)工艺、高密度等离子体(HDP)工艺或者基于臭氧的热化学气相沉积(VCD)工艺(也被称为高深宽比工艺(HARP))。随后可以通过在氮气或氧气环境中在900°C至1100°C下热退火至少30分钟来使沟槽填充介电材料434变得致密。

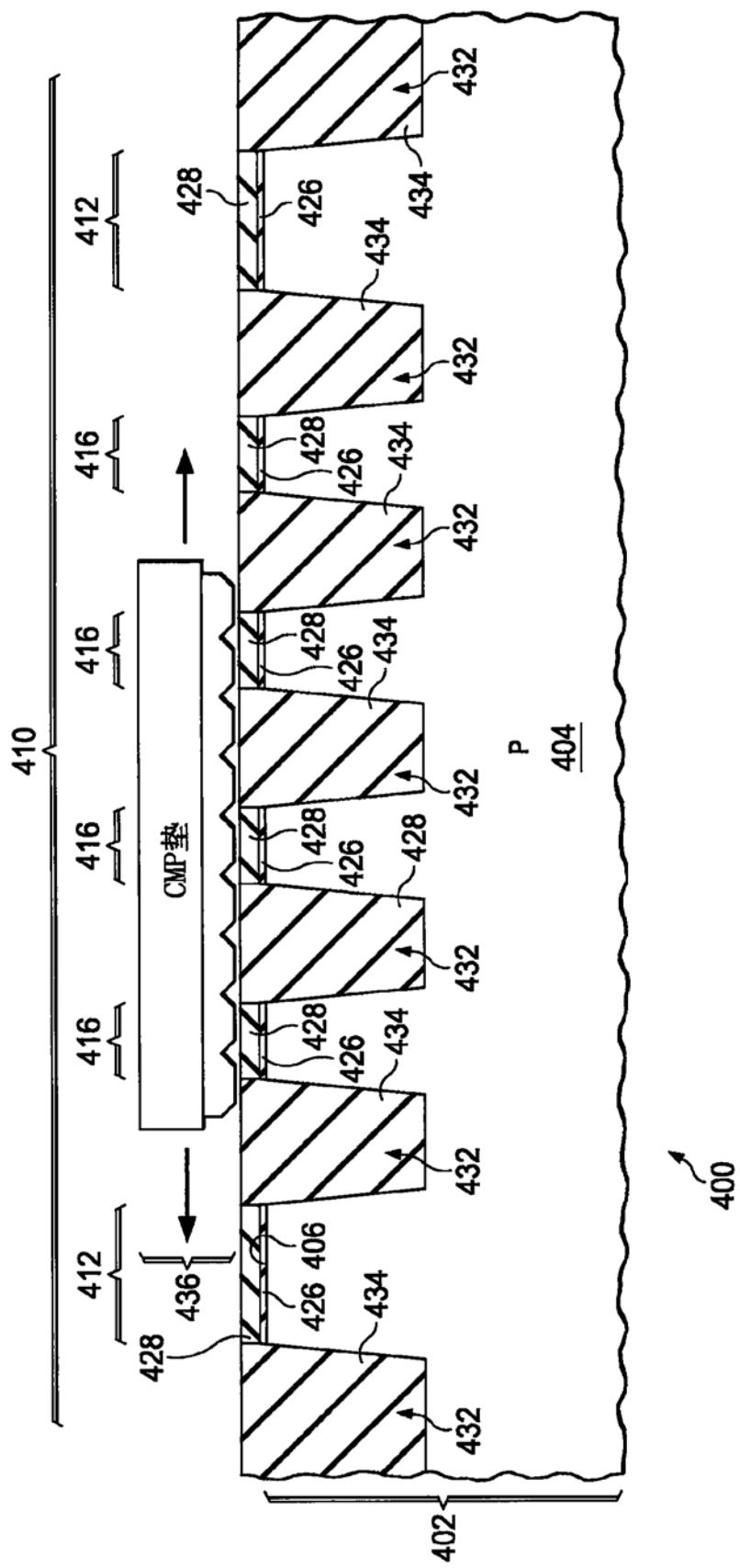

[0019] 参考图4D,沟槽填充介电材料434通过CMP工艺436(在图4D中以CMP垫436图示地描绘)被向下平坦化至CMP停止层428。电阻前端有源区412和电阻虚设有源区416上方的沟槽填充介电材料434对CMP垫436提供充分的阻抗以有利地防止阱电阻410的区域中的沟槽填充介电材料434的过度抛光。在该示例中,阱电阻410区域中的CMP停止层428上方的所有沟槽填充介电材料434都通过CMP工艺436被去除,并且没有半导体材料404通过CMP工艺436被从电阻前端有源区412和电阻虚设有源区416去除。

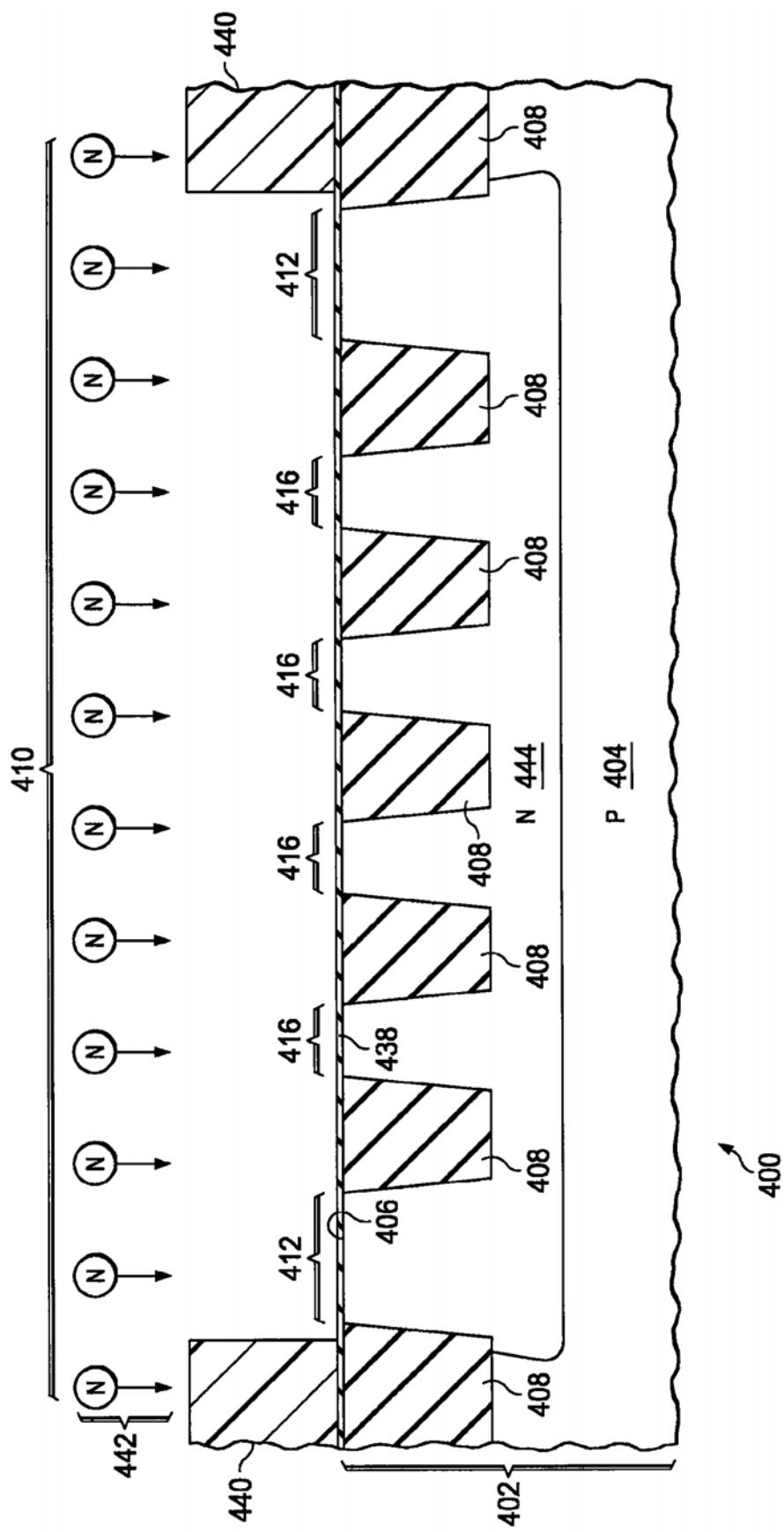

[0020] 参考图4E,图4D中的CMP停止层428的剩余部分被去除,留下STI沟槽432中的沟槽

填充介电材料434以便为集成电路400提供场氧化物408。并且,如图4E所示,氧化物垫层426可以可选地被去除。CMP停止层428可以在155°C下通过磷酸溶液去除。氧化物垫层426可以通过氢氟酸的稀释缓冲溶液去除。

[0021] 参考图4F,厚度为5纳米至15纳米的二氧化硅的第二氧化物垫层438可以形成在衬底402上方。如图4F所示,第二氧化物垫层438可以通过PECVD工艺在衬底402和场氧化物408上方沉积均厚的(blanket)二氧化硅层来形成。可替代地,可以通过在衬底402的顶表面406处的半导体材料404中的硅的热氧化在包括电阻前端有源区412和电阻虚设有源区416的集成电路400的有源区上方形成第二氧化物垫层438。阱注入掩膜440被形成在衬底402和场氧化物408上方以暴露阱电阻410的区域。阱注入掩膜440可以暴露集成电路400中的其他n型阱的区域,诸如p沟道金属氧化半导体(PMOS)晶体管下方的n型阱,这有利地降低了集成电路400的制造成本和制造复杂性。n型掺杂剂442(诸如磷)被注入到衬底402中由阱注入掩膜440暴露的区域以便在衬底102的半导体材料404中形成阱注入区444。n型掺杂剂442可以以 $1 \times 10^{13} \text{ cm}^{-2}$ 至 $1 \times 10^{14} \text{ cm}^{-2}$ 的剂量以及400keV至700keV的能量注入。阱注入区444在场氧化物408下方延伸。例如参考图4B的STI掩膜430所描述,随后阱注入掩膜440被去除。

[0022] 参考图4G,执行阱退火工艺,其扩散并激活图4F的阱注入区444中的注入的n型掺杂剂442以形成阱电阻410。在该示例的一个版本中,阱退火工艺可以包括在800°C至900°C下熔炉退火30分钟至2小时。在可替代的版本中,阱退火可以包括在1025°C至1060°C下快速热处理器退火20秒至60秒。阱电阻410的薄层阻抗可以是100Ω/□到1000Ω/□。

[0023] 参考图4H,接触件注入掩膜446被形成在集成电路400的现有顶表面上方以暴露电阻前端有源区412。在该示例中,接触件注入掩膜446覆盖电阻虚设有源区416。接触件注入掩膜446还可以暴露集成电路400中的n沟道金属氧化物半导体(NMOS)中的n沟道源/漏(NSD)区的区域,这有利地降低了集成电路400的制造成本和制造复杂度。n型掺杂剂448(诸如磷和/或砷)被注入到电阻前端有源区412以形成接触件注入区450,接触件注入区450从衬底402的顶表面406延伸100纳米至300纳米的深度。接触件注入区450不延伸得像场氧化物408那么深。n型掺杂剂448可以以 $1 \times 10^{15} \text{ cm}^{-2}$ 至 $5 \times 10^{16} \text{ cm}^{-2}$ 的剂量和30keV至80keV的能量注入。诸如参考图4B的STI掩膜430所描述,接触件注入掩膜446随后被去除。

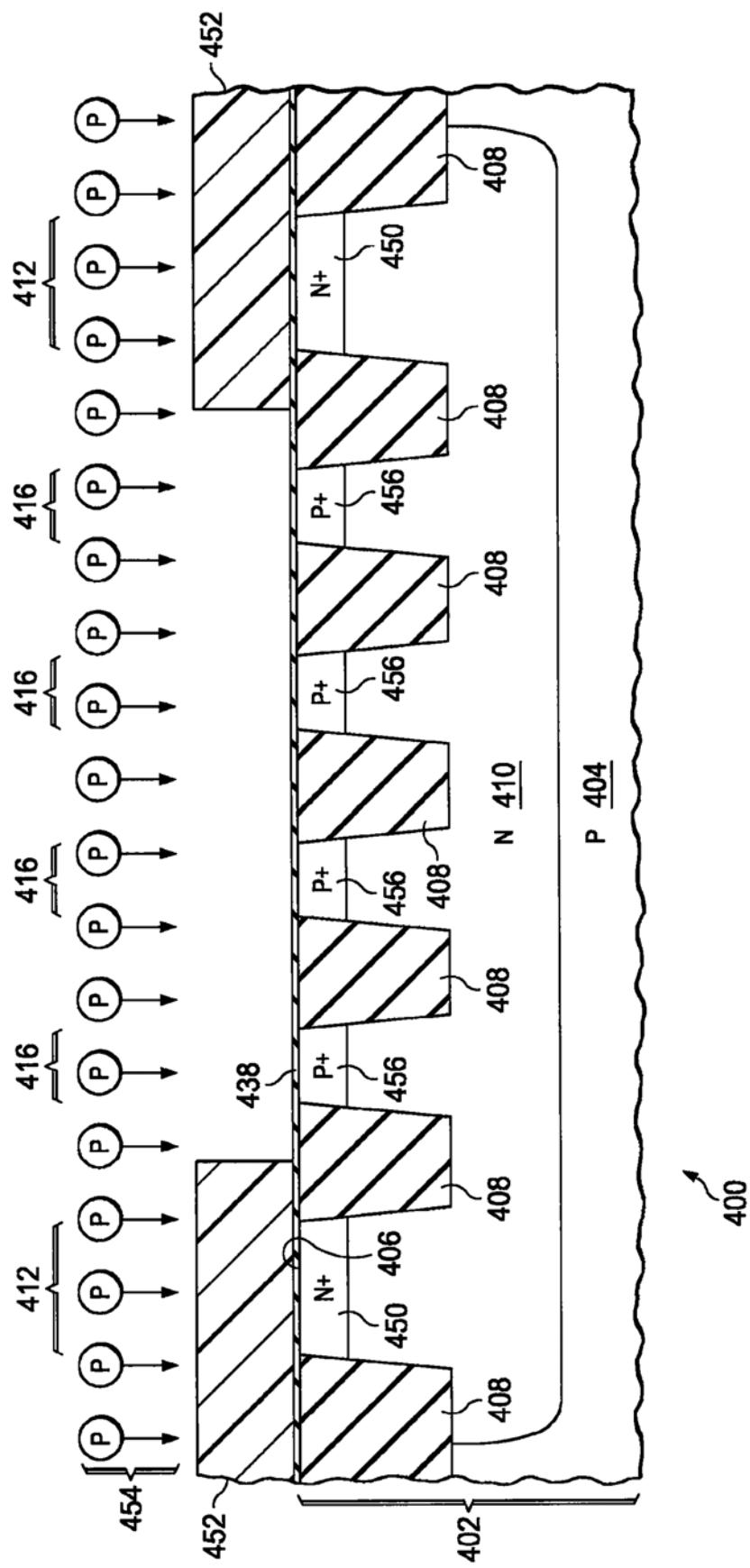

[0024] 参考图4I,虚设区注入掩膜452被形成在集成电路400的现有顶表面上方以暴露电阻虚设有源区416并覆盖电阻前端有源区412。虚设区注入掩膜452还可以暴露集成电路400中的PMOS晶体管中的p沟道源/漏(PSD)区的区域,这有利地降低了集成电路400的制造成本和制造复杂度。p型掺杂剂454(诸如硼)被注入到电阻虚设有源区416中以形成虚设注入区456,虚设注入区456从衬底402的顶表面406延伸至100纳米至300纳米的深度。虚设注入区456不延伸得像场氧化物408那么深。p型掺杂剂454可以以 $1 \times 10^{15} \text{ cm}^{-2}$ 至 $5 \times 10^{16} \text{ cm}^{-2}$ 的剂量和5keV至15keV的能量注入。诸如参考图4B的STI掩膜430所描述,虚设注入掩膜452随后被去除。

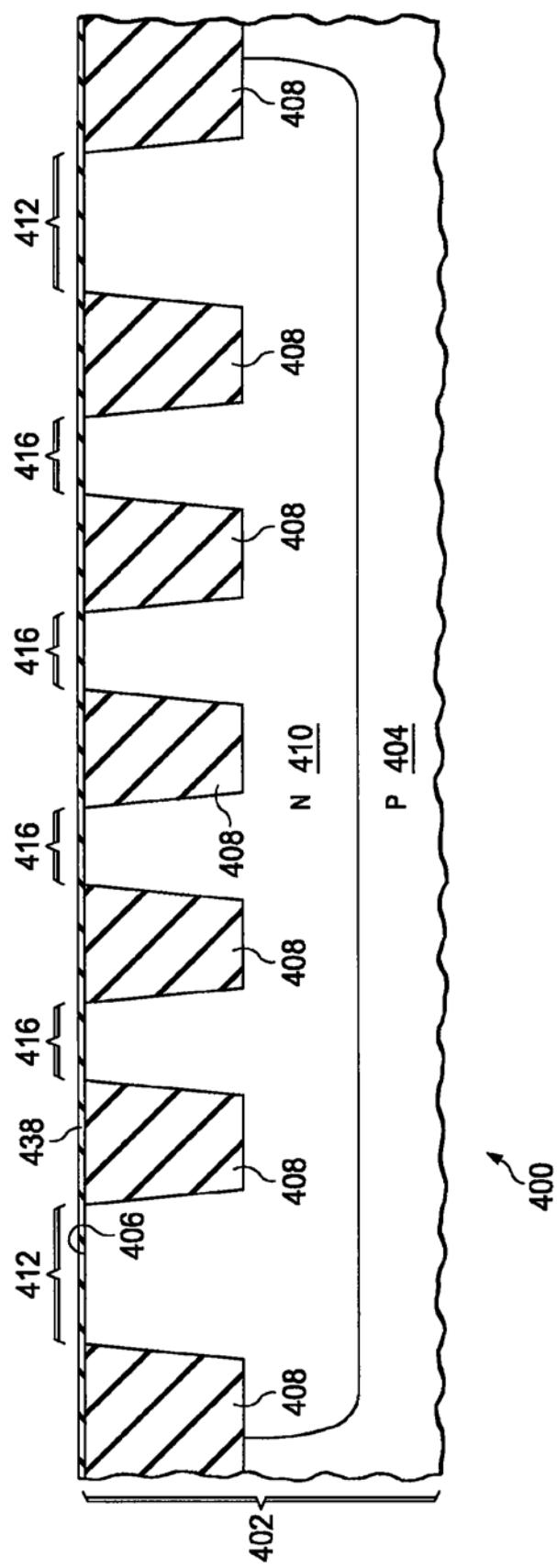

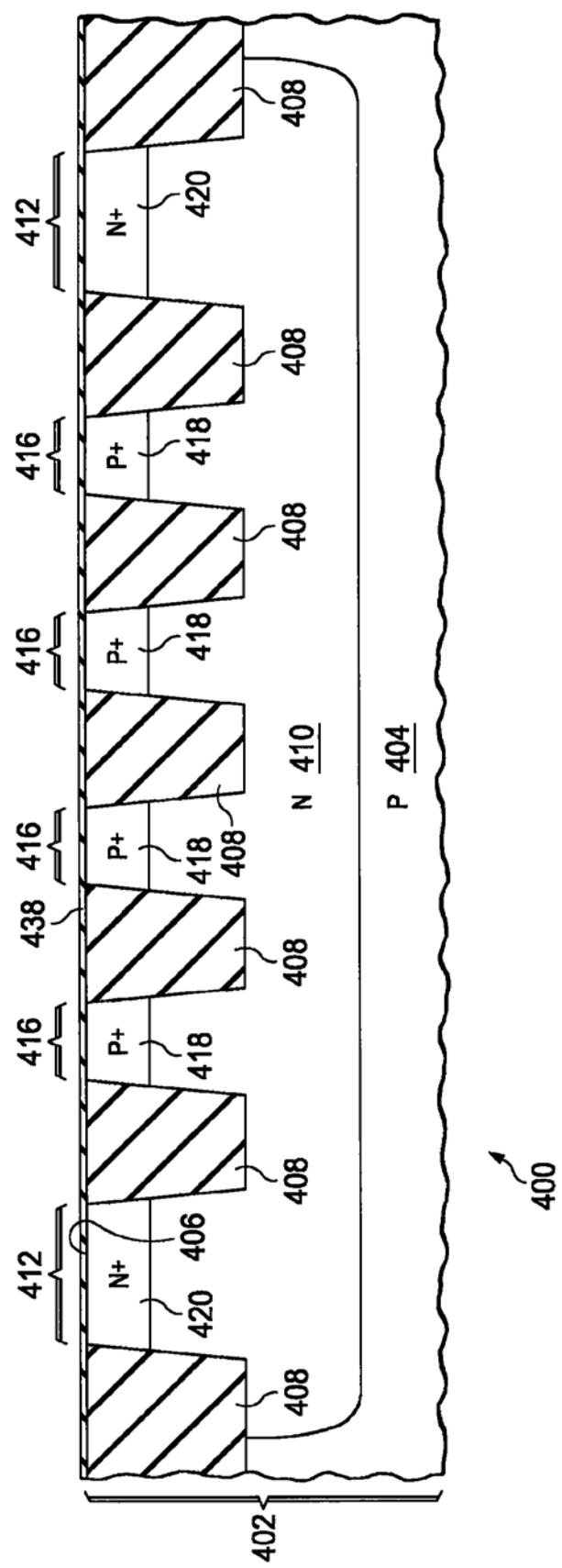

[0025] 参考图4J,执行退火操作,该退火操作在接触件注入区450中激活图4H中的注入的n型掺杂剂448以便在电阻前端有源区412中形成n型电阻前端接触区420,并在虚设注入区456中激活图4I中的注入的p型掺杂剂454以便在电阻虚设有源区416中形成p型虚设扩散区418。该退火操作可以包括在985°C至1025°C下快速热处理器退火10秒至30秒。虚设扩散区418和电阻前端接触区420都没有延伸得像场氧化物408那样深。

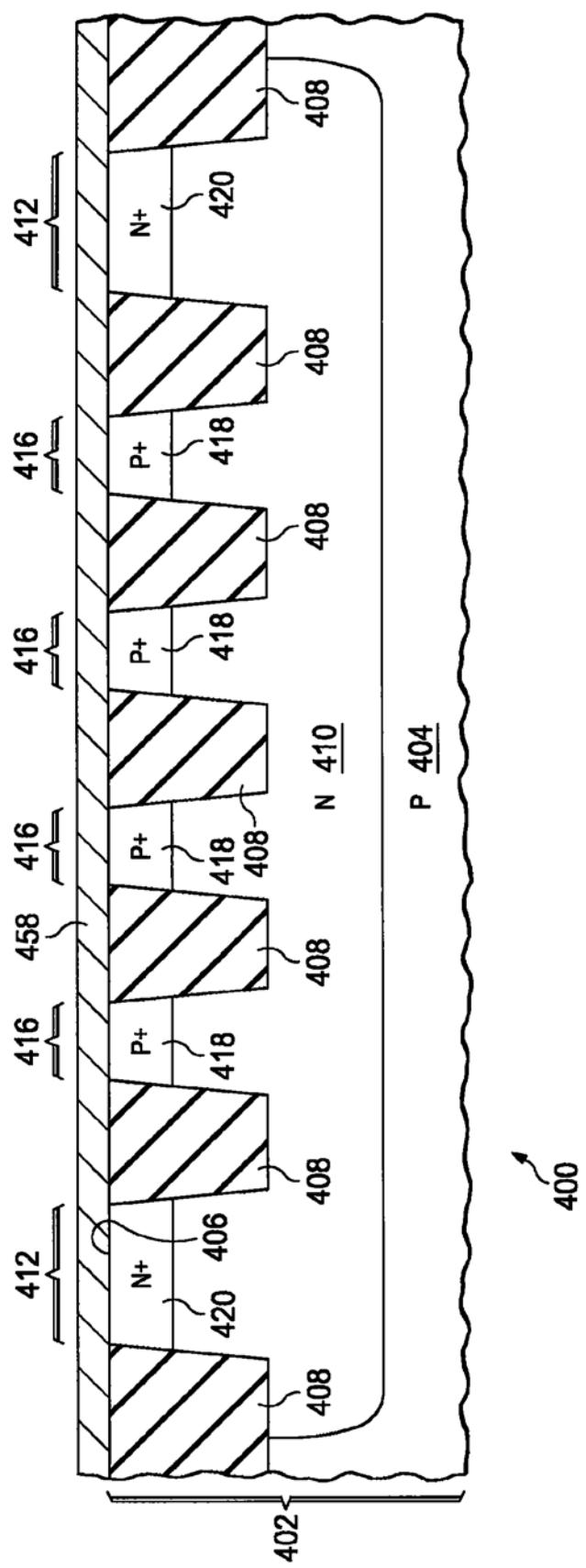

[0026] 参考图4K,通过诸如氢氟酸的稀释缓冲溶液以及随后的相继干法蚀刻(诸如Siconi蚀刻)去除介电材料(诸如图4J中的第二氧化物垫层438,其在电阻前端有源区412的顶表面406上,并且可能在电阻虚设有源区416上)。难熔金属层458形成在电阻前端有源区412上,并且可能形成在电阻虚设有源区416(如果暴露的话)上。例如,难熔金属层458可以包括铂、钛、钴、镍或钼,并且可以是5纳米至50纳米厚,并且可以可选地包括盖层。难熔金属层458可以通过溅射或通过金属有机化学气相沉积(MOCVD)工艺形成。

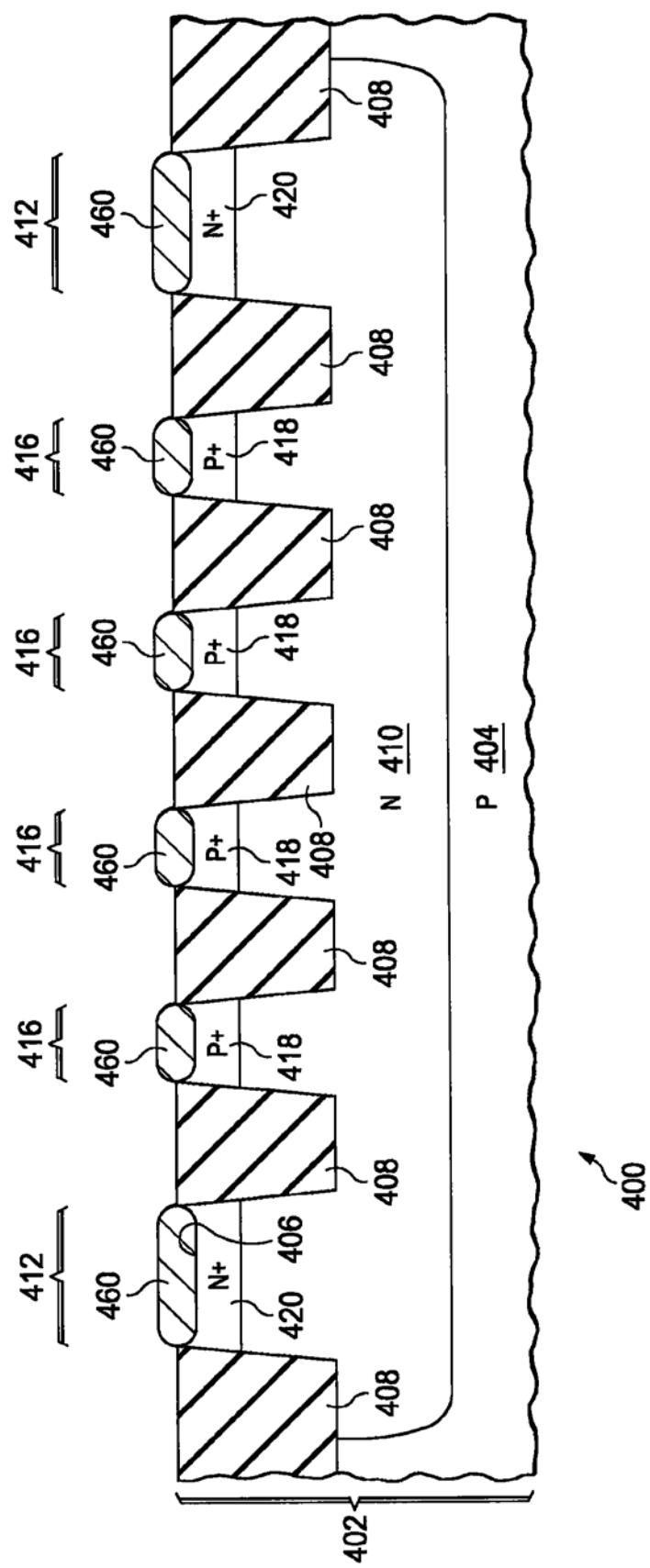

[0027] 参考图4L,加热衬底402,使得图4K的难熔金属层458中的难熔金属与衬底402的顶表面406处的电阻前端有源区412和电阻虚设有源区416中的硅反应,以在电阻前端有源区412和电阻虚设有源区416的顶部形成金属硅化物层460。形成金属硅化物层460所需要的温度取决于难熔金属层458中的具体难熔金属。随后,诸如通过使用硫酸和过氧化氢的混合物的湿法蚀刻去除难熔金属层458中未反应的难熔金属。金属硅化物层460和电阻前端接触区420有利地提供至阱电阻410的低阻抗连接。在电阻虚设有源区416上形成金属硅化物层460可以降低用于制造程序的制造成本和制造复杂度,该制造程序不包括硅化物阻挡层。继续集成电路400的制造,在金属硅化物层460上方形成金属前介电(PMD)层并且形成穿过PMD层的接触件,以便制作穿过金属硅化物层460和电阻前端连接区420至阱电阻410的电连接。

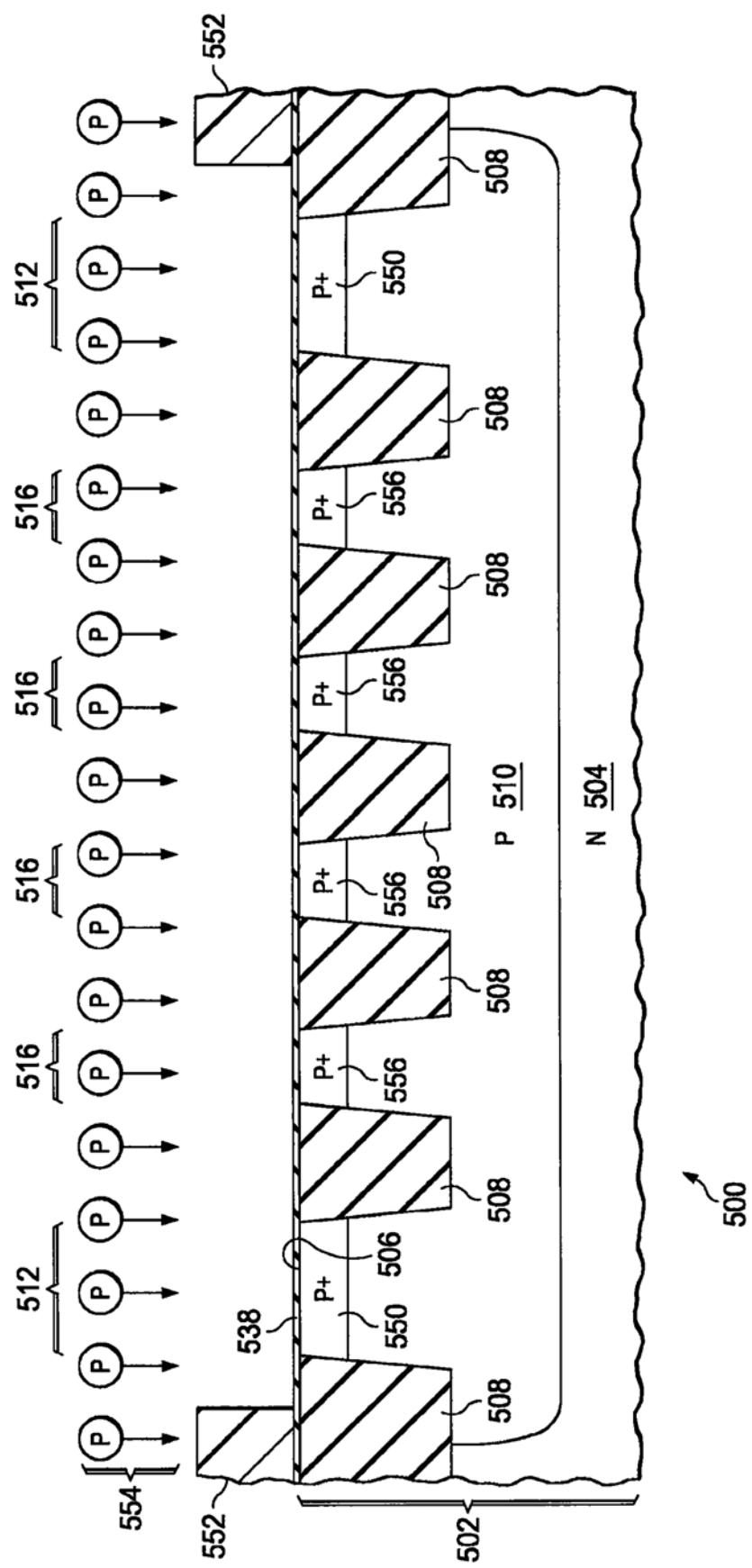

[0028] 图5A至图5D是以连续的制造阶段描绘的包含阱电阻的另一示例集成电路的截面图。参考图5A,集成电路500形成在衬底502上,衬底502包括延伸到衬底502的顶表面506的半导体材料504。在该示例中,半导体材料504是n型的。如参考图4A至图4E所描述,场氧化物508形成在衬底502中。集成电路500包括电阻前端有源区512和电阻虚设有源区516。氧化物垫层538(相当于图4F的第二氧化物垫层438)形成在衬底502上方。如参考图4F至图4G所描述,p型阱电阻510形成在场氧化物508下方的半导体材料504中,其中注入的掺杂剂适当地改变。组合式接触件/虚设注入掩膜552形成在集成电路500的现有顶表面上方以暴露电阻前端有源区512和电阻虚设有源区516。组合式接触件/虚设注入掩膜552还可以暴露集成电路500中的PMOS晶体管中的PSD区的区域,这有利地降低了集成电路500的制造成本和制造复杂度。如参考图4I所描述,p型掺杂剂554(诸如硼)被注入到电阻前端有源区512和电阻虚设有源区516中,以便在电阻前端有源区512中形成接触件注入区550并且在电阻虚设有源区516中形成虚设注入区556。接触件注入区550和虚设注入区556可以具有与图4I的虚设注入区456类似的性能。组合式接触件/虚设注入掩膜552随后被去除。

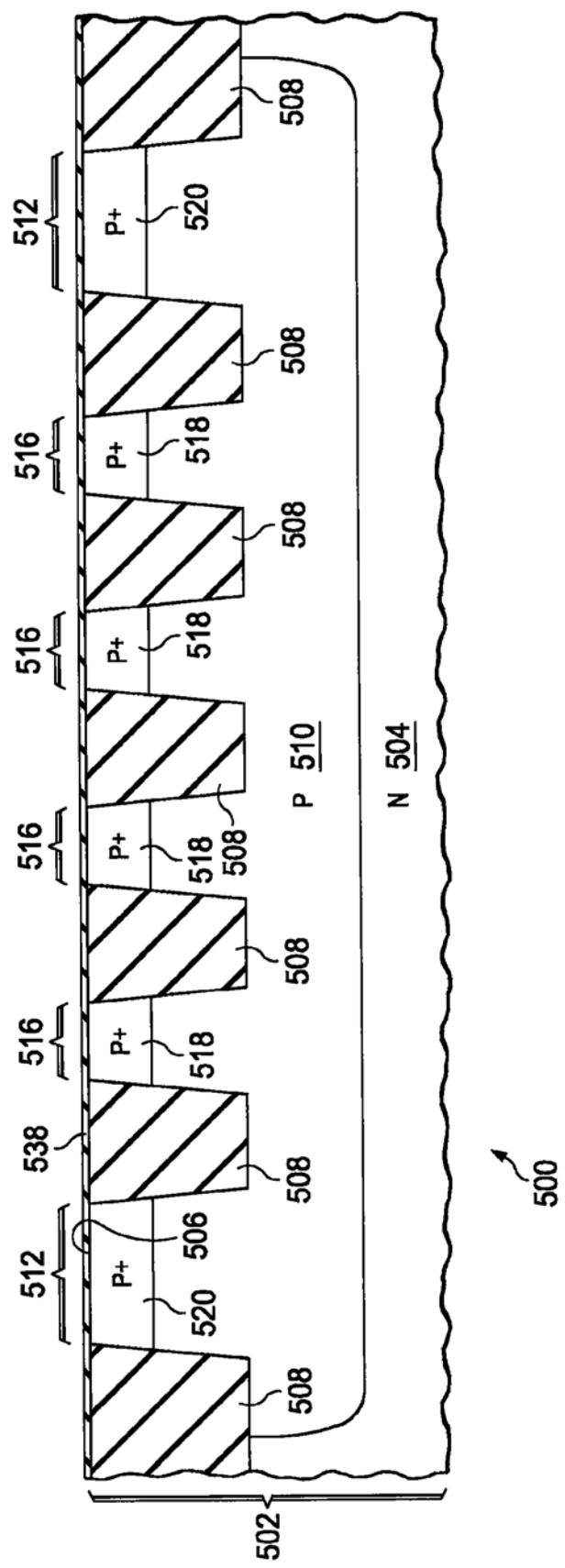

[0029] 参考图5B,执行退火操作,该退火操作在接触件注入区550中激活图5A中的注入的p型掺杂剂554以便在电阻前端有源区512中形成p型电阻前端接触区520,并且在虚设注入区556中激活图5A中的注入的p型掺杂剂554以便在电阻虚设有源区516中形成p型虚设扩散区518。可以如参考图4J所描述的那样执行退火操作。

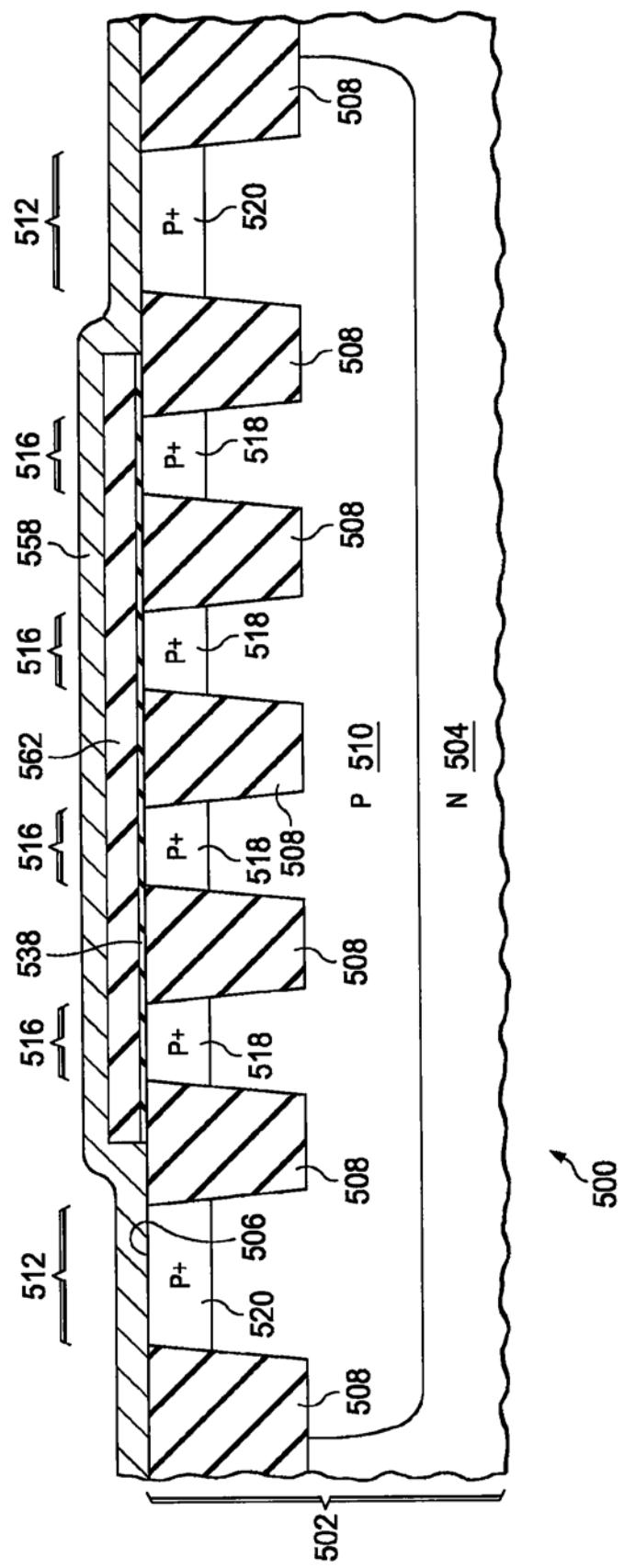

[0030] 参考图5C,介电材料的硅化物阻挡层562(诸如氮化硅和/或二氧化硅)形成在氧化物垫层538上方。蚀刻掩膜形成在硅化物阻挡层562和氧化物垫层538上方,其暴露电阻前端有源区512并覆盖电阻虚设有源区516。蚀刻工艺在被蚀刻掩膜暴露的区域中去除硅化物阻挡层562和氧化物垫层538。随后去除蚀刻掩膜。如参考图4K所描述,电阻前端有源区512被清理,而电阻虚设有源区516被硅化物阻挡层562和氧化物垫层538覆盖。难熔金属层558形成在集成电路500的现有顶表面上。难熔金属层558形成在电阻前端有源区512上,并且通过硅化物阻挡层562和氧化物垫层538与电阻虚设有源区516分离。难熔金属层558可以具有如

参考图4K所描述的成分和厚度。

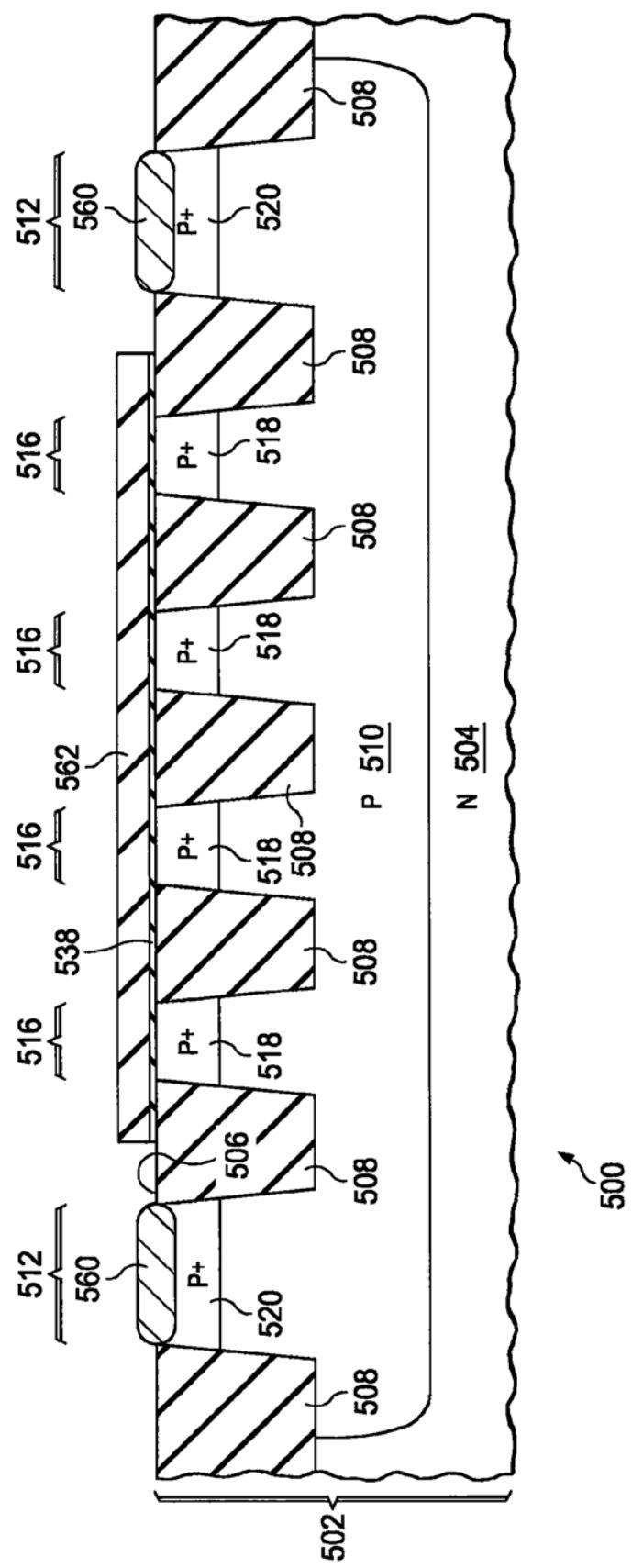

[0031] 参考图5D,如参考图4L所描述的,加热衬底502,使得图5C的难熔金属层558中的难熔金属与电阻前端有源区512中的硅在衬底502的顶表面506处反应,以便在电阻前端有源区512的顶部形成金属硅化物层560。难熔金属层558中未反应的难熔金属随后被去除。继续集成电路500的制造,形成PMD层和穿过金属硅化物层560和电阻前端连接区520至阱电阻510的接触件。阻挡金属硅化物形成在电阻虚设有源区516上可以有利地为阱电阻510的实例提供比电阻虚设有源区上的金属硅化物的阻抗更均匀的阻抗值。

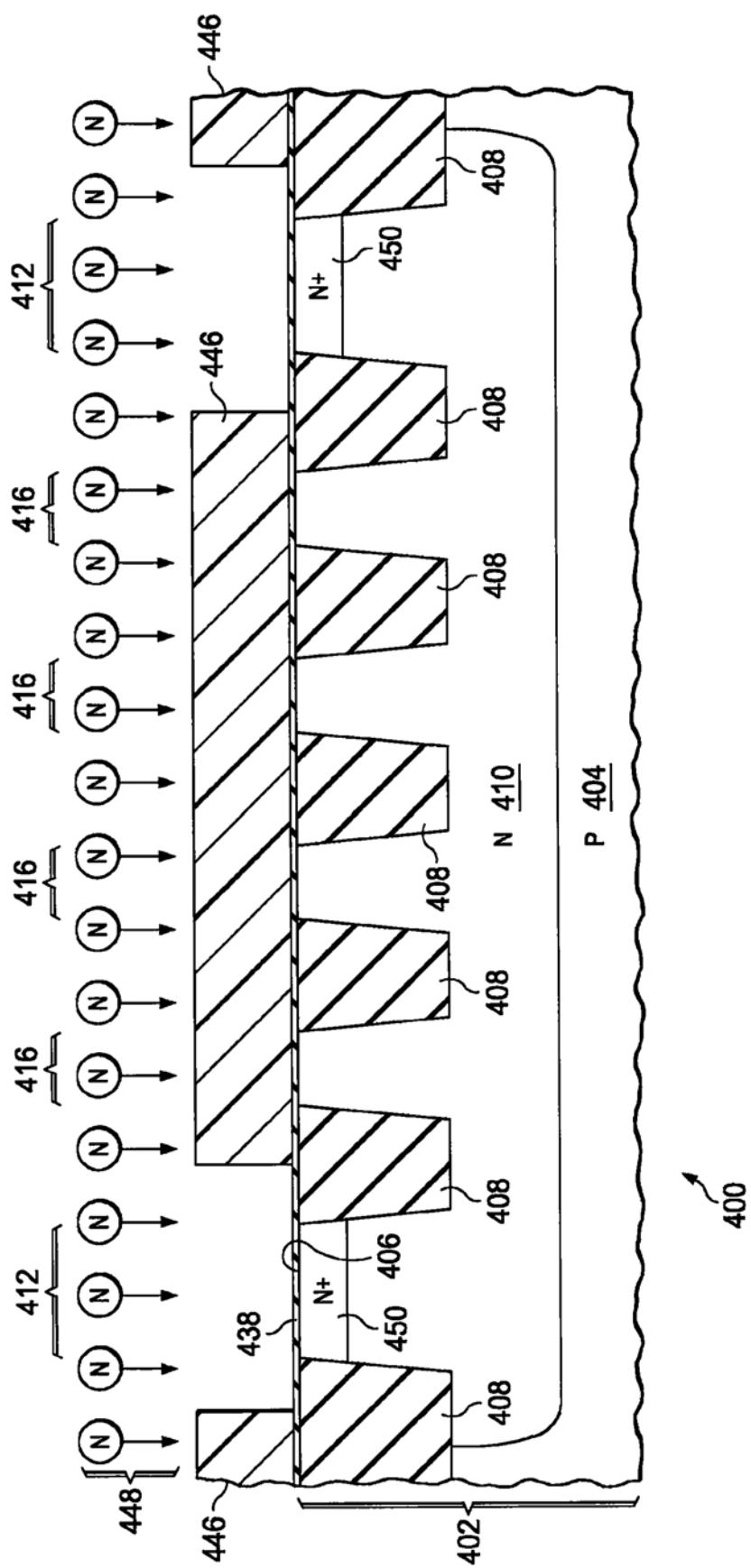

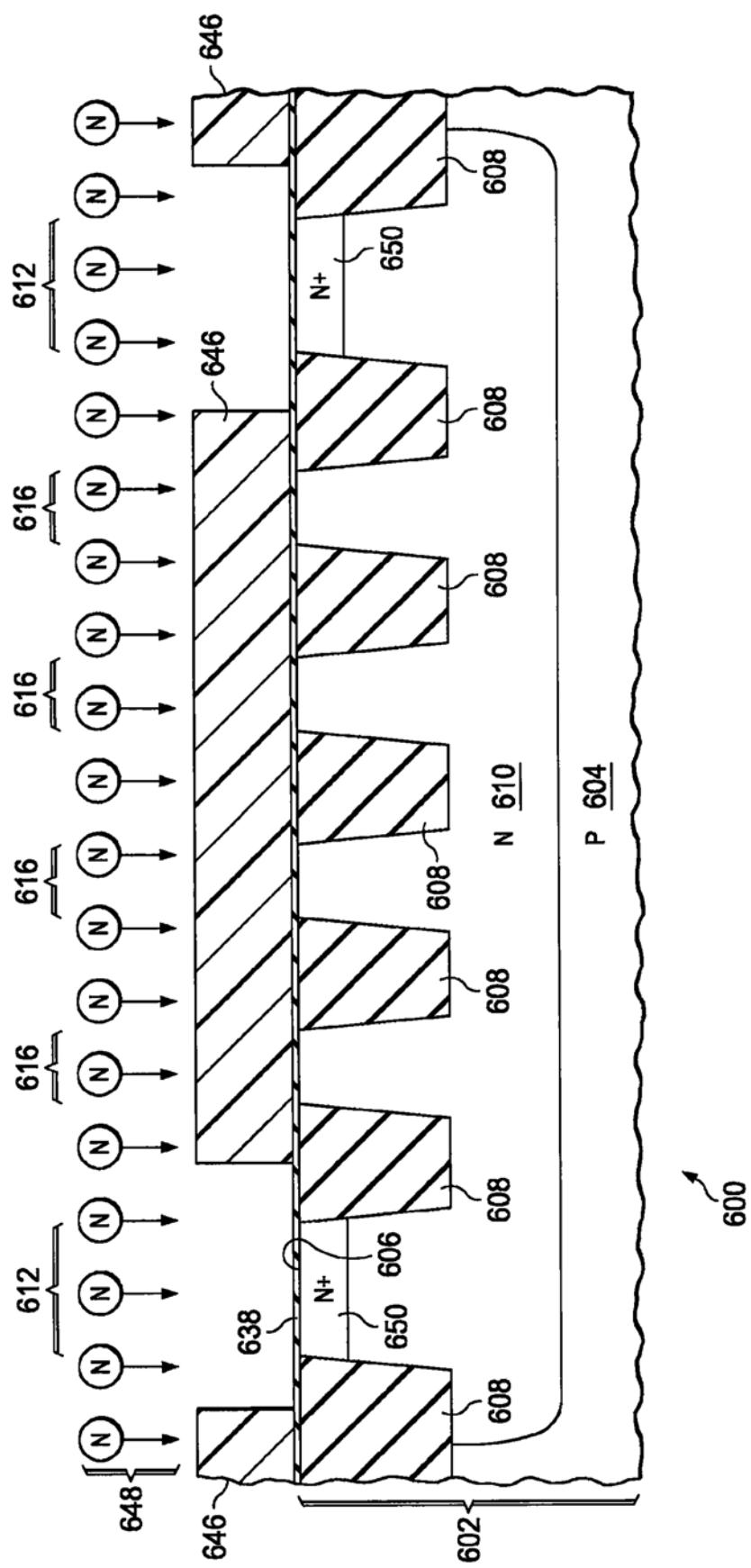

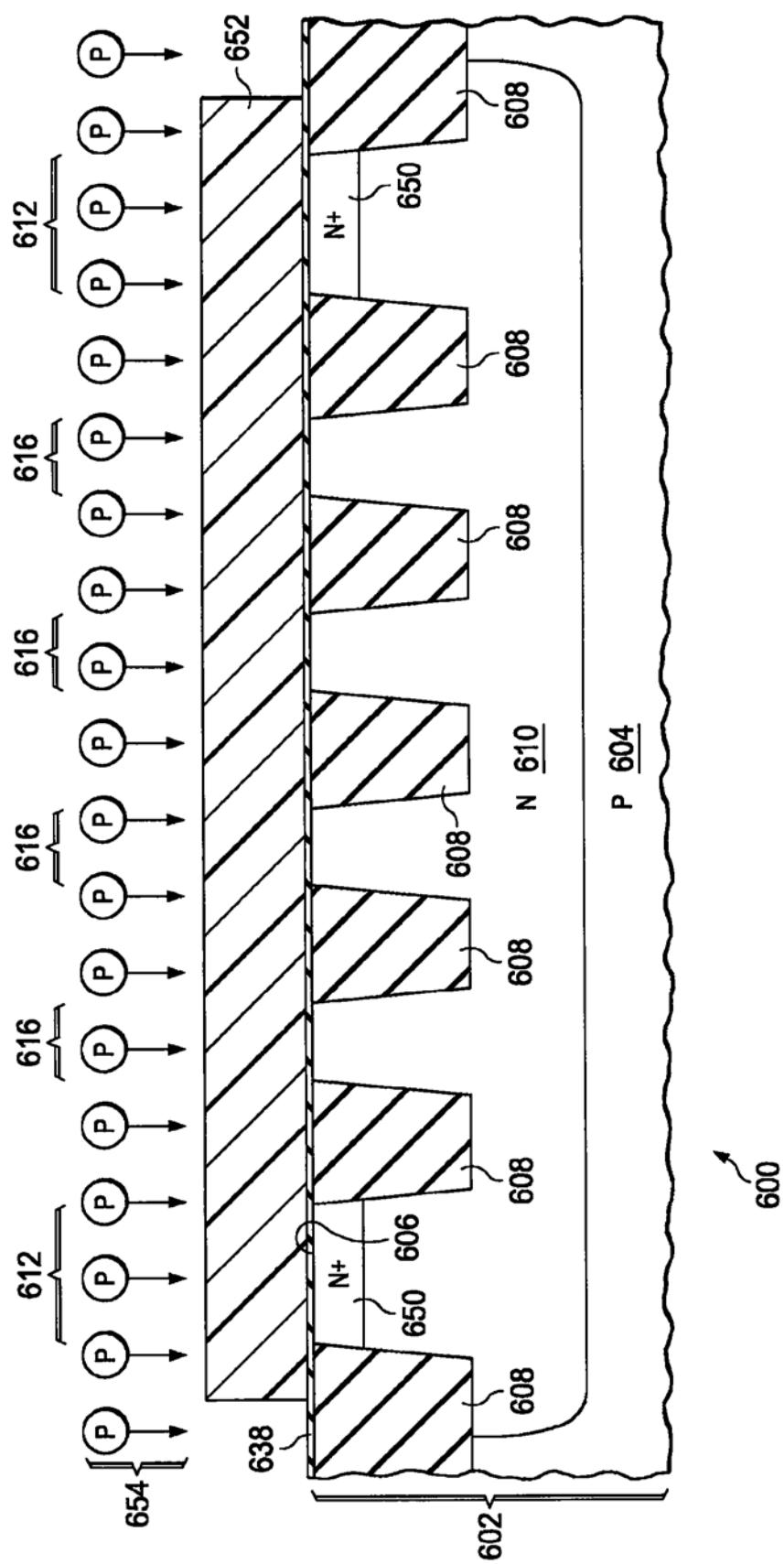

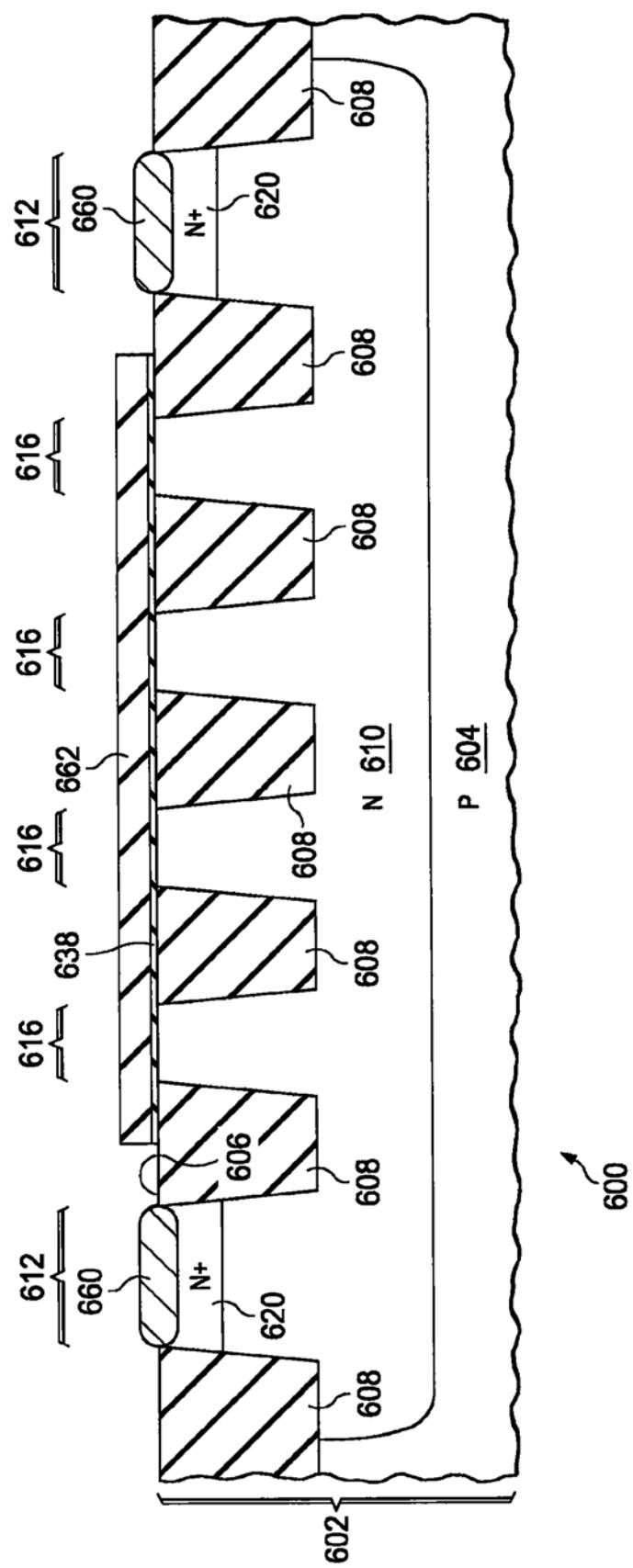

[0032] 图6A至图6C是以连续的制造阶段描绘的包含阱电阻的又一示例集成电路的截面图。参考图6A,集成电路形成在衬底602上,该衬底602包括延伸到衬底602的顶表面606的半导体材料604。在该示例中,半导体材料604是p型的。如参考图4A至图4E所描述,场氧化物608形成在衬底602上。集成电路600包括电阻前端有源区612和电阻虚设有源区616。氧化物垫层638(相当于图4F的第二二氧化物垫层638)形成在衬底602上方。如参考图4F和图4G所描述,n型阱电阻610形成在场氧化物608下方的半导体材料604中。接触件注入掩膜646形成在集成电路600的现有顶表面上方以暴露电阻前端有源区612。在该示例中,接触件注入掩膜646覆盖电阻虚设有源区616。接触件注入掩膜646还可以暴露集成电路600中的NMOS晶体管中的NSD区的区域。如参考图4H所描述,n型掺杂剂648(诸如磷和/或砷)被注入到电阻前端有源区612中以形成接触件注入区650。接触件注入掩膜646随后被去除。

[0033] 参考图6B,PSD掩膜652形成在集成电路600的现有顶表面上方以覆盖电阻前端有源区612和电阻虚设有源区616。PSD掩膜652暴露集成电路600中的PMOS晶体管中的PSD区的区域。p型掺杂剂654(诸如硼)在由PSD掩膜652暴露的区域中被注入到衬底602中。电阻前端有源区612和电阻虚设有源区616基本不含p型掺杂剂654。PSD掩膜652随后被去除。除了形成阱电阻610中使用的掺杂外,电阻虚设有源区616基本免于掺杂。

[0034] 参考图6C,执行退火操作,该退火操作在接触件注入区650中激活图6A的注入的n型掺杂剂648以便在电阻前端有源区612中形成n型电阻前端连接区620。如参考图5C所描述,在衬底602上方形成硅化物阻挡层662并利用氧化物垫层638将其图案化以暴露电阻前端有源区612并覆盖电阻虚设有源区616。如参考图5C和图5D所描述,金属硅化物层660形成在电阻前端有源区612的顶表面处。在电阻虚设有源区616中没有额外注入的情况下形成阱电阻610可以有利地为阱电阻610的实例提供比在电阻虚设有源区中有额外注入的情况下更均匀的阻抗值。

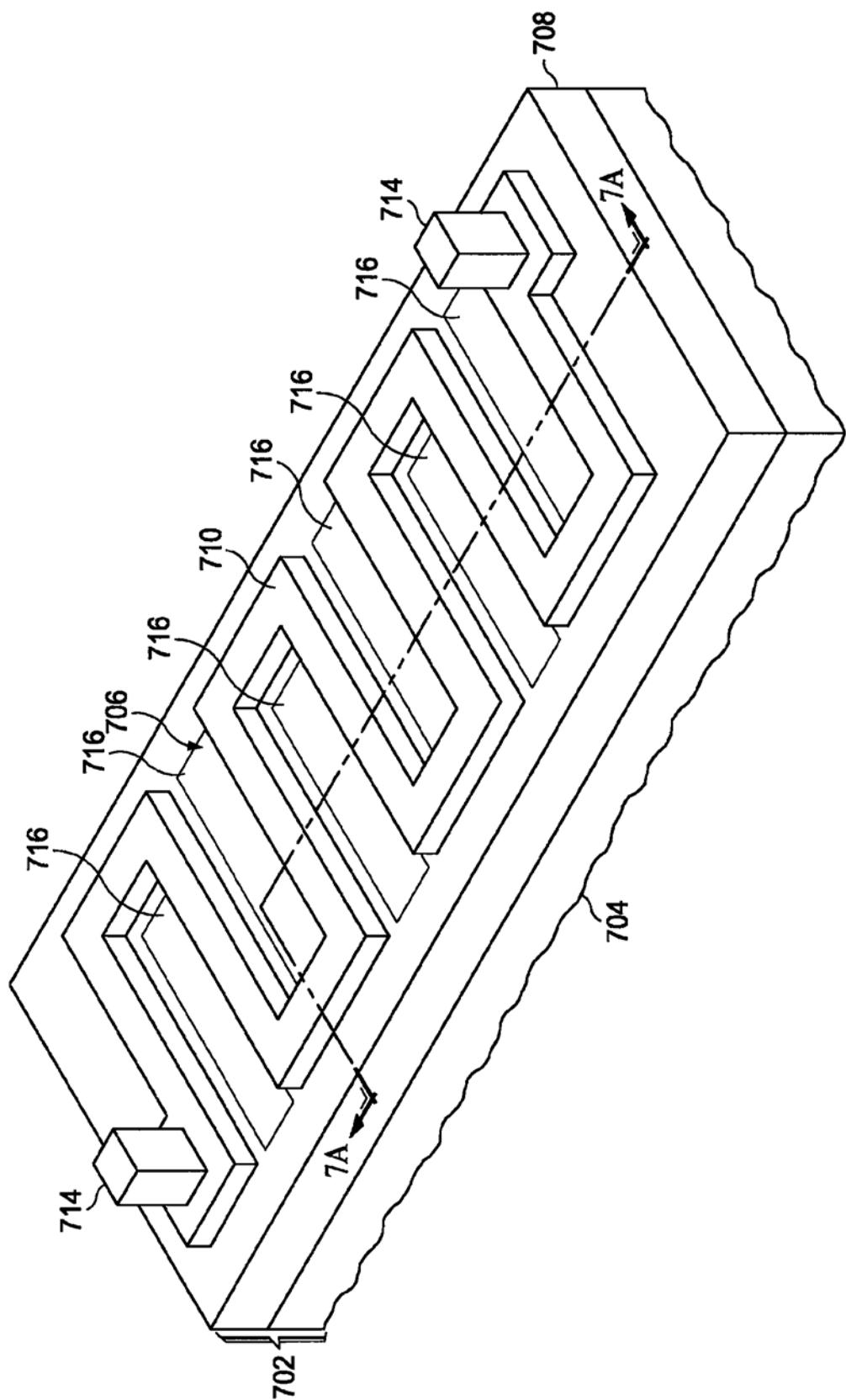

[0035] 图7描绘包含多晶硅电阻的示例集成电路。集成电路700形成在衬底702上,该衬底702包括延伸至衬底702的顶表面706的半导体材料704。由STI工艺形成的场氧化物708被设置在衬底702的顶表面706处。多晶硅电阻710被设置在场氧化物708上方。多晶硅电阻710由已被CMP工艺平坦化的多晶硅层形成。形成场氧化物708,使得电阻虚设有源区716被设置为穿过多晶硅电阻710的区域中的场氧化物708。不在衬底702的顶表面706之上形成至电阻虚设有源区716的电连接。电阻虚设有源区716的密度是10%至80%。在多晶硅电阻710的区域中形成具有10%至80%的密度的电阻虚设有源区716可以防止在STI工艺期间过度抛光场氧化物708,有利地提供多晶硅电阻710中的平坦化多晶硅的期望厚度,这为多晶硅电阻710提供了期望的阻抗。在该示例的一个版本中,电阻虚设有源区716的密度是20%至50%,这有利地提供更接近期望厚度的场氧化物708的厚度。在进一步的版本中,电阻虚设有源区

716的密度是25%至30%，这有利地更进一步缩小场氧化物708的厚度范围。接触件714形成在多晶硅电阻710上以提供至多晶硅电阻710的电连接。图7A是图7的集成电路的截面图，更清晰地示出电阻虚设有源区716。

[0036] 图8和图9是包含多晶硅电阻的示例集成电路的俯视图。参考图8，集成电路800形成在衬底802上，衬底802包括延伸至衬底802的顶表面806的半导体材料804。由STI工艺形成的场氧化物808被设置在衬底802的顶表面806处。多晶硅电阻810由场氧化物808上方的CMP平坦化的多晶硅层形成。形成接触件814以便制作至多晶硅电阻810的电连接。形成场氧化物808，使得电阻虚设有源区816被设置为穿过多晶硅电阻810的区域中的场氧化物808。在该示例中，电阻虚设有源区816不在多晶硅电阻810下方延伸，这可以有利地降低多晶硅电阻810上的电容性负载。可选的周围虚设有源区822可以被设置为穿过场氧化物808连续地包围多晶硅电阻810的区域。周围虚设有源区822(如果有的话)在多晶硅电阻810的宽度824内。形成周围虚设有源区822以在多晶硅电阻810的宽度824内连续地包围多晶硅电阻810可以有利地为场氧化物808的厚度提供更严格的工艺范围，同时降低电阻虚设有源区816的密度。降低电阻虚设有源区816的密度可能对于降低多晶硅电阻810的整体面积是合乎期望的。

[0037] 参考图9，集成电路900形成在衬底902上，衬底902包括延伸至衬底902的顶表面906的半导体材料904。由STI工艺形成的场氧化物908被设置在衬底902的顶表面906处。多晶硅电阻910由场氧化物908上方的CMP平坦化的多晶硅层形成。形成接触件914以便制作至多晶硅电阻910的电连接。形成场氧化物908，使得电阻虚设有源区916被设置为穿过多晶硅电阻910的区域中的场氧化物908。在该示例中，电阻虚设有源区916在多晶硅电阻910下方延伸，这可以增加电阻虚设有源区916的密度并因此有利地减少场氧化物908的过度抛光。可选的周围虚设有源区922可以被设置为在多晶硅910的区域周围穿过场氧化物908。如图9所示，周围虚设有源区922可以是分段的。周围虚设有源区922(如果有的话)在多晶硅电阻910的宽度924内。

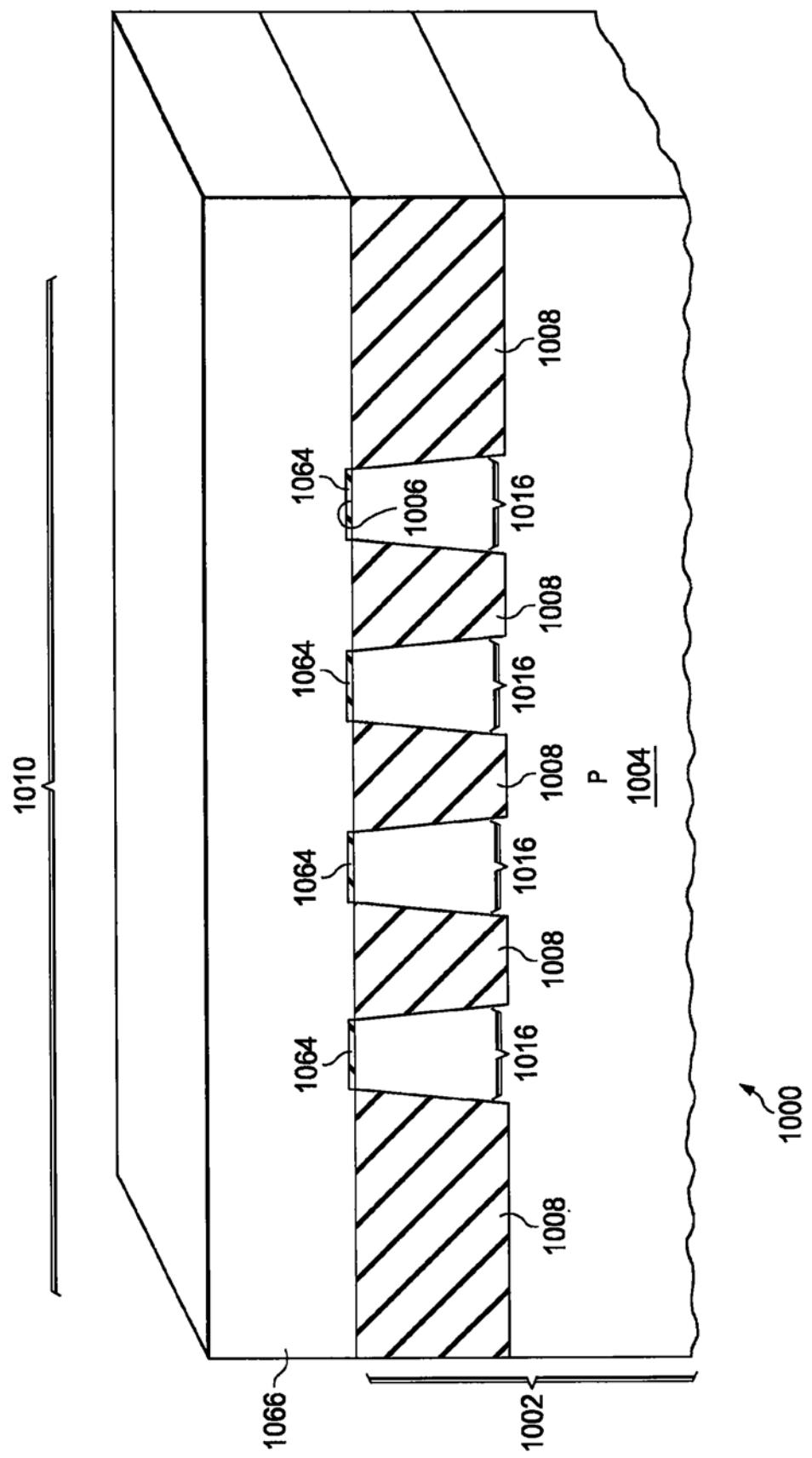

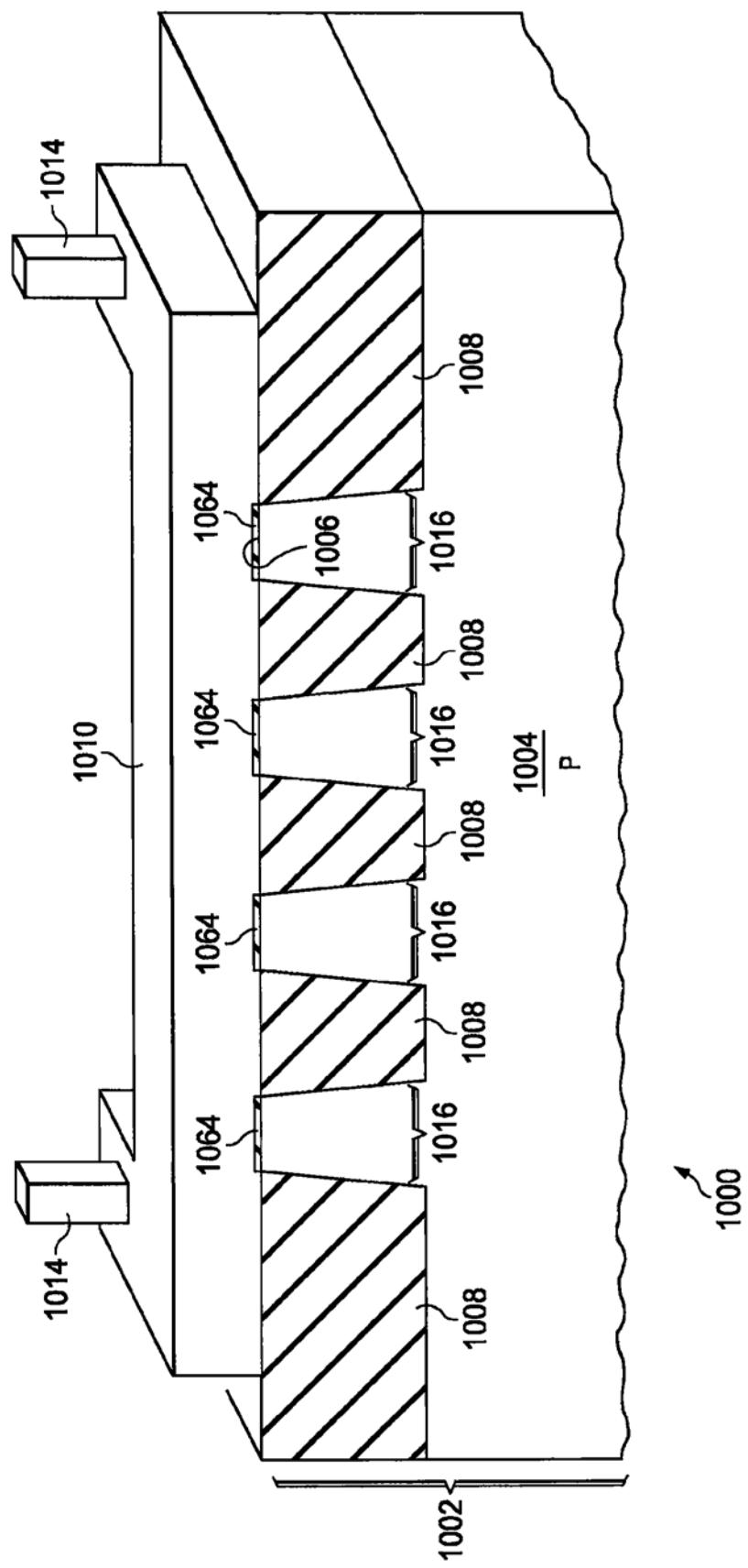

[0038] 图10A至图10F是以连续的制造阶段描绘的包含多晶硅电阻的示例集成电路的截面图。参考图10A，集成电路1000形成在衬底1002上，衬底1002包括延伸到衬底1002的顶表面1006的半导体材料1004。在该示例中，半导体材料1004是p型的。如参考图4A至图4E所描述，场氧化物1008通过STI工艺形成在衬底1002的顶表面1006处。形成场氧化物1008，使得电阻虚设有源区1016被设置为穿过多晶硅电阻1010的区域中的场氧化物1008。介电层1064被设置在电阻虚设有源区1016上方。介电层1064可以与集成电路的NMOS晶体管和PMOS晶体管的栅极介电层同时形成。介电层可以在场氧化物1008上方延伸。

[0039] 参考图10B，多晶硅层1066形成在场氧化物1008和介电层1064的上方。多晶硅层1066可以由保形工艺(诸如通过在580°C至650°C下热解硅烷)形成。多晶硅层1066可以在形成期间通过包括掺杂剂气体(诸如磷化氢、砷化氢或三氯化硼)与硅烷而被原位掺杂。可替代地，多晶硅层1066可以在形成之后通过离子注入被掺杂。原位掺杂可以产生恒定的平均掺杂密度，其不依赖于多晶硅层1066的厚度。离子注入可以产生多晶硅层1066中的恒定的掺杂剂总剂量，其不依赖于厚度。

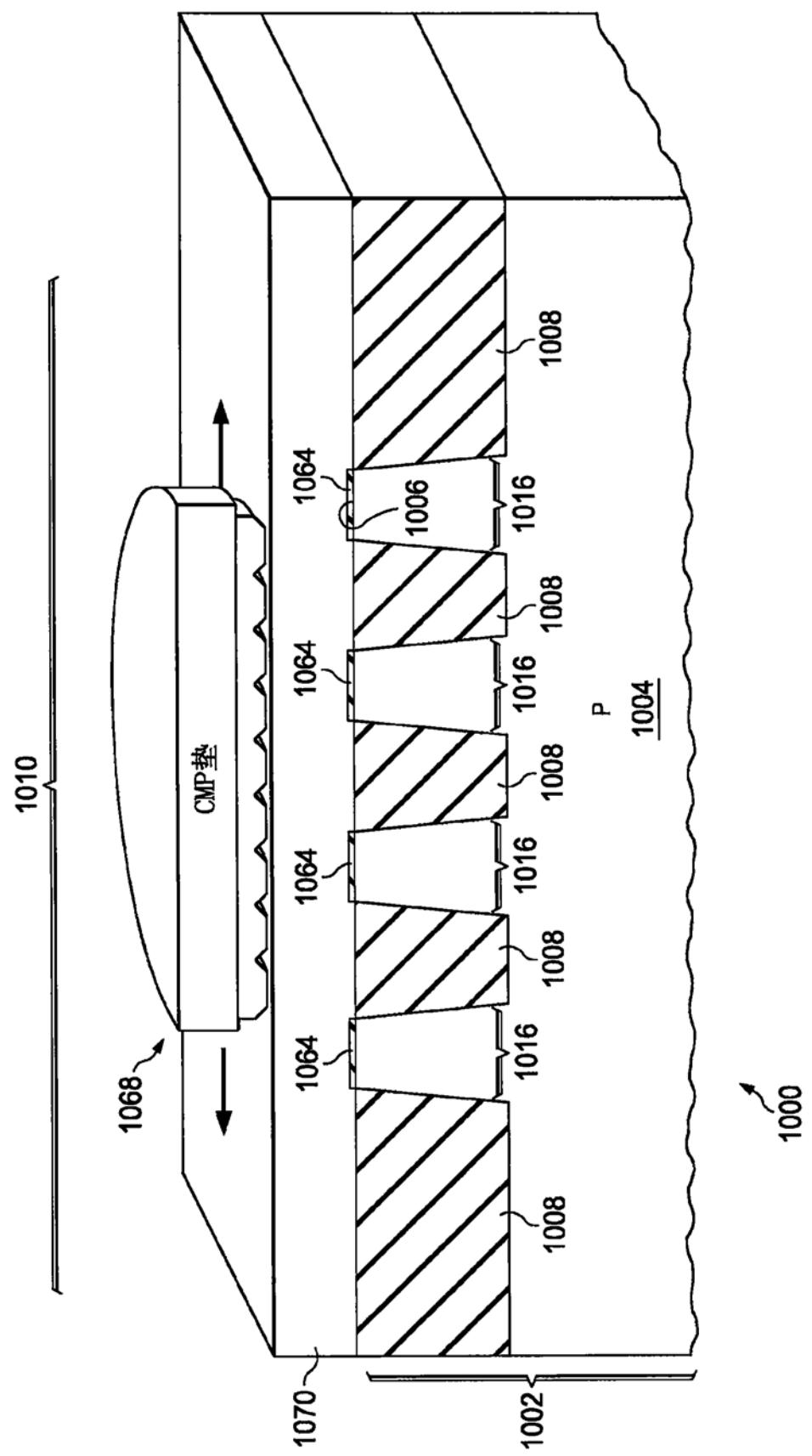

[0040] 参考图10C，图10B的多晶硅层1066通过CMP工艺1068(在图10C中由CMP垫1068示意地描绘)被平坦化，以形成具有期望厚度的CMP平坦化的多晶硅层1070。例如，CMP工艺1068

可以用于从多晶硅层1066去除由于多晶硅成形工艺的共形性质而导致的任何表面拓扑结构。通过降低STI工艺期间的过度抛光,在多晶硅电阻1010的区域中形成具有电阻虚设有源区1016的场氧化物1008为场氧化物1008提供期望厚度,这进而有利地为CMP平坦化的多晶硅层1070提供期望厚度。过度抛光的场氧化物将产生较薄的场氧化物,然后其将不利地产生较厚的CMP平坦化的多晶硅层。

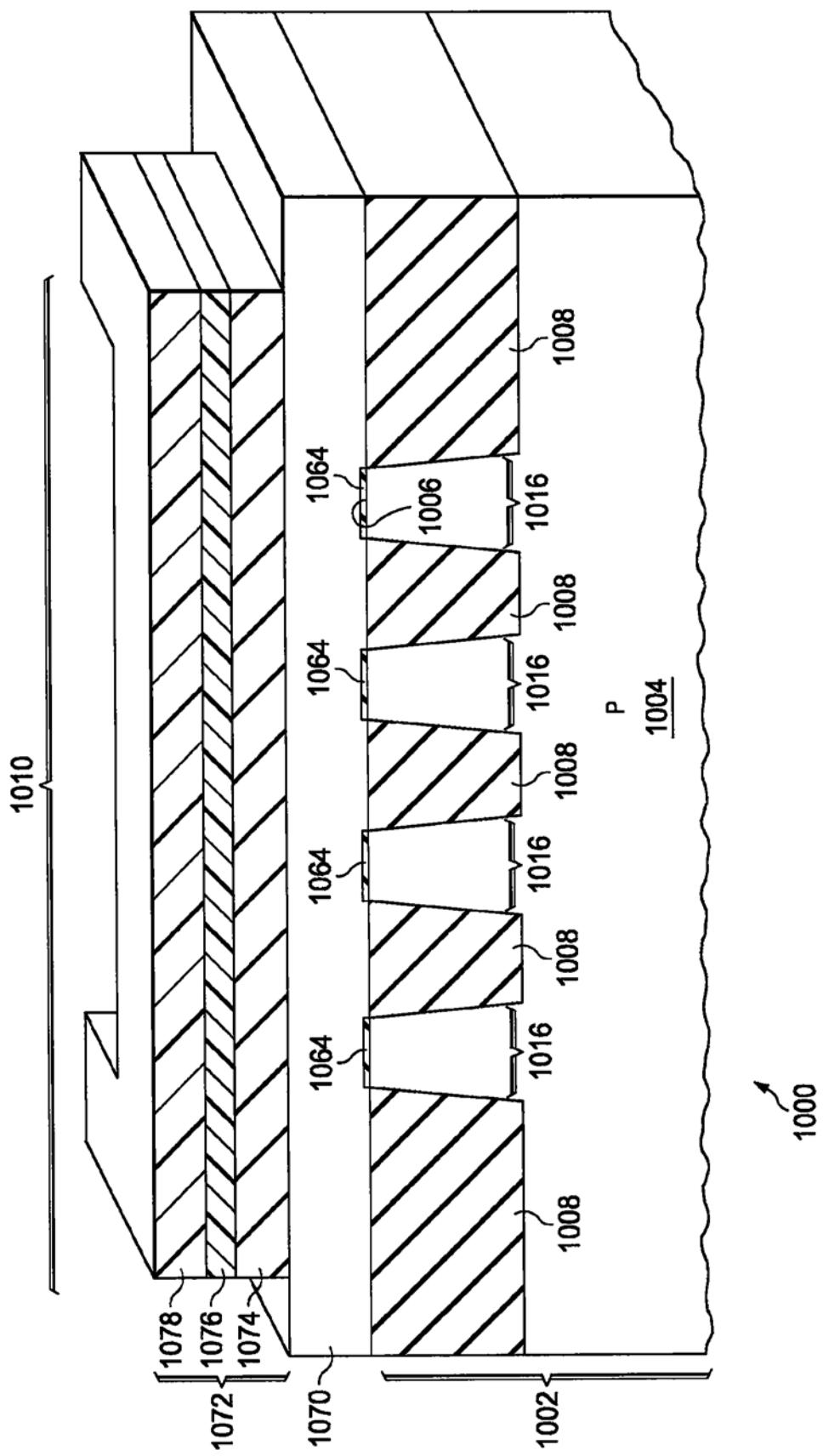

[0041] 参考图10D,多晶硅蚀刻掩膜1072形成在CMP平坦化的多晶硅层1070上方以限定多晶硅电阻1010。多晶硅蚀刻掩膜1072还可以覆盖集成电路1000中的NMOS和PMOS晶体管的栅极区域。多晶硅蚀刻掩膜1072可以包括氮化硅或无定形碳的硬掩膜层1074、被称为底部抗反射涂层(BARC)的旋涂有机材料的抗反射层1076和/或由光刻工艺形成的光致抗蚀剂层1078。

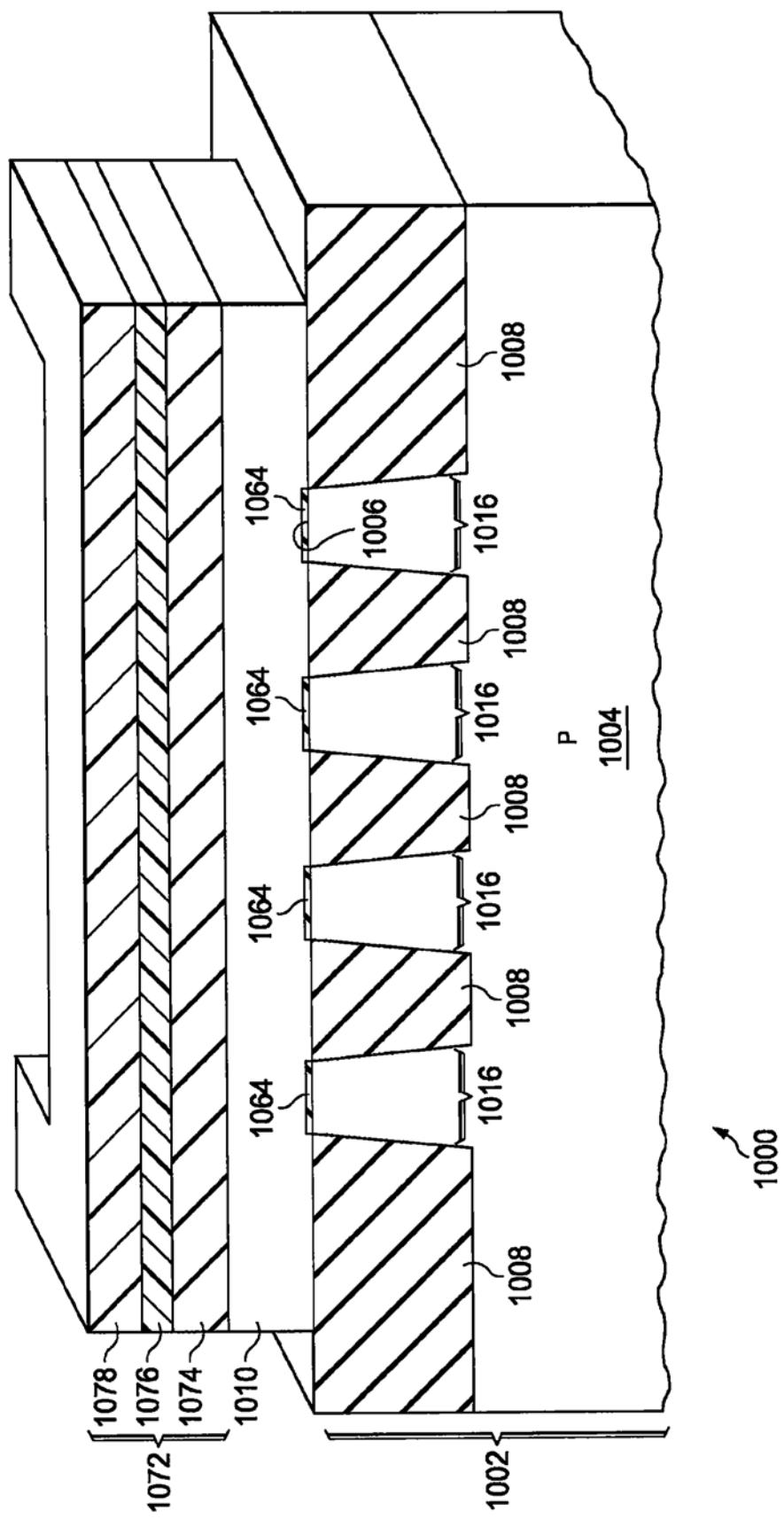

[0042] 参考图10E,多晶硅蚀刻工艺在由多晶硅蚀刻掩膜1072暴露的区域中将多晶硅从CMP平坦化的多晶硅层1070中去除以形成多晶硅电阻1010。在多晶硅蚀刻工艺期间,可以去除一部分或全部光致抗蚀剂层1078和抗反射层1076。多晶硅蚀刻掩膜1072的任何剩余部分随后被去除。

[0043] 参考图10F,接触件1014形成在多晶硅电阻1010上以便制作至多晶硅电阻的电连接。金属硅化物(图10F中未示出)可以形成在多晶硅电阻1010上接触件1014下方的区域,以便改善至多晶硅电阻1010的电连接。

[0044] 在权利要求的范围内,所描述的实施例可能有修改,并且可能有其他实施例。

图1

图2

图3

图4A

图4B

图4C

图4D

图4E

图4F

图4G

图4H

图4I

图4J

图4K

图4L

图5A

图5B

图5C

图5D

图6A

图6B

图6C

图7

图7A

图8

图9

图10A

图10B

图10C

图10D

图10E

图10F