(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6679499号

(P6679499)

(45) 発行日 令和2年4月15日(2020.4.15)

(24) 登録日 令和2年3月23日(2020.3.23)

|                      |                               |

|----------------------|-------------------------------|

| (51) Int.Cl.         | F 1                           |

| HO3L 7/089 (2006.01) | HO3L 7/089                    |

| HO3L 7/197 (2006.01) | HO3L 7/197 110                |

| HO3K 5/26 (2006.01)  | HO3L 7/197 160<br>HO3K 5/26 P |

請求項の数 12 (全 18 頁)

|                    |                               |           |                                                                                                                |

|--------------------|-------------------------------|-----------|----------------------------------------------------------------------------------------------------------------|

| (21) 出願番号          | 特願2016-565298 (P2016-565298)  | (73) 特許権者 | 595020643<br>クアアルコム・インコーポレイテッド<br>QUALCOMM INCORPORATED<br>アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775 |

| (86) (22) 出願日      | 平成27年4月15日(2015.4.15)         | (74) 代理人  | 100108855<br>弁理士 蔵田 昌俊                                                                                         |

| (65) 公表番号          | 特表2017-518685 (P2017-518685A) | (74) 代理人  | 100109830<br>弁理士 福原 淑弘                                                                                         |

| (43) 公表日           | 平成29年7月6日(2017.7.6)           | (74) 代理人  | 100158805<br>弁理士 井関 守三                                                                                         |

| (86) 國際出願番号        | PCT/US2015/025967             | (74) 代理人  | 100112807<br>弁理士 岡田 貴志                                                                                         |

| (87) 國際公開番号        | W02015/167805                 |           |                                                                                                                |

| (87) 國際公開日         | 平成27年11月5日(2015.11.5)         |           |                                                                                                                |

| 審査請求日              | 平成30年3月22日(2018.3.22)         |           |                                                                                                                |

| (31) 優先権主張番号       | 14/266,730                    |           |                                                                                                                |

| (32) 優先日           | 平成26年4月30日(2014.4.30)         |           |                                                                                                                |

| (33) 優先権主張国・地域又は機関 | 米国(US)                        |           |                                                                                                                |

最終頁に続く

(54) 【発明の名称】低雑音位相ロックループ

## (57) 【特許請求の範囲】

## 【請求項 1】

発振信号を生成するための位相ロックループ回路であって、

2つの入力信号(基準信号、フィードバック信号)間の位相差に応答して第1の信号(アップ信号)および第2の信号(ダウン信号)を出力するように構成された位相検出器であって、ここにおいて、前記位相検出器が前記第2の信号を出力するときに第3の信号によって前記第1の信号の無効および有効を切り替え、および前記位相検出器が前記第1の信号を出力するときに前記第3の信号によって前記第2の信号の無効および有効を切り替えるようにさらに構成された、位相検出器と、

前記第1の信号および前記第2の信号に応答して、同調可能周波数を有する発振信号を生成するように構成された電圧制御発振器(VCO)と、

電荷ポンプヒループフィルタであって、ここにおいて、前記電荷ポンプが前記第1の信号に応答して充電電流をソースすることと前記第2の信号に応答して放電電流をシンクすることによって前記ヒループフィルタに電流源を与えるように構成され、かつ前記電荷ポンプが前記ヒループフィルタに結合された漏れ電流源をさらに備える、電荷ポンプヒループフィルタと、を備える、位相ロックループ回路。

## 【請求項 2】

前記ヒループフィルタが、前記VCOの周波数を同調させるための制御電圧を生成するために、前記充電電流および前記放電電流を積分するように構成された、請求項1に記載の位相ロックループ回路。

10

20

## 【請求項 3】

前記位相検出器が、前記第2の信号を出力するときに前記第1の信号を無効にすることと、第1の信号を出力するときに前記第2の信号を無効にすることとを行うように構成されたゲーティング回路を備える、請求項1に記載の位相ロックループ回路。

## 【請求項 4】

前記2つの入力信号が、基準信号とフィードバック信号とを備え、前記フィードバック信号が、前記発振信号から導出される、請求項1に記載の位相ロックループ回路。

## 【請求項 5】

前記発振信号から前記フィードバック信号を生成するように構成されたフラクショナルN周波数分割器をさらに備える、請求項4に記載の位相ロックループ回路。 10

## 【請求項 6】

発振信号を生成する方法であって、

2つの入力信号間の位相差を検出することであって、ここにおいて、前記検出することが、第2の信号を出力するときに第3の信号によって第1の信号の無効および有効を切り替え、および前記第1の信号を出力するときに前記第3の信号によって前記第2の信号の無効および有効を切り替えることによって、2つの入力信号間の前記位相差に応答して前記第1の信号および前記第2の信号を出力することを備える、位相差を検出することと、

前記第1の信号および前記第2の信号に応答して、同調可能周波数を有する発振信号を生成することとを備える、方法。

## 【請求項 7】

前記発振信号の周波数を同調させるための制御電圧を生成することと、

前記第1の信号に応答して充電電流をソースすることと、前記第2の信号に応答して放電電流をシンクすることとによって、前記制御電圧を生成するための電流源を与えることと

をさらに備える、請求項6に記載の方法。 20

## 【請求項 8】

制御電圧を前記生成することが、前記充電電流および前記放電電流を積分することを備える、請求項7に記載の方法。

## 【請求項 9】

制御電圧を前記生成することに漏れ電流を与えることをさらに備える、請求項7に記載の方法。 30

## 【請求項 10】

位相差を前記検出することが、前記第2の信号を出力するときに第3の信号によって前記第1の信号の無効および有効を切り替え、および第1の信号を出力するときに前記第3の信号によって前記第2の信号の無効および有効を切り替えるためにゲーティング回路を使用することを備える、請求項6に記載の方法。

## 【請求項 11】

前記2つの入力信号が、基準信号とフィードバック信号とを備え、前記フィードバック信号が、前記発振信号の関数である、請求項6に記載の方法。

## 【請求項 12】

前記発振信号の周波数をフラクショナルに分割することによって、前記フィードバック信号を生成することをさらに備える、請求項11に記載の方法。 40

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

関連出願の相互参照

[0001]本出願は、その全体が参照により本明細書に明確に組み込まれる、2014年4月30日に出願された「LOW NOISE PHASE LOCKED LOOPS」と題する米国特許出願第14/266,730号の利益を主張する。

## 【0002】

[0002] 本開示は、一般に電子回路に関し、より詳細には、低雑音位相ロックループ (low noise phase locked loops) に関する。

【背景技術】

【0003】

[0003] ワイヤレスデバイス (たとえば、セルラーフォンまたはスマートフォン) は、ワイヤレス通信システムとの双方向通信のためのデータを送信および受信し得る。ワイヤレスデバイスは、データ送信のための送信機と、データ受信のための受信機とを含み得る。データ送信では、送信機は、局部発振器 (LO) 信号をデータで変調して変調された無線周波数 (RF) 信号を取得し、変調されたRF信号を増幅して所望の出力電力レベルを有する出力RF信号を取得し、アンテナを介して出力RF信号をリモートデバイスに送信し得る。データ受信では、受信機は、アンテナを介して受信RF信号を取得し、受信RF信号をLO信号で増幅し、ダウンコンバートし、ダウンコンバートされた信号を処理して、リモートデバイスによって送られたデータを復元し得る。

【0004】

[0004] LO信号を生成するために電圧制御発振器 (VCO: Voltage-controlled oscillators) がしばしば使用される。VCOは、その周波数が電圧入力によって制御される発振器である。送信機または受信機を同調させるようにVCOの入力電圧を調整するためには、位相ロックループがしばしば使用される。位相ロックループは、概して、VCO出力の位相を基準信号の位相と比較し、位相を整列された (aligned) 状態に保つようにVCOへの電圧入力を調整する、位相検出器 (phase detector) を用いて実装される。基準信号とVCO出力との間の位相整列 (phase alignment) を正確に維持する位相ロックループの能力は、部分的に、VCO中で生成される雑音に依存する。位相ロックループを設計することにおける当業者 (skilled artisans) の間の共通課題は、雑音低減である。

【発明の概要】

【0005】

[0005] 発振信号 (oscillating signal) を生成するための回路の態様が開示される。本回路は、2つの入力信号間の位相差 (phase difference) に応答して第1の信号および第2の信号を出力するように構成された位相検出器を含む。位相検出器は、第2の信号を出力するときに第1の信号を無効にすることと、第1の信号を出力するときに第2の信号を無効にすることとを行うようにさらに構成される。本回路は、第1の信号および第2の信号に応答して、同調可能周波数 (tunable frequency) を有する発振信号を生成するように構成された電圧制御発振器 (VCO) をも含む。

【0006】

[0006] 発振信号を生成するための回路の態様が開示される。本回路は、2つの入力信号間の位相差を検出するための手段を含む。位相差を検出するための手段は、2つの入力信号間の位相差に応答して第1の信号および第2の信号を出力するように構成される。位相差を検出するための手段は、第2の信号を出力するときに第1の信号を無効にすることと、第1の信号を出力するときに第2の信号を無効にすることとを行うようにさらに構成される。本回路は、第1の信号および第2の信号に応答して、同調可能周波数を有する発振信号を生成するための手段をも含む。

【0007】

[0007] 発振信号を生成する方法の態様が開示される。本方法は、2つの入力信号間の位相差を検出することを含む。位相差を検出することは、第2の信号を出力するときに第1の信号を無効にすることと、第1の信号を出力するときに第2の信号を無効にすることによって、2つの入力信号間の位相差に応答して第1の信号および第2の信号を出力することを含む。本方法は、第1の信号および第2の信号に応答して、同調可能周波数を有する発振信号を生成することをも含む。

【0008】

[0008] 以下の詳細な説明から、当業者には装置、回路および方法の他の態様が容易に明らかになることが理解され、ここにおいて、装置、回路および方法の様々な態様が例とし

10

20

30

40

50

て図示され説明される。了解されるように、これらの態様は、他のおよび異なる形態で実装され得、そのいくつかの詳細は、様々な他の点において変更が可能である。したがって、図面および詳細な説明は、本質的に例示的なものと見なされるべきであり、限定的なものと見なされるべきではない。

【0009】

[0009]次に、添付の図面を参照しながら、限定としてではなく例として、詳細な説明において装置、回路および方法の様々な態様を提示する。

【図面の簡単な説明】

【0010】

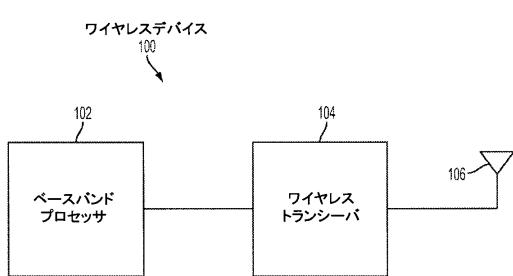

【図1】[0010]ワイヤレスデバイスの例示的な実施形態を示す概念プロック図。

10

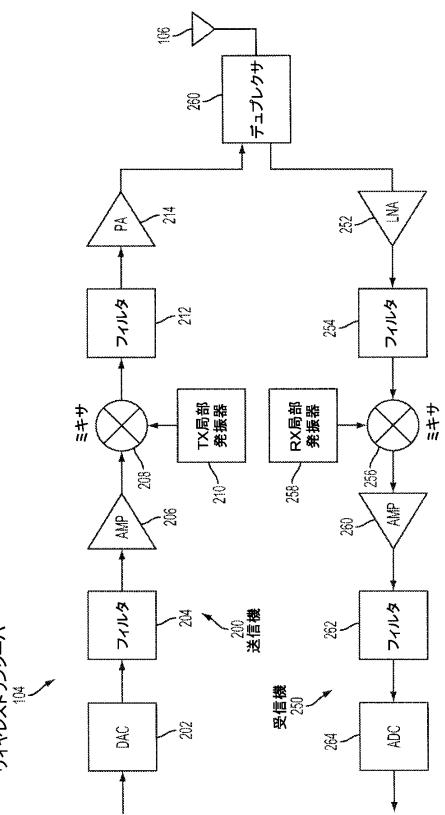

【図2】[0011]ワイヤレストランシーバの例示的な実施形態を示すプロック図。

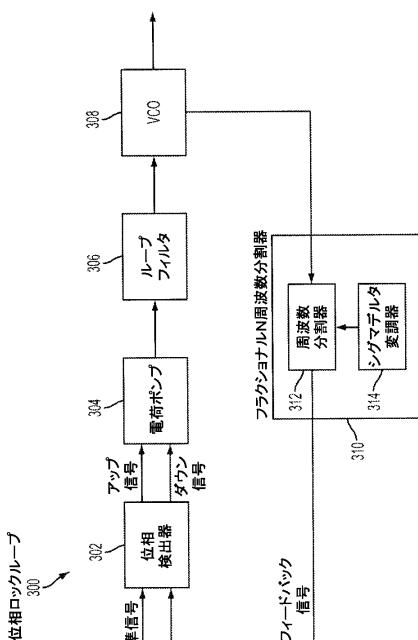

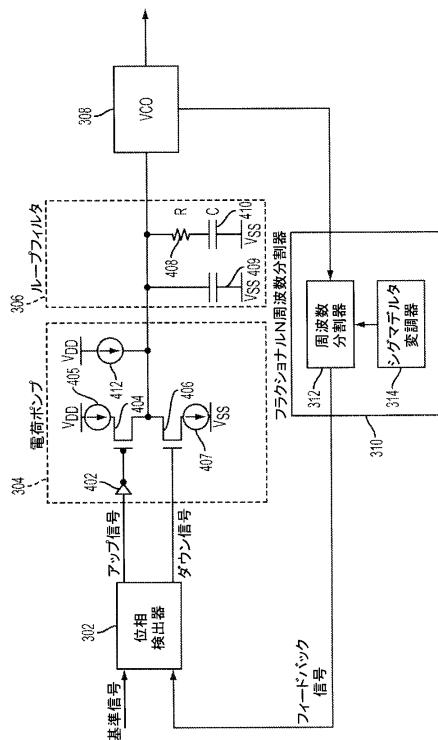

【図3】[0012]局部発振器のための位相ロックループの例示的な実施形態を示す機能プロック図。

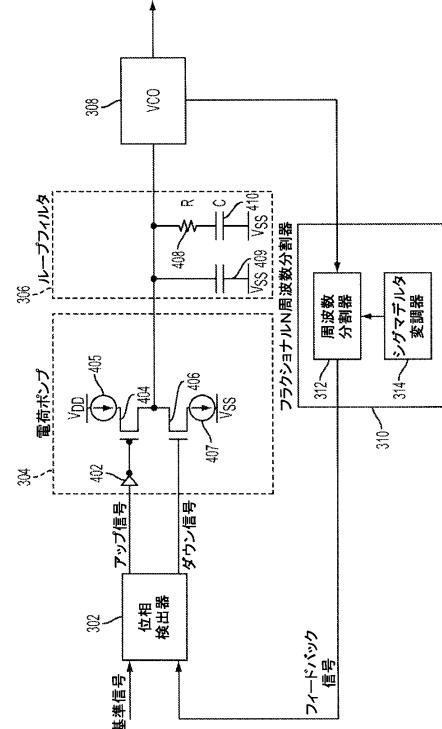

【図4A】[0013]電荷ポンプ (charge pump) およびループフィルタのための追加の概略図詳細をもつ、局部発振器のための位相ロックループの例示的な実施形態を示す機能プロック図。

【図4B】[0014]電荷ポンプ中の漏れ電流源 (leakage current source) を追加した、図4Aの局部発振器のための位相ロックループの例示的な実施形態を示す機能プロック図。

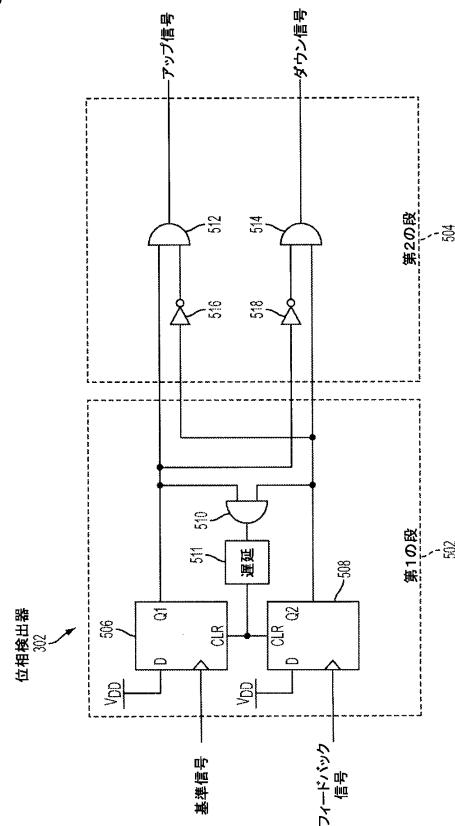

【図5】[0015]位相ロックループのための位相検出器の例示的な実施形態を示す機能プロック図。

20

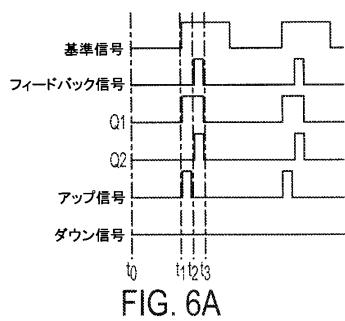

【図6A】[0016]基準信号がフィードバック信号に先行する (lead) ときの、図5の位相検出器の例示的な実施形態の動作を示すタイミング図。

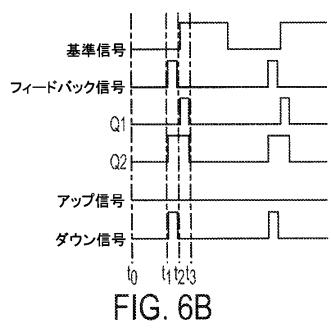

【図6B】[0017]基準信号がフィードバック信号に後続する (trail) ときの、図5の位相検出器の例示的な実施形態の動作を示すタイミング図。

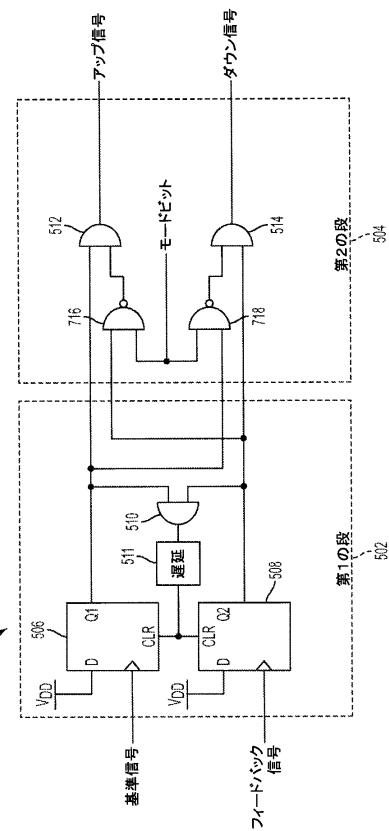

【図7】[0018]位相ロックループのための位相検出器の代替の例示的な実施形態を示す機能プロック図。

【図8】[0019]発振信号を生成する例示的な方法を示すフローチャート。

【詳細な説明】

【0011】

[0020]添付の図面に関して以下に記載される詳細な説明は、本発明の様々な例示的な実施形態を説明するものであり、本発明が実施され得る実施形態のみを表すものではない。詳細な説明は、本発明の完全な理解を与えるための具体的な詳細を含む。ただし、本発明はこれらの具体的な詳細なしに実施され得ることが当業者には明らかであろう。いくつかの事例では、本発明の概念を不明瞭にすることを回避するために、よく知られている構造および構成要素がプロック図の形式で示される。頭字語および他の記述的専門用語は、単に便宜のためにおよび明瞭にするために使用され得、本発明の範囲を限定するものではない。

30

【0012】

[0021]「例示的」という単語は、本明細書では例、事例、または例示の働きをすることを意味するために使用される。本明細書で「例示的」と記載されたいかなる実施形態も、必ずしも他の実施形態よりも好ましいまたは有利であると解釈されるべきであるとは限らない。同様に、装置、回路または方法の「実施形態」という用語は、本発明のすべての実施形態が、説明する構成要素、構造、特徴、機能、プロセス、利点、利益、または動作モードを含むことを必要としない。

40

【0013】

[0022]「接続された」、「結合された」という用語、またはその任意の変形態は、2つまたはそれ以上の要素間の、直接的または間接的のいずれかの任意の接続または結合を意味し、互いに「接続された」または「結合された」2つの要素間の1つまたは複数の中間要素の存在を包含することがある。要素間の結合または接続は、物理的、論理的、またはそれらの組合せであり得る。本明細書で使用する、2つの要素は、いくつかの非限定的で

50

非網羅的な例として、1つまたは複数のワイヤ、ケーブル、および／またはプリントされた電気的接続を使用することによって、ならびに無線周波数領域、マイクロ波領域、および光学的（可視と非可視の両方）領域中の波長を有する電磁エネルギーなど、電磁エネルギーを使用することによって互いに「接続された」または「結合された」ものと見なされ得る。

【0014】

[0023]本明細書における「第1」、「第2」などの名称を使用した要素への言及は、それらの要素の数量または順序を概括的に限定するものでない。むしろ、これらの名称は、本明細書において2つまたはそれ以上の要素またはある要素の複数の事例を区別する便利な方法として使用される。したがって、第1の要素および第2の要素への言及は、2つの要素のみが採用され得ること、または第1の要素が第2の要素に先行しなければならないことを意味するものではない。

10

【0015】

[0024]本明細書で使用する、「備える（comprises）」、「備える（comprising）」、「含む（includes）」、および／または「含む（including）」という用語は、本明細書で使用されるとき、述べられた特徴、インテージャ（integer）、ステップ、動作、要素、および／または構成要素の存在を明示するが、1つまたは複数の他の特徴、インテージャ、ステップ、動作、要素、構成要素、および／またはそれらのグループの存在または追加を排除しない。

【0016】

20

[0025]次に、ワイヤレスデバイス中の送信機と受信機との周波数を同調させるための位相ロックループの様々な態様を提示する。ただし、当業者が容易に諒解するように、そのような態様は、他の回路構成およびデバイスに拡張され得る。例として、本発明の様々な態様は、雑音の多いチャネルにおける信号復元、周波数合成、クロック分配、および位相ロックループまたは同様の回路を必要とする他の好適な使用のために使用され得る。位相ロックループのための特定の適用例、あるいは位相ロックループ内の任意の構成要素、構造、特徴、機能、またはプロセスへのすべての言及を与えることは、そのような態様が幅広い適用例を有し得るという理解とともに、位相ロックループの例示的な態様を示すためのものにすぎない。

【0017】

30

[0026]モバイルフォン、携帯情報端末（PDA）、デスクトップコンピュータ、ラップトップコンピュータ、手のひらサイズのコンピュータ、タブレットコンピュータ、セットトップボックス、ナビゲーションデバイス、ワーカステーション、ゲーム機、メディアプレーヤ、または任意の他の好適なデバイスなど、ワイヤレスデバイスでは、位相ロックループの様々な実施形態が使用され得る。図1は、そのようなワイヤレスデバイスの例示的な実施形態を示す概念プロック図である。ワイヤレスデバイス100は、例として、符号分割多元接続（CDMA）システム、マルチキャリアCDMA（MC-CDMA）、広帯域CDMA（W-CDMA（登録商標））、高速パケットアクセス（HSPA、HSPA+）システム、時分割多元接続（TDMA）システム、周波数分割多元接続（FDMA）システム、シングルキャリアFDMA（SC-FDMA）システム、直交周波数分割多元接続（OFDMA）システム、または他の多元接続技術を含む、任意の好適な多元接続技術をサポートするように構成され得る。ワイヤレスデバイス100は、例として、ロングタームエボリューション（LTE（登録商標））、エボリューションデータ・オプティマイズド（EV-DO）、ウルトラモバイル・ブロードバンド（UMB）、ユニバーサル地上無線アクセス（UTRA）、モバイル信用グローバルシステム（GSM（登録商標））、発展型UTRA（E-UTRA）、IEEE802.11（Wi-Fi（登録商標））、IEEE802.16（WiMAX（登録商標））、IEEE802.20、Flash-OFDM、Blueooth、または任意の他の好適なエアインターフェース規格を含む、任意の好適なエアインターフェース規格をサポートするようにさらに構成され得る。ワイヤレスデバイス100によってサポートされる実際のエアインターフェース規格お

40

50

より多元接続技術は、特定の適用例、およびシステムに課される全体的な設計制約に依存することになる。

【0018】

[0027] ワイヤレスデバイス 100 は、ベースバンドプロセッサ 102 と、ワイヤレストラんシーバ 104 と、アンテナ 106 を含む。ワイヤレストラんシーバ 104 は、送信機能と受信機能の両方をサポートするために 1 つまたは複数の LO 信号を生成するために、本開示全体にわたって提示される位相ロックループの様々な態様を採用し得る。ワイヤレストラんシーバ 104 は、アンテナ 106 を通したワイヤレスチャネルを介した送信のために、1 つまたは複数のキャリア信号を、ベースバンドプロセッサ 102 によって生成されたデータで変調することによって、送信機能を実行する。ワイヤレストラんシーバ 104 は、ベースバンドプロセッサ 102 によるさらなる処理のためにデータを復元するために、アンテナ 106 を通してワイヤレスチャネルから受信された 1 つまたは複数のキャリア信号を復調することによって、受信機能を実行する。ベースバンドプロセッサ 102 は、ワイヤレスチャネルへの物理および電気的インターフェースに従ってデータを送信および受信するための物理レイヤ、ワイヤレスチャネルへのアクセスを管理するためのデータリンクレイヤ、ソース・宛先間データ転送を管理するためのネットワークレイヤ、エンドユーザ間のデータの透過的な転送を管理するためのトランスポートレイヤ、ならびにワイヤレスチャネルを通してネットワークへの接続を確立またはサポートするために必要なまたは望ましい任意の他のレイヤを例として含む、ワイヤレス通信をサポートするために必要とされる基本プロトコルスタックを与える。

10

20

【0019】

[0028] 図 2 は、ワイヤレストラんシーバの例示的な実施形態のブロック図である。ワイヤレストラんシーバ 104 は、双方向通信をサポートする送信機 200 と受信機 250 とを含む。送信機 200 および / または受信機 250 は、スーパー・ヘテロダイン・アーキテクチャまたは直接変換アーキテクチャを用いて実装され得る。スーパー・ヘテロダイン・アーキテクチャでは、信号が、複数の段において RF とベースバンドとの間で、(たとえば、受信機について、1 つの段において RF から中間周波数 (IF) に、次いで別の段において IF からベースバンドに) 周波数変換される。ゼロ IF アーキテクチャとも呼ばれる直接変換アーキテクチャでは、信号が、1 つの段において RF とベースバンドとの間で周波数変換される。スーパー・ヘテロダイン・アーキテクチャおよび直接変換アーキテクチャは、異なる回路ブロックを使用し、および / または異なる要件を有し得る。図 2 に示されている例示的な実施形態では、送信機 200 および受信機 250 は直接変換アーキテクチャを用いて実装される。

30

【0020】

[0029] 送信経路では、ベースバンドプロセッサ 104 (図 1 参照) は、デジタル・アナログ変換器 (DAC) 202 にデータを与える。DAC 202 は、デジタル入力信号をアナログ出力信号に変換する。アナログ出力信号は、DAC 202 による前のデジタル・アナログ変換によって生じたイメージを除去するためにアナログ出力信号をフィルタ処理する、フィルタ 204 に与えられる。増幅器 206 が、増幅されたベースバンド信号を与えるために、フィルタ 204 からの信号を増幅するために使用される。ミキサ 208 が、増幅されたベースバンド信号と TX 局部発振器 210 からの LO 信号とを受信する。ミキサ 208 は、アップコンバートされた信号を与えるために、増幅されたベースバンド信号を LO 信号と混合する。フィルタ 212 が、周波数混合 (frequency mixing) によって生じたイメージを除去するために、アップコンバートされた信号をフィルタ処理するために使用される。電力増幅器 (PA) 214 が、所望の出力電力レベルにおける出力 RF 信号を取得するために、フィルタ 212 からの信号を増幅するために使用される。出力 RF 信号は、ワイヤレスチャネルを介した送信のために、デュプレクサ 260 を通してアンテナ 106 にルーティングされる。

40

【0021】

[0030] 受信経路では、アンテナ 106 は、リモートデバイスによって送信された信号を

50

受信し得る。受信RF信号は、デュプレクサ260を通して受信機250にルーティングされ得る。受信機250内で、受信RF信号は、入力RF信号を取得するために、低雑音増幅器(LNA)252によって増幅され、フィルタ254によってフィルタ処理される。ミキサ256が、入力RF信号と、RX局部発振器258からのLO信号とを受信する。ミキサ256は、ダウンコンバートされた信号を与えるために、入力RF信号をLO信号と混合する。ダウンコンバートされた信号は、増幅されたダウンコンバートされた信号を取得するために、増幅器260によって増幅される。フィルタ262が、周波数混合によって生じたイメージを除去するために、増幅されたダウンコンバートされた信号をフィルタ処理するために使用される。フィルタ262からの信号は、アナログ・デジタル変換器(ADC)264に与えられる。ADC264は、その信号をデジタル出力信号に変換する。デジタル出力信号は、ベースバンドプロセッサ104(図1参照)に与えられ得る。

#### 【0022】

[0031]送信機200および受信機250における信号の調整は、増幅器、フィルタ、ミキサなどの1つまたは複数の段によって実行され得る。これらの回路は、図2に示されている構成とは異なってアレンジされ(arranged)得る。さらに、図2に示されていない他の回路も送信機200および受信機250において信号を調整するために使用され得る。たとえば、インピーダンス整合回路が、PA216の出力において、LNA252の入力において、アンテナ106とデュプレクサ260との間などに配置され得る。

#### 【0023】

[0032]送信機および受信機機能をサポートするために、局部発振器の様々な実施形態が使用され得る。例示的な一実施形態では、局部発振器は、混合のために送信機および/または受信機にLO信号を与えるVCOを用いて実装され得る。VCOは、フィードバックループ中の同調共振器(tuned resonator)を有する正のフィードバック増幅器である。発振は共振周波数(resonant frequency)において生じ、共振周波数は位相ロックループによって同調させられ得る。位相ロックループは、VCO出力の位相を基準信号の位相と比較し、位相を整列された状態に保つようにVCOの共振器を同調させる、位相検出器を用いて実装され得る。

#### 【0024】

[0033]図3は、局部発振器のための位相ロックループの例示的な実施形態を示す機能ブロック図である。この実施形態では、局部発振器は、位相ロックループ300を用いて実装される。位相ロックループ300は、位相検出器302と、電荷ポンプ304と、ループフィルタ306と、VCO308と、周波数分割器312およびシグマデルタ変調器314を有するフラクショナルN周波数分割器(fractional-N frequency divider)310とを含む。位相検出器302は、2つの入力信号間の位相差を検出するための手段を与える。位相検出器302は、基準信号とフラクショナルN周波数分割器310からのフィードバック信号との間の位相誤差を検出するために使用される。位相検出器302は、位相誤差に基づいてアップ信号とダウン信号とを生成する。アップ信号およびダウン信号は、電荷ポンプ304を駆動するために使用される。電荷ポンプ304は、ループフィルタ306に電流源を与えるための手段を与える。電荷ポンプ304は、検出された位相誤差に比例する電荷をループフィルタ306に注入する。ループフィルタ306は、VCO308を同調させるための制御電圧を生成するための手段を与える。ループフィルタ306は、VCO308に入力される制御電圧を生成するために、電荷ポンプ304からの出力を積分する(integrate)。VCO308は、同調可能周波数を有する発振信号を生成するための手段を与える。VCO308は、その周波数が、ループフィルタ306によって生成された制御電圧に比例する発振信号を生成する。フラクショナルN周波数分割器310は、発振信号の周波数をフラクショナルに分割する(fractionally dividing)ことによって、フィードバック信号を生成するための手段を与える。フラクショナルN周波数分割器310は、位相検出器へのフィードバック信号入力を生成するために、VCO出力の周波数を整数Nで分割する周波数分割器312を含む。フラクショナルN周波数分割器3

10

20

30

40

50

10 はまた、N から N + 1 の間の非整数である平均分割器を実現するために、ロック状態中に (during the locked state) N の値を動的に切り替えるデルタシグマ変調器 314 を含む。

【0025】

[0034] 図 4 A は、電荷ポンプおよびループフィルタのための追加の概略図詳細をもつ、局部発振器のための位相ロックループの例示的な実施形態を示す機能ブロック図である。上記で説明したように、位相検出器 302 は、基準信号をフラクショナル N 周波数分割器 310 からのフィードバック信号と比較し、2 つの信号間の位相差に基づいて電荷ポンプ 304 をアクティブにする。位相検出器 302 は、位相検出モードおよび位相ロック状態において動作する。このために、位相検出器は、位相 / 周波数検出器 (PFD : phase/frequency detector) と呼ばれることがある。本開示では、「位相検出器」という用語は、2 つの入力信号の位相および / または周波数における差を検出することが可能な構成要素を含むように広く解釈されるものとする。

【0026】

[0035] 位相検出器 302 は、位相検出器 302 によって測定された位相誤差に基づいて、アップ信号およびダウン信号のデューティサイクルが変化させられる、位相検出モードにおいて動作する。その結果、電荷ポンプ 304 は、2 つの信号間の位相差に比例する、時間の一部分の間のみアクティブにされる。ループフィルタ 306 は、位相差が 0 に達するまで、VCO 出力信号の周波数を調整するフィルタ処理された制御電圧を生成する電荷を蓄積する。これが生じると、位相検出器 302 は位相ロック状態に入る。この状態では、アップ信号のデューティサイクルとダウン信号のデューティサイクルとは実質的に等しく、したがって、正味電荷 (net charge) はループフィルタ 306 に注入されない。VCO 308 への制御電圧入力は一定のままであり、それは、VCO 出力信号が一定の周波数のままであることを保証する。

【0027】

[0036] ループフィルタ 306 は、アクティブまたはパッシブであり得る。パッシブループフィルタ 306 の例示的な実施形態が、図 4 に示されている。この実施形態では、ループフィルタ 306 は、電荷ポンプ 304 出力と負電源電圧 V<sub>SS</sub> (たとえば、接地) との間に直列に接続された抵抗 R408 とキャパシタ C410 とを備える、1 次ループフィルタ (first order loop filter) を備える。ループフィルタの代替実施形態も採用され得る。たとえば、ループフィルタ 306 は、抵抗 R408 およびキャパシタ C410 に並列に接続された余分の極キャパシタ (extra pole capacitor) 409 を含み得る。

【0028】

[0037] 電荷ポンプ 304 は、いくつかの方法でも実装され得る。例示的な実施形態では、電荷ポンプ 304 は、充電電流 (a charge current) をループフィルタ 306 にソースする (sourcing) ための手段を与える第 1 のスイッチ 404 と、放電電流 (discharge current) をループフィルタ 306 からシンクする (sinking) ための手段を与える第 2 のスイッチ 406 とを用いて実装される。第 1 のスイッチ 404 は、PMOS トランジスタであり得、第 2 のスイッチ 406 は、NMOS トランジスタ 406 であり得る。PMOS トランジスタは、電流源 405 を介して正電源電圧 V<sub>DD</sub> に接続される。NMOS トランジスタは、図 4 A に示されているような電流源 407 を介して、負電源電圧 V<sub>SS</sub> に接続される。電流源 405 および 407 は、電荷ポンプ 304 に定電流源を与える。位相検出器 302 からのアップ信号は、インバータ 402 を通して PMOS トランジスタ 404 を制御し、位相検出器 302 からのダウン信号は、NMOS トランジスタ 406 を制御する。アップ信号が位相検出器 302 によって高論理レベル状態に駆動されるとき、ループフィルタ 306 中のキャパシタ C410 は PMOS トランジスタ 404 を通して充電される。ダウン信号が位相検出器 302 によって高論理レベル状態に駆動されるとき、ループフィルタ 306 中のキャパシタ C410 は NMOS トランジスタ 406 を通して放電される。余分の極キャパシタ 409 は、ループフィルタ 306 をさらに調整するために、抵抗 R408 およびキャパシタ C410 と並列に追加される。

10

20

30

40

50

## 【0029】

[0038]図4Bは、電荷ポンプ中の漏れ電流源を追加した、図4Aの局部発振器のための位相ロックループの例示的な実施形態を示す機能ブロック図である。漏れ電流源は、ループフィルタ306に漏れ電流を与えるための手段を与える。この実施形態では、フラクショナルN位相ロックループ(fractional-N phase locked loop)における電荷ポンプ302の非線形性により場合によっては生じるであろう近傍オフセット周波数(close-in offset frequencies)におけるデルタシグマ変調器の雑音重畠(noise folding)を回避するために、漏れ電流源410が使用される。漏れ電流源412は、適切なバイアシング(appropriate biasing)をもつ1つまたは複数のトランジスタを用いて、または他の好適な手段によって実装され得る。漏れ電流源410は、ロック状態にある位相検出器302に入力される基準信号とフィードバック信号との間の一定の平均位相差を生じさせる。その結果、漏れ電流がどのように実装されるかに応じて、アップ信号またはダウン信号のうちの一方が他方よりも高いデューティサイクルを常に有する。いくつかの実施形態では、より広いパルスが位相差に等しい幅を維持する間、より狭いパルスが連続的「低」論理状態に駆動され得る。この手法では、電荷ポンプ302において電流源のスイッチングがなく、それにより、雑音を減少させる。10

## 【0030】

[0039]図5は、位相ロックループのための位相検出器の例示的な実施形態を示す機能ブロック図である。この実施形態では、位相検出器302は、2つの段、すなわち第1の段502と第2の段504とを含む。第1の段502は、基準信号とフィードバック信号との間の位相差に基づいて、アップ信号とダウン信号とを生成する。第2の段504は、アップ信号またはダウン信号のどの信号がより低いデューティサイクルを有するかに応じて、アップ信号またはダウン信号のいずれかを低論理状態(low logic state)に駆動する。20

## 【0031】

[0040]第1の段502は、第1のフリップフロップ506と、第2のフリップフロップ508と、リセットゲート510と、遅延511とを含む。この実施形態では、フリップフロップ506とフリップフロップ508の両方がDフリップフロップであり、リセットゲート510がANDゲートであるが、代替実施形態では、他のフリップフロップ、ゲート、および/または構成要素が使用、追加、および/または省略され得る。フリップフロップ506とフリップフロップ508の両方への入力は、V<sub>DD</sub>(すなわち、高論理状態(high logic state))にプルアップされる。第1のフリップフロップ506をクロック制御する(clock)ために基準信号が使用され、第2のフリップフロップ508をクロック制御するためにフィードバックが使用される。その結果、基準信号が高論理状態に遷移するとき、第1のフリップフロップ506の出力Q1が高論理状態に駆動され、フィードバック信号が高論理状態に遷移するとともに、第2のフリップフロップ508の出力Q2が高論理状態に駆動される。リセットゲート510は、フリップフロップ506および508からの2つの出力のための「AND」機能を与えるために使用される。フリップフロップ506からの出力とフリップフロップ508からの出力の両方が、適切な遅延の後に高論理状態に入ると、フリップフロップ506とフリップフロップ508の両方をリセットするために、リセットゲート510からの出力が使用される。30

## 【0032】

[0041]第2の段504は、第1のゲート512と、第2のゲート514と、第1のインバータ516と、第2のインバータ518とを備える、ゲーティング回路(gating circuit)を含む。第1のゲート512は、アップ信号を生成するために使用され、第2のゲート514は、ダウン信号を生成するために使用される。一実施形態では、ゲート512とゲート514の両方がANDゲートであるが、代替実施形態では異なって実装され得る。たとえば、各ゲートは、代替的に、他の好適な手段によって、またはインバータによって統かれるNANDゲートとして実装され得る。各ゲート512および514は、第2の入力が高論理状態にあるとき、第1の入力における信号を出力にパスするように機能する。40

したがって、各ゲート 512 および 514 への第 2 の入力は、イネーブル信号と見なされ得る。すなわち、イネーブル信号が高論理状態にあるとき、各ゲート 512 および 514 は第 1 の入力における信号を出力にパスする。イネーブル信号が低論理状態にあるとき、出力は第 1 の入力の状態にかかわらず低く強制される (forced low)。第 1 のインバータ 516 および第 2 のインバータ 518 は、イネーブル信号を生成するために使用される。詳細には、第 1 のインバータ 516 は、第 1 のゲート 512 へのイネーブル信号を生成するために使用され、第 2 のインバータ 518 は、第 2 のゲート 514 へのイネーブル信号を生成するために使用される。説明する実施形態では、第 1 のゲート 512 のためのイネーブル信号は、第 2 のフリップフロップ 508 の反転出力 (inverted output) Q2 であり、第 2 のゲート 514 のためのイネーブル信号は、第 1 のフリップフロップ 506 の反転出力 Q1 である。

#### 【0033】

[0042]動作中、第 2 のフリップフロップ 508 からの出力 Q2 が低論理状態にあるとき、第 1 のフリップフロップ 506 からの出力 Q1 がアップ信号として第 1 のゲート 512 を通してパスされる。第 2 のフリップフロップ 508 からの出力 Q2 が高論理状態にあるとき、第 1 のゲート 512 から出力されたアップ信号が低論理状態に強制される。同様に、第 1 のフリップフロップ 506 からの出力 Q1 が低論理状態にあるとき、第 2 のフリップフロップ 508 からの出力 Q2 がダウン信号として第 2 のゲート 514 を通してパスされる。第 1 のフリップフロップ 506 からの出力 Q1 が高論理状態にあるとき、第 2 のゲート 514 から出力されたダウン信号が低論理状態に強制される。

#### 【0034】

[0043]図 6 A および図 6 B は、図 5 の位相ロックループの例示的な実施形態の動作を示すタイミング図である。図 6 A に、基準信号が周波数分割器からのフィードバック信号に先行するときの、位相検出器のタイミングを示す。図 6 B に、基準信号がフィードバック信号に後続するときの、位相検出器のタイミングを示す。

#### 【0035】

[0044]図 5 および図 6 A を参照すると、第 1 のフリップフロップ 506 からの出力 Q1 と第 2 のフリップフロップ 508 からの出力 Q2 の両方が、 $t_0$ において低論理状態にある。その結果、第 1 のゲート 512 と第 2 のゲート 514 の両方は、それぞれ、インバータ 516 および 518 からの反転されたフリップフロップ出力 Q1 および Q2 によって有効にされる。第 1 のゲート 512 が有効にされると、低論理状態におけるアップ信号を生成するために、第 1 のフリップフロップ 506 からの低論理状態出力 Q1 が第 1 のゲート 512 を通して出力にパスされる。第 2 のゲート 514 が有効にされると、低論理状態におけるダウン信号を生成するために、第 2 のフリップフロップ 506 からの低論理状態出力 Q2 が第 2 のゲート 514 を通して出力にパスされる。

#### 【0036】

[0045]  $t_1$ において、基準信号が低論理状態から高論理状態に遷移し、それにより、第 1 のフリップフロップ 506 の出力 Q1 を高論理状態に設定する。アップ信号を高論理状態に駆動するために、高論理状態が第 1 のゲート 512 を通して出力にパスされる。同時に、第 2 のインバータ 518 からの反転されたフリップフロップ出力 Q1 が低論理状態に遷移し、それにより、第 2 のゲート 514 を無効にする。

#### 【0037】

[0046]  $t_2$ において、フィードバック信号が低論理状態から高論理状態に遷移し、それにより、第 2 のフリップフロップ 508 の出力 Q2 を高論理状態に設定する。第 2 のゲート 514 が無効にされるので、第 2 のフリップフロップ 508 からの出力 Q2 の高論理状態は第 2 のゲート 514 を通してパスされない。その結果、ダウン信号は、低論理状態にあるままである。第 1 のインバータ 516 からの反転されたフリップフロップ出力 Q2 が低論理状態に遷移し、それにより、第 1 のゲート 512 を無効にし、アップ信号を低論理状態に強制する。出力 Q1 と出力 Q2 の両方が高論理状態にあると、リセットゲート 510 からの出力は、高論理状態に遷移し、 $t_3$ において適切な遅延の後にフリップフロップ

10

20

30

40

50

506とフリップフロップ508の両方をリセットする。フリップフロップ506とフリップフロップ508の両方がリセットされると、インバータ516および518からの反転されたフリップフロップ出力Q1およびQ2が高論理状態に駆動され、それにより、次のサイクルの間、第1のゲート512と第2のゲート514の両方を有効にする。このプロセスは、フィードバック信号を基準信号に整列させることによって位相ロックループがロックを達成するまで続く。

【0038】

[0047]図5および図6Bを参照すると、第1のフリップフロップ506からの出力Q1と第2のフリップフロップ508からの出力Q2の両方は、 $t_0$ において低論理状態にある。その結果、第1のゲート512と第2のゲート514の両方は、それぞれ、インバータ516および518からの反転されたラッチ出力(inverted latch outputs)Q1およびQ2によって有効にされる。第1のゲート512が有効にされると、低論理状態におけるアップ信号を生成するために、第1のフリップフロップ506からの低論理状態出力Q1が第1のゲート512を通して出力にバスされる。第2のゲート514が有効にされると、低論理状態におけるダウン信号を生成するために、第2のフリップフロップ506からの低論理状態出力Q2が第2のゲート514を通して出力にバスされる。

【0039】

[0048] $t_1$ において、フィードバック信号が低論理状態から高論理状態に遷移し、それにより、第2のフリップフロップ508の出力Q2を高論理状態に設定する。ダウン信号を高論理状態に駆動するために、高論理状態が第2のゲート514を通して出力にバスされる。同時に、第1のインバータ516からの反転されたフリップフロップ出力Q2が低論理状態に遷移し、それにより、第1のゲート512を無効にする。

【0040】

[0049] $t_2$ において、基準信号が低論理状態から高論理状態に遷移し、それにより、第1のフリップフロップ506の出力Q1を高論理状態に設定する。第1のゲート512が無効にされるので、第1のフリップフロップ506からの出力Q1の高論理状態は第1のゲート512を通してバスされない。その結果、アップ信号は、低論理状態にあるままである。第2のインバータ518からの反転されたフリップフロップ出力Q1が低論理状態に遷移し、それにより、第2のゲート514を無効にし、ダウン信号を低論理状態に強制する。出力Q1と出力Q2の両方が高論理状態にあると、リセットゲート510からの出力は、高論理状態に遷移し、 $t_3$ において適切な遅延の後にフリップフロップ506とフリップフロップ508の両方をリセットする。フリップフロップ506とフリップフロップ508の両方がリセットされると、インバータ516および518からの反転されたフリップフロップ出力Q1およびQ2が高論理状態に駆動され、それにより、次のサイクルの間、第1のゲート512と第2のゲート514の両方を有効にする。このプロセスは、フィードバック信号を基準信号に整列させることによって位相ロックループがロックを達成するまで続く。

【0041】

[0050]図7は、位相ロックループのための位相検出器の代替の例示的な実施形態を示す機能プロック図である。この実施形態では、第2の段におけるインバータは、NANDゲートと交換される。詳細には、第1のインバータ516(図5参照)が第1のNANDゲート716と交換され、第2のインバータ518(図5参照)が第2のNANDゲート718と交換される。NANDゲート716および718は、モードビットが2つの異なる動作モード間で位相検出器302を切り替えることを可能にする。モードビットが高論理状態に設定されると、NANDゲート716および718はインバータとして機能し、位相検出器の動作が、図5、図6Aおよび図6Bに関して上記で説明したのと同じである。モードビットが低論理状態に駆動されると、NANDゲート716とNANDゲート718の両方からの出力は、それぞれ、第1のフリップフロップ506の出力Q1および第2のフリップフロップ508の出力Q2の状態にかかわらず、常に高論理状態にある。その結果、第1のゲート512および第2のゲート514が常に有効にされる。ゲート512

10

20

30

40

50

とゲート 514 の両方が有効にすると、アップ信号が第 1 のフリップフロップ 506 からの出力 Q1 に後続し (follow) 、ダウン信号が第 2 のフリップフロップ 508 からの出力 Q2 に後続する。このモードでは、アップ信号とダウン信号の両方が、各サイクル、パルス化される (pulsed each cycle) ことになる。

【0042】

[0051] ここまで説明した位相検出器の例示的な実施形態では、より低いデューティサイクルをもつアップ信号またはダウン信号は、ゲートオフされる (gated off) (すなわち、低論理状態に強制される)。しかしながら、より低いデューティサイクルをもつ信号は、ゲーティング以外の手段によって低論理状態に強制され得る。たとえば、ダウン信号に対するアップ信号のデューティサイクルに応じてアップ信号と低論理状態との間で切り替えるために、マルチプレクサが使用され得る。同様に、アップ信号に対してダウン信号のデューティサイクルに応じてダウン信号と低論理状態との間で切り替えるために、マルチプレクサが使用され得る。代替的に、いくつかの例示的な実施形態では、より低いデューティサイクルをもつアップ信号またはダウン信号は、信号を高論理状態に駆動することによってオフにされ (turned off) 得る。当業者は、特定の適用例とシステムに課される全体的な設計制約とに応じて、最も低いデューティサイクルをもつアップ信号またはダウン信号のターンオフ (turn off) を強制するように、様々な回路構成を容易に設計することができよう。

【0043】

[0052] 図 8 は、発振信号を生成する例示的な方法を示すフローチャートである。

20

【0044】

[0053] 方法は、ブロック 802 において、2 つの入力信号間の位相差を検出することを含む。位相差は、位相差に応答して第 1 および第 2 の信号を出力することによって検出され得、ここで、第 2 の信号を出力するときに第 1 の信号が無効にされ、第 1 の信号を出力するときに第 2 の信号が無効にされる。例示的な一実施形態では、第 2 の信号を出力するときに第 1 の信号を無効にすることと、第 1 の信号を出力するときに第 2 の信号を無効にすることとを行うために、ゲーティング回路が使用され得る。2 つの入力信号は、基準信号とフィードバック信号とを備え得る。フィードバック信号は、発振信号の関数である。例示的な一実施形態では、フィードバック信号は、発振信号の周波数をフラクショナルに分割することによって生成され得る。

30

【0045】

[0054] 方法は、ブロック 804 において、第 1 の信号および第 2 の信号に応答して、同調可能周波数を有する発振信号を生成することをさらに含む。発振信号の周波数を同調させるために、制御電圧が使用され得る。制御電圧を生成するために、電流源が使用され得る。電流源は、第 1 の信号に応答して充電電流をソースし、第 2 の信号に応答して放電電流をシンクし得る。制御電圧は、充電電流および放電電流を積分することによって生成され得る。制御電圧の生成において漏れ電流源も使用され得る。

【0046】

[0055] 上記で説明した動作方法におけるブロックの特定の順序または階層は、一例として与えられたにすぎない。設計選好に基づいて、動作方法におけるブロックの特定の順序または階層は、並べ替えられ、修正され、および / または変更され得る。添付の方法クレームは、動作方法に関係する様々な限定を含むが、具陳された限定は、特許請求の範囲において明記されていない限り、特定の順序または階層によっていかなる形でも限定されるものではない。

40

【0047】

[0056] 以上の説明は、いかなる当業者も本開示の全範囲を完全に理解することができるよう与えたものである。本明細書で開示する様々な例示的な実施形態への変更は当業者には容易に明らかであろう。したがって、特許請求の範囲は、本明細書で説明した本開示の様々な態様に限定されるべきではなく、特許請求の範囲の言い回しに矛盾しない全範囲を与えられるものとする。当業者に知られている、または後に知られることになる、本開

50

示全体にわたって説明した様々な態様の要素のすべての構造的および機能的均等物は、参照により本明細書に明確に組み込まれ、特許請求の範囲に包含されるものである。さらに、本明細書で開示するいかなることも、そのような開示が特許請求の範囲に明示的に具陳されているかどうかにかかわらず、公に供するものではない。いかなるクレーム要素も、その要素が「ための手段」という句を使用して明確に具陳されていない限り、または方法クレームの場合には、その要素が「ためのステップ」という句を使用して具陳されていない限り、米国特許法第112条( f )の規定の下で解釈されるべきではない。

以下に、本願の出願当初の特許請求の範囲に記載された発明を付記する。

[ C 1 ]

10

発振信号を生成するための回路であって、

2つの入力信号間の位相差に応答して第1の信号および第2の信号を出力するように構成された位相検出器と、前記位相検出器が、前記第2の信号を出力するときに前記第1の信号を無効にすることと、前記第1の信号を出力するときに前記第2の信号を無効にすることを行なうようにさらに構成された、

前記第1の信号および前記第2の信号に応答して、同調可能周波数を有する発振信号を生成するように構成された電圧制御発振器( VCO )と

を備える、回路。

[ C 2 ]

20

電荷ポンプとループフィルタとをさらに備え、ここにおいて、前記電荷ポンプが、前記第1の信号に応答して充電電流をソースすることと、前記第2の信号に応答して放電電流をシンクすることによって前記ループフィルタに電流源を与えるように構成された、 C 1 に記載の回路。

[ C 3 ]

前記ループフィルタが、前記 VCO の前記周波数を同調させるための制御電圧を生成するために、前記充電電流および前記放電電流を積分するように構成された、 C 2 に記載の回路。

[ C 4 ]

30

前記電荷ポンプが、前記ループフィルタに結合された漏れ電流源をさらに備える、 C 2 に記載の回路。

[ C 5 ]

前記位相検出器が、前記第2の信号を出力するときに前記第1の信号を無効にすることと、第1の信号を出力するときに前記第2の信号を無効にすることを行なうように構成されたゲーティング回路を備える、 C 1 に記載の回路。

[ C 6 ]

前記2つの入力信号が、基準信号とフィードバック信号とを備え、前記フィードバック信号が、前記発振信号から導出される、 C 1 に記載の回路。

[ C 7 ]

40

前記発振信号から前記フィードバック信号を生成するように構成されたフラクショナル N 分割器をさらに備える、 C 6 に記載の回路。

[ C 8 ]

発振信号を生成するための回路であって、

2つの入力信号間の位相差を検出するための手段と、ここにおいて、位相差を検出するための前記手段が、2つの入力信号間の前記位相差に応答して第1の信号および第2の信号を出力するように構成され、ここにおいて、位相差を検出するための前記手段が、前記第2の信号を出力するときに前記第1の信号を無効にすることと、前記第1の信号を出力するときに前記第2の信号を無効にすることを行なうようにさらに構成された、

前記第1の信号および前記第2の信号に応答して、同調可能周波数を有する発振信号を生成するための手段と

を備える、回路。

50

## [ C 9 ]

前記発振信号の前記周波数を同調させるための制御電圧を生成するための手段、前記第1の信号に応答して充電電流をソースするための手段および前記第2の信号に応答して放電電流をシンクするための手段を備える制御電圧を生成するための前記手段に電流源を与えるための手段、をさらに備える、C 8 に記載の回路。

## [ C 10 ]

制御電圧を生成するための前記手段が、前記発振信号の前記周波数を同調させるための前記制御電圧を生成するために、前記充電電流および前記放電電流を積分するように構成された、C 9 に記載の回路。

## [ C 11 ]

電流源を与えるための前記手段が、制御電圧を生成するための前記手段に漏れ電流を与えるための手段をさらに備える、C 9 に記載の回路。

10

## [ C 12 ]

位相差を検出するための前記手段が、前記第2の信号を出力するときに前記第1の信号を無効にすることと、第1の信号を出力するときに前記第2の信号を無効にすることを行なうように構成されたゲーティング回路を備える、C 8 に記載の回路。

## [ C 13 ]

前記2つの入力信号が、基準信号とフィードバック信号とを備え、前記フィードバック信号が、前記発振信号の関数である、C 8 に記載の回路。

## [ C 14 ]

前記発振信号の前記周波数をフラクショナルに分割することによって、前記フィードバック信号を生成するための手段をさらに備える、C 13 に記載の回路。

20

## [ C 15 ]

発振信号を生成する方法であって、

2つの入力信号間の位相差を検出することと、前記検出することが、第2の信号を出力するときに第1の信号を無効にすることと、前記第1の信号を出力するときに前記第2の信号を無効にすることによって、2つの入力信号間の前記位相差に応答して前記第1の信号および前記第2の信号を出力することを備える、

前記第1の信号および前記第2の信号に応答して、同調可能周波数を有する発振信号を生成することと

30

を備える、方法。

## [ C 16 ]

前記発振信号の前記周波数を同調させるための制御電圧を生成することと、前記第1の信号に応答して充電電流をソースすることと、前記第2の信号に応答して放電電流をシンクすることによって、前記制御電圧を生成するための電流源を与えることとをさらに備える、C 15 に記載の方法。

## [ C 17 ]

制御電圧を前記生成することが、前記充電電流および前記放電電流を積分することを備える、C 16 に記載の方法。

## [ C 18 ]

制御電圧を前記生成することに漏れ電流を与えることをさらに備える、C 16 に記載の方法。

40

## [ C 19 ]

位相差を前記検出することが、前記第2の信号を出力するときに前記第1の信号を無効にすることと、第1の信号を出力するときに前記第2の信号を無効にすることを行なうためにゲーティング回路を使用することを備える、C 15 に記載の方法。

## [ C 20 ]

前記2つの入力信号が、基準信号とフィードバック信号とを備え、前記フィードバック信号が、前記発振信号の関数である、C 15 に記載の方法。

## [ C 21 ]

50

前記発振信号の前記周波数をフラクショナルに分割することによって、前記フィードバック信号を生成することをさらに備える、C 2 0 に記載の方法。

【図 1】

図 1

FIG. 1

【図 2】

図 2

FIG. 2

【 义 3 】

図 3

FIG. 3

【図4A】

図 4A

FIG. 4A

### 【図4B】

図 4B

FIG. 4B

【図5】

図 5

5

FIG.

【図 6 A】

図 6A

【図 6 B】

図 6B

【図 7】

図 7

【図 8】

図 8

---

フロントページの続き

(72)発明者 ワン、シェン

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドラ

イブ 5775、クワアルコム・インコーポレイテッド気付

(72)発明者 ヤン、ジョンシク

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドラ

イブ 5775、クワアルコム・インコーポレイテッド気付

(72)発明者 ヌゲイエン、シン・カト

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドラ

イブ 5775、クワアルコム・インコーポレイテッド気付

(72)発明者 ピカッキ、アラ

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドラ

イブ 5775、クワアルコム・インコーポレイテッド気付

(72)発明者 サブラ、アヌプ

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドラ

イブ 5775、クワアルコム・インコーポレイテッド気付

審査官 高 橋 徳浩

(56)参考文献 特開平07-142966 (JP, A)

特開2001-230668 (JP, A)

特開2004-120443 (JP, A)

特開2005-260866 (JP, A)

米国特許出願公開第2003/0231729 (US, A1)

特開平05-129946 (JP, A)

特開2000-349625 (JP, A)

特開2008-219815 (JP, A)

特開昭56-001619 (JP, A)

特開平04-326624 (JP, A)

特表2008-515344 (JP, A)

米国特許出願公開第2009/0160487 (US, A1)

特開平06-152396 (JP, A)

国際公開第2007/060756 (WO, A1)

(58)調査した分野(Int.Cl. , DB名)

H03L1/00 - H03L9/00

H03K5/00 - H03K99/00