(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第5176050号

(P5176050)

(45) 発行日 平成25年4月3日(2013.4.3)

(24) 登録日 平成25年1月18日(2013.1.18)

(51) Int.Cl.

F 1

|              |           |

|--------------|-----------|

| HO1L 21/822  | (2006.01) |

| HO1L 27/04   | (2006.01) |

| HO1L 21/3205 | (2006.01) |

| HO1L 21/768  | (2006.01) |

| HO1L 23/522  | (2006.01) |

|            |

|------------|

| HO1L 27/04 |

| HO1L 21/88 |

|   |

|---|

| R |

| S |

請求項の数 11 (全 15 頁)

(21) 出願番号

特願2001-261004 (P2001-261004)

(22) 出願日

平成13年8月30日 (2001.8.30)

(65) 公開番号

特開2002-158290 (P2002-158290A)

(43) 公開日

平成14年5月31日 (2002.5.31)

審査請求日

平成20年8月21日 (2008.8.21)

(31) 優先権主張番号

09/650604

(32) 優先日

平成12年8月30日 (2000.8.30)

(33) 優先権主張国

米国(US)

(73) 特許権者

500587067

アギア システムズ インコーポレーテッド

アメリカ合衆国、18109 ペンシルヴァニア、アレンタウン、アメリカン・パークウェイ エヌイー 1110

(74) 代理人

100094112

弁理士 岡部 譲

(74) 代理人

100106183

弁理士 吉澤 弘司

(74) 代理人

100064447

弁理士 岡部 正夫

(74) 代理人

100085176

弁理士 加藤 伸晃

最終頁に続く

(54) 【発明の名称】 上に増加したルート形成領域を有するフィールドプレート抵抗

## (57) 【特許請求の範囲】

## 【請求項 1】

- フィールドプレート抵抗を有する集積回路であって、該フィールドプレート抵抗は、

a、半導体基板中に形成され、第1および第2の接触領域を有する抵抗基体と、

b、該抵抗基体上の第1の絶縁性層であって、該抵抗基体上に位置し、頂部表面および底部表面を有する第1の絶縁性層と、

c、該第1の絶縁性層中の接触窓であって、該第1の絶縁性層の頂部表面から該第1の絶縁性層を通して該抵抗基体まで延びる接触窓と、

d、該第1の絶縁性層上にあり、それと同延するフィールドプレートであって、頂部表面および底部表面を有し、底部表面の一部分が該第1の絶縁性層中の該接触窓を通して延び、該抵抗基体の該第1の接触領域と接触するようになっているフィールドプレートと、

e、第2の絶縁性層であって、その第1の部分が少なくとも該フィールドプレートを被覆する第2の絶縁性層と、

f、該フィールドプレートの該頂部表面への電気的接触と、

g、該抵抗基体の第2の接触領域への電気的接触であって、該フィールドプレートから電気的に絶縁されている電気的接触と、

h、該第2の絶縁性層の該第1の部分上に形成される複数の金属導電体と、

から成る集積回路であって、構成要素f、gおよびhが、单一の金属層から成る集積回路。

## 【請求項 2】

10

20

請求項 1 に記載の集積回路において、

該フィールドプレートが、ポリシリコンから成る集積回路。

**【請求項 3】**

請求項 2 に記載の集積回路において、

該第 1 および第 2 の絶縁性層が  $\text{SiO}_2$  である集積回路。

**【請求項 4】**

請求項 2 に記載の集積回路において、さらに、

該フィールドプレートのまわりに形成された絶縁性スペーサを有する集積回路。

**【請求項 5】**

請求項 2 に記載の集積回路において、

該フィールドプレートの頂部表面への電気的接触が、障壁層から成る集積回路。

**【請求項 6】**

請求項 5 に記載の集積回路において、

該抵抗基体の第 2 の接触領域への電気的接触が、障壁層から成る集積回路。

**【請求項 7】**

請求項 1 に記載の集積回路において、

該フィールドプレートの頂部表面への電気的接触が、該第 1 の絶縁性層中の接触窓を通して延び、該抵抗基体の第 1 の接触領域と接触する該フィールドプレートの底部表面の該一部分の上にある集積回路。

**【請求項 8】**

フィールド抵抗を有する集積回路を製作する方法であって、

a、第 1 および第 2 の接触領域を有する抵抗基体を、半導体基板中に形成する工程と、

b、第 1 の絶縁性層であって、頂部表面と底部表面を有する第 1 の絶縁性層を該抵抗基体上に形成する工程と、

c、該第 1 の絶縁性層中に、該第 1 の絶縁性層の頂部表面から該第 1 の絶縁性層を通して該抵抗基体まで延びる接触窓を形成する工程と、

d、該第 1 の絶縁性層上にあり、それと同延するフィールドプレートであって、頂部表面および底部表面を有し、該底部表面の一部分が該第 1 の絶縁性層中の接触窓を通して該抵抗基体の該第 1 の接触領域と接触するフィールドプレートを形成する工程と、

e、第 2 の絶縁性層を堆積する工程であって、該第 2 の絶縁性層の第 1 の部分が、少なくとも該フィールドプレートを被覆している工程と、

f、金属層を堆積する工程と、

g、( i ) 該フィールドプレートの頂部表面に対する電気的接触と、

( ii ) 該抵抗基体の該第 2 の接触領域に対する電気的接触であって、該フィールドプレートから電気的に絶縁される電気的接触と、

( iii ) 該第 2 の絶縁性層の該第 1 の部分上に形成される複数の金属導電体と、を形成するために該金属層をパターン化する工程と、を含む方法。

**【請求項 9】**

請求項 8 に記載の方法において、

該フィールドプレートが、ポリシリコンから成る方法。

**【請求項 10】**

請求項 9 に記載の方法において、

該第 1 および第 2 の絶縁性層が、 $\text{SiO}_2$  である方法。

**【請求項 11】**

請求項 10 に記載の方法において、さらに

該フィールドプレートのまわりに形成される絶縁性スペーサを形成する工程を含む方法。

**【発明の詳細な説明】**

**【0001】**

**技術分野**

10

20

30

40

50

本発明は一般的には半導体プロセス技術、より具体的には、フィールドプレート抵抗上に最大ルートを形成するためのフィールドプレート抵抗に関する。

### 【0002】

#### 本発明の背景

半導体基板上に抵抗を作製する各種の方法が知られている。米国特許第4,140,817号、5,548,268号、5,683,928号、5,976,392号、5,989,970号、6,069,398号及び6,093,596号は、ここに参照文献として含まれており、抵抗の作製方法を明らかにしている。

### 【0003】

集積回路中で、トレースのような金属は、高シート抵抗値の拡散抵抗の基体上を通り、トレースに電圧が印加された時、抵抗の抵抗値に変化を生じさせる可能性がある。トレース上の電圧は、トレース下の抵抗領域を反転、空乏又は蓄積にする可能性があり、望ましくない。

10

### 【0004】

1つの解決法は、その問題を軽減するために、抵抗上に金属導体のルートを形成しないことであった。しかし、この技術では、価値のある面積を無駄に使い、この技術を用いた集積回路基体を、金属導電体のルートを形成するために抵抗上の面積を用いた集積回路基体より、面積的に大きくする。

### 【0005】

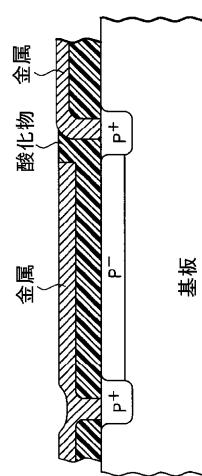

図18に示される別の解は、抵抗基体上に抵抗接触の最初の1つに接觸する金属トレースを延ばすことであった。フィールドプレートとして知られる金属延長部は、レイアウト、設計及び作製則が許すように、第2の抵抗に接続される金属まで、ほぼ延びる。このようにして、第1の抵抗に印加された電圧は、抵抗基体上のフィールドプレートにも印加される。第2の抵抗接觸は、別の電位に接続される。しかし、第1の接觸及びフィールドプレートに印加された電圧のために、抵抗の抵抗値の変化は残り、少くともその電圧は知られている。金属フィールドプレートを用いる欠点は、接觸領域を除く抵抗基体上の領域が、抵抗への接觸と同じ金属層中に、他の金属導電体のルート形成に使えないことである。もちろん、当業者にはよく知られているように、金属導電体は金属のより高い層中で、抵抗基体上でルート形成することはできる。

20

### 【0006】

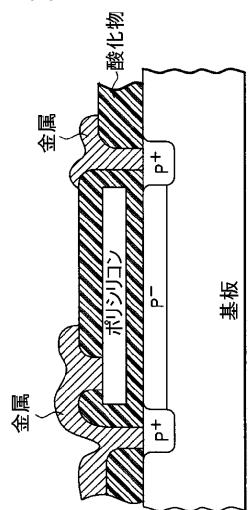

図19に示された更に別の解は、抵抗の基体上にポリシリコンフィールドプレートを形成することである。抵抗接觸の第1の接觸に接続される金属トレースはまた、ポリシリコンフィールドプレートにも接続される。この技術を用いると、抵抗の基体上の領域の一部が、抵抗への接觸と同じ金属層で、他の金属導体のルート形成に使える。抵抗接觸の最初の1つに接続された金属は、ポリシリコンフィールドプレートと第2の接觸を作るから、ポリシリコンフィールドプレートと接觸する領域は、ポリシリコンとの接觸の近くのいずれの領域とともに、レイアウト、設計及び作製則のため、抵抗への接觸と同じ金属層中で、他の金属導電体のルート形成に使うことはできない。

30

### 【0007】

必要なことは、抵抗の基体上の本質的にすべての領域を、レイアウト、設計及び作製則が、抵抗への接觸と同じ金属層で、金属導電体のルート形成に使えるようにするフィールドプレート抵抗である。

40

### 【0008】

#### 本発明の要約

本発明に従うと、集積回路は抵抗への接觸と同じ金属層中に形成された金属導電体のルートを形成するための増加した領域をその上有するフィールドプレート抵抗を含み、一連のプロセス工程で作製される。抵抗基体と各端部の接觸領域を有する抵抗は、半導体基板の活性領域中に形成される。絶縁材料の第1の層が抵抗上に形成され、第1の接觸領域を形成するため、絶縁性材料の第1の層を通して、抵抗基体まで窓が開けられる。フィールドプレートを規定するために、第1の絶縁層の上にポリシリコンの層が形成され、ポリシ

50

リコンフィールドプレートは抵抗の第1の接触領域と連続し、レイアウト、設計及び作製則で許されるように、抵抗基体上を本質的に他の接触領域まで延びる。第2の絶縁層が、ポリシリコン層上に形成される。ポリシリコンフィールドプレート及び第2の接触領域に接続するため、第2の絶縁層中に窓を開ける。抵抗への接触と同じ金属層中に形成された金属導電体のルートを形成するために、増加した領域を有するフィールドプレート抵抗のポリシリコンフィールドプレート上に、導電体を形成するために、金属層を形成し、不要な金属をエッティング除去する。

#### 【0009】

##### 詳細な記述

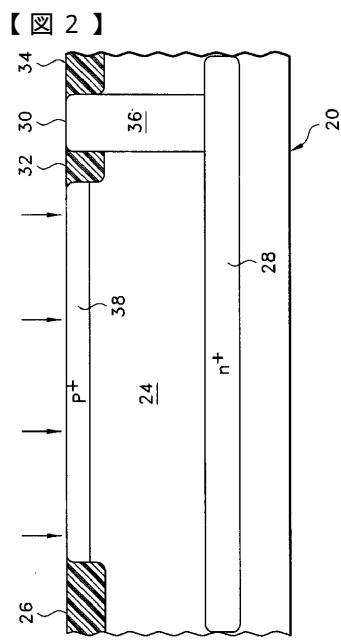

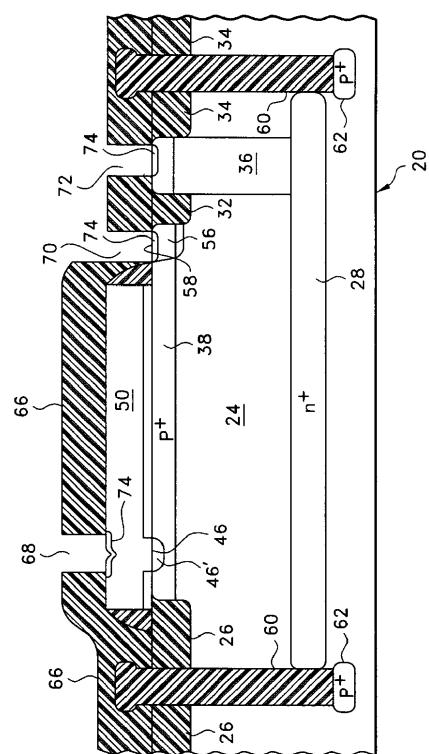

図1ないし16は、抵抗への接触と同じ金属層中に形成された金属導電体のルートを形成するための領域を上にもつフィールドプレート抵抗(22)の作製方法における工程を示すウエハ又は半導体基板(20)の一連の断面図である。好ましい実施例において、半導体基板はシリコンであるが、本発明はそれに限定されない。他の周知の半導体を用いてよい。 $p$ 形シリコン抵抗の作製について示されているが、本発明はそれに限定されない。ここで述べる方法は、金属の第1層中に作製された金属接触を有する半導体基板中に、フィールドプレート抵抗を作製することを示しているが、本発明は金属のより高い層中に作製された金属接触を有するフィールドプレート抵抗を作製するために用いることができる。

10

#### 【0010】

図1に示されるように、フィールドプレート抵抗(22)が中に作製されることになるタブ又は活性領域(24)が、半導体基板(20)中に形成される。活性領域(24)への $n^+$ 注入工程と、たとえば化学気相堆積プロセスにより、約1ミクロン厚のシリコンのエピタキシャル層を成長させることによって、基板(20)の上部表面(30)の下に、埋込み $n^+$ 層(28)が生じる。活性領域(24)の大きさ及び形は、中に含まれるフィールドプレート抵抗を含むデバイスの数とともに、その中に作製すべきフィールドプレート抵抗の大きさに依存する。

20

#### 【0011】

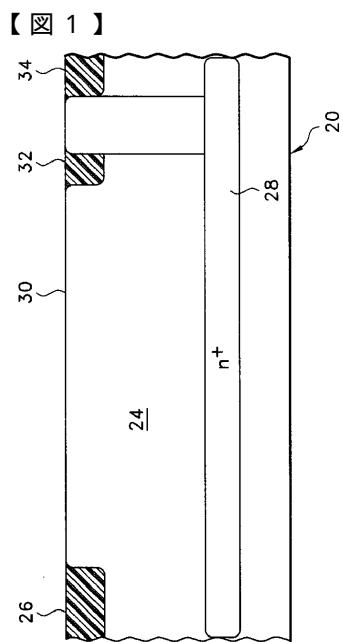

全面のエッティング工程により、基板(20)の上部表面(30)から酸化物(図示されていない)を除き、活性領域(24)への接続を作る。くぼみ(26, 32)及び(34)は、たとえばプラズマエッティングプロセスにより、基板(20)の上部表面中にエッティングされる。活性領域(24)内で、抵抗(22)の外側に、接触(36)を形成するために、深いコレクタ中への $n^+$ 注入が行われる。接触(36)は上部表面(30)から埋込み $n$ 層(28)への電気的接続を作る。たとえば、リセスピリバッファLOCO<sub>S</sub>(ロコス)プロセスといった周知のプロセスにより、分離のための溝の中に、フィールド酸化物を成長させる。

30

酸化物の成長と同時に、 $n^+$ 注入種が拡散する。

#### 【0012】

図2に示されるように、フォトレジストのマスク(図示されていない)が、注入が必要ない表面(30)の部分上で、パターン形成される。活性領域(24)の一部には、抵抗基体(38)を形成するために、ホウ素のような $p^+$ 注入種が注入されるが、ホウ素には限定されない。注入するドーパントの量は、当業者には周知のように、抵抗(22)が持つべき抵抗値によって決る。次に、フォトレジストを除去する。

40

#### 【0013】

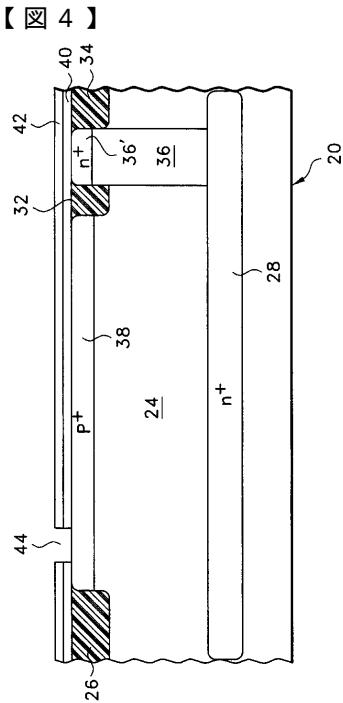

別のフォトレジスト層(図示されていない)が、 $n^+$ 接触促進注入が必要ない表面(30)上で、パターン形成される。図3に示されるように、 $n^+$ 接触促進注入により、接触(36)内に、接触領域(36')を形成する。接触領域(36')は $n^+$ 注入により、接触(36)より低い抵抗を有する。その後、フォトレジスト層を除去する。以後、フォトレジスト又はマスクの堆積、パターン形成及び除去については、いちいち述べない。当業者はそのような工程の必要性を知るであろう。

#### 【0014】

ポリシリコン形成工程では、TEOS酸化物のような絶縁材料層を、全基板(20)の表

50

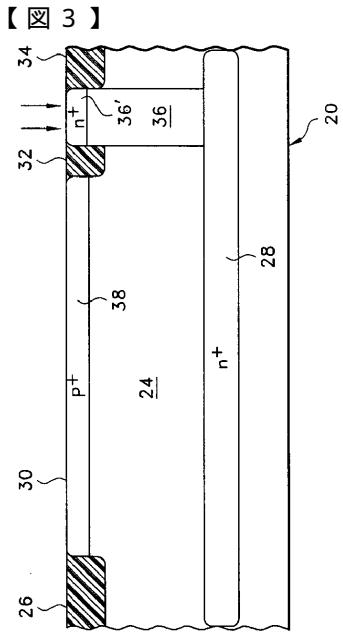

面(30)上に形成する。図4に示されるように、酸化物層(40)は、典型的な場合、350オングストロームの厚さである。約600オングストロームの厚さをもつアモルファス多結晶シリコン層(42)は、酸化物層(40)上に、化学気相堆積によって堆積させてよい。層(42)上にマスクをパターン形成し、抵抗基体(38)との第1の接触(46)として、接触を形成する中で、アモルファス多結晶シリコン層(42)及び酸化物層(40)を抵抗基体(38)のシリコンまで貫くプラズマエッチングプロセスにより、エミッタ窓(44)がエッチングされる。

#### 【0015】

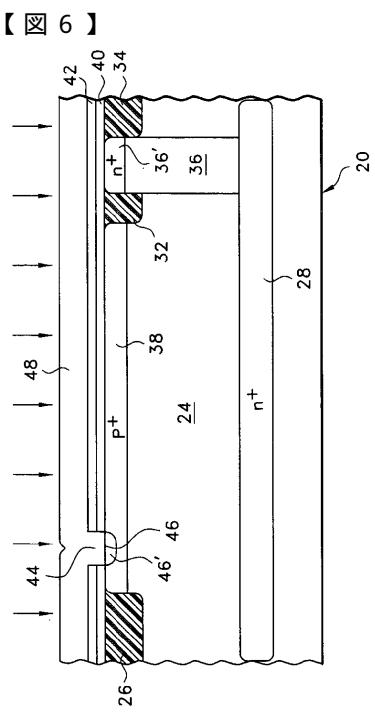

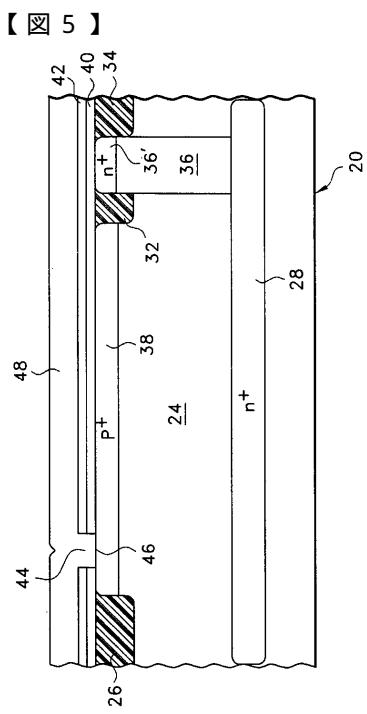

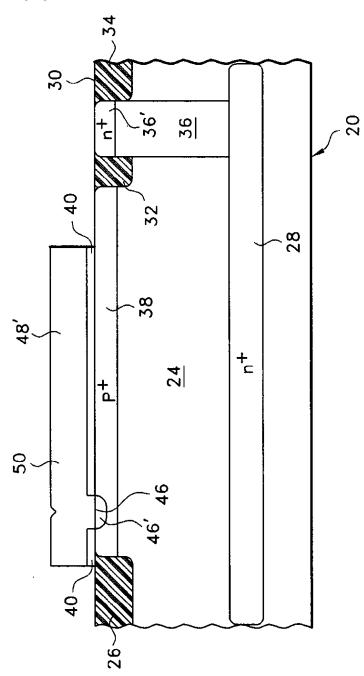

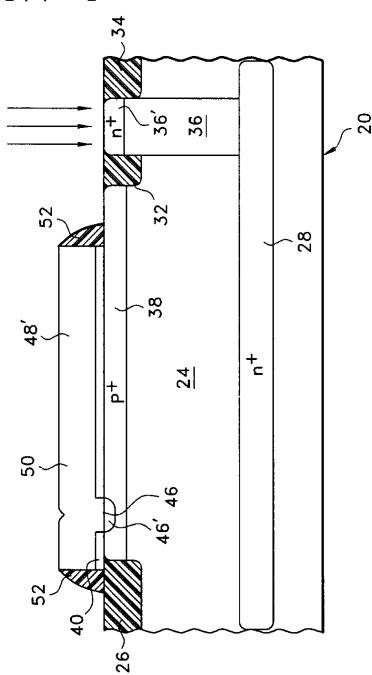

図5は化学気相堆積プロセスにより、アモルファス多結晶シリコン層(42)上に、典型的な場合3100オングストロームの厚さのポリシリコンの層(48)を全面に堆積させた後の基板(20)の断面図である。アモルファス多結晶シリコン上に層を形成するのに加えて、ポリシリコンの層(48)が窓(44)を満し、抵抗基体(38)との接触を作り、第1の抵抗接触(46)を規定する。ドープエミッタプロセスの一部として、ポリシリコンの層(48)に図6に示されるように、p-ドープポリシリコンを形成するため、ホウ素のようなp形ドーパントが注入されるが、ホウ素には限定されない。ポリシリコンのドーピングは、他の周知の方法によってもできる。本発明では注入は必要ではないが、プロセス工程をつけ加えることなく、既存のプロセスで作製中のフィールドプレート抵抗(22)には寄与する。p形ドーパントは接触(46)中に促進された接触領域(46')を形成する。促進された接触領域(46')は、接触(46)より低い抵抗値をもつ。

#### 【0016】

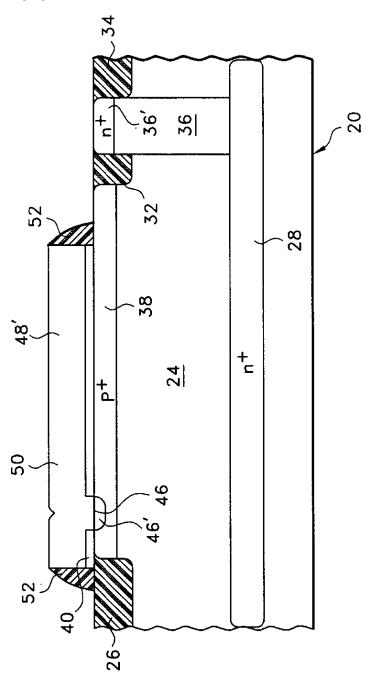

注入に続いて、ポリシリコンの層(48)にハードマスクを形成し、次にプラズマエッチングプロセスによってエッチングされる。ポリシリコンの層(48)がエッチングされる時、ポリシリコンの層(48)の不要の領域が除去されるだけでなく、アモルファス多結晶シリコン層(42)及びTEOS層(40)の不要の領域も、エッチング除去される。フィールドプレート(50)を形成する残ったポリシリコンが、図7に示されている。ポリシリコンの層(48)の残った部分は、抵抗基体(38)の本質的に全体の上に延びる。フィールドプレート(56)のドープポリシリコンは、窓(44)及び促進接触領域(46')中のドープポリシリコンを通った抵抗基体(38)への導電路を作る。熱処理工程中、アモルファス多結晶シリコン層(42)は、ポリシリコンの層(48)中に入り、一体となり、ポリシリコン層(48')を形成する。ポリシリコン(48')は抵抗基体(38)の本質的に全体上に延び、酸化物層(40)により、それから分離される。レイアウト、設計及び作製則により、ポリシリコン層(48')は別の窓を形成すべき領域(図7の右側)から、エッチング除去される。

#### 【0017】

他の工程は本発明では必要ないが、既存のプロセスでは存在し、エミッタ接触(図示されていない)のポリシリコン構造の周辺及びポリシリコン層(48)又は(48')で形成されたフィールドプレート(50)の周囲に、スペーサ(52)を形成する。TEOS酸化物のような絶縁性材料の層を、基板(20)の全体上に堆積させる。ドライエッチングプロセスにより、不要な絶縁性材料を除去すると、図8に示されるように、ポリシリコン構造の周囲にスペーサ(52)が残る。スペーサ(52)は表面(30)で典型的な場合、1500オングストロームの幅である。既存のプロセスにおいて、スペーサ(52)は同じ基板上に作製される金属-酸化物-半導体デバイス又は自己整合デバイスに適合するよう、ポリシリコン構造の周囲に置かれる。スペーサ(52)は第2の抵抗接触(58)と自己整合し、抵抗基体(38)上の領域が、より多く使えるようになる。本発明では必要ではないが、プロセス工程を変えたり追加することなく、この工程は既存のプロセスでフィールドプレート抵抗(22)を作製するのに寄与する。

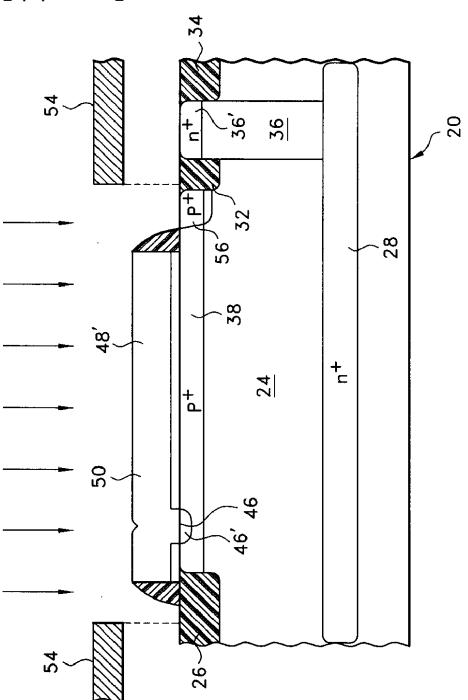

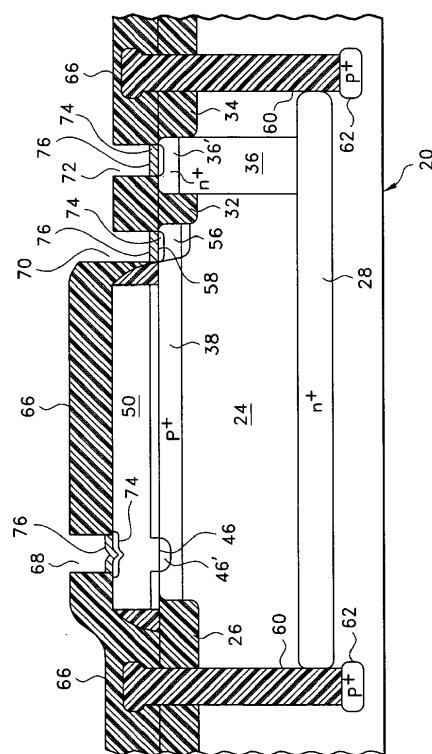

#### 【0018】

図9に示されるように、表面注入工程で、コレクタ接触(36)の促進接触領域(36')に、ひ素又はリンのようなn形ドーパントを注入するが、これらのドーパントには限定されない。注入により、促進接触領域(36')及びコレクタ接触(36)の抵抗が下る

10

20

30

40

50

。注入を  $n$  タブコレクタ接触に限定するため、マスク（図示されていない）を形成すると、埋込み層（28）まで下方に延びる深い  $n^+$  コレクタ接触ができる。

#### 【0019】

本発明では必要ないが既存のプロセスには存在する更に別の工程は、図10に示されているベース促進注入である。ベース促進注入において、抵抗を下るために、エミッタ接触（図示されていない）のポリシリコン構造及びフィールドプレート（50）に再びホウ素のような  $p$  形ドーパントが注入されるが、ホウ素に限定されない。（54）と示されたフォトレジストマスクは注入を避けるべき領域をマスクする。より重要なことは、抵抗基体（38）中の第2の抵抗接触（58）が形成される領域（56）で、自己整合  $p^+$  注入が実現されることである。

10

#### 【0020】

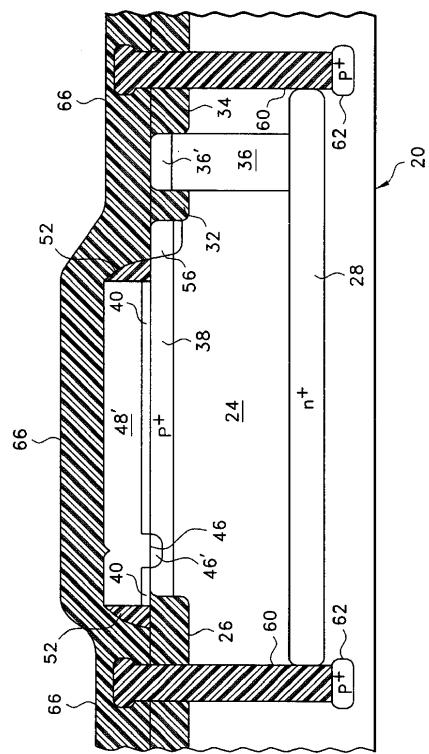

当業者には周知のように、電気的及び熱的雑音の遮断のため、活性領域（24）周囲に、溝（60）が形成される。その工程は示されていないが、最終的（60）な溝（60）は図11に示されている。溝（60）の形成中、マスクが形成され、たとえばプラズマエッチングプロセスにより、溝がエッチングされる。 $p^+$  注入により、溝（60）の底に注入領域（62）が形成される。溝に側壁酸化物が形成され、溝はポリシリコンで満される。熱処理により、注入されたドーパントが窓（44）下の抵抗基体（38）中に拡散し、接触（46）を形成する。

#### 【0021】

図11に示されるように、一括して誘電体層（66）として示される酸化物のような絶縁性材料の1ないし複数の層に、平坦化工程を施す。好ましい実施例において、TEOSの層、プラズマ促進TEOSの層及びホウ素-リンTEOSの層が形成される。表面を平滑にするために、熱処理工程で、層（66）を再流動化させる。

20

#### 【0022】

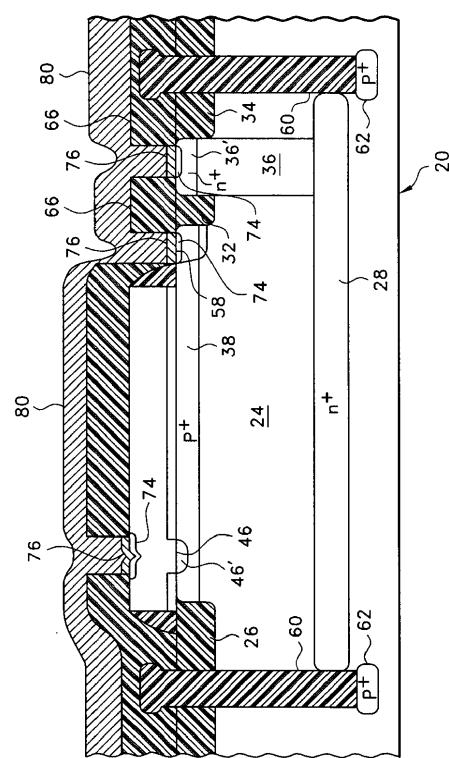

図12に示されるように、窓（68，70）及び（72）を開けるために、誘電体層（66）をマスクし、ドライエッチングプロセスによってエッチングするが、この方法に限定されない。窓（68）はポリシリコンフィールドプレート（50）まで開ける。窓（70）は  $p^+$  領域（56）まで開ける。窓（72）はコレクタ接触（36）まで開ける。

#### 【0023】

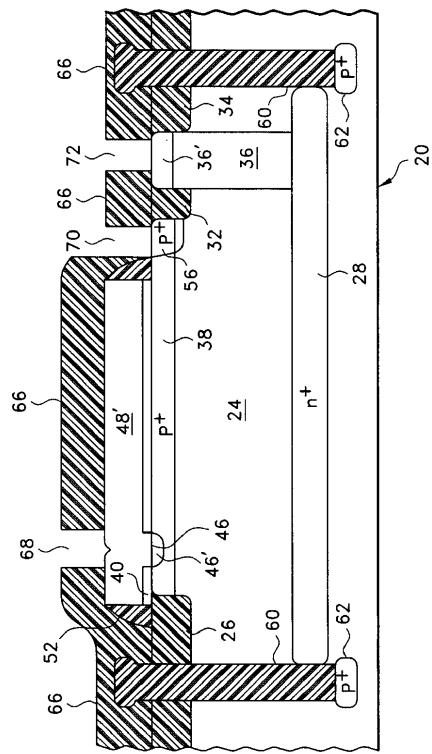

図13に示されるように、白金シリサイドのような第1の障壁層（74）を各窓（68，70）及び（72）のそれぞれの中に形成してよいが、この材料には限定されない。白金を基板上に堆積させ、シリコンと接触する所で、シリコンと反応するよう加熱される。当業者には周知のように、未反応の白金はエッチング除去される。窓（68）中の第1の障壁層（74）は領域（56）内でドープシリコン中に形成され、抵抗（22）への第2の接触（76）を形成する。窓（72）中の第1の障壁層（74）は、接触（36）の  $n^+$  ドープシリコン中に形成される。

30

#### 【0024】

図14に示されるように、タンゲステンのような第2の障壁層（76）を、第1の障壁層（74）上に堆積させるが、タンゲステンには限定されない。第2の障壁層（76）は、タンゲステンを用いる時、当業者には周知のように、スパッタリングプロセスにより形成してよいが、それには限定されない。障壁層は増やしても、減してもよい。

40

#### 【0025】

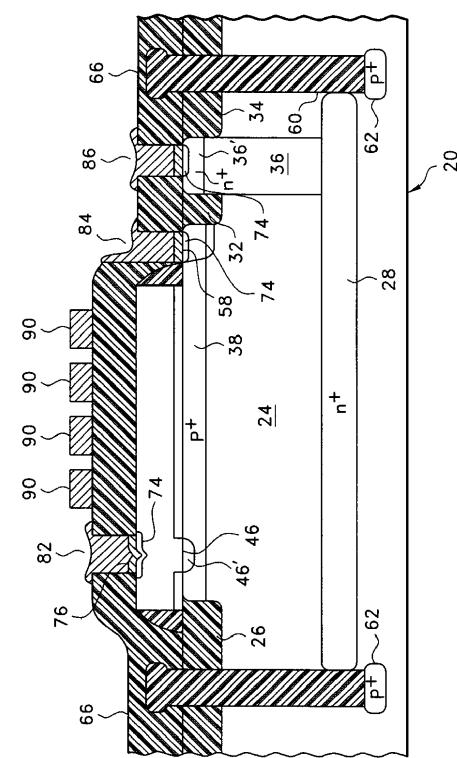

導電体又はトレースを形成する際、アルミニウム又は銅のような金属層（80）を、当業者には周知のように、最上面全体上に、図15に示されるように堆積させるが、これらの材料に限定されない。図15に示された実施例において、金属層（80）は金属の第1層であるが、本発明はそれには限定されない。本発明は集積回路を作製する金属多層プロセス中の任意の金属層に適用できる。

#### 【0026】

層（80）中の不要の金属は、当業者には周知のように除去され、図16及び17に示されるように、上に延びるトレースを有するフィールドプレート抵抗（22）が得られる。

50

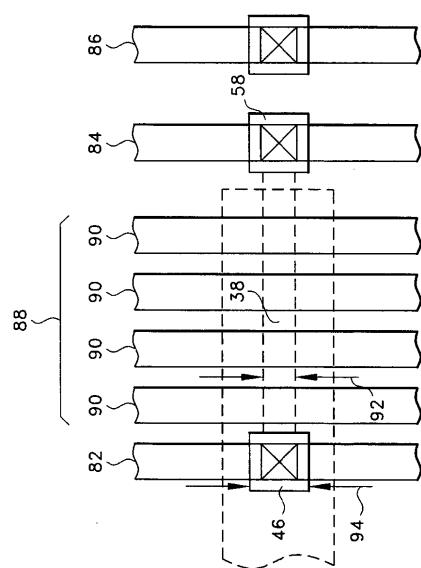

金属層(80)はエミッタ(図示されていない)及びフィールドプレート(50)へのリード(82)、第2の抵抗接触(58)へのリード(84)、接触(36)へのリード(86)及び一部分のトレース(90)が抵抗基体(38)上にルート形成されたトレース(88)を形成する。図15に示されたフィールドプレート抵抗(22)は、抵抗(22)が中に作製される集積回路(98)の一部を示す。抵抗(22)の基体(38)上の増加した領域を有するフィールドプレート抵抗(22)は、抵抗への接触を形成するのと同じ金属層中で、抵抗(22)の基体(38)上に、他の金属導電体のルートを形成するために使用できる。

#### 【0027】

図17は図16のフィールドプレート抵抗(22)の上面図で、抵抗基体(38)上の導電体(90)の1つの可能なルート形成を示す。抵抗基体(38)の幅(92)は、抵抗基体(38)の端部で、第1の抵抗接触(46)及び第2の抵抗接触(58)の幅(94)より狭いように示されているが、本発明はそれには限定されない。抵抗基体(38)上の本質的に全ての領域が、レイアウト、設計及び作製則にのみ従って、トレース又は金属導電体のルートを形成するのに使用できる。

10

#### 【0028】

このようにして作製されたフィールドプレート抵抗(22)は、抵抗基体(38)上に、導電体又はトレース(90)のルートを形成するための増大した領域をもつ。レイアウト、設計及び作製則が、導電体のルート形成のために抵抗基体(38)上の領域を使用する上での制限要因となる可能性がある。

20

#### 【0029】

本発明は任意の周知のプロセスで作製してよく、BICMOS(相補バイポーラ)プロセスで容易に作製できるが、プロセスのすべての工程が含まれているわけではなく、あるいは全ての工程の全ての詳細がここに含まれているわけではないが、当業者にとっては十分な開示がされている。開示された工程は、ポリシリコンエミッタプロセスに用いるものである。ルート形成のために増加された領域を有するポリシリコンフィールドプレート抵抗は、プロセス工程を加えることなく、このプロセスで作製できる。その上、ルート形成するための増加した領域を有するポリシリコンフィールドプレート抵抗は、ポリシリコンエミッタプロセスのすべての工程より少い工程で作製することができる。

30

#### 【0030】

本発明について、シリコン基板上に作製するように述べてきたが、本発明はそれには限定されない。任意の半導体を使用することができる。p形ドープ領域の抵抗について述べてきたが、本発明はそれには限定されず、本発明はドーピングの他の形のフィールドプレート抵抗を作製するために使用できる。

#### 【図面の簡単な説明】

【図1】本発明に従い、上に増加したルート形成領域を有するフィールドプレート抵抗を含む集積回路作製方法における工程を示す一連の半導体基板の断面図である。

【図2】本発明に従い、上に増加したルート形成領域を有するフィールドプレート抵抗を含む集積回路作製方法における工程を示す一連の半導体基板の断面図である。

【図3】本発明に従い、上に増加したルート形成領域を有するフィールドプレート抵抗を含む集積回路作製方法における工程を示す一連の半導体基板の断面図である。

40

【図4】本発明に従い、上に増加したルート形成領域を有するフィールドプレート抵抗を含む集積回路作製方法における工程を示す一連の半導体基板の断面図である。

【図5】本発明に従い、上に増加したルート形成領域を有するフィールドプレート抵抗を含む集積回路作製方法における工程を示す一連の半導体基板の断面図である。

【図6】本発明に従い、上に増加したルート形成領域を有するフィールドプレート抵抗を含む集積回路作製方法における工程を示す一連の半導体基板の断面図である。

【図7】本発明に従い、上に増加したルート形成領域を有するフィールドプレート抵抗を含む集積回路作製方法における工程を示す一連の半導体基板の断面図である。

【図8】本発明に従い、上に増加したルート形成領域を有するフィールドプレート抵抗を

50

含む集積回路作製方法における工程を示す一連の半導体基板の断面図である。

【図9】本発明に従い、上に増加したルート形成領域を有するフィールドプレート抵抗を含む集積回路作製方法における工程を示す一連の半導体基板の断面図である。

【図10】本発明に従い、上に増加したルート形成領域を有するフィールドプレート抵抗を含む集積回路作製方法における工程を示す一連の半導体基板の断面図である。

【図11】本発明に従い、上に増加したルート形成領域を有するフィールドプレート抵抗を含む集積回路作製方法における工程を示す一連の半導体基板の断面図である。

【図12】本発明に従い、上に増加したルート形成領域を有するフィールドプレート抵抗を含む集積回路作製方法における工程を示す一連の半導体基板の断面図である。

【図13】本発明に従い、上に増加したルート形成領域を有するフィールドプレート抵抗を含む集積回路作製方法における工程を示す一連の半導体基板の断面図である。 10

【図14】本発明に従い、上に増加したルート形成領域を有するフィールドプレート抵抗を含む集積回路作製方法における工程を示す一連の半導体基板の断面図である。

【図15】本発明に従い、上に増加したルート形成領域を有するフィールドプレート抵抗を含む集積回路作製方法における工程を示す一連の半導体基板の断面図である。

【図16】本発明に従い、上に増加したルート形成領域を有するフィールドプレート抵抗を含む集積回路作製方法における工程を示す一連の半導体基板の断面図である。

【図17】抵抗上にトレースをめぐらす1つの可能性を示す図6上の増加したルート形成領域を有するフィールドプレート抵抗の上面図である。

【図18】金属フィールドプレートを有する従来技術の抵抗の断面図である。 20

【図19】ポリシリコンフィールドプレートを有する従来技術の抵抗の断面図である。

#### 【符号の説明】

20 半導体基板、基板

22 フィールドプレート抵抗、抵抗

24 活性領域

26 くぼみ

28 埋込み $n^+$ 層、埋込み層

30 上部表面、表面

32, 34 くぼみ

36 接触

36' 接触領域

38 抵抗基体

40 酸化物層

42 層

44 窓

46 第1の接触

46' 接触領域

48, 48' 層

50 フィールドプレート

52 スペーサ

54 フォトレジストマスク

56 フィールドプレート

58 第2の抵抗接触

60 溝

62 注入領域

66 誘電体層

68, 70, 72 窓

74 第1の障壁層

76 第2の接触

80 金属層

10

20

30

40

50

8 2 , 8 4 , 8 6 リード

8 8 トレース

9 0 トレース、導電体

9 2 , 9 4 幅

9 8 集積回路

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

---

フロントページの続き

(74)代理人 100106703

弁理士 産形 和央

(74)代理人 100096943

弁理士 白井 伸一

(74)代理人 100091889

弁理士 藤野 育男

(74)代理人 100101498

弁理士 越智 隆夫

(74)代理人 100096688

弁理士 本宮 照久

(74)代理人 100102808

弁理士 高梨 憲通

(74)代理人 100104352

弁理士 朝日 伸光

(74)代理人 100107401

弁理士 高橋 誠一郎

(72)発明者 トーマス ジェー. クラットシック

アメリカ合衆国 19522 ペンシルヴァニア, フリートウッド, クレストビュー ドライヴ

23

審査官 増山 慎也

(56)参考文献 特開平02-312273(JP,A)

特開平05-090509(JP,A)

特開昭55-162255(JP,A)

特開昭58-070566(JP,A)

特開平11-340424(JP,A)

特開平04-348560(JP,A)

特開平03-036759(JP,A)

特開昭62-295445(JP,A)

特開昭61-251162(JP,A)

特開昭56-133863(JP,A)

特開昭63-226956(JP,A)

特開2002-134625(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/822

H01L 21/3205

H01L 21/768

H01L 23/522

H01L 27/04