(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4838502号

(P4838502)

(45) 発行日 平成23年12月14日(2011.12.14)

(24) 登録日 平成23年10月7日(2011.10.7)

(51) Int.Cl.

F 1

|             |              |                  |      |      |         |

|-------------|--------------|------------------|------|------|---------|

| <b>G09G</b> | <b>3/30</b>  | <b>(2006.01)</b> | G09G | 3/30 | J       |

| <b>G09G</b> | <b>3/20</b>  | <b>(2006.01)</b> | G09G | 3/20 | 6 1 1 D |

| <b>H05B</b> | <b>33/12</b> | <b>(2006.01)</b> | G09G | 3/20 | 6 1 2 E |

| <b>H01L</b> | <b>51/50</b> | <b>(2006.01)</b> | G09G | 3/20 | 6 2 4 B |

|             |              |                  | G09G | 3/20 | 6 4 1 D |

請求項の数 6 (全 18 頁) 最終頁に続く

|              |                              |           |                                            |

|--------------|------------------------------|-----------|--------------------------------------------|

| (21) 出願番号    | 特願2004-221606 (P2004-221606) | (73) 特許権者 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (22) 出願日     | 平成16年7月29日 (2004.7.29)       | (74) 代理人  | 100096828<br>弁理士 渡辺 敏介                     |

| (65) 公開番号    | 特開2005-70761 (P2005-70761A)  | (74) 代理人  | 100110870<br>弁理士 山口 芳広                     |

| (43) 公開日     | 平成17年3月17日 (2005.3.17)       | (72) 発明者  | 結城 修<br>東京都大田区下丸子3丁目30番2号 キ<br>ヤノン株式会社内    |

| 審査請求日        | 平成18年6月26日 (2006.6.26)       | (72) 発明者  | 中島 芳紀<br>東京都大田区下丸子3丁目30番2号 キ<br>ヤノン株式会社内   |

| (31) 優先権主張番号 | 特願2003-288401 (P2003-288401) |           |                                            |

| (32) 優先日     | 平成15年8月7日 (2003.8.7)         |           |                                            |

| (33) 優先権主張国  | 日本国 (JP)                     |           |                                            |

| (31) 優先権主張番号 | 特願2003-288520 (P2003-288520) |           |                                            |

| (32) 優先日     | 平成15年8月7日 (2003.8.7)         |           |                                            |

| (33) 優先権主張国  | 日本国 (JP)                     |           |                                            |

最終頁に続く

(54) 【発明の名称】 画像表示装置とその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

表示部と電圧源とを含む画像表示装置であって、

前記表示部が表示素子と画素回路とを有し、

前記画素回路が、

前記表示素子の一方の端子に接続される第1主電極と、第1の共通電極に接続される第2主電極と、制御電極と、を有する、該表示素子に駆動電流を供給するためのPチャネル型駆動トランジスタと、

前記Pチャネル型駆動トランジスタの前記制御電極と前記第1主電極との間に設けられ、

前記駆動トランジスタの前記制御電極の電位を設定するための制御トランジスタと、

前記Pチャネル型駆動トランジスタの前記制御電極と前記第1の共通電極との間に設けられ、前記Pチャネル型駆動トランジスタの前記制御電極の電位を保持するためのコンデンサと、

を備え、

前記表示素子の他方の端子は第2の共通電極に接続されており、

前記電圧源は、前記Pチャネル型駆動トランジスタの前記制御電極に設定された電位に基づいて前記表示素子を発光させて測定した輝度変動を、前記制御トランジスタがオフ状態におけるリーク電流を抑制することで抑制すべく、前記第1の共通電極の電位を下げるための又は前記第2の共通電極の電位を上げるための調整回路を備えることを特徴とする画像表示装置。

## 【請求項 2】

カラー表示部と電圧源とを含む画像表示装置であって、

前記カラー表示部が、第1の色を呈する第1の表示素子と、第2の色を呈する第2の表示素子と、第1の画素回路と、第2の画素回路と、を有し、

前記第1の画素回路が、

前記第1の表示素子の一方の端子に接続される第1主電極と、第1の共通電極に接続される第2主電極と、制御電極と、を有する、該第1の表示素子に駆動電流を供給するための第1のPチャネル型駆動トランジスタと、

前記第1のPチャネル型駆動トランジスタの前記制御電極と前記第1主電極との間に設けられ、前記第1のPチャネル型駆動トランジスタの前記制御電極の電位を設定するための第1の制御トランジスタと、

前記第1のPチャネル型駆動トランジスタの前記制御電極と前記第1の共通電極との間に設けられ、前記第1のPチャネル型駆動トランジスタの前記制御電極の電位を保持するための第1のコンデンサと、を備え、

前記第2の画素回路が、

前記第2の表示素子の一方の端子に接続される第1主電極と、第2の共通電極に接続される第2主電極と、制御電極と、を有する、該第2の表示素子に駆動電流を供給するための第2のPチャネル型駆動トランジスタと、

前記第2のPチャネル型駆動トランジスタの前記制御電極と前記第1主電極との間に設けられ、前記第2のPチャネル型駆動トランジスタの前記制御電極の電位を設定するための第2の制御トランジスタと、

前記第2のPチャネル型駆動トランジスタの前記制御電極と前記第2の共通電極との間に設けられ、前記第2のPチャネル型駆動トランジスタの前記制御電極の電位を保持するための第2のコンデンサと、を備え、

前記第1の表示素子の他方の端子は第3の共通電極、前記第2の表示素子の他方の端子は第4の共通電極に接続されており、

前記電圧源は、前記Pチャネル型駆動トランジスタの前記制御電極に設定された電位に基づいて前記表示素子を発光させて測定した輝度変動を、少なくとも前記第1の制御トランジスタがオフ状態におけるリーク電流又は前記第2の制御トランジスタがオフ状態におけるリーク電流を抑制することで抑制すべく、前記第1の共通電極の電位又は前記第2の共通電極の電位を下げるための若しくは前記第3の共通電極の電位又は前記第4の共通電極の電位を上げるための調整回路を備えることを特徴とする画像表示装置。

## 【請求項 3】

表示部が表示素子と画素回路と調整回路とを有し、

前記画素回路が、

前記表示素子の一方の端子に接続される第1主電極と、第1の共通電極に接続される第2主電極と、制御電極と、を有する、該表示素子に駆動電流を供給するためのPチャネル型駆動トランジスタと、

前記Pチャネル型駆動トランジスタの前記制御電極と前記第1主電極との間に設けられ、前記Pチャネル型駆動トランジスタの前記制御電極の電位を設定するための制御トランジスタと、

前記Pチャネル型駆動トランジスタの前記制御電極と前記第1の共通電極との間に設けられ、前記Pチャネル型駆動トランジスタの前記制御電極の電位を保持するためのコンデンサと、

を備え、

前記表示素子の他方の端子は第2の共通電極に接続されており、

前記調整回路によって前記第1の共通電極又は前記第2の共通電極の電位の調整が可能である画像表示装置の製造方法であって、

(i) 表示部を用意するステップと、

(ii) 前記第1の共通電極と前記第2の共通電極との間に電圧を印加するステップと、

10

20

30

40

50

( i i i ) 前記表示部の発光輝度の変動を測定するステップと、

( i v ) 測定した前記発光輝度の変動を、前記制御トランジスタがオフ状態におけるリーク電流を抑制することで抑制すべく、前記第1の共通電極の電位を下げる又は前記第2の共通電極の電位を上げるように、前記調整回路を調整するステップと、

を含むことを特徴とする画像表示装置の製造方法。

## 【請求項4】

前記 ( i v ) のステップは、表示素子の劣化による電圧上昇を加味することを特徴とする請求項3に記載の画像表示装置の製造方法。

## 【請求項5】

カラー表示部が、第1の色を呈する第1の表示素子と、第2の色を呈する第2の表示素子と、第1の画素回路と、第2の画素回路と、第1の調整回路と、第2の調整回路と、を有し、

10

前記第1の画素回路が、

前記第1の表示素子の一方の端子に接続される第1主電極と、第1の共通電極に接続される第2主電極と、制御電極と、を有する、該第1の表示素子に駆動電流を供給するための第1のPチャネル型駆動トランジスタと、

前記第1のPチャネル型駆動トランジスタの前記制御電極と前記第1主電極との間に設けられ、前記第1のPチャネル型駆動トランジスタの前記制御電極の電位を設定するための第1の制御トランジスタと、

20

前記第1のPチャネル型駆動トランジスタの前記制御電極と前記第1の共通電極との間に設けられ、前記第1のPチャネル型駆動トランジスタの前記制御電極の電位を保持するための第1のコンデンサと、を備え、

前記第2の画素回路が、

前記第2の表示素子の一方の端子に接続される第1主電極と、第2の共通電極に接続される第2主電極と、制御電極と、を有する、該第2の表示素子に駆動電流を供給するための第2のPチャネル型駆動トランジスタと、

前記第2のPチャネル型駆動トランジスタの前記制御電極と前記第1主電極との間に設けられ、前記第2のPチャネル型駆動トランジスタの前記制御電極の電位を設定するための第2の制御トランジスタと、

30

前記第2のPチャネル型駆動トランジスタの前記制御電極と前記第2の共通電極との間に設けられ、前記第2のPチャネル型駆動トランジスタの前記制御電極の電位を保持するための第2のコンデンサと、を備え、

前記第1の表示素子の他方の端子は第3の共通電極、前記第2の表示素子の他方の端子は第4の共通電極に接続され、

前記第1の調整回路は、前記第1の共通電極又は前記第3の共通電極の電位の調整が可能であり、

前記第2の調整回路は、前記第2の共通電極又は前記第4の共通電極の電位の調整が可能である画像表示装置の製造方法であって、

( i ) カラー表示部を用意するステップと、

( i i ) 前記第1の共通電極と前記第3の共通電極との間又は前記第2の共通電極と前記第4の共通電極との間に電圧を印加するステップと、

40

( i i i ) 前記表示部の発光輝度の変動を測定するステップと、

( i v ) 測定した前記発光輝度の変動を、少なくとも前記第1の制御トランジスタがオフ状態におけるリーク電流又は前記第2の制御トランジスタがオフ状態におけるリーク電流を抑制することで抑制すべく、前記第1の共通電極の電位を下げるよう又は前記第3の共通電極の電位を上げるように前記第1の調整回路を調整する若しくは前記第2の共通電極の電位を下げるよう又は前記第4の共通電極の電位を上げるように前記第2の調整回路を調整するステップと、

を含むことを特徴とする画像表示装置の製造方法。

## 【請求項6】

50

前記 (i v) のステップは、前記第 1 の表示素子又は前記第 2 の表示素子の劣化による電圧上昇を加味することを特徴とする請求項 5 に記載の画像表示装置の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は画像表示装置とその製造方法に関する。特には、表示素子と駆動用トランジスタと制御用トランジスタとを有する画素回路を複数配置した画像表示装置とその製造方法に関する。

【背景技術】

【0002】

駆動回路として、定電流で駆動を行う方法が知られている。例えば、電流で駆動するのに適した発光素子としては、発光ダイオード (Light Emission Diode、以下 LED と略) や近年注目されている有機エレクトロルミネッセンス素子 (以下、有機 EL 素子又は OEL と略) などが挙げられる。これらの発光素子の特性は温度に殆ど依存せず、電流に対し略リニアな発光強度カーブが得られるため、定電流駆動の方法が提案されている。

【0003】

以下、有機 EL 素子を例にとり、従来の発光のための電流駆動について述べる。

【0004】

有機 EL 素子は、高輝度発光が可能な薄膜積層の面状の自発光が得られることを特徴とする。有機 EL 素子は、有機層の機能積層数を増やすことにより (非特許文献 1 及び 2 参照)、低電圧で高効率な発光を実現することができる。そして、上記で述べたように有機 EL 素子は一定の電流により発光させる為に定電流駆動方法がいくつか提案されている。

【0005】

例えば、図 3 で示されるような、入力電流 (idata) をコピーして OEL13 に供給する駆動回路が、特許文献 1 や 2 で提案されている。この駆動方法は、電流を入力としてトランジスタ 11 の制御電極の電位を設定する電流制御型の方法であり、トランジスタ 11 の閾値や OEL13 の劣化電圧に影響を受けず、入力電流と略同じ量の電流を OEL13 に供給できるという利点を有している。

【0006】

また、特許文献 3 には発光色が異なる発光ダイオードを集合してなる表示ドットを複数個配設した情報表示装置を開示し、特に前記発光ダイオードに対して各発光色毎に電圧を供給する電源を備える構成を開示する。

【0007】

また、特許文献 4 には、カソードコモンタイプの複数色の LED を用いる電光表示装置において、色ごとに DC 出力電圧が異なる独立したスイッチング電源を設ける構成や、一つのスイッチング電源と、電圧調整用の簡易電源回路とを組み合わせて用いる構成が開示されている。

【0008】

また、特許文献 5 には、選択トランジスタと駆動トランジスタをそれぞれオン / オフの 2 値信号で制御し、各サブフレーム期間に固有の値の電圧値あるいは電流値を可変駆動電源から可変的に出力する構成を開示している。

【0009】

【非特許文献 1】アプライド・フィジクス・レターズ (Applied Physics Letters), 米国, 1987 年, 51巻, p. 913

【非特許文献 2】アプライド・フィジクス・レターズ (Applied Physics Letters), 米国, 1989 年, 65巻, p. 3610

【特許文献 1】特開 2001-056667 号公報

【特許文献 2】米国特許第 6229506 号明細書

【特許文献 3】特開昭 63-280300 号公報

10

20

30

40

50

【特許文献4】特開2002-23666号公報

【特許文献5】特開平10-232649号公報

【発明の開示】

【発明が解決しようとする課題】

【0010】

本発明は、高品位の表示を実現することができる画像表示装置を実現することを課題とする。

【課題を解決するための手段】

【0011】

本発明に係わる第1の発明は、

10

表示部と電圧源とを含む画像表示装置であって、

前記表示部が表示素子と画素回路とを有し、

前記画素回路が、

前記表示素子の一方の端子に接続される第1主電極と、第1の共通電極に接続される第2主電極と、制御電極と、を有する、該表示素子に駆動電流を供給するためのPチャネル型駆動トランジスタと、

前記Pチャネル型駆動トランジスタの前記制御電極と前記第1主電極との間に設けられ、前記駆動トランジスタの前記制御電極の電位を設定するための制御トランジスタと、

前記Pチャネル型駆動トランジスタの前記制御電極と前記第1の共通電極との間に設けられ、前記Pチャネル型駆動トランジスタの前記制御電極の電位を保持するためのコンデンサと、

を備え、

20

前記表示素子の他方の端子は第2の共通電極に接続されており、

前記電圧源は、前記Pチャネル型駆動トランジスタの前記制御電極に設定された電位に基づいて前記表示素子を発光させて測定した輝度変動を、前記制御トランジスタがオフ状態におけるリーク電流を抑制することで抑制すべく、前記第1の共通電極の電位を下げるための又は前記第2の共通電極の電位を上げるための調整回路を備えることを特徴とする画像表示装置である。

【0012】

30

本発明に係わる第2の発明は、

カラー表示部と電圧源とを含む画像表示装置であって、

前記カラー表示部が、第1の色を呈する第1の表示素子と、第2の色を呈する第2の表示素子と、第1の画素回路と、第2の画素回路と、を有し、

前記第1の画素回路が、

前記第1の表示素子の一方の端子に接続される第1主電極と、第1の共通電極に接続される第2主電極と、制御電極と、を有する、該第1の表示素子に駆動電流を供給するための第1のPチャネル型駆動トランジスタと、

前記第1のPチャネル型駆動トランジスタの前記制御電極と前記第1主電極との間に設けられ、前記第1のPチャネル型駆動トランジスタの前記制御電極の電位を設定するための第1の制御トランジスタと、

40

前記第1のPチャネル型駆動トランジスタの前記制御電極と前記第1の共通電極との間に設けられ、前記第1のPチャネル型駆動トランジスタの前記制御電極の電位を保持するための第1のコンデンサと、を備え、

前記第2の画素回路が、

前記第2の表示素子の一方の端子に接続される第1主電極と、第2の共通電極に接続される第2主電極と、制御電極と、を有する、該第2の表示素子に駆動電流を供給するための第2のPチャネル型駆動トランジスタと、

前記第2のPチャネル型駆動トランジスタの前記制御電極と前記第1主電極との間に設けられ、前記第2のPチャネル型駆動トランジスタの前記制御電極の電位を設定するための第2の制御トランジスタと、

50

前記第2のPチャネル型駆動トランジスタの前記制御電極と前記第2の共通電極との間に設けられ、前記第2のPチャネル型駆動トランジスタの前記制御電極の電位を保持するための第2のコンデンサと、を備え、

前記第1の表示素子の他方の端子は第3の共通電極、前記第2の表示素子の他方の端子は第4の共通電極に接続されており、

前記電圧源は、前記Pチャネル型駆動トランジスタの前記制御電極に設定された電位に基づいて前記表示素子を発光させて測定した輝度変動を、少なくとも前記第1の制御トランジスタがオフ状態におけるリーク電流又は前記第2の制御トランジスタがオフ状態におけるリーク電流を抑制することで抑制すべく、前記第1の共通電極の電位又は前記第2の共通電極の電位を下げるための若しくは前記第3の共通電極の電位又は前記第4の共通電極の電位を上げるための調整回路を備えることを特徴とする画像表示装置である。10

#### 【0017】

本発明に係わる第3の発明は、

表示部が表示素子と画素回路と調整回路とを有し、

前記画素回路が、

前記表示素子の一方の端子に接続される第1主電極と、第1の共通電極に接続される第2主電極と、制御電極と、を有する、該表示素子に駆動電流を供給するためのPチャネル型駆動トランジスタと、

前記Pチャネル型駆動トランジスタの前記制御電極と前記第1主電極との間に設けられ、前記Pチャネル型駆動トランジスタの前記制御電極の電位を設定するための制御トランジスタと、20

前記Pチャネル型駆動トランジスタの前記制御電極と前記第1の共通電極との間に設けられ、前記Pチャネル型駆動トランジスタの前記制御電極の電位を保持するためのコンデンサと、

を備え、

前記表示素子の他方の端子は第2の共通電極に接続されており、

前記調整回路によって前記第1の共通電極又は前記第2の共通電極の電位の調整が可能である画像表示装置の製造方法であって、

(i) 表示部を用意するステップと、

(ii) 前記第1の共通電極と前記第2の共通電極との間に電圧を印加するステップと、30

(iii) 前記表示部の発光輝度の変動を測定するステップと、

(iv) 測定した前記発光輝度の変動を、前記制御トランジスタがオフ状態におけるリーク電流を抑制することで抑制すべく、前記第1の共通電極の電位を下げる又は前記第2の共通電極の電位を上げるように、前記調整回路を調整するステップと、

を含むことを特徴とする画像表示装置の製造方法である。

#### 【0018】

本発明に係わる第4の発明は、

カラー表示部が、第1の色を呈する第1の表示素子と、第2の色を呈する第2の表示素子と、第1の画素回路と、第2の画素回路と、第1の調整回路と、第2の調整回路と、を有し、40

前記第1の画素回路が、

前記第1の表示素子の一方の端子に接続される第1主電極と、第1の共通電極に接続される第2主電極と、制御電極と、を有する、該第1の表示素子に駆動電流を供給するための第1のPチャネル型駆動トランジスタと、

前記第1のPチャネル型駆動トランジスタの前記制御電極と前記第1主電極との間に設けられ、前記第1のPチャネル型駆動トランジスタの前記制御電極の電位を設定するための第1の制御トランジスタと、

前記第1のPチャネル型駆動トランジスタの前記制御電極と前記第1の共通電極との間に設けられ、前記第1のPチャネル型駆動トランジスタの前記制御電極の電位を保持するための第1のコンデンサと、を備え、50

前記第2の画素回路が、

前記第2の表示素子の一方の端子に接続される第1主電極と、第2の共通電極に接続される第2主電極と、制御電極と、を有する、該第2の表示素子に駆動電流を供給するための第2のPチャネル型駆動トランジスタと、

前記第2のPチャネル型駆動トランジスタの前記制御電極と前記第1主電極との間に設けられ、前記第2のPチャネル型駆動トランジスタの前記制御電極の電位を設定するための第2の制御トランジスタと、

前記第2のPチャネル型駆動トランジスタの前記制御電極と前記第2の共通電極との間に設けられ、前記第2のPチャネル型駆動トランジスタの前記制御電極の電位を保持するための第2のコンデンサと、を備え、

前記第1の表示素子の他方の端子は第3の共通電極、前記第2の表示素子の他方の端子は第4の共通電極に接続され、

前記第1の調整回路は、前記第1の共通電極又は前記第3の共通電極の電位の調整が可能であり、

前記第2の調整回路は、前記第2の共通電極又は前記第4の共通電極の電位の調整が可能である画像表示装置の製造方法であって、

(i) カラー表示部を用意するステップと、

(ii) 前記第1の共通電極と前記第3の共通電極との間又は前記第2の共通電極と前記第4の共通電極との間に電圧を印加するステップと、

(iii) 前記表示部の発光輝度の変動を測定するステップと、

(iv) 測定した前記発光輝度の変動を、少なくとも前記第1の制御トランジスタがオフ状態におけるリーク電流又は前記第2の制御トランジスタがオフ状態におけるリーク電流を抑制することで抑制すべく、前記第1の共通電極の電位を下げるよう又は前記第3の共通電極の電位を上げるように前記第1の調整回路を調整する若しくは前記第2の共通電極の電位を下げるよう又は前記第4の共通電極の電位を上げるように前記第2の調整回路を調整するステップと、

を含むことを特徴とする画像表示装置の製造方法である。

#### 【発明の効果】

#### 【0020】

本発明によれば、制御用トランジスタに流れるリーク電流を抑制することによって、結果として表示素子の輝度の変動を抑制することができる。また、該表示素子の輝度の変動を素子の発光色毎に制御することができる。よって、本発明によれば、所望の発光輝度を安定して得ることができ、高品位な画像表示が実現する。

#### 【発明を実施するための最良の形態】

#### 【0021】

本発明は表示素子として自発光型の表示素子を用いる構成に特に好適に適用できる。具体的にはエレクトロルミネッセンス表示素子や、特に好適には有機エレクトロルミネッセンス表示素子を用いる構成に特に好適に適用できる。更には、各表示素子がアクティブマトリックス駆動される構成において特に好適に適用できる。

#### 【0022】

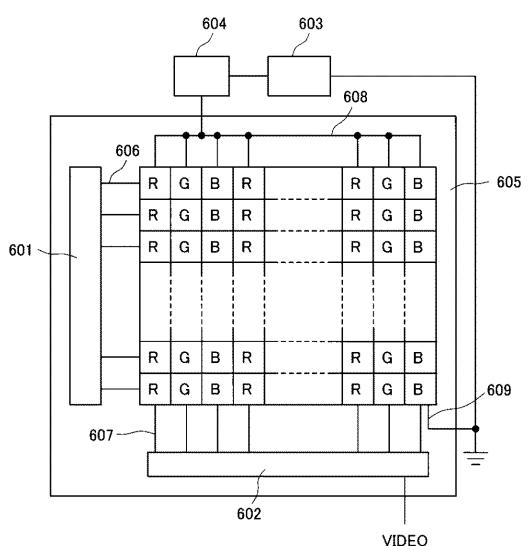

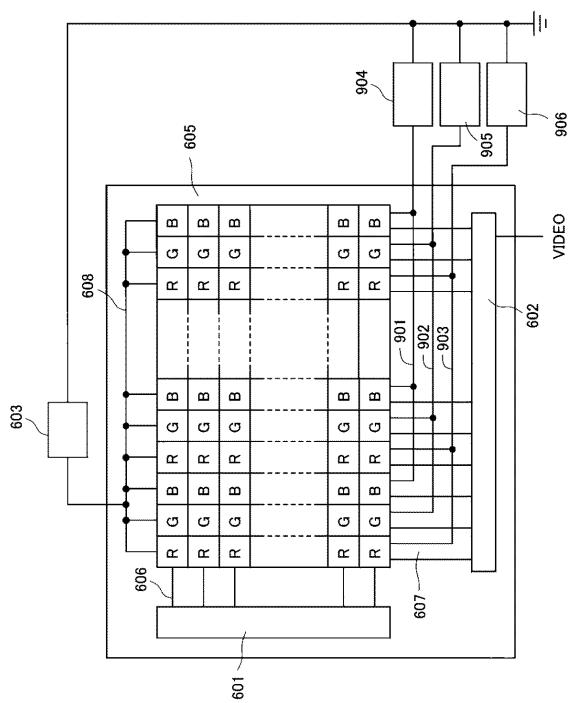

第1の実施形態の画像表示装置の構成を図6に示している。図6において表示部605は赤の画素回路(図中Rで示す)と緑の画素回路(図中Gで示す)と青の画素回路(図中Bで示す)を有している。各画素回路は表示素子としてそれぞれ赤、緑、青の発光色のOELを有している。なお図6では行方向、列方向ともに直線状に画素回路を配置した例を示しているが、赤、緑、青の画素回路を三角形状に配置した構成など種々の配置を採用できる。

#### 【0023】

また表示部605は走査回路601と変調回路602を有している。各画素回路と走査回路601の間は走査信号配線606で接続され、また各画素回路と変調回路602の間は変調信号配線607で接続されている。走査信号配線606を介して各行の画素回路に

10

20

30

40

50

走査信号が印加され、走査信号が印加されている画素回路に対して変調信号配線 607 から変調信号が与えられて各画素回路の発光状態が設定される。

【0024】

また各画素回路には第1の電位源である電源装置 603 が出力できる電位を調整回路である D C - D C コンバータ 604 で調整した電位が第1の共通電極 608 を介して共通に供給される。

【0025】

また各画素回路には第2の電位源であるグランド部が供給する電位が第2の共通電極 609 を介して共通に供給される。

【0026】

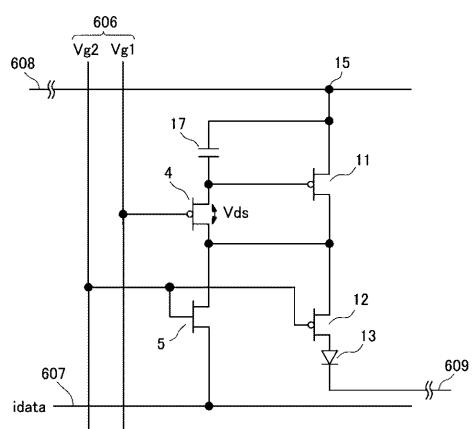

各画素回路の好適な形態を図3に示している。図6では明瞭な表示とするため走査信号配線 606 は各画素回路に対してひとつのみ表示しているが、図3に示す電流プログラミング型の画素回路を採用する場合には、各画素回路に少なくとも2本の変調信号配線を接続するのが好適である。具体的には、図3の制御用トランジスタ4に走査信号 Vg1 を供給する走査信号配線と、信号書き込みタイミングを設定するトランジスタ5及び信号書き込み時に OEL13 に電流が流れるのを抑止するトランジスタ12とに走査信号 Vg2 を与える走査信号配線を用いるのが好適である。なお表示素子である OEL13 のカソード電極は第2の共通電極 609 に接続された全画素回路共通のべた電極である。この画素回路は第1の共通電極 608 と第2の共通電極 609 の間に、OEL13 に所望の駆動電流を流す駆動用トランジスタ11と OEL13 が直列に接続され、更に駆動用トランジスタ11の制御電極に接続され該制御電極の電位設定状態及び電位保持状態を切り替える制御用トランジスタ4を有する構成となっている。

【0027】

駆動用トランジスタ11の制御電極（ゲート）には複数のオン状態に対応した駆動電流を駆動用トランジスタ11の2つの主電極（ソース、ドレイン）間に流すための電位が、制御用トランジスタ4を介して設定される。複数のオン状態とはオンかオフかの2値の切り替えではなく、変調信号に対応して有意なある値の駆動電流を流す状態と有意な他の値の駆動電流を流す状態のことである。

【0028】

変調信号に対応した電位を駆動用トランジスタの制御電極の電位として設定するための構成としては、より簡単な構成として、制御用トランジスタの2つの主電極（制御電極ではない電極であって、具体的にはソース電極とドレイン電極がこれに相当する）にそれぞれ変調信号配線、駆動用トランジスタの制御電極を接続する構成とし、制御用トランジスタを介して変調信号に印加される変調電位が駆動用トランジスタの制御電極の電位として書き込まれる構成を採用することもできる。これが電圧プログラミング型の構成である。

【0029】

一方図3に示している例は、電流プログラミング型の構成である。この構成においては変調信号配線 607 には変調電流信号（図3の i data）を印加する。変調信号配線 607 に流される電流信号は駆動用トランジスタ11の2つの主電極に流れる。それとともに、制御用トランジスタ4が駆動用トランジスタ11の制御電極の電位設定のための経路として機能し、駆動用トランジスタ11の主電極間に流れる変調電流に応じた電位が駆動用トランジスタ11の制御電極の電位として設定される。

【0030】

電圧プログラミング型、電流プログラミング型のいずれの構成においても、制御用トランジスタは電位設定期間の後オフ状態にされ、駆動用トランジスタの制御電極の電位は保持される。この状態で駆動用トランジスタの主電極間に流れる電流が OEL13 に流れ、それによって OEL13 は発光する。

【0031】

なお、電圧プログラミング型、電流プログラミング型のいずれの構成においても、駆動用トランジスタの制御電極の電位が制御電極の容量のみで保持しにくい場合には、該電位

10

20

30

40

50

を保持するための容量（図3では保持コンデンサ17がこれに相当する）を付加的に用いるのが好適である。

【0032】

このように駆動用トランジスタの制御電極の電位を制御用トランジスタをオフにすることによって保持する構成においては特有の問題が生じる。

【0033】

以下ではこの問題を図3の電流プログラミング型の構成を例に挙げて具体的に説明する。なお後述する好適な実施形態ではトランジスタとして薄膜トランジスタを用いているので、以下ではトランジスタをTFTとして表記している。また後述する好適な実施形態では表示素子としては有機エレクトロルミネッセンス素子を用いており、それをOELとして表記している。本実施形態ではガラス基板上にポリシリコンを形成し、該ポリシリコンを用いてTFTを形成している。ただしポリシリコンのように結晶性を有するシリコンを用いる構成に限るものではなく、アモルファスシリコンを用いることもできる。

10

【0034】

TFT11（第1のトランジスタ）の入出力第1電極と制御電極との間にはコンデンサ17が接続されている。またTFT11の入出力第2電極は、TFT12の入出力第1電極に接続され、TFT12の入出力第2電極は、OEL13の一方の電極に接続され、OEL13の他方の電極は、第2の共通電極609に接続される共通電極に接続されている。一方、TFT11の制御電極と入出力第2電極とには、スイッチとして機能するTFT4（第2のトランジスタ）の2つの入出力電極がそれぞれ接続されている。さらに、TFT11の入出力第2電極は、入力電流（idata）の入力、遮断を切り替えるスイッチであるTFT5の一方の入出力電極に接続されていて、TFT5の他方の入出力電極からは入力電流（idata）が入力される。TFT4の制御電極の電圧は、Vg1により制御される。またTFT5とTFT12とはオン状態とオフ状態とが互いに異なることが必要であるが、TFT5とTFT12とにキャリア極性の異なるものを使用することで、これらの制御電極の電圧を単一のVg2により制御できるよう構成されている。

20

【0035】

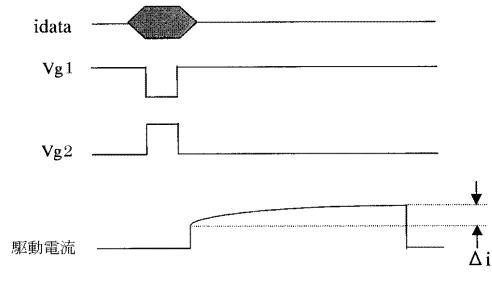

次に、図4のタイミング図を交えて、この駆動回路の動作を説明する。先ず、輝度信号idataが設定される。その後、Vg1が低レベルになりPチャネル型TFT4がオンする。同時に、Vg2は高レベルになりNチャネル型TFT5はオンしidataの電流をTFT11のソース・ドレイン間に流す。また、Vg2が高レベルとなることでPチャネル型TFT12はオフしてOEL13への電流を遮断する。

30

【0036】

この間に、コンデンサ17へは、ソース・ドレイン間にidataの電流を流されたTFT11のゲート電圧が蓄積される。従って、Pチャネル型TFT4のゲート電圧Vg1を図4で示されるように再び高レベルとしてTFT4をオフ状態とし、Pチャネル型TFT12のゲート電圧Vg2を再び低レベルとして、TFT12をオン状態に、TFT5をオフ状態に変えると、電源15からTFT11のソース・ドレインを通してOEL13を発光させるためにidataと同量の電流が流れる。

40

【0037】

上記の一連の動作によりPチャネル型TFT11がidataをコピーして定電流動作を行う。

【0038】

次に本発明の駆動回路で抑制しようとするTFT4のリーク電流について述べる。

【0039】

上述したように、Pチャネル型TFT4は輝度信号idataがTFT11のソース・ドレイン間に流される時Vg1が低レベルになりオンされ、TFT11のゲート電圧がコンデンサ17へ蓄積されるとオフされる。この時の、TFT4\_Vds = (Vdd - TFT11\_Vgs - TFT12\_Vds - OEL\_V - Vcom)が、TFT4のソース・ドレイン間電圧になる。ここで、TFT4\_VdsはTFT4のソース・ドレイン間の電

50

圧、 $V_{dd}$ は第1の共通電極に与えられる電位、 $TFT11\_Vgs$ は $TFT11$ のゲート・ソース間の電圧、 $TFT12\_Vds$ は $TFT12$ のソース・ドレイン間の電圧、 $OEL\_V$ は $OEL13$ のアノード・カソード間の電圧、そして $Vcom$ は第2の共通電極に与えられる電位である。

#### 【0040】

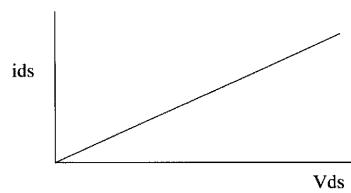

ここで、トランジスタのオフ状態におけるソース・ドレイン間の電圧と電流の関係は図5のグラフのような定性を示し、ゲート電位の制御なしにリーク電流が流れる。これに因り、保持コンデンサ17の電荷は変化していく。この結果、 $TFT11$ のゲート電位は変化し、これに従って $OEL13$ に流れる電流が変わるため、 $OEL13$ の輝度も変化してしまう。従って、図4に示すように、 $Vg2$ が低レベルの間においても、このリーク電流によって駆動電流は上昇していき、これに従って $OEL13$ の輝度も上昇していくことになる。

10

#### 【0041】

この制御用トランジスタ4のリーク電流の状態は製造する表示部ごとに異なってしまう場合がある。そこで本実施形態においては、準備した表示部を実際に駆動して発光させ、その状態で表示素子の発光輝度を測定する。そしてその発光輝度の変動を抑制できるよう第1の共通電極に供給する電位を調整している。具体的には実際の画像表示と同じ条件で全白表示を行い1フレームにおける輝度の変動をホトマルチプレクサで輝度を測定する。そして調整回路であるDC-DCコンバータの動作条件を調整して第1の共通電極に供給する電位を低くしていくことで制御用トランジスタ4のリーク電流を好適に抑制している。

20

#### 【0042】

また、他の形態としては、第2の共通電極に印加する電位を調整する構成も採用できる。

#### 【0043】

また、他の形態としては、所定の色に対応する表示素子を有する画素回路に対して前記第1の共通電極で電位を供給し、他の所定の色に対応する表示する画素回路に対して第3の共通電極で電位を供給し、更に他の所定の色に対応する画素回路に対して第5の共通電極で電位を供給し、第1の共通電極に供給する電位を上記のように設定し、第3の共通電極に供給する電位も同様に設定し、第5の共通電極に供給する電位も同様に設定する形態も採用できる。なお第1、第3、第5の共通電極に供給する電位は各色の表示素子に対応させて適宜異ならせることができる。

30

#### 【0044】

また他の形態としては、表示素子の他端に第2の共通電極から供給される電位を全画素回路に共通のべた電極によって全画素回路に供給するのではなく、所定の色の表示素子を有する画素回路のみに供給するようにし、他の所定の色の表示素子を有する画素回路に対しては第4の共通電極を介して供給するようにし、更に他の所定の色の表示素子を有する画素回路に対しては第6の共通電極を介して供給するようにしても良い。この構成において、第2、第4、第6の共通電極に供給する電位を上記と同様に設定するようにすることができる。

40

#### 【0045】

以下ではより詳細に各実施形態を説明していく。

#### 【0046】

##### 〔実施の形態1〕

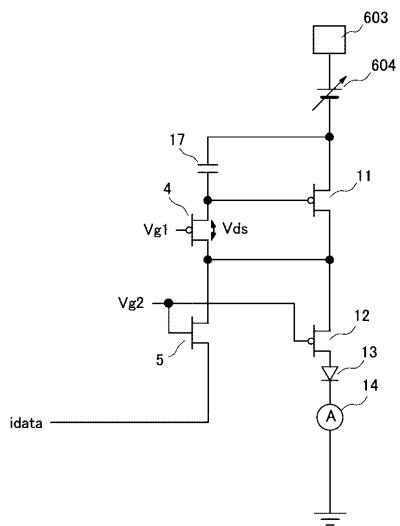

図1は、本発明の画像形成装置の実施形態のひとつの画素回路と電位源である電源装置及び電位源であるグランド部及び調整回路であるDC-DCコンバータの接続の状態を略等価的に示した図である。

#### 【0047】

図1で示される本形態の発光素子駆動回路では、このリーク電流を抑えるために $TFT4$ のソース・ドレイン間電圧を、駆動用トランジスタ11に対して $OEL13$ とは反対側

50

(ここでは高電位側)に設けたDC-DCコンバータ(可変電圧電源として図示)604で制御している。

【0048】

より具体的には、OEL13の定電流性を損なわないOEL\_V、すなわち、OEL13のV-I特性を満足し、さらにOEL13の劣化時電圧上昇をも加味するようDC-DCコンバータ604で制御している。具体的には、TFT4\_Vds = (Vdd - TFT11\_Vgs - TFT12\_Vds - OEL\_V - Vcom)のVddに相当する電位を下げる(第2の共通電極に与えられる電位に近づける)ことにより、TFT4\_Vdsの電圧を低くしている。

【0049】

この電位調整に際しては、実際に電流プログラミングを行って駆動用トランジスタ11のゲート電位を設定し、それに基づいてOEL13を発光させて1フレーム期間の輝度変動をホトマルチプレクサで測定している。それによって検出された輝度変動を抑制できるよう電位設定を行っている。

【0050】

なお調整回路による電位設定は画像表示装置の製造時に1回行えばよく、その電位に固定してしまって構わない。ただしある期間画像表示装置を使用した後、必要に応じて画像表示装置の使用者もしくはメンテナンス担当者が調整回路による調整を行うようにしても良い。

【0051】

以上の様にして、TFT4のソース・ドレイン間の電圧を下げることにより、駆動用トランジスタ11の制御電極電位保持動作時に制御用トランジスタ4の主電極間(ソース・ドレイン間)に流れるリーク電流を抑制することができる。この結果、図1の形態の駆動回路の一連の駆動時において、TFT11のゲート電位変動が抑制され、OEL13に流れる電流の変動を抑制することが可能となる。従って、OEL13の輝度の変動を抑制することができる。

【0052】

図1の駆動回路で、先ず、輝度信号idataが設定される。その後、Vg1が低レベルになりPチャネル型TFT4がオンする。同時に、Vg2は高レベルになりNチャネル型TFT5はオンしidataの電流をTFT11のソース・ドレイン間に流す。

【0053】

また、Vg2が高レベルとなることでPチャネル型TFT12はオフしてOEL13への電流を遮断する。この間に、コンデンサ17へは、ソース・ドレイン間にidataの電流を流されたTFT11のゲート電圧が蓄積される。そして、Pチャネル型TFT4のゲート電圧Vg1を図4で示されるように再び高レベルとしてTFT4をオフ状態とし、Pチャネル型TFT12のゲート電圧Vg2を再び低レベルとして、TFT12をオン状態に、TFT5をオフ状態に変えると、DC-DCコンバータ604からTFT11のソース・ドレインを通してOEL13を発光させるためにidataと同量の電流が第2の共通電極へ流れる。この際、DC-DCコンバータ604により、TFT4のソース・ドレイン間電圧を低下させるような調整が行われており、上記のようにOEL13の定電流性を損なわないOEL\_V、すなわち、OEL13のV-I特性を満足し、さらにOEL13の劣化時電圧上昇をも加味した電圧がTFT11、TFT4、TFT12及びOEL13の一連の素子に印加される。

【0054】

上記の一連の動作によりPチャネル型TFT11がidataをコピーして定電流動作を行うが、TFT4のソース・ドレイン間電圧が低く抑えられているため、リーク電流が抑制され、TFT11のゲート電位は一定に保持され、OEL13に流れる電流も一定に保つことが可能となる。従って、OEL13の輝度も一定に発光させることができる。

【0055】

[実施の形態2]

10

20

30

40

50

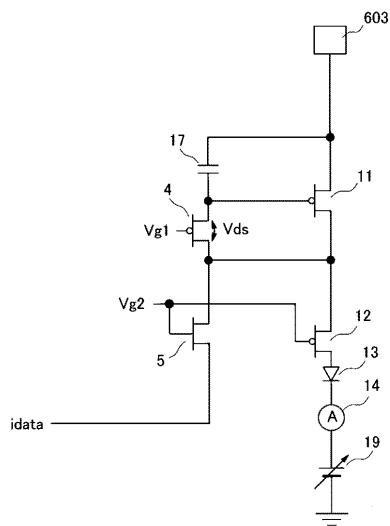

実施の形態 1 では、駆動用トランジスタの主電極のうちの表示素子が接続される主電極ではない主電極に供給する電位を調整回路で調整した構成を示したが、本実施形態では、表示素子に対して駆動用トランジスタが接続される側とは反対側に供給する電位を調整回路で調整する構成を採用している。具体的には図 6 では調整回路を第 1 の共通電極 608 に供給する電位を調整するように配置しているが、本実施形態では調整回路を第 2 の共通電極 609 に供給する電位を調整するように配置する。具体的には調整回路を第 2 の電位源となるグランド部と各画素回路の表示素子が共通に接続される共通電極との間に設けている。

#### 【 0 0 5 6 】

本形態の駆動回路の構成を等価的に示す概略回路図を図 2 に示す。このように本形態の発光素子駆動回路では、TFT4 のリーク電流を抑えるために TFT4 のソース・ドレイン間電圧を第 2 の共通電極側に設けた調整回路（可変電圧電源 19 として図示）で制御している。 10

#### 【 0 0 5 7 】

調整回路の電位設定は実施の形態 1 と同様に行うことができる。具体的には輝度測定を行い、輝度変動が抑制できるように電位を調整する。

#### 【 0 0 5 8 】

より具体的には、OEL13 の定電流性を損なわない OEL\_V、すなわち、OEL13 の V - I 特性を満足し、さらに OEL13 の劣化時電圧上昇をも加味するように第 2 の共通電極側に設けた調整回路で制御している。この手段により、TFT4\_Vds = (Vdd - TFT11\_Vgs - TFT12\_Vds - OEL\_V - Vcom) の Vcom に相当する電位を上げる（第 1 の共通電極に与える電位に近づける）ことにより、TFT4\_Vds の電圧を低くする。 20

#### 【 0 0 5 9 】

この様にして、TFT4 のソース・ドレイン間の電圧を下げることにより、該ソース・ドレイン間に流れるリーク電流を抑制することができる。この結果、以下に説明する図 2 の形態の駆動回路の駆動時において、TFT11 のゲート電位の変動を抑制でき、OEL13 に流れる電流の変動を抑制することが可能となる。従って、OEL13 の輝度の変動を抑制することができる。

#### 【 0 0 6 0 】

図 2 の駆動回路で、先ず、輝度信号 idata が設定される。その後、Vg1 が低レベルになり P チャネル型 TFT4 がオンする。同時に、Vg2 は高レベルになり N チャネル型 TFT5 はオンし idata の電流を TFT11 のソース・ドレイン間に流す。また、Vg2 が高レベルとなることで P チャネル型 TFT12 はオフして OEL13 への電流を遮断する。この間に、コンデンサ 17 へは、ソース・ドレイン間に idata の電流を流された TFT11 のゲート電圧が蓄積される。そして、P チャネル型 TFT4 のゲート電圧 Vg1 を図 4 で示されるように再び高レベルとして TFT4 をオフ状態とし、P チャネル型 TFT12 のゲート電圧 Vg2 を再び低レベルとして、TFT12 をオン状態に、TFT5 をオフ状態に変えると、電源 15 から TFT11 のソース・ドレインを通して OEL13 を発光させるために idata と同量の電流が可変電圧電源 19 へ流れる。この際、調整回路により、TFT11 の設定されたゲート電圧に応じて、TFT4 のソース・ドレイン間電圧を低下させながらも、上記のように OEL13 の V - I 特性を満足し、さらに OEL13 の劣化時電圧上昇をも加味した電圧が TFT11、TFT4、TFT12 及び OEL13 の一連の素子に印加されるように電圧が制御されている。 40

#### 【 0 0 6 1 】

上記の一連の動作により P チャネル型 TFT11 が idata をコピーして定電流動作を行うが、TFT4 のソース・ドレイン間電圧が低く抑えられているため、リーク電流が抑制され、TFT11 のゲート電位の変動が抑制され、OEL13 に流れる電流の変動を抑制することが可能となる。従って、OEL13 の輝度変動を抑制することができる。 50

## 【0062】

## [実施の形態3]

上記実施の形態1、2では第1の共通電極は異なる色に対応する表示素子を有する画素回路が共通に接続されたものであった。

## 【0063】

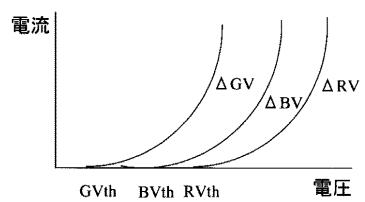

ここで表示素子の特性が対応する色ごとに異なる場合がある。例えば以上述べてきたOEL13が色毎に異なる有機材料で構成されている場合は、OEL13の発光までの電圧閾値や発光時の電流・電圧特性が各色の材料で異なるために、上記、TFT4のソース・ドレイン間の電圧Vdsもこれに応じて変わり、従ってリーク電流の値も用いる有機材料毎に変わることとなる。また、経時劣化によっても上記R, G, B画素材料の電流、電圧特性は変わっていく、この変化の仕方も有機材料毎に異なるものとなる。

10

## 【0064】

ここで、TFTのソース・ドレイン間の電圧が画素回路が対応する色毎に異なる理由を図8を用いて述べる。上述したように、TFT4\_Vds = (Vdd - TFT11\_Vgs - TFT12\_Vds - OEL\_V - Vcom)である。従って、R, G, B各発光材料の電圧・電流特性が異なる(もしくは変化する)とTFT4のソース・ドレイン間電圧は異なる(変化する)。これらのR, G, B各画素材料の電圧・電流特性は以下の要因等により初期状態で夫々異なる。図8で、GVthがG画素1\_2材料の電流の流れ始め電圧、BVthがB画素1\_3材料の電流の流れ始め電圧、RVthがR画素1\_1材料の電流の流れ始め電圧、GVがG画素1\_2材料の電圧に対する電流増加率、BVがB画素1\_3材料の電圧に対する電流増加率、RVがR画素1\_1材料の電圧に対する電流増加率である。従って、G画素1\_2、B画素1\_3、R画素1\_1に設けられた、駆動回路の上記TFT4のソース・ドレイン間の電圧は、同輝度でも初期状態から異なっている。また、Vの違いによっても上記TFT4のソース・ドレイン間の電圧は異なる。また、経時劣化によっても上記R, G, B発光材料の電流、電圧特性は変わっていく。

20

## 【0065】

この場合、これら異なる特性の発光素子を駆動するTFT4のソース・ドレイン間のリーク電流をより好適に抑制できる構成としては、各色に対応する画素回路ごとに共通電極を介して供給する電位をそれぞれ個別に調整した構成とするのが好ましい。そこで本実施形態では、各画素回路の駆動用トランジスタの主電極のうちの表示素子が接続される主電極ではない主電極に電位を供給する共通電極を各色ごとに設ける。そして各色毎の共通電極にそれぞれ印加する電位をそれぞれ別個に調整する構成を採用している。

30

## 【0066】

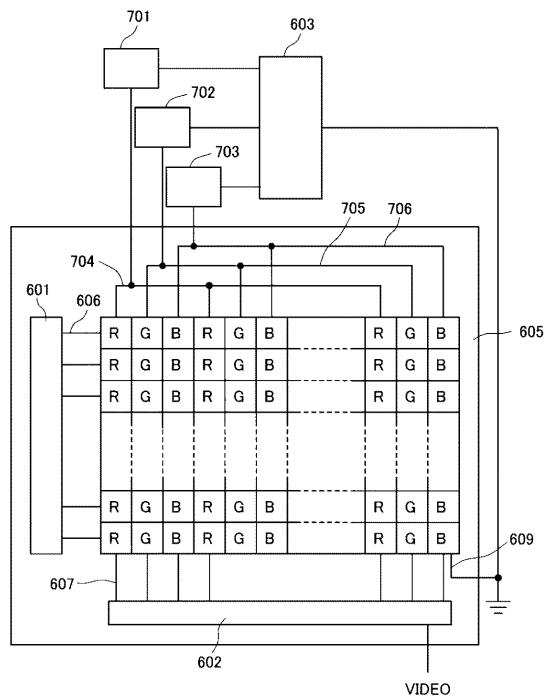

図7に、本実施形態の画像表示装置の構成を概略的に示す。図中、上記実施形態1、2と共に接続する部分は同じ符号を付与している。

## 【0067】

実施形態1、2と異なる部分は、実施形態1、2では第1の共通電極に異なる色に対応する画素回路が共通に接続されていたのに対し、本実施形態では、赤に対応する複数の画素回路は第1の共通電極704に共通に接続され、緑に対応する複数の画素回路は第3の共通電極705に共通に接続され、青に対応する複数の画素回路は第5の共通電極706に共通に接続されている点である。また第1の共通電極704には電源装置603の出力する電位を調整する調整回路であるDC-DCコンバータ701から電位が供給され、第3の共通電極705には電源装置603の出力する電位を調整するDC-DCコンバータ702から電位が供給され、第5の共通電極706には電源装置603の出力する電位を調整するDC-DCコンバータ703から電位が供給される点である。各調整回路の出力電位は個別に調整される。

40

## 【0068】

具体的には、赤に対応する画素回路のみを駆動して赤の表示を行い、輝度測定を行う。そして、1フレーム期間内での赤の輝度変動を抑制するようにDC-DCコンバータ701の出力電位を調整する。次に緑に対応する画素回路のみを駆動して緑の表示を行い、

50

輝度測定を行う。そして、1フレーム期間内での緑の輝度変動を抑制できるようにDC-DCコンバータ702の出力電位を調整する。次に青に対応する画素回路のみを駆動して青の表示を行い、輝度測定を行う。そして、1フレーム期間内での青の輝度変動を抑制できるようにDC-DCコンバータ703の出力電位を調整する。

【0069】

これによって駆動用トランジスタに供給する電位を色毎に調整することができる。

【0070】

[実施の形態4]

図9に、本実施形態の画像形成装置の構成を概略的に示す。図中、上記実施形態1~3と共に示す部分は同じ符号を付与している。

10

【0071】

実施の形態3では駆動用トランジスタの主電極のうちの表示素子が接続される主電極ではない主電極に供給する電位を色毎に設けた調整回路で調整した構成を示したが、本実施形態では、表示素子に対して駆動用トランジスタが接続される側とは反対側に供給する電位を調整回路で調整する構成を採用している。具体的には図7では複数の調整回路を第1の共通電極704、第3の共通電極705、第5の共通電極706に供給する電位を調整するようにそれぞれ配置しているが、本実施形態では色毎の調整回路を表示素子の駆動用トランジスタと接続される側とは反対側の電位を調整するように配置している。以上述べてきた実施の形態1から3では第2の共通電極609によって全画素回路に共通に電位を与えることができたが、本実施形態では表示素子のカソード電極は色毎に配置している。

20

【0072】

そして、赤に対応する複数の画素回路の表示素子のカソード電極は第2の共通電極903に共通に接続され、緑に対応する複数の画素回路の表示素子のカソード電極は第4の共通電極902に共通に接続され、青に対応する複数の画素回路の表示素子のカソード電極は第6の共通電極901に共通に接続されている。また第2の共通電極903にはグランド部の出力する電位を調整する調整回路であるDC-DCコンバータ906から電位が供給され、第4の共通電極902にはグランド部の出力する電位を調整するDC-DCコンバータ905から電位が供給され、第6の共通電極901にはグランド部の出力する電位を調整するDC-DCコンバータ904から電位が供給される。各調整回路の出力電位は個別に調整される。調整の具体的な方法は実施の形態3と同様である。

30

【0073】

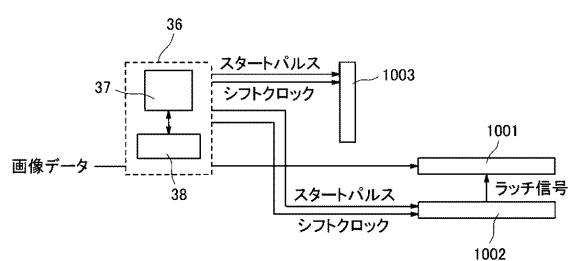

なお以上各実施の形態を説明してきたが、そこで説明した走査回路601、変調回路602の構成としては図10に示すものを用いることができる。

【0074】

図10には走査回路601を構成するVシフトレジスタ1003と変調回路602を構成するHシフトレジスタ1002及びラッチ1001を示している。Vシフトレジスタ1003から走査信号配線に走査信号が印加され、ラッチ1001から変調信号配線に変調信号が印加される。表示制御部36はコントローラ37と映像信号変換メモリ38を有しており、画像データや必要に応じてタイミング制御信号が入力され、走査回路及び変調回路にシフトパルスやスタートパルスといったタイミング信号や、ビデオ信号を入力する。

40

【図面の簡単な説明】

【0075】

【図1】本発明に係る駆動回路の一実施形態の構成を示す概略回路図である。

【図2】本発明に係る駆動回路の一実施形態の構成を示す概略回路図である。

【図3】本発明に係る電流設定型の画素回路の構成を示す概略回路図である。

【図4】本発明の効果を説明するための発光素子電流駆動回路の動作タイミングと駆動電流値を示す図である。

【図5】トランジスタのオフ状態におけるソース・ドレイン間の電圧と電流の関係を示す図である。

【図6】本発明の実施形態の画像表示装置の構成を示す図である。

50

【図7】本発明の実施形態の画像表示装置の構成を示す図である。

【図8】特性の異なる有機EL素子の電流と電圧の関係を示す図である。

【図9】本発明の実施形態の画像表示装置の構成を示す図である。

【図10】実施形態で用いた走査回路及び変調回路の構成を示す図である。

【符号の説明】

【0076】

4, 5, 11, 12 トランジスタ

13 OEL

14 電流計

15 電源

10

17 コンデンサ

19 可変電圧電源

36 表示制御部

37 コントローラ

38 映像信号変換メモリ

601 走査回路

602 変調回路

603 電源装置

604 DC - DCコンバータ

605 表示部

20

606 走査信号配線

607 変調信号配線

608, 609 共通電極

701 ~ 703 DC - DCコンバータ

704 ~ 706, 901 ~ 903 共通電極

904 ~ 906 DC - DCコンバータ

1001 ラッチ

1002 Hシフトレジスタ

1003 Vシフトレジスタ

【 図 1 】

【 図 2 】

【図3】

【 図 4 】

【 図 5 】

【 6 】

【図7】

【図8】

【図9】

【図10】

---

フロントページの続き

(51)Int.Cl.

F I

|         |       |         |

|---------|-------|---------|

| G 0 9 G | 3/20  | 6 4 2 C |

| G 0 9 G | 3/20  | 6 4 2 L |

| G 0 9 G | 3/20  | 6 4 2 P |

| G 0 9 G | 3/20  | 6 7 0 Q |

| H 0 5 B | 33/12 | Z       |

| H 0 5 B | 33/14 | A       |

(72)発明者 近藤 茂樹

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 奈良田 新一

(56)参考文献 特開2002-215095 (JP, A)

特開2003-202837 (JP, A)

特表2002-514320 (JP, A)

国際公開第98/040871 (WO, A1)

特開2002-032058 (JP, A)

特開2003-280583 (JP, A)

特開2002-304156 (JP, A)

特開2001-265283 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 0 9 G 3 / 2 0 , 3 / 3 0 - 3 / 3 2