#### (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2008-263381 (P2008-263381A)

(43) 公開日 平成20年10月30日(2008, 10, 30)

(51) Int.Cl.

FΙ

テーマコード (参考)

HO4N 1/00 GO6F 12/16 (2006.01) (2006.01) HO4N 1/00 GO6F 12/16

C 340F 5CO62

審査請求 未請求 請求項の数 8 OL (全 13 頁)

(21) 出願番号 (22) 出願日 特願2007-104215 (P2007-104215) 平成19年4月11日 (2007.4.11) (71) 出願人 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74)代理人 100076428

弁理士 大塚 康徳

(74)代理人 100112508

弁理士 高柳 司郎

(74)代理人 100115071

弁理士 大塚 康弘

(74)代理人 100116894

弁理士 木村 秀二

(72) 発明者 片岡 淳之介

東京都大田区下丸子3丁目30番2号 キ

ヤノン株式会社内

Fターム(参考) 5C062 AA02 AA05 AA30 AA35 AB42

AB49 AC48

(54) 【発明の名称】情報処理装置とその装置におけるメモリバックアップ方法

## (57)【要約】

【課題】 拡張メモリが実装された場合でも基本メモリの容量の内の多くをワーク領域として確保しなければならないため、拡張メモリを実装してもファクシミリ用の画像メモリ領域を十分に拡張できない。

【解決手段】 複数のメモリ基板を実装して、当該メモリ基板にアクセスできる情報処理装置であって、メモリをバックアップするための電池113と、電池113からメモリ基板への電力供給を制御するとともに、複数のメモリの内の拡張メモリ基板が実装された状態で装置の電源がオフされると、電池113から基本メモリへの電力供給を遮断するバックアップ回路116とを有する。 【選択図】 図1

#### 【特許請求の範囲】

#### 【請求項1】

複数 の メモ リ 基 板 を 実 装 し て 、 当 該 メ モ リ 基 板 に ア ク セ ス で き る 情 報 処 理 装 置 で あ っ て

メモリをバックアップするための電池と、

前記電池から前記メモリ基板への電力供給を制御し、前記複数のメモリ基板の内の第 1 の メ モ リ 基 板 が 実 装 さ れ た 状 態 で 前 記 装 置 の 電 源 が オ フ さ れ た 場 合 、 前 記 電 池 か ら 前 記 複 数 の メ モ リ 基 板 の 内 の 第 2 の メ モ リ 基 板 へ の 電 力 供 給 を 遮 断 し 、 前 記 第 1 の メ モ リ 基 板 が 実装されていない状態で前記装置の電源がオフされると、前記電池からの電力を前記第2 のメモリ基板へ供給するように制御するバックアップ制御手段と、

を有することを特徴とする情報処理装置。

#### 【請求項2】

前記バックアップ制御手段によりバックアップされるメモリ基板を識別する識別手段と

前記装置の電源がオフされると、前記識別手段によりバックアップされると識別された メモリ基板にデータを転送する転送手段と、

を更に有することを特徴とする請求項1に記載の情報処理装置。

#### 【請求項3】

前記第1のメモリ基板は拡張メモリ基板で、前記第2のメモリ基板は、前記装置の基本 メモリを搭載したメモリ基板であることを特徴とする請求項1又は2に記載の情報処理装 置。

【請求項4】

複数 の メ モ リ 基 板 を 実 装 し て 、 当 該 メ モ リ 基 板 に ア ク セ ス で き る 情 報 処 理 装 置 で あ っ て

メモリをバックアップするための電池と、

前 記 複 数 の メ モ リ 基 板 の う ち 、 バ ッ ク ア ッ プ 対 象 の デ ー タ を 記 憶 し て い る メ モ リ 基 板 を 検知する検知手段と、

前記装置の電源がオフされると、前記電池よりの電力を、前記複数のメモリの内の前記 検 知 手 段 で 検 知 さ れ た メ モ リ 基 板 へ 供 給 し て 当 該 メ モ リ 基 板 を バ ッ ク ア ッ プ し 、 前 記 複 数 のメモリの内の前記検知手段で検知されたメモリ基板以外のメモリ基板へ供給しないよう に制御するバックアップ制御手段と、

を有することを特徴とする情報処理装置。

#### 【請求項5】

複数のメモリ基板を実装して、当該メモリ基板にアクセスできる情報処理装置における メモリバックアップ方法であって、

前 記 複 数 の メ モ リ 基 板 の 内 の 第 1 の メ モ リ 基 板 が 実 装 さ れ た 状 態 で 前 記 装 置 の 電 源 が オ フ さ れ た 場 合 、 メ モ リ を バ ッ ク ア ッ プ す る た め の 電 池 か ら 前 記 複 数 の メ モ リ 基 板 の 内 の 第 2のメモリ基板への電力供給を遮断する工程と、

前記第1のメモリ基板が実装されていない状態で前記装置の電源がオフされると、前記 電 池 か ら の 電 力 を 前 記 第 2 の メ モ リ 基 板 へ 供 給 す る よ う に 制 御 す る 工 程 と 、

を有することを特徴とする情報処理装置におけるメモリバックアップ方法。

前 記 バ ッ ク ア ッ プ 制 御 工 程 に よ り バ ッ ク ア ッ プ さ れ る メ モ リ 基 板 を 識 別 す る 識 別 工 程 と

前記装置の電源がオフされると、前記識別工程によりバックアップされると識別された メモリ基板にデータを転送する転送工程と、

を 更 に 有 す る こ と を 特 徴 と す る 請 求 項 5 に 記 載 の 情 報 処 理 装 置 に お け る メ モ リ バ ッ ク ア ッ プ方法。

## 【請求項7】

前記第1のメモリ基板は拡張メモリ基板で、前記第2のメモリ基板は、前記装置の基本

10

20

30

40

メモリを搭載したメモリ基板であることを特徴とする請求項 5 又は 6 に記載の情報処理装置におけるメモリバックアップ方法。

#### 【請求項8】

複数のメモリ基板を実装して、当該メモリ基板にアクセスできる情報処理装置における メモリバックアップ方法であって、

前記複数のメモリ基板のうち、バックアップ対象のデータを記憶しているメモリ基板を 検知する検知工程と、

前記装置の電源がオフされると、メモリをバックアップするための電池よりの電力を、 前記複数のメモリの内の前記検知工程で検知されたメモリ基板へ供給して当該メモリ基板 をバックアップし、前記複数のメモリの内の前記検知工程で検知されたメモリ基板以外の メモリ基板へ供給しないように制御するバックアップ制御工程と、

を有することを特徴とする情報処理装置におけるメモリバックアップ方法。

【発明の詳細な説明】

## 【技術分野】

#### [00001]

本発明は、複数のメモリ基板を実装して、当該メモリ基板にアクセスできる情報処理装置とその装置におけるメモリバックアップ方法に関する。

#### 【背景技術】

## [0002]

複写機能とファクシミリ機能を備えた複合機(多機能装置)では、複写機能で使用する画像データを記憶する第1メモリ領域と、ファクシミリ機能で使用する画像データを記憶する第2メモリ領域とをそれぞれ区別している。そして複写機能では、スキャナで読み取った画像データを、その一時的に第1メモリ領域に格納した後、その画像データを読み出して印刷(コピー)している。また、ファクシミリ機能では、メモリ受信時或はメモリ送信時に、受信した画像データ或は送信対象の画像データを第2メモリ領域に蓄積している。この第2メモリ領域の画像データは、印刷或は送信する前に本体の電源がオフされた場合にもその内容を保持する必要があるため、バッテリによりバックアップされている。但し、第1メモリのデータ、及び実行中のプログラムのワーク領域のデータは、電源オフの際には保持する必要がないため、電池によるバックアップはなされていない。

### [0003]

ここで、メモリのバックアップに必要な電力は、バックアップするメモリの容量に比例して大きくなる。このため、メモリ容量が拡張された場合には、バックアップ時間が短縮されてします。このため、メモリ容量に応じてバッテリ容量を増やす必要が生じる。このような問題を解決するために、メモリ容量を拡張した場合でも、基本のメモリ領域だけをバックアップし、拡張メモリの領域をバックアップしない方法が提案されている(特許文献 1 参照)。この特許文献 1 では、ファクシミリ用のメモリ領域及びプログラムのワーク領域は、常に基本メモリに配置される。そして拡張メモリが実装された場合は、コピー用(展開、回転、ソート等)の画像メモリ領域が拡張メモリに配置されている。

【特許文献1】特開2002-209074公報

## 【発明の開示】

【発明が解決しようとする課題】

## [0004]

しかしながら、この特許文献1の方法では、基本メモリにプログラム実行用のワーク領域が配置されているので、拡張メモリが実装された場合でも基本メモリの容量の内の多くをワーク領域として確保しなければならない。その結果、拡張メモリを実装してもファクシミリ用の画像メモリ領域を十分に拡張できないという問題があった。

## [0005]

本発明の目的は上記従来技術の問題点を解決することにある。

## [0006]

本 発 明 の 特 徴 は 、 バ ッ ク ア ッ プ 対 象 の メ モ リ 領 域 を 制 限 す る こ と に よ り 、 バ ッ ク ア ッ プ

10

20

30

40

に要する電池のバッテリ容量を大きくする必要がなくなる。

#### [0007]

またバッテリバックアップされるメモリ領域を制限し、そのバックアップされる領域に 消滅させたくないデータを格納することにより、バックアップ領域を制限しながら必要な データを維持できる。

【課題を解決するための手段】

#### [00008]

上記目的を達成するために本発明の一態様に係る情報処理装置は以下のような構成を備える。即ち、

複数のメモリ基板を実装して、当該メモリ基板にアクセスできる情報処理装置であって

メモリをバックアップするための電池と、

前記電池から前記メモリ基板への電力供給を制御し、前記複数のメモリ基板の内の第1のメモリ基板が実装された状態で前記装置の電源がオフされた場合、前記電池から前記複数のメモリ基板の内の第2のメモリ基板への電力供給を遮断し、前記第1のメモリ基板が実装されていない状態で前記装置の電源がオフされると、前記電池からの電力を前記第2のメモリ基板へ供給するように制御するバックアップ制御手段と、

## [0009]

を有することを特徴とする。

上記目的を達成するために本発明の一態様に係る情報処理装置は以下のような構成を備える。即ち、

複数のメモリ基板を実装して、当該メモリ基板にアクセスできる情報処理装置であって

メモリをバックアップするための電池と、

前記複数のメモリ基板のうち、バックアップ対象のデータを記憶しているメモリ基板を 検知する検知手段と、

前記装置の電源がオフされると、前記電池よりの電力を、前記複数のメモリの内の前記検知手段で検知されたメモリ基板へ供給して当該メモリ基板をバックアップし、前記複数のメモリの内の前記検知手段で検知されたメモリ基板以外のメモリ基板へ供給しないように制御するバックアップ制御手段と、を有することを特徴とする。

### [0010]

上記目的を達成するために本発明の一態様に係る情報処理装置におけるメモリバックアップ方法は以下のような工程を備える。即ち、

複数のメモリ基板を実装して、当該メモリ基板にアクセスできる情報処理装置における メモリバックアップ方法であって、

前記複数のメモリ基板の内の第 1 のメモリ基板が実装された状態で前記装置の電源がオフされた場合、メモリをバックアップするための電池から前記複数のメモリ基板の内の第 2 のメモリ基板への電力供給を遮断する工程と、

前記第1のメモリ基板が実装されていない状態で前記装置の電源がオフされると、前記電池からの電力を前記第2のメモリ基板へ供給するように制御する工程と、 を有することを特徴とする。

#### [0011]

上記目的を達成するために本発明の一態様に係る情報処理装置におけるメモリバックアップ方法は以下のような工程を備える。即ち、

複数のメモリ基板を実装して、当該メモリ基板にアクセスできる情報処理装置における メモリバックアップ方法であって、

前記複数のメモリ基板のうち、バックアップ対象のデータを記憶しているメモリ基板を 検知する検知工程と、

前記装置の電源がオフされると、メモリをバックアップするための電池よりの電力を、前記複数のメモリの内の前記検知工程で検知されたメモリ基板へ供給して当該メモリ基板

10

20

30

40

をバックアップし、前記複数のメモリの内の前記検知工程で検知されたメモリ基板以外の メモリ基板へ供給しないように制御するバックアップ制御工程と、 を有することを特徴とする。

#### 【発明の効果】

## [0012]

本発明によれば、バックアップ対象のメモリ基板を制限することにより、バックアップに要する電池のバッテリ容量を大きくする必要がない。またバックアップ領域を制限しながら必要なデータを保持できる。

【発明を実施するための最良の形態】

## [0013]

以下、添付図面を参照して本発明の好適な実施の形態を詳しく説明する。尚、以下の実施の形態は特許請求の範囲に係る本発明を限定するものでなく、また本実施の形態で説明されている特徴の組み合わせの全てが本発明の解決手段に必須のものとは限らない。

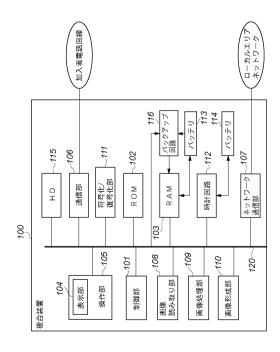

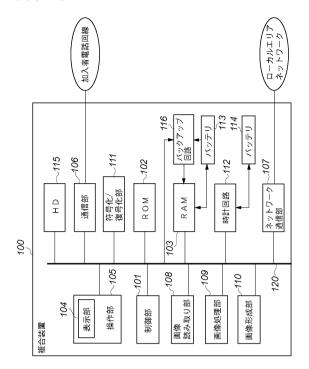

## [0014]

図 1 は、本発明の実施の形態に係る複合装置(多機能処理装置)の構成を示すブロック図である。

## [0015]

図1において、制御部101はCPUを有し、この複合装置100の全体的な動作を制御する。ROM102は、制御部101が実行するプログラムや各種のデータ等を格納している。RAM103には、制御部101により実行されるプログラムがHD115からロードされ、このRAM103にプログラムがロードされた状態で、そのプログラムが制御部101の制御の下に実行される。また、このRAM103は、制御部101による制御処理の実行時に各種データを記憶するワークエリア及び、複写機能で使用する画像データを記憶する第1のメモリ領域、ファクシミリ機能で使用する画像データを記憶する第2のメモリ領域をも提供している。更に、このRAM103は、1つ以上のユニットに分割され、DIMMスロットに挿抜することで、各ユニットが着脱可能なように構成されている。

## [0016]

時計回路112は、時刻情報を出力するためのものであり、バッテリ114からの電力により駆動されて常時計時を行なっている。操作部105は、ユーザが操作するための各種キーや表示部104を有している。表示部104はタッチパネルで構成されており、この複合装置100を操作するための各種情報やソフトキー等を表示し、ユーザによる操作を受付けている。

## [0017]

通信部106は、アナログ電話回線を介してファクシミリ(FAX)通信を行う。この通信部106は、ファクシミリにより受信した画像を直接画像形成部110に出力して印刷せずに、一旦RAM103に蓄積した後で印刷するメモリ受信機能を有する。また、この通信部106は、ファクシミリ送信用の画像データを一旦RAM103に蓄積した後、設定された時間になると送信するタイマ送信機能も有している。このRAM103に蓄積されたファクシミリの送受信画像は、本体の電源がオフされた場合でも一定時間は、バッテリ113からの電力供給により保持される。

## [0018]

画像読み取り部(スキャナ部)108は、原稿を読み取り、その原稿画像に対応する画像データを生成する。画像処理部109は、画像読み取り部108で生成した画像データや印刷する画像データに対する画像処理を実行する。画像形成部(プリンタエンジン)110は、画像データに基づいて記録シートに画像を形成(印刷)する。複写動作の場合は画像読み取り部108で読み取った画像データに基づいて複写画像を印刷し、プリント動作の場合は、ネットワークを介してPC(不図示)から受信した画像データに基づいて画像を印刷する。

10

20

30

### [0019]

通信部107は、ネットワークとの間でのデータの送受信を制御している。この通信部107は、ネットワークを介してPC(不図示)から印刷データを受信したり、画像読み取り部108で読み取って生成した画像データを、ネットワークを介してPC等に転送する。符号化/復号化部111は、画像読み取り部108で生成した画像データを通信部106で送信する際に符号化したり、また通信部106で受信した画像データを復号化する機能を有する。また更に符号化/復号化部111は、複写動作をする際に、画像読み取り部108で生成した画像データを旧り115に記憶するために符号化したり、或はHD115に記憶された符号化データを復号する。116はメモリのバックアップ回路で、例えば図4B或は図7に示すような回路を有している。

[0020]

CPUバス120は、制御部101、ROM102、RAM103、操作部105、通信部106、通信部107、画像読み取り部108、画像処理部109、画像形成部110、符号化/復号化部111を接続する。このCPUバス120は、アドレス信号を転送するアドレスバス、制御信号を転送するコントロールバス及び各種データを転送するデータバスの総称である。

[0021]

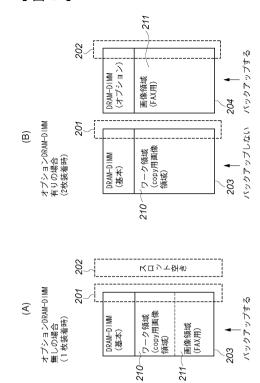

図2(A)(B)は、本実施の形態に係る複合装置100のRAMの構成を説明する図である。この実施の形態1では、RAM103は基本メモリと拡張メモリの2つに分かれており、基本メモリ基板(以下、基本メモリ)及び拡張メモリ基板(以下、拡張メモリ)は両者共DIMM形状で抜き挿しできる形態をとっている。図2において、201は基本メモリ203を実装するためのRAM・DIMMスロットを示し、202は拡張メモリ204を実装するためのRAM・DIMMスロットを示す。尚、ここでは基本メモリが実装された基板を第1のメモリ基板とし、拡張メモリが実装された基板を第2のメモリ基板とするが、本発明はこれに限定されない。

[0022]

図 2 ( A ) は、基本メモリ 2 0 3 だけが実装されて拡張メモリが装着されない状態を示している。そして図 2 ( B ) は、基本メモリ 2 0 3 と拡張メモリ 2 0 4 の両方が装着された状態を示している。

[0023]

図 2 ( A ) では、実装されている基本メモリ 2 0 3 に、ワーク領域 2 1 0 と F A X 用の画像領域 2 1 1 とが割り当てられている。ワーク領域 2 1 0 は、制御部 1 0 1 がプログラムを展開及び実行するメモリ領域及び、複写機能で使用する画像データを記憶するメモリ領域を含んでいる。また画像領域 2 1 1 は、ファクシミリ機能で使用する画像データを記憶するメモリ領域である。

[0024]

図 2 ( B ) では、基本メモリ 2 0 3 に、制御部 1 0 1 がプログラムを展開及び実行するワーク領域及び、複写機能で使用する画像データを記憶するワーク領域 2 1 0 が割り当てられている。そして、拡張メモリ 2 0 4 には、ファクシミリ機能で使用する画像データを記憶する画像領域が割り当てられている。

[ 0 0 2 5 ]

また本実施の形態 1 では、、拡張メモリ 2 0 4 が装着された場合とそうでない場合とで、バッテリ 1 1 3 によりバックアップされるメモリが変更される。即ち、図 2 ( A ) では、基本メモリ 2 0 3 はバックアップされず、拡張メモリ 2 0 4 だけがバッテリ 1 1 3 でバックアップされている。

[0026]

こうすることにより、ファクシミリ機能で使用する画像データを記憶する画像領域21 1 は常にバッテリ113によりバックアップされる。また基本メモリ203の容量と拡張 メモリ204の容量とが同じであれば、拡張メモリ204が実装された場合でも拡張メモ 10

20

30

40

10

20

30

40

50

リ 2 0 4 が実装されない場合でも、バッテリ 1 1 3 でバックアップされるメモリ容量は同じになる。従って、拡張メモリ 2 0 4 が実装された場合でも、バックアップ時間が変更されることはない。

## [ 0 0 2 7 ]

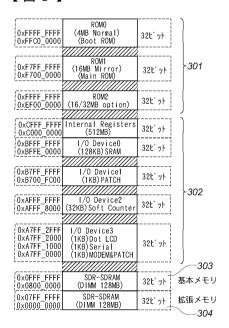

図3は、本実施の形態に係る複合装置の制御部101からみたメモリマップを説明する図で、このメモリマップ上に基本メモリ203及び拡張メモリ204のアドレス空間上の配置を示している。

## [0028]

図において、301はROM102のアドレス空間を示し、302は制御部101のレジスタ、I/Oマップ用のメモリ空間を示している。基本メモリ203のアドレス空間303は、80000番地からFFFFFFF番地までの128MBであり、拡張メモリ204のアドレス空間303は、00000番地から7FFFFFFF番地までの128MBである。

## [0029]

[実施の形態1]

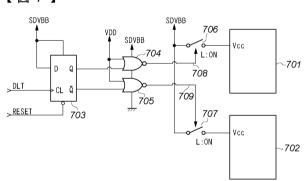

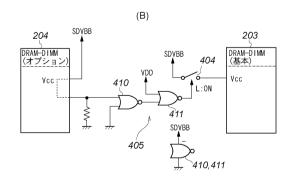

図4A,図4Bは、本実施の形態1に係る複合装置におけるRAM103のバックアップ(バックアップ制御)回路の一例を示す図である。

#### [0030]

図 4 A は、バックアップ用の電池(バッテリ) 1 1 3 を示している。図 4 ( B ) は、バックアップ回路 1 1 6 の一例を示している。

#### [0031]

バッテリ113から供給されるバックアップ電源(+3.3V)が、条件に応じて基本メモリ203のVcc端子、或は拡張メモリ204のVcc端子に供給される。スイッチ404は、オンの場合に基本メモリ203のVcc端子に駆動用の電源を供給し、オフの場合には、基本メモリ203のVcc端子に駆動用の電源を供給しない。拡張メモリ204には、駆動用の電源をメインボード(制御部101のCPUが搭載されている基板)に戻すための端子があり、この戻された信号がロジック回路405(メインボードに実装されている)を介して、スイッチ404に入力される。このロジック回路405に入力されるVDD信号は、本体の主電源がオフされた時は供給されない+3.3V電源電圧に接続されている。尚、このロジック回路405において、410,411はNOR回路で、このNOR回路411の出力がロウレベルの時にスイッチ404がオンされる。

## [0032]

本実施の形態 1 では、基本メモリ 2 0 3 は常に実装されており、拡張メモリ 2 0 4 は実装されている場合と、実装されていない場合とがある。

## [0033]

ここで拡張メモリ204が実装されていない場合について説明する。この場合は、拡張メモリ204を介してバッテリ113から供給される電源電圧(SDVBB)がメインボードに戻されない。このためNOR回路410の2つの入力は共にロウレベルとなり、その出力はハイレベルになる。よって、本体の電源がオンされているかオフされていないかに拘わらず、NOR回路411の出力はロウレベルとなってスイッチ404がオンされたままとなり、基本メモリ203には電圧(SDVBB)が供給されることになる。尚、この電圧(SDVBB)は、複合装置100の電源がオンの状態では電源電圧VDDとなっている。

## [0034]

次に拡張メモリ204が実装されている場合について説明する。

## [0035]

この場合は、この拡張メモリ204を介してバッテリ113からの電圧(SDVBB)がメインボードに戻される。これにより、NOR回路410の出力がロウレベルとなる。そして本体電源がオフされている時(VDD=0)は、NOR回路411の出力がハイレベルとなってスイッチ404をオフにする。また本体電源がオンされている時(VDD=

ハイレベル)は、NOR回路411の出力がロウレベルとなりスイッチ404をオンにする。

## [0036]

このようにして、本体の電源がオフされたとき、拡張メモリ204が実装されていない場合は、基本メモリ203がバッテリ113によりバックアップされる。一方、拡張メモリ204が実装されている場合は、本体の電源がオフされたときは基本メモリ203への電池113からの電力供給が遮断されるためバッテリ113によりバックアップされず、拡張メモリ204だけがバックアップされる。また本体の電源がオンされた状態では、拡張メモリ204の有無に拘わらずスイッチ404がオンされ、基本メモリ203にもバッテリ113からの電圧が入力される。

[0037]

以上説明したように本実施の形態1によれば、拡張メモリ204が実装された状態で、装置の電源がオフされると、自動的にその拡張メモリ204だけをバッテリによりバックアップする。これにより、バックアップ対象のメモリ領域の増大を抑えることにより、バッテリの消費電力を抑えてバックアップに要する時間が短縮されるのを防止できる。この際、実装された拡張メモリ204にバックアップすべきデータを保持し、バックアップされない基本メモリには、電源オフで消去されても良いデータだけを保持している。これにより、電源オフによるデータの消滅による影響を少なくできる。

[0038]

[実施の形態2]

次に本発明に係る実施の形態2について説明する。

[0039]

本実施の形態 2 では、複合装置本体の電源がオフされると、ファクシミリ用の画像データが記憶されているメモリ領域を検知する。そして、その画像データが蓄積されている領域だけをバッテリ 1 1 3 によりバックアップする。尚、この実施の形態 2 に係る複合装置 1 0 0 のハードウェア構成は、前述の実施の形態 1 の複合装置のハードウェア構成と同じであるため、その説明を省略する。

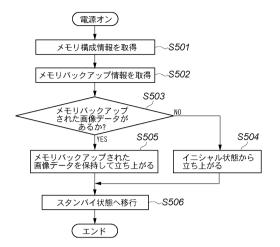

[0040]

図5は、本発明の実施の形態2に係る複合装置100における電源オン時の動作を示すフローチャートである。尚、この処理を実行するプログラムは、実行時にはRAM103に記憶されており、制御部101のCPUの制御の下に実行される。

[0041]

この処理は複合装置100の電源オンにより開始され、まずステップS501で、拡張メモリ204が装着されているかどうかを判別して、メモリの構成情報を取得する。次にステップS502で、メモリのバックアップ情報を求める。次にステップS503に進み、バッテリ113でバックアップされた画像データがあるかどうかを判定し、バックアップされた画像データがなければステップS504に進み、イニシャル状態から立ち上げる。そしてステップS506に進み、スタンバイ状態へ移行する。

[0042]

一方ステップS503で、バッテリ113でバックアップされた画像データがあればステップS505に進み、そのバックアップされた画像データを保持して立ち上げ処理を実行する。そしてステップS506のスタンバイ状態へ移行する。

[ 0 0 4 3 ]

このように本実施の形態 2 では、バックアップすべき画像データのある領域のみをバックアップしているので、バッテリーバックアップされた画像データがある領域以外の領域のデータは不定である。

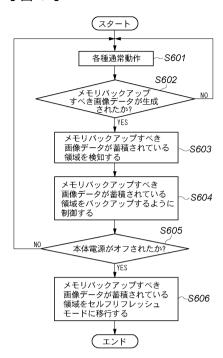

[0044]

図 6 は、本発明の実施の形態 2 に係る複合装置 1 0 0 の電源オフ時の動作を示すフローチャートである。尚、この処理を実行するプログラムは、実行時には R A M 1 0 3 に記憶されており、制御部 1 0 1 の C P U の制御の下に実行される。

10

20

30

40

[0045]

ステップS601では、コピー動作やファクシミリ動作などの各種動作をしている。ステップS602で、バックアップすべき画像データ(例えば、メモリ受信したファクショリデータ、或はタイマ送信が指定されたファクシミリデータ)が生成されたか否かを判する。そしてバックアップすべき画像データが生成されていない場合はステップS601に戻って通常動作を継続する。ステップS602で、バックアップすべき画像データが直されている領域を識別する。次にステップS604に進み、バックアップするようにバックアップするようにバックアップするようにバックアップするようにバックアップするようにバックアップするようにがカフされたかを検知した場合はステップS605で本体電源がオフされたことを検知した場合はステップS606に進み、バックアップすべき画像データが蓄積されているメモリ領域をセルフ・リフレッシュモードに移行して電源オフに備える。

[0046]

図7は、この実施の形態2に係るバックアップ回路116を説明する回路図である。

[0047]

図において、701,702はそれぞれメモリ基板を示し、これらは前述の基本メモリ203と拡張メモリ204であっても良く、或は拡張メモリ204とは別の2つの拡張メモリであっても良い。703はフリップフロップ、704,705はそれぞれNOR回路である。尚、これらフリップフロップ703、NOR回路704,705は共にバッテリ113から供給される電力により動作している。スイッチ706,707は共に、前述の図4(B)のスイッチ404と同様に、各対応する制御信号708,709がロウレベルの時にオンし(閉じ)、ハイレベルの時にオフ(開く)になる。

[0048]

いま、この複合装置100の電源がオンされている状態では、電源電圧VDDが供給されているためNOR回路704,705にはハイレベルの信号が入力されて、その出力は共にロウレベルになっている。よってスイッチ706,707は閉じた状態で、メモリ基板701,702には電源電圧が供給されている。

[0049]

フリップフロップ703に入力されているDLT信号及びRESET信号は共に、制御部101のCPUから供給される。即ち、複合装置100の電源がオフされた状態でメモリ基板701だけをバックアップする場合は、CPUはRESET信号をハイレベルにした状態でDLT信号を出力する。これによりフリップフロップ703のQ出力がハイレベルとなり、NOR回路704の出力がロウレベルとなってスイッチ706がオンされる。こうしてメモリ基板701が電池113によりバックアップされることになる。

[0050]

逆に、複合装置100の電源がオフされた状態でメモリ基板702だけをバックアップする場合は、CPUはRESET信号をロウレベルにする。これによりフリップフロップ703のQ出力がロウレベル、Q/(Qの反転)がハイレベルとなり、NOR回路705の出力がロウレベルとなってスイッチ707がオンされる。こうしてメモリ基板702が電池113によりバックアップされることになる。

[0051]

従って前述の図6のステップS604では、バックアップすべき画像データが格納されている領域のバックアップするように、DLT信号或はRESET信号を出力してスイッチ706,707を切替える。

[0052]

尚、この実施の形態2では、メモリ基板が2枚の場合で説明したが、より多くの枚数であっても良い。

[ 0 0 5 3 ]

50

10

20

30

10

20

30

40

50

#### 「実施の形態31

また本発明の実施の形態 3 では、複合装置 1 0 0 の電源がオフされた時に、予め、バックアップすべき画像データを記憶しているメモリ領域を検知しておく。そして、その画像データの容量からバックアップする時間を算出する。そのバックアップ時間に応じてバックアップ対象のメモリ基板を切り換えることにより、更に高精度に上記の課題を解決するものである。

#### [0054]

本発明の実施の形態3に係る動作フローチャートは、図5及び図6に示す実施の形態2に係る動作フローと基本的には同じであるので説明は省略する。

#### [0.055]

またバックアップ対象のメモリ基板を切り換えるバックアップ回路の構成は前述の実施 の形態 2 と同じである。

#### [0056]

また前述の実施の形態では、複合装置の場合で説明したが本発明はこれに限定されるものでなく、複数のメモリ基板が装着できる機器(PC等の装置)であっても良い。複合装置やPC等の装置を総称して、情報処理装置と呼ぶ。

## [0057]

(他の実施形態)

以上、本発明の実施形態について詳述したが、本発明は、複数の機器から構成されるシステムに適用しても良いし、また一つの機器からなる装置に適用しても良い。

#### [0058]

なお、本発明は、前述した実施形態の機能を実現するソフトウェアのプログラムを、システム或いは装置に直接或いは遠隔から供給し、そのシステム或いは装置のコンピュータが該供給されたプログラムを読み出して実行することによっても達成され得る。その場合、プログラムの機能を有していれば、形態は、プログラムである必要はない。

## [0059]

従って、本発明の機能処理をコンピュータで実現するために、該コンピュータにインストールされるプログラムコード自体も本発明を実現するものである。つまり、本発明のクレームでは、本発明の機能処理を実現するためのコンピュータプログラム自体も含まれる。その場合、プログラムの機能を有していれば、オブジェクトコード、インタプリタにより実行されるプログラム、OSに供給するスクリプトデータ等、プログラムの形態を問わない。

## [0060]

プログラムを供給するための記録媒体としては、様々なものが使用できる。例えば、フロッピー(登録商標)ディスク、ハードディスク、光ディスク、光磁気ディスク、MO、CD-ROM、CD-R、CD-RW、磁気テープ、不揮発性のメモリカード、ROM、DVD(DVD-ROM,DVD-R)などである。

## [0061]

その他、プログラムの供給方法としては、クライアントコンピュータのブラウザを用いてインターネットのホームページに接続し、該ホームページからハードディスク等の記録媒体にダウンロードすることによっても供給できる。その場合、ダウンロードされるのは、本発明のコンピュータプログラムそのもの、もしくは圧縮され自動インストール機能を含むファイルであってもよい。また、本発明のプログラムを構成するプログラムコードを複数のファイルに分割し、それぞれのファイルを異なるホームページからダウンロードすることによっても実現可能である。つまり、本発明の機能処理をコンピュータで実現するためのプログラムファイルを複数のユーザに対してダウンロードさせるWWWサーバも、本発明のクレームに含まれるものである。

## [0062]

また、本発明のプログラムを暗号化してCD-ROM等の記憶媒体に格納してユーザに 配布する形態としても良い。その場合、所定の条件をクリアしたユーザに対し、インター ネットを介してホームページから暗号化を解く鍵情報をダウンロードさせ、その鍵情報を使用することにより暗号化されたプログラムが実行可能な形式でコンピュータにインストールされるようにする。

[0063]

また、コンピュータが、読み出したプログラムを実行することによって、前述した実施 形態の機能が実現される形態以外の形態でも実現可能である。例えば、そのプログラムの 指示に基づき、コンピュータ上で稼動しているOSなどが、実際の処理の一部または全部 を行ない、その処理によっても前述した実施形態の機能が実現され得る。

[0064]

更に、記録媒体から読み出されたプログラムが、コンピュータに挿入された機能拡張ボードやコンピュータに接続された機能拡張ユニットに備わるメモリに書き込まれるようにしてもよい。この場合、その後で、そのプログラムの指示に基づき、その機能拡張ボードや機能拡張ユニットに備わるCPUなどが実際の処理の一部または全部を行ない、その処理によって前述した実施形態の機能が実現される。

【図面の簡単な説明】

[0065]

- 【図1】本発明の実施の形態に係る複合装置(多機能処理装置)の構成を示すブロック図である。

- 【図2】本実施の形態に係る複合装置のRAMの構成を説明する図である。

- 【図3】本実施の形態に係る複合装置の制御部からみたメモリマップを説明する図である

【図4】本実施の形態1に係る複合装置におけるRAMのバックアップ回路の一例を示す図である。

【図 5 】本発明の実施の形態 2 に係る複合装置における電源オン時の動作を示すフローチャートである。

【図 6 】本発明の実施の形態 2 に係る複合装置の電源オフ時の動作を示すフローチャートである。

【図7】実施の形態2に係るバックアップ回路を説明する回路図である。

10

【図1】

【図2】

【図3】

【図4】

## 【図5】

# 【図6】

## 【図7】