(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6026270号

(P6026270)

(45) 発行日 平成28年11月16日(2016.11.16)

(24) 登録日 平成28年10月21日(2016.10.21)

(51) Int.Cl.

G06F 1/26 (2006.01)

G11C 11/413 (2006.01)

F 1

G06F 1/26 335C

G06F 1/26 334D

G11C 11/34 335A

請求項の数 10 (全 21 頁)

(21) 出願番号 特願2012-286531 (P2012-286531)

(22) 出願日 平成24年12月28日 (2012.12.28)

(65) 公開番号 特開2014-130406 (P2014-130406A)

(43) 公開日 平成26年7月10日 (2014.7.10)

審査請求日 平成27年8月27日 (2015.8.27)

(73) 特許権者 302062931

ルネサスエレクトロニクス株式会社

東京都江東区豊洲三丁目2番24号

(74) 代理人 110001195

特許業務法人深見特許事務所

(72) 発明者 野谷 宏美

神奈川県川崎市中原区下沼部1753番地

ルネサスエレクトロニクス株式会社内

(72) 発明者 福岡 孝之

神奈川県川崎市中原区下沼部1753番地

ルネサスエレクトロニクス株式会社内

(72) 発明者 山木 貴志

神奈川県川崎市中原区下沼部1753番地

ルネサスエレクトロニクス株式会社内

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

動作モードとして、アクティブモードとスタンバイモードとを有する半導体装置であつて、

前記アクティブモード時、外部電源回路から第1の内部電源電圧の供給を受ける第1の電源線と、

外部電源電圧に基づいて第2の内部電源電圧を生成する内部電源回路と、

前記内部電源回路から前記第2の内部電源電圧の供給を受ける第2の電源線と、

前記第1の電源線および前記第2の電源線の間に接続されるスイッチ回路と、

前記スイッチ回路のオン／オフを制御する制御回路とを備え、

前記制御回路は、前記アクティブモード時、前記スイッチ回路をオンするための制御指令を出力する一方で、前記スタンバイモード時、前記スイッチ回路をオフするための制御指令を出力するように構成され、

前記スイッチ回路は、

ソースおよびN型ウェルが前記第1の電源線に接続される第1のPMOSトランジスタと、

ソースおよびN型ウェルが前記第2の電源線に接続され、ドレインが前記第1のPMOSトランジスタのドレインに接続される第2のPMOSトランジスタと、

前記制御指令および前記第2の電源線の電圧に基づいて、前記第1のPMOSトランジスタのゲートに入力する第1の制御信号を生成するための第1の制御信号生成部と、

10

20

前記制御指令および前記第1の電源線の電圧に基づいて、前記第2のPMOSトランジスタのゲートに入力する第2の制御信号を生成するための第2の制御信号生成部とを含む、半導体装置。

**【請求項2】**

前記第1の制御信号生成部は、前記第2の電源線が前記第2の内部電源電圧に立ち上がった状態で前記制御指令に対応付けて前記第1の制御信号を生成し、

前記第2の制御信号生成部は、前記第1の電源線が前記第1の内部電源電圧に立ち上がった状態で前記制御指令に対応付けて前記第2の制御信号を生成する、請求項1に記載の半導体装置。

**【請求項3】**

前記第1の制御信号生成部は、前記第2の電源線が前記第2の内部電源電圧に立ち上った状態で、前記オンするための制御指令に応じて前記第1のPMOSトランジスタをオンするように前記第1の制御信号を生成し、

前記第2の制御信号生成部は、前記第1の電源線が前記第1の内部電源電圧に立ち上った状態で、前記オンするための制御指令に応じて前記第2のPMOSトランジスタをオンするように前記第2の制御信号を生成する、請求項2に記載の半導体装置。

**【請求項4】**

前記スイッチ回路は、前記第1の電源線および前記第2の電源線の間に複数個並列に接続され、

前記制御回路は、前記アクティブモードから前記スタンバイモードへの移行時において、前記複数個のスイッチ回路を時間差を設けてオフする、請求項1に記載の半導体装置。

**【請求項5】**

前記内部電源回路は、前記アクティブモード時、前記第1の内部電源電圧よりも低電圧となるように前記第2の内部電源電圧を生成する、請求項1に記載の半導体装置。

**【請求項6】**

前記第1の電源線に接続され、前記アクティブモード時に前記第1の内部電源電圧によって動作し、前記スタンバイモード時に前記第1の内部電源電圧の供給が停止される第1の内部回路と、

前記第2の電源線に接続され、前記アクティブモード時に前記第1の内部電源電圧によって動作し、前記スタンバイモード時に前記第2の内部電源電圧によって動作する第2の内部回路とをさらに備える、請求項5に記載の半導体装置。

**【請求項7】**

前記内部電源回路は、

互いに電圧レベルの異なる複数の基準電圧を生成可能に構成され、前記動作モードに応じて前記複数の基準電圧のうちから選択された1つの基準電圧を出力する基準電圧発生部と、

前記選択された1つの基準電圧を参照して前記第2の内部電源電圧を生成するレギュレータとを含む、請求項5または6に記載の半導体装置。

**【請求項8】**

前記内部電源回路は、

基準電圧を生成する基準電圧発生回路と、

前記基準電圧を参照して前記第2の内部電源電圧を生成するレギュレータとを含み、

前記レギュレータは、互いに電圧レベルの異なる複数の前記第2の内部電源電圧を生成可能に構成され、前記動作モードに応じて前記複数の第2の内部電源電圧のうちから選択された1つの第2の内部電源電圧を出力する、請求項5または6に記載の半導体装置。

**【請求項9】**

動作モードとして、アクティブモードとスタンバイモードとを有する半導体装置であつて、

前記アクティブモード時に電源供給を受け、前記スタンバイモード時に電源供給を受けない第1の電源線と、

10

20

30

40

50

前記アクティブモード時および前記スタンバイモード時に、共に電源供給を受ける第2の電源線と、

前記第1の電源線から電源供給を受けて駆動される内部回路と、

前記第2の電源線から電源供給を受けてデータを保持するメモリ回路と、

前記アクティブモード時に前記第1の電源線と前記第2の電源線とを電気的に接続するスイッチ回路とを備え、

前記スイッチ回路は、前記第1の電源線と前記第2の電源線との間に直列に接続された第1および第2のPMOSトランジスタを含み、

前記第1のPMOSトランジスタは、ソースが前記第1の電源線に接続され、かつ、前記第1の電源線から電源供給を受ける第1のウェル領域に形成され、

前記第2のPMOSトランジスタは、ソースが前記第2の電源線に接続され、かつ、前記第2の電源線から電源供給を受ける、前記第1のウェル領域とは異なる第2のウェル領域に形成される、半導体装置。

#### 【請求項10】

前記半導体装置は、外部電源に基づいて前記第2の電源線に内部電圧を供給する内部電源回路をさらに備え、

前記第1および第2のPMOSトランジスタは、前記内部電源回路に含まれるトランジスタより膜厚の薄いトランジスタで構成される、請求項9に記載の半導体装置。

#### 【発明の詳細な説明】

##### 【技術分野】

20

##### 【0001】

この発明は、動作モードとしてアクティブモードおよびスタンバイモードを有する半導体装置の電源制御に関する。

##### 【背景技術】

##### 【0002】

マイクロコンピュータなどの半導体装置は、内部回路に供給する電源電圧（以下、内部電源電圧とも称する）を生成するための電源回路を備えている。このような半導体装置には、高速動作および低消費電力の実現のために、半導体装置の動作時（アクティブモード）と待機時（スタンバイモード）とで、動作させる電源回路を切替えるように構成したものが広く用いられている。

30

##### 【0003】

電源回路は、半導体装置のアクティブモードおよびスタンバイモードの両動作モードにおいて、安定した電源電圧を発生させる必要がある。このため、消費電力が大きく、電圧降下が起こりやすいアクティブモード時には、電力供給能力の高い電源回路が用いられる一方で、消費電力が小さいスタンバイモード時には、低消費電力化のため、消費電力を抑えた電源回路が用いられる。

##### 【先行技術文献】

##### 【特許文献】

##### 【0004】

##### 【特許文献1】特開2008-217509号公報

40

##### 【発明の概要】

##### 【発明が解決しようとする課題】

##### 【0005】

多電源のチップにおいて、オンチップレギュレータの出力と外部電源との間をスイッチ制御している場合、電源投入時、各回路が順方向にバイアスされるといった不具合が生じないよう、予め定められた電源立ち上げシーケンスに従って複数の電源電圧を順次立ち上げる必要がある。この立ち上げシーケンス制御は、ユーザへの制約となってしまう。その他の課題と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

##### 【課題を解決するための手段】

##### 【0006】

50

一実施の形態による半導体装置は、動作モードとして、アクティブモードとスタンバイモードとを有する。半導体装置は、アクティブモード時、外部電源回路から第1の内部電源電圧の供給を受ける第1の電源線と、外部電源電圧に基づいて第2の内部電源電圧を生成する内部電源回路と、内部電源回路から第2の内部電源電圧の供給を受ける第2の電源線と、第1の電源線および第2の電源線の間に接続されるPMOSスイッチと、PMOSスイッチのオン／オフを制御する制御回路とを備える。PMOSスイッチは、ソースおよびN型ウェルが第1の電源線に接続される第1のPMOSトランジスタと、ソースおよびN型ウェルが第2の電源線に接続され、ドレインが第1のPMOSトランジスタのドレインに接続される第2のPMOSトランジスタと、制御回路からの制御指令および第2の電源線の電圧に基づいて、第1のPMOSトランジスタのゲートに入力する第1の制御信号を生成するための第1の制御信号生成部と、制御指令および第1の電源線の電圧に基づいて、第2のPMOSトランジスタのゲートに入力する第2の制御信号を生成するための第2の制御信号生成部とを含む。

#### 【発明の効果】

#### 【0007】

上記の一実施の形態によれば、アクティブモードとスタンバイモードとで動作させる電源回路を切替えるように構成された半導体装置において、電源立ち上げシーケンスをフリーア化することができる。

#### 【図面の簡単な説明】

#### 【0008】

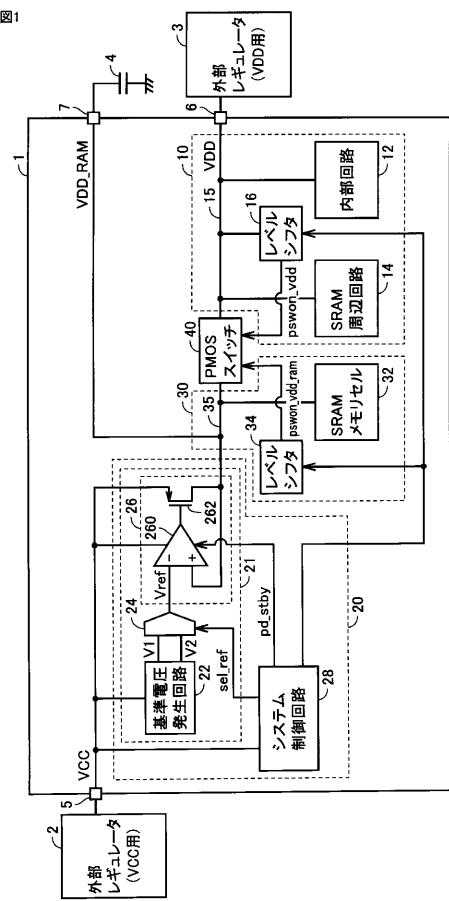

【図1】実施の形態1による半導体装置の構成を示す回路図である。

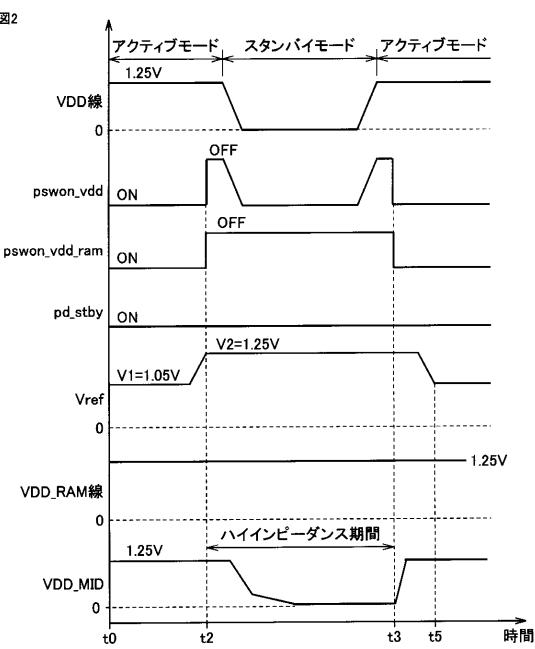

【図2】実施の形態1による半導体装置における内部電源電圧の切替え動作を説明するためのタイミングチャートである。

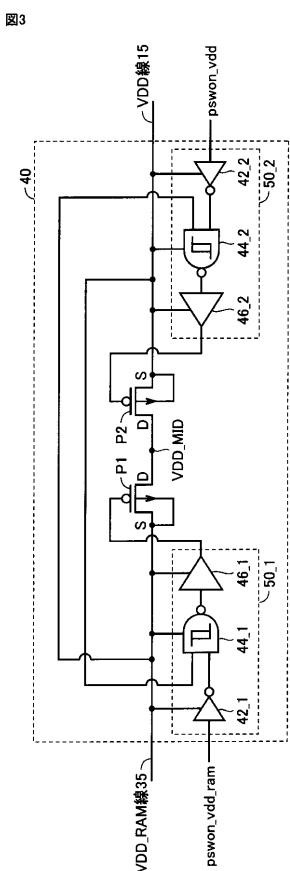

【図3】図1におけるPMOSスイッチの構成を示す回路図である。

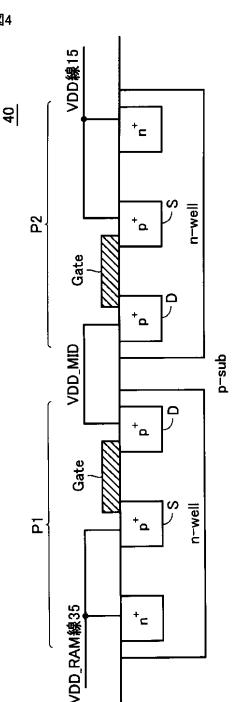

【図4】PMOSスイッチの構成を模式的に示す断面図である。

【図5】実施の形態2による半導体装置に適用される内部電源回路の構成を示す回路図である。

【図6】実施の形態3による半導体装置に適用されるPMOSスイッチの構成の一例を示す回路図である。

【図7】実施の形態1による半導体装置の動作を示すタイミングチャートである。

【図8】実施の形態3による半導体装置の動作を示すタイミングチャートである。

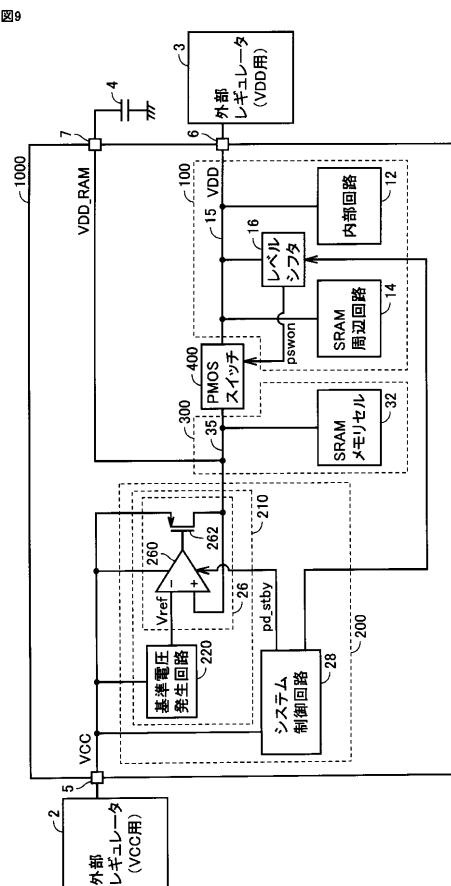

【図9】関連技術の半導体装置の全体構成を示す回路図である。

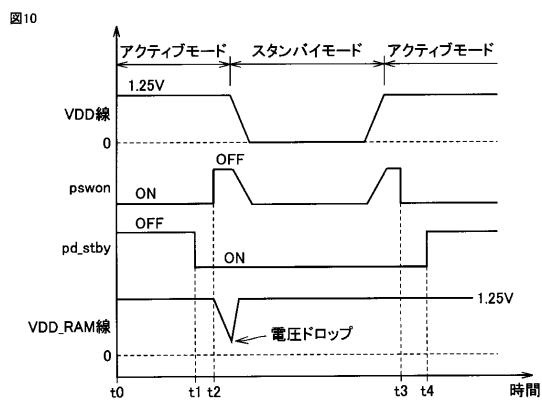

【図10】関連技術の半導体装置における外部レギュレータおよび内部レギュレータの切替え動作を説明するためのタイミングチャートである。

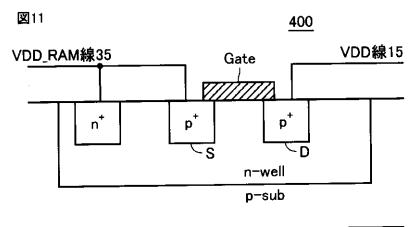

【図11】一般的なPMOSスイッチの構成を模式的に示す断面図である。

#### 【発明を実施するための形態】

#### 【0009】

以下、一実施の形態について図面を参照して詳しく説明する。なお、同一または相当する部分には同一の参照符号を付して、その説明を繰返さない。

#### 【0010】

<実施の形態1>

一実施の形態による半導体装置を説明するにあたり、最初に、関連技術の半導体装置における電源制御について説明する。次に、一実施の形態による半導体装置の主要部分について説明する。

#### 【0011】

[関連技術の半導体装置における電源制御]

図9は、関連技術の半導体装置の全体構成を示す回路図である。

#### 【0012】

図9を参照して、関連技術の半導体装置1000は、半導体装置1000の外部から供給される外部電源電圧VCCを受ける電源端子5と、外部電源電圧VCCを降圧して内部

10

20

30

40

50

電源電圧を生成する内部電源回路 210 と、電源線 15 とを備える。半導体装置 1000 は、内部回路 12 と、SRAM (Static Random Access Memory) メモリセル 32 と、SRAM 周辺回路 14 と、システム制御回路 28 とをさらに備える。

#### 【0013】

電源端子 5 は、半導体装置 1000 の外部に設けられたレギュレータ（以下、「外部レギュレータ」とも称する）2 によって生成された外部電源電圧 VCC を受ける。内部電源回路 210 は、外部電源電圧 VCC を降圧した内部電源電圧を生成し、生成した内部電源電圧を電源線 35 に供給する。電源線 35 には SRAM メモリセル 32 が接続される。SRAM メモリセル 32 は、電源線 35 から供給される内部電源電圧を受けて駆動する。以下の説明では、SRAM メモリセル 32 を駆動するための内部電源電圧を「内部電源電圧 VDD\_RAM」と表記する。また、内部電源電圧 VDD\_RAM を伝達する電源線 35 を「VDD\_RAM 線」と表記する。

10

#### 【0014】

内部電源回路 210 は、外部電源電圧 VCC によって動作する。内部電源回路 210 は、基準電圧発生回路 220 と、内部レギュレータ 26 とを含む。基準電圧発生回路 220 は、外部電源電圧 VCC を降圧した基準電圧 Vref を生成する。基準電圧 Vref は、例えば 1.25V 程度に設定される。内部レギュレータ 26 は、基準電圧 Vref を参照して内部電源電圧 VDD\_RAM を生成する。

#### 【0015】

具体的には、内部レギュレータ 26 は、誤差増幅器 260 と、PMOS (Positive-channel Metal Oxide Semiconductor) トランジスタ 262 を含む。誤差増幅器 260 は、反転入力端子（- 端子）に基準電圧 Vref を受け、非反転入力端子（+ 端子）に内部レギュレータ 26 の出力端子からのフィードバック電圧を受ける。誤差増幅器 260 は、基準電圧 Vref とフィードバック電圧との電圧差に応じて制御電圧を生成し、生成した制御電圧を PMOS トランジスタ 262 の制御端子（ゲート端子）に供給する。

20

#### 【0016】

誤差増幅器 260 から出力される制御電圧は、フィードバック電圧が基準電圧 Vref よりも大きくなるにつれて増大する。この結果、PMOS トランジスタ 262 を流れる電流が減少するので、フィードバック電圧の増大が抑制される。逆に、制御電圧は、フィードバック電圧が基準電圧 Vref よりも小さくなるにつれて減少する。この結果、PMOS トランジスタ 262 を流れる電流が増大するので、フィードバック電圧の減少が抑制される。このようにして、フィードバック電圧は、基準電圧 Vref (1.25V) に等しくなる。

30

#### 【0017】

内部レギュレータ 26 の出力端子は VDD\_RAM 線 35 に接続される。これにより、VDD\_RAM 線 35 には、基準電圧 Vref に等しい出力電圧が内部電源電圧 VDD\_RAM として供給される。

#### 【0018】

なお、誤差増幅器 260 は、システム制御回路 28 から与えられる制御信号 pd\_stby に応じて活性状態（オン状態）または非活性状態（オフ状態）に制御される。具体的には、誤差増幅器 260 は、L (論理ロー) レベルに活性化された制御信号 pd\_stby を受けてオン状態となり、H (論理ハイ) レベルに非活性化された制御信号 pd\_stby を受けてオフ状態となる。

40

#### 【0019】

また、VDD\_RAM 線 35 には、内部電源電圧 VDD\_RAM を安定化するために、電源端子 7 を介して外部容量 4 が取り付けられている。

#### 【0020】

半導体装置 1000 は、半導体装置 1000 の外部から直接的に内部電源電圧の供給を受けるための構成として、電源端子 6 と、電源線 15 と、PMOS スイッチ 400 と、レベルシフタ 16 とをさらに備える。

50

## 【0021】

電源端子 6 は、外部レギュレータ 3 によって生成された内部電源電圧を受ける。電源線 15 には内部回路 12、S R A M 周辺回路 14 およびレベルシフタ 16 が接続される。半導体装置 1000 が例えばマイクロコンピュータの場合、内部回路 12 は、C P U (Central Processing Unit)、フラッシュメモリ等の書換え可能な不揮発性メモリ、論理回路および周辺回路などを含む。S R A M 周辺回路 14 は、センスアンプなど S R A M メモリセル 32 の書き込み・読み出し動作に必要な周辺回路および制御回路などを含む。内部回路 12 および S R A M 周辺回路 14 は、電源線 15 から供給される内部電源電圧を受けて駆動する。以下の説明では、内部回路 12 および S R A M 周辺回路 14 を駆動するための内部電源電圧を「内部電源電圧 V D D」と表記する。また、内部電源電圧 V D D を伝達する電源線 15 を「V D D 線」と表記する。内部電源電圧 V D D は、内部電源電圧 V D D \_ R A M と同じ電圧レベルであり、例えば 1.25 V 程度に設定される。10

## 【0022】

P M O S スイッチ 400 は、V D D 線 15 および V D D \_ R A M 線 35 の間に接続される。P M O S スイッチ 400 のオン（導通）／オフ（非導通）は、システム制御回路 28 によって生成され、かつ、レベルシフタ 16 によってレベル変換された制御信号 p s w o n によって制御される。具体的には、制御信号 p s w o n が L レベルに活性化されたとき、P M O S スイッチ 400 がオンされる。これにより、V D D 線 15 および V D D \_ R A M 線 35 が電気的に接続される。一方、制御信号 p s w o n が H レベルに非活性化されたとき、P M O S スイッチ 400 がオフされる。これにより、V D D 線 15 および V D D \_ R A M 線 35 が電気的に遮断される。20

## 【0023】

半導体装置 1000 は、図 9 に示すように、内部電源電圧 V D D によって動作する回路が配置された領域（以下、「V D D 電源領域」とも称する）100 と、外部電源電圧 V C C によって動作する回路が配置された領域（以下、「V C C 電源領域」とも称する）200 と、内部電源電圧 V D D \_ R A M によって動作する回路が配置された領域（以下、「V D D \_ R A M 電源領域」とも称する）300 とに分けられる。V D D 電源領域 100 には、内部回路 12 と、S R A M 周辺回路 14 と、レベルシフタ 16 とが含まれる。V C C 電源領域 200 には、内部電源回路 210 およびシステム制御回路 28 が含まれる。V D D \_ R A M 電源領域 300 には、S R A M メモリセル 32 が含まれる。30

## 【0024】

以上に示す半導体装置 1000 は、動作モードとして、半導体装置の動作時に対応するアクティブモードと、半導体装置の待機時（非動作時とも称する）に対応するスタンバイモードとを有する。システム制御回路 28 は、このアクティブモード時とスタンバイモード時とで内部電源電圧の供給源を切替える。

## 【0025】

具体的には、種々の回路動作が行なわれるため、消費電力が大きく、電圧降下が起こりやすいアクティブモード時には、電流供給能力の高い外部レギュレータ 3 を用いて内部電源電圧 V D D を発生させる。V D D 電源領域 100 において、内部回路 12 および S R A M 周辺回路 14 は、V D D 線 15 から内部電源電圧 V D D の供給を受けて駆動する。40

## 【0026】

このとき、システム制御回路 28 は、L レベルに活性化された制御信号 p s w o n をレベルシフタ 16 へ出力する。P M O S スイッチ 400 がレベル変換された制御信号 p s w o n を受けてオンされることにより、V D D 線 15 および V D D \_ R A M 線 35 が接続される。システム制御回路 28 はさらに、H レベルに非活性化された制御信号 p d \_ s t b y を生成して内部レギュレータ 26 へ出力する。誤差増幅器 260 が H レベルの制御信号 p d \_ s t b y を受けてオフ状態となるため、内部レギュレータ 26 は内部電源電圧 V D D \_ R A M を発生しない。したがって、V D D \_ R A M 線 35 は、V D D 線 15 から P M O S スイッチ 400 を介して内部電源電圧 V D D の供給を受ける。このようにして、アクティブモード時には、S R A M メモリセル 32 は、内部回路 12 および S R A M 周辺回路50

14と同様に、外部レギュレータ3から供給される内部電源電圧VDDによって駆動する。

#### 【0027】

これに対して、種々の回路動作が行なわれない待機状態のため、消費電力が小さいスタンバイモード時には、低消費電力化対策として、消費電力を抑えた内部レギュレータ26を用いて内部電源電圧VDD\_RAMを発生させる。詳細には、スタンバイモード時は、内部回路12およびSRAM周辺回路14への内部電源電圧VDDの供給が不要となる一方で、SRAMメモリセル32に対しては、データ保持のために内部電源電圧VDD\_RAMを供給する必要がある。一方で、外部レギュレータ3を用いて内部電源電圧VDD\_RAMを発生させると消費電力が大きくなる。そのため、外部レギュレータ3をオフ状態とし、内部レギュレータ26をオン状態として内部電源電圧VDD\_RAMを発生させる。

#### 【0028】

このとき、システム制御回路28は、Hレベルに非活性化された制御信号p\_swonをレベルシフタ16へ出力する。PMOSスイッチ400がレベル変換された制御信号p\_swonを受けてオフされることにより、VDD線15およびVDD\_RAM線35が電気的に遮断される。システム制御回路28はさらに、Lレベルに活性化された制御信号p\_d\_stbyを内部レギュレータ26へ出力する。誤差増幅器260がLレベルの制御信号p\_d\_stbyを受けてオン状態となると、内部レギュレータ26は内部電源電圧VDD\_RAMを発生する。この結果、VDD\_RAM線35は、内部レギュレータ26から内部電源電圧VDD\_RAMの供給を受ける。このようにして、スタンバイモード時、SRAMメモリセル32は、内部レギュレータ26から供給される内部電源電圧VDD\_RAMによって駆動する。

#### 【0029】

##### (1) VDD\_RAM線の電圧ドロップの発生

以上に説明したように、関連技術の半導体装置1000では、アクティブモード時とスタンバイモード時とで、電流供給能力の異なる2つのレギュレータ（外部レギュレータ3および内部レギュレータ26）を切替えて用いることにより、低消費電力化を実現する。

#### 【0030】

しかしながら、一般に内部レギュレータ26はできるだけ消費電力を抑えたいため、外部レギュレータ3に比べて出力電圧の反応が鈍い。このため、半導体装置1000がアクティブモードからスタンバイモードに移行する際に、内部レギュレータ26をオン状態にしてからVDD\_RAM線35に電圧が供給されるまでに時間差が生じてしまう。その結果、スタンバイモードへの移行直後において、VDD\_RAM線35の電圧が一時的に低下する、いわゆる電圧ドロップが発生するという問題がある。

#### 【0031】

図10は、関連技術の半導体装置1000における外部レギュレータ3および内部レギュレータ26の切替え動作を説明するためのタイミングチャートである。

#### 【0032】

図10を参照して、半導体装置1000がアクティブモードのときには（時刻t0）、VDD線15に外部レギュレータ3から内部電源電圧VDD（1.25V）が供給される。PMOSスイッチ400は、Lレベルに活性化された制御信号p\_swonによってオンされる。一方、内部レギュレータ26は、Hレベルに非活性化された制御信号p\_d\_stbyによってオフ状態となる。VDD線15およびVDD\_RAM線35がPMOSスイッチ400によって接続されることにより、VDD\_RAM線35には内部電源電圧VDDが供給される。

#### 【0033】

アクティブモードからスタンバイモードへ移行するときには、制御信号p\_d\_stbyをLレベルに活性化させて内部レギュレータ26をオン状態とする（時刻t1）。続いて、制御信号p\_swonをHレベルに非活性化させてPMOSスイッチ400をオフする（

時刻  $t_2$ ）。なお、スタンバイモードでは外部レギュレータ3がオフ状態となるため、VDD線15は、内部電源電圧VDD(1.25V)から接地電圧(0V)に向かって低下する。

#### 【0034】

ここで、内部レギュレータ26からVDD\_RAM線35に内部電源電圧VDD\_RAMが供給されるタイミングが、PMOSスイッチ400がオフされるタイミング(時刻  $t_2$ )よりも遅れると、VDD\_RAM線35では電源供給が一時的に途絶える。このため、VDD\_RAM線35に、図10に示すように電圧ドロップが発生する。

#### 【0035】

なお、スタンバイモードからアクティブモードへ復帰するときには、制御信号p\_swonをLレベルに活性化させてPMOSスイッチ400をオンするとともに(時刻  $t_3$ )、制御信号p\_d\_stbyをHレベルに非活性化させて内部レギュレータ26をオフ状態とする。アクティブモードでは外部レギュレータ3がオン状態となるため、VDD線15は、接地電圧(0V)から再び内部電源電圧VDD(1.25V)に上昇する。外部レギュレータ3は応答性が良いため、VDD\_RAM線35に電圧ドロップは生じない。

#### 【0036】

上記のように、スタンバイモードへの移行直後のVDD\_RAM線35の電圧ドロップは内部レギュレータ26の応答性に起因したものであるため、内部レギュレータ26を常時オン状態にしておくことで電圧ドロップを抑えることも考えられる。しかしながら、図9に示す構成のままでアクティブモード時に内部レギュレータ26をオン状態にしておくと、内部レギュレータ26から供給される内部電源電圧VDD\_RAMと、外部レギュレータ3から供給される内部電源電圧VDDとの間に電圧差が生じたときに、内部レギュレータ26に無駄に電力を消費させる可能性が生じてしまう。

#### 【0037】

例えば、内部電源電圧VDDが1.15Vであって、内部電源電圧VDD\_RAMが1.35Vである場合、内部レギュレータ26から外部レギュレータ3に向かって、内部レギュレータ26が供給できる限界まで電流が流れ続ける。これは無駄な電力を消費されるとともに、VDD線15およびVDD\_RAM線35にエレクトロマイグレーションが発生しやすくなり、半導体装置の信頼性にも影響を及ぼす。このため、内部レギュレータ26を常時オン状態にしておくことは現実的でない。

#### 【0038】

##### (2) 電源立ち上げシーケンスの制約

図9に示すように、VDD線15およびVDD\_RAM線35は、PMOSスイッチ400を介して接続されている。図11は、一般的なPMOSスイッチの構成を模式的に示す断面図である。

#### 【0039】

図11を参照して、PMOSスイッチ400は、PMOSトランジスタにより構成される。PMOSトランジスタは、P型半導体基板p-subに設けられたN型ウェルn-wellに形成される。PMOSトランジスタにおいて、ドレインDはVDD線15に接続され、ソースSはVDD\_RAM線35に接続される。N型ウェルn-wellはVDD\_RAM線35に接続される。VDD\_RAM線35にはアクティブモード時およびスタンバイモード時の双方で電源が供給されるのに対して、VDD線15はスタンバイモード時に電源の供給が停止されるためである。

#### 【0040】

半導体装置1000に電源が投入されると、外部レギュレータ3および内部電源回路210がそれぞれ起動されることによって、内部電源電圧VDDおよびVDD\_RAMがそれぞれ立ち上がる。PMOSトランジスタは、ドレインDに内部電源電圧VDDを受け、ソースSおよびN型ウェルn-wellに内部電源電圧VDD\_RAMを受ける。

#### 【0041】

例えば、内部電源電圧VDD\_RAMの立ち上がりが内部電源電圧VDDの立ち上がり

10

20

30

40

50

よりも遅い場合を想定する。この場合、ドレインDの電圧に対してN型ウェルn-wellの電圧が低くなるため、ドレインDおよびN型ウェルn-well間のPN接合が順方向にバイアスされる。このため、PN接合に電流が流れる可能性がある。

#### 【0042】

一方、内部電源電圧VDDの立ち上がりが内部電源電圧VDD\_RAMの立ち上がりよりも遅い場合には、ドレインDの電圧に対してN型ウェルn-wellの電圧が高くなるため、ドレインDおよびN型ウェルn-well間のPN接合が順方向にバイアスされず、PN接合に電流が流れない。

#### 【0043】

したがって、半導体装置1000の電源投入時には、内部電源電圧VDD\_RAMを内部電源電圧VDDよりも先に立ち上げなければならないという制約が生じる。10

#### 【0044】

以上のように、関連技術の半導体装置1000における電源制御には、スタンバイモードへの移行直後のVDD\_RAM線35の電圧ドロップ、および、電源立ち上げシーケンスの制約という課題があった。実施の形態1では、以下のように、内部レギュレータ26を常時オン状態にすることを可能とすることにより、スタンバイモードへの移行直後の電圧ドロップを抑制する。また、PMOSスイッチ400を、電源投入時にPN接合が順方向にバイアスされるのを防止可能な構造とすることにより、電源立ち上げシーケンスのフリーアクションを実現する。

#### 【0045】

##### [実施の形態1による半導体装置における電源制御]

以下、実施の形態1による半導体装置における電源制御について説明する。20

#### 【0046】

図1は、実施の形態1による半導体装置の構成を示す回路図である。

図1を参照して、実施の形態1による半導体装置1は、図9に示す関連技術の半導体装置1000において、内部電源回路210に代えて、内部電源回路21を設けたものである。また、PMOSスイッチ400に代えて、PMOSスイッチ40およびレベルシフタ34を設けたものである。半導体装置1の全体構成は、内部電源回路21、PMOSスイッチ40およびレベルシフタ34を除いて、図9と同様であるので、詳細な説明は繰り返さない。30

#### 【0047】

##### (内部電源回路21の構成)

内部電源回路21は、外部電源電圧VCCによって動作する。内部電源回路21は、基準電圧発生回路22と、セレクタ24と、内部レギュレータ26とを含む。

#### 【0048】

基準電圧発生回路22は、外部電源電圧VCCを降圧した基準電圧Vrefを生成する。基準電圧発生回路22は、互いに電圧レベルの異なる2つの基準電圧V1, V2を生成可能に構成される。基準電圧V1は例えば1.05V程度に設定され、基準電圧V2は例えば1.25V程度に設定される。

#### 【0049】

セレクタ24は、システム制御回路28から与えられる制御信号sel\_refに従って、基準電圧発生回路22が出力する電圧V1, V2のいずれか一方を選択する。セレクタ24は、その選択した電圧を基準電圧Vrefとして内部レギュレータ26へ出力する。

#### 【0050】

内部レギュレータ26は、セレクタ24から入力される基準電圧Vrefを参照して、内部電源電圧VDD\_RAMを生成する。具体的には、内部レギュレータ26は、誤差増幅器260およびPMOSトランジスタ262を含み、誤差増幅器260の反転入力端子に基準電圧Vrefを受ける。また、誤差増幅器260の非反転入力端子に内部レギュレータ26の出力端子からのフィードバック電圧を受ける。4050

## 【0051】

誤差増幅器 260 は、図 9 で説明したように、基準電圧  $V_{ref}$  とフィードバック電圧との電圧差に応じて制御電圧を生成し、生成した制御電圧を PMOS トランジスタ 262 の制御端子（ゲート端子）に供給する。これにより、 $VDD\_RAM$  線 35 には、基準電圧  $V_{ref}$  に等しい出力電圧が内部電源電圧  $VDD\_RAM$  として供給される。上述のように、制御信号  $sel\_ref$  に従って基準電圧  $V_{ref}$  を 2 値  $V1 (1.05V)$ ,  $V2 (1.25V)$  の間で切替えることにより、内部電源電圧  $VDD\_RAM$  はこの 2 値  $V1$ ,  $V2$  の間で切替えられる。

## 【0052】

誤差増幅器 260 は、システム制御回路 28 から与えられる制御信号  $pd\_stby$  に応じてオン状態またはオフ状態に制御される。具体的には、誤差増幅器 260 は、L レベルに活性化された制御信号  $pd\_stby$  を受けてオン状態となり、H レベルに非活性化された制御信号  $pd\_stby$  を受けてオフ状態となる。

10

## 【0053】

PMOS スイッチ 40 は、 $VDD$  線 15 および  $VDD\_RAM$  線 35 の間に接続される。PMOS スイッチ 40 は、システム制御回路 28 によって生成され、かつ、レベルシフタ 16 によってレベル変換された制御信号  $pswon\_vdd$  を受ける。PMOS スイッチ 40 はさらに、システム制御回路 28 によって生成され、かつ、レベルシフタ 34 によってレベル変換された制御信号  $pswon\_vdd\_ram$  を受ける。PMOS スイッチ 40 は、後述するように、これら 2 つの制御信号に応答してオン / オフが制御される。

20

## 【0054】

具体的には、制御信号  $pswon\_vdd$ ,  $pswon\_vdd\_ram$  がともに L レベルに活性化されたとき、PMOS スイッチ 40 がオンされる。これにより、 $VDD$  線 15 および  $VDD\_RAM$  線 35 が電気的に接続される。一方、制御信号  $pswon\_vdd$ ,  $pswon\_vdd\_ram$  の少なくとも一方が H レベルに非活性化されたとき、PMOS スイッチ 40 がオフされる。これにより、 $VDD$  線 15 および  $VDD\_RAM$  線 35 が電気的に遮断される。

## 【0055】

半導体装置 1 は、図 1 に示すように、 $VDD$  電源領域 10 と、 $VCC$  電源領域 20 と、 $VDD\_RAM$  電源領域 30 とに分けられる。 $VDD$  電源領域 10 には、内部回路 12 と、 $SRAM$  周辺回路 14 と、レベルシフタ 16 とが含まれる。 $VCC$  電源領域 20 には、内部電源回路 21 およびシステム制御回路 28 が含まれる。 $VDD\_RAM$  電源領域 30 には、 $SRAM$  メモリセル 32 およびレベルシフタ 34 が含まれる。

30

## 【0056】

ここで、 $VCC$  電源領域 20 に含まれる回路では、主として膜厚の厚い高耐圧用トランジスタが使用される。一方、 $VDD$  電源領域 10 および  $VDD\_RAM$  電源領域 30 に含まれる回路では、主として高耐圧用トランジスタよりも膜厚の薄い低耐圧用トランジスタが使用される。

## 【0057】

実施の形態 1 による半導体装置 1 は、関連技術の半導体装置 1000 (図 9) と同様に、動作モードとして、アクティブモードとスタンバイモードとを有する。システム制御回路 28 は、アクティブモード時とスタンバイモード時とで内部電源電圧の供給源を切替える。

40

## 【0058】

ここで、上述のように、関連技術に示した構成において、アクティブモード時とスタンバイモード時とで、電流供給能力の異なる 2 つのレギュレータ (外部レギュレータ 3 および内部レギュレータ 26) を切替えて用いると、内部レギュレータ 26 の応答性に起因して、スタンバイモードへの移行直後に  $VDD\_RAM$  線 35 に電圧ドロップが生じてしまう (図 10 参照)。

## 【0059】

50

そのため、実施の形態1による半導体装置1では、内部電源回路21が生成する内部電源電圧VDD\_RAMの電圧レベルを、半導体装置1の動作モードに応じて切替える。これにより、内部電源電圧VDDおよびVDD\_RAMの電圧差による無駄な電力消費を抑制し、内部電源回路21を常時オン状態とすることを可能とする。

#### 【0060】

図2は、実施の形態1による半導体装置1における内部電源電圧VDD\_RAMの切替え動作を説明するためのタイミングチャートである。

#### 【0061】

図2を参照して、半導体装置1がアクティブモードのとき(時刻t0)、VDD線15には外部レギュレータ3から内部電源電圧VDD(1.25V)が供給される。PMOSスイッチ40は、Lレベルに活性化された制御信号p\_swon\_vdd, p\_swon\_vdd\_ramによってオンされる。VDD\_RAM線35は、PMOSスイッチ40によってVDD線15に電気的に接続されるため、VDD線15から内部電源電圧VDDが供給される。

10

#### 【0062】

このとき、内部電源回路21においては、Lレベルに活性化された制御信号p\_d\_stbyによって内部レギュレータ26がオン状態となる。これにより、VDD\_RAM線35には、内部レギュレータ26から内部電源電圧VDD\_RAMが供給される。

#### 【0063】

上述のように、内部電源電圧VDD\_RAMが内部電源電圧VDDより高い場合、内部レギュレータ26から外部レギュレータ3に向かって、内部レギュレータ26が供給できる限界まで電流が流れ続けてしまう。

20

#### 【0064】

そこで、実施の形態1では、アクティブモード時に内部レギュレータ26に与える基準電圧Vrefを、内部電源電圧VDD(1.25V)よりも低い電圧V1(1.05V)とする。具体的には、セレクタ24は、システム制御回路28からの制御信号sel\_refに従って電圧V1を選択して内部レギュレータ26に出力する。内部レギュレータ26が電圧V1を基準電圧Vrefとして動作することにより、VDD\_RAM線35には、電圧V1に等しい内部電源電圧VDD\_RAMが供給される。なお、電圧V1は、内部電源電圧VDDのばらつきを考慮して、内部電源電圧VDDの下限値よりも低くなるように設定される。

30

#### 【0065】

このように、アクティブモード時に内部レギュレータ26が発生する内部電源電圧VDD\_RAM(1.05V)を内部電源電圧VDD(1.25V)より低くしたことにより、内部レギュレータ26から外部レギュレータ3に向かって電流が流れるのを防止できる。これにより、内部レギュレータ26の無駄な電力消費が抑制されるため、内部レギュレータ26を常時オン状態にすることが可能となる。

#### 【0066】

アクティブモードからスタンバイモードへの移行するときには、セレクタ24は、システム制御回路28からの制御信号sel\_refに従って電圧V2(1.25V)を選択して内部レギュレータ26に出力する。内部レギュレータ26が電圧V2を基準電圧Vrefとして動作することにより、VDD\_RAM線35には、電圧V2に等しい内部電源電圧VDD\_RAMが供給される。

40

#### 【0067】

なお、上述の説明では、電圧V2を内部電源電圧VDD(1.25V)と同じ電圧レベルとする構成について例示したが、電圧V2はSRAMメモリセル32のデータ保持可能な電圧レベル(例えば1.1V程度)であればよい。

#### 【0068】

システム制御回路28は、制御信号p\_swon\_vdd, p\_swon\_vdd\_ramをともにHレベルに非活性化させてPMOSスイッチ40をオフする(時刻t2)。スタ

50

ンバイモードでは外部レギュレータ3がオフ状態となるため、VDD線15は、内部電源電圧VDD(1.25V)から接地電圧(0V)に向かって低下する。一方、VDD\_RAM線35は、内部レギュレータ26が既にオン状態となっているため、電圧ドロップの発生が抑制される。

#### 【0069】

(PMOSスイッチ40の構成)

図3は、図1におけるPMOSスイッチ40の構成を示す回路図である。

#### 【0070】

図3を参照して、PMOSスイッチ40は、直列に接続された2個のPMOSトランジスタP1, P2と、2個の制御信号生成部50\_1, 50\_2とを含む。

10

#### 【0071】

PMOSトランジスタP1, P2は、VDD\_RAM線35およびVDD線15の間に直列に接続される。PMOSトランジスタP1は、ソースSがVDD\_RAM線35に接続され、ドレインDがPMOSトランジスタP2のドレインに接続される。PMOSトランジスタP2は、ソースSがVDD線15に接続される。以下の説明では、PMOSトランジスタP1およびP2の接続ノードを「中間ノードVDD\_MID」と表記する。

#### 【0072】

制御信号生成部50\_1は、PMOSトランジスタP1のオン／オフを制御するための制御信号を生成する。制御信号生成部50\_1は、インバータ42\_1と、NANDゲート44\_1と、バッファ46\_1とを含む。インバータ42\_1、NANDゲート44\_1およびバッファ46\_1は、内部電源電圧VDD\_RAMによって動作する。また、バッファ46\_1は、インバータ2段で構成されることが多い。

20

#### 【0073】

インバータ42\_1は、システム制御回路28(図1)から与えられる制御信号p\_sw\_on\_vdd\_ramの反転信号をNANDゲート44\_1の一方入力ノードに出力する。NANDゲート44\_1の他方入力ノードはVDD線15に接続される。NANDゲート44\_1は、制御信号p\_sw\_on\_vdd\_ramの反転信号と、VDD線15に供給される内部電源電圧VDDとの論理積を反転させた信号をバッファ46\_1に出力する。バッファ46\_1は、NANDゲート44\_1の出力信号に応じた制御信号をPMOSトランジスタP1の制御端子(ゲート端子)に出力する。

30

#### 【0074】

制御信号生成部50\_2はPMOSトランジスタP2のオン／オフを制御するための制御信号を生成する。制御信号生成部50\_2は、インバータ42\_2と、NANDゲート44\_2と、バッファ46\_2とを含む。インバータ42\_2、NANDゲート44\_2およびバッファ46\_2は、内部電源電圧VDDによって動作する。また、バッファ46\_2は、インバータ2段で構成されることが多い。

#### 【0075】

インバータ42\_2は、システム制御回路28(図1)から与えられる制御信号p\_sw\_on\_vddの反転信号をNANDゲート44\_2の一方入力ノードに出力する。NANDゲート44\_2の他方入力ノードはVDD\_RAM線35に接続される。NANDゲート44\_2は、制御信号p\_sw\_on\_vddの反転信号と、VDD\_RAM線35に供給される内部電源電圧VDD\_RAMとの論理積を反転させた信号をバッファ46\_2に出力する。バッファ46\_2は、NANDゲート44\_2の出力信号に応じた制御信号をPMOSトランジスタP2の制御端子(ゲート端子)に出力する。

40

#### 【0076】

ここで、PMOSトランジスタP1およびその制御信号生成部50\_1に着目する。

制御信号生成部50\_1に入力される制御信号p\_sw\_on\_vdd\_ramは、PMOSトランジスタP1をオンさせるときにLレベルに活性化される一方で、PMOSトランジスタP1をオフさせるときにHレベルに非活性化される。NANDゲート44\_1は、制御信号p\_sw\_on\_vdd\_ramの反転信号と、内部電源電圧VDDとの論理積を反

50

転させた信号を出力する。

#### 【0077】

具体的には、内部電源電圧VDDがHレベル（例えば1.25V）のとき、NANDゲート44\_1はインバータとして機能し、制御信号p\_swon\_vdd\_ramの反転信号の論理を反転させて出力する。したがって、制御信号p\_swon\_vdd\_ramがLレベルのときにPMOSトランジスタP1がオンされ、制御信号p\_swon\_vdd\_ramがHレベルのときにPMOSトランジスタP1がオフされる。

#### 【0078】

一方、内部電源電圧VDDがLレベル(0V)のときには、制御信号p\_swon\_vdd\_ramの論理に拘わらず、NANDゲート44\_1はHレベルの信号を出力する。したがって、PMOSトランジスタP1は、制御信号p\_swon\_vdd\_ramの論理によらず、オフされる。

10

#### 【0079】

このように、PMOSトランジスタP1は、内部電源電圧VDDがHレベルに立ち上ることではじめてオン／オフの制御が可能となる。同様にして、PMOSトランジスタP2およびその制御信号生成部50\_2においても、PMOSトランジスタP2は、内部電源電圧VDD\_RAMがHレベルに立ち上ることではじめてオン／オフの制御が可能となる。すなわち、PMOSスイッチ40は、内部電源電圧VDD, VDD\_RAMがともにHレベル立ち上った状態で、制御信号p\_swon\_vdd, p\_swon\_vdd\_ramに応じてオン／オフが制御される。

20

#### 【0080】

このような構成としたことにより、実施の形態1による半導体装置1では、内部電源電圧VDD\_RAMの立ち上がりと内部電源電圧VDDの立ち上がりとの間に時間差が生じた場合であっても、各PMOSトランジスタのドレインDおよびN型ウェルn-well間のPN接合に電流が流れることがない。これにより、電源立ち上げシーケンスのフリー化が可能となる。以下、その理由について説明する。

#### 【0081】

図4は、PMOSスイッチ40の構成を模式的に示す断面図である。

図4を参照して、PMOSトランジスタP1, P2は、P型半導体基板p-subに設けられたN型ウェルn-wellに形成される。PMOSトランジスタP1は、ソースSがVDD\_RAM線35に接続され、ドレインDが中間ノードVDD\_MIDにおいてPMOSトランジスタP2のドレインDに接続される。PMOSトランジスタP1が形成されるN型ウェルn-wellはVDD\_RAM線35に接続される。

30

#### 【0082】

PMOSトランジスタP2は、ソースSがVDD線15に接続され、ドレインDが中間ノードVDD\_MIDにおいてPMOSトランジスタP1のドレインDに接続される。PMOSトランジスタP2が形成されるN型ウェルn-wellはVDD線15に接続される。

#### 【0083】

半導体装置1に電源が投入されると、外部レギュレータ3および内部電源回路21がそれぞれ起動されることによって、内部電源電圧VDDおよびVDD\_RAMがそれぞれ立ち上がる。PMOSトランジスタP1は、ソースSおよびN型ウェルn-wellに内部電源電圧VDD\_RAMを受ける。PMOSトランジスタP2は、ソースSおよびN型ウェルn-wellに内部電源電圧VDDを受ける。

40

#### 【0084】

ここで、内部電源電圧VDD\_RAMの立ち上がりが内部電源電圧VDDの立ち上がりよりも遅い場合を想定する。この場合、PMOSトランジスタP2では、上述のように、内部電源電圧VDDがHレベルとなっていても、内部電源電圧VDD\_RAMがHレベルに立ち上るまではPMOSトランジスタP2がオンされない。このため、PMOSトランジスタP2のドレインDおよび中間ノードVDD\_MIDは、ハイインピーダンス状態と

50

なる。

**【0085】**

一方、PMOSトランジスタP1では、内部電源電圧VDDがHレベルとなっていても、内部電源電圧VDD\_RAMがHレベルに立ち上がるまでは制御信号生成部50\_1がオン状態にならないため、PMOSトランジスタP1がオンされない。このような状態であっても、中間ノードVDD\_MIDに接続されるPMOSトランジスタP1のドレインDはハイインピーダンス状態となっているため、ドレインDおよび対応のN型ウェルn\_well間のPN接合が順方向にバイアスされることがない。よって、PN接合に電流が流れることがない。

**【0086】**

なお、内部電源電圧VDDの立ち上がりが内部電源電圧VDD\_RAMの立ち上がりよりも遅い場合においても同様のことがいえる。この場合は、PMOSトランジスタP2において、ドレインDおよび対応のN型ウェルn-well間のPN接合が順方向にバイアスされないため、PN接合に電流が流れることがない。

**【0087】**

このように、内部電源電圧VDDおよびVDD\_RAMのいずれが先にHレベルに立ち上がってもPMOSトランジスタP1, P2のPN接合が順方向にバイアスされることがない。したがって、電源立ち上げシーケンスに対する制約が不要となるため、電源立ち上げシーケンスのフリー化を実現することができる。

**【0088】**

なお、実施の形態1による半導体装置1では、内部電源回路21が生成する内部電源電圧VDD\_RAMの電圧レベルを、半導体装置1の動作モードに応じて切替える構成とした。しかしながら、関連技術に示したように、アクティブモード時とスタンバイモード時とで、電流供給能力の異なる2つのレギュレータ（外部レギュレータ3および内部レギュレータ26）を切替えて用いる構成に対しても、図4に示すPMOSスイッチ40の構成を適用することが可能である。そして、そのような構成においても、電源立ち上げシーケンスに対する制約を不要とすることができる。

**【0089】**

さらに、実施の形態1による半導体装置1では、VDD\_RAM線35およびVDD線15の間のスイッチトランジスタを、高耐圧用トランジスタではなく、低耐圧用トランジスタであるPMOSトランジスタP1, P2で構成することができる。これにより、スイッチトランジスタを高耐圧用トランジスタで構成する場合に比べて面積（トランジスタサイズL/W）の削減が図られる。

**【0090】**

<実施の形態2>

上述の実施の形態1による半導体装置1では、内部電源回路21が生成する内部電源電圧VDD\_RAMを動作モードに応じて切替えるための構成として、互いに電圧レベルが異なる2つの基準電圧V1, V2を生成可能な基準電圧発生回路22を用いる構成について説明したが、基準電圧を1つの電圧レベルのままで、内部レギュレータ26側で内部電源電圧VDD\_RAMを2値V1, V2の間で切替えるようにしてもよい。実施の形態2では、内部レギュレータ26で内部電源電圧VDD\_RAMを切替える構成について説明する。

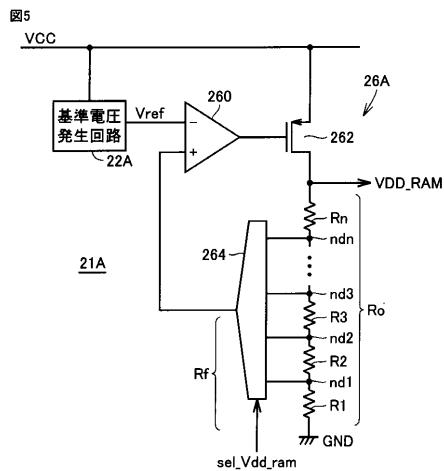

**【0091】**

図5は、実施の形態2による半導体装置に適用される内部電源回路21Aの構成を示す回路図である。実施の形態2による半導体装置の構成は、内部電源回路21Aを除いて、図1と同様であるので、詳細な説明は繰り返さない。

**【0092】**

図5を参照して、実施の形態2による内部電源回路21Aは、基準電圧発生回路22Aと、内部レギュレータ26Aとを含む。

**【0093】**

10

20

30

40

50

内部電源回路 21A は、外部電源電圧 VCC によって動作する。内部電源回路 21A は、基準電圧発生回路 22A と、内部レギュレータ 26A とを含む。基準電圧発生回路 22A は、外部電源電圧 VCC を降圧した基準電圧 Vref を生成する。

#### 【0094】

内部レギュレータ 26A は、基準電圧 Vref を参照して内部電源電圧 VDD\_RAM を生成する。具体的には、内部レギュレータ 26A は、誤差増幅器 260 と、PMOSトランジスタ 262 と、n 個 (n は 2 以上の自然数) の抵抗素子 R1 ~ Rn と、セレクタ 264 とを含む。

#### 【0095】

誤差増幅器 260 は、反転入力端子 (- 端子) が基準電圧発生回路 22A の出力ノードに接続され、非反転入力端子 (+ 端子) がセレクタ 264 の出力ノードに接続され、出力ノードが PMOS トランジスタ 262 の制御端子 (ゲート端子) に接続される。

#### 【0096】

抵抗素子 R1 ~ Rn は、この順で PMOS トランジスタ 262 のドレインと接地ノードとの間に直列に接続される。セレクタ 264 は、抵抗素子 R1 ~ Rn の接続ノード n1 ~ nn のうち、システム制御回路 28 (図 1) からの制御信号 sel\_vdd\_ram によって選択されたノード (以下、選択ノードと称する) の電圧を誤差増幅器 260 の非反転入力端子に出力する。

#### 【0097】

内部レギュレータ 26Aにおいて、選択ノードと接地ノードとの間の抵抗値を Rf とし、直列接続された抵抗素子 R1 ~ Rn の合成抵抗値を Ro とすると、出力ノードの電圧 (内部電源電圧 VDD\_RAM) は、誤差増幅器 260 の反転入力端子への入力電圧 (基準電圧 Vref) の Ro / Rf 倍になる。抵抗値 Rf は制御信号 sel\_vdd\_ram によって調整可能であるため、内部電源電圧 VDD\_RAM を高精度に調整することができる。

#### 【0098】

システム制御回路 28 は、アクティブモード時とスタンバイモード時とで抵抗値 Rf を切替える。具体的には、システム制御回路 28 は、アクティブモード時には、内部電源電圧 VDD\_RAM が内部電源電圧 VDD (1.25V) よりも低くなるように (例えば 1.05V)、抵抗値 Rf を調整する。これにより、内部レギュレータ 26 から外部レギュレータ 3 に向かって電流が流れるのを防止できる。

#### 【0099】

一方、スタンバイモード時には、システム制御回路 28 は、内部電源電圧 VDD\_RAM が SRAM メモリセル 32 がデータ保持可能な電圧 (例えば 1.1V) となるように抵抗値 Rf を調整する。

#### 【0100】

このように、実施の形態 2 によれば、内部レギュレータ 26A を、半導体装置の動作モードに応じて出力電圧 (内部電源電圧 VDD\_RAM) を切替え可能な構成としたことにより、上述の実施の形態 1 と同様の効果を得ることができる。

#### 【0101】

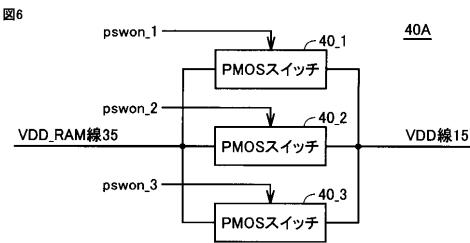

< 実施の形態 3 >

上述の実施の形態 1 による半導体装置 1 では、VDD 線 15 および VDD\_RAM 線 35 の遮断を 2 つの PMOS トランジスタで構成された 1 個の PMOS スイッチ 40 で行なう構成について説明した。しかしながら、この PMOS スイッチを複数個並列に接続し、これら複数個の PMOS スイッチを時間差を設けてオフするようにしてもよい。実施の形態 3 では、複数個の PMOS スイッチで VDD 線 15 および VDD\_RAM 線 35 の遮断を行なう構成について説明する。

#### 【0102】

図 6 は、実施の形態 3 による半導体装置に適用される PMOS スイッチ回路 40A の構成の一例を示す回路図である。実施の形態 3 による半導体装置の構成は、PMOS スイッ

10

20

30

40

50

チ回路 40A を除いて、図 1 と同様であるので、詳細な説明は繰り返さない。

#### 【0103】

図 6 を参照して、実施の形態 3 による PMOS スイッチ回路 40A は、VDD 線 15 および VDD\_RAM 線 35 の間に並列に接続された複数個（例えば 3 個とする）の PMOS スイッチ 40\_1, 40\_2, 40\_3 を含む。PMOS スイッチ 40\_1, 40\_2, 40\_3 の各々の回路構成は、図 3 に示す PMOS スイッチ 40 と同様であるので詳細な説明は繰り返さない。

#### 【0104】

PMOS スイッチ 40\_1 は、システム制御回路 28 から与えられる制御信号 pswon\_1 に応じてオン／オフが制御される。図示は省略するが、制御信号 pswon\_1 には、PMOS スイッチ 40\_1 を構成する PMOS トランジスタ P1 のオン／オフを制御するための制御信号 pswon\_vdd\_ram と、PMOS トランジスタ P2 のオン／オフを制御するための制御信号 pswon\_vdd とが含まれる。

10

#### 【0105】

同様に、PMOS スイッチ 40\_2 は、システム制御回路 28 から与えられる制御信号 pswon\_2 に応じてオン／オフが制御される。PMOS スイッチ 40\_3 は、システム制御回路 28 から与えられる制御信号 pswon\_3 に応じてオン／オフが制御される。

。

#### 【0106】

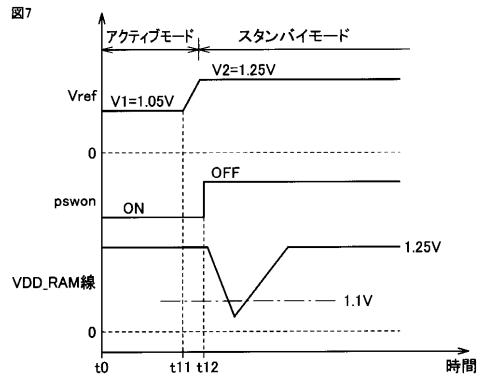

実施の形態 3 による半導体装置では、アクティブモードからスタンバイモードへの移行時に、並列接続された PMOS スイッチ 40\_1, 40\_2, 40\_3 を時間差を設けてオフする。実施の形態 3 による半導体装置の作用効果について、図 7 に示す比較例を参照しながら説明する。

20

#### 【0107】

図 7 は、実施の形態 1 による半導体装置 1（図 1）の動作を示すタイミングチャートである。図 7 には、アクティブモードからスタンバイモードへの移行時における基準電圧 Vref、制御信号 pswon および VDD\_RAM 線 35 の時間的变化が示される。

#### 【0108】

図 7 を参照して、半導体装置 1 がアクティブモードのとき（時刻 t0）、PMOS スイッチ 40 は、L レベルに活性化された制御信号 pswon ( pswon\_vdd, pswon\_vdd\_ram ) によってオンされる、VDD\_RAM 線 35 は、PMOS スイッチ 40 によって VDD 線 15 に電気的に接続されるため、VDD 線 15 から内部電源電圧 VDD ( 1.25V ) の供給を受ける。

30

#### 【0109】

このとき、内部電源回路 21 では、基準電圧発生回路 22 から内部レギュレータ 26 に与える基準電圧 Vref が、内部電源電圧 VDD ( 1.25V ) よりも低い電圧 V1 ( 1.05V ) に設定される。内部レギュレータ 26 が電圧 V1 を基準電圧 Vref として動作することにより、VDD\_RAM 線 35 には電圧 V1 に等しい内部電源電圧 VDD\_RAM が供給される。

#### 【0110】

アクティブモードからスタンバイモードへ移行するときには、内部電源回路 21 は、基準電圧発生回路 22 から内部レギュレータ 26 に与える基準電圧 Vref を、電圧 V2 ( 1.05V ) から電圧 V2 ( 1.25V ) に切替える（時刻 t11）。続いて、制御信号 pswon を H レベルに非活性化させて PMOS スイッチ 40 をオフする（時刻 t12）

。

40

#### 【0111】

内部レギュレータ 26 は、電圧 V2 を基準電圧 Vref として動作することにより、電圧 V2 に等しい内部電源電圧 VDD\_RAM を VDD\_RAM 線 35 に供給する。しかしながら、上述のように、内部レギュレータ 26 は出力電圧の反応が鈍いため、PMOS スイッチ 40 がオンされるタイミング（時刻 t12）に、内部電源電圧 VDD\_RAM が未

50

だ電圧 V<sub>2</sub> に達していない事態が起こり得る。そのような事態が生じると、図 7 に示すように、V<sub>D D</sub>\_R<sub>A M</sub>線 3 5 に電圧ドロップが発生し、内部電源電圧 V<sub>D D</sub>\_R<sub>A M</sub> が S<sub>R A M</sub>メモリセル 3 2 がデータ保持可能な電圧（例えば 1.1V）を下回ってしまう可能性がある。

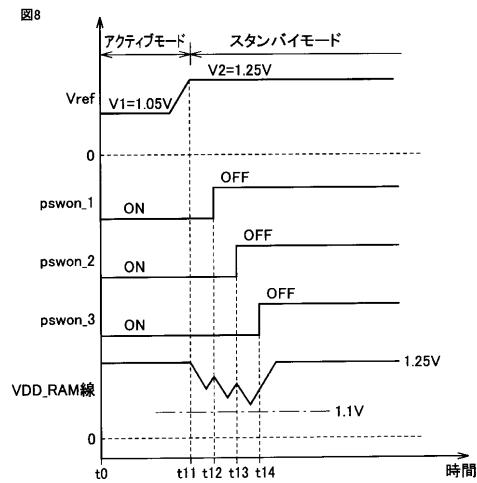

#### 【0112】

図 8 は、実施の形態 3 による半導体装置の動作を示すタイミングチャートである。図 8 には、アクティブモードからスタンバイモードへの移行時における基準電圧 V<sub>r e f</sub>、制御信号 p<sub>s w o n</sub> および V<sub>D D</sub>\_R<sub>A M</sub> 線 3 5 の時間的变化が示される。

#### 【0113】

図 8 を参照して、実施の形態 3 による半導体装置では、アクティブモードからスタンバイモードへ移行するときに、PMOSスイッチ回路 40A を構成する複数個の PMOS スイッチ 40\_1, 40\_2, 40\_3 を時間差を設けてオフする。具体的には、最初に制御信号 p<sub>s w o n</sub>\_1 (p<sub>s w o n</sub>\_vdd, p<sub>s w o n</sub>\_vdd\_ram) を H レベルに非活性化させて PMOS スイッチ 40\_1 をオフする（時刻 t<sub>12</sub>）。次に、制御信号 p<sub>s w o n</sub>\_2 を H レベルに非活性化させて PMOS スイッチ 40\_2 をオフする（時刻 t<sub>13</sub>）。最後に、制御信号 p<sub>s w o n</sub>\_3 を H レベルに非活性化させて PMOS スイッチ 40\_3 をオフする（時刻 t<sub>14</sub>）。

#### 【0114】

このように、PMOSスイッチ 40\_1, 40\_2, 40\_3 を時間差を設けてオフすることにより、V<sub>D D</sub>\_R<sub>A M</sub> 線 3 5 の電圧は、PMOSスイッチがオフされるごとに徐々に低下する。最初の PMOSスイッチ 40\_1 がオフされてから最後の PMOSスイッチ 40\_3 がオフされるまでの V<sub>D D</sub>\_R<sub>A M</sub> 線 3 5 の電圧の降下量は、図 7 の比較例における電圧の降下量と比べて小さく抑えられている。したがって、内部電源電圧 V<sub>D D</sub>\_R<sub>A M</sub> が、S<sub>R A M</sub>メモリセル 3 2 がデータ保持可能な電圧（1.1V）を下回るのを回避できる。この結果、実施の形態 3 によれば、V<sub>D D</sub>\_R<sub>A M</sub> 線 3 5 の電圧ドロップをより効果的に抑制することが可能となる。

#### 【0115】

また、関連技術に示したように、アクティブモード時とスタンバイモード時とで電流供給能力の異なる 2 つのレギュレータ（外部レギュレータ 3 および内部レギュレータ 26）を切替えて用いる構成に対しても、図 6 に示される PMOSスイッチ回路 40A の構成を適用することが可能であることはいうまでもない。

#### 【0116】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は上記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

#### 【符号の説明】

#### 【0117】

1, 1000 半導体装置、2, 3 外部レギュレータ、4 外部容量、5, 6, 7 電源端子、10, 100 V<sub>D D</sub>電源領域、12 内部回路、14 S<sub>R A M</sub>周辺回路、15 V<sub>D D</sub>線、16, 34 レベルシフタ、35 V<sub>D D</sub>\_R<sub>A M</sub>線、40, 40A スイッチ回路、200 V<sub>C C</sub>電源領域、21, 21A, 210 内部電源回路、22, 22A, 220 基準電圧発生回路、24, 264 セレクタ、26 内部レギュレータ、28 システム制御回路、30, 300 V<sub>D D</sub>\_R<sub>A M</sub>電源領域、32 S<sub>R A M</sub>メモリセル、40, 40\_1, 40\_2, 40\_3, 400 PMOSスイッチ、40A PMOSスイッチ回路、42\_1, 42\_2 インバータ、44\_1, 44\_2 NAN Dゲート、46\_1, 46\_2 バッファ、50\_1, 50\_2 制御信号生成部、260 誤差増幅器、262, P1, P2 PMOSトランジスタ。

【図1】

【図2】

【図3】

【図4】

【図5】

【図7】

【図6】

【図8】

【図9】

【図10】

【図11】

---

フロントページの続き

審査官 白石 圭吾

(56)参考文献 特開平07-049729(JP,A)

特開平06-012876(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 06 F 1 / 2 6

G 11 C 1 1 / 4 1 3