(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2017년02월08일

(11) 등록번호 10-1704831

(24) 등록일자 2017년02월02일

(51) 국제특허분류(Int. Cl.)

H01L 31/0224 (2006.01) H01L 31/0216

(2014.01)

H01L 31/0232 (2014.01) H01L 33/38 (2010.01)

H01L 33/40 (2010.01)

(21) 출원번호 10-2011-7003395

(22) 출원일자(국제) 2009년08월05일

심사청구일자 2014년07월16일

(85) 번역문제출일자 2011년02월14일

(65) 공개번호 10-2011-0068974

(43) 공개일자 2011년06월22일

(86) 국제출원번호 PCT/DE2009/001111

(87) 국제공개번호 WO 2010/020213

국제공개일자 2010년02월25일

(30) 우선권주장

10 2008 039 360.6 2008년08월22일 독일(DE)

(56) 선행기술조사문헌

US20030111667 A1\*

US20070145380 A1\*

US05502316 A\*

US20040211968 A1\*

\*는 심사관에 의하여 인용된 문헌

(73) 특허권자

오스람 옵토 세미컨덕터스 게엠베하

독일 레겐스부르크 라이브니츠슈트라쎄 4 (

우:93055)

(72) 발명자

그롤리어, 빙센트

독일, 93047 레겐스부르그, 본-더-坦-스트라베 24

플로슬, 안드레아스

독일, 93051 레겐스부르그, 조한-아이지1-웨그 24

(74) 대리인

김태홍

전체 청구항 수 : 총 15 항

심사관 : 방기인

(54) 발명의 명칭 가스 충전된 거울을 포함하는 광전 반도체칩

**(57) 요 약**

광전 반도체칩이 제공되며, 상기 반도체칩은 활성 영역(10)을 구비한 반도체 몸체(1), 거울층(2), 및 상기 반도체 몸체(1)와 거울층(2) 사이에 배치되는 접촉부(3)를 포함하며, 상기 접촉부는 상기 반도체 몸체(2)와 거울층(2) 사이에 간격(D)을 개재하여 적어도 하나의 중공(4)이 상기 거울층(2)과 반도체 몸체(1) 사이에 형성되도록 하고, 이때 상기 적어도 하나의 중공(4)은 가스(40)를 수용한다.

**대 표 도** - 도1a

## 명세서

### 청구범위

#### 청구항 1

활성 영역(10)을 구비한 반도체 몸체(1);

거울층(2); 및

상기 반도체 몸체(1)와 상기 거울층(2) 사이에 배치되고, 상기 반도체 몸체(1)와 상기 거울층(2) 사이에 간격(D)을 개재하여, 상기 거울층(2)과 상기 반도체 몸체(1) 사이에서 적어도 하나의 중공(4)이 형성되도록 하는 접촉부(3)

를 포함하고,

상기 적어도 하나의 중공(4)은 가스(40)를 수용하는 것을 특징으로 하는 광전 반도체칩.

#### 청구항 2

청구항 1에 있어서,

적어도 하나의 접촉부(3)는 폐쇄된 경로를 형성하는 것을 특징으로 하는 광전 반도체칩.

#### 청구항 3

청구항 2에 있어서,

적어도 접촉부(3) 중 하나에 의해 광전 반도체칩의 구동 시 전기 전류가 상기 활성 영역(10)으로 입력되는 것을 특징으로 하는 광전 반도체칩.

#### 청구항 4

청구항 1 내지 청구항 3 중 어느 한 항에 있어서,

상기 적어도 하나의 중공(4)은 패시베이션 물질(5)로 밀봉되는 것을 특징으로 하는 광전 반도체칩.

#### 청구항 5

청구항 1 내지 청구항 3 중 어느 한 항에 있어서,

상기 가스(40)는 정상압보다 낮은 압력으로 상기 중공(4) 중 적어도 하나에 삽입되는 것을 특징으로 하는 광전 반도체칩.

#### 청구항 6

청구항 1 내지 청구항 3 중 어느 한 항에 있어서,

상기 접촉부(3)는 상기 반도체 몸체(1)와 직접 접촉하는 것을 특징으로 하는 광전 반도체칩.

#### 청구항 7

청구항 1 내지 청구항 3 중 어느 한 항에 있어서,

상기 거울층(2)과 상기 반도체 몸체(1) 사이의 간격(D)은 적어도 10 nm이고 최대 10 μm인 것을 특징으로 하는 광전 반도체칩.

#### 청구항 8

청구항 1 내지 청구항 3 중 어느 한 항에 있어서,

상기 접촉부(3)와 상기 거울층(2)은 적어도 하나의 공통 금속을 포함하는 것을 특징으로 하는 광전 반도체칩.

**청구항 9**

청구항 8에 있어서,

상기 접촉부(3) 및 상기 거울층(2)은 동일한 물질로 구성되는 것을 특징으로 하는 광전 반도체칩.

**청구항 10**

청구항 1 내지 청구항 3 중 어느 한 항에 있어서,

상기 접촉부(3)는 Sn, In, Ga, Bi 중 적어도 하나의 땜납 물질을 포함하는 것을 특징으로 하는 광전 반도체칩.

**청구항 11**

광전 반도체칩의 제조 방법에 있어서,

적어도 하나의 활성 영역(10)을 구비한 반도체 몸체(1)를 제공하는 단계;

거울층(2)을 구비한 캐리어(7)를 제공하는 단계;

상기 거울층(2)의 상측(2a) 및 상기 반도체 몸체(1)의 하측(1b) 중 적어도 하나 상에 접촉부(3)를 마련하는 단계;

열 압축을 이용하여 상기 반도체 몸체(1)와 상기 거울층(2)을 상기 접촉부(3)를 통해 결합하는 단계

를 포함하고,

상기 접촉부(3)가 상기 반도체 몸체(1)와 상기 거울층(2) 사이에 간격(D)을 개재하여, 상기 거울층(2)과 상기 반도체 몸체(1) 사이에 적어도 하나의 중공(4)이 형성되며, 상기 중공은 가스(40)를 수용하는 것을 특징으로 하는 광전 반도체칩의 제조 방법.

**청구항 12**

청구항 11에 있어서,

상기 접촉부(3)는 상기 거울층(2)과 동일한 물질로 구성되는 것을 특징으로 하는 광전 반도체칩의 제조 방법.

**청구항 13**

청구항 11 또는 청구항 12에 있어서,

상기 접촉부(3)는 인쇄 방법에 의해 마련되는 것을 특징으로 하는 광전 반도체칩의 제조 방법.

**청구항 14**

청구항 11 또는 청구항 12에 있어서,

상기 접촉부(3)는 기상증착에 의해 마련되는 것을 특징으로 하는 광전 반도체칩의 제조 방법.

**청구항 15**

청구항 11 또는 청구항 12에 있어서,

상기 접촉부(3)는 비드(bead)로서 마련되는 것을 특징으로 하는 반도체칩의 제조 방법.

**발명의 설명****기술 분야**

[0001]

본 발명은 광전 반도체칩에 관한 것이다.

**배경 기술**

[0002]

광전 반도체칩이 제공된다.

## 발명의 내용

### 해결하려는 과제

[0003] 본 발명의 과제는 효율이 개선된 광전 반도체칩을 제공하는 것이다.

### 과제의 해결 수단

[0004] 광전 반도체칩의 적어도 일 실시예에 따르면, 광전 반도체칩은 활성 영역을 구비한 반도체 몸체를 포함한다. 바람직하게는, 반도체 몸체는 에피택시얼 성장된 반도체 몸체를 가리킨다. 반도체 몸체는 성장 기판과 결합되어 있을 수 있다. 그러나, 성장 기판이 반도체 몸체로부터 제거되거나 적어도 얇아져 있을 수 있다. 바람직하게는, 반도체 몸체의 활성 영역은 전자기 복사의 생성 또는 검출을 위해 적합하다.

[0005] 활성 영역이 전자기 복사의 생성을 위해 적합한 경우, 광전 반도체칩은 루미네슨스 다이오드칩을 가리킨다. 즉, 광전 반도체칩은 레이저다이오드칩 또는 발광다이오드칩으로 형성된다. 활성 영역이 전자기 복사의 검출을 위해 적합하면, 광전 반도체칩은 검출기칩, 예를 들면 포토다이오드칩을 가리킨다. 예를 들면, 포토다이오드칩은 적외선 검출을 위해 고려될 수 있다.

[0006] 광전 반도체칩은 거울층을 더 포함한다.

[0007] 예를 들면, 거울층은 금속 거울층을 가리킨다. 즉, 거울층은 금속으로 이루어지거나 금속을 함유하고, 양호한 전기 전도도 및 높은 반사도와 같은 금속 특성을 특징으로 한다.

[0008] 또한, 거울층이 브래그 거울을 나타낼 수도 있는데, 이때 상기 브래그 거울은 고굴절성 물질과 저굴절성 물질의 층들이 교번적으로 배치되어 구성된다.

[0009] 또한, 거울층은 브래그 거울과 금속 거울의 조합을 가리킬 수 있다. 금속 거울은 활성 영역을 향해있고 브래그 거울 상에 배치된다.

[0010] 거울층은 활성 영역에서 생성되거나 검출될 전자기 복사에 대해 바람직하게는 적어도 90%의 반사도를 가진다.

[0011] 적어도 일 실시예에 따르면, 광전 반도체칩은 접촉부를 포함한다. 접촉부는 거울층과 반도체 몸체 사이에 기계적 결합을 이룬다. 즉, 거울층과 반도체 몸체는 접촉부에 의해 기계적으로 상호 결합된다. 광전 반도체칩은 이러한 접촉부 중 적어도 하나를 포함하고, 바람직하게는, 광전 반도체칩은 이러한 접촉부를 다수로 포함한다.

[0012] 접촉부는 반도체 몸체와 거울층 사이에 배치된다. 접촉부는 반도체 몸체에 직접 접하거나/접하고 거울층에 직접 접할 수 있다. 즉, 접촉부는 예를 들면 반도체 몸체와 직접 접촉하거나/접촉하고 거울층과 직접 접촉할 수 있다.

[0013] 접촉부는 반도체 몸체와 거울층 사이에 간격을 개재한다. 즉, 접촉부는 예를 들면 기둥 또는 지주와 같은 방식으로 형성되어, 기계적 고정 역할 외에도 반도체 몸체와 거울층 사이에 간격을 개재한다. 이는, 반도체 몸체와 거울층이 접촉하고 있지 않음을 의미한다. 반도체 몸체와 거울층은 직접 접촉하고 있지 않으며, 접촉부에 의해 분리되어 있다.

[0014] 반도체 몸체와 거울층 사이에서 접촉부가 개재되는 간격에 의해, 반도체 몸체와 거울층 사이에는 적어도 하나의 중공이 형성된다. 즉, 반도체 몸체와 거울층은 서로 이격되어 배치되고, 접촉부가 위치하지 않은 자리에서 반도체 몸체와 거울층 사이에 중공이 위치한다.

[0015] 광전 반도체칩의 적어도 일 실시예에 따르면, 중공은 가스를 수용한다. 중공은 예를 들면 공기로 채워질 수 있다. 그러나, 중공이 예를 들면 헬륨과 같은 희귀가스로 채워질 수도 있다. 또한, 중공은 질소나 수소로 채워질 수 있다. 즉, 접촉부에 의해 형성되는 적어도 하나의 중공은 가스를 수용하고, 바람직하게는 이러한 가스로 채워진다. 이를 통해, 예를 들면, 반도체 몸체, 거울층 및 접촉부는 중공체의 가스에 인접할 수 있다. 적어도 반도체 몸체의 영역에는, 즉 반도체 몸체와 거울층 사이에 가스가 있다. 이때, 반도체 몸체와 거울층 사이에 접촉부와 가스만 있을 수 있다. 이 경우, 다른 물질은 반도체 몸체와 거울층 사이에 존재하지 않는다.

[0016] 광전 반도체칩의 적어도 일 실시예에 따르면, 광전 반도체칩은 활성 영역을 구비한 반도체 몸체를 포함한다. 또한, 반도체칩은 거울층과 접촉부를 포함하고, 상기 접촉부는 반도체 몸체와 거울층 사이에 배치된다. 접촉부는 반도체 몸체와 거울층 사이에 간격을 개재하여, 거울층과 반도체 몸체 사이에 적어도 하나의 중공이 형성된다. 적어도 하나의 중공은 가스를 수용한다.

- [0017] 광전 반도체칩의 적어도 일 실시예에 따르면, 접촉부는 반도체 몸체의 활성 영역의 전기 접촉을 위해 고려된다. 즉, 접촉부에 의해, 광전 반도체칩의 구동 시 전기 전류가 반도체 몸체로 입력되고, 그로 인하여 활성 영역으로 입력되며, 상기 전류에 의해 활성 영역에서 전자기 복사가 생성되거나 검출된다. 이 경우, 바람직하게는, 접촉부는 전기 전도성으로 형성된다.

- [0018] 본 명세서에 기술된 광전 반도체칩은, 특히, 거울층과 반도체 몸체사이의 중공을 가스로 채우는 것이 예를 들면 규소질화물 또는 규소산화물과 같은 유전체 고체로 상기 중공을 채우는 것보다 유리하다는 인식을 기초로 한다.

- [0019] 한편으로는, 중공을 가스로 채움으로써 반도체 몸체와 중공 사이에서 굴절률의 비약적 변화가 매우 심하다. 이러한 심한 굴절률의 비약적 변화는 반도체 몸체와 중공 사이의 경계면에 도달하는 전자기 복사가 전반사에 대해 매우 낮은 각으로 도달하도록 한다. 반도체 몸체와 중공 사이의 경계면은 높은 굴절률차에 의해 거울로서 역할 한다. 이와 같이 형성된 "가스 거울"은 평각에 대한 반사를 개선할 수 있다. 급경사각으로 입사되는 전자기 복사는, 금속성이거나/금속성이면서 브래그 거울로서 형성된 거울층에 의해 반사된다.

- [0020] 활성 영역에서 생성되어 중공의 방향으로 방출되는 전자기 복사는 경계면에서의 전반사를 이용하여 반사되고, 복사 출사면 또는 반도체 몸체의 활성 영역의 방향으로 방향 전환될 수 있다. 이러한 점은 활성 영역에서 검출되어야 할 전자기 복사에 대해서도 동일하게 적용된다. 전반사되지 않고 반도체 몸체와 중공 사이의 경계면을 투과하는 전자기 복사는 계속 진행하여 접촉부 및/또는 거울층 상에 도달하고, 이러한 구성 요소로부터 복사 출사면의 방향 및/또는 광전 반도체칩의 활성 영역의 방향으로 반사된다.

- [0021] 중공을 가스로 채움으로써, 즉 접촉부에 의해 반도체 몸체와 거울층 사이의 중공이 형성됨으로써, 광전 반도체 칩의 효율이 증가한다. 또한, 가스로 중공을 채우는 것은 방열 개선을 위해 매우 유리하다. 구동 시 광전 반도체칩에서 생성된 열은 중공에 삽입된 가스에 의해 매우 양호하게 반도체 몸체로부터 거울층으로, 그리고 상기 거울층으로부터 예를 들면 캐리어로 배출될 수 있다. 방열 개선을 위해서는, 중공을 헬륨 또는 수소( $H_2$ )로 채우는 것이 매우 잘 맞다. 그러나, 질소 또는 아르곤과 같은 다른 가스도 고려될 수 있다.

- [0022] 가스 충전된 중공은 유전체 물질을 대체하고, 예를 들면 유전체 거울층을 대체한다. 상기 중공은 여타 그와 같은 것에 의해 개선된 광학 특성 및 열 특성을 가진다는 특징이 있다. 종합적으로, 가스 충전된 중공은 광전 반도체칩의 효율을 개선하는 데 기여한다.

- [0023] 광전 반도체칩의 적어도 일 실시예에 따르면, 접촉부 중 적어도 하나는 폐쇄된 경로를 형성한다. 즉, 접촉부 중 적어도 하나는 예를 들면 프레임 방식으로 연장된다. 이러한 접촉부는 연속적으로 연장되며, 거울층과 반도체 몸체 사이의 영역을 둘러싼다.

- [0024] 바꾸어 말하면, 접촉부는 적어도 거울층과 반도체 몸체 사이의 영역을 프레임 방식으로 둘러싸고, 이때 "프레임 방식"이란 이러한 접촉부의 기하학에 대한 암시가 아니다. 예를 들면 접촉부는 원형 프레임, 직사각형 프레임 또는 타원형 프레임의 방식으로 형성될 수 있다. 바람직하게는, 폐쇄된 경로로서 형성된 접촉부는 광전 반도체 칩의 테두리 영역에 배치된다.

- [0025] 즉, 예를 들면 반도체 몸체의 테두리에서, 거울층을 향해있는 반도체 몸체의 측에 프레임형으로 형성된 접촉부가 배치되고, 상기 접촉부는 폐쇄된 경로로서 반도체 몸체의 테두리를 따라 연장된다. 접촉부는 거울층 및/또는 반도체 몸체와 직접 접촉할 수 있다. 폐쇄된 경로를 형성하는 이러한 접촉부는 거울층과 반도체 몸체사이에서 가스로 채워지는 매우 큰 중공을 형성하기에 매우 잘 맞다. 이러한 접촉부에 의해, 가스는 밀봉식으로 (hermetically) 조밀하게 중공에 삽입되며, 상기 중공은 접촉부, 거울층 및 반도체 몸체에 의해 형성된다.

- [0026] 바람직하게는, 폐쇄된 경로로서 형성된 접촉부에 의해 닫히는 중공에는 수많은 다른 접촉부들이 배치되고, 상기 접촉부들은 주로 기둥으로서 형성될 수 있다. 테두리에서 연속적으로 연장되며 폐쇄된 경로로서 형성된 접촉부에 의해, 반도체 몸체와 거울층의 결합 시 열 전도도가 양호한 가스가 광전 반도체칩에 조밀하게 삽입될 수 있다.

- [0027] 광전 반도체칩의 적어도 일 실시예에 따르면, 적어도 하나의 중공은 패시베이션 물질로 밀봉된다. 예를 들면, 패시베이션 물질은 광전 반도체칩의 테두리 영역에서 광전 반도체칩의 둘레에 제공될 수 있다. 패시베이션 물질은, 폐쇄된 경로로서 형성된 접촉부에 대해 대안적 또는 부가적으로 사용될 수 있다. 패시베이션 물질은 예를 들면 거울층과 반도체 몸체 사이의 중공에 삽입된 가스에 대해 불투과성(tight)일 수 있다. 패시베이션 물질은 가스의 밀봉부를 형성한다. 패시베이션 물질은 폐쇄된 경로로서 형성된 접촉부에 대해 부가적 또는 대안적으로 사용될 수 있다.

- [0028] 적어도 일 실시예에 따르면, 가스는 정상압보다 작은 압력으로 중공 중 적어도 하나의 중공에 삽입된다. 거울층과 반도체 몸체 사이에 형성된 중공이 폐쇄된 경로로서 형성된 접촉부 및/또는 폐시베이션 물질에 의해 밀봉된다면, 가스는 정상의 외부압보다 낮은 압력으로 거울층과 반도체 몸체 사이에 삽입될 수 있다. 저압으로 삽입된 가스는 중공에서의 가스의 열 특성을 개선한다. 즉, 이 경우에, 중공에서 가스에 의한 열 소산은 더욱 개선된다. 바람직하게는, 가스는 0.9와 1.1 bar 사이의 압력으로 중공에서 밀봉된다. 그러나, 가스가 중공에서 과압으로 밀봉될 수도 있다. 특히, 1 mbar와 5 bar 사이의 압력 범위가 고려될 수 있다.

- [0029] 광전 반도체칩의 적어도 일 실시예에 따르면, 거울층과 반도체 몸체 사이의 간격은 적어도 10 nm이며, 바람직하게는 최대 10  $\mu\text{m}$ 이다. 상기 간격은 접촉부에 의해 개재된다. 즉, 바람직하게는, 접촉부의 높이가 적어도 10 nm이고 최대 10  $\mu\text{m}$ 이다. 예를 들면, 거울층과 반도체 몸체 사이의 간격은 100 nm과 1  $\mu\text{m}$  사이이다. 거울층과 반도체 몸체 사이의 간격에 대해 제공된 상기 범위는 열 소산을 위해 이상적인 것으로서 도출되며, 적어도 하나의 중공체에서의 상기 가스에 의해 반도체 몸체로부터 거울층의 방향으로 열 소산이 이루어진다.

- [0030] 광전 반도체칩의 적어도 일 실시예에 따르면, 접촉부 및 거울층은 적어도 하나의 공통 금속을 포함한다. 즉, 접촉부 및 거울층은 각각 적어도 하나의 금속을 포함할 수 있다. 접촉부와 거울층이 포함하는 금속 중 적어도 하나는 서로가 공통으로 포함하고 있다. 예를 들면, 접촉부뿐만 아니라 거울층도 은, 알루미늄 또는 금을 포함한다.

- [0031] 광전 반도체칩의 적어도 일 실시예에 따르면, 접촉부 및 거울층은 동일한 물질로 이루어진다. 예를 들면, 접촉부 및 거울층은 알루미늄, 은 또는 금으로 구성된다.

- [0032] 광전 반도체칩의 적어도 일 실시예에 따르면, 접촉부는 적어도 하나의 땜납 물질을 포함한다. 예를 들면, 접촉부는 아연, 인듐, 갈륨, 비스무트 중 적어도 하나의 땜납 물질을 포함한다. 이러한 땜납 물질은 용점이 매우 낮다는 특징이 있다. 이러한 땜납 물질 중 적어도 하나를 포함하는 접촉부는 납땜을 이용하여 반도체 몸체와 거울층 상에 매우 양호하게 마련될 수 있다.

- [0033] 예를 들면, 접촉부를 위해 은-아연 화합물 또는 은-인듐 화합물이 땜납으로서 사용될 수 있다. 접촉부는 반도체칩의 제조 시 반도체 몸체 상에 마련될 수 있고, 이때 접촉부는 차단층 또는 부착 증진층을 포함할 수 있으며, 이러한 층들은 반도체 몸체를 향해있다. 이러한 층들은 예를 들면 반도체 몸체에서의 접촉부의 부착을 개선하거나, 예를 들면 은과 같은 금속이 접촉부로부터 반도체 몸체로 확산되는 것을 방지할 수 있다.

- [0034] 접촉부를 포함한 반도체 몸체는 거울층 상에 본딩되고, 상기 거울층은 예를 들면 캐리어 상에 적층되어 있다. 이때, 예를 들면 Ag-Sn 상 또는 Ag-In 상이 형성되고, 이러한 상은 이후의 가공 시 - 예를 들면 도체판 상의 납땜 시 - 반도체칩의 내온도성을 보장한다. 즉, 본딩은 바람직하게는 등온 응고를 이용하여 수행된다. 상기 형성된 상은 본딩 온도보다 높은 재용융점을 포함한다. 이러한 점은 본딩 이후의 칩의 추가 공정 시, 그리고 칩의 자체 구동 시 유리한데, 본딩 결합이 예기치 않게 풀릴 확률이 감소하기 때문이다.

- [0035] 또한, 광전 반도체칩의 제조 방법이 제공된다. 바람직하게는, 본 방법은 본 명세서에 기술된 실시예 중 적어도 하나에 따른 광전 반도체칩을 제조하기에 적합하다. 즉, 본 명세서에 기술된 광전 반도체칩은 기술된 방법으로 제조될 수 있거나, 기술된 방법으로 제조된다. 광전 반도체칩과 관련하여 개시된 전체 특징은 방법과 관련하여 서도 개시된다.

- [0036] 방법의 적어도 일 실시예에 따르면 방법은 이하의 단계를 포함한다:

- [0037] 우선, 적어도 하나의 활성 영역을 구비한 반도체 몸체가 제공되고, 상기 활성 영역은 예를 들면 복사 생성 또는 복사 겸출을 위해 고려될 수 있다. 또한, 캐리어가 제공되고, 상기 캐리어 상에 거울층이 적층된다. 캐리어와 거울층 사이에 예를 들면 층 또는 층 시퀀스가 배치될 수 있고, 상기 층 또는 층 시퀀스는 거울층으로부터의 물질 확산 장벽 역할을 한다. 반도체 몸체는 이후의 단계에서 상기 반도체 몸체의 하측이 상기 거울층의 상측에 제공되고, 이때 상기 거울층의 상측은 캐리어와 반대 방향에 있다. 이를 위해, 우선 접촉부가 거울층의 상측에 마련되거나/마련되고 반도체 몸체의 하측에 마련된다. 즉, 접촉부는 거울층 상에 또는 반도체 몸체 상에 또는 상기 언급한 두 구성 요소상에 마련될 수 있다. 마지막 단계에서, 반도체 몸체 및 거울층은 접촉부에 의해 서로 결합되는데, 열 압축을 이용한다. 이러한 열 압축에 의해, 접촉부는 반도체 몸체 및 거울층과 기계적으로 단단히 결합된다.

- [0038] 열 압축은 바람직하게는 150°C와 450°C의 온도에서 수행된다. 압력은 0.4 MPa와 15 MPa 사이에서 조절된다. 열 압축은 - 각 온도와 압력에 따라 - 2분과 10시간 사이의 지속 시간동안 수행되며, 이때 열 압축이 길게 지속

될수록 온도와 압력은 더 낮게 조절된다.

[0039] 방법의 적어도 일 실시예에 따르면, 접촉부는 거울층과 동일한 물질로 이루어진다. 예를 들면, 거울층은, 예를 들면 PVD(물리적 기상 증착)를 이용하여 증착된 은 층으로 구성된다. 은 소재의 접촉부는 거울층과 반도체 몸체 사이에 삽입된다. 예를 들면, 접촉부는 스크린 인쇄 또는 잉크젯 인쇄(inkjet)와 같은 인쇄 방법을 이용하여, PVD를 이용하여 또는 예비 성형된 미립자으로서, 특히 비드(bead)로서 마련될 수 있다.

[0040] 이하, 본 명세서에 기술된 광전 반도체칩 및 본 명세서에 기술된 방법이 실시예 및 그에 속한 도면에 의거하여 더욱 상세히 설명된다.

### 도면의 간단한 설명

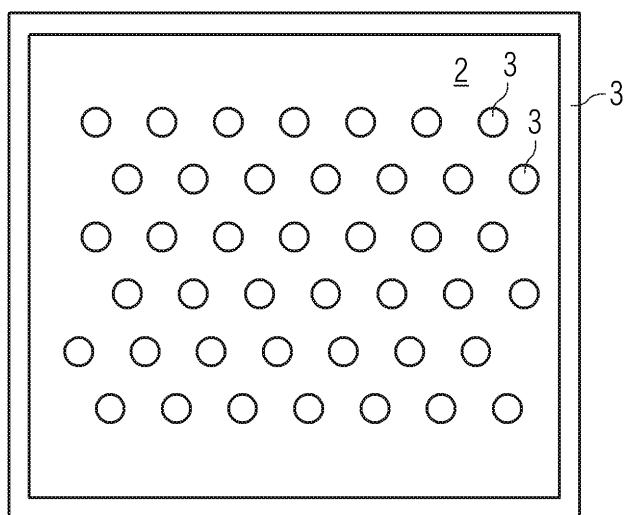

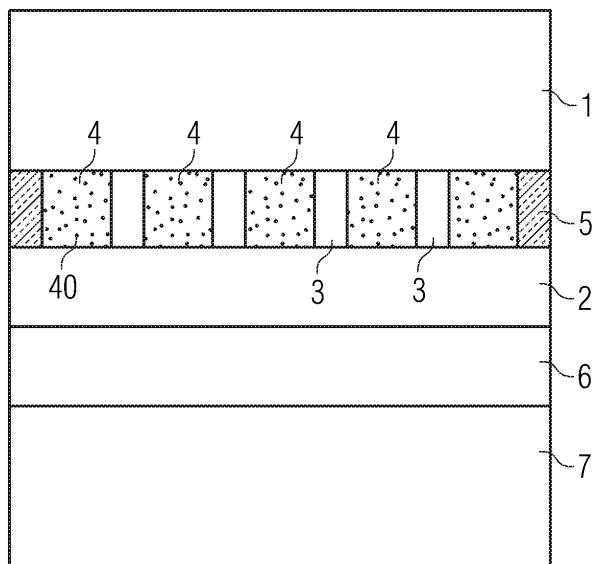

[0041] 도 1a는 제1실시예에 따라 본 명세서에 기술된 광전 반도체칩을 개략적 단면도로 도시한다.

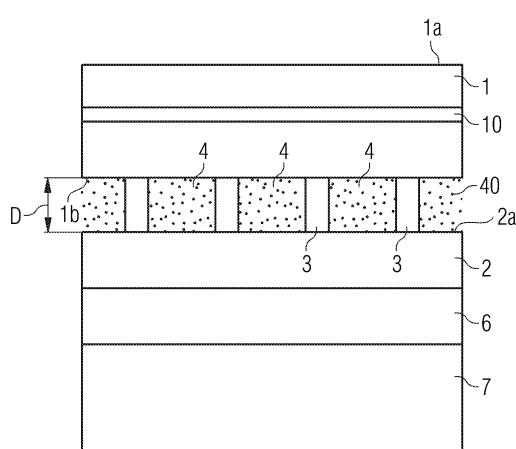

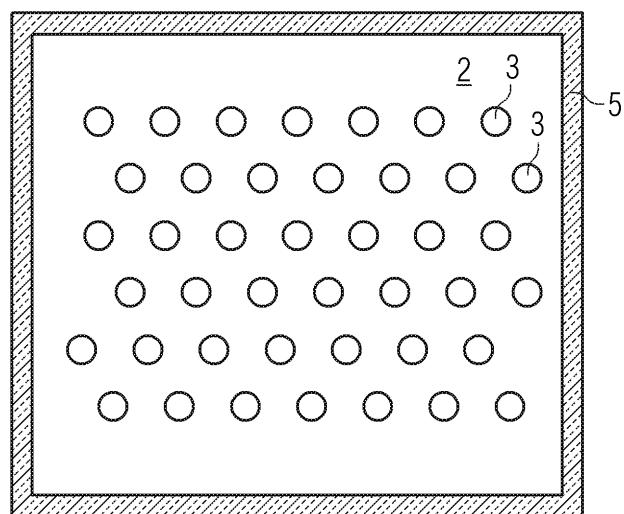

도 1b는 제1실시예에 따른 광전 반도체칩을 거울층 상의 개략적 평면도로 도시한다.

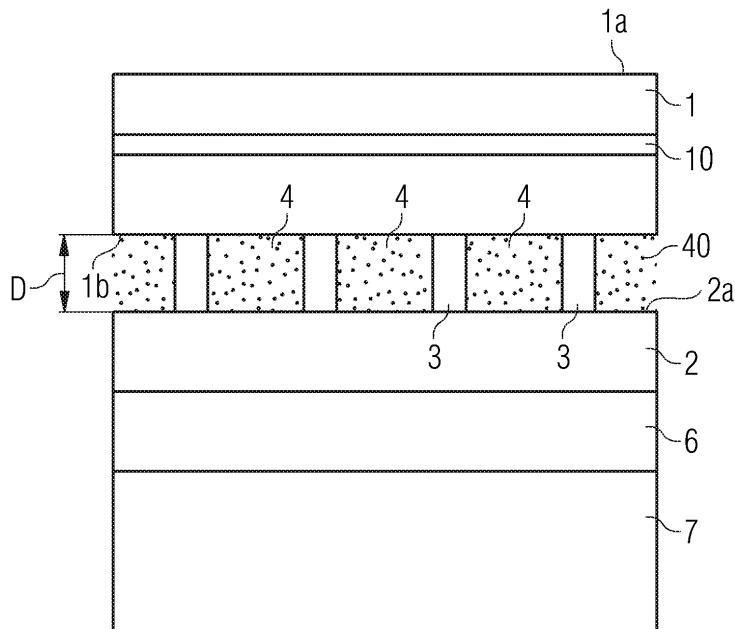

도 2a는 제2실시예에 따라 본 명세서에 기술된 광전 반도체칩을 개략적 단면도로 도시한다.

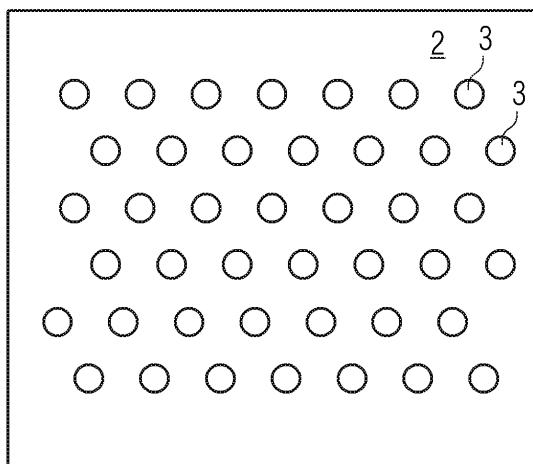

도 2b는 제2실시예에 따른 광전 반도체칩을 거울층 상의 개략적 평면도로 도시한다.

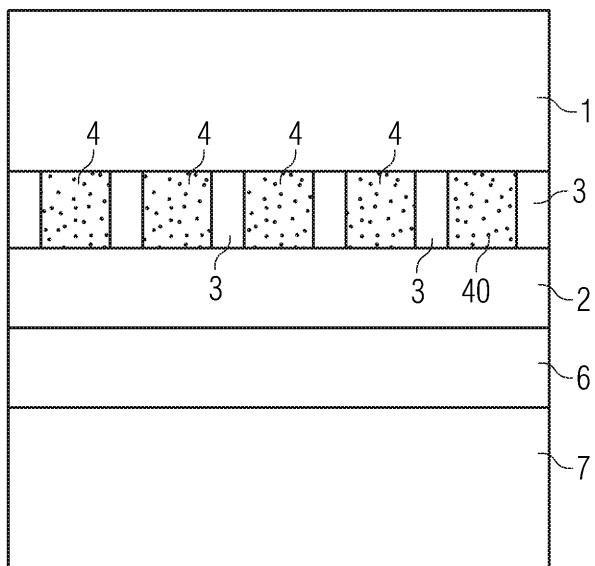

도 3a는 제3실시예에 따라 본 명세서에 기술된 광전 반도체칩을 개략적 단면도로 도시한다.

도 3b는 제3실시예에 따른 광전 반도체칩을 거울층(2) 상의 개략적 평면도로 도시한다.

### 발명을 실시하기 위한 구체적인 내용

[0042] 동일하거나, 동일한 방식이거나 동일한 효과를 가진 요소는 도면에서 동일한 참조 번호를 가진다. 도면 및 도면에 도시된 요소들간의 크기비는 치수가 정확한 것으로 볼 수 없다. 오히려, 개별 요소는 더 나은 표현 및/또는 더 나은 이해를 위해 과장되어 크게 도시되어 있을 수 있다.

[0043] 도 1a의 개략적 단면도는 제1실시예에 따라 본 명세서에 기술된 광전 반도체칩을 도시한다. 반도체칩은 반도체 몸체(1)를 포함한다.

[0044] 반도체 몸체(1)는 예를 들면 에피택시얼 제조된다. 본래 반도체 몸체(1)의 상측(1a)에 배치되는 성장 기판은 반도체 몸체(1)로부터 제거되어 있다. 광전 반도체칩은 소위 박막칩이다. 반도체 몸체(1)는 활성 영역(10)을 포함한다. 활성 영역은 예를 들면 복사 생성 또는 복사 검출을 위해 고려된다. 반도체 몸체(1)는 상기 반도체 몸체의 하측(1b)에서 거울층(2)의 상측(2a)을 향해있다. 거울층은 예를 들면 은, 금 또는 알루미늄으로 이루어진다. 거울층을 위해 알루미늄이 사용되면, 상기 알루미늄은 거울층(2)이 반도체 몸체(1)와 결합하기 전에 바람직하게는 용제(fluoride)로 처리되고, 상기 용제는 거울층(2)의 상측(2a)으로부터 산화물층을 제거한다.

[0045] 반도체 몸체(1) 및 거울층(2)은 예를 들면 기동 또는 지주로서 형성된 접촉부(3)를 이용하여 상호 간에 기계적 및 전기적으로 결합된다.

[0046] 접촉부(3)는 땜납 시스템으로 형성될 수 있고, 상기 땜납 시스템은 거울층(2)의 물질뿐만 아니라 아연, 인듐, 갈륨 또는 비스무트와 같은 적어도 하나의 저융점 땜납 물질을 포함한다. 거울층이 예를 들면 은으로 이루어지면, 접촉부(3)는 은-아연-땡납 또는 은-인듐 땜납을 포함하는 것이 바람직하다. 접촉층(2)이 금 소재이면, 접촉부(3)는 금-인듐 땜납을 포함하는 것이 바람직하다. 거울층(2)이 알루미늄 소재이면, 접촉부(3)는 알루미늄-갈륨 땜납을 포함하여 형성되는 것이 바람직하다. 접촉부(3)는 바람직하게는 반도체 몸체(1)를 향해 있는 측에서 차단층 및 부착 증진층을 포함할 수 있다.

[0047] 차단층은 예를 들면 Ni, Pd, Pt, Ti, TiW, TiN, TiW:N 중 적어도 하나의 물질을 포함하거나 적어도 하나의 물질로 이루어질 수 있다.

[0048] 부착 증진층은 예를 들면 Cr, Ni, Pd, Pt, Ti 중 적어도 하나의 물질을 포함하거나 적어도 하나의 물질로 이루어질 수 있다.

[0049] 땜납 물질에 대해 대안적으로, 접촉부(3)는 거울층(2)과 동일한 물질로 형성될 수 있다. 이 경우, 반도체 몸체(1) 및 거울층(2)은 열 압축을 이용하여 결합되는 것이 바람직하다.

[0050] 접촉부(3)는 반도체 몸체(1)와 거울층(2) 사이의 간격(D)을 조절한다. 이러한 간격(D)에 의해 반도체 몸체(1)와 거울층(2) 사이에 적어도 하나의 중공(4)이 발생한다. 상기 실시예에서, 정확히 하나의 중공(4)이

발생하며, 상기 중공에 수많은 접촉부(3)가 배치된다(이에 대하여 도 1b의 거울층(2) 상의 개략적 평면도 참조). 중공은 가스(40)로 채워지고, 본원에서는 공기로 채워진다. 이상적인 간격으로는, 적어도 100 nm과 최대 1500 nm인 간격, 바람직하게는 1000 nm의 간격임이 확인되었다.

[0051] 반도체칩은 캐리어(7)를 더 포함하고, 상기 캐리어 상에 거울층(2)이 적층되어 있다. 이때 캐리어(7)와 거울층(2) 사이에 차단층(6)이 배치될 수 있고, 상기 차단층은 거울층(2)으로부터 캐리어(7)로의 금속의 확산을 방지한다.

[0052] 캐리어(7)는 금속을 포함하거나 금속으로 구성될 수 있다. 예를 들면, 캐리어는 몰리브덴 필름으로 형성될 수 있다. 또한, 캐리어는 알루미늄산화물과 같은 세라믹 물질을 포함하거나 이러한 물질로 이루어질 수 있다. 마지막으로, 캐리어는 반도체 물질을 포함하거나 그러한 물질로 이루어질 수 있다. 예를 들면, 이를 위해 규소, 게르마늄, GaAs와 같은 물질이 제공된다.

[0053] 차단층(6)은 예를 들면 Ni, Pd, Pt, Ti, TiW, TiN, TiW:N 중 적어도 하나의 물질을 포함하거나 적어도 하나의 물질로 구성될 수 있다. 접촉부(3)는 캐리어(7)로부터 반도체 몸체(1)로 전기 전류를 안내할 뿐만 아니라 반도체 몸체(1)로부터 캐리어(7)로의 열류(heat flow)의 일부를 안내한다. 접촉점의 밀도 및 크기, 즉 접촉부(3)의 밀도 및 크기는 가능한 한 낮게 유지되어, 거울층(2)의 효과 및 중공(4)에서의 굴절률의 비약적 변화의 효과를 가능한 한 크게 유지하도록 한다. 이와 동시에, 접촉점의 밀도 및 크기가 충분히 커야 하는데, 그로 인하여 칩이 전기적 및 열적으로 부하력을 가지며 기계적으로 안정된다. 이때, 접촉부(3)의 크기, 즉 직경은 적어도 1  $\mu\text{m}$ 이고 최대 50  $\mu\text{m}$ 인 것이 유리한 것으로 확인되었다. 접촉부(3)의 밀도는 바람직하게는 0.5% 내지 50%라는 거울층(2)의 면 덮임율에 상응한다.

[0054] 접촉점은 예를 들면 규칙적 격자의 - 예를 들면 직사각형 격자 또는 삼각형 격자의 - 격자점에 배치될 수 있다. 접촉부(3)는 PVD, 인쇄 방법 또는 예비 성형된 미립자를 이용하여 거울층(2)과 반도체 몸체(1)사이에 삽입되거나 이러한 구성 요소들 상에 마련될 수 있다.

[0055] 접촉부(3)를 포함한 가스 거울을 다양한 식각 단계로부터 보호하기 위해, 공정 시간 동안 희생층을 삽입하는 것을 고려할 수 있다. 즉, 희생층이 칩의 측면에 제공되고, 상기 희생층은 칩의 추가 공정을 허용하되, 이때 접촉부(3)가 식각되지 않도록 허용된다. 이러한 희생층은 제조 방법의 종료 이후 제거될 수 있고, 예를 들면 음의 포토레지스트, 양의 포토레지스트, 규소질화물, 규소산화물 중 하나를 포함하거나 이 중 하나로 이루어질 수 있다.

[0056] 도 2a 및 2b를 참조하여, 본 명세서에 기술된 광전 반도체칩의 제2실시예가 더욱 상세하게 설명된다. 도 1a 및 1b와 관련하여 기술된 실시예에 대해 보완적으로, 상기 실시예에서는 패시베이션 물질(5)이 반도체 몸체(1)와 거울층(2) 사이에 위치한 중공의 둘레에 프레임형으로 배치된다. 패시베이션 물질(5)은 중공(4)을 밀봉식으로 닫는다. 이러한 방식으로, 공기외의 가스(40)가 중공(4)에 삽입될 수 있다. 예를 들면, 이를 위해 헬륨 또는 수소( $\text{H}_2$ )가 사용되고, 이러한 가스는 매우 높은 열 전도도를 특징으로 한다. 가스는 정상압보다 낮은 압력으로 반도체 몸체(1)와 거울층(2) 사이에 삽입될 수 있어서, 열 전도도가 더욱 증가한다. 예를 들면 패시베이션 물질(5)은 규소질화물, 규소산화물, 실리콘, 비스벤조사이클로부텐 중 하나의 물질을 포함하거나 그것으로 구성될 수 있다.

[0057] 도 3a 및 3b와 관련하여, 본 명세서에 기술된 광전 반도체칩의 제3실시예가 더욱 상세하게 설명된다. 이 실시예에서는, 도 1a 및 1b의 실시예와 달리 접촉부(3)가 폐쇄된 경로로서 형성된다. 이러한 접촉부(3)는 다른 접촉부(3)를 프레임형으로 둘러싼다. 폐쇄된 경로로서 형성된 접촉부(3)는 칩의 테두리 영역에 배치된다. 접촉부(3)는 전기적 및 광학적 특성 외에 반도체 몸체와 거울층 사이의 중공(4)을 밀봉하는 역할도 한다. 이러한 방식으로, 가스(40)는 정상압보다 낮은 압력으로 광전 반도체칩안에서 밀봉될 수 있다.

[0058] 이러한 프레임형 접촉층은, 거울층(2)의 면적이 큰 광전 반도체칩에 있어 매우 유리한 것으로 확인되었는데, 이때 테두리에서 발생하는 접촉부(3)에의 흡수 문제가 소형 칩에 비해 덜 중요하다. 폐쇄된 경로로서 형성된 접촉부(3)가 더 작은 크기의 칩에 사용되면, 은 소재로 형성되어 높은 반사도를 가지는 접촉부(3)가 마련된다. 이러한 방식으로, 폐쇄된 경로로서 형성된 접촉부(3)에서는 거의 흡수 순실이 발생하지 않는다. 큰 칩이란, 500  $\mu\text{m}$ 보다 큰 모서리 길이를 가지는 칩을 가리킨다. 작은 칩은 이보다 작은 것을 나타낸다.

[0059] 본 명세서에 기술된 반도체칩의 접촉은 서로 다른 방식으로 수행될 수 있다: 구조화된 상측 접촉 - 예를 들면 본딩 패드- 와 대면적의 하측 접촉이 사용될 수 있다. 또한, 2개의 구조화된 상측 접촉 - 예를 들면 2개의 본딩 패드 - 이 사용될 수 있다. 또한, 2개의 구조화된 하측 접촉이 사용될 수 있고 - 이 경우 반도체칩은 예를

들면 플립칩의 경우와 같이 실장되어 전기적으로 연결될 수 있다.

[0060] 본 발명은 실시예에 의거한 설명에 의하여 이러한 실시예에 한정되지 않는다. 오히려, 본 발명은 각 새로운 특징 및 특징들의 각 조합을 포함하고, 이러한 점은 특히, 비록 이러한 특징 또는 이러한 조합이 그 자체로 명백하게 특히 청구 범위 또는 실시예에 제공되지 않더라도 특히 청구 범위에서의 특징들의 각 조합을 포함한다.

[0061] 본 특허 출원은 독일 특허 출원 10 2008 039360.6의 우선권을 청구하고, 그 공개 내용은 참조로 포함된다.

## 도면

### 도면1a

### 도면1b

도면2a

도면2b

도면3a

도면3b