### (19) United States

### (12) Patent Application Publication (10) Pub. No.: US 2004/0147109 A1 Yau et al.

(43) Pub. Date:

Jul. 29, 2004

### (54) LOW DIELECTRIC CONSTANT FILM PRODUCED FROM SILICON COMPOUNDS COMPRISING SILICON-CARBON BOND

(75) Inventors: Wai-Fan Yau, Mountain View, CA (US); David Cheung, Foster City, CA (US); Shin-Puu Jeng, Cupertino, CA (US); Kuowei Liu, Santa Clara, CA

(US); Yung-Cheng Yu, San Jose, CA

(US)

Correspondence Address:

**Patent Counsel** APPLIED MATERIALS, INC. P.O. Box 450-A Santa Clara, CA 95052 (US)

(73) Assignee: Applied Materials, Inc.

(21)Appl. No.: 10/756,122

(22) Filed: Jan. 13, 2004

### Related U.S. Application Data

(60) Continuation of application No. 09/477,126, filed on Dec. 30, 1999, which is a division of application No. 09/021,788, filed on Feb. 11, 1998, now Pat. No. 6,054,379.

### **Publication Classification**

| (51) | Int. Cl. <sup>7</sup> | H01L | 21/4763   |

|------|-----------------------|------|-----------|

| (52) | U.S. Cl.              |      | . 438/623 |

#### (57)ABSTRACT

A method and apparatus for depositing a low dielectric constant film by reaction of an organo silane compound and an oxidizing gas. The oxidized organo silane film has excellent barrier properties for use as a liner or cap layer adjacent other dielectric layers. The oxidized organo silane film can also be used as an etch stop or an intermetal dielectric layer for fabricating dual damascene structures. The oxidized organo silane films also provide excellent adhesion between different dielectric layers. A preferred oxidized organo silane film is produced by reaction of methyl silane, CH<sub>3</sub>SiH<sub>3</sub>, and N<sub>2</sub>O.

Fig. 1A (PRIOR ART)

Fig. 1B (PRIOR ART)

FIG. 4

Fig. 6A

Fig. 6B

Fig. 6C

Fig. 6D

Fig. 6E

# LOW DIELECTRIC CONSTANT FILM PRODUCED FROM SILICON COMPOUNDS COMPRISING SILICON-CARBON BOND

## CROSS-REFERENCE TO RELATED APPLICATIONS

[0001] The present application is a continuation of pending U.S. patent application Ser. No. 09/477,126, filed Dec. 30, 1999, which is a continuation of U.S. patent application Ser. No. 09/021,788, filed Feb. 11, 1998, and now issued as U.S. Pat. No. 6,054,379. Furthermore, this application is related to all applications and patents claiming priority to Ser. No. 09/021,788.

#### BACKGROUND OF THE DISCLOSURE

[0002] 1. Field of the Invention

[0003] The present invention relates to the fabrication of integrated circuits. More particularly, the invention relates to a process and apparatus for depositing dielectric layers on a semiconductor substrate.

[0004] 2. Background of the Invention

[0005] One of the primary steps in the fabrication of modern semiconductor devices is the formation of metal and dielectric films on a semiconductor substrate by chemical reaction of gases. Such deposition processes are referred to as chemical vapor deposition or CVD. Conventional thermal CVD processes supply reactive gases to the substrate surface where heat-induced chemical reactions take place to produce a desired film. The high temperatures at which some thermal CVD processes operate can damage device structures having layers previously formed thereon. A preferred method of depositing metal and dielectric films at relatively low temperatures is plasma-enhanced CVD (PECVD) techniques such as described in U.S. Pat. No. 5,362,526. Plasmaenhanced CVD techniques promote excitation and/or disassociation of the reactant gases by the application of radio frequency (RF) energy to a reaction zone near the substrate surface, thereby creating a plasma of highly reactive species. The high reactivity of the released species reduces the energy required for a chemical reaction to take place, and thus lowers the required temperature for such PECVD processes.

[0006] Semiconductor device geometries have dramatically decreased in size since such devices were first introduced several decades ago. Since then, integrated circuits have generally followed the two-year, half-size rule (often called Moore's Law), which means that the number of devices that will fit on a chip doubles every two years. Today's wafer fabrication plants are routinely producing devices having 0.35  $\mu$ m and even 0.18  $\mu$ m feature sizes, and tomorrow's plants soon will be producing devices having even smaller geometries.

[0007] In order to further reduce the size of semiconductor devices on integrated circuits, it has become necessary to use conductive materials having low resistivity and insulators having low k (dielectric constant <4.0) to reduce the capacitive coupling between adjacent metal lines. For example, copper is now being considered as an interconnect material in place of aluminum because copper has a lower resistivity and higher current carrying capacity. However, these materials present new problems for integrated circuit manufac-

turing processes. For example, many low k dielectric materials are porous and are preferably protected by liner layers to prevent diffusion of metals. Conventional liner layers, such as SiN, have higher dielectric constants, and the combination of low k dielectric layers with high k dielectric liner layers may result in little or no improvement in the overall stack dielectric constant and capacitive coupling.

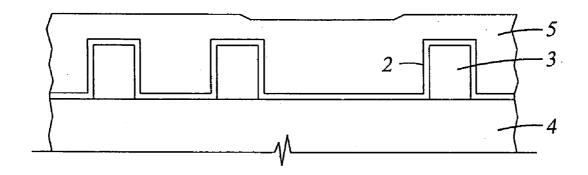

[0008] As shown in FIG. 1A, International Publication Number WO 94/01885 describes a PECVD process for depositing a multi-component dielectric layer wherein a silicon dioxide (SiO<sub>2</sub>) liner layer 2 is first deposited on a patterned metal layer having metal lines 3 formed on a substrate 4. The liner layer 2 is deposited by reaction of silane (SiH<sub>4</sub>) and nitrous oxide (N<sub>2</sub>O). A self-planarizing low k dielectric layer 5 is then deposited on the liner layer 2 by reaction of a silane compound and a peroxide compound. The liner layer 2 is an oxidized silane film that has excellent barrier properties when deposited in a manner which provides a dielectric constant of about 4.5. The dielectric constant of the oxidized silane film can be decreased to about 4.1 by altering process conditions in a manner that decreases barrier properties of the film.

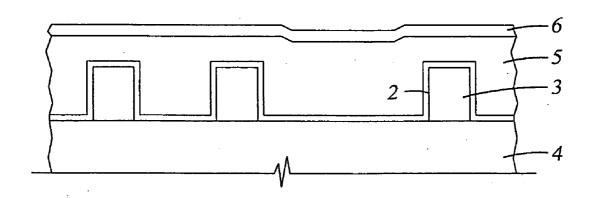

[0009] As shown in FIG. 1B, WO 94/01885 further describes an optional  $\mathrm{SiO}_2$  cap layer 6 that is deposited on the low k dielectric layer 5 by the reaction of silane and  $\mathrm{N}_2\mathrm{O}$ . The cap layer 6 is also an oxidized silane film that has excellent barrier properties when deposited in a manner which provides a dielectric constant of about 4.5. Both the liner layer 2 and the cap layer 6 have a dielectric constant greater than 4.0 and the high dielectric constant layers substantially detract from the benefit of the low k dielectric layer.

[0010] The benefit of some low k dielectric materials is further compromised by low oxide content which makes the material inadequate as an etch stop layer. Silicon nitride has been the etch stop material of choice for use with low k dielectric materials. However, the silicon nitride disposed between low k dielectric layers is within the fringing field between the interconnects. Silicon nitride has a relatively high dielectric constant (dielectric constant of about 7) compared to the surrounding dielectric, and it has been discovered that the silicon nitride may significantly increase the capacitive coupling between interconnect lines, even when an otherwise low k dielectric material is used as the primary insulator. This may lead to cross talk and/or resistance-capacitance (RC) delay which degrades the overall performance of the device.

[0011] As devices get smaller, liner layers, cap layers, and etch stop layers contribute more to the overall dielectric constant of pa multi-component dielectric layer. There remains a need for low k dielectric layers which have excellent barrier properties for use as liner or cap layers. There also remains a need for low k dielectric layers which have sufficient oxide content for use as etch stop layers. Ideally, the low k dielectric layers would be compatible with existing low k dielectric materials and could be deposited in the same chambers as existing low k dielectric materials.

### SUMMARY OF THE INVENTION

[0012] The present invention provides a method and apparatus for deposition of a low dielectric constant layer which is produced by oxidation of an organo silane compound

during plasma enhanced chemical vapor deposition. The oxidized organo silane layers have excellent barrier properties for use as a liner or cap layer adjacent other dielectric layers such as porous low k dielectric layers. In addition, the oxidized organo silane layers have can be used as an etch stop layer, as an adhesive layer between different layers, or as an intermetal dielectric layer. A preferred oxidized organ silane layer is produced by reaction of methyl silane, CH<sub>3</sub>SiH<sub>3</sub>, and nitrous oxide, N<sub>2</sub>O.

[0013] In a preferred embodiment, a low k dielectric layer is deposited on a patterned metal layer by reaction of an organo silane compound and an oxidizing compound. A self-planarizing dielectric layer is then deposited in the same chamber by reaction of an organo-silane compound and a peroxide bonding compound. The self-planarizing dielectric layer is optionally capped in the same chamber by further reaction of the organo silane compound and the oxidizing compound. The liner and cap layers provide strength to the self-planarizing dielectric layer during annealing of the self-planarizing dielectric layer. After annealing, the liner and cap layers serve as diffusion barriers which protect the self-planarizing dielectric layer.

[0014] The present invention further provides an etch stop material which provides a reliable dual damascene structure while minimizing the contribution of the etch stop layer to the capacitive coupling between interconnect lines. In a preferred embodiment, a low k dielectric film, such as an amorphous carbon ( $\alpha$ -C) or amorphous fluorinated carbon ( $\alpha$ -FC) film is used as the etch stop below an intermetal dielectric (IMD). Other low k materials, such as parylene, AF<sub>4</sub>, BCB, or PAE, or high k materials, such as oxynitride and silicon carbide, may also be used with the etch stop material.

[0015] A preferred etch stop process sequence comprises forming a dual damascene structure by depositing a first dielectric layer, such as parylene or a fluorinated silicate glass (FSG) layer, on a substrate, depositing the low k dielectric etch stop of the present invention on the first dielectric layer, patterning the etch stop to define the contacts/vias, depositing a second layer of a dielectric, patterning a resist layer on the second layer of dielectric to define one or more interconnects, and etching the interconnects and contacts/vias. The interconnects are etched down to the etch stop, and then the etching continues past the patterned etch stop to define the contacts/vias. Once the dual damascene structure has been formed, a barrier layer is preferably deposited conformably in the structure prior to filling the structure with copper to isolate the copper from other materials, such as silicon. The upper surface is then planarized using chemical mechanical polishing techniques.

[0016] The invention further provides an intermetal dielectric material comprising the low k dielectric film which is deposited on a conventional etch stop such as silicon oxide or silicon nitride. The low k dielectric film can also be deposited as a thin adhesive layer.

### BRIEF DESCRIPTION OF THE DRAWINGS

[0017] So that the manner in which the above recited features, advantages and objects of the present invention are attained and can be understood in detail, a more particular description of the invention, briefly summarized above, may

be had by reference to the embodiments thereof which are illustrated in the appended drawings.

[0018] It is to be noted, however, that the appended drawings illustrate only typical embodiments of this invention and are therefore not to be considered limiting of its scope, for the invention may admit to other equally effective embodiments.

[0019] FIGS. 1A-1B (Prior Art) are schematic diagrams of dielectric layers deposited on a substrate by the processes known in the art:

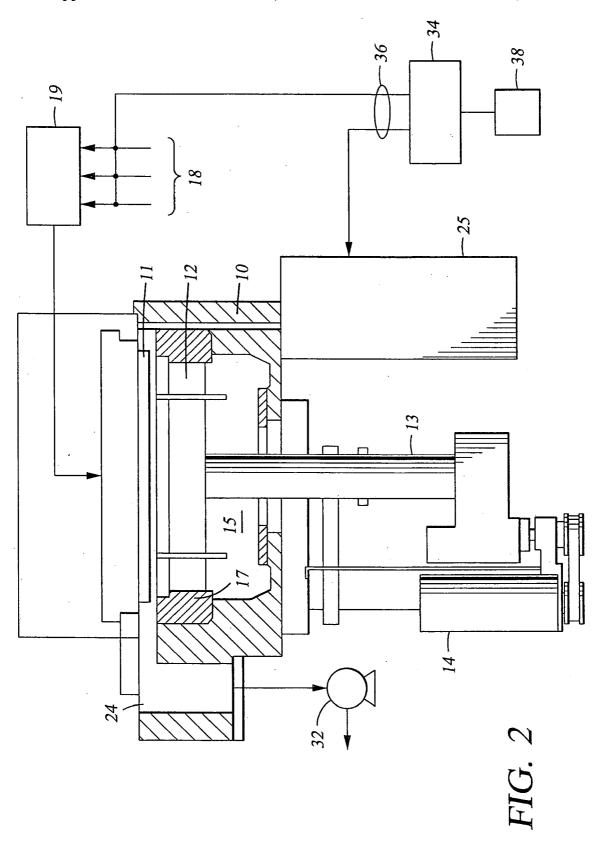

[0020] FIG. 2 is a cross-sectional diagram of an exemplary CVD plasma reactor configured for use according to the present invention;

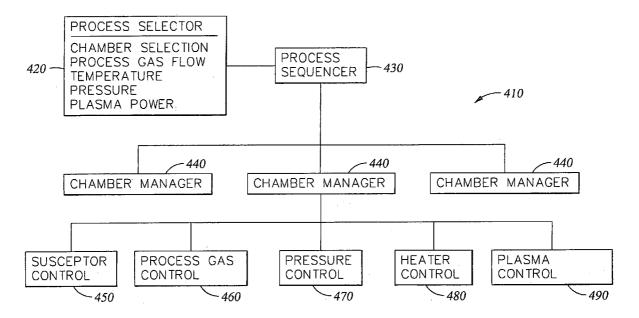

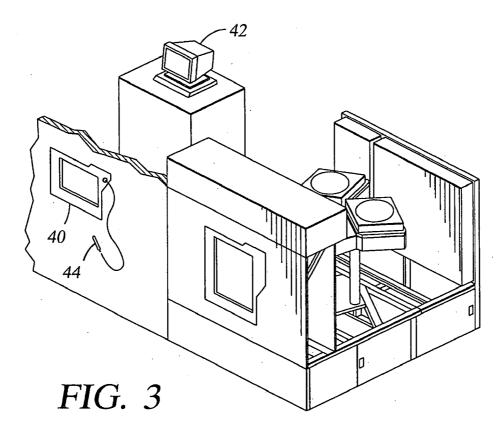

[0021] FIG. 3 is a diagram of the system monitor of the CVD plasma reactor of FIG. 2;

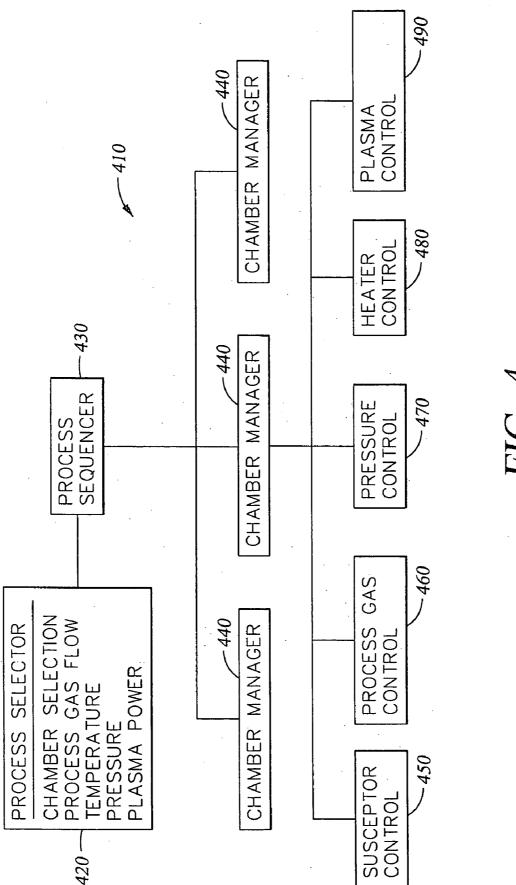

[0022] FIG. 4 is a flowchart of a process control computer program product used in conjunction with the exemplary CVD plasma reactor of FIG. 2;

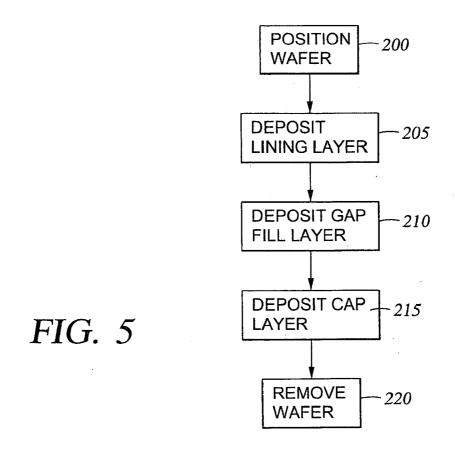

[0023] FIG. 5 is a flow chart illustrating steps undertaken in depositing liner and cap layers in a gap filling process according to one embodiment of the present invention;

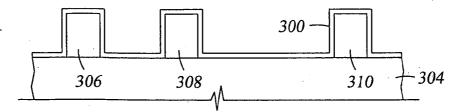

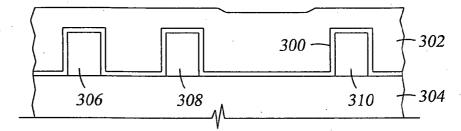

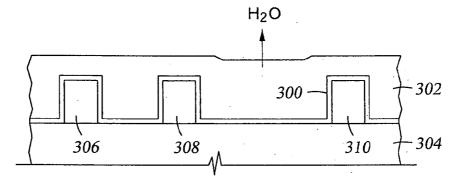

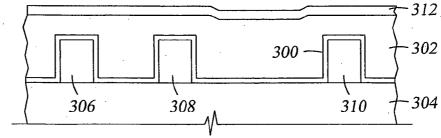

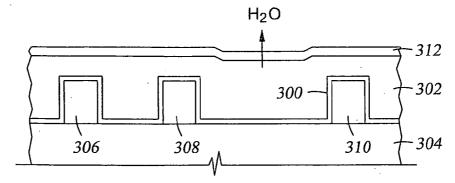

[0024] FIGS. 6A-6E is a schematic diagram of the layers deposited on a substrate by the process of FIG. 5;

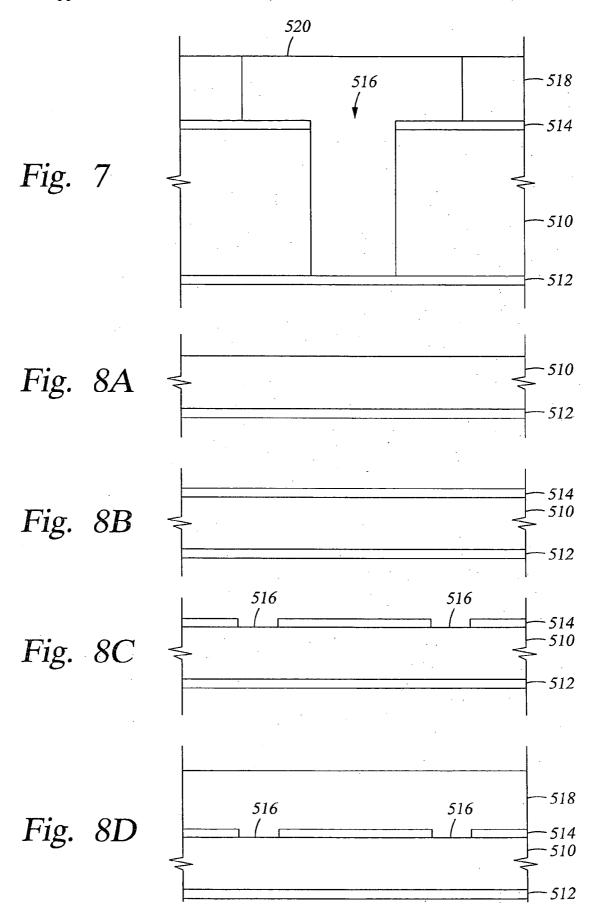

[0025] FIG. 7 is a cross sectional view showing a dual damascene structure comprising the low k dielectric layers of the present invention;

[0026] FIGS. 8A-8H are cross sectional views showing one embodiment of a dual damascene deposition sequence of the present invention;

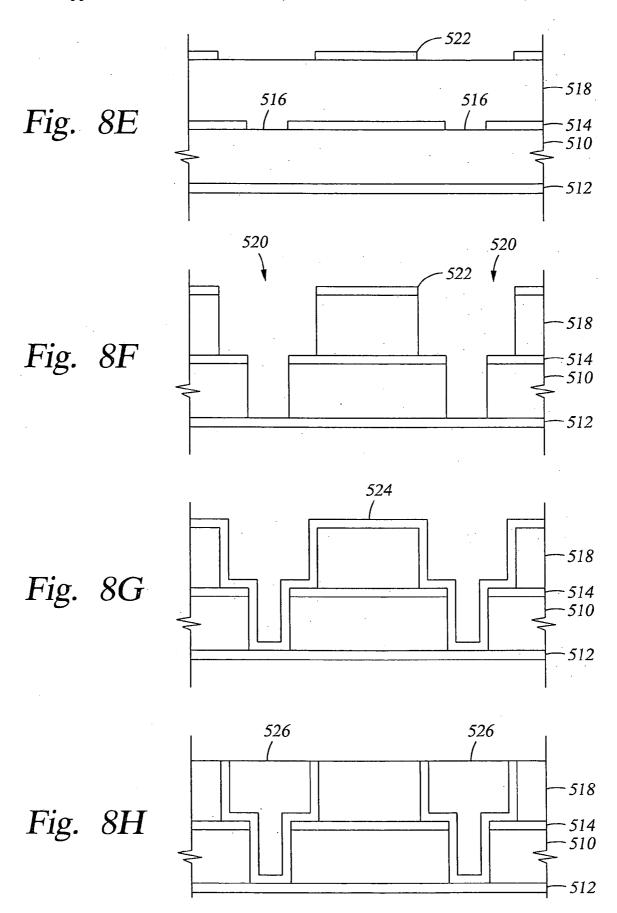

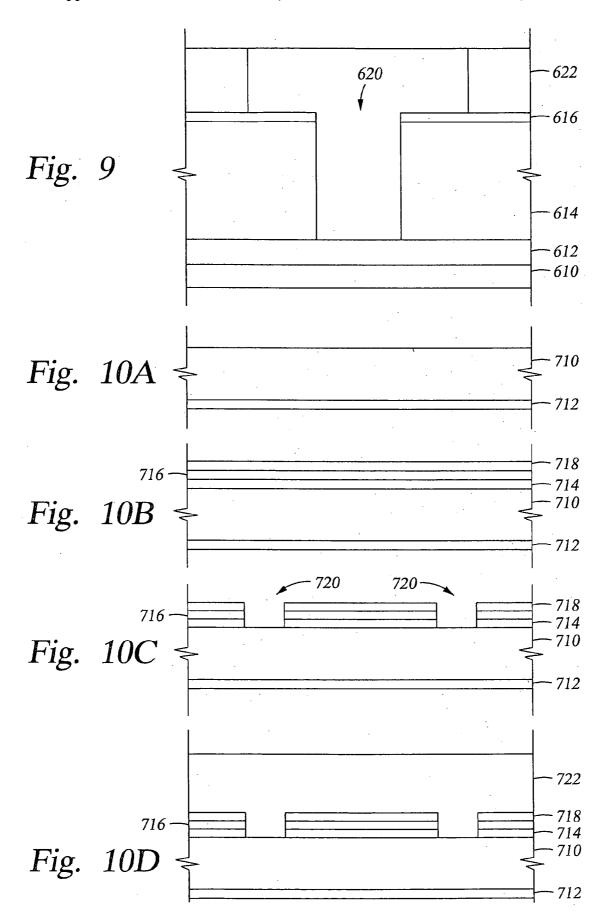

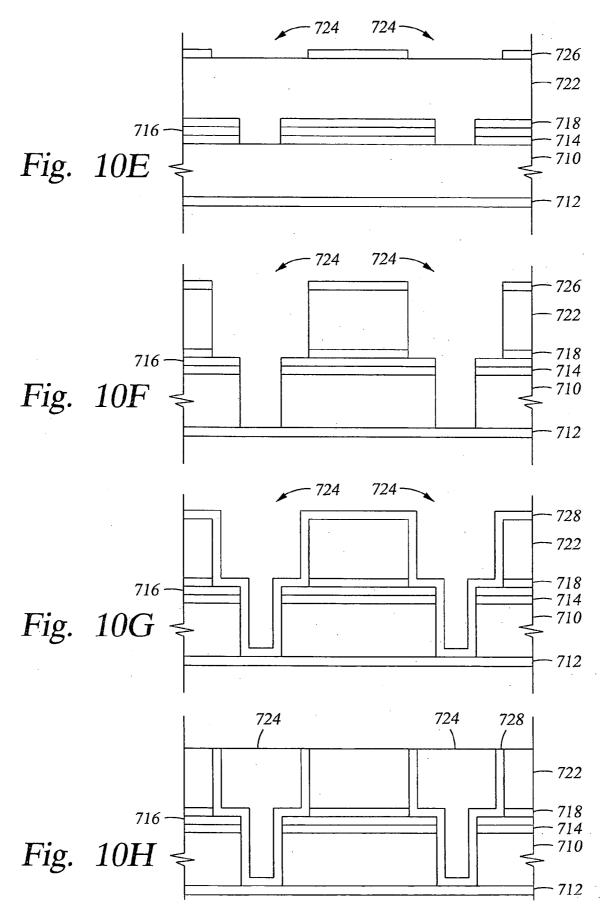

[0027] FIG. 9 is a cross sectional view showing an adhesive layer comprising the low k dielectric layers of the present invention between a premetal dielectric layer and an intermetal dielectric layer; and

[0028] FIGS. 10A-10H are cross sectional views showing a dual damascene deposition sequence wherein the low k dielectric film of the present invention is used to adhere an intermetal dielectric film to a conventional etch stop.

[0029] For a further understanding of the present invention, reference should be made to the ensuing detailed description.

# DESCRIPTION OF A PREFERRED EMBODIMENT

[0030] The present invention provides a method and apparatus for depositing a low dielectric constant layer which has excellent barrier properties and high oxide content. The low dielectric layer is an oxidized organo silane layer that can be used as a lining layer adjacent other dielectric materials, as an etch stop layer adjacent dielectric materials having lower oxide content, as an intermetal dielectric layer, and as an adhesion layer between different materials. The oxidized organo silane material is deposited by oxidation of an organo silane compound which does not fully oxidize. Carbon, including some organo functional groups, which remains in the oxidized organo silane layer contribute to low dielectric constants and excellent barrier properties.

[0031] The organo silane compounds generally include the structure:

[0032] wherein —C— is included in an organo group and some C-Si bonds are not broken during oxidation. Preferably —C— is included in an alkyl, such as methyl or ethyl, or an aryl, such as phenyl. Suitable organo groups also can include alkenyl and cyclohexenyl groups and functional derivatives. The preferred organo silane compounds have the structure  $SiH_a(CH_3)_b(C_2H_5)_c(C_6H_5)_d$ , where a=1 to 3, b=0 to 3, c=0 to 3, d=0 to 3, and a+b+c+d=4, or the structure  $Si_2H_e(CH_3)_f(C_2H_5)_g(C_2H_5)_g(C_6H_5)_h$ , where e=1 to 5, f=0 to 5, g=0 to 5, h=0 to 5, and e+f+g+h=6. Preferred organo silane compounds include methyl silane compounds having the structure  $SiH_n(CH_3)_{4-n}$ , where n=1 to 3, or the structure  $Si_2H_m(CH_3)_{6-m}$ , where m=1 to 5. The most preferred organo silane compound is methyl silane, CH<sub>3</sub>SiH<sub>3</sub>. The organo silane compounds are oxidized during deposition by reaction with oxygen (O<sub>2</sub>) or oxygen containing compounds such as nitrous oxide  $(N_2O)$ , preferably  $N_2O$ , such that the carbon content of the deposited film is from 1 to 50% by atomic weight, preferably about 20%. The oxidized organo silane layer has a dielectric constant of about 3.0 and has excellent barrier properties. The oxidized organo silane layers further have high oxide contents in comparison to conventional low k dielectric layers and good adhesion properties.

[0033] The present invention further provides a substrate processing system having a plasma reactor including a reaction zone, a substrate holder for positioning a substrate in the reaction zone, and a vacuum system. The processing system further comprises a gas/liquid distribution system connecting the reaction zone of the vacuum chamber to supplies of an organo silane compound, an oxidizing gas, and an inert gas, and an RF generator coupled to the gas distribution system for generating a plasma in the reaction zone. The processing system further comprises a controller comprising a computer for controlling the plasma reactor, the gas distribution system, and the RF generator, and a memory coupled to the controller, the memory comprising a computer usable medium comprising a computer readable program code for selecting the process steps of depositing a low dielectric constant film with a plasma of an organo silane compound and an oxidizing gas.

[0034] The processing system may further comprise in one embodiment computer readable program code for selecting the process steps of depositing a liner of the oxidized organo silane compound, depositing a different dielectric layer, and optionally depositing a capping layer of the oxidized organo silane compound.

[0035] Further description of the invention will be directed toward specific embodiments.

[0036] Exemplary CVD Plasma Reactor

[0037] One suitable CVD plasma reactor in which a method of the present invention can be carried out is shown in FIG. 2, which is a vertical, cross-section view of a parallel

plate chemical vapor deposition reactor 10 having a high vacuum region 15. Reactor 10 contains a gas distribution manifold 11 for dispersing process gases through perforated holes in the manifold to a substrate or wafer (not shown) that rests on a substrate support plate or susceptor 12 which is raised or lowered by a lift motor 14. A liquid injection system (not shown), such as typically used for liquid injection of TEOS, may also be provided for injecting a liquid organo silane compound. The preferred methyl silanes and ethyl silanes are gases.

[0038] The reactor 10 includes heating of the process gases and substrate, such as by resistive heating coils (not shown) or external lamps (not shown). Referring to FIG. 2, susceptor 12 is mounted on a support stem 13 so that susceptor 12 (and the wafer supported on the upper surface of susceptor 12) can be controllably moved between a lower loading/off-loading position and an upper processing position which is closely adjacent to manifold 11.

[0039] When susceptor 12 and the wafer are in processing position 14, they are surrounded by an insulator 17 and process gases exhaust into a manifold 24. During processing, gases inlet to manifold 11 are uniformly distributed radially across the surface of the wafer. A vacuum pump 32 having a throttle valve controls the exhaust rate of gases from the chamber.

[0040] Before reaching manifold 11, deposition and carrier gases are input through gas lines 18 into a mixing system 19 where they are combined and then sent to. manifold 11. Generally, the process gases supply lines 18 for each of the process gases include (i) safety shut-off valves (not shown) that can be used to automatically or manually shut off the flow of process gas into the chamber, and (ii) mass flow controllers (also not shown) that measure the flow of gas through the gas supply lines. When toxic gases are used in the process, several safety shut-off valves are positioned on each gas supply line in conventional configurations.

[0041] The deposition process performed in reactor 10 can be either a thermal process or a plasma enhanced process. In a plasma process, a controlled plasma is typically formed adjacent to the wafer by RF energy applied to distribution manifold 11 from RF power supply 25 (with susceptor 12 grounded). Alternatively, RF power can be provided to the susceptor 12 or the RF power can be split between different components. RF power supply 25 can supply either single or mixed frequency RF power to enhance the decomposition of reactive species introduced into the high vacuum region 15. A mixed frequency RF power supply typically supplies power at a high RF frequency (RF1) of 13.56 MHz and at a low RF frequency (RF2) of 360 KHz.

[0042] Typically, any or all of the chamber lining, gas inlet manifold faceplate, support stem 13, and various other reactor hardware is made out of material such as aluminum or anodized aluminum. An example of such a CVD reactor is described in U.S. Pat. No. 5,000,113, entitled "Thermal CVD/PECVD Reactor and Use for Thermal Chemical Vapor Deposition of Silicon Dioxide and In-situ Multi-step. Planarized Process," issued to Wang et al. And assigned to Applied Materials, Inc., the assignee of the present invention.

[0043] The lift motor 14 raises and lowers susceptor 12 between a processing position and a lower, wafer-loading

position. The motor, the gas mixing system 19, and the RF power supply 25 are controlled by a system controller 34 over control lines 36. The reactor includes analog assemblies, such as mass flow controllers (MFCs) and RF generators, that are controlled by the system controller 34 which executes system control software stored in a memory 38, which in the preferred embodiment is a hard disk drive. Motors and optical sensors are used to move and determine the position of movable mechanical assemblies such as the throttle valve of the vacuum pump 32 and motor for positioning the susceptor 12.

[0044] The system controller 34 controls all of the activities of the CVD reactor and a preferred embodiment of the controller 34 includes a hard disk drive, a floppy disk drive, and a card rack. The card rack contains a single board computer (SBC), analog and digital input/output boards, interface boards and stepper motor controller boards. The system controller conforms to the Versa Modular Europeans (VME) standard which defines board, card cage, and connector dimensions and types. The VME standard also defines the bus structure having a 16-bit data but and 24-bit address bus.

[0045] The system controller 34 operates under the control of a computer program stored on the hard disk drive 38. The computer program dictates the timing, mixture of gases, RF power levels, susceptor position, and other parameters of a particular process. The interface between a user and the system controller is via a CRT monitor 40 and light pen 44 which are depicted in FIG. 3. In the preferred embodiment a second monitor 42 is used, the first monitor 40 being mounted in the clean room wall for the operators and the other monitor 42 behind the wall for the service technicians. Both monitors 40, 42 simultaneously display the same information but only one light pen 44 is enabled. The light pen 44 detects light emitted by CRT display with a light sensor in the tip of the pen. To select a particular screen or function, the operator touches a designated area of the display screen and pushes the button on the pen 44. The touched area changes its highlighted color, or a new menu or screen is displayed, confirming communication between the light pen and the display screen.

[0046] Referring to FIG. 4, the process can be implemented using a computer program product 410 that runs on, for example, the system controller 34. The computer program code can be written in any conventional computer readable programming language such as for example 68000 assembly language, C, C++, or Pascal. Suitable program code is entered into a single file, or multiple files, using a conventional text editor, and stored or embodied in a computer usable medium, such as a memory system of the computer. If the entered code text is in a high level language, the code is compiled, and the resultant compiler code is then linked with an object code of precompiled windows library routines. To execute the linked compiled object code, the system user invokes the object code, causing the computer system to load the code in memory, from which the CPU reads and executes the code to perform the tasks identified in the program.

[0047] FIG. 4 shows an illustrative block diagram of the hierarchical control structure of the computer program 410. A user enters a process set number and process chamber number into a process selector subroutine 420 in response to

menus or screens displayed on the CRT monitor 40 by using the light pen 44 interface. The process sets are predetermined sets of process parameters necessary to carry out specified processes, and are identified by predefined set numbers. The process selector subroutine 420 the (i) selects a desired process chamber on a cluster tool such as an Centura™ platform (available from Applied Materials, Inc.), and (ii) selects a desired set of process parameters needed to operate the process chamber for performing the desired process. The process parameters for performing a specific process relate to process conditions such as, for example, process gas composition and flow rates, temperature, pressure, plasma conditions such as RF bias power levels and magnetic field power levels, cooling gas pressure, and chamber wall temperature and are provided to the user in the form of a recipe. The parameters specified by the recipe are entered utilizing the light pen/CRT monitor interface.

[0048] The signals for monitoring the process are provided by the analog input and digital input boards of system controller and the signals for controlling the process are output on the analog output and digital output boards of the system controller 34.

[0049] A process sequencer subroutine 430 comprises program code for accepting the identified process chamber and set of process parameters from the process selector subroutine 420, and for controlling operation of the various process chambers. Multiple users can enter process set numbers and process chamber numbers, or a user can enter multiple process chamber numbers, so the sequencer subroutine 430 operates to schedule the selected processes in the desired sequence. Preferably the sequencer subroutine 430 includes computer readable program code to perform the steps of (i) monitoring the operation of the process chambers to determine if the chambers are being used, (ii) determining what processes are being carried out in the chambers being used, and (iii) executing the desired process based on availability of a process chamber and type of process to be carried out. Conventional methods of monitoring the process chambers can be used, such as polling. When scheduling which process is to be executed, the sequencer subroutine 430 can be designed to take into consideration the present condition of the process chamber being used in comparison with the desired process conditions for a selected process, or the age of each particular user entered request, or any other relevant factor a system programmer desires to include for determining the scheduling priorities.

[0050] Once the sequencer subroutine 430 determines which process chamber and process set combination is going to be executed next, the sequencer subroutine 430 causes execution of the process set by passing the particular process set parameters to a chamber manager subroutine 440 which controls multiple processing tasks in a process chamber 10 according to the process set determined by the sequencer subroutine 430. For example, the chamber manager subroutine 440 comprises program code for controlling CVD process operations in the process chamber 10. The chamber manager subroutine 440 also controls execution of various chamber component subroutines which control operation of the chamber component necessary to carry out the selected process set. Examples of chamber component subroutines are susceptor control subroutine 450, process gas control subroutine 460, pressure control subroutine 470, heater control subroutine **480**, and plasma control subroutine **490**. Those having ordinary skill in the art would readily recognize that other chamber control subroutines can be included depending on what processes are desired to be performed in the reactor **10**.

[0051] In operation, the chamber manager subroutine 440 selectively schedules or. calls the process component subroutines in accordance with the particular process set being executed. The chamber manager subroutine 440 schedules the process component subroutines similarly to how the sequencer subroutine 430 schedules which process chamber 10 and process set is to be executed next. Typically, the chamber manager subroutine 440 includes steps of monitoring the various chamber components, determining which components needs to be operated based on the process parameters for the process set to be executed, and causing execution of a chamber component subroutine responsive to the monitoring and determining steps.

[0052] Operation of particular chamber components subroutines will now be described with reference to FIG. 4. The susceptor control positioning subroutine 450 comprises program code for controlling chamber components that are used to load the substrate onto the susceptor 12, and optionally to lift the substrate to a desired height in the reactor 10 to control the spacing between the substrate and the gas distribution manifold 11. When a substrate is loaded into the reactor 10, the susceptor 12 is lowered to receive the substrate, and thereafter, the susceptor 12 is raised to the desired height in the chamber, to maintain the substrate at a first distance or spacing from the gas distribution manifold 11 during the CVD process. In operation, the susceptor control subroutine 450 controls movement of the susceptor 12 in response to process set parameters that are transferred from the chamber manager subroutine 440.

[0053] The process gas control subroutine 460 has program code for controlling process gas composition and flow rates. The process gas control subroutine 460 controls the open/close position of the safety shut-off valves, and also ramps up/down the mass flow controllers to obtain the desired gas flow rate. The process gas control subroutine 460 is invoked by the chamber manager subroutine 440, as are all chamber components subroutines, and receives from the chamber manager subroutine process parameters related to the desired gas flow rates. Typically, the process gas control subroutine 460 operates by opening the gas supply lines, and repeatedly (i) reading the necessary mass flow controllers, (ii) comparing the readings to the desired flow rates received from the chamber manager subroutine 440, and (iii) adjusting the flow rates of the gas supply lines as necessary. Furthermore, the process gas control subroutine 460 includes steps for monitoring the gas flow rates for unsafe rates, and activating the safety shut-off valves when an unsafe condition is detected.

[0054] In some processes, an inert gas such as helium or argon is flowed into the reactor 10 to stabilize the pressure in the chamber before reactive process gases are introduced into the chamber. For these processes, the process gas control subroutine 460 is programmed to include steps for flowing the inert gas into the chamber 10 for an amount of time necessary to stabilize the pressure in the chamber, and then the steps described above would be carried out. Additionally, when a process gas it to be vaporized from a liquid

precursor, for example phenyl silane, the process gas control subroutine 460 would be written to include steps for bubbling a delivery gas such as helium through the liquid precursor in a bubbler assembly. For this type of process, the process gas control subroutine 460 regulates the flow of the delivery gas, the pressure in the bubbler, and the bubbler temperature in order to obtain the desired process gas flow rates. As discussed above, the desired process gas flow rates are transferred to the process gas control subroutine 460 as process parameters. Furthermore, the process gas control subroutine 460 includes steps for obtaining the necessary delivery gas flow rate, bubbler pressure, and bubbler temperature for the desired process gas flow rate by accessing a stored table containing the necessary values for a given process gas flow rate. Once the necessary values are obtained, the delivery gas flow rate, bubbler pressure and bubbler temperature are monitored, compared to the necessary values and adjusted accordingly.

[0055] The pressure control subroutine 470 comprises program code for controlling the pressure in the reactor 10 by regulating the size of the opening of the throttle valve in the exhaust pump 32. The size of the opening of the throttle valve is set to control the chamber pressure to the desired level in relation to the total process gas flow, size of the process chamber, and pumping set point pressure for the exhaust pump 32. When the pressure control subroutine 470 is invoked, the desired, or target pressure level is received as a parameter from the chamber manager subroutine 440. The pressure control subroutine 470 operates to measure the. pressure in the reactor 10 by reading one or more conventional pressure manometers connected to the chamber, compare the measure value(s) to the target pressure, obtain PID (proportional, integral, and differential) values from a stored pressure table corresponding to the target pressure, and adjust the throttle valve according to the PID values obtained from the pressure table. Alternatively, the pressure control subroutine 470 can be written to open or close the throttle valve to a particular opening size to regulate the reactor 10 to the desired pressure.

[0056] The heater control subroutine 480 comprises program code for controlling the temperature of the heat modules or radiated heat that is used to heat the susceptor 12. The heater control subroutine 480 is also invoked by the chamber manager subroutine 440 and receives a target, or set point, temperature parameter. The heater control subroutine 480 measures the temperature by measuring voltage output of a thermocouple located in a susceptor 12, compares the measured temperature to the set point temperature, and increases or decreases current applied to the heat module to obtain the set point temperature. The temperature is obtained from the measured voltage by looking up the corresponding temperature in a stored conversion table, or by calculating the temperature using a fourth order polynomial. The heater control subroutine 480 gradually controls a ramp up/down of current applied to the heat module. The gradual ramp up/down increases the life and reliability of the heat module. Additionally, a built-in-fail-safe mode can be included to detect process safety compliance, and can shut down operation of the heat module if the reactor 10 is not properly set up.

[0057] The plasma control subroutine 490 comprises program code for setting the RF bias voltage power level applied to the process electrodes in the reactor 10, and

optionally, to set the level of the magnetic field generated in the reactor. Similar to the previously described chamber component subroutines, the plasma control subroutine 490 is invoked by the chamber manager subroutine 440.

[0058] The above CVD system description is mainly for illustrative purposes, and other plasma CVD equipment such as electrode cyclotron resonance (ECR) plasma CVD devices, induction-coupled RF high density plasma CVD devices, or the like may be employed. Additionally, variations of the above described system such as variations in susceptor design, heater design, location of RF power connections and others are possible. For example, the wafer could be supported and heated by a resistively heated susceptor. The pretreatment and method for forming a pretreated layer of the present invention is not limited to any specific apparatus or to any specific plasma excitation method.

[0059] Deposition of the Oxidized Organo Silane Dielectric in a Three-Layer Gap Filling Process

[0060] The oxidized organo silane layer of the present invention can be used in a three-layer gap filling process as shown in FIG. 5 using the PECVD chamber of FIG. 2. Referring to FIG. 5, a wafer is positioned 200 in the reactor 10 and an oxidized organo silane layer having a low dielectric constant is deposited 205 by a PECVD process from a plasma comprising an organo silane compound, such as methyl silanes, ethyl silanes, or phenyl silanes, and an oxidizing gas. The deposition step 205 can include a capacitively coupled plasma or both an inductively and a capacitively coupled plasma in the process chamber 15 according to methods known in the art. An inert gas such as helium is commonly used in the PECVD deposition to assist in plasma generation. A gap fill layer is then deposited 210 on the liner layer by known methods. The gap fill layer is preferably self-planarizing, such as spin-on polymers or porous oxides deposited in liquid form by reaction of methyl silane and hydrogen peroxide. A cap layer is then deposited 215 on the gap fill layer, preferably using the same process for depositing the lining layer. The wafer is then removed 220 from the reactor 10.

[0061] Referring to FIGS. 6A-6E, the three-layer gap filling process provides a PECVD lining layer 300 of the oxidized organo silane polymer. The lining layer 300 acts as an isolation layer between a subsequent PECVD gap fill layer 302 and the underlying substrate surface 304 and metal lines 306, 308, 310 formed on the substrate surface. The gap fill layer 302 is capped by a PECVD capping layer 312 of the oxidized organo silane polymer. This process is implemented and controlled using a computer program stored in the memory 38 of a computer controller 34 for a CVD reactor 10.

[0062] Referring to FIG. 6A, the PECVD lining layer 300 is deposited in the reactor 10 by introducing an organo silane compound such as  $CH_3SiH_3$ , an oxidizing gas such as  $N_2O$ , and a carrier gas such as helium. The substrate is maintained at a temperature of from about -10 to about  $450^{\circ}$  C., and preferably is maintained at a temperature of approximately  $0^{\circ}$  C. throughout the deposition of the PECVD lining layer. The PECVD lining layer 300 is deposited with a process gas that includes a mixture of the organo silane compound at a flow rate of about 5 sccm to about 500 sccm and the oxidizing gas at a flow rate of about 5 sccm to about 2000

sccm. The process gases are carried by an inert gas such He, Ar, Ne, or a relatively inert gas such as nitrogen, which are typically not incorporated into the film, at a flow rate of from about 0.2 to about 20 lpm. The process gases react at a pressure from about 0.2 to about 20 Torr to form a conformal polymer layer on the substrate surface 304 and metal lines 306, 308, 310, on the substrate surface. The reaction is plasma enhanced with a power density ranging from 0.05 W/cm² to 1000 W/cm², preferably about 0.3 W/cm.

[0063] For an 8" single wafer chamber, the high frequency RF source of approximately 13.56 MHz is preferably driven at about 30 to about 500 W and a low frequency RF source of about 350 KHz to MHz is preferably driven at about 0 to about 500 W. In a currently preferred embodiment, the high frequency RF source is driven at about 50-150 W, while the low frequency RF source is driven at about 0-100 W.

[0064] The above process conditions result in the deposition of a PECVD lining layer 300 (at about 2000 Å per minute) with improved barrier characteristics for the subsequent deposition of the PECVD gap filling layer 302.

[0065] Referring to FIG. 6B, the PECVD gap filling layer 302 is deposited using similar reactor conditions as used for depositing the liner layer 300. The process gases for the gap filling layer 302 are preferably SiH<sub>4</sub>, or CH<sub>3</sub>SiH<sub>3</sub>, and 50 wt % of hydrogen peroxide (H<sub>2</sub>O<sub>2</sub>) which is vaporized and mixed with an inert carrier gas, such as helium. However, the gap filling layer can be any dielectric layer which has an acceptable dielectric constant. The process gas flows range from 0-2000 sccm for He, 10-200 sccm for CH<sub>3</sub>SiH<sub>3</sub>, and 0.1 to 3 g/min. for H<sub>2</sub>O<sub>2</sub>. The preferred gas flows range from 100-500 sccm for He, 20-100 sccm for CH<sub>3</sub>SiH<sub>3</sub>, and 0.1 to 1 g/min. for H<sub>2</sub>O<sub>2</sub>. These flow rates are given for a chamber having a volume of approximately 5.5 to 6.5 liters. Preferably, reactor 10 is maintained at a pressure of about 0.2 to about 5 torr during deposition of the PECVD gap filling layer 302. The gap filling layer 302 may be partially cured as shown in FIG. 6C to remove solvents such as water prior to deposition of a cap layer 312 as shown in FIG. 6D. Curing is done in the reactor 10 by pumping under an inert gas atmosphere under 10 Torr.

[0066] Referring to FIG. 6D, after deposition of the PECVD gap filling layer 302, the reactor 10 optionally resumes deposition of the oxidized organo silane layer of the present invention for deposition of a capping layer 312. Referring to FIG. 6E, after deposition of the capping layer, if any, the gap fill layer 302 is preferably annealed in a furnace or another chamber at a temperature from about 100 to about 450° C. to drive off remaining solvent such as water. Of course, processing conditions will vary according to the desired characteristics of the deposited films.

[0067] Deposition of a Dual Damascene Structure

[0068] A dual damascene structure which includes an oxidized organo silane layers as an etch stop or as an intermetal dielectric layer is shown in FIG. 7. When the oxidized organo silane is used as an etch stop, a first dielectric layer 510 is deposited on a substrate 512 and then the oxidized organo silane etch stop 514 is deposited on the first dielectric layer. The etch stop is then pattern etched to define the openings of the contacts/vias 516. A second dielectric layer 518 is then deposited over the patterned etch stop and then pattern etched by conventional methods to

define the interconnect lines **520**. A single etch process is then performed to define the interconnects down to the etch stop and to etch the unprotected dielectric exposed by the patterned etch stop to define the contacts/vias.

[0069] Referring again to FIG. 7, the damascene structure alternatively includes the oxidized organo silane as an intermetal dielectric. A first dielectric layer 510, preferably consisting of the oxidized organo silane, is deposited on a substrate 512 and then a conventional silicon oxide or silicon nitride etch stop 514 is deposited on the first dielectric layer. The etch stop is then patterned to define the openings of the contacts/vias 516. A second dielectric layer 518, consisting of the oxidized organo silane, is then deposited over the patterned etch stop and then patterned to define the interconnect lines 520. A single etch process is then performed to define the interconnects down to the etch stop and to etch the unprotected dielectric exposed by the patterned etch stop to define the contacts/vias.

[0070] A preferred dual damascene structure fabricated in accordance with the invention includes a lining layer as shown in FIG. 8H, and the method of making the structure is sequentially depicted schematically in FIGS. 8A-8H, which are cross sectional views of a substrate having the steps of the invention formed thereon.

[0071] As shown in FIG. 8A, an initial first dielectric layer 510, such as parylene, FSG, silicon oxide, or the like, is deposited on the substrate 512 to a thickness of about 5,000 to about 10,000 Å, depending on the size of the structure to be fabricated. As shown in FIG. 8B, the low k etch stop 514, which is the oxidized organo silane layer, is then deposited on the first dielectric layer to a thickness of about 200 to about 1000 Å. Low k etch stop 514 is then pattern etched to define the contact/via openings 516 and to expose first dielectric layer 510 in the areas where the contacts/vias are to be formed as shown in FIG. 8C. Preferably, low k etch stop 514 is pattern etched using conventional photolithography and etch processes using fluorine, carbon, and oxygen ions. After low k etch stop 514 has been etched to pattern the contacts/vias and the photo resist has been removed, a second dielectric layer 518 is deposited over etch stop 514 to a thickness of about 5,000 to about 10,000 Å as shown in FIG. 8D. A second dielectric layer 518 is then patterned to define interconnect lines 520, preferably using conventional photolithography processes with a photo resist layer 522 as shown in FIG. 8E. The interconnects and contacts/vias are then etched using reactive ion etching or other anisotropic etching techniques to define the metallization structure (i.e., the interconnect and contact/via) as shown in FIG. 8F. Any photo resist or other material used to pattern the etch stop 514 or the second dielectric layer 518 is removed using an oxygen strip or other suitable process.

[0072] The metallization structure is then formed with a conductive material such as aluminum, copper, tungsten or combinations thereof. Presently, the trend is to use copper to form the smaller features due to the low resistivity of copper (1.7  $\mu\Omega$ -cm compared to 3.1  $\mu\Omega$ -cm for aluminum). Preferably, as shown in FIG. 8G, a barrier layer 524 of the oxidized organo silane material, or other suitable barrier is first deposited conformally in the metallization pattern to prevent copper migration into the surrounding silicon and/or dielectric material. Thereafter, copper is deposited using

either chemical vapor deposition, physical vapor deposition, electroplating, or combinations thereof to form the conductive structure. Once the structure has been filled with copper or other metal, the surface is planarized using chemical mechanical polishing, as shown in **FIG. 8H**.

[0073] Deposition of Adhesive Layers

[0074] A dual damascene structure which includes an oxidized organo silane layer as an adhesive layer between a premetal dielectric layer and an intermetal dielectric layer is shown in FIG. 9. The oxidized organo silane adhesive layer 612 is deposited on a premetal dielectric layer 610 such as a conventional PSG or BPSG layer. An intermetal dielectric layer 614, preferably a low k dielectric polymer layer, is then deposited over the adhesive layer 612. A conventional silicon oxide or silicon nitride etch stop 616 and then patterned by conventional methods to define vias 620. A second intermetal dielectric layer 622, preferably the low k dielectric polymer, is then deposited over the patterned etch stop and then patterned to define the interconnect lines. A single etch process is then performed to define the interconnects down to the etch stop and to etch the unprotected dielectric exposed by the patterned etch stop to define the contacts/vias prior to metallization.

[0075] A preferred dual damascene structure comprising an adhesive layer in accordance with the invention is shown in FIG. 10H, and the method of making the structure is sequentially depicted schematically in FIGS. 10A-10H, which are cross sectional views of a substrate having the steps of the invention formed thereon.

[0076] As shown in FIG. 10A, an initial first intermetal dielectric layer 710, such as. parylene, FSG, silicon oxide, or the like, is deposited on a substrate 712 to a thickness of about 5,000 to about 10,000 Å, depending on the size of the structure to be fabricated. As shown in FIG. 10B, a low k adhesive layer 714, which is the oxidized organo silane layer, is then deposited on the first intermetal dielectric layer 710 to a thickness of about 50 to about 200 Å. A conventional silicon oxide or silicon nitride etch stop 716 is the deposited on the adhesive layer 714 to a thickness of about 50 to about 200 Å. A second low k adhesive layer 718, which is the oxidized organo silane layer, is then deposited on the etch stop 716 to a thickness of about 50 to about 200 Å. The etch stop 716 and adhesive layers 714, 718 are then pattern etched to define the contact/via openings 720 and to expose first intermetal dielectric layer 710 in the areas where the contacts/vias are to be formed as shown in FIG. 10C. Preferably, the etch stop 716 is pattern etched using conventional photolithography and etch processes using fluorine, carbon, and oxygen ions. After the etch stop 716 and adhesive layers 714, 718 have been etched to pattern the contacts/vias and the photo resist has been removed, a second intermetal dielectric layer 722 is deposited over second adhesive layer 718 to a thickness of about 5,000 to about 10,000 Å as shown in FIG. 10D. The second intermetal dielectric layer 722 is then patterned to define interconnect lines 724, preferably using conventional photolithography processes with a photo resist layer 726 as shown in FIG. 10E. The interconnects and contacts/vias are then etched using reactive ion etching or other anisotropic etching techniques to define the metallization structure (i.e., the interconnect and contact/via) as shown in FIG. 10F. Any photo resist or other material used to pattern the etch stop

716 or the second intermetal dielectric layer 722 is removed using an oxygen strip or other suitable process.

[0077] The metallization structure is then formed with a conductive material such as aluminum, copper, tungsten or combinations thereof. Presently, the trend is to use copper to form the smaller features due to the low resistivity of copper (1.7  $\mu\Omega$ -cm compared to 3.1  $\mu\Omega$ -cm for aluminum). Preferably, as shown in FIG. 10G, a barrier layer 728 of the oxidized organo silane material, or other suitable barrier is first deposited conformally in the metallization pattern to prevent copper migration into the surrounding silicon and/or dielectric material. Thereafter, copper is deposited using either chemical vapor deposition, physical vapor deposition, electroplating, or combinations thereof to form the conductive structure. Once the structure has been filled with copper or other metal, the surface is planarized using chemical mechanical polishing, as shown in FIG. 10H.

[0078] The invention is further described by the following example of a deposited methyl silane film.

### **EXAMPLE**

[0079] The following example demonstrates deposition of an oxidized organo silane film having excellent barrier and adhesion properties. This example was undertaken using a chemical vapor deposition chamber, and in particular, a CENTURA DxZTM system which includes a solid-state RF matching unit with a two-piece quartz process kit, both fabricated and sold by Applied Materials, Inc., Santa Clara, Calif.

[0080] An oxidized methyl silane film was deposited at a chamber pressure of 3.0 Torr and temperature of 0° C. from reactive gases which were flown into the reactor as follows:

Methyl silane, CH<sub>3</sub>SiH<sub>3</sub>, at 55 sccm Nitrous oxide, N<sub>2</sub>O, at 300 sccm Helium, He, at 4000 sccm.

[0081] The substrate was positioned 600 mil from the gas distribution showerhead and 80 W of high frequency power (13 MHz) was applied to the showerhead for plasma enhanced deposition of an oxidized methyl silane layer.

[0082] The oxidized methyl silane material was deposited at a rate of 1800 Å. The deposited film had a dielectric constant of 3.0and a refractive index of 1.44. The film had a measured tensile stress of  $0.8 \times 109$  dynes/cm<sup>2</sup>.

[0083] While the foregoing is directed to a preferred embodiment of the present invention, other and further embodiments of the invention may be devised without departing from the basic scope thereof, and the scope thereof is determined by the claims which follow.

### What is claimed is:

1. A method comprising depositing on a substrate a plurality of layers, wherein one or more of the layers is a low dielectric constant oxidized organosilane layer comprising carbon, wherein the carbon content of the low dielectric constant oxidized organosilane layer is from 1% to 50% by atomic weight, and a top layer of the plurality of layers is a photoresist.

2. The method of claim 1, wherein the low dielectric constant oxidized organosilane layer is deposited in the presence of RF power from a mixture comprising an organosilane compound including the structure:

- 3. The method of claim 2, wherein the organosilane compound is methylsilane.

- 4. The method of claim 2, wherein the mixture further comprises an oxidizing gas.

- 5. The method of claim 4, wherein the oxidizing gas is  $N_2\mathrm{O}$ .

- **6.** The method of claim 2, wherein the organosilane compound includes the  $SiH_a(CH_3)_b(C_2H_5)_e(C_6H_5)_d$ , where a=1 to 3, b=0 to 3, c=0 to 3, d=0 to 3, and a+b+c+d=4, or the structure  $Si_2H_e(CH_3)_f(C_2H_5)_g(C_2H_5)_g(C_6H_5)_h$ , where e=1 to 5, f=0 to 5, g=0 to 5, h=0 to 5, and e+f+g+h=6.

- 7. The method of claim 1, wherein the low dielectric constant oxidized organosilane layer is deposited in the presence of RF power from a mixture comprising an organosilane compound comprising an organo group selected from the group consisting of alkyl, aryl, alkenyl, and cyclohexenyl groups.

- 8. The method of claim 1, further comprising etching the low dielectric constant oxidized organosilane layer using fluorine, carbon, and oxygen ions.

- 9. The method of claim 1, further comprising etching a pattern in the plurality of the layers.

- 10. The method of claim 1, wherein the dielectric constant of the low dielectric constant oxidized organosilane layer is about 3.0.

- 11. A method comprising depositing on a substrate a plurality of layers, wherein the plurality of layers comprises one low dielectric constant oxidized organosilane etch stop layer comprising carbon, wherein the carbon content of the low dielectric constant oxidized organosilane layer is from 1% to 50% by atomic weight, a layer selected from the group consisting of parylene, FSG, and silicon oxide layers, and a top layer of the plurality of layers that is a photoresist.

- 12. The method of claim 11, wherein the low dielectric constant oxidized organosilane etch stop layer is between two dielectric layers in the plurality of layers.

- 13. The method of claim 11, wherein the low dielectric constant oxidized organosilane etch stop layer is deposited in the presence of RF power from a mixture comprising an organosilane compound including the structure:

- 14. The method of claim 13, wherein the mixture further comprises an oxidizing gas.

- 15. A method comprising depositing on a substrate a plurality of layers, wherein two of the layers are low dielectric constant oxidized organosilane layers comprising carbon, wherein the carbon content of the low dielectric

constant oxidized organosilane layer is from 1% to 50% by atomic weight, and a top layer of the plurality of layers is a photoresist.

- 16. The method of claim 15, wherein the plurality of layers further comprises a layer selected from the group consisting of parylene, FSG, silicon oxide, and silicon nitride layers.

- 17. The method of claim 15, wherein the plurality of layers comprises an etch stop layer adjacent both of the two low dielectric constant oxidized organosilane layers.

- **18**. The method of claim 17, wherein the etch stop layer is a silicon oxide or silicon nitride layer.

- 19. The method of claim 15, where in the low dielectric constant oxidized organosilane layers are deposited in the

presence of RF power from a mixture comprising an organosilane compound including the structure:

**20**. The method of claim 19, wherein the mixture further comprises an oxidizing gas.

\* \* \* \* \*