(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6261122号

(P6261122)

(45) 発行日 平成30年1月17日(2018.1.17)

(24) 登録日 平成29年12月22日(2017.12.22)

(51) Int.Cl.

F 1

H01L 21/336 (2006.01)

H01L 29/78 301D

H01L 29/78 (2006.01)

H01L 29/78 301W

H01L 29/06 (2006.01)

H01L 29/06 301F

H01L 29/06 301D

請求項の数 19 (全 24 頁)

(21) 出願番号

特願2014-9652 (P2014-9652)

(22) 出願日

平成26年1月22日(2014.1.22)

(65) 公開番号

特開2014-143419 (P2014-143419A)

(43) 公開日

平成26年8月7日(2014.8.7)

審査請求日

平成29年1月20日(2017.1.20)

(31) 優先権主張番号

13/748,076

(32) 優先日

平成25年1月23日(2013.1.23)

(33) 優先権主張国

米国(US)

(73) 特許権者

504199127 エヌエックスピー ユーエスエイ インコ

ーポレイテッド

N X P U S A, I n c .

アメリカ合衆国 テキサス州 78735

オースティン ウィリアム キャノン

ドライブ ウエスト 6501

(74) 代理人

100142907 弁理士 本田 淳

(72) 発明者

ホンニン ヤン

アメリカ合衆国 85249 アリゾナ州

チャンドラー イー. サン カルロス

プレイス 2648

最終頁に続く

(54) 【発明の名称】 3次元的な表面電界緩和が増強された半導体デバイス

## (57) 【特許請求の範囲】

## 【請求項 1】

デバイスであって、

半導体基板と、

前記半導体基板におけるソース領域およびドレイン領域であって、第1の横方向に沿つて互いから離間されているソース領域およびドレイン領域と、

前記半導体基板におけるドリフト領域であって、動作時に前記ソース領域と前記ドレイン領域との間にバイアス電圧が印加されるとドリフト領域を通じて電荷担体がドリフトするドリフト領域と、を備え、

前記ドリフト領域および前記ドレイン領域は、接合部において互いに接続されており、

前記ドリフト領域は、該ドリフト領域と前記ドレイン領域との間の前記接合部に沿った第2の横方向において平面視における切り欠きの境界を有するとともに、前記ドリフト領域と前記ドレイン領域との間の接合部において、前記ドレイン領域の垂直厚さ方向に狭まっている、デバイス。

## 【請求項 2】

前記ドリフト領域は前記ドレイン領域の下の開口を備え、

前記開口は櫛形状境界を有する、請求項1に記載のデバイス。

## 【請求項 3】

前記ドリフト領域は前記ドレイン領域を通じて横方向に延在していない、請求項1に記載のデバイス。

10

20

**【請求項 4】**

前記ドリフト領域は外側部分および内側部分を備え、該内側部分は該外側部分によって包囲され、前記ドレイン領域の下に配置されており、

前記内側部分は、動作時に前記ドリフト領域の完全な空乏化が達成されるように、前記外側部分に対して縮小されている、請求項 1 に記載のデバイス。

**【請求項 5】**

前記切り欠きの境界は方形波状の切り欠きパターンを有する、請求項 1 に記載のデバイス。

**【請求項 6】**

前記切り欠きの境界は周期的な切り欠きパターンを有する、請求項 1 に記載のデバイス

10

。

**【請求項 7】**

前記半導体基板はエピタキシャル層を備え、前記ソース領域、前記ドレイン領域、および前記ドリフト領域は該エピタキシャル層に形成されており、

前記ドリフト領域は前記エピタキシャル層に対する切り欠きの境界に沿って前記ドレイン領域の下で切り詰められている、請求項 1 に記載のデバイス。

**【請求項 8】**

前記半導体基板において前記ソース領域と前記ドレイン領域との間にトレンチ分離領域をさらに備え、

前記ドリフト領域は、前記トレンチ分離領域の下の第 1 の領域と、前記ドレイン領域の下の第 2 の領域とを備え、

20

前記ドリフト領域の前記第 2 の領域におけるドーパント濃度は、前記第 1 の領域に対して低減されている、請求項 1 に記載のデバイス。

**【請求項 9】**

前記切り欠きの境界は、櫛形状境界を含む、請求項 1 に記載のデバイス。

**【請求項 10】**

前記ドリフト領域は、前記ドレイン領域と横方向において重なっており、

前記ドリフト領域は、前記ドレイン領域の横方向の範囲全体を通じては延在していない、請求項 1 に記載のデバイス。

**【請求項 11】**

30

前記切り欠きの境界は、前記ドリフト領域の歯部を含み、

前記歯部は前記ドリフト領域および前記ドレイン領域を結合している、請求項 1 に記載のデバイス。

**【請求項 12】**

前記ドリフト領域は、前記切り欠きの境界に沿った歯部を含み、

前記歯部は、前記ドレイン領域と横方向において重なっており、

前記歯部は、前記ドレイン領域の横方向の範囲全体を通じては延在していない、請求項 1 に記載のデバイス。

**【請求項 13】**

前記ドレイン領域下における前記ドリフト領域の厚さは、前記ドレイン領域下にない前記ドリフト領域の部分より狭い、請求項 1 に記載のデバイス。

40

**【請求項 14】**

電子装置であって、

半導体基板と、

前記半導体基板におけるリサーフトランジスタと、を備え、該リサーフトランジスタは

、

第 1 の導電型を有し、動作時にチャネルが形成される第 1 の半導体領域と、

第 2 の導電型を有し、第 1 の横方向に沿って互いから離間されている第 2 の半導体領域および第 3 の半導体領域と、

前記第 2 の導電型を有する第 4 の半導体領域であって、前記第 2 の半導体領域と第 3 の

50

半導体領域との間にバイアス電圧が印加されると、電荷担体が動作時に前記第1の半導体領域に形成される前記チャネルからを第4の半導体領域を通じてドリフトする第4の半導体領域と、を備え、

前記第3の半導体領域および前記第4の半導体領域は、接合部において互いに接続されており、

前記第4の半導体領域は、前記第3の半導体領域と第4の半導体領域との間の前記接合部に沿った第2の横方向において平面視における切り欠きの境界を有するとともに、前記第4の半導体領域と前記第3の半導体領域との間の接合部において、前記第3の半導体領域の垂直厚さ方向に狭まっている、電子装置。

#### 【請求項15】

10

前記第4の半導体領域は前記第3の半導体領域の下の開口を備え、

前記開口は櫛形状境界を有する、請求項14に記載の電子装置。

#### 【請求項16】

前記第4の半導体領域は前記第3の半導体領域を通じて横方向に延在していない、請求項14に記載の電子装置。

#### 【請求項17】

前記第4の半導体領域は外側領域および内側領域を備え、該内側領域は該外側領域によって包囲され、前記第3の半導体領域の下に配置されており、

前記内側領域は、動作時に前記第4の半導体領域の完全な空乏化が達成されるように、前記外側領域に対して縮小されている、請求項14に記載の電子装置。

20

#### 【請求項18】

前記半導体基板はエピタキシャル層を備え、前記第1の半導体領域、第2の半導体領域、第3の半導体領域、および第4の半導体領域は該エピタキシャル層に形成されており、

前記第4の半導体領域は前記エピタキシャル層に対する切り欠きの境界に沿って前記第3の半導体領域の下で切り詰められている、請求項14に記載の電子装置。

#### 【請求項19】

前記リサーフトランジスタは、前記第2の半導体領域と前記第3の半導体領域との間にトレンチ分離領域をさらに備え、

前記第4の半導体領域は、前記トレンチ分離領域の下の第1の領域と前記第3の半導体領域の下の第2の領域とを備え、

30

前記第4の半導体領域の前記第2の領域におけるドーパント濃度は、前記第1の領域に対して低減されている、請求項14に記載の電子装置。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明の実施形態は、半導体デバイスに関する。

##### 【背景技術】

##### 【0002】

集積回路（I C）および他の電子デバイスは多くの場合、金属酸化膜半導体電界効果トランジスタ（M O S F E T）、または単純にM O Sトランジスタもしくはデバイスとも称される、相互接続された電界効果トランジスタ（F E T）の構成を含む。一般的なM O Sトランジスタは、制御電極としてのゲート電極と、離間されたソース電極およびドレイン電極とを含む。ゲート電極に印加される制御電圧が、ソース電極とドレイン電極との間の制御可能な導電性チャネルを通じた電流の流れを制御する。

40

##### 【0003】

電力トランジスタデバイスは、運動制御、エアバッグ配備、および自動車燃料噴射器ドライバのような電力用途に存在する高電流および電圧に耐えるように設計されている。1つのタイプの電力M O Sトランジスタは、側方拡散金属酸化膜半導体（L D M O S）トランジスタである。L D M O Sデバイスにおいて、チャネル領域とドレイン領域との間にドリフト空間が設けられる。

50

**【0004】**

LDMOSデバイスは、デバイス端子のすべてが基板電位に対してレベルシフトされているハイサイド構成において動作するように設計されている場合がある。ハイサイド動作のために構成されているデバイスは、ハイサイドおよびローサイドにそれぞれのLDMOSデバイスを有するDC-DCコンバータ内の電力スイッチに適用されている。ハイサイド対応可能デバイスは、LDMOSデバイスのボディ領域から下方にある基板へと直接突き抜ける経路を防止するように設計され得る。

**【0005】**

LDMOSデバイスは、自動車用途のような、40ボルトを超える動作電圧を含む用途において使用されることが多い。そのような高電圧をドレインに印加する結果として生じる絶縁破壊は多くの場合、LDMOSデバイス設計内の表面電界緩和（リサーフ；RESURF）構造を通じて防止される。リサーフ構造は、垂直方向および横方向（側方）の両方においてLDMOSデバイスのドリフト空間を空乏化するように設計され、それによって、ドリフト領域における表面付近において電界が低減され、従ってデバイスのオフ状態絶縁破壊電圧（BV<sub>dss</sub>）が上昇する。

10

**【0006】**

一般的に、BV<sub>dss</sub>とドレイン-ソースオン抵抗（R<sub>ds on</sub>）との間にはトレードオフが存在する。BV<sub>dss</sub>は、そのデバイスについての達成可能な出力定格電圧を決定する。R<sub>ds on</sub>は、所与の量の電流、たとえば、そのデバイスの定格電流または電力を取り扱うのに必要とされるデバイス面積を決定する。より高いBV<sub>dss</sub>レベル（および、それゆえにより高い動作電圧）を達成するためのデバイスを設計することは多くの場合、R<sub>ds on</sub>の増大（および、従って単位面積当たりの定格電流の低下）を犠牲にする。たとえば、BV<sub>dss</sub>レベルはデバイスのドリフト空間の長さを増大させること、またはドリフト空間のドーパント濃度を低減することによって増大し得、これらの両方がR<sub>ds on</sub>を増大させる。逆に、R<sub>ds on</sub>を低減する（従って、単位面積当たりの定格電流を増大させる）ようにデバイスを設計することによって、BV<sub>dss</sub>レベルを低下させる（従って、動作電圧を低下させる）ことになる。たとえば、ドリフト空間内のドーパント濃度をより高くすることによって、BV<sub>dss</sub>が低下することを犠牲としてR<sub>ds on</sub>が低下する。他のR<sub>ds on</sub>低減技法は、デバイス面積を増大させること、および従って、デバイスの製造費用を増大させることを含む。

20

**【0007】**

パルタサラティらによる非特許文献1には、特定のドレインプロファイルを有するリサーフLDMOSについて記載されている。

**【先行技術文献】****【非特許文献】****【0008】**

**【非特許文献1】** エレクトロン・デバイス・レターズ（Electron Device Letters）、IEEE、第23巻、第4号、p. 212-214

**【発明の概要】****【発明が解決しようとする課題】**

30

**【0009】**

3次元的な表面電界緩和が増強された半導体デバイスを提供する。

**【課題を解決するための手段】****【0010】**

3次元的な表面電界緩和（3D RESURF）効果が増強された側方拡散金属酸化膜半導体（LDMOS）ならびに他の電力トランジスタデバイスおよび電子装置の実施形態が説明される。デバイスおよび装置の実施形態は、ノッチ（切り欠き）部分を含むドーパントプロファイルを有して構成されたドリフト領域を有してもよい。ドーパントプロファイルは、デバイスの導電路に直交する横方向において、またはそれに沿って切り欠きされてもよい。たとえば、ドーパントプロファイルは、ソースおよびドレイン領域がそれに沿

40

50

って互いに離間される横方向に直交する横方向に沿って切り欠きされてもよい。リサーフ効果の増強は、開示されているデバイスの実施形態の絶縁破壊電圧レベル ( $BV_{dss}$ ) を、2次元的なリサーフ効果によって達成されるレベルを超えて引き延ばすことができる。

#### 【0011】

いくつかの実施形態において、切り欠きドーパントプロファイルは、ドレイン領域との接合部分に沿ったドリフト領域内の櫛形構造を含む。櫛構造は周期的な切り欠きパターンを含んでもよい。パターン内の各切り欠きまたは溝は、p型エピタキシャル層のドリフト領域が形成される部分のような、低濃度ドープp型半導体材料を充填されるか、またはそれを含んでもよい。櫛構造に沿った接合部分は、それに沿って切り欠きパターンが形成される横方向からのドリフト領域の空乏化を増強することができる。そのような利点は、インプラント層または作製段階を追加することなく達成される。10

#### 【0012】

ドリフト領域の切り欠きドーパントプロファイルは、ドリフト領域における、その下の、または他の様態で付近の空乏化を促進するためにともにドリフト領域を縮小する、ドリフト領域の他の特徴と組み合わされてもよい。たとえば、ドリフト領域はオープンドレイン構造を呈してもよく、ドレインの下の、ドリフト領域のカットオフ部分または内側端部がドリフト領域内の開口を画定する。カットオフ部分または端部は、ドレイン領域付近の（ドリフト領域を形成するのに使用される）ウェル領域の同様のカットオフ部分または端部のアーチファクトであってもよい。開口は、切り欠きドーパントプロファイルを呈するための1つ以上の切り欠き境界を有してもよい。オープンドレイン構造は、ドレイン付近でドリフト領域を縮小することによって長いドリフト長（たとえば、 $5\mu m$ を超えるトレーンチ分離長）を有するデバイスに対するリサーフ効果を増強することができ、それによって  $BV_{dss}$  レベルを最大130ボルトまで増大させるが、オープンドレイン構造を切り欠き境界と組み合わせて櫛構造を形成することによって、さらに空乏化を増強することができる。 $BV_{dss}$  レベルは、130ボルトを超えて、たとえば、最大139ボルトにさらに増大することができる。オープンドレイン構造および切り欠きドレイン側境界の組合せを有する実施形態に関連して説明されるが、開示される実施形態の切り欠きドーパントプロファイルは、ウェル領域内に注入されたドーパントが拡散した後にドリフト領域がドレイン領域を通じて横方向（側方）に延在する、閉ドレイン構造に組み込まれてもよい。20

#### 【0013】

切り欠きドーパントプロファイルは、開示されるデバイスの実施形態の  $BV_{dss}$  を向上させるための多次元リサーフ効果（たとえば、側方および垂直）を提供することができる。しかしながら、リサーフ効果の利点は、オフ状態絶縁破壊電圧レベル ( $BV_{dss}$ ) とオン状態抵抗値 ( $R_{ds(on)}$ )との間のトレードオフに設計上の柔軟性を付加することによって達成される。従って、 $BV_{dss}$  および  $R_{ds(on)}$  の値は、ドーパントプロファイル内の切り欠きの幅（またはサイズ）および間隔を調整することによって、特定のデバイスまたは用途に対して調整またはカスタマイズされ得る。幅および間隔は、本開示に応じて構成されるデバイスの設計中に操作されるべき追加の変数または自由度を提供する。 $BV_{dss}$  と  $R_{ds(on)}$  との間の最適なバランスは、切り欠き、または切り欠きの間の領域の幅を調整することによって達成され得る。そのように設計上の柔軟性が付加されることによって、開示されるデバイスの実施形態の他の電気的特性が最適化または調整されることが可能になり得る。たとえば、衝突イオン化によって生成されるホットキャリアが、設計最適化全体を通じて  $BV_{dss}$  または  $R_{ds(on)}$  を犠牲にすることなく最小限に抑えられ得る。そのような最適化またはカスタマイズは、作製工程段階を変更または追加することなく提供され得る。40

#### 【0014】

下記、ドレイン領域を包囲するドリフト領域境界に沿った周期的な櫛形状開口（またはドレイン領域付近の櫛形状ドーパントプロファイル）を有する実施形態に関連して説明す50

るが、いくつかの他のパターンまたは構造が可能である。たとえば、境界は櫛形状である必要はない。切り欠きのサイズおよび形状は示されている例とは異なってもよい。切り欠き（および／または切り欠きによって画定される突起）は、示されている櫛形状境界以外の三角形、台形、橢円形、正弦曲線形、または他の断面形状を有してもよい。本明細書の記載の通り、切り欠きおよび／またはドレイン領域の横方向の広がりも異なってよい。

#### 【0015】

下記、nチャネルLDMOSトランジスタに関連して説明するが、開示されるデバイスは特定のトランジスタ構成に限定されない。たとえば、開示されるデバイスの特徴の適用は、LDMOSまたは他の電力MOSトランジスタに限定されない。開示されるデバイスの1つ以上の特徴は、たとえば、バイポーラトランジスタを含む他のデバイス構成に適用されてもよい。開示されるデバイスのドリフト領域は、広範な電力電子デバイスにおいて有用であり得る。ドリフト領域はまた、1つの特定のタイプのリサーフ構成に限定されない。開示されるデバイスは、単一、二重、または他のリサーフ構造配列を含む各種のリサーフ構造を有してもよく、それらの各々が本明細書において「リサーフトランジスタ」と称される場合がある。

10

#### 【0016】

説明を簡便にするために、また一切の限定を意図せず、本明細書においてnチャネルLDMOSデバイスが説明され示されている。従って、p型アイランドまたは他の領域がn型ドリフト領域に対して記載される。しかしながら、pチャネルおよび他の型のデバイスが、たとえば、反対の導電型の半導体領域に置き換えることによって設けられてもよいため、開示されるデバイスはnチャネルデバイスには限定されない。従って、たとえば、下記に説明する例における各半導体領域、層または他の構造は、下記の例において特定されている型とは反対の導電型（たとえば、n型またはp型）を有してもよい。

20

#### 【図面の簡単な説明】

#### 【0017】

【図1】一実施形態に応じて構成されている切り欠きドーパントプロファイルを有するドリフト領域を有する例示的なLDMOSトランジスタの概略部分断面図。

【図2】アニーリング段階の後のドリフト領域を示す図1の例示的なLDMOSトランジスタの概略部分断面図。

【図3】一実施形態に応じた切り欠きドーパントプロファイルを有するドリフト領域を有する例示的なLDMOSトランジスタの平面図。

30

【図4】一実施形態に応じた切り欠きドーパントプロファイルを有するLDMOSトランジスタを構築するための例示的な作製順序のフローチャート。

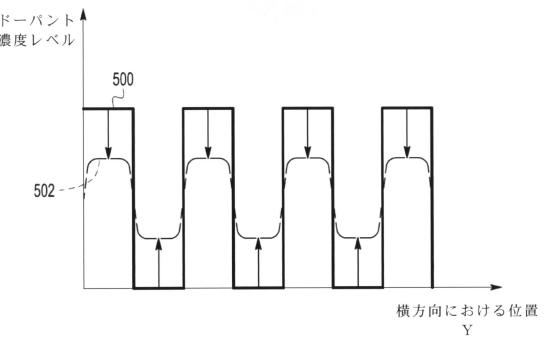

【図5】導電路に直交する横方向位置の関数としての、アニーリング段階の前後のドリフト領域内のドーパントレベルのグラフ図。

#### 【発明を実施するための形態】

#### 【0018】

構成要素および図面は必ずしも原寸に比例しておらず、代わりにさまざまな実施形態の原理を示すことに重点が置かれている。さらに、図面において、同様の参照符号は種々の図全体を通じて対応する部分を示している。

40

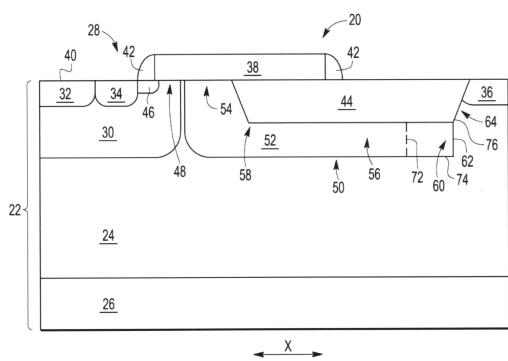

#### 【0019】

図1は、一実施形態に応じて構築されているnチャネルLDMOSデバイス20の一例の概略断面図である。デバイス20はリサーフトランジスタとして構成されてもよい。デバイス20は半導体基板22を含み、当該半導体基板はいくつかのエピタキシャル層24を含む。この例において、半導体基板22は、原基板26上に成長される単一のp型エピタキシャル層P-EPIを含む。原基板26は、いくつかの場合において、複数のエピタキシャル層を有するもののような高濃度ドープp型基板であってもよい。デバイス20は、これに代えてまたはこれに加えて、1つ以上のデバイス領域が形成される非エピタキシャル層を含んでもよい。半導体基板22の層のいずれか1つ以上はシリコンを含んでもよい。半導体基板22の構造、材料、および他の特性は、示されている例とは異なってもよ

50

い。たとえば、半導体基板 2 2 はシリコン・オン・インシユレータ（S O I）構造を含んでもよい。追加、より少ない、または代替的な層が半導体基板 2 2 に含まれてもよい。たとえば、任意の数の追加の半導体および／または非半導体層が含まれてもよい。従って、開示されるデバイスは、たとえば、バルクシリコン基板またはエピタキシャル成長層を含む基板には限定されず、代わりに広範な他のタイプの半導体基板によって支持されてもよい。

#### 【 0 0 2 0 】

デバイス 2 0 のデバイスエリア 2 8 が図 1 に描かれている。いくつかの実施形態においては、デバイスエリア 2 8 の一方の側または半分のみが示されている。たとえば、デバイスエリア 2 8 は側方に対称であり、従って図示されている部分を鏡像とした部分を含んでもよい（たとえば、図 2 および図 3 参照）。

10

#### 【 0 0 2 1 】

デバイスエリア 2 8 は、半導体基板 2 2 における 1 つ以上のドープデバイス分離層または領域（図示せず）によって画定されてもよい（たとえば、エピタキシャル層 2 4）。1 つ又は複数のドープ分離層または 1 つ又は複数の領域は、デバイスエリア 2 8 を横方向においてかつ／または他の様態で包囲してもよい。これらの層または領域は、デバイスエリア 2 8 を基板 2 2 の残りの部分（または原基板 2 6）から隔てる障壁または絶縁層として作用する。いくつかの場合において、埋め込み n 型層が半導体基板 2 2 に形成または配置されてもよい。たとえば、埋め込み n 型層は、半導体基板 2 2 に、そのエピタキシャル層 2 4 を成長させる前に形成されてもよい。埋め込み n 型層は、活性エリア 2 8 を原基板 2 6 から隔てる障壁または絶縁層として作用するためにデバイスエリア 2 8 を通じて（たとえば、デバイスエリア 2 8 の下に）側方に延在してもよい。埋め込み n 型層は、これに代えてまたはこれに加えて、下記に説明するリサーフ効果をサポートするためにドリフト領域の空乏化を補助してもよい。埋め込み n 型層は、デバイスエリア 2 8 を包囲する複数のドープデバイス分離領域（図示せず）のうちの 1 つを構成してもよい。たとえば、中濃度または高濃度ドープ n 型分離ウェル（図示せず）が、デバイスエリア 2 8 を横方向において包囲してもよい。分離ウェルは環形状であってもよい。分離ウェルは、デバイスエリア 2 8 の側方周縁の外側で、またはそれに沿って、埋め込み n 型層上に接して、または他の様態でその上方に配置されてもよい。上述の分離領域のうちの 1 つ以上は、パンチスルーフォードを含む、高電圧（H V）動作（たとえば、デバイス 2 0 の端子が、一般的には接地されている半導体基板 2 2 に対してレベルシフトされているハイサイド動作）のためのドーパント濃度レベルを有し、かつ／または他の様態でそのために構成されてもよい。任意の数のデバイス分離ウェル、シンク、または埋め込み層が互いに接続されてもよい。追加、より少ない、または代替的なデバイス分離層または領域が半導体基板 2 2 に設けられてもよい。

20

#### 【 0 0 2 2 】

デバイス 2 0 は、半導体基板 2 2 にデバイス本体またはボディ領域 3 0 を含む。この例において、ボディ領域 3 0 は、基板 2 2 のエピタキシャル層 2 4 内に形成される p 型ウェルである。p 型ウェルは、高電圧動作（たとえば、ハイサイド動作）のために構成されてもよい。ボディ領域 3 0 は、半導体基板 2 2 におけるボディ領域 3 0 の p 型ウェル内にまたは他の様態でその上方に形成される 1 つ以上の高濃度ドープ p 型ボディコンタクト領域または電極 3 2 を介してバイアスされてもよい。各コンタクト領域 3 2 のドーパント濃度は、ボディ領域 3 0 への抵抗接触を確立するのに十分なレベルであってもよい。

30

#### 【 0 0 2 3 】

デバイス 2 0 は、半導体基板 2 2 における高濃度ドープソース領域 3 4 およびドレイン領域 3 6 を含む。ソース領域 3 4 とドレイン領域 3 6 とは、図 1 の断面に示す横方向位置において互いから横方向（側方）に離間されている。いくつかの実施形態において、ソース領域 3 4 およびドレイン領域 3 6 は、追加のまたは代替的な側方間隔を有してもよい。任意の数のソース領域 3 4 またはドレイン領域 3 6 が設けられてもよい。ドレイン領域 3 6 は図示のように、ソース領域 3 4 の中央に置かれるか、もしくは他の様態でその間に配

40

50

置される必要はなく、またはそれによって横方向において包囲される必要もない。この例において、ソース領域34およびドレイン領域36は、エピタキシャル層24のn型ドープ部分である。高濃度ドープn型ソース領域34は、ボディ領域30の中に、上に接して、かつ／または他の様態でその上方に配置される。高濃度n型ドープドレイン領域36は、図1に示す横方向に沿ってボディ領域30から離間されている。そのような離間が、ソース領域34とドレイン領域36との間のデバイスの導電路を画定する。従って、導電路は図1に示す横方向に沿って配向されてもよい。領域34、36、またはそれらの一部は、ソース領域34およびドレイン領域36をバイアスするための抵抗接触を確立するのに十分なレベルのドーパント濃度を有してもよい。一般的なLDMOS構成において、ドレイン領域36はソース領域34に対する相対的に高いドレイン－ソース電圧Vdsにバイアスされる。

#### 【0024】

デバイス20は、半導体基板22の表面40の上に接して、またはその上方に形成される1つ以上のゲート構造38を含む。ゲート構造38は、ソース領域34とドレイン領域36との間に配置される。いくつかの実施形態において、ゲート構造38は、図2および図3に示すようにデバイスエリア28内で中央または内部に位置し得るドレイン領域36を包囲している。代替的に、ゲート構造38は、2つのトランジスタが同じドレイン領域36を共有するために対称に配置される二重ゲートフィンガ構造に配列されてもよい。ゲート構造38はゲート誘電体（図示せず）の上に接して、またはその上方に位置する。たとえば、ゲート誘電体は表面40上に堆積または他の様態で形成されるシリコンジオキサイド（またはオキサイド）を含んでもよい。各ゲート構造38は、ゲート誘電体の上に接してまたはその上方に導電性ゲート層（たとえば、ポリシリコン板）を含み、ゲート誘電体は導電性ゲート層を基板22から絶縁する。ゲート構造38は、ゲート構造38の側方端部に沿って配置される1つ以上の誘電体側壁スペーサ42を含んでもよい。側壁スペーサ42は、表面40に沿ったシリサイド短絡を防止するためにシリサイド遮断物として作用するために側方端部を被覆してもよい。側壁スペーサ42は、ゲート構造38の導電性構成要素をソース領域34およびデバイス領域28の他の領域から隔てるための間隔を提供してもよい。この例において、側壁スペーサ42のうちの1つは、ソース領域34の端部の画定における位置整合に使用される。

#### 【0025】

ゲート構造38の構成は異なってもよい。ゲート構造38の構成は、複数の導電層（たとえば、ポリシリコン板）を含んでもよい。ゲート構造38の構成要素、材料、および他の特性は、示されている例とは異なってもよい。

#### 【0026】

いくつかのシャロー・トレチ・アイソレーション（STI）領域44が、半導体基板22において表面40に形成されてもよい。この実施形態において、STI領域44は、ゲート構造38を、ドレイン領域36に印加される高電圧から離間する。これらのおよび他のSTI領域44は、ゲート構造38の酸化物層へのホットキャリア注入（HCI）を防止または最小限に抑えるように構成されてもよい。

#### 【0027】

ボディコンタクト領域32およびソース領域34、ならびにデバイス20の構成要素をバイアスするための他の領域のような、さまざまなコンタクト領域を絶縁または隔てるために、半導体基板22に他のSTI領域が配置されてもよい。たとえば、分離コンタクト領域および基板コンタクト領域は、STI領域44のうちの1つによって隔てられてもよい。

#### 【0028】

デバイス20は、ソース領域34およびドレイン領域36に、またはその付近に1つ以上の低濃度または中濃度ドープ遷移領域（たとえば、n型低濃度ドープドレイン、またはNLDN領域）を有して構成されてもよい。各遷移領域は、ソース領域34および／またはドレイン領域36と接続して形成される拡散領域であるか、またはそれを含んでもよい

10

20

30

40

50

。そのような遷移領域は、ソース領域34またはドレイン領域36付近のエリア以外のエリア内を含む、表面40にある、またはその付近の電界を制御するのを補助することができる。この例において、デバイス20は、ソース領域34に隣接するNLD領域46を含む。NLD領域46は、図示のようにゲート構造38の下で側方に延在してもよい。

#### 【0029】

ゲート構造44がバイアスされると、電荷担体（この場合は電子、代替的には正孔）が1つ以上のチャネルエリアまたは領域48内に蓄積する。各チャネル領域48（またはその一部分）は、ゲート構造38の下のボディ領域30内に位置してもよい。この例において、電子が蓄積する結果として、チャネル領域48内で、半導体基板22の表面40付近においてp型ボディ領域30からn型導電層またはエリアへと電荷が反転する。十分な量の電荷担体が導電層またはエリア内に蓄積すると、電荷担体はチャネル領域48を通じてソース領域34からドレイン領域36へと流れることが可能になる。

#### 【0030】

チャネル領域48は、ゲート構造38にバイアスが印加される結果として電荷反転または蓄積が発生する、半導体基板22における他の領域またはエリアを含んでもよい。電荷担体はまた、ボディ領域30の外側またはそれを超えて蓄積してもよい。たとえば、電荷担体はボディ領域30に隣接するエピタキシャル層24の領域内に蓄積してもよい。このエリアは、いくつかの場合において、デバイス20の蓄積領域の一部分とみなされてもよい。チャネル領域48および蓄積領域は、デバイス20の導電領域または経路の一部分を形成してもよい。

10

#### 【0031】

デバイス20の導電路は、電荷反転が発生する領域、またはゲート構造38に印加されるバイアス電圧によって導電が可能になるかもしくは増強される領域には限定されない。従って、デバイス20の導電路または領域は、表面40にあるかまたはその付近の領域には限定されない。たとえば、導電路は、それを通じて電荷担体がドリフトしてドレイン領域36に達する、LDMOSデバイスのドリフト領域50の一部分を含む。ドリフト領域50は、ドレイン領域36とチャネル領域48とを電気的に結合してもよい。この例において、ドリフト領域50は、STI領域44の下のn型ウェル52の一部分と対応する。デバイス20のドリフト領域50に関するさらなる詳細を下記に記載する。

20

#### 【0032】

n型ウェル領域52は、ゲート構造38の下で側方に伸長してデバイス20の蓄積領域54を形成してもよい。蓄積領域54は、STI領域44の下ではなく表面40に沿って配置されてもよい。動作時には、電荷担体はドリフト領域50を通じてドリフトする前に蓄積領域54内に蓄積する。デバイス20の導電路は、ボディ領域30とは異なる導電型を有する追加のまたは代替的なエリアまたは領域を含んでもよい。

30

#### 【0033】

図1の実施形態において、ドリフト領域50は、電界ドリフト領域として構成されている。蓄積領域54とドレイン領域36との間にSTI領域44が配置されている。蓄積領域54とドレイン領域36との間に代替的なまたは追加の電界分離構造が配置されてもよい。電界分離構造は、表面40の上方に配置される1つ以上のフィールドプレートを含んでもよい。

40

#### 【0034】

デバイス20の導電路または領域は、n型であるかp型であるかにかかわらず、表面40にあるかまたはその付近にあるさらに他の領域を含んでもよい。たとえば、チャネル領域48および/またはデバイス20の他の導電領域は、半導体基板22における1つ以上の中濃度ドープn型遷移領域（上述のたとえば、NLD領域46のうちの1つ）を含んでもよい。

#### 【0035】

電荷担体は、半導体基板22のドリフト領域50を通過する経路に沿って、ソース領域34からドレイン領域36へ流れる。ドリフト領域50は、電荷担体が、ドレイン領域3

50

6とソース領域34との間に印加されるドレイン-ソース電圧によって確立される電界の下でドリフトすることを可能にするように構成されてもよい。従って、ドリフト領域50（またはその1つ以上の部分）は、デバイス20の導電路の一部分を形成する。動作時には、ドリフト領域50は、ドレイン領域36をチャネル領域48およびソース領域36と電気的に結合する。

#### 【0036】

ドリフト領域50は、動作時には、絶縁破壊性能を改善するためにデバイスエリア28におけるさまざまなロケーションにおいて、表面電界緩和（リサーフ）効果を介して、電界の大きさを低減するための空乏化のために構成されてもよい。この例において、ドリフト領域50内および／またはその周囲のエリアにおける電界を低減するように意図されるリサーフ効果を確立するために、n型ウェル52とp型エピタキシャル層24および／またはボディ領域30との間に接合部が形成される。<sup>10</sup> n型ウェル52および／またはドリフト領域50は、ボディ領域30に隣接してもよいし、かつ／またはボディ領域から離間されてもよい。電界を低減することによって、導電路に沿った絶縁破壊を回避することができ、従って、デバイス20の固有の絶縁破壊電圧（BV<sub>dss</sub>）が増大する。ドリフト領域50は、ドリフト領域50における特定のロケーションにおける電界を同じレベルにすることによって、高い絶縁破壊電圧レベルおよび低いドレイン-ソース抵抗（R<sub>ds on</sub>）の両方を達成するようにさらに構成されてもよい。ドリフト領域50は、少なくとも部分的に、動作時には、たとえば、エピタキシャル層24および／またはボディ領域30との逆バイアスPN接合部に沿って側方および垂直方向の両方に空乏化されてもよい。<sup>20</sup> ソース領域34とドレイン領域36との間にドレイン電圧V<sub>ds</sub>が印加される結果として、接合部は逆バイアスされる。逆バイアス接合部は、絶縁破壊性能を改善するために、リサーフ効果のように、電界を低減することができる。代替的な実施形態において、デバイス20は二重リサーフ効果を確立するように構成されてもよく、デバイスエリア28においてさらに空乏化するために、たとえば、1つ以上の追加の領域がドリフト領域50に隣接して（たとえば、その下に接してまたは下方に）配置されてもよい。適切なリサーフ領域の構造的および動作上の特性に関するさらなる詳細は、米国特許第6,882,023号明細書（「浮遊リサーフ LD MOSFET およびその製造方法（Floating RE SURF LD MOSFET and Method of Manufacturing Same）」）に記載されている。<sup>30</sup>

#### 【0037】

ドリフト領域50は、STI領域44の下の電界ドリフト部または電界ドリフト部部分56を含む。電界ドリフト部分56は、約5マイクロメートル（ミクロン）以上の側方長さを有してもよい。電界ドリフト部分56は、ドリフト領域50のチャネルまたは蓄積側（もしくは端部）58からドレイン側（もしくは端部）60まで延在する。動作時には、電荷担体は、ドレイン-ソースバイアス電圧から生じる電界の下で電界ドリフト部分56を通じてチャネル側58からドレイン側60へとドリフトする。この例において、電荷担体は、チャネル領域48および／または蓄積領域54を出た後、チャネル側58に達する。その後、電荷担体はSTI領域44の周囲で電界ドリフト部分56を通じてドリフトしてドレイン側60に達する。<sup>40</sup>

#### 【0038】

ドリフト領域50は、適切なR<sub>ds on</sub>値を確立するために、電界ドリフト部分56内およびチャネル側58およびドレイン側60において1つ以上のドーパント濃度レベルを呈するように構成されてもよい。ドーパント濃度レベルは、電界ドリフト部分56の深さを通じて、ならびに／またはチャネル側58および／もしくはドレイン側60において異なってもよい。たとえば、電界ドリフト部分56内（ならびに／またはチャネル側58および／もしくはドレイン側60における）のドーパント濃度レベルは、STI領域44付近において、エピタキシャル層24とのPN接合部付近よりも高くてもよい。これに代えてまたはこれに加えて、電界ドリフト部分56におけるドーパント濃度レベルは、横方向における位置の関数として変化してもよい。たとえば、ドレイン側60の所与の深さにお

けるドーパント濃度レベルは、ドレイン領域36までの側方距離が低減するにつれて低減されてもよい。所与の深さにおけるドリフト領域50におけるドーパント濃度レベルは、ドレイン領域36との重なりが増大するにつれてさらに低減されてもよい。いくつかの場合において（たとえば、図2参照）、ドーパント濃度レベルは、ドレイン領域36の下でドリフト領域50内に開口が形成される程度まで低減されてもよい。ドレイン側60における、またはそれに沿った電界ドリフト部分56におけるドーパント濃度レベルは、下記に説明するように、もう1つの横方向（たとえば、図1に示す横方向に直交する横方向）において異なってもよい。

#### 【0039】

熱アニールまたは他の1つ又は複数の作製段階がドリフト領域50とドレイン領域36との間の接続部を形成する前の、ドリフト領域50のドレイン側または端部60が図1に示されている。図1に示す実施形態において、n型ウェル52は、アニールまたは他の1つ又は複数の作製段階の前は、横方向においてドレイン領域36と重なっていない。n型ウェル52には、ドレイン領域36から横方向において離間されているカットオフ部分または端部62が形成される。この例において、n型ウェル52は、端部62が直立または垂直壁を有するように構成されている。n型ウェル52を形成する注入後の熱アニールは壁の1つ又は複数の鋭利端部を平滑化することができる。この例におけるカットオフ部分62はSTI領域44の下に位置する。他の実施形態において、カットオフ部分62は、n型ウェル52が熱アニールの前はドレイン領域36を通じて横方向に延在しないよう、ドレイン領域36の下に位置する。カットオフ部分62は他の実施形態においては非垂直に配向されてもよい。

#### 【0040】

ドレイン領域36とドリフト領域50との間の接続部が、n型ウェル52およびドレイン領域36の一方または両方からのドーパントの拡散を通じて形成される。そのような拡散の結果として、ドーパントがn型ウェル52とドレイン領域36との間の空間64へと分散する。この分散は、図1に示す横方向における側方分散を含んでもよい。拡散はまた、垂直成分をも含んでもよい。たとえば、ドレイン領域36からのドーパントは半導体基板22へと下向きに（および横方向において外向きに）拡散してもよい。これに代えてまたはこれに加えて、n型ウェル52からのドーパントは上向きに（および横方向において内向きに）拡散してもよい。最終的に、拡散は、n型ウェル52とドレイン領域36との間の空間64内に1つ以上の電流バスまたは経路を確立する。電流路はSTI領域44に沿って配置されてもよい。電流路は、それを通じて電荷担体が印加されているバイアス電圧下での動作時にドリフトする低抵抗経路を提供することができる。従って、カットオフ部分または端部62から生じるデバイス20のオン抵抗に対する悪影響を回避することができる。

#### 【0041】

ドリフト領域50のドレイン側60におけるカットオフ部分または端部62は、ドリフト領域50がドレイン領域36の下で縮小するように構成される。たとえば、ドリフト領域50は、図1に示す横方向においてドレイン領域36を通じて変化する側方プロファイルを有してもよい。ドリフト領域50のそのような縮小によって、ドリフト領域50は、n型ウェル52とボディ領域（および/またはp型エピタキシャル層24）との間のPB接合部からの距離にかかわらず、動作時にドレイン領域36の下でまたはそれに沿って十分に空乏化することが可能になり得る。そのような縮小は、長いドリフト長を有するデバイスにおいて有用であり得る。ドリフト領域50は、切り欠きドーパントプロファイルに関連して下記に説明するように、ドレイン領域36において、それに沿って、またはその付近でさらに縮小されることができる。

#### 【0042】

図1はまた、デバイス20を、デバイス20の一方の側のみが示されているという意味においても簡略化された形態で示し得る。デバイス20は、示されている側と同様に構成された別の側を含んでもよい。たとえば、デバイス20の他の側は、デバイス20がドレ

10

20

30

40

50

イン領域 3 6 を中心として対称になるように、示されている側の鏡像としてもよい。あるいは、デバイス 2 0 の他の側は、示されている側と一致してもよい。従って、ドレイン領域 3 6 はデバイス 2 0 の中央に（または中心線に沿って）配置されてもよい。従って、他の側は、第 2 のゲート構造によってドレイン領域 3 6 から隔てられた第 2 のソース領域を含んでもよい。いくつかの実施形態において、第 2 のソース領域および第 2 のゲート構造は、図 1 に示す横方向断面からずれた 1 つ以上の接続構造を介して上述のデバイス 2 0 の対応する領域と連続的に形成される。たとえば、ゲート構造 3 8 は上から見ると（たとえば、図 3 参照）U 字状もしくはアーチ状（たとえば、単一の側方接続部）またはトロイダルもしくはループ状（たとえば、2 つの側方接続部）であってもよい。デバイス 2 0 上述の領域の形状は、これらの例から相當に異なってもよい。

10

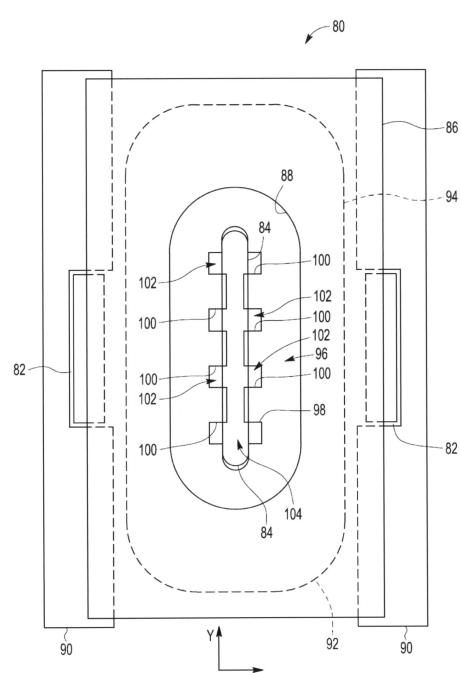

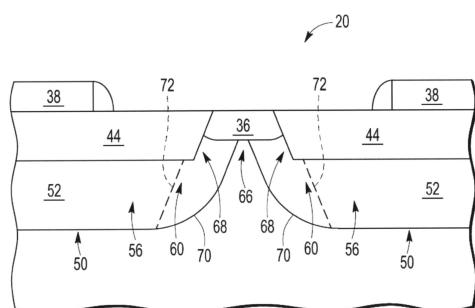

#### 【 0 0 4 3 】

図 2 は、デバイス 2 0 の両方の側のそれぞれの部分を示すための、1 つ又は複数のゲート構造 3 8 からドレイン領域 3 6 へと内向きの、デバイス 2 0 の内側または中央部分の断面図を示す。デバイス 2 0 の側は中央ドレイン領域 3 6 を中心として対称に配向されている。断面図は、拡散が図 1 に示す領域の境界を越えてドーパントを分散させた後のドリフト領域 5 0 の例示的な横方向プロファイルを提示している。ドリフト領域 5 0 はドレイン領域 3 6 と電気的に接続されているが、この例では拡散は、図示されている横方向においてドレイン領域 3 6 の側方範囲全体を通じて完全に延在しているドリフト領域 5 0 をもたらさない。ドリフト領域 5 0 は、ドレイン領域 3 6 の下の開口 6 6 を含む。この例において、開口 6 6 は、拡散によって形成されたドリフト領域 5 0 の電流バスまたは経路 6 8 の間に配置されている。電流路 6 8 は、ドレイン領域 3 6 を、ドリフト領域 5 0 の電界ドリフト部分 5 6 およびデバイス 2 0 の電流路の残りの部分に電気的に連結する。

20

#### 【 0 0 4 4 】

ドリフト領域 5 0 における開口 6 6 は、動作時にドレイン領域 3 6 の下または付近でドリフト領域 5 0 が空乏化される範囲を増大するためにドレイン領域 3 6 における、またはその付近のドリフト領域 5 0 を縮小する。いくつかの場合において、ドリフト領域 5 0 の縮小によって、動作時にドレイン領域 3 6 の下または付近でドリフト領域 5 0 が完全に空乏化することになる。従って、他の様態でリサーフ効果を制限する可能性がある条件（たとえば、長い電界ドリフト領域）にかかわらず、リサーフ効果が増強されることができる。ドレイン領域 3 6 とドリフト領域 5 0 との間の接続を確立するためのドーパントの分散によっても、そのような縮小がもたらされ得る。さらに、電流路 6 8 によって、電荷担体は、低ドーパント濃度または高抵抗のエリアに行き当たることなくドレイン領域 7 2 に達することができる。従って、電荷担体のための 1 つ以上の低抵抗経路を維持しながら、リサーフ効果の増強をもたらすことができる。

30

#### 【 0 0 4 5 】

この例において、各電流路 6 8 は、電界ドリフト部分 5 6 のそれぞれのドレイン側 6 0 から図示のようにドレイン領域 3 6 を通じて部分的にのみ S T I 領域 4 4 に沿って伸長する。電流路 6 8 がドレイン領域 3 6 に達するために内向きに伸長するにつれて、ドリフト領域 5 0 の下側境界 7 0 の深さは低減する。ドレイン領域 3 6 からの拡散は電流路 6 8 の形成に寄与し得るが、電流路 6 8 はドリフト領域 5 0 の内側部分とみなされてもよく、この内側部分はドリフト領域の外側部分（たとえば、電界ドリフト部分 5 6 ）によって包囲されている。ドリフト領域の内側部分は外側部分に対してより狭く、より薄く、ドープ濃度がより低く、かつ／または他の様態で縮小されていてもよい。従って、ドリフト領域の完全なまたは増大した空乏化が達成され得る。

40

#### 【 0 0 4 6 】

拡散に起因して、ドレイン側 6 0 および／または電流路 6 8 は、直立壁ではなく、下側境界 7 0 のような、傾斜した境界を有してもよい。ドリフト領域 5 0 はまた、カットオフ部分 6 2（図 1）および拡散の結果として、ドレイン側 6 0 が（垂直厚さ方向に）狭まっていてもよい。たとえば、電流路 6 8 の垂直厚さは、ドリフト領域 5 0 の電界ドリフト部分 5 6 の垂直厚さよりも小さくてもよい。電流路 6 8 の形状は異なってもよい。電流路 6

50

8は、適切なまたは許容可能なオン抵抗のために構成されたドーパント濃度レベルを有してもよい。ドーパント濃度レベルは、S T I 領域 4 4 からの間隔または距離が増大するにつれて低減されてもよい。

#### 【 0 0 4 7 】

デバイス 2 0 の 1 つ以上のパラメータまたは特性は、開口 6 6 が拡散にかかわらず電流路 6 8 の間に留まることを保証するように構成されてもよい。例は、端部 6 2 ( 図 1 ) の横方向における位置、ドレイン領域 3 6 を形成するインプラントの用量およびエネルギー、ならびに S T I 領域 4 4 の深さを含む。

#### 【 0 0 4 8 】

ドリフト領域 5 0 の側方範囲をドレイン領域 3 6 の下で切り詰めることによって、デバイス 2 0 は、リサーフ効果を低減し得る、ドリフト領域 5 0 のいくらか ( たとえば、内側部分 ) が完全に空乏化されない動作条件を回避することができる。従って、カットオフ部分 6 2 は、従来のドリフト領域の、電界ドリフト部分 5 6 の長さに起因して空乏化が発生する可能性が低い部分を除去し得る。10

#### 【 0 0 4 9 】

電流路 6 8 ( および、従ってドリフト領域 5 0 ) の形状、ドーパント濃度レベル、および他の特性は図示の例とは異なってもよい。たとえば、図示の横方向における電流路 6 8 ( および、従ってドリフト領域 5 0 ) の横幅は異なってもよい。これに代えてまたはこれに加えて、電流路 6 8 のドーパント濃度レベルが異なってもよい。それに応じて、ドリフト領域 5 4 がドレイン領域 3 8 の横幅を通じて伸長する範囲が異なってもよい。これらの特性は、カットオフ部分 6 2 ( 図 1 ) の横方向における位置を変更することによって調整または構成されてもよい。20

#### 【 0 0 5 0 】

いくつかの代替的な実施形態において、ドリフト領域 5 0 は、開口 6 6 なしで、ドレイン領域 3 6 の下でさらに縮小される。たとえば、ドリフト領域 5 0 は、電流路 6 8 を画定するためにドレイン領域 3 6 において ( 垂直厚さにおいて ) 狹くなっていてもよい。そのような場合、電流路 6 8 の一部分 ( または n 型ウェル 5 2 ( 図 1 ) もしくはドレイン領域 3 6 からの他のドーパントの拡散 ) はドレイン領域 3 6 を通じて延在してもよい。ドレイン領域 3 6 の下のそのようなエリアにおけるドーパント濃度レベルは、それを通じて電荷担体がドリフトしてドレイン領域 3 6 に達する S T I 領域 4 4 に沿ったレベルよりも低くてもよい。従って、濃度レベルは所与の深さにおいて、S T I 領域 4 4 からの距離が ( デバイス 2 0 の中央に達するまで ) 増大するにつれて低減してもよい。これに代えてまたはこれに加えて、ドレイン領域 3 6 の下の濃度レベルは深さが増大するとともに低減してもよい。それに応じて、ドレイン領域 3 6 の下のドリフト領域 5 0 の縮小は、ドリフト領域 5 0 の電界ドリフト部分 5 6 において達するレベルに対して低下したドーパント濃度レベルを含んでもよい。30

#### 【 0 0 5 1 】

ドリフト領域 5 0 ( ドレイン領域 3 6 の下の開口の有無にかかわらず ) のドーパント濃度レベルおよび他の特性は、同時係属の共通の譲受人に譲渡される、2 0 1 2 年 5 月 7 日に提出された「ドレイン端部ドリフト縮小を用いる半導体デバイス ( Semiconductor Device with Drain-End Drift Diminution ) 」と題する米国特許出願第 1 3 / 4 6 5 , 7 6 1 号明細書に記載されているように変更されてもよい。40

#### 【 0 0 5 2 】

再び図 1 を参照すると、ドリフト領域 5 0 はまた、さらなるパターニングによってドレイン領域 3 6 との接合部においてまたはそれに沿って縮小されてもよい。パターニングは、図 1 に示す横方向に直交する横方向において行われてもよい。ソース領域 3 4 とドレイン領域 3 6 とは、図 1 に示す横方向において互いに離間されている。その横方向は図 1 に示す線 X と対応し、これはデバイス 2 0 の導電路の大まかな方向と対応している。ドリフト領域 5 0 は、線 X に直交する横方向における切り欠き境界または切り欠きドーパントブ50

ロファイルを含んでもよい。切り欠き境界またはプロファイルは、ドリフト領域 50 とドレイン領域 36 との間の接合部に沿って配置されてもよい。切り欠き境界はドリフト領域 50 のドレイン側に沿って配置され、ドレイン側境界と称される場合がある。切り欠き境界および接合部は、下記に説明するように、図 3 により明瞭に示されている。切り欠きドーパントプロファイルは図 5 により明瞭に示されている。

#### 【0053】

ドリフト領域 50 の切り欠き境界またはプロファイルは、n 型ウェル領域 52 の対応する切り欠き境界またはプロファイルによって形成されてもよい。切り欠き境界またはプロファイルは n 型ウェル領域 52 の端部 62 に沿って配置され、これはいくつかの切り欠き 72 を含む。各切り欠き 72 は、端部 62 の凹んだ部分よりもさらにドレイン領域 36 から横方向において離間されている、端部 62 の凹んでいない部分を画定する。凹んでいない部分はそれぞれの歯部 74 として構成されてもよく、そのうちの 1 つが図 1 に示されている。各切り欠き 72 は一対の歯部 74 の間の間隔を確立する。この例において、端部 62 における切り欠き 72 は STI 領域 44 のドレイン側端部またはコーナー 76 から横方向において離間されており、一方で歯部 74 の側方範囲はドレイン側コーナー 76 の横方向における位置と対応する。図 1 に示す横方向における切り欠き 72 および歯部 74 の側方範囲（たとえば、側方深さ）および位置は図示されている例とは異なってもよい。たとえば、切り欠き 72 は図示されている例よりも深くてもよく、それによって、図 1 に示す破線はチャネル領域 48 に向かってドレイン領域 36 から外方に移動する。これに代えてまたはこれに加えて、切り欠き 72 および歯部 74 の横方向における位置は異なってもよい。

10

#### 【0054】

n 型ウェル領域 52 の拡散は、横方向（側方）X において歯部 74 内に存在するドーパントを分散させる。横方向 X における拡散は、上述のようにドリフト領域 50 とドレイン領域 36 とを接続する。この接続は、ドレイン領域 36 に向かって横方向に伸長する歯部 74 を含むか、または伴ってもよい。一例が図 3 に関連して図示および説明される。

20

#### 【0055】

n 型ウェル領域 52 の拡散は、切り欠き 72 および歯部 74 が画定される直交横方向においてもドーパントを分散させてもよい。そのような分散の一例を、図 5 に示すドーパントプロファイルのグラフ図に関連して下記に説明する。

30

#### 【0056】

n 型ウェル領域 52 の切り欠き状境界またはドーパントプロファイルは、そのようにドーパントが側方に分散しているにもかかわらず、ドリフト領域 50 の特徴を維持してもよい。拡散を引き起こすアニールまたは他の段階は、切り欠き境界または切り欠きドーパントプロファイルが失われるような範囲に分散が発生するのを許容しないようにしながら、電流路 68（図 2）が形成するのを可能にするように構成されてもよい。たとえば、拡散は、切り欠き 72 の境界を図 2 に示すようにドレイン領域 36 に向かってシフトしてもよい。いくつかの場合において、各歯部 74 はそれぞれの電流路 68 に通じてもよい。

#### 【0057】

図 3 は、一実施形態に応じて構成され、ウェル領域ドーパントの拡散後に示されている例示的な LDMOS デバイス 80 の上面図である。上面図は、デバイス 80 の 2 つの横方向 X および Y を示している。第 1 の横方向 X は図 1 の断面に示す横方向 X と対応している。第 2 の横方向 Y は、切り欠き境界が配置されている直交横方向と対応している。

40

#### 【0058】

デバイス 80 のソース領域 82 および中央ドレイン領域 84 は第 1 の横方向 X に沿って互いから離間されている。従って、デバイス 80 の導電路は横方向 X に沿って配向されてもよい。第 2 の横方向 Y は第 1 の横方向 X に直交しており、所望の電流密度を確立するよう意図されているデバイス 80 の幅と対応している。この例において、デバイスは、ゲート構造 86 のドレイン側を画定する橙円開口 88 を有するゲート構造 86 の下の二重フィンガチャネル領域を有する。チャネル領域は、ボディコンタクト領域 90 を介してそれ

50

への接続が確立される、デバイス 8 0 のボディ領域の上に接した、またはその上方のゲート構造 8 6 の下に配置されている。デバイス 8 0 は、上述のように n チャネルデバイスであってもよい。n 型ウェル領域 9 2 は、ボディ領域に隣接し、かつゲート構造 8 6 の下にある外側境界 9 4 を有する。この例において、ボディ領域および n 型ウェル領域 9 2 は一直線上にある、または連続している。他の実施形態において、n 型ウェル領域 9 2 はボディ領域から離間されている（たとえば、図 1 参照）。

#### 【 0 0 5 9 】

n 型ウェル領域 9 2 の内側部分が、中央ドレイン領域 8 4 を包囲および接続するドリフト領域 9 6 を画定する。ドリフト領域 9 6 は、ドリフト領域 9 6 とドレイン領域 8 4 との間の接合部に沿って横方向 Y 内に配置されている切り欠き境界 9 8 を有する。切り欠き境界 9 8 は、n 型ウェル領域 9 2 の内側境界と対応している。切り欠き境界 9 8 は、ドリフト領域 9 6 とドレイン領域 8 4 とを結合するいくつかの歯部、枝角部、または他の突起 100 を含む。歯部 100 は櫛形状または他の周期的なパターンに配列されてもよい。切り欠き境界 9 8 は、それぞれの対の歯部 100 の間の切り欠きまたは間隙 102 を含む。切り欠き境界 9 8 に沿った各切り欠き 102 は、上述の p 型エピタキシャル層との接合部を画定してもよい。従って、各切り欠き 102 は、n 型ウェル領域 9 2 を形成するように意図されている n 型インプラントによってドープされていない p 型エピタキシャル層の部分と対応してもよい。従って、各切り欠き 102 は p 型導電性を有してもよい。代替的に、各切り欠き 102 は p 型導電性を有しなくてもよく、代わりに、歯部 100 のドーパント濃度レベルよりも低い n 型ドーパント濃度レベルを有してもよい。n 型の例において、各切り欠き 102 は非常に低濃度にドープされてもよい（たとえば、ほぼ、本明細書に記載のエピタキシャル層のドーパント濃度レベル）。いずれの場合においても、ドリフト領域 9 6 は、ドリフト領域 9 6 が空乏化される程度を増大するためにドリフト領域 9 6 をさらに縮小するために横方向 Y における切り欠きドーパントプロファイルを有する。従って、ドレイン領域 8 4 付近のドリフト領域 9 6 の部分においてリサーフ効果が増強されることが可能、これはそのような部分が、それに沿って空乏化が発生する P N 接合部から相当に離れているときに有用であり得る。切り欠き 102 が n 型領域（たとえば、ウェル領域）と p 型領域（たとえば、エピタキシャル層）との間の接合部または境界を提示する場合において、ドレイン領域 8 4 付近のエリアにおけるドリフト領域 8 4 は横方向 X、Y と垂直方向との両方において空乏化される。空乏化は、たとえば、ドレイン領域 7 4 とソース領域 7 2 との間の電圧差が高いときのデバイスの O F F 状態においてはドリフト領域 8 2 の側方範囲全体に及んでもよい。そのような広範に及ぶ空乏化が、絶縁破壊電圧レベルを上昇させるのを助けるために、ドリフト領域 8 2 内およびその周囲の電界を低減することができる。

#### 【 0 0 6 0 】

横方向 Y に沿った各歯部 100 の幅および各切り欠き 102 のサイズは異なってもよい。いくつかの例において、各歯部 100 の幅は約 1 . 0  $\mu\text{m}$  ~ 約 10  $\mu\text{m}$  の範囲内に入るが、各歯部 100 の幅はまた、この範囲よりも小さくても大きくてもよい。いくつかの例において、隣接する歯部 100 間の間隙または距離（たとえば、各切り欠き 102 のサイズ）は約 1 . 0  $\mu\text{m}$  ~ 約 10  $\mu\text{m}$  の範囲内に入るが、隣接する歯部 100 間の距離はまた、この範囲よりも小さくても大きくてもよい。各歯部 100 の幅および / または各切り欠き 102 のサイズは、たとえば、特定のオン抵抗 R<sub>dson</sub> および絶縁破壊電圧 B<sub>Vds</sub> を含むさまざまなデバイスパラメータを達成するように調整またはカスタマイズされてもよい。たとえば、各歯部 100 の横幅（たとえば、横方向 Y における）は、ドリフト領域 9 6 の抵抗を変更するように調整されてもよい。サイズ決定は、同じく異なってもよいドリフト領域 9 6 のドーパント濃度に応じて異なってもよい。各歯部 100 の横方向における長さも異なってもよい。

#### 【 0 0 6 1 】

ドリフト領域 9 6 の歯部 100 は、横方向 X に沿ってドレイン領域 8 4 と横方向において重なってもよい。そのような横方向における重なりは、導電路の厚さ（たとえば、図 2

10

20

30

40

50

内の導電路 6 8 参照 ) の厚さと対応してもよい。横方向における重なりは、ドレイン領域 8 4 およびドリフト領域 9 6 の電気的結合を確立してもよい。そのような横方向における重なりは図 3 の上面図よりも図 2 の断面図に容易に示されており、歯部 1 0 0 がドレイン領域 8 4 に横方向において重なる範囲は図示の例とは異なってもよい。

#### 【 0 0 6 2 】

歯部 1 0 0 および切り欠き 1 0 2 の形状は示されている例とは異なってもよい。歯部 1 0 0 および / または切り欠き 1 0 2 は、方形波状または他の直線的なパターンを呈する必要はなく、ドリフト領域 9 6 とドレイン領域 8 4 との間の任意のタイプの不均一な接合部を呈してもよい。たとえば、切り欠き境界は鋸歯または他の三角形切り欠きパターンを有してもよい。これに代えてまたはこれに加えて、切り欠きは丸みを帯びたコーナーまたは辺を有してもよい。歯部 1 0 0 および切り欠き 1 0 2 の形状およびサイズは異なってもよい。切り欠き境界 9 8 によってもたらされる利点は、n 型領域と p 型領域との間の電荷平衡に基づくものではない。事実、切り欠き境界 9 8 に沿って相当の電荷不均衡が存在する。

#### 【 0 0 6 3 】

図 3 の例において、切り欠き境界 9 8 はドリフト領域 9 6 における開口 1 0 4 を画定する。従って、ドリフト領域 9 6 の少なくとも一部分は切り欠き境界 8 4 に沿ってドレイン領域 8 4 の下で切り詰められてもよい。開口 1 0 4 は完全にまたは部分的にドレイン領域 8 4 の下に配置されてもよい。この例において、開口 1 0 4 はドレイン領域 8 4 ( たとえば、切り欠き 1 0 2 参照 ) を越えて延在する。開口 1 0 4 は、境界 9 8 のような、1 つ以上の櫛形状境界を含む。この例において、開口 1 0 4 は、横方向 Y において延在する開口の各側に櫛形状境界を有する。

#### 【 0 0 6 4 】

開口 1 0 4 の切り欠き境界は、周期的なパターンまたは一定のパターンを呈してもよい。この例において、パターンは横方向 Y において配置されている辺に沿った方形波状のパターンである。開口 1 0 4 の他の辺または端部はそのパターンを呈する必要はなく、異なるパターンを有してもよい。他の実施形態において、切り欠き境界は開口 1 0 4 の1 つ以上の辺または端部に沿った非周期的なパターンを有する。

#### 【 0 0 6 5 】

歯部 1 0 0 の側方分布、配列、間隔、サイズ、深さ ( 垂直厚さ ) 、構成、および他の特性は、デバイス 8 0 の設計上の柔軟性をもたらすことができる。たとえば、デバイス 8 0 の B V d s s および R d s o n 値は下記にさらに説明するように、特定の用途に適合するために調整されてもよい。ドリフト領域 9 6 を通じた全体的な導電が横方向 Y を通じて対処されてもよい。用途仕様に適応するために切り欠きドーパントプロファイルに対する調整が行われるよく、デバイス 8 0 のチャネル幅のようなデバイス 8 0 の他の特性が所望のとおりに構成されることが可能になる。切り欠きドーパントプロファイルはさまざまなデバイス設計に適合する。たとえば、デバイス 8 0 は、横幅が所望のとおりのサイズにされてもよい二重フィンガチャネル構成を有してもよい。

#### 【 0 0 6 6 】

上述のデバイスは、簡略化された形態で示されている。たとえば、図 1 ~ 図 3 は、ソース領域、ドレイン領域、およびゲート構造との電気的結合のために構成された、導電性 ( たとえば、抵抗 ) コンタクト、および他の金属層を示していない。デバイスは、説明を容易にするために図 1 には示されていない、接続、分離、不動態化、および他の目的のためのいくつかの他の構造または構成要素を有してもよい。たとえば、デバイスは任意の数の追加の分離領域または層を含んでもよい。いくつかの例において、別の p 型エピタキシャル層 ( 図示せず ) が原基板とデバイスエリアとの間に配置されてもよい。1 つ以上のさらなる S T I 領域、他の分離トレーンチ、および / または分離ウェル ( 図示せず ) がデバイスエリアおよび / またはデバイスの他の領域を分離するために設けられてもよい。

#### 【 0 0 6 7 】

半導体基板 2 2 における上述の半導体領域のドーパント濃度、厚さ、および他の特性は

10

20

30

40

50

異なってもよい。図1の示す実施形態の一例において、上述の半導体領域は以下のとおりその濃度および厚さを有してもよい。

### 【0068】

【表1】

|               | 濃度                                                     | 厚さ                           |    |

|---------------|--------------------------------------------------------|------------------------------|----|

| p-e p i 2 4 : | $1 \times 10^{13} \sim 1 \times 10^{15} / \text{cm}^3$ | $3 \sim 10 \mu\text{m}$      |    |

| 基板26:         | $1 \times 10^{15} \sim 1 \times 10^{18} / \text{cm}^3$ | 該当なし                         |    |

| ボディ30:        | $1 \times 10^{16} \sim 1 \times 10^{18} / \text{cm}^3$ | $0.5 \sim 1.5 \mu\text{m}$   |    |

| ソース34:        | $1 \times 10^{21} \sim 5 \times 10^{21} / \text{cm}^3$ | $0.15 \sim 0.25 \mu\text{m}$ |    |

| ドレイン36:       | $1 \times 10^{21} \sim 5 \times 10^{21} / \text{cm}^3$ | $0.15 \sim 0.25 \mu\text{m}$ | 10 |

| NLDD46:       | $1 \times 10^{18} \sim 1 \times 10^{19} / \text{cm}^3$ | $0.2 \sim 0.3 \mu\text{m}$   |    |

| nウェル52:       | $5 \times 10^{15} \sim 5 \times 10^{17} / \text{cm}^3$ | $0.5 \sim 1.5 \mu\text{m}$   |    |

濃度および厚さは他の実施形態においては異なってもよい。たとえば、原基板26のドーパント濃度は相当に異なってもよい。

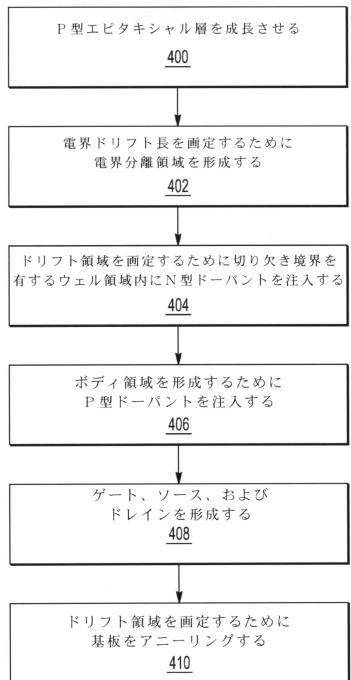

### 【0069】

図4は、上述のような切り欠きドーパントプロファイルまたは切り欠きドレイン側境界を有するドリフト領域を有するデバイスを作製するための例示的な作製方法を示している。方法は、上述の特徴の1つ以上を有する表面電界緩和(リサーフ)トランジスタを作製するように意図されてもよい。トランジスタは半導体基板を用いて作製され、その領域または層は、上述のnチャネルの例の導電型を有してもよく、または代替的にpチャネルデバイスをサポートするように構成されてもよい。方法は一連の動作を含み、説明を簡便にするためにその重要な部分のみが示されている。動作の順序は他の実施形態においては異なってもよい。作製方法は任意の特定のドーピングメカニズムには限定されず、将来開発されるドーピング技法を含んでもよい。

### 【0070】

方法は、p型エピタキシャル層(p-e p i)が高濃度ドープp型半導体基板上に成長される動作400によって開始するか、またはそれを含んでもよい。いくつかの場合において、動作400は、エピタキシャル層を成長させる前に、1つ以上の埋め込みデバイス分離層の、たとえば、イオン注入による形成を含む。1つ又は複数の埋め込みデバイス分離層は、リサーフトランジスタの活性エリアを通じて延在するためのマスクによって構成されてもよい。いくつかの場合において、動作400は、別のp型エピタキシャル層の成長を含む。任意の数のエピタキシャル層が成長されてもよい。

### 【0071】

この実施形態において、STI領域(または電界分離領域)が、動作402において電界ドリフト長を画定するために基板に形成される。STI領域は、任意の既知のまたは今後開発される手順によって形成されてもよい。たとえば、動作402は、トレンチの形成およびトレンチ内の1つ以上の材料の堆積(たとえば、化学気相成長、またはCVD)を含んでもよい。いくつかの実施形態において、トレンチはシリコンオキサイドを充填される。追加のまたは代替的な材料が堆積されてもよい。代替的な実施形態において、STI領域はドリフト領域が形成された後に形成される。

### 【0072】

動作404において、エピタキシャル層のウェル領域において基板がドーピングされる。ウェル領域は、トランジスタの蓄積領域およびドリフト領域を形成するように意図されてもよい。ドーピング手順は、n型ドーパント注入を含んでもよい。たとえば、ウェル領域は、ウェル領域が図1に示すように構成されるようにマスクを用いて形成されてもよい。従って、ウェル領域は、上述のように、ドレイン領域における、またはその下のドリフト領域を縮小するためにドリフト領域のドレイン側の、直立、垂直、または他のカットオフ部分を有する側方プロファイルを有してもよい。たとえば、ウェル領域は、上述のように、ドレイン領域の下に開口を含んでもよい。いくつかの場合において、ウェル領域の側

10

20

30

40

50

方範囲は、ドレイン領域のロケーションと重ならない。ウェル領域のドレイン側は、図1の断面に示す横方向に直交する横方向に沿った切り欠き境界をも含む。切り欠き境界は、ウェル領域における開口に沿って配置されてもよい。イオン注入手順は、本明細書に記載のように、ドリフト領域の第2のまたは最終プロファイルまたは領域に向かって注入されたドーパントイオンを分散させる、1つ以上のアニーリングまたは他の拡散手順と組み合わされてもよい。従って、結果もたらされるドリフト領域は、本明細書に記載のように、切り欠き境界（たとえば、ドレイン領域の下に開口を有するオープンドレイン実施形態における）または切り欠きドーパントプロファイル（たとえば、ドレイン領域の下に開口を有しない閉ドレイン実施形態における）をも含んでもよい。

## 【0073】

10

動作406において、p型ウェルが基板のボディ領域にドーピングすることによって形成される。いくつかの実施形態において、動作406は注入手順を含む。ボディ領域は、上述のように、ドリフト領域から離間されてもよく、またはドリフト領域に隣接してもよい。ボディ領域のための高濃度ドープp型コンタクト領域が、別個のイオン注入手順によってp型ウェル内に形成されてもよい。

## 【0074】

その後、作製工程は、まとめて動作408内に示されている1つ以上の手順を含んでもよい。手順はさまざまな順序で実施されてもよい。追加のまたは代替的な手順が実施されてもよい。最初にゲート構造が形成されてもよい。その後、ソース領域の自己整合のためにゲート構造を使用してソース領域およびドレイン領域が形成されてもよい。1つ以上のn型イオン注入手順が実行されてもよい。たとえば、ソース領域およびドレイン領域の一方または両方の形成は、1つ以上の遷移領域（たとえば、図1参照）を作成するためにゲート構造の側壁スペーサを形成する前の中濃度の注入を含んでもよい。その後、側壁スペーサの形成後の高濃度の注入が、そのような遷移領域に隣接するソース領域および/またはドレイン領域を形成するために実施されてもよい。

20

## 【0075】

ドレイン領域は、動作408において、動作404において形成されたウェル領域と横方向において重なる領域内に形成されてもよいし、形成されなくてもよい。重なりは、トランジスタのための導電路を画定してもよい。しかしながら、重なりは、上述および図1に図示のように、ドレインが形成される領域を通じて横方向に延在していない。

30

## 【0076】

動作410において、基板がアニーリングされる。アニーリング手順が実施される様式は異なってもよい。アニーリング手順の結果として、ドリフト領域のためのドーパントイオンが再分配されて、ウェル領域からドレイン領域までの1つ以上の電流路が形成されてもよい。従って、ドリフト領域は、ドレイン領域に電気的に結合されてもよい。いくつかの場合において、ドリフト領域はドレイン領域を通じて横方向に延在するが、上述のように容量は縮小している。

## 【0077】

注入およびアニーリング手順は、ドレイン領域の下のまたはそれに沿ったドリフト領域が、導電路における第1の部分、および、導電路の外側のより薄い第2の部分を含むように構成されてもよい。従って、第1の部分は、電流パスまたは経路を形成してもよく、一方で第2の部分は、より容易な空乏化を通じてリサーフ効果を増強するように構成される。電流パスのために適切な低抵抗を維持するために、第1の部分は、第2の部分よりも高いドーパント濃度レベルを有してもよい。

40

## 【0078】

作成手順のさまざまな時点において追加の動作が実施されてもよい。たとえば、1つ以上の動作はデバイスの活性エリアを画定するように意図されてもよい。いくつかの場合において、そのような動作は、1つ以上のデバイス分離ウェル、層、または他の領域の形成を含んでもよい。1つ以上の金属層が堆積されてもよい。任意の数の追加のSTI領域が形成されてもよい。

50

## 【0079】

図5は、ドレイン領域との接合部に沿ったドリフト領域のドーパント濃度レベルのグラフ図である。プロットは、横方向Y(図3)の関数としてのドーパント濃度レベルを示している。ドーパント濃度レベルは、カットオフ部分または端部62(図1)と切り欠き72(図1)との間の他の横方向Xに沿った位置についてのものであってもよい。

## 【0080】

実線500は、拡散前のドーパント濃度レベルを示している。たとえば、実線は、図1に示すようなn型ウェル領域52のドーパントプロファイルを示してもよい。拡散の効果は破線502によって示されている。実線500の拡散前ピークレベルは、ドーパントが、切り欠きに関連付けられる拡散前の凹みへと拡散する結果として低減されている。ピーカドーパント濃度レベルは、ドリフト領域とドレイン領域との間に導電路を形成する、他の横方向Xにおける拡散の結果としても低減してもよい。

10

## 【0081】

いくつかの実施形態において、図5に示す横方向Yにおける側方拡散はまた、導電路間の切り欠きを充填する。従って、切り欠きドーパントプロファイルは、中濃度ドーピングと低濃度ドーピングが交互になった領域を呈してもよい。切り欠きの低濃度ドーピングの結果としてn型ドープ接合部がもたらされる場合であっても、ドレイン領域との接合部は均一ではない。低濃度ドープ領域が周期的に存在することによって、ドリフト領域がさらに縮小し(より低いドーパント濃度レベルを通じて)、それによってリサーフ効果を増強してもよい。

20

## 【0082】

上述のドリフト領域のドーパント濃度レベルは、ドリフト領域のドレイン側境界を画定するのに使用されてもよい。ドーパント濃度レベルは、横方向Yにおいてドレインの端部に沿って、方形波、正弦波、または他のさまざまな関数で表されるように変更されてもよい。上述の歯部は、相対的に高いドーパント濃度と対応してもよい。ドーパント濃度レベルは、歯部間の空間内で0に達するかまたは0に近づいてもよい。

## 【0083】

第1の態様において、デバイスは、半導体基板と、半導体基板における、第1の横方向に沿って互いから離間されているソース領域およびドレイン領域と、半導体基板における、動作時にソース領域およびドレイン領域の間にバイアス電圧が印加されるとそれを通じて電荷担体がドリフトするドリフト領域とを含む。ドリフト領域は、ドリフト領域とドレイン領域との間の接合部に沿った第2の横方向における切り欠きドーパントプロファイルを有する。

30

## 【0084】

第2の態様において、電子装置は、半導体基板と、半導体基板に配置されている表面電界緩和(リサーフ)トランジスタとを含む。リサーフトランジスタは、第1の導電型を有し、動作時にチャネルが形成される第1の半導体領域と、第2の導電型を有し、第1の横方向に沿って互いから離間されている第2の半導体領域および第3の半導体領域と、第2の導電型を有し、動作時に第2の半導体領域と第3の半導体領域との間にバイアス電圧が印加されると第1の半導体領域内に形成されるチャネルからの電荷担体がそれを通じてドリフトする第4の半導体領域とを含む。第4の半導体領域は、第3の半導体領域と第4の半導体領域との間の接合部に沿って第2の横方向における切り欠きドーパントプロファイルを有する。

40

## 【0085】

第3の態様において、トランジスタを作製する方法は、ドリフト領域を形成するための基板の第1の領域内にドーパントを注入するステップと、ソース領域およびドレイン領域を、それぞれ基板の第2の領域および第3の領域内に形成するステップであって、第2の領域および第3の領域は第1の横方向において互いから離間されている、形成するステップとを含む。第1の領域は第3の領域を通じて横方向に延在しておらず、第2の横方向における切り欠きドレイン側境界を含む。

50

## 【0086】

誘電体または他の絶縁体の上に配置された導電性ゲート電極を有する半導体デバイスは、金属ゲート電極および酸化物ゲート絶縁体がないにもかかわらず、MOSデバイスとみなされてもよい。従って、金属酸化膜半導体という用語および略称「MOS」は、そのようなデバイスが金属または酸化物を利用せず、単純な金属の代わりの導電性材料、たとえば、金属、合金、シリサイド、ドープ半導体などと、酸化物以外の絶縁材料（たとえば、窒化物、オキシ窒化物混合物など）とのさまざまな組合せを利用するにもかかわらず、使用されてもよい。従って、本明細書において使用される場合、MOSおよびLDMOSという用語は、そのような変形形態を含むように意図されている。

## 【0087】

本発明は、以下の特許請求の範囲およびそれらの均等物によって定義され、この節における記載にはこれらの特許請求項に対する限定としてとられるべきものはない。本発明のさらなる態様および利点は、好ましい実施形態とともに上述しており、独立してまたは組み合わせて後に特許請求され得る。

## 【0088】

本発明をさまざまな実施形態を参照して上述したが、本発明の範囲から逸脱することなく多くの変更および修正を行うことができるることは理解されたい。それゆえ、上記の詳細な説明は限定ではなく例示とみなされること、ならびに、すべての均等物を含む以下の特許請求の範囲が、本発明の精神および範囲を画定するように意図されていることが理解されることが意図されている。

10

20

## [項目1]

デバイスであって、

半導体基板と、

前記半導体基板におけるソース領域およびドレイン領域であって、第1の横方向に沿つて互いから離間されているソース領域およびドレイン領域と、

前記半導体基板におけるドリフト領域であって、動作時に前記ソース領域と前記ドレイン領域との間にバイアス電圧が印加されるとドリフト領域を通じて電荷担体がドリフトするドリフト領域と、を備え、

前記ドリフト領域は、該ドリフト領域と前記ドレイン領域との間の接合部に沿った第2の横方向において切り欠きドーパントプロファイルを有する、デバイス。

30

## [項目2]

前記ドリフト領域は前記ドレイン領域の下の開口を備え、

前記開口は櫛形状境界を有する、項目1に記載のデバイス。

## [項目3]

前記ドリフト領域は、前記ドリフト領域と前記ドレイン領域との間の接合部において、前記ドレイン領域の垂直厚さ方向に狭まっている、項目1に記載のデバイス。

## [項目4]

前記ドリフト領域は前記ドレイン領域を通じて横方向に延在していない、項目1に記載のデバイス。

## [項目5]

前記ドリフト領域は外側部分および内側部分を備え、該内側部分は該外側部分によって包囲され、前記ドレイン領域の下に配置されており、

前記内側部分は、動作時に前記ドリフト領域の完全な空乏化が達成されるように、前記外側部分に対して縮小されている、項目1に記載のデバイス。

40

## [項目6]

前記切り欠きドーパントプロファイルは方形波状の切り欠きパターンを有する、項目1に記載のデバイス。

## [項目7]

前記切り欠きドーパントプロファイルは周期的な切り欠きパターンを有する、項目1に記載のデバイス。

50

[項目 8]

前記半導体基板はエピタキシャル層を備え、前記ソース、ドレイン、およびドリフト領域は該エピタキシャル層に形成されており、

前記ドリフト領域は前記エピタキシャル層に対する切り欠きの境界に沿って前記ドレン領域の下で切り詰められている、項目 1 に記載のデバイス。

[項目 9]

前記半導体基板において前記ソース領域と前記ドレン領域との間にトレンチ分離領域をさらに備え、

前記ドリフト領域は、前記トレンチ分離領域の下の第 1 の領域と、前記ドレン領域の下の第 2 の領域とを備え、

前記ドリフト領域の前記第 2 の領域におけるドーパント濃度は、前記第 1 の領域に対して低減されている、項目 1 に記載のデバイス。

10

[項目 10]

電子装置であって、

半導体基板と、

前記半導体基板におけるリサーフトランジスタと、を備え、該リサーフトランジスタは

、

第 1 の導電型を有し、動作時にチャネルが形成される第 1 の半導体領域と、

第 2 の導電型を有し、第 1 の横方向に沿って互いから離間されている第 2 の半導体領域

および第 3 の半導体領域と、

20

前記第 2 の導電型を有する第 4 の半導体領域であって、前記第 2 の半導体領域と第 3 の半導体領域との間にバイアス電圧が印加されると、電荷担体が動作時に前記第 1 の半導体領域に形成される前記チャネルからを第 4 の半導体領域を通じてドリフトする第 4 の半導体領域と、を備え、

前記第 4 の半導体領域は、前記第 3 の半導体領域と第 4 の半導体領域との間の接合部に沿って第 2 の横方向に切り欠きドーパントプロファイルを有する、電子装置。

[項目 11]

前記第 4 の半導体領域は前記第 3 の半導体領域の下の開口を備え、

前記開口は櫛形状境界を有する、項目 10 に記載の電子装置。

[項目 12]

30

前記第 4 の半導体領域は前記第 3 の半導体領域を通じて横方向に延在していない、項目 10 に記載の電子装置。

[項目 13]

前記第 4 の半導体領域は外側領域および内側領域を備え、該内側領域は該外側領域によって包囲され、前記第 3 の半導体領域の下に配置されており、

前記内側領域は、動作時に前記第 4 の半導体領域の完全な空乏化が達成されるように、前記外側領域に対して縮小されている、項目 10 に記載の電子装置。

[項目 14]

前記半導体基板はエピタキシャル層を備え、前記第 1 の半導体領域、第 2 の半導体領域、第 3 の半導体領域、および第 4 の半導体領域は該エピタキシャル層に形成されており、

40

前記第 4 の半導体領域は前記エピタキシャル層に対する切り欠きの境界に沿って前記第 3 の半導体領域の下で切り詰められている、項目 10 に記載の電子装置。

[項目 15]

前記リサーフトランジスタは、前記第 2 の半導体領域と前記第 3 の半導体領域との間にトレンチ分離領域をさらに備え、

前記第 4 の半導体領域は、前記トレンチ分離領域の下の第 1 の領域と前記第 3 の半導体領域の下の第 2 の領域とを備え、

前記第 4 の半導体領域の前記第 2 の領域におけるドーパント濃度は、前記第 1 の領域に対して低減されている、項目 10 に記載の電子装置。

[項目 16]

50

トランジスタを作製する方法であって、

ドリフト領域を形成するための基板の第1の領域にドーパントを注入するステップと、

前記基板の第2の領域および第3の領域にソース領域およびドレイン領域をそれぞれ形

成するステップであって、該第2の領域および該第3の領域は第1の横方向において互い

から離間されている、前記ステップと、を備え、

前記第1の領域は前記第3の領域を通じて横方向に延在しておらず、第2の横方向に切

り欠きのドレイン側境界を有する、方法。

[項目17]

前記第1の領域は前記第3の領域の下の開口を備え、該開口は切り欠きのドレイン側境

界を有する、項目16に記載の方法。

10

[項目18]

前記ドリフト領域が前記ドレイン領域に電気的に結合されるように、前記基板をアニ

リングするステップをさらに備える、項目16に記載の方法。

[項目19]

前記第1の領域および前記第3の領域は横方向において重ならない、項目16に記載の

方法。

[項目20]

前記基板のエピタキシャル層を形成するステップをさらに備え、前記第1の領域、第2

の領域、および第3の領域は前記エピタキシャル層に配置される、項目16に記載の方法

。

20

【図1】

【図3】

【図2】

【図4】

【図5】

---

フロントページの続き

(72)発明者 シン リン

アメリカ合衆国 85045 アリゾナ州 フェニックス ダブリュ.グレンヘイブン ドライブ

2816

(72)発明者 チホン チャン

アメリカ合衆国 85225 アリゾナ州 チャンドラー エヌ.ローラ ドライブ 465

(72)発明者 ジアン - カイ ツオ

アメリカ合衆国 85249 アリゾナ州 チャンドラー イー.アクエリアス プレイス 41

30

審査官 市川 武宜

(56)参考文献 米国特許出願公開第2012/0217579(US, A1)

特開2000-260984(JP, A)

特開平07-050413(JP, A)

特開2010-010408(JP, A)

特開平05-259444(JP, A)

特開平07-038097(JP, A)

特開2005-093775(JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/336

H01L 29/06

H01L 29/78