(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6482559号

(P6482559)

(45) 発行日 平成31年3月13日(2019.3.13)

(24) 登録日 平成31年2月22日(2019.2.22)

(51) Int.Cl.

HO3H 11/12 (2006.01)

F 1

HO3H 11/12

A

請求項の数 13 (全 10 頁)

(21) 出願番号 特願2016-536722 (P2016-536722)

(86) (22) 出願日 平成26年12月1日 (2014.12.1)

(65) 公表番号 特表2017-505007 (P2017-505007A)

(43) 公表日 平成29年2月9日 (2017.2.9)

(86) 國際出願番号 PCT/US2014/067875

(87) 國際公開番号 WO2015/088801

(87) 國際公開日 平成27年6月18日 (2015.6.18)

審査請求日 平成29年11月13日 (2017.11.13)

(31) 優先権主張番号 14/103,645

(32) 優先日 平成25年12月11日 (2013.12.11)

(33) 優先権主張国 米国(US)

(73) 特許権者 507364838

クアルコム、インコーポレイテッド

アメリカ合衆国 カリフォルニア 921

21 サンディエゴ モアハウス ドラ

イブ 5775

(74) 代理人 100108453

弁理士 村山 靖彦

(74) 代理人 100163522

弁理士 黒田 晋平

(72) 発明者 ギレーシュ・ラジェンドラン

アメリカ合衆国・カリフォルニア・921

21-1714・サン・ディエゴ・モアハ

ウス・ドライブ・5775

最終頁に続く

(54) 【発明の名称】面積効率の良いベースバンドフィルタ

## (57) 【特許請求の範囲】

## 【請求項1】

入力ポートにおいて入力電流信号を受信し、かつフィードバックトランスクンダクタンスに基づいて出力ポートにおいてフィルタリング済み出力電圧信号を生成するように構成される電流/電圧(I-V)フィルタであって、前記入力電流信号は入力DC電流を含む、電流/電圧(I-V)フィルタと、

前記出力ポートと前記入力ポートとの間に接続されるフィードバック回路であって、前記フィードバック回路は、前記入力DC電流を信号グラウンドに結合し、かつ前記I-Vフィルタに前記フィードバックトランスクンダクタンスを与えるように構成される少なくとも1つのトランジスタを有し、前記フィードバック回路は、前記入力ポートの第1の入力端子に接続されるドレン端子と、信号グラウンドに接続されるソース端子と、前記出力ポートの第1の出力端子および第2の出力端子にそれぞれ接続される第1のゲート端子および第2のゲート端子とを有する、第1のトランジスタおよび第2のトランジスタを備える、フィードバック回路と

を備える、装置。

## 【請求項2】

前記フィルタリング済み出力電圧信号を受信し、かつ対応するフィルタリング済み電圧信号を生成するように構成される二次フィルタをさらに備える、請求項1に記載の装置。

## 【請求項3】

前記対応するフィルタリング済み電圧信号を受信し、かつ局部発振器信号に基づいて、

対応する電流を無線周波数信号にアップコンバートするように動作するアップコンバータに入力される電流を生成するように構成されるトランスコンダクタをさらに備える、請求項2に記載の装置。

【請求項4】

前記I-Vフィルタは、前記出力ポートから前記入力ポートまでの少なくとも1つのフィードバック要素を有するマルチステージフィルタを備える、請求項1に記載の装置。

【請求項5】

前記マルチステージフィルタは、利得ステージおよびトランスコンダクタンスステージを備える、請求項4に記載の装置。

【請求項6】

前記フィードバック回路は、前記入力ポートの第2の入力端子に接続されるドレイン端子と、前記信号グラウンドに接続されるソース端子と、前記出力ポートの前記第1の出力端子および前記第2の出力端子にそれぞれ接続される第1のゲート端子および第2のゲート端子とを有する、第3のトランジスタおよび第4のトランジスタを備える、請求項1に記載の装置。

10

【請求項7】

前記フィードバック回路は、前記入力ポートの前記第1の入力端子と前記出力ポートの前記第1の出力端子との間に接続される第1のキャパシタと、前記入力ポートの前記第2の入力端子と前記出力ポートの前記第2の出力端子との間に接続される第2のキャパシタとを備える、請求項6に記載の装置。

20

【請求項8】

電流/電圧(I-V)フィルタによって、フィードバックトランスコンダクタンスに基づいて出力ポートにおいてフィルタリング済み出力電圧信号を生成するために、入力ポートにおいて入力電流信号をフィルタリングするステップであって、前記入力電流信号は入力DC電流を含む、ステップと、

フィードバック回路によって、前記出力ポートを前記入力ポートに結合するステップであって、前記フィードバック回路は、前記入力DC電流を信号グラウンドに結合し、かつ前記I-Vフィルタに前記電流に対する前記フィードバックトランスコンダクタンスを与えるように構成され、前記フィードバック回路は、前記入力ポートの第1の入力端子に接続されるドレイン端子と、信号グラウンドに接続されるソース端子と、前記出力ポートの第1の出力端子および第2の出力端子にそれぞれ接続される第1のゲート端子および第2のゲート端子とを有する、第1のトランジスタおよび第2のトランジスタを備える、ステップと

30

を備える、方法。

【請求項9】

二次フィルタによって前記出力電圧信号を受信し、かつ対応するフィルタリング済み電圧信号を生成するステップをさらに備える、請求項8に記載の方法。

【請求項10】

前記対応するフィルタリング済み電圧信号を受信し、かつ局部発振器信号に基づいて、対応する電流を無線周波数信号にアップコンバートするように動作するアップコンバータに入力される電流を生成するステップをさらに備える、請求項9に記載の方法。

40

【請求項11】

前記電流/電圧(I-V)フィルタは、前記出力ポートから前記入力ポートまでの少なくとも1つのフィードバック要素を有するマルチステージフィルタを備える、請求項8に記載の方法。

【請求項12】

前記マルチステージフィルタは、利得ステージおよびトランスコンダクタンスステージを備える、請求項11に記載の方法。

【請求項13】

前記フィードバック回路は、前記入力ポートの第2の入力端子に接続されるドレイン端子と、前記信号グラウンドに接続されるソース端子と、前記出力ポートの前記第1の出力

50

端子および前記第2の出力端子にそれぞれ接続される第1のゲート端子および第2のゲート端子とを有する、第3のトランジスタおよび第4のトランジスタを備え、前記フィードバック回路は、前記入力ポートの前記第1の入力端子と前記出力ポートの前記第1の出力端子との間に接続される第1のキャパシタと、前記入力ポートの前記第2の入力端子と前記出力ポートの前記第2の出力端子との間に接続される第2のキャパシタとを備える、請求項8に記載の方法。

【発明の詳細な説明】

【技術分野】

【0001】

関連出願の相互参照

10

本出願は、参照によりその内容全体が本明細書に明確に組み込まれる、本願の譲受人が所有する2013年12月11日出願の米国非仮特許出願第14/103,645号の優先権を主張する。

【0002】

本出願は包括的には、アナログフロントエンドの動作および設計に関し、より詳細には、面積効率の良いベースバンドフィルタの動作および設計に関する。

【背景技術】

【0003】

ワイヤレスデバイスは、次第に複雑になりつつあり、現在では、マルチモードおよびマルチバンド動作を提供するのが普通である。結果として、回路面積の効率的な利用が主な問題となってきた。通常のトランスマッタフロントエンドは、デジタルデータをベースバンドアナログ信号に変換するデジタル/アナログコンバータ(DAC)を含む。ベースバンドフィルタリングのような信号調整を用いて、アップコンバート用混合器に入力するためのベースバンドアナログ信号を準備する。トランスマッタフロントエンドが依然として所望のレベルの信号対雑音比(SNR)性能を達成できるようにしながら、信号調整にできる限り少ない回路面積を利用させることができることを望ましい。

20

【0004】

通常のベースバンドフィルタは、増幅器と、トランスコンダクタと、フィルタ応答を設定するために用いられる、フィードバック構成における種々の受動構成要素とを含むことができる。たとえば、フィルタ応答は、フィードバック構成において使用される抵抗器とキャパシタとの積から決定することができる。通常、回路面積の大部分は、受動構成要素および増幅器面積によって占有され、それによって、回路面積は、所望のSNRを達成するために必要とされる構成要素の数およびタイプによって決定される。

30

【発明の概要】

【発明が解決しようとする課題】

【0005】

したがって、従来のベースバンドフィルタより少ない回路面積を利用してながら、所望のレベルの雑音性能を与える改善されたベースバンドフィルタを有することが望ましいであろう。

【課題を解決するための手段】

【0006】

40

本明細書において説明される上記の態様は、添付の図面と併用されるときに、以下の説明を参照することによって、より容易に明らかとなるであろう。

【図面の簡単な説明】

【0007】

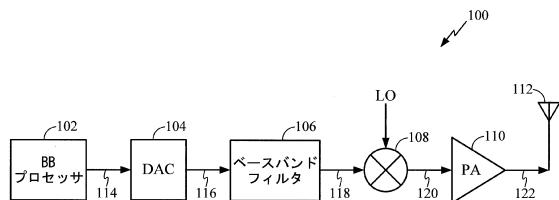

【図1】ワイヤレスデバイスにおいて使用するための新規のベースバンドフィルタを備えるフロントエンドの例示的な実施形態を示す図である。

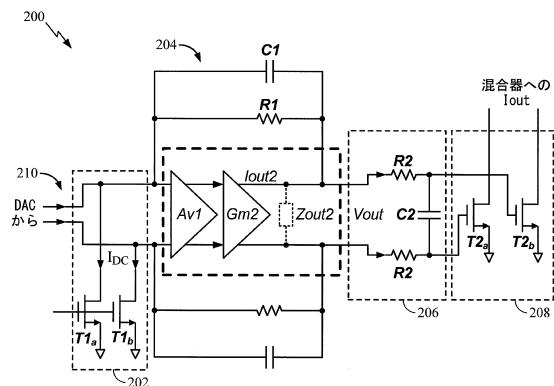

【図2】従来のベースバンドフィルタの図である。

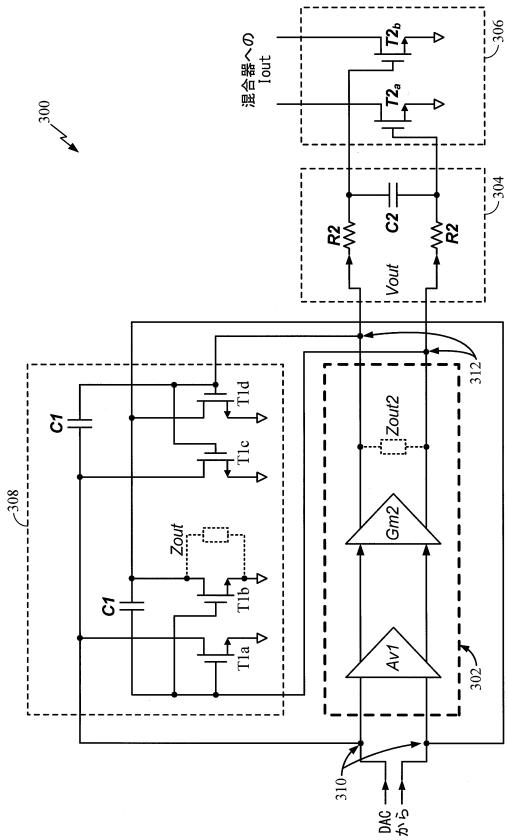

【図3】改善された線形性および縮小された回路面積のために構成されたベースバンドフィルタの例示的な実施形態を示す図である。

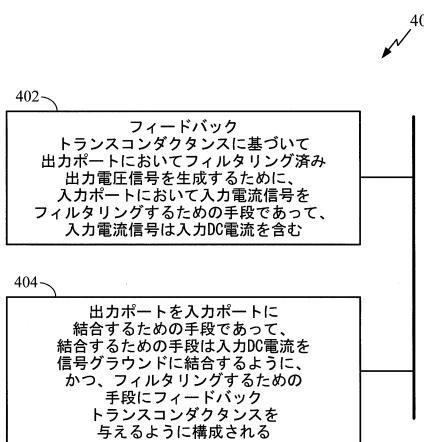

【図4】改善された線形性および縮小された回路面積のために構成されたベースバンドフ

50

イルタ装置の例示的な実施形態を示す図である。

【発明を実施するための形態】

【0008】

添付の図面に関連して以下で述べられる発明を実施するための形態は、本発明の例示的な実施形態を説明することを意図しており、本発明が実施することができる唯一の実施形態を表すことは意図していない。本説明全体にわたって使用される「例示的」という用語は、「一例、実例、または例示としての役割を果たす」ことを意味し、必ずしも、他の例示的な実施形態よりも好ましいまたは有利であると解釈されるべきではない。詳細な説明は、本発明の例示的な実施形態を完全に理解してもらうために、具体的な詳細を含む。本発明の例示的な実施形態は、これらの具体的な詳細なしに実施される場合もあることは、当業者には明らかになるであろう。場合によっては、本明細書において提示される例示的な実施形態の新規性を曖昧にするのを回避するために、周知の構造およびデバイスがプロック図の形で示される。

10

【0009】

図1は、ワイヤレスデバイスにおいて使用するための新規のベースバンドフィルタ106を備えるフロントエンド100の例示的な実施形態を示す。フロントエンド100は、ベースバンド(BB)プロセッサ102と、デジタル/アナログコンバータ(DAC)104と、新規のベースバンドフィルタ106と、混合器(またはアップコンバータ)108と、電力増幅器(PA)110と、アンテナ112とを備える。

20

【0010】

動作中に、BBプロセッサ102は、送信するためのデジタル信号114を出力する。デジタル信号114はDAC104に入力され、アナログベースバンド信号116に変換される。アナログベースバンド信号116は、混合器108に入力されるフィルタリング済みベースバンド信号118を生成するために、新規のベースバンドフィルタ106に入力される。混合器108は、局部発振器(L0)信号に基づいて、フィルタリング済みベースバンド信号118を無線周波数(RF)信号120にアップコンバートするように動作する。RF信号120は、アンテナ112によって送信される増幅済みRF信号122を生成するために、PA110に入力される。

20

【0011】

種々の例示的な実施形態において、新規のベースバンドフィルタ106は、従来のベースバンドフィルタより、良好な線形性を与え、必要とする回路面積が少ないよう構成され、それにより、フロントエンド100が、少ない回路面積を利用しながら、従来の回路と同じ、またはそれより良好な雑音性能を達成できるようにする。新規のベースバンドフィルタ106の種々の例示的な実施形態のより詳細な説明が、以下に提供される。

30

【0012】

図2は、従来のベースバンドフィルタ200の図を示す。ベースバンドフィルタ200は、電流シンク回路202と、電流/電圧(I-V)フィルタ204と、二次フィルタ206と、トランスコンダクタ208とを備える。

【0013】

動作中に、電流シンク回路202は、DC電流成分( $I_{DC}$ )を含むアナログベースバンド電流信号210を受信する。たとえば、電流信号210は、図1に示されるDAC104のようなDACから受信される。電流シンク回路202は、トランジスタ(T1a)および(T1a')を備え、これらのトランジスタは、DC電流( $I_{DC}$ )を信号グラウンドにシンクし、I-Vフィルタ204の動作点を設定するように動作する。

40

【0014】

(I-V)フィルタ204は、入力アナログ電流信号をフィルタリングし、これらの信号を二次フィルタ206に入力される電圧に変換するように構成される。I-Vフィルタ204は2つのステージ( $Av_1$ および $Gm_2$ )を備え、入力電流信号をフィルタリングし、フィルタリング済み出力電圧信号( $V_{out}$ )を生成するために、フィードバック構成において抵抗器R1およびキャパシタC1を利用する。インピーダンス $Z_{out2}$ は、 $gm_2$ を形成するデバイスに内在する。出力電圧信号( $V_{out}$ )は、二次フィルタ206によってフィルタリングされ、フィルタリング済みの出

50

力が、トランスコンダクタ208のトランジスタ(T2a)および(T2b)に入力される。トランスコンダクタ208の出力(Iout)は、アップコンバート用混合器に入力される電流信号である。

#### 【 0 0 1 5 】

従来のベースバンドフィルタ200は、利用される回路面積の量を与えられたとすると、線形性および雑音性能に関して制限がある。たとえば、フィルタ200の線形性はトランスコンダクタT2のI-V曲線によって制限される。雑音性能に関して、雑音バジェットは、トランジスタ“T1”、増幅器(Av1, gm2)、およびフィルタ抵抗器(R1, R2)に関連付けられる雑音を含む。(いかなる信号整形機能のためにも使用されないトランジスタである)“T1”からの雑音は、増幅器およびフィルタ抵抗器に配分することができる雑音レベルを低減する。増幅器およびフィルタ抵抗器のための雑音割当量が低減されると、合計の雑音仕様を満たすために、増幅器およびフィルタ抵抗器構成要素のために必要とされる回路面積が大きくなる。したがって、従来のベースバンドフィルタ200と同じ、またはそれより良好な性能を与えるために、良好な線形性を与え、少ない回路面積を利用する改善されたベースバンドフィルタを有することが望ましいであろう。10

#### 【 0 0 1 6 】

図3は、線形性を改善し、回路面積を小さくするために構成されるベースバンドフィルタ300の詳細な例示的実施形態を示す。たとえば、ベースバンドフィルタ300は、図1に示されるベースバンドフィルタ106として使用するのに適しており、図2に示される従来のベースバンドフィルタ200より優れた線形性および回路面積効率を与えるように構成される。20

。ベースバンドフィルタ300はI-Vフィルタを備え、I-Vフィルタは増幅器302とフィードバック回路308とを含む。また、ベースバンドフィルタ300は、二次フィルタ304とトランスコンダクタ306とを含む。

#### 【 0 0 1 7 】

ベースバンドフィルタ300は、従来のベースバンドフィルタ200の場合のような、増幅器302の入力にあるDC電流シンク回路(すなわち、図2に示される回路202)を含まないことに留意されたい。DC電流シンク回路202をなくすことは、回路面積を節約するように働き、フィルタ300の面積効率を上げる。したがって、DC電流(I<sub>DC</sub>)を含むDACからのアナログ電流信号は、入力端子310において受信される。増幅器302は2つのステージ、すなわち、Av1およびGm2を備える。Gm2ステージからの出力端子312において生成された出力電圧は、二次フィルタ304に入力される。30

#### 【 0 0 1 8 】

増幅器302構成、および出力端子312からトランジスタT1a～T1dを通して入力端子310に接続されるフィードバック回路308が、出力端子312において生成される電圧が、トランジスタT1a～T1dを通って流れる電流を極めて線形にするのに十分であるのを確実にすることになる。トランジスタT1a～T1dの任意の非線形(電圧入力対出力電流)変換特性が、構成の全利得(すなわち、Av1\*Gm2\*Zout2)によって抑圧されることになる。T1a～T1dと同様の(電圧入力/電流出力)挙動を有するトランジスタT2aおよびT2bを用いることによって、トランジスタT2aおよびT2bから、線形性の高い出力電流(Iout)を得ることができる。トランジスタT1a～T1bのトランスコンダクタンスは、図3に示されるような単純な積分器構造の最終的なフィードバック抵抗器として、または最終的な出力から入力への少なくとも1つのフィードバック抵抗器を備える任意の汎用フィルタ構造のフィードバック抵抗器として解析することができる。40

#### 【 0 0 1 9 】

トランジスタT1(a～d)を備えるフィードバック回路308は、2つの機能を果たすように構成される。第一に、トランジスタT1(a～d)は、フィルタ極を実現するために用いられる(1/R)を与えるために(すなわち、I-Vフィルタの伝達関数を決定するフィードバックトランスコンダクタンスを与えるために)、DC入力電流を利用して、Gm2ステージにバイアスをかけるように構成される。また、トランジスタT1(a～d)は、ノード310においてDACから受信された入力電流からDC電流を除去するために、DC電流シンクとして用いられる。したがつ50

て、トランジスタT1a～T1dは、2つの機能、すなわち、積分器/フィルタのために必要とされる“R”を実現するための機能と、DACにバイアスをかけるための機能とを果たす。結果として、従来のベースバンドフィルタ200内に含まれる少なくとも1つの雑音源、すなわち、DC電流シンク回路202が、新規のベースバンドフィルタ300から除去される。

#### 【0020】

トランジスタT1(a～d)は、フィルタリングのために必要とされるRのうちの1つとして用いられる( $R1 = 1/gm$  of T2)。差動トランスコンダクタンス(Gm)は $1/R1$ と同じままに保たれ、これは、図2に示される構造による“T1”的コモンモードトランスコンダクタンスとは異なるようにすることができる。さらに、( $R2*C2$ )と $((1/Gm)*C1)$ との組合せを用いて、ベースバンドフィルタ300のフィルタ応答を実現することができる。

10

#### 【0021】

種々の例示的な実施形態において、新規のフィルタ300が開示され、そのフィルタは、雑音要素の数を削減することによって線形性を改善し、全体の面積を削減するために、トランスマッタのベースバンドアーキテクチャにおいて利用することができる。それらの実施形態は、同様の帯域内雑音を維持しながら、所与のフィルタ応答を得るために、R値を大きくし、C値を小さくする。さらに、種々の例示的な実施形態は、主要雑音要素のうちの1つをフィードバック要素およびレプリカバイアス要素の両方として利用することによって、混合器入力電流の線形性を改善する。

#### 【0022】

図4は、線形性を改善し、回路面積を小さくするために構成されるベースバンドフィルタ装置400の例示的な実施形態を示す。たとえば、装置400は、図1に示されるベースバンドフィルタ106または図3に示されるベースバンドフィルタ300として使用するのに適している。一態様では、装置400は、本明細書において説明されるような機能を提供するよう構成される1つまたは複数のモジュールによって実現される。たとえば、一態様では、各モジュールは、ハードウェアおよび/またはハードウェア実行ソフトウェアを含む。

20

#### 【0023】

装置400は、フィードバックトランスコンダクタンスに基づいて出力ポートにおいてフィルタリング済み出力電圧信号を生成するために、入力ポートにおいて入力電流信号をフィルタリングするための手段(402)を備える第1のモジュールを備え、入力電流信号は入力DC電流を含み、一態様では、その手段は増幅器302を備える。

30

#### 【0024】

装置400は、出力ポートを入力ポートに結合するための手段(404)を備える第2のモジュールを備え、結合するための手段は、入力DC電流を信号グラウンドに結合するように、かつ、フィルタリングするための手段にフィードバックトランスコンダクタンスを与えるように構成され、一態様では、その手段はフィードバック回路308を備える。

#### 【0025】

当業者は、情報および信号が、種々の異なる技術および技法のうちのいずれかを使用して表されるか、または処理され得ることは理解されよう。たとえば、先の説明全体にわたって参照される場合があるデータ、命令、コマンド、情報、信号、ビット、シンボル、およびチップは、電圧、電流、電磁波、磁界もしくは磁性粒子、光場もしくは光粒子、またはそれらの任意の組合せによって表される場合がある。トランジスタタイプおよびトランジスタ技術は、同じ結果を達成するように置換され、再構成され、または別 の方法で変更される場合があることにさらに留意されたい。たとえば、PMOSトランジスタを利用して示される回路は、NMOSトランジスタを使用するように変更される場合があり、その逆も成り立つ。したがって、本明細書において開示される増幅器は、種々のトランジスタタイプおよびトランジスタ技術を用いて実現される場合があり、図面に示されるトランジスタタイプおよびトランジスタ技術には限定されない。たとえば、BJT、GaAs、MOSFET、または任意の他のトランジスタ技術のようなトランジスタタイプが使用される場合がある。

40

#### 【0026】

本明細書において開示される実施形態に関連して説明される種々の例示的な論理プロツ

50

ク、モジュール、回路、およびアルゴリズムステップは、電子ハードウェア、コンピュータソフトウェア、または両方の組合せとして実現される場合があることは、当業者はさらに理解されよう。ハードウェアおよびソフトウェアのこの互換性を明確に示すために、種々の例示的な構成要素、ロック、モジュール、回路およびステップが、一般にそれらの機能についてこれまで説明してきた。そのような機能が、ハードウェアとして実現されるか、ソフトウェアとして実現されるかは、具体的な適用例と、システム全体に課せられる設計制約とによって決まる。当業者は、説明された機能を特定の適用例ごとに種々のやり方で実現することができるが、そのような実施態様の決定は、本発明の例示的な実施形態の範囲からの逸脱を生じるものと解釈されるべきではない。

#### 【0027】

本明細書において開示される実施形態に関する説明される種々の例示的な論理プロック、モジュールおよび回路は、汎用プロセッサ、デジタルシグナルプロセッサ(DSP)、特定用途用集積回路(ASIC)、フィールドプログラマブルゲートアレイ(FPGA)もしくは他のプログラマブル論理デバイス、個別のゲートもしくはトランジスタロジック、個別のハードウェア構成要素、または本明細書において説明された機能を果たすように設計されたこれらの任意の組合せを用いて、実現されるか、または実行される場合がある。汎用プロセッサはマイクロプロセッサとすることができますが、代替形態では、プロセッサは、任意の従来のプロセッサ、コントローラ、マイクロコントローラ、またはステートマシンとすることができます。プロセッサは、たとえばDSPとマイクロプロセッサの組合せ、複数のマイクロプロセッサ、DSPコアと連結した1つまたは複数のマイクロプロセッサ、または任意の他のそのような構成など、コンピューティングデバイスの組合せとして実現することもできる。

#### 【0028】

本明細書において開示される実施形態に関する説明された方法またはアルゴリズムのステップは、直接ハードウェアの形で、プロセッサによって実行されるソフトウェアモジュールの形で、またはその2つの組合せの形で具体化される場合がある。ソフトウェアモジュールは、ランダムアクセスメモリ(RAM)、フラッシュメモリ、リードオンリーメモリ(ROM)、電気的プログラマブルROM(EPROM)、電気的消去可能プログラマブルROM(EEPROM)、レジスタ、ハードディスク、リムーバブルディスク、CD-ROM、または当技術分野において既知の任意の形の記憶媒体内に存在する場合がある。例示的な記憶媒体は、プロセッサが記憶媒体から情報を読み出し、記憶媒体に情報を書き込むことができるようにプロセッサに結合される。代替的には、記憶媒体はプロセッサと一体化することができる。プロセッサおよび記憶媒体は、ASIC内に存在する場合がある。ASICは、ユーザ端末内に存在する場合がある。代替形態では、プロセッサおよび記憶媒体は、ユーザ端末内に個別の構成要素として存在する場合がある。

#### 【0029】

1つまたは複数の例示的な実施形態では、説明された機能が、ハードウェア、ソフトウェア、ファームウェア、またはそれらの任意の組合せにおいて実現される場合がある。ソフトウェアにおいて実現される場合、それらの機能は、1つまたは複数の命令またはコードとして、コンピュータ可読媒体上に記憶されるか、またはコンピュータ可読媒体を介して送信される場合がある。コンピュータ可読媒体は、非一時的コンピュータ記憶媒体と、ある場所から別の場所へのコンピュータプログラムの転送を容易にする任意の媒体を含む通信媒体との両方を含む。非一時的記憶媒体は、コンピュータによってアクセスすることができる任意の入手可能な媒体とすることができます。例であって、限定はしないが、そのようなコンピュータ可読媒体は、RAM、ROM、EEPROM、CD-ROMもしくは他の光ディスク記憶装置、磁気ディスク記憶装置もしくは他の磁気記憶デバイス、または命令もしくはデータ構造の形をとる所望のプログラムコードを搬送もしくは記憶するために使用することができます。コンピュータによってアクセスすることができる、他の任意の媒体を含むことができる。また、あらゆる接続も厳密にはコンピュータ可読媒体と呼ばれる。たとえば、ソフトウェアがウェブサイト、サーバ、または他のリモートソースから、同軸ケーブル、光ファ

10

20

30

40

50

イバケーブル、より対線、デジタル加入者回線(DSL)、または赤外線、無線、マイクロ波などのワイヤレス技術を用いて送信される場合には、同軸ケーブル、光ファイバケーブル、より対線、DSL、または赤外線、無線、マイクロ波などのワイヤレス技術は、媒体の定義に含まれる。ディスク(disk)およびディスク(disc)は、本明細書において用いられるときに、コンパクトディスク(CD:compact disc)、レーザディスク(laser disc)、光ディスク(optical disc)、デジタル多用途ディスク(DVD:digital versatile disc)、フロッピーディスク(floppy disk)、およびブルーレイディスク(blu-ray disc)を含み、ただし、ディスク(disk)は通常、データを磁気的に再生し、一方ディスク(disc)は、レーザを用いてデータを光学的に再生する。上記の組合せも、コンピュータ可読媒体の範囲内に含まれるべきである。

10

## 【0030】

開示された例示的な実施形態の説明は、当業者であればだれでも本発明を実施または使用できるようにするために提供される。これらの例示的な実施形態に対する種々の変更が当業者には容易に明らかとなり、本明細書において規定された一般原理は、本発明の趣旨または範囲から逸脱することなく他の実施形態に適用することができる。したがって、本発明は、本明細書に示される例示的な実施形態に限定されるものではなく、本明細書において開示する原理および新規の特徴に一致する最も広い範囲を与えられるべきである。

## 【符号の説明】

## 【0031】

|     |                     |    |

|-----|---------------------|----|

| 100 | フロントエンド             | 20 |

| 102 | BBプロセッサ             |    |

| 104 | デジタル/アナログコンバータ(DAC) |    |

| 106 | ベースバンドフィルタ          |    |

| 108 | 混合器(アップコンバータ)       |    |

| 110 | 電力増幅器(PA)           |    |

| 112 | アンテナ                |    |

| 114 | デジタル信号              |    |

| 116 | アナログベースバンド信号        |    |

| 118 | フィルタリング済みベースバンド信号   |    |

| 120 | 無線周波数(RF)信号         | 30 |

| 122 | 増幅済みRF信号            |    |

| 200 | 従来のベースバンドフィルタ       |    |

| 202 | 電流シンク回路             |    |

| 204 | 電流/電圧(I-V)フィルタ      |    |

| 206 | 二次フィルタ              |    |

| 208 | トランスコンダクタ           |    |

| 210 | アナログベースバンド電流信号      |    |

| 300 | ベースバンドフィルタ          |    |

| 302 | 増幅器                 |    |

| 304 | 二次フィルタ              | 40 |

| 306 | トランスコンダクタ           |    |

| 308 | フィードバック回路           |    |

| 310 | 入力端子                |    |

| 312 | 出力端子                |    |

| 400 | ベースバンドフィルタ装置        |    |

| 402 | フィルタリングするための手段      |    |

| 404 | 結合するための手段           |    |

【図1】

【図3】

【図2】

【図4】

---

フロントページの続き

(72)発明者 ラケッシュ・クマール

アメリカ合衆国・カリフォルニア・92121-1714・サン・ディエゴ・モアハウス・ドライ

ヴ・5775

(72)発明者 ヴィノド・ヴェヌゴバル・パニッカート

アメリカ合衆国・カリフォルニア・92121-1714・サン・ディエゴ・モアハウス・ドライ

ヴ・5775

(72)発明者 アユシュ・ミッタル

アメリカ合衆国・カリフォルニア・92121-1714・サン・ディエゴ・モアハウス・ドライ

ヴ・5775

(72)発明者 アロク・ジョシ

アメリカ合衆国・カリフォルニア・92121-1714・サン・ディエゴ・モアハウス・ドライ

ヴ・5775

審査官 鬼塚 由佳

(56)参考文献 特開平10-173482(JP,A)

特開2005-286778(JP,A)

米国特許出願公開第2013/0183914(US,A1)

特開平08-172339(JP,A)

特表2012-509033(JP,A)

特開平06-334479(JP,A)

特開平10-065461(JP,A)

(58)調査した分野(Int.Cl., DB名)

H03H11/04-11/12

H04B1/02-1/04

H04B1/38-1/58