【公報種別】特許法第17条の2の規定による補正の掲載

【部門区分】第6部門第4区分

【発行日】平成21年3月19日(2009.3.19)

【公開番号】特開2007-250060(P2007-250060A)

【公開日】平成19年9月27日(2007.9.27)

【年通号数】公開・登録公報2007-037

【出願番号】特願2006-70587(P2006-70587)

【国際特許分類】

G 11 C 29/08 (2006.01)

G 11 C 11/401 (2006.01)

【F I】

G 11 C 29/00 6 7 1 S

G 11 C 11/34 3 7 1 A

【手続補正書】

【提出日】平成21年1月28日(2009.1.28)

【手続補正1】

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

【補正の内容】

【特許請求の範囲】

【請求項1】

メモリセル群とセンスアンプ回路とから構成されるメモリセルアレイを複数備えた半導体記憶装置であって、

前記複数のメモリセルアレイは、それぞれ

複数のサブメモリセルアレイと、

前記複数のサブメモリセルアレイのそれぞれに配置され、前記メモリセル群に接続されたサブビット線と、

選択スイッチを介して前記サブビット線と接続され、かつ前記センスアンプ回路に接続される、前記メモリセルアレイ内に配置されたメインビット線と、

外部入力される第1の制御信号に応じて、全ての前記メモリセルアレイに配置された全ての前記選択スイッチを活性化させる手段とを備える、半導体記憶装置。

【請求項2】

メモリセル群とセンスアンプ回路とから構成されるメモリセルアレイを複数備えた半導体記憶装置であって、

前記複数のメモリセルアレイは、それぞれ

複数のサブメモリセルアレイと、

前記複数のサブメモリセルアレイのそれぞれに配置され、前記メモリセル群に接続されたサブビット線と、

選択スイッチを介して前記サブビット線と接続され、かつ前記センスアンプ回路に接続される、前記メモリセルアレイ内に配置されたメインビット線と、

外部入力される第1の制御信号、アドレス信号、及び第2の制御信号に応じて、選択された前記メモリセルアレイに配置された前記複数のサブメモリセルアレイ内の前記選択スイッチのうち、選択ワード線を含む選択サブメモリセルアレイ内の選択スイッチを活性化させ、前記選択ワード線を含まない非選択サブメモリセルアレイ内の前記選択スイッチを非活性化させる手段と、

前記選択されたメモリセルアレイに配置された前記非選択サブメモリセルアレイ内の前記選択スイッチを非活性化させた後に、再度活性化させる手段とを備える、半導体記憶

装置。

【請求項3】

前記選択されたメモリセルアレイ内で、かつ前記非選択サブメモリセルアレイ内の前記選択スイッチが非活性状態になるタイミングは、前記選択ワード線が活性状態になる前であることを特徴とする、請求項2に記載の半導体記憶装置。

【請求項4】

前記選択されたメモリセルアレイ内で、かつ前記非選択サブメモリセルアレイ内の前記選択スイッチが非活性状態から活性状態になるタイミングは、前記選択ワード線が活性状態になった後で、かつ前記センスアンプ回路が活性状態になった後であることを特徴とする、請求項2に記載の半導体記憶装置。

【手続補正2】

【補正対象書類名】明細書

【補正対象項目名】0003

【補正方法】変更

【補正の内容】

【0003】

まず、全メモリセルに H i g h (又は L o w ) データを書き込む。全メモリセルへの書き込み動作 (ライト動作) の後、ある任意のワード線を活性化させてワード線に直交するビット線にメモリセルの電荷を読み出す。そして、その読み出した電荷をセンスアンプ回路において增幅 (リード / リフレッシュ動作) することで、ビット線及び相補ビット線の電位を H i g h 又は L o w にする。この状態は、メモリセルのデータ保持時間を保証可能な時間 (以下、リフレッシュ検査時間という) だけ保持される。

【手続補正3】

【補正対象書類名】明細書

【補正対象項目名】0004

【補正方法】変更

【補正の内容】

【0004】

この状態において、非選択ワード線に接続されているメモリセルキャパシタは、 H i g h データが保持されており、かつ接続されているビット線が L o w レベルになっているメモリセルに対しては、メモリセルトランジスタのドレイン - ソース間に電位差が生じ、サブスレショルド電流が流れる。ここで、トランジスタのしきい値電圧が低いメモリセルの場合、サブスレショルド電流が多く流れるため、リフレッシュ検査時間内でデータ保持ができず不良セルとなる。よって、リフレッシュ検査時間終了後に、検査対象メモリセルに対して読み出し動作を行い、データが正しく読み出されるかどうかを確認する。

【手続補正4】

【補正対象書類名】明細書

【補正対象項目名】0005

【補正方法】変更

【補正の内容】

【0005】

しかし、非選択ワード線に接続されているメモリセルに対して、ビット線及び相補ビット線の電位を H i g h 又は L o w にできるのは、メモリセル群とセンスアンプ回路とで構成されたメモリセルアレイ単位でしかできない。また、上記リフレッシュ検査時間は、通常数 m s から数十 m s のオーダーで設定されることが多く、この時間はメモリに対してデータの読み出し及び書き込みする時間に比べて十分に長いことから、ディスター・リフレッシュ検査は、メモリの検査時間の中で大きな割合を占めている。

【手続補正5】

【補正対象書類名】明細書

【補正対象項目名】0010

【補正方法】変更

【補正の内容】

【0010】

本発明は、メモリセル群とセンスアンプ回路とから構成されるメモリセルアレイを複数備えた半導体記憶装置に向けられている。そして、上記目的を達成させるために、本発明の半導体記憶装置は、複数のメモリセルアレイが、複数のサブメモリセルアレイと、複数のサブメモリセルアレイのそれぞれに配置され、メモリセル群に接続されたサブビット線と、選択スイッチを介してサブビット線と接続され、かつセンスアンプ回路に接続される、メモリセルアレイ内に配置されたメインビット線と、外部入力される第1の制御信号に応じて、全てのメモリセルアレイに配置された全ての選択スイッチを活性化させる手段とを、それぞれ備える。

【手続補正6】

【補正対象書類名】明細書

【補正対象項目名】0011

【補正方法】変更

【補正の内容】

【0011】

又は、上記目的を達成させるために、本発明の半導体記憶装置は、複数のメモリセルアレイが、複数のサブメモリセルアレイと、複数のサブメモリセルアレイのそれぞれに配置され、メモリセル群に接続されたサブビット線と、選択スイッチを介してサブビット線と接続され、かつセンスアンプ回路に接続される、メモリセルアレイ内に配置されたメインビット線と、外部入力される第1の制御信号、アドレス信号、及び第2の制御信号に応じて、選択されたメモリセルアレイに配置された複数のサブメモリセルアレイ内の選択スイッチのうち、選択ワード線を含む選択サブメモリセルアレイ内の選択スイッチを活性化させ、選択ワード線を含まない非選択サブメモリセルアレイ内の選択スイッチを非活性化させる手段と、選択されたメモリセルアレイに配置された非選択サブメモリセルアレイ内の選択スイッチを非活性化させた後に、再度活性化させる手段とを、それぞれ備える。

【手続補正7】

【補正対象書類名】明細書

【補正対象項目名】0018

【補正方法】変更

【補正の内容】

【0018】

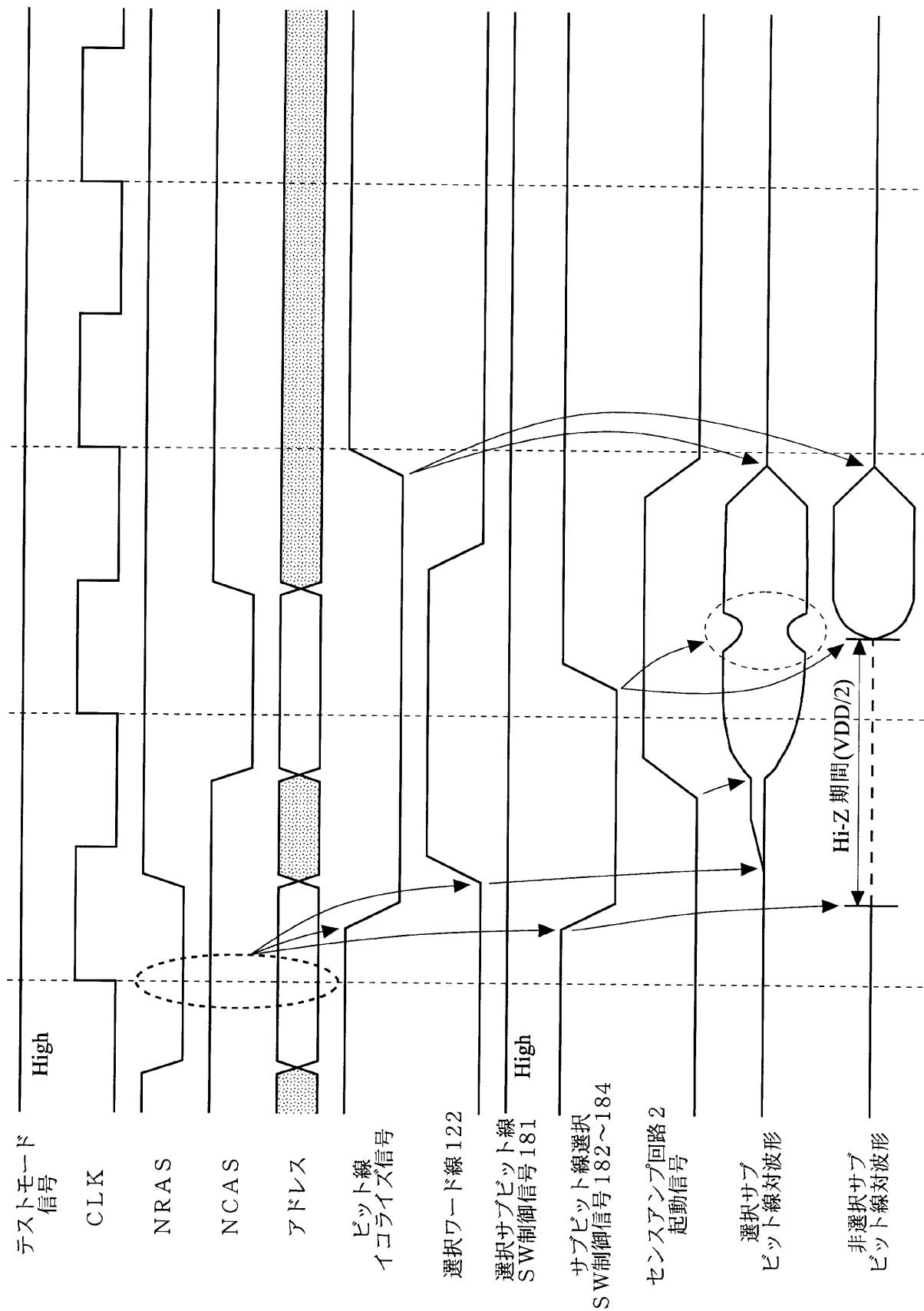

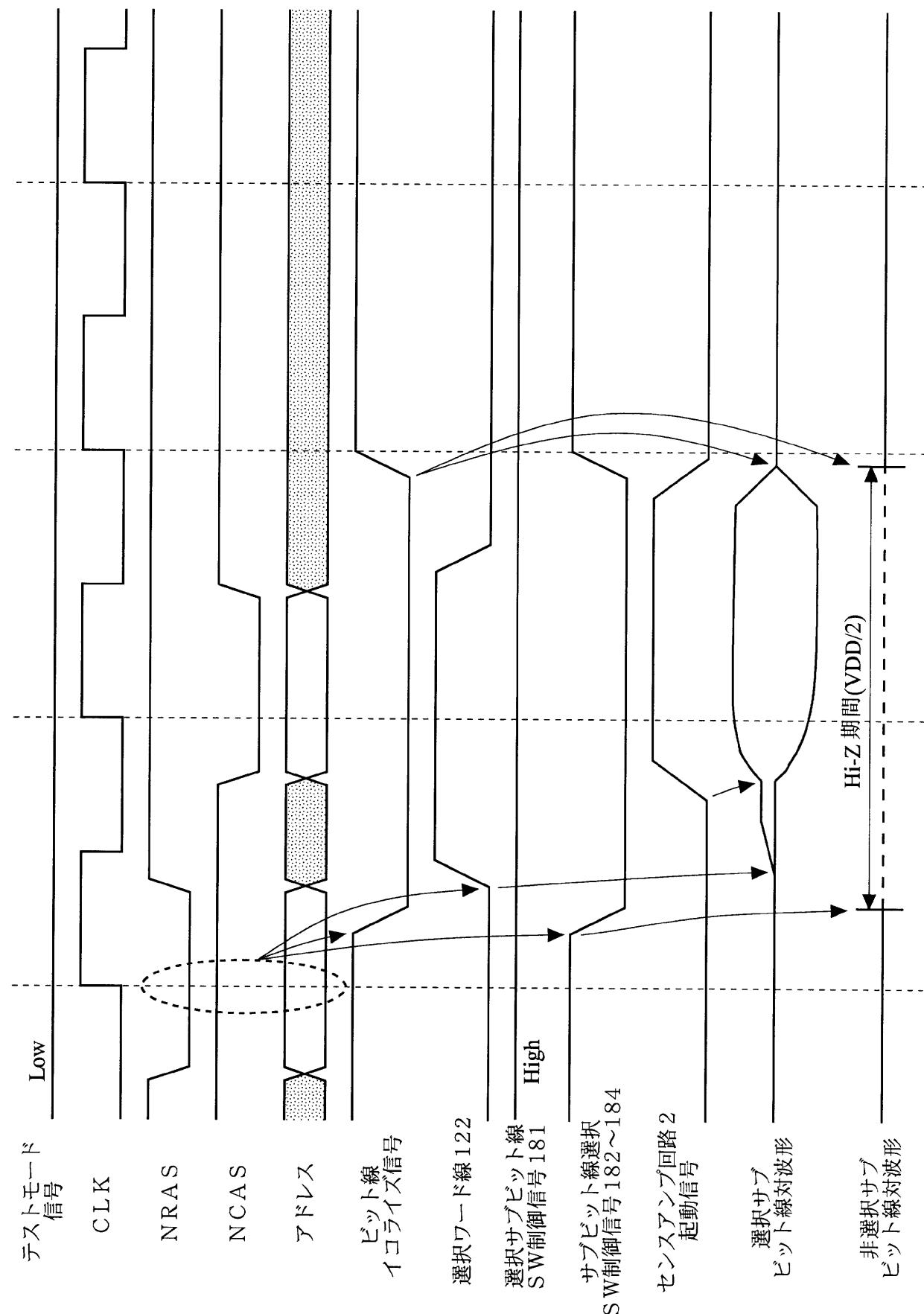

次のサイクルにて、外部入力コマンドのN R A Sとアドレス信号とによって、内部動作が開始される。この動作により、活性化メモリセルアレイ内においても、選択されたワード線を含むサブメモリセルアレイとその他のサブメモリセルアレイとで動作が異なる。ここで、ワード線122が選択された場合には、サブメモリセルアレイ171が選択されることになり、その他のサブメモリセルアレイ172～174は、非選択サブメモリセルアレイとなる。そして、センスアンプ回路2内にあるビット線イコライズ回路(図示せず)は、非選択状態とほぼ同タイミングで、非選択サブメモリセルアレイ172～174内のサブビット線選択スイッチ142～144を非活性状態にさせる。

【手続補正8】

【補正対象書類名】明細書

【補正対象項目名】0019

【補正方法】変更

【補正の内容】

【0019】

これにより、メインビット線20及び相補メインビット線21から非選択サブビット線152～154及び非選択相補サブビット線162～164を切り離すことができるため、ビット線の総負荷容量を減らすことが可能になる。そのため、メモリセルからの読み出

し電位を多くすることができる。そして、選択ワード線1 2 2を活性化することにより、メインビット線20に接続されたままの選択サブビット線151上にメモリセルからデータを読み出し、センスアンプ回路2で増幅する。この期間、非選択サブビット線152～154は、電気的に切り離されているため高インピーダンス(Hi-Z)状態である。選択サブビット線151が十分に増幅された後にワード線1 2 2を非活性状態にし、その後、ビット線のイコライズ開始及び非選択サブメモリセルアレイ172～174内のサブビット線選択スイッチ142～144を活性状態へ戻す制御を行う。

#### 【手続補正9】

【補正対象書類名】明細書

【補正対象項目名】0022

【補正方法】変更

【補正の内容】

#### 【0022】

よって、通常モード動作においては、非選択のサブメモリセルアレイのメモリセルトランジスタのソース-ドレイン間に十分な電位差が与えらず、メモリセルへのディスター~~ブリ~~フレッシュ検査ができないことが原因で、ディスター~~ブリ~~フレッシュ検査時間が増大するという課題があったが、本発明では、上述したテストモード[1]動作を用いて、非選択のサブビット線もHighレベル又はLowレベルに振幅するため、メモリセルアレイ単位での検査ができ、検査時間の短縮が可能になる。

#### 【手続補正10】

【補正対象書類名】明細書

【補正対象項目名】0023

【補正方法】変更

【補正の内容】

#### 【0023】

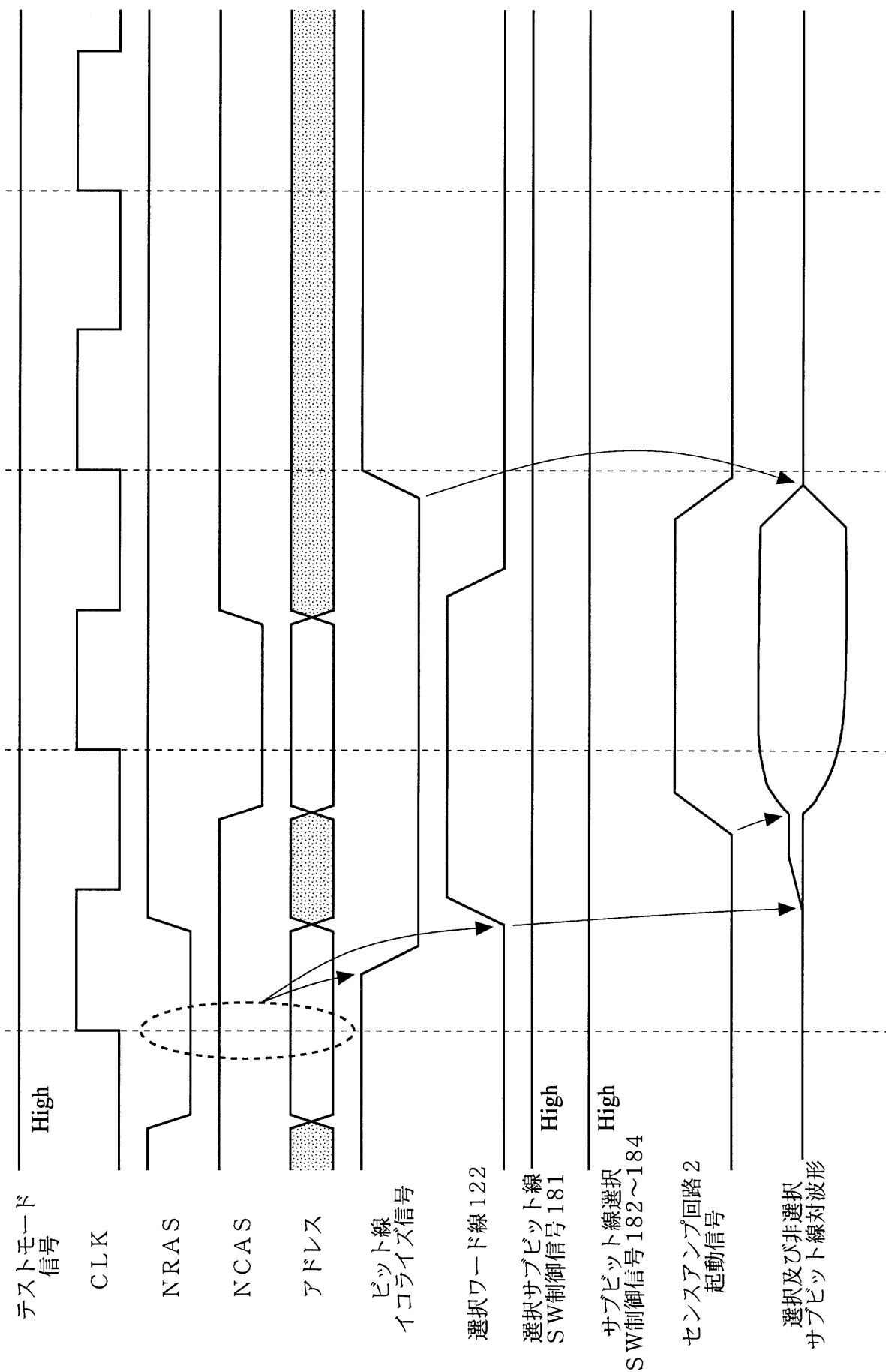

次に、図4を参照して、第2のテストモードが設定されたテストモード[2]動作を説明する。

外部入力コマンドのN R A Sとアドレス信号とによって、内部動作が開始される。これにより、通常モード動作と同じように、活性化メモリセルアレイ内においても選択されたワード線を含むサブメモリセルアレイとその他のサブメモリセルアレイとで異なる制御が行われる。ここで、外部入力アドレスによってワード線1 2 2が選択された場合には、サブメモリセルアレイ171が選択されることになり、その他のサブメモリセルアレイ172～174は、非選択サブメモリセルアレイとなる。非選択サブメモリセルアレイ172～174内のサブビット線選択スイッチ制御信号182～184は、内部動作開始に応じて、サブビット線選択スイッチ142～144を非活性状態にする。この選択サブビット線151のみをメインビット線20に接続する制御は、通常モードと同様である。

#### 【手続補正11】

【補正対象書類名】図面

【補正対象項目名】図2

【補正方法】変更

【補正の内容】

【図2】

【補正対象項目名】図 3

【補正方法】変更

【補正の内容】

【図3】

【手続補正 1 3】

【補正対象書類名】図面

【補正対象項目名】図 4

【補正方法】変更

【補正の内容】

【図4】