(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-142319

(P2005-142319A)

(43) 公開日 平成17年6月2日(2005.6.2)

(51) Int.Cl.<sup>7</sup>

H01L 21/76

H01L 21/762

F 1

H01L 21/76

H01L 21/76

テーマコード(参考)

5 F O 3 2

D

審査請求 未請求 請求項の数 11 O L (全 16 頁)

(21) 出願番号

特願2003-376639 (P2003-376639)

(22) 出願日

平成15年11月6日 (2003.11.6)

(71) 出願人 503121103

株式会社ルネサステクノロジ

東京都千代田区丸の内二丁目4番1号

(74) 代理人 100089233

弁理士 吉田 茂明

(74) 代理人 100088672

弁理士 吉竹 英俊

(74) 代理人 100088845

弁理士 有田 貴弘

(72) 発明者 辻内 幹夫

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

(72) 発明者 岩松 俊明

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

最終頁に続く

(54) 【発明の名称】半導体装置の製造方法

## (57) 【要約】

【課題】半導体デバイスがもつ性能及び信頼性が金属汚染物質により低下することを防止する。

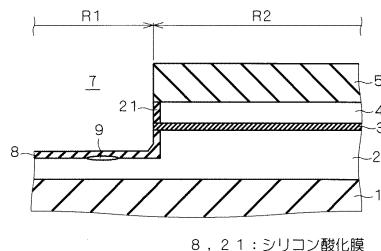

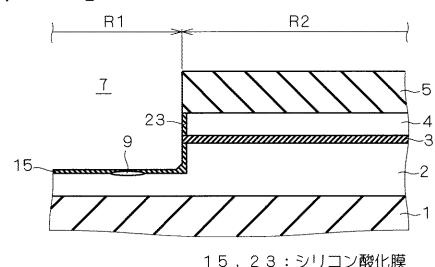

【解決手段】酸化シリコン基板1とシリコン膜2でSOI基板が形成される。シリコン膜2の表面が酸化されてシリコン酸化膜3が形成される。多結晶シリコン4とシリコン窒化膜5がシリコン酸化膜3上に順に形成される。そして、トレンチ7が領域R1に形成される。このとき、トレンチ7の底面に金属汚染物質が付着する可能性がある。基板温度を200乃至600とし、励起エネルギーをプラズマで与えてシリコン膜2の表面に酸化反応を起こす。これにより、トレンチ7において露出したシリコン膜2の表面にシリコン酸化膜8が形成される。金属汚染物質は、シリコン酸化膜8とシリコン膜2の界面で凝集して金属シリサイド9となる。シリコン酸化膜8をHF系溶液によって除去する。これに伴って金属シリサイド9も除去される。

【選択図】図4

8, 21: シリコン酸化膜

**【特許請求の範囲】****【請求項 1】**

(a) 酸化シリコン基板上のシリコン膜上にシリコン酸化膜と、多結晶シリコンと、シリコン窒化膜とをこの順に積層する工程と、

(b) 所定領域において前記シリコン窒化膜と、前記多結晶シリコンと、前記シリコン酸化膜と、前記シリコン膜とをエッチングして、前記シリコン膜中に底面を有するトレンチを形成する工程と、

(c) 前記トレンチに露出する前記シリコン膜の表面に 600 以下で絶縁膜を形成する工程と、

(d) 前記絶縁膜を除去する工程と、

(e) 前記トレンチに絶縁材料を埋め込む工程と

を備える、半導体装置の製造方法。

10

**【請求項 2】**

前記工程 (c) は、200 乃至 600 で前記シリコン膜の表面をラジカル酸化、プラズマ酸化もしくはプラズマ窒化する、請求項 1 記載の半導体装置の製造方法。

**【請求項 3】**

前記工程 (c) は、オゾン系溶液を用いて 20 乃至 120 で前記シリコン膜の表面を酸化する、請求項 1 記載の半導体装置の製造方法。

**【請求項 4】**

(a) 酸化シリコン基板上のシリコン膜上にシリコン酸化膜と、多結晶シリコンと、シリコン窒化膜とをこの順に積層する工程と、

(b) 所定領域において前記シリコン窒化膜と、前記多結晶シリコンと、前記シリコン酸化膜と、前記シリコン膜とをエッチングして、前記シリコン膜中に底面を有するトレンチを形成する工程と、

(c) 800 乃至 1200 で、30 秒乃至 4 時間のアニールを行い、前記トレンチに露出する前記シリコン膜の表面に絶縁膜を形成する工程と、

(d) 前記絶縁膜を除去する工程と、

(e) 前記トレンチに絶縁材料を埋め込む工程と

を備える、半導体装置の製造方法。

20

**【請求項 5】**

前記工程 (d) と、前記工程 (e)との間に、前記トレンチに露出する前記シリコン膜の表面に酸化膜を形成する工程を、更に備える、請求項 1 乃至 請求項 4 のいずれか一つに記載の半導体装置の製造方法。

30

**【請求項 6】**

(a) 酸化シリコン基板上のシリコン膜上にシリコン酸化膜と、多結晶シリコンと、シリコン窒化膜とをこの順に積層する工程と、

(b) 所定領域において前記シリコン窒化膜と、前記多結晶シリコンと、前記シリコン酸化膜と、前記シリコン膜とをエッチングして、前記シリコン膜中に底面を有するトレンチを形成する工程と、

(c) 前記トレンチに露出する前記シリコン膜の表面を、ウェットエッチングにより 1 nm 乃至 20 nm の厚みを除去する工程と、

(d) 前記トレンチに絶縁材料を埋め込む工程と

を備える、半導体装置の製造方法。

40

**【請求項 7】**

前記工程 (c) と、前記工程 (d)との間に、前記トレンチに露出する前記シリコン膜の表面に酸化膜を形成する工程を、更に備える、請求項 6 記載の半導体装置の製造方法。

**【請求項 8】**

前記トレンチに前記絶縁材料を埋め込む工程の後に、600 以下で 1 時間以上アニールする工程を、更に備える、請求項 1 乃至 請求項 7 のいずれか一つに記載の半導体装置の製造方法。

50

**【請求項 9】**

(a) 酸化シリコン基板上のシリコン膜上にシリコン酸化膜と、多結晶シリコンと、シリコン窒化膜とをこの順に積層する工程と、

(b) 所定領域において前記シリコン窒化膜と、前記多結晶シリコンと、前記シリコン酸化膜と、前記シリコン膜とをエッティングして、前記シリコン膜中に底面を有するトレンチを形成する工程と、

(c) 前記トレンチに露出する前記シリコン膜の表面に酸化膜を形成する工程と、

(d) 前記トレンチに絶縁材料を埋め込む工程と、

(e) 600 以下で1時間以上アニールする工程と

を備える、半導体装置の製造方法。

10

**【請求項 10】**

前記工程(e)の後に、前記シリコン膜にウェル領域を形成する工程を、更に備える、請求項9記載の半導体装置の製造方法。

**【請求項 11】**

前記トレンチに前記絶縁材料を埋め込む工程の後に、表面に露出した前記絶縁材料の前記シリコン膜側を曲面形状にする工程を、更に備える、請求項1乃至請求項10のいずれか一つに記載の半導体装置の製造方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

この発明は、半導体装置の製造方法に関し、例えばトランジスタや集積回路・メモリに適用することができる。

**【背景技術】****【0002】**

従来から、半導体デバイスを製造する技術の一つとして、MOS(Metal Oxide Semiconductor)構造等を有するデバイスをSOI(Silicon on Insulating substrate)基板上に形成している。また、素子間の分離を行うために、pn接合分離や酸化膜分離(例えばLOCOS(Local Oxidation of Silicon)法など)等が用いられている。

**【0003】**

なお、シリコン基板中の汚染物質の濃度を低下させて、その後に形成される酸化膜に汚染物質が拡散することを防止する技術が、特許文献1に開示されている。素子間の分離を行うためのトレンチ分離領域を形成する技術が、特許文献2に開示されている。またシリコン窒化膜と多結晶シリコン・シリコン酸化膜の積層構造を、後述するCMPのマスクに採用する技術が非特許文献1に紹介されている。汚染金属の拡散係数と温度の関係が、非特許文献2に紹介されている。

**【0004】****【特許文献1】特開平10-209446号公報****【特許文献2】特表平11-513538号公報**

**【非特許文献1】**ケイ・ホリタ(K.Horita)、他7名、「Advanced Shallow Trench Isolation to Suppress the Inverse Narrow Channel Effects for 0.24μm Pitch Isolation and Beyond」, 2000シンポジウムオンバイエルエスアイテクノロジー・ダイジェスト・オブ・テクニカル・ペイパーズ(2000 Symposium on VLSI Technology Digest of Technical Papers), 2000年, p. 178-179

**【非特許文献2】**大見忠弘、他監修、「シリコンの科学」、リアライズ(REALIZE Inc)社, p. 1015

**【発明の開示】****【発明が解決しようとする課題】**

20

30

40

50

## 【0005】

ところが、SOI基板上にデバイスを形成する際に金属汚染物質が層間に残留し、また素子分離を行うためのトレンチを形成する際にトレンチ底部に金属汚染物質が付着する。金属汚染物質は、半導体デバイスがもつ性能及び信頼性を低下させる原因となる。

## 【0006】

これまでにも、金属汚染物質を取り除く方法が提案されている。すなわち、シリコン表面上にゲート絶縁膜を形成する前に、そのゲート絶縁膜が形成される位置に犠牲酸化膜を形成する。そして、シリコンと犠牲酸化膜の界面へと金属汚染物質を拡散・凝集させて、犠牲酸化膜を除去するとともに金属汚染物質を取り除く。

## 【0007】

しかし、この方法には次の可能性が考えられる。すなわち、その凝集した金属汚染物質がシリコン表面上に凹部の痕を残し、そのシリコン表面上にゲート絶縁膜を形成すると、その凹部の痕に応力が発生し、絶縁膜に亀裂が生じて絶縁破壊を起こす。

## 【0008】

本発明は、上記の事情に鑑みてなされたものであり、半導体デバイスがもつ性能及び信頼性の低下を防止する。

## 【課題を解決するための手段】

## 【0009】

本発明にかかる第一の半導体装置の製造方法は、(a)酸化シリコン基板上のシリコン膜上にシリコン酸化膜と、多結晶シリコンと、シリコン窒化膜とをこの順に積層する工程と、(b)所定領域において前記シリコン窒化膜と、前記多結晶シリコンと、前記シリコン酸化膜と、前記シリコン膜とをエッティングして、前記シリコン膜中に底面を有するトレンチを形成する工程と、(c)前記トレンチに露出する前記シリコン膜の表面に600以下で絶縁膜を形成する工程と、(d)前記絶縁膜を除去する工程と、(e)前記トレンチに絶縁材料を埋め込む工程とを備える。

## 【0010】

本発明にかかる第二の半導体装置の製造方法は、(a)酸化シリコン基板上のシリコン膜上にシリコン酸化膜と、多結晶シリコンと、シリコン窒化膜とをこの順に積層する工程と、(b)所定領域において前記シリコン窒化膜と、前記多結晶シリコンと、前記シリコン酸化膜と、前記シリコン膜とをエッティングして、前記シリコン膜中に底面を有するトレンチを形成する工程と、(c)800乃至1200で、30秒乃至4時間のアニールを行い、前記トレンチに露出する前記シリコン膜の表面に絶縁膜を形成する工程と、(d)前記絶縁膜を除去する工程と、(e)前記トレンチに絶縁材料を埋め込む工程とを備える。

## 【0011】

本発明にかかる第三の半導体装置の製造方法は、(a)酸化シリコン基板上のシリコン膜上にシリコン酸化膜と、多結晶シリコンと、シリコン窒化膜とをこの順に積層する工程と、(b)所定領域において前記シリコン窒化膜と、前記多結晶シリコンと、前記シリコン酸化膜と、前記シリコン膜とをエッティングして、前記シリコン膜中に底面を有するトレンチを形成する工程と、(c)前記トレンチに露出する前記シリコン膜の表面を、ウェットエッティングにより1nm乃至20nmの厚みだけ除去する工程と、(d)前記トレンチに絶縁材料を埋め込む工程とを備える。

## 【0012】

本発明にかかる第四の半導体装置の製造方法は、(a)酸化シリコン基板上のシリコン膜上にシリコン酸化膜と、多結晶シリコンと、シリコン窒化膜とをこの順に積層する工程と、(b)所定領域において前記シリコン窒化膜と、前記多結晶シリコンと、前記シリコン酸化膜と、前記シリコン膜とをエッティングして、前記シリコン膜中に底面を有するトレンチを形成する工程と、(c)前記トレンチに露出する前記シリコン膜の表面に酸化膜を形成する工程と、(d)前記トレンチに絶縁材料を埋め込む工程と、(e)600以下で1時間以上アニールする工程とを備える。

10

20

30

40

50

**【発明の効果】****【0013】**

この発明にかかる第一もしくは第二の半導体装置の製造方法によれば、工程(c)によってシリコン膜と絶縁膜の界面に金属汚染物質を拡散・凝集させることができ、絶縁膜の除去とともにその金属汚染物質を取り除くことができる。よって、半導体装置がもつ性能及び信頼性の低下を防止することができる。

**【0014】**

この発明にかかる第三の半導体装置の製造方法によれば、工程(c)によってシリコン膜の表面に付着する金属汚染物質を取り除くことができる。よって、半導体装置がもつ性能及び信頼性の低下を防止することができる。

10

**【0015】**

この発明にかかる第四の半導体装置の製造方法によれば、工程(e)によってシリコン膜と酸化膜の界面に金属汚染物質を拡散・凝集させることができる。よって、半導体装置がもつ性能及び信頼性の低下を防止することができる。

**【発明を実施するための最良の形態】****【0016】****実施の形態1.**

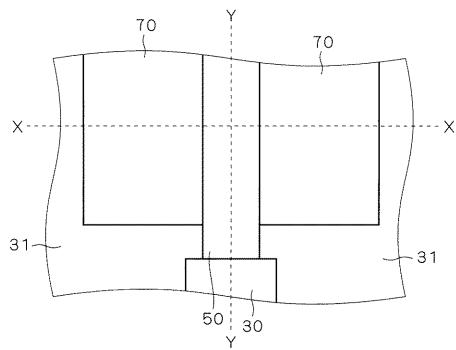

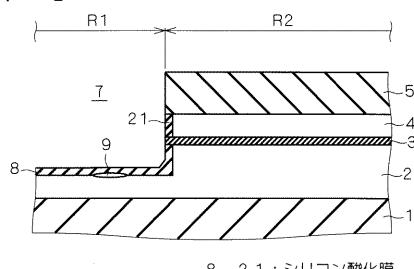

本実施の形態では、トレンチ内部を低温で酸化する。図1は本実施の形態で説明される方法によって作製される半導体装置の平面図である。図10および図11は、それぞれ図1で示される位置Y-Yおよび位置X-Xでの概念的な断面図であり、図2乃至図10は、位置Y-YにおいてSOI基板上にMOSデバイスを形成する過程を順に示す断面図である。但し、本明細書でいうMOSデバイスはゲート電極の材料として金属(Metal)に限定されず、導電性半導体を用いる場合をも含む概念である。

20

**【0017】**

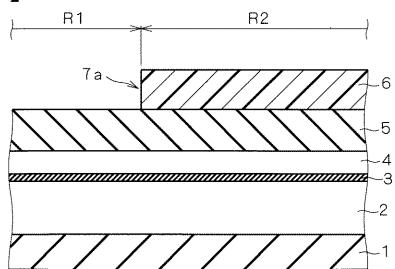

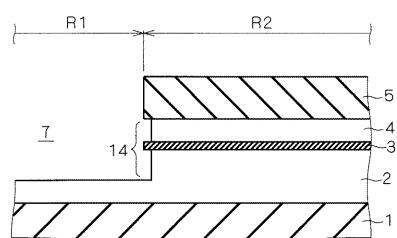

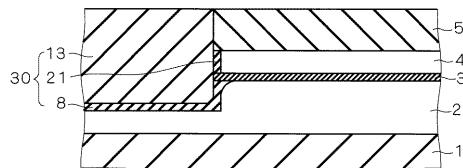

第1に、SOI基板が酸化シリコン基板1とシリコン膜2で形成される。酸化シリコン基板1とは反対側でシリコン膜2の表面上に、シリコン酸化膜3が酸化によって形成される。そしてシリコン酸化膜3上に、多結晶シリコン4とシリコン窒化膜5が順に積層される。領域R1は素子分離のための構成を形成するために、領域R2は素子を形成するためにそれぞれ設定される。シリコン窒化膜5上には、領域R1で開口し領域R2を覆うレジスト樹脂6が積層される。レジスト樹脂6の端面7aは領域R1, R2の境界に位置する(図2)。

30

**【0018】**

シリコン酸化膜3や多結晶シリコン4・シリコン窒化膜5を形成する段階ごとに金属汚染物質が付着する可能性がある。金属汚染物質として、鉄(Fe)やニッケル(Ni)・コバルト(Co)・チタン(Ti)・アルミニウム(Al)・クロム(Cr)などが考えられる。

30

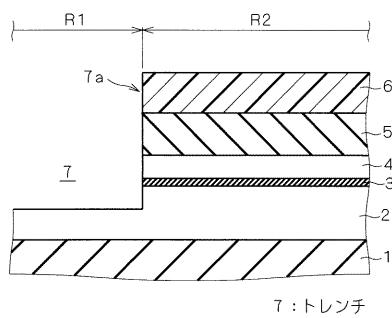

**【0019】**

第2に、レジスト樹脂6の端面7aで形成されるパターンに従って、シリコン窒化膜5と多結晶シリコン4・シリコン酸化膜3・シリコン膜2とをエッチングすることで、領域R1にトレンチ7が形成される。レジスト6の表面上に開口し内部が中空のトレンチ7では、シリコン膜2中に底面が位置する(図3)。トレンチ7の形成の際にもトレンチ7の底面に金属汚染物質が付着する可能性がある。

40

**【0020】**

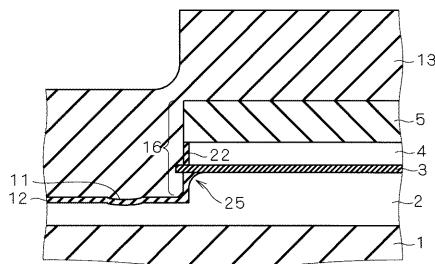

第3に、レジスト樹脂6を除去し、トレンチ7に露出するシリコン膜2の表面に600以下で絶縁膜を形成する。絶縁膜を形成する方法としてシリコン膜2をラジカル酸化もしくは高密度プラズマ酸化すること等が採用できる。例えば高密度プラズマ酸化を行う際には、基板温度を200乃至600とし、励起エネルギーをプラズマで与える。これによって、トレンチ7において露出したシリコン膜2の表面上で酸化反応を起こり、シリコン酸化膜8が絶縁膜として形成される。これに伴って、トレンチ7の側面に露出した多結晶シリコン4についても酸化され、シリコン酸化膜21が形成される。トレンチ7の底

50

面に付着した金属汚染物質は、シリコン酸化膜 8 とシリコン膜 2 の界面で、若しくはシリコン酸化膜 8 の内部で凝集して金属シリサイド 9 となる（図 4）。

#### 【0021】

形成するシリコン酸化膜 8 の厚みは、トレンチ 7 の底面に付着した金属汚染物質がシリコン膜 2 へ侵入する深さと、金属汚染物質をどこに凝集されるかとによって決めてよい。金属汚染物質は、シリコン膜 2 とシリコン酸化膜 8 の界面に凝集させてもよいし、シリコン酸化膜 8 の内部に凝集させてもよい。例えば、金属汚染物質の侵入深さが最大で 10 nm あるとすると、シリコン膜 2 とシリコン酸化膜 8 との界面に汚染金属を凝集させる場合には、シリコン酸化膜 8 の厚みを 1 ~ 10 nm 程度にし、金属汚染物質をシリコン酸化膜 8 の内部に凝集させる場合には、シリコン酸化膜の厚みを 1 ~ 30 nm 程度にする。このような膜厚の決め方は、シリコン膜 2 の表面に形成される絶縁膜が後述するようなシリコン窒化膜の場合においても適用することができる。10

#### 【0022】

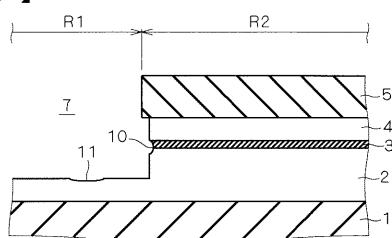

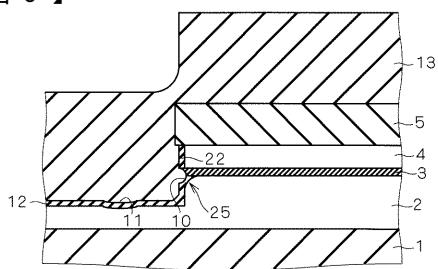

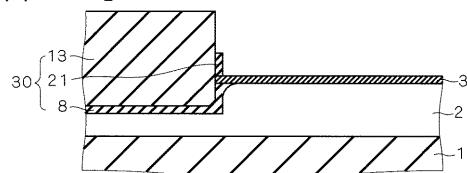

第 4 に、第 3 の工程で形成したシリコン酸化膜 8 を HF ( フッ化水素酸 ) 系溶液によって除去する。これに伴って金属シリサイド 9 も除去され、トレンチ 7 のシリコン膜 2 において窪み 11 が形成される。この際には、トレンチ 7 の側面に露出している部分について第 1 の工程で形成されたシリコン酸化膜 3 も HF 系溶液によって侵食され、その侵食された部分が窪み 10 となる。また第 3 の工程で形成されたシリコン酸化膜 21 も HF 系溶液によって除去される（図 5）。20

#### 【0023】

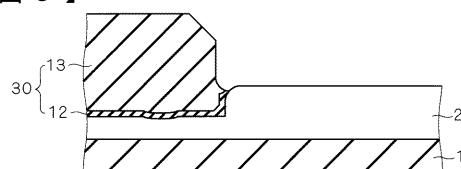

第 5 に、再び酸化することで、トレンチ 7 において露出したシリコン膜 2 の表面にシリコン酸化膜 12 を形成する。これに伴い、トレンチ 7 の側面に露出した部分について多結晶シリコン 4 も酸化され、シリコン酸化膜 22 が形成される。このときの酸化は、シリコン酸化膜 8 の形成時とは異なり、600 以下であることを必要としない。その後、トレンチ 7 を埋め込みかつシリコン窒化膜 5 の表面上を覆う絶縁材料、例えばシリコン酸化膜 13 が堆積される。前者と後者に堆積されるシリコン酸化膜 13 は連続している（図 6）。30

#### 【0024】

シリコン酸化膜 12 の形成の際には、窪み 10 に応力が発生して亀裂が生じる可能性も考えられる。しかし、シリコン酸化膜 13 が埋め込まれたトレンチ 7 は素子分離のための構成として機能するため、亀裂の発生は当該機能に対して問題とならない。30

#### 【0025】

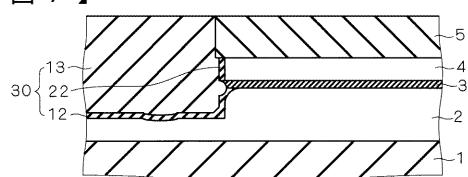

第 6 に、CMP ( Chemical and Mechanical Polishing ) により、第 5 の工程で形成したシリコン酸化膜 13 を研磨して平坦化するとともに、シリコン窒化膜 5 の表面全体を露出させる（図 7）。このとき、トレンチ 7 の内部に残存するシリコン酸化膜 12, 13 が素子を分離するための酸化膜、すなわち分離酸化膜 30 となる。40

#### 【0026】

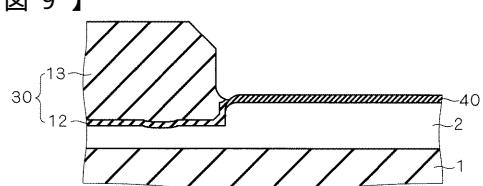

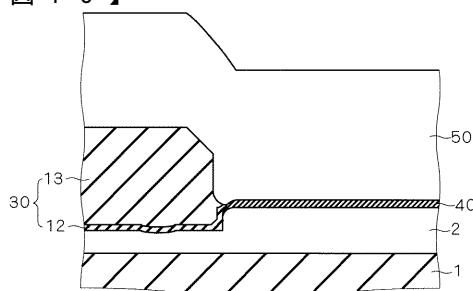

第 7 に、シリコン窒化膜 5 と多結晶シリコン 4・シリコン酸化膜 3・シリコン酸化膜 2 が除去される（図 8）。これらの除去により露出したシリコン膜 2 の表面を酸化することで、シリコン酸化膜 40 が形成される（図 9）。そして、シリコン酸化膜 13, 40 の表面上に多結晶シリコン 50 を堆積する（図 10）。40

#### 【0027】

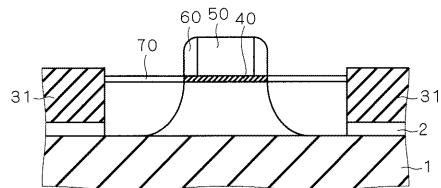

第 8 に、第 7 の工程後、多結晶シリコン 50 のパターンエッチング、絶縁膜の形成及び絶縁膜のパターンエッチングを経て、多結晶シリコン 50 の側面に絶縁膜 60 を形成する。そして、不純物イオンの打ち込み及び金属シリサイド膜 70 の形成により半導体デバイスを作製する（図 11）。50

#### 【0028】

金属汚染物質は、半導体デバイス中で相対的に応力の大きな部分に拡散・凝集しやすい。トレンチ 7 にかかる応力は他の部分と比較して大きくなると考えられるため、トレンチ

7の底面に付着した金属汚染物質は酸化の際にそこに留められやすくなる。

#### 【0029】

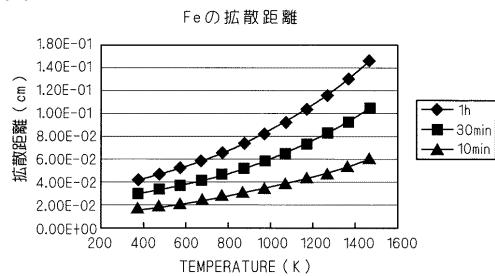

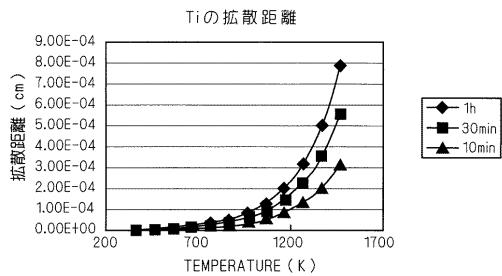

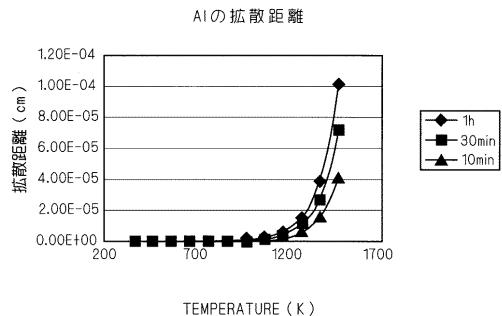

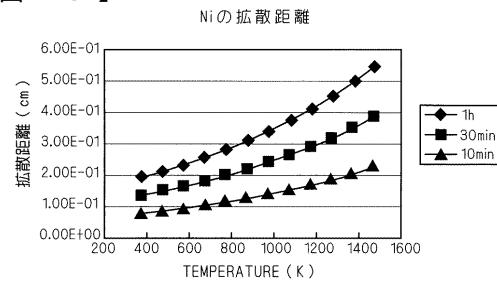

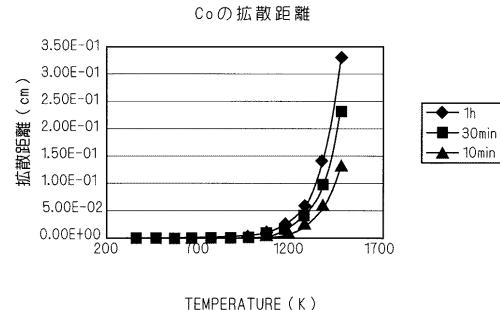

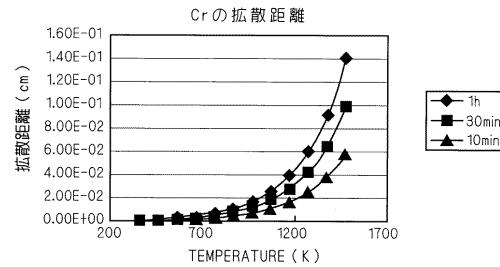

一方、金属汚染物質の拡散は温度に依存する。金属汚染物質の温度と拡散距離の関係が金属汚染物質の種類ごとに図24乃至図29に示されている。金属汚染物質の拡散距離は、 $(D \times t)$ により求められる。ここで、Dは拡散係数（単位は $\text{cm}^2/\text{sec}$ である）を、tは拡散時間（単位は $\text{sec}$ である）をそれぞれ表す。拡散係数Dは、非特許文献2中のFig.1に紹介される拡散係数Dと温度との関係から、金属汚染物質ごとに求められる。

#### 【0030】

シリコン膜2の表面上にシリコン酸化膜8を形成する温度が600（図に示されるグラフの横軸を表す温度の単位はケルビン（K）であり、873Kに対応する）以下であるため、図24～図29から金属汚染物質の拡散距離が小さくなることが理解できる。このため、トレンチ7の底面にある金属汚染物質は、領域R1から領域R2へ拡散しにくく、シリコン酸化膜8とシリコン膜2の界面、あるいはシリコン酸化膜8の内部で凝集しやすくなる。図26～図29に示されるように600以下ではCo・Ti・Al・Crの拡散距離が非常に小さく、特にこれらの汚染物質に対して本実施の形態が有効である。よって、半導体デバイスの作製過程で混入する金属汚染物質を取り除くことができ、半導体デバイスがもつ性能及び信頼性の低下を防止することができる。

#### 【0031】

トレンチ7の底面に付着した金属汚染物質を取り除く場合のみならず、第1の工程に記載するシリコン膜2やシリコン酸化膜3・多結晶シリコン4・シリコン窒化膜5のそれぞれの界面（領域R2にある界面）に存在する金属汚染物質を取り除く場合にも、シリコン酸化膜8の形成が有効である。すなわちシリコン酸化膜8の形成により、領域R2にある界面に存在する金属汚染物質がシリコン膜2とシリコン酸化膜8の界面、あるいはシリコン酸化膜8の内部に拡散・凝集して、金属汚染物質は金属シリサイド9となる。よって、図24、図25に示されるように600以下においても拡散距離が大きいFe・Niなどに特に有効である。

#### 【0032】

この場合にも上述の内容と同様に、シリコン酸化膜8とともに金属シリサイド9がHF系溶液により除去される。よって、半導体デバイスの作製過程で混入する金属汚染物質を取り除くことができ、半導体デバイスがもつ性能及び信頼性の低下を防止することができる。

#### 【0033】

上記第3の工程において、トレンチ7に露出したシリコン膜2の表面上をプラズマ窒化してもよい。この場合、基板温度を200乃至600とし、励起エネルギーをプラズマで与える。これによって、トレンチ7において露出したシリコン膜2と多結晶シリコン4の表面上で窒化反応が起こり、シリコン窒化膜が絶縁膜として形成される。金属汚染物質は、シリコン窒化膜とシリコン膜2の界面に、若しくはシリコン窒化膜の内部に拡散・凝集して金属シリサイド9となる。その後、第4の工程においてHF系溶液に替えて磷酸系溶液を用いることで、シリコン窒化膜とともに金属シリサイド9が除去される。

#### 【0034】

上記第3の工程において、トレンチ7に露出したシリコン膜2の表面上をオゾン系溶液により酸化してもよい。この場合、基板温度を20乃至120とする。これによって、トレンチ7において露出したシリコン膜2と多結晶シリコン4の表面上で酸化反応が起こり、シリコン酸化膜8が絶縁膜として形成される。金属汚染物質は、シリコン酸化膜8とシリコン膜2の界面に、若しくはシリコン酸化膜8の内部に拡散・凝集して金属シリサイド9となる。その後、第4の工程において、シリコン酸化膜8とともに金属シリサイド9がHF系溶液により除去される。

#### 【0035】

シリコン膜2の表面上を、プラズマによる窒化およびオゾン系溶液による酸化のいずれ

10

20

30

40

50

の方法においても、上述した例えはプラズマにより酸化する方法と同様に、半導体デバイスの作製過程で混入する金属汚染物質を取り除くことができる。よって、半導体デバイスがもつ性能及び信頼性の低下を防止することができる。

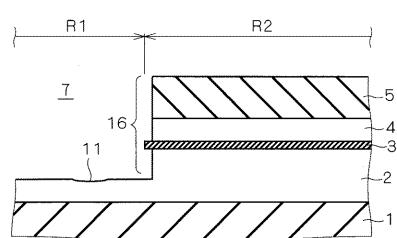

#### 【0036】

実施の形態2.

本実施の形態では、窒素雰囲気中でアニールを行う。図12乃至図14は、図1で示される位置Y-Yでの概念的な断面図であり、SOI基板上にMOSデバイスを形成する過程を順に示す。

#### 【0037】

第1に、実施の形態1で記載される第1及び第2の工程と同様にSOI基板上に各種の膜を形成し、その後にトレンチ7を形成する(図3)。このときシリコン膜2やシリコン酸化膜3・多結晶シリコン4・シリコン窒化膜5を形成するそれぞれの段階で金属汚染物質が付着すること、またトレンチ7の底面に金属汚染物質が付着することのそれぞれの可能性が考えられる。

#### 【0038】

第2に、レジスト樹脂6を除去し、窒化する。この窒化では、800乃至1200の窒素雰囲気中で30秒間乃至4時間、シリコン膜2の表面をアニールする。これにより、トレンチ7において露出したシリコン膜2の表面に、シリコン窒化膜15が絶縁膜として形成される。これに伴って、トレンチ7の側面に露出した部分について多結晶シリコン4も窒化されて、シリコン窒化膜23が形成される。シリコン膜2やシリコン酸化膜3・多結晶シリコン4・シリコン窒化膜5のそれぞれの界面にある金属汚染物質は、シリコン膜2とシリコン窒化膜15の界面に、若しくはシリコン窒化膜15の内部に拡散・凝集して金属シリサイド9となる(図12)。

#### 【0039】

実施の形態1と同様に、形成するシリコン窒化膜15の厚みは、トレンチ7の底面に付着した金属汚染物質がシリコン膜2へ侵入する深さと、金属汚染物質をどこに凝集されるかとによって決めてよい。

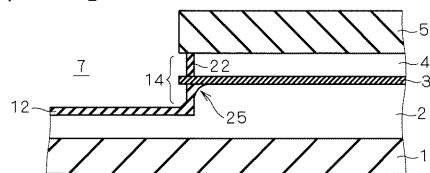

#### 【0040】

第3に、第2の工程で形成したシリコン窒化膜15を、20乃至180の磷酸系溶液により除去する。これに伴って金属シリサイド9も除去され、トレンチ7のシリコン膜2において窪み11が形成される。この際には、トレンチ7の側面に露出している部分について第1の工程で形成されたシリコン窒化膜5も磷酸系溶液によって侵食される。また、シリコン窒化膜23も磷酸系溶液によって除去される。このとき、シリコン酸化膜3は磷酸系溶液に反応しないため、シリコン酸化膜3が突出した形状16をトレンチ7の側面に呈する(図13)。

#### 【0041】

シリコン窒化膜15の除去に、20乃至100のHF溶液を用いてよい。この場合においても同様に、金属シリサイド9を除去することができる。

#### 【0042】

第4に、酸化することで、トレンチ7に露出したシリコン膜2の表面にシリコン酸化膜12を形成する。これに伴い、トレンチ7の側面に露出した部分について多結晶シリコン4も酸化され、シリコン酸化膜22が形成される。その後、トレンチ7を埋め込みかつシリコン窒化膜5の表面上を覆う絶縁材料、例えばシリコン酸化膜13が堆積される。前者と後者に堆積されたシリコン酸化膜13は連続している(図14)。

#### 【0043】

シリコン酸化膜12の形成の際には、窪み10に応力が発生して亀裂が生じる可能性も考えられる。しかし、シリコン酸化膜13が埋め込まれたトレンチ7は素子分離のための構成として機能するため、亀裂の発生は当該機能に対して問題とならない。

#### 【0044】

第5に、実施の形態1で記載される第6乃至8の工程と同様に、半導体デバイスを作製

10

20

30

40

50

する。

#### 【0045】

半導体デバイスの他の部分と比較してトレンチ7にかかる応力は大きくなると考えられる。このため、シリコン膜2とシリコン窒化膜15の界面へとアニールによって拡散した金属汚染物質は、その界面に留められて凝集しやすくなる。また、30秒間乃至4時間に設定されたアニール時間は、シリコン膜2とシリコン窒化膜15の界面に金属汚染物質が到達するために十分な時間と考えられる。

#### 【0046】

例えばFeやNi・Co・Crについて、これらの金属汚染物質が拡散しなければならない距離を0.1mmとする場合、1200で1.22秒乃至18.3秒の拡散時間を、800で2.60秒乃至53.6分の拡散時間をそれぞれ必要とする。また、拡散しなければならない距離を1mmとする場合、1200で2.03分乃至30.4分の拡散時間を、800で4.34分乃至89.4時間の拡散時間をそれぞれ必要とする。このように、アニール時間は金属汚染物質の種類や温度・拡散距離により設定される。

#### 【0047】

上述の内容から、800乃至1200の窒素雰囲気中で30秒間乃至4時間かけてシリコン膜2の表面をアニールすることで、領域R2の中の金属汚染物質はR1へ拡散し、シリコン膜2とシリコン窒化膜15の界面で凝集しやすくなる。よって、半導体デバイスの作製過程で混入する金属汚染物質を取り除くことができ、半導体デバイスがもつ性能及び信頼性の低下を防止することができる。

#### 【0048】

シリコン膜2やシリコン酸化膜3・多結晶シリコン4・シリコン窒化膜5のそれぞれの界面に存在する金属汚染物質を取り除く場合のみならず、トレンチ7の底面に付着する金属汚染物質を取り除く場合にも、本実施の形態の特徴のうち800乃至1200の窒素雰囲気中でアニールすることが有効である。

#### 【0049】

上記第2の工程において、トレンチ7に露出したシリコン膜2の表面を、800乃至1200のアルゴン/酸素雰囲気中でアニールしてもよい。この場合、シリコン膜2の表面上が酸化されてシリコン酸化膜が絶縁膜として形成されるとともに、シリコン膜2とシリコン酸化膜との界面に微細な凹凸が形成される。これによって、そこに留まりやすくなったり金属汚染物質は、シリコン酸化膜とシリコン膜2との界面で、若しくはシリコン酸化膜の内部で凝集して金属シリサイド9となる。その後、第3の工程において、シリコン酸化膜とともに金属シリサイド9がHF系溶液により除去される。

#### 【0050】

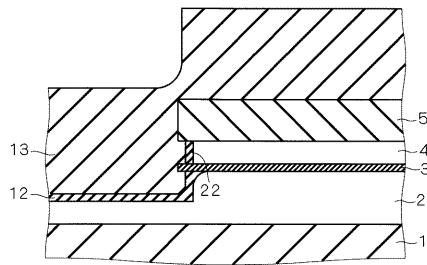

##### 実施の形態3.

本実施の形態では、トレンチ内部をエッチングする。図15乃至図17は、図1で示される位置Y-Yでの概念的な断面図であり、SOI基板上にMOSデバイスを形成する過程が順に示される。

#### 【0051】

第1に、実施の形態1で記載される第1及び第2の工程と同様にSOI基板上に各種の膜を形成し、その後にトレンチ7を形成する(図3)。このとき、トレンチ7の底面に金属汚染物質が付着する可能性がある。

#### 【0052】

第2に、レジスト樹脂6を除去し、20乃至150のアンモニア過水系溶液を用いて、トレンチ7に露出したシリコン膜2の表面をウェットエッチングする。これにより、シリコン膜2に付着した金属汚染物質を取り除くことができる。例えば、金属汚染物質のシリコン膜2への侵入深さが10nm程度である場合には、ウェットエッチングにより除去するシリコン膜の厚みは10nm乃至20nmであることが望ましい。アンモニア過水系溶液は多結晶シリコン4をもエッチングするため、トレンチ7の側面にある多結晶シリコン4とシリコン膜2のそれぞれの端面が退き、シリコン酸化膜3が突出した形状14を

10

20

30

40

50

トレンチ 7 の側面に呈する(図 15)。

【0053】

第3に、トレンチ 7 に露出したシリコン膜 2 の表面を酸化してシリコン酸化膜 12 を形成する。これに伴って、トレンチ 7 の側面に露出した部分について多結晶シリコン 4 も酸化されて、シリコン酸化膜 22 が形成される(図 16)。その後、トレンチ 7 を埋め込みかつシリコン窒化膜 5 の表面上を覆う絶縁材料、例えばシリコン酸化膜 13 が堆積される。前者と後者に堆積されたシリコン酸化膜 13 は連続している(図 17)。

【0054】

第4に、実施の形態 1 で記載される第6乃至第8の工程と同様に半導体デバイスを作製する。

【0055】

アンモニア過水系溶液により、トレンチ 7 に露出したシリコン膜 2 の表面をエッティングすることで、トレンチ 7 の底面に付着した金属汚染物質を除去する。よって、半導体デバイスの作製過程で混入する金属汚染物質を取り除くことができ、半導体デバイスがもつ性能及び信頼性の低下を防止することができる。

【0056】

上記第2の工程において、20 乃至 150 のアンモニア水溶液や 20 乃至 150 のバッファードフッ酸(BHF)溶液、20 乃至 150 の水酸化カリウム(KOH)溶液等を用いて、トレンチ 7 に露出したシリコン膜 2 の表面をウェットエッティングしてもよい。この場合においても、上述した 20 乃至 150 のアンモニア過水系溶液を用いたときと同様の効果を得ることができる。

【0057】

上述した実施の形態 1 の第5の工程、実施の形態 2 の第4の工程、実施の形態 3 の第3の工程において、それぞれトレンチ 7 において露出したシリコン膜 2 の表面にシリコン酸化膜 12 を形成することで、シリコン膜 2 のトレンチ 7 側のエッジ部分 25 が曲面状になる(図 6、図 14、図 16)。これにより、エッジ部 25 が角張っている際に起る可能性のある電界集中を低減することができる。よって、半導体装置がもつ性能及び信頼性の低下を防止することができる。

【0058】

上記いずれの実施の形態においてもシリコン酸化膜 12 を形成しない場合が考えられるが、例えばシリコン酸化膜 12 を形成することで電界集中を回避することができる。

【0059】

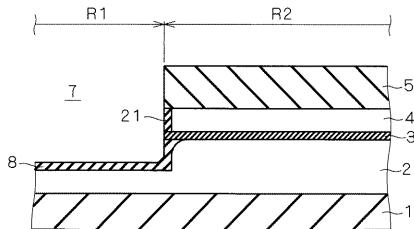

実施の形態 4.

本実施の形態では、低温でアニールを行う。図 18 乃至 図 22 は、図 1 で示される位置 Y-Y での概念的な断面図であり、SOI 基板上に MOS デバイスを形成する過程を順に示す。

【0060】

第1に、実施の形態 1 で記載される第1及び第2の工程と同様に SOI 基板上に各種の膜を形成し、その後にトレンチ 7 を形成する(図 3)。このとき、シリコン膜 2 やシリコン酸化膜 3・多結晶シリコン 4・シリコン窒化膜 5 を形成するそれぞれの段階で金属汚染物質が付着すること、またトレンチ 7 の底面に金属汚染物質が付着することのそれぞれの可能性が考えられる。

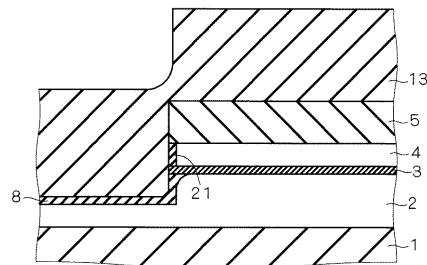

【0061】

第2に、レジスト樹脂 6 を除去し、酸化することで、トレンチ 7 に露出したシリコン酸化膜 8 を形成する。これに伴って、トレンチ 7 の側面に露出した部分について多結晶シリコン 4 も酸化されて、シリコン酸化膜 21 が形成される(図 18)。その後、トレンチ 7 を埋め込みかつシリコン窒化膜 5 の表面上を覆う絶縁材料、例えばシリコン酸化膜 13 が堆積される。前者と後者に堆積されたシリコン酸化膜 13 は連続している(図 19)。

【0062】

第3に、第2の工程で形成したシリコン酸化膜 13 を CMP により研磨して平坦化する

10

20

30

40

50

とともに、シリコン窒化膜5の表面全体を露出させる(図20)。このとき、トレンチ7の内部に残存するシリコン酸化膜8, 13, 21が分離酸化膜30となる。そして、シリコン窒化膜5と多結晶シリコン4が除去される(図21)。

#### 【0063】

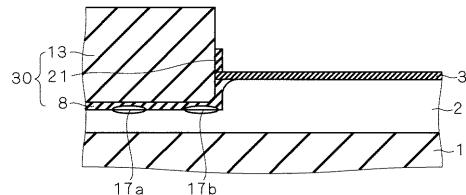

第4に、第3の工程までで作製された半導体デバイス全体を600以下で1時間以上アニールする。これにより、第1の工程で混入した金属汚染物質は、シリコン膜2とシリコン酸化膜8の界面で凝集して金属シリサイド17a, 17bとなる。金属シリサイド17aは、トレンチ7の形成時に付着した金属汚染物質が凝集して、また金属シリサイド17bは、シリコン膜2やシリコン酸化膜3・多結晶シリコン4・シリコン窒化膜5のそれぞれの界面に存在する金属汚染物質が拡散・凝集してそれぞれ形成される(図22)。

10

#### 【0064】

第5に、シリコン酸化膜3, 13, 21の表面上に多結晶シリコン50を堆積する。以下、実施の形態1の第8の工程と同様に半導体デバイスを作製する。

#### 【0065】

半導体デバイスの他の部分と比較して応力が大きくなるトレンチ7で金属汚染物質が留まりやすくなる。そして、そこで凝集した金属汚染物質は金属シリサイド17a, 17bとなる。よって、デバイスとして働く主要部分(領域R2)には金属汚染物質がほとんど存在せず、半導体デバイスがもつ性能及び信頼性の低下を防止することができる。

#### 【0066】

上述した半導体デバイスの作製において、シリコン膜2にウェル領域を形成する必要がある場合には、第3の工程と第4の工程の間、すなわち図21に示される状態で、シリコン膜2にシリコン酸化膜3側から不純物の注入を行ってウェル領域を形成してもよい。この場合、第4の工程で行うアニールによって、ウェル領域に注入された不純物は金属汚染物質とともに拡散し、ウェル領域の不純物濃度が設定値からずれる可能性がある。このため、アニールの後にウェル領域の不純物濃度を再調整することが望ましい。

20

#### 【0067】

シリコン膜2にウェル領域を形成する必要がある場合には、第4の工程の後で前記シリコン膜2にウェル領域を形成してもよい。この場合、ウェル領域の不純物濃度を再調整する必要がなく、よって工程が単純化される。

#### 【0068】

実施の形態1の第7の工程(実施の形態2の第4の工程又は実施の形態3の第5の工程において採用される場合を含む)において、シリコン酸化膜3を除去する前に本実施の形態の第4の工程で説明したアニールの方法を適用することで、より効果的に半導体デバイスがもつ性能及び信頼性の低下を防止することができる。

30

#### 【0069】

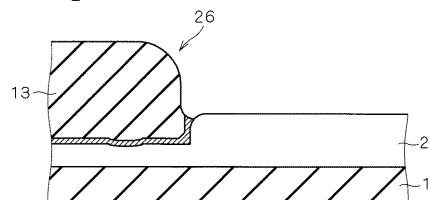

上述いずれの実施の形態においても、トレンチ7に絶縁材料13を埋め込んだ後に、表面に露出した絶縁材料13のシリコン酸化膜2側を曲面形状にしてもよい。図23には、例えば図8に対応させて、表面に露出した絶縁材料13のシリコン酸化膜2側の部分26が曲面形状を呈する場合が示されている。

#### 【0070】

絶縁材料13の部分26が曲面形状を呈する場合には、絶縁材料13の部分26のシリコン膜2の表面に対する傾斜が緩やかになる。よって、ゲートを形成するプロセスが容易になる。

40

#### 【図面の簡単な説明】

#### 【0071】

【図1】半導体装置を示す概念的な平面図である。

【図2】実施の形態1で説明する、製造段階での半導体装置を示す断面図である。

【図3】実施の形態1で説明する、製造段階での半導体装置を示す断面図である。

【図4】実施の形態1で説明する、製造段階での半導体装置を示す断面図である。

【図5】実施の形態1で説明する、製造段階での半導体装置を示す断面図である。

50

- 【図6】実施の形態1で説明する、製造段階での半導体装置を示す断面図である。

- 【図7】実施の形態1で説明する、製造段階での半導体装置を示す断面図である。

- 【図8】実施の形態1で説明する、製造段階での半導体装置を示す断面図である。

- 【図9】実施の形態1で説明する、製造段階での半導体装置を示す断面図である。

- 【図10】実施の形態1で説明する、製造段階での半導体装置を示す断面図である。

- 【図11】実施の形態1で説明する、製造される半導体装置を示す断面図である。

- 【図12】実施の形態2で説明する、製造段階での半導体装置を示す断面図である。

- 【図13】実施の形態2で説明する、製造段階での半導体装置を示す断面図である。

- 【図14】実施の形態2で説明する、製造段階での半導体装置を示す断面図である。

- 【図15】実施の形態3で説明する、製造段階での半導体装置を示す断面図である。

- 【図16】実施の形態3で説明する、製造段階での半導体装置を示す断面図である。

- 【図17】実施の形態3で説明する、製造段階での半導体装置を示す断面図である。

- 【図18】実施の形態4で説明する、製造段階での半導体装置を示す断面図である。

- 【図19】実施の形態4で説明する、製造段階での半導体装置を示す断面図である。

- 【図20】実施の形態4で説明する、製造段階での半導体装置を示す断面図である。

- 【図21】実施の形態4で説明する、製造段階での半導体装置を示す断面図である。

- 【図22】実施の形態4で説明する、製造段階での半導体装置を示す断面図である。

- 【図23】絶縁材料およびシリコン膜が曲面形状を呈する、製造段階での半導体装置を示す断面図である。 10

- 【図24】実施の形態1で説明する、Feの温度と拡散距離の関係を示す図である。

- 【図25】実施の形態1で説明する、Niの温度と拡散距離の関係を示す図である。

- 【図26】実施の形態1で説明する、Coの温度と拡散距離の関係を示す図である。

- 【図27】実施の形態1で説明する、Tiの温度と拡散距離の関係を示す図である。

- 【図28】実施の形態1で説明する、Alの温度と拡散距離の関係を示す図である。

- 【図29】実施の形態1で説明する、Crの温度と拡散距離の関係を示す図である。 20

- 【符号の説明】

- 【0072】

- 1 酸化シリコン基板、2 シリコン膜、3, 8, 12, 13, 15, 21, 22, 2

3 シリコン酸化膜、4 多結晶シリコン、5 シリコン窒化膜、7 トレンチ、R1

領域。 30

【図1】

【図2】

1:酸化シリコン基板

2:シリコン膜

3:シリコン酸化膜

4:多結晶シリコン

5:シリコン窒化膜

R1:領域

R2:幅

【図3】

7:トレチ

【図4】

8, 21:シリコン酸化膜

【図5】

【図6】

1, 2, 13, 22:シリコン酸化膜

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図17】

【図18】

【図14】

【図15】

【図16】

【図19】

【図20】

【図21】

【 図 2 2 】

【 図 2 3 】

【 図 2 4 】

【図27】

【 図 2 8 】

【 図 25 】

【 図 2 6 】

【 図 2 9 】

---

フロントページの続き

F ターム(参考) 5F032 AA09 AA35 AA44 AA45 AA67 BB01 CA03 CA17 DA22 DA24

DA33 DA53 DA57 DA74