(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7112873号

(P7112873)

(45)発行日 令和4年8月4日(2022.8.4)

(24)登録日 令和4年7月27日(2022.7.27)

(51)国際特許分類

|        |                 |     |        |       |         |

|--------|-----------------|-----|--------|-------|---------|

| H 01 L | 21/60 (2006.01) | F I | H 01 L | 21/60 | 3 1 1 Q |

| H 01 L | 23/12 (2006.01) |     | H 01 L | 23/12 | 5 0 1 B |

| H 05 K | 3/34 (2006.01)  |     | H 05 K | 3/34  | 5 0 1 E |

|        |                 |     | H 01 L | 21/92 | 6 0 2 E |

|        |                 |     | H 01 L | 21/92 | 6 0 2 J |

請求項の数 11 (全13頁) 最終頁に続く

(21)出願番号 特願2018-73456(P2018-73456)

(22)出願日 平成30年4月5日(2018.4.5)

(65)公開番号 特開2019-186330(P2019-186330)

A)

(43)公開日 令和1年10月24日(2019.10.24)

審査請求日 令和2年12月24日(2020.12.24)

(73)特許権者 000190688

新光電気工業株式会社

長野県長野市小島田町80番地

(74)代理人 100107766

弁理士 伊東 忠重

(74)代理人 100070150

弁理士 伊東 忠彦

(72)発明者 山口 康之

長野県長野市小島田町80番地 新光電

気工業株式会社内

審査官 堀江 義隆

最終頁に続く

(54)【発明の名称】 配線基板、半導体パッケージ及び配線基板の製造方法

## (57)【特許請求の範囲】

## 【請求項1】

Cuパッドと、

前記Cuパッドを覆い、前記Cuパッド上に開口部が形成された絶縁層と、

前記開口部内で前記Cuパッド上に形成され、前記Cuパッドよりも弾性率が高い第1の金属層と、

前記第1の金属層上に形成され、前記開口部内から前記絶縁層の上面より上方まで突出する接続端子と、

を有し、

前記接続端子は、

前記第1の金属層上に形成されたシード層と、

前記シード層上に形成された第2の金属層と、

を有し、

前記第1の金属層及び前記接続端子の積層体は、前記第1の金属層の厚さ方向の中間に断面積が最小となる括れ部を有し、

前記シード層は、前記第1の金属層の上から前記絶縁層の上面まで延びるように、前記第1の金属層の上面と、前記開口部の壁面と、前記絶縁層の上面とに形成されており、前記第1の金属層の上面は平坦であることを特徴とする配線基板。

## 【請求項2】

前記第1の金属層の前記括れ部よりも前記Cuパッド側の部分の上面は、外縁に向かって

下方に傾斜していることを特徴とする請求項 1 に記載の配線基板。

**【請求項 3】**

Cuパッドと、

前記Cuパッドを覆い、前記Cuパッド上に開口部が形成された絶縁層と、

前記開口部内で前記Cuパッド上に形成され、前記Cuパッドよりも弾性率が高い第1の金属層と、

前記第1の金属層上に形成され、前記開口部内から前記絶縁層の上面より上方まで突出する接続端子と、

を有し、

前記接続端子は、

前記第1の金属層上に形成されたシード層と、

前記シード層上に形成された第2の金属層と、

を有し、

前記第1の金属層及び前記接続端子の積層体は、前記第1の金属層の厚さ方向の中間に断面積が最小となる括れ部を有し、

前記シード層は、前記第1の金属層の上から前記絶縁層の上面まで延びるように、前記第1の金属層の上面と、前記開口部の壁面と、前記絶縁層の上面とに形成されており、

前記第1の金属層の前記括れ部よりも前記Cuパッド側の部分の上面は、外縁に向かって下方に傾斜していることを特徴とする配線基板。

**【請求項 4】**

前記第2の金属層はCuめっき層を含むことを特徴とする請求項1乃至3のいずれか1項に記載の配線基板。

**【請求項 5】**

前記第1の金属層はNiめっき層を含むことを特徴とする請求項1乃至4のいずれか1項に記載の配線基板。

**【請求項 6】**

前記Cuパッドの表面に窪みが形成されており、

前記第1の金属層の前記括れ部より下の部分が前記窪み内にあることを特徴とする請求項1乃至5のいずれか1項に記載の配線基板。

**【請求項 7】**

前記絶縁層はソルダレジスト層であることを特徴とする請求項1乃至6のいずれか1項に記載の配線基板。

**【請求項 8】**

前記開口部の側壁の断面形状は直線状であり、

前記開口部の直径は前記Cuパッドに近い部分ほど小さいことを特徴とする請求項1乃至6のいずれか1項に記載の配線基板。

**【請求項 9】**

請求項1乃至8のいずれか1項に記載の配線基板と、

前記配線基板に実装された電子部品と、

を有し、

前記電子部品は、前記接続端子に接続された接続端子を有することを特徴とする半導体パッケージ。

**【請求項 10】**

Cuパッドを覆う絶縁層を形成する工程と、

前記絶縁層に前記Cuパッドの一部を露出する開口部を形成する工程と、

前記開口部を通じて前記Cuパッドのウェットエッチングを行うことにより、前記Cuパッドの表面に窪みを形成する工程と、

前記開口部の下端よりも上面が上方に位置する第1の金属層を前記窪み及び前記開口部内に無電解めっき法により形成する工程と、

無電解めっき法により、前記第1の金属層の上から前記絶縁層の上面まで延びるように

10

20

30

40

50

、前記第1の金属層の上面と、前記開口部の壁面と、前記絶縁層の上面とにシード層を形成する工程と、

電解めっき法により前記シード層上に第2の金属層を形成する工程と、

有し、

前記第1の金属層の上面は平坦であることを特徴とする配線基板の製造方法。

【請求項11】

Cuパッドを覆う絶縁層を形成する工程と、

前記絶縁層に前記Cuパッドの一部を露出する開口部を形成する工程と、

前記開口部を通じて前記Cuパッドのウェットエッチングを行うことにより、前記Cuパッドの表面に窪みを形成する工程と、

前記開口部の下端よりも上面が上方に位置する第1の金属層を前記窪み及び前記開口部内に形成する工程と、

無電解めっき法により、前記第1の金属層の上から前記絶縁層の上面まで延びるように、前記第1の金属層の上面と、前記開口部の壁面と、前記絶縁層の上面とにシード層を形成する工程と、

電解めっき法により前記シード層上に第2の金属層を形成する工程と、

有し、

前記第1の金属層、前記シード層及び前記第2の金属層の積層体は、前記第1の金属層の厚さ方向の中間に断面積が最小となる括れ部を有し、

前記第1の金属層の前記括れ部よりも前記Cuパッド側の部分の上面は、外縁に向かって下方に傾斜していることを特徴とする配線基板の製造方法。

10

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、配線基板、半導体パッケージ及び配線基板の製造方法に関する。

【背景技術】

【0002】

配線基板では、銅(Cu)パッドにCuポストが接続端子として接続されている。そして、半導体チップ等の電子部品の実装の際には、はんだボール等を用いて、Cuポストと電子部品の導電パッドとを接合している。

30

【先行技術文献】

【特許文献】

【0003】

【文献】特開2013-93405号公報

特開2016-35969号公報

特開2014-103295号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

近年、電子部品の高性能化、高機能化及び小型化が進められており、これに対応するために配線基板の接続端子の微細化が望まれている。ところが、接続端子を微細化すると、Cuパッドに亀裂等の破損が生じやすくなる。また、Cuパッドに破損が生じると、その周辺の保護絶縁層にも破損が生じることがある。

40

【0005】

本発明は、接続端子の微細化に伴うCuパッドの破損を抑制することができる配線基板、半導体パッケージ及び配線基板の製造方法を提供することを目的とする。

【課題を解決するための手段】

【0006】

配線基板の一態様は、Cuパッドと、前記Cuパッドを覆い、前記Cuパッド上に開口部が形成された絶縁層と、前記開口部内で前記Cuパッド上に形成され、前記Cuパッド

50

よりも弾性率が高い第1の金属層と、前記第1の金属層上に形成され、前記開口部内から前記絶縁層の上面より上方まで突出する接続端子と、を有し、前記接続端子は、前記第1の金属層上に形成されたシード層と、前記シード層上に形成された第2の金属層と、を有し、前記第1の金属層及び前記接続端子の積層体は、前記第1の金属層の厚さ方向の中間に断面積が最小となる括れ部を有し、前記シード層は、前記第1の金属層の上から前記絶縁層の上面まで延びるように、前記第1の金属層の上面と、前記開口部の壁面と、前記絶縁層の上面とに形成されており、前記第1の金属層の上面は平坦である。

【発明の効果】

【0007】

開示の技術によれば、接続端子の微細化に伴うCuパッドの破損を抑制することができる。

10

【図面の簡単な説明】

【0008】

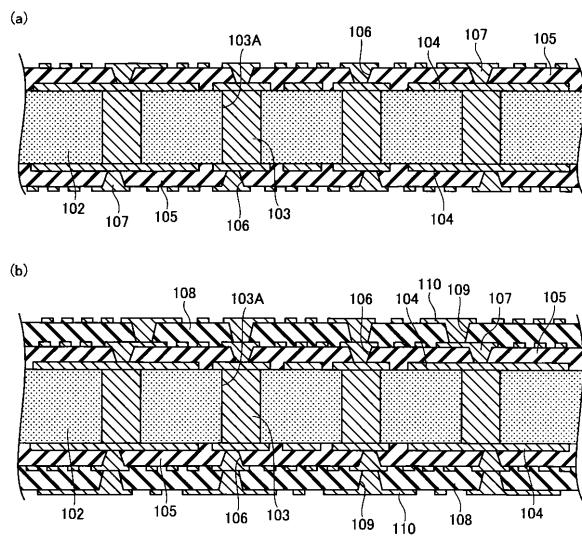

【図1】接続端子の例を示す断面図である。

【図2】接続端子の他の例を示す断面図である。

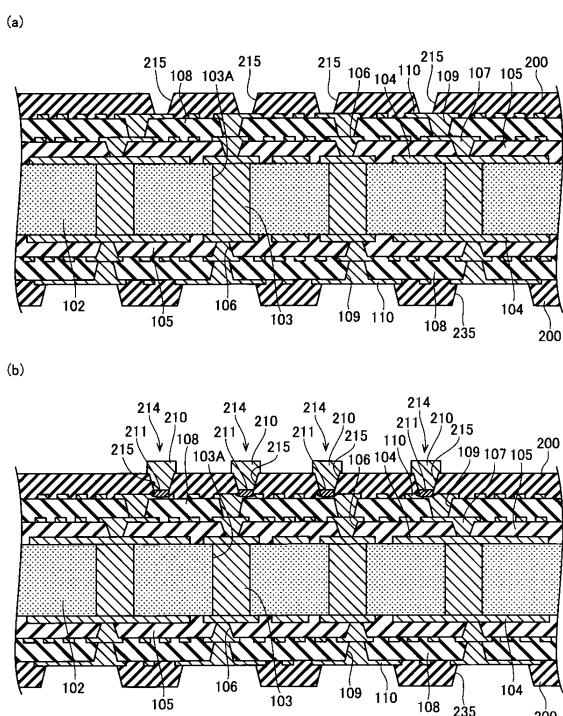

【図3】第1の実施形態に係る配線基板の構造を示す断面図である。

【図4】第1の実施形態に係る配線基板に含まれる接続端子の構造を示す断面図である。

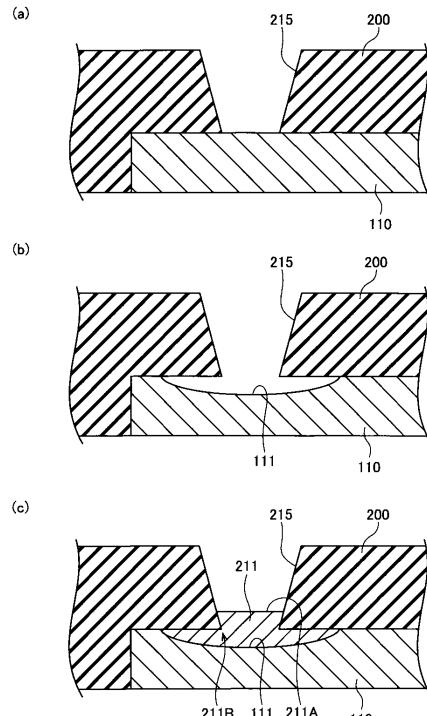

【図5】第1の実施形態に係る配線基板の製造方法を示す断面図（その1）である。

【図6】第1の実施形態に係る配線基板の製造方法を示す断面図（その2）である。

【図7】第1の実施形態に係る配線基板の製造方法を示す断面図（その3）である。

20

【図8】第1の実施形態に含まれる積層体の形成方法を示す断面図（その1）である。

【図9】第1の実施形態に含まれる積層体の形成方法を示す断面図（その2）である。

【図10】第1の実施形態に含まれる積層体の形成方法を示す断面図（その3）である。

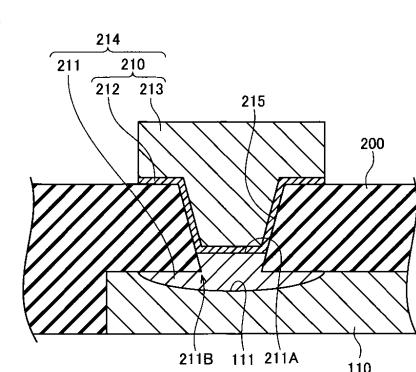

【図11】第1の実施形態に係る配線基板に含まれる積層体の変形例の構造を示す断面図である。

【図12】第2の実施形態に係る半導体パッケージを示す断面図である。

【発明を実施するための形態】

【0009】

本発明者は、接続端子の微細化に伴うCuパッドの破損の原因を究明すべく鋭意検討を行った。そして、本発明者による詳細な解析の結果、電子部品の実装の際に接続端子とCuパッドとの界面近傍に大きな応力が作用しやすく、接続端子の直径が上端から下端にかけて減少する場合は特に大きな応力が作用しやすいことが明らかになった。ここで、この新たな知見について説明する。

30

【0010】

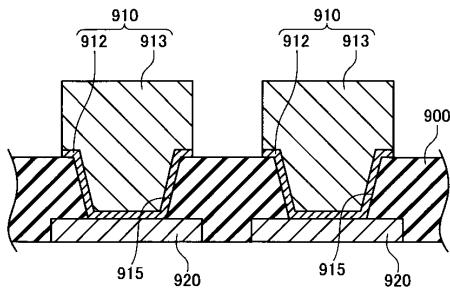

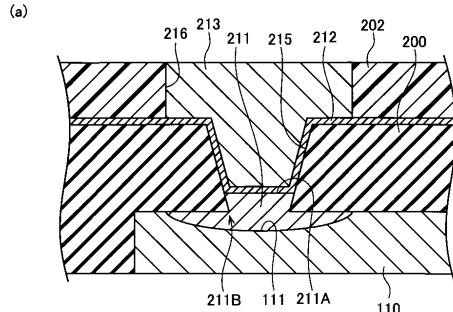

図1は、接続端子の例を示す断面図である。図1に示すように、この例では、ソルダレジスト層900にCuパッド920に達するビアホール915が形成されている。ビアホール915はレーザの照射により形成されており、その直径が上端から下端にかけて減少している。そして、Cuパッド920に接続される接続端子910がビアホール915内に形成されている。接続端子910は、Cuシード層912及びその上に形成されたCuめっき層913を含む。

40

【0011】

半導体チップ等の電子部品の実装時には、接続端子910に荷重がかかり、断面積が最小となる接続端子910とCuパッド920との界面近傍に大きな応力が作用する。そして、Cuパッド920が応力に耐えきれない場合、Cuパッド920に亀裂等の破損が生じる。

【0012】

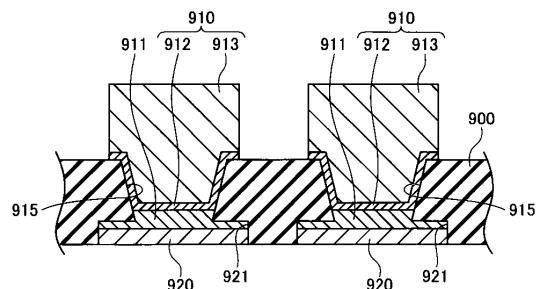

このような破損を抑制すべく本発明者が更に鋭意検討を行った結果、図2に示すように、断面積が最小となり大きな応力が作用しやすい部分にCuパッド920よりも弾性率が高い金属層911を設け、その上に接続端子910を設けることで、電子部品の実装時の破損を抑制できることが明らかになった。

50

## 【0013】

本発明者らは、これらの新たな知見に基づいて、以下のような実施形態に想到した。以下、実施形態について添付の図面を参照しながら具体的に説明する。なお、本明細書及び図面において、実質的に同一の機能構成を有する構成要素については、同一の符号を付すことにより重複した説明を省くことがある。

## 【0014】

## (第1の実施形態)

第1の実施形態について説明する。第1の実施形態は配線基板に関する。

## 【0015】

## [配線基板の構造]

10

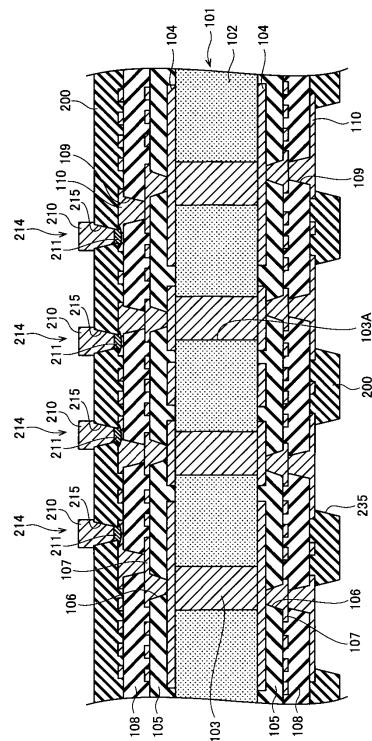

先ず、第1の実施形態に係る配線基板の構造について説明する。図3は、第1の実施形態に係る配線基板の構造を示す断面図である。図4は、第1の実施形態に係る配線基板に含まれる接続端子の構造を示す断面図である。

## 【0016】

図3に示すように、第1の実施形態に係る配線基板100は、支持体としてコア配線基板101を含む。コア配線基板101はガラスエポキシ樹脂等の絶縁材料から形成されるコア基板102を含む。コア基板102の両面にCu等からなる第1の配線層104が形成されている。コア基板102には厚さ方向に貫通するスルーホール103Aが形成されており、スルーホール103A内に貫通導体103が設けられている。コア基板102の両側の第1の配線層104は貫通導体103を介して相互に接続されている。スルーホール103Aの側壁にスルーホールめっき層が形成され、スルーホール103Aの残りの孔には樹脂体が充填されてもよい。この場合、コア基板102の両側の第1の配線層104はスルーホールめっき層を介して相互に接続される。

20

## 【0017】

コア基板102の両側に第1の絶縁層105が形成されている。第1の絶縁層105には、第1の配線層104の接続部に到達するビアホール106が形成されており、第1の絶縁層105上に、ビアホール106内のビア導体を介して第1の配線層104に接続される第2の配線層107が形成されている。第2の配線層107はCu等からなる。更に、コア基板102の両側において、第1の絶縁層105上に第2の絶縁層108が形成されている。第2の絶縁層108には、第2の配線層107の接続部に到達するビアホール109が形成されており、第2の絶縁層108上に、ビアホール109内のビア導体を介して第2の配線層107に接続されるCuの第3の配線層110が形成されている。

30

## 【0018】

コア基板102の両側において、第2の絶縁層108上にソルダレジスト層200が形成されている。コア基板102の半導体チップと接続される側のソルダレジスト層200に第3の配線層110の接続部に達するビアホール215が形成されている。第3の配線層110の接続部がCuパッドとして用いられる。ビアホール215の直径は上端から下端にかけて減少している。コア基板102の反対側のソルダレジスト層200には第3の配線層110の接続部に達する開口部235が形成されている。

40

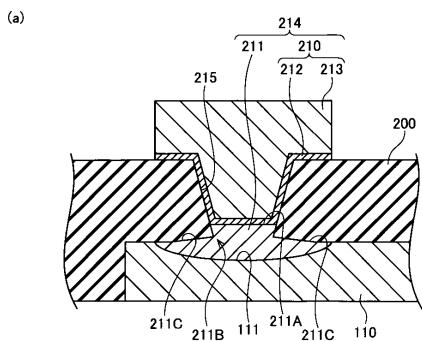

## 【0019】

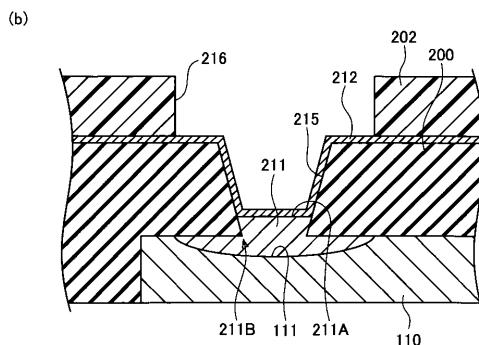

図4に示すように、コア基板102の半導体チップと接続される側において、第3の配線層110の表面にビアホール215と連なる窪み111が形成されており、窪み111を埋めるようにニッケル(Ni)めっき層211が形成されている。例えば、Niめっき層211の厚さは5μm～10μmである。Niめっき層211の上面211Aは、ビアホール215の下端よりも上方にある。Niめっき層211上に、ビアホール215を通じてソルダレジスト層200の上方まで突出するCuポスト210が形成されている。Cuポスト210はCuシード層212及びその上のCuめっき層213を有する。Niめっき層211は第1の金属層の一例であり、Cuシード層212はシード層の一例であり、Cuめっき層213は第2の金属層の一例であり、Cuポスト210は接続端子の一例である。Niめっき層211とCuシード層212との間にパラジウム(Pd)めっき層

50

及び金(Au)めっき層が形成されていることが好ましい。

【0020】

Niめっき層211及びCuポスト210の積層体214は、Niめっき層211の厚さ方向の中間に断面積が最小となる括れ部211Bを有する。つまり、積層体214の断面積は、ピアホール215の下端に対応する部分で最小となっており、積層体214はこの部分で括れている。そして、Niめっき層211の括れ部211Bより下の部分が窪み111内にあり、ソルダレジスト層200の窪み111に対向する下面にNiめっき層211が接している。

【0021】

このように、本実施形態においては、接続部がCuパッドとして用いられる第3の配線層110とCuポスト210との間にNiめっき層211が介在し、積層体214の断面積が最小となる部分がNiめっき層211内にある。そして、Niめっき層211は第3の配線層110及びCuポスト210よりも高い弾性率を有する。従って、Cuポスト210を第3の配線層110上に直接形成した場合と比較して高い強度が得られ、電子部品の実装の際にCuポスト210に荷重がかからても、第3の配線層110の亀裂等の破損を抑制することができる。また、第3の配線層110の破損の抑制により、ソルダレジスト層200の破損も抑制することができる。

10

【0022】

[配線基板の製造方法]

次に、配線基板の製造方法について説明する。図5～図7は、第1の実施形態に係る配線基板の製造方法を示す断面図である。

20

【0023】

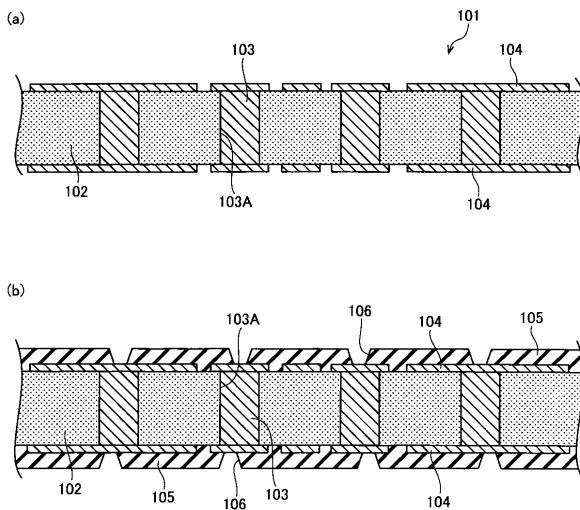

先ず、図5(a)に示すように、支持体としてコア配線基板101を準備する。コア配線基板101はコア基板102及び第1の配線層104を備えている。コア基板102には厚さ方向に貫通するスルーホール103Aが形成されており、スルーホール103A内に貫通導体103が設けられている。例えば、スルーホール103Aはドリルを用いた加工等により形成することができ、貫通導体103及び第1の配線層104はめっき法及びフォトリソグラフィ等により形成することができる。

【0024】

次いで、図5(b)に示すように、コア基板102の両側に未硬化の樹脂フィルムを貼付し、加熱処理して硬化させることにより、第1の絶縁層105を形成する。第1の絶縁層105は、エポキシ樹脂又はポリイミド樹脂等から形成される。液状樹脂を塗布することにより、第1の絶縁層105を形成してもよい。その後、コア基板102の両側の第1の絶縁層105をレーザで加工することにより、第1の配線層104の接続部に到達するピアホール106を第1の絶縁層105に形成する。

30

【0025】

続いて、図6(a)に示すように、コア基板102の両側において、ピアホール106内のピア導体を介して第1の配線層104に接続される第2の配線層107を第1の絶縁層105上に形成する。

【0026】

第2の配線層107はセミアディティブ法によって形成することができる。ここで、第2の配線層107の形成方法について詳しく説明する。先ず、第1の絶縁層105上及びピアホール106の内面に無電解めっき法又はスパッタ法により、Cu等からなるシード層(不図示)を形成する。次いで、第2の配線層107を形成する部分に開口部が設けられためっきレジスト層(不図示)を形成する。続いて、シード層をめっき給電経路に利用する電解めっき法により、めっきレジスト層の開口部にCu等からなる金属めっき層を形成する。その後、めっきレジスト層を除去する。次いで、金属めっき層をマスクにしてシード層をウェットエッティングにより除去する。このようにして、シード層及び金属めっき層を含む第2の配線層107を形成することができる。

40

【0027】

50

第2の配線層107の形成後、図6(b)に示すように、コア基板102の両側において、第1の絶縁層105上に、第2の配線層107の接続部上にピアホール109が設けられた第2の絶縁層108を形成する。第2の絶縁層108は、第1の絶縁層105と同様の方法で形成することができる。

【0028】

更に、同じく図6(b)に示すように、コア基板102の両側において、ピアホール109内のピア導体を介して第2の配線層107に接続される第3の配線層110を第2の絶縁層108上に形成する。第3の配線層110は、第2の配線層107と同様の方法で形成することができる。

【0029】

次いで、図7(a)に示すように、コア基板102の両側において、第2の絶縁層108上にソルダレジスト層200を形成する。その後、コア基板102の半導体チップと接続される側のソルダレジスト層200に第3の配線層110の接続部に達するピアホール215を形成する。また、コア基板102の反対側のソルダレジスト層200に第3の配線層110の接続部に達する開口部235を形成する。

【0030】

続いて、図7(b)に示すように、コア基板102の半導体チップと接続される側において、ピアホール215を通じて第3の配線層110の接続部に窪み111を形成し、第3の配線層110の接続部上にNiめっき層211及びCuポスト210の積層体214を形成する。

【0031】

このようにして第1の実施形態に係る配線基板100を製造することができる。

【0032】

ここで、積層体214の形成方法について詳しく説明する。図8～図10は、積層体214の形成方法を示す断面図である。

【0033】

図8(a)に示すように、ピアホール215を形成した後、図8(b)に示すように、ウェットエッティングにより第3の配線層110の表面に窪み111を形成する。

【0034】

次いで、図8(c)に示すように、Niめっき層211を形成する。Niめっき層211は、窪み111を埋め、かつその上面211Aがピアホール215の下端よりも上方に位置するように形成する。Niめっき層211は無電解めっき法により形成することができ、例えば、その厚さは5μm～10μmとする。

【0035】

その後、図9(a)に示すように、Cuシード層212を形成する。Cuシード層212は無電解Cuめっき法により形成することができる。Cuシード層212の形成前に、無電解めっき法によりPdめっき層及びAuめっき層をこの順でNiめっき層211上に形成しておくことが好ましい。

【0036】

続いて、図9(b)に示すように、接続端子210を形成する部分に開口部216が設けられためっきレジスト層202をCuシード層212上に形成する。開口部216はフォトリソグラフィにより形成することができる。

【0037】

次いで、図10(a)に示すように、ピアホール215及び開口部216内にCuめっき層213を形成する。Cuめっき層213は電解めっき法により形成することができる。

【0038】

その後、図10(b)に示すように、めっきレジスト層202を除去し、Cuめっき層213をマスクにしてCuシード層212をウェットエッティングにより除去する。

【0039】

このようにしてNiめっき層211及びCuポスト210の積層体214を形成するこ

10

20

30

40

50

とができる。

【0040】

このような製造方法によれば、適切な部分にNiめっき層211を備えた配線基板100を容易に製造することができる。

【0041】

なお、図3及び図7(b)ではシード層212を省略してある。

【0042】

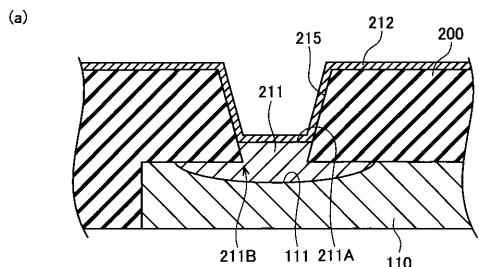

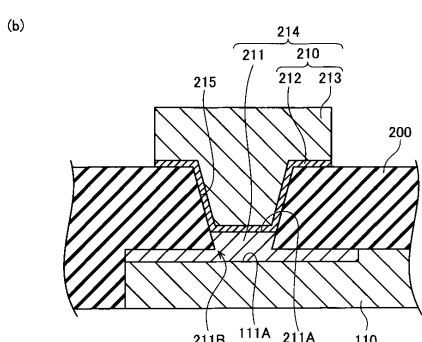

(第1の変形例)

図11(a)に示すように、Niめっき層211の括れ部211Bより下の部分が凸状に膨らんだ形状を有していてもよい。この場合、括れ部211Bより第3の配線層110側の部分の上面211C、すなわちソルダレジスト層200との界面は、外縁に向かって下方に傾斜する。

10

【0043】

上面211Cの傾斜が急になるほど、括れ部211Bの上方の側面と下方の側面とがなす角が鈍くなり、括れ部211Bの近傍における応力集中が緩和されやすくなる。

【0044】

(第2の変形例)

椀状の窪み111に代えて、図11(b)に示すように、底面が平らな窪み111Aが第3の配線層110に形成されていてもよい。このような窪み111Aが形成されている場合であっても、Niめっき層211による強度の向上及び第3の配線層110の破損の抑制の効果を得ることができる。

20

【0045】

ただし、窪み111と窪み111Aとを比較すると、窪み111の方が、Niめっき層211に上方からかかる荷重を分散させやすく好ましい。

【0046】

(第2の実施形態)

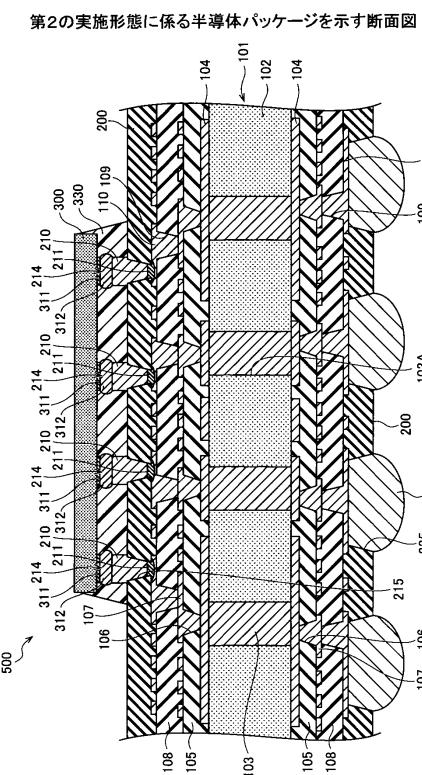

次に、第2の実施形態について説明する。第2の実施形態は半導体パッケージに関する。図12は、第2の実施形態に係る半導体パッケージを示す断面図である。

【0047】

図12に示すように、第2の実施形態に係る半導体パッケージ500は、第1の実施形態に係る配線基板100、半導体チップ300、バンプ312、アンダーフィル樹脂330及び外部接続端子331を有する。

30

【0048】

半導体チップ300は、バンプ312を介してCuポスト210に接続される接続端子311を含む。接続端子311は、例えば電極パッドである。バンプ312には、例えば、はんだボールが用いられる。はんだボールの材料としては、錫銀(SnAg)系合金、錫亜鉛(SnZn)系合金及び錫銅(SnCu)系合金等の無鉛はんだ、並びに鉛錫(PbSn)系合金の有鉛はんだが例示される。半導体チップ300と配線基板100のソルダレジスト層200との間に、エポキシ樹脂等のアンダーフィル樹脂330が充填されている。

40

【0049】

配線基板100の半導体チップ300とは反対側の面において、第3の配線層110上に外部接続端子331が設けられている。外部接続端子331には、例えば、バンプ312と同様のはんだボールが用いられる。

【0050】

このような半導体パッケージ500を製造するには、バンプ312を用いて、半導体チップ300を配線基板100にフリップチップ実装する。次いで、半導体チップ300とソルダレジスト層200との間にアンダーフィル樹脂330を充填する。また、外部接続端子331を第3の配線層110上に形成する。

【0051】

50

このようにして、半導体パッケージ 500 を製造することができる。

【0052】

なお、フリップチップ実装時に行われるリフロー中に熱が付与されて、図 11 (a) に示すような形状の Niめっき層 211 が得られることもある。

【0053】

以上、好ましい実施の形態等について詳説したが、上述した実施の形態等に制限されることではなく、特許請求の範囲に記載された範囲を逸脱することなく、上述した実施の形態等に種々の変形及び置換を加えることができる。

【符号の説明】

【0054】

- 100 配線基板

- 101 コア配線基板

- 102 コア基板

- 110 第3の配線層

- 111、111A 窪み

- 200 ソルダレジスト層

- 210 Cu ポスト

- 211 Niめっき層

- 211A、211C 上面

- 211B 括れ部

- 212 Cu シード層

- 213 Cuめっき層

- 214 積層体

- 300 半導体チップ

- 311 接続端子

- 312 バンプ

- 330 アンダーフィル樹脂

- 500 半導体パッケージ

10

20

30

40

50

【図面】

【図 1】

【図 2】

接続端子の例を示す断面図

接続端子の他の例を示す断面図

10

【図 3】

【図 4】

第1の実施形態に係る配線基板の構造を示す断面図

【図5】

第1の実施形態に係る配線基板の製造方法を示す断面図(その1)

【図6】

第1の実施形態に係る配線基板の製造方法を示す断面図(その2)

10

20

【図7】

第1の実施形態に係る配線基板の製造方法を示す断面図(その3)

【図8】

第1の実施形態に含まれる積層体の形成方法を示す断面図(その1)

30

40

50

【図9】

【図10】

### 第1の実施形態に含まれる積層体の形成方法を示す断面図(その2)

10

20

### 【図11】

【 図 1 2 】

## 第1の実施形態に係る配線基板に含まれる積層体の 変形例の構造を示す断面図

30

40

---

フロントページの続き

(51)国際特許分類

F I

H 01 L 21/92 604 B

(56)参考文献 特開2014-103295 (JP, A)

特開2015-233085 (JP, A)

特開2017-112318 (JP, A)

(58)調査した分野 (Int.Cl., DB名)

H 01 L 21/60

H 01 L 23/12

H 05 K 3/34