(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2017-204510

(P2017-204510A)

(43) 公開日 平成29年11月16日(2017.11.16)

| (51) Int.Cl.                  | F 1        | テーマコード (参考) |

|-------------------------------|------------|-------------|

| <b>H01L 27/14 (2006.01)</b>   | H01L 27/14 | D 4M118     |

| <b>H01L 21/02 (2006.01)</b>   | H01L 21/02 | C 5C024     |

| <b>H01L 21/768 (2006.01)</b>  | H01L 21/02 | B 5FO33     |

| <b>H01L 23/522 (2006.01)</b>  | H01L 21/90 | B           |

| <b>H01L 21/3205 (2006.01)</b> | H01L 21/88 | J           |

審査請求 未請求 請求項の数 13 O L (全 18 頁) 最終頁に続く

|           |                            |          |                                            |

|-----------|----------------------------|----------|--------------------------------------------|

| (21) 出願番号 | 特願2016-94171 (P2016-94171) | (71) 出願人 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (22) 出願日  | 平成28年5月9日(2016.5.9)        | (74) 代理人 | 100126240<br>弁理士 阿部 琢磨                     |

|           |                            | (74) 代理人 | 100124442<br>弁理士 黒岩 創吾                     |

|           |                            | (72) 発明者 | 桑原 英司<br>東京都大田区下丸子3丁目30番2号キヤノン株式会社内        |

|           |                            | (72) 発明者 | 浮ヶ谷 信貴<br>東京都大田区下丸子3丁目30番2号キヤノン株式会社内       |

最終頁に続く

(54) 【発明の名称】光電変換装置の製造方法

## (57) 【要約】

【課題】 光電変換装置の性能を向上する

【解決手段】 光電変換素子が設けられた半導体層を含む第1基板を、第2基板に固定する工程と、第2基板に固定された第1基板を、第1基板に対して第2基板の側とは反対側から薄化する工程と、薄化された第1基板を、半導体素子が設けられた第3基板が第1基板に対して第2基板の側とは反対側に位置するように、第3基板に固定する工程と、第1基板を第3基板に固定する工程の後に、第2基板を除去する工程と、を備える。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

光電変換素子が設けられた半導体層を含む第1基板を、第2基板に固定する工程と、前記第2基板に固定された前記第1基板を、前記第1基板に対して前記第2基板の側とは反対側から薄化する工程と、

前記薄化された第1基板を、半導体素子が設けられた第3基板が前記第1基板に対して前記第2基板の側とは反対側に位置するように、前記第3基板に固定する工程と、

前記第1基板を前記第3基板に固定する工程の後に、前記第2基板を除去する工程と、を備えることを特徴とする光電変換装置の製造方法。

**【請求項 2】**

前記第2基板を除去する工程の後に、前記第1基板に対して前記第3基板の側とは反対側に集光部および波長選択部の少なくともいずれかを形成する工程を更に備える、請求項1に記載の光電変換装置の製造方法。

**【請求項 3】**

前記第2基板に固定する工程において、前記第1基板にはトランジスタが設けられている、請求項1または2に記載の光電変換装置の製造方法。

**【請求項 4】**

前記第2基板に固定する工程において、前記第1基板には配線部材が設けられている、請求項1乃至3のいずれか1項に記載の光電変換装置の製造方法。

**【請求項 5】**

前記第2基板を除去する工程の後に、前記第1基板に対して前記第3基板の側とは反対側に配線部材を形成する工程を更に備える、請求項1乃至4のいずれか1項に記載の光電変換装置の製造方法。

**【請求項 6】**

前記第2基板に固定する工程において前記第1基板はコンタクトプラグを含み、前記第2基板を除去する工程の後に、前記第1基板に対して前記第3基板の側とは反対側に複数の配線層を形成する工程を更に備える、請求項1乃至3のいずれか1項に記載の光電変換装置の製造方法。

**【請求項 7】**

前記第2基板を除去する工程の後に、前記第1基板に対して前記第3基板の側とは反対側に導光部を形成する工程を更に備える、請求項1乃至6のいずれか1項に記載の光電変換装置の製造方法。

**【請求項 8】**

前記半導体層を貫通する導電部材を形成する工程を更に備える、請求項1乃至7のいずれか1項に記載の光電変換装置の製造方法。

**【請求項 9】**

前記第3基板に固定する工程の前に、前記導電部材を形成する、請求項8に記載の光電変換装置の製造方法。

**【請求項 10】**

前記第3基板に固定する工程の後に、前記導電部材を形成する、請求項8に記載の光電変換装置の製造方法。

**【請求項 11】**

前記第2基板に固定する工程において、前記第1基板は前記半導体層と、前記半導体層に設けられた孔の中に配された導電部材と、を含み、前記薄化する工程では、前記第1基板に対して前記第2基板の側とは反対側に前記導電部材を露出させる、請求項1乃至7のいずれか1項に記載の光電変換装置の製造方法。

**【請求項 12】**

前記第2基板に固定する工程において、前記第1基板は、前記半導体層に対して前記第2基板の側とは反対側に位置する基体と、前記半導体層と前記基体との間に配された絶縁部層と、を含み、前記薄化する工程では、少なくとも前記基体の一部を除去する、請求項

10

20

30

40

50

1乃至11のいずれか1項に記載の光電変換装置の製造方法。

【請求項13】

前記薄化する工程において、前記第1基板の前記半導体層の厚さが10μmより大きく100μmより小さい、請求項1乃至12のいずれか1項に記載の光電変換装置の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、光電変換装置に関する。

【背景技術】

【0002】

光電変換素子が設けられた受光基板と、半導体素子が設けられた回路基板と、を積層した光電変換装置が提案されている。複数の基板を積層することにより、光電変換装置の性能の向上が期待される。

【0003】

特許文献1には、光電変換素子を有する第1の基板と、周辺回路部を有する第2の基板とを積層した、裏面照射型の固体撮像装置が開示されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2011-138841号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

複数の基板を積層すると光電変換装置が厚くなってしまうため、基板を薄くする要求がある。特許文献1ではフォトダイオード形成部材の薄膜化を行っているが、薄膜化によって新たに形成される面が受光面となるため、薄膜化に起因したノイズが生じやすい。そのため、光電変換装置の性能の向上が十分ではないという課題があった。

【0006】

本発明は、光電変換装置の性能を向上することを目的とする。

【課題を解決するための手段】

【0007】

上記課題を解決するための手段の一つの観点は、光電変換素子が設けられた半導体層を含む第1基板を、第2基板に固定する工程と、前記第2基板に固定された前記第1基板を、前記第1基板に対して前記第2基板の側とは反対側から薄化する工程と、前記薄化された第1基板を、半導体素子が設けられた第3基板が前記第1基板に対して前記第2基板の側とは反対側に位置するように、前記第3基板に固定する工程と、前記第1基板を前記第3基板に固定する工程の後に、前記第2基板を除去する工程と、を備えることを特徴とする光電変換装置の製造方法である。

【発明の効果】

【0008】

本発明によれば、性能を向上した光電変換装置を提供することができる。

【図面の簡単な説明】

【0009】

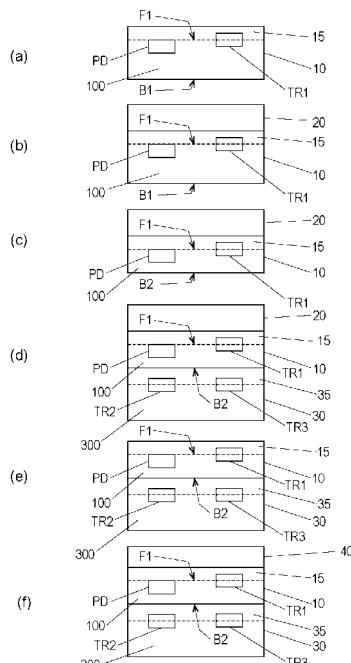

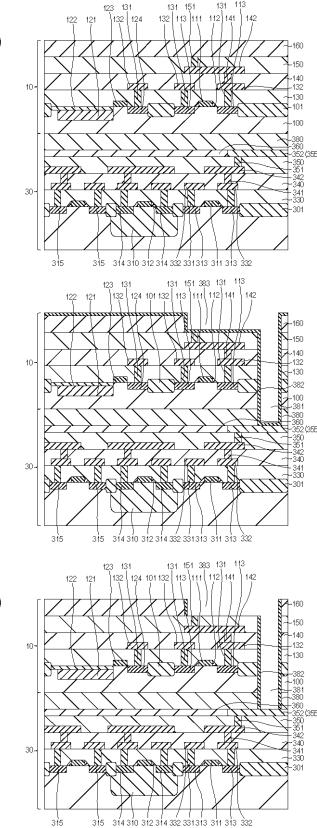

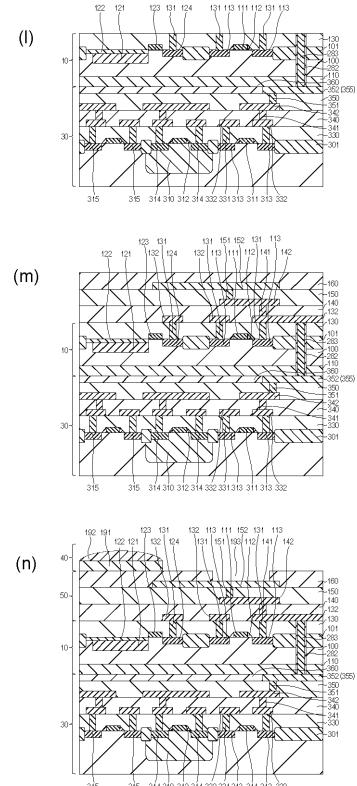

【図1】光電変換装置の製造方法を説明する模式図。

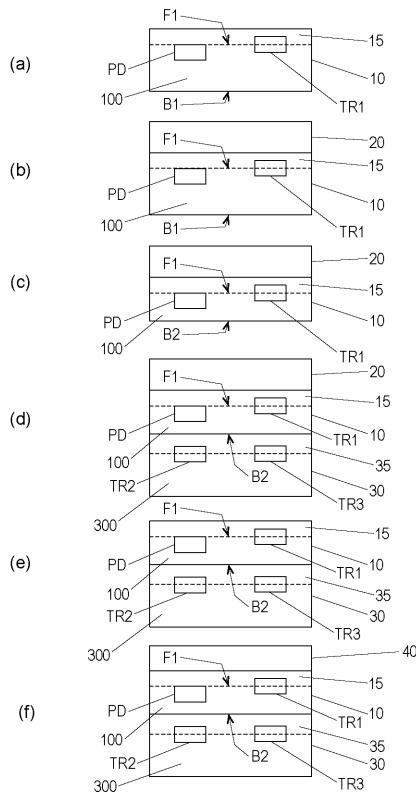

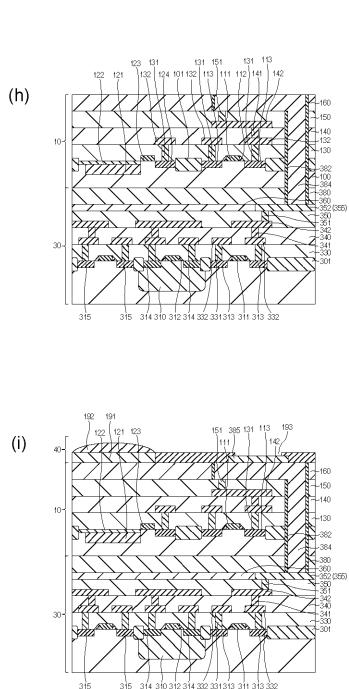

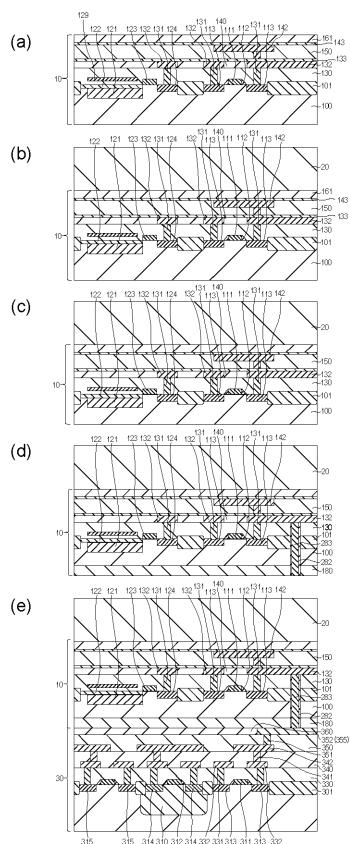

【図2】光電変換装置の製造方法の実施例1を説明する模式図。

【図3】光電変換装置の製造方法の実施例1を説明する模式図。

【図4】光電変換装置の製造方法の実施例1を説明する模式図。

【図5】光電変換装置の製造方法の実施例1を説明する模式図。

【図6】光電変換装置の製造方法の変形例を説明する模式図。

10

20

30

40

50

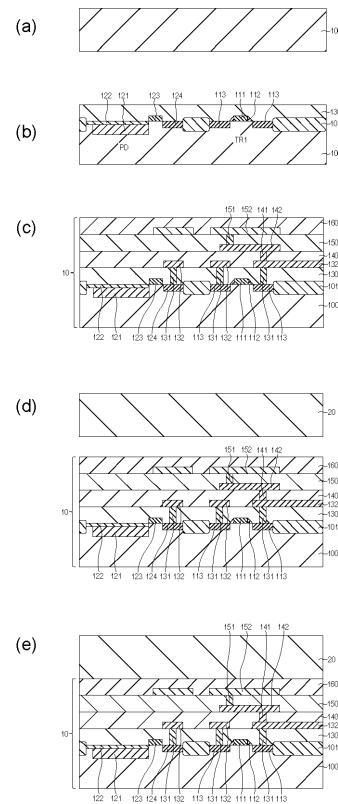

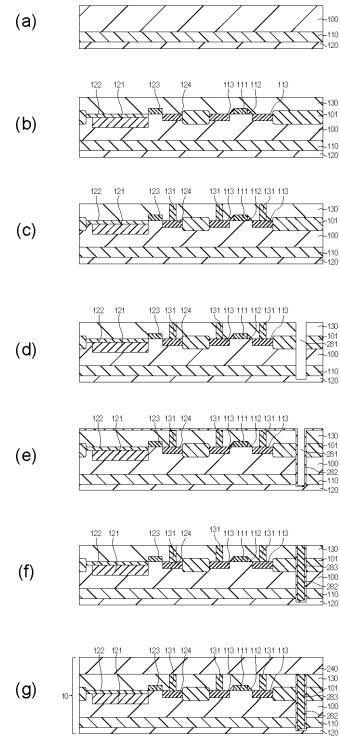

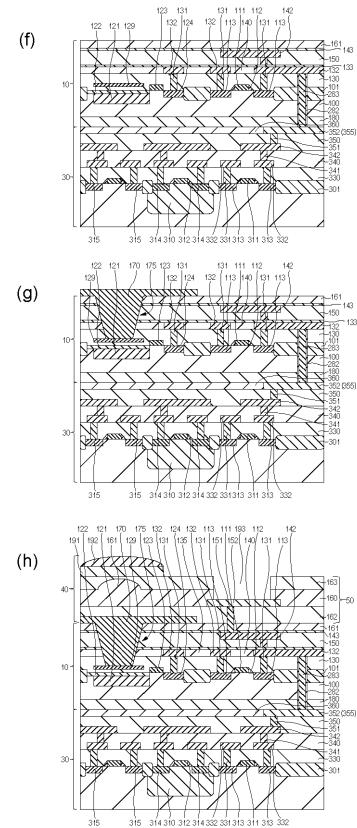

【図7】光電変換装置の製造方法の実施例2を説明する模式図。

【図8】光電変換装置の製造方法の実施例2を説明する模式図。

【図9】光電変換装置の製造方法の実施例2を説明する模式図。

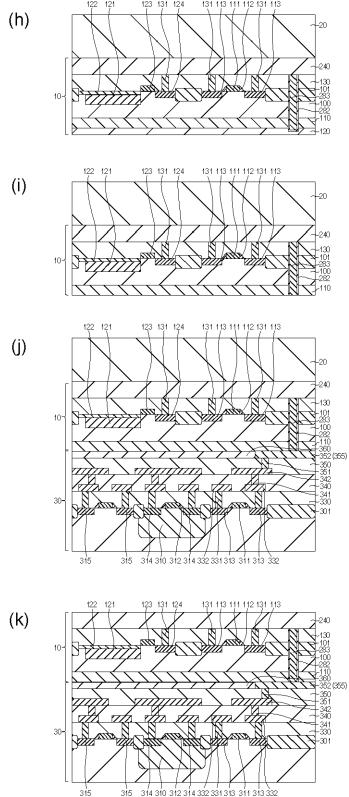

【図10】光電変換装置の製造方法の実施例3を説明する模式図。

【図11】光電変換装置の製造方法の実施例3を説明する模式図。

【図12】光電変換装置の製造方法の実施例3を説明する模式図。

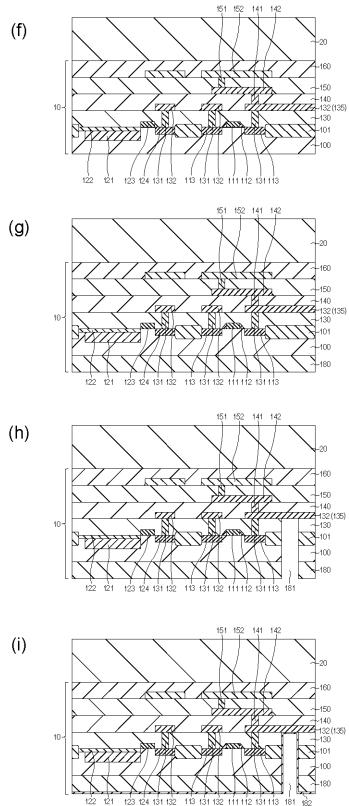

【図13】光電変換装置の製造方法の実施例4を説明する模式図。

【図14】光電変換装置の製造方法の実施例4を説明する模式図。

【発明を実施するための形態】

【0010】

以下、図面を参照して、本発明を実施するための形態を説明する。なお、以下の説明および図面において、複数の図面に渡って共通の構成については共通の符号を付している。そして、共通する構成を断りなく複数の図面を相互に参照して説明する場合がある。また、共通の符号を付した構成については説明を省略する場合がある。

【0011】

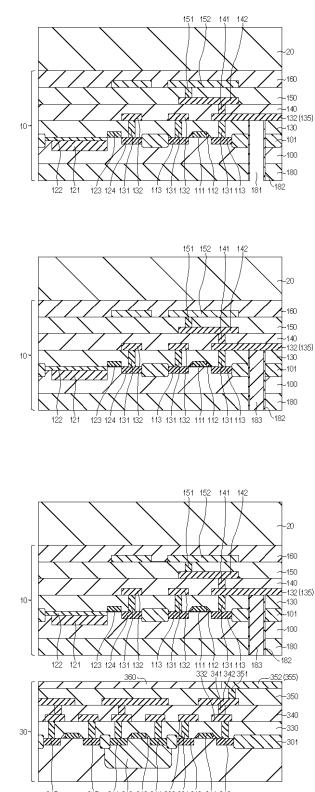

図1では、光電変換装置の断面模式図を用いて光電変換装置の製造方法を工程順に示している。

【0012】

図1(a)に示す工程Aでは、光電変換素子PDが設けられた受光基板10を用意する。受光基板10には光電変換素子PD以外に半導体素子TR1が設けられていてもよい。受光基板10は光電変換素子PDや半導体素子TR1の少なくとも一部を含む半導体層100を有する。工程Aにおいて半導体層100は表面F1と裏面B1とを有する。受光基板10における表面F1は最終的な光電変換装置における半導体層100の受光面となる。なお、受光基板10の裏面は半導体層100の裏面B1に一致しうるが、受光基板10の裏面が半導体層100以外の層で構成されていてもよい。半導体素子TR1は例えばn型のMOSトランジスタである。半導体素子TR1は光電変換素子PDと共に画素回路を構成しうる。受光基板10は半導体層100の上に設けられた第1配線部材15を含むことができる。第1配線部材15は、半導体装置で一般的に用いられる配線構造(多層配線構造)の複数の構成要素の少なくともいずれかを含みうる。配線構造(多層配線構造)の複数の構成要素とは、コンタクトプラグ、配線層、ビアプラグ、コンタクトプラグ用や配線層用のエッチングトップ層、層間絶縁層、配線層の拡散防止層、およびパッシバーション層である。受光基板10は第1配線部材15を含まなくてもよい。

【0013】

図1(b)に示す工程Bでは、光電変換素子PDが設けられた受光基板10を支持基板20に固定する。工程Bにおいて、受光基板10が第1配線部材15を含む場合には、第1配線部材15が半導体層100と支持基板20との間に位置する。

【0014】

図1(c)に示す工程Cでは、支持基板20に固定された受光基板10を、受光基板10に対して支持基板20の側とは反対側(裏面B1側)から薄化する。半導体層100の薄化とは半導体層100の厚さを小さくすることである。薄化においては、受光基板10のうち、受光基板10の支持基板20の側とは反対側の面(裏面B1)を含む部分が除去される。工程Cにおける半導体層100の薄化によって、半導体層100には新たな裏面B2が形成される。

【0015】

図1(d)に示す工程Dでは、薄化された受光基板10を、半導体素子TR2が設けられた回路基板30に固定する。この固定は、回路基板30が受光基板10に対して支持基板20の側とは反対側(裏面B2側)に位置するように行われる。回路基板30には半導体素子TR2以外に半導体素子TR3が設けられていてもよい。回路基板30は半導体素子TR2や半導体素子TR3の少なくとも一部を含む半導体層300を有する。半導体素子TR2は例えばn型のMOSトランジスタであり、半導体素子TR3は例えばp型のM

10

20

30

40

50

O Sトランジスタである。半導体素子TR2と半導体素子TR3は共にアナログ信号処理回路やデジタル信号処理回路、A D変換回路あるいは駆動回路を構成しうる。回路基板30には光電変換素子が設けられていてもよい。回路基板30に設けられた光電変換素子は、受光基板10を透過した光を受光することができる。

## 【0016】

回路基板30は半導体層300の上に設けられた第2配線部材35を含むことができる。第2配線部材35は、第1配線部材15と同様に半導体装置で一般的に用いられる配線構造(多層配線構造)における構成要素の少なくともいずれかを含みうる。回路基板30は第2配線部材35を含まなくてもよい。図1(d)に示すように、工程Dにおいて、回路基板30が第2配線部材35を含む場合には、第2配線部材35が半導体層300と受光基板10との間に位置しうる。これに限らず、半導体層300が第2配線部材35と受光基板10との間に位置するように、回路基板30を配置することもできる。

10

## 【0017】

図1(e)に示す工程Eでは、回路基板30に固定された受光基板10の上から支持基板20を除去する。支持基板20は完全に除去することが好ましいが、支持基板20の少なくとも一部が除去されればよく、受光に影響を与えない範囲で支持基板20の一部が受光基板10の上に残っていてもよい。

## 【0018】

図1(f)示す工程Fでは、支持基板20を除去する工程Eの後に、受光基板10に対して回路基板30の側とは反対側(表面F1側)に光学部材40を形成する。光学部材40はトップレンズ(マイクロレンズ)や層内レンズなどの集光部、カラーフィルタなどの波長選択部、およびコアクラッド構造を有する導光部(導光路、光導波路とも言う)、遮光部の少なくともいずれかを含みうる。

20

## 【0019】

なお、工程Bにおいて受光基板10が第1配線部材15を含まない場合には、工程Eと工程Fとの間に、第1配線部材15に相当する配線部材を形成してもよい。工程Aで第1配線部材15の一部を形成し、工程Eと工程Fとの間に第1配線部材15の残りの一部を形成してもよい。

## 【0020】

この後、受光基板10と回路基板30の積層体をダイシングして、複数基板を積層したチップを得ることができる。チップはパッケージングされる。

30

## 【0021】

本実施形態によれば、受光基板10を薄化することにより回路基板30を設けても光電変換装置の厚みの増加を抑制できる。

## 【0022】

また、本実施形態によれば、支持基板20とは反対側の面から受光基板10を薄化し、支持基板20側の面を受光面として用いることができるため、薄化に伴って生じ得るノイズを低減することができる。

## 【0023】

また、本実施形態によれば、支持基板20を除去することにより、支持基板20による半導体層100への入射光の減衰を抑制できる。

40

## 【0024】

また、本実施形態によれば、光学部材40を支持基板20の除去後に形成することで、光学部材40が、支持基板20の着脱時(工程B.E)や受光基板10の薄化時(工程C)に損傷することを避けることができる。よって、光学特性に優れた光電変換装置を得ることができる。同様に、第1配線部材15の少なくとも一部を支持基板20の除去後に形成すれば、第1配線部材15の損傷を低減することができる。そのため、電気的特性や信頼性に優れた光電変換装置を得ることができる。このように、受光面上に配されることになる部材の少なくとも一部を、薄化する工程Cの前ではなく、支持基板20を除去する工程Eの後に行なうことで、受光面上に配されることになる部材に、薄化時や支持基板20の固定時ある

50

いは除去時に生じるダメージを低減することできる。よって、信頼性の高い光電変換装置を製造することができ、また、歩留まり良く光電変換装置を製造することができる。

#### 【0025】

受光基板10と回路基板30は電気的に相互接続される。この電気的接続は、チップの外でワイヤボンディング接続やフリップチップ接続によって実現することができる。あるいは、受光基板10と回路基板30との接続を、チップ内で半導体層100および／または半導体層300を貫通する導電部材である貫通電極によって実現することができる。貫通電極の形成には、スルーシリコンビア(TSV)技術を用いることができる。

#### 【0026】

貫通電極の形成は、導電部材の形成と、導電部材による半導体層の貫通の実現の2つに分けて考えることができる。貫通電極の形成の第1例では、工程Cの後に、受光基板10に対して支持基板20とは反対側から、受光基板10の半導体層100に貫通孔を形成する。そして、貫通孔内に導電部材を形成する。これにより、半導体層100を貫通する導電部材である貫通電極を形成する。その後に、回路基板30が貫通電極に接続するように工程Dを行う。

#### 【0027】

貫通電極の形成の第2例では、工程Eの後に、受光基板10に対して回路基板30とは反対側から、受光基板10の半導体層100に貫通孔を、形成する。そして、貫通孔内に導電部材を形成する。これにより、半導体層100を貫通する導電部材である貫通電極を形成する。貫通孔を回路基板30に達するように形成することで、半導体層100を貫通する導電部材を回路基板30に接続できる。

#### 【0028】

貫通電極の形成の第3例では、工程Bの前に、受光基板10の半導体層100に孔を形成する。そして、この孔の中に導電部材を形成する。そして、工程Cで、受光基板10にに対して支持基板20側とは反対側に導電部材を露出させる。これにより、半導体層100を貫通する導電部材である貫通電極を形成する。支持基板20側とは反対側に露出した導電部材を回路基板30に接続できる。

#### 【0029】

ウェハレベルチップサイズパッケージ(WL CSP)型の光電変換装置を製造することもできる。WL CSP型の光電変換装置では、受光基板10と回路基板30の積層体のダイシング前にガラスウエハなどの透光基板(不図示)に受光基板10と回路基板30の積層体を接着する。このとき、透光基板と回路基板30との間に受光基板10が位置することになる。そして、透光基板と受光基板10と回路基板30とを併せてダイシングする。これにより、透光基板、受光基板、回路基板がこの順で積層された光電変換装置を得ることができる。

#### 【0030】

また、チップオンボード(COB)型の光電変換装置を製造することもできる。COB型の光電変換装置では、配線基板に受光基板10と回路基板30の積層体を接続する。このとき、受光基板10と配線基板との間に回路基板30が位置することになる。そして、受光基板10と回路基板30と配線基板を併せてダイシングする。これにより、受光基板、回路基板、配線基板がこの順で積層された光電変換装置を得ることができる。もちろん、WL CSP型とCOB型を組み合わせて、透光基板、受光基板、回路基板、配線基板がこの順で積層された光電変換装置を得ることもできる。

#### 【0031】

以上説明した光電変換装置は、カメラに用いられる撮像装置(イメージセンサ)として使用できる。この他、焦点検出(AF:オートフォーカス)用のセンサや測光(AE:オートエクスポージャー)用のセンサ、測距用のセンサにも適用できる。

#### 【0032】

カメラは、撮像装置としての光電変換装置以外に、信号処理装置、記憶装置、表示装置および光学装置の少なくともいずれかを備えることができる。信号処理装置は、例えばC

10

20

30

40

50

P U や D S P であり、撮像装置から得られた信号を処理する。記憶装置は、例えば D R A M やフラッシュメモリであり、撮像装置から得られた信号に基づく情報を記憶する。表示装置は、例えば液晶ディスプレイや有機 E L ディスプレイであり、撮像装置で得られた信号に基づく情報を表示する。光学装置は、例えばレンズやミラー、シャッター、フィルタであり、撮像装置へ光を導く。ここでいうカメラとはスチルカメラやビデオカメラ、監視カメラ等のカメラ専用機器以外に、撮影機能を有する情報端末や撮影機能を有する移動体(車両や飛行体)も包含する。

#### 【0033】

以下、実施例 1 ~ 3 を挙げて、詳細に説明する。なお実施例 1 ~ 3 で重複する事項は説明を省略する。

10

#### 【実施例 1】

#### 【0034】

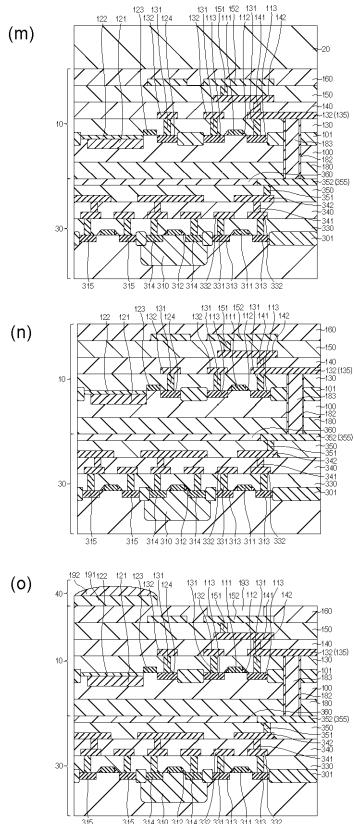

図 2 ( a ) ~ ( c ) に示す工程は、図 1 で説明した工程 A に相当する。

#### 【0035】

図 2 ( a ) に示すように、半導体層 100 を有する半導体ウエハを用意する。

#### 【0036】

図 2 ( b ) に示す工程では、半導体層 100 の素子部(活性部)を画定する素子分離部 101 を形成する。ここで、素子分離部 101 は酸化シリコン膜等のフィールド絶縁膜によって構成され、LOCOS、STI の何れの方法で形成しても良い。そして、半導体層 100 にフォトダイオードである光電変換素子 PD やトランジスタである半導体素子 TR 1 を形成する。半導体素子 TR 1 は、MOS 構造を有するゲート 111 、サイドスペーサ 112 、ソース、ドレインの不純物領域 113 を有する。ウェル、ゲート絶縁膜及び LDD 用の不純物領域については図が細かくなる為、敢えて図示していない。フォトダイオードである光電変換素子 PD は、電荷蓄積領域である n 型の不純物領域 121 と、その周囲の p 型の不純物領域を含む。さらに、不純物領域 121 と半導体層 100 の表面との間には p 型の不純物領域 122 が設けられており、これによって、光電変換素子 PD は埋め込み型フォトダイオードとなっている。転送ゲート 123 は浮遊拡散領域(フローティングディフェュージョン)である n 型の不純物領域 124 に電荷(電子)を転送する。

20

#### 【0037】

図 2 ( c ) に示す工程では、受光基板 10 を形成する。受光基板 10 は半導体層 100 の上に配線部材を有する。配線部材は、層間絶縁層 130 、層間絶縁層 130 を貫通するコントакトプラグ 131 を含む。配線部材は、さらに、第 1 配線層 132 、第 1 配線層 132 上の層間絶縁層 140 、第 1 配線層 132 と第 2 配線層 142 の間の第 1 ビアプラグ 141 、第 2 配線層 142 を含む。配線部材は、さらに、第 2 配線層 142 上の層間絶縁層 150 、第 2 配線層 142 と第 3 配線層 152 の間の第 2 ビアプラグ 151 、第 3 配線層 152 、第 3 配線層 152 上のパッシベーション膜としての絶縁体膜 160 を含む。このように、受光基板 10 には、第 3 配線層 152 上のパッシベーション膜としての絶縁体膜 160 まで設けられている。以上のようにして受光基板 10 が用意される。

30

#### 【0038】

図 2 ( d ) 、( e ) に示す工程は、図 1 で説明した工程 B に相当する。図 2 ( d ) は、パッシベーション膜としての絶縁体膜 160 まで形成した受光基板 10 と支持基板 20 の接合前の状態を示している。図 2 ( e ) は、受光基板 10 と支持基板 20 の接合後の状態を示している。受光基板 10 と支持基板 20 の接合方法は直接接合あるいは各種接着剤を用いた何れの方法でも構わない。支持基板 20 はシリコンウエハでもよいし、ガラスウエハでもよいが、熱膨張率の違いによる反りを考慮すると、受光基板 10 がシリコンウエハであれば、支持基板 20 もシリコンウエハであることが好ましい。

40

#### 【0039】

図 3 ( f ) は、図 1 で説明した工程 C に相当する。受光基板 10 をバックグラインド (BG) 、化学機械研磨 (CMP) 、および / またはウェットエッチングにより受光基板 10 を薄化した状態を表わしている。詳細には、受光基板 10 の半導体層 100 の一部が除

50

去され、半導体層 100 が薄くなる。この時、半導体層 100 の厚さは薄い方が後の貫通電極用の孔を形成する際のエッティング工程で有利である。一方、半導体層 100 が薄過ぎるとフォトダイオード特性に影響がある。薄化後の半導体層 100 の厚さは、5 μm 以上であることが好ましく、10 μm より大きいことがより好ましい。また、薄化後の半導体層 100 の厚さは、100 μm より小さいことが好ましく、50 μm 以下であることがより好ましい。薄化によって現れる半導体層 100 の裏面と受光面となる表面との距離が 10 μm より大きければ、裏面の近傍で生じるノイズの影響を低減できる。

## 【0040】

図 3 (g) ~ (k) は、貫通電極を形成する工程を示す。

## 【0041】

図 3 (g) は受光基板 10 の薄化後、裏面（研磨面）に絶縁膜 180 を形成する工程を示している。

## 【0042】

図 3 (h) は、半導体層 100 に貫通孔 181 を形成する工程を示している。貫通孔 181 は、受光基板 10 の裏面にレジストを塗布し、レジストの露光、現像を行なってマスクを形成する。マスクを用いて半導体層 100 をドライエッティングすることにより第 1 配線層 132 の接続電極 135 に達する貫通孔 181 を形成する。なお、貫通孔 181 が接続電極 135 に達するために、半導体層 100 のエッティングに続いて、素子分離部 101 のフィールド絶縁膜や層間絶縁層 130 もエッティングする。図 3 (h) は、貫通孔 181 の形成後に、レジストマスクを除去した状態を示している。

## 【0043】

図 3 (i) は、貫通孔 181 の内面および半導体層 100 の裏面上に絶縁膜 182 を形成した状態を示している。

## 【0044】

図 4 (j) は、絶縁膜 182 のうち、貫通孔 181 の底（接続電極 135 上）に位置する部分を、異方性エッティングにより除去した状態を示している。なお、絶縁膜 182 のうち、半導体層 100 の裏面上に位置する部分も除去される。これらの工程は、後に貫通孔 181 に埋め込む導電部材と半導体層 100 との絶縁及び、接続電極 135 との導通を実現する為に行なわれる。

## 【0045】

図 4 (k) は、貫通孔 181 の中に導電部材 183 を埋め込む工程を示している。導電部材 183 は、銅シード層および銅メッキ層の形成により導電材料を形成し、CMP により貫通孔 181 外の余分な導電材料を除去することにより形成できる。

## 【0046】

図 4 (l)、図 5 (m) は、図 1 で説明した工程 D に相当する。続く図 4 (l) では受光基板 10 と、別途用意した回路基板 30 の接合前の状態を示している。回路基板 30 は半導体層 300 を含む。半導体層 300 にはトランジスタである半導体素子 TR2、TR3、TR4 をはじめとして、抵抗素子、容量素子などの各種の半導体素子が形成されている。回路基板 30 には半導体集積回路として画素回路以外の回路である周辺回路が設かれている。周辺回路は、画素回路を駆動する駆動回路や画素回路からのアナログ信号を処理するアナログ信号処理回路や、アナログ信号をデジタル信号に変換する A/D 変換回路、デジタル信号を処理するデジタル信号処理回路を含みうる。半導体素子 TR2、TR3、TR4 は MOS 構造を有するゲート 311、サイドスペーサ 312、ソース、ドレインの不純物領域 313、314、315 を有する。半導体素子 TR3 は n 型のウェル 310 に配されている。なお、ゲート絶縁膜は図示を省略している。半導体素子 TR2、TR3、TR4 は LDD 用の不純物領域や HALL 用の不純物領域を設けることができるが、図示を省略している。また、半導体素子 TR2、TR3、TR4 のゲート、ソース、ドレインにはサリサイドプロセスにより、コバルトシリサイドやニッケルシリサイドを包含するシリサイド層が設けることができるが、これも図示を省略している。

## 【0047】

10

20

30

40

50

半導体層 300 の上には配線部材が形成されている。配線部材は、コンタクトプラグ 331、第1配線層 332、ビアプラグ 341、第2配線層 342、ビアプラグ 351、第3配線層 352 含む。また、これらの配線層間には、層間絶縁層 330、340、350 が配されている。配線部材には、ダマシン構造を有する銅配線を用いることができる。パッシベーション膜としての絶縁体膜 360 も設けられている。最上層の配線層である第3配線層 352 に含まれる接続電極 355 が露出した状態にある。

#### 【0048】

図 5 (m) は、パッシベーション膜としての絶縁体膜 360 まで形成した回路基板 30 と受光基板 10 の受光基板 10 と支持基板 20 の接合後の状態を示している。受光基板 10 と回路基板 30 の接合方法は直接接合あるいは各種接着剤を用いた何れの方法でも構わない。受光基板 10 の裏面と、回路基板 30 の表面を接合（貼り合わせる）する事により、受光基板 01 の第1配線層 132 の接続電極と回路基板 30 の接続電極 355 が導電部材 183 を通して導通する。

#### 【0049】

図 5 (n) は、図 1 で説明した工程 E に相当する。支持基板 20 を受光基板 10 から除去する。支持基板 20 除去方法は剥離でも、機械研磨、機械化学研磨、ウェットエッチング、剥離の何れの方法でも構わない。

#### 【0050】

図 5 (o) は、図 1 で説明した工程 F に相当する。カラーフィルタ 191、マイクロレンズ 192 を形成し、さらに絶縁体膜 160 もパッド開口 193 を形成する。その後、ウエハをダイシングしてチップを得て、必要に応じてパッケージングを行う。

#### 【0051】

これにより、受光基板 10 と回路基板 30 を積層した、表面照射型 (FSI) の光電変換装置が完成する。

#### 【0052】

実施例 1 では貫通電極が回路基板 30 の接続電極 355 から第1配線層 132 までとなるので、エッティング対象が、絶縁膜 180、半導体層 100、素子分離部 101 フィールド絶縁膜、層間絶縁層 130 と、少なくて済む。このことは貫通孔 181 を良好に形成する上で有利である。

#### 【0053】

実施例 1 では第1配線層 132 に含まれる接続電極 135 に導電部材 183 を接続したが、貫通孔 181 の加工が可能であれば、どの配線層に含まれる接続電極と接続しても構わない。

#### 【0054】

図 6 (a) は実施例 1 の第1変形例を示している。第1変形例では導電部材 183 が第2配線層 142 に含まれる接続電極 145 に接続されている。

#### 【0055】

図 6 (b) は実施例 1 の第2変形例を示している。第2変形例では導電部材 183 が第3配線層 152 に含まれる接続電極 155 に接続されている。

#### 【実施例 2】

#### 【0056】

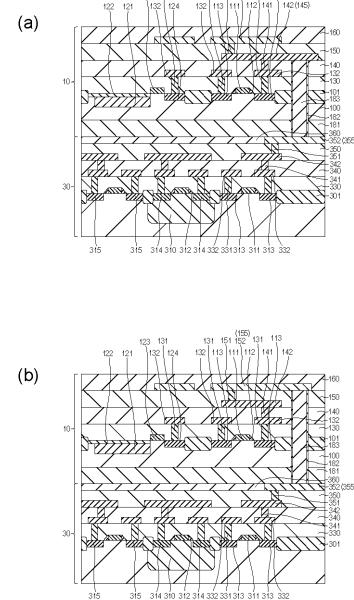

図 7 (a) に示す工程は、図 1 で説明した工程 A に相当する。受光基板 10 には、ビアプラグ 151 と絶縁体膜 160 までが形成されている。実施例 1 とは第3配線層 152 が形成されていない点が相違する。

#### 【0057】

図 7 (b) に示す工程は、図 1 で説明した工程 B に相当する。受光基板 10 に支持基板 20 を貼り合わせ、相互に固定する。

#### 【0058】

図 7 (c) に示す工程は、図 1 で説明した工程 C に相当する。受光基板 10 を機械研磨 (MP)、化学機械研磨 (CMP)、あるいはウェットエッティングにより薄化する。

10

20

30

40

50

**【0059】**

図7(d)に示す工程は、図1で説明した工程Dに相当する。実施例2においては、回路基板30の接続電極355は絶縁膜380で覆われている。絶縁膜380は受光基板10と回路基板30との接合の前に回路基板30に設けられている。なお、本例では実施例1における絶縁膜180に相当する絶縁膜を省略して、絶縁膜380と半導体層100が接するようにしている。半導体層100の上に絶縁膜180を設けて、絶縁膜180と絶縁膜380とが直接接合するあるいは、接着剤を介して接合するようにしてもよい。

**【0060】**

図8(e)に示す工程は、図1で説明した工程Eに相当する。支持基板20は受光基板10の上から除去されている。10

**【0061】**

図8(f)～図9(h)に示す工程は、貫通電極を形成する工程である。

**【0062】**

図8(f)に示す工程では、受光基板10に対して回路基板30とは反対側から、半導体層100を貫通する貫通孔381を形成する。

**【0063】**

貫通孔381は、受光基板10の裏面にレジストを塗布し、レジストの露光、現像を行なってマスクを形成する。マスクを用いて半導体層100をドライエッティングすることにより第3配線層352の接続電極355に達する貫通孔381を形成する。なお、半導体層100のエッティングの前に、絶縁体膜160、層間絶縁層150、140、130および素子分離部101のフィールド絶縁膜もエッティングする。また、貫通孔381が接続電極355に達するために、半導体層100のエッティングの後に、絶縁膜380もエッティングする。20

**【0064】**

また、絶縁体膜160には凹部383を形成する。凹部は絶縁体膜160のエッティングによって形成できる。凹部383と貫通孔381はどちらを先に形成してもかまわない。さらに、貫通孔381および凹部383の内面に絶縁膜382を形成する。

**【0065】**

図8(g)に示す工程では、絶縁膜382のうち、貫通孔381の底(接続電極355上)に位置する部分と、ビアプラグ151上に位置する部分とを、異方性エッティングにより除去した状態を示している。なお、絶縁膜382のうち、絶縁体膜160に位置する部分も除去される。これらの工程は、後に貫通孔381に埋め込む導電部材と半導体層100との絶縁と、ビアプラグ151や接続電極355との導通を実現する為に行なわれる。30

**【0066】**

図9(h)は、貫通孔381の中に導電部材383を埋め込む工程を示している。導電部材383は、銅シード層および銅メッキ層の形成により導電材料を形成し、CMPにより貫通孔181外の余分な導電材料を除去することにより形成できる。

**【0067】**

図9(i)は、パッド電極385、カラーフィルタ191、マイクロレンズ192、パッド開口193を形成する工程を示している。40

**【0068】**

実施例2では、貫通孔381の形成を受光基板10の表面側で行なえるので、実施例1よりも重ね合わせ精度を高く出来る。

**【実施例3】****【0069】**

図10(a)～(g)に示す工程は、図1で説明した工程Aに相当する。

**【0070】**

図10(a)は、半導体層100を有する半導体ウエハとして、SOIウエハを用いていることを示している。SOIウエハは、半導体層100を支持する基体120と、半導体層100と基体120との間に配された絶縁体層110と、を含む。50

**【 0 0 7 1 】**

図 10 ( b ) に示すように、各種半導体素子が形成された半導体層 100 の上に、層間絶縁層 130 を形成する。

**【 0 0 7 2 】**

図 10 ( c ) に示すように、層間絶縁層 130 を貫通して半導体素子に接続されたコンタクトプラグ 131 を形成する。

**【 0 0 7 3 】**

図 10 ( d ) は、半導体層 100 に孔 281 を形成する工程を示している。絶縁体膜 160 の上にレジストを塗布し、レジストの露光、現像を行なってマスクを形成する。マスクを用いて半導体層 100 をドライエッティングすることにより、半導体層 100 に孔 281 を形成する。本例において、孔 281 は半導体層 100 および絶縁体層 110 を貫通して基体 120 に達しているが、孔 281 を絶縁体層 110 内で止めてよいし、半導体層 100 内で止めてよい。なお、孔 281 が半導体層 100 に達するために、半導体層 100 のエッティングの前に、層間絶縁層 130 や素子分離部 101 のフィールド絶縁膜もエッティングする。図 10 ( c ) は、孔 281 の形成後に、レジストマスクを除去した状態を示している。なお、孔 281 とコンタクトプラグ 131 の形成はどちらが先でもよく、エッティングレートの違いを利用して同時に形成してもよい。

**【 0 0 7 4 】**

図 10 ( e ) は孔 281 内に絶縁膜 282 を形成した状態を示している。

**【 0 0 7 5 】**

図 10 ( f ) は孔 281 内にタンゲステン (W) を含む導電部材 283 を埋め込んだ工程を示している。

**【 0 0 7 6 】**

図 10 ( g ) は、層間絶縁層 130 の上に、導電部材 283 およびコンタクトプラグ 131 を覆う様に保護膜 240 を形成する工程を示している。

**【 0 0 7 7 】**

図 11 ( h ) に示す工程は、図 1 で説明した工程 B に相当する。受光基板 10 に支持基板 20 を貼り合わせ、相互に固定する。

**【 0 0 7 8 】**

図 11 ( i ) に示す工程は、図 1 で説明した工程 C に相当する。受光基板 10 を機械研磨 (M P) 、化学機械研磨 (C M P) 、あるいはウェットエッティングにより薄化する。本例では、受光基板 10 に対して支持基板 20 の側とは反対側に、孔 281 内の導電部材 283 を露出させる。受光基板 10 の薄化において除去されるべき部分は、孔 281 の深さに応じて設定される。孔 281 が絶縁体層 110 を貫通していれば、基体 120 を除去すれば導電部材 283 を露出できる。孔 281 が絶縁体層 110 を貫通していれば、基体 120 を除去すれば導電部材 283 を露出できる。孔 281 が絶縁体層 110 内にとどまつていれば、基体 120 および絶縁体層 110 の少なくとも一部を除去すれば導電部材 283 を露出できる。孔 281 が半導体層 100 を貫通していなければ、絶縁体層 110 を除去し、さらに半導体層 100 の一部を除去する必要がある。絶縁体層 110 を残しておく方が半導体層 100 に生じるダメージを低減できる。

**【 0 0 7 9 】**

図 11 ( j ) では受光基板 001 と回路基板 30 とを接合する工程を示している。回路基板 30 には各種トランジスタ、抵抗、容量、配線が形成されており、最上層の配線層 352 に含まれる接続電極 355 が露出した状態にある。受光基板 001 と回路基板 30 とを接合することで、受光基板 10 側の導電部材 283 と回路基板 30 の電極 355 が導通する。

**【 0 0 8 0 】**

図 11 ( k ) に示す工程は、図 1 で説明した工程 E に相当する。支持基板 20 を受光基板 10 上から除去する。除去方法は剥離でも、B G、C M P、ウェットエッティング何れの方法でも構わない。

10

20

30

40

50

**【0081】**

図11(1)に示す工程では、保護膜240を除去する。

**【0082】**

図12(m)に示す工程では、層間絶縁層130の上に、第1配線層132、層間絶縁層140、ピアプラグ141、第2配線層142、層間絶縁層150、ピアプラグ151、絶縁体膜160を形成する。なお、図11(1)に示す工程で保護膜240を除去せずに、保護膜240を層間絶縁層として利用してもよい。

**【0083】**

図12(n)に示す工程では、図1で説明した工程Fに相当する。受光基板10の上に、カラーフィルタ191、マイクロレンズ192を形成する。

10

**【0084】**

実施例3では、配線層を形成する前に、支持基板20の接合と受光基板10の薄化、および支持基板20の除去を行なっている。これにより、カラーフィルタ191やマイクロレンズ192だけでなく、配線層へのダメージを抑制する事が出来る。また、銅配線を用いた場合、配線層と絶縁層あるいは配線層と拡散防止層の界面で剥がれを抑制できる。

**【実施例4】****【0085】**

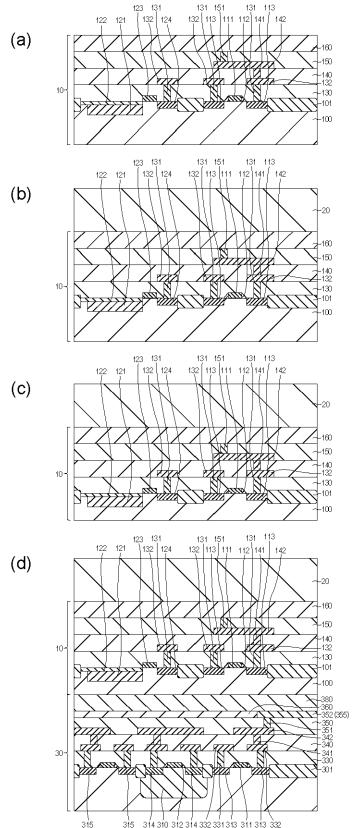

図13(a)に示す工程は、図1で説明した工程Aに相当する。配線層132、142はダマシン構造を有する、銅配線である。第1配線層132はシングルダマシン構造、第2配線層142はデュアルダマシン構造を有する。また、第1配線層132と層間絶縁層150の間に拡散防止層133が配されており、第2配線層142と層間絶縁層150の間に拡散防止層143が配されている。拡散防止層143の上には絶縁層161が配されている。

20

**【0086】**

図13(b)に示す工程は、図1で説明した工程Bに相当する。受光基板10の絶縁層161上に支持基板20が接合される。

**【0087】**

図13(c)に示す工程は、図1で説明した工程Cに相当する。受光基板10の半導体層100が薄化される。

30

**【0088】**

図13(d)に示す工程は、実施例1における貫通電極を形成する工程に相当する。半導体層100を貫通する導電部材283が形成される。

**【0089】**

図13(e)に示す工程は、図1で説明した工程Dに相当する。受光基板10に回路基板30が接合される。

**【0090】**

図14(f)に示す工程は、図1で説明した工程Eに相当する。支持基板20が受光基板10の上から除去される。

**【0091】**

図14(g)、(h)に示す工程は、図1で説明した工程Fに相当する。

40

**【0092】**

図14(g)に示す工程では、導光部170を形成する。まず、光電変換素子PD上に開口を有するマスクを用いて、層間絶縁層161、150、140、130および拡散防止層143、133をエッティングする。これによって、開口部175を形成する。開口部175を形成する際に、図13(a)に示す工程で層間絶縁層130の下に配された絶縁層129がエッティングストップ層として機能する。さらに、開口部175の中に窒化シリコンや樹脂などの透光材料を埋め込むことにより、導光部170が形成される。開口部175の外に位置する透光材料は必要に応じて除去される。

**【0093】**

図14(g)に示す工程では、導光部170を覆って層間絶縁層162が形成される。

50

さらに層間絶縁層 162、161にピアプラグ 151を形成し、ピアプラグ 151の上にパッド電極 152を形成する。パッド電極 152を覆うようにパッシベーション膜としての絶縁体膜 160を形成する。絶縁体膜 160をエッチバック法等を用いて集光部 161を有するように加工することができる。集光部 161は層内レンズとして機能する。集光部 161を形成する上で好適な絶縁体膜 160は窒化シリコン膜でありうる。絶縁体膜 160の上に樹脂からなる平坦化膜 163を形成する。平坦化膜 163の上にカラーフィルタ 191、マイクロレンズ 192を形成する。導光部 170や集光部 161、平坦化膜 163、カラーフィルタ 191、マイクロレンズ 192は図1で説明した光学部材 40に相当する。また、ピアプラグ 151やパッド電極 152、層間絶縁層 162は、支持基板 20の除去後に形成された配線部材 50である。

10

#### 【0094】

本実施形態は、導光部 170を設けているために、半導体層 100の受光面上に複数の配線層があつても、迷光等を抑制でき、また、光利用効率を向上できる。

#### 【0095】

さらに、導光部 170を、支持基板 20の除去後に形成しているため、薄化時のダメージや支持基板 20の除去時に生じ得るダメージが導光部 170に与える影響を低減できる。

#### 【0096】

なお、本実施例では、実施例 1のようにして配線層を薄化間に形成したが、実施例 2のように、支持基板 20の除去後に、複数の配線層や層間絶縁層を形成することもできる。また、貫通電極の形成は実施例 2と同様でもよいし、実施例 3と同様でもよい。

20

#### 【0097】

以上説明した実施形態に関しては、本明細書に明確な記載がなくとも、添付の図面や技術常識から把握できる事項も本開示の一部を構成する。また、本発明は、本開示の技術思想の範囲を逸脱しない限り、適宜な変更が可能である。

#### 【符号の説明】

#### 【0098】

10 受光基板

P D 光電変換素子

20 支持基板

30 回路基板

T R 2、T R 3 半導体素子

30

【図1】

【図2】

【図3】

【 図 4 】

【図5】

【 図 6 】

【図7】

【 図 8 】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

---

フロントページの続き

(51) Int.Cl. F I テーマコード(参考)

**H 04N 5/369 (2011.01)** H 01L 21/88 T

H 04N 5/335 690

F ターム(参考) 4M118 AA10 AB01 BA14 BA19 CA04 CA22 DD04 EA01 EA14 FA28

GA09 GB03 GC07 GD04 GD11 HA02 HA21 HA22 HA24 HA25

HA30 HA33

5C024 BX04 CY47 EX42 EX43 EX52 GX07

5F033 HH11 JJ11 KK11 MM01 MM30 PP27 PP28 QQ09 QQ11 QQ48