(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5498762号

(P5498762)

(45) 発行日 平成26年5月21日(2014.5.21)

(24) 登録日 平成26年3月14日(2014.3.14)

|                       |                 |

|-----------------------|-----------------|

| (51) Int.Cl.          | F 1             |

| HO1L 29/786 (2006.01) | HO1L 29/78 618A |

| HO1L 21/336 (2006.01) | HO1L 29/78 618B |

| HO1L 21/20 (2006.01)  | HO1L 29/78 618E |

| HO1L 21/316 (2006.01) | HO1L 29/78 616K |

| HO1L 21/205 (2006.01) | HO1L 21/20      |

請求項の数 3 (全 37 頁) 最終頁に続く

|              |                               |

|--------------|-------------------------------|

| (21) 出願番号    | 特願2009-257696 (P2009-257696)  |

| (22) 出願日     | 平成21年11月11日 (2009.11.11)      |

| (65) 公開番号    | 特開2010-141306 (P2010-141306A) |

| (43) 公開日     | 平成22年6月24日 (2010.6.24)        |

| 審査請求日        | 平成24年11月1日 (2012.11.1)        |

| (31) 優先権主張番号 | 特願2008-293954 (P2008-293954)  |

| (32) 優先日     | 平成20年11月17日 (2008.11.17)      |

| (33) 優先権主張国  | 日本国 (JP)                      |

|           |                                                |

|-----------|------------------------------------------------|

| (73) 特許権者 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (72) 発明者  | 高橋 絵里香<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内  |

| (72) 発明者  | 加藤 高之<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (72) 発明者  | 宮入 秀和<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (72) 発明者  | 神保 安弘<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

最終頁に続く

(54) 【発明の名称】薄膜トランジスタの作製方法

## (57) 【特許請求の範囲】

## 【請求項 1】

基板上のゲート電極と、

前記ゲート電極上のゲート絶縁層と、

前記ゲート絶縁層上の半導体層と、

前記半導体層上の不純物元素を含む半導体層と、

前記不純物元素を含む半導体層上のソース電極とドレイン電極とを有する薄膜トランジ

スタの作製方法であって、

前記半導体層は、前記ゲート絶縁層側から、第1の層と、前記第1の層上の第2の層と

、前記第2の層上の第3の層とを有し、

前記第1の層は、微結晶半導体層であり、

前記第2の層は、微結晶半導体領域と、非晶質半導体領域とを有し、

前記第3の層は、非晶質半導体層であり、

前記第1の層は、前記ゲート絶縁層側の第1の領域と、前記第1の部分上の第2の領域

とを有し、

シリコンまたはゲルマニウムを含む堆積性気体と、水素と、希ガスとを混合し、シリコ

ンまたはゲルマニウムを含む堆積性気体の流量に対して、水素の流量を10～2000倍

にし、高周波電力を印加することで、前記第1の領域を形成し、

前記第1の領域を形成後、シリコンまたはゲルマニウムを含む堆積性気体と、水素と、

窒素を含む気体を混合し、シリコンまたはゲルマニウムを含む堆積性気体の流量に対して

、水素の流量を10～2000倍にし、高周波電力を印加することで、前記第2の領域と前記第2の層と前記第3の層とを形成することを特徴とする薄膜トランジスタの作製方法。

【請求項2】

請求項1において、

前記第2の領域は、前記第1の領域を種結晶として結晶成長することで形成されることを特徴とする薄膜トランジスタの作製方法。

【請求項3】

請求項1または請求項2において、

前記第2の層の前記微結晶半導体領域は、前記第1の層から前記第3の層に向かって、

先端が狭まる凸状の領域であり、

10

前記第2の層の前記微結晶半導体領域以外は、前記非晶質半導体領域であることを特徴

とする薄膜トランジスタの作製方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、薄膜トランジスタの作製方法、及び該薄膜トランジスタを用いた表示装置に関する。

【背景技術】

【0002】

電界効果トランジスタの一種として、絶縁表面を有する基板上に形成された半導体層にチャネル領域が形成される薄膜トランジスタが知られている。薄膜トランジスタに用いられる半導体層として、非晶質シリコン、微結晶シリコン及び多結晶シリコンを用いる技術が開示されている（特許文献1乃至5参照）。薄膜トランジスタの代表的な応用例は、液晶テレビジョン装置であり、表示画面を構成する各画素のスイッチングトランジスタとして実用化されている。

20

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2001-053283号公報

30

【特許文献2】特開平5-129608号公報

【特許文献3】特開2005-049832号公報

【特許文献4】特開平7-131030号公報

【特許文献5】特開2005-191546号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

非晶質シリコン層を用いてチャネルが形成される薄膜トランジスタは、電界効果移動度及びオン電流が低いといった問題がある。一方、微結晶シリコン層にチャネルが形成される薄膜トランジスタは、非晶質シリコンでチャネルが形成される薄膜トランジスタと比較して、電界効果移動度が向上するもののオフ電流が高くなってしまい、十分なスイッチング特性が得られないといった問題がある。

40

【0005】

多結晶シリコン層がチャネル形成領域となる薄膜トランジスタは、上記二種類の薄膜トランジスタよりも電界効果移動度が格段に高く、高いオン電流が得られるといった特性がある。この薄膜トランジスタは、前記した特性により、画素に設けられるスイッチング用のトランジスタのみならず、高速動作が要求されるドライバ回路をも構成することができる。

【0006】

しかし、多結晶シリコン層により薄膜トランジスタは、非晶質シリコン層で薄膜トランジ

50

スタを形成する場合に比べ半導体層の結晶化工程が必要となり、製造コストが増大することが問題となっている。例えば、多結晶シリコン層の製造のために必要なレーザアニール技術は、レーザビームの照射面積が小さく大画面の液晶パネルを効率良く生産することができないといった問題がある。

【0007】

ところで、表示パネルの製造に用いられているガラス基板は、第3世代(550mm×650mm)、第3.5世代(600mm×720mm、または620mm×750mm)、第4世代(680mm×880mm、または730mm×920mm)、第5世代(1100mm×1300mm)、第6世代(1500mm×1850mm)、第7世代(1870mm×2200mm)、第8世代(2200mm×2400mm)と年々大型化が進んでおり、今後は第9世代(2400mm×2800mm、2450mm×3050mm)、第10世代(2950mm×3400mm)へと大面積化が進むと予測されている。ガラス基板の大型化はコストミニマム設計の思想に基づいている。

【0008】

これに対して、第10世代(2950mm×3400mm)におけるような大面積のマザーガラス基板に、高速動作が可能な薄膜トランジスタを、生産性良く製造することができる技術は依然として確立されておらず、そのことが産業界の問題となっている。

【0009】

そこで、電気特性が良好な薄膜トランジスタを、生産性高く作製する方法を提供することを課題の一とする。

20

【課題を解決するための手段】

【0010】

基板上にゲート電極を形成し、ゲート電極上にゲート絶縁層を形成し、ゲート絶縁層上にシリコンまたはゲルマニウムを含む堆積性気体と、水素と、ヘリウム、アルゴン、ネオン、クリプトン、キセノン等の希ガスとを用い、プラズマを発生させて、厚さ3~10nm、好ましくは3~5nmの第1の半導体層を形成する。

【0011】

次に、シリコンまたはゲルマニウムを含む堆積性気体と、水素と、窒素を含む気体とを用い、プラズマを発生させて、第1の半導体層を種結晶として部分的に結晶成長させて、微結晶半導体で形成される複数の錐形状の凸部を有する第2の半導体層を形成する。

30

【0012】

次に、一導電型を付与する不純物元素が添加された半導体層(以下、不純物半導体層と示す。)を形成し、導電層を形成して、薄膜トランジスタを作製する。

【0013】

第1の半導体層としては微結晶半導体層を形成する。第2の半導体層は、第1の半導体層を含む半導体層であり、ゲート絶縁層に接する微結晶半導体層と、当該微結晶半導体層に接する微結晶半導体及び非晶質半導体を有する層とを有する。さらに、微結晶半導体及び非晶質半導体を有する層に接する非晶質半導体層を有してもよい。なお、ゲート絶縁層に接する微結晶半導体層は、第1の半導体層と、第1の半導体層を種結晶として結晶成長した微結晶半導体層とを含む。

40

【0014】

第2の半導体層に含まれる微結晶半導体層は、薄膜トランジスタのチャネル形成領域として機能し、非晶質半導体層は、高抵抗領域として機能する。不純物半導体層は、薄膜トランジスタのソース領域及びドレイン領域として機能し、導電層は配線として機能する。

【0015】

第1の半導体層の原料ガスとして、ヘリウム、アルゴン、ネオン、クリプトン、キセノン等の希ガスを用いることで、プラズマが安定し、シリコンまたはゲルマニウムを含む堆積性気体、及び水素の解離が促進され、活性種の量が増加する。このため、活性種同士の反応が促進され、第1の半導体層の成膜速度が高まる。また、成膜速度が高まると、第1の半導体層の堆積時間が短くなり、堆積中に取り込まれる処理室内の不純物量が低減するた

50

め、第1の半導体層に含まれる不純物量が低減し、第1の半導体層の結晶性が高まる。このため、薄膜トランジスタのオン電流及び電界効果移動度を高めることができる。

【0016】

また、シリコンまたはゲルマニウムを含む堆積性気体、水素と共に、アンモニア、窒素、フッ化窒素、塩化窒素等の窒素を含む気体を用いて、第2の半導体層を形成することで、微結晶半導体で形成される複数の錐形状の凸部を有する、微結晶半導体及び非晶質半導体を有する層を形成することができる。更には、微結晶半導体及び非晶質半導体を有する層上に窒素を有する非晶質半導体層を形成することができる。このため、ソース領域及びドレイン領域に接する領域及びバックチャネル側は高抵抗な非晶質半導体層であるものの、チャネル形成領域と、ソース領域及びドレイン領域との間ににおいて、低抵抗である微結晶半導体で形成される複数の錐形状の凸部が形成されるため、オフ電流を低減することができると共に、ソース領域及びドレイン領域と、チャネル形成領域の間の抵抗を低減することによりオン電流が上昇する。また、第2の半導体層の原料ガスに窒素を含む気体を用いることで、しきい値電圧を制御することができる。

【0017】

なお、第2の半導体層の原料ガスとして、ヘリウム、アルゴン、ネオン、クリプトン、キセノン等の希ガスを用いることで、成膜速度を上昇させることができる。

【発明の効果】

【0018】

以上のことから、オフ電流が低く、オン電流が高く、しきい値電圧が制御された薄膜トランジスタを生産性高く作製することができる。

【図面の簡単な説明】

【0019】

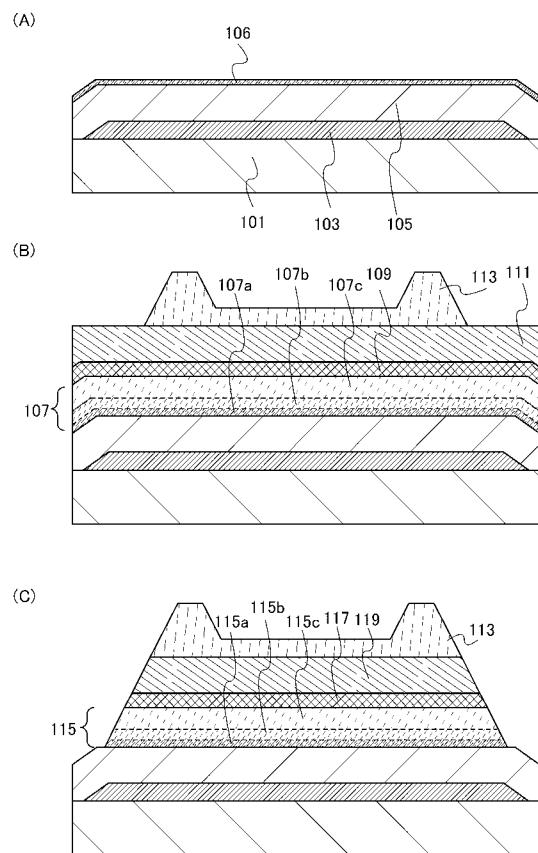

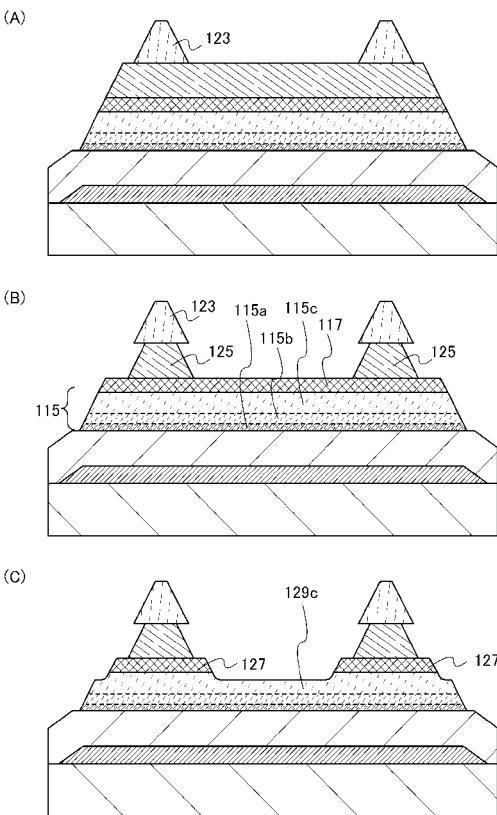

【図1】薄膜トランジスタの作製方法を説明する断面図である。

【図2】薄膜トランジスタの作製方法を説明する断面図である。

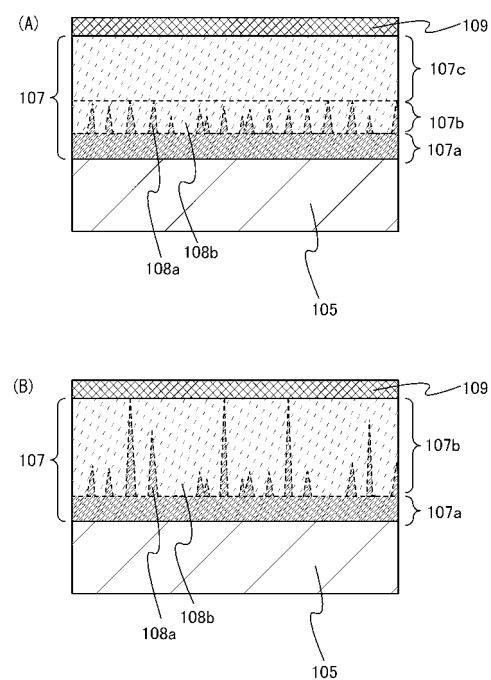

【図3】薄膜トランジスタを形成する工程を説明するタイムチャートの一例である。

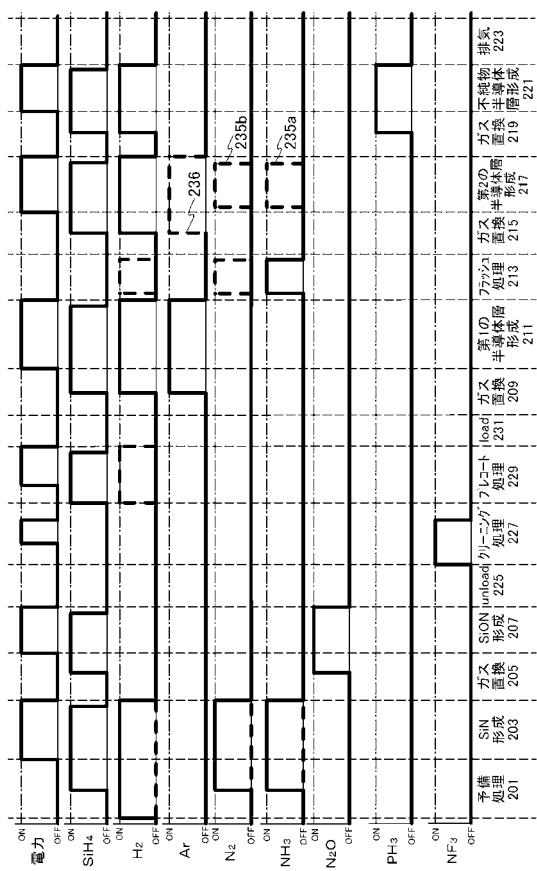

【図4】薄膜トランジスタの作製方法に適用可能な多階調マスクを説明する図。

【図5】薄膜トランジスタの作製方法を説明する断面図である。

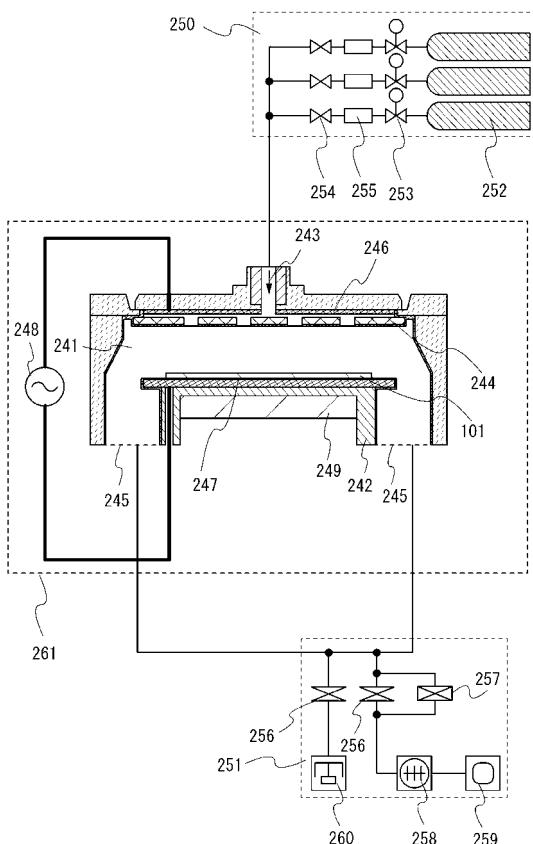

【図6】薄膜トランジスタの作製工程に使用可能なCVD装置の一例を示す図である。

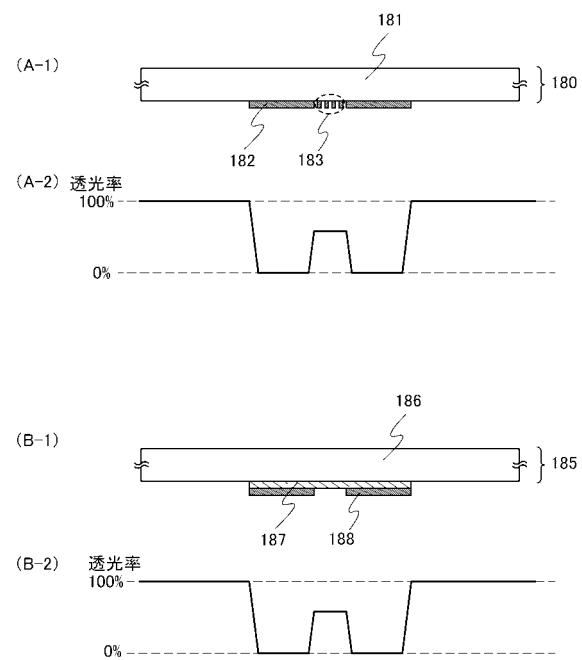

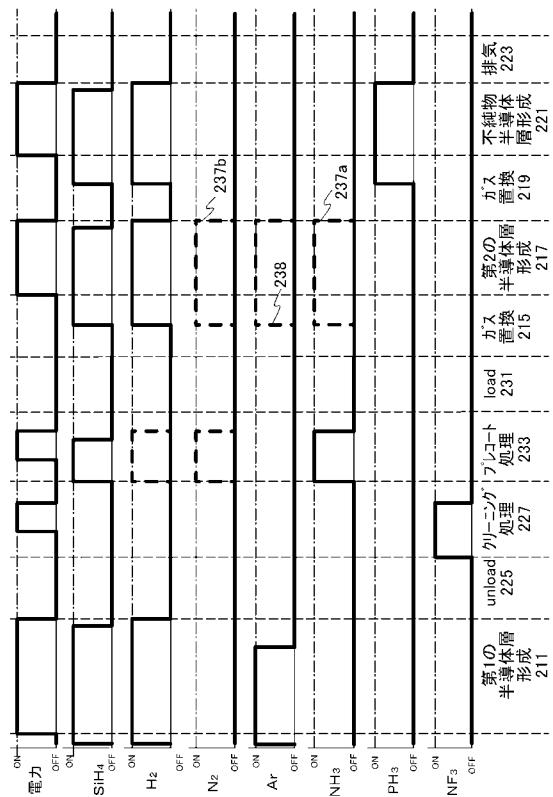

【図7】薄膜トランジスタを形成する工程を説明するタイムチャートの一例である。

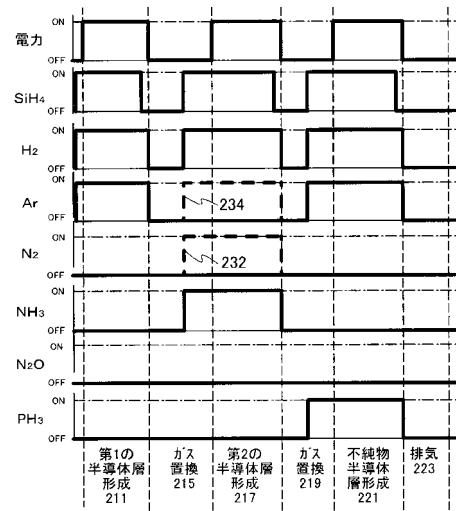

【図8】薄膜トランジスタを形成する工程を説明するタイムチャートの一例である。

【図9】薄膜トランジスタを形成する工程を説明するタイムチャートの一例である。

【図10】薄膜トランジスタの作製方法を説明する断面図である。

【図11】薄膜トランジスタの作製方法を説明する断面図である。

【図12】表示装置を説明する断面図である。

【図13】表示装置を説明する断面図である。

【図14】薄膜トランジスタを適用した電子機器である。

【図15】微結晶シリコン層の成膜速度を示す図である。

【図16】ラマン分光分析の測定結果を示す図である。

【図17】ラマン分光分析の測定結果を示す図である。

【図18】薄膜トランジスタの電気特性の測定結果を示す図である。

【図19】微結晶シリコン層に含まれる窒素濃度を示す図である。

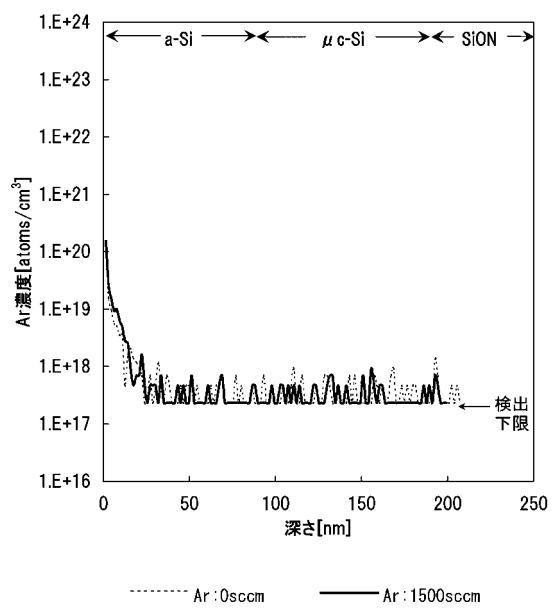

【図20】微結晶シリコン層に含まれるアルゴン濃度を示す図である。

【発明を実施するための形態】

【0020】

以下に開示する実施の形態について、図面を用いて詳細に説明する。但し、開示される発明は以下の説明に限定されず、開示される発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、開示される発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する発明の構成において、同一部分または同様な機能を有する部分には

10

20

30

40

50

同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する。

【0021】

(実施の形態1)

本実施の形態では、薄膜トランジスタの作製方法について、図1乃至図9を用いて示す。薄膜トランジスタは、p型よりもn型の方が、キャリアの移動度が高い。また、同一の基板上に形成する薄膜トランジスタを全て同じ極性に統一すると、工程数を抑えることができ、好ましい。そのため、本実施の形態では、n型の薄膜トランジスタの作製方法について説明する。

【0022】

基板101上にゲート電極103を形成する。次に、ゲート電極103を覆ってゲート絶縁層105を形成し、ゲート絶縁層105上に第1の半導体層106を形成する(図1(A)参照)。

10

【0023】

基板101としては、ガラス基板、セラミック基板の他、本作製工程の処理温度に耐えうる程度の耐熱性を有するプラスチック基板等を用いることができる。また、基板に透光性を要しない場合には、ステンレス合金等の金属の基板の表面に絶縁層を設けたものを用いてもよい。ガラス基板としては、例えば、バリウムホウケイ酸ガラス、アルミノホウケイ酸ガラス若しくはアルミノケイ酸ガラス等の無アルカリガラス基板を用いるとよい。

【0024】

ゲート電極103は、モリブデン、チタン、クロム、タンタル、タングステン、アルミニウム、銅、ネオジム、スカンジウム等の金属材料またはこれらを主成分とする合金材料を用いて、単層でまたは積層して形成することができる。また、リン等の不純物元素をドーピングした多結晶シリコンに代表される半導体層やAgPdCu合金を用いてもよい。

20

【0025】

ゲート電極103は、基板101上に、スパッタリング法または真空蒸着法を用いて上記した材料を用いた導電層を形成し、該導電層上にフォトリソグラフィ法またはインクジェット法等によりマスクを形成し、該マスクを用いて導電層をエッチングして形成することができる。フォトリソグラフィ工程においては、レジストを基板全面に塗布してもよいが、レジストマスクを形成する領域に印刷法によりレジストを印刷した後、露光することで、レジストを節約することが可能であり、コスト削減が可能である。

30

【0026】

また、銀、金または銅等の導電性ナノペーストをインクジェット法により基板上に吐出し、焼成することで形成することもできる。なお、ゲート電極103と、基板101との密着性向上のため、上記の金属材料の窒化物層を、基板101と、ゲート電極103との間に設けてもよい。ここでは、基板101上に導電層を形成し、フォトマスクを用いて形成した第1のレジストマスクによりエッチングする。

【0027】

なお、ゲート電極103の側面は、テーパー形状とすることが好ましい。ゲート電極103上には、後の工程で半導体層及び配線層を形成するので、段差の箇所における配線切れ防止のためである。ゲート電極103の側面をテーパー形状にするためには、レジストマスクを後退させつつエッチングを行えばよい。

40

【0028】

また、ゲート電極103を形成する工程によりゲート配線(走査線)及び容量配線も同時に形成することができる。なお、走査線とは画素を選択する配線をいい、容量配線とは画素の保持容量の一方の電極に接続された配線をいう。ただし、これに限定されず、ゲート配線及び容量配線の一方または双方と、ゲート電極103とは別に設けてもよい。

【0029】

ゲート絶縁層105は、酸化シリコン層、窒化シリコン層、酸化窒化シリコン層または窒化酸化シリコン層を単層でまたは積層して形成することができる。また、ゲート絶縁層105を酸化シリコン層または酸化窒化シリコン層により形成することで、薄膜トランジス

50

タのしきい値電圧の変動を抑制することができる。

【0030】

ゲート絶縁層105は、CVD法またはスパッタリング法等を用いて形成することができる。また、ゲート絶縁層105は、高周波数(1GHz以上)のマイクロ波プラズマCVD装置を用いて形成してもよい。マイクロ波プラズマCVD装置を用いて高い周波数によりゲート絶縁層105を形成すると、ゲート電極と、ドレイン電極及びソース電極との間の耐圧を向上させることができるために、信頼性の高い薄膜トランジスタを得ることができる。また、ゲート絶縁層105として、有機シランガスを用いたCVD法により酸化シリコン層を形成することで、ゲート絶縁層の水素含有量を低減することが可能であり、薄膜トランジスタのしきい値電圧の変動を低減することができる。有機シランガスとしては、

10 硅酸エチル(TEOS:化学式Si(OCH<sub>3</sub>)<sub>4</sub>)、テトラメチルシラン(TMS:化学式Si(CH<sub>3</sub>)<sub>4</sub>)、テトラメチルシクロテトラシロキサン(TMCTS)、オクタメチルシクロテトラシロキサン(OMCTS)、ヘキサメチルジシラザン(HMDS)、トリエトキシシラン(SiH(OCH<sub>3</sub>)<sub>3</sub>)、トリスジメチルアミノシラン(SiH(N(CH<sub>3</sub>)<sub>2</sub>)<sub>3</sub>)等のシリコン含有化合物を用いることができる。

【0031】

ゲート絶縁層105上に第1の半導体層106を形成する。第1の半導体層106は、微結晶半導体層を用いて形成し、代表的には微結晶シリコン層、微結晶ゲルマニウム層、微結晶シリコンゲルマニウム層を形成する。第1の半導体層106の厚さは、厚さ3~10nm、好ましくは3~5nmと薄くすることで、後に形成される第2の半導体層において、

20 微結晶半導体で形成される複数の錐形状の凸部の長さを制御することができる。

【0032】

第1の半導体層106は、プラズマCVD装置の処理室内において、シリコンまたはゲルマニウムを含む堆積性気体と、水素と、希ガスとを混合し、グロー放電プラズマにより形成する。代表的には、シリコンまたはゲルマニウムを含む堆積性気体と、水素と、ヘリウム、ネオン、アルゴン、キセノン、またはクリプトンとを混合し、グロー放電プラズマにより形成する。シリコンまたはゲルマニウムを含む堆積性気体の流量に対して、水素の流量を10~2000倍、好ましくは10~200倍に希釈して、微結晶シリコン、微結晶シリコンゲルマニウム、微結晶ゲルマニウム等を形成する。

【0033】

シリコンまたはゲルマニウムを含む堆積性気体の代表例としては、SiH<sub>4</sub>、Si<sub>2</sub>H<sub>6</sub>、GeH<sub>4</sub>、Ge<sub>2</sub>H<sub>6</sub>等がある。希ガスとしては、ヘリウム、ネオン、アルゴン、キセノン、またはクリプトンの一または複数を用いる。

【0034】

第1の半導体層106の原料ガスとして、ヘリウム、アルゴン、ネオン、クリプトン、キセノン等の希ガスを用いることで、プラズマが安定し、シリコンまたはゲルマニウムを含む堆積性気体、及び水素の解離が促進され、活性種の量が増加する。このため、活性種同士の反応が促進され、第1の半導体層の成膜速度が高まる。また、成膜速度が高まると、第1の半導体層106が堆積する際に、処理室内の不純物が取り込まれにくくなるため、第1の半導体層106に含まれる不純物量が低減し、第1の半導体層106の結晶性が高まる。このため、薄膜トランジスタのオン電流及び電界効果移動度が高まると共に、薄膜トランジスタの生産性を高めることができる。

【0035】

また、第1の半導体層106を形成する際の、グロー放電プラズマの生成は、3MHzから30MHz、代表的には13.56MHz、27.12MHzのHF帯の高周波電力、または30MHzより大きく300MHz程度までのVHF帯の高周波電力、代表的には、60MHzを印加することで行われる。また、1GHz以上のマイクロ波の高周波電力を印加することで行われる。なお、VHF帯やマイクロ波の高周波電力を用いることで、成膜速度を高めることができる。更には、HF帯の高周波電力と、VHF帯の高周波電力を重畠させることで、大面積基板においてもプラズマのムラを低減し、均一性を高め

50

ることができると共に、成膜速度を高めることができる。

【0036】

なお、第1の半導体層106を形成する前に、CVD装置の処理室内を減圧しながら、シリコンまたはゲルマニウムを含む堆積性気体を導入して、処理室内の不純物元素を除去することで、後に形成される薄膜トランジスタのゲート絶縁層105及び第1の半導体層106の界面における不純物元素を低減することが可能であり、薄膜トランジスタの電気特性を向上させることができる。

【0037】

次に、図1(B)に示すように、第1の半導体層106上に半導体層を堆積して、第2の半導体層107を形成し、第2の半導体層107上に不純物半導体層109を形成し、不純物半導体層109上に導電層111を形成する。その後、導電層111上に第2のレジストマスク113を形成する(図1(B)を参照)。ここでは、第1の半導体層106を種結晶として、部分的に結晶成長させる条件で第2の半導体層107を形成する。なお、プラズマCVD装置の処理室内において、シリコンまたはゲルマニウムを含む堆積性気体と、水素と、窒素を含む気体とを混合し、グロー放電プラズマにより形成する。窒素を含む気体としては、アンモニア、窒素、フッ化窒素、塩化窒素等があるが、これに限定されず窒素を有する気体であればよい。

【0038】

このとき、シリコンまたはゲルマニウムを含む堆積性気体と、水素との流量比は、第1の半導体層106と同様に微結晶半導体層を形成する条件を用い、原料ガスに窒素を含む気体を用いることで、第1の半導体層106の成膜条件よりも、結晶成長を低減する条件とすることができます。なお、第2の半導体層107の成膜条件として、シリコンまたはゲルマニウムを含む堆積性気体と、水素との流量比を、通常の非晶質半導体層を形成する条件とし、かつ窒素を含む気体を用いても、第2の半導体層107において、微結晶半導体及び非晶質半導体を有する層107bを形成することが困難であるため、好ましくない。

【0039】

ここでは、微結晶半導体層を形成する条件の代表例は、シリコンまたはゲルマニウムを含む堆積性気体の流量に対する水素の流量が10~2000倍、好ましくは50~200倍である。なお、通常の非晶質半導体層を形成する条件の代表例は、シリコンまたはゲルマニウムを含む堆積性気体の流量に対する水素の流量は0~5倍である。

【0040】

また、第2の半導体層107の原料ガスに、ヘリウム、ネオン、アルゴン、キセノン、またはクリプトン等の希ガスを導入し、成膜速度を高めることができる。

【0041】

第2の半導体層107の堆積初期においては、第1の半導体層106を種結晶として、第1の半導体層106上全体的に微結晶半導体層が堆積される(堆積初期)。この後、部分的に、結晶成長が抑制され、錐形状の微結晶半導体領域が成長する(堆積中期)。さらに、錐形状の微結晶半導体領域の結晶成長が抑制され、非晶質半導体層が形成される(堆積後期)。

【0042】

このことから、図1(B)及び図2(A)に示す第2の半導体層107において、ゲート絶縁層105に接する微結晶半導体層107aが、第1の半導体層106、及び第2の半導体層107の堆積初期に形成される微結晶半導体層に相当する。

【0043】

また、図1(B)及び図2(A)に示す第2の半導体層107において、微結晶半導体及び非晶質半導体を有する層107bは、第2の半導体層107の堆積中期に形成される錐状の微結晶半導体領域108a、及びその間を充填する非晶質半導体層108bに相当する。

【0044】

また、図1(B)及び図2(A)に示す第2の半導体層107において、非晶質半導体層

10

20

30

40

50

107cは、第2の半導体層107の堆積後期に形成される非晶質半導体層に相当する。

【0045】

微結晶半導体層107aは、非晶質と結晶構造(単結晶、多結晶を含む)の中間的な構造の半導体で形成される。微結晶半導体は、自由エネルギー的に安定な第3の状態を有する半導体であって、短距離秩序を持ち格子歪みを有する結晶質な半導体であり、結晶粒径が2nm以上200nm以下、好ましくは10nm以上80nm以下、より好ましくは、20nm以上50nm以下の柱状結晶または錐形状結晶が基板表面に対して法線方向に成長している。このため、柱状結晶または錐形状結晶の界面には、結晶粒界が形成される場合もある。

【0046】

微結晶半導体の代表例である微結晶シリコンは、そのラマンスペクトルが単結晶シリコンを示す520cm<sup>-1</sup>よりも低波数側に、シフトしている。即ち、単結晶シリコンを示す520cm<sup>-1</sup>とアモルファスシリコンを示す480cm<sup>-1</sup>の間に微結晶シリコンのラマンスペクトルのピークがある。また、未結合手(ダンギングボンド)を終端するため水素またはハロゲンを少なくとも1原子%またはそれ以上含ませている。さらに、ヘリウム、アルゴン、クリプトン、またはネオンなどの希ガス元素を含ませて格子歪みをさらに助長させることで、安定性が増し良好な微結晶半導体が得られる。このような微結晶半導体に関する記述は、例えば、米国特許4,409,134号で開示されている。

【0047】

また、微結晶半導体層107aに含まれる酸素及び窒素の二次イオン質量分析法によって計測される濃度は、 $1 \times 10^{18}$  atoms/cm<sup>3</sup>未満とすることで、微結晶半導体層107aの結晶性を高めることができるため好ましい。

【0048】

非晶質半導体層107cは、窒素及び非晶質半導体を有する半導体層、またはNH基及び非晶質半導体を有する半導体層である。ここでの窒素及び非晶質半導体を有する半導体層、またはNH基及び非晶質半導体を有する半導体層の原料ガスの成膜条件として、シリコンまたはゲルマニウムを含む堆積性気体と、水素との流量比を、第1の半導体層106と同様に微結晶半導体層を形成する条件を用い、更に窒素を含む気体を用いることで、通常の窒素を有する非晶質半導体層やNH基を有する非晶質半導体層よりも、CPMや低温PL(フォトルミネッセンス)で測定すると、Urbach端のエネルギーが小さい。また、バンドギャップにおける準位のテール(裾)の傾きが急峻である。即ち、欠陥が少なく、通常の窒素を有する非晶質半導体層やNH基を有する非晶質半導体層より、秩序性が高く、結晶構造を有する。

【0049】

非晶質半導体層107cを、窒素及びアモルファスシリコンを有する半導体層、好ましくはNH基及びアモルファスシリコンを有する半導体層で形成すると、アモルファスシリコンのバンドギャップのバンドテールと比較して、傾斜が急峻となり、バンドギャップが広くなり、トンネル電流が流れにくくなる。この結果、薄膜トランジスタのオフ電流を低減することができる。また、後に形成される薄膜トランジスタのしきい値電圧のシフト量を低減することができる。

【0050】

図2(A)に示すように、微結晶半導体及び非晶質半導体を有する層107bは、微結晶半導体層107a及び非晶質半導体層107cの間に設けられる。また、微結晶半導体及び非晶質半導体を有する層107bは、微結晶半導体領域108a、及び当該微結晶半導体領域108aの間に充填される非晶質半導体層108bを有する。具体的には、微結晶半導体層107aから凸状に伸びた微結晶半導体領域108aと、非晶質半導体層107cと同様の非晶質半導体層108bとで形成される。

【0051】

非晶質半導体層107cを、電気伝導度が低く、抵抗率が高い、窒素を有する非晶質半導体層、またはNH基を有する非晶質半導体層で形成することで、薄膜トランジスタのオフ

10

20

30

40

50

電流を低減することができる。また、微結晶半導体及び非晶質半導体を有する層 107b において、錐形状の微結晶半導体領域 108a を有するため、ソース領域またはドレイン領域に電圧が印加されたときの、縦方向（膜厚方向）における抵抗、即ち、第 2 の半導体層 107 と、ソース領域またはドレイン領域との間の抵抗を下げることが可能であり、薄膜トランジスタのオン電流を高めることが可能である。

#### 【0052】

また、図 2 (B) に示すように、微結晶半導体及び非晶質半導体を有する層 107b は、微結晶半導体層 107a 及び不純物半導体層 109 の間に設けられ、微結晶半導体及び非晶質半導体を有する層 107b と不純物半導体層 109 との間に、非晶質半導体層 107c が形成されない構成となる場合がある。このような、図 2 (B) に示す構造においては、非晶質半導体層 108b に対する微結晶半導体領域 108a の割合が低いことが好ましい。この結果、薄膜トランジスタのオフ電流を低減することができる。また、微結晶半導体及び非晶質半導体を有する層 107b において、ソース領域またはドレイン領域に電圧が印加されたときの、縦方向（膜厚方向）における抵抗、即ち、第 2 の半導体層 107 と、ソース領域またはドレイン領域との間の抵抗を下げることが可能であり、薄膜トランジスタのオン電流を高めることが可能である。

#### 【0053】

微結晶半導体領域 108a は、ゲート絶縁層 105 から非晶質半導体層 107c へ向けて、先端が狭まる凸状の微結晶半導体である。なお、ゲート絶縁層 105 から非晶質半導体層 107c へ向けて幅が広がる凸の微結晶半導体であってもよい。

#### 【0054】

微結晶半導体及び非晶質半導体を有する層 107b においては、微結晶半導体領域 108a は、ゲート絶縁層 105 から非晶質半導体層 107c へ向けて、先端が狭まる凸状の結晶粒の場合は、微結晶半導体層 107a 側のほうが、非晶質半導体層 107c 側と比較して、微結晶半導体領域の割合が高い。これは、微結晶半導体層 107a の表面から、微結晶半導体領域 108a が膜厚方向に成長するが、原料ガスにおけるシランに対する水素の流量が少ないと、または窒素を含む原料ガスの濃度が高いと、微結晶半導体領域 108a の結晶粒の成長が抑制され、錐状の結晶粒となるとともに、やがて非晶質半導体層のみが堆積するためである。

#### 【0055】

また、微結晶半導体及び非晶質半導体を有する層 107b は、窒素、代表的には NH 基を有することが好ましい。これは、微結晶半導体領域 108a に含まれる結晶粒の界面、微結晶半導体領域 108a と非晶質半導体層 108b との界面において、窒素、代表的には NH 基が、シリコン原子のダングリングボンドと結合すると、欠陥が低減し、キャリアが流れやすくなるためである。このため、窒素、好ましくは NH 基を  $1 \times 10^{20} \text{ cm}^{-3}$  以上  $1 \times 10^{21} \text{ cm}^{-3}$  以下、好ましくは  $2 \times 10^{20} \text{ cm}^{-3}$  以上  $1 \times 10^{21} \text{ cm}^{-3}$  以下とすることで、シリコン原子のダングリングボンドを窒素、好ましくは NH 基で架橋しやすくなり、キャリアが流れやすくなる。この結果、結晶粒界や欠陥におけるキャリアの移動を促進する結合ができる、微結晶半導体及び非晶質半導体を有する層 107b の移動度が上昇することがわかる。即ち、薄膜トランジスタの電界効果移動度が上昇する。

#### 【0056】

また、微結晶半導体及び非晶質半導体を有する層 107b の酸素濃度を低減することにより、結晶粒と非晶質半導体層との界面や、結晶粒同士の界面における、キャリアの移動を阻害する結合を低減することができる。

#### 【0057】

なお、ここでは、微結晶半導体層 107a は、概略厚さが等しい領域をいう。また、微結晶半導体層 107a と微結晶半導体及び非晶質半導体を有する層 107b との界面は、微結晶半導体領域 108a と非晶質半導体層 108b との界面における平坦部において、ゲート絶縁層 105 に最も近い領域を延長した領域をいう。

#### 【0058】

10

20

30

40

50

微結晶半導体層 107a 及び微結晶半導体及び非晶質半導体を有する層 107b の厚さの合計、即ち、ゲート絶縁層 105 の界面から、微結晶半導体及び非晶質半導体を有する層 107b の凸部の先端の距離は、3 nm 以上 80 nm 以下、好ましくは 5 nm 以上 30 nm 以下とすることで、TFT のオフ電流を低減できる。

【0059】

また、第 2 の半導体層 107 の原料ガスとして、シリコンまたはゲルマニウムを含む堆積性気体と、水素と共に、窒素を含む気体を用いることで、微結晶半導体及び非晶質半導体を有する層 107b、及び非晶質半導体層 107c の結晶性と非晶質性を制御することが可能であり、この結果、薄膜トランジスタのしきい値電圧のシフト量を低減することが可能である。

10

【0060】

なお、第 2 の半導体層 107 の原料ガスに、ヘリウム、ネオン、アルゴン、キセノン、またはクリプトン等の希ガスを導入する場合は、第 2 の半導体層 107 の結晶性が上昇してしまい、薄膜トランジスタのオフ電流が高くなるため、シリコンまたはゲルマニウムを含む堆積性気体と、水素と、窒素を含む気体との混合比を制御することが好ましい。代表的には、非晶質性を高める条件である水素に対するシリコンまたはゲルマニウムを含む堆積性気体を増やす条件とすることで、微結晶半導体及び非晶質半導体を有する層 107b、及び非晶質半導体層 107c の結晶性と非晶質性を制御することが可能である。

【0061】

不純物半導体層 109 は、プラズマ CVD 装置の処理室内において、シリコンまたはゲルマニウムを含む堆積性気体と、水素と、フォスフィン（水素希釈またはシラン希釈）とを混合し、グロー放電プラズマにより形成する。シリコンまたはゲルマニウムを含む堆積性気体を水素で希釈して、リンが添加されたアモルファスシリコン、リンが添加された微結晶シリコン、リンが添加されたアモルファスシリコンゲルマニウム、リンが添加された微結晶シリコンゲルマニウム、リンが添加されたアモルファスゲルマニウム、リンが添加された微結晶ゲルマニウム等を形成する。

20

【0062】

また、不純物半導体層 109 の原料ガスに、ヘリウム、ネオン、アルゴン、キセノン、またはクリプトン等の希ガスを導入し、成膜速度を高めることができる。

【0063】

30

なお、第 2 の半導体層 107 と、後に形成されるソース電極及びドレイン電極 125 とがオーミックコンタクトをする場合は、不純物半導体層 109 を形成しなくともよい。

【0064】

ゲート絶縁層 105 の形成から不純物半導体層の形成までについて、図 3 に示すタイムチャートを参照して以下に説明する。なお、ゲート絶縁層 105 は、窒化シリコン層上に酸化窒化シリコン層を積層して形成する。

【0065】

まず、ゲート電極 103 が形成された基板を、実施の形態 2 に示す CVD 装置の処理室 241 内にて加熱しつつ、窒化シリコン層の堆積に用いる材料ガスを処理室 241 内に導入する（図 3 の予備処理 201）。ここでは、一例として、SiH<sub>4</sub> の流量を 40 sccm、H<sub>2</sub> の流量を 500 sccm、N<sub>2</sub> の流量を 550 sccm、NH<sub>3</sub> の流量を 140 sccm として材料ガスを導入して安定させ、処理室内の圧力を 100 Pa、基板の温度を 280 とし、370 W の出力によりプラズマ放電を行うことで、約 110 nm の窒化シリコン層を形成する。その後、SiH<sub>4</sub> の供給のみを停止して数秒後にプラズマの放電を停止させる（図 3 の SiN 形成 203）。これは、処理室内に SiH<sub>4</sub> が存在する状態でプラズマの放電を停止させると、シリコンを主成分とする粒状物又は粉状物が形成され、歩留まりを低下させる原因となるためである。

40

【0066】

次に、窒化シリコン層の堆積に用いた材料ガスを排気し、酸化窒化シリコン層の堆積に用いる材料ガスを処理室 241 内に導入する（図 3 のガス置換 205）。ここでは、一例と

50

して、 $\text{SiH}_4$  の流量を 30 sccm、 $\text{N}_2\text{O}$  の流量を 1200 sccm とし、材料ガスを導入して安定させ、処理室内の圧力を 40 Pa、基板の温度を 280 としして 50 W の出力によりプラズマ放電を行うことで、約 110 nm の酸化窒化シリコン層を形成する。その後、窒化シリコン層と同様に、 $\text{SiH}_4$  の供給のみを停止し、その数秒後にプラズマの放電を停止させる（図 3 の SiON 形成 207）。

#### 【0067】

上記の工程により、ゲート絶縁層 105 を形成することができる。ゲート絶縁層 105 の形成後、基板 101 を処理室 241 から搬出する（図 3 の unload 225）。

#### 【0068】

基板 101 を処理室 241 から搬出した後、処理室 241 に、例えば  $\text{NF}_3$  ガスを導入し、処理室 241 内をクリーニングする（図 3 のクリーニング処理 227）。その後、処理室 241 に非晶質シリコン層を形成する処理を行う（図 3 のプレコート処理 229）。この処理により、処理室 241 の内壁に非晶質シリコン層が形成される。その後、基板 101 を処理室 241 内に搬入する（図 3 の load 231）。

10

#### 【0069】

次に、第 1 の半導体層 106 の堆積に用いる材料ガスを処理室 241 内に導入する（図 3 のガス置換 209）。次に、ゲート絶縁層 105 上の全面に第 1 の半導体層 106 を形成する。ここでは、一例として、 $\text{SiH}_4$  の流量を 10 sccm、 $\text{H}_2$  の流量を 1500 sccm、Ar の流量を 1500 sccm として材料ガスを導入して安定させ、処理室内の圧力を 280 Pa、基板の温度を 280 とし、50 W の出力によりプラズマ放電を行うことで、第 1 の半導体層 106 として、約 5 nm の微結晶シリコン層を形成することができる。その後、上記した窒化シリコン層等の形成と同様に、 $\text{SiH}_4$  の供給のみを停止し、その数秒後にプラズマの放電を停止させる（図 3 の第 1 の半導体層形成 211）。

20

#### 【0070】

次に、第 1 の半導体層 106 の表面に窒素を供給する。ここでは、第 1 の半導体層 106 の表面をアンモニアに曝すことで窒素を供給する（ここでは、フラッシュ処理という。）（図 3 のフラッシュ処理 213）。また、アンモニアには水素を含ませてもよい。または、アンモニアの代わりに窒素ガスを処理室 241 に導入してもよい。または、アンモニアと窒素ガスを処理室 241 に導入してもよい。ここでは、一例として、処理室 241 内の圧力は概ね 20 Pa ~ 30 Pa、基板の温度は 280 とし、処理時間は 60 秒間とする。なお、本工程の処理では基板 101 をアンモニアに曝すのみであるが、プラズマ処理を行ってもよい。その後、これらのガスを排気し、第 2 の半導体層 107 の堆積に用いるガスを導入する（図 3 のガス置換 215）。

30

#### 【0071】

次に、第 2 の半導体層 107 を形成する。ここで、第 2 の半導体層 107 は、窒素を有する非晶質半導体層を用いて形成する。ここでは、一例として、 $\text{SiH}_4$  の流量を 30 sccm、 $\text{H}_2$  の流量を 1425 sccm、1000 ppm のアンモニア（水素希釈）の流量を 25 sccm として材料ガスを導入して安定させ、処理室内の圧力を 280 Pa、基板の温度を 280 とし、RF 電源周波数 13.56 MHz、RF 電源の電力 50 W の出力によりプラズマ放電を行うことで、約 150 nm の第 2 の半導体層 107、ここでは微結晶半導体層 107a として微結晶シリコン層、微結晶半導体及び非晶質半導体を有する層 107b として、微結晶シリコン及び NH 基を有するアモルファスシリコンを有する層、非晶質半導体層 107c として窒素を有するアモルファスシリコン層を形成することができる。なお、微結晶半導体及び非晶質半導体を有する層 107b の微結晶シリコンに窒素を有してもよい。

40

#### 【0072】

第 2 の半導体層 107 の形成工程において、フラッシュ処理により処理室内に導入されたアンモニアがプラズマ放電により分解され、NH 基が生成される。また、第 2 の半導体層 107 が堆積される際に、ダンギングボンドを架橋することができる。なお、処理室に窒素を有するガスとして、窒素ガスを導入した場合は、プラズマ放電により、当該窒素ガ

50

スと、第2の半導体層107の原料ガスである、水素ガスとが反応し、NH基を生成する。また、当該NH基が第2の半導体層107の異なるダングリングボンドを架橋する。

【0073】

その後、上記した窒化シリコン層等の形成と同様に、SiH<sub>4</sub>の供給のみを停止し、その数秒後にプラズマの放電を停止させる(図3の第2の半導体層形成217)。その後、これらのガスを排気し、不純物半導体層109の堆積に用いるガスを導入する(図3のガス置換219)。

【0074】

本実施の形態における第2の半導体層107を形成する処理室には、窒素を有するガスが供給されている。窒素を有するガスは、プラズマ放電により、NH基が形成される。また、上記したように、NH基は第2の半導体層107に含まれるダングリングボンドを架橋する。このため、窒素を有するガスを供給した処理室において、ダングリングボンドを架橋したNH基を有する非晶質半導体層107cを形成することができる。

【0075】

このような方法により形成した第2の半導体層107において、二次イオン質量分析法によって計測される窒素濃度は、微結晶半導体層107aと、微結晶半導体及び非晶質半導体を有する層107bとの界面でピーク濃度を有し、微結晶半導体及び非晶質半導体を有する層107b及び非晶質半導体層107cの堆積方向に対して減少する濃度となる。

【0076】

なお、図3の破線235aに示すように、第2の半導体層形成217において、アンモニアを処理室内に流してもよい。または、アンモニアの代わりに、破線235bに示すように窒素ガスを流してもよい。または、アンモニア及び窒素ガスを流しても良い。この結果、第2の半導体層107の窒素濃度が高まり、第2の半導体層107に含まれるダングリングボンドが架橋され、欠陥準位が低減する。

【0077】

このような方法により形成した第2の半導体層107において、二次イオン質量分析法によって計測される窒素濃度は、微結晶半導体層107a、または微結晶半導体層107aと、微結晶半導体及び非晶質半導体を有する層107bとの界面でピーク濃度を有し、微結晶半導体及び非晶質半導体を有する層107b及び非晶質半導体層107cの堆積方向に対して一定な濃度となる。

【0078】

また、第2の半導体層形成217において、破線236で示すように、原料ガスとして希ガスを用いてもよい。この結果、第2の半導体層107の成長速度を速めることが可能である。

【0079】

次に、第2の半導体層107上の全面に不純物半導体層109を形成する。不純物半導体層109は、後の工程でパターン形成されてソース領域及びドレイン領域127となるものである。まず、不純物半導体層109の堆積に用いる材料ガスを処理室241内に導入する。ここでは、一例として、SiH<sub>4</sub>の流量を100sccm、PH<sub>3</sub>をH<sub>2</sub>により0.5vol%まで希釈した混合ガスの流量を170sccmとして材料ガスを導入して安定させる。処理室241内の圧力を280Pa、基板の温度を280とし、60Wの出力によりプラズマ放電を行うことで、約50nmのリンを含むアモルファスシリコン層を形成することができる。その後、上記した窒化シリコン層等の形成と同様に、SiH<sub>4</sub>の供給のみを停止し、その数秒後にプラズマの放電を停止させる(図3の不純物半導体層形成221)。その後、これらのガスを排気する(図3の排気223)。

【0080】

以上説明したように、不純物半導体層109までを形成することができる。

【0081】

導電層111は、アルミニウム、銅、チタン、ネオジム、スカンジウム、モリブデン、クロム、タンタル若しくはタンクステン等により単層で、又は積層して形成することができ

10

20

30

40

50

る。または、ヒロック防止元素が添加されたアルミニウム合金（代表的には、ゲート電極 103 に用いることができるアルミニウム・ネオジム合金等）により形成してもよい。また、ドナーとなる不純物元素を添加した結晶性シリコンを用いてもよい。ドナーとなる不純物元素が添加された結晶性シリコンと接する側の層を、チタン、タンタル、モリブデン、タンゲステン又はこれらの元素の窒化物により形成し、その上にアルミニウム又はアルミニウム合金を形成した積層構造としても良い。更には、アルミニウム又はアルミニウム合金の上面及び下面を、チタン、タンタル、モリブデン、タンゲステン又はこれらの元素の窒化物で挟んだ積層構造としてもよい。例えば、導電層 111 として、アルミニウム層を窒化チタン層で挟んだ層の積層構造とするとよい。

## 【0082】

10

導電層 111 は、CVD 法、スパッタリング法または真空蒸着法を用いて形成する。また、導電層 111 は、銀、金または銅等の導電性ナノペーストを用いてスクリーン印刷法またはインクジェット法等を用いて吐出し、焼成することで形成しても良い。

## 【0083】

第 2 のレジストマスク 113 は厚さの異なる領域を有する。このようなレジストマスクは、多階調マスクを用いて形成することができる。多階調マスクを用いることで、使用するフォトマスクの枚数が低減され、作製工程数が減少するため好ましい。本実施の形態において、第 2 の半導体層 107 のパターンを形成する工程と、ソース領域とドレイン領域を分離する工程において、多階調マスクを用いることができる。

## 【0084】

20

多階調マスクとは、多段階の光量で露光を行うことが可能なマスクであり、代表的には、露光領域、半露光領域及び未露光領域の 3 段階の光量で露光を行う。多階調マスクを用いることで、一度の露光及び現像工程によって、複数（代表的には二種類）の厚さを有するレジストマスクを形成することができる。そのため、多階調マスクを用いることで、フォトマスクの枚数を削減することができる。

## 【0085】

図 4 (A - 1) 及び図 4 (B - 1) は、代表的な多階調マスクの断面図を示す。図 4 (A - 1) にはグレートーンマスク 180 を示し、図 4 (B - 1) にはハーフトーンマスク 185 を示す。

## 【0086】

30

図 4 (A - 1) に示すグレートーンマスク 180 は、透光性を有する基板 181 上に遮光層により形成された遮光部 182、及び遮光層のパターンが設けられた回折格子部 183 で構成されている。

## 【0087】

回折格子部 183 は、露光に用いる光の解像度限界以下の間隔で設けられたスリット、ドットまたはメッシュ等を有することで、光の透過率を制御する。なお、回折格子部 183 に設けられるスリット、ドットまたはメッシュは周期的なものであってもよいし、非周期的なものであってもよい。

## 【0088】

透光性を有する基板 181 としては、石英等を用いることができる。遮光部 182 及び回折格子部 183 を構成する遮光層は、金属を用いて形成すればよく、好ましくはクロムまたは酸化クロム等により設けられる。

40

## 【0089】

グレートーンマスク 180 に露光するための光を照射した場合、図 4 (A - 2) に示すように、遮光部 182 に重畳する領域における透光率は 0 % となり、遮光部 182 または回折格子部 183 が設けられていない領域における透光率は 100 % となる。また、回折格子部 183 における透光率は、概ね 10 ~ 70 % の範囲であり、回折格子のスリット、ドットまたはメッシュの間隔等により調整可能である。

## 【0090】

図 4 (B - 1) に示すハーフトーンマスク 185 は、透光性を有する基板 186 上に半透

50

光層により形成された半透光部 187、及び遮光層により形成された遮光部 188 で構成されている。

【0091】

半透光部 187 は、MoSiN、MoSi、MoSiO、MoSiON、CrSi 等の層を用いて形成することができる。遮光部 188 は、グレートーンマスクの遮光層と同様の金属を用いて形成すればよく、好ましくはクロムまたは酸化クロム等により設けられる。

【0092】

ハーフトーンマスク 185 に露光するための光を照射した場合、図 4 (B-2) に示すように、遮光部 188 に重畳する領域における透光率は 0 % となり、遮光部 188 または半透光部 187 が設けられていない領域における透光率は 100 % となる。また、半透光部 187 における透光率は、概ね 10 ~ 70 % の範囲であり、形成する材料の種類または形成する膜厚等により、調整可能である。

10

【0093】

多階調マスクを用いて露光して現像を行うことで、厚さの異なる領域を有するレジストマスクを形成することができる。

【0094】

次に、第 2 のレジストマスク 113 を用いて、第 2 の半導体層 107、不純物半導体層 109、及び導電層 111 をエッチングする。この工程により、第 2 の半導体層 107、不純物半導体層 109 及び導電層 111 を素子毎に分離し、第 2 の半導体層 115、不純物半導体層 117、及び導電層 119 を形成する。なお、第 2 の半導体層 115 は、微結晶半導体層 115a、微結晶半導体及び非晶質半導体を有する層 115b、及び非晶質半導体層 115c を有する (図 1 (C) を参照)。

20

【0095】

次に、第 2 のレジストマスク 113 を後退させて、分離された第 3 のレジストマスク 123 を形成する。レジストマスクの後退には、酸素プラズマによるアッシングを用いればよい。ここでは、ゲート電極上で分離するように第 2 のレジストマスク 113 をアッシングすることで、第 3 のレジストマスク 123 を形成することができる (図 5 (A) 参照)。

【0096】

次に、第 3 のレジストマスク 123 を用いて導電層 119 をエッチングし、ソース電極及びドレイン電極 125 を形成する (図 5 (B) を参照)。導電層 119 のエッチングは、ウエットエッチングを用いることが好ましい。ウエットエッチングにより、導電層が等方的にエッチングされる。その結果、導電層は第 3 のレジストマスク 123 よりも内側に後退し、ソース電極及びドレイン電極 125 が形成される。ソース電極またはドレイン電極 125 は、ソース電極またはドレイン電極のみならず信号線としても機能する。ただし、これに限定されず、信号線とソース電極及びドレイン電極とは別に設けてもよい。

30

【0097】

次に、第 3 のレジストマスク 123 を用いて、非晶質半導体層 115c、及び不純物半導体層 117 のそれぞれ一部をエッチングする。ここでは、ドライエッチングを用いる。本工程までで、表面に凹部を有する非晶質半導体層 129c、ソース領域及びドレイン領域 127 を形成する (図 5 (C) 参照)。この後、第 3 のレジストマスク 123 を除去する。

40

【0098】

なお、ここでは、導電層 119 をウエットエッチングし、非晶質半導体層 115c、及び不純物半導体層 117 のそれぞれ一部をドライエッチングしたため、導電層 119 が等方的にエッチングされ、ソース電極及びドレイン電極 125 の側面と、ソース領域及びドレイン領域 127 の側面は一致せず、ソース電極及びドレイン電極 125 の側面の外側に、ソース領域及びドレイン領域 127 の側面が形成される形状となる。

【0099】

また、第 3 のレジストマスク 123 を除去した後、不純物半導体層 117 及び非晶質半導体層 115c の一部をエッチングしてもよい。当該エッチングより、ソース電極及びドレ

50

イン電極 125 を用いて不純物半導体層 117 をエッティングするため、ソース電極及びソース領域のそれぞれ端部が概略一致する。また、ドレイン電極及びドレイン領域のそれぞれ端部が概略一致する。

【0100】

次に、第3のレジストマスク 123 を除去した後、ドライエッティングを行ってもよい。ドライエッティングの条件は、露出している非晶質半導体層 129c にダメージが入らず、且つ非晶質半導体層 129c に対するエッティングレートが低い条件を用いる。つまり、露出している非晶質半導体層 129c 表面にほとんどダメージを与えず、且つ露出している非晶質半導体層 129c の厚さがほとんど減少しない条件を用いる。エッティングガスとしては、Cl<sub>2</sub> に代表される塩素系ガス、CF<sub>4</sub>、N<sub>2</sub> 等を用いる。また、エッティング方法については特に限定はなく、誘導結合型プラズマ (ICP: Inductively Coupled Plasma) 方式、容量結合型プラズマ (CCP: Capacitively Coupled Plasma) 方式、電子サイクロotron 共鳴プラズマ (ECR: Electron Cyclotron Resonance) 方式、反応性イオンエッティング (RIE: Reactive Ion Etching) 方式等を用いることができる。

10

【0101】

次に、非晶質半導体層 129c の表面に水プラズマ、アンモニアプラズマ、窒素プラズマ等を照射してもよい。

【0102】

20

水プラズマ処理は、反応空間に水蒸気 (H<sub>2</sub>O 蒸気) に代表される、水を主成分とするガスを導入し、プラズマを生成して、行うことができる。

【0103】

上記したように、ソース領域及びドレイン領域 127 を形成した後に、非晶質半導体層 129c にダメージを与えない条件で更なるドライエッティングを行うことで、露出した非晶質半導体層 129c 上に存在する残渣などの不純物を除去することができる。また、ドライエッティングに続けて水プラズマ処理を行うことで、レジストマスクの残渣を除去することができる。水プラズマ処理を行うことで、ソース領域とドレイン領域との間の絶縁を確実なものにすることことができ、完成する薄膜トランジスタのオフ電流を低減し、電気的特性のばらつきを低減することができる。

30

【0104】

以上の工程により、少ないマスク数で、オフ電流が低く、オン電流が高く、しきい値電圧が制御された薄膜トランジスタを生産性高く作製することができる。

【0105】

(実施の形態 2)

本実施の形態では、ゲート絶縁層 105、第1の半導体層 106、第2の半導体層 107、及び不純物半導体層 109 の形成に用いることが可能なプラズマ CVD 装置の一形態について詳細に説明する。これらの層は CVD 法等を用いて形成する。

【0106】

図 6 に示すプラズマ CVD 装置 261 は、ガス供給手段 250 及び排気手段 251 に接続されている。

40

【0107】

図 6 に示すプラズマ CVD 装置 261 は、処理室 241 と、ステージ 242 と、ガス供給部 243 と、シャワープレート 244 と、排気口 245 と、上部電極 246 と、下部電極 247 と、交流電源 248 と、温度制御部 249 と、を具備する。

【0108】

処理室 241 は剛性のある素材で形成され、内部を真空排気できるように構成されている。処理室 241 には、上部電極 246 と下部電極 247 が備えられている。なお、図 6 では、容量結合型 (平行平板型) の構成を示しているが、異なる二以上の高周波電力を印加して処理室 241 の内部にプラズマを生成できるものであれば、誘導結合型など他の構成

50

を適用してもよい。

【0109】

図6に示すプラズマCVD装置により処理を行う際には、所定のガスをガス供給部243から供給する。供給されたガスは、シャワープレート244を通って、処理室241に導入される。上部電極246と下部電極247に接続された交流電源248により、高周波電力が印加されて処理室241内のガスが励起され、プラズマが生成される。また、真空ポンプに接続された排気口245によって、処理室241内のガスが排気されている。また、温度制御部249によって、被処理物を加熱しながらプラズマ処理することができる。

【0110】

ガス供給手段250は、反応ガスが充填されるシリンド252、圧力調整弁253、ストップバルブ254、マスフローコントローラ255などで構成されている。処理室241内において、上部電極246と基板101との間には板状に加工され、複数の細孔が設けられたシャワープレートを有する。上部電極246に供給される反応ガスは、中空構造である上部電極246の内部の細孔から処理室241内に供給される。

【0111】

処理室241に接続される排気手段251は、真空排気と、反応ガスを流す場合において処理室241内を所定の圧力に保持するように制御する機能が含まれている。排気手段251の構成としては、バタフライバルブ256、コンダクタンスバルブ257、ターボ分子ポンプ258、ドライポンプ259などが含まれる。バタフライバルブ256とコンダクタンスバルブ257を並列に配置する場合には、バタフライバルブ256を閉じてコンダクタンスバルブ257を動作させることで、反応ガスの排気速度を制御して処理室241の圧力を所定の範囲に保つことができる。また、コンダクタンスの大きいバタフライバルブ256を開くことで高真空排気が可能となる。

【0112】

なお、処理室241を $10^{-5}$ Paよりも低い圧力まで超高真空排気する場合には、クライオポンプ260を併用することが好ましい。その他、到達真空度として超高真空まで排気する場合には、処理室241の内壁を鏡面加工し、内壁からのガス放出を低減するためにベーキング用のヒータを設けても良い。

【0113】

なお、図6に示すように、処理室241の全体を覆って膜が形成（被着）されるようにプレコート処理を行うと、処理室（チャンバー）内壁に付着した不純物元素、または処理室（チャンバー）内壁を構成する不純物元素が素子に混入することを防止することができる。本実施の形態では、プレコート処理はシリコンを主成分とする層を形成すればよく、例えば、非晶質シリコン膜等を形成すればよい。ただし、この膜には酸素が含まれないことが好ましい。

【0114】

（実施の形態3）

本実施の形態では、実施の形態1に適用可能な第2の半導体層107の形成工程について説明する。

【0115】

本実施の形態では、第2の半導体層107の形成前に処理室内をクリーニングし、その後チャンバー内壁を窒化シリコン層で覆うことで、第2の半導体層107に窒素を含ませて、酸素濃度を低く抑え、窒素濃度を酸素濃度よりも高くする。ゲート絶縁層105の形成から第1の半導体層106の形成方法は実施の形態1と同様であるため、ここでは、第2の半導体層107から不純物半導体層109の形成までについて、図7を参照して以下に説明する。

【0116】

ゲート絶縁層105上の全面に第1の半導体層106を形成する。まず、第1の半導体層106の堆積に用いる材料ガスを処理室内に導入する。ここでは、一例として、実施の形

10

20

30

40

50

態1と同様の方法により、第1の半導体層106として約5nmの微結晶シリコン層を形成する。その後、プラズマの放電を停止させる(図7の第1の半導体層形成211)。その後、基板101を処理室241から搬出する(図7のunload225)。

【0117】

基板101を処理室241から搬出した後、処理室241に、例えばNF<sub>3</sub>ガスを導入し、処理室241内をクリーニングする(図7のクリーニング処理227)。その後、処理室241内に窒化シリコン層を形成する処理を行う(図7のプレコート処理233)。窒化シリコン層としては、実施の形態1のゲート絶縁層で形成した窒化シリコン層と同様の条件を用いる。この処理により、処理室241の内壁に窒化シリコン層が形成される。その後、基板101を処理室241内に搬入する(図7のload231)。

10

【0118】

なお、クリーニング処理227は行わなくてもよい。この結果、スループットを向上させることができる。

【0119】

次に、第2の半導体層107の堆積に用いる材料ガスを処理室241内に導入する(図7のガス置換215)。次に、第2の半導体層107を形成する。ここでは、実施の形態1と同様に、厚さ150nmの第2の半導体層107を形成する。具体的には、微結晶半導体層107aとして微結晶シリコン層、微結晶半導体及び非晶質半導体を有する層107bとして、微結晶シリコン及びアモルファスシリコンを有する層、非晶質半導体層107cとして窒素およびアモルファスシリコンを有する半導体層を形成することができる。その後、プラズマの放電を停止させる(図7の第2の半導体層形成217)。

20

【0120】

なお、図7の破線237aに示すように、第2の半導体層形成217において、アンモニアを処理室内に流してもよい。または、アンモニアの代わりに、破線237bに示すように窒素ガスを流してもよい。または、アンモニア及び窒素ガスを流しても良い。この結果、第2の半導体層107の窒素濃度が高まり、第2の半導体層107のダングリングボンドが架橋され、欠陥準位が低減する。

【0121】

このような方法により形成した第2の半導体層107において、二次イオン質量分析法によって計測される窒素濃度は、微結晶半導体層107aの上方、または微結晶半導体層107aと、微結晶半導体及び非晶質半導体を有する層107bとの界面で、ピーク濃度を有し、第2の半導体層107の堆積方向に対して一定な濃度となる。

30

【0122】

また、第2の半導体層形成217において、破線238で示すように、原料ガスとして希ガスを用いてもよい。この結果、第2の半導体層107の成長速度を速めることが可能である。

【0123】

その後、これらのガスを排気し、不純物半導体層109の堆積に用いるガスを導入する(図7のガス置換219)。また、実施の形態1と同様に、不純物半導体層109を形成する(図7の不純物半導体層形成221)。その後、不純物半導体層109の原料ガスを排気する(図7の排気223)。

40

【0124】

当該工程において、処理室内にプレコート処理において導入されたアンモニアがプラズマ放電により解離しNH基となる。また、プラズマ放電により、当該窒素ガスと、非晶質半導体層の原料ガスである、水素ガスとが反応しNH基を生成する。また、処理室内の内壁に形成された窒化シリコン層がプラズマに曝されることにより、窒化シリコンの一部が解離しNH基が生成される。

【0125】

本実施の形態において、第2の半導体層107を形成する処理室には、窒素を有するガスが供給され、更にはNH基が生成される。上記したように、NH基はアモルファスシリコ

50

ン層に含まれるダングリングボンドを架橋する。このため、窒素を有するガスを供給した処理室において、第2の半導体層107を形成することで、ダングリングボンドを架橋したNH基を有する非晶質半導体層を形成することができる。

【0126】

さらに、第2の半導体層を形成する直前に処理室の内壁を窒化シリコン層により覆うことで、酸素濃度を低く抑え、窒素濃度を酸素濃度よりも高くすることができる、NH基を有する非晶質半導体層を形成することができる。

【0127】

また、処理室の内壁を窒化シリコン層で覆うことで、処理室の内壁を構成する元素等が第2の半導体層107に混入することをも防ぐことができる。

10

【0128】

なお、上記の説明では、第1の半導体層106を形成した処理室と同様の処理室で第2の半導体層107を形成したため、第1の半導体層106の形成後にクリーニング処理とプレコート処理を行う形態について説明したが、本実施の形態は、実施の形態1と組み合わせて実施してもよい。すなわち、第1の半導体層106を堆積した後、処理室241内に窒化シリコン層を形成し、更にフラッシュ処理213してもよい。

【0129】

以上の工程により、オフ電流が低く、オン電流が高く、しきい値電圧が制御された薄膜トランジスタを生産性高く作製することができる。

【0130】

20

(実施の形態4)

本実施の形態では、実施の形態1に適用可能な第2の半導体層107の形成工程について説明する。

【0131】

本実施の形態では、第2の半導体層107の堆積ガスに、窒素を混入させることで、酸素濃度を低く抑え、窒素濃度を酸素濃度よりも高くする。ゲート絶縁層105の形成から第1の半導体層106の形成方法は、実施の形態1と同様であるため、ここでは、第1の半導体層106から不純物半導体層109の形成までについて、図8を参照して以下に説明する。

【0132】

30

ゲート絶縁層105上の全面に第1の半導体層106を形成する。まず、第1の半導体層106の堆積に用いる材料ガスを処理室内に導入する。ここでは、一例として、実施の形態1と同様の方法により、第1の半導体層106として約5nmの微結晶シリコン層を形成する。その後、プラズマの放電を停止させる(図8の第1の半導体層形成211)。その後、これらのガスを排気し、第2の半導体層107の堆積に用いるガスを導入する(図8のガス置換215)。

【0133】

次に、第2の半導体層107を形成する。ここでは、一例として、SiH<sub>4</sub>の流量を30sccm、H<sub>2</sub>の流量を1425sccm、1000ppmのNH<sub>3</sub>(水素希釈)の流量を25sccmとして材料ガスを導入して安定させ、処理室内の圧力を280Pa、基板の温度を280とし、RF電源周波数13.56MHz、RF電源の電力50Wの出力によりプラズマ放電を行い、約150nmの第2の半導体層を形成する。具体的には、微結晶半導体層107a、微結晶半導体及び非晶質半導体を有する層107b、及び非晶質半導体層107cを形成する。当該工程において、アンモニアがプラズマ放電により解離しNH基を生成する。さらには、第2の半導体層が堆積される際に、ダングリングボンドを架橋することができる。(図8の第2の半導体層形成217)。

40

【0134】

なお、処理室に窒素を有するガスとして、アンモニアの代わりに、破線232に示すように窒素ガスを流してもよい。または、アンモニア及び窒素ガスを流しても良い。この結果、第2の半導体層107の窒素濃度が高まり、第2の半導体層107のダングリングボン

50

ドが架橋され、欠陥準位が低減する。

【0135】

このような方法により形成した第2の半導体層107において、二次イオン質量分析法によって計測される窒素濃度は、微結晶半導体層107aの上方、または微結晶半導体層107aと、微結晶半導体及び非晶質半導体を有する層107bとの界面から、不純物半導体層の界面まで一定の濃度を示す。

【0136】

また、第2の半導体層形成217において、破線234で示すように、原料ガスとして希ガスを用いてもよい。この結果、第2の半導体層107の成長速度を速めることが可能である。

10

【0137】

その後、これらのガスを排気し、不純物半導体層109の堆積に用いるガスを導入する(図8のガス置換219)。また、実施の形態1と同様に、不純物半導体層109を形成する(図8の不純物半導体層形成221)。その後、不純物半導体層109の原料ガスを排気する(図8の排気223)。

【0138】

本実施の形態における第2の半導体層107の堆積ガスには窒素を有するガスが含まれている。窒素を有するガスは、プラズマ放電により、NH基が形成される。上記したように、NH基は第2の半導体層107に含まれるダングリングボンドを架橋する。このため、ダングリングボンドを架橋したNH基を有する非晶質半導体層を形成することができる。その後、不純物半導体層109の原料ガスを排気する(図8の排気223)。

20

【0139】

以上の工程により、オフ電流が低く、オン電流が高く、しきい値電圧が制御された薄膜トランジスタを生産性高く作製することができる。

【0140】

(実施の形態5)

実施の形態1において、第2の半導体層107の作製方法について、図9を用いて示す。

【0141】

本実施の形態では、第2の半導体層107を形成する方法として、実施の形態1において、第1の半導体層形成211処理の後、フラッシュ処理213で窒素を有するガスを処理室内に導入すると共に、第2の半導体層107を形成している途中で(即ち、第2の半導体層形成217において)、実線239aで示すように窒素を有するガスを再度処理室内に導入する(図9参照)。窒素を有するガスとして、ここではアンモニアを用いる。なお、アンモニアの代わりに窒素ガスを用いてもよい。または、アンモニア及び窒素ガスを用いてもよい。この結果、第2の半導体層107の堆積初期及び堆積途中において、窒素濃度が高くなり欠陥準位を低減することができる。

30

【0142】

または、第2の半導体層107に、窒素、更にはNH基を添加する方法として、実施の形態3において、第1の半導体層106を形成した後、処理室内に窒化シリコン層を形成すると共に、第2の半導体層107を形成している途中で、窒素を有するガスを再度処理室内に導入してもよい。窒素を有するガスとして、ここではアンモニアを用いる。なお、アンモニアの代わりに窒素ガスを用いてもよい。または、アンモニア及び窒素ガスを用いてもよい。この結果、第2の半導体層107の堆積初期及び堆積途中において、窒素濃度が高くなり欠陥準位を低減することができる。その後、不純物半導体層109の原料ガスを排気する(図9の排気223)。

40

【0143】

以上の工程により、オフ電流が低く、オン電流が高く、しきい値電圧が制御された薄膜トランジスタを生産性高く作製することができる。

【0144】

(実施の形態6)

50

実施の形態 1 とは異なる薄膜トランジスタの作製方法について、図 10 及び図 11 を用いて示す。

【 0145 】

実施の形態 1 と同様に、基板 101 上にゲート電極 103 を形成する。次に、ゲート電極 103 を覆ってゲート絶縁層 105、第 1 の半導体層を形成する。次に、実施の形態 1 と同様に、第 1 の半導体層から結晶成長させて、第 2 の半導体層 107（微結晶半導体層 107a、微結晶半導体及び非晶質半導体を有する層 107b、非晶質半導体層 107c）を形成する。次に、第 2 の半導体層 107 上に不純物半導体層 109 を形成する。その後、不純物半導体層 109 上にレジストマスク（図示せず）を形成する（図 10（A）を参照）。

10

【 0146 】

次に、レジストマスクを用いて、第 2 の半導体層 107 及び不純物半導体層 109 をエッチングする。この工程により、第 2 の半導体層 107 及び不純物半導体層 109 を素子毎に分離し、第 2 の半導体層 115（微結晶半導体層 115a、微結晶半導体及び非晶質半導体を有する層 115b、非晶質半導体層 115c）、及び不純物半導体層 117 を形成する（図 10（B）を参照）。

【 0147 】

次に、ゲート絶縁層 105、第 2 の半導体層 115、及び不純物半導体層 117 上に導電層 111 を形成する（図 10（C）参照）。

【 0148 】

次に、導電層 111 上にレジストマスク（図示せず。）を形成し、当該レジストマスクを用いて導電層 111 をエッチングして、ソース電極及びドレイン電極 133 を形成する（図 11（A）参照）。

20

【 0149 】

次に、ソース電極 133 ドレイン電極 133 をマスクとして、不純物半導体層 117 をエッチングして、ソース領域及びドレイン領域 127 を形成する。また、非晶質半導体層 115c をエッチングして、非晶質半導体層 129c を形成する。こののち、レジストマスクを除去する（図 11（B）参照）。

【 0150 】

以上の工程により、薄膜トランジスタを作製することができる。

30

【 0151 】

なお、本実施の形態では、ソース電極及びドレイン電極 133 を形成した後、レジストマスクを除去せず非晶質半導体層 115c の一部をエッチングしたが、当該レジストマスクを除去した後、不純物半導体層 117 及び非晶質半導体層 115c の一部をエッチングしてもよい。当該エッチングより、ソース電極及びドレイン電極 133 を用いて不純物半導体層 117 をエッチングするため、ソース電極及びソース領域のそれぞれ端部が概略一致する。また、ドレイン電極及びドレイン領域のそれぞれ端部が概略一致する。

【 0152 】

なお、本実施の形態に示す第 2 の半導体層 107 の代わりに、実施の形態 3 乃至実施の形態 5 の第 2 の半導体層 107 の作製方法を適宜適用することができる。

40

【 0153 】

（実施の形態 7）

本実施の形態では、チャネル長が  $10 \mu m$  以下と短い薄膜トランジスタにおいて、ソース領域及びドレイン領域の抵抗を低減することが可能な形態について、以下に示す。ここでは、実施の形態 1 を用いて説明するが、適宜他の実施の形態に適用可能である。

【 0154 】

不純物半導体層 109 を、リンが添加された微結晶シリコン、またはボロンが添加された微結晶シリコンで形成する場合は、図 1（B）に示す第 2 の半導体層 107 において、微結晶半導体及び非晶質半導体を有する層 107b または非晶質半導体層 107c と、不純物半導体層 109 との間に、微結晶半導体層、代表的には微結晶シリコン層を形成するこ

50

とで、不純物半導体層 109 の堆積初期に低密度層が形成されず、微結晶半導体層を種結晶として、不純物半導体層 109 を結晶成長させることができるのであるため、界面の特性を向上させることができるのである。この結果、不純物半導体層 109 と、微結晶半導体及び非晶質半導体を有する層 107b または非晶質半導体層 107c との界面に生じる抵抗を低減することができる。この結果、薄膜トランジスタのソース領域、半導体層、及びドレイン領域を流れる電流量を増加させ、オン電流及び電界効果移動度の増加させることができるのである。

#### 【0155】

(実施の形態 8)

本実施の形態では、実施の形態 1 乃至実施の形態 7 で示す薄膜トランジスタを用いることが可能な、素子基板、及び当該素子基板を有する表示装置について、以下に示す。表示装置としては、液晶表示装置、発光表示装置、電子ペーパー等があるが、上記実施の形態の薄膜トランジスタは他の表示装置の素子基板にも用いることができる。ここでは、上記実施の形態 1 で示す薄膜トランジスタを有する液晶表示装置、代表的には、VA (Vertical Alignment) 型の液晶表示装置について、図 12 及び図 13 を用いて説明する。

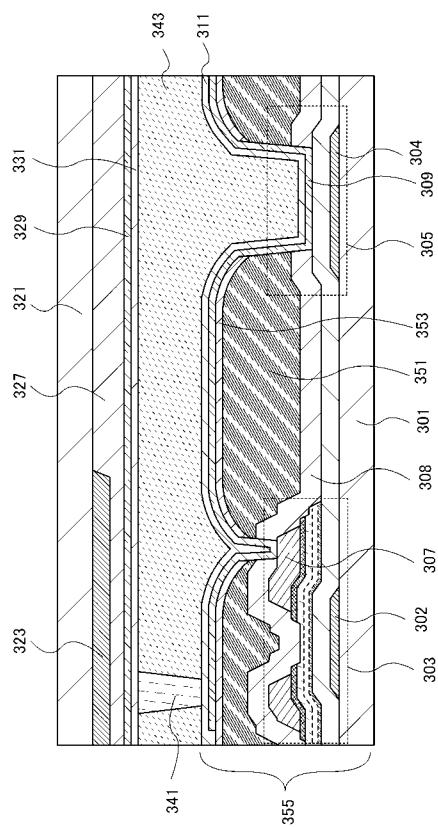

#### 【0156】

図 12 において、液晶表示装置の画素部の断面構造を示す。基板 301 上に、上記実施の形態で作製される薄膜トランジスタ 303 及び容量素子 305 が形成される。また、薄膜トランジスタ 303 上に形成される絶縁層 308 上に画素電極 309 が形成される。薄膜トランジスタ 303 のソース電極またはドレイン電極 307 と、画素電極 309 とは、絶縁層 308 に設けられる開口部において、接続される。画素電極 309 上には配向膜 311 が形成される。

#### 【0157】

容量素子 305 は、薄膜トランジスタ 303 のゲート電極 302 と同時に形成される容量配線 304 と、ゲート絶縁層 306 と、画素電極 309 とで構成される。

#### 【0158】

基板 301 から配向膜 311 までの積層体を素子基板 313 という。

#### 【0159】

対向基板 321 には、薄膜トランジスタ 303 への光の入射を遮断する遮光層 323 と、着色層 325 とが形成される。また、遮光層 323 及び着色層 325 上に平坦化層 327 が形成される。平坦化層 327 上に対向電極 329 が形成され、対向電極 329 上に配向膜 331 が形成される。

#### 【0160】

なお、対向基板 321 上の、遮光層 323、着色層 325、及び平坦化層 327 は、カラーフィルタとして機能する。なお、遮光層 323、平坦化層 327 の何れか一方、または両方は、対向基板 321 上に形成されていなくともよい。

#### 【0161】

また、着色層は、可視光の波長範囲のうち、任意の波長範囲の光を優先的に透過させる機能を有する。通常は、赤色波長範囲の光、青色波長範囲の光、及び緑色波長範囲の光、それぞれを優先的に透過させる着色層を組み合わせて、カラーフィルタに用いることが多い。しかしながら、着色層の組み合わせに関しては、これに限られない。

#### 【0162】

基板 301 及び対向基板 321 は、シール材 (図示しない) で固定され、基板 301、対向基板 321、及びシール材の内側に液晶層 343 が充填される。また、基板 301 及び対向基板 321 の間隔を保つために、スペーサ 341 が設けられている。

#### 【0163】

画素電極 309、液晶層 343、及び対向電極 329 が重なり合うことで、液晶素子が形成されている。

#### 【0164】

10

20

30

40

50

図13に、図12とは異なる液晶表示装置を示す。ここでは、対向基板321側に着色層が形成されず、薄膜トランジスタ303が形成される基板301側に着色層が形成されることを特徴とする。

【0165】

図13において、液晶表示装置の画素部の断面構造を示す。基板301上に、上記実施の形態作製される薄膜トランジスタ303及び容量素子305が形成される。

【0166】

また、薄膜トランジスタ303上に形成される絶縁層308上に、着色層351が形成される。また、着色層351上には、着色層351に含まれる不純物が液晶層343に混入するのを防ぐために、保護層353が形成される。着色層351及び保護層353上に、画素電極309が形成される。着色層351は、各画素毎に、任意の波長範囲の光（赤色、青色、または緑色）を優先的に透過させる層で形成すればよい。また、着色層351は平坦化層としても機能するため、液晶層343の配向ムラを低減することができる。

10

【0167】

薄膜トランジスタ303のソース電極またはドレイン電極307と、画素電極309とは、絶縁層308、着色層351、及び保護層353に設けられる開口部において、接続される。画素電極309上には配向膜311が形成される。

【0168】

容量素子305は、薄膜トランジスタ303のゲート電極302と同時に形成される容量配線304と、ゲート絶縁層306と、画素電極309とで構成される。

20

【0169】

基板301から配向膜311までの積層体を素子基板355という。

【0170】

対向基板321には、薄膜トランジスタ303への光の入射を遮断する遮光層323と、遮光層323及び対向基板321を覆う平坦化層327が形成される。平坦化層327上に対向電極329が形成され、対向電極329上に配向膜331が形成される。

【0171】

画素電極309、液晶層343、及び対向電極329が重なり合うことで、液晶素子が形成されている。

【0172】

なお、ここでは、液晶表示装置として、VA型の液晶表示装置を示したが、これに限定されない。すなわち、実施の形態1、実施の形態3乃至実施の形態6に示す薄膜トランジスタを用いて形成した素子基板を、FFS型の液晶表示装置、IPS型の液晶表示装置、TN型の液晶表示装置又はその他の液晶表示装置に用いることができる。

30

【0173】

本実施の形態の液晶表示装置は、オン電流及び電解効果移動度が高くオフ電流が低い薄膜トランジスタを画素トランジスタとして用いているため、液晶表示装置の表示画質を高めることができる。また、薄膜トランジスタの大きさを小さくしても、薄膜トランジスタの電気特性が低減されないため、薄膜トランジスタの面積を小さくすることで、液晶表示装置の開口率を向上させることができる。または、画素の面積を小さくすることが可能であり、液晶表示装置の解像度を高めることができる。

40

【0174】

また、図13に示す液晶表示装置は、遮光層323と、着色層351を同一基板上に形成しない。このため、着色層351の形成におけるマスクずれを回避できる。このため、遮光層323の面積を大きくする必要がなくなり、画素における開口率を向上させることができる。

【0175】

（実施の形態9）

実施の形態8で示す素子基板313において、配向膜311を形成せず、発光素子を設けることにより、当該素子基板を発光表示装置や、発光装置に用いることができる。発光表

50

示装置や発光装置は、発光素子として代表的には、エレクトロルミネッセンスを利用する発光素子がある。エレクトロルミネッセンスを利用する発光素子は、発光材料が有機化合物であるか、無機化合物であるかによって大別され、一般的に、前者は有機EL素子、後者は無機EL素子と呼ばれている。

【0176】

本実施の形態の発光表示装置及び発光装置は、オン電流及び電解効果移動度が高くオフ電流が低い薄膜トランジスタを画素トランジスタとして用いているため、画質が良好（例えば、高コントラスト）であり、且つ消費電力の低い発光表示装置及び発光装置を作製することができる。

【0177】

（実施の形態10）

上記実施の形態に係る薄膜トランジスタを有する表示装置は、さまざまな電子機器（遊技機も含む）に適用することができる。電子機器としては、例えば、テレビジョン装置（テレビ、またはテレビジョン受信機ともいう）、コンピュータ用などのモニタ、電子ペーパー、デジタルカメラやデジタルビデオカメラ等のカメラ、デジタルフォトフレーム、携帯電話機（携帯電話、携帯電話装置ともいう）、携帯型ゲーム機、携帯情報端末、音響再生装置、パチンコ機などの大型ゲーム機などが挙げられる。特に、実施の形態8及び実施の形態9で示したように、上記実施の形態に係る薄膜トランジスタを液晶表示装置、発光装置、電気泳動方式表示装置などに適用することにより、電子機器の表示部に用いることができる。以下に具体的に例示する。

10

20

【0178】

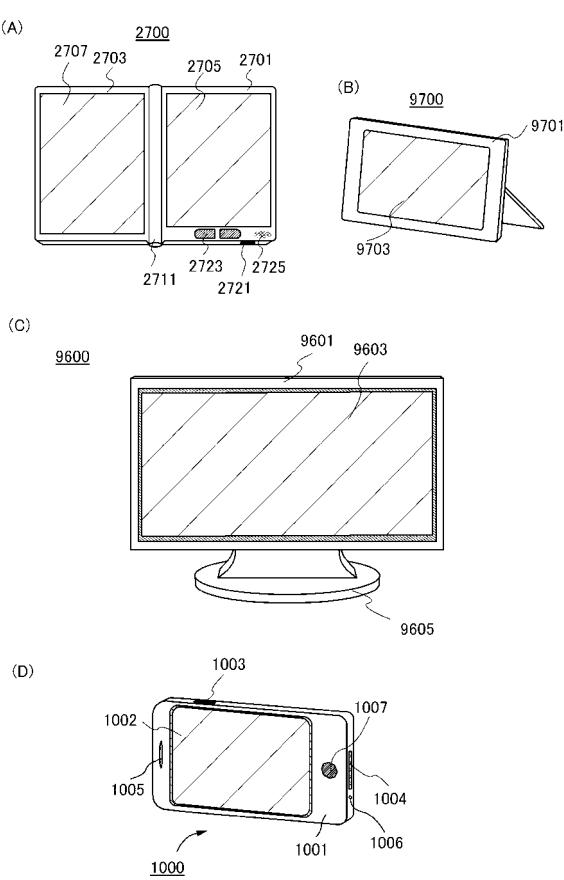

上記実施の形態に係る薄膜トランジスタを有する半導体装置は、電子ペーパーに適用することができる。電子ペーパーは、情報を表示するものであればあらゆる分野の電子機器に用いることが可能である。例えば、電子ペーパーを用いて、電子書籍（電子ブック）、ポスター、電車などの乗り物の車内広告、クレジットカード等の各種カードにおける表示等に適用することができる。電子機器の一例を図14（A）に示す。

【0179】

図14（A）は、電子書籍2700の一例を示している。例えば、電子書籍2700は、筐体2701および筐体2703の2つの筐体で構成されている。筐体2701および筐体2703は、蝶番2711により一体になっており、開閉動作を行うことができる。このような構成により、紙の書籍のような動作を行うことが可能となる。

30

【0180】

筐体2701には表示部2705が組み込まれ、筐体2703には表示部2707が組み込まれている。表示部2705および表示部2707は、続き画面を表示する構成としてもよいし、異なる画面を表示する構成としてもよい。異なる画面を表示する構成として、例えば右側の表示部（図14（A）では表示部2705）に文章を表示し、左側の表示部（図14（A）では表示部2707）に画像を表示することができる。

【0181】

また、図14（A）では、筐体2701に操作部などを備えた例を示している。例えば、筐体2701において、電源2721、操作キー2723、スピーカ2725などを備えている。操作キー2723により、頁を送ることができる。なお、筐体の表示部と同一面にキーボードやポインティングディバイスなどを備える構成としてもよい。また、筐体の裏面や側面に、外部接続用端子（イヤホン端子、USB端子、またはACアダプタおよびUSBケーブルなどの各種ケーブルと接続可能な端子など）、記録媒体挿入部などを備える構成としてもよい。さらに、電子書籍2700は、電子辞書としての機能を持たせた構成としてもよい。

40

【0182】

また、電子書籍2700は、無線で情報を送受信できる構成としてもよい。無線により、電子書籍サーバから、所望の書籍データなどを購入し、ダウンロードする構成とすることも可能である。

50

## 【0183】

図14(B)は、デジタルフォトフレーム9700の一例を示している。例えば、デジタルフォトフレーム9700は、筐体9701に表示部9703が組み込まれている。表示部9703は、各種画像を表示することが可能であり、例えばデジタルカメラなどで撮影した画像データを表示させることで、通常の写真立てと同様に機能させることができる。

## 【0184】

なお、デジタルフォトフレーム9700は、操作部、外部接続用端子(USB端子、USBケーブルなどの各種ケーブルと接続可能な端子など)、記録媒体挿入部などを備える構成とする。これらの構成は、表示部と同一面に組み込まれていてもよいが、側面や裏面に備えるとデザイン性が向上するため好ましい。例えば、デジタルフォトフレームの記録媒体挿入部に、デジタルカメラで撮影した画像データを記憶したメモリを挿入して画像データを取り込み、取り込んだ画像データを表示部9703に表示させることができる。

10

## 【0185】

また、デジタルフォトフレーム9700は、無線で情報を送受信出来る構成としてもよい。無線により、所望の画像データを取り込み、表示させる構成とすることもできる。

## 【0186】

図14(C)は、テレビジョン装置9600の一例を示している。テレビジョン装置9600は、筐体9601に表示部9603が組み込まれている。表示部9603により、映像を表示することが可能である。また、ここでは、スタンド9605により筐体9601を支持した構成を示している。表示部9603は、実施の形態8及び実施の形態9に示した表示装置を適用することができる。

20

## 【0187】

テレビジョン装置9600の操作は、筐体9601が備える操作スイッチや、別体のリモコン操作機により行うことができる。リモコン操作機が備える操作キーにより、チャンネルや音量の操作を行うことができ、表示部9603に表示される映像を操作することができる。また、リモコン操作機に、当該リモコン操作機から出力する情報を表示する表示部を設ける構成としてもよい。

## 【0188】

なお、テレビジョン装置9600は、受信機やモデムなどを備えた構成とする。受信機により一般的のテレビ放送の受信を行うことができ、さらにモデムを介して有線または無線による通信ネットワークに接続することにより、一方向(送信者から受信者)または双方(送信者と受信者間、あるいは受信者間同士など)の情報通信を行うことも可能である。

30

## 【0189】

図14(D)は、携帯電話機1000の一例を示している。携帯電話機1000は、筐体1001に組み込まれた表示部1002の他、操作ボタン1003、1007、外部接続ポート1004、スピーカ1005、マイク1006などを備えている。表示部1002には、実施の形態8及び実施の形態9に示した表示装置を適用することができる。

## 【0190】

図14(D)に示す携帯電話機1000は、表示部1002がタッチパネルになっており、指などの接触により、表示部1002の表示内容を操作することができる。また、電話の発信、或いはメールの作成は、表示部1002を指などで接触することにより行うことができる。

40

## 【0191】

表示部1002の画面は主として3つのモードがある。第1は、画像の表示を主とする表示モードであり、第2は、文字等の情報の入力を主とする入力モードである。第3は表示モードと入力モードの2つのモードが混合した表示+入力モードである。

## 【0192】

例えば、電話の発信、或いはメールを作成する場合は、表示部1002を文字の入力を主とする文字入力モードとし、画面に表示させた文字の入力操作を行えばよい。この場合、表示部1002の画面の大部分の領域にキーボードまたは番号ボタンを表示させることができ

50

好ましい。

【0193】

また、携帯電話機1000内部に、ジャイロ、加速度センサ等の傾きを検出するセンサを有する検出装置を設けることで、携帯電話機1000の向き（縦または横）を判断して、表示部1002の表示情報を自動的に切り替えるようにすることができる。

【0194】

また、画面モードの切り替えは、表示部1002の接触、又は筐体1001の操作ボタン1007の操作により行われる。また、表示部1002に表示される画像の種類によって切り替えるようにすることもできる。例えば、表示部に表示する画像信号が動画のデータであれば表示モード、テキストデータであれば入力モードに切り替えることができる。

10

【0195】

また、入力モードにおいて、表示部1002の光センサで検出される信号を検知し、表示部1002のタッチ操作による入力が一定期間ない場合には、画面のモードを入力モードから表示モードに切り替えるように制御してもよい。

【0196】

表示部1002は、イメージセンサとして機能させることもできる。例えば、表示部1002を掌や指で触れることで、掌紋、指紋等をイメージセンサで撮像することで、本人認証を行うことができる。また、表示部に近赤外光を発光するバックライトまたは近赤外光を発光するセンシング用光源を用いれば、指静脈、掌静脈などを撮像することもできる。

20

【0197】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

【実施例1】

【0198】

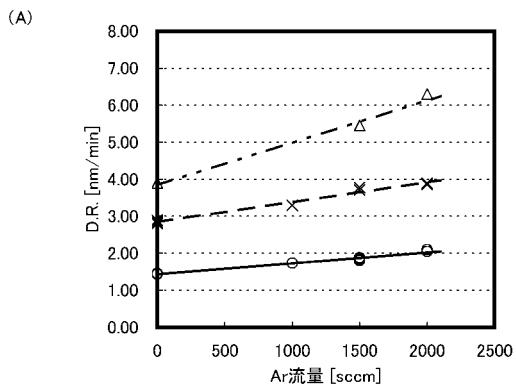

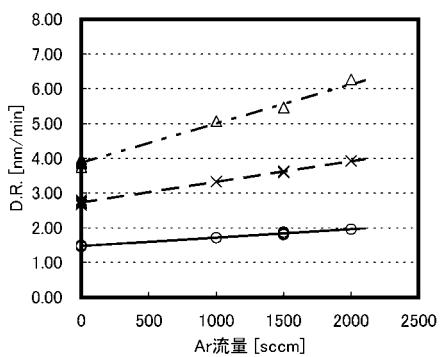

本実施例では、微結晶シリコン層の原料ガスにおけるアルゴンの有無と成膜速度について、図15(A)を用いて示す。

【0199】

以下に試料の作製方法を示す。

【0200】

ガラス基板（旭ガラス社製AN100）上に、厚さ50nmの微結晶シリコン層を形成した。このときの堆積条件は、材料ガスを、流量が1250sccmの水素と、シランと、アルゴンとし、材料ガスをプラズマCVD装置の処理室に導入して安定させ、処理室の圧力を280Pa、基板の温度を280とし、RF電源周波数を13.56MHz、RF電源の電力を50Wとして、プラズマ放電を行った。

30

【0201】

このとき、シランの流量をそれぞれ10sccm、20sccm、30sccmとした。また、アルゴンの流量を、それぞれ0sccm、1000sccm、1500sccm、2000sccmとした。

【0202】

このときのアルゴンの流量と、成膜速度の関係を図15(A)に示す。なお、丸印はシラン流量が10sccmのときの、アルゴンの流量及び成膜速度の関係を示す。また、バツ印は、シランの流量が20sccmのときの、アルゴンの流量及び成膜速度の関係を示す。また、三角印は、シランの流量が30sccmのときの、アルゴンの流量及び成膜速度の関係を示す。また、微結晶シリコン層の厚さの測定は、SCI (Scientific Computing International)社製、光学式薄膜解析システム、FilmTek1000(反射タイプ)を用いて行った。

40

【0203】

シランの流量が10~30sccmで、アルゴンの流量が2000sccmのときの成膜速度は、アルゴンの流量が0sccmの成膜速度の約1.3~1.6倍である。図15(A)から、アルゴンの流量を増やすほど、微結晶シリコン層の成膜速度が増加したことが

50

分かる。

【0204】

次に、窒素を有する微結晶シリコン層の形成において、希ガスとしてアルゴンの有無による成膜速度について、図15(B)に示す。

【0205】

以下に試料の作製方法を示す。

【0206】

ガラス基板(旭ガラス社製AN100)上に、厚さ50nmの窒素を有する微結晶シリコン層を形成した。このときの堆積条件は、材料ガスを、流量が1250sccmの水素と、流量が250sccmの100ppmアンモニア(水素希釈)と、シランと、アルゴンとし、材料ガスを処理室に導入して安定させ、処理室内の圧力を280Pa、基板の温度を280 とし、RF電源周波数を13.56MHz、RF電源の電力を50Wとしてプラズマ放電を行い、窒素を有する微結晶シリコン層を形成した。10

【0207】

このとき、シランの流量をそれぞれ10ccm、20ccm、30ccmとした。また、アルゴンの流量を、それぞれ0sccm、1000sccm、1500sccm、2000sccmとした。

【0208】

このときのアルゴンの流量と、成膜速度の関係を図15(B)に示す。なお、丸印はシラン流量が10sccmのときの、アルゴンの流量及び成膜速度の関係を示す。また、バツ印は、シランの流量が20sccmのときの、アルゴンの流量及び成膜速度の関係を示す。また、三角印は、シランの流量が30sccmのときの、アルゴンの流量及び成膜速度の関係を示す。20

【0209】

シランの流量が10~30sccmで、アルゴンの流量が2000sccmのときの成膜速度は、アルゴンの流量が0sccmの成膜速度の約1.3~1.6倍である。図15(B)から、アルゴンの流量を増やすほど、窒素を有する微結晶シリコン層の成膜速度が増加したことが分かる。

【実施例2】

【0210】

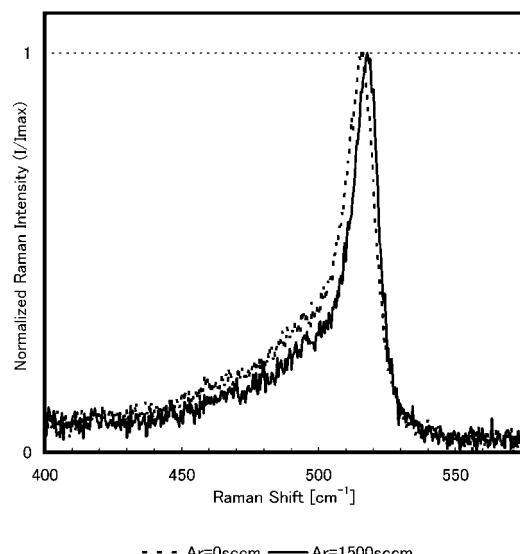

本実施例では、微結晶シリコン層の原料ガスにおけるアルゴンの有無と微結晶シリコン層の結晶性について、図16及び図17を用いて示す。30

【0211】

基板上に下地層として、酸化窒化シリコン層を形成した後、酸化窒化シリコン層上に微結晶シリコン層を形成した。

【0212】

ここでは、基板として、ガラス基板(旭ガラス社製AN100)を用いた。

【0213】

次に、SiH<sub>4</sub>の流量を30sccm、N<sub>2</sub>Oの流量を1200sccmとし、材料ガスを導入して安定させ、処理室内の圧力を40Pa、基板の温度を280 として50Wの出力によりプラズマ放電を行うことで、約100nmの酸化窒化シリコン層を形成した。40

【0214】

次に、SiH<sub>4</sub>の流量を10sccm、H<sub>2</sub>の流量を1500sccm、アルゴンの流量を0sccm、500sccm、1000sccm、1500sccm、2000sccmとして、材料ガスを導入して安定させ、処理室内の圧力を280Pa、基板の温度を280 とし、RF電源周波数を13.56MHz、RF電源の電力を50Wとしてプラズマ放電を行うプラズマCVD法を用いて、厚さ50nmの微結晶シリコン層を形成した。

【0215】

次に、微結晶シリコン層の結晶性について、ラマン分光分析を行った。ここでは、HORIBA JOBIN YVON社製のダブルラマン分光装置U-1000を用いてラマン50

分光分析を行った。

【0216】

ここでは、代表例として、アルゴンの流量を  $0 \text{ sccm}$  とした試料と、アルゴンの流量を  $1500 \text{ sccm}$  とした試料のラマン分光分析を行った結果を規格化したラマンスペクトルを図16に示す。実線がアルゴンの流量が  $1500 \text{ sccm}$  の試料であり、破線がアルゴンの流量が  $0 \text{ sccm}$  の試料のラマンスペクトルである。実線において、ラマンスペクトルのピーク位置が、単結晶シリコンを示す  $520 \text{ cm}^{-1}$  側の高波長側に、シフトしていることが分かる。

【0217】

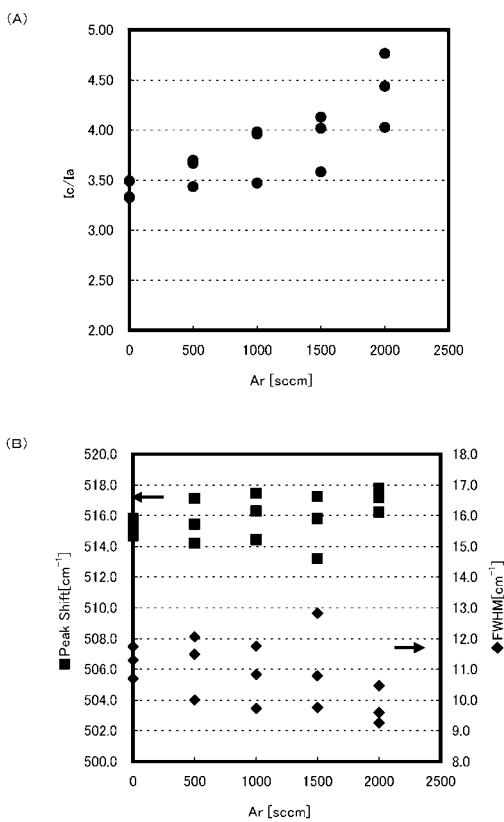

次に、原料ガスのアルゴンの流量を変えて形成した微結晶シリコン層をラマン分光分析したときの、結晶 / 非晶質ピーク強度比 ( $I_c / I_a$ ) を、図17(A)に示す。

10

【0218】

アルゴンの流量が増えるにつれ、結晶 / 非晶質ピーク強度比 ( $I_c / I_a$ ) が大きくなっていることが分かる。

【0219】

次に、原料ガスのアルゴンの流量を変えて形成した微結晶シリコン層をラマン分光分析したときの、ピークシフト値と、半値幅 (FWHM) を図17(B)に示す。なお、図17(B)において、左縦軸及び四角印でピークシフト値を示し、右縦軸及び菱形印で半値幅を示す。

20

【0220】

アルゴンの流量が増えるにつれ、ピークシフト値が若干上昇し、単結晶シリコンのピークである  $520 \text{ cm}^{-1}$  に近づいている。

【0221】

また、アルゴンの流量が増えるにつれ、半値幅 (FWHM) が小さくなっている。

【0222】

以上のことから、図16及び図17より、微結晶シリコン層の原料ガスにアルゴンを入れることで、微結晶シリコン層の結晶性が高まっていることが分かる。

【実施例3】

【0223】

はじめに薄膜トランジスタの作製工程を、図1、図10及び図11を用いて示す。

30

【0224】

基板101上にゲート電極103を形成した。

【0225】

ここでは、基板101として、ガラス基板 (コーニング製 EAGLE 2000) を用いた。

【0226】

モリブデンターゲットを流量  $50 \text{ sccm}$  のアルゴンイオンでスパッタリングして、厚さ  $150 \text{ nm}$  のモリブデン層を基板101上に形成した。次に、モリブデン層上にレジストを塗布した後、第1のフォトマスクを用いて露光した後、現像してレジストマスクを形成した。

40

【0227】

次に、当該レジストマスクを用いてモリブデン層をエッティングして、ゲート電極103を形成した。ここでは、ICP (Inductively Coupled Plasma: 誘導結合型プラズマ) 装置を用い、ICPパワー  $800 \text{ W}$ 、バイアスパワー  $100 \text{ W}$ 、圧力  $1.5 \text{ Pa}$ 、エッティングガスに流量  $25 \text{ sccm}$  のフッ化炭素、流量  $25 \text{ sccm}$  の塩素、流量  $10 \text{ sccm}$  の酸素を用いたエッティング条件を用いた。

【0228】

この後、レジストマスクを除去した。

【0229】

次に、ゲート電極103及び基板101上に、ゲート絶縁層105、第1の半導体層10

50

6を形成した。ここまで の工程を、図1(A)に示す。

【0230】

ここでは、ゲート絶縁層105として厚さ110nmの窒化シリコン層及び厚さ110nmの酸化シリコン層を形成した。

【0231】

窒化シリコン層の堆積条件としては、SiH<sub>4</sub>の流量を40sccm、H<sub>2</sub>の流量を500sccm、N<sub>2</sub>の流量を550sccm、NH<sub>3</sub>の流量を140sccmとして材料ガスを導入して安定させ、処理室内の圧力を100Pa、基板の温度を280とし、RF電源周波数を13.56MHz、RF電源の電力を370Wとしてプラズマ放電を行う、プラズマCVD法を用いた。

10

【0232】

酸化シリコン層の堆積条件としては、オルトケイ酸テトラエチル(Tetraethyl Orthosilicate:TEOS)の流量を15sccm、O<sub>2</sub>の流量を750sccmとして材料ガスを導入して安定させ、処理室内の圧力を100Pa、上部電極の温度を300、下部電極の温度を297とし、RF電源周波数を27MHz、RF電源の電力を300Wとしてプラズマ放電を行う、プラズマCVD法を用いた。

【0233】

ここでは、第1の半導体層106として、厚さ5nmの微結晶シリコン層を形成した。

【0234】

第1の半導体層106の堆積条件を以下に示す。はじめに、処理室内の圧力を100Paとし、処理室に流量300sccmのシランを導入して、処理室内の不純物を除去した。次に、SiH<sub>4</sub>の流量を10sccm、H<sub>2</sub>の流量を1500sccm、アルゴンの流量を1500sccmとして材料ガスを導入して安定させ、処理室内の圧力を280Pa、基板の温度を280とし、RF電源周波数を13.56MHz、RF電源の電力を50Wとしてプラズマ放電を行うプラズマCVD法を用いた。

20

【0235】

次に、図10(A)に示すように、第2の半導体層107を形成し、第2の半導体層107上に不純物半導体層109を形成した。

【0236】

ここでは、厚さ150nmの第2の半導体層107を形成した。また、第2の半導体層107として、微結晶半導体層107aに微結晶シリコン層、微結晶半導体及び非晶質半導体を有する層107bに微結晶シリコン、アモルファスシリコン、及び窒素を有する半導体層、非晶質半導体層107cに窒素及びアモルファスシリコンを有する半導体層を形成した。

30

【0237】

第2の半導体層107の堆積条件としては、SiH<sub>4</sub>の流量を30sccm、1000ppm NH<sub>3</sub>(水素希釈)の流量を25sccm、H<sub>2</sub>の流量を1475sccmとして材料ガスを導入して安定させ、処理室内の圧力を280Pa、基板の温度を280とし、RF電源の電力を50Wとしてプラズマ放電を行った。

【0238】

40

不純物半導体層109として、厚さ50nmのリンが添加されたアモルファスシリコン層を形成した。このときの堆積条件は、堆積温度を280、シラン流量100sccm、0.5%フォスフィン(水素希釈)流量を170sccm、圧力170Pa、RF電源周波数を13.56MHz、RF電源の電力を60Wとしてプラズマ放電を行うプラズマCVD法を用いた。

【0239】

次に、不純物半導体層109上にレジストを塗布した後、第2のフォトマスクを用いて露光し、現像してレジストマスクを形成した。次に、当該レジストマスクを用いて、第2の半導体層107、不純物半導体層109をエッチングして、第2の半導体層115、不純物半導体層117を形成した(図10(B)参照)。ここでは、ICP装置を用い、ソーダ

50

スパワー 1000W、バイアスパワー 80W、圧力 1.51Pa、エッティングガスに流量 100 sccm の塩素を用いたエッティング条件を用いた。この後レジストマスクを除去した。

#### 【0240】

次に、図 10 (C) に示すように、ゲート絶縁層 105、第 2 の半導体層 115、不純物半導体層 117 を覆う導電層 111 を形成した。ここでは、モリブデンターゲットを流量 50 sccm のアルゴンイオンでスパッタリングして、厚さ 300 nm のモリブデン層を形成した。

#### 【0241】

次に、導電層 119 上にレジストを塗布した後、第 3 のフォトマスクを用いて露光し、現像してレジストマスクを形成した。当該レジストマスクを用いて導電層 111 をウエットエッティングして、図 11 (A) に示すように、ソース電極及びドレイン電極 133 を形成した。ここでは、ウエットエッティングにより、導電層 111 をエッティングした。なお、本実施例では、ソース電極及びドレイン電極 133 の平面形状は、並行型である。

#### 【0242】

次に、レジストマスクを用いて不純物半導体層 117 エッティングして、ソース領域及びドレイン領域 127 形成した。なお、当該工程において、第 2 の半導体層 115 の一部もエッティングされ、凹部を有する非晶質半導体層 129c が形成された（図 11 (B) 参照）。ここでは、ICP パワー 150W、バイアスパワー 40W、圧力 1.2Pa、エッティングガスに流量 100 sccm の塩素を用いたエッティング条件を用い、90 nm エッティングした。このときの、微結晶半導体層 115a、微結晶半導体及び非晶質半導体を有する層 115b、及び非晶質半導体層 129c のエッティングされた領域の合計の厚さを 110 nm とした。

#### 【0243】

次に、レジストマスクを除去した後、非晶質半導体層 129c、ソース領域及びドレイン領域 127 表面にフッ化炭素プラズマを照射し、非晶質半導体層 129c の表面に残留する不純物を除去した。ここでは、ソースパワー 1000W、バイアスパワー 0W、圧力 0.67Pa、エッティングガスに流量 100 sccm のフッ化炭素を用いたエッティング条件を用いた。

#### 【0244】

次に、絶縁層として、窒化シリコン層を形成した。このときの堆積条件は、SiH<sub>4</sub> の流量を 20 sccm、NH<sub>3</sub> の流量を 220 sccm、窒素の流量を 450 sccm、水素の流量を 450 sccm として材料ガスを導入し、処理室内の圧力を 160 Pa、基板の温度を 250 とし、200 W の出力によりプラズマ放電を行って、厚さ 300 nm の窒化シリコン層を形成した。

#### 【0245】

次に、絶縁層上にレジストを塗布した後、第 4 のフォトマスクを用いて露光し、現像してレジストマスクを形成した。当該レジストマスクを用いて絶縁層の一部をドライエッティングして、ソース電極及びドレイン電極 133 を露出した。また、絶縁層及びゲート絶縁層 105 の一部をドライエッティングして、ゲート電極 103 を露出した。この後、レジストマスクを除去した。

#### 【0246】

以上の工程により、薄膜トランジスタを作製した。

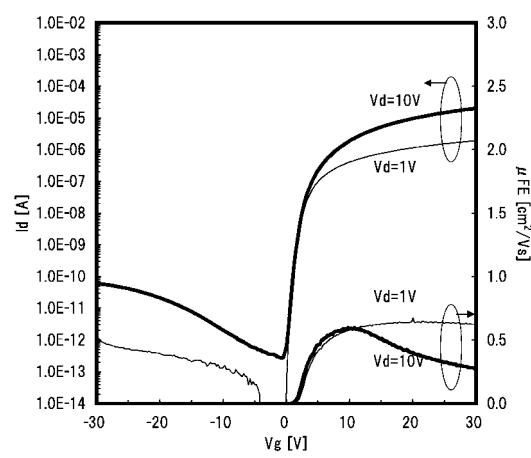

#### 【0247】

こののち、薄膜トランジスタの電気特性を測定した結果を図 18 に示す。ドレイン電圧が 1V 及び 10V の電流電圧特性及び電界効果移動度を実線で示した。なお、本実施例の薄膜トランジスタのチャネル長を 3.5 μm、チャネル幅を 20 μm として形成した。

#### 【0248】

このときの、16 個の薄膜トランジスタの電気特性を測定した平均値を以下に示す。しきい値電圧 (V<sub>th</sub>) は 2.83V、V<sub>d</sub> が 1V のときの電界効果移動度は 0.65 cm<sup>2</sup>

10

20

30

40

50

/ V<sub>s</sub>、V<sub>d</sub>が10Vのときの電界効果移動度は0.59 cm<sup>2</sup> / V s、S値は0.46 V / decであった。また、V<sub>d</sub>が10Vで、V<sub>g</sub>が15Vのときのオン電流(I<sub>on</sub>)は5.13 μA、最小オフ電流(I<sub>off\_f\_min</sub>)は0.31 pA、V<sub>g</sub>が-14Vのときのオフ電流(I<sub>off\_f</sub>)は9.6 pAであった。このことから、しきい値電圧のシフトが少なく、オン電流が高く、オフ電流が低い、良好な電気特性を有する薄膜トランジスタを作製することができた。

## 【実施例4】

## 【0249】

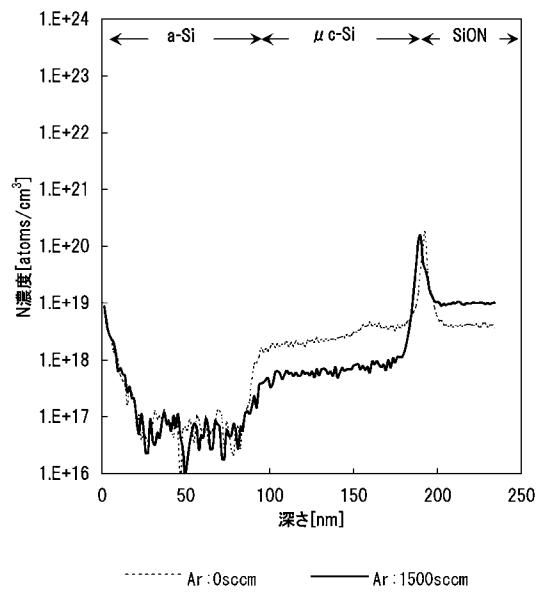

本実施例では、微結晶シリコン層の原料ガスにおけるアルゴンの有無と微結晶シリコン層含まれる不純物について、図19及び図20を用いて示す。

10

## 【0250】

はじめに試料の作製方法について示す。

## 【0251】

基板上に下地層として、窒化シリコン層を形成し、窒化シリコン層上に酸化窒化シリコン層を形成した後、酸化窒化シリコン層上に微結晶シリコン層を形成した。また、微結晶シリコン層上に保護層としてアモルファスシリコン層を形成した。

## 【0252】

ここでは、基板として、ガラス基板(旭ガラス社製AN100)を用いた。

## 【0253】

窒化シリコン層の堆積条件としては、SiH<sub>4</sub>の流量を40 sccm、H<sub>2</sub>の流量を500 sccm、N<sub>2</sub>の流量を550 sccm、NH<sub>3</sub>の流量を140 sccmとして材料ガスを導入して安定させ、処理室内の圧力を100 Pa、基板の温度を280 ℃とし、RF電源周波数を13.56 MHz、RF電源の電力を370 Wとしてプラズマ放電を行う、プラズマCVD法を用いた。

20

## 【0254】

次に、SiH<sub>4</sub>の流量を30 sccm、N<sub>2</sub>Oの流量を1200 sccmとし、材料ガスを導入して安定させ、処理室内の圧力を40 Pa、基板の温度を280 ℃として50 Wの出力によりプラズマ放電を行うことで、約100 nmの酸化窒化シリコン層(図19及び図20においてはSiONと示す。)を形成した。

## 【0255】

次に、プラズマCVD装置の処理室から基板を搬出した後、NF<sub>3</sub>で処理室内をクリーニングした後、処理室内に保護膜として酸化シリコン層を形成した。

30

## 【0256】

次に、SiH<sub>4</sub>の流量を10 sccm、H<sub>2</sub>の流量を1500 sccm、アルゴンの流量を0 sccmまたは1500 sccmとして、材料ガスを導入して安定させ、処理室内の圧力を280 Pa、基板の温度を280 ℃とし、RF電源周波数を13.56 MHz、RF電源の電力を50 Wとしてプラズマ放電を行うプラズマCVD法を用いて、厚さ100 nmの微結晶シリコン層(図19及び図20においてはμc-Siと示す。)を形成した。

## 【0257】

次に、保護層として、微結晶シリコン層上に厚さ100 nmのアモルファスシリコン層(図19及び図20においてはa-Siと示す。)を形成した。

40

## 【0258】

次に、各試料をSIMS測定した結果を図19及び図20に示す。図19は窒素濃度を示し、図20はアルゴン濃度を示す。図19及び図20において、微結晶シリコン層の原料ガスにおけるアルゴンの流量が0 sccmの試料の濃度プロファイルを破線で示し、アルゴンの流量が1500 sccmの試料の濃度プロファイルを実線で示す。

## 【0259】

図19より、原料ガスにおけるアルゴンの流量が1500 sccmの微結晶シリコン層(μc-Si)は窒素濃度が低減していることがわかる。このことから、原料ガスとしてア

50

ルゴンを用いることで、微結晶シリコン層の不純物濃度を低減できることがわかる。一方、図20より原料ガスにアルゴンを用いても微結晶シリコン層に含まれるアルゴンの量は検出下限以下である。このため、原料ガスにアルゴンを用いても微結晶シリコン層にアルゴンは取り込まれにくいことがわかる。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図 7】

【図 8】

【図 9】

【図 10】

【図 1 1】

【図 1 2】

【図 1 3】

【図 1 4】

【図15】

(B)

○ SiH<sub>4</sub>=10sccm、× SiH<sub>4</sub>=20sccm、△ SiH<sub>4</sub>=30sccm

【図16】

【図17】

【図18】

$V_{th} = 2.83V$

$\mu_{FE}(Vd=1V) = 0.65\text{cm}^2/\text{Vs}$

$\mu_{FE}(Vd=10V) = 0.59\text{cm}^2/\text{Vs}$

$S\text{值} = 0.46V/\text{dec}$

$\text{Ion}(Vg=15V) = 5.13\mu\text{A}$

$I_{off\ min} = 0.31\text{pA}(@Vg = -0.95V)$

$I_{off}(Vg=-14V) = 9.6\text{pA}$

【図19】

【図20】

---

フロントページの続き

|                |                         |                |   |

|----------------|-------------------------|----------------|---|

| (51)Int.Cl.    | F I                     |                |   |

| <b>G 0 2 F</b> | <b>1/1368 (2006.01)</b> | H 0 1 L 21/316 | X |

|                |                         | H 0 1 L 21/205 |   |

|                |                         | G 0 2 F 1/1368 |   |

(72)発明者 一條 充弘

神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内

(72)発明者 横井 智和

神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内

審査官 大橋 達也

(56)参考文献 特開2008-124392(JP, A)

特開昭62-141776(JP, A)

特開平05-335607(JP, A)

(58)調査した分野(Int.Cl., DB名)

|         |             |

|---------|-------------|

| H 0 1 L | 2 1 / 3 3 6 |

| G 0 2 F | 1 / 1 3 6 8 |

| H 0 1 L | 2 1 / 2 0   |

| H 0 1 L | 2 1 / 2 0 5 |

| H 0 1 L | 2 1 / 3 1 6 |

| H 0 1 L | 2 9 / 7 8 6 |