(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-39799

(P2005-39799A)

(43) 公開日 平成17年2月10日(2005.2.10)

(51) Int.CI.<sup>7</sup>

**H03F 3/60**

**H01P 5/12**

**H03F 1/02**

**H03F 3/26**

F 1

H03F 3/60

H01P 5/12

H01P 5/12

H03F 1/02

H03F 3/26

テーマコード(参考)

5 J 0 6 7

5 J 5 0 0

Z

審査請求 未請求 請求項の数 20 O L (全 18 頁)

(21) 出願番号 特願2004-178371 (P2004-178371)

(22) 出願日 平成16年6月16日 (2004.6.16)

(31) 優先権主張番号 特願2003-183231 (P2003-183231)

(32) 優先日 平成15年6月26日 (2003.6.26)

(33) 優先権主張国 日本国 (JP)

(71) 出願人 000005821

松下電器産業株式会社

大阪府門真市大字門真1006番地

(74) 代理人 100098291

弁理士 小笠原 史朗

森本 滋

大阪府門真市大字門真1006番地 松下

電器産業株式会社内

(72) 発明者 足立 寿史

大阪府門真市大字門真1006番地 松下

電器産業株式会社内

最終頁に続く

(54) 【発明の名称】電力増幅器、電力分配器および電力合成器

## (57) 【要約】

【課題】 プシュブル型の電力増幅器を高効率化するために一対の直列共振回路を設けると回路が大型化し、また特性ばらつきが生じる。

【解決手段】 分布定数線路105a, 105bは、第1の増幅素子102aによって増幅された第1の信号における基本波成分の位相を反転させるため、基本波の1/2波長の線路長を有する。直列共振回路106の一端は、2次高調波成分の位相が反転する分布定数線路105aと105bとの間に並列に接続されている。その他端は、第2の増幅素子102bの出力側に接続されている。直列共振回路106は、2次高調波成分の周波数で共振することによって、2次高調波成分を打ち消す。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

高周波信号を増幅するための電力増幅器であって、

第1の信号を増幅するための第1の増幅素子と、

前記第1の増幅素子とプッシュプル型に接続されており、前記第1の信号と逆相の第2の信号を増幅するための第2の増幅素子と、

前記第1の増幅素子によって増幅された前記第1の信号における基本波成分の位相を反転させる線路長を有する第1の分布定数線路と、

短絡させたい偶数次高調波成分の位相が反転する前記第1の分布定数線路上の位置と前記第2の増幅素子の出力側との間に接続され、前記短絡させたい偶数次高調波成分の周波数で直列共振する第1の共振回路と、

前記第1の分布定数線路からの信号と前記第2の増幅素子からの信号とを合成して出力する出力端子とを備える、電力増幅器。

**【請求項 2】**

前記第1の分布定数線路の線路長は、基本波の1/2波長であり、前記第1の共振回路を接続するための前記第1の分布定数線路上の位置は、前記第1の分布定数線路の端から基本波の1/4波長のところであり、前記第1の共振回路は、2次高調波の周波数で直列共振することを特徴とする、請求項1に記載の電力増幅器。

**【請求項 3】**

前記第1の共振回路は、インダクタおよびコンデンサが対称に配置された直列共振回路であることを特徴とする、請求項2に記載の電力増幅器。

**【請求項 4】**

前記第1の共振回路は、前記短絡させたい偶数次高調波成分の波長の1/2の電気長を有する分布定数線路であることを特徴とする、請求項1に記載の電力増幅器。

**【請求項 5】**

前記第1および第2の信号をそれぞれ前記第1および第2の増幅素子に入力するための電力分配器をさらに備え、

前記電力分配器は、

入力される信号を二分配し、一方を前記第1の信号として前記第1の増幅素子に入力する分配手段と、

前記分配手段からの他方の信号における基本波成分の位相を反転させる線路長を有し、当該位相を反転させた信号を第2の信号として前記第2の増幅素子に入力する第2の分布定数線路と、

短絡させたい偶数次高調波成分の位相が反転する前記第2の分布定数線路上の位置と前記第2の増幅素子の入力側との間に接続され、前記短絡させたい偶数次高調波成分の周波数で直列共振する第2の共振回路とを含む、請求項1に記載の電力増幅器。

**【請求項 6】**

前記第2の分布定数線路の線路長は、基本波の1/2波長であり、前記第2の共振回路を接続するための前記第2の分布定数線路上の位置は、前記第2の分布定数線路の端から基本波の1/4波長のところであり、前記第2の共振回路は、2次高調波の周波数で直列共振することを特徴とする、請求項5に記載の電力増幅器。

**【請求項 7】**

前記第2の共振回路は、インダクタおよびコンデンサが対称に配置された直列共振回路であることを特徴とする、請求項6に記載の電力増幅器。

**【請求項 8】**

前記第2の共振回路は、前記短絡させたい偶数次高調波成分の波長の1/2の電気長を有する分布定数線路であることを特徴とする、請求項5に記載の電力増幅器。

**【請求項 9】**

高周波信号を増幅するための電力増幅器であって、

第1の信号、および前記第1の信号と逆相の第2の信号を出力する電力分配器と、

10

20

30

40

50

前記第1の信号を増幅するための第1の増幅素子と、

前記第1の増幅素子とプッシュプル型に接続されており、前記第2の信号を増幅するための第2の増幅素子と、

前記第1の増幅素子によって増幅された前記第1の信号における基本波成分の位相を反転させて、当該位相を反転させた前記第1の信号と前記第2の増幅素子によって増幅された前記第2の信号と合成して出力する電力合成器とを備え、

前記電力分配器は、

入力される信号を二分配し、一方を前記第1の信号として前記第1の増幅素子に入力する分配手段と、

前記分配手段からの他方の信号における基本波成分の位相を反転させる線路長を有し、当該位相を反転させた信号を第2の信号として前記第2の増幅素子に入力する分布定数線路と、

短絡させたい偶数次高調波成分の位相が反転する前記分布定数線路上の位置と前記第2の増幅素子の入力側との間に接続され、前記短絡させたい偶数次高調波成分の周波数で直列共振する共振回路とを含む、電力増幅器。

#### 【請求項10】

前記分布定数線路の線路長は、基本波の1/2波長であり、前記共振回路を接続するための前記分布定数線路上の位置は、前記分布定数線路の端から基本波の1/4波長のところであり、前記共振回路は、2次高調波の周波数で直列共振することを特徴とする、請求項9に記載の電力増幅器。

#### 【請求項11】

前記共振回路は、インダクタおよびコンデンサが対称に配置された直列共振回路であることを特徴とする、請求項10に記載の電力増幅器。

#### 【請求項12】

前記共振回路は、前記短絡させたい偶数次高調波成分の波長の1/2の電気長を有する分布定数線路であることを特徴とする、請求項9に記載の電力増幅器。

#### 【請求項13】

入力信号を二分配するための電力分配器であって、

前記入力信号の電力を二分配する分配手段と、

前記分配手段によって二分配された一方の信号を、第1の信号として出力するための第1の出力端子と、

前記分配手段によって二分配された他方の信号における基本波成分の位相を反転させる線路長を有し、当該位相を反転させた信号を第2の信号とするための分布定数線路と、

前記分布定数線路からの前記第2の信号を出力するための第2の出力端子と、

短絡させたい偶数次高調波成分の位相が反転する前記分布定数線路上の位置と前記第1の出力端子との間に接続され、前記短絡させたい偶数次高調波成分の周波数で直列共振する共振回路とを備える、電力分配器。

#### 【請求項14】

前記分布定数線路の線路長は、基本波の1/2波長であり、前記共振回路を接続するための前記分布定数線路上の位置は、前記分布定数線路の端から基本波の1/4波長のところであり、前記共振回路は、2次高調波の周波数で直列共振することを特徴とする、請求項13に記載の電力分配器。

#### 【請求項15】

前記共振回路は、インダクタおよびコンデンサが対称に配置された直列共振回路であることを特徴とする、請求項14に記載の電力分配器。

#### 【請求項16】

前記共振回路は、前記短絡させたい偶数次高調波成分の波長の1/2の電気長を有する分布定数線路であることを特徴とする、請求項13に記載の電力分配器。

#### 【請求項17】

入力される第1の信号と第2の信号とを合成するための電力合成器であって、

10

20

30

40

50

前記第1の信号を入力するための第1の入力端子と、

前記第2の信号を入力するための第2の入力端子と、

前記第2の入力端子からの前記第2の信号における基本波成分の位相を反転させる線路長を有する分布定数線路と、

短絡させたい偶数次高調波成分の位相が反転する前記分布定数線路上の位置と前記第1の入力端子との間に接続され、前記短絡させたい偶数次高調波成分の周波数で直列共振する共振回路と、

前記第1の入力端子からの前記第1の信号と、前記分布定数線路からの信号とを合成する合成手段とを備える、電力合成器。

**【請求項 1 8】**

前記分布定数線路の線路長は、基本波の1/2波長であり、前記共振回路を接続するための前記分布定数線路上の位置は、前記分布定数線路の端から基本波の1/4波長のところであり、前記共振回路は、2次高調波の周波数で直列共振することを特徴とする、請求項17に記載の電力合成器。

**【請求項 1 9】**

前記共振回路は、インダクタおよびコンデンサが対称に配置された直列共振回路であることを特徴とする、請求項18に記載の電力合成器。

**【請求項 2 0】**

前記共振回路は、前記短絡させたい偶数次高調波成分の波長の1/2の電気長を有する分布定数線路であることを特徴とする、請求項17に記載の電力合成器。

10

20

**【発明の詳細な説明】**

**【技術分野】**

**【0 0 0 1】**

本発明は、高周波電力増幅器に関し、より特定的には、プッシュプル型の高周波電力増幅器およびそれに用いられる電力分配器および電力合成器に関する。

**【背景技術】**

**【0 0 0 2】**

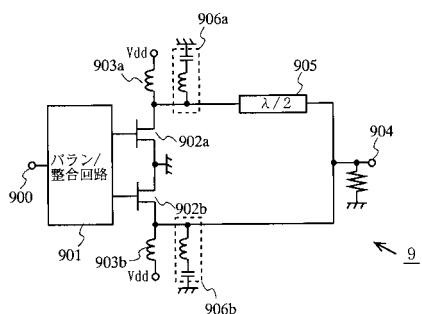

図6は、従来のプッシュプル型の高周波電力増幅器の構成を示す図である。図6において、従来の電力増幅器9は、入力端子900と、バラン/整合回路901と、同一規格の電界効果トランジスタ(以下、FETという)902a, 902bと、FET902a, 902bのドレインに接続されたインダクタ903a, 903bと、出力端子904と、出力端子904とFET902aのドレインとの間に接続された分布定数線路905と、分布定数線路905とFET902aのドレインとの間に並列に接続された直列共振回路906aと、出力端子904とFET902bのドレインとの間に並列に接続された直列共振回路906bとを含む。

30

**【0 0 0 3】**

バラン/整合回路901は、入力端子900に入力される基本波の位相を回転させ、互いに逆相の基本波成分を有する第1および第2の信号を出力する。第1および第2の信号は、それぞれFET902a, 902bによって増幅される。ここで、基本波の波長をとする。分布定数線路905の長さは、基本波の1/2波長(1/2)の長さとなっている。FET902aから出力された信号は、分布定数線路905によって基本波成分の位相を180度回転させられ、FET902bから出力された信号と合成される。合成された信号は、出力端子904から出力される。

40

**【0 0 0 4】**

基本波の周波数を $f_0$ (=1/ $\lambda$ )とした場合、直列共振回路906a, 906bは、 $f_0$ の2倍の周波数 $2f_0$ で共振するように設定されている。したがって、増幅素子902a, 902bで発生した互いに同相の2次高調波は、直列共振回路906a, 906bにおいて短絡する。したがって、図6に示す従来の電力増幅器9は、2次歪みの発生を抑制することができる。

50

## 【0005】

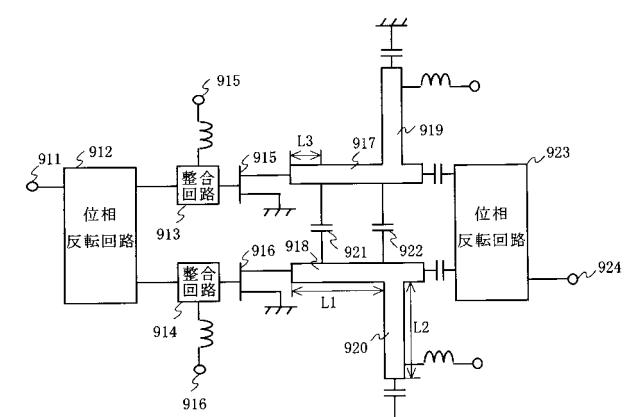

図7は、高調波に対するインピーダンスを考慮した整合回路を設けた従来のプッシュプル型の電力増幅器の構成を示す図である(特許文献1参照)。図7に示す従来の電力増幅器において、入力端子911に入力された基本波は、位相反転回路912によって、互いに逆相の二つの信号として出力され、それぞれ整合回路913, 914を介して、FET915, 916へ入力される。

## 【0006】

FET915, 916のドレインには、分布定数線路917, 918が接続されている。分布定数線路917, 918において、基本波の1/4波長の整数倍の長さL1の位置に、偶数次高調波に対して短絡となる基本波の1/4波長の長さL2となる一端を短絡したスタブ919, 920が接続されている。

## 【0007】

また、分布定数線路917, 918において、3次高調波に対して開放するために基本波の1/12波長の長さL3の位置に、分布定数線路917と分布定数線路918とを結ぶコンデンサ921が接続されている。さらに、コンデンサ921の接続位置とスタブ919, 920の接続位置との間の分布定数線路917, 918において、基本波に対するインピーダンスの整合を取るために、コンデンサ922が接続されている。分布定数線路917, 918からの信号は、位相反転器923で互いに同相の信号とされて合成され、出力端子924から出力される。

## 【0008】

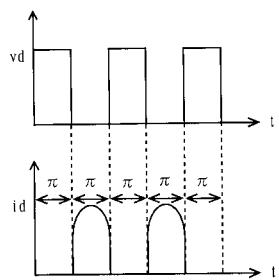

図7に示す従来の電力増幅器において、FET915, 916のゲート電圧をピッチオフ点に設定し、入力信号を十分振り込んだ場合、FETのドレイン電圧vdおよびドレイン電流idは、図8に示すような形状の波形となる。すなわち、ドレイン電圧vdは基本波と奇数次高調波成分からなる矩形波になり、ドレイン電流idは基本波と偶数次高調波からなる半波整流波形になる。したがって、電圧と電流とが同時に存在することができないため増幅素子内の電力消費がなくなるので、効率が100%になる。

## 【特許文献1】特開平05-029851号公報

## 【発明の開示】

## 【発明が解決しようとする課題】

## 【0009】

図6に示した従来の電力増幅器では、2次高調波に対してインピーダンスを短絡するために、直列共振回路906a, 906bを一対のFETに対してそれぞれ設ける必要があった。

## 【0010】

また、図7に示した従来の電力増幅器では、偶数次高調波に対してインピーダンスを短絡とするためのスタブ919, 920を、一対のFETに対してそれぞれ設ける必要があった。

## 【0011】

そのため、いずれの従来の電力増幅器においても、回路が大型化してしまうという問題があった。

## 【0012】

また、これら一対の直列共振回路やスタブは、それぞれが同じ特性である必要がある。しかし、増幅器を集積してモジュール化するような場合には、周辺部品の影響などにより一対の直列共振回路やスタブの高周波特性が微妙に異なることがある。これは、利得特性にばらつきを生じさせる原因となる。

## 【0013】

それゆえ、本発明の目的は、小型でかつ特性ばらつきの小さい高効率の電力増幅器を提供することである。さらに、本発明の他の目的は、このような電力増幅器で用いられる電力分配器および電力合成器を提供することである。

## 【課題を解決するための手段】

10

20

30

40

50

## 【0014】

上記課題を解決するために本発明は以下のような特徴を有する。本発明は、高周波信号を増幅するための電力増幅器であって、第1の信号を増幅するための第1の増幅素子と、第1の増幅素子とプッシュプル型に接続されており、第1の信号と逆相の第2の信号を増幅するための第2の増幅素子と、第1の増幅素子によって増幅された第1の信号における基本波成分の位相を反転させる線路長を有する第1の分布定数線路と、短絡させたい偶数次高調波成分の位相が反転する第1の分布定数線路上の位置と第2の増幅素子の出力側との間に接続され、短絡させたい偶数次高調波成分の周波数で直列共振する第1の共振回路と、第1の分布定数線路からの信号と第2の増幅素子からの信号とを合成して出力する出力端子とを備える。

10

## 【0015】

本発明によれば、プッシュプル型の電力増幅器において、所望の偶数次高調波成分の周波数で直列共振し、かつ当該偶数次高調波の位相が反転する位置に接続されている一つの共振回路が、第1および第2の増幅素子で発生する偶数次高調波を相殺する。このように、1つの共振回路によって偶数次高調波歪みの発生を抑えることができるので、回路が小型化される電力増幅器を提供することができる。また、プッシュプル型の電力増幅器で用いられる二つの増幅素子毎に偶数次高調波歪みの発生を抑圧するための共振回路をそれぞれ設ける場合に比べ、特性ばらつきを低減することができる。

## 【0016】

好ましくは、第1の分布定数線路の線路長は、基本波の1/2波長であり、第1の共振回路を接続するための第1の分布定数線路上の位置は、第1の分布定数線路の端から基本波の1/4波長のところであり、第1の共振回路は、2次高調波の周波数で直列共振することを特徴とする。

20

## 【0017】

これにより、第1の分布定数線路の線路長が基本波の1/2波長となるので、第1の信号における基本波の位相が180度回転する。また、第1の共振回路は、第1の分布定数線路の端から基本波の1/4波長のところ、すなわち2次高調波の1/2波長のところに接続されているので、第1の共振回路の両端において、2次高調波の位相は互いに反転している。さらに、第1の共振回路は、2次高調波の周波数で直列共振するので、2次高調波に対して短絡回路として働く。したがって、第1および第2の増幅素子の出力端において、2次高調波は相殺されることとなる。このように、各増幅素子の出力端に、個別に共振回路を設けなくとも、1つの共振回路によって構成される小型の電力増幅器が提供されることとなる。

30

## 【0018】

好ましくは、第1の共振回路は、インダクタおよびコンデンサが対称に配置された直列共振回路であるとよい。これにより、第1の共振回路の両端から見たときのインピーダンスのずれを防止することができる。

## 【0019】

好ましくは、第1の共振回路は、短絡させたい偶数次高調波成分の波長の1/2の電気長を有する分布定数線路であるとよい。これにより、第1の共振回路の両端から見たときのインピーダンスのずれ防止できると共に、素子点数を低減することができる。

40

## 【0020】

好ましくは、第1および第2の信号をそれぞれ第1および第2の増幅素子に入力するための電力分配器をさらに備え、電力分配器は、入力される信号を二分配し、一方を第1の信号として第1の増幅素子に入力する分配手段と、分配手段からの他方の信号における基本波成分の位相を反転させる線路長を有し、当該位相を反転させた信号を第2の信号として第2の増幅素子に入力する第2の分布定数線路と、短絡させたい偶数次高調波成分の位相が反転する第2の分布定数線路上の位置と第2の増幅素子の入力側との間に接続され、短絡させたい偶数次高調波成分の周波数で直列共振する第2の共振回路とを含む。

## 【0021】

50

これにより、偶数次高調波が短絡されている第1および第2の信号が入力されることとなる。第1および第2の信号を入力するための電力分配器では、所望の偶数次高調波成分の周波数で直列共振し、かつ当該偶数次高調波の位相が反転する位置に接続されている一つの共振回路が、第1および第2の増幅素子で発生する偶数次高調波を相殺する。このように、1つの共振回路によって偶数次高調波歪みの発生が抑えられている信号を入力することができるので、電力分配器が内蔵されている小型の電力増幅器を提供することができる。1つの共振回路を用いるので、特性ばらつきを低減することができる。

#### 【0022】

好ましくは、第2の分布定数線路の線路長は、基本波の1/2波長であり、第2の共振回路を接続するための第2の分布定数線路上の位置は、第2の分布定数線路の端から基本波の1/4波長のところであり、第2の共振回路は、2次高調波の周波数で直列共振することを特徴とする。10

#### 【0023】

これにより、第2の分布定数線路の線路長が基本波の1/2波長となるので、入力信号における基本波の位相が180度回転する。また、第2の共振回路は、第2の分布定数線路の端から基本波の1/4波長のところ、すなわち2次高調波の1/2波長のところに接続されているので、第2の共振回路の両端において、2次高調波の位相は互いに反転している。さらに、第2の共振回路は、2次高調波の周波数で直列共振するので、2次高調波に対して短絡回路として働く。したがって、第1および第2の増幅素子の入力端において、2次高調波は相殺されることとなり、2次高調波歪みの発生を抑圧する小型の電力増幅器が提供されることとなる。20

#### 【0024】

好ましくは、第2の共振回路は、インダクタおよびコンデンサが対称に配置された直列共振回路であるとよい。これにより、第2の共振回路の両端から見たときのインピーダンスのずれを防止することができる。

#### 【0025】

好ましくは、第2の共振回路は、短絡させたい偶数次高調波成分の波長の1/2の電気長を有する分布定数線路であるとよい。これにより、第2の共振回路の両端から見たときのインピーダンスのずれ防止できると共に、素子点数を低減することができる。

#### 【0026】

また、本発明は、高周波信号を増幅するための電力増幅器であって、第1の信号、および第1の信号と逆相の第2の信号を出力する電力分配器と、第1の信号を増幅するための第1の増幅素子と、第1の増幅素子とプッシュプル型に接続されており、第2の信号を増幅するための第2の増幅素子と、第1の増幅素子によって増幅された第1の信号における基本波成分の位相を反転させて、当該位相を反転させた第1の信号と第2の増幅素子によって増幅された第2の信号と合成して出力する電力合成器とを備え、電力分配器は、入力される信号を二分配し、一方を第1の信号として第1の増幅素子に入力する分配手段と、分配手段からの他方の信号における基本波成分の位相を反転させる線路長を有し、当該位相を反転させた信号を第2の信号として第2の増幅素子に入力する分布定数線路と、短絡させたい偶数次高調波成分の位相が反転する分布定数線路上の位置と第2の増幅素子の入力側との間に接続され、短絡させたい偶数次高調波成分の周波数で直列共振する共振回路とを含む。30

#### 【0027】

これにより、偶数次高調波歪みの発生を抑圧する電力分配器が内蔵された電力増幅器が提供されることとなる。

#### 【0028】

好ましくは、分布定数線路の線路長は、基本波の1/2波長であり、共振回路を接続するための分布定数線路上の位置は、分布定数線路の端から基本波の1/4波長のところであり、共振回路は、2次高調波の周波数で直列共振するとよい。これにより、2次高調波歪みの発生を抑圧する電力分配器が提供されることとなる。40

**【 0 0 2 9 】**

好ましくは、共振回路は、インダクタおよびコンデンサが対称に配置された直列共振回路であるとよい。これにより、共振回路の両端から見たときのインピーダンスのずれを防止することができる。

**【 0 0 3 0 】**

好ましくは、共振回路は、短絡させたい偶数次高調波成分の波長の $1/2$ の電気長を有する分布定数線路であるとよい。これにより、共振回路の両端から見たときのインピーダンスのずれ防止できると共に、素子点数を低減することができる。

**【 0 0 3 1 】**

また、本発明は、入力信号を二分配するための電力分配器であって、入力信号の電力を二分配する分配手段と、分配手段によって二分配された一方の信号を、第1の信号として出力するための第1の出力端子と、分配手段によって二分配された他方の信号における基本波成分の位相を反転させる線路長を有し、当該位相を反転させた信号を第2の信号とするための分布定数線路と、分布定数線路からの第2の信号を出力するための第2の出力端子と、短絡させたい偶数次高調波成分の位相が反転する分布定数線路上の位置と第1の出力端子との間に接続され、短絡させたい偶数次高調波成分の周波数で直列共振する共振回路とを備える。10

**【 0 0 3 2 】**

これにより、偶数次高調波歪みの発生を抑圧する電力分配器が提供されることとなる。

**【 0 0 3 3 】**

好ましくは、分布定数線路の線路長は、基本波の $1/2$ 波長であり、共振回路を接続するための分布定数線路上の位置は、分布定数線路の端から基本波の $1/4$ 波長のところであり、共振回路は、2次高調波の周波数で直列共振することを特徴とする。20

**【 0 0 3 4 】**

これにより、2次高調波歪みの発生を抑圧する電力分配器が提供されることとなる。

**【 0 0 3 5 】**

好ましくは、共振回路は、インダクタおよびコンデンサが対称に配置された直列共振回路であることとよい。これにより、共振回路の両端から見たときのインピーダンスのずれを防止することができる。

**【 0 0 3 6 】**

好ましくは、共振回路は、前記短絡させたい偶数次高調波成分の波長の $1/2$ の電気長を有する分布定数線路であるとよい。これにより、第1の共振回路の両端から見たときのインピーダンスのずれ防止できると共に、素子点数を低減することができる。30

**【 0 0 3 7 】**

また、本発明は、入力される第1の信号と第2の信号とを合成するための電力合成器であって、第1の信号を入力するための第1の入力端子と、第2の信号を入力するための第2の入力端子と、第2の入力端子からの第2の信号における基本波成分の位相を反転させる線路長を有する分布定数線路と、短絡させたい偶数次高調波成分の位相が反転する分布定数線路上の位置と第1の入力端子との間に接続され、短絡させたい偶数次高調波成分の周波数で直列共振する共振回路と、第1の入力端子からの第1の信号と、分布定数線路からの信号とを合成する合成手段とを備える。40

**【 0 0 3 8 】**

これにより、偶数次高調波歪みの発生を抑圧する電力合成器が提供されることとなる。

**【 0 0 3 9 】**

好ましくは、分布定数線路の線路長は、基本波の $1/2$ 波長であり、共振回路を接続するための分布定数線路上の位置は、分布定数線路の端から基本波の $1/4$ 波長のところであり、共振回路は、2次高調波の周波数で直列共振することを特徴とする。

**【 0 0 4 0 】**

これにより、2次高調波歪みの発生を抑圧する電力合成器が提供されることとなる。

**【 0 0 4 1 】**

10

20

30

40

50

好ましくは、共振回路は、インダクタおよびコンデンサが対称に配置された直列共振回路であるとよい。これにより、第1の共振回路の両端から見たときのインピーダンスのずれを防止することができる。

#### 【0042】

好ましくは、共振回路は、前記短絡させたい偶数次高調波成分の波長の $1/2$ の電気長を有する分布定数線路であるとよい。これにより、第1の共振回路の両端から見たときのインピーダンスのずれ防止できると共に、素子点数を低減することができる。

#### 【発明の効果】

#### 【0043】

本発明によれば、所望の偶数次高調波成分の周波数で直列共振し、かつ当該偶数次高調波の位相が反転する位置に接続されている一つの共振回路が、第1および第2の増幅素子で発生する偶数次高調波を相殺する。プッシュプル型の電力増幅器で用いられる二つの増幅素子毎に偶数次高調波歪みの発生を抑圧するための共振回路をそれぞれ設ける場合に比べ、一つの共振回路によって偶数次高調波歪みの発生を抑えることができるので、回路が小型化される電力増幅器、電力分配器および電力合成器を提供することができ、特性ばらつきを低減することができる。

10

#### 【発明を実施するための最良の形態】

#### 【0044】

以下、本発明の実施形態について説明する。

20

#### (第1の実施形態)

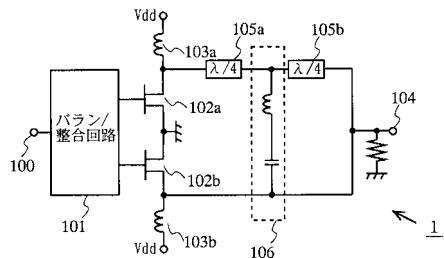

図1は、本発明の第1の実施形態に係る電力増幅器1の構成を示す図である。図1において、電力増幅器1は、入力端子100と、バラン/整合回路101と、第1の増幅素子102aと、第2の増幅素子102bと、第1の増幅素子102aのドレインに接続されたインダクタ103aと、第2の増幅素子102bのドレインに接続されたインダクタ103bと、出力端子104と、出力端子104と第1の増幅素子102aのドレインとの間に接続された分布定数線路105a, 105bと、直列共振回路106とを含む。第1の増幅素子102aと第2の増幅素子102bとは、同一規格である。

20

#### 【0045】

直列共振回路106の一端は、分布定数線路105aと分布定数線路105bとの間に並列に接続されている。他端は、第2の増幅素子102bのドレインと出力端子104との間に並列に接続されている。直列共振回路106は、基本波の2次高調波の周波数で共振するように設定されている。

30

#### 【0046】

入力端子100に入力される信号における基本波成分の波長を $\lambda$ とする。分布定数線路105a, 105bの長さは、基本波の $1/4$ 波長の長さ、すなわち、 $\lambda/4$ である。なお、図1では、説明を分かりやすくするために、分布定数線路105aと分布定数線路105bとの間が離れているように記載したが、実際は、二つの分布定数線路は、つながっており、基本波の $1/2$ 波長の長さの分布定数線路を構成している。直列共振回路106は、当該分布定数線路における第1の増幅素子102aのドレイン側から基本波の $1/4$ 波長の位置に、接続されている。

40

#### 【0047】

バラン/整合回路101は、入力端子100に入力された基本波の位相を反転させて、互いに逆相の基本波成分を有する第1および第2の信号を出力する。第1および第2の増幅素子102a, 102bは、バラン/整合回路101から出力される互いに逆相の二つの信号を増幅する。分布定数線路105aおよび分布定数線路105bによって、第1の増幅素子102aから出力された信号は、位相が180度回転させられ、第2の増幅素子102bから出力された信号と合波されて、出力端子104から出力される。

#### 【0048】

第1および第2の増幅素子102a, 102bで発生する2次高調波は互いに同相である。基本波の周波数を $f_0$ とした場合、2次高調波の波長 $\lambda_2$ は、 $1/(2f_0)$ となる

50

したがって、分布定数線路 105a の線路長は、2 次高調波に対して、1 / 2 波長となる。よって、分布定数線路 105a によって、2 次高調波の位相は 180 度回転する。直列共振回路 106 は 2 次高調波の周波数で共振すると想定したので、分布定数線路 105a によって 180 度位相が回転した 2 次高調波と第 2 の増幅素子 102b から出力される 2 次高調波とは、互いに打ち消し合うこととなる。結果、電力増幅器 1 は、2 次歪みを抑圧することができる。

#### 【0049】

##### (第 2 の実施形態)

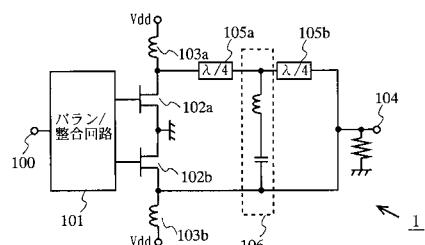

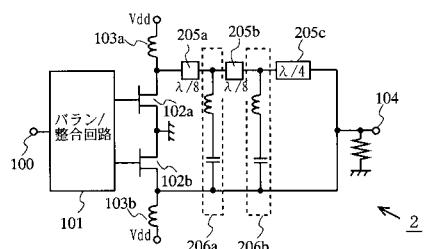

図 2 は、本発明の第 2 の実施形態に係る電力増幅器 2 の構成を示す図である。図 2 において、電力増幅器 2 は、入力端子 100 と、バラン / 整合回路 101 と、第 1 の増幅素子 102a と、第 2 の増幅素子 102b と、第 1 の増幅素子 102a のドレインに接続されたインダクタ 103a と、第 2 の増幅素子 102b のドレインに接続されたインダクタ 103b と、出力端子 104 と、出力端子 104 と第 1 の増幅素子 102a のドレインとの間に接続された分布定数線路 205a, 205b, 205c と、直列共振回路 206a, 206b を含む。なお、図 2 において、電力増幅器 1 と同一の部分については、図 1 に示したのと同一の参照符号を付し、説明を省略する。

#### 【0050】

直列共振回路 206a の一端は、分布定数線路 205a と分布定数線路 205b との間に並列に接続されている。その他端は、第 2 の増幅素子 102b のドレインと出力端子 104 との間に並列に接続されている。直列共振回路 206a は、基本波の 4 次高調波の周波数で共振するように設定されている。

#### 【0051】

直列共振回路 206b の一端は、分布定数線路 205b と分布定数線路 205c との間に並列に接続されている。その他端は、第 2 の増幅素子 102b のドレインと出力端子 104 との間に並列に接続されている。直列共振回路 206b は、基本波の 2 次高調波の周波数で共振するように設定されている。

#### 【0052】

分布定数線路 205a, 205b の長さは、基本波の 1 / 8 波長の長さである。分布定数線路 205c の長さは、基本波の 1 / 4 波長の長さである。なお、図 2 では、説明を分かりやすくするために、分布定数線路 205a, 205b, 205c がそれぞれ離れているように記載したが、実際は、三つの分布定数線路は、つながっており、基本波の 1 / 2 波長の長さの分布定数線路を構成している。直列共振回路 206a は、当該分布定数線路における第 1 の増幅素子 102a のドレイン側から基本波の 1 / 8 波長の位置に、接続されている。また、直列共振回路 206b は、当該分布定数線路における第 1 の増幅素子 102a のドレイン側から基本波の 1 / 4 波長の位置に、接続されている。

#### 【0053】

分布定数線路 205a, 205b, 205c で構成される分布定数線路によって、第 1 の増幅素子 102a から出力された基本波は、位相が 180 度回転させられ、第 2 の増幅素子 102b から出力された基本波と合波されて、出力端子 104 から出力される。

#### 【0054】

また、分布定数線路 205a, 205b で構成される分布定数線路によって、2 次高調波の位相は 180 度回転させられる。直列共振回路 206b は 2 次高調波の周波数で共振するので、180 度位相が回転した 2 次高調波と第 2 の増幅素子 102b から出力される 2 次高調波とは、互いに打ち消し合うこととなる。結果、電力増幅器 2 は、2 次高調波を打ち消すことができる。

#### 【0055】

さらに、分布定数線路 205a によって、4 次高調波の位相は 180 度回転させられる。直列共振回路 206a は 4 次高調波の周波数で共振するので、180 度位相が回転した 4 次高調波と第 2 の増幅素子 102b から出力される 4 次高調波とは、互いに打ち消し合うこととなる。結果、電力増幅器 2 は、4 次高調波を打ち消すことができる。

10

20

30

40

50

## 【0056】

図1および図2に示すように、本発明の実施形態に係る電力増幅器では、打ち消したい偶数次高調波を短絡させるための回路として、当該偶数次高調波の周波数で共振する直列共振回路が、分布定数線路の所定の位置に、一方の増幅素子の出力と他方の増幅素子の出力をバイパスするように接続されている。これにより、偶数次高調波が直列共振回路で相殺されてしまうこととなるので、偶数次高調波歪みの発生を抑圧することができる。

## 【0057】

なお、図1および図2に示すような直列共振回路を有する電力合成側の構成をバラン/整合回路内に設け、互いに逆相の基本波成分を有する第1および第2の信号を出力するよ10にしてよい。

## 【0058】

なお、図1および/または図2では、2次高調波および/または4次高調波を抑圧するための構成を示したが、その他の偶数次高調波を抑圧する場合にも同様の構成を取ることができ。具体的には、 $2n$  ( $n$ は自然数) 次高調波を抑圧したい場合、分布定数線路における増幅端子の出力側から基本波の $1/(4n)$  波長の位置に、相殺したい偶数次高調波の周波数で共振する直列共振回路を接続すればよい。

## 【0059】

なお、直列共振回路を接続する位置は、分布定数線路における増幅端子の出力側から基本波の $1/(4n)$  波長の位置の他、分布定数線路における出力端子側から基本波の $1/(4n)$  波長の位置であってよい。

## 【0060】

また、接続される直列共振回路は、少なくとも1つあれば所望の効果を得ることができる。

## 【0061】

なお、2次高調波の位相が反転する $/4$  の位置では、2次高調波以外の偶数次高調波の位相も反転している。したがって、図1に示す電力増幅器1において、直列共振回路106が、2次高調波以外の偶数次高調波の波長でも直列共振するように、スタブを設けておけば、2次高調波以外の偶数次高調波も打ち消されることとなる。図2に示す場合も同様に、直列共振回路206aまたは206bが、2次高調波以外の偶数次高調波の波長でも直列共振するように、スタブを設けておけば、2次高調波以外の偶数次高調波も打ち消されることとなる。これにより所望の効果を得ることが期待できる。

## 【0062】

## (実施例)

以下、本発明の実施例について説明する。

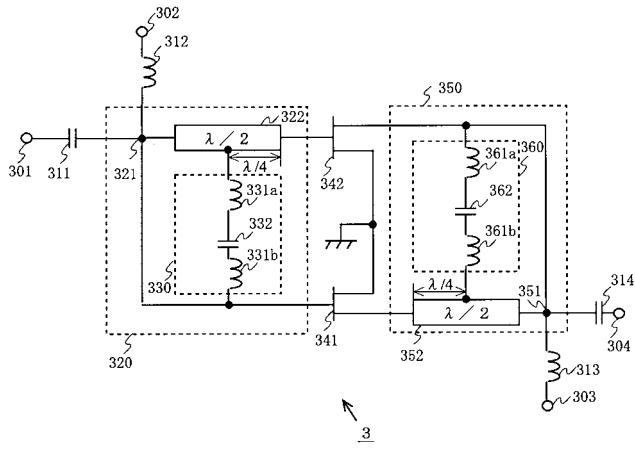

図3は、本発明の電力増幅器の実施例を示す回路図である。図3において、電力増幅器3は、入力端子301と、ゲートバイアス端子302と、ドレインバイアス端子303と、出力端子304と、入力結合コンデンサ311と、ゲートバイアスインダクタ312と、ドレインバイアスインダクタ313と、出力結合コンデンサ314と、第1のFET341と、第2のFET342と、合成端子351と、第1の分布定数線路352と、インダクタ361aと、コンデンサ362と、インダクタ361bと、分配端子321と、第2の分布定数線路322と、インダクタ331aと、コンデンサ332と、インダクタ331bとを含む。

## 【0063】

第1のFET341のソースと第2のFET342のソースとは、それぞれ接地されている。第1および第2のFET341, 342は、第1の実施形態における第1および第2の増幅素子102a, 102bに相当する(図1参照)。

## 【0064】

第2のFET342のドレインと合成端子351とは接続されている。第1のFET341のドレインと合成端子351との間には、第1の分布定数線路352が接続されている。第1の分布定数線路352は、基本波の $1/2$  波長の長さの線路である。第1の分布

定数線路 352において第1のFET341のゲート側から基本波の1/4波長の長さの位置に、直列に接続されたインダクタ361b、コンデンサ362、およびインダクタ361aが、並列に接続される。インダクタ361aの一端は、合成端子351と第2のFET342のドレインとの間に並列に接続される。

#### 【0065】

インダクタ361a、コンデンサ362、およびインダクタ361bによって、第1の直列共振回路360が構成される。第1の直列共振回路360では、基本波の2倍の周波数で直列共振するように、インダクタ361a、コンデンサ362、およびインダクタ361bの値が設定されている。第1の直列共振回路360は、第1の実施形態における直列共振回路106に相当する(図1参照)。第1の直列共振回路360、第1の分布定数線路352、および合成端子351によって、電力合成器350が構成される。第1の直列共振回路360では、インダクタとコンデンサとが、LCLの関係になるように対称に接続されているので、第1の直列共振回路360の両端から見たときのインピーダンスが等しくなり、インピーダンスがずれることによるばらつきを防止することができる。なお、CLCの直列共振回路となるように、第1の直列共振回路360を構成してもよい。

#### 【0066】

合成端子351とドレインバイアス端子303との間には、ドレインバイアスインダクタ313が接続される。合成端子351と出力端子304との間には、出力結合コンデンサ314が接続される。

#### 【0067】

入力端子301と分配端子321との間には、入力結合コンデンサ311が接続されている。ゲートバイアス端子302と分配端子321との間には、ゲートバイアスインダクタ312が接続されている。

#### 【0068】

分配端子321と第2のFET342のゲートとの間には、第2の分布定数線路322が接続されている。分配端子321と第1のFET341のゲートとは接続されている。第2の分布定数線路322は、基本波の1/2波長の長さの線路である。第2の分布定数線路322において第2のFET342のゲート側から基本波の1/4波長の長さの位置に、直列に接続されたインダクタ331a、コンデンサ332、およびインダクタ331bが、並列に接続される。インダクタ331bの一端は、分配端子321と第1のFET341のゲートとの間に並列に接続される。

#### 【0069】

インダクタ331a、コンデンサ332、およびインダクタ331bによって、第2の直列共振回路330が構成される。第2の直列共振回路330において、基本波の2倍の周波数で直列共振するように、インダクタ331a、コンデンサ332、およびインダクタ331bの値が設定されている。第2の直列共振回路330、第2の分布定数線路322、および分配端子321によって、電力分配器320が構成される。電力分配器320は、第1の実施形態におけるバラン/整合回路101に相当する(図1参照)。第2の直列共振回路330では、インダクタとコンデンサとが、LCLの関係になるように対称に接続されているので、第2の直列共振回路330の両端から見たときのインピーダンスが等しくなり、インピーダンスがずれることによるばらつきを防止することができる。なお、CLCの直列共振回路となるように、第2の直列共振回路330を構成してもよい。

#### 【0070】

以下、図3に示す電力増幅器3の動作について説明する。

入力端子301に入力された基本波は、入力結合コンデンサ311を介して、電力分配器320の分配端子321に入力され、第1および第2の信号として分配される。分配端子321からの第2の入力信号は、基本波の1/2波長の長さを有する第2の分布定数線路322を介して、第2のFET342のゲートに入力される。分配端子321からの第1の信号は、第1のFET341のゲートに直接入力される。

#### 【0071】

10

20

30

40

50

第2の分布定数線路322によって、第2の信号における基本波成分および奇数次高調波成分の位相が180度回転する。したがって、第2のFET342のゲートに入力される信号と第1のFET341のゲートに入力される信号とは、基本波成分および奇数次高調波成分において逆位相となり、偶数次高調波成分において同相となる。なお、ゲートバイアスはゲートバイアス端子302からゲートバイアスインダクタ312を介して印加される。

#### 【0072】

第2の直列共振回路330は、第2の分布定数線路322において第2のFET342のゲート側から基本波の1/4波長の長さの所、すなわち、2次高調波に対して1/2波長の長さの所に接続されている。したがって、第2の直列共振回路330と第2の分布定数線路322との接続点では、2次高調波の位相は180度回転していることとなるので、第2の直列共振回路330の両端における2次高調波は互いに逆相となる。第2の直列共振回路330は、2次高調波の周波数で直列共振し、短絡回路として働くので、2次高調波は相殺される。よって、第1のFET341および第2のFET342のゲート端では、2次高調波が存在しないこととなる。

#### 【0073】

第2のFET342で増幅された第2の信号は、合成端子351に入力される。一方、第1のFET341で増幅された第1の信号は、基本波の1/2波長の長さを有する第1の分布定数線路352を介して、合成端子351に入力される。第1の分布定数線路352によって、第1の入力信号における基本波成分および奇数次高調波成分の位相が180度回転する。したがって、合成端子351において、第2のFET342から出力される第2の信号と第1のFET341から出力される第1の信号とは、基本波成分および奇数次高調波成分において同相となる。なお、ドレインバイアスはドレインバイアス端子303からドレインバイアスインダクタ313を介して印加される。

#### 【0074】

第1の直列共振回路360は、第1の分布定数線路352において第1のFET341のドレイン側から基本波の1/4波長の長さの所、すなわち、2次高調波に対して1/2波長の長さの所に接続されている。したがって、第1の直列共振回路360と第1の分布定数線路352との接続点では、2次高調波の位相は180度回転している。第1の増幅素子341から出力される信号および第2の増幅素子342から出力される信号において、2次高調波は互いに同相であるので、第1の直列共振回路360の両端における2次高調波は互いに逆相となる。第1の直列共振回路360は、2次高調波の周波数で直列共振し、短絡回路として働くので、2次高調波は相殺される。よって、第1のFET341および第2のFET342のドレイン端では、2次高調波が存在しないこととなる。

#### 【0075】

このように、図3に示す回路構成を有する電力増幅器では、二つのFETの入出力端で2次高調波が存在しないこととなるので、歪みが抑圧され、高い効率が得られることとなる。また、2次高調波を打ち消すための構成として、電力分配器側に一つの直列共振回路を設け、電力合成器側に一つの直列共振回路を設けるだけでよいので、小型化された電力増幅器が提供されることとなる。さらに、2次高調波を打ち消すための短絡回路として、電力分配器または電力合成器において、それぞれ一つの直列共振回路が用いられることとなるので、短絡回路のばらつきをなくすことができる。結果、パワー特性のばらつきが低減される電力増幅器が提供されることとなる。

#### 【0076】

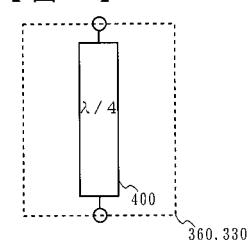

なお、第1の直列共振回路360および/または第2の直列共振回路330は、分布定数回路であってもよい。図4は、第1の直列共振回路360および/または第2の直列共振回路330を分布定数線路400としたときの図を示す。図4において、第1の直列共振回路360および/または第2の直列共振回路330は、基本波の波長の1/4の電気長（2次高調波の波長の1/2の電気長）を有する分布定数線路400からなる。分布定数線路400の両端において、2次高調波は互いに逆相となるので、分布定数線路400

10

20

30

40

50

の両端では、2次高調波は相殺される。

【0077】

インダクタおよびコンデンサなどの受動素子から構成される直列共振回路が、高い周波数において、直列共振回路の両端で高調波のインピーダンスを完全に制御することは、困難である。しかし、分布定数線路からなる直列共振回路を用いることにより、高い周波数においても、分布定数線路その両端で高調波のインピーダンスを高い精度で容易に制御することができる。したがって、直列共振回路に分布定数線路を用いることによって、高い周波数においても、高調波成分を相殺することが可能となる。

【0078】

また、図3に示すように、直列共振回路において、受動素子を対称に接続するのが好ましいが、対称な接続とすることによって、受動素子の素子点数が増加することとなる。しかし、分布定数線路を用いれば、両端から見たときのインピーダンスを等しくすることができるので、インピーダンスがずれることによるばらつきを防止することができ、かつ素子点数を低減することができる。

【0079】

なお、図3に示す実施例では、電力分配器および電力合成器に2次高調波の短絡回路として直列共振回路を設けることとしたが、いずれか一方にのみ直列共振回路を設けることとしてもよい。

【0080】

なお、図3に示す電力分配器または電力合波回路は、それぞれ単独の部品として実施することができる。これらの部品は、プッシュプル型の電力増幅器に用いるものに限られない。

【0081】

なお、第1および第2の直列共振回路360, 330は、2次高調波だけでなく、短絡させたい他の偶数次高調波に対しても同時に直列共振するように構成されていてもよい。これにより、2次高調波以外の偶数次高調波の発生を抑圧することができ、高効率化が図れる。

【0082】

また、第1および第2の直列共振回路360, 330の接続位置は、第1および第2の分布定数線路352, 322のいずれかの端辺から偶数次高調波の1/2波長の長さの位置に接続されていてもよい。これにより、短絡させたい偶数次高調波の発生を抑圧することができる。

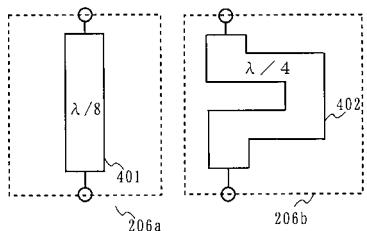

【0083】

たとえば、2次高調波および4次高調波の発生を抑圧したい場合、各直列共振回路を分布定数線路とする構成を考える。図5は、2次高調波および4次高調波の発生を抑圧したい場合、各直列共振回路を分布定数線路とする構成を示す図である。基本波の波長の1/8の電気長(4次高調波の波長の1/2の電気長)を有する分布定数線路401は、図2に示す直列共振回路206aの役割を果たす。また、基本波の波長の1/4の電気長(2次高調波の波長の1/2の電気長)を有する分布定数線路402は、図2に示す直列共振回路206bの役割を果たす。このように、短絡させたい偶数次高調波に対して共振するような分布定数線路を図2に示すような受動素子を用いた直列共振回路の代わりに接続することで、偶数次高調波の発生を抑圧することができ、高効率化が図れる。ここで、短絡させたい偶数次高調波に対して共振するような分布定数線路の電気長は、短絡させたい偶数次高調波の波長の1/2の電気長となる。なお、図5に示すように、長い方の分布定数線路402は、折り曲げるなどして、短い方の分布定数線路401と端が一直線上に並ぶようにすればよい。また、分布定数線路同士を立体交差させるなどして、端が一直線上に並ぶようにしてもよい。同様のことが、その他の偶数次高調波についても言える。

【0084】

さらに、以上の構成に奇数次高調波を制御する回路を組み合わせれば、さらに高い効率が期待できる。

10

20

30

40

50

## 【産業上の利用可能性】

## 【0085】

本発明にかかる電力増幅器、電力分配器および電力合成器は、小型でかつ特性ばらつきが小さく高効率であるので、通信機器等の分野において有用である。

## 【図面の簡単な説明】

## 【0086】

【図1】本発明の第1の実施形態に係る電力増幅器1の構成を示す図

【図2】本発明の第2の実施形態に係る電力増幅器2の構成を示す図

【図3】本発明の電力増幅器の実施例を示す回路図

【図4】第1の直列共振回路360および／または第2の直列共振回路330を分布定数線路400としたときの図 10

【図5】2次高調波および4次高調波の発生を抑圧したい場合、各直列共振回路を分布定数線路とする構成を示す図

【図6】従来のプッシュプル型の高周波電力増幅器の構成を示す図

【図7】高調波に対するインピーダンスを考慮した整合回路を設けた従来のプッシュプル型の電力増幅器の構成を示す図

【図8】図7に示す電力増幅器におけるFETのドレイン電圧vdおよびドレイン電流idの波形を示す図

## 【符号の説明】

## 【0087】

20

1, 2, 3, 電力増幅器

100, 301 入力端子

101 バラン／整合回路

102a 第1の増幅素子

102b 第2の増幅素子

103a, 103b インダクタ

104, 304 出力端子

105a, 105b, 205a, 205b, 205c 分布定数線路

106, 206a, 206b 直列共振回路

321 分配端子

30

351 合成端子

341 第1のFET

342 第2のFET

352 第1の分布定数線路

322 第2の分布定数線路

360 第1の直列共振回路

330 第2の直列共振回路

320 電力分配器

350 電力合成器

302 ゲートバイアス端子

40

303 ドレインバイアス端子

311 入力結合コンデンサ

312 ゲートバイアスインダクタ

313 ドレインバイアスインダクタ

314 出力結合コンデンサ

331a, 331b, 361a, 361b インダクタ

332, 362 コンデンサ

400, 401, 402 分布定数線路

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

## フロントページの続き

F ターム(参考) 5J067 AA04 AA15 AA41 CA00 CA36 CA92 FA00 FA12 HA09 HA29

HA32 HA33 KA00 KA13 KA29 KA47 KA68 KS01 LS00 MA21

TA06

5J500 AA04 AA15 AA41 AC00 AC36 AC92 AF00 AF12 AH09 AH29

AH32 AH33 AK00 AK13 AK29 AK47 AK68 AM21 AT06 RG00