(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5425585号

(P5425585)

(45) 発行日 平成26年2月26日(2014.2.26)

(24) 登録日 平成25年12月6日(2013.12.6)

(51) Int.Cl.

H03F 3/45 (2006.01)

F 1

H03F 3/45

A

請求項の数 2 外国語出願 (全 12 頁)

(21) 出願番号 特願2009-240433 (P2009-240433)

(22) 出願日 平成21年10月19日 (2009.10.19)

(65) 公開番号 特開2010-148094 (P2010-148094A)

(43) 公開日 平成22年7月1日 (2010.7.1)

審査請求日 平成24年9月7日 (2012.9.7)

(31) 優先権主張番号 12/339,572

(32) 優先日 平成20年12月19日 (2008.12.19)

(33) 優先権主張国 米国(US)

(73) 特許権者 500575824

ハネウェル・インターナショナル・インコ

ーポレーテッド

アメリカ合衆国ニュージャージー州079

62-2245, モーリスタウン, コロン

ピア・ロード 101, ピー・オー・ボッ

クス 2245

(74) 代理人 100140109

弁理士 小野 新次郎

(74) 代理人 100089705

弁理士 社本 一夫

(74) 代理人 100075270

弁理士 小林 泰

(74) 代理人 100080137

弁理士 千葉 昭男

最終頁に続く

(54) 【発明の名称】マルチ・モード増幅器

## (57) 【特許請求の範囲】

## 【請求項 1】

マルチ・モードで動作可能な増幅器において、

第1及び第2の電圧入力と、

第1及び第2の双方向性の電流出力であって、実質的に同じ振幅と実質的に同じ極性を有する双方向性の第1及び第2の電流出力と、

第3の双方向性の電流出力を備え、

該第3の双方向性の電流出力は、実質的に第1及び第2の電流出力の振幅と同じ振幅を有し、該第3の双方向性の電流出力は、第1及び第2の双方向性の電流出力の極性と実質的に反対の極性を有し、

前記増幅器が、前記第1の双方向性の電流出力、及び、前記第2の双方向性の電流出力が、一緒に結合されるときに、第1のモードで動作し、

前記増幅器が、前記第1の双方向性の電流出力と前記第2の双方向性の電流出力の1つが、前記第2の電圧入力に結合されるときに、第2のモードで動作する、

ことを特徴とする増幅器。

## 【請求項 2】

請求項1記載の増幅器において、前記増幅器が、

前記第1の双方向性の電流出力と、前記第2の双方向性の電流出力の1つが、フロー・ティング(浮遊)状態であるときに、第1のモードで動作する、

ことを特徴とする増幅器。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、マルチ・モード増幅器に関する。

なお、米国政府が、空軍調査研究所との契約番号 F A 8 6 5 0 - 0 5 - C - 5 7 0 7 に遵守する本発明の確実性権利を獲得している。

## 【背景技術】

## 【0002】

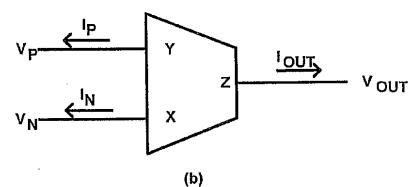

集積回路設計での2つの重要アナログ構成要素はオペレーション増幅器（“オペアンプ”）とタイプII電流搬送器（“C C I I”（Second Generation Current Conveyor: 第2世代電流搬送器）である。図1(a)に、2つの入力と単一出力を有する高利得増幅器であるオペアンプを示す。図示のように、オペアンプは電圧 $V_p$ と電流 $I_p$ を有する正の入力と、電圧 $V_N$ と電流 $I_N$ を有する負の入力と、電圧 $V_{OUT}$ と電流 $I_{OUT}$ を有する出力とを有する。理想的には、入力電流 $I_p$ と $I_N$ がゼロと成るよう入力インピーダンスは極めて高い。更に、オペアンプは理想的には、これら2つの入力間の差分を開放利得 $A_v$ で増幅する差動増幅器として動作するものであって、該開放利得 $A_v$ は典型的には非常に大きい（例えば、 $A_v > 10,000$ ）。したがって、オペアンプの動作は $V_{OUT} = A_v (V_p - V_N)$ として表現される。実際には、大部分のアプリケーションでは、必要とされる増幅利得は開放利得 $A_v$ よりはるかに小さい。このようなことから、オペアンプは、通常、閉成ループ動作を行うように何らかの形態の帰還を備えるよう構成される。この構成においては、オペアンプは $V_p = V_N$ が確実となるように、 $V_{OUT}$ の値を出力する。従って、オペアンプの動作は次の2つの近似式で定義され、すなわち、(1)  $V_p - V_N = 0$  及び (2)  $I_p = I_N = 0$  である。オペアンプの実装形態には種々異なる形態がある。10

## 【0003】

図1(b)は、C C I Iを示し、このC C I Iもまた2つの入力と単一の出力を有する。図示のように、C C I Iは、電圧 $V_p$ と電流 $I_p$ を有する正の入力Yと、電圧 $V_N$ と電流 $I_N$ を有する負の入力Xと、電圧 $V_{OUT}$ と電流 $I_{OUT}$ を有する出力Zとを有する。理想的には、負の入力Xのインピーダンスは非常に低く、正の端子Yのインピーダンスは非常に高い。C C I Iの動作は3つの近似式で定義される、すなわち (1)  $V_N = V_p$ 、(2)  $I_{OUT} = I_N$ 、及び (3)  $I_p = 0$  である。C C I Iの実装形態には種々異なる形態がある。20

## 【発明の開示】

## 【発明が解決しようとする課題】

## 【0004】

集積回路設計者は、同様な機能を実現するにあたり、オペアンプ及び/又はC C I Iを使用可能であるが、オペアンプとC C I Iはそれぞれ個別の作用効果と問題点とを有している。すなわち、オペアンプはあるアプリケーションにはより適切であり、他方C C I Iはその他のアプリケーションに対してより適切である。集積回路設計者は、通常、これら作用効果と問題点とを校了して、新しいアプリケーションそれぞれについて、どちらの構成要素を使用するかを判断しなければならない。これにより、集積回路設計者のライブラリには双方の構成要素が含まれていなければならない。したがって、オペアンプとC C I Iの双方として機能する単一のアナログ構成要素を実現することが望まれている。30

文脈により明示されない限りにおいて、本発明の異なる実施例は一緒に用いることができる。

## 【課題を解決するための手段】

## 【0005】

ここで開示される例示的な増幅器は、マルチ・モードで動作可能である。一つの特徴では、例示的な増幅器は、(a)第1及び第2の電圧入力と、(b)実質的に同じ振幅と実質的に同じ極性を有する第1及び第2の電流出力とを含む。この点において、例示的な増4050

幅器は、(a) 差動増幅回路の形態と(b) 第2の出力ステージを有する形態をとり、該差動増幅回路は、第1及び第2の電圧入力を受け付ける入力ステージと第1の電流出力を提供する第1の出力ステージとを有し、該第2の出力ステージは、第2の電流出力を提供するものであって、第2の電流出力は第1の電流出力と実質的に同じ振幅と実質的に同じ極性を有している。

#### 【0006】

例示的な増幅器は、マルチモードで動作可能である。例えば、例示的な増幅器は、第1の電流出力と第2の電流出力とが一体に結合されるとき、あるいは第1の電流出力と第2の電流出力の一方が浮遊状態である時に第1のモードで動作する。第1のモードである間は、例示的な増幅器はオペレーションナル増幅器として機能する。他の実施例では、例示的な増幅器は、第2の電流出力が第2の電圧入力に結合される場合には、第2のモードで動作する。第2のモードである間は、例示的な増幅器は、タイプ2の電流搬送器(CCII)として機能する。

#### 【0007】

一実施例では、第1の電圧入力と第2の電圧入力はそれぞれ、高インピーダンスである。他の実施例では、第1の電圧入力は非反転電圧入力であり、第2の電圧入力は反転電圧入力である。

更なる実施例では、第1の電流出力と第2の電流出力はそれぞれ、高インピーダンスである。更なる実施例では、第1の電流出力と第2の電流出力はそれぞれ、第1の電圧入力と第2の電圧入力間の差分の増幅形態である。

#### 【0008】

更なる実施例では、例示的な増幅器は、追加的に第3の電流出力(例えば、第3の出力ステージで提供される)を含んでおり、該第3の電流出力は、(a) 実質的に第1及び第2の電流出力の振幅と同じ振幅を有し、第3の電流出力は(b) 第1及び第2の電流出力の極性と実質的に反対の極性を有する。この点において、第1の電流出力と第2の電流出力の一方がフローティング(浮遊)状態である時には、増幅器は4端子フローティング・ヌラー(nullor)として機能する。

#### 【0009】

また、開示される電圧基準回路は例示的増幅器に基づく回路である。電圧基準回路において、例示的増幅器の第1の電圧入力は、(a) 第1の抵抗器と並列に接続される第1のダイオードを介してグランドに接地され、また(b) 第2の抵抗器を介して電流出力に接続される。例示的増幅器の第2の電圧入力は、(a) 直列に接続される第4の抵抗器と第2のダイオードと並列に結合される第3の抵抗器を介してグランドに接地され、また(b) 第5の抵抗器を介して第1の電流出力に接続される。この構成において、第1及び第2の電流出力は一定のバンドギャップを提供する。第2の電流出力は第6の抵抗器を介してグランドに接地される、また第6の抵抗器の両端の電圧は基準電圧である。

#### 【0010】

これらの特徴は、その他の特徴及び利点と同じく、通常の当業者は添付の図面を参照して以下の詳細な説明を読むことで明らかになるであろう。更には、本明細書に記載される実施の形態は単なる実施例を示すものであり、本発明の範囲を限定するものではないことは理解されるべきである。

#### 【図面の簡単な説明】

#### 【0011】

【図1】オペレーションナル増幅器(オペアンプ)とタイプ2電流搬送器(CCII)を示す図である。

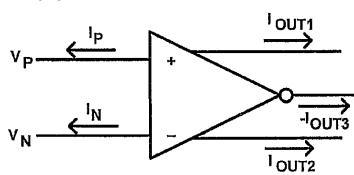

【図2】第1の例示的増幅器とその可能な構成を示す図である。

【図3】第1の例示的増幅器の実施の形態を示す図である。

【図4】第2の例示的増幅器を示す図である。

【図5】第2の例示的増幅器の実施の形態を示す図である。

【図6】第1の例示的増幅器に基づく電圧基準回路を示す図である。

10

20

30

40

50

**【発明を実施するための形態】**

**【0012】**

明示されない限りにおいて、本発明の異なる実施例は共同に用いることができる。

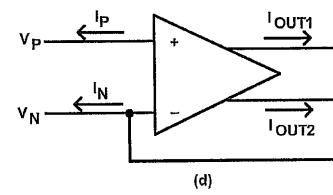

本明細書に開示される例示的な増幅器は多種多様な形態で動作可能な増幅器である。図面を参照すると、図2(a)は例示的な増幅器を示すものであって、増幅器は、(a)第1及び第2の入力と(b)第1及び第2の出力を含む。(ただし、図2の(a)は、第1の例示的な増幅器を示し、オペアンプ("op-amp")に共通な三角記号を用いて示しており、第1の例示的な増幅器は、タイプ2の電流搬送器("CCI"(Second Generation Current Conveyor:第2世代電流搬送器))についての記号を用いて示しても良い。図示しないが、第1の例示的な増幅器はまた第1と第2の電力入力を含んでいる。)

**【0013】**

第1の例示的な増幅器の第1入力は、電圧 $V_p$ と電流 $I_p$ を有する正の(非反転)入力であり、例示的な増幅器の第2入力は、電圧 $V_N$ と電流 $I_N$ を有する負の(すなわち、反転)入力である。好適には、第1の例示的な増幅器の第1及び第2の入力は、入力電流 $I_p$ 及び $I_N$ がほぼゼロであるような高インピーダンスを有する電圧入力である。

**【0014】**

第1の例示的な増幅器の第1の出力は、好ましくは、電流 $I_{OUT_1}$ を有する電流出力であり、また第1の例示的な増幅器の第2の出力は、好ましくは、電流 $I_{OUT_2}$ を有する電流出力である。更に、第1の例示的な増幅器の第1及び第2の電流出力は、好ましくは、実質的に同じ振幅(例えば、1%以内)と実質的に同じ極性を有する。これをわかりやすくすると、第1の例示的な増幅器の第1と第2の出力は、高インピーダンスを有している。

**【0015】**

第1の例示的な増幅器は、好ましくは、2つの電圧入力の差分を大きな利得で増幅するよう動作する。更に、何らかの形態の帰還を備えて構成される場合、第1の例示的な増幅器は、好ましくは、 $V_p = V_N$ を確実に実現する電流出力での値を出力するよう動作する。そのようなものとして、第1の例示的な増幅器の電流出力は、 $I_{OUT_1} = I_{OUT_2} = G(V_p - V_N)$ として表示される。加えて、第1及び第2の電流出力はそれぞれ、抵抗 $R_L$ を有する負荷抵抗器(図示せず)に接続される場合、第1の例示的な増幅器の電圧出力は $V_{OUT_1} = V_{OUT_2} = A_v(V_p - V_N)$ として表示される。ここで $A_v = G * R_L$ である。

**【0016】**

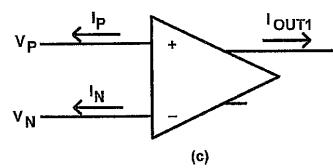

そして、第1の例示的な増幅器の2つの整合した電流出力がどのように得られるかにより、第1の例示的な増幅器は異なる多種多様なモードで動作する。例えば、図2(b)に示されるように、第1の例示的な増幅器は、第1の電流出力と第2の電流出力が電流 $I_{OUT}$ を有する単一の電流出力を形成するよう結合されるとき、第1のモードで動作する。第1のモードでは、第1の例示的な増幅器は、好ましくはオペアンプとして機能する。この点、第1モードの例示的増幅器の電流出力は、 $I_{OUT_1} = I_{OUT_1} + I_{OUT_2} = 2 * G(V_p - V_N)$ と表示される。更に、仮に電流出力が抵抗 $R_L$ を有する負荷抵抗器(図示せず)に接続される場合、第1の例示的増幅器の電圧出力は $V_{OUT} = A_v(V_p - V_N)$ として表される。ここで $A_v = 2 * G * R_L$ である。更にまた、何らかの形態の帰還を備えている場合、第1モードの例示的増幅器の動作は、以下の2つの近似式で表される。

$$(1) V_p - V_N = 0$$

$$(2) I_p = I_N = 0$$

**【0017】**

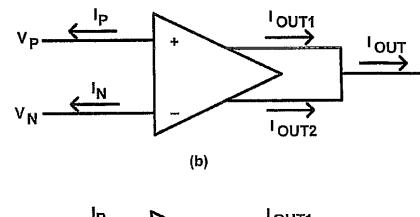

他の実施例では、図2(c)に示されるように、第1の例示的な増幅器は、電流出力の1つが浮遊状態である時、第1のモードで動作する。上述のように、この第1モードの例示的増幅器は、好ましくは、低い利得を有するオペアンプとして機能する。特に、この構

10

20

30

40

50

成により、第1モードの例示的増幅器の電流出力は、 $I_{OUT} = G(V_P - V_N)$ と表示され、電圧出力 $V_{OUT} = A_v(V_P - V_N)$ と表示される。ここで $A_v = G * R_L$ である。この低い利得にも拘らず、何らかの形態の帰還を備えているとき、第1モードの例示的増幅器の動作は、依然として上記近似式、すなわち、 $V_P - V_N = 0$ 及び $I_P = I_N = 0$ で近似される。

#### 【0018】

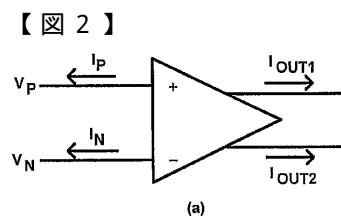

更なる他の実施例では、図2(d)に示されるように、第1の例示的増幅器は、電流出力の1つ(例えば、第2の電流出力)が第2の入力と接続される場合、第2のモードで動作する。この第2のモードでは、第1の例示的増幅器は、好ましくはCCIIとして機能する。この点、第1モードの例示的増幅器の2つの電圧出力は、実質的に同じであり、第2の入力での電流は実質的に整合した電流出力と同じであり、また第2の入力での電流はゼロである。以上から、第2モードの例示的増幅器の動作は、以下の3つの近似式で定義される。すなわち、

$$(1) V_N = V_{OUT} = V_P$$

$$(2) I_{OUT_1} = I_{OUT_2} = I_N$$

$$(3) I_P = 0$$

である。

#### 【0019】

好適には、此処で記載される第1の例示的増幅器により、柔軟性の増加と効率の増加が集積回路設計者に提供される。特に、第1の例示的増幅器は、オペアンプもしくはCCIIとして機能する単一のアナログ構成要素である。

#### 【0020】

したがって、集積回路設計者は、第1の例示的増幅器をオペアンプとCCIIとの代替としてアナログ構成要素のライブラリに組み入れることができ、かくしてライブラリのインフラ・コストを軽減することができる。加えて、集積回路設計者は、オペアンプとCCIIのどちらかがより集積回路に適しているかを始めに判断しなくとも、集積回路に第1の例示的増幅器を実装しても良く、かくして設計者は集積回路のその他の設計の側面に集中できることとなる。第1の例示的増幅器は、その他の利益を提供するが、その幾つかを以下に記載する。

#### 【0021】

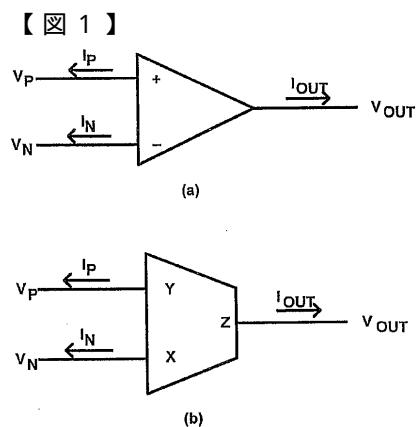

オペアンプ及びCCII(Second Generation Current Conveyor)に関し、第1の例示的増幅器には各種異なる実施形態がある。図3に第1の例示的増幅器100のこのような実装形態の1つを示す。図示のように、第1の例示的増幅器100は、(a)差動増幅回路102、及び(b)非反転出力ステージ104の形態である。第1の例示的増幅器100は、好ましくは正の電圧を供給する第1の電圧源 $V_{DD}$ と好ましくは負の電圧を供給する第2の電圧源 $V_{SS}$ とに接続される。しかし、電圧源は、異極性を持つ電圧を含む、異なる電圧値を供給してもよい。この場合、以下に記載するトランジスタのタイプが変更されても良い(例えば、PMOS(Positive Metal Oxide Semiconductor)トランジスタをNMOS(Negative Metal Oxide Semiconductor)トランジスタに、あるいはその逆に変更しても良い)。

#### 【0022】

一般的に、差動増幅回路102は、2つの電圧入力を受け取る入力ステージと、電流出力を提供する出力ステージとを有する差動増幅回路である。図3に示すように、差動増幅回路102は、入力ステージ106と出力ステージ108を有しているが、差動増幅回路102はその他のステージと構成要素も同様に含んでもよい。

#### 【0023】

図示のように、差動増幅器の入力ステージ106は、電流源120と同じく、4個のトランジスタを含んでいる。すなわち、第1のトランジスタ112、第2のトランジスタ114、第3のトランジスタ116、第4のトランジスタ118を含んでいる。好ましくは

10

20

30

40

50

、PMOSトランジスタである第1のトランジスタ112は、電流源120を介して第1の電圧源 $V_{DD}$ と接続されるソースと、第3のトランジスタ116のドレインと接続されるドレインと、差動増幅器102の正の電圧入力として動作するゲートを有している。同様に、好ましくはPMOSトランジスタである第2のトランジスタ114は、電流源120を介して第1の電圧源 $V_{DD}$ と接続されるソースと、第4のトランジスタ118のドレインと接続されるドレインと、差動増幅器102の負の電圧入力として動作するゲートを有している。好ましくは、NMOSトランジスタである第3のトランジスタ116は、第1のトランジスタ112のドレインと接続されるドレインと、第2の電圧源 $V_{SS}$ と接続されるソースと、そのドレインに接続されるゲートを有している。同様に、好ましくはNMOSトランジスタである第4のトランジスタ118は、第2のトランジスタ114のドレインと接続されるドレインと、第2の電圧源 $V_{SS}$ と接続されるソースと、そのドレインに接続されるゲートを有している。図示のように、第3のトランジスタ116のゲート／ドレインは入力ステージ106の第1の出力として作用し、第4のトランジスタ118のゲート／ドレインは入力ステージ106の第2の出力として作用する。

#### 【0024】

差動増幅器の出力ステージ108は、4個のトランジスタ、すなわち、第5のトランジスタ122、第6のトランジスタ124、第7のトランジスタ126、及び第8のトランジスタ128を含んでいる。好ましくはNMOSトランジスタである第5のトランジスタ122は、第2の電圧源 $V_{SS}$ と接続されるソースと、第6のトランジスタ124のドレインと接続されるドレインと、差動増幅器の入力ステージ106の第1の出力と接続するゲートを有している。好ましくはPMOSトランジスタである第6のトランジスタ124は、第1の電圧源 $V_{DD}$ と接続されるソースと、第5のトランジスタ122のドレインと接続されるドレインと、そのドレインに接続するゲートを有している。好ましくはPMOSトランジスタである第7のトランジスタ126は、第1の電圧源 $V_{DD}$ と接続されるソースと、第8のトランジスタ128のドレインと接続されるドレインと、第6のトランジスタ124のゲート／ドレインに接続するゲートを有している。好ましくはNMOSトランジスタである第8のトランジスタ128は、第7のトランジスタ126のドレインと接続するドレインと、第2の電圧源 $V_{SS}$ と接続するソースと、差動増幅器の入力ステージ106の第2の出力と接続するゲートを有している。図示のように、第7及び第8のトランジスタ126、128の接続されたドレインは、出力ステージ108の電流出力として作用し、電流 $I_{OUT1}$ を提供するように、第1の例示的増幅器100の第1の電流出力として作用する。

#### 【0025】

非反転出力ステージ104は、例えば、差動増幅回路102の出力ステージ108を反復させることのように、差動増幅回路102の電流出力と実質的に同じ振幅と位相を有する第2の電流出力を提供するよう機能する。差動増幅回路102の出力ステージ108を反復させるために、非反転出力ステージ104は2個のトランジスタ、すなわち、第1のトランジスタ130と第2のトランジスタ132を含むブッシュ・プル型出力ステージである。好ましくは、第1及び第2のトランジスタ130、132は、実質的に同じ特性を有し、差動増幅器の出力ステージ108の第7及び第8トランジスタ126、128と実質的に同じ構成に配置される。特に、好ましくはPMOSトランジスタである第1のトランジスタ130は、第1の電圧源 $V_{DD}$ と接続されるソースと、第2のトランジスタ132のドレインと接続されるドレインと、第6のトランジスタ124のゲート／ドレインに接続するゲートを有している。好ましくはNMOSトランジスタである第2のトランジスタ132は、第1のトランジスタ130のドレインと接続されるドレインと、第2の電圧源 $V_{SS}$ と接続されるソースと、差動増幅器の入力ステージ106の第2の出力と接続されるゲートを有している。図示のように、第1及び第2のトランジスタ130、132の接続されたドレインは、非反転出力ステージ104の電流出力として作用し、電流 $I_{OUT2}$ を提供するように、第1の例示的増幅器100の第2の電流出力として作用する。

#### 【0026】

10

20

30

40

50

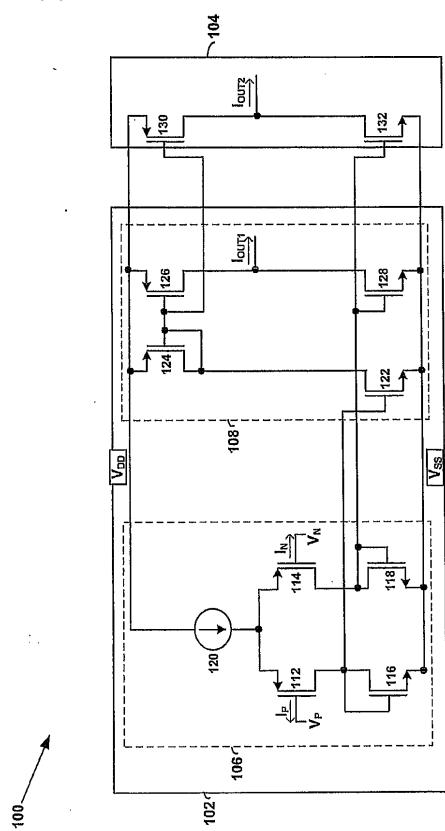

図4に第2の例示的増幅器を示しており、該増幅器は第3の出力を有する例示的増幅器の形態を取る。図示のように、第2の例示的増幅器の第3の出力は、好ましくは、電流- $I_{OUT_3}$ を有する電流出力である。更に、第2の例示的増幅器の第3の出力は、好ましくは、第1及び第2の電流出力と実質的に同じ振幅（例えば、1%以内）でかつ極性が異なる。これをわかりやすくすると、第3の電流出力は高インピーダンスを有している。

#### 【0027】

上記のように、第2の例示的増幅器は、好ましくは2つの電圧入力の差分を大きな利得で増幅するよう動作する。更に、何らかの形態の帰還を備えているとき、例示的増幅器は好ましくは、 $V_P = V_N$ を確実にする値の電流出力を出力するよう動作する。そのようなものとして、例示的増幅器の電流出力は、 $I_{OUT_1} = I_{OUT_2} = -I_{OUT_3} = G(V_P - V_N)$ として表される。加えて、第1、第2及び第3の電流出力はそれぞれ、抵抗 $R_L$ を有する負荷抵抗器（図示せず）に接続される場合、例示的増幅器の電圧出力は $V_{OUT_1} = V_{OUT_2} = -V_{OUT_3} = A_v(V_P - V_N)$ として示される。ただし $A_v = G * R_L$ である。

#### 【0028】

作用効果を奏するものとして、第2の例示的増幅器の第3の電流出力により、更なる柔軟性が集積回路設計者に提供される。特に、第3の電流出力と共に第1及び第2の電流出力の一方を用いて、第2の例示的増幅器は第3のモードで動作するが、この場合、4端子浮遊ヌラー（FTFN）として機能する。このようなことから、集積回路設計者は、第2の例示的増幅器を、オペアンプとCCIに加えてFTFN（Four Terminal Floating Nullor）の代替としてアナログ構成要素のライブラリに組み入れても良い。これにより、ライブラリのインフラ・コストが更に軽減される。第2の例示的増幅器は、その他のモードでも動作可能であり、またその他の作用効果も同じく奏することができる。

#### 【0029】

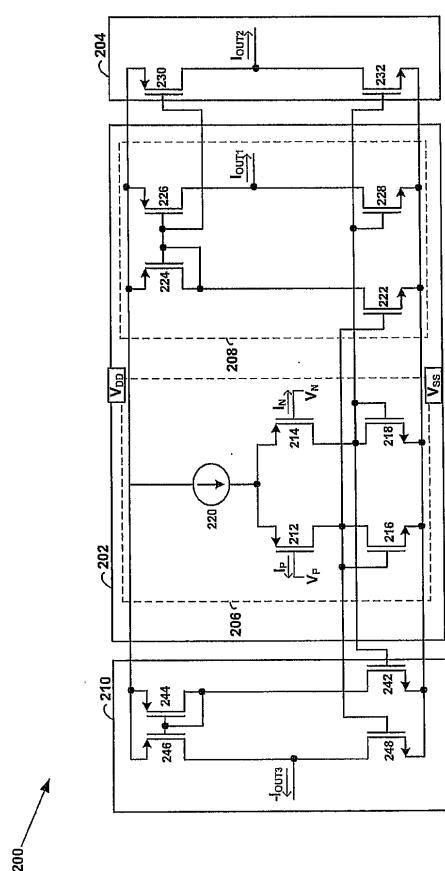

図5は、第2の例示的増幅器の実装形態の一つを示している。図3に示す第1の例示的増幅器100と同様に、第2の例示的増幅器200は、(a)差動増幅回路202と(b)非反転出力ステージ204の形態をとっている。加えて、第2の例示的増幅器200は、反転出力ステージ210を含んでいる。第2の例示的増幅器200は、好ましくは正の電圧を供給する第1の電圧源 $V_{DD}$ と、好ましくは負の電圧を供給する第2の電圧源 $V_{SS}$ とに接続される。しかし、電圧源は、異極性を持つ電圧を含む異なる電圧値を供給してもよいと理解されるべきであり、この場合、以下に記載するトランジスタのタイプが変更されても良い（例えば、PMOSトランジスタをNMOSトランジスタに、あるいはその逆に変更しても良い）。

#### 【0030】

差動増幅回路202は、2つの入力を受け付ける入力ステージと電流出力を提供する出力ステージを有する差動増幅回路である。図示のように、図5の差動増幅回路202は、実質的に図3の差動増幅回路102と同じである。差動増幅回路202は、入力ステージ206と出力ステージ208を有している。しかしながら、差動増幅回路202は、その他のステージと構成要素も備えることができることは理解されるべきであろう。

#### 【0031】

図示のように、差動増幅器の入力ステージ206は、電流源220と4個のトランジスタ、すなわち第1のトランジスタ212、第2のトランジスタ214、第3のトランジスタ216、第4のトランジスタ218を含んでいる。好ましくはPMOSトランジスタである第1のトランジスタ212は、電流源220を介して第1の電圧源 $V_{DD}$ と接続されるソースと、第3のトランジスタ216のドレインと接続されるドレインと、差動増幅器202の正の入力として動作するゲートを有している。同様に、好ましくはPMOSトランジスタである第2のトランジスタ214は、電流源220を介して第1の電圧源 $V_{DD}$ と接続されるソースと、第4のトランジスタ218のドレインと接続されるドレインと、

10

20

30

40

50

差動増幅器 202 の負の入力として動作するゲートを有している。好ましくはN M O Sトランジスタである第3のトランジスタ216は、第1のトランジスタ212のドレインと接続されるドレインと、第2の電圧源 $V_{SS}$ と接続されるソースと、自身のドレインに接続されるゲートを有している。同様に、好ましくはN M O Sトランジスタである第4のトランジスタ218は、第2のトランジスタ214のドレインと接続されるドレインと、第2の電圧源 $V_{SS}$ と接続されるソースと、自身のドレインに接続されるゲートを有している。図示のように、第3のトランジスタ216のゲート／ドレインは、入力ステージ206の第1の出力として作用し、第4のトランジスタ218のゲート／ドレインは、入力ステージ206の第2の出力として作用する。

## 【0032】

10

差動増幅器の出力ステージ208は、4個のトランジスタ、すなわち第5のトランジスタ222、第6のトランジスタ224、第7のトランジスタ226、及び第8のトランジスタ228を含んでいる。好ましくはN M O Sトランジスタである第5のトランジスタ222は、第2の電圧源 $V_{SS}$ と接続されるソースと、第6のトランジスタ224のドレインと接続されるドレインと、差動増幅器の入力ステージ206の第1の出力と接続するゲートを有している。好ましくはP M O Sトランジスタである第6のトランジスタ224は、第1の電圧源 $V_{DD}$ と接続されるソースと、第5のトランジスタ222のドレインと接続されるドレインと、自身のドレインに接続するゲートを有している。好ましくはP M O Sトランジスタである第7のトランジスタ226は、第1の電圧源 $V_{DD}$ と接続されるソースと、第8のトランジスタ228のドレインと接続されるドレインと、第6のトランジスタ224のゲート／ドレインに接続するゲートを有している。好ましくはN M O Sトランジスタである第8のトランジスタ228は、第7のトランジスタ226のドレインと接続するドレインと、第2の電圧源 $V_{SS}$ と接続するソースと、差動増幅器の入力ステージ206の第2の出力と接続するゲートを有している。図示のように、第7及び第8のトランジスタ226、228の接続されたドレインは、出力ステージ208の電流出力として作用し、かくして電流 $I_{OUT_1}$ を提供するように、第1の例示的増幅器100の第1の電流出力として作用する。

## 【0033】

20

非反転出力ステージ204は、差動増幅回路202の出力ステージ208を複製(rePLICATE)することによって、差動増幅回路202の電流出力と実質的に同じ振幅及び位相を有する第2の電流出力を提供するよう機能する。差動増幅回路の出力ステージ208を複製するために、非反転出力ステージ204は、2個のトランジスタ、すなわち、第1のトランジスタ230及び第2のトランジスタ232を含むプッシュ・プル型出力ステージである。好ましくは、第1及び第2のトランジスタ230、232は、実質的に同じ特性を持ち、差動増幅回路202の第7と第8トランジスタ226、228と実質的に同じ構成に配置される。特に、好ましくはP M O Sトランジスタである第1のトランジスタ230は、第1の電圧源 $V_{DD}$ と接続されるソースと、第2のトランジスタ232のドレインと接続されるドレインと、第6のトランジスタ224のゲート／ドレインに接続されるゲートを有している。好ましくはN M O Sトランジスタである第2のトランジスタ232は、第1のトランジスタ230のドレインと接続されるドレインと、第2の電圧源 $V_{SS}$ と接続されるソースと、差動増幅器の入力ステージ206の第2の出力と接続されるゲートを有している。図示のように、第1及び第2のトランジスタ230、232の接続されたドレインは、非反転出力ステージ204の電流出力として作用し、かくして電流 $I_{OUT_2}$ を提供するように、第2の例示的増幅器200の第2の電流出力として作用する。

## 【0034】

40

反転出力ステージ210は、第3の電流出力に対して第1及び第2の電流出力とは実質的に同じ振幅であるが、これら第1及び第2の電流出力とは実質的に逆の極性を提供するよう機能する。この点、図示するように、反転出力ステージ210は、4個のトランジスタすなわち、第1のトランジスタ242、第2のトランジスタ244、第3のトランジスタ246、及び第4のトランジスタ248を含んでいる。好ましくはN M O Sトランジス

50

タである第1のトランジスタ242は、第2の電圧源 $V_{SS}$ と接続されるソースと、第2のトランジスタ244のドレインと接続されるドレインと、差動増幅器の入力ステージ206の第2の出力と接続されるゲートを有している。好ましくはPMOSトランジスタである第2のトランジスタ244は、第1の電圧源 $V_{DD}$ と接続されるソースと、第1のトランジスタ242のドレインと接続されるドレインと、そのドレインに接続されるゲートを有している。好ましくはPMOSトランジスタである第3のトランジスタ246は、第1の電圧源 $V_{DD}$ と接続されるソースと、第4のトランジスタ248のドレインと接続されるドレインと、第2のトランジスタ244のゲート/ドレインに接続されるゲートを有している。好ましくは、NMOSトランジスタである第4のトランジスタ248は、第2の電圧源 $V_{SS}$ と接続するソースと、第3のトランジスタ246のドレインと接続されるドレインと、差動増幅器の入力ステージ206の第1の出力と接続されるゲートを有している。図示のように、第3及び第4のトランジスタ246、248の接続されたドレインは、出力ステージ210の電流出力として作用し、かくして電流 $I_{OUT_3}$ を提供するように、第2の例示的増幅器200の第3の電流出力として作用する。

#### 【0035】

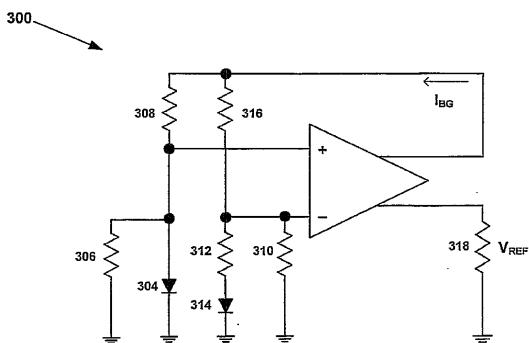

更なる態様では、本明細書に記述される第1の例示的増幅器等の増幅器は、例えば、例示的増幅器の2個の整合電流出力を活用する電圧基準回路のような回路に実装されても良い。図6に、上述の第1の例示的増幅器に基づく例示的電圧基準回路300を示す。図示のように、例示的増幅器の第1の入力は、(a)第1のダイオード304と第1の抵抗器306を介してグランドと接続されており、第1のダイオード304と第1の抵抗器306は並列接続されており、更に第1の入力は、(b)第2の抵抗器308を介して例示的増幅器の第1の出力に接続されている。例示的増幅器の第2の入力は、(a)直列接続された第4の抵抗器312及び第2のダイオード314に並列接続される第3の抵抗器を介してグランドと接続され、(b)第5の抵抗器316を介して例示的増幅器の第1の出力に接続される。

#### 【0036】

電圧基準回路300の抵抗器とダイオードは、各種の形態を取ってよい。好ましくは、電圧入力を第1の電流出力、すなわち、第2の抵抗器308及び第5の抵抗器316に接続されるそれぞれの抵抗器は、実質的に同様な抵抗値を有し、また電圧入力を直接グランドに、すなわち、第1の抵抗器306及び第3の抵抗器310に接続される抵抗器は、実質的に同じ抵抗値を有する。更に、電圧入力を第1の電流出力に接続する抵抗器の概ね2倍の抵抗値を持つ。更にまた、第2のダイオード314と直列接続する第4の抵抗器312は、好ましくは、電圧基準回路300の他の抵抗器と相対して小さな抵抗値を持つ。例えば、第4の抵抗器312は、電圧入力を第1の電流出力に接続する抵抗器の概ね1/4の抵抗値を持ち、かくして、電圧入力を直接グランドに結合する抵抗器の概ね1/8の抵抗値を持つ。更にまた、好ましくは、第2のダイオード314は第1のダイオード304よりも大きい。例えば、第2のダイオード314は第1のダイオード304よりも約8倍の大きさである。その他多くの実施例が同様に可能である。

#### 【0037】

この構成において、電圧基準回路300は例示的増幅器の第1の電流出力で一定のバンドギャップ電流 $I_{BG}$ を生成する。例示的増幅器の第2の電流出力が第1の電流出力と整合していることから、第2の電流出力もまた一定のバンドギャップ電流 $I_{BG}$ を提供する。図示のように、この第2の電流出力は、第6の抵抗器318を介してグランドに接続され、第6の抵抗器318を通過する電圧は、電圧基準回路300の電圧基準出力 $V_{REF}$ である。第6の抵抗器318の抵抗値 $R_{318}$ は、所望の基準電圧が出力されるように選定される。基準電圧出力は、 $V_{REF} = I_{BG} * R_{318}$ として表現される。この基準電圧出力は温度に対して安定であることが好ましい。

#### 【0038】

例示的増幅器に基づく電圧基準回路は、オペアンプあるいはCCIIに基づく電圧基準

10

20

30

40

50

回路以上のコスト効率と電力効率を有することが好ましい。特に、例示的増幅器に基づく電圧基準回路は、必要とされる増幅器は1つのみであり、他方オペアンプあるいはC C I Iに基づく電圧基準回路は、典型的には、多くの増幅器あるいはコンベーラを必要とする。このようなことから、例示的増幅器に基づく電圧基準回路は、集積回路において、必要領域が少なく、またその必要動作電力も少ない。

## 【0039】

此處に記述される例示的増幅器は、その他各種集積回路に実装してもよい。例えば、例示的増幅器はオペアンプあるいはC C I Iの代替として用いてよい。もう一つの実施例として、例示的増幅器はF T F Nの代替として用いてよい。更なる実施例として、例示的増幅器は、2つの整合電流出力及び／もしくは反転電流出力を有する分離アナログ構成要素として用いてもよい。その他の実施例もまた同じく可能である。10

本発明の例示的な実施の形態を説明した。しかし、当業者は変更と修正が、特許請求の範囲で定義される本発明の範囲と技術的思想から逸脱することなく、上述の実施の形態に対してなされることを理解できるであろう。

【図3】

【図4】

【図5】

【図6】

---

フロントページの続き

(74)代理人 100096013

弁理士 富田 博行

(74)代理人 100096068

弁理士 大塚 住江

(72)発明者 ポール・エム・ワーキング

アメリカ合衆国ニュージャージー州 07962-2245, モーリスタウン, コロンビア・ロード

101, ピー・オー・ボックス 2245, ハネウェル・インターナショナル・インコーポレー

テッド, パテント・サービス エム/エス エイビー/2ピー

審査官 德 田 賢二

(56)参考文献 特開平04-227102(JP, A)

欧州特許出願公開第01001474(EP, A1)

米国特許第05124666(US, A)

(58)調査した分野(Int.Cl., DB名)

H 03 F 3 / 45