(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2016-504892

(P2016-504892A)

(43) 公表日 平成28年2月12日(2016.2.12)

(51) Int.Cl.

|      |       |           |

|------|-------|-----------|

| H03F | 1/02  | (2006.01) |

| H03F | 3/189 | (2006.01) |

| H03F | 3/24  | (2006.01) |

F 1

|        |       |

|--------|-------|

| HO 3 F | 1/02  |

| HO 3 F | 3/189 |

| HO 3 F | 3/24  |

テーマコード(参考)

5 J 5 0 0

審査請求 未請求 予備審査請求 未請求 (全 20 頁)

(21) 出願番号 特願2015-555218 (P2015-555218)

(86) (22) 出願日 平成26年1月21日 (2014. 1. 21)

(85) 翻訳文提出日 平成27年9月15日 (2015. 9. 15)

(86) 國際出願番号 PCT/US2014/012393

(87) 國際公開番号 WO2014/116608

(87) 國際公開日 平成26年7月31日 (2014. 7. 31)

(31) 優先権主張番号 13/752,287

(32) 優先日 平成25年1月28日 (2013. 1. 28)

(33) 優先権主張国 米国(US)

(71) 出願人 595020643

クアアルコム・インコーポレイテッド

Q U A L C O M M I N C O R P O R A T

E D

アメリカ合衆国、カリフォルニア州 92

121-1714、サン・ディエゴ、モア

ハウス・ドライブ 5775

(74) 代理人 100108855

弁理士 蔵田 昌俊

(74) 代理人 100109830

弁理士 福原 淑弘

(74) 代理人 100158805

弁理士 井関 守三

(74) 代理人 100194814

弁理士 奥村 元宏

最終頁に続く

(54) 【発明の名称】エンベロープトラッキングのための動的ヘッドルーム

## (57) 【要約】

エンベロープトラッキングシステムのためのヘッドルーム電圧を動的に生成する技術。1つの態様において、初期ヘッドルーム電圧は電力増幅器(PA)からの信号がPAヘッドルームが不十分であると示した時に更新される。当該初期ヘッドルーム電圧は、初期電圧に不足電圧とマージンを加算したものを含む動作ヘッドルーム電圧へ更新されてもよい。このようにして、動作ヘッドルーム電圧は、PAが線形であることを保証しているうちに、電力消費を最小化するように動的に選択されてもよい。さらなる態様において、カウンタを用いたヘッドルーム電圧生成器の特定の例示的な実施形態が記載される。

**【特許請求の範囲】****【請求項 1】**

増幅器に関する増幅器供給電圧を生成するように構成可能なブースト変換器と、ここでにおいて、前記増幅器はトラッキング供給電圧を出力するように構成され、前記トラッキング供給電圧は入力電圧を増幅して出力電圧を生成するように構成された電力増幅器に供給される、ここでにおいて、前記増幅器供給電圧は前記ブースト変換器に結合されたブースト供給電圧よりも高くなるように構成可能であり、前記ブースト変換器はヘッドルーム電圧と前記増幅器供給電圧より大きい前記トラッキング供給電圧のピークとの合計に応答してイネーブルにされるように構成される、

前記ヘッドルーム電圧を生成するように構成された動的ヘッドルーム生成ブロックと、ここでにおいて、前記ヘッドルーム電圧はヘッドルーム到達信号の検出に応答して初期ヘッドルーム電圧から更新される、

10

を備える装置。

**【請求項 2】**

前記電力増幅器は少なくとも一つのトランジスタを備え、前記ヘッドルーム到達信号は前記少なくとも一つのトランジスタが飽和であることを示す、請求項 1 に記載の装置。

**【請求項 3】**

前記更新されたヘッドルーム電圧は、前記ヘッドルーム電圧と、不足電圧と、電圧マージンとの合計を備える、請求項 1 に記載の装置。

**【請求項 4】**

前記不足電圧は、前記増幅器供給電圧と、前記トラッキング供給電圧のピークと前記初期ヘッドルーム電圧の合計との差を備える、請求項 3 に記載の装置。

20

**【請求項 5】**

前記更新されたヘッドルーム電圧は、電圧マージンと、前記増幅器供給電圧と前記トラッキング供給電圧の前記ピークの差との合計を備える、請求項 1 に記載の装置。

**【請求項 6】**

前記ブースト変換器は前記増幅器供給電圧をターゲット電圧に引き上げるように構成可能であり、前記ターゲット電圧は前記ヘッドルーム電圧と前記トラッキング供給電圧の前記ピークの合計に対応する、請求項 1 に記載の装置。

**【請求項 7】**

前記トラッキング供給電圧の前記ピークは所定の時間間隔にわたる前記トラッキング供給電圧の前記ピークに対応する、請求項 1 に記載の装置。

30

**【請求項 8】**

前記動的ヘッドルーム生成ブロックは、

前記初期ヘッドルーム電圧に対応する値で初期化されたカウンタを備え、前記カウンタは前記ヘッドルーム到達信号および前記増幅器供給電圧が前記ヘッドルーム電圧と前記トラッキング供給電圧の前記ピークの合計より小さいことを示す信号とを検出することに応答してイネーブルにされるように構成される、請求項 1 に記載の装置。

**【請求項 9】**

前記カウンタはクロックに結合され、前記カウンタは、イネーブルにされている時、その値が前記クロックの立ち上がりエッジに応答してインクリメントするように構成される、請求項 8 に記載の装置。

40

**【請求項 10】**

前記動的ヘッドルーム生成ブロックは前記ヘッドルーム到達信号を検出することに応答して前記ヘッドルーム電圧を一回更新するように構成される、請求項 1 に記載の装置。

**【請求項 11】**

トラッキング供給電圧を増幅器を用いて生成して出力電圧を生成するために入力電圧を増幅するように構成された電力増幅器を供給すること、

増幅器供給電圧を前記増幅器のために生成することと、ここでにおいて前記増幅器供給電圧はブースト供給電圧よりも高くなるように構成可能である、

50

前記增幅器供給電圧をヘッドルーム電圧と前記增幅器供給電圧よりも大きいトラッキング供給電圧のピークとの合計とに応答して前記ブースト供給電圧よりも高くなるように構成することと、

ヘッドルーム到達信号の検出に応答して、前記ヘッドルーム電圧を初期値から更新することと、

を備える方法。

【請求項 1 2】

前記ヘッドルーム到達信号を検出することは前記電力増幅器の少なくとも 1 つのトランジスタが飽和であることを検出することを備える、請求項 1 1 に記載の方法。

【請求項 1 3】

前記ブースト供給電圧はバッテリ電圧である、請求項 1 1 に記載の方法。

【請求項 1 4】

前記更新することは、

前記初期値でカウンタを初期化することと、

前記ヘッドルーム到達信号と、前記增幅器供給電圧が前記トラッキング供給電圧と前記トラッキング供給電圧の前記ピークの合計より小さいことを示す信号とを検出することに応答して、前記カウンタをクロック信号の毎立ち上がりエッジでインクリメントすることと、

前記ヘッドルーム到達信号が偽である時か、前記增幅器供給電圧が前記トラッキング電圧と前記トラッキング供給電圧のピークの合計より小さくない時のどちらかの時、前記カウンタをディスエーブルにすることと、

を備える、請求項 1 1 に記載の方法。

【請求項 1 5】

前記更新することはヘッドルーム到達信号を検出することに応答して前記ヘッドルーム電圧を一回更新することを備える、請求項 1 1 に記載の方法。

【請求項 1 6】

トラッキング供給電圧を増幅器を用いて生成して出力電圧を生成するために入力電圧を増幅するように構成された電力増幅器を供給する手段と、

増幅器供給電圧を前記増幅器のために生成する手段と、ここにおいて前記増幅器供給電圧はブースト供給電圧よりも高くなるように構成可能である、

前記増幅器供給電圧をヘッドルーム電圧と前記増幅器供給電圧よりも大きいトラッキング供給電圧のピークとの合計とに応答してブースト供給電圧よりも高くなるように構成する手段と、

ヘッドルーム到達信号の検出に応答して、前記ヘッドルーム電圧を初期値から更新する手段と、

を備える装置。

【請求項 1 7】

前記ヘッドルーム到達信号は前記電力増幅器の少なくとも 1 つのトランジスタが飽和であることを示す信号を備える、請求項 1 6 に記載の装置。

【請求項 1 8】

前記ブースト供給電圧はバッテリ電圧である、請求項 1 6 に記載の装置。

【請求項 1 9】

前記更新する手段は、

前記初期値で初期化されたカウンタを備え、前記カウンタは前記ヘッドルーム到達信号と、前記増幅器供給電圧が前記ヘッドルーム電圧と前記トラッキング供給電圧のピークの合計より小さいことを示す信号とを検出することに応答してイネーブルにされるように構成される、請求項 1 6 に記載の装置。

【請求項 2 0】

前記更新する手段はヘッドルーム到達信号を検出することに応答して前記ヘッドルーム電圧を更新する手段を備える、請求項 1 6 に記載の装置。

10

20

30

40

50

## 【発明の詳細な説明】

## 【関連出願】

## 【0001】

[0001]本国際出願は、その全体が参照により本明細書に明確に組み込まれる、2013年1月28日に出願された「DYNAMIC HEADROOM FOR ENVELOPE TRACKING」と題する米国非仮特許出願第13/752,287号の利益を主張する。

## 【技術分野】

## 【0002】

[0002]本開示は電力増幅器のためのエンベロープトラッキング(envelope tracking)に関する。 10

## 【背景技術】

## 【0003】

[0003]エンベロープトラッキングは電力増幅器の効率性を高めるための技術である。エンベロープトラッキング(ET)システムにおいて、直流電力消費を最小化する一方で、直線性を保持するのに十分なヘッドルームで電力増幅器を動作し続けるために、電力増幅器の供給電圧は動的に調節される。電力増幅器の供給電圧は、電力増幅器出力のエンベロープをトラックする独立した線形増幅器を用いて通常生成される。いくつかの先行技術実施において、線形増幅器自体はブースト変換器によって生成された増幅器供給電圧に結合され、ブースト変換器は、例えばバッテリ電圧のようなシステムが利用可能な最大供給電圧を上回る、ブーストされた供給電圧を線形増幅器のために生成することができる。このやり方によって電力増幅器出力が、必要に応じて、バッテリ電圧に到達する、さらにはそれを上回ることができる。 20

## 【0004】

[0004]増幅器供給電圧は、ピーク要求電力増幅器出力プラスいくらかの追加ヘッドルーム電圧よりも高くなるように典型的に設定される。いくつかの先行技術実施において、このヘッドルーム電圧は、あらかじめプログラムされ時が経つにつれて更新されない、静止値である。しかしながら、異なる動作シナリオにわたって、例えば異なる処理、温度、負荷条件等にわたって、好ましいヘッドルーム電圧はかなり変動するので、ヘッドルーム電圧に対する単一の静止値はすべての場合において最適でないかもしれない。さらに、あまりに低く選ばれたヘッドルーム電圧は、ブースト変換器におけるスタートアップ失敗を望ましくなく引き起こすかもしれません、それはシステムの線形性を損なうことになる。 30

## 【0005】

[0005]特定の動作シナリオに従ってETシステムにとって最適のヘッドルーム電圧を動的に決定するための技術、さらにETシステムにおけるブースト変換器のためのスタートアップ失敗を防止するための技術を提供することが望ましいだろう。

## 【図面の簡単な説明】

## 【0006】

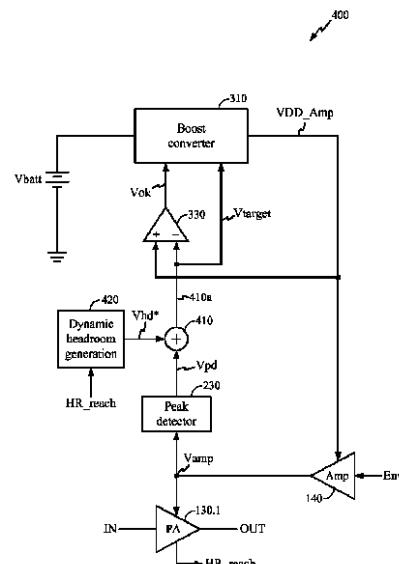

【図1】エンベロープトラッキング(ET)システムの先行技術実施を図示する。

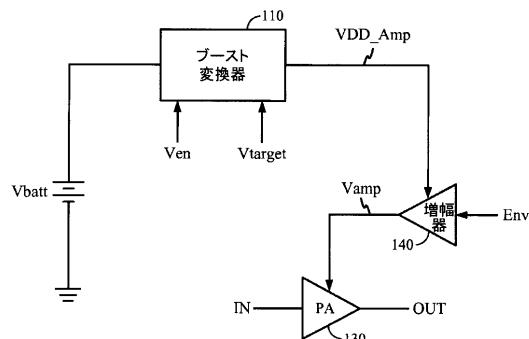

【図2】 $V_{en}$ と $V_{target}$ が示された特定のやり方で生成される、エンベロープトラッキング(ET)システムの実施を図示する。 40

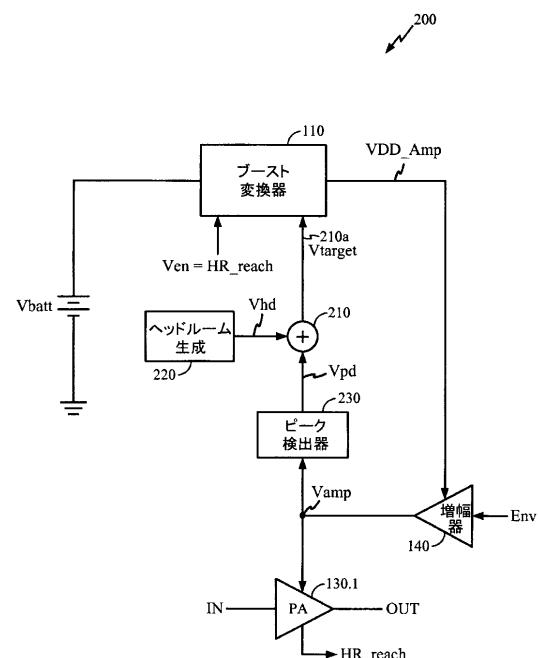

【図3】ETシステムの代替の実施を図示する。

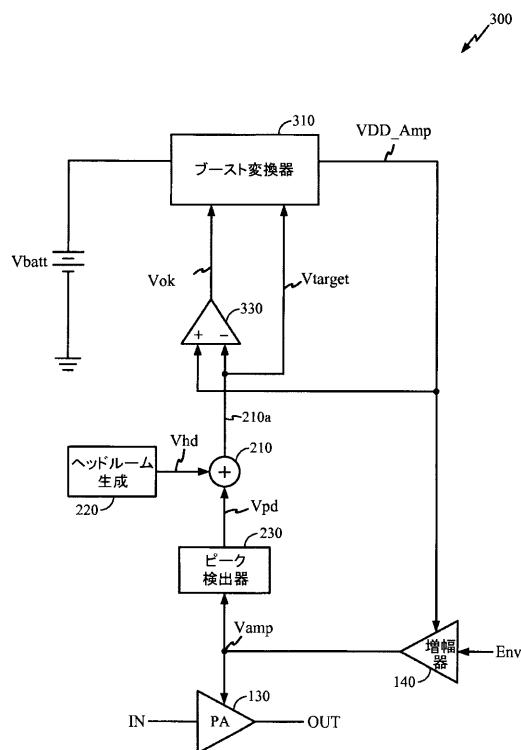

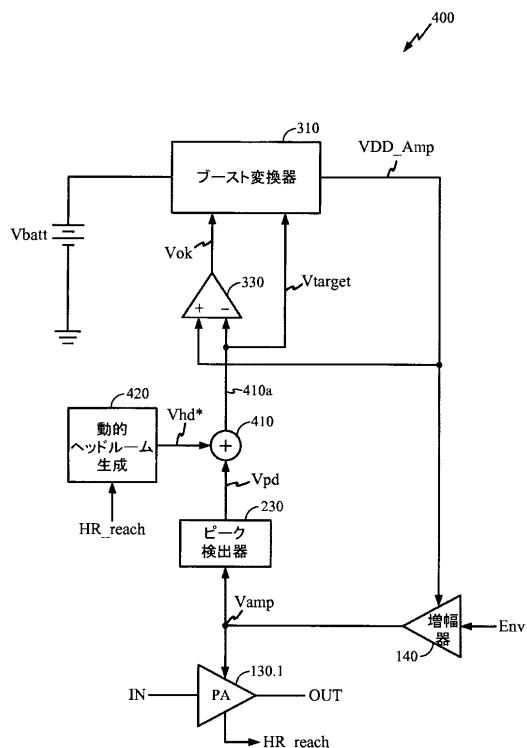

【図4】本開示にしたがったETシステムの例示的な実施形態を例示する。

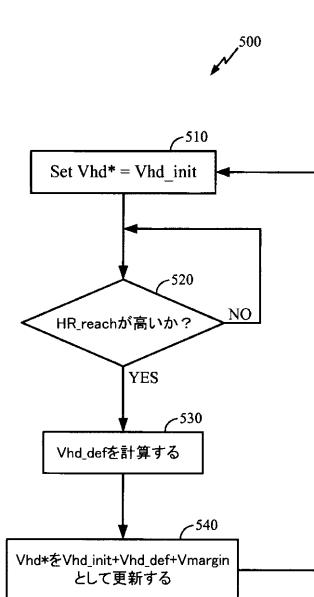

【図5】動的ヘッドルーム生成プロックによって実施されてもよい方法の例示的な実施形態を図示する。

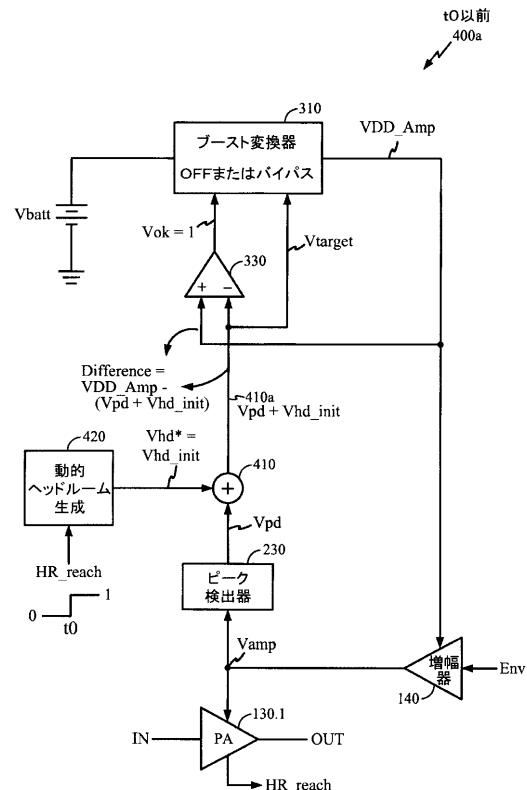

【図6】上記の本開示の技術による例示的な動作シナリオを図示する。

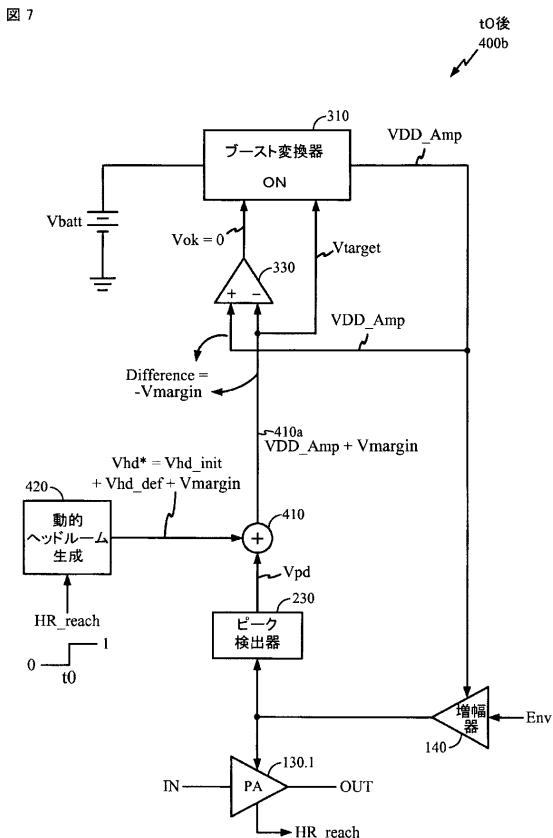

【図7】上記の本開示の技術による例示的な動作シナリオを図示する。

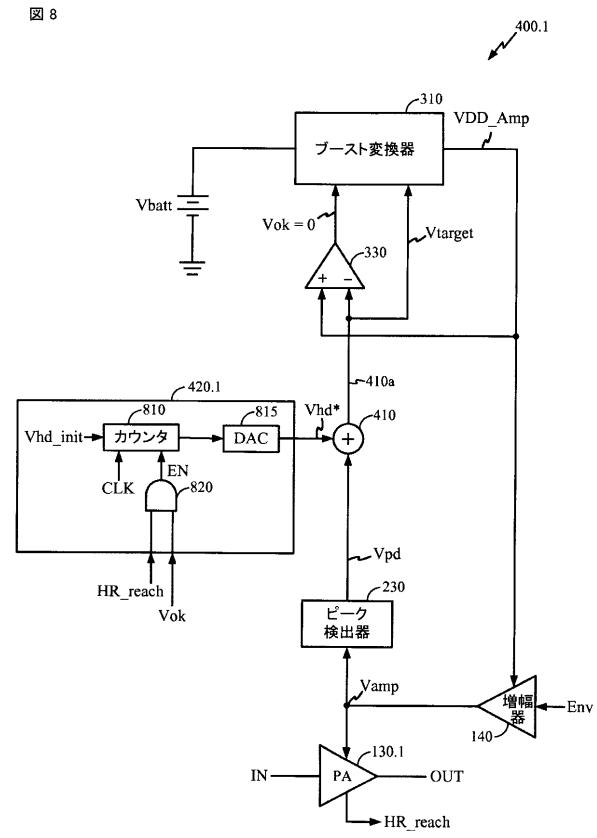

【図8】本開示にしたがったETシステムの例示的な実施形態を例示し、ここにおいて動的ヘッドルーム生成プロックの特定の例示的な実施形態が示される。

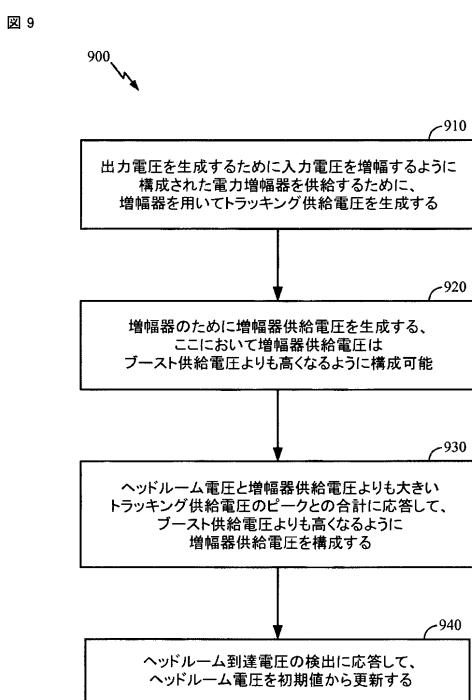

【図9】本開示にしたがった方法の例示的な実施形態を例示する。

## 【発明を実施するための形態】

## 【0007】

[0014]下記において、添付の図面を参照し、本開示のさまざまな態様がより十分に説明される。しかしながら、本開示は、多くの異なる形態で具現化することができるものであり、この開示全体を通して提示される任意の特定の構成または機能に限定されるものと解釈されるべきではない。むしろ、これらの態様は、本開示を徹底的かつ完全なものとし、本開示の範囲が当業者に十分に伝達されるように提供される。本明細書における教示に基づき、当業者は、本開示の任意の他の態様と独立して実装されようと、組み合わされて実装されようと、本開示の範囲が本明細書において開示される開示の任意の態様をカバーするよう意図されることを認識すべきである。例えば、本明細書において述べられる任意の数の態様を使用して、装置が実装されうる、または方法が実現されうる。加えて、開示の範囲は、本明細書において述べられる開示の様々な態様に加えて、またはそれ以外の、他の構造、機能性、あるいは構造および機能性を使用して実現されるそのような装置または方法をカバーするよう意図される。本明細書において開示される開示の任意の態様が特許請求の範囲の1つまたは複数の要素によって具現化されうることは理解されるべきである。

10

## 【0008】

[0015]添付された図面に関連して以下に記載の詳細な説明は、本発明の例示的な態様の説明として意図され、本発明が実現されることができる唯一の例示的な態様を表すよう意図されない。本明細書全体にわたって使用される「例示的(exemplary)」という用語は、「例、事例、または例証(illustration)としての役割を果たす」ことを意味し、他の例示的な態様に対して必ずしも好ましいまたは有利であると解釈されるべきではない。詳細な記述は、本発明の例示的な態様の完全な理解を提供する目的とした特定の詳細を含む。本発明の例示的な態様は、これらの特定の詳細なしで実現されうることが当業者に明らかになるであろう。いくつかの事例において、周知の構造およびデバイスは、本明細書において提示される例示的な態様の新規性を曖昧にすることを避けるためにブロック図形式で示される。本明細書および特許請求の範囲において、「モジュール」とおよび「ブロック」という用語は、記述される動作を遂行するよう構成されるエンティティを示すよう交換可能に使用されうる。

20

## 【0009】

[0016]本明細書および請求項において、信号または電圧が「高い(high)」または「低い(low)」の表記は、その信号または電圧が論理的に高いまたは低い状態を表し、それは信号または電圧の「真」(例えば、=1)または「偽」(例えば、=0)の状態に(必ずしもではないが)対応する。ここに記載される回路と実質的に同等の機能性を持つ回路を得るために、例えば「高」を「低」に置き換えるおよびまたは「低」を「高」に置き換えるなど、当業者はここに記載される論理的慣行を容易に変更してもよいと認識されるだろう。そのような代替の例示的な実施形態は、本開示の範囲内であると熟考される。

30

## 【0010】

[0017]図1は、エンベロープトラッキング(ET)システム100の先行技術実施を図示する。図1は例証的な目的のみのために提示され、ETシステムの特定の実施に対する本開示の範囲を限定するよう意図されないことに留意されたい。例えば、以下において記載される技術は、電力増幅器のためにステップダウン電圧を同時に生成するための、V<sub>batt</sub>をV<sub>amp</sub>に結合するバック変換器のような、図示されない代替のまたは追加のモジュールを組み込むシステムに容易に適用されてもよい。

40

## 【0011】

[0018]図1において、電力増幅器(PA)130は入力電圧INを受け取り、増幅された出力電圧OUTを生成する。「トラッキング供給電圧」とも呼ばれる電圧V<sub>amp</sub>はPA130に供給電圧として供給される。V<sub>amp</sub>は、少なくとも部分的に増幅器140によって発生され、増幅器140は線形増幅器であってもよい。増幅器140には、「増幅器供給電圧」とも呼ばれる電圧V<sub>DD\_Amp</sub>が供給される。ETシステムのいくつかの実施において、V<sub>amp</sub>を発生するために、増幅器140は、PA出力電圧OUTのエン

50

ペロープをトラッキングする電圧  $V_{en}$  を増幅してもよい。

【0012】

[0019] PA130に提供されたトラッキング供給電圧  $V_{amp}$  は、PA130の線形動作を保証するために十分なレベルに保たれてもよく、すなわち、不要なDC電力消費を減少しながら十分な「ヘッドルーム」が与えられてもよい。上記に述べられているように、いくつかの実施において、バック変換器(buck converter)(図示されない)が、PA130の電力駆動能力を高めるために、例えば、 $V_{amp}$  でPA130に結合されて、PA130に供給するために同時に設けられてもよい。

【0013】

[0020] いくつかの動作シナリオにおいて、PAのための十分なヘッドルームを確保するために、「ブースト供給電圧」とも呼ばれる、システムに利用可能な最大供給電圧であるところの  $V_{batt}$ 、例えば、システムのバッテリからの最大供給電圧、のレベルを超えるレベルまで  $V_{amp}$  を押し上げる(drive)必要があるかもしれない。増幅器140によって  $V_{batt}$  より大きい出力  $V_{amp}$  を生成可能とするために、ブースト変換器110を設けて  $V_{DD\_Amp}$  を生成してもよい。ブースト変換器110は、ブーストされた電圧を生成するためにインダクタを充電と放電するように交互に構成された複数のスイッチを例えば使って、図1には示されないが周知の動作原理に従って  $V_{DD\_Amp}$  を高いレベルまでブーストしてもよい。

10

【0014】

[0021] ETシステムの効率性を高くするために、例えば、PA130に対して十分なヘッドルームを確保するために  $V_{DD\_Amp}$  が  $V_{batt}$  を超えて上昇する必要があると決定された時に、ブースト変換器110は、必要に応じてオンにされる、またはイネーブルにされてもよい。このように、ブースト変換器110は、 $V_{DD\_Amp}$  が  $V_{batt}$  より高いレベルにブーストされなければいけない時を示す「イネーブル」信号電圧  $V_{en}$  を入力として受け取ってもよい。ブースト変換器110に、ブースト変換器110がイネーブルにされる時に  $V_{DD\_Amp}$  がそこまでブーストされるべきターゲット電圧  $V_{target}$  も提供されてもよい。 $V_{batt}$  より高い  $V_{DD\_Amp}$  が提供される必要がない時、ブースト変換器110は、オフにされるまたはディスエーブルにされてもよく、そうでなければ  $V_{batt}$  を  $V_{DD\_Amp}$  に直接結合する「バイパス」モードで設けられることが認識されるだろう。

20

【0015】

[0022] 図2は、ETシステム200の実施を図示し、ここにおいて  $V_{en}$  および  $V_{target}$  は示された特定のやり方で生成される。図2は例証的な目的のみのために提示され、 $V_{en}$  および / または  $V_{target}$  を生成するための特定の技術に対する本開示の範囲を限定するよう意図されないことに留意されたい。

30

【0016】

[0023] 図2において、PA130の特定の実施130.1は、PA130.1の電圧ヘッドルームがPAの線形性を確保するために不十分である(または、不十分に近い)時を示す、「ヘッドルーム到達信号」とも呼ばれる、電圧  $H_R\_reach$  を生成する。例えば、PA130.1における1以上のトランジスタ(図示されない)が飽和する時はいつでも、 $H_R\_reach$  は高くアサート(asserted)される。例えば、ある例示的な実施形態において、電圧増幅器がPA130.1のトランジスタのドレインとソースにわたって電圧降下を感知するために提供されてもよく、感知された電圧降下は、電圧比較器によって所定の閾値電圧と比較されてもよい。もしトランジスタにわたる電圧降下が当該所定の閾値電圧より小さいまたは等しい場合、 $H_R\_reach$  は高くアサートされてもよい。この場合、当該所定の閾値電圧は、対応するトランジスタが飽和になると期待される値に対応してもよい。

40

【0017】

[0024] 図2において、 $H_R\_reach$  は、 $V_{en}$  としてブースト変換器110に直接結合される。このようにして、 $H_R\_reach$  が、PA130.1の電圧ヘッドルーム

50

が不十分であると示す時はいつでも、ブースト変換器 110 もイネーブルにされる。代替の実施において、HR\_reach の値における潜在的な過渡のトグル (transient toggling) に鑑みて、ブースト変換器 110 に供給することに先立って HR\_reach を処理するために、Ven の値を例えば所定の時間の間保持するためのラッチまたは他の記憶素子も設けられてよいことに留意されたい。

#### 【0018】

[0025] Vamp の検出されたピーク値に対応する電圧 Vpd を、例えば所定の時間間隔にわたって生成するために、Vamp に結合されたピーク検出器 230 が図 2 にさらに示される。ヘッドルーム生成ブロック 220 も所定の「ヘッドルーム電圧」Vhd を生成するために設けられる。示された実施において、ブースターゲット電圧 Vtarget を生成するための加算器 210、または 210a を使用して、Vhd は Vpd に加えられる。イネーブルにされた時、ブースト変換器 110 は増幅器供給電圧 VDD\_Amp をターゲット電圧 Vtarget まで押し上げてもよいことが認識されるだろう。

10

#### 【0019】

[0026] 図 2 は例証的な目的のために提示され、Ven および Vtarget が示されるように必ず生成される、ET システムに対する本開示の範囲を限定するよう意図されないことに留意されたい。例えば、いくつかの実施においては、Vtarget が図 2 に示されるように生成されてもよい一方で、Ven は周知の他の技術（図 2 に図示されない）を使って生成されてもよい；同様に、Ven が示されるように生成されてもよく、Vtarget は他の技術を使って生成されてもよい。それらのような代替の実施は、本開示の範囲内であると熟考される。

20

#### 【0020】

[0027] 図 3 は ET システムの代替の実施 300 を図示する。図 2 および 3 において同様にラベル付けされた要素は、言及がない限り同様の機能性を実行する要素に対応するかもしれないことに留意されたい。図 3 におけるブースト変換器 310 は例証的な目的のために提示され、図 11 におけるブースト変換器 110 は、信号協定 (signaling conventions) を当業者に自明のやり方で変更することによって、ET システム 300 において使用されてもよいことが認識されるだろう。そのような代替の例示的な実施形態は、本開示の範囲内であると熟考される。

30

#### 【0021】

[0028] 図 3 において、ET システム 200 におけるように、ブースト変換器 110 のための Vtarget は加算器 210 の出力 210a として生成される。電圧 Vok は、正 (+) 入力端子における VDD\_Amp を負 (-) 入力端子における加算器 210 の出力 210a と比較する比較器 330 の出力において生成される。高い Vok は現在の増幅器供給電圧 VDD\_Amp が Vtarget を超過することを表すことが認識されるだろう；この場合、十分な (ample) ヘッドルームが PA にあるので、ブースト変換器 310 はイネーブルにされる必要がない。

#### 【0022】

[0029] ブースト変換器 310 がイネーブルにされる時、VDD\_Amp は Vtarget に等しい DC 値を持つかもしれません、しかし VDD\_Amp に AC 構成要素があるかもしれません、それゆえ、Vok はある期間にわたって高と低の間で交互にトグルしているかもしれないことが認識されるだろう。従って、Ven は、Vok の反転したものがフィルタされたおよび / またはラッチされたバージョンとしてこのようにして生成されることができる。特に、いくつかの例示的な実施形態において、Vok の潜在的に交互にトグルする値を定期的にラッチするためのラッチと同様に、例えばインバータ（図示されない）を使用して Vok から Ven を導き出すために論理回路（図示されない）が設けられてもよい。

40

#### 【0023】

[0030] ET システム 300 によると、検出されたピーク (Vpd) とヘッドルーム Vhd の合計が VDD\_Amp を超過する時、Vok は低くなり（例えば、Ven は高くなるだろう）、ブースト変換器 310 はイネーブルにされるだろう。上記の記載に従って、V

50

$V_{amp}$  の検出されたピークレベル  $V_{pd}$  が  $VDD\_Amp$  の電圧降下  $V_{hd}$  以内である時、すなわち  $V_{pd} > VDD\_Amp - V_{hd}$  である時のみ、 $V_{ok}$  は低くなるだろうことが認識されるだろう。この明細書および特許請求の範囲において、低くある  $V_{ok}$  の状態は、増幅器供給電圧がヘッドルーム電圧とトランシッキング供給電圧のピークの合計より小さいことを示す信号に対応することを意味してもよい。

#### 【0024】

[0031] 図3および関連する例示的な実施形態は例証的な目的のために提示され、提示される任意の特定の例示的な実施形態に対する本開示の範囲を限定するよう意図されないことに留意されたい。当業者は、本開示に照らし合わせて、代替で同等の論理シグナリング方式を容易に導き出すかもしれない。例えば、比較器330は代わりに、正(+)および負(-)入力端子に結合された信号電圧を切り替えることによって、 $V_{ok}'$ (すなわち、 $V_{ok}$ の論理反転)を生成するように構成されてもよく、このような場合にはブースト変換器310は、 $V_{ok}$ よりむしろ  $V_{en}$  を直接処理するように代替的に構成されてもよい。そのような代替の例示的な実施形態は、本開示の範囲内であると熟考される。

10

#### 【0025】

[0032] さらに、図3(および本明細書のその他の図面)に示された構成要素はアナログ入力および/または出力電圧を一般的には処理する一方、そのようなアナログ構成要素はどれも、信号の内部デジタル処理を可能にするために、1以上のデジタル アナログ変換器(DAC)および/またはアナログ デジタル変換器(ADC)を組み込んでもよい。例えば、ヘッドルーム生成ブロックはDAC(図示されない)を組み込んでもよい。

20

#### 【0026】

[0033] いくつかの従来技術実施において、図2および3の両方におけるヘッドルーム生成ブロック220は、 $V_{hd}$ を固定された所定の電圧として生成するように構成されてもよい。この場合、必要とされるヘッドルームに対して「最適な」値  $V_{hd\_opt}$ 、例えばDC電力消費を同時に最小限にする一方でPA130の無歪み(distortion-free)動作を可能にするヘッドルーム電圧のための値、に近づける(approximate)ために  $V_{hd}$  の当該固定値は設計によって選ばれてもよい。しかしながら、通常動作の間は、最適値  $V_{hd\_opt}$  は、異なる動作シナリオにわたって、例えば、異なる処理、温度、負荷条件にわたってはっきりとばらつきがあるかもしれないことが認識されるだろう。例えば、一例として、例えばPA130の動作温度に応じて、 $V_{hd\_opt}$  は150mVから400mVに及んでもよい。

30

#### 【0027】

[0034] もし所与のシナリオに対して  $V_{hd}$  の固定設定が最適なヘッドルーム  $V_{hd\_opt}$  より大きい場合、例えば、 $V_{hd} > V_{hd\_opt}$  それゆえ  $V_{hd}$  が  $V_{hd\_opt}$  を高く見積もりすぎる場合、増幅器140のための供給電圧  $VDD\_Amp$  はブーストされすぎるかもしれないことが認識されるだろう。この場合、PA130は無歪みで動作するものの、電力は不必要に無駄にされる。一方、もし所与のシナリオに対して  $V_{hd}$  が最適なヘッドルーム  $V_{hd\_opt}$  より小さい場合、例えば、 $V_{hd} < V_{hd\_opt}$  それゆえ  $V_{hd}$  が  $V_{hd\_opt}$  を低く見積もりすぎる場合、歪みが増幅器130の出力に望ましくなくもたらされるかもしれない。

40

#### 【0028】

[0035] 図3に示された具体的なETシステム300について、 $V_{hd} < V_{hd\_opt}$  に関するさらなる問題はブースト変換器310がいくつかの場合において全体的に(altogether)スタートアップに失敗するかもしれないことが認識されるだろう。特に、十分なヘッドルームを保持するために、ブースト変換器310は、 $V_{amp}$  が( $VDD\_Amp - V_{hd\_opt}$ )を超過した時、イネーブルにされるべきである；しかしながら、 $V_{hd} < V_{hd\_opt}$  であることを判断して、ブースト変換器310は実際のところ  $V_{amp}$  が( $VDD\_Amp - V_{hd\_opt}$ )よりも高いレベルであろう( $VDD\_Amp - V_{hd}$ )を超過するまでイネーブルにされない。言い換えれば、 $V_{hd} < V_{hd\_opt}$  であるそれらの場合に、ブースト変換器310はかなり遅れてイネーブルにされて、ま

50

たは全くイネーブルにされないかもしだれ、それゆえ P A 1 3 0 の線形性に悪い影響を与える。

#### 【 0 0 2 9 】

[0036] 線形性の最大化と電力消費の最小化の間のトレードオフ (trade-offs) を最適化するように、さらにはブーストスタートアップ失敗の可能性を最小化するように、ヘッドルーム電圧 V h d を設定する技術を提供することが望ましいだろう。

#### 【 0 0 3 0 】

[0037] 図 4 は本開示による E T システム 4 0 0 の例示的な実施形態を例示する。図 4 において、動的ヘッドルーム生成ブロック 4 2 0 は、電圧 H R \_ r e a c h を P A 1 3 0 . 1 から受け取り、加算器 4 1 0 によって V p d に加えられるヘッドルーム電圧 V h d \* を生成する。ある例示的な実施形態において、V h d \* は、初期ヘッドルーム電圧 V h d \_ i n i t から、所与の動作シナリオに対する V h d \_ o p t により近づく 1 以上の連続した値へ、時間が経つにつれ (over time) 更新される。ヘッドルーム生成ブロック 4 2 0 は時間が経つにつれ少なくとも一度は変化する「動的」ヘッドルーム電圧を生成するとして理解されてもよい。

10

#### 【 0 0 3 1 】

[0038] 特に、図 5 は動的ヘッドルーム生成ブロック 4 2 0 によって実施されてもよい方法 5 0 0 の例示的な実施形態を図示する。方法 5 0 0 は例示的な実施形態は例証的な目的のみのために提示され、提示される任意の特定の方法に対する本開示の範囲を限定するよう、または動的ヘッドルーム生成ブロック 4 2 0 を方法 5 0 0 を実施するそれらの例示的な実施形態のみに制限されないよう意図されないように留意されたい。

20

#### 【 0 0 3 2 】

[0039] 図 5 において、ブロック 5 1 0 では、V h d \* が初期値 V h d \_ i n i t に設定される。ある例示的な実施形態において、V h d \_ i n i t は固定の所定値、例えば 4 0 0 mV に対応するように選ばれてもよい。V h d \_ i n i t は必要とされる V h d のための初期の最良推定値に対応するように選ばれてもよいことに留意されたい。

#### 【 0 0 3 3 】

[0040] ブロック 5 2 0 では、H R \_ r e a c h が高いかどうかチェックされる。既に上記されたように、これは例えば、P A 1 3 0 における 1 以上のトランジスタ (図示されない) が飽和していることを示すかもしだれ。もし H R \_ r e a c h が高ければ、方法はブロック 5 3 0 に進んでもよい。そうでなければ、方法はブロック 5 2 0 を繰り返してもよい。

30

#### 【 0 0 3 4 】

[0041] ブロック 5 3 0 では、H R \_ r e a c h が高いことを検出することに反応して、「不足 (deficiency) 電圧」とも呼ばれる電圧 V h d \_ d e f が以下のように計算される (数式 1) :

$$V h d _ d e f = V D D _ A m p - (V p d + V h d _ i n i t) .$$

特に、検出されたピーク電圧 V p d と初期ヘッドルーム電圧 V h d \_ i n i t の合計が増幅器 1 4 0 の現在の供給電圧 V D D \_ A m p から減算される。この減算が H R \_ r e a c h が高いことを検出することと同時に行われるために、P A 1 3 0 の 1 以上のトランジスタが飽和に至る時、V h d \_ d e f がヘッドルーム電圧における不足 (または過剰) の数量 (measures) を提供することが認識されるだろう。ある例示的な実施形態において、H R \_ r e a c h が高くアサートされるようにさせる V a m p における対応する値を V p d の値が正確に (例えば、最小限の遅延で) 反映するように、数式 1 は H R \_ r e a c h が高いことを検出してすぐ後に計算される。

40

#### 【 0 0 3 5 】

[0042] ブロック 5 4 0 では、V h d \* が以下のように更新される (数式 2) :

$$V h d ^ * = V h d _ i n i t + V h d _ d e f + V m a r g i n ;$$

ここにおいて、「電圧マージン」とも呼ばれる V m a r g i n は固定の所定の正マージン、例えば 5 0 mV である。

50

## 【0036】

[0043] 数式 1 により、もし  $V_{hd\_def}$  が正の数量 (positive quantity) である場合、すなわち、 $VD\_Amp > (Vpd + Vhd\_init)$  である場合、これは  $Vhd\_init < Vhd\_opt$ 、すなわち  $Vhd\_init$  が  $Vhd\_opt$  の推定値に対して低すぎる場合に対応するかもしれないことに留意されたい。この場合、数式 2 により、 $Vhd^*$  が  $Vhd\_def$  (正の数量) を  $Vhd\_init$  に加算しマージン  $Vmargin$  をプラスすることで増加されるかもしれない。一方、もし  $Vhd\_def$  が負の数量 (negative quantity) である場合、すなわち、 $VD\_Amp < (Vpd + Vhd\_init)$  である場合、これは  $Vhd\_init > Vhd\_opt$ 、すなわち  $Vhd\_init$  が  $Vhd\_opt$  の推定値に対して高すぎる場合に対応するかもしれない。この場合、数式 2 により、 $Vhd\_def$  (負の数量) を  $Vhd\_init$  に加算しマージン  $Vmargin$  をプラスすることによって、 $Vhd^*$  が減少されるかもしれない。

10

## 【0037】

[0044] いくつかの場合において、 $Vhd\_init > Vgd\_opt$  は、ブロック 520 の検出が行われた時低い  $HR\_reach$  という結果になり、それゆえ、これらの場合方法 500 はブロック 530、540 に進まないかもしれない。

## 【0038】

[0045] 以上に記載された動作に従って、 $Vhd^*$  は、高いと検出される  $HR\_reach$  に対応する時間に更新され、従って  $Vhd^*$  は、 $HR\_reach$  が高いと検出された時に必要とされるヘッドルームに対応する値に更新されるかもしれないことが認識されるだろう。

20

## 【0039】

[0046] ある例示的な実施形態において、ブロック 540 における  $Vhd^*$  の更新に続いて、 $Vhd^*$  のさらなる更新は行われる必要が無く、ETシステム 400 は  $Vhd^*$  の当該更新された値で機能するかもしれない。代替の例示的な実施形態 (図示されない)において、 $Vhd^*$  の追加の更新がブロック 540 に従ってさらに行われてもよい。例えば、ブロック 540 後の固定時間間隔および / または高から低への  $HR\_reach$  の推移に続いてある代替の例示的な実施形態による方法は  $HR\_reach$  が高いと検出される次の瞬間を待つためにブロック 520 に戻ってもよい。このやり方によって、 $Vhd^*$  は必要に応じて複数回更新されてもよい。そのような代替の例示的な実施形態は、本開示の範囲内であると熟考される。

30

## 【0040】

[0047] 図 4 に戻ると、動的ヘッドルーム生成ブロック 420 が、例えば、方法 500 がブロック 510、520、または 530 を実行している時、 $Vhd\_init$  に対応する  $Vhd^*$  の値を最初に出力するだろう。続いて、高い  $HR\_reach$  を検出するのに応答して、 $Vhd^*$  は上記の数式 1 および 2 に従って更新されてもよく、 $Vhd^*$  の当該更新された値はそののち、例えば方法 500 がブロック 540 に到達した後で、アサートされてもよい。

30

## 【0041】

[0048] 図 4 に示されるように、 $Vhd^*$  は  $Vtarget$  と  $Ven$  の両方の生成に利用されることに留意されたい。特に、 $Vhd^*$  は、410a または  $Vtarget$  を直接的に生成するために加算器 410 によって  $Vpd$  に加算されてもよく、410a または  $Vtarget$  は  $VDD\_Amp$  の目標レベルを設定するためにブースト変換器 310 に提供される。さらに、電圧 410a または  $Vtarget$  は、 $Vok$  を生成するために比較器 330 の負 (-) 端子に提供され、 $Vok$  はイネーブル電圧  $Ven$  を導き出すためにブースト変換器 310 によって利用される (例えば、ラッチングと論理反転に続いて)。

40

## 【0042】

[0049] 図 6 および 7 は、上記の本開示の技術による例示的な動作シナリオを図示する。図 6 および 7 の動作シナリオが例証的な目的のみのために提示され、本開示の範囲を如何様にも限定するよう意図されないことに留意されたい。

50

## 【0043】

[0050]図6において、時間 $t_0$ 以前のETシステム400の初期状態が示されており、ここにおいて $V_{hd}^*$ が $V_{hd\_init}$ に初めに設定される。ある例示的な実施形態において、 $V_{hd\_init}$ は例えば400mVであってもよい。時間 $t_0$ に先立って、 $V_{hd\_init}$ はPA130.1のための十分なヘッドルームを提供し、それゆえ $HR\_reach$ は低くなるだろう。加算器410の出力410aは( $V_{pd} + V_{hd\_init}$ )に対応し、比較器330の正(+)と負(-)の端子間の差は $VDD\_Amp - (V_{pd} + V_{hd\_init})$ である。 $VDD\_Amp - (V_{pd} + V_{hd\_init})$ は $t_0$ に先立って正であると予期され、それゆえ、ブースト変換器310がオフかバイパスモードの状態で、比較器330の出力 $V_{ok}$ は高いと予期されることに留意されたい。図6にさらに示されるのは、これより以前に記載されたように、PA130.1が不十分なヘッドルームを持つという検出に応答して時間 $t_0$ における低から高への $HR\_reach$ 推移である。

10

## 【0044】

[0051]図7は $t_0$ に続いた、例えば、上記ブロック540を参照して記載されたように数式2に従って $V_{hd}^*$ が更新された後の、ETシステム400の状態を図示する。図7において、更新された $V_{hd}^*$ は $V_{hd\_init} + V_{hd\_def} + V_{margin}$ に等しい。加算器410の出力410aは、( $V_{pd} + V_{hd\_init} + V_{hd\_def} + V_{margin}$ )、または $VDD\_Amp + V_{margin}$ にそれゆえ対応するだろう。 $V_{hd\_def}$ を定義する数式1により、比較器330の正(+)と負(-)の端子間の差は $-V_{margin}$ に単純化する。 $V_{margin}$ が正の値に設定され、それゆえ $-V_{margin}$ が負の値なので、比較器330の出力は低いと予期される。この場合、ブースト変換器310によって導き出された $V_{en}$ は高くなつて、ブースト変換器310がイネーブルにされ、 $VDD\_Amp$ はそれに応じて $V_{hd\_init} + V_{hd\_def} + V_{margin} + V_{pd}$ に対応するターゲット電圧 $V_{target}$ まで引き上げられるだろう。

20

## 【0045】

[0052]図7に図示されるように、 $VDD\_Amp - V_{pd}$ の必要とされるヘッドルーム( $HR\_reach$ が高い時)を上回る $V_{margin}$ の存在が比較器330の出力 $V_{ok}$ が高から低にトグルする(そしてそれゆえ、 $V_{en}$ に低から高にトグルする)ことになるので、加法的な項(additive term) $V_{margin}$ を更新された $V_{hd}^*$ に提供することは、ブースト変換器310の時宜を得たスタートアップを有利に保証する。

30

## 【0046】

[0053]図8は本開示にしたがったETシステム400の例示的な実施形態400.1を例示し、ここにおいて動的ヘッドルーム生成ブロック420の特定の例示的な実施形態420.1が示される。図8は例証的な目的のみのために提示され、動的ヘッドルーム生成ブロックの特定の例示的な実施形態に対する本開示の範囲を限定するよう意図されないことに留意されたい。

## 【0047】

[0054]図8において、動的ヘッドルーム生成ブロック420.1はANDゲート820とクロック信号CLKによって駆動されるカウンタ810を含む。カウンタ810は、例えば、 $V_{hd\_init}$ に対応する値に初期化されるNビットレジスタ(図示されない)を含んでもよい。ANDゲート820の出力ENが低い時、カウンタ810はディスエーブルにされ、カウンタ出力 $V_{hd}^*$ は $V_{hd\_init}$ で一定である。ANDゲート820の出力ENが高いと検出されると、カウンタ810はイネーブルにされ、これによってNビットレジスタ値をCLKの立ち上がり(rising)(または代替的に、立ち下がり)エッジごとにインクリメントすることを始める。ENが低い時、カウンタ810はディスエーブルにされ、これによって、そのレジスタコンテンツをインクリメントすることを止める。ある例示的な実施形態において、デジタルアナログ変換器(DAC)815はカウンタ810のデジタル出力をアナログ信号に変換するためにカウンタ810の出力に設け

40

50

られてもよい。

#### 【0048】

[0055] E T システム 400.1 における動的ヘッドルーム生成ブロック 420.1 のリアルタイム動作は以下のように記載されるかもしれない。初期状態において、HR\_reach は低く、Vok は高い。これは PA130.1 が十分なヘッドルームで動作している状態に対応し、VDD\_Amp は Vpd + Vhd \* より大きい。AND ゲート 820 の出力 EN はそれゆえ低く、それゆえ、Vhd \* が VHD\_init の初期値に等しい状態で、カウンタ 810 はディスエーブルにされる。

#### 【0049】

[0056] 第 2 の状態において、HR\_reach は高いと検出されて、PA130.1 は十分なヘッドルームを持たないと示す。HR\_reach と Vok がともに高いので、AND ゲート 820 の出力 EN も高く、カウンタ 810 がそれに従ってイネーブルにされる。<sup>10</sup> EN が高い間、カウンタ 810 は CLK の毎立ち上がりエッジでそのレジスタ値を連続的にインクリメントする。EN が低く推移するまでインクリメントは続き、その時点でカウンタ 810 はディスエーブルにされる。例えば Vok の高から低への推移に応答して EN は低に推移してもよく、これは次々に (in turn)、Vhd \* における連続的なインクリメントのために、例えば Vhd \* + Vpd または電圧 410a が VDD\_Amp をいくらかのマージン分を最終的に超過することによって生じてもよいことに留意されたい。一旦カウンタ 810 がディスエーブルにされると、カウンタ 810 における N ビットレジスタのその時存在する値は保存され、当該更新されたヘッドルーム電圧 Vhd \* <sup>20</sup> としてその後保持される。

#### 【0050】

[0057] 図 9 は、本開示にしたがった方法 900 の例示的な実施形態を例示する。図 9 は例証的な目的のみのために提示され、示された方法の特定の実施に対する本開示の範囲を限定するよう意図されないことに留意されたい。

#### 【0051】

図 9において、ブロック 910 では、出力電圧を生成するために入力電圧を增幅するように構成された電力増幅器を供給するために、トラッキング供給電圧は増幅器を用いて生成される。

#### 【0052】

[0059] ブロック 920 では、増幅器供給電圧は増幅器のために生成され、ここにおいて増幅器供給電圧はブースト供給電圧よりも高くなるように構成可能である。<sup>30</sup>

#### 【0053】

[0060] ブロック 930 では、増幅器供給電圧は、ヘッドルーム電圧と増幅器供給電圧よりも大きいトラッキング供給電圧のピークとの合計に応答してブースト供給電圧よりも高くなるように構成される。

#### 【0054】

[0061] ブロック 940 では、ヘッドルーム到達電圧、例えば、HR\_reach の検出に応答して、ヘッドルーム電圧は初期値から更新される。例示的な実施形態において、HR\_reach 信号は増幅器が不十分なヘッドルームで動作しているかどうか示す。<sup>40</sup>

#### 【0055】

[0062] 本明細書および特許請求の範囲において、要素が別の要素に「接続される」または「結合される」として言及される場合、それは他の要素に直接結合または結合されることができ、あるいは介在する要素が存在しうることが理解されるだろう。対照的に、要素が別の要素に「直接接続される」または「直接結合される」として言及される場合、介在する要素は、存在しない。さらに、要素が単に別の要素に「結合される」として言及される場合、そのような要素の間に低抵抗のパスが存在しうる、または存在しない可能性がある一方で、要素が別の要素に「電気的に結合される」として言及される場合、低抵抗のパスがそのような要素の間に存在することを示す。

#### 【0056】

10

20

30

40

50

[0063]当業者は、情報および信号が様々な異なる技術ならびに技法のいずれかを使用して表されうることを理解するだろう。例えば、上記の説明全体にわたって参照されうるデータ、命令、コマンド、情報、信号、ビット、シンボル、およびチップは、電圧、電流、電磁波、磁場または磁性粒子、光場または光粒子、あるいはそれらの任意の組み合わせによって表されうる。

#### 【0057】

[0064]当業者はさらに、本明細書において開示される例示的な態様に関連して説明される様々な例証的な論理ブロック、モジュール、回路、およびアルゴリズムステップが電子ハードウェア、コンピュータソフトウェアまたは両方の組み合わせとして実装されうることを認識するだろう。ハードウェア及びソフトウェアのこの互換性を明確に例示するために、様々な例証的な構成要素、ブロック、モジュール、回路、及びステップは、概してこれらの機能の観点から上記に説明された。このような機能が、ハードウェアとして実装されるか、あるいはソフトウェアとして実装されるかは、特定のアプリケーション及びシステム全体に課せられる設計制約に依存する。当業者は、各特定のアプリケーションのために、説明された機能性を様々な方法で実装しうるが、そのような実装の決定は、発明の例示的な態様の範囲から逸脱を引き起こしていると解釈されるべきでない。

10

#### 【0058】

[0065]本明細書において開示される例示的な態様に関連して説明される様々な例証的な論理ブロック、モジュール、および回路は、汎用プロセッサ、デジタル信号プロセッサ(DSP)、特定用途向け集積回路(ASIC)、フィールドプログラマブルゲートアレイ(FPGA)または他のプログラマブル論理デバイス、離散ゲートまたはトランジスタ論理、離散ハードウェアコンポーネント、あるいは本明細書において説明される機能を遂行するよう設計されるそれらの任意の組み合わせで実装または遂行されうる。汎用プロセッサは、マイクロプロセッサでありうるが、代替として、プロセッサは、任意の従来のプロセッサ、コントローラ、マイクロコントローラ、またはストートマシンでありうる。プロセッサはまた、計算デバイスの組み合わせ、例えば、DSPおよびマイクロプロセッサ、複数のマイクロプロセッサ、DSPコアと連携した1つまたは複数のマイクロプロセッサ、または任意の他のそのような構成の組み合わせとして実装されうる。

20

#### 【0059】

[0066]本明細書において開示される例示的な態様に関連して説明される方法またはアルゴリズムのステップは、直接ハードウェアにおいて、プロセッサによって実行されるソフトウェアモジュールにおいて、またはこれら2つの組み合わせにおいて、具現化されうる。ソフトウェアモジュールは、ランダムアクセスメモリ(RAM)、フラッシュメモリ、読み出し専用メモリ(ROM)、電気的プログラマブルROM(E PROM)、電気的消去可能プログラマブルROM(EEPROM(登録商標))、レジスタ、ハードディスク、リムーバルディスク、CD-ROM、または当該技術分野において周知である任意の他の形状の記憶媒体内において存在しうる。例示的な記憶媒体は、プロセッサが記憶媒体から情報を読み取り、記憶媒体に情報を書き込むことができるよう、プロセッサに結合される。代替において、記憶媒体は、プロセッサと一体化されうる。プロセッサおよび記憶媒体は、ASIC内において存在しうる。ASICは、ユーザ端末内において存在しうる。代替として、プロセッサおよび記憶媒体は、ユーザ端末内に個別構成要素として存在しうる。

30

#### 【0060】

[0067]1つまたは複数の例示的な態様において、説明される機能は、ハードウェア、ソフトウェア、ファームウェア、またはそれらの任意の組み合わせ内において実装されうる。ソフトウェア内において実装される場合、機能は、コンピュータ可読媒体上における1つまたは複数の命令またはコードとして記憶または送信されうる。コンピュータ可読媒体は、1つの場所から別の場所へのコンピュータプログラムの転送を容易にする任意の媒体を含むコンピュータ記憶媒体および通信媒体の両方を含む。記憶媒体は、コンピュータによってアクセスされることができる任意の利用可能な媒体でありうる。限定ではなく例と

40

50

して、そのようなコンピュータ可読媒体は、RAM、ROM、EEPROM（登録商標）、CD-ROMまたは他の光学ディスク記憶装置、磁気ディスク記憶装置または他の磁気記憶デバイス、あるいは命令もしくはデータ構造の形で所望のプログラムコードを搬送または記憶するよう使用されることができ、コンピュータによってアクセスされることができる任意の他の媒体を備えることができる。また、任意の接続は、厳密にはコンピュータ可読媒体と称される。例えば、ソフトウェアが、同軸ケーブル、光ファイバケーブル、ツイストペア、デジタル加入者回線（DSL）、または赤外線、無線、およびマイクロ波のようなワイヤレス技術を使用して、ウェブサイト、サーバ、または他の遠隔ソースから送信される場合、同軸ケーブル、光ファイバケーブル、ツイストペア、DSL、または赤外線、無線、およびマイクロ波のようなワイヤレス技術は、媒体の定義に含まれる。本明細書で使用される場合、ディスク（disk）およびディスク（disc）は、コンパクトディスク（CD）、レーザーディスク（登録商標）、光ディスク、デジタル多用途ディスク（DVD）、フロッピー（登録商標）ディスク、およびブルーレイディスクを含み、ここでディスク（disk）は通常、磁気的にデータを再生し、ディスク（disc）は、レーザーを用いて光学的にデータを再生する。上記の組み合わせはまた、コンピュータ可読媒体の範囲内に含まれるべきである。

10

20

## 【0061】

[0068]開示される例示的な態様の先の説明は、いかなる当業者であっても、本発明の製造または使用を可能にするよう提供される。これらの例示的な態様に対する様々な修正は、当業者には容易に明らかとなり、本明細書において定義される包括的な原理は、本発明の精神または範囲から逸脱することなく他の例示的な態様に適用されうる。したがって、本開示は、本明細書において提示される例示的な態様に限定されるよう意図されず、本明細書において開示される原理および新規な特徴と一致する最も広い範囲が付与されるべきである。

【図1】

図1

FIG 1

【図2】

図2

FIG 2

【図3】

図3

FIG 3

【図4】

図4

FIG 4

【図5】

図5

FIG 5

【図6】

図6

FIG 6

【図7】

【図8】

【図9】

## 【国際調査報告】

## INTERNATIONAL SEARCH REPORT

International application No

PCT/US2014/012393

A. CLASSIFICATION OF SUBJECT MATTER

INV. H03F1/02

ADD.

According to International Patent Classification (IPC) or to both national classification and IPC

## B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)

H03F

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)

EPO-Internal, WPI Data

## C. DOCUMENTS CONSIDERED TO BE RELEVANT

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                   | Relevant to claim No. |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| A         | WO 2011/007556 A1 (PANASONIC CORP [JP]; MORIMOTO SHIGERU; ISHIDA KAORU; NAKAMURA MAKI) 20 January 2011 (2011-01-20)<br>paragraph [0051] - paragraph [0075];<br>figure 1A<br>-----    | 1-20                  |

| A         | US 2006/068830 A1 (KLOMSDORF ARMIN W [US]<br>ET AL) 30 March 2006 (2006-03-30)<br>paragraph [0030]; figure 5<br>-----                                                                | 1-20                  |

| A         | US 2010/105343 A1 (STEBBINGS KENNETH E [US] ET AL STEBBINGS KENNETH [US] ET AL)<br>29 April 2010 (2010-04-29)<br>paragraph [0013] - paragraph [0023];<br>figures 1-3<br>-----<br>-/- | 1-20                  |

Further documents are listed in the continuation of Box C.

See patent family annex.

## \* Special categories of cited documents :

- "A" document defining the general state of the art which is not considered to be of particular relevance

- "E" earlier application or patent but published on or after the international filing date

- "L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

- "O" document referring to an oral disclosure, use, exhibition or other means

- "P" document published prior to the international filing date but later than the priority date claimed

"T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

"X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

"Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art

"&" document member of the same patent family

Date of the actual completion of the international search

Date of mailing of the international search report

13 October 2014

23/10/2014

Name and mailing address of the ISA/

European Patent Office, P.B. 5818 Patentlaan 2

NL - 2280 HV Rijswijk

Tel. (+31-70) 340-2040,

Fax: (+31-70) 340-3016

Authorized officer

Lorenzo, Carlos

**INTERNATIONAL SEARCH REPORT**

|                                                   |

|---------------------------------------------------|

| International application No<br>PCT/US2014/012393 |

|---------------------------------------------------|

**C(Continuation). DOCUMENTS CONSIDERED TO BE RELEVANT**

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                 | Relevant to claim No. |

|-----------|------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| A         | WO 02/37672 A2 (LEWYN CONSULTING INC [US])<br>10 May 2002 (2002-05-10)<br>page 11, line 1 - page 13, line 33; figure<br>2<br>----- | 1-20                  |

1

**INTERNATIONAL SEARCH REPORT**

Information on patent family members

|                                                   |

|---------------------------------------------------|

| International application No<br>PCT/US2014/012393 |

|---------------------------------------------------|

| Patent document cited in search report | Publication date | Patent family member(s) |                                                                                                                                                        |                                                                                                                            | Publication date |

|----------------------------------------|------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|------------------|

| WO 2011007556                          | A1               | 20-01-2011              | NONE                                                                                                                                                   |                                                                                                                            |                  |

| US 2006068830                          | A1               | 30-03-2006              | BR P10516733 A<br>CN 101032093 A<br>EP 1797647 A1<br>KR 20070058552 A<br>US 2006068830 A1<br>WO 2006049669 A1                                          | 23-09-2008<br>05-09-2007<br>20-06-2007<br>08-06-2007<br>30-03-2006<br>11-05-2006                                           |                  |

| US 2010105343                          | A1               | 29-04-2010              | NONE                                                                                                                                                   |                                                                                                                            |                  |

| WO 0237672                             | A2               | 10-05-2002              | AT 262748 T<br>AU 2011402 A<br>CA 2425668 A1<br>DE 60102486 D1<br>DE 60102486 T2<br>EP 1330871 A2<br>JP 2004513553 A<br>US 6417736 B1<br>WO 0237672 A2 | 15-04-2004<br>15-05-2002<br>10-05-2002<br>29-04-2004<br>24-02-2005<br>30-07-2003<br>30-04-2004<br>09-07-2002<br>10-05-2002 |                  |

---

フロントページの続き

(81)指定国 AP(BW,GH,GM,KE,LR,LS,MW,MZ,NA,RW,SD,SL,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,RU,TJ,TM),EP(AL,AT,BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,HR,HU,IE,IS,IT,LT,LU,LV,MC,MK,MT,NL,NO,PL,PT,RO,R,S,SE,SI,SK,SM,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,KM,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AO,AT,AU,AZ,BA,BB,BG,BH,BN,BR,BW,BY,BZ,CA,CH,CL,CN,CO,CR,CU,CZ,DE,DK,DM,DO,DZ,EC,EE,EG,ES,FI,GB,GD,GE,GH,GM,GT,HN,H,R,HU,ID,IL,IN,IR,IS,JP,KE,KG,KN,KP,KR,KZ,LA,LC,LK,LR,LS,LT,LU,LY,MA,MD,ME,MG,MK,MN,MW,MX,MY,MZ,NA,NG,NI,NO,NZ,OM,PA,PE,PG,PH,PL,PT,QA,RO,RS,RU,RW,SA,SC,SD,SE,SG,SK,SL,SM,ST,SV,SY,TH,TJ,TM,TN,TR,TT,TZ,UA,UG,US

(72)発明者 マセ、レナート・カール・アクセル

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775、クワアルコム・インコーポレイテッド気付

(72)発明者 リ、ベンフェイ

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775、クワアルコム・インコーポレイテッド気付

(72)発明者 シ、ソン

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775、クワアルコム・インコーポレイテッド気付

(72)発明者 シ、ユンフェイ

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775、クワアルコム・インコーポレイテッド気付

(72)発明者 ルツコウスキ、ジョセフ

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775、クワアルコム・インコーポレイテッド気付

F ターム(参考) 5J500 AA01 AA41 AC36 AC85 AF10 AH39 AK02 AK33 AK34 AK35

AK49 AM15 AM20 AS14 AT01 RG01